Page 1

( ●) Preliminary Specification

( ) Final Specification

P08##-##

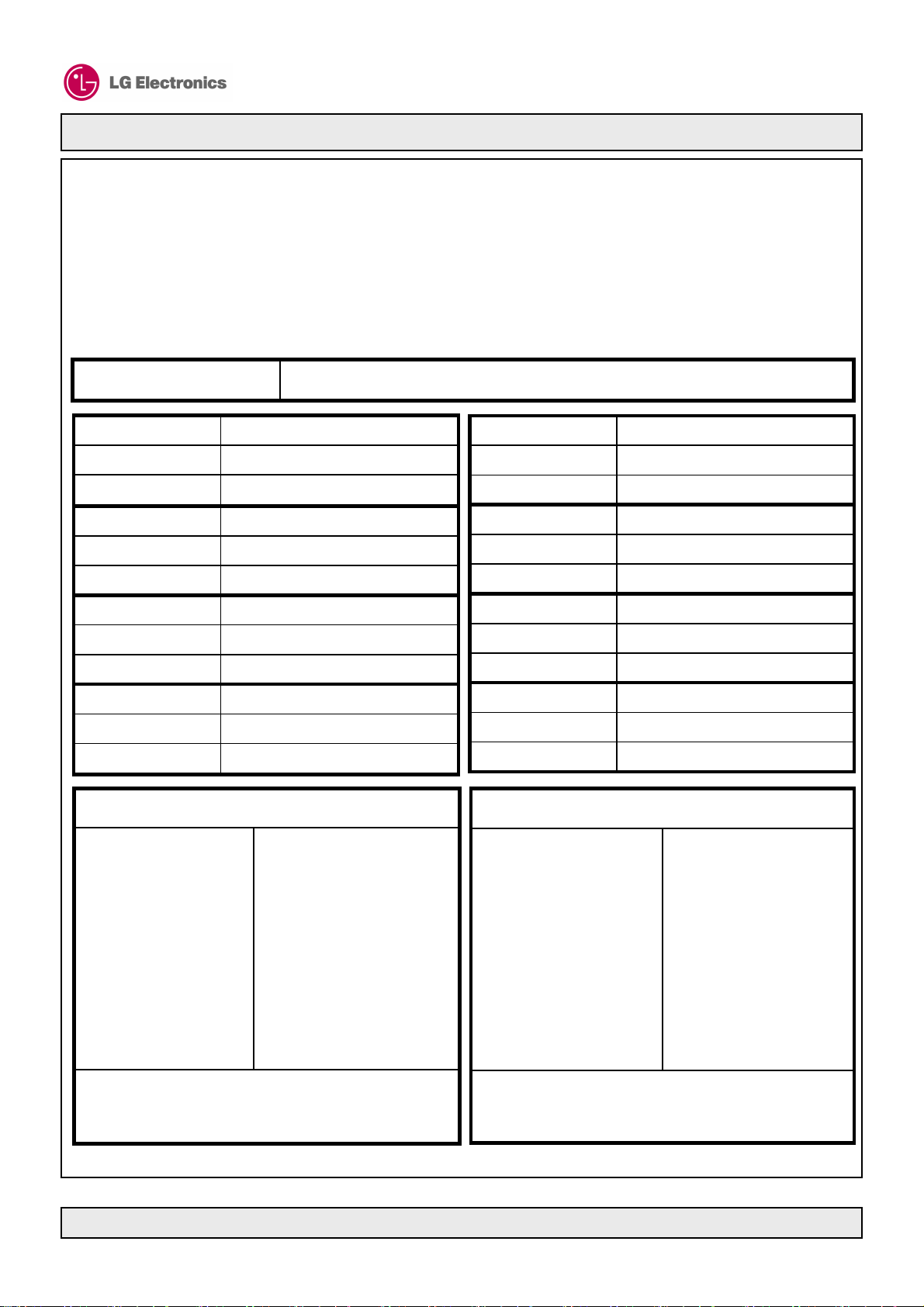

Product Specification of PDP Module

CUSTOMER

APPROVAL

SPECIFICATION

PDP50T4 (50” HD PDP MODULE)Title

Customer

Model Name

Part No.

Customer

Model Name

Part No.

Customer

Model Name

Part No.

PDP50T4T010.ASBBBModel Name

EAJ61908544Part No.

Signature / Date

-Customer

Supplier

Model Name

Part No.

Supplier

Model Name

Part No.

Supplier

Model Name

Part No.

PDP DivisionSupplier

PDP50T4T010.ASBBBModel Name

EAJ61908544Part No.

Signature / Date

Approved by

Please return 1 copy for our confirmation

With your signature

Confidential

Approved by

PDP Division LG Electronics Inc.

Page 1/44Revision No. 0.0 30/Mar./ 2012

Page 2

Product Specification of PDP Module

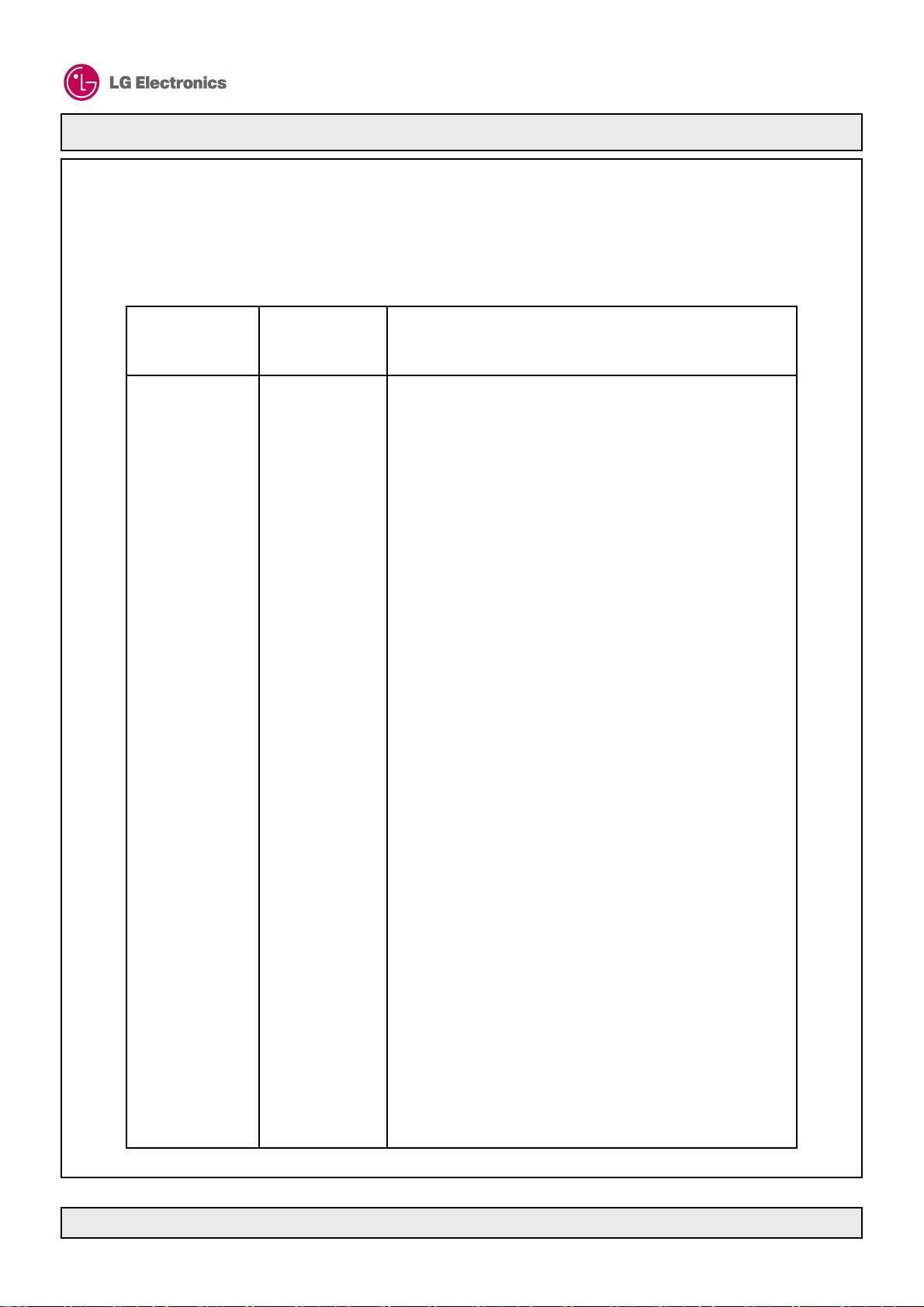

Record of Revisions

P08##-##

Revision

No.

Effective

Comments

Date

- Established2013.03.300.0

Confidential

Page 2/44Revision No. 0.0 30/Mar./ 2012

Page 3

Product Specification of PDP Module

CONTENTS

P08##-##

4WARNINGS AND CAUTIONS0.

Warning

Caution

Description

Applications

Electrical Interface of Plasma Display

General Specifications

Block Diagram

Absolute Power Specifications

Input Power Specifications

Power Supply Sequence

LVDS Signal and LVDS Receiver

Input Signal Timing Diagram

Input Signal Timing Specification

I2C Timing Diagram & Specifications

Mechanical Characteristic Specifications

Vibration and Drop Specifications

Recommended Environmental Conditions

4

5

8GENERAL DESCRIPTION1.

8

8

9

9

10

11ELECTRICAL SPECIFICATIONS2.

11

11

13

14

18

19

27

28ELECTRO OPTICAL SPECIFICATIONS3.

28 Electro Optical characteristic Specifications (60Hz)

29MECHANICAL & ENVIRONMENTAL SPECIFICATIONS4.

29

29

29

Image Sticking

Secular change in brightness

Cause of deterioration in brightness

Practical value for Image sticking

Proposed measures taken to relieve image sticking

Front View

Rear View

Confidential

30IMAGE STICKING CHARACTERISTICS5.

30

30

30

30

31

32OUTLINE DRAWING6.

32

33

34LABEL7.

36PACKING8.

38PSU SPECIFICATION9.

Page 3/44Revision No. 0.0 30/Mar./ 2012

Page 4

P08##-##

Product Specification of PDP Module

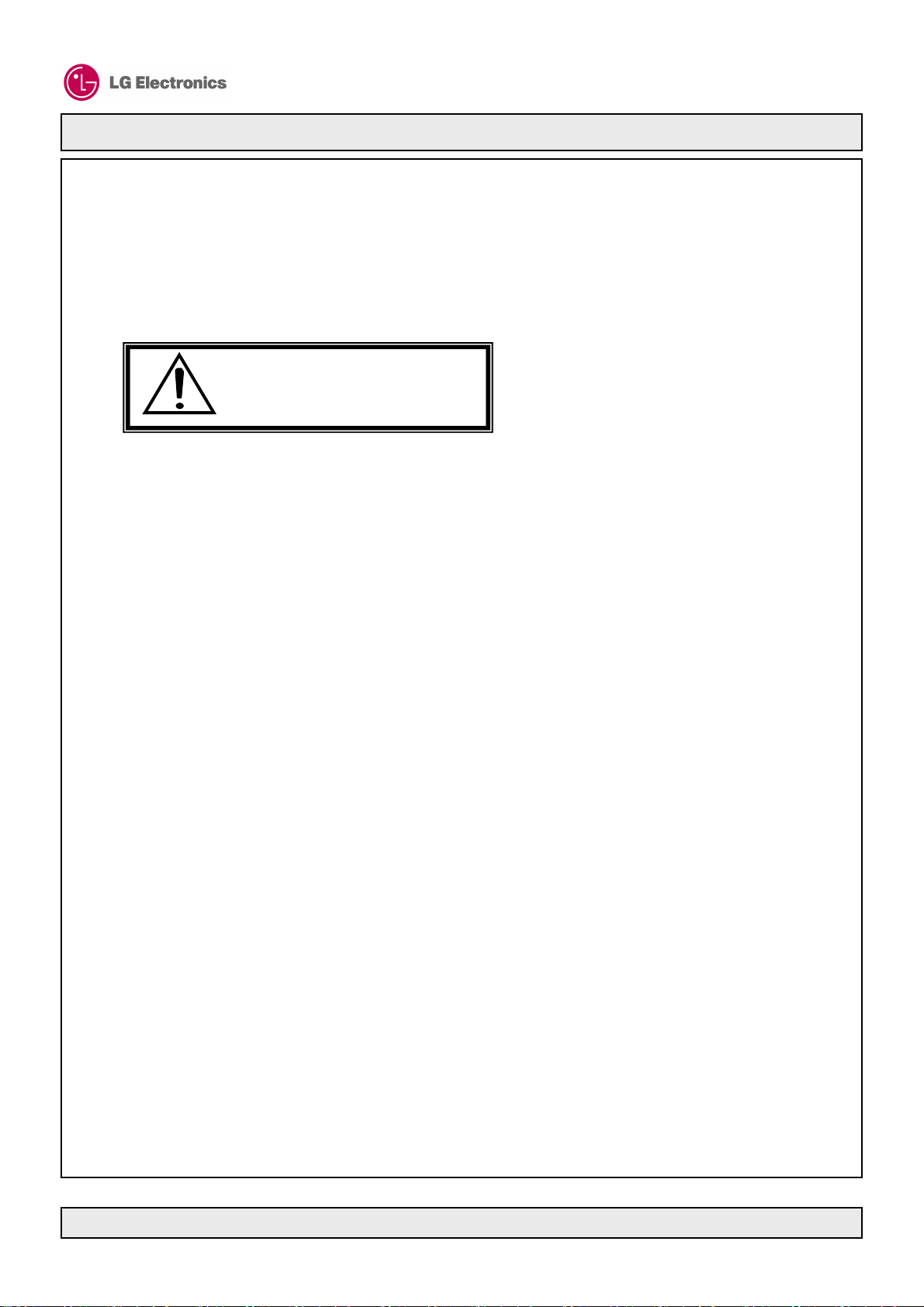

0. Warnings and Cautions

WARNING indicates hazards that may lead to death or injury if ignored.

CAUTION indicates hazards that may lead to injury or damage to property if ignored.

WARNING

1) This product uses a high voltage (450 V max.). Do not touch the circuitry of this product with your hands when

power is supplied to the product or immediately after turning off the power. Be sure to confirm that the voltage

is dropped to a sufficiently low level.

2) Do not supply a voltage higher than that specified to this product. This may damage the product and may cause a

fire.

3) Do not use this product in locations where the humidity is extremely high, where it may be splashed with water,

or where flammable materials surround it. Do not install or use the product in a location that does no satisfy the

specified environmental conditions. This may damage the product and may cause a fire.

4) If a foreign substance (such as water, metal, or liquid) gets inside the product, immediately turn off the power.

Continuing to use the products it may cause fire or electric shock.

5) If the product emits smoke, an abnormal smell, or makes an abnormal sound, immediately turn off the power. If

noting is displayed or if the display goes out during use, immediately turn off the power. Continuing to use the

product as it is may cause fire or electric shock.

6) Do not disconnect or connect the connector while power to the product is on. It takes some time for the voltage

to drop to a sufficiently low level after the power has been turned off. Confirm that the voltage has dropped to a

safe level before disconnecting or connecting the connector. Otherwise, this may cause fire, electric shock, or

malfunction.

7) Do not pull out or insert the power cable from/to an outlet with wet hands. It may cause electric shock.

8) Do not damage or modify the power cable. It may cause fire or electric shock.

9) If the power cable is damaged, or if the connector is loose, do not use the product; otherwise, this can lead to fire

or electric shock.

10) If the power connector or the connector of the power cable becomes dirty or dusty, wipe it with a dry cloth.

Otherwise, this can lead to fire.

Confidential

Page 4/44Revision No. 0.0 30/Mar./ 2012

Page 5

P08##-##

Product Specification of PDP Module

CAUTION

General

1) Do not place this product in a location that is subject to heavy vibration, or on an unstable surface such as an

inclined surface. The product may fall off or fall over, causing injuries.

2) When moving the product, be sure to turn off the power and disconnect all the cables. While moving the

product, watch your step. The product may be dropped or fall, leading to injuries of electric shock.

3) Do not place this product in a location that is subject to heavy vibration, or on an unstable surface such as an

inclined surface. The product may fall off or fall over, causing injuries.

4) Before disconnecting cable from the product, be sure to turn off the power. Be sure to hold the connector when

disconnecting cables. Pulling a cable with excessive force may cause the core of the cable to be exposed or

break the cable, and this can lead to fire or electric shock.

5) This product should be moved by two or more persons. If one person attempts to carry this product alone, he/she

may be injured.

6) This product contains glass. The glass may break, causing injuries, if shock, vibration, heat, or distortion is

applied to the product.

7) The temperature of the glass surface of the display may rise to 80°C or more depending on the conditions of use.

If you touch the glass inadvertently, you may be burned.

8) Do not poke or strike the glass surface of the display with a hard object. The glass may break or be scratched. If

the glass breaks, you may be injured.

9) If you glass surface of the display breaks or is scratched, do not touch the broken pieces or the scratches with

bare hands. You may be injured.

10) Do not place an object on the glass surface of the display. The glass may break or be scratched.

Design

1) This product may be damaged if it is subject to excessive stresses (such as excessive voltage, current, or

temperature). The absolute maximum ratings specify the limits of these stresses, and system design must ensure

that none of the absolute maximum ratings are exceeded.

2) The recommended operating conditions are conditions in which the normal operation of this product is

guaranteed. All the rated values of the electrical specifications are guaranteed within these conditions. Always

use the product within the range of the recommended operating conditions. Otherwise, the reliability of the

product may be degraded. Use of the product with a combination of parameters, conditions, or logic not

specified in the specifications of this product is not guaranteed. If intending to use the product in such a way, be

sure to consult LGE in advance.

3) This product emits near infrared rays (800 to 1000nm) that may cause the remote controllers of other electric

products to malfunction. To avoid this, use an infrared absorption filter and thoroughly evaluate the system and

environment.

Confidential

Page 5/44Revision No. 0.0 30/Mar./ 2012

Page 6

P08##-##

Product Specification of PDP Module

Design (continued)

4) This product uses high-voltage switching and a high –speed clock. A system using this product should be

designed so that it does not affect the other systems, and should be thoroughly evaluated.

5) The materials which contain sulfur are forbidden to use, because they may damage PDP module.

6) This product has a glass display surface. Design your system so that excessive shock and load are not applied to

the glass. Exercise care that the vent at the corner of the glass panel is not damaged. If the glass panel or vent is

damaged, the product is inoperable.

7) There are some exposed components on the rear panel of this product. Touching these components may cause an

electric shock.

8) This product uses a high voltage. Design your system so that any residual voltage in this product is dissipated

quickly when power is turned off, observing the specifications.

9) This product uses heat-emitting components. Take the heat emitted by these components into consideration

when designing your system. If the product is used outside the specified temperature range, it may malfunction.

10) This product uses a high voltage and, because of its compact design, components are densely mounted on the

circuit board. If dust collects on these components, it can cause short-circuiting between the pins of the

components and moisture can cause the insulation between the components to break down, causing the product

to malfunction.

11) Regulations and standards on safety and electromagnetic interference differ depending on the country. Design

your system in compliance with the regulations and standards of the country for which your system is intended.

12) To obtain approval under certain safety standards (such as UL and EN), a filter that passes a shock test must be

fitted over the glass surface of the finished product. In addition, it must be confirmed that the level of UV

emissions is within the range specified by such standards.

13) If this product is used as a display board to display a static image, “image sticking” occurs. This means that the

luminance of areas of the display that remain lit for a long time drops compared with the luminance of areas that

are lit for a shorter time, causing uneven luminance across the display. The degree to which this occurs is in

proportion to the luminance at which the display is used. To prevent this phenomenon, therefore, avoid static

images as much as possible and design your system so that it is used at a low luminance, by reducing signal level

difference between bright area and less bright area through signal processing.

14) In case of AC PDP driving mechanism, Because the brightness of output is not always proportional to input

signals. Therefore the non-linearity of gray can occasionally be observed in certain gray levels as well as

Contour and Error Diffusion Noise can be appeared when a dark picture is on the screen especially. These are

phenomena that can be observed on the PDP driving mechanism. With simple adjustment to picture brightness

control, these can be reduced considerably.

15) Because of the need to control the power consumption on the PDP driving mechanism, the APL (Average

Picture Level) mode was equipped. Thus, as the picture on the screen changes, there can be slightly switched in

brightness. This also is a phenomenon that can be observed on the PDP driving mechanism.

16) This product is designed to LGE’s “Standard” quality grade. If you wish to use the product for applications

outside the scope of the “Standard” quality grade, be sure to consult LGE in advance to assess the technological

feasibility before starting to design your system.

Confidential

Page 6/44Revision No. 0.0 30/Mar./ 2012

Page 7

P08##-##

Product Specification of PDP Module

USE

1) Because this product uses a high voltage, connecting or disconnecting the connectors while power is supplied to

the product may cause malfunctioning. Never connect or disconnect the connectors while the power is on.

Immediately after power has been turned off, a residual voltage remains in the product. Be sure to confirm that

the voltage has dropped to a sufficiently low level.

2) Watching the display for a long time can tire the eyes. Take a break at appropriate intervals.

3) PDP ’s brightness and contrast ratio is lower than that of the CRT. The picture is dimmer with surrounding light

and better for viewing in dark condition.

4) Do not cover or wrap the product with a cloth or other covering while power is supplied to the product.

5) Before turning on power to the product, check the wiring of the product and confirm that the supply voltage is

within the rated voltage range. If the wiring is wrong or if a voltage outside the rated range is applied, the

product may malfunction or be damaged.

6) Do not store this product in a location where temperature and humidity are high. This may cause the product to

malfunction. Because this product uses a discharge phenomenon, it may take time to light (operation may be

delayed) when the product is used after it has been stored for a long time. In this case, it is recommended to light

all cells for about 2hours (aging).

7) If the glass surface of the display becomes dirty, wipe it with a soft cloth moistened with a neutral detergent. Do

not use acidic or alkaline liquids, or organic solvents.

8) Do not tilt or turn upside down while the module package is carried, the product may be damaged.

9) This product is made from various materials such as glass, metal, and plastic. When discarding it, be sure to

contact a professional waste disposal operator.

Others

1) If your system requires the user to observe any particular precautions, in addition to the above warnings and

cautions, include such caution and warning statements in the manual for your system.

2) If you have any questions concerning design, such as on housing, storage, or operating environment, consult

LGE in advance.

Confidential

Page 7/44Revision No. 0.0 30/Mar./ 2012

Page 8

Product Specification of PDP Module

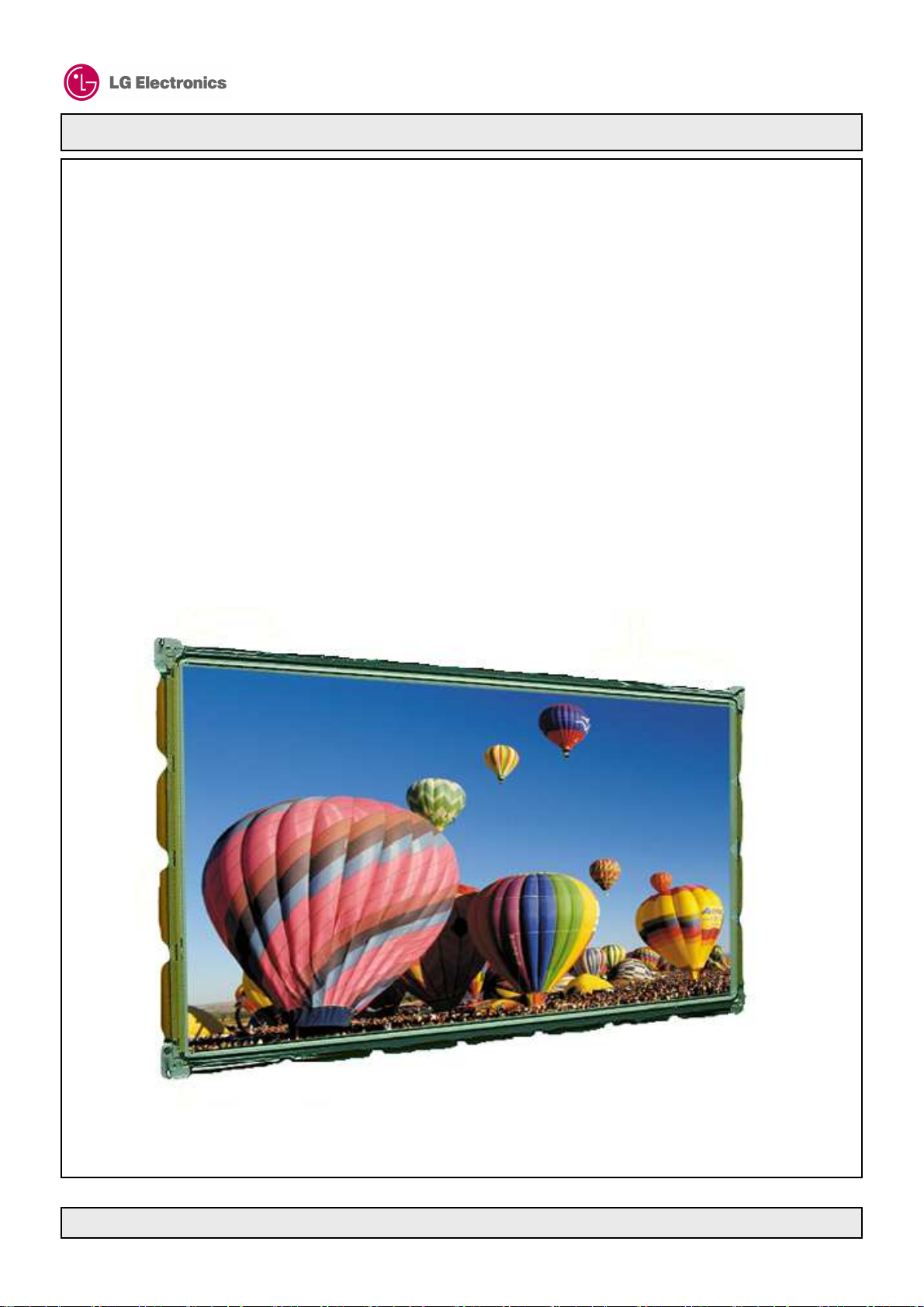

1. GENERAL DESCRIPTION

DESCRIPTION

The PDP50T4#### is a 50-inch 16:9 color plasma display module with resolution of 1024(H) × 768(V) pixels.

APPLICATIONS

Public information display

Video conference systems

Education and training systems

P08##-##

Confidential

(Image)

Page 8/44Revision No. 0.0 30/Mar./ 2012

Page 9

Product Specification of PDP Module

ELECTRICAL INTERFACE OF PLASMA DISPLAY

The PDP50T4#### requires only 8/12bits of digital video signals for each RGB color.

In addition to the video signals, five different DC voltages are required to operate the display.

GENERAL SPECFICATIONS

P08##-##

Model Name

Number of Pixels

Pixel Pitch

Cell Pitch

Display Area

Outline Dimension

Pixel Type

Number of Gradations

PDP50T4#### ( 50T4 Model )

1024(H) X 768(V) (1pixel=3 RGB cells)

1080 ㎛ (H) X 810 ㎛ (V)

360 ㎛ (H) X 810 ㎛ (V)

1105.92(H) X 622.08(V) ±0.5 (mm)

1156 ±1.5 (H) X 677.6 ±1 (V) X 37.9(D) ±1.5 (mm)

RGB Closed (Well) type

10bit : (R)1024 X (G)1024 X (B)1024 (1.07billion Color)

8bit : (R)256 X (G)256 X (B)256 (16.78 Million Color)

Weight

Glass filter 14.65±0.5 (Kg) : Net

Glass filter 250.2±5 (Kg) : Gross

Aspect Ratio

Power Consumption

16:9

Max. 300 W (Full-White)

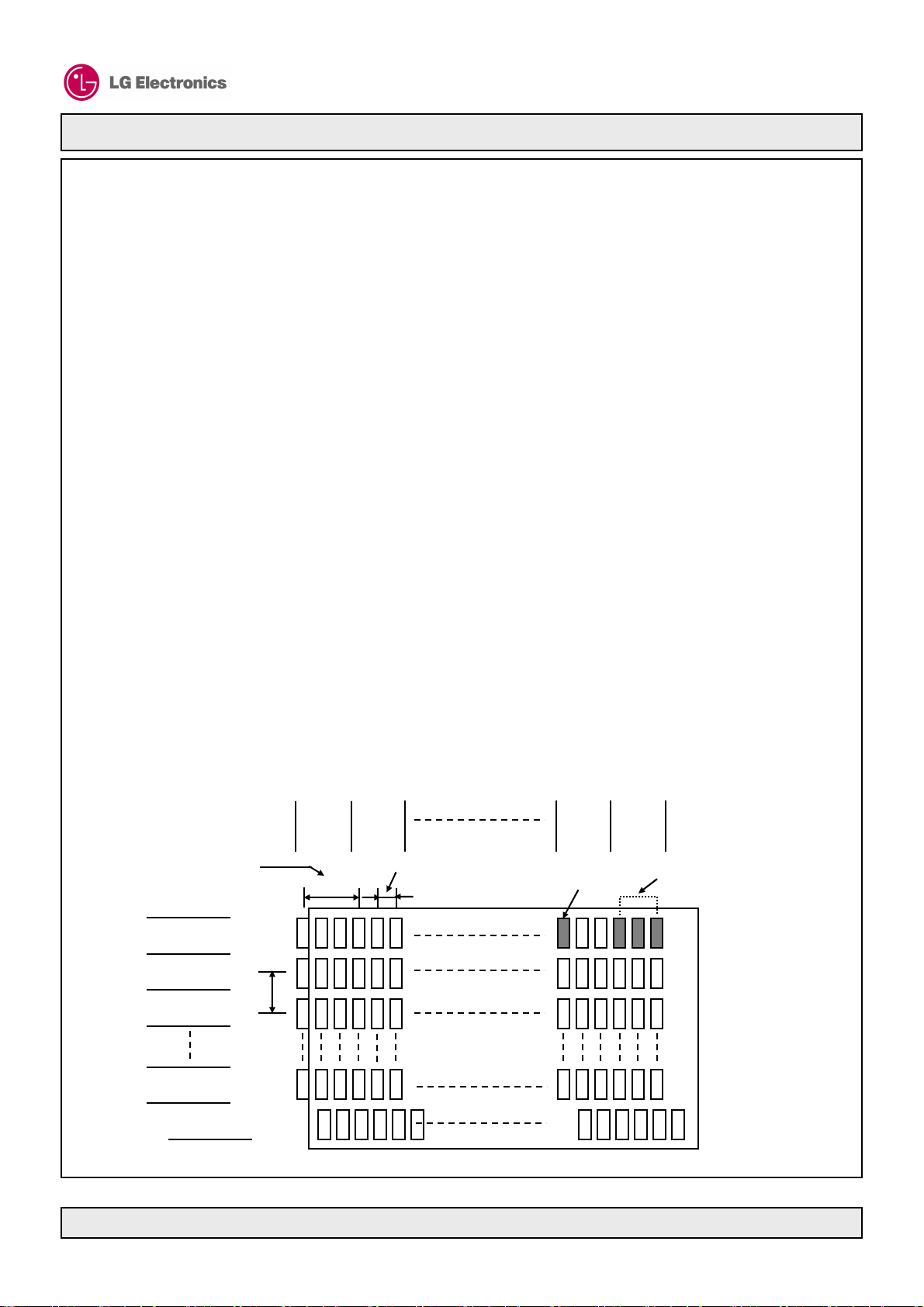

Display Dot Diagram

Pixel Pitch (width)

1st pixel

row

2nd pixel

row

3rd pixel

row

767th pixel

row

768th pixel

row

1st

pixel

column

R G B G BRR G B G BRR

1.08 ㎜

G B G BRR

G B G BRR

2nd

pixel

column

Cell pitch

R: 0. 36 ㎜

G: 0. 36 ㎜

B: 0. 36 ㎜

1023th

pixel

column

cell

G B G BRR

G B G BRR

1024th

pixel

column

pixel

Pitch (height)

0.81 ㎜

G B G BRR

G B G BRR

G B G BRR

G B G BRR

Confidential

Page 9/44Revision No. 0.0 30/Mar./ 2012

Page 10

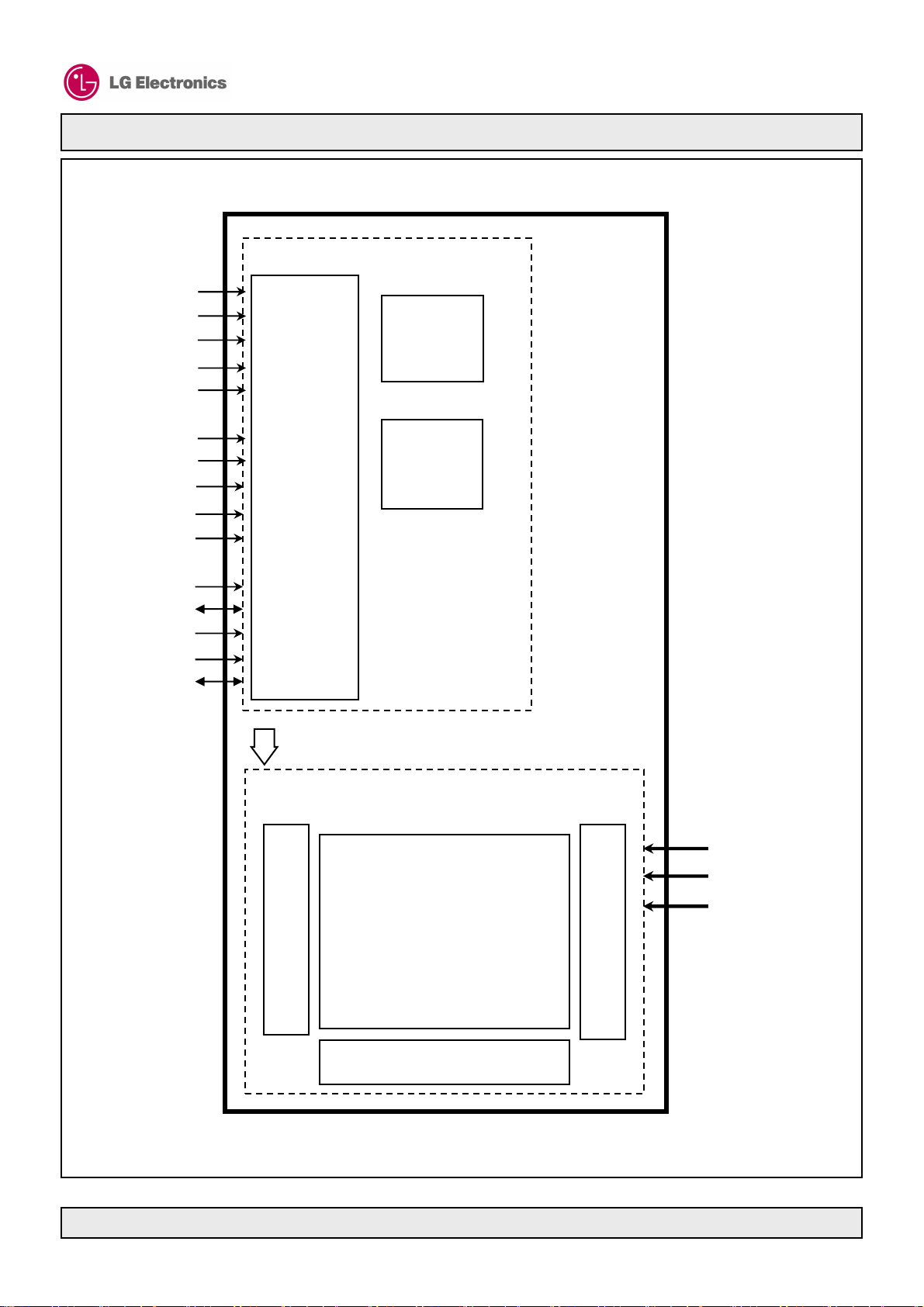

BLOCK DIAGRAM

put

D

V

(

L

RCLK1+/ -

In

S

RA1+/ RB1+/ -

RC1+/ -

RD1+/ -

)

P08##-##

Product Specification of PDP Module

Controller

Memory

Controller

Input

Interface

Controller

RA3+/ RB3+/ -

RC3+/ -

RCLK3+/ -

RD3+/ -

DIPEN

I2C I/F

Serial D/L

UART D/L

VS_3D

Driver

Timing

Controller

Display data, Driver timing

(External Power)

Common sustain driver

Vs(200V~206V)

Va(54V~56V)

Color PDP

1024 X 768 pixels

Scan Driver

Address Driver

Applied Voltage is set by input voltage of several board

☞ Applied Voltage level is specified at the time when Full-White pattern is displayed on the panel.

Vcc(4.75 ~5.25V)

Confidential

Page 10/44Revision No. 0.0 30/Mar./ 2012

Page 11

Product Specification of PDP Module

2. ELECTRICAL SPECIFICATIONS

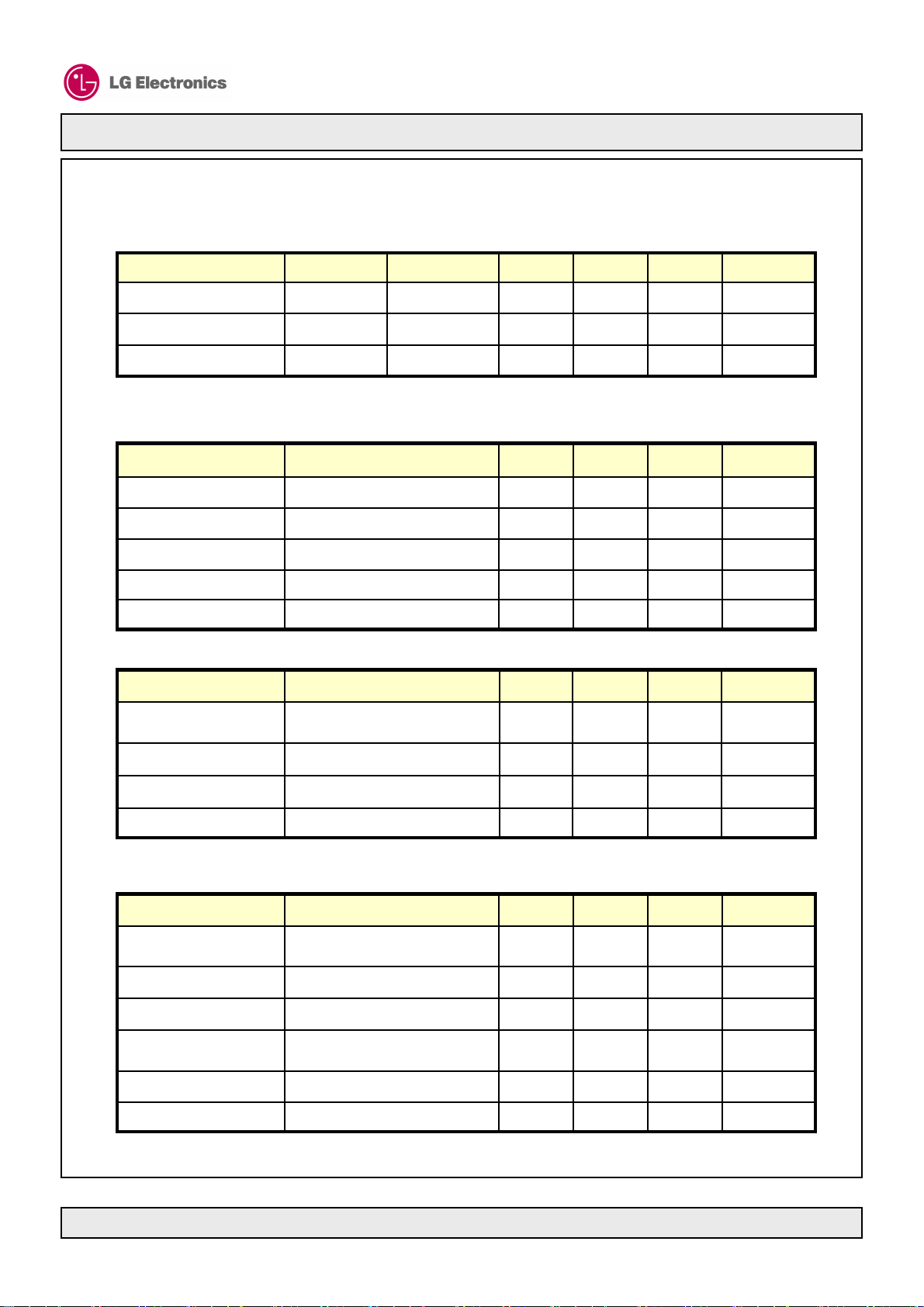

Absolute Power Specifications

P08##-##

Input Power Specifications

Logic Power Supply (Vcc)

Address Power Supply (Va)

Adjustable Range

characteristics of each PDP

Condition

25°C

25°C

25°C

Dependent on the

RemarksUnitMax.Min.SymbolItem

V6-VccLogic Voltage

V57-VaAddress Voltage

V215-VsSustain Voltage

UnitMax.Typ.Min.ConditionItem

V5.2554.75-Adjustable Range

%± 3.0---Voltage Stability

Amean2.5-0.1-Average Current

mVp-p30---Ripple

mVp-p300---Noise

UnitMax.Typ.Min.Condition & RemarksItem

V565554

Sustain Power Supply(Vs)

Adjustable Range

Average Current

☞ Voltage should be set to a specified value which is indicated on the label attached to the module.

characteristics of each PDP

characteristics of each PDP

2.0-0.01Variable with the imageAverage Current

300---Ripple & Noise

☞ Max current of Va is measured when 2-dot on/off pattern is displayed.

Dependent on the

Dependent on the

1.4-0.1

A

mV

UnitMax.Typ.Min.ConditionItem

A

mVp-p500---Ripple & Noise

Confidential

%± 1.5---Voltage Stability

mean

p-p

V206-200

%± 1.0---Voltage Stability

A21---Peak Current

mean

V3--At the peak currentVoltage Regulation

Page 11/44Revision No. 0.0 30/Mar./ 2012

Page 12

Product Specification of PDP Module

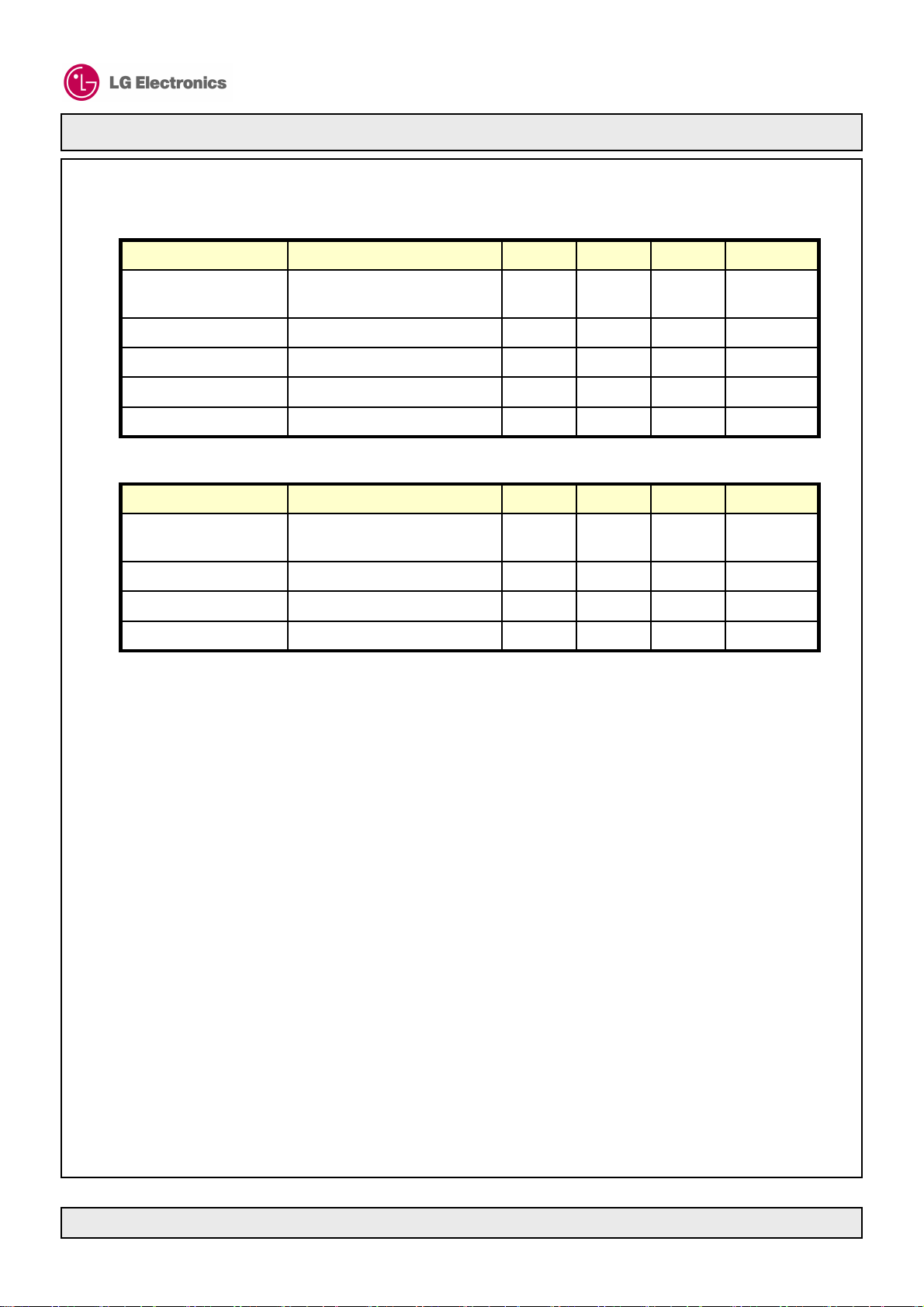

Input Power Specifications (Continued)

Writing Scan Bias Power Supply (-Vy)

P08##-##

UnitMax.Typ.Min.ConditionItem

Adjustable Range

Dependent on the

characteristics of each PDP

-Voltage Stability

-Average Current

At the peak currentVoltage Regulation

-Ripple & Noise

Z-bias Power Supply (Vzb)

Adjustable Range

☞ Voltage should be set to a specified value which is indicated on the label attached to the module.

Dependent on the

characteristics of each PDP

-Voltage Stability

-Average Current

At the peak currentVoltage Regulation

V-188- 190-198

%±3.0--

mA100--

V2-V-188- 190-198

UnitMax.Typ.Min.ConditionItem

V135120115

%±3.0--

mA250--

V5--

Confidential

Page 12/44Revision No. 0.0 30/Mar./ 2012

Page 13

Product Specification of PDP Module

P08##-##

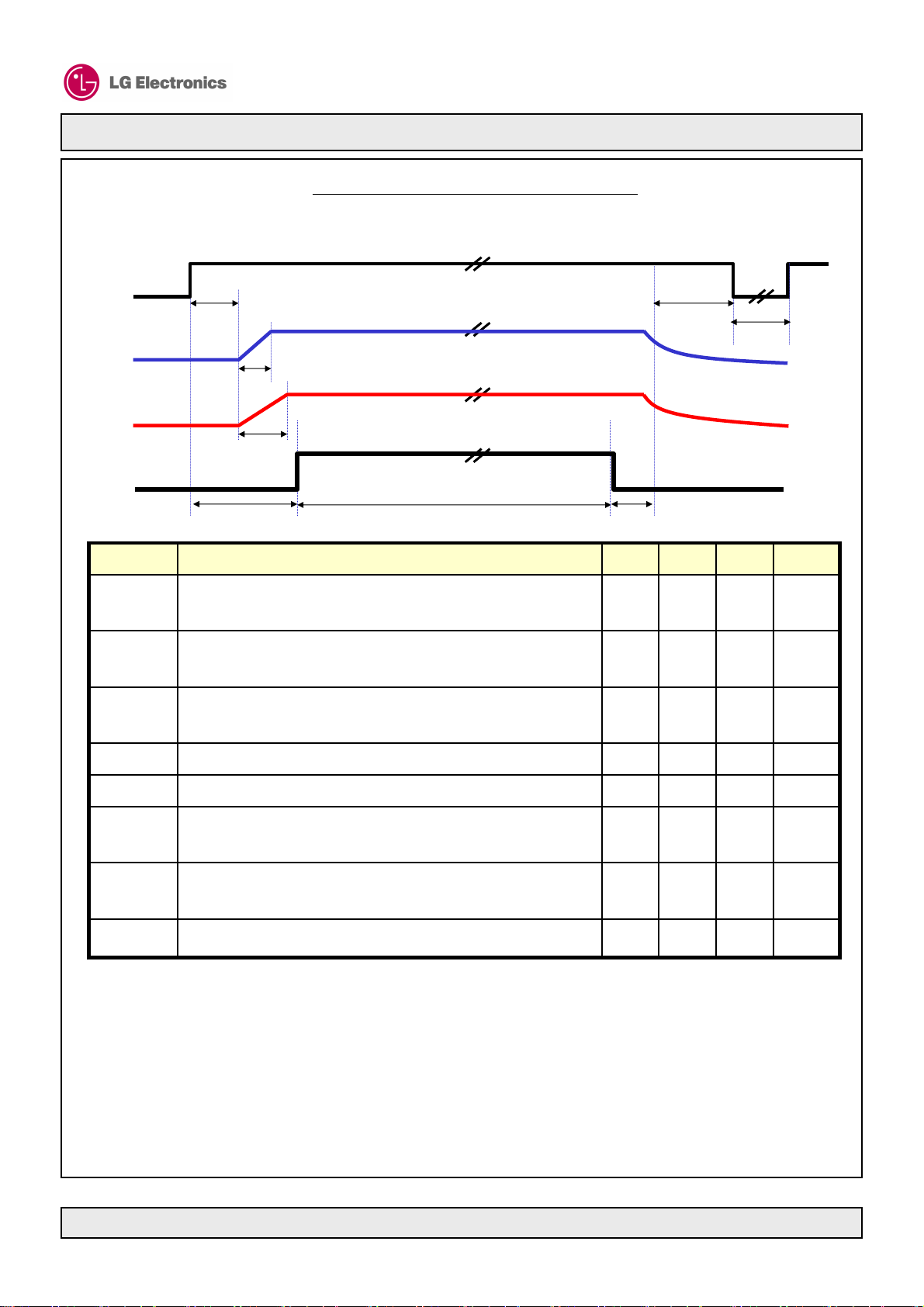

Power Supply Sequence

V

CC

(5V)

T

On

Va

T

VaR

Vs

T

VsR

DISPEN

T

d_on

T

On

Time interval between 90% of Vcc and 10% of Vs

(In Case of Discharge resistance remove)

Normal Display

when Power On

T

d_off

Vcc OFF Vcc ON

T

Off

T

OnR

Max.

300

unitTypMin.DescriptionSymbol

msec250200

T

Off

T

OnR

VaR

VsR

T

d_on

T

d_off

d_off_I2C

Time interval between 90% of Vs and 10% of Vcc

when Power Off

Time interval between 20% of Vcc OFF (falling)

to 20% of Vcc On (rising) when Power On

Time interval between 90% of Vcc

and DISPEN rising edge when Power On

Time interval between DISPEN falling edge

and 90% of Vs when Power Off

200

200

6000

msec25002000

msec2000

msec50Rising Time of Va (10% to 90%)T

msec50Rising Time of Vs (10% to 90%)T

msec2000

msec1000800

msec700Time between DISPEN OFF to I2C ON (off sequence)T

☞ Vcc should be lower than 0.1V when turn on just after turn off.

☞ If power sequence does not meet to above sequence diagram, PDP drivers may be damaged permanently.

☞ If Vs is off on purpose (or not), for example recording mode, Vcc should be off before turn on again.

Again, When you are turn on, 5V on. And then, Va, Vs on.

☞ AC off Condition is treated as the exception. But It can make optical noise in a short time,

for example uncontrollable dot and image sticking, etc.

☞ DISPEN signal shall be certainly applied after Vs On..

☞ T

Min time is except for turn Off using AC Power supply.

off

Confidential

Page 13/44Revision No. 0.0 30/Mar./ 2012

Page 14

Product Specification of PDP Module

LVDS Signal and LVDS Receiver

Definitions and Functions of LVDS Signal

P08##-##

Symbol

SymbolSymbol

Function and DescriptionSymbol

Channel A Pos. Receiver Input for 2D video signalRA1+

Channel A Neg. Receiver Input for 2D video signalRA1Channel B Pos. Receiver Input for 2D video signalRB1+

Channel B Neg. Receiver Input for 2D video signalRB1Channel C Pos. Receiver Input for 2D video signalRC1+

Channel C Neg. Receiver Input for 2D video signalRC1Channel D Pos. Receiver Input for 2D video signalRD1+

Channel D Neg. Receiver Input for 2D video signalRD1Channel E Pos. Receiver Input for 2D video signalRE1+

Channel E Neg. Receiver Input for 2D video signalRE1Clock Pos. Receiver Input for 2D video signalRCLK1+

Clock Neg. Receiver Input for 2D video signalRCLK1-

Confidential

Page 14/44Revision No. 0.0 30/Mar./ 2012

Page 15

Product Specification of PDP Module

P08##-##

2D Video Input Connector (P106)

For 2D video signal

SymbolPin

GND1

Serial Download CLK2

Serial Download Data3

I2C_SCLK4

DISPEN5

I2C_SDATA6

NC7

NC8

NC9

NC10

GND11

Pin

18

19

20

21

22

23

24

25

26

27

28

Symbol

GND

RCLK1RCLK+

GND

RD-

RD+

GND

GND

GND

GND

RA3-

Connector Type : C-NET, 3018-56151 51P

Pin

35

36

37

38

39

40

41

42

43

44

45

Symbol

RCLK3-

RCLK3+

GND

RD3-

RD3+

GND

GND

GND

GND

GND

GND

NC46RA3+29RA1-12

NC47RB3-30RA1+13

UART Rx48RB3+31RB1-14

UART Tx49RC3-32RB1+15

VS_3D50RC3+33RC1-16

GND51GND34RC1+17

3018-56151 51P Pin number ( Top view )

Pin number :

12

3 4

· · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · ·

5 6

① Housing, ② Actuator, ③ Shell, ④ Pin

51

1) When using the 2D video signal Differential Signal (RA3, RB3, RC3, RD3, RCLK3) is

not used.

Confidential

Page 15/44Revision No. 0.0 30/Mar./ 2012

Page 16

Product Specification of PDP Module

LVDS Signal and LVDS Receiver (continued)

For 2D video signal

Function and DescriptionSymbol

8 bit Red video signal (R9 : MSB, R2 : LSB)R9~R2

8 bit Green video signal (G9 : MSB, G2 : LSB)G9~G2

8 bit Blue video signal (B9 : MSB, B2 : LSB)B9~B2

Clock Signal which synchronous to video signalPIX_CLK

Vertical synchronous signalVsync

Horizontal synchronous signalHsync

‘HIGH’ level : data is valid, ‘LOW’ level : data is invalidBLANK

The panel will not malfunction, if DISPEN is high at start upDispen

P08##-##

☞ Each of the RGB signals can be changed with the Gamma Mode.

☞ You should not adjust any inverse gamma compensation. Because the inverse gamma compensation

is adjusted in the PDP side already.

☞ In preparing the LDVS signal cable, The twisted pair cable should be used for the differential signal.

☞ Dispen signal is HIGH (3.3V) in normal state. However Dispen can be inversed to LOW(GND) from

time to time.

Confidential

Page 16/44Revision No. 0.0 30/Mar./ 2012

Page 17

Product Specification of PDP Module

LVDS-Rx IP Signal mapping for 8 bit video signal

P08##-##

RA1

RB1

RC1

RD1

RCLK1

1) RE1 is not used for 8bit video signal.

For 2D 8bit application

TCLK1+/-

LVDS Transmitter

TA1+/-

(8 bit)

TB1+/-

TC1+/-

TD1+/-

3.3V

GND

G4

B5

BLANK

R

R

R9 R8 R7 R6 R5 R4

B4 G9 G8 G7 G6 G5

VSYNC HSYNC B9 B8 B7 B6

B3 B2 G3 G2 R3 R2

LVDS Connector (Tx)

LVDS Connector (Rx)

RCLK1+/-

RA1+/-

RB1+/-

(10 bit)

RC1+/-

RD1+/-

TE1-

TE1+

RE1+/-

LVDS Receiver

R

R

R

R

R

R

R

R

R

R

R

R

Set

TCLK3-

TCLK3+

TA3TA3+

TB3-

TB3+

TC3-

TC3+

TD3-

TD3+

TE3-

TE3+

RCLK3+/-

RA3+/-

RB3+/-

RC3+/-

RD3+/-

RE3+/-

PDP module side

NC

3.3V

GND

3.3V

GND

3.3V

GND

3.3V

GND

3.3V

GND

3.3V

GND

1) To use 2D video signal, “TCLK3+, TA3+, TB3+, TC3+, TD3+, TE3+” are to be tied to ground signal

and “TCLK3-, TA3-, TB3-, TC3-, TD3-, TE3-” are to be tied to 3.3V signal.

2) Pull up / down R value is recommended 10kΩ

Confidential

Page 17/44Revision No. 0.0 30/Mar./ 2012

Page 18

Product Specification of PDP Module

Input Signal Timing Diagram ( Non-interlaced Signal )

T

VSYNC

Vsync

Hsync

1 2 3

768+N 768+N

1 2 3 1 2 3

T

VSYNC

768+N 768+N

P08##-##

1 2 3

Vsync

Hsync

DCLK

BLANK

DATA

Hsync

DCLK

BLANK

t

t

WV

t

VH

768+N

T

BPV

T

HSYNC

1 2 3 4 768

t

WB

HV

※※※※TWB> 4.6us

( Period of valid data )

T

HSYNC

t

WH

t

WCLK1

t

SUB

t

BPH

t

HC

T

CLK

1 2

t

WCLK2

t

CH

1024

t

HB

( Period of valid data )

t

SUD

t

hd

DATA

Shaded Area : Invalid

☞ TWBmust be longer than 4.6㎲

d1 d2 d1024

Confidential

Should be ‘0’

Page 18/44Revision No. 0.0 30/Mar./ 2012

Page 19

Product Specification of PDP Module

Input Signal Timing Specification

60Hz Mode

No. Symbol Min. Typ. Max. Unit Remark

P08##-##

10

11

12

13

14

1

2

3

4

5

6

7

8

9

T

vsync

t

wv

t

vh

t

hv

T

hsync

t

wh

t

hc

t

ch

t

clk

t

wclk1

t

wclk2

t

sub

t

hb

t

sud

16.531

(799H)

82 (4H) 124 (6H)

393 (19H) 455 (22H) 517 (25H)

103(5H)

20.63 (1340D) 20.69 (1344D) 20.75 (1348D)

2.03(132D) 2.09(136D) 2.15(140D)

4.49 (292D) 4.55(296D) 4.62(300D)

15.2

(65.8MHz)

16.676

(806H)

331(16H)

0.36(24D)

15.4

(65MHz)

7.7

7.7

7.7

7.7

7.7

16.820

(813H)

165 (8H)

15.6

(64MHz)

㎳ (H)

㎲ (H)

㎲ (H)

㎲ (H)

㎲ (D)

㎲ (D)

㎲ (D)

㎲ (D)

㎱

㎱

㎱

㎱

㎱

㎱

1 frame =

59.47Hz ~ 60.52Hz

t

vh

≥ 19H

t

clk =twclk1+twclk2

≤

t

hc

t

ch

t

sub

t

hb ≤

15

t

hd

7.7

㎱

☞ Min. & Max. of each signal is measured value when other signal is Typ.

☞ When Timing is changed, Recommend even value of VSYNC and HSYNC(D, H)

☞ Thv ( Vertical Front Porch ) ≥ 5H

☞ Tvh ( Vertical sync width + Vertical Back Porch ) ≥ 19H

Confidential

Page 19/44Revision No. 0.0 30/Mar./ 2012

Page 20

Product Specification of PDP Module

Input Signal Timing Specification (Continued)

48Hz Mode

No. Symbol Min. Typ. Max. Unit Remark

P08##-##

10

11

12

13

14

1

2

3

4

5

6

7

8

9

T

vsync

t

wv

t

vh

t

hv

T

hsync

t

wh

t

hc

t

ch

t

clk

t

wclk1

t

wclk2

t

sub

t

hb

t

sud

20.627

(997H)

82 (4H) 124 (6H)

393 (19H) 455 (22H) 517 (25H)

103 (5H)

20.63 (1340D) 20.69 (1344D) 20.75 (1348D)

2.03(132D) 2.09(136D) 2.15(140D)

4.49 (292D) 4.55(296D) 4.62(300D)

15.2

(65.8MHz)

20.834

(1007H)

4487 (217H)

0.36(24D)

15.4

(65MHz)

7.7

7.7

7.7

7.7

7.7

21.062

(1018H)

165 (8H)

15.6

(64MHz)

㎳ (H)

㎲ (H)

㎲ (H)

㎲ (H)

㎲ (D)

㎲ (D)

㎲ (D)

㎲ (D)

㎱

㎱

㎱

㎱

㎱

㎱

1 frame =

47.50Hz ~ 48.50Hz

t

vh

≥

≥ 19H

≥≥

t

clk =twclk1+twclk2

≤

t

hc

t

ch

t

sub

t

hb ≤

15

t

hd

7.7

㎱

☞ Min. & Max. of each signal is measured value when other signal is Typ.

☞ When Timing is changed, Recommend even value of VSYNC and HSYNC(D, H)

☞ Thv ( Vertical Front Porch ) ≥ 5H

☞ Tvh ( Vertical sync width + Vertical Back Porch ) ≥ 19H

Confidential

Page 20/44Revision No. 0.0 30/Mar./ 2012

Page 21

Product Specification of PDP Module

Input Signal Timing Specification (Continued)

50Hz Mode

No. Symbol Min. Typ. Max. Unit Remark

P08##-##

10

11

12

13

1

2

3

4

5

6

7

8

9

T

vsync

t

t

vh

t

T

hsync

t

t

hc

t

ch

t

clk

t

wclk1

t

wclk2

t

sub

t

hb

wv

hv

wh

19.800

(957H)

82 (4H) 124 (6H)

393 (19H) 455 (22H) 517 (25H)

103 (5H)

20.63 (1340D) 20.69 (1344D) 20.75 (1348D)

2.03(132D) 2.09(136D) 2.15(140D)

4.49 (292D) 4.55(296D) 4.62(300D)

15.2

(65.8MHz)

20.007

(967H)

3660 (177H)

0.36(24D)

15.4

(65MHz)

7.7

7.7

7.7

7.7

20.214

(977H)

165 (8H)

15.6

(64MHz)

㎳ (H)

㎲ (H)

㎲ (H)

㎲ (H)

㎲ (D)

㎲ (D)

㎲ (D)

㎲ (D)

㎱

㎱

㎱

㎱

㎱

1 frame =

49.49Hz ~ 50.52Hz

t

vh

≥

≥ 19H

≥≥

t

clk =twclk1+twclk2

≤

t

hc

t

ch

t

sub

t

hb ≤

14

15

t

t

sud

hd

7.7

7.7

㎱

㎱

☞ Min. & Max. of each signal is measured value when other signal is Typ.

☞ When Timing is changed, Recommend even value of VSYNC and HSYNC(D, H)

☞ Thv ( Vertical Front Porch ) ≥ 5H

☞ Tvh ( Vertical sync width + Vertical Back Porch ) ≥ 19H

Confidential

Page 21/44Revision No. 0.0 30/Mar./ 2012

Page 22

Product Specification of PDP Module

Brightness Variation Function by Frequency

▶ If input Vsync period is longer than normal range,

brightness reduction mode operates for protecting waveform overflow.

▶ This function is for special range of input Vsync frequency.

P08##-##

46.17

AV/PC

48Hz

AV/PC

50Hz

AV/PC

60Hz

FF Mode is at specific region.

(Brightness is lower than

Normal Mode.)

Normal

Mode

48.01

Normal

Mode

FF

Mode

50.6

3

Frequency ( Hz )

51.5 57.14

Normal

Mode

Min. Max. value of Vsync is the value when timing spec is typical of timing spec(4.51~2)

When input Vsync is out of the above frequency range, making mode operates.

(Making Mode: Vsync, 22msec[45.45Hz] displayed black)

60.9

0

FF

Mode

: Timing Overflow Protection

Function

63.90

Confidential

Page 22/44Revision No. 0.0 30/Mar./ 2012

Page 23

I2C Timing Specification

I2C Timing Diagram

SDA

P08##-##

Product Specification of PDP Module

tttt

LOW

LOW

LOWLOW

tttt

rrrr

tttt

SU:DAT

SU:DAT

SU:DATSU:DAT

tttt

ffff

tttt

HD:STA

HD:STA

HD:STAHD:STA

SCL

tttt

HD:STA

HD:STA

HD:STAHD:STA

S Sr

tttt

HD:DAT

HD:DAT

HD:DATHD:DAT

tttt

HIGH

HIGH

HIGHHIGH

tttt

SU:STA

SU:STA

SU:STASU:STA

I2C Timing Specification (Characteristics of the SDA and SCL bus lines)

STANDARD-MODE

MAX.MIN.

-4.0t

-4.7t

-4.0t

-5.0

(2)

0

3.45

(3)

-4.0t

-4.7t

DD

DD

SCL clock frequency

Hold time (repeated) START condition

After this period, the first clock pulse is

generated

LOW period of the SCL clock

HIGH period of the SCL clock

Set-up time for a repeated START condition

Data hold time:

for CBUS compatible masters

for I2C bus devices

DATA Set-up time

Rise time of both SDA and SCL signals

Fall time of both SDA and SCL signals

Set-up time for STOP condition

Bus free time between a STOP and START

condition

Capacitive load for each bus line

Noise margin at the LOW level for each

connected device (including hysteresis)

Noise margin at the High level for each

connected device (including hysteresis)

SYMBOLPARAMETER

SCL

HD;STA

LOW

HIGH

f

SCL

t

HD;DAT

SU;DAT

f

SU;STO

BUF

V

nL

V

nH

r

b

tttt

SP

SP

SPSP

tttt

UNIT

kHz1000f

µs

µs

µs

µs

µs

µs

ns-250t

ns1000-t

nst

µs

µs

pF400-C

V-0.1V

V-0.2V

SU:STO

SU:STO

SU:STOSU:STO

tttt

rrrr

tttt

BUF

BUF

BUFBUF

P

S

MSC610

Notes

1. All values referred to V

2. A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the V

undefined region of the falling edge of SCL.

3. The maximum t

4. A Fast-mode I2C-bus device can be used in a Standard-mode I2C-bus system, but the requirement t

HD;DAT

This will automatically be the case if the device does not stretch the LOW period of the SCL signal.

If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t

= 1250 ns (according to the Standard-mode I2C-bus specification) before the SCL line is released.

IHmin

and V

ILmax

levels.

has only to be met if the device does not stretch the LOW period (t

IHmin

) of the SCL signal.

LOW

SU;DAT

of the SCL signal) to bridge the

≥ 250 ns must then be met.

+ t

r max

SU;DAT

5. Cb= total capacitance of one bus line in pF. If mixed with Hs-mode devices, faster fall-times according to Table 6 are allowed.

※n/a = not applicable

Confidential

= 1000 + 250

Page 23/44Revision No. 0.0 30/Mar./ 2012

Page 24

Product Specification of PDP Module

I2C Timing Specification

I2C Timing Specification (Characteristics of the SDA and SCL I/O stages)

P08##-##

LOW level input voltage:

fixed input levels

VDD-related input levels

HIGH level input voltage:

fixed input levels

VDD-related input levels

VDD > 2V

VDD < 2V

LOW level output voltage (open drain or open

collector) at 3 mA sink current:

VDD > 2V

VDD < 2V

Out fall time from VIHmin to VILmax with

a bus capacitance from 10 pF to 400 pF

Pulse width of spikes which must be

suppressed by the input filter

Input current each I/O pin with an input

voltage between 0.1 VDD and 0.9VDDmax

SYMBOLPARAMETER

VIL

VIH

VhysHysteresis of Schmit trigger inputs:

VOL1

VOL3

STANDARD-MODE

MAX.MIN.

-0.5

-0.5

3.0

n/a

n/a

0

n/a

1.5

0.3VDD

n/a

n/a

0.4

n/a

UNIT

V

V

V(2)

V(2)0.7VDD

V

V

V

V

ns250(4)-Tof

nsn/an/atSP

ΜA10-10Ii

pF10-CiCapacitance for each I/O pin

Notes

1. Devices that use non-standard supply voltages which do not conform to the intended I2C-bus system levels must relate their input levels to

the VDDvoltage to which the pull-up resistors Rpare connected.

2. Maximum VIH= V

3. Cb= capacitance of one bus line in pF.

4. The maximum tffor the SDA and SCL bus lines quoted in Table 5 (300 ns) is longer than the specified maximum toffor the output stages (250 ns).

This allows series protection resistors (Rs) to be connected between the SDA/SCL pins and the SDA/SCL bus lines as shown in Fig.36 without

exceeding the maximum specified tf.

5. I/O pins of Fast-mode devices must not obstruct the SDA and SCL lines if VDDis switched off.

※ n/a = not applicable

DDmax

+ 0.5 V.

Confidential

Page 24/44Revision No. 0.0 30/Mar./ 2012

Page 25

Product Specification of PDP Module

ASIC I2C Timing & Register Description

P08##-##

Individual data Write mode of I2C control

SCL

SDA

Start

By

Master

SCL (continue)

SDA (continue)

1

0 0

0

1 1 1

Chip ID Address Byte

(0x0E)

9 1

D7

ACK

By Slave

For “Write” function, first 1byte data should be 000 1110 (0) last 1bit is 0(write mode).

Start /Stop condition is generated by Master (=Image B’D).

Before start condition and/or after stop condition, SDA should not be recognized as a valid data.

Start condition : SCL high & SDA transition from H to L

Stop condition : SCL high & SDA transition from L to H

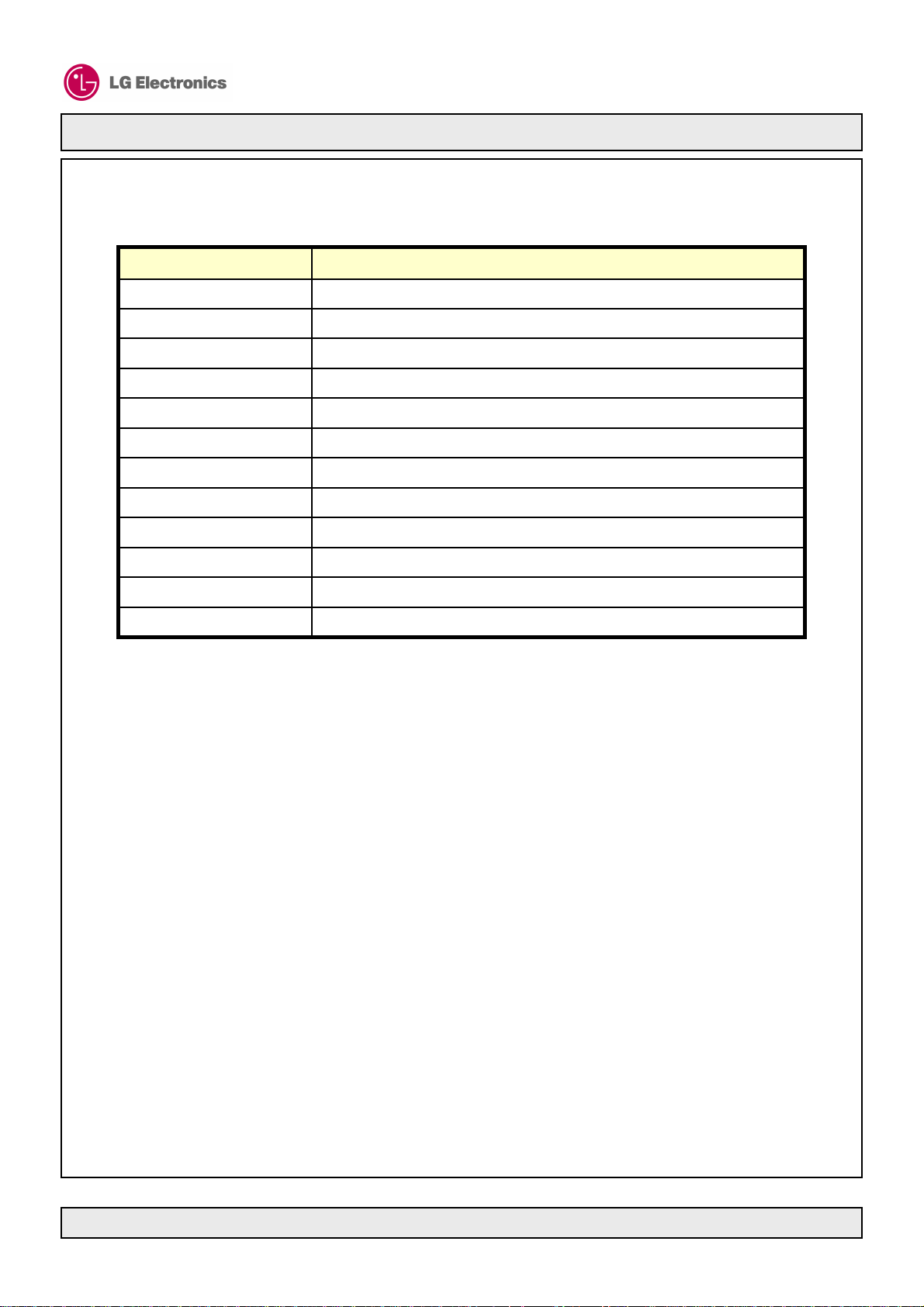

I2C Register Brief

I2C

Addr.

0x07

0x08

0x09

0x0A

R

0x18

R

0x20

0x49

R

R

0RR

※ Master: Image Board, Slave: PDP Module

9

W

0

Write

only

ACK

By Slave

D6

Command Data

for Addr

I2C Data

Bright Mode Registers

50_2D(2)RRR

Bright Mode Registers

Power Save Mode Registers

Power Save Mode Registers

ISM Mode Registers

Pattern Generation Registers

auto_

pat_gen

Power-Off Sequence

1

A7

D0

0br_mode_60_2D(1:0)br_mode_50_2D(1:0)

A6

Command Address

Addr=A[7:0]

9

ACK

By Slave

By Master

R : Reserved(don’t care)

ps_mode_60_2D(2:0)ps_mode_50_2D(2:0)R

Stop

060_2D(2)R

000000R

8

A1 A0

01234567

0

0

11ism_modeRRRR

RRRR

Power_offRRRRRR

Confidential

Page 25/44Revision No. 0.0 30/Mar./ 2012

Page 26

Product Specification of PDP Module

P08##-##

ASIC I2C Timing & Register Description

Bright Mode Registers

I2C Addr.

0x07

R

0x08

• br_mode_50_2D(2:0) : Bright mode for 2D 50Hz mode

• br_mode_60_2D(2:0) : Bright mode for 2D 60Hz mode

R

Power Save Mode Registers

I2C Addr.

0x09

R

R

(continued)

I2C Data

Bright Mode Registers

RR

Bright Mode Registers

I2C Data

Power Save Mode Registers

01234567

0060_2D(2)50_2D(2)

00br_mode_60_2D(1:0)br_mode_50_2D(1:0)

0000 0000Default

01234567

ps_mode_60_2D(2:0)ps_mode_50_2D(2:0)

RR0x0A

• ps_mode_50_2D(2:0) : Power save mode for 2D 50Hz mode

• ps_mode_60_2D(2:0) : Power save mode for 2D 60Hz mode

Power-Off Sequence

I2C Data

I2C Addr.

Power-Off Sequence

0x49

• power_off : power off sequence start , ‘1’ on , ‘0’ off

• 0x49 address is a password region , the password must be transferred before use that.

Password : address 0x38, transfer data : 0x19

000000

0000 00RRDefault

01234567

RRRR RRR

power_off

Confidential

Page 26/44Revision No. 0.0 30/Mar./ 2012

Page 27

Product Specification of PDP Module

P08##-##

ASIC I2C Timing & Register Description

ISM Mode Registers

▷ Image Sticking Minimization Method

ISM_CTRL, BWINV and SCROLL are all Image Sticking Minimization methods.

Two/three of them can be activated at a time, because they operate independently.

I2C Addr.

0x18

R

• ims_mode : ISM mode switch (1: ON, 0:OFF)

Sustain number

ISM

Limit line

(continued)

I2C Data

ISM Mode Registers

If there is no movement (APL data variation is

less tan ± 5) for 5min. approximately, the brightness

can be fallen near to Full White level.

ISM mode doesn’t activated when APL is

over the ISM limit line.

01234567

RRRR

ism_mode

11

111RRRRRDefault

0

Current APL

Timing increment

1023 (Full White)

APL

Pattern Generation Registers

I2C Addr.

Pattern Generation Registers

0x20

R

• pat_auto_gen : Automatically pattern generation mode switch, 0:OFF, 1:ON

• automatically generated pattern sequence

1) 1 pixel with fore-ground color at the start coordinate

2) full window with foreground

3) Peak window with X-Y coordinates

4) Life Pattern

5) 9 point box

6) 5 point box for testing the load effect

7) color bar

8) cross bar

0R

I2C Data

auto_

pat_gen

9) gray level with 32*32 rectangular

10) vertical gray bar, 256 level

11) horizontal gray bar, 256 level

12) box window

13) horizontally scrolling the vertical gray bar

14) vertically scrolling the horizontal gray bar

15) horizontally moving the vertical bar

16) vertically moving the horizontal bar

17) Random Pattern

01234567

RRRR

RRRR00RRDefault

Confidential

Page 27/44Revision No. 0.0 30/Mar./ 2012

Page 28

Product Specification of PDP Module

3. ELECTRO OPTICAL SPECIFICATIONS

Electro Optical characteristic Specifications (60/50Hz)

Item Symbol Condition Min Typical Max Unit

P08##-##

Peak White Brightness B

Average White Brightness B

Brightness Uniformity B

X X

Red

Y Y

X X

Green

Color

Coordinate

Y Y

X X

Blue

Y Y

X X

White

Y Y

Color Coordinate Uniformity C

WP

W

W

W

1% White Window 700 - - cd/㎡

Full White 90 100 - cd/㎡

V

R

R

G

G

B

B

Full White -25 0 +25 %

0.635 0.655 -

0.315 0.335 0.355

0.295 0.315 0.325

0.600 0.620 -

Full Pattern

- 0.150 0.170

- 0.060 0.080

-

0.275 0.295 0.315

0.280 0.300 0.320

V

Full White -0.020 Center 0.020 -

Power Consumption Pw Full / 25% White Window - 276 300 W

• Respective value is measured at stable panel’s characteristics (over 20 min.)

• Basis on CA-210

• Vs margin set -4V at 2 period (room temperature)

Confidential

Page 28/44Revision No. 0.0 30/Mar./ 2012

Page 29

Product Specification of PDP Module

4. MECHANICAL & ENVIRONMENTAL SPECIFICATIONS

Mechanical Characteristic Specifications

Remark

Item

ItemItem

SpecificationItem

SpecificationSpecification

UnitSpecification

UnitUnit

RemarkUnit

RemarkRemark

P08##-##

Outline Dimensions

Display Area

Module

Weight

Net

Gross

1156.0 ± 1.5 (H) X 677.6 ± 1 (V)

X 37.9(D) ± 1.5

Vibration and Drop Specifications

Item

ItemItem

Vibration

Drop

1.04Grms, 2~ 200Hz random,

ConditionItem

ConditionCondition

total 30 min

20 cm

mm

mm1105.92(H) X 622.08(V) ± 0.5

kg14.2± 0.5(1EA)

kg250.2± 5 (15EA / 1BOX)

SpecCondition

SpecSpec

Meet

Characteristi

cs and other

Spec.

Glass Filter

(GLOBAL)

Common

Glass Filter

(GLOBAL)

Remark

RemarkSpec

RemarkRemark

boxing

state

(Y dir.)

Recommended Environmental Conditions

Item

ItemItem

Ambient

temperature

Panel

Temperature

Humidity

Air pressure

Operation

Surface

Storage

- 20℃ ~ 60℃Storage

Under 120℃

800 ~ 1100 hPaOperation

700 ~ 1100 hPa

Confidential

ConditionItem

ConditionCondition

0℃ ~ 60℃

< 20℃/cmChange ratio

20% ~ 80%Operation

10% ~ 90%Storage

Spec.Condition

Spec.Spec.

Meet

Characteristic

s and other

Spec.

Remark

RemarkSpec.

RemarkRemark

Module

Condition

Page 29/44Revision No. 0.0 30/Mar./ 2012

Page 30

Product Specification of PDP Module

5. IMAGE STICKING CHARACTERISTICS

Image Sticking

The fluorescent substance used in the plasma module loses its brightness with the lapse of lighting time. This

deterioration in brightness appears to be a difference in brightness in relation to the surroundings, and comes to

be recognized as image sticking.

In other words, the image sticking is defined as follows: when the same pattern (of the fixed display) is

displayed for a long time, a difference in brightness is caused around the lighting area and non-lighting area due

to deterioration in the fluorescent substance.

When the present pattern is changed over to another one, the boundary comes to be seen between the lighting

area and non-lighting area due to difference in brightness in the pattern shown shortly before changeover. If this

conditions is accumulated, the boundary or image sticking comes to be seen with the naked eyes.

Secular change in brightness

The life of brightness, defined as the reduction to half the initial level, is more than 25 thousand hours on average.

Conditions: All white (100% white) input at an ambient temperature of 25°C.

P08##-##

However, this lifetime is not a guarantee value for life and brightness. It should be recognized simply as the data

for reference.

Cause of deterioration in brightness

A major possible cause of deterioration in brightness is damage in the fluorescent substance due to impact caused

by ions generated at the time of plasma discharges.

Practical value for Image sticking

The relationship between integrated lighting time and brightness in this plasma module is described in the

attached material. In particular, the deterioration in brightness tends to be accelerated up to 100 hours in the initial

period. In the initial period, the fixed display of patterns particularly tends to cause image sticking. The practical

value for image sticking is difficult in concrete numerals. As described below, you are advised to take proper

measures to make the occurrence of image sticking as slow as possible.

Confidential

Page 30/44Revision No. 0.0 30/Mar./ 2012

Page 31

Product Specification of PDP Module

Proposed measures taken to relieve image sticking

So long as there is the reduction of brightness in the fluorescent substance, it is impossible to avoid the

occurrence of image sticking. Therefore, to relieve image sticking, we offer you a method of entering an image

input that may ensure reluctance to the generation of the difference in brightness reduction among the displayed

dots.

The images from TV broadcasting involve a high rate of motion picture displays. Therefore, there is less chance

of being a cause of difference in brightness reduction among the cells. Even when the fixed patterns are

displayed, they generally last for a few minutes. Since the same pattern is less liable to be displayed, there is

almost no influence toward image sticking.

If the fixed patterns tend to be displayed for a long time, however, there occurs a substantial imbalance between

the lighting and non-lighting areas, thus causing a difference in brightness as a result. In this document, we offer

you some proposals of installation, paying attentions to the two points: the reduction of difference in brightness

achieved by integrated lighting time leveling and the method of edge smearing to make image sticking hard to be

discerned.

The result from these proposals can, however, greatly depend on the contents of images and the operating

environment. Therefore, we consider that it is essential to take the suitable measures in consideration of the

customer’s operating environment.

P08##-##

Example of Proposal 1: The display position is moved while the fixed display pattern is changed over, or it is

scrolled during the display.

Example of Proposal 2: If possible, a pattern of complementary color is incorporated (for integrated time

leveling).

Example of Proposal 3: The fixed pattern and the motion picture display are reciprocally exchanged, in order to

minimize display period of the fixed pattern.

Example of Proposal 4: During operation, the brightness of screen is suppressed as low as possible. For the

display patterns, characters are indicated not on the black ground (non-picture area) but on the colored ground

(mixture of R, G, B recommended).

Confidential

Page 31/44Revision No. 0.0 30/Mar./ 2012

Page 32

Product Specification of PDP Module

6. OUTLINE DRAWING

Front View

P08##-##

Confidential

Page 32/44Revision No. 0.0 30/Mar./ 2012

Page 33

Rear View

P08##-##

Product Specification of PDP Module

Confidential

Page 33/44Revision No. 0.0 30/Mar./ 2012

Page 34

Product Specification of PDP Module

8. LABEL

LABEL Sticking Position

LABEL ①①①① : Unification Label

P08##-##

150mm

MODEL : PDP50T4####

①①①①

②②②②

107K450T4######.ASBBBDD

③③③③

Voltage Setting: 5V/Va:55/Vs:205

④④④④

N.A /-190 / 150 / N.A / 120

⑤⑤⑤⑤

⑥⑥⑥⑥

Model Name

①

Bar Code (Code 128, Contains the manufacture No.)

②

Manufacture No.

③

Adjusting Voltage (DC Va, Vs)

④

Adjusting Voltage (Set up/ -Vy/ Vsc/ Ve/ Vzb)

⑤

-

⑥

Manufactured date (Year & Month)

⑦

Warning

⑧

UL Approval Mark

⑨

UL Approval No.

⑩

Model Name

⑪

Max. Volts

⑫

Max. Amps

⑬

⑦⑦⑦⑦

KOREA 2011.07

⑧⑧⑧⑧

DO NOT TOUCH ELECTRIC AND POINTED PART

WARNING

HIGH VOLTAGE

HOT SURFACE

MECHANICAL HAZARD

⑨⑨⑨⑨

E227451

⑩⑩⑩⑩

MODEL : PDP50T4####

Rating

Max Volt() : 5.25V/56Va/206Vs

Max Amps : 2.5/2.0/1.4A

PDP50T4####

5V / Va:55 / Vs:205

N.A / -190 / 150 / N.A / 120

E227451

PDP50T4####

5.25V/56Va/206Vs

2.5A/2.0A/1.4A

⑪⑪⑪⑪

27mm

⑫⑫⑫⑫

⑬⑬⑬⑬

LABEL ②②②② : Unification Label

①

P/N : AFT########

②

③

W50117023018

① Module frame ass’y part number

② Bar Code Containing the manufacture No.

③ Manufacture No.

55mm

14.5mm

Confidential

Page 34/44Revision No. 0.0 30/Mar./ 2012

Page 35

Product Specification of PDP Module

LABEL Sticking Position

LABEL ③③③③ : Label Sticking Position

P08##-##

Attachment at incuse position

combined label

Module ID

Confidential

Page 35/44Revision No. 0.0 30/Mar./ 2012

Page 36

Product Specification of PDP Module

9. PACKING

Box packing (15 modules per each Box)

Packing composition : cover plate, M4 screw, pallet, bottom / top packing

box, bottom / top box, tape, band, box label

Module quantity in box : 15 EA

Top Box

Top Packing

Cover Plate

Assembled with M4 screws

P08##-##

Tape

Band

Bottom Packing

Box label

Pallet

Confidential

Page 36/44Revision No. 0.0 30/Mar./ 2012

Page 37

Product Specification of PDP Module

Packing movement, loading and Keeping

Packing movement, loading and Keeping

Packing movement, loading and KeepingPacking movement, loading and Keeping

- Left & right Direction of Module should be matched with direction of forklift.

- When forklift is moving into direction of module’s front and rear,

Don’t rapidly accelerate and decelerate.

- Two layer loading and Keeping.

- Humidity and temperature is maintained in sharehouse.

Forklift loading

Forklift loading

Forklift loadingForklift loading

- When module box is loaded in car, length direction of product should be

matched with Direction of forklift.

- Spare packing (under 14ea) should be loaded at last top in car and Quantity

should be written at box.

P08##-##

Direction of forklift

40 feet Container

40 feet Container

40 feet Container 40 feet Container

36 boxes (540 Modules) loading

36 boxes (540 Modules) loading

36 boxes (540 Modules) loading36 boxes (540 Modules) loading

2layer

9row

Direction of forklift.

20 feet Container

20 feet Container

20 feet Container20 feet Container

16 boxes (240 Modules) loading

16 boxes (240 Modules) loading

16 boxes (240 Modules) loading16 boxes (240 Modules) loading

2layer

4row

2column

2column

Confidential

Page 37/44Revision No. 0.0 30/Mar./ 2012

Page 38

Product Specification of PDP Module

10. PSU SPECIFICATION

P08##-##

Confidential

Page 38/44Revision No. 0.0 30/Mar./ 2012

Page 39

Product Specification of PDP Module

P08##-##

Confidential

Page 39/44Revision No. 0.0 30/Mar./ 2012

Page 40

Product Specification of PDP Module

P08##-##

Confidential

Page 40/44Revision No. 0.0 30/Mar./ 2012

Page 41

Product Specification of PDP Module

P08##-##

Confidential

Page 41/44Revision No. 0.0 30/Mar./ 2012

Page 42

Product Specification of PDP Module

P08##-##

Confidential

Page 42/44Revision No. 0.0 30/Mar./ 2012

Page 43

Product Specification of PDP Module

P08##-##

Confidential

Page 43/44Revision No. 0.0 30/Mar./ 2012

Page 44

Product Specification of PDP Module

P08##-##

Confidential

Page 44/44Revision No. 0.0 30/Mar./ 2012

Loading...

Loading...