LG W720 2 BLOCK DIAGRAM

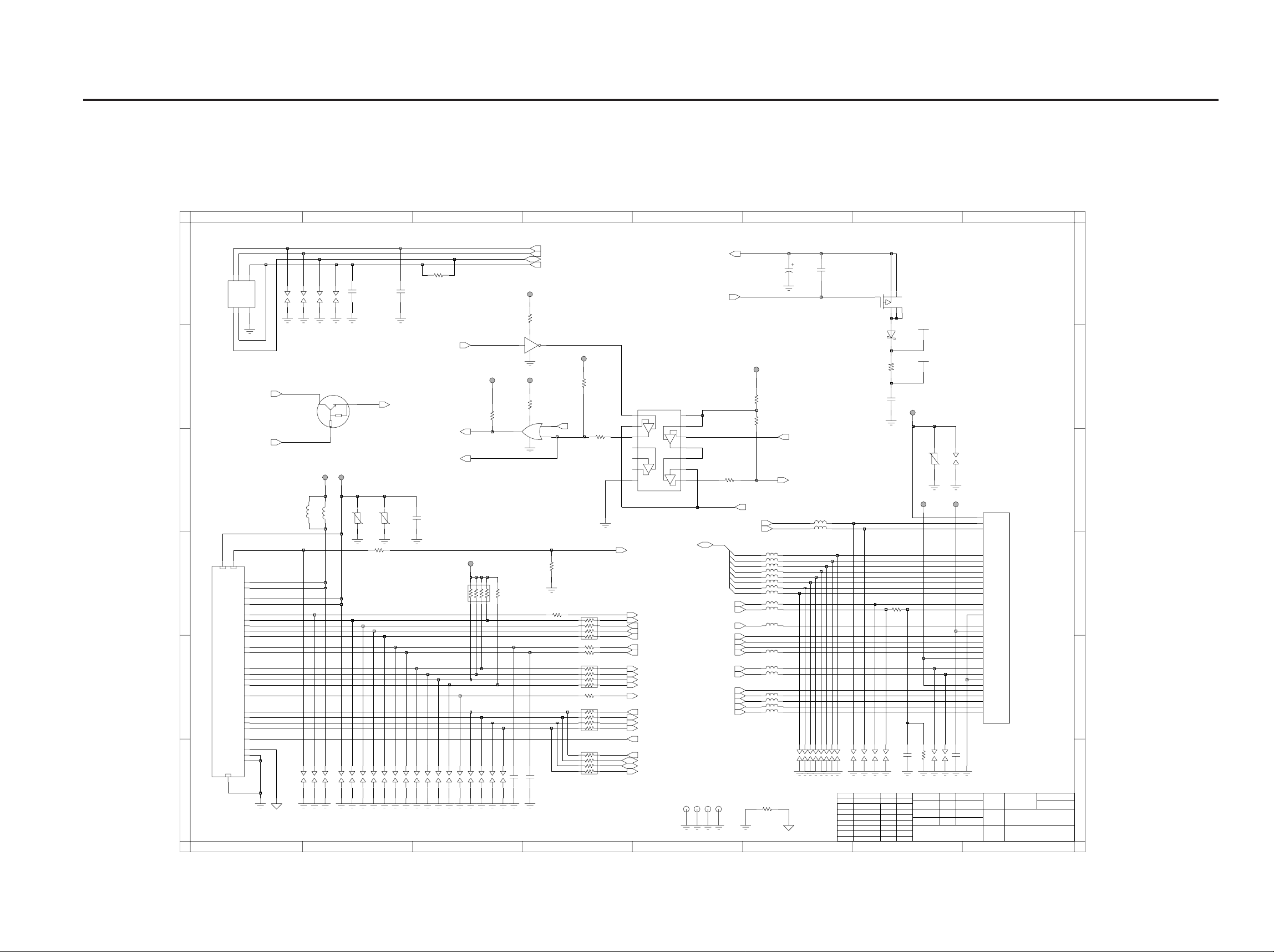

10. CIRCUIT DIAGRAM

10.1 BB Circuit

10. CIRCUIT DIAGRAM

A

LG_AMP_SIM

B

C

J100

123

2

1

3

CLK

RST

VCC

VPP

GND

IO

6

5

7

HSP100

HSP101

VCHG

L100

HSP102

OUT

IN

Q101

RN1307

VBAT

C109

HSP103

100n/16V

(2012)

GND

P0402FC12C

V100

P0402FC12C

V101

C103

150p

C105

47p

R100

20K

SN74HC1GU04DCKR

U101

VR2B

R121

10K

U103

NC7SZ32

VR2B

R117

0R

5

2

3

VR2B

R120

0R

5

4

3

J102

VDD_3.0V

MAIN_CS

(D/I)

A0

8

A

B

C

U102

5

VR2B

R119

14

VCC

13

A2

12

B2

11

O2

10

A3

9

B3

8

O3

R124

0R

R122

10K

6

C100

C101

10u/16V

A_case

22n

D100

CRS08

R116

0.2R(1%)

(2012)

0R

L104

BLM15AG121PN1

7

456

12

Q100

NDC652P

3

VBAT_2

VBAT

VCC_EXT

HSP129

V102

P0402FC12C

VBACKUP

VBAT

LG_LCD_CON_30P

1

2

3

4

4

VR2B

R118

10K

1

A0

2

1

2

R123

0R

B0

3

O0

4

A1

5

B1

6

O1

7

GND

MC74VHC126

D

E

F

L

27

26

4

VCHG2

5

VCHG1

21

BATT2

22

BATT1

24

AUXI

23

CTS

20

RTS

15

TX

14

TXD

18

AUXOP

17

AUXON

13

RXD

10

RX

3

DSR

2

HANDSFREE

6

POWER_ON

11

TDO

9

TMS

8

TCK

7

TDI

16

DCD

1

AUXGND

12

GND2

19

GND1

25

J101

LG-IO_CONN_24P

1

HSP104

HSP106

HSP107

HSP108

R101

20K

HSP110

HSP109

HSP112

HSP111

HSP113

HSP114

R103

MNR04

10K

HSP116

HSP117

VR2B

HSP118

78

HSP119

123456

HSP120

HSP121

R104

10K

HSP122

C106

47p

C107

47p

R105

100R

4.7RR107

R108 4.7R

R110

47R

n.mR113 MNR04

12

34

56

78

12

34

56

78

MNR04

(REC_N)

5

L106

L108

L110

L111

L113

L114

L190

L124

L115

L116

L117

L118

L119

L120

R115

0R

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

BLM15AG121PN1

HSP134

6234

HSP512

HSP137

issue

Notice NO. Data Name

HSP127

HSP126

R109

220R

HSP128

C108

7

47p

R114

1M

Section

Designer

Checked

Approved

HSP514

Date

02.04.11

02.04.11

LG

Electronics Inc

C110

1uF

(1608)

Sign & Name

D.S.JUNG

N.S.KIM

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

D0

D1

D2

D3

D4

D5

D6

D7

_WR

_RES

VSS

LED_EN

VBACKUP

I_LED1

I_LED2

I_LED3

EL_EN

VBAT

SUB_CS

(A2)

CS2

VSS1

VBAT1

MOTOR

RECREC+

SPKSPK+

Model

Drawing

BASEBAND INTERFACE

Name

Drawing

No.

D

E

Sheet/Sheets

F

1/6

8

- 89 -

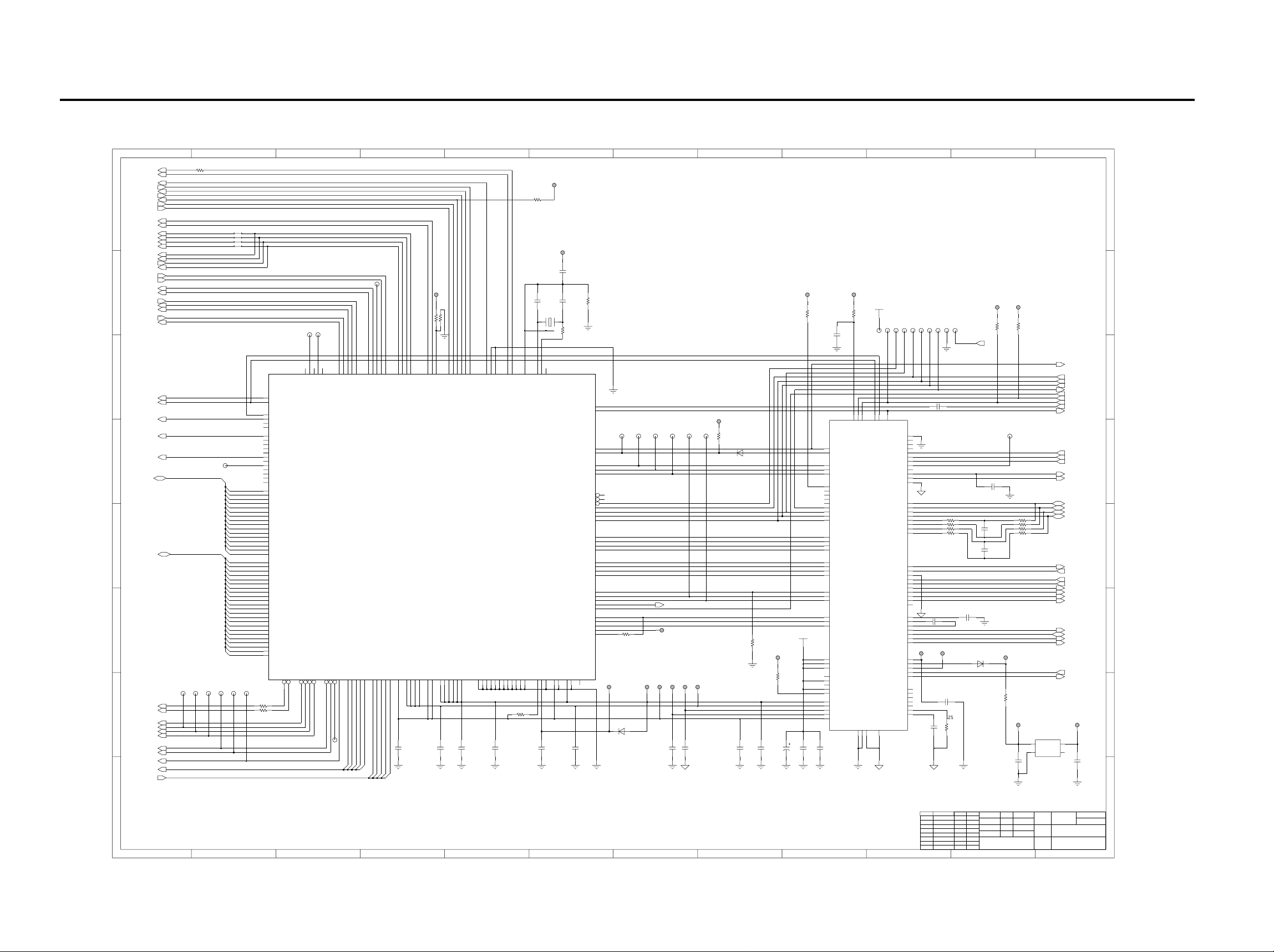

10. CIRCUIT DIAGRAM

12 8910

KEYLIGHT

LCD_RESET

JACK_DETECT

SUB_BACKLIGHT

MELODY_INT

A

SUB_LED2

SUB_LED3

SUB_LED1

MELODY_RESET

PCM_CLK

PCM_SYNC

B

RXIR_IRDA

TXIR_IRDA

FOLDER

XO_ENA

RF_ENA

PCM_RX

PCM_TX

SD_IRDA

PWT

DTR

DCD

CTS

RXD

RTS

TXD

RX

TX

0RR231

C

J14

TP214

H11

H13

H12

H14

G12

M12

M14

L12

L13

J10

K11

K13

K12

K14

J11

J12

J13

B7

D7

E7

D6

A6

C6

E6

C5

B5

D5

E5

B4

C4

D4

A3

B3

F3

F2

G5

G4

G2

G3

H1

H3

H2

H4

H5

J1

J2

J3

J4

K3

K2

K4

J5

L1

L2

L3

D2

TSPCLKX

TSPDO

TSPEN0

TSPEN1

TSPEN2

nSCS2_TSPEN3

TSPACT00

TSPACT01

TSPACT02

TSPACT03

TSPACT04

TSPACT05

TSPACT06

TSPACT07

TSPACT08

TSPACT09

TSPACT10

TSPACT11

DATA00

DATA01

DATA02

DATA03

DATA04

DATA05

DATA06

DATA07

DATA08

DATA09

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

ADD00

ADD01

ADD02

ADD03

ADD04

ADD05

ADD06

ADD07

ADD08

ADD09

ADD10

ADD11

ADD12

ADD13

ADD14

ADD15

ADD16

ADD17

ADD18

ADD19

ADD20

ADD21

ADD22

0RR227

0RR228

B2

CLK

DATA

EN

RESET_RF

PA_ON

D

TP208

D(0:15)

D(0)

D(1)

D(2)

D(3)

D(4)

D(5)

D(6)

D(7)

D(8)

D(9)

D(10)

D(11)

D(12)

TP210

TP211

TP212

D(13)

D(14)

D(15)

A(0)

A(1)

A(2)

A(3)

A(4)

A(5)

A(6)

A(7)

A(8)

A(9)

A(10)

A(11)

A(12)

A(13)

A(14)

A(15)

A(16)

A(17)

A(18)

A(19)

A(20)

A(21)

A(22)

TP213

E

A(0:22)

F

TP209

_WR

_RD

G

_CS3

_CS2

_CS1

_CS0

_BLE

_BHE

FDP

KBC(0:4)

KBR(0:4)

nFOE_X_A3

RnW_

E2

TP221

nCS3_

D3

K8

M9

SDI_SDA

SDO_INT10n

nCS1_

nCS2_

C3

C1

3

L9

P9

NSCS0_SCL

SCLK_INT1n

nCS0_

C2

TP222

N9

NSCS1_X_A2

nBLE_I_O15

F5

E4

C8

TX_IRDA

nBHE_I_O14

nFWE_X_A0

FDP_nIACK

F4

E3

FWE

D8

A8

B8

B9

C7

RX_IRDA

X_A1RXIR_IRDA

X_A4_TXIR_IRDA

CLKOUT_DSP_SD_IRDA

KBC0_NFIQN4KBC1_NIRQK5KBC2_XD1_00

KBC3_XD1_01

KBC4_XD1_02

L5

P5

M5

KBC(0)

KBC(1)

KBC(2)

KBC(3)

KBC(4)

4 6

5

TP220

VR2B

R222n.m

10K R223

L4

E8

A9

C9

D9

TX_MODEM

RX_MODEM

CTS_MODEM_XF

DSR_MODEM_LPG

RTS_MODEM_TOUT

K9

L10

N10

M10

TXD_MCSI_1_09

RXD_MCSI_1_010

FSYNCH_MCSI_1_012

CLK_MCSI_1_011

A13

A12

TCXOEN

RFEN_NoPC

N1

niBOOT

P3

N3

M4

I_O2_IRQ4

I_O0_TPU_WAIT

I_001_TPU_IDLE

N11

H10

TSPDI_I_O4

BCLKX_I_O6

I_O3_SIM_RnW

N2

M2

P11

IDDQ

ARMCLK_BCLKR

I_O7_NRESET_OUT

U200

CALYPSO

XD1_03_KBR0

XD1_04_KBR1

K6

P6

M6

KBR(0)

KBR(1)

KBR(2)

XD1_07_KBR4

XD1_05_KBR2

XD1_06_KBR3

L6

N6

KBR(3)

KBR(4)

A11

VDDS_2

C223

100n

VDDS_MIF0

A4

VDDS_MIF1G1VDDS_MIF2D1VDDS_MIF3

B6

VDDS_1_1

N5

L14

VDDS_1_2

A5

VDD0

VDD1

VDD2

VDD3

P7

B12

N14

C224

100n

GND2

GND3

C225

100n

GND0F1GND1

N8

GND4

K1

P2

P4

P10

VDD5

VDD4

E1

M1

C226

GND5

100n

7

VR2B

10KR672

VDD_RTC

C233

100p

C229

C204

D10

H10

100n

18p

F6

D7

F7

H4

F2

C8

B8

A9

B9

C7

A7

B7

A8

J5

K5

G5

H5

K7

G6

G7

H6

J6

K6

F5

B2

C4

B3

K3

D2

G9

K2

J1

H3

E2

D3

H1

E1

C1

D1

R201

220K

ON_OFF

RESPWRONZ

RTC_ALARM

INT1

INT2

TESTRESETZ

TEST1

TEST2

TEST3

TEST4

TDO

TDI

TCK

TMS

BFSX

BDX

BFSR

BDR

VDR

VDX

VFS

VCK

UDX

UDR

UEN

SDIO3

SCLK3

SRST3

VCC1

VCC2

VCC3

SWITCH

FDBK

RESERVED

VR2IN

VR2SEL

VR1OUT

VR2OUT

VR3OUT

VR1BOUT

VR2BOUT

UPR

VBAT

J4

K4

A10

F1

B10

TDR

PWON

OSCAS

RPWON

U201

NAUSICA_CS

GRND1

GRND2

GRND3

F3

K1

C2

G10

VBAT

A4

TEN

CK13M

ADIN4_TSCXP

ADIN5_TSCYP

REFGND

RPWRON

nBSCAN

LCDSYNC

TSCYM

TSCXM

ADIN1

ADIN2

ADIN3

DAC

AFC

APC

AUXGND

BDLQM

BDLQP

BDLIM

BDLIP

BULQM

BULQP

BULIM

BULIP

MICBIAS

AUXI

AGNDA1

MICIP

MICIN

EARP

EARN

AUXOP

AUXON

BUZZOP

VAUX

VS2

VS1

SVDD

SDIO5

SCLK5

SRST5

UPR

VBACKUP

VBAT

VCHG

ICTL

BGTR1

BGTR2

BGTR3

BGTR4

BGTR5

IBIAS

VREF

TDI

TDO_ARM

C5

A6

B6

B5

A5

E6

D6

C6

F10

F8

F9

G8

E10

E9

E8

E7

D9

D8

C10

C9

K9

H7

J7

K8

J8

H9

H8

J9

J10

K10

A3

A1

B1

A2

D4

B4

D5

C3

J3

E5

E4

E3

G4

G3

G2

H2

J2

G1

F4

UPR

C232

33u/6.3V

A-CASE

VBAT_2

UPR

C228

100n

R220

10K

C202

C203

20P

R224

0R

INT4n_IT_WAKEUP

MCUEN1_I_O8

MCUEN2_I_O13

SIM_CD_MAS0

SIM_PWCTRL_I_O5

VDD_PLL

GND_ANG

GND_PLL

F11

E14

CLKTCXO

ON_OFF

nRESPWON

EXT_FIQ

EXT_IRQ

NEMU0_

NEMU1_

NBSCAN_

BFSR

BFSX

VFSRX

VCLKRX

MCUDI

MCUDO

MCUEN0

SIM_IO

SIM_CLK

SIM_RST

N.C

C11

C234

10u

(2012)

R221

n.m

E13

F12

TP218

TP217

TP216

F10

D12

B14

P1

M3

B11

E10

D11

D10

TDI

C10

TDO

B10

TCK

E9

TMS

L11

K10

BDR

P12

M11

BDX

P14

VDX

N13

VDR

M13

N12

N7

M7

M8

P8

L8

G13

F13

G10

G11

F14

R208

20K

VDD_RTC

D202

1SS388

TP204

SPK_EN

VR2B

VR1

VR2B

V1B

C222

2.2u

(2012)

TP205

VR3

C219

10u

(2012)

VR2

TP206

VBACKUP

R225

1M

C220

10u

(2012)

D201

1SS388

R209

1M

C221

10u

(2012)

R211

20K

20P

X200

MC-146

4

1

3

2

L7

K7

B13

A14

C13

C12

VSSO

PWL_LTGND8

PWT_BU

OSC32K_IN

CLK32K_OUT

OSC32K_OUT

START_BIT_CLK13M_OUT

GND7

GND10

GND11

GND6

P13

G14

R229

VDDS_RTC

VDD_ANG

VDD_RTC

GND9

GND_RTC

A2

B1

A7

A10

E11

E12

D13

D14

C14

0R

C227

100n

H

1

23

4

56

7

89

10 11

100n

TMS

C218

issue

TCK

TDO

1nC205

R204 390R

R205 390R

R206 390R

C215

220n

VBATUPR

Notice NO.

GND

C216

100nC217

R219

120K

_WR

390RR207

Data

(1608)

Name

1u

1SS388

D200

11

UPR

UPR

R203

R202

10K

10K

_WR

TP219

33n

C206

R281 0R

R282 0R

C213

270p

C211

270p

VBACKUP

R226

n.m

VDD_RTC

C231

100n

Section Date Sign & Name

02.04.11

Designer

Checked

02.04.11

Approved

LG

Electronics Inc

D.S.JUNG

N.S.KIM

0RR280

0RR283

3

OUT

1

GND

Model

Drawing

Name

Drawing

No.

U202

S-817

IN

NC

12

ON_OFF

TDI

TMS

TCK

TDO

HANDSFREE

END_ON_OFF

RPWRON

13MHZ

MCLK

BATT_TEMP

RADIO_TEMP

HOOK_DETECT

AFC

PA_LEVEL

QN

QP

IN

IP

MICBIAS

AUXI

MICIP

MICIN

EARP

EARN

AUXOP

AUXON

SIM_VDD

SIM_I_O

SIM_CLK

SIM_RST

VCHG

ICTL

VBACKUP

2

4

C230

100n

Sheet/Sheets

2/6

BASEBAND CHIPSET

12

A

B

C

D

E

F

G

H

- 90 -

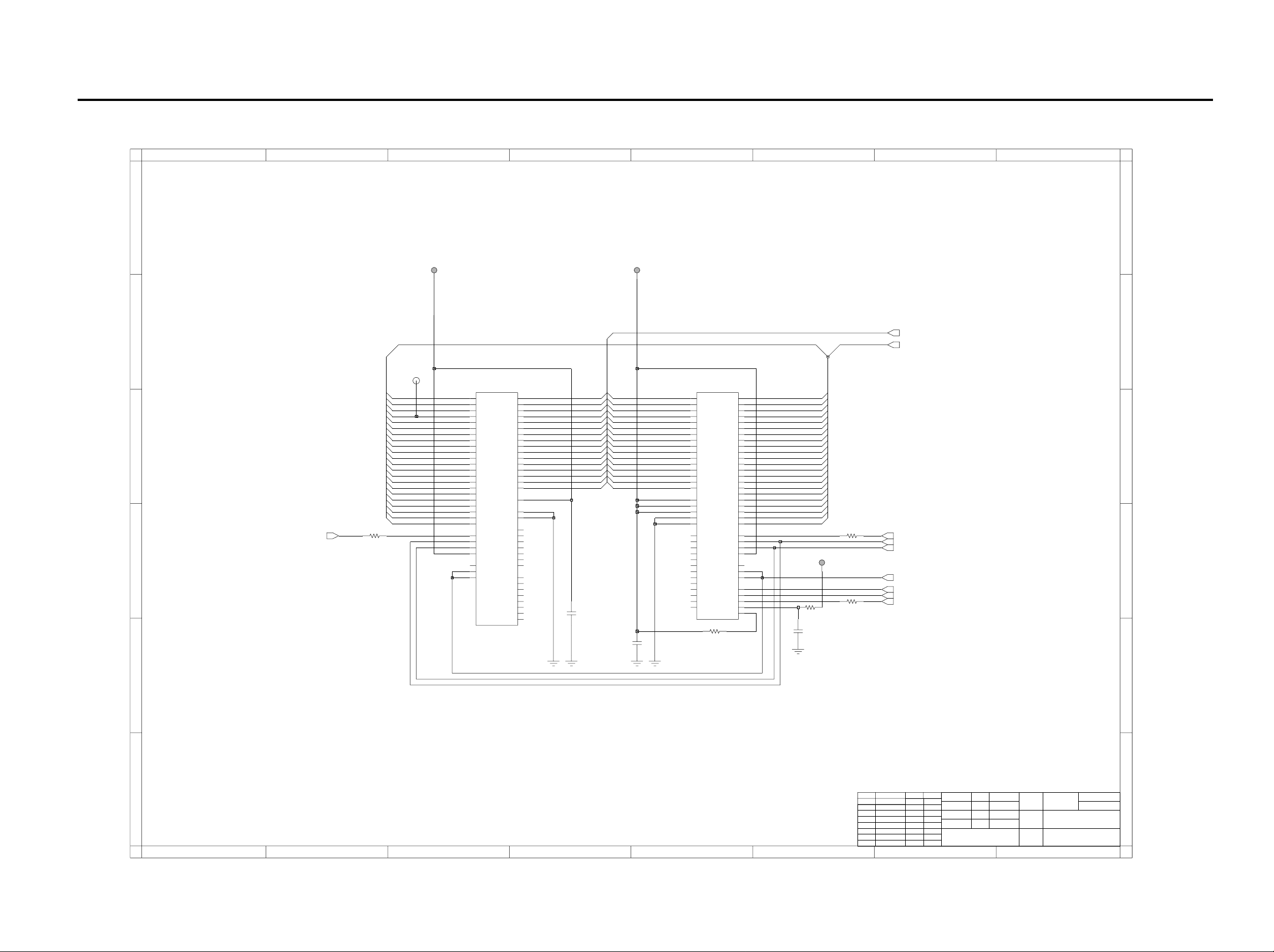

10. CIRCUIT DIAGRAM

1 52

43

6

A

VR2

VR2

B

78

D(0:15)

A

B

A(1:22)

TP301

A(1)

A(2)

A(3)

A(4)

A(5)

A(6)

A(7)

A(8)

C

R302

_CS1

A(9)

A(10)

A(11)

A(12)

A(13)

A(14)

A(15)

A(16)

A(17)

A(18)

A(19)

A(20)

A(21)

A(22)

0R

D

G2

A0

F2

A1

E2

A2

C2

A3

D2

A4

F3

A5

E3

A6

C3

A7

D6

A8

C6

A9

E6

A10

F6

A11

D7

A12

C7

A13

E7

A14

F7

A15

G7

A16

D3

A17

E4

A18

F5

A19

F4

A20

E5

A21

H2

CE_

J2

OE_

C5

WE_

H7

BYTE_

C4

RY_BY_

D4

WP_

D5

RESET_

U302

TC58FVB641

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VDD

VSS0

VSS1

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

G3

K3

G4

K4

K5

G5

K6

G6

H3

J3

H4

J4

H5

J6

H6

J7

J5

K2

K7

A1

A2

A7

A8

B1

B7

B8

L1

L2

L7

L8

M1

M2

M7

M8

C300

100n

D(0)

D(1)

D(2)

D(3)

D(4)

D(5)

D(6)

D(7)

D(8)

D(9)

D(10)

D(11)

D(12)

D(13)

D(14)

D(15)

D(0)

D(1)

D(2)

D(3)

D(4)

D(5)

D(6)

D(7)

D(8)

D(9)

D(10)

D(11)

D(12)

D(13)

D(14)

D(15)

C301

J3

DQ0

G4

DQ1

K4

DQ2

H5

DQ3

H6

DQ4

K7

DQ5

G7

DQ6

J8

DQ7

K3

DQ8

H4

DQ9

J4

DQ10

K5

DQ11

J7

DQ12

H7

DQ13

K8

DQ14

H8

DQ15

J5

VCCF

J6

VCCS

K6

DU_CIOS

J9

VSS0

G3

VSS1

A1

NC0

A10

NC1

B1

NC2

B10

NC3

C1

NC4

F1

NC5

F10

NC6

G1

NC7

G10

NC8

L1

NC9

L10

NC10

M1

NC11

M10

NC12

U301

TH50VSF4683

CEF_

OE_

WE_

BYTE_

RY_BY_

WP_

RESET_

UB_

CE1S_

CE2S_

R301 n.m

G2

A0

F2

A1

E2

A2

D2

A3

F3

A4

E3

A5

D3

A6

C3

A7

C7

A8

E7

A9

F7

A10

C8

A11

D8

A12

E8

A13

F8

A14

D9

A15

G9

A16

F4

A17

E4

A18

D7

A19

E6

A20

E9

A21

H2

H3

C6

H9

E5

C5

D5

C4

LB_

D4

J2

D6

G8

DU

A(10)

A(11)

A(12)

A(13)

A(14)

A(15)

A(16)

A(17)

A(18)

A(19)

A(20)

A(21)

A(22)

R305

10K

A(1)

A(2)

A(3)

A(4)

A(5)

A(6)

A(7)

A(8)

A(9)

VR2

R300 0R

0RR303

_CS0

_RD

_WR

FDP

_BLE

_BHE

_CS2

C

D

C304

33n

100n

E

F

123 678

45

issue Notice NO. Data Name

Section Date Sign & Name

Designer

02.04.11

02.04.11

LG

Electronics Inc

D.S.JUNG

N.S.KIM

Checked

Approved

Model

Drawing

Name

Drawing

No.

Sheet/Sheets

MEMORY DEVICE

E

F

3/6

- 91 -

Loading...

Loading...