Page 1

A

1 1

B

C

D

E

Compal Confidential

Schematics Document

2 2

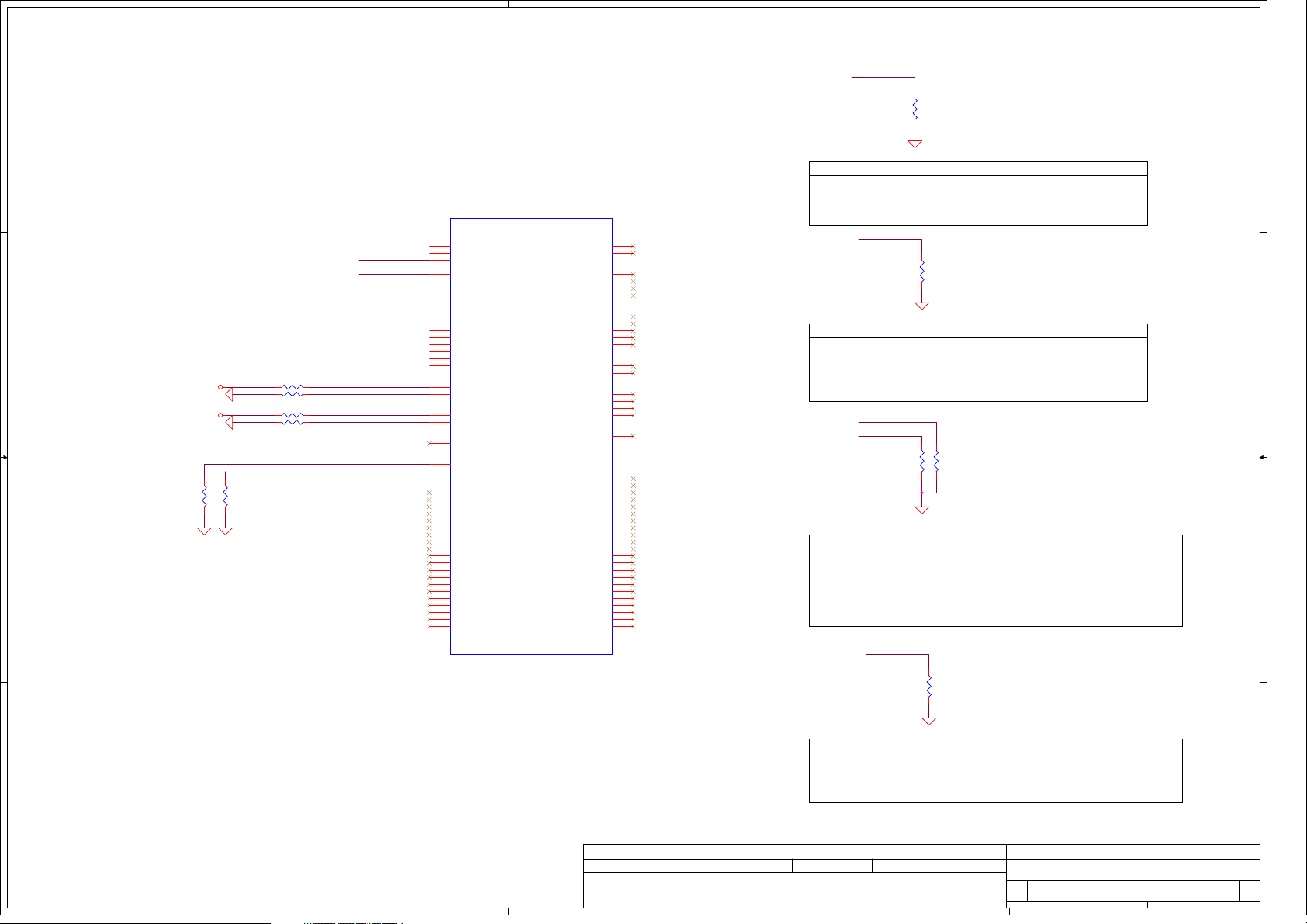

Intel Huron River Platform

Sandy Bridge (Dual Core BGA 1023) With

Couger Point Core Logic

3 3

4 4

A

B

LA-7401P

2011-03-24

REV:1.0

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/08/23 2011/08/25

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet of

Compal Electronics, Inc.

Cover Page

1 56Sunday, April 10, 20 11

E

1.0

Page 2

A

B

C

D

E

Compal Confidential

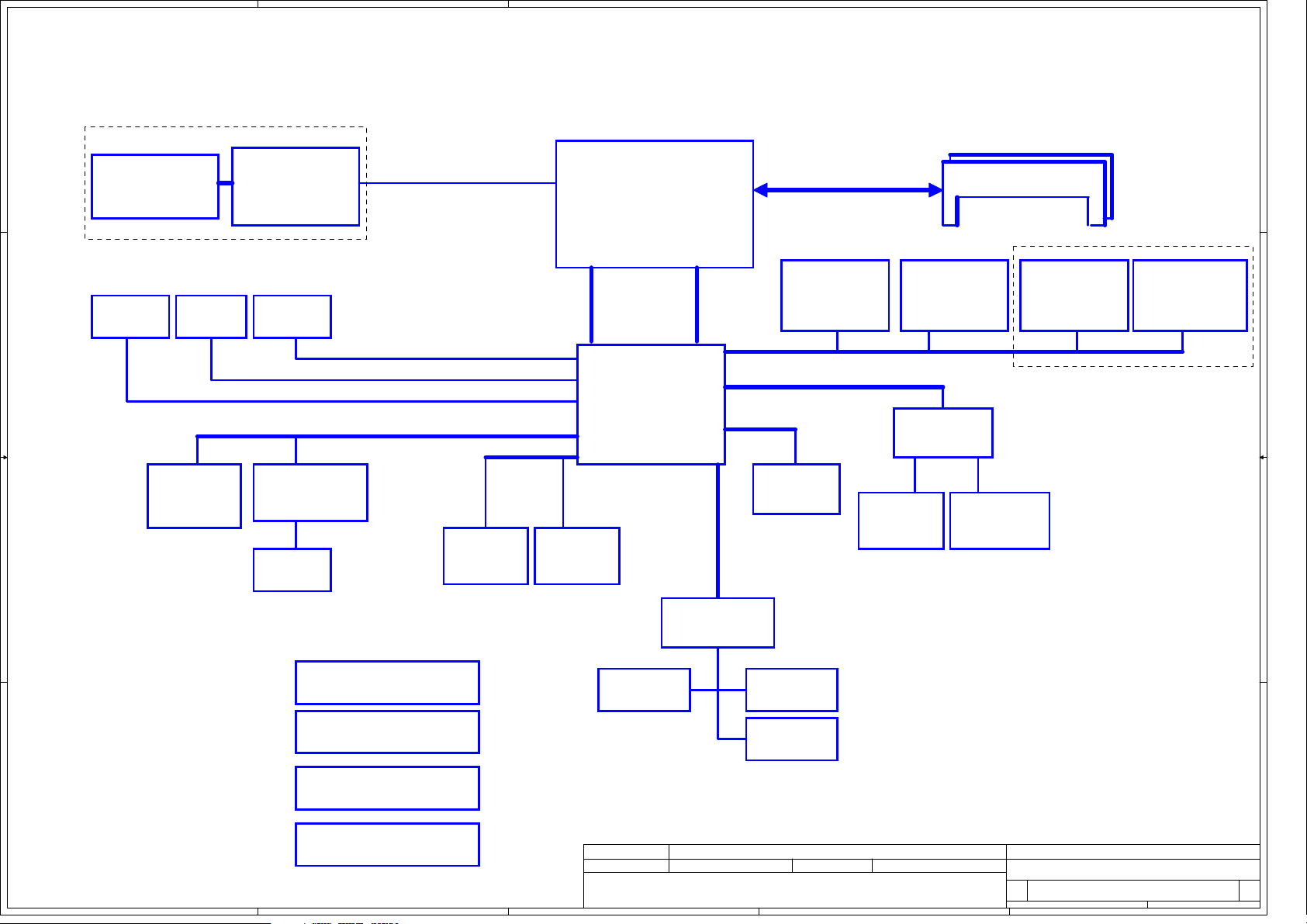

Model Name : PAJ80(14" UMA/Dis)/PAJ90(15.6" UMA/Dis)

File Name : LA-7401P

1 1

VRAM

128Mx16 4pcs=1G

64Mx16 4pcs=512M

800MHz

Page 29-32

N12P-GV

OPTIMUS SETUP

Page 22-33

PCI-E 2.0x16100MHz 5GT/s PER LANE

PEG(OPT)

Intel

Sandy Bridge

Processor

Dual Channel

DD R3-SO-DIMM X 2DDR3 1066/1333MHz 1.5V

BANK 0 , 1, 2 , 3

Page 11,12

FC BGA 1023

Optimus

FDI x8

HD MI Conn.

2 2

LV D S Conn.CR T Conn.

Page 34Page 35 Page 36

100MHz

2.7GT/s

LVDS

CRT

HDMI

PCI-Express x 8 ( PCIE2.0 2.5GT/s)

SATA x 6 (GEN1 1.5GT/S ,GEN2 3GT/S)

MINI Card x1

WLAN

USB Port 4

Page 41

LAN(GbE)

RTL8111E-VL

Page 37

SATA HDD

3 3

RJ45

Page 37

Conn.

100MHz

100MHz

SATA ODD

Conn.

Page 40Page40

31mm*24mm

Page 4-10

Intel

Cougar Point-M

PC H

98 9pin BGA

25mm*25mm

Page 13-21

DMI x4

100MHz

1GB/s x4

LPC BUS

33MHz

USB connx1

USB Port 2 USB port 3

USB charger

Page 42

USBx12

HD Audio

3.3V 48MHz

3.3V 24MHz

SPI

SPI ROM x1

4 M B

Page 13

Int. Speaker

CMOS Camera

Page 34

USB connx2

USB port 0,1

HDA Codec

ALC259

Page 38

Phone Jack x 2

Page 39 Page 39

Digital Micx1

Card Rea der

RT S5129 7 in 1

Page 42

Daughter board

USB port 10

Page 42

ENE KB930

Page 44

USB/CR daughter board

PWR BTN/Led daughter board

15.6 ODD daughter board

4 4

T/P daughter board

A

B

Touch Pad Int.KBD

Page 45

Page 45

BI OS ROM

Page 44

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/08/23 2011/08/25

Compal Secret Data

Deciphered Date

D

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

Compal Electronics, Inc.

Block Diagrams

LA-7401P

E

2 56Sunday, April 10, 20 11

1.0

Page 3

A

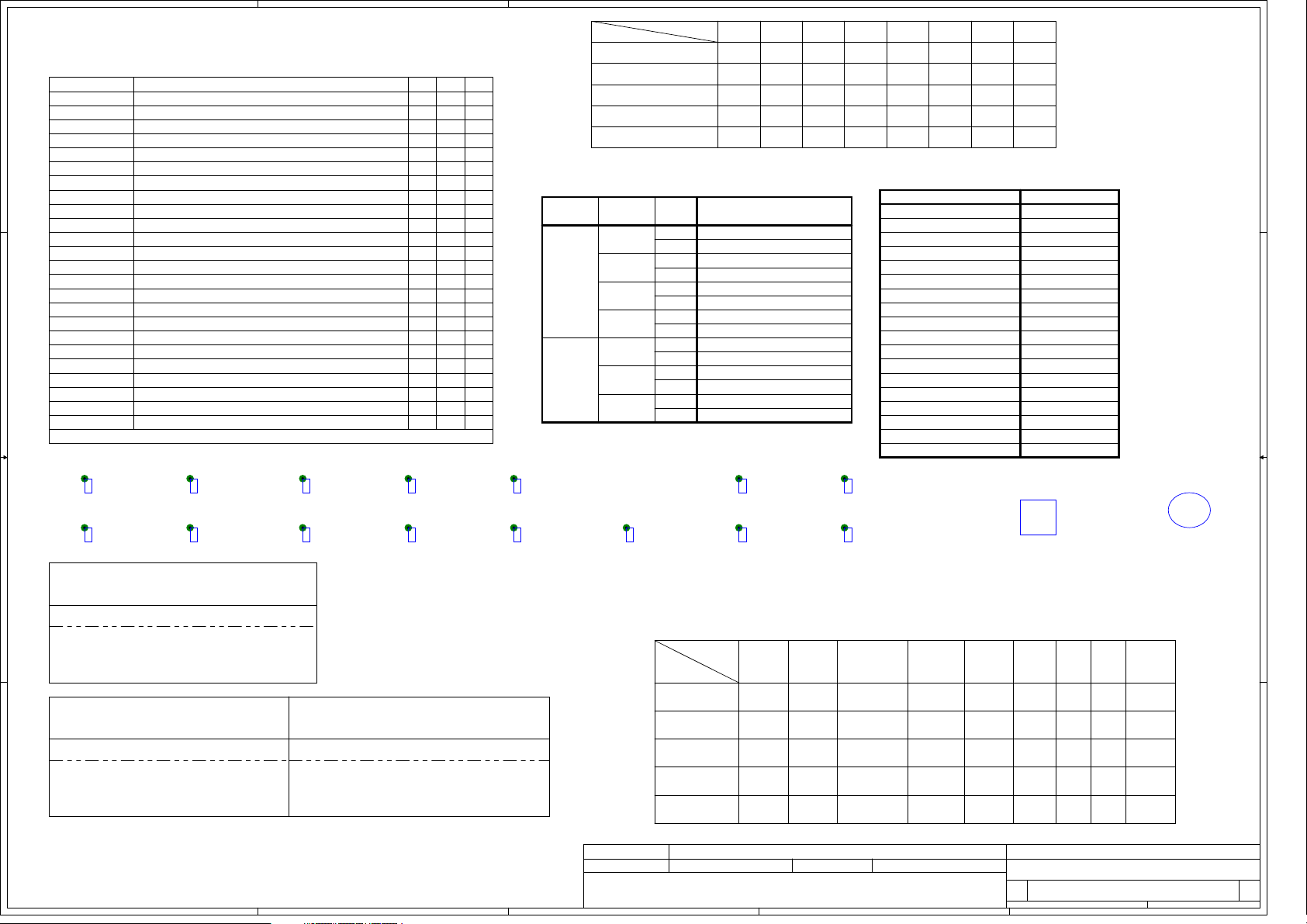

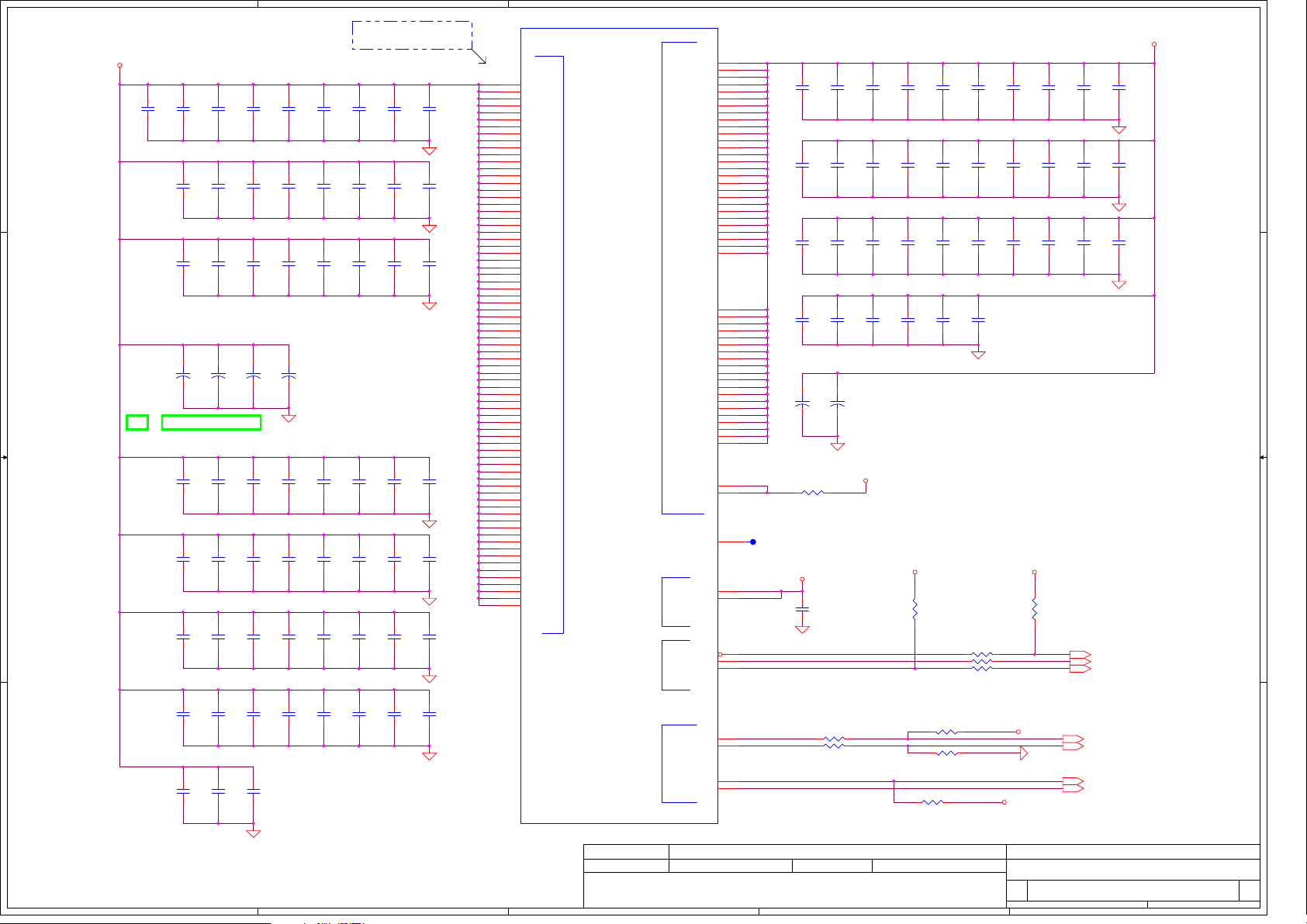

Voltage Rails

Power Plane Description

VIN

1 1

2 2

BATT+ Battery power supply (12.6V) N/A N/A N/A

B+

+CPU_CORE

+VGA_CORE Core voltage for GPU

+VGFX_CORE Core voltage for UMA graphic ON OFF OFF

+0.75VS +0.75VP to +0.75VS switched power rail for DDR terminator

+1.05VS_DGPU +1.05VS to +1.05VS_DGPU switched power rail for GPU

+1.05VS

+1.5V

+1.5VS

+VRAM_1.5VS +1.5V to +VRAM_1.5VS power rail for GPU ON OFF OFF

+1.8VS +5VALW to 1.8VS switched power rail to CPU,PCH

+3VALW +3VALW always on power rail

+3VALW_EC +3VALW always to KBC ON ON ON*

+LAN_IO

+3VALW_PCH

+3VS

+5VALW

+5VALW_PCH

+5VS +5VALW to +5VS switched power rail OFFON OFF

+VSB +VSBP to +VSB always on power rail for sequence control ON ON*

+RTCVCC RTC power

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

+VCCPP to +1.05VS switched power rail for CPU,PCH

+1.5VP to +1.5V power rail for DDRIII ON ON OFF

+1.5V to +1.5VS switched power rail

+3VALW to +LAN_IO power rail for LAN

+3VALW to +3VALW_PCH power rail for PCH (Short Jumper)

+3VALW to +3VS power rail

+5VALWP to +5VALW power rail

+5VALW to +5VALW_PCH power rail for PCH (Short resister)

B

S1

S3 S5

N/A N/A N/A

ON

ON

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON

ON

ON ON

ON ON

ON

ON

ON ON

ON

ON

N/AN/AN/A

OFF

OFF

OFF

OFF

OFF

OFF

ON ON*

ON*

ON*

OFF

OFF

ON ON*

ON*

ONON

C

STATE

Full ON

S1(P ower On Suspend)

S3 ( Suspend to RAM)

S4 ( Suspend to Disk)

S5 ( Soft OFF)

USB Port Table

USB 2.00USB 1.1

UHCI0

EHCI1

EHCI2

UHCI1

UHCI2

UHCI3

UHCI4

UHCI5

UHCI6

SIGNAL

Port

1

2

3

4

5

6

7

8

9

10

11

12

13

D

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

ON

ON

ON

ON

OFF

OFF

ON ON

ON

OFF

OFF

OFF

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

LOW LOW LOW LOW

ON

ON

ON

ON

BTO Option Table

2 External

USB Port

CONN

CONN

CONN

Camera

Mini Card(WLAN/BT)

NA

NA

NA

Card Reader

BTO Item BOM Structure

Connector CONN@

Unpop

14" PCB 14@

15.6" PCB 15@

UMA PCB UMA@

Dis PCB (Optimus) OPT@

X76 512M

X76 1G

E

LOW

OFF

OFF

OFF

OPT@Optimus

@

512M@

1G@

2540M m ean 2.6G CPU2410M m ean 2.3G CPU 2520M m ean 2.5G CPU 2310M m ean 2.2G CPU 2620M mean 2.7G CPU PCH R3 GPU R32330M m ean 2.2G CPU

U2

U2

2410MR3@

2410M CPU

U2

2410MR1@

2410M CPU

3 3

2540M CPU

U2

2540M CPU

2540MR3@

2540MR1@

U2

2520M CPU

U2

2520M CPU

2520MR3@

2520MR1@

U2

2310M CPU

U2

2310M CPU

2310MR3@

2310MR1@

U2

2620M CPU

U2

2620M CPU

2620MR3@

2620MR1@

U2

2330M CPU

2330M@

U14

PCH B3

U14

PCH B3

PCHR3@

PCHR1@

UV1

GPUR3@

GPU

UV1

GPUR1@

GPU

PCB DAZ X7613432L03

ZZZ 1

PCB_LA-7401P

ZZZ 3

X76-VRAM

1G@

PCH SM Bus Address

HEX

0001 0110 bSmart B attery

Address

1010 0000 bA0 H

EC SM Bus2 Address

PowerPower

+3VS

+3VS NVIDIA GPU

Devi ce

B

96 H

9E H

1001 0110 bPCH

1001 1110 b

SMBUS Control Table

SOURCE

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_LCD_CLK

PCH_LCD_DATA

SDVO_SCLK

SDVO_SDATA

PCH_SMBCLK

PCH_SMBDATA

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

KB930

KB930

PCH

PCH

PCH

2010/08/23 2011/08/25

BATT

V

Compal Secret Data

Deciphered Date

CPU

THERMAL

SENSOR

SODIMM 0

SODIMM 1

V

D

WLAN

WWAN

LCD

DDC

ROM

HDMI

DDC

ROM

PCH

GPU

V

V

V

V

V

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

Compal Electronics, Inc.

Notes List

E

3 56Monday, A pril 11, 2011

1.0

Power

+3VS

+3VS 1010 0100 bA4 H

Devi ce

DDR SO-DIMM 0

DDR SO-DIMM 1

EC SM Bus1 Address

Devi ce Address Address

+3VL

4 4

A

HEX HEX

16 H

Page 4

5

D D

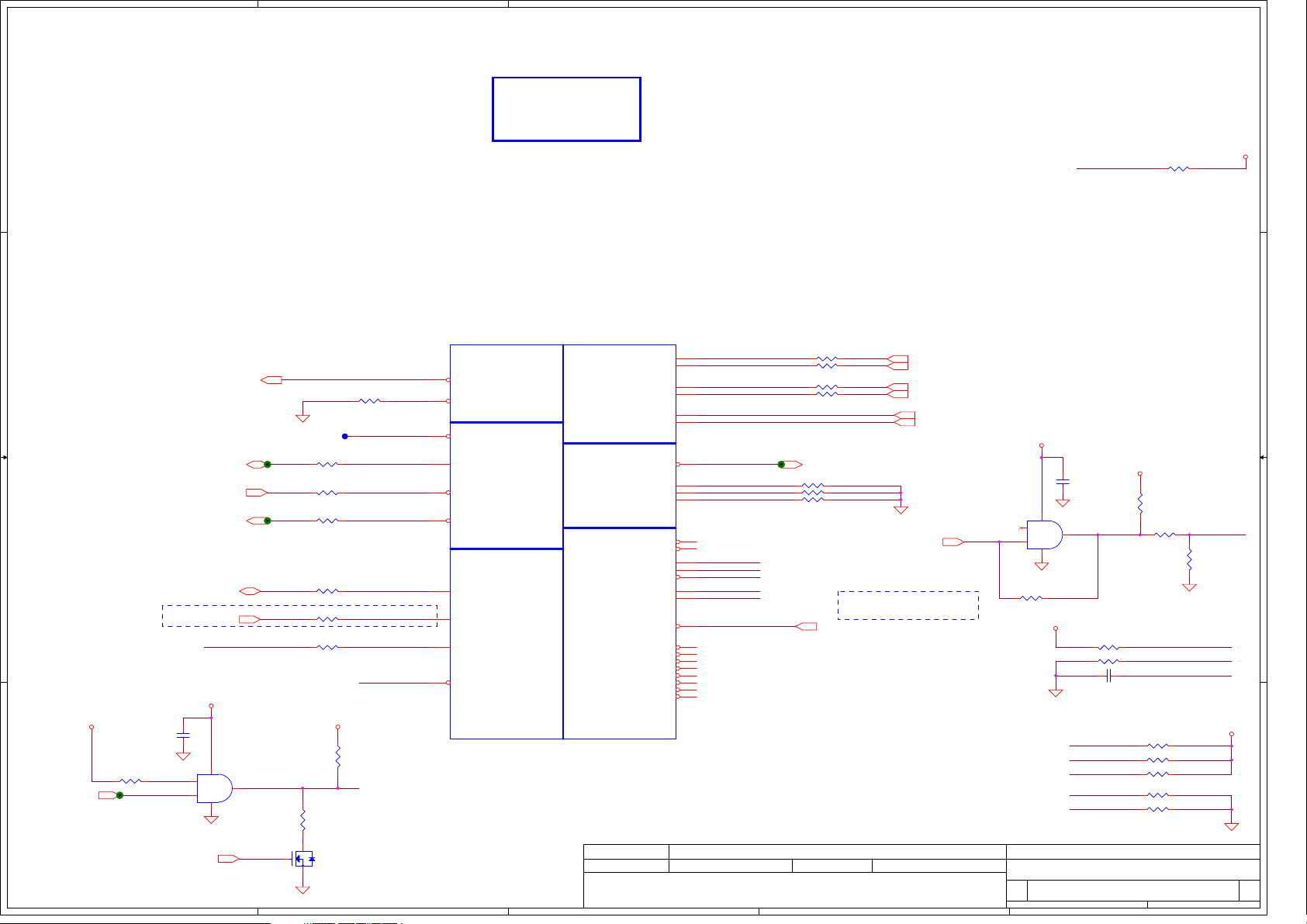

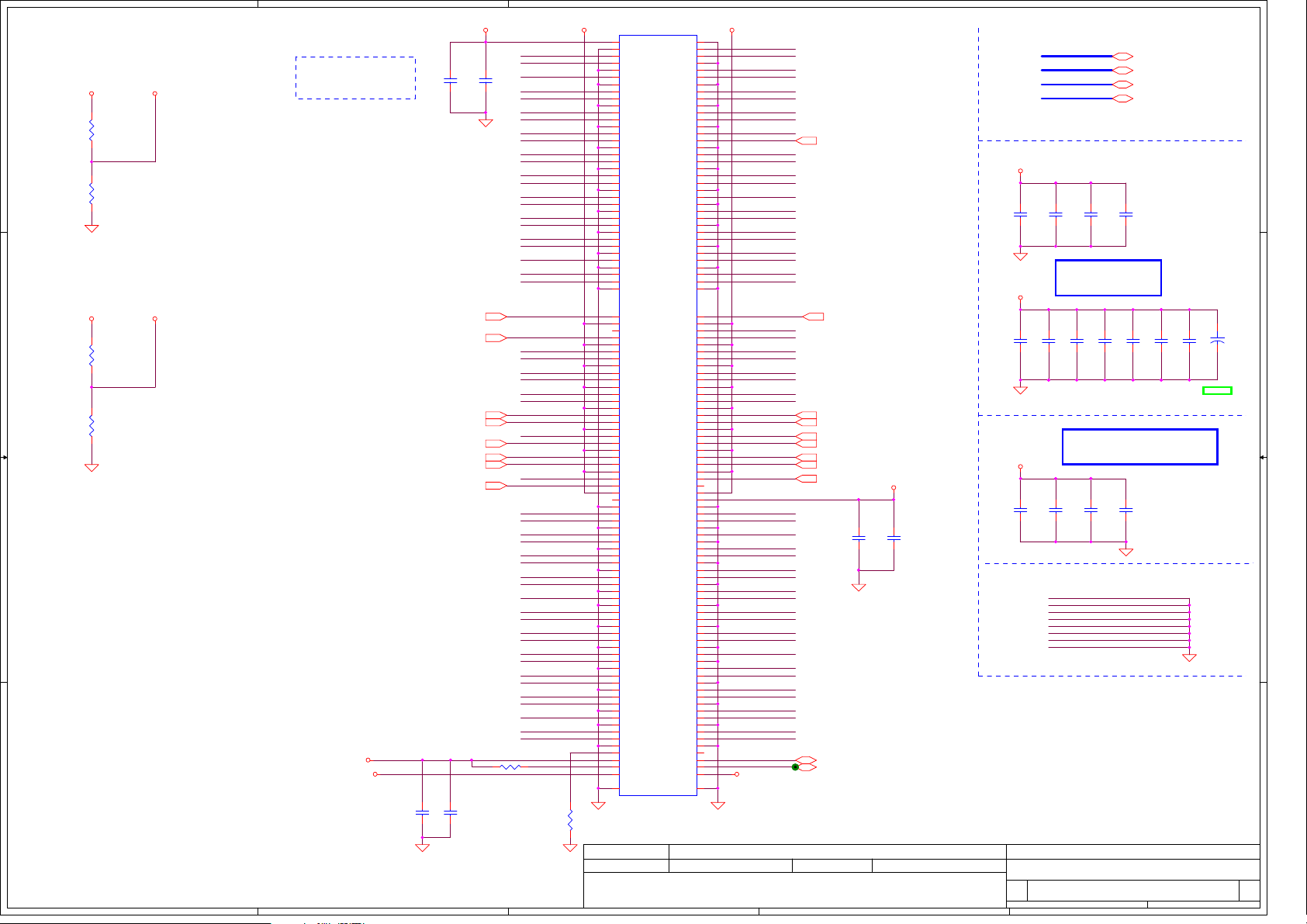

<P CH >

C C

<P CH >

+1.05VS

eDP_ COMP IO and ICO MPO signa ls

shou ld b e shorted near ball s

and routed with typ ical

impe dance < 25 mohms

B B

12

R19

24.9_0402_1%

4

U2A

DMI_CRX_PTX_N0<15>

DMI_CRX_PTX_N1<15>

DMI_CRX_PTX_N2<15>

DMI_CRX_PTX_N3<15>

DMI_CRX_PTX_P0<15>

DMI_CRX_PTX_P1<15>

DMI_CRX_PTX_P2<15>

DMI_CRX_PTX_P3<15>

DMI_CTX_PRX_N0<15>

DMI_CTX_PRX_N1<15>

DMI_CTX_PRX_N2<15>

DMI_CTX_PRX_N3<15>

DMI_CTX_PRX_P0<15>

DMI_CTX_PRX_P1<15>

DMI_CTX_PRX_P2<15>

DMI_CTX_PRX_P3<15>

FDI_CTX_PRX_N0<15>

FDI_CTX_PRX_N1<15>

FDI_CTX_PRX_N2<15>

FDI_CTX_PRX_N3<15>

FDI_CTX_PRX_N4<15>

FDI_CTX_PRX_N5<15>

FDI_CTX_PRX_N6<15>

FDI_CTX_PRX_N7<15>

FDI_CTX_PRX_P0<15>

FDI_CTX_PRX_P1<15>

FDI_CTX_PRX_P2<15>

FDI_CTX_PRX_P3<15>

FDI_CTX_PRX_P4<15>

FDI_CTX_PRX_P5<15>

FDI_CTX_PRX_P6<15>

FDI_CTX_PRX_P7<15>

FDI _FSYNC 0<15>

FDI _FSYNC 1<15>

FDI_I NT<15>

FDI _LSYNC0<15>

FDI _LSYNC1<15>

EDP_COMP

M2

DMI_RX#[0]

P6

DMI_RX#[1]

P1

DMI_RX#[2]

P10

DMI_RX#[3]

N3

DMI_RX[0]

P7

DMI_RX[1]

P3

DMI_RX[2]

P11

DMI_RX[3]

K1

DMI_TX#[0]

M8

DMI_TX#[1]

N4

DMI_TX#[2]

R2

DMI_TX#[3]

K3

DMI_TX[0]

M7

DMI_TX[1]

P4

DMI_TX[2]

T3

DMI_TX[3]

U7

FDI0_TX#[0]

W11

FDI0_TX#[1]

W1

FDI0_TX#[2]

AA6

FDI0_TX#[3]

W6

FDI1_TX#[0]

V4

FDI1_TX#[1]

Y2

FDI1_TX#[2]

AC9

FDI1_TX#[3]

U6

FDI0_TX[0]

W10

FDI0_TX[1]

W3

FDI0_TX[2]

AA7

FDI0_TX[3]

W7

FDI1_TX[0]

T4

FDI1_TX[1]

AA3

FDI1_TX[2]

AC8

FDI1_TX[3]

AA11

FDI0_FSYNC

AC12

FDI1_FSYNC

U11

FDI_INT

AA10

FDI0_LSYNC

AG8

FDI1_LSYNC

AF3

eDP_COMPIO

AD2

eDP_ICOMPO

AG11

eDP_HPD

AG4

eDP_AUX#

AF4

eDP_AUX

AC3

eDP_TX#[0]

AC4

eDP_TX#[1]

AE11

eDP_TX#[2]

AE7

eDP_TX#[3]

AC1

eDP_TX[0]

AA4

eDP_TX[1]

AE10

eDP_TX[2]

AE6

eDP_TX[3]

SAND Y-BRIDGE_BGA1023~D

PEG_RCOMPO

DMI Intel(R) FDI DP

PCI EXPRESS -- GRAPHICS

PEG_ICOMPI

PEG_ICOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

3

PEG_ICO MPI and RCOMPO signals should be

+1.05VS

12

R18

24.9_0402_1%

PEG_COMP

G3

G1

G4

PEG_GTX_C_HRX_N15

H22

PEG_GTX_C_HRX_N14

J21

PEG_GTX_C_HRX_N13

B22

PEG_GTX_C_HRX_N12

D21

PEG_GTX_C_HRX_N11

A19

PEG_GTX_C_HRX_N10

D17

PEG_GTX_C_HRX_N9

B14

PEG_GTX_C_HRX_N8

D13

PEG_GTX_C_HRX_N7

A11

PEG_GTX_C_HRX_N6

B10

PEG_GTX_C_HRX_N5

G8

PEG_GTX_C_HRX_N4

A8

PEG_GTX_C_HRX_N3

B6

PEG_GTX_C_HRX_N2

H8

PEG_GTX_C_HRX_N1

E5

PEG_GTX_C_HRX_N0

K7

PEG_GTX_C_HRX_P15

K22

PEG_GTX_C_HRX_P14

K19

PEG_GTX_C_HRX_P13

C21

PEG_GTX_C_HRX_P12

D19

PEG_GTX_C_HRX_P11

C19

PEG_GTX_C_HRX_P10

D16

PEG_GTX_C_HRX_P9

C13

PEG_GTX_C_HRX_P8

D12

PEG_GTX_C_HRX_P7

C11

PEG_GTX_C_HRX_P6

C9

PEG_GTX_C_HRX_P5

F8

PEG_GTX_C_HRX_P4

C8

PEG_GTX_C_HRX_P3

C5

PEG_GTX_C_HRX_P2

H6

PEG_GTX_C_HRX_P1

F6

PEG_GTX_C_HRX_P0

K6

PEG_HTX_GRX_N15 PEG_HTX_C_GRX_N15

G22

PEG_HTX_GRX_N14 PEG_HTX_C_GRX_N14

C23

PEG_HTX_GRX_N13 PEG_HTX_C_GRX_N13

D23

PEG_HTX_GRX_N12 PEG_HTX_C_GRX_N12

F21

PEG_HTX_GRX_N11 PEG_HTX_C_GRX_N11

H19

PEG_HTX_GRX_N10 PEG_HTX_C_GRX_N10

C17

PEG_HTX_GRX_N9 PEG_HTX_C_GRX_N9

K15

PEG_HTX_GRX_N8 PEG_HTX_C_GRX_N8

F17

PEG_HTX_GRX_N7 PEG_HTX_C_GRX_N7

F14

PEG_HTX_GRX_N6 PEG_HTX_C_GRX_N6

A15

PEG_HTX_GRX_N5 PEG_HTX_C_GRX_N5

J14

PEG_HTX_GRX_N4 PEG_HTX_C_GRX_N4

H13

PEG_HTX_GRX_N3 PEG_HTX_C_GRX_N3

M10

PEG_HTX_GRX_N2 PEG_HTX_C_GRX_N2

F10

PEG_HTX_GRX_N1 PEG_HTX_C_GRX_N1

D9

PEG_HTX_GRX_N0 PEG_HTX_C_GRX_N0

J4

PEG_HTX_GRX_P15 PEG_HTX_C_GRX_P15

F22

PEG_HTX_GRX_P14 PEG_HTX_C_GRX_P14

A23

PEG_HTX_GRX_P13 PEG_HTX_C_GRX_P13

D24

PEG_HTX_GRX_P12 PEG_HTX_C_GRX_P12

E21

PEG_HTX_GRX_P11 PEG_HTX_C_GRX_P11

G19

PEG_HTX_GRX_P10 PEG_HTX_C_GRX_P10

B18

PEG_HTX_GRX_P9 PEG_HTX_C_GRX_P9

K17

PEG_HTX_GRX_P8 PEG_HTX_C_GRX_P8

G17

PEG_HTX_GRX_P7 PEG_HTX_C_GRX_P7

E14

PEG_HTX_GRX_P6 PEG_HTX_C_GRX_P6

C15

PEG_HTX_GRX_P5 PEG_HTX_C_GRX_P5

K13

PEG_HTX_GRX_P4 PEG_HTX_C_GRX_P4

G13

PEG_HTX_GRX_P3 PEG_HTX_C_GRX_P3

K10

PEG_HTX_GRX_P2 PEG_HTX_C_GRX_P2

G10

PEG_HTX_GRX_P1 PEG_HTX_C_GRX_P1

D8

PEG_HTX_GRX_P0 PEG_HTX_C_GRX_P0

K4

Typ- suggest 220nF. The change in AC capacitor

value from 10 0nF to 220nF is to enable

compati bilit y with futu re platforms having PCIE

Gen3 (8GT/s)

C16 0.1U_0402_16V7KOPT@

1 2

C17 0.1U_0402_16V7KOPT@

1 2

C18 0.1U_0402_16V7KOPT@

1 2

C19 0.1U_0402_16V7KOPT@

1 2

C20 0.1U_0402_16V7KOPT@

1 2

C21 0.1U_0402_16V7KOPT@

1 2

C22 0.1U_0402_16V7KOPT@

1 2

C23 0.1U_0402_16V7KOPT@

1 2

C24 0.1U_0402_16V7KOPT@

1 2

C25 0.1U_0402_16V7KOPT@

1 2

C26 0.1U_0402_16V7KOPT@

1 2

C27 0.1U_0402_16V7KOPT@

1 2

C28 0.1U_0402_16V7KOPT@

1 2

C29 0.1U_0402_16V7KOPT@

1 2

C30 0.1U_0402_16V7KOPT@

1 2

C31 0.1U_0402_16V7KOPT@

1 2

C32 0.1U_0402_16V7KOPT@

1 2

C33 0.1U_0402_16V7KOPT@

1 2

C34 0.1U_0402_16V7KOPT@

1 2

C35 0.1U_0402_16V7KOPT@

1 2

C36 0.1U_0402_16V7KOPT@

1 2

C37 0.1U_0402_16V7KOPT@

1 2

C38 0.1U_0402_16V7KOPT@

1 2

C39 0.1U_0402_16V7KOPT@

1 2

C40 0.1U_0402_16V7KOPT@

1 2

C41 0.1U_0402_16V7KOPT@

1 2

C42 0.1U_0402_16V7KOPT@

1 2

C43 0.1U_0402_16V7KOPT@

1 2

C44 0.1U_0402_16V7KOPT@

1 2

C45 0.1U_0402_16V7KOPT@

1 2

C46 0.1U_0402_16V7KOPT@

1 2

C47 0.1U_0402_16V7KOPT@

1 2

shorted and routed

with - max length = 50 0 mils - typical

impedan ce = 43 mohms

PEG_ICO MPO signals should be routed w ith max len gth = 500 mils

- typical impedance = 14.5 mohms

<P EG >

2

PEG_GTX_C_H RX_N[0..15]

PEG_GTX_C_HRX_P [0..15]

PEG_HTX_C _GRX_N[0..15]

PEG_HTX_C_GRX_P [0..15]

1

PEG_GTX_C_H RX_N[0..15] <22>

PEG_GTX_C_HRX_P[0..15] <2 2>

PEG_HTX_C _GRX_N[0..15] <22>

PEG_HTX_C_GRX_P [0..15] <22>

<P EG >

A A

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/08/23 2011/08/25

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

2

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(1/7) DMI,FDI,PEG

of

1

4 56Monday, A pril 11, 2011

1.0

Page 5

5

D D

4

3

2

1

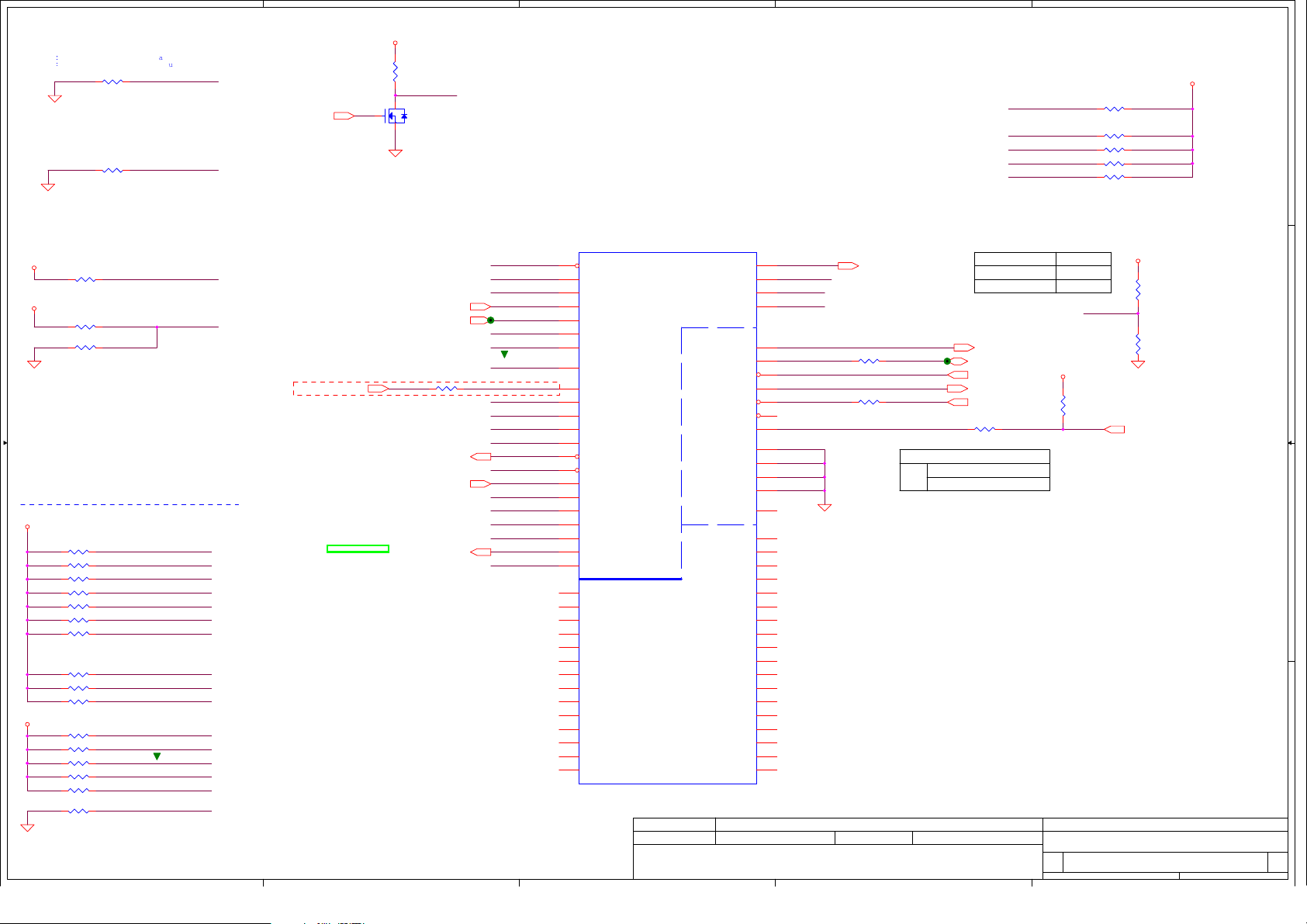

XDP_DBRESET#

R34 1K_0402_5%

+3VS

12

PVT:R emove X DP connector for ESD request

C C

H_SNB_IVB#<18>

PROC_DETECT (Processor Detect): pulled to

ground on the processor package. There is no

connection to the processor silicon for this

signal. System board designers may use this

signal to determine if the processor is present

H_PEC I<18,43>

H_PRO CHOT#<43,55>

H_THRMTRIP#<18>

B B

H_PM _SYNC<15>

H_CPU PWRGD<18>

Layout note: Route in High Speed layer to prevent EMC issue

+3VALW

+3VS

0.1U_0402_16V4Z

PM_DRAM_PWR GD<15>

A A

R2630 10K_0402_5%

5

1

C51

2

U4

74AHC1G09GW_TSSOP5

5

1

12

P

B

4

O

2

A

G

3

SUSP<46,50>

This pin is for compability with future

platforms. A pull up resistor to VCCIO is

required if connected to the DF_TVS strap

on the PCH.

R813 10K_0 402_5%

T5 P AD

1 2

R49 0_0402_5%

1 2

R50 56_0402_5%

1 2

R52 0_0402_5%

1 2

R53 0_0402_5%

1 2

R56 0_0402_5%

1 2

R59 130_0402_5%

+1.5V_ CPU_VDDQ

12

PM_SYS _PWRGD_BUF

12

R79

@

39_0402_5%

13

2

G

D

Q4

S

@

2N7002_SOT23-3

SUSP

@

1 2

H_CATERR #

H_PEC I_ISO

H_PRO CHOT#_R

H_THEMTRIP#_R

H_PM _SYNC_R

H_CPU PWRGD_R

PM_SYS _PWRGD_BUF_RPM_SYS _PWRGD_BUF

BUF_C PU_RST#

R76

200_0402_5%

4

U2B

F49

PROC_SELECT#

C57

PROC_DETECT#

C49

CATERR#

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPWRGOOD

BE45

SM_DRAMPWR OK

D44

RESET#

SAND Y-BRIDGE_BGA1023~D

MISC THERMAL PWR MANAGEMENT

CLOCKS

DDR3

JTAG & BPM

MISC

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

BCLK_ITP

BCLK_ITP#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

TRST#

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

CLK_C PU_DMI#_R

H2

CLK_C PU_DPLL_R

AG3

CLK_C PU_DPLL#_R

AG1

CLK_RES_ITP

N59

CLK_RES_ITP#

N58

H_DRAMRST#

AT30

SM_RCOMP0

BF44

SM_RCOMP1

BE43

SM_RCOMP2

BG43

DDR3 Compensation Signals

N53

N55

XDP_TCK

L56

TCK

XDP_TMS

L55

TMS

XDP_TRST#

J58

XDP_TDI

M60

TDI

XDP_TDO

L59

TDO

XDP_DBRESET#

K58

G58

E55

E59

G55

G59

H60

J59

J61

2010/08/23 2011/08/25

CLK_C PU_DMI_R

J3

1 2

R44 0_0402_5%

1 2

R45 0_0402_5%

1 2

R47 0_0402_5%

1 2

R46 0_0402_5%

H_DRAMRST# <6>

R74 140_0402_1%

R75 25.5_0402_1%

R77 200_0402_1%

12

12

12

XDP_DBRESET# <15>

Compal Secret Data

Deciphered Date

CLK_CP U_DMI <14>

CLK_CP U_DMI# <14>

CLK_CP U_DPLL <14>

CLK_CP U_DPLL# <14>

PLT_RST#<17,2 2,37,41,43>

2

CLK_RES_ITP <14>

CLK_RES_ITP# <14>

SN74L VC1G07DCKR_SC70-5

PLT_RST#

Buffered reset to CPU

+3VS

+1.05VS

12

R58

75_0402_5%@

1 2

R64

1.5K_0402_5%

Processor Pullups

12

12

12

BUF_C PU_RST#

12

R69

750_0402_1%

H_PROCH OT#

H_CPU PWRGD_R

H_CPU PWRGD_R

@

1

NC

2

A

R956

0_0402_5%

1 2

1

C50

0.1U_0402_16V4Z

2

@

5

U3

P

BUFO_ CPU_RST#

4

Y

G

3

+1.05VS

R48 62_0402_5%

R51 10K_0402_5%

@

C2580 220P_0402_50V7K

PU/PD for JTAG signals

XDP_TMS

R80 51_0402_5%@

XDP_TDI

R81 51_0402_5%@

XDP_TDO

R82 51_0402_5%@

Layout note: Close to XDP

XDP_TCK

R83 51_0402_5%@

XDP_TRST#

R84 51_0402_5%@

Compal Electronics, Inc.

Title

PROCESSOR(2/7) PM,XDP,CLK

Size Doc ument Number Re v

Cus tom

Date: Sheet of

1

+1.05VS

12

12

12

12

12

5 56Monday, A pril 11, 2011

1.0

Page 6

5

4

3

2

1

DDR_ A_D[0..63 ]<11>

D D

C C

DDR_A_BS 0<11>

B B

DDR_A_BS 1<11>

DDR_A_BS 2<11>

DDR_A _CAS#<11>

DDR_A _RAS#<11>

DDR_A_W E#<11>

DDR_A _D0

DDR_A _D1

DDR_A _D2

DDR_A _D3

DDR_A _D4

DDR_A _D5

DDR_A _D6

DDR_A _D7

DDR_A _D8

DDR_A _D9

DDR_A _D10

DDR_A _D11

DDR_A _D12

DDR_A _D13

DDR_A _D14

DDR_A _D15

DDR_A _D16

DDR_A _D17

DDR_A _D18

DDR_A _D19

DDR_A _D20

DDR_A _D21

DDR_A _D22

DDR_A _D23

DDR_A _D24

DDR_A _D25

DDR_A _D26

DDR_A _D27

DDR_A _D28

DDR_A _D29

DDR_A _D30

DDR_A _D31

DDR_A _D32

DDR_A _D33

DDR_A _D34

DDR_A _D35

DDR_A _D36

DDR_A _D37

DDR_A _D38

DDR_A _D39

DDR_A _D40

DDR_A _D41

DDR_A _D42

DDR_A _D43

DDR_A _D44

DDR_A _D45

DDR_A _D46

DDR_A _D47

DDR_A _D48

DDR_A _D49

DDR_A _D50

DDR_A _D51

DDR_A _D52

DDR_A _D53

DDR_A _D54

DDR_A _D55

DDR_A _D56

DDR_A _D57

DDR_A _D58

DDR_A _D59

DDR_A _D60

DDR_A _D61

DDR_A _D62

DDR_A _D63

U2C

AG6

SA_DQ[0]

AJ6

SA_DQ[1]

AP11

SA_DQ[2]

AL6

SA_DQ[3]

AJ10

SA_DQ[4]

AJ8

SA_DQ[5]

AL8

SA_DQ[6]

AL7

SA_DQ[7]

AR11

SA_DQ[8]

AP6

SA_DQ[9]

AU6

SA_DQ[10]

AV9

SA_DQ[11]

AR6

SA_DQ[12]

AP8

SA_DQ[13]

AT13

SA_DQ[14]

AU13

SA_DQ[15]

BC7

SA_DQ[16]

BB7

SA_DQ[17]

BA13

SA_DQ[18]

BB11

SA_DQ[19]

BA7

SA_DQ[20]

BA9

SA_DQ[21]

BB9

SA_DQ[22]

AY13

SA_DQ[23]

AV14

SA_DQ[24]

AR14

SA_DQ[25]

AY17

SA_DQ[26]

AR19

SA_DQ[27]

BA14

SA_DQ[28]

AU14

SA_DQ[29]

BB14

SA_DQ[30]

BB17

SA_DQ[31]

BA45

SA_DQ[32]

AR43

SA_DQ[33]

AW48

SA_DQ[34]

BC48

SA_DQ[35]

BC45

SA_DQ[36]

AR45

SA_DQ[37]

AT48

SA_DQ[38]

AY48

SA_DQ[39]

BA49

SA_DQ[40]

AV49

SA_DQ[41]

BB51

SA_DQ[42]

AY53

SA_DQ[43]

BB49

SA_DQ[44]

AU49

SA_DQ[45]

BA53

SA_DQ[46]

BB55

SA_DQ[47]

BA55

SA_DQ[48]

AV56

SA_DQ[49]

AP50

SA_DQ[50]

AP53

SA_DQ[51]

AV54

SA_DQ[52]

AT54

SA_DQ[53]

AP56

SA_DQ[54]

AP52

SA_DQ[55]

AN57

SA_DQ[56]

AN53

SA_DQ[57]

AG56

SA_DQ[58]

AG53

SA_DQ[59]

AN55

SA_DQ[60]

AN52

SA_DQ[61]

AG55

SA_DQ[62]

AK56

SA_DQ[63]

BD37

SA_BS[0]

BF36

SA_BS[1]

BA28

SA_BS[2]

BE39

SA_CAS#

BD39

SA_RAS#

AT41

SA_WE#

SAND Y-BRIDGE_BGA1023~D

SA_CLK[0]

SA_CLK#[0]

SA_CKE[0]

SA_CLK[1]

SA_CLK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

DDR SYSTEM MEMORY A

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AU36

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

M_CLK_DD R0

M_CLK_DDR#0

DDR_CKE 0_DIMMA

DDR_A _DQS#0

DDR_A _DQS#1

DDR_A _DQS#2

DDR_A _DQS#3

DDR_A _DQS#4

DDR_A _DQS#5

DDR_A _DQS#6

DDR_A _DQS#7

DDR_A _DQS0

DDR_A _DQS1

DDR_A _DQS2

DDR_A _DQS3

DDR_A _DQS4

DDR_A _DQS5

DDR_A _DQS6

DDR_A _DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

M_CLK_DD R0 <11>

M_CLK_DD R#0 <11>

DDR_C KE0_DIMMA <11>

M_CLK_DD R1 <11>

M_CLK_DD R#1 <11>

DDR_C KE1_DIMMA <11>

DDR_C S0_DIMMA# <11>

DDR_C S1_DIMMA# <11>

M_ODT0 <11>

M_ODT1 <11>

DDR_A _DQS#[0.. 7] <11>

DDR_ A_DQS[0.. 7] <11>

DDR_A _MA[0..15] <11>

DDR_ B_D[0..63 ]<12>

DDR_B_BS 0<12>

DDR_B_BS 1<12>

DDR_B_BS 2<12>

DDR_B _CAS#<12>

DDR_B _RAS#<12>

DDR_B _WE#<12>

DDR_B _D0

DDR_B _D1

DDR_B _D2

DDR_B _D3

DDR_B _D4

DDR_B _D5

DDR_B _D6

DDR_B _D7

DDR_B _D8

DDR_B _D9

DDR_B _D10

DDR_B _D11

DDR_B _D12

DDR_B _D13

DDR_B _D14

DDR_B _D15

DDR_B _D16

DDR_B _D17

DDR_B _D18

DDR_B _D19

DDR_B _D20

DDR_B _D21

DDR_B _D22

DDR_B _D23

DDR_B _D24

DDR_B _D25

DDR_B _D26

DDR_B _D27

DDR_B _D28

DDR_B _D29

DDR_B _D30

DDR_B _D31

DDR_B _D32

DDR_B _D33

DDR_B _D34

DDR_B _D35

DDR_B _D36

DDR_B _D37

DDR_B _D38

DDR_B _D39

DDR_B _D40

DDR_B _D41

DDR_B _D42

DDR_B _D43

DDR_B _D44

DDR_B _D45

DDR_B _D46

DDR_B _D47

DDR_B _D48

DDR_B _D49

DDR_B _D50

DDR_B _D51

DDR_B _D52

DDR_B _D53

DDR_B _D54

DDR_B _D55

DDR_B _D56

DDR_B _D57

DDR_B _D58

DDR_B _D59

DDR_B _D60

DDR_B _D61

DDR_B _D62

DDR_B _D63

U2D

AL4

SB_DQ[0]

AL1

SB_DQ[1]

AN3

SB_DQ[2]

AR4

SB_DQ[3]

AK4

SB_DQ[4]

AK3

SB_DQ[5]

AN4

SB_DQ[6]

AR1

SB_DQ[7]

AU4

SB_DQ[8]

AT2

SB_DQ[9]

AV4

SB_DQ[10]

BA4

SB_DQ[11]

AU3

SB_DQ[12]

AR3

SB_DQ[13]

AY2

SB_DQ[14]

BA3

SB_DQ[15]

BE9

SB_DQ[16]

BD9

SB_DQ[17]

BD13

SB_DQ[18]

BF12

SB_DQ[19]

BF8

SB_DQ[20]

BD10

SB_DQ[21]

BD14

SB_DQ[22]

BE13

SB_DQ[23]

BF16

SB_DQ[24]

BE17

SB_DQ[25]

BE18

SB_DQ[26]

BE21

SB_DQ[27]

BE14

SB_DQ[28]

BG14

SB_DQ[29]

BG18

SB_DQ[30]

BF19

SB_DQ[31]

BD50

SB_DQ[32]

BF48

SB_DQ[33]

BD53

SB_DQ[34]

BF52

SB_DQ[35]

BD49

SB_DQ[36]

BE49

SB_DQ[37]

BD54

SB_DQ[38]

BE53

SB_DQ[39]

BF56

SB_DQ[40]

BE57

SB_DQ[41]

BC59

SB_DQ[42]

AY60

SB_DQ[43]

BE54

SB_DQ[44]

BG54

SB_DQ[45]

BA58

SB_DQ[46]

AW59

SB_DQ[47]

AW58

SB_DQ[48]

AU58

SB_DQ[49]

AN61

SB_DQ[50]

AN59

SB_DQ[51]

AU59

SB_DQ[52]

AU61

SB_DQ[53]

AN58

SB_DQ[54]

AR58

SB_DQ[55]

AK58

SB_DQ[56]

AL58

SB_DQ[57]

AG58

SB_DQ[58]

AG59

SB_DQ[59]

AM60

SB_DQ[60]

AL59

SB_DQ[61]

AF61

SB_DQ[62]

AH60

SB_DQ[63]

BG39

SB_BS[0]

BD42

SB_BS[1]

AT22

SB_BS[2]

AV43

SB_CAS#

BF40

SB_RAS#

BD45

SB_WE#

SAND Y-BRIDGE_BGA1023~D

SB_CLK[0]

SB_CLK#[0]

SB_CKE[0]

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

DDR_B _DQS#0

DDR_B _DQS#1

DDR_B _DQS#2

DDR_B _DQS#3

DDR_B _DQS#4

DDR_B _DQS#5

DDR_B _DQS#6

DDR_B _DQS#7

DDR_B _DQS0

DDR_B _DQS1

DDR_B _DQS2

DDR_B _DQS3

DDR_B _DQS4

DDR_B _DQS5

DDR_B _DQS6

DDR_B _DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

M_CLK_DD R2 <12>

M_CLK_DD R#2 <12>

DDR_C KE2_DIMMB <12>

M_CLK_DD R3 <12>

M_CLK_DD R#3 <12>

DDR_C KE3_DIMMB <12>

DDR_C S2_DIMMB# <12>

DDR_C S3_DIMMB# <12>

M_ODT2 <12>

M_ODT3 <12>

DDR_B _DQS#[0.. 7] <12>

DDR_ B_DQS[0.. 7] <12>

DDR_B _MA[0..15] <12>

R88

@

0_0402_5%

1 2

D

S

DDR3_ DRAMRST#_RH_DRAMRST#

1 2

13

Q5

G

BSS138_NL_SOT23-3

2

0.047U_0402_16V 4Z

C52

1

2

H_DRAMRST#<5>

R91

4.99K_0402_1%

A A

DRAMRST_CNTRL

DRAMRS T_CNTRL_PCH<14>

1 2

R92 0_0402_5%

5

+1.5V

R89

1K_0402_5%

12

1 2

R90 1K_0402_5%

4

DDR3_DRA MRST# <11,12>

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/08/23 2011/08/25

Compal Secret Data

Deciphered Date

2

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(3/7) DDRIII

6 56Monday, A pril 11, 2011

1

1.0

Page 7

5

4

3

2

1

CFG Straps for Processor

CFG2

12

R94

D D

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

U2E

B50

CFG[0]

C51

CFG2

CFG4

CFG5

CFG6

CFG7

C C

@

+CPU_C ORE

+VGFX_CORE

12

12

R96

1K_0402_1%

B B

1 2

R858 49.9_0402_1%

@

R859 49.9_0402_1%

@

1 2

R860 49.9_0402_1%

@

R861 49.9_0402_1%

CPU_R SVD6

CPU_R SVD7

R97

1K_0402_1%

12

12

VCC_VAL_SENSE

VSS_VAL_SENSE

VAXG_VAL_SENSE

VSSAXG_VAL_SENSE

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

SAND Y-BRIDGE_BGA1023~D

RESERVED

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

BE7

BG7

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

Display Port Presence Strap

PCIE Port Bifurcation Straps

CFG[6:5 ]

*

CFG4

CFG4

*

1K_0402_1%

11: (Def aul t) x 16 - Devic e 1 functi ons 1 and 2 disabled

*

10: x8, x8 - Devi ce 1 funct ion 1 enab led ; func tion 2

d isabled

01: Rese rve d - (Device 1 function 1 disabled ; function

2 enabled )

00: x8,x 4,x 4 - Devi ce 1 funct ions 1 and 2 enable d

1K_0402_1%

1: N orma l O peration ; Lane # definition matches

sock et p in map def inition

0:La ne Revers ed

12

R95

@

1K_0402_1%

1 : Disa bled; No Physi cal Displa y Port

atta ched to Embe dded Displ ay Port

0 : Enab led ; An ext ernal Disp lay Port d evice is

conn ecte d to the Embed ded Displa y Port

CFG6

CFG5

12

12

R98

@

CFG7

12

@

R99

@

1K_0402_1%

R100

1K_0402_1%

PEG DEFER TRAINING

1: ( Defa ult ) PEG Train imme diately fo llowing xx RESETB

CFG7

de as sertion

A A

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/08/23 2011/08/25

Compal Secret Data

Deciphered Date

0: P EG W ait for BIOS for t raining

Title

PROCESSOR(4/7) RSVD,CFG

Size Doc ument Number Re v

Cus tom

2

Date: Sheet of

Compal Electronics, Inc.

1

7 56Sunday, April 10, 20 11

1.0

Page 8

5

1.9m[ Loadline Design

+CPU_C ORE

Mid-Frequency D eco upling

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

C761

1

1

C104

2

D D

C C

2

22U_0805_6.3V6M

C762

1

2

22U_0805_6.3V6M

C100

1

2

Low-Frequency D eco upling

330U_ D2_2V_Y

1

C105

+

2

DVT:Reserved C918 (Co-layout C106)

High-Frequency Dec oup ling

2.2U_0402_6.3V6M

C769

1

2

2.2U_0402_6.3V6M

C777

1

B B

A A

5

2

2.2U_0402_6.3V6M

C785

1

2

2.2U_0402_6.3V6M

C793

1

2

2.2U_0402_6.3V6M

C801

1

2

22U_0805_6.3V6M

C86

1

2

1

2

1

2

1

+

2

C87

1

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C94

C95

1

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C98

C99

1

2

330U_ D2_2V_Y

330U_ D2_2V_Y

1

C106

C107

+

2

DVT:Update C105 C106 C107 C108 footprint

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

C770

1

2

1

2

1

2

1

2

1

2

C771

1

2

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

C778

C779

1

2

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

C786

C787

1

2

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

C794

C795

1

2

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

C802

C803

1

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C88

1

1

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C93

1

1

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C97

1

1

2

2

330U_ D2_2V_Y

1

C108

+

Note:

2Pin 470uF PN SGA00004200

Need confirm Type with Power Team before SMT

2

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

C772

1

1

2

2

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

C780

1

1

2

2

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

C788

1

1

2

2

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

C796

1

1

2

2

22U_0805_6.3V6M

C89

1

2

22U_0805_6.3V6M

C92

1

2

22U_0805_6.3V6M

C96

1

2

2.2U_0402_6.3V6M

C773

1

2

2.2U_0402_6.3V6M

C781

1

2

2.2U_0402_6.3V6M

C789

1

2

2.2U_0402_6.3V6M

C797

1

2

4

SV type CPU

22U_0805_6.3V6M

C672

C90

C91

C101

C774

C782

C790

C798

4

1

1

2

2

22U_0805_6.3V6M

C763

1

1

2

2

22U_0805_6.3V6M

1

1

C102

2

2

2.2U_0402_6.3V6M

C775

1

1

2

2

2.2U_0402_6.3V6M

C783

1

1

2

2

2.2U_0402_6.3V6M

C791

1

1

2

2

2.2U_0402_6.3V6M

C799

1

1

2

2

3

U2F

18A

AF46

VCCIO[1]

AG48

53A

22U_0805_6.3V6M

C670

22U_0805_6.3V6M

C764

22U_0805_6.3V6M

C103

2.2U_0402_6.3V6M

C776

2.2U_0402_6.3V6M

C784

2.2U_0402_6.3V6M

C792

2.2U_0402_6.3V6M

C800

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

SAND Y-BRIDGE_BGA1023~D

CORE SUPPLY

POWER

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

VCCIO[3]

VCCIO[4]

VCCIO[5]

VCCIO[6]

VCCIO[7]

VCCIO[8]

VCCIO[9]

VCCIO[10]

VCCIO[11]

VCCIO[12]

VCCIO[13]

VCCIO[14]

VCCIO[15]

VCCIO[16]

VCCIO[17]

VCCIO[18]

VCCIO[19]

VCCIO[20]

VCCIO[21]

VCCIO[22]

VCCIO[23]

VCCIO[24]

VCCIO[25]

VCCIO[26]

VCCIO[27]

VCCIO[28]

VCCIO[29]

VCCIO[30]

VCCIO[31]

VCCIO[32]

VCCIO[33]

PEG AND DDRSENSE LINES SVID QUIET RAILS

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

AG50

AG51

AJ17

AJ21

AJ25

AJ43

AJ47

AK50

AK51

AL14

AL15

AL16

AL20

AL22

AL26

AL45

AL48

AM16

AM17

AM21

AM43

AM47

AN20

AN42

AN45

AN48

AA14

AA15

AB17

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

H_CPU _SVIDALRT#

A44

H_CPU _SVIDCLK

B43

H_CPU _SVIDDAT

C44

VCCS ENSE_R

F43

VSSSENSE_R

G43

VCCIO_S ENSE

AN16

VSS_SE NSE_VCCIO

AN17

2010/08/23 2011/08/25

Mid-Frequency D eco upling

10U_0603_6.3V6M

1

C53

2

High-Frequency Dec oup ling

1U_0402_6.3V6K

1

C68

2

1U_0402_6.3V6K

1

C503

2

1U_0402_6.3V6K

1

C721

2

Mid-Frequency D eco upling

330U_ D2_2V_Y

1

C83

+

2

1 2

R862 0_0805_5%

PAD@

T85

+1.05VS

2

C722

1U_0402_6.3V6K

1

R108 0_0402_5%

1 2

R109 0_0402_5%

1 2

Compal Secret Data

Deciphered Date

2

10U_0603_6.3V6M

1

C54

2

1U_0402_6.3V6K

1

C69

2

1U_0402_6.3V6K

1

C527

2

1U_0402_6.3V6K

1

C648

2

330U_ D2_2V_Y

1

C84

+

2

+1.05VS

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

2

1

2

1

2

1

2

C56

C55

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C71

C70

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C505

C507

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C646

C655

2

12

R102

130_0402_5%

Pla ce th e PU re si stor s cl ose to CP U

1 2

R107 100_0402_1%

1 2

R111 100_0402_1%

Pla ce th e PU re sis tors clo se t o VR

R954 10_0402_5%

1 2

@

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

2

1

2

1

2

1

2

R104 43_0402_1%

R105 0_0402_5%

R106 0_0402_5%

C57

1U_0402_6.3V6K

C72

1U_0402_6.3V6K

C509

1U_0402_6.3V6K

C647

1 2

1 2

1 2

C58

2

1U_0402_6.3V6K

1

C73

2

1U_0402_6.3V6K

1

C506

2

1U_0402_6.3V6K

1

C528

2

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C59

2

1U_0402_6.3V6K

1

C74

2

1U_0402_6.3V6K

1

C136

2

+1.05VS+1.05VS

+CPU_ CORE

12

1

C60

2

1U_0402_6.3V6K

1

C75

2

1U_0402_6.3V6K

1

C504

2

R103

75_0402_5%

1

2

1

2

1

2

+1.05VS

Compal Electronics, Inc.

PROCESSOR(5/7) PWR,BYPASS

1

+1.05VS

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C61

C62

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C508

C76

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C529

C649

2

VR_SVID_ALR T# <54>

VR_SV ID_CLK <54>

VR_SVID_DAT <54>

VCCSENS E <54>

VSSSENSE <54>

VCCIO_S ENSE <51>

VSS_SE NSE_VCCIO <51>

1

8 56Sunday, April 10, 20 11

1.0

Page 9

5

4

3

2

1

GT2 3.9mΩ Loadline Design

+VGFX_CORE

D D

C C

Mid-Frequency D eco upling

22U_0805_6.3V6M

C111

1

2

10U_0603_6.3V6M

1

C114

2

Low-Frequency D eco upling

330U_ D2_2V_Y

1

C131

+

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C112

1

2

10U_0603_6.3V6M

1

C122

2

470U_ D2_2V_Y

1

C132

+

Note:

2Pin 470uF PN SGA00004200

Need confirm Type with Power Team before SMT

2

22U_0805_6.3V6M

C113

1

2

1

2

C118

1

1

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C116

1

C115

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C120

C119

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C117

C123

2

DVT:Update C131 C132 footprint

High-Frequency Dec oup ling

1

2

1

2

B B

+VCCSA

330U_ D2_2V_Y

1

C142

+

2

Low -F req ue nc y Dec oupl ing

A A

VCC_AXG_SENSE<54>

VSS_AXG_SENSE<54>

PVT:< Memo>

5

1U_0402_6.3V6K

1U_0402_6.3V6K

C836

C835

1U_0402_6.3V6K

C841

1

1

2

2

1U_0402_6.3V6K

C842

1

1

2

2

+1.8VS

10U_0603_6.3V6M

1

2

Low -F req ue nc y Dec oupl ing

10U_0603_6.3V6M

10U_0603_6.3V6M

C143

C144

1

2

Hig h- Fre qu en cy De coup ling

1U_0402_6.3V6K

1U_0402_6.3V6K

C846

C847

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C838

C837

1

1

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C843

C844

1

1

2

2

R934 0_0402_5%

1 2

R935 0_0402_5%

1 2

10U_0603_6.3V6M

@

C916

C915

1

1

2

2

10U_0603_6.3V6M

C145

C146

1

1

2

2

1U_0402_6.3V6K

C848

C849

1

1

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C839

C840

1

2

1U_0402_6.3V6K

C845

C138

330U_ D2_2V_Y

C140

1U_0402_6.3V6K

1

+

@

2

10U_0603_6.3V6M

10U_0603_6.3V6M

C765

1

1

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C850

1

1

2

2

26A

C141

1U_0402_6.3V6K

1

2

4

6A

AA46

AB47

AB50

AB51

AB52

AB53

AB55

AB56

AB58

AB59

AC61

AD47

AD48

AD50

AD51

AD52

AD53

AD55

AD56

AD58

AD59

AE46

W50

W51

W52

W53

W55

W56

W61

BC1

BC4

W20

N45

P47

P48

P50

P51

P52

P53

P55

P56

P61

T48

T58

T59

T61

U46

V47

V48

V50

V51

V52

V53

V55

V56

V58

V59

Y48

Y61

F45

G45

BB3

L17

L21

N16

N20

N22

P17

P20

R16

R18

R21

U15

V16

V17

V18

V21

U2G

VAXG[1]

VAXG[2]

VAXG[3]

VAXG[4]

VAXG[5]

VAXG[6]

VAXG[7]

VAXG[8]

VAXG[9]

VAXG[10]

VAXG[11]

VAXG[12]

VAXG[13]

VAXG[14]

VAXG[15]

VAXG[16]

VAXG[17]

VAXG[18]

VAXG[19]

VAXG[20]

VAXG[21]

VAXG[22]

VAXG[23]

VAXG[24]

VAXG[25]

VAXG[26]

VAXG[27]

VAXG[28]

VAXG[29]

VAXG[30]

VAXG[31]

VAXG[32]

VAXG[33]

VAXG[34]

VAXG[35]

VAXG[36]

VAXG[37]

VAXG[38]

VAXG[39]

VAXG[40]

VAXG[41]

VAXG[42]

VAXG[43]

VAXG[44]

VAXG[45]

VAXG[46]

VAXG[47]

VAXG[48]

VAXG[49]

VAXG[50]

VAXG[51]

VAXG[52]

VAXG[53]

VAXG[54]

VAXG[55]

VAXG[56]

VAXG_SENSE

VSSAXG_SENSE

GRAPHI CS

LINES

1.8V R AIL

VCCPLL[1]

VCCPLL[2]

VCCPLL[3]

VCCSA[1]

VCCSA[2]

VCCSA[3]

VCCSA[4]

VCCSA[5]

VCCSA[6]

VCCSA[7]

VCCSA[8]

VCCSA[9]

VCCSA[10]

VCCSA[11]

VCCSA[12]

VCCSA[13]

VCCSA[14]

VCCSA[15]

VCCSA[16]

SAND Y-BRIDGE_BGA1023~D

SA RAIL

POWER

SENSE

+V_SM_VREF,+V_SM_VREF_CNT should

have 20 mil trace width

+V_SM_VREF_CNT +V_SM_VREF

AY43

DDR3 - 1.5V RAILS

SM_VREF

VDDQ[1]

VDDQ[2]

VDDQ[3]

VDDQ[4]

VDDQ[5]

VDDQ[6]

VDDQ[7]

VDDQ[8]

VDDQ[9]

VDDQ[10]

VDDQ[11]

VDDQ[12]

VDDQ[13]

VDDQ[14]

VDDQ[15]

VDDQ[16]

VDDQ[17]

VDDQ[18]

VDDQ[19]

VDDQ[20]

VDDQ[21]

VDDQ[22]

VDDQ[23]

VDDQ[24]

VDDQ[25]

VDDQ[26]

AJ28

AJ33

AJ36

AJ40

AL30

AL34

AL38

AL42

AM33

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

5A

C121

0.1U_0402_16V4Z

High-Frequency Dec oup ling

1U_0402_6.3V6K

1U_0402_6.3V6K

C824

C825

1

2

Mid-Frequency D eco upling

10U_0603_6.3V6M

C133

1

2

1

1

2

2

10U_0603_6.3V6M

C134

1

1

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C827

C826

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

C124

C125

1

2

R112 0_0402_ 5%

1

2

1U_0402_6.3V6K

C828

1

1

2

2

10U_0603_6.3V6M

C126

1

1

2

2

Low-Frequency D eco upling

1

+

C130

330U_2.5V_M

2

+1.5V_ CPU_VDDQ

AM28

VCCDQ[1]

AN26

VCCDQ[2]

QUIET RAILS

Issued Date

BC43

BA43

U10

D48

D49

3

VDDQ_SENSE

VSS_SENSE_VDDQ

SENSE LINES

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

Secur ity Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

C723

1U_0402_6.3V6K

2

T86PAD

T87PAD

VCCSA_SENSE

VCCS A_VID0

VCCS A_VID1

VCCS A_VID1 <52>

2010/08/23 2011/08/25

Compal Secret Data

DVT:Update C130 footprint

12

Deciphered Date

R863

10K_0402_5%

2

12

1U_0402_6.3V6K

1U_0402_6.3V6K

C829

1

2

10U_0603_6.3V6M

C127

1

2

1U_0402_6.3V6K

C830

C831

1

1

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

C129

C128

1

2

Vaxg

Can connec t to G ND if motherbo

‧‧‧‧

supports external graphics and if GFX VR is not

stuffed in a common motherboard design,

V AX

‧‧‧‧

G can be left floating in a common

motherboard d esign (Gfx VR keeps VAXG from

floating) if the VR is stuffed

VCCSA_SENSE <52>

R124

0_0402_5%@

1 2

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

+1.5V_ CPU_VDDQ

12

R113

1K_0402_1%

12

R115

1K_0402_1%

+1.5V_ CPU_VDDQ +1.5VS

1U_0402_6.3V6K

1U_0402_6.3V6K

C833

C832

1

2

ard only

Compal Electronics, Inc.

PROCESSOR(6/7) PWR

1

@

JP100

1 2

PAD-OP EN 4x4m

Need to open

9 56Sunday, April 10, 20 11

1.0

Page 10

5

4

3

2

1

+1.5V_CPU_VDDQ Source

+1.5V +1.5V_ CPU_VDDQ

Q7

B+_BIAS

D D

C C

B B

A A

U2H

A13

VSS[1]

A17

VSS[2]

A21

VSS[3]

A25

VSS[4]

A28

VSS[5]

A33

VSS[6]

A37

VSS[7]

A40

VSS[8]

A45

VSS[9]

A49

VSS[10]

A53

VSS[11]

A9

VSS[12]

AA1

VSS[13]

AA13

VSS[14]

AA50

VSS[15]

AA51

VSS[16]

AA52

VSS[17]

AA53

VSS[18]

AA55

VSS[19]

AA56

VSS[20]

AA8

VSS[21]

AB16

VSS[22]

AB18

VSS[23]

AB21

VSS[24]

AB48

VSS[25]

AB61

VSS[26]

AC10

VSS[27]

AC14

VSS[28]

AC46

VSS[29]

AC6

VSS[30]

AD17

VSS[31]

AD20

VSS[32]

AD4

VSS[33]

AD61

VSS[34]

AE13

VSS[35]

AE8

VSS[36]

AF1

VSS[37]

AF17

VSS[38]

AF21

VSS[39]

AF47

VSS[40]

AF48

VSS[41]

AF50

VSS[42]

AF51

VSS[43]

AF52

VSS[44]

AF53

VSS[45]

AF55

VSS[46]

AF56

VSS[47]

AF58

VSS[48]

AF59

VSS[49]

AG10

VSS[50]

AG14

VSS[51]

AG18

VSS[52]

AG47

VSS[53]

AG52

VSS[54]

AG61

VSS[55]

AG7

VSS[56]

AH4

VSS[57]

AH58

VSS[58]

AJ13

VSS[59]

AJ16

VSS[60]

AJ20

VSS[61]

AJ22

VSS[62]

AJ26

VSS[63]

AJ30

VSS[64]

AJ34

VSS[65]

AJ38

VSS[66]

AJ42

VSS[67]

AJ45

VSS[68]

AJ48

VSS[69]

AJ7

VSS[70]

AK1

VSS[71]

AK52

VSS[72]

AL10

VSS[73]

AL13

VSS[74]

AL17

VSS[75]

AL21

VSS[76]

AL25

VSS[77]

AL28

VSS[78]

AL33

VSS[79]

AL36

VSS[80]

AL40

VSS[81]

AL43

VSS[82]

AL47

VSS[83]

AL61

VSS[84]

AM13

VSS[85]

AM20

VSS[86]

AM22

VSS[87]

AM26

VSS[88]

AM30

VSS[89]

AM34

VSS[90]

SAND Y-BRIDGE_BGA1023~D

VSS

VSS[91]

VSS[92]

VSS[93]

VSS[94]

VSS[95]

VSS[96]

VSS[97]

VSS[98]

VSS[99]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

VSS[164]

VSS[165]

VSS[166]

VSS[167]

VSS[168]

VSS[169]

VSS[170]

VSS[171]

VSS[172]

VSS[173]

VSS[174]

VSS[175]

VSS[176]

VSS[177]

VSS[178]

VSS[179]

VSS[180]

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

R120

0_0402_5%

CPU1.5V_S3_GATE<43>

SUSP#<43,46,51>

1 2

R121

@

0_0402_5%

1 2

+3VALW

12

R118

100K_0402_5%

61

Q8A

2N7002DW-T/R7_SOT363-6

2

U2I

BG17

VSS[181]

BG21

VSS[182]

BG24

VSS[183]

BG28

VSS[184]

BG37

VSS[185]

BG41

VSS[186]

BG45

VSS[187]

BG49

VSS[188]

BG53

VSS[189]

BG9

VSS[190]

C29

VSS[191]

C35

VSS[192]

C40

VSS[193]

D10

VSS[194]

D14

VSS[195]

D18

VSS[196]

D22

VSS[197]

D26

VSS[198]

D29

VSS[199]

D35

VSS[200]

D4

VSS[201]

D40

VSS[202]

D43

VSS[203]

D46

VSS[204]

D50

VSS[205]

D54

VSS[206]

D58

VSS[207]

D6

VSS[208]

E25

VSS[209]

E29

VSS[210]

E3

VSS[211]

E35

VSS[212]

E40

VSS[213]

F13

VSS[214]

F15

VSS[215]

F19

VSS[216]

F29

VSS[217]

F35

VSS[218]

F40

VSS[219]

F55

VSS[220]

G48

VSS[221]

G51

VSS[222]

G6

VSS[223]

G61

VSS[224]

H10

VSS[225]

H14

VSS[226]

H17

VSS[227]

H21

VSS[228]

H4

VSS[229]

H53

VSS[230]

H58

VSS[231]

J1

VSS[232]

J49

VSS[233]

J55

VSS[234]

K11

VSS[235]

K21

VSS[236]

K51

VSS[237]

K8

VSS[238]

L16

VSS[239]

L20

VSS[240]

L22

VSS[241]

L26

VSS[242]

L30

VSS[243]

L34

VSS[244]

L38

VSS[245]

L43

VSS[246]

L48

VSS[247]

L61

VSS[248]

M11

VSS[249]

M15

VSS[250]

SAND Y-BRIDGE_BGA1023~D

VSS

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

12

R116

100K_0402_5%

RUN_O N_CPU1.5VS3

3

Q8B

2N7002DW-T/R7_SOT363-6

5

4

330K_0402_5%

M4

VSS[251]

M58

VSS[252]

M6

VSS[253]

N1

VSS[254]

N17

VSS[255]

N21

VSS[256]

N25

VSS[257]

N28

VSS[258]

N33

VSS[259]

N36

VSS[260]

N40

VSS[261]

N43

VSS[262]

N47

VSS[263]

N48

VSS[264]

N51

VSS[265]

N52

VSS[266]

N56

VSS[267]

N61

VSS[268]

P14

VSS[269]

P16

VSS[270]

P18

VSS[271]

P21

VSS[272]

P58

VSS[273]

P59

VSS[274]

P9

VSS[275]

R17

VSS[276]

R20

VSS[277]

R4

VSS[278]

R46

VSS[279]

T1

VSS[280]

T47

VSS[281]

T50

VSS[282]

T51

VSS[283]

T52

VSS[284]

T53

VSS[285]

T55

VSS[286]

T56

VSS[287]

U13

VSS[288]

U8

VSS[289]

V20

VSS[290]

V61

VSS[291]

W13

VSS[292]

W15

VSS[293]

W18

VSS[294]

W21

VSS[295]

W46

VSS[296]

W8

VSS[297]

Y4

VSS[298]

Y47

VSS[299]

Y58

VSS[300]

Y59

VSS[301]

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

NCTF

VSS_NCTF_11

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

2010/08/23 2011/08/25

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

Compal Secret Data

AO4728L_SO8

8

7

6

5

12

R119

Deciphered Date

1

2

3

4

1

C137

0.1U_0402_16V4Z

2

2

R117

220_0402_5%

1 2

61

RUN_O N_CPU1.5VS3#RUN_O N_CPU1.5VS3#

2

Q9A

2N7002DW-T/R7_SOT363-6

Q9A on P46

+1.5V +1.5V_ CPU_VDDQ

Title

PROCESSOR(7/7) VSS

Size Doc ument Number Re v

Cus tom

Date: Sheet

1 2

C2596 0.1U _0402_16V4Z

1 2

C2597 0.1U _0402_16V4Z

1 2

C2598 0.1U _0402_16V4Z

1 2

C2599 0.1U _0402_16V4Z

Compal Electronics, Inc.

1

10 56Monday , April 11, 2011

of

1.0

Page 11

5

All VREF traces should

have 10 mil trace width

D D

+1.5 V

12

R2 017

1K_ 0402_1%

12

R2 018

1K_ 0402_1%

C C

12

R2 609

1K_ 0402_1%

12

R2 612

1K_ 0402_1%

B B

+VR EF_D Q_DIMMA

+VR EF_C A_DIMMA+1.5 V

4

+VR EF_D Q_DIMMA +1.5V

2.2U _0603 _6.3V6K

+3VS

+0.75 VS

0.1U _0402 _16V4Z

C2 023

C2 000

1

1

2

2

DDR_ CKE0 _DIM MA<6>

DD R_A_B S2<6>

M_ CLK_D DR0<6>

M_C LK_DD R#0<6>

DD R_A_B S0<6>

DD R_A_ WE#<6>

DD R_A_ CAS#<6>

DDR_ CS1_ DIMM A#<6>

C2 042

0.1U _0402 _16V4Z

1

2

DDR_ CKE0 _DIM MA

DD R_A_ BS2

C2 043

2.2U _0603 _6.3V6K

1

2

DD R_A _D0

DD R_A _D1

DD R_A_ DM0

DD R_A _D2

DD R_A _D3

DD R_A _D8

DD R_A _D9

DD R_A_ DQS# 1

DD R_A _DQS 1

DD R_A _D10

DD R_A _D11

DD R_A _D16

DD R_A _D17

DD R_A_ DQS# 2

DD R_A _DQS 2

DD R_A _D18

DD R_A _D19

DD R_A _D24

DD R_A _D25

DD R_A_ DM3

DD R_A _D26

DD R_A _D27

DDR_ A_MA 12

DDR_ A_M A9

DDR_ A_M A8

DDR_ A_M A5

DDR_ A_M A3

DDR_ A_M A1

M _CLK_ DDR0

M _CLK_ DDR#0

DDR_ A_MA 10

DD R_A_ BS0

DD R_A _WE#

DD R_A_ CAS#

DDR_ A_MA 13

DDR_ CS1_ DIMM A#

DD R_A _D32

DD R_A _D33

DD R_A_ DQS# 4

DD R_A _DQS 4

DD R_A _D34

DD R_A _D35

DD R_A _D40

DD R_A _D41

DD R_A_ DM5

DD R_A _D42

DD R_A _D43

DD R_A _D48

DD R_A _D49

DD R_A_ DQS# 6

DD R_A _DQS 6

DD R_A _D50

DD R_A _D51

DD R_A _D56

DD R_A _D57

DD R_A_ DM7

DD R_A _D58

DD R_A _D59

12

3

VSS3

DQS#0

DQS0

VSS6

VSS8

DQ12

DQ13

VSS10

DM1

DQ14

DQ15

DQ20

DQ21

DM2

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS3

DQ30

DQ31

CKE1

VDD2

VDD4

VDD6

VDD8

VDD10

CK1#

VDD12

RAS#

VDD14

ODT0

VDD16

ODT1

VDD18

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

VTT2

+1.5 V

2

DD R_A _D4

4

DQ4

DQ5

DQ6

DQ7

A15

A14

A11

A7

A6

A4

A2

A0

CK1

BA1

S0#

NC2

SCL

G2

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

DD R_A _D5

DD R_A_ DQS# 0

DD R_A _DQS 0

DD R_A _D6

DD R_A _D7

DD R_A _D12

DD R_A _D13

DD R_A_ DM1

DD R3_DR AMRS T#

DD R_A _D14

DD R_A _D15

DD R_A _D20

DD R_A _D21

DD R_A_ DM2

DD R_A _D22

DD R_A _D23

DD R_A _D28

DD R_A _D29

DD R_A_ DQS# 3

DD R_A _DQS 3

DD R_A _D30

DD R_A _D31

DDR_ CKE1 _DIM MA

DDR_ A_MA 15

DDR_ A_MA 14

DDR_ A_MA 11

DDR_ A_M A7

DDR_ A_M A6

DDR_ A_M A4

DDR_ A_M A2

DDR_ A_M A0

M _CLK_ DDR1

M _CLK_ DDR#1

DD R_A_ BS1

DD R_A_ RAS#

DDR_ CS0_ DIMM A#

M_OD T0

M_OD T1

DD R_A _D36

DD R_A _D37

DD R_A_ DM4

DD R_A _D38

DD R_A _D39

DD R_A _D44

DD R_A _D45

DD R_A_ DQS# 5

DD R_A _DQS 5

DD R_A _D46

DD R_A _D47

DD R_A _D52

DD R_A _D53

DD R_A_ DM6

DD R_A _D54

DD R_A _D55

DD R_A _D60

DD R_A _D61

DD R_A_ DQS# 7

DD R_A _DQS 7

DD R_A _D62

DD R_A _D63

D_CK _SD ATA

D_ CK_S CLK

+0.7 5VS

DD R3_DR AMRS T# <6,12 >

DDR_ CKE1 _DIM MA <6>

M_ CLK_D DR1 <6>

M_C LK_DD R#1 <6>

DD R_A_B S1 <6>

DD R_A_ RAS# <6>

DDR_ CS0_ DIMM A# <6>

M_ODT 0 <6>

M_ODT 1 <6>

+VR EF_C A_DIMMA

2.2U _0603 _6.3V6K

C2 036

1

2

D_CK _SDA TA <12 ,14,41>

D_ CK_SC LK <12 ,14,41>

C2 037

0.1U _0402 _16V4Z

1

2

JDI MM0

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

9

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

DQS247VSS17

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26