Page 1

Internal Use Only

North/Latin America http://aic.lgservice.com

Europe/Africa http://eic.lgservice.com

Asia/Oceania http://biz.lgservice.com

PLASMA TV

SERVICE MANUAL

CHASSIS : PD43A

MODEL : 50PB690V 50PB690V-ZC

CAUTION

BEFORE SERVICING THE CHASSIS,

READ THE SAFETY PRECAUTIONS IN THIS MANUAL.

Printed in KoreaP/NO : MFL68163301 (1403-REV00)

Page 2

CONTENTS

CONTENTS .............................................................................................. 2

SAFETY PRECAUTIONS ........................................................................ 3

SPECIFICATION ....................................................................................... 4

ADJUSTMENT INSTRUCTION ................................................................ 6

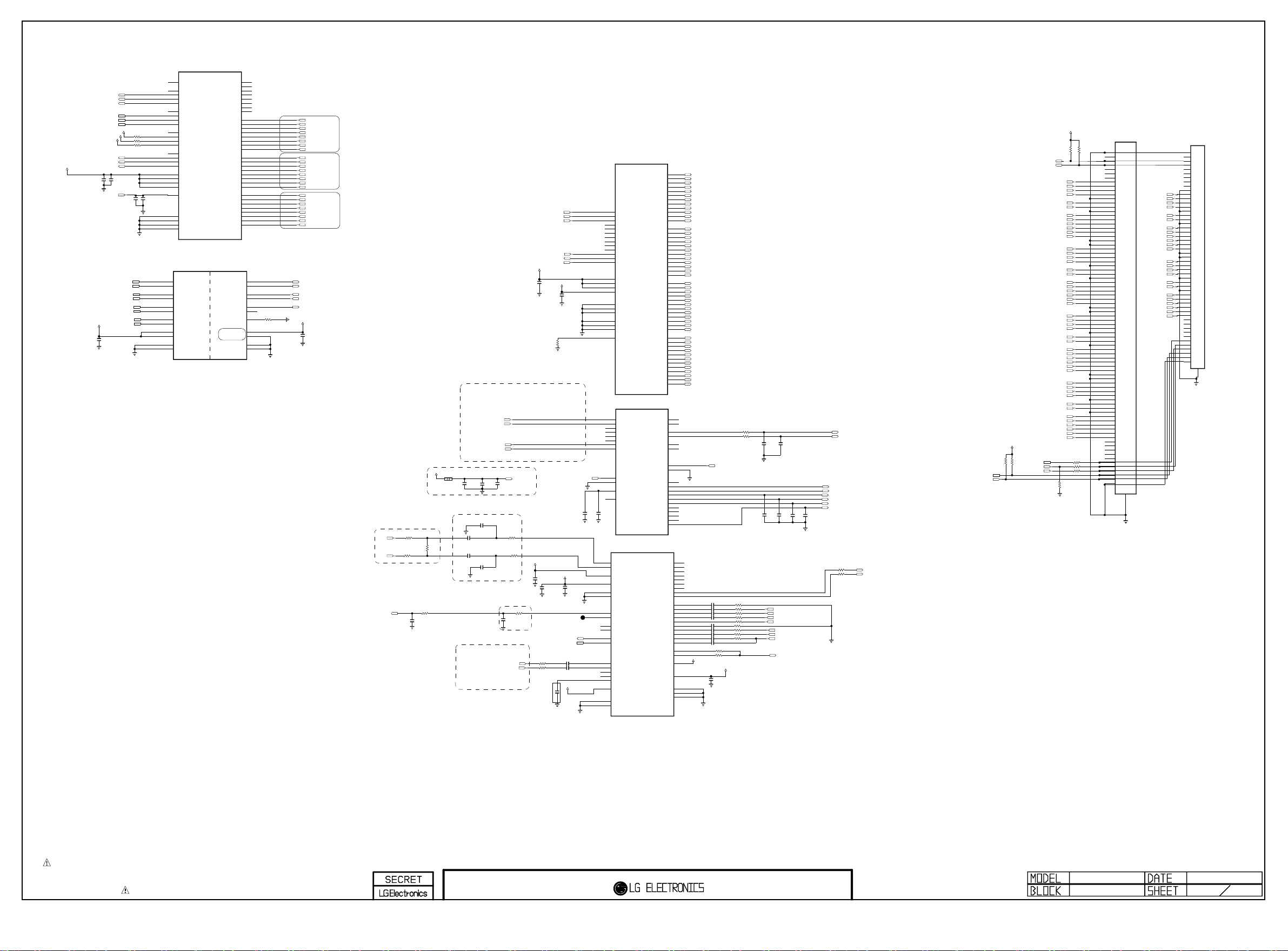

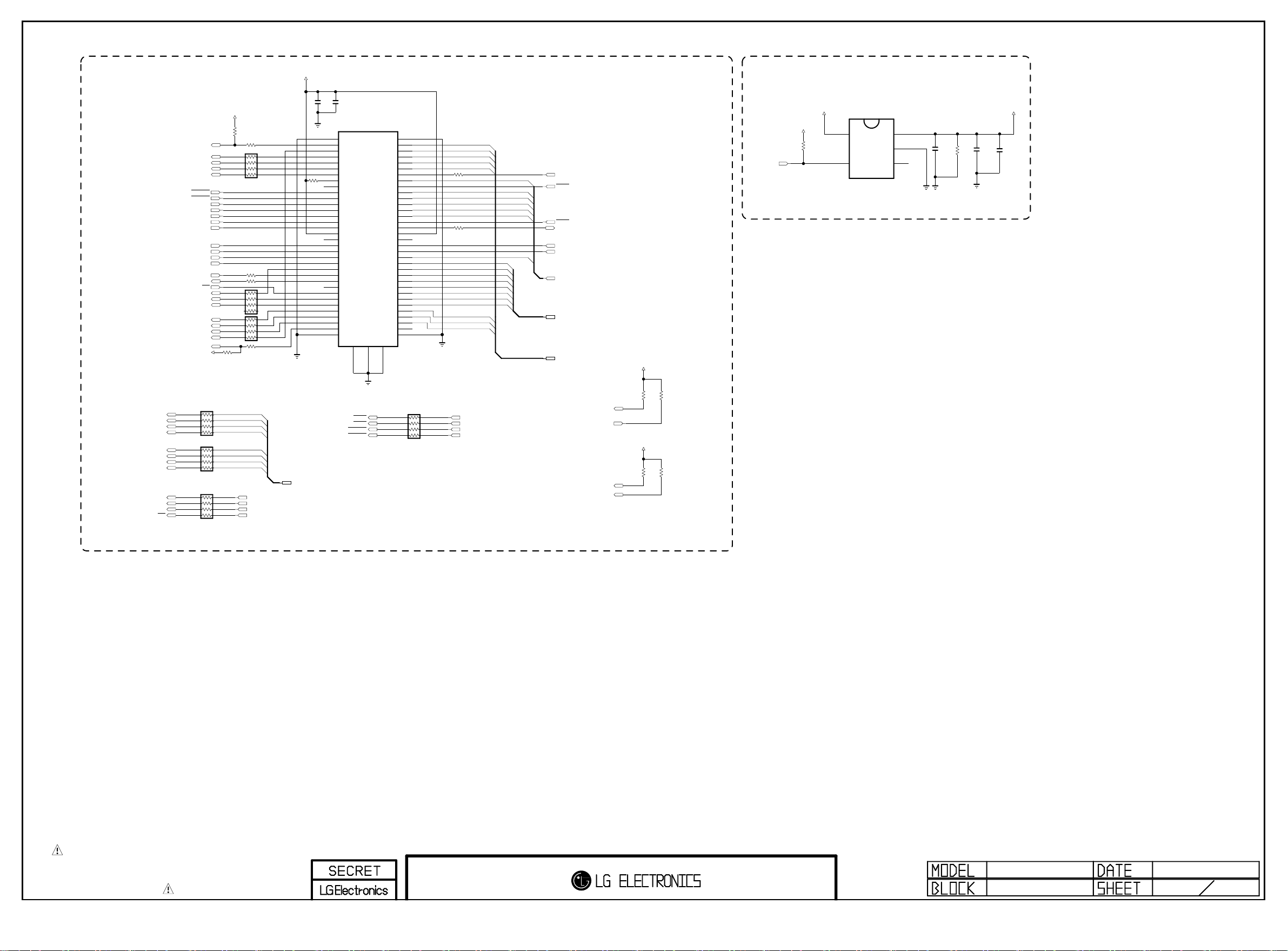

BLOCK DIAGRAM .................................................................................. 11

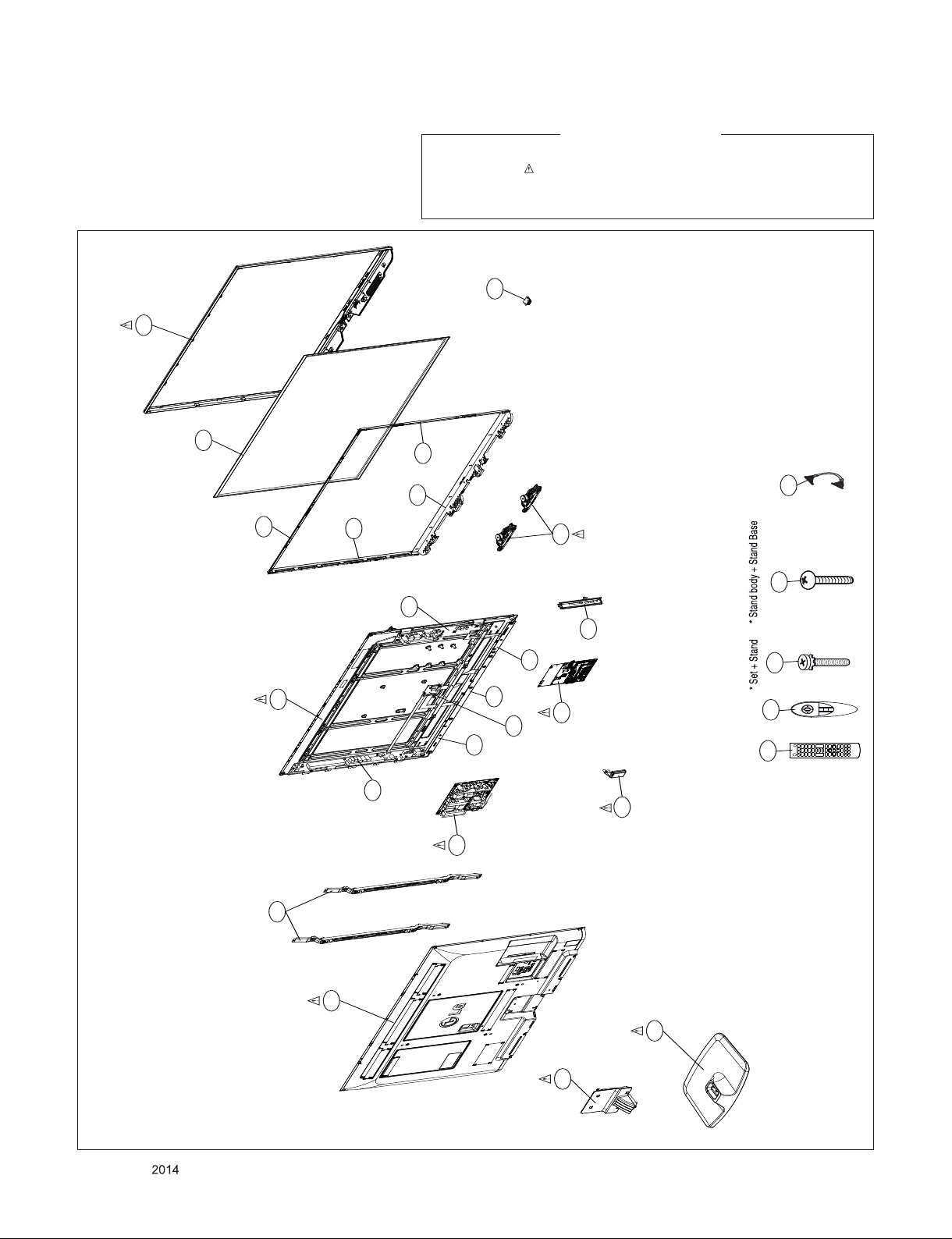

EXPLODED VIEW .................................................................................. 12

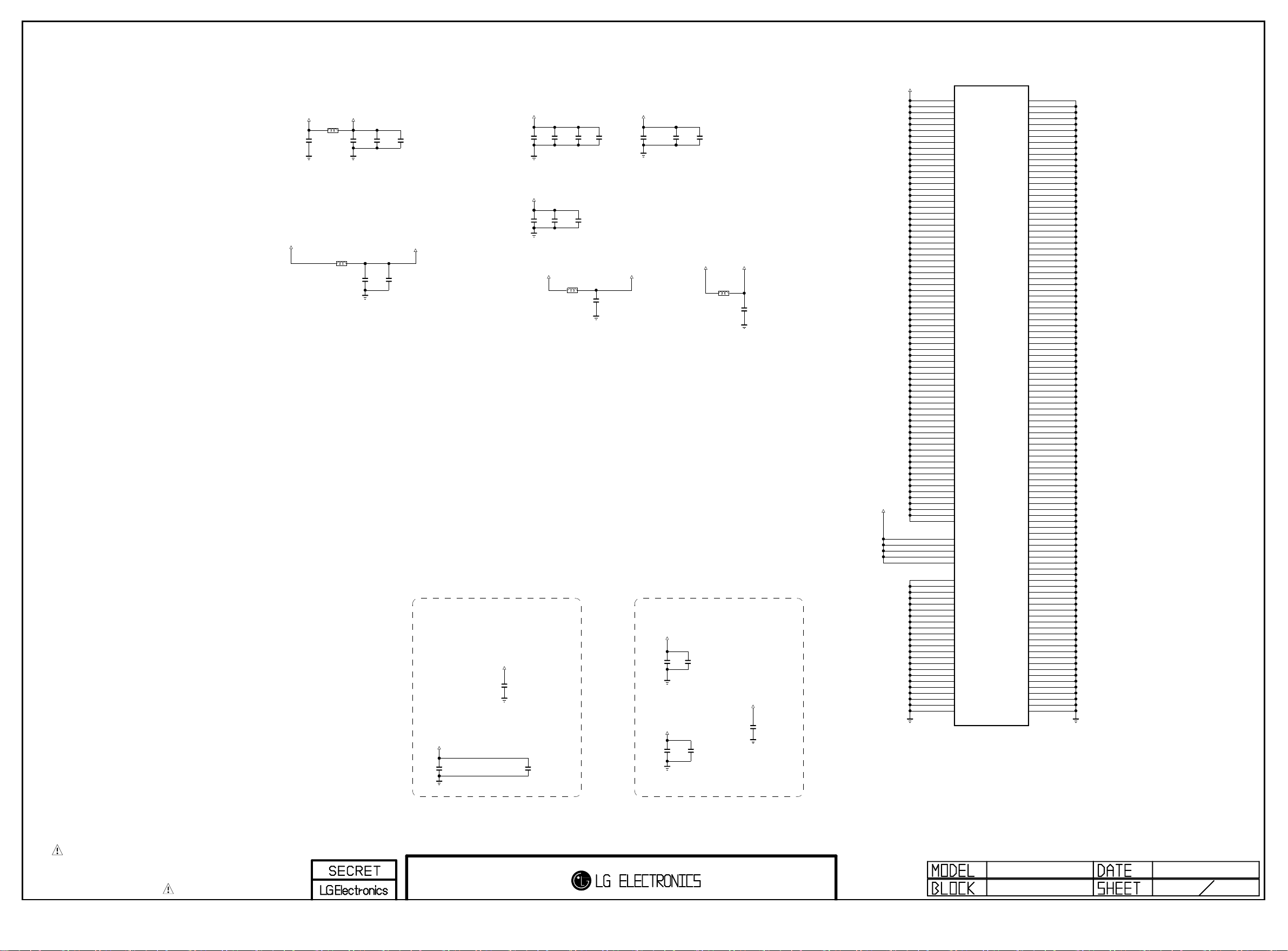

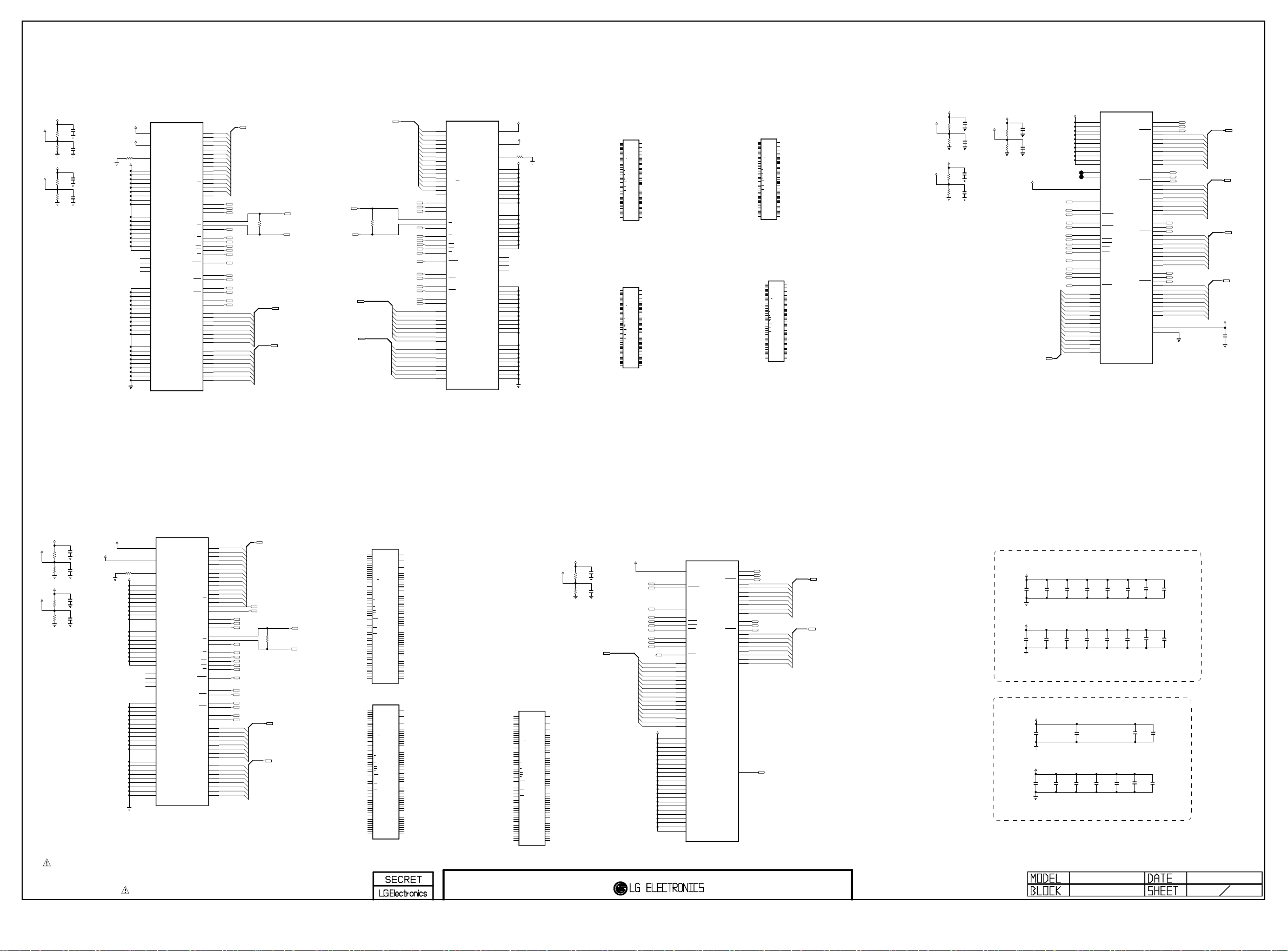

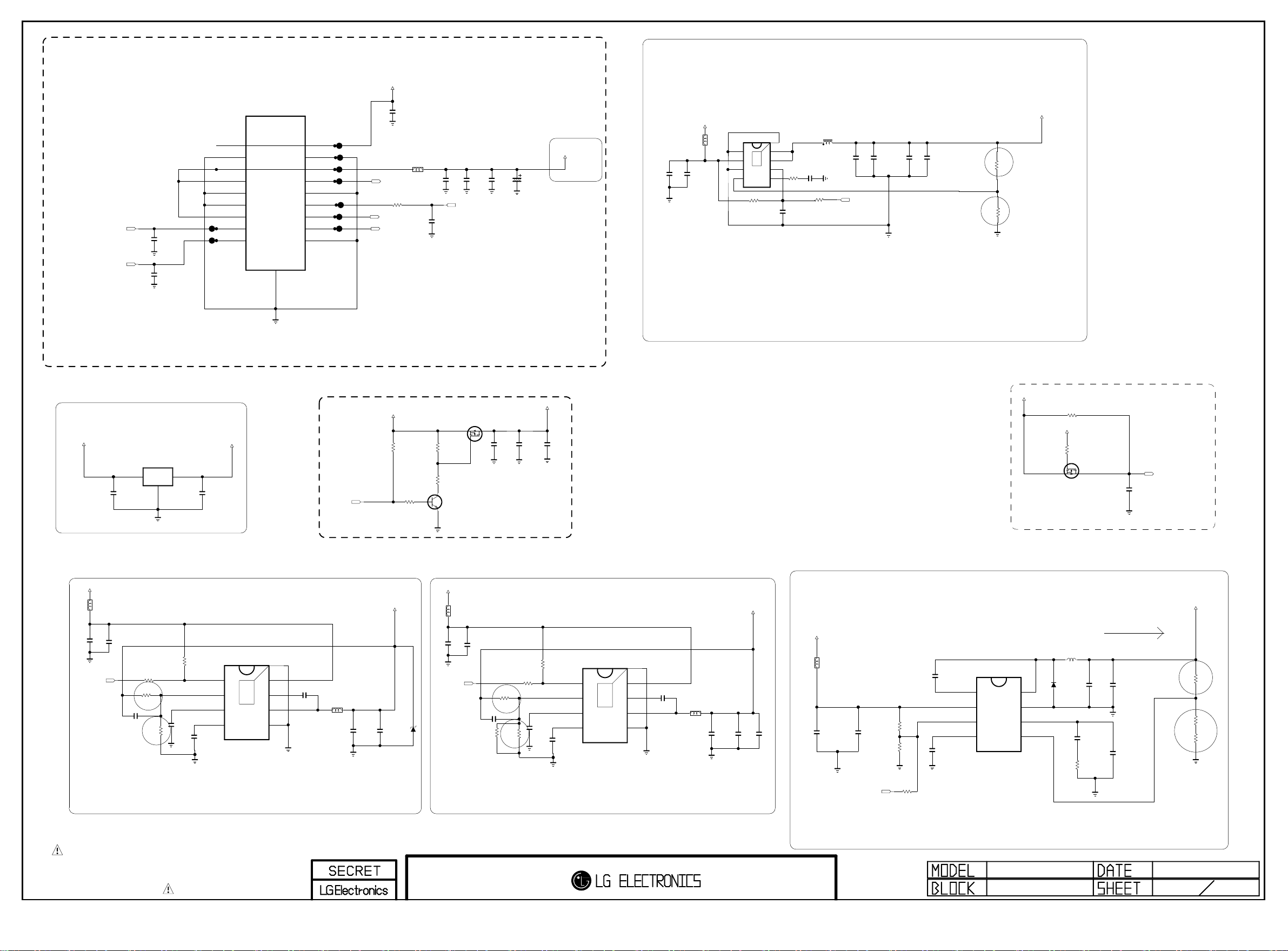

SCHEMATIC CIRCUIT DIAGRAM ..............................................................

Only for training and service purposes

- 2 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 3

AC Volt-meter

SAFETY PRECAUTIONS

IMPORTANT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These parts are identified by in the

Schematic Diagram and Exploded View.

It is essential that these special safety parts should be replaced with the same components as recommended in this manual to prevent

Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

General Guidance

An isolation Transformer should always be used during the

servicing of a receiver whose chassis is not isolated from the AC

power line. Use a transformer of adequate power rating as this

protects the technician from accidents resulting in personal injury

from electrical shocks.

It will also protect the receiver and it's components from being

damaged by accidental shorts of th e circuitry that may be

inadvertently introduced during the service operation.

If any fuse (or Fusible Resistor) in this TV receiver is blown,

replace it with the specified.

When replacing a high wattage resistor (Oxide Metal Film Resistor,

over 1 W), keep the resistor 10 mm away from PCB.

Keep wires away from high voltage or high temperature parts.

Before returning the receiver to the customer,

always perform an AC leakage current check on the exposed

metallic parts of the cabinet, such as antennas, terminals, etc., to

be sure the set is safe to operate without damage of electrical

shock.

Leakage Current Cold Check(Antenna Cold Check)

With the instrument AC plug removed from AC source, connect an

electrical jumper across the two AC plug prongs. Place the AC

switch in the on position, connect one lead of ohm-meter to the AC

plug prongs tied together and touch other ohm-meter lead in turn to

each exposed metallic parts such as antenna terminals, phone

jacks, etc.

If the exposed metallic part has a return path to the chassis, the

measured resistance should be between 1 MΩ and 5.2 MΩ.

When the exposed metal has no return path to the chassis the

reading must be infinite.

An other abnormality exists that must be corrected before the

receiver is returned to the customer.

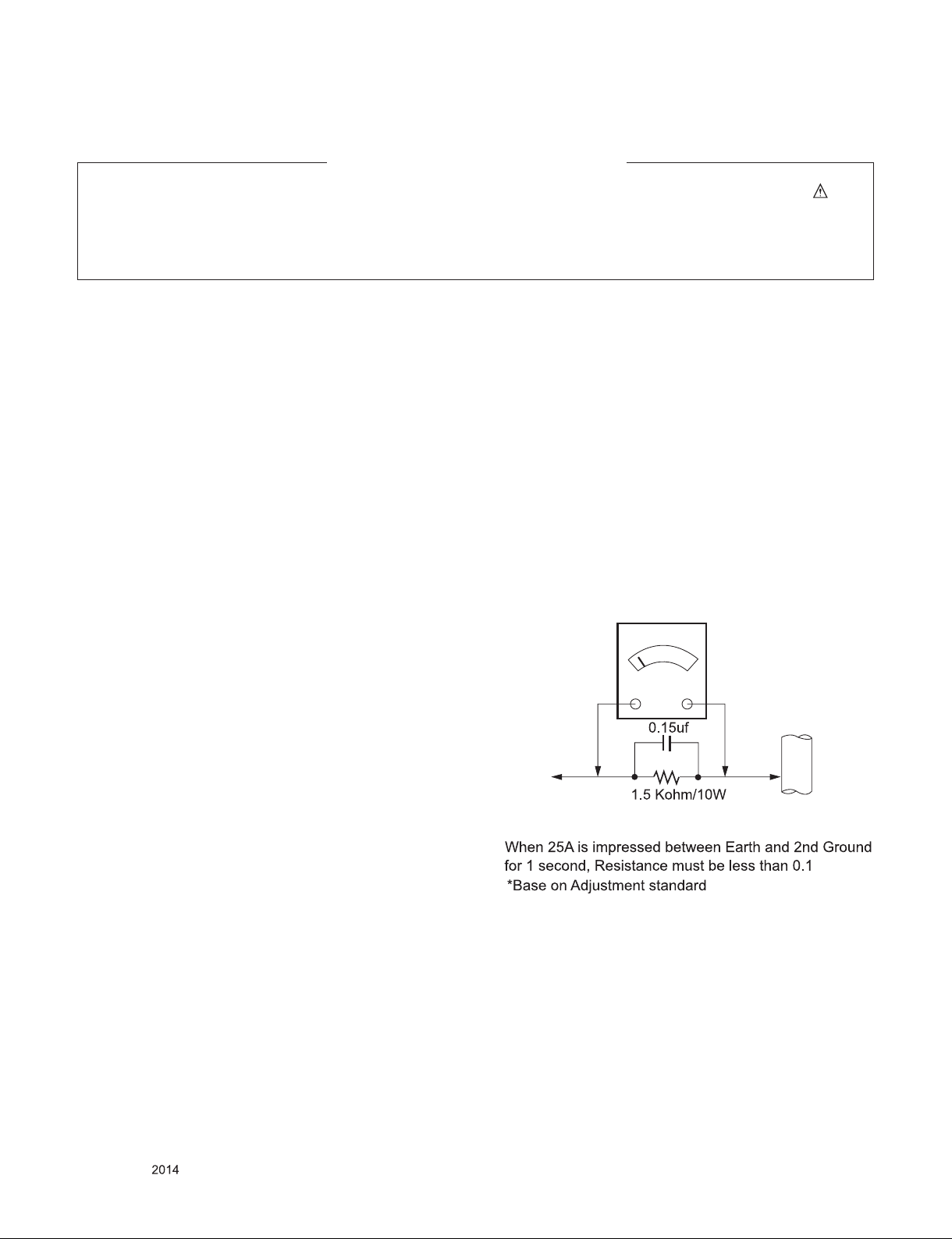

Leakage Current Hot Check (See below Figure)

Plug the AC cord directly into the AC outlet.

Do not use a line Isolation Transformer during this check.

Connect 1.5 K / 10 watt resistor in parallel with a 0.15 uF capacitor

between a known good earth ground (Water Pipe, Conduit, etc.)

and the exposed metallic parts.

Measure the AC voltage across the resistor using AC voltmeter

with 1000 ohms/volt or more sensitivity.

Reverse plug the AC cord into the AC outlet and repeat AC voltage

measurements for each exp ose d metallic par t. Any voltage

measured must not exceed 0.75 volt RMS which is corresponds to

0.5 mA.

In case any measurement is out of the limits specified, there is

possibility of shock hazard and the set must be checked and

repaired before it is returned to the customer.

Leakage Current Hot Check circuit

Good Earth Ground

such as WATER PIPE,

To Instrument's

exposed

METALLIC PARTS

CONDUIT etc.

Only for training and service purposes

- 3 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 4

SPECIFICATION

NOTE : Specifications and others are subject to change without notice for improvement

1. Application range

This spec sheet is applied all of the PDP TV with PD43A chassis.

2. Requirement for Test

Each part is tested as below without special appointment.

(1) Temperature: 25 °C ± 5 °C(77 °F ± 9 °F), CST: 40 °C ± 5 °C

(2) Relative Humidity: 65 % ± 10 %

(3) Power Voltage

: Standard input voltage (AC 100-240 V~, 50/60 Hz)

* Standard Voltage of each products is marked by models.

(4) Specification and performance of each parts are followed each drawing and specification by part number in accordance with

BOM.

(5) The receiver must be operated for about 5 minutes prior to the adjustment.

3. Test method

(1) Performance: LGE TV test method followed

(2) Demanded other specification

- Safety : CE, IEC specification

- EMC : CE, IEC

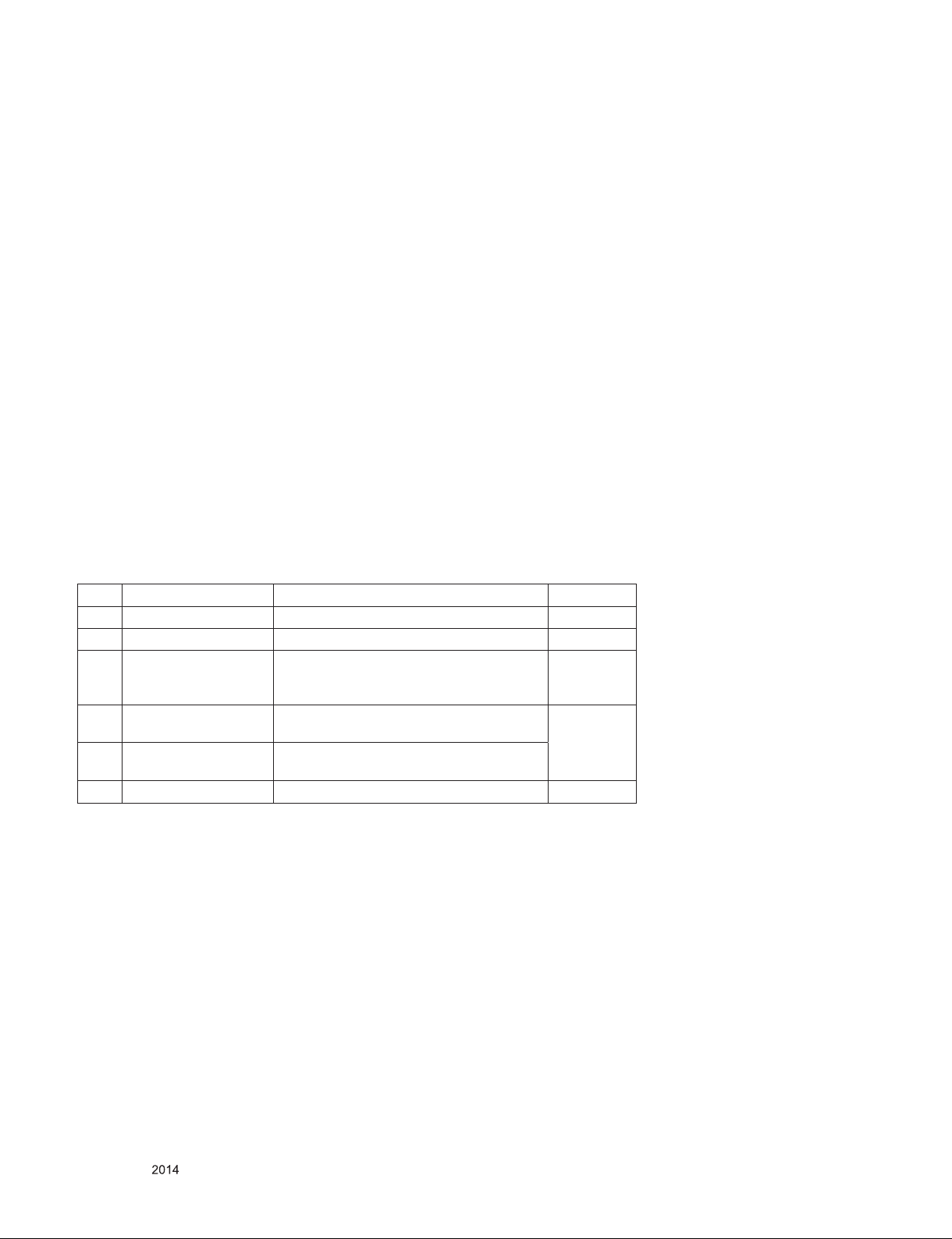

4. Module General Specification

- 50" FHD

No Item Specication Remark

1 Display Screen Device 127 cm (50 inch) wide Color Display Module PDP

2 Aspect Ratio 16:9

3 PDP Module PDP50R6####,

RGB Closed (Well) Type, Glass Filter (43%)

Pixel Format: 1920 horiz. By 1080 ver.

4 Operating Environment 1) Temp. : 0 ~ 40 deg

2) Humidity : 20 ~ 80%

5 Storage Environment 3) Temp. : -20 ~ 60 deg

4) Humidity : 10 ~ 90 %

6 Input Voltage AC220 ~ 240V, 50/60Hz Maker LG

.

LGE SPEC

Only for training and service purposes

- 4 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 5

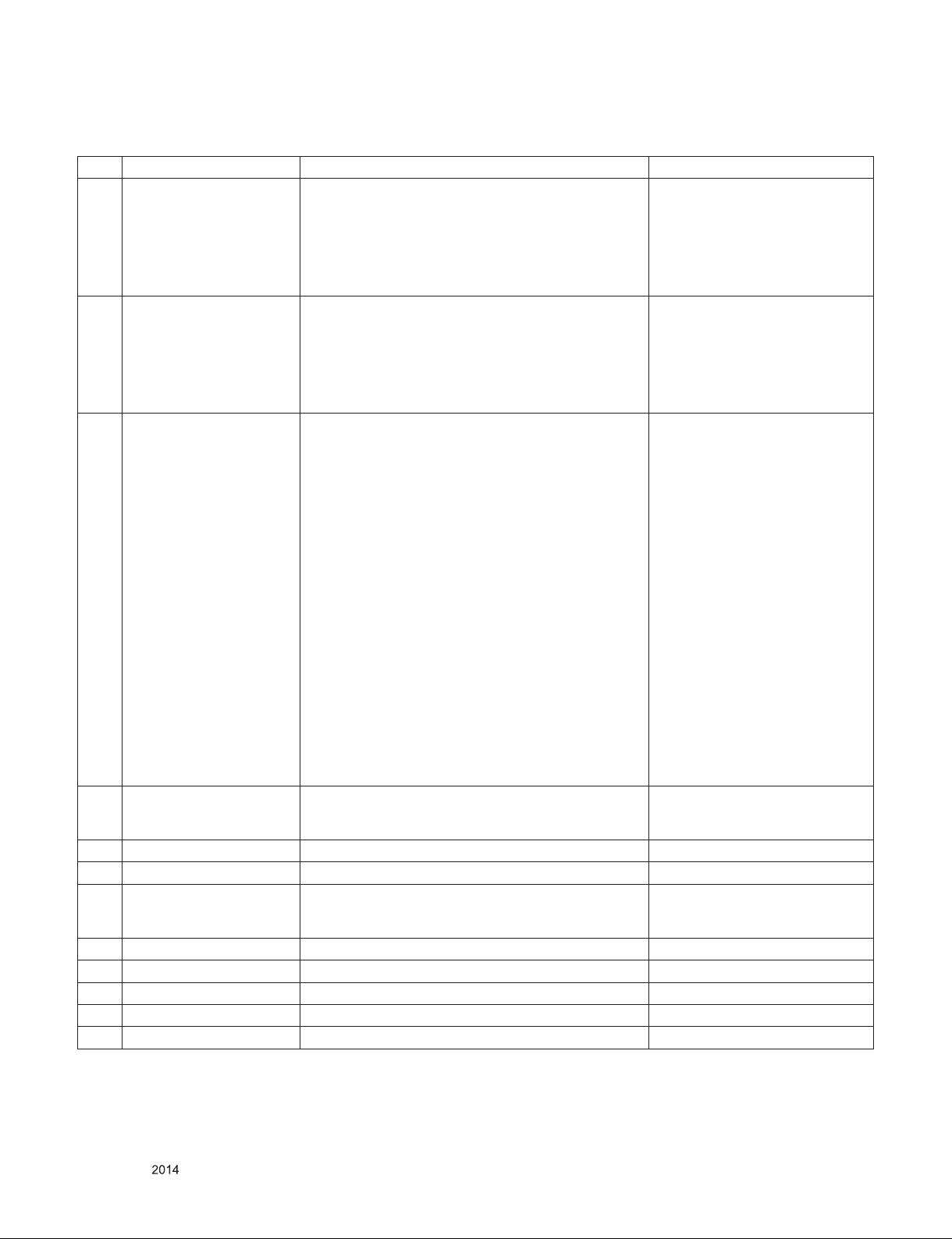

5. Model General Specification

No Item Specication Remark

1 Market Albania, Austria, Belgium, Bosnia, Bulgaria, Coratia,

Czech, Denmark, Estonia, Finland, France, Germany,

Greece, Hungary, Ireland, Italy, Kazakhstan, Latvia,

Lithuania, Luxembourg, Morocco, Netherlands, Norway,

Poland, Portugal, Romania, Russia, Serbia, Slovenia,

Spain, Sweden, Slovakia, Switzerland, Turkey, Ukraine,

UK

2 Broadcasting system 1) PAL/SECAM BG

2) PAL/SECAM DK

3) PAL I / II

4) SECAM L/L’

5) DVB T / T2

6) DVB C

7) DVB S/S2

3 Receiving system Analog : Upper Heterodyne

Digital : COFDM

4 Scart Jack (1EA) PAL, SECAM Scart 1 Jack is Full scart and sup-

5 Video Input (1EA) PAL, SECAM, NTSC

6 Component Input (1EA) Y/Cb/Cr, Y/ Pb/Pr

7 HDMI Input (3EA) HDMI-PC

HDMI-DTV

HDMI-MHL

8 Audio Input (1EA) Component + AV(Hybrid) L/R Input

9 SPDIF Out (1 EA) SPDIF Out

10 USB(3EA-FHD) For SVC, S/W Download, X-Studio, DivX-HD

11 Ethernet LAN(1EA)

12 PCMCIA(1EA) Common Interface

36 Country

EU (PAL Market)

Supporting T2/C/S is for **PB***V

► DVB-T (T2 Need Update)

- Guard Interval(Bitrate_Mbit/s)

1/4, 1/8, 1/16, 1/32

- Modulation : Code Rate

QPSK : 1/2, 2/3, 3/4, 5/6, 7/8

16-QAM : 1/2, 2/3, 3/4, 5/6, 7/8

64-QAM : 1/2, 2/3, 3/4, 5/6, 7/8

► DVB-C

- Symbolrate :

4.0Msymbols/s to 7.2Msymbols/s

- Modulation :

16QAM, 64-QAM, 128-QAM and

256-QAM

► DVB-S

- symbolrate

DVB-S2 (8PSK / QPSK) : 2 ~

45Msymbol/s

DVB-S (QPSK) : 2 ~ 45Msymbol/s

- viterbi

DVB-S mode : 1/2, 2/3, 3/4, 5/6,

7/8

DVB-S2 mode : 1/2, 2/3, 3/4, 3/5,

4/5, 5/6, 8/9, 9/10

port

RF-OUT(Analog), MNT-OUT

HDMI1(ARC), HDMI2(DVI) , Side

HDMI3(MHL)

Only for training and service purposes

- 5 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 6

ADJUSTMENT INSTRUCTION

1. Application Range

This spec. sheet applies to PD43A chassis applied PDP TV all

models manufactured in TV factory.

2. Specification

(1) Because this is not a hot chassis, it is not necessary to

use an isolation transformer. However, the use of isolation

transformer will help protect test instrument.

(2) Adjustment must be done in the correct order.

(3) The adjustment must be performed in the circumstance of

25 °C ± 5 °C of temperature and 65±10% of relative

humidity if there is no specific designation.

(4) The input voltage of the receiver must keep 100~240V,

50/60Hz.

(5) The receiver must be operated for about 5 minutes prior to

the adjustment when module is in the circumstance of over

15 °C

- In case of keeping module is in the circumstance of 0°C, it

should be placed in the circumstance of above 15°C for 2

hours

- In case of keeping module is in the circumstance of below

-20 °C, it should be placed in the circumstance of above 15

°C for 3 hours,.

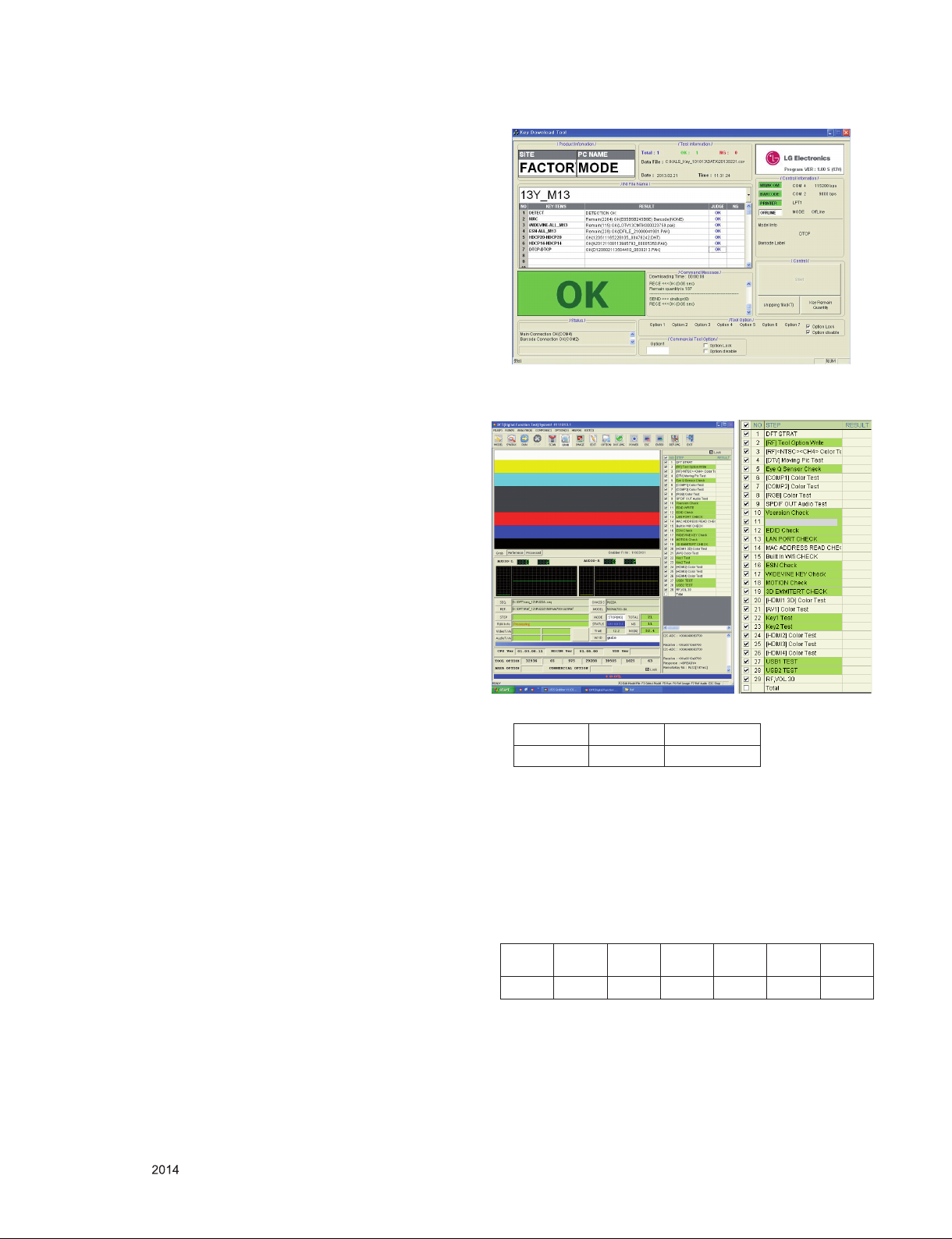

3.2. DFT Process

* Depend on situation, Step can be changed.

■ After RGB Full White in HEAT-RUN Mode, the receiver must

be operated prior to the adjustment.

■ Enter into HEAT-RUN MODE

1) Press the POWER ON KEY on R/C for adjustment.

2) OSD display and screen display PATTERN MODE.

● Set is activated HEAT run without signal generator in this

mode.

● Single color pattern ( WHITE ) of HEAT RUN MODE uses to

check panel.

● Caution : If you turn on a still screen more than 20 minutes

(Especially digital pattern, cross hatch pattern), an

after image may be occur in the black level part of

the screen.

3. PCB Assembly adjustment

* Caution : Using ‘power on’ button of the control R/C power on

TV

3.1. MAC address D/L , CI+ key D/L ,

Widevine key D/L, ESN D/L,

HDCP14/20 D/L, DTCP(optional)

Connect: USB port

Communication Prot connection

▪ Com 1,2,3,4 and 115200(Baudrate)

Mode check: Online Only

▪ check the test process

DETECT -> MAC -> CI -> Widevine -> ESN -> HDCP14 ->

HDCP20 -> DTCP(Optional)

▪.Play : Press Enter key

▪. Result: Ready, Test, OK or NG

▪. Printer Out (MAC Address Label)

* Condition spec

Mode Volume Power Off

RF 0 DC On

3.3. Tool OPTION (MANUAL)

(1) Insert Access USB Memory Stick

(2) Press ADJ key on R/C to insert Tool OPTION

(3) On the “ Tool Option ”, Insert Tool Option by a number key

(4) Press the ENTER(■)

(5) Press ENTER(■) again.

(6) Select “OK to Download” by using ◄/►(VOL +/-) and

press ►(VOL +)

Tool

option 1

32886 12306 161 64093 6295 1609 13455

Tool

option 2

Tool

option 3

Tool

option 4

Tool

option 5

Tool

option 6

option 7

Tool

Only for training and service purposes

- 6 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 7

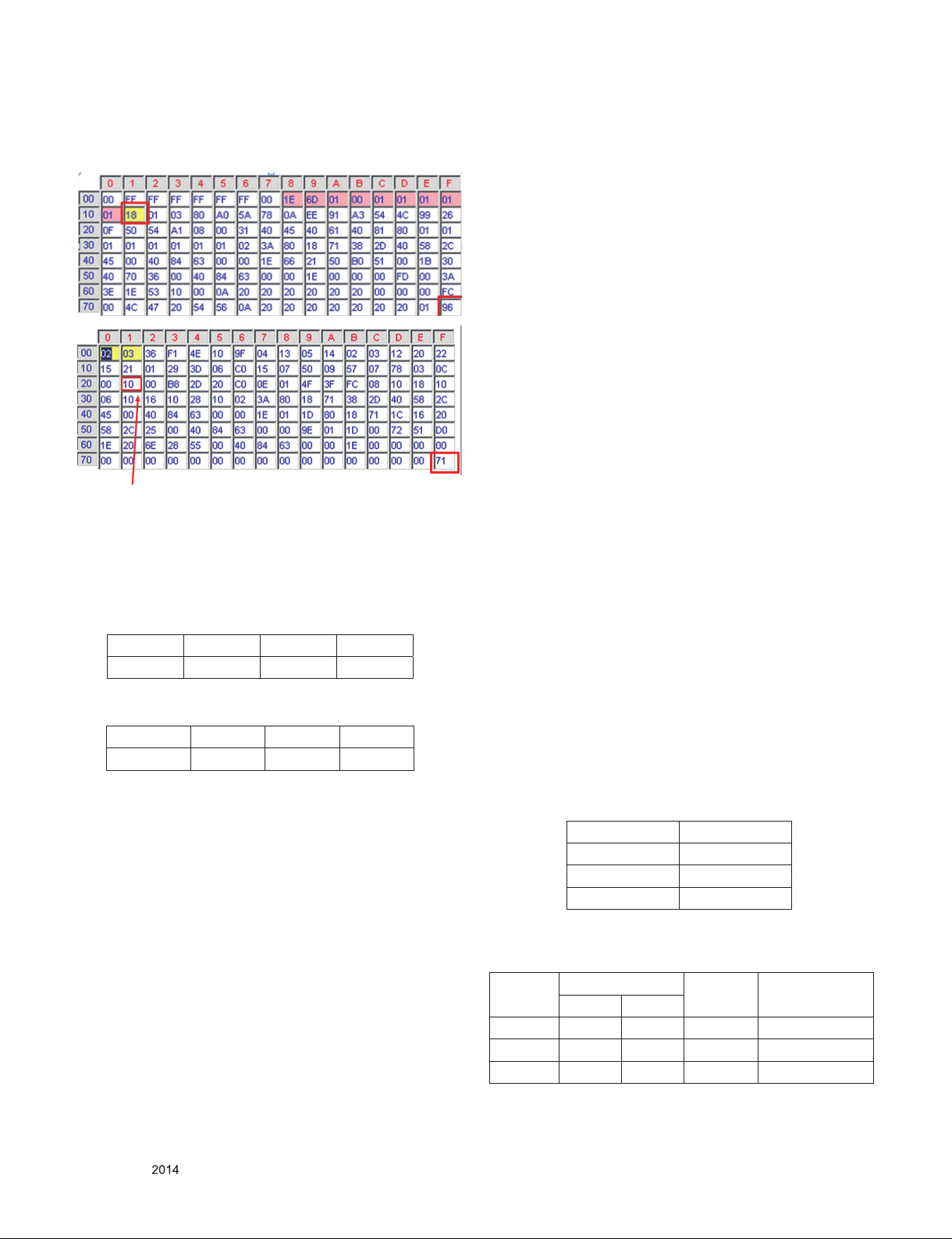

3.4. EDID (The Extended Display Identification Data)

■ HDMI [C/S: 96 71] : For 3D FHD (DTS) Models

4. SET assembly adjustment method

* Caution: Each PCB assembly must be checked by check

JIG set. (Because power PCB Assembly damages

to PDP Module, especially be careful)

Physical Address

* CheckSum & Physical Address Table.

- Each HDMI Input has their own physical address(on

Address:9E). So, each HDMI Input has different C/S

value.

■ HDMI INPUT Physical Address Table

Address HDMI1 HDMI2 HDMI3

A1 10 20 30

■ HDMI INPUT C/S Table.

- FHD 3D DTS

HDMI1 HDMI2 HDMI3

CheckSum 9671 9661 9651

4.1. POWER PCB Assembly Voltage adjustment

(Va, Vs voltage adjustment)

Test equipment : D.M.M 1EA

Connection Diagram for Measuring : refer to g.4

Adjustment method

4.1.1. Va adjustment

(1) Connect + terminal of D. M.M. to Va pin of P811, connect

-terminal to GND pin of P811.

(2) After turning VR502,voltage of D.M.M adjustment as same

as Va voltage which on label of panel right/top (deviation;

±0.5V)

4.1.2. Vs adjustment

(1) Connect + terminal of D. M..M. to Vs pin of P811, connect

-terminal to GND pin of P811.

(2) After turning VR901, voltage of D.M.M adjustment as

same as Vs voltage which on label of panel right/top (

deviation ; ±0.5V)

4.2. Adjustment of White Balance

- Required Equipment

● Remote controller for adjustment

● Color Analyzer ( CS-1000, CA-210 or same product

: CH 10 (PDP)

* Please adjust CA-210 by CS-1000 before measuring

● A uto W /B adjus tment in st rum en t(o nl y f or A uto

adjustment)

● 9 Pin D-Sub Jack(RS232C) is connected to the AUTO

W/B EQUIPMENT

Before Adjust of White Balance, Please press

POWER ONLY key

Only for training and service purposes

- Adjust Process will start by execute RS232C Command.

● Color temperature standards according to CSM and Module

CSM PLASMA

Cool 11000K

Medium 9300K

Warm 6500K

● CS-1000/CA-100+/CA-210(CH 10) White balance adjustment coordinates and color temperature.

CSM Color Coordination Temp ± Color

x y

COOL 0.276 0.283 11000K 0.002

MEDIUM 0.285 0.293 9300K 0.002

WARM 0.313 0.329 6500K 0.002

- 7 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Coordination

Page 8

● Change target luminance and range of the Auto adjustment

W/B equipment

- 50/60R5

Target luminance 50

Range ±23

* Manual W/B process (using adjusts Remote control)

- Please Adjust in AV 1 MODE, Turn off Energy Saving Mode.

1) Enter ‘PICTURE RESET’ on Picture Mode, and then turn

off Fresh Contrast and Fresh colour in Advanced Control

2) After enter Service Mode by pushing “ADJ” key,

3) Enter White Pattern off of service mode, and change off

-> on.

4) Enter “W/B ADJUST” by pushing “►” key at “3. W/B

ADJUST”.

* Gain Max Value is 192. So, Never make any Gain Value

over 192 and please x one Value on 192, between R, G

and B.

Min Typ Max

R-GAIN 0 192 192

G-GAIN 0 192 192

B-GAIN 0 192 192

* Auto-control interface and directions

(1) Adjust in the place where the inux of light like oodlight

around is blocked. (Illumination is less than 10ux).

(2) Measure and adjust after sticking the Color Analyzer (CA-

100+, CA210) to the side of the module.

(3) Aging time

- After aging start, keep the Power on (no suspension of

power supply) and heat-run over 5 minutes

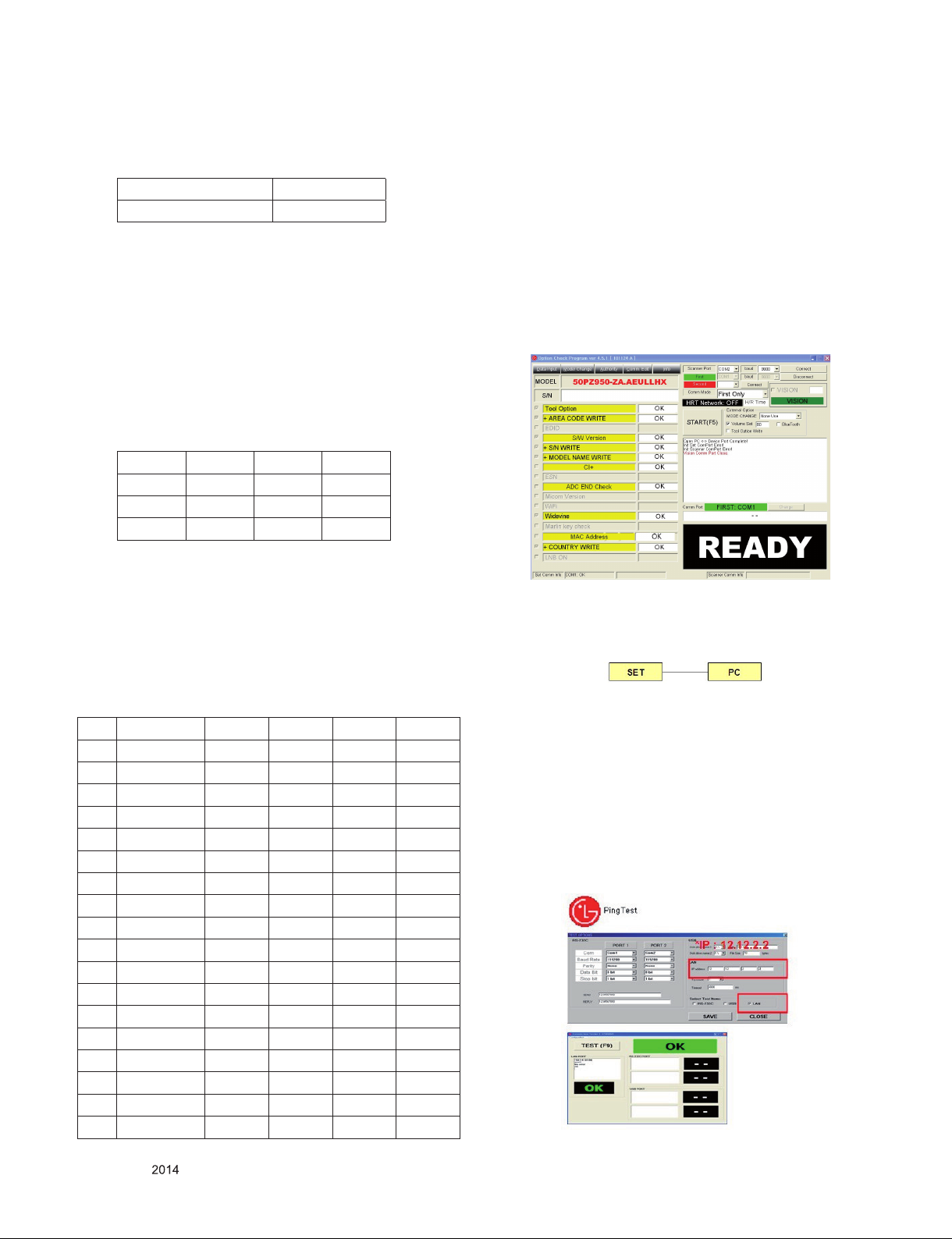

4.3. Serial number download & Model name D/L.

(1) Press "Power on" button of a service R/C.(Baud rate :

115200 bps)

(2) Connect RS232-C Signal Cable and start ‘Option Check

Program Ver3.8’

(3) Scan serial Number and press ‘F5’ button.

(4) Check ‘OK’ on program 1) program.

(5) Press ‘In start’ button on SVC R/C, check Serial Number

and Model Name.

4.4. Check Tool Option and write Country

Group & Area Code(Option) D/L

- Refer to Table 3.3 insert tool option.

4.5. PING TEST

* In this case Network setting is on Manual Setting.

Connect : SET->LAN Port == PC->LAN Port

* Auto adjustment Map (RS232C)

No Index CMD1 CMD2 Set ID Data

1 Start w b 0 00

2 Gain Start w b 0 10

3 Gain End w b 0 1F

4 Offset Start w b 0 20

5 Offset End w b 0 2F

6 End w b 0 FF

7 Medium R j a 0 00~FF

8 Medium G j b 0 00~FF

9 Medium B j c 0 00~FF

10 Warm R j d 0 00~FF

11 Warm G j e 0 00~FF

12 Warm B j f 0 00~FF

13 Cool R j g 0 00~FF

14 Cool G j h 0 00~FF

15 Cool B j i 0 00~FF

16 Cool R,G,B j j 0 00~FF

17 Medium j k 0 00~FF

18 Warm j l 0 00~FF

4.5.1. Equipment Setting

(1) Play the LAN Port Test PROGRAM.

(2) Input IP set up for an inspection to Test

* IP Number : 12.12.2.2

4.5.2. LAN PORT inspection (PING TEST)

* In this case Network setting is on Manual Setting.

(1) Play the LAN Port Test Program.

(2) connect each other LAN Port Jack.

(3) Play Test (F9) button and confirm OK Message.

(4) remove LAN CABLE

Only for training and service purposes

- 8 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 9

4.6. Magic Motion Remote Controller test

(1) Equipment: RF R/C for test,

(2) You must confirm the battery power of RF-R/C before test

(Recommend that change the battery per every lot)

(3) Sequence (test)

1) if you select the ‘start key(Wheel Key)’ on the controller,

you can pairing with the TV SET.

2) You can check the cursor on the TV Screen, when select

the ‘Wheel Key’ on the controller

3) You must remove the pairing with the TV Set by select

‘Mute Key’ on the controller.

4.7. Wi-Fi Test

Step 1) Turn on TV

Step 2) Select ‘Network Connection’ option in Network Menu.

Step 3) Select ‘Start Connection’ Button in ‘Network

Connection’.

(2) When 3D OSD appear automatically, then press OK button

on ADJ Remote Controller.

(3) Check the picture. The picture must be same as below.

(Don’t have to wear 3D glasses.)

4.9 LNB voltage and 22KHz tone check

(1) Test method

1) Press "Power on" button of a service R/C.(Baud rate :

115200 bps)

2) Connect cable between satellite ANT and test JIG.

3) Connect RS232-C Signal Cable.

4) Write LNB ON control command through RS-232-C.

5) check LED light ‘ON’ at 18V menu.

6) check LED light ‘ON’ at 22KHz tone menu.

7) Write LNB OFF control command through RS-232-C.

8) check LED light ‘OFF’ at 18V menu.

9) check LED light ‘OFF’ at 22KHz tone menu.

(2) RS-232 command for test LNB

Command Set ACK

LNB On [A][I][ ][Set ID][ ][30][Cr] [O][K][x] or NG : [N][G][x]

LNB Off [A][I][ ][Set ID][ ][40][Cr] [O][K][x] or NG : [N][G][x]

Step 4) If the system finds any AP like blow PIC, it is working

well.

4.8. 3D function test

- Required Equipment

● Pattern Generator :

MSHG-600, MSPG-6100 [SUPPORT HDMI1.4])

MODE : HDMI mode NO. 872

Pattern No.83

(1) Please input 3D test pattern like below (HDMI mode NO.

872 , pattern No.83)

(3) Test result

- After send LNB On command, ‘18V LED’ and ‘22KHz

tone LED’ should be ON.

- After send LNB Off command, ‘18V LED’ and ‘22KHz tone

LED’ should be OFF.

k}iTzYGG

4;Y 46Y

4;Y 46Y

4;Y 46Y

55NK}#

55NK}#

55NK}#

W

W

W

rqh RQ

rqh RQ

rqh RQ

55NK}

55NK}

55NK}

Wrqh#Rii

Wrqh#Rii

Wrqh#Rii

k}iTzYGG

ck}iGGGqpnGGe

ck}iGGGqpnGGe

tGi

tGi

{

{

<Remark>

After the measurement conditions witnessed in the last state.

HDMI Mode No.872, Pattern No.83

Only for training and service purposes

- 9 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 10

5. Set Information (Serial No & Model name)

5.1. Check the serial number & Model Name

(1) Push the menu button and press red button on R/C to

enter ‘Customer Support’menu.

(2) Move to ‘signal test’ menu. And check Serial No & Model

Name Select the STATION -> Diagnostics -> To set

6. SW Download Guide.

* Before put a *.epk to USB Stick make ‘LG_DTV’ folder in

USB. Then, put *.epk file to ‘LG_DTV’ folder and Turn on TV

(1) Put the USB Stick to the USB socket

(2) Automatically detecting update file in USB Stick

* If your downloaded program version in USB Stick is Low,

it didn’t work.

But your downloaded version is High, USB data is

automatically detecting.

(3) Show the message “Copying files from memory”

(4) Updating is staring.

(5) Updating Completed, The TV will restart automatically.

After turn on TV, Please press ‘IN-STOP’ button on ADJ

Remote-control.

* IF you don’t have ADJ R/C, enter ‘Factory Reset’ in

OPTION MENU.

(6) When TV turns on, check the Updated version on Product/

Service Info. MENU.

* After downloading, have to adjust TOOL OPTION again.

Only for training and service purposes

- 10 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 11

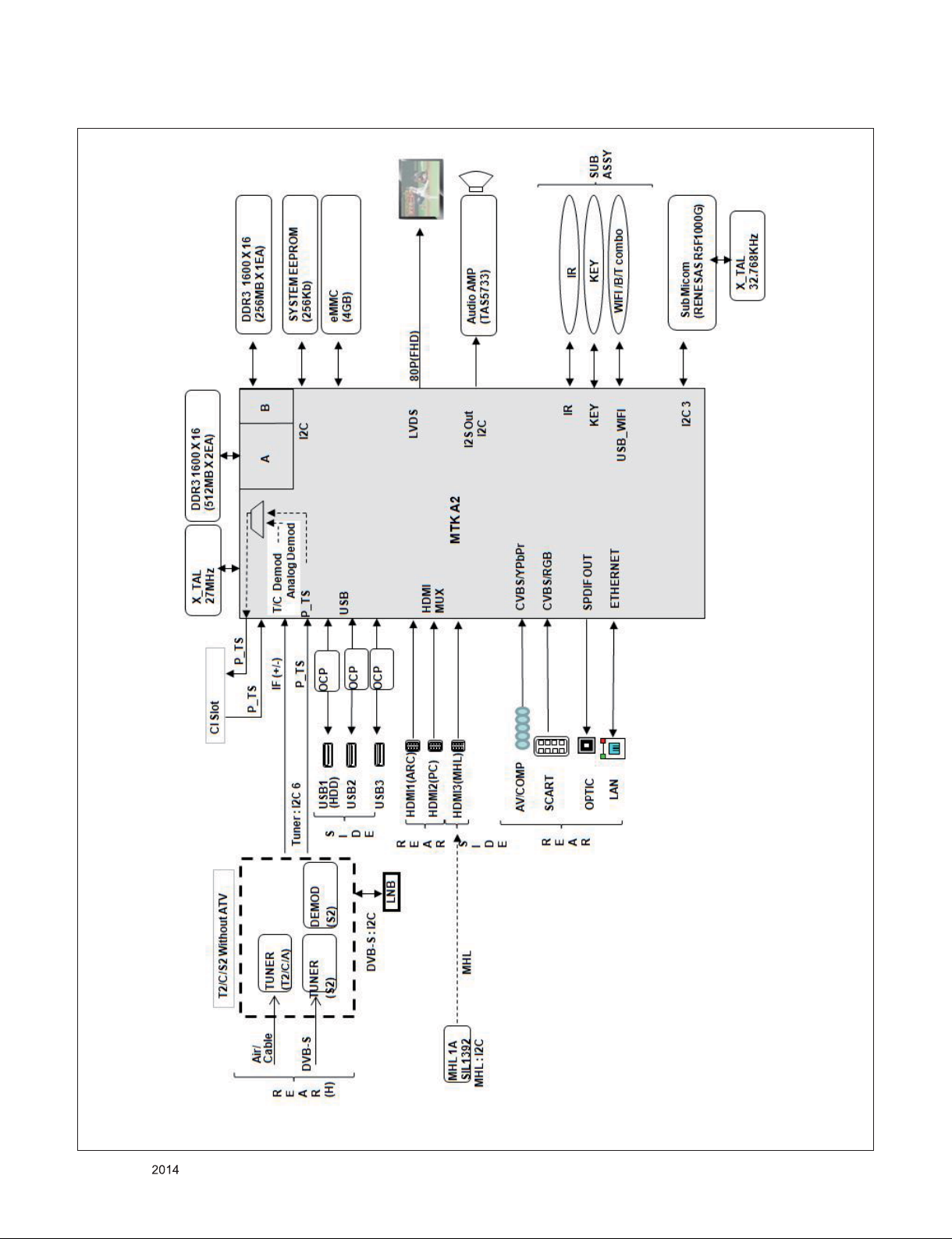

BLOCK DIAGRAM

Only for training and service purposes

- 11 -

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 12

300

EXPLODED VIEW

IMPORTANT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essential that these special safety parts should be replaced with the same components as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

560

305

301

200

302

205

206

303

304

580

202

203

201

204

120

520

LV1

A9

601

A10

A22

A2

530

Only for training and service purposes

240

400

- 12 -

900

910

LGE Internal Use OnlyCopyright © LG Electronics. Inc. All rights reserved.

Page 13

PDP ATSC/DVB:EAX65399301

Copyright © 2014 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

NVRAM_Rohm

IC100-*1

+3.3V_MULTI

R101

4.7K

R100

4.7K

OPT

NVRAM

R102

4.7K

OPT

GND

IC100

AT24C256C-SSHL-T

A0

1

A1

2

A2

3

4

+3.3V_MULTI

VCC

8

WP

7

SCL

6

SDA

5

BR24G256FJ-3

VCC

A0

8

1

A1

WP

2

7

A2

SCL

3

6

GND

SDA

4

5

Write Protection

- Low : Normal Operation

- High : Write Protection

R135 33

R134 33

JIG_GND

I2C_SCL5

I2C_SDA5

NVRAM_ATMEL

HDCP EEPROM

OPT

IC101

M24C16-R

NC_1

NC_2

NC_3

VSS

VCC

8

1

WC

2

7

SCL

3

6

SDA

4

5

I2C

R121

1.2K

+3.3V_MULTI

R105

4.7K

OPT

R103

4.7K

R120 33

R115 33

R116 33

R117 33

R118 33

R119 33

R110 33

R111 33

R112 33

R113 33

R114 33

R109 33

R106

4.7K

OPT

R104

4.7K

FHD

HD

STB_SCL

STB_SDA

OPCTRL_11_SCL

OPCTRL_10_SDA

OSCL1

OSDA1

OSCL2

OSDA2

OSCL0

OSDA0

OPCTRL_1_SCL

OPCTRL_0_SDA

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

+3.3V_MULTI

OPT

C100

0.1uF

R132

1.2K

R133

1.2K

16V

OPT

R125 4.7K

OPT

R126 22

OPT

R127 22

R124

1.2K

Model Option

R130

4.7K

R108

R107

4.7K

4.7K

R123

4.7K

Country_AJJA

R122

4.7K

Non_Country_AJJA

R131

R129

OPT

OPT

R128

4.7K

4.7K

4.7K

R138

2.7K

I2C_SCL1

I2C_SDA1

R141

2.7K

OPT

R137

4.7K

R136

4.7K

T2

NO_T2

R142

2.7K

R140

R139

4.7K

4.7K

+3.3V_MULTI

R147

2.7K

S

OPT

R145

4.7K

R143

4.7K

NO_S

+3.3V_MULTI

R155

1K

R154

1K

OPT

I2C_1 : AMP,HDCP KEY

I2C_2 : PDP_MODULE

I2C_3 : MICOM

I2C_4 : S/Demod,T2/Demod,LNB,MHL

I2C_5 : NVRAM

I2C_6 : TUNER_MOPLL(T/C,ATV)

R150

R151

R1522KR153

1.2K

OPT

R149

4.7K

R148

4.7K

2K

MODEL_OPT_0

MODEL_OPT_1

MODEL_OPT_2

MODEL_OPT_3

/S2_RESET

MODEL_OPT_5

MODEL_OPT_6

MODEL_OPT_7

MODEL_OPT_8

MODEL_OPT_9

MODEL_OPT_10

R146

R144

1.2K

4.7K

4.7K

OPT

MODEL_OPT_4

R157

1K

R156

1K

OPT

I2C_SCL1

I2C_SDA1

I2C_SCL2

I2C_SDA2

I2C_SCL3

I2C_SDA3

I2C_SCL4

I2C_SDA4

I2C_SCL5

I2C_SDA5

I2C_SCL6

I2C_SDA6

R162

1K

R160

1K

R163

1K

R161

OPT

1K

MODEL_OPT_0

MODEL_OPT_1

MODEL_OPT_2

MODEL_OPT_3

MODEL_OPT_4

MODEL_OPT_5

MODEL_OPT_6

MODEL_OPT_7

MODEL_OPT_8

MODEL_OPT_9

MODEL_OPT_10

MODEL_OPT_5

MODEL_OPT_9

JP_GND_1

JP_GND_2

JP_GND_3

JP_GND_4

STRAPPING LED_PWM0 LED_PWM1 OPCTRL3 OPCTRL7

ICE mode + 27M + serial boot 1 0 0 0

LED_PWM0

LED_PWM1

OPCTRL3

OPCTRL7

Country_TW

Country_AJJA

ICE mode + 27M + ROM to Nand boot 1 0 0 1

ICE mode + 27M + ROM to 60bit ECC Nand boot 1 0 1 0

ICE mode + 27M + ROM to eMMC boot from 1 0 1 1

EMMC pins (share pins w/s NAND)

ICE mode + 27M + ROM to eMMC 1 1 0 0

Boot from SDIO pins

HIGH

FRC FRC_120Hz NO_FRC_60Hz

Reserved

DDR

CP BOX

T2 Tuner

S Tuner

DDR

EPI

DDR_1.25G

High

Low

TW

FHD HD

AJJA

Module_V13 Module_V12

DDR_1.25GB

Enable

Support

Support

DDR_0.78G

Support

DDR_1.5G

Low

Low

3D_SYNC_RF

LOW

Non_TW

Non_AJJA

DDR_1.5GB

Disable

Not Support

Not Support

NON_DDR_0.78G

Not Support

DDR_0.768G

High

High

R194 0

PB690

Place the P901

MODEL_OPT_5

SOC -> CI SLOT

MT5369_MCLKI

MT5369_MIVAL_ERR

MT5369_MISTRT

SOC -> CI SLOT

MT5369_TS_OUT[0-7]

CI_DATA[0-7]

GPIO45(EMMC_RST) is dedicated to reset

EMMC for improving A1’s leakage current

/USB_OCD2

/USB_OCD1

/USB_OCD3

EMMC_RST

USB_CTL1

#SIL_RESET

SC_ID

Close to eMMC Flash

(IC8100)

EMMC_CLK

CI_ADDR[0-14]

CI SLOT -> SOC

CI_DATA[0]

CI_DATA[1]

CI_DATA[2]

CI_DATA[3]

CI_DATA[4]

CI_DATA[5]

CI_DATA[6]

CI_DATA[7]

NO_EU

R169

R170

R167

R168

10K

MT5369_TS_OUT[0]

MT5369_TS_OUT[1]

MT5369_TS_OUT[2]

MT5369_TS_OUT[3]

MT5369_TS_OUT[4]

MT5369_TS_OUT[5]

MT5369_TS_OUT[6]

MT5369_TS_OUT[7]

MT5369_TS_IN[0]

MT5369_TS_IN[1]

MT5369_TS_IN[2]

MT5369_TS_IN[3]

MT5369_TS_IN[4]

MT5369_TS_IN[5]

MT5369_TS_IN[6]

MT5369_TS_IN[7]

10K

10K

10K

MODEL_OPT_4

CI_ADDR[0-14]

MODEL_OPT_0

M_REMOTE_RST

/TU_RESET

/S2_RESET

CI_ADDR[0]

CI_ADDR[1]

CI_ADDR[2]

CI_ADDR[3]

CI_ADDR[4]

CI_ADDR[5]

CI_ADDR[6]

CI_ADDR[7]

CI_ADDR[8]

CI_ADDR[9]

CI_ADDR[10]

CI_ADDR[11]

CI_ADDR[12]

CI_ADDR[13]

CI_ADDR[14]

LCD:EPI_LOCK6

OTP_WRITE

MODEL_OPT_3

MODEL_OPT_7

MODEL_OPT_5

MODEL_OPT_6

LCD:OPC_EN

+3.3V_MULTI

AR100

10K

R171

AVDD_33SB

AVDD_33SB

VDD3V3

LGE2122[A2_M13]

B30

GPIO0

A31

GPIO1

B31

GPIO2

A32

GPIO3

C30

GPIO4

A33

GPIO5

B32

GPIO6

C31

GPIO7

E30

GPIO8

F29

GPIO9

F27

GPIO10

F28

GPIO11

C32

GPIO12

F30

GPIO13

F32

GPIO14

D30

GPIO15

D32

GPIO16

F31

GPIO17

F33

GPIO18

E31

GPIO19

E32

GPIO20

D31

GPIO21

D33

GPIO22

E29

GPIO23

C33

GPIO24

B33

GPIO25

A30

GPIO26

E28

GPIO27

C29

GPIO28

J28

GPIO29

H29

GPIO30

J26

GPIO31

G30

GPIO32

G27

GPIO33

E27

GPIO34

D29

GPIO35

D28

GPIO36

H28

GPIO37

J27

GPIO38

G29

GPIO39

G31

GPIO40

G28

GPIO41

B28

GPIO42

K28

GPIO43

E25

GPIO44

D21

GPIO45

G23

GPIO46

C28

GPIO47

F24

GPIO48

AB8

GPIO49

AA7

GPIO50

AD6

GPIO51

AC8

GPIO52

AC7

GPIO53

AB6

GPIO54

AC6

GPIO55

AJ23

ADIN0_SRV

AH23

ADIN1_SRV

AE28

ADIN2_SRV

AD28

ADIN3_SRV

AF22

ADIN4_SRV

AK21

ADIN5_SRV

AG24

ADIN6_SRV

AM18

ADIN7_SRV

X-TAL

10K

OSDA0

OSCL0

OSDA1

OSCL1

MT5369_XTAL_IN

MT5369_XTAL_OUT

C111

0.1uF

C110

0.1uF

C109

0.1uF

C107

4.7uF

10V

IC105

MT5369_XTAL_IN

C112

4.7uF

10V

DEMOD_RST

DEMOD_TSCLK

DEMOD_TSDATA0

DEMOD_TSDATA1

DEMOD_TSDATA2

DEMOD_TSDATA3

DEMOD_TSDATA4

DEMOD_TSDATA5

DEMOD_TSDATA6

DEMOD_TSDATA7

DEMOD_TSSYNC

DEMOD_TSVAL

CI_INT

CI_TSCLK

CI_TSDATA0

CI_TSSYNC

CI_TSVAL

PVR_TSCLK

PVR_TSVAL

PVR_TSSYNC

PVR_TSDATA0

PVR_TSDATA1

SPI_CLK1

SPI_CLK

SPI_DATA

SPI_CLE

OPWM2

OPWM1

OPWM0

SD_D0

SD_D1

SD_D2

SD_D3

SD_CMD

SD_CLK

LED_PWM1

LED_PWM0

OPCTRL11

OPCTRL10

OPCTRL9

OPCTRL8

OPCTRL7

OPCTRL6

OPCTRL5

OPCTRL4

OPCTRL3

OPCTRL2

OPCTRL1

OPCTRL0

Crystal Matching Test result : 3pF

X100

27MHz

C114

5pF

LGE2122[A2_M13]

AK10

JTCK

AK11

JTDI

AL9

JTDO

AJ11

JTMS

AJ12

JTRST

AH11

OSDA0

AH10

OSCL0

AF11

OSDA1

AG11

OSCL1

AN29

XTALI

AM29

XTALO

AN30

AVDD33_XTAL_STB

AL29

AVSS33_XTAL_STB

AN17

AVDD33_VGA_STB

AL17

AVSS33_AVSS33_VGA_STB

AL26

AVDD33_PLL

AC21

AVSS33_PLLGP

H21

AVSS33_CPUPLL

AM17

AVDD10_LDO

AN16

AVDD10_ELDO

P30

N32

R27

T26

T27

P26

R28

U27

U26

R26

R29

P27

L25

N33

K26

N30

N31

M31

M27

L27

M29

M30

L30

L33

L32

K27

AL8

TP121

AM8

TP122

AM9

3D_SYNC_RF

D27

C27

D26

C26

A28

E24

AF15

AG15

AL16

AM16

AE17

AG19

AH17

AE19

AH19

AK16

AG17

AJ17

AF19

AJ19

X-TAL_1

GND_1

Wake On Lan

/CI_CD2

/CI_CD1

/PCM_IORD

/PCM_IOWR

SMARTCARD_FOR JAPAN

1

2

IC105

PCM_RST

FE_TS_CLK

GND_2

4

X-TAL_2

3

EMMC_CLK

FSRC_WR

STB_SCL

STB_SDA

POR_BND

FE_TS_DATA[0]

FE_TS_DATA[1]

FE_TS_DATA[2]

FE_TS_DATA[3]

FE_TS_DATA[4]

FE_TS_DATA[5]

FE_TS_DATA[6]

FE_TS_DATA[7]

FE_TS_SYNC

FE_TS_VAL

/PCM_REG

/PCM_CE1

MT5369_TS_SYNC

/PCM_WE

/PCM_OE

MT5369_TS_VAL

MT5369_TS_CLK

/PCM_IRQA

/PCM_WAIT

LED_PWM1

LED_PWM0

5V Tolerance

OPCTRL_11_SCL

OPCTRL_10_SDA

COMP1_DET

SC_DET

OPCTRL7

AV1_CVBS_DETUSB_CTL3

AMP_RESET_SOC

OPCTRL3

RF_SWITCH_CTL

OPCTRL_1_SCL

OPCTRL_0_SDA

U0TX

U0RX

U1TX

U1RX

POWE

POOE

POCE1

POCE0

PDD7

PDD6

PDD5

PDD4

PDD3

PDD2

PDD1

PDD0

PARB

PACLE

PAALE

OPWRSB

ORESET

OIRI

C115

5pF

AH15

AH14

AH13

AG13

D24

B25

D25

A25

C22

B22

A22

C23

A23

B23

D23

C24

C25

A26

B26

C21

AL15

AK20

AF17

C20

AL14

AK15

AE14

CI SLOT -> SOC

CI SLOT -> SOC

LCD : CI_A_VS1

CI SLOT -> SOC

MID_MAIN_1

MT5369_XTAL_OUT

EMMC_DATA[7]

EMMC_DATA[6]

EMMC_DATA[5]

EMMC_DATA[4]

EMMC_DATA[3]

EMMC_DATA[2]

R180 4.7K

R193 4.7K

FE_TS_DATA[0-7]

EXTERNAL DEMOD

-> SOC

AMP_RESET_SOC

RS232_TXD

RS232_RXD

EMMC_CMD

EMMC_DATA[1]

EMMC_DATA[0]

EMMC_CLK

STB_SCL

STB_SDA

D100

1N4148W

100V

R182

33

R198

10K

R186

22

AVDD_33SB

R196

240

EMMC_DATA[2-7]

R188

4.7K

OPT

R187

4.7K

OPT

+3.3V_MULTI

R189

10K

OPT

C117

0.1uF

16V

Q100

PMV48XP

D

G

2011.12.13

8

WOL_ON

TP153

SOC_RESET

JTP-1127WEM

DEBUG

+3.3V_MULTI

S

AMP_RESET_N

SW100

1 2

10K

R199

OTP_WRITE

43

Page 14

+1.2V_MTK_AVDD

Copyright © 2014 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

HDMI_CEC

DDC_SCL_3

DDC_SCL_2

DDC_SCL_MHL

DDC_SDA_3

DDC_SDA_2

DDC_SDA_MHL

HDMI_HPD_MHL

C303

0.1uF

VDD3V3_HDMI

VDD3V3

5V_HDMI_3

5V_HDMI_2

5VBUS

HPD3

HPD2

C302

0.1uF

0.1uF

C306

0.1uF

USB_DP3

USB_DM3

USB_DP2

USB_DM2

USB_DP1

USB_DM1

WIFI_DP

WIFI_DM

IC105

LGE2122[A2_M13]

V26

HDMI_CEC

AC27

HDMI_0_SCL

AB27

HDMI_1_SCL

AA26

HDMI_2_SCL

W27

HDMI_3_SCL

AC26

HDMI_0_SDA

AB26

HDMI_1_SDA

Y26

HDMI_2_SDA

W26

HDMI_3_SDA

AE29

HDMI_0_PWR5V

R305

R306

R307

C304

Y27

1K

1K

1K

C307

0.1uF

AA28

V28

AD29

AA27

AA29

V29

AA33

AA32

P33

P32

AH33

AE27

T25

W25

AD27

H32

H33

J32

J31

K32

K31

AN10

AM10

K33

AN8

M25

AE11

HDMI_1_PWR5V

HDMI_2_PWR5V

HDMI_3_PWR5V

HDMI_0_HPD

HDMI_1_HPD

HDMI_2_HPD

HDMI_3_HPD

AVDD12_HDMI_0_RX

AVDD12_HDMI_1_RX

AVDD12_HDMI_2_RX

AVDD12_HDMI_3_RX

AVDD33_HDMI

AVSS33_HDMI_RX_1

AVSS33_HDMI_RX_2

AVSS33_HDMI_RX_3

AVSS33_HDMI_RX_4

LGE2122[A2_M13]

USB_DP_P0

USB_DM_P0

USB_DP_P1

USB_DM_P1

USB_DP_P2

USB_DM_P2

USB_DP_P3

USB_DM_P3

AVDD33_USB_P0P1P2

AVDD33_USB_P3

AVSS33_USB_P1

AVSS33_USB_P3

IC105

HDMI_0_RX_0

HDMI_0_RX_0B

HDMI_0_RX_1

HDMI_0_RX_1B

HDMI_0_RX_2

HDMI_0_RX_2B

HDMI_0_RX_C

HDMI_0_RX_CB

HDMI_1_RX_0

HDMI_1_RX_0B

HDMI_1_RX_1

HDMI_1_RX_1B

HDMI_1_RX_2

HDMI_1_RX_2B

HDMI_1_RX_C

HDMI_1_RX_CB

HDMI_2_RX_0

HDMI_2_RX_0B

HDMI_2_RX_1

HDMI_2_RX_1B

HDMI_2_RX_2

HDMI_2_RX_2B

HDMI_2_RX_C

HDMI_2_RX_CB

HDMI_3_RX_0

HDMI_3_RX_0B

HDMI_3_RX_1

HDMI_3_RX_1B

HDMI_3_RX_2

HDMI_3_RX_2B

HDMI_3_RX_C

HDMI_3_RX_CB

Wake On Lan

AVDD33_ETH

AVSS33_ELDO

AVSS33_LD

AVSS33_COM

TXVP_0

TXVN_0

RXVP_1

RXVN_1

PHYLED1

PHYLED0

AG30

AG31

AF30

AF31

AE32

AE33

AG32

AG33

AD30

AD31

AC32

AC33

AC30

AC31

AE30

AE31

Y30

Y31

W32

W33

W30

W31

AA30

AA31

U30

U31

T32

T33

T30

T31

V30

V31

AL13

AM13

AL12

AM12

AF13

AJ13

AN12

REXT

R31524K

AN14

AE13

AC16

AC15

AVDD_33SB

D0+_HDMI3

D0-_HDMI3

D1+_HDMI3

D1-_HDMI3

D2+_HDMI3

D2-_HDMI3

CK+_HDMI3

CK-_HDMI3

D0+_HDMI2

D0-_HDMI2

D1+_HDMI2

D1-_HDMI2

D2+_HDMI2

D2-_HDMI2

CK+_HDMI2

CK-_HDMI2

D0+_HDMI1_MHL

D0-_HDMI1_MHL

D1+_HDMI1_MHL

D1-_HDMI1_MHL

D2+_HDMI1_MHL

D2-_HDMI1_MHL

CK+_HDMI1_MHL

CK-_HDMI1_MHL

EPHY_TDP

EPHY_TDN

EPHY_RDP

EPHY_RDN

MODEL_OPT_1

C328

1uF

125C

REAR_HDMI1

SIDE_HDMI2

SIDE_HDMI3

IF_P

Close to Tuner

IF_N

IF_AGC

1/16W

1/16W

R331

R346

1K

1%

1K

1%

R3801K1/16W

R332 10K

C341

0.047uF

Close to AVDD33_ADAC & AVDD33_AADC

VDD3V3

L304

C365

10uF

10V

C336

10V

1%

C337 1uF

10V

Close to Tuner

For PCB Pattern

For PCB Pattern

COMP1/AV1_R_IN

COMP1/AV1_L_IN

C305

C362

1uF

0.1uF

10V

C312

33pF

1uF

Close to MT5369

C310

33pF

COMP1_Y/AV1_CVBS

SC_R_IN

SC_L_IN

R334 51

R335 51

R342 10K

C355

0.047uF

SC_CVBS_IN

+1.2V_MTK_AVDD

C350

10uF

AVDD3V3_AADC

VDD3V3

R308 100EUC308 0.047uF

R341 100

Near the SOC

MODEL_OPT_8

MODEL_OPT_9

MODEL_OPT_10

MODEL_OPT_2

PCM_5V_CTL

USB_CTL2

VDD3V3

C347

0.1uF

R343

24K

1%

+1.2V_MTK_AVDD

C364

0.1uF

C353

0.1uF

Close to MT5369

1uF

C361

AVDD3V3_AADC

C358

0.1uF

C351

0.1uF

TP300

OSCL2

OSDA2

EU

C360 0.047uF

VDD3V3

C363

1uF

10V

LGE2122[A2_M13]

AA8

TCON0

AA9

TCON1

W6

TCON2

U6

TCON3

U7

TCON4

V8

TCON5

V6

TCON6

AB7

TCON7

W9

TCON8

U8

TCON9

U9

TCON10

V9

TCON11

V7

TCON12

AN1

AVDD12_LVDS_1

AN2

AVDD12_LVDS_2

AN3

AVDD12_LVDS_3

AN4

AVDD33_LVDS

AM4

AVSS12_LVDS_1

AM3

AVSS12_LVDS_2

AF5

AVSS12_LVDS_3

AE5

AVSS33_LVDS_1

AC5

AVSS33_LVDS_2

V5

AVSS33_LVDS_3

T1

REXT_VPLL

LGE2122[A2_M13]

AL32

AIN1_R_AADC

AN32

AIN1_L_AADC

AM33

AIN2_R_AADC

AM31

AIN2_L_AADC

AM32

AIN3_R_AADC

AK33

AIN3_L_AADC

AL33

AIN4_R_AADC

AN33

AIN4_L_AADC

AJ32

AVDD33_AADC

AC24

AVSS33_AADC

AN31

VMID_AADC

AH25

MPXP

LGE2122[A2_M13]

AM27

ADCINP_DEMOD

AN27

ADCINN_DEMOD

AN26

AVDD33_DEMOD

AN28

AVDD12_DEMOD

AL28

AVSS33_DEMOD

AL27

AVSS12_DEMOD

L26

IF_AGC

M28

RF_AGC

AJ27

LOUTN

AK27

LOUTP

N27

OSCL2

N26

OSDA2

AK26

CVBS3P

AM25

CVBS2P

AH26

CVBS1P

AK25

CVBS0P

AJ26

CVBS_COM

AM26

AVDD33_CVBS

AB20

AVSS33_CVBS_1

AB22

AVSS33_CVBS_2

IC105

IC105

IC105

BE0P

BE0N

BE1P

BE1N

BE2P

BE2N

BECKP

BECKN

BE3P

BE3N

BE4P

BE4N

BO0P

BO0N

BO1P

BO1N

BO2P

BO2N

BOCKP

BOCKN

BO3P

BO3N

BO4P

BO4N

AE0P

AE0N

AE1P

AE1N

AE2P

AE2N

AECKP

AECKN

AE3P

AE3N

AE4P

AE4N

AO0P

AO0N

AO1P

AO1N

AO2P

AO2N

AOCKP

AOCKN

AO3P

AO3N

AO4P

AO4N

AR0_ADAC

AL0_ADAC

AR1_ADAC

AL1_ADAC

AR2_ADAC

AL2_ADAC

AVDD33_ADAC

AVSS33_ADAC

ALIN

ASPDIF0

ASPDIF1

AOBCK

AOLRCK

AOMCLK

AOSDATA4

AOSDATA3

AOSDATA2

AOSDATA1

AOSDATA0

HSYNC

VSYNC

VGA_SDA

VGA_SCL

VDACX_OUT

VDACY_OUT

AVDD33_VIDEO

AVDD12_RGB

AVSS33_VDAC_BG

AVSS12_RGB

AVSS33_VDAC

+3.3V_MULTI

R560

ROM_DL_UART_RX

DEBUG

R377

4.7K

+3.3V_MULTI

DEBUG

R378

4.7K

ROM_DL_UART_TX

I2C_SDA2

DISP_EN

I2C_SCL2

Y1

RXD0+

Y2

RXD0-

W3

RXD1+

W4

RXD1-

V3

RXD2+

V4

RXD2-

V1

RXDCK+

V2

RXDCK-

U3

RXD3+

U4

RXD3-

T3

RXD4+

T4

RXD4-

AD1

RXC0+

AD2

RXC0-

AC3

RXC1+

AC4

RXC1-

AB3

RXC2+

AB4

RXC2-

AB1

RXCCK+

AB2

RXCCK-

AA3

RXC3+

AA4

RXC3-

Y3

RXC4+

Y4

RXC4-

AH1

RXB0+

AH2

RXB0-

AG3

RXB1+

AG4

RXB1-

AF3

RXB2+

AF4

RXB2-

AF1

RXBCK+

AF2

RXBCK-

AE3

RXB3+

AE4

RXB3-

AD3

RXB4+

AD4

RXB4-

AM1

RXA0+

AM2

RXA0-

AL3

RXA1+

AL4

RXA1-

AK3

RXA2+

AK4

RXA2-

AK1

RXACK+

AK2

RXACK-

AJ3

RXA3+

AJ4

RXA3-

AH3

RXA4+

AH4

RXA4-

AK30

AJ29

AJ31

AK29

AJ30

AH28

AJ33

AC23

AG9

AG10

V27

AK9

AJ9

AF10

AH9

AK8

AJ8

AH8

AJ10

RP

GP

BP

COM

SOG

COM1

PB1P

PR1P

Y1P

SOY1

COM0

PB0P

PR0P

Y0P

SOY0

Don’t use as GPIO

AK18

AL18

AL20

AM20

AL19

AN20

AK19

AG22

AH22

EU

AL21

AK22

EU

EU

AL22

EU

AM21

AN21

AM23

AL23

AL24

AN23

AK23

AH24

AJ24

AN25

AN18

AC19

AK17

AE20

VDD3V3

R349 0

R350 10

AVDD3V3_AADC

C3770.01uF

C3780.01uF

C3790.01uF

C3710.01uF

C3720.01uF

C3730.01uF

C3740.01uF

C3751500pF

OPT

EU

+1.2V_MTK_AVDD

C382

0.1uF

EU

R38215K

R38315K

EU

R391100EUC3760.01uF

R392100

EU

EU

R393100

R394100

EU

EU

R3950

R361100

R362100

R363100

R364100

C320

330pF

50V

EU

C387

22pF

OPT

SC_G

SC_R

SC_B

SC_FB

COMP1_Pb

COMP1_Pr

COMP1_Y/AV1_CVBS

SC_CVBS_OUT

C321

330pF

50V

EU

C389

C393

22pF

22pF

OPT

OPT

SC_ROUT

SC_LOUT

ROM_DW_DA

SPDIF_OUT

ARC

AUD_SCK

AUD_LRCK

AUD_MASTER_CLK

AUD_LRCH

C396

33pF

OPT

R590

22

ROM_DL_UART_TX

ROM_DL_UART_RX

R591

22

For PCB Pattern

ROM_DW_CK

4.7K

RXD4+

RXD4RXD3+

RXD3-

RXDCK+

RXDCK-

RXD2+

RXD2RXD1+

RXD1RXD0+

RXD0-

RXC4+

RXC4RXC3+

RXC3-

RXCCK+

RXCCK-

RXC2+

RXC2RXC1+

RXC1RXC0+

RXC0-

RXB4+

RXB4RXB3+

RXB3-

RXBCK+

RXBCK-

RXB2+

RXB2RXB1+

RXB1RXB0+

RXB0-

RXA4+

RXA4RXA3+

RXA3-

RXACK+

RXACK-

RXA2+

RXA2RXA1+

RXA1RXA0+

RXA0-

R384

R385

R386 22

R387

27K

LVDS

P300

104060-8017

4.7K

R561

22

100

FHD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

RXB4+

RXB4RXB3+

RXB3-

RXBCK+

RXBCK-

RXB2+

RXB2RXB1+

RXB1RXB0+

RXB0-

RXA4+

RXA4RXA3+

RXA3-

RXACK+

RXACK-

RXA2+

RXA2RXA1+

RXA1RXA0+

RXA0-

TF05-51S

P301

HD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

MID_MAIN_2

2011.12.19

9

Page 15

VDD3V3

Copyright © 2014 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

+3.3V_MULTI

BLM18PG121SN1D

C503

10uF

VDD3V3

L501

L502

BLM18PG121SN1D

C505

10uF

C504

0.1uF

60mA

C507

0.1uF

C506

0.1uF

C508

2.2uF

AVDD_33SB

DECAP FOR SOC (HIDDEN - UCC)

+1.5V_DDR

C509

0.1uF

+1.2V_MTK_CORE

C555

OPT

0.1uF

+1.2V_MTK_CORE

C514

10uF

+1.5V_DDR

C526

0.1uF

+1.2V_MTK_CORE

C511

0.1uF

5600mA

C517

C522

10uF

10uF

C537

C530

0.1uF

0.1uF

L504

BLM18PG121SN1D

C518

10uF

C523

0.1uF

+1.2V_MTK_CORE

+1.2V_MTK_AVDD

OPT

C513

10uF

C520

0.1uF

OPT

C532

0.1uF

+3.3V_MULTI

3.3V_EMMC

L505

BLM18PG121SN1D

DECAP FOR SOC Rework (BOTTOM)

+1.2V_MTK_CORE

C533

0.1uF

C539

0.1uF

C534

0.1uF

C541

0.1uF

16V

OPT

OPT

OPT

+1.5V_DDR

OPT

C531

0.1uF

16V

VDD3V3

OPT

C536

0.1uF

VDD3V3

+1.2V_MTK_CORE

LGE2122[A2_M13]

L11

VCCK_1

N12

VCCK_2

P12

VCCK_3

AG5

VCCK_4

AH5

VCCK_5

AJ5

VCCK_6

AK5

VCCK_7

AL5

VCCK_8

AM5

VCCK_9

AN5

VCCK_10

AK6

VCCK_11

AL6

VCCK_12

AM6

VCCK_13

AN6

VCCK_14

M11

VCCK_15

N11

VCCK_16

P11

VCCK_17

R11

VCCK_18

M12

VCCK_19

R12

VCCK_20

L13

VCCK_21

L14

VCCK_22

L15

VCCK_23

L17

VCCK_24

L18

VCCK_25

L19

VCCK_26

T11

VCCK_27

U11

VCCK_28

V11

VCCK_29

W11

VCCK_30

Y11

VCCK_31

AA11

VCCK_32

AB11

VCCK_33

AC11

VCCK_34

R23

VCCK_35

L12

VCCK_36

W12

VCCK_37

V23

VCCK_38

Y12

VCCK_39

AF6

VCCK_40

AG6

VCCK_41

AH6

VCCK_42

AJ6

VCCK_43

AE7

VCCK_44

AF7

VCCK_45

AG7

VCCK_46

AD8

VCCK_47

AE8

VCCK_48

AF8

VCCK_49

AE9

VCCK_50

AC10

VCCK_51

AD10

VCCK_52

AD11

VCCK_53

AE10

VCCK_54

AF9

VCCK_55

AG8

VCCK_56

AH7

VCCK_57

AJ7

VCCK_58

AK7

VCCK_59

AL7

VCCK_60

AM7

VCCK_61

AN7

VCCK_62

L16

VCCK_63

V12

VCCK_64

U12

VCCK_65

T12

VCCK_66

AD13

VCCK_67

AD17

VCCK_68

AD14

VCCK_69

AB12

VCCK_70

AA12

VCCK_71

AC12

VCCK_72

T9

VCC3IO_C

Y10

VCC3IO_B_1

AA10

VCC3IO_B_2

D22

VCC3IO_A_1

E22

VCC3IO_A_2

AC18

DVSS_1

AB21

DVSS_2

AB14

DVSS_3

N13

DVSS_4

P13

DVSS_5

R13

DVSS_6

T13

DVSS_7

U13

DVSS_8

V13

DVSS_9

W13

DVSS_10

Y13

DVSS_11

P18

DVSS_12

N14

DVSS_13

P14

DVSS_14

R14

DVSS_15

T14

DVSS_16

U14

DVSS_17

V14

DVSS_18

W14

DVSS_19

Y14

DVSS_20

R18

DVSS_21

N15

DVSS_22

P15

DVSS_23

IC105

DVSS_24

DVSS_25

DVSS_26

DVSS_27

DVSS_28

DVSS_29

DVSS_30

DVSS_31

DVSS_32

DVSS_33

DVSS_34

DVSS_35

DVSS_36

DVSS_37

DVSS_38

DVSS_39

DVSS_40

DVSS_41

DVSS_42

DVSS_43

DVSS_44

DVSS_45

DVSS_46

DVSS_47

DVSS_48

DVSS_49

DVSS_50

DVSS_51

DVSS_52

DVSS_53

DVSS_54

DVSS_55

DVSS_56

DVSS_57

DVSS_58

DVSS_59

DVSS_60

DVSS_61

DVSS_62

DVSS_63

DVSS_64

DVSS_65

DVSS_66

DVSS_67

DVSS_68

DVSS_69

DVSS_70

DVSS_71

DVSS_72

DVSS_73

DVSS_74

DVSS_75

DVSS_76

DVSS_77

DVSS_78

DVSS_79

DVSS_80

DVSS_81

DVSS_82

DVSS_83

DVSS_84

DVSS_85

DVSS_86

DVSS_87

DVSS_88

DVSS_89

DVSS_90

DVSS_91

DVSS_92

DVSS_93

DVSS_94

DVSS_95

DVSS_96

DVSS_97

DVSS_98

DVSS_99

DVSS_100

DVSS_101

DVSS_102

DVSS_103

DVSS_104

DVSS_105

DVSS_106

DVSS_107

DVSS_108

DVSS_109

DVSS_110

DVSS_111

DVSS_112

DVSS_113

DVSS_114

DVSS_115

DVSS_116

DVSS_117

DVSS_118

DVSS_119

DVSS_120

DVSS_121

DVSS_122

DVSS_123

DVSS_124

DVSS_125

DVSS_126

DVSS_127

R15

T15

U15

V15

W15

Y15

AA15

AB15

T18

R16

T16

U16

V16

W16

Y16

AA16

AB16

R17

T17

U17

V17

Y17

N16

V18

Y18

P16

V19

Y19

W17

AA17

AB17

N19

AC14

C13

K24

K25

L24

M17

M18

M19

P17

P19

N18

U20

V20

W20

Y20

AA20

R19

T19

M20

N20

U21

V21

W21

Y21

AA21

P20

R20

T20

U22

V22

W22

Y22

AA22

N21

P21

R21

T21

M22

N22

P22

R22

T22

M21

AC17

AA19

M13

M14

M15

AA13

AB13

AA14

AB19

D6

W19

U19

N17

L3

AB18

AA18

W18

U18

D16

AC13

M16

AC20

AC22

AD20

Y23

AA23

AB23

V24

W23

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

MID_MAIN_3

2011.12.09

10

Page 16

CH : A , (512MB x16) x2

Copyright © 2014 LG Electronics Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

A_RVREF1

A_RVREF4

+1.5V_DDR

+1.5V_DDR

DDR_512MB_SS

IC701

K4B4G1646B-HCK0

R710

A_RVREF4

A_RVREF1

+1.5V_DDR

A10/AP

A12/BC

RESET

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

ARA[10]

L7

ARA[11]

R7

A11

ARA[12]

N7

ARA[13]

T3

A13

ARA[14]

T7

A14

M7

A15

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE

L2

CS

K1

ODT

J3

RAS

K3

CAS

L3

WE

T2

F3

DQSL

G3

DQSL

C7

DQSU

B7

DQSU

E7

DML

D3

DMU

E3

DQL0

F7

DQL1

F2

DQL2

F8

DQL3

H3

DQL4

H8

DQL5

G2

DQL6

H7

DQL7

D7

DQU0

C3

DQU1

C8

DQU2

C2

DQU3

A7

DQU4

A2

DQU5

B8

DQU6

A3

DQU7

M8

VREFCA

H1

VREFDQ

1%

240

L8

ZQ

B2

VDD_1

D9

VDD_2

G7

VDD_3

K2

VDD_4

K8

VDD_5

N1

VDD_6

N9

VDD_7

R1

VDD_8

R9

VDD_9

A1

VDDQ_1

A8

VDDQ_2

C1

VDDQ_3

C9

VDDQ_4

D2

VDDQ_5

E9

VDDQ_6

F1

VDDQ_7

H2

VDDQ_8

H9

VDDQ_9

J1

NC_1

J9

NC_2

L1

NC_3

L9

NC_4

A9

VSS_1

B3

VSS_2

E1

VSS_3

G8

VSS_4

J2

VSS_5

J8

VSS_6

M1

VSS_7

M9

VSS_8

P1

VSS_9

P9

VSS_10

T1

VSS_11

T9

VSS_12

B1

VSSQ_1

B9

VSSQ_2

D1

VSSQ_3

D8

VSSQ_4

E2

VSSQ_5

E8

VSSQ_6

F9

VSSQ_7

G1

VSSQ_8

G9

VSSQ_9

C713

R706

0.1uF

1K

1%

R707

C714

1K

1%

0.1uF

C715

R708

0.1uF

1K

1%

R709

C716

1K

1%

0.1uF

ARA[0]

ARA[1]

ARA[2]

ARA[3]

ARA[4]

ARA[5]

ARA[6]

ARA[7]

ARA[8]

ARA[9]

ARBA0

ARBA1

ARBA2

ARCKE

/ARCS

ARODT

/ARRAS

/ARCAS

/ARWE

ARREST

ARDQS0

/ARDQS0

ARDQS1

/ARDQS1

ARDQM0

ARDQM1

ARDQ[0]

ARDQ[1]

ARDQ[2]

ARDQ[3]

ARDQ[4]

ARDQ[5]

ARDQ[6]

ARDQ[7]

ARDQ[8]

ARDQ[9]

ARDQ[10]

ARDQ[11]

ARDQ[12]

ARDQ[13]

ARDQ[14]

ARDQ[15]

ARA[0-14]

ARCLK0

R712

100

5%

/ARCLK0

ARDQ[0-7]

ARDQ[8-15]

ARCLK1

/ARCLK1

ARDQ[16-23]

ARDQ[24-31]

ARA[0-14]

R714

100

5%

DDR_512MB_SS

ARA[0]

N3

ARA[1]

P7

ARA[2]

P3

ARA[3]

N2

ARA[4]

P8

ARA[5]

P2

ARA[6]

R8

ARA[7]

R2

ARA[8]

T8

ARA[9]

R3

ARA[10]

L7

ARA[11]

R7

ARA[12]

N7

ARA[13]

T3

ARA[14]

T7

M7

M2

N8

M3

J7

K7

K9

L2

K1

J3

K3

L3

T2

F3

G3

C7

B7

E7

D3

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

ARDQ[16]

ARDQ[17]

ARDQ[18]

ARDQ[19]

ARDQ[20]

ARDQ[21]

ARDQ[22]

ARDQ[23]

ARDQ[24]

ARDQ[25]

ARDQ[26]

ARDQ[27]

ARDQ[28]

ARDQ[29]

ARDQ[30]

ARDQ[31]

ARBA0

ARBA1

ARBA2

ARCKE

/ARCSX

ARODT

/ARRAS

/ARCAS

/ARWE

ARREST

ARDQS2

/ARDQS2

ARDQS3

/ARDQS3

ARDQM2

ARDQM3

IC703

K4B4G1646B-HCK0

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC

A13

A14

A15

BA0

BA1

BA2

CK

CK

CKE

CS

ODT

RAS

CAS

WE

RESET

DQSL

DQSL

DQSU

DQSU

DML

DMU

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VREFCA

VREFDQ

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

VSS_10

VSS_11

VSS_12

VSSQ_1

VSSQ_2

VSSQ_3

VSSQ_4

VSSQ_5

VSSQ_6

VSSQ_7

VSSQ_8

VSSQ_9

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

A_RVREF2

M8

A_RVREF3

H1

1%

240

R716

L8

ZQ

+1.5V_DDR

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

J1

NC_1

J9

NC_2

L1

NC_3

L9

NC_4

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

DDR_512MB_HYNIX

H5TQ4G63AFR-PBC

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

M7

M2

N8

M3

J7

K7

K9

L2

K1

J3

K3

L3

T2

F3

G3

C7

B7

E7

D3

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

IC701-*1

M8

VREFCA

A0

A1

A2

H1

VREFDQ

A3

A4

A5

L8

ZQ

A6

A7

A8

B2

A9

VDD_1

D9

A10/AP

VDD_2

G7

A11

VDD_3

K2

A12/BC

VDD_4

K8

VDD_5

A13

N1

A14

VDD_6

N9

VDD_7

A15

R1

VDD_8

R9

VDD_9

BA0

BA1

BA2

A1

VDDQ_1

A8

VDDQ_2

CK

C1

VDDQ_3

CK

C9

VDDQ_4

CKE

D2

VDDQ_5

E9

VDDQ_6

CS

F1

VDDQ_7

ODT

H2

VDDQ_8

RAS

H9

VDDQ_9

CAS

WE

J1

NC_1

J9

NC_2

RESET

L1

NC_3

L9

NC_4

DQSL

DQSL

A9

VSS_1

DQSU

B3

VSS_2

DQSU

E1

VSS_3

G8

VSS_4

DML

J2

VSS_5

DMU

J8

VSS_6

M1

VSS_7

DQL0

M9

VSS_8

DQL1

P1

VSS_9

DQL2

P9

VSS_10

DQL3

T1

VSS_11

DQL4

T9

VSS_12

DQL5

DQL6

DQL7

B1

VSSQ_1

B9

VSSQ_2

DQU0

D1

VSSQ_3

DQU1

D8

VSSQ_4

DQU2

E2

VSSQ_5

DQU3

E8

VSSQ_6

DQU4

F9

VSSQ_7

DQU5

G1

VSSQ_8

DQU6

G9

VSSQ_9

DQU7

DDR_512MB_HYNIX

IC703-*1

H5TQ4G63AFR-PBC

M8

N3

VREFCA

A0

P7

A1

P3

A2

N2

H1

A3

VREFDQ

P8

A4

P2

A5

R8

L8

A6

ZQ

R2

A7

T8

A8

R3

B2

A9

VDD_1

L7

D9

A10/AP

VDD_2

R7

G7

A11

VDD_3

N7

K2

A12/BC

VDD_4

T3

K8

A13

VDD_5

T7

N1

A14

VDD_6

N9

M7

VDD_7

A15

R1

VDD_8

R9

M2

VDD_9

BA0

N8

BA1

M3

BA2

A1

VDDQ_1

A8

J7

VDDQ_2

CK

C1

K7

VDDQ_3

CK

C9

K9

VDDQ_4

CKE

D2

VDDQ_5

E9

L2

VDDQ_6

CS

F1

K1

VDDQ_7

ODT

H2

J3

VDDQ_8

RAS

H9

K3

VDDQ_9

CAS

L3

WE

J1

NC_1

J9

T2

NC_2

RESET

L1

NC_3

L9

NC_4

F3

DQSL

G3

DQSL

A9

C7

VSS_1

DQSU

B3

B7

VSS_2

DQSU

E1

VSS_3

G8

E7

VSS_4

DML

J2

D3

VSS_5

DMU

J8

VSS_6

M1

E3

VSS_7

DQL0

M9

F7

VSS_8

DQL1

P1

F2

VSS_9

DQL2

P9

F8

VSS_10

DQL3

T1

H3

VSS_11

DQL4

T9

H8

VSS_12

DQL5

G2

DQL6

H7

DQL7

B1

VSSQ_1

B9

D7

VSSQ_2

DQU0

D1

C3

VSSQ_3

DQU1

D8

C8

VSSQ_4

DQU2

E2

C2

VSSQ_5

DQU3

E8

A7

VSSQ_6

DQU4

F9

A2

VSSQ_7

DQU5

G1

B8

VSSQ_8

DQU6

G9

A3

VSSQ_9

DQU7

DDR_512MB_MICRON

DDR_512MB_MICRON

IC701-*2

MT41K256M16HA-125:E

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC

T3

A13

M7

NC_5

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE

L2

CS

K1

ODT

J3

RAS

K3

CAS

L3

WE

T2

RESET

F3

DQSL

G3

DQSL

C7

DQSU

B7

DQSU

E7

DML

D3

DMU

E3

DQ0

F7

DQ1

F2

DQ2

F8

DQ3

H3

DQ4

H8

DQ5

G2

DQ6

H7

DQ7

D7

DQ8

C3

DQ9

C8

DQ10

C2

DQ11

A7

DQ12

A2

DQ13

B8

DQ14

A3

DQ15

MT41K256M16HA-125:E

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

M7

M2

N8

M3

J7

K7

K9

L2

K1

J3

K3

L3

T2

F3

G3

C7

B7

E7

D3

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

M8

VREFCA

H1

VREFDQ

L8

ZQ

B2

VDD_1

D9

VDD_2

G7

VDD_3

K2

VDD_4

K8

VDD_5

N1

VDD_6

N9

VDD_7

R1

VDD_8

R9

VDD_9

A1

VDDQ_1

A8

VDDQ_2

C1

VDDQ_3

C9

VDDQ_4

D2

VDDQ_5

E9

VDDQ_6

F1

VDDQ_7

H2

VDDQ_8

H9

VDDQ_9

J1

NC_1

J9

NC_2

L1

NC_3

L9

NC_4

T7

A14

A9

VSS_1

B3

VSS_2

E1

VSS_3

G8

VSS_4

J2

VSS_5

J8

VSS_6

M1

VSS_7

M9

VSS_8

P1

VSS_9

P9

VSS_10

T1

VSS_11

T9

VSS_12

B1

VSSQ_1

B9

VSSQ_2

D1

VSSQ_3

D8

VSSQ_4

E2

VSSQ_5

E8

VSSQ_6

F9

VSSQ_7

G1

VSSQ_8

G9

VSSQ_9

IC703-*2

M8

VREFCA

A0

A1

A2

H1

VREFDQ

A3

A4

A5

L8

A6

ZQ

A7

A8

B2

A9

VDD_1

D9

A10/AP

VDD_2

G7

A11

VDD_3

K2

A12/BC

VDD_4

K8

VDD_5

A13

N1

VDD_6

N9

VDD_7

NC_5

R1

VDD_8

R9

VDD_9

BA0

BA1

BA2

A1

VDDQ_1

A8

VDDQ_2

CK

C1

VDDQ_3

CK

C9

VDDQ_4

CKE

D2

VDDQ_5

E9

VDDQ_6

CS

F1

VDDQ_7

ODT

H2

VDDQ_8

RAS

H9

VDDQ_9

CAS

WE

J1

NC_1

J9

NC_2

RESET

L1

NC_3

L9

NC_4

T7

A14

DQSL

DQSL

A9

VSS_1

DQSU

B3

VSS_2

DQSU

E1

VSS_3

G8

VSS_4

DML

J2

VSS_5

DMU

J8

VSS_6

M1

VSS_7

DQ0

M9

VSS_8

DQ1

P1

VSS_9

DQ2

P9

VSS_10

DQ3

T1

VSS_11

DQ4

T9

VSS_12

DQ5

DQ6

DQ7

B1

VSSQ_1

B9

VSSQ_2

DQ8

D1

VSSQ_3

DQ9

D8

VSSQ_4

DQ10

E2

VSSQ_5

DQ11

E8

VSSQ_6

DQ12

F9

VSSQ_7

DQ13

G1

VSSQ_8

DQ14

G9

VSSQ_9

DQ15

A_RVREF2

A_RVREF3

+1.5V_DDR

R720

1K

1%

R721

1K

1%

R718

1K

1%

R719

1K

1%

+1.5V_DDR

C735

0.1uF

C736

0.1uF

C733

0.1uF

C734

0.1uF

RVREF_A

+1.5V_DDR

C746

R730

0.1uF

1K

1%

R731

1K

C747

1%

0.1uF

RVREF_A

ARA[0-14]

ARCKE

ARCLK1

/ARCLK1

ARCLK0

/ARCLK0

ARODT

/ARRAS

/ARCAS

/ARCS

/ARWE

ARREST

ARBA0

ARBA1

ARBA2

/ARCSX

+1.5V_DDR

TP700

TP701

ARA[14]

ARA[13]

ARA[12]

ARA[11]

ARA[10]

ARA[9]

ARA[8]

ARA[7]

ARA[6]

ARA[5]

ARA[4]

ARA[3]

ARA[2]

ARA[1]

ARA[0]

LGE2122[A2_M13]

R1

DDRV_1

R2

DDRV_2

R3

DDRV_3

R4

DDRV_4

R5

DDRV_5

K3

DDRV_6

R6

DDRV_7

L8

DDRV_8

M8

DDRV_9

D17

DDRV_10

A19

DDRV_11

J22

MEMTP

K22

MEMTN

D18

RVREF_A

G8

ARCKE

B5

ARCLK1

A5

ARCLK1

B14

ARCLK0

A14

ARCLK0

F13

ARODT

E13

ARRAS

G13

ARCAS

G15

ARCS

H18

ARWE

G16

ARRESET

D15

ARBA0

F9

ARBA1

G18

ARBA2

F15

ARCSX

D11

ARA14

F16

ARA13

D8

ARA12

E11

ARA11

G9

ARA10

E16

ARA9

F11

ARA8

G17

ARA

F10

ARA6

E17

ARA5

E10

ARA4

E15

ARA3

F17

ARA2

G10

ARA1

F18

ARA0

IC105

ARDQM0

ARDQS0

ARDQS0

ARDQ0

ARDQ1

ARDQ2

ARDQ3

ARDQ4

ARDQ5

ARDQ6

ARDQ7

ARDQM1

ARDQS1

ARDQS1

ARDQ8

ARDQ9

ARDQ10

ARDQ11

ARDQ12

ARDQ13

ARDQ14

ARDQ15

ARDQM2

ARDQS2

ARDQS2

ARDQ16

ARDQ17

ARDQ18

ARDQ19

ARDQ20

ARDQ21

ARDQ22

ARDQ23

ARDQM3

ARDQS3

ARDQS3

ARDQ24

ARDQ25

ARDQ26

ARDQ27

ARDQ28

ARDQ29

ARDQ30

ARDQ31

AVDD33_MEMPLL

AVSS33_MEMPLL

D12

ARDQM0

D14

ARDQS0

C14

/ARDQS0

ARDQM1

ARDQS1

/ARDQS1

ARDQM2

ARDQS2

/ARDQS2

ARDQM3

ARDQS3

/ARDQS3

ARDQ[0]

ARDQ[1]

ARDQ[2]

ARDQ[3]

ARDQ[4]

ARDQ[5]

ARDQ[6]

ARDQ[7]

ARDQ[8]

ARDQ[9]

ARDQ[10]

ARDQ[11]

ARDQ[12]

ARDQ[13]

ARDQ[14]

ARDQ[15]

ARDQ[16]

ARDQ[17]

ARDQ[18]

ARDQ[19]

ARDQ[20]

ARDQ[21]

ARDQ[22]

ARDQ[23]

ARDQ[24]

ARDQ[25]

ARDQ[26]

ARDQ[27]

ARDQ[28]

ARDQ[29]

ARDQ[30]

ARDQ[31]

B17

D10

C17

C10

C18

B9

E18

D9

C15

A13

B13

B11

B16

A11

A17

C12

A16

C11

C16

A3

D5

C5

E7

B2

C8

B1

A9

C1

C9

C3

C6

A4

B4

A1

B7

C4

C7

B3

A7

A2

D7

A20

H9

0.1uF

ARDQ[0-7]

ARDQ[8-15]

ARDQ[16-23]

ARDQ[24-31]

VDD3V3

C700

B_RVREF5

B_RVREF6

+1.5V_DDR

+1.5V_DDR

CH : B , 256MB x16

DDR_512MB_SS

B_RVREF5

B_RVREF6

R711

+1.5V_DDR

1%

240

C709

R702

0.1uF

1K

1%

R703

1K

C710

1%

0.1uF

C711

R704

0.1uF

1K

1%

R705

C712

1K

1%

0.1uF

IC702

K4B4G1646B-HCK0

M8

VREFCA

H1

VREFDQ

L8

ZQ

B2

VDD_1

D9

VDD_2

G7

VDD_3

K2

VDD_4

K8

VDD_5

N1

VDD_6

N9

VDD_7

R1

VDD_8

R9

VDD_9

A1

VDDQ_1

A8

VDDQ_2

C1

VDDQ_3

C9

VDDQ_4

D2

VDDQ_5

E9

VDDQ_6

F1

VDDQ_7

H2

VDDQ_8

H9

VDDQ_9

J1

NC_1

J9

NC_2

L1

NC_3

L9

NC_4

A9

VSS_1

B3

VSS_2

E1

VSS_3

G8

VSS_4

J2

VSS_5

J8

VSS_6

M1

VSS_7

M9

VSS_8

P1

VSS_9

P9

VSS_10

T1

VSS_11

T9

VSS_12

B1

VSSQ_1

B9

VSSQ_2

D1

VSSQ_3

D8

VSSQ_4

E2

VSSQ_5

E8

VSSQ_6

F9

VSSQ_7

G1

VSSQ_8

G9

VSSQ_9

A10/AP

A12/BC

RESET

DDR_256MB_SS

BRA[0-14]

BRA[0]

N3

A0

BRA[1]

P7

A1

BRA[2]

P3

A2

BRA[3]

N2

A3

BRA[4]

P8

A4

BRA[5]

P2

A5

BRA[6]

R8

A6

BRA[7]

R2

A7

BRA[8]

T8

A8

BRA[9]

R3

A9

BRA[10]

L7

BRA[11]

R7

A11

BRA[12]

N7

BRA[13]

T3

A13

T7

A14

M7

A15

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE

L2

CS

K1

ODT

J3

RAS

K3

CAS

L3

WE

T2

F3

DQSL

G3

DQSL

C7

DQSU

B7

DQSU

E7

DML

D3

DMU

E3

BRDQ[0]

DQL0

F7

BRDQ[1]

DQL1

F2

BRDQ[2]

DQL2

F8

BRDQ[3]

DQL3

H3

BRDQ[4]

DQL4

H8

BRDQ[5]

DQL5

G2

BRDQ[6]

DQL6

H7

BRDQ[7]

DQL7

BRDQ[8]

D7

DQU0

BRDQ[9]

C3

DQU1

BRDQ[10]

C8

DQU2

BRDQ[11]

C2

DQU3

BRDQ[12]

A7

DQU4

BRDQ[13]

A2

DQU5

BRDQ[14]

B8

DQU6

BRDQ[15]

A3

DQU7

BRBA0

BRBA1

BRBA2

BRCKE

/BRCS

BRODT

/BRRAS

/BRCAS

/BRWE

BRREST

BRDQS0

/BRDQS0

BRDQS1

/BRDQS1

BRDQM0

BRDQM1

BRA[14]

BRA[15]

R713

100

5%

BRDQ[0-7]

BRDQ[8-15]

BRCLK0