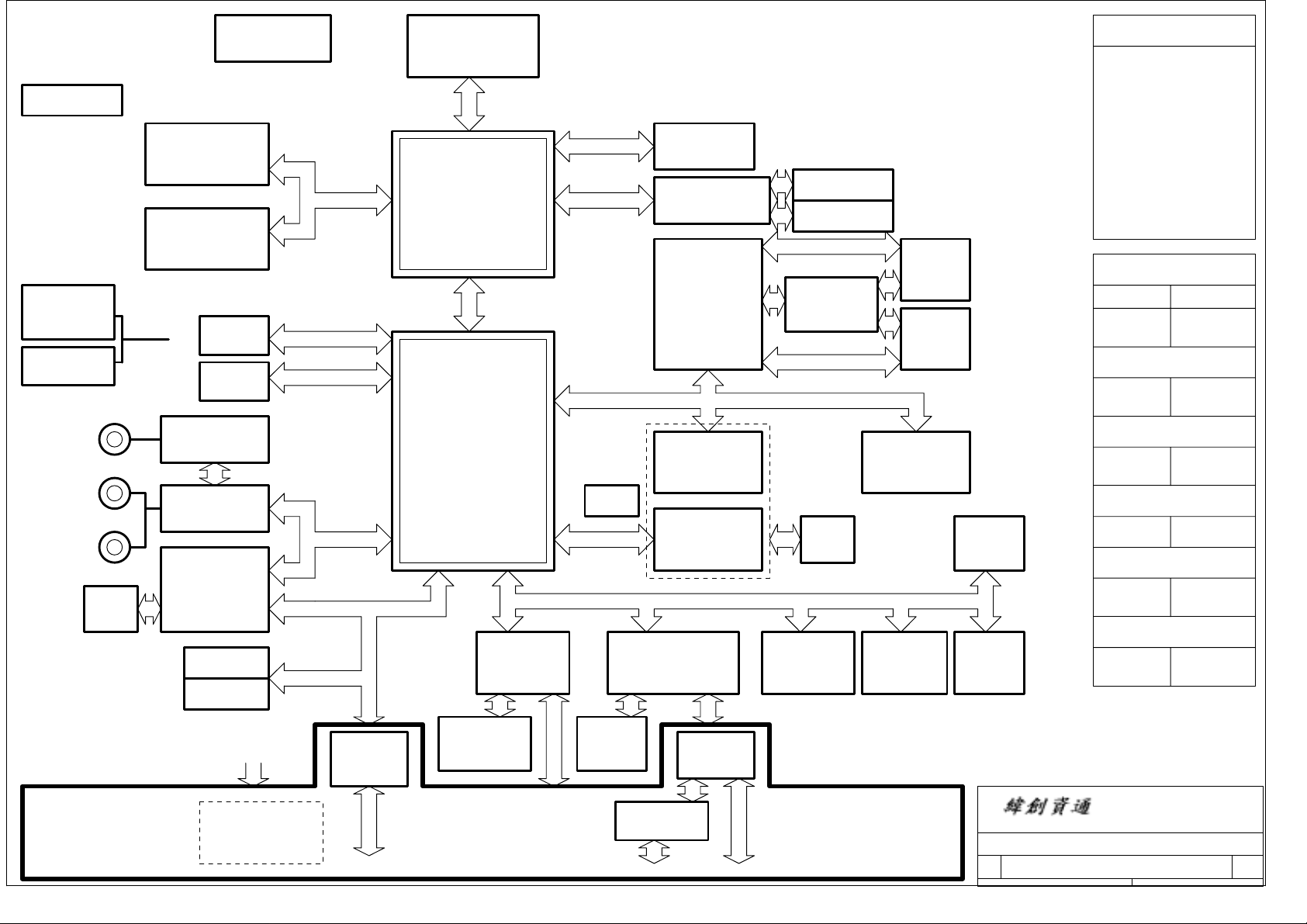

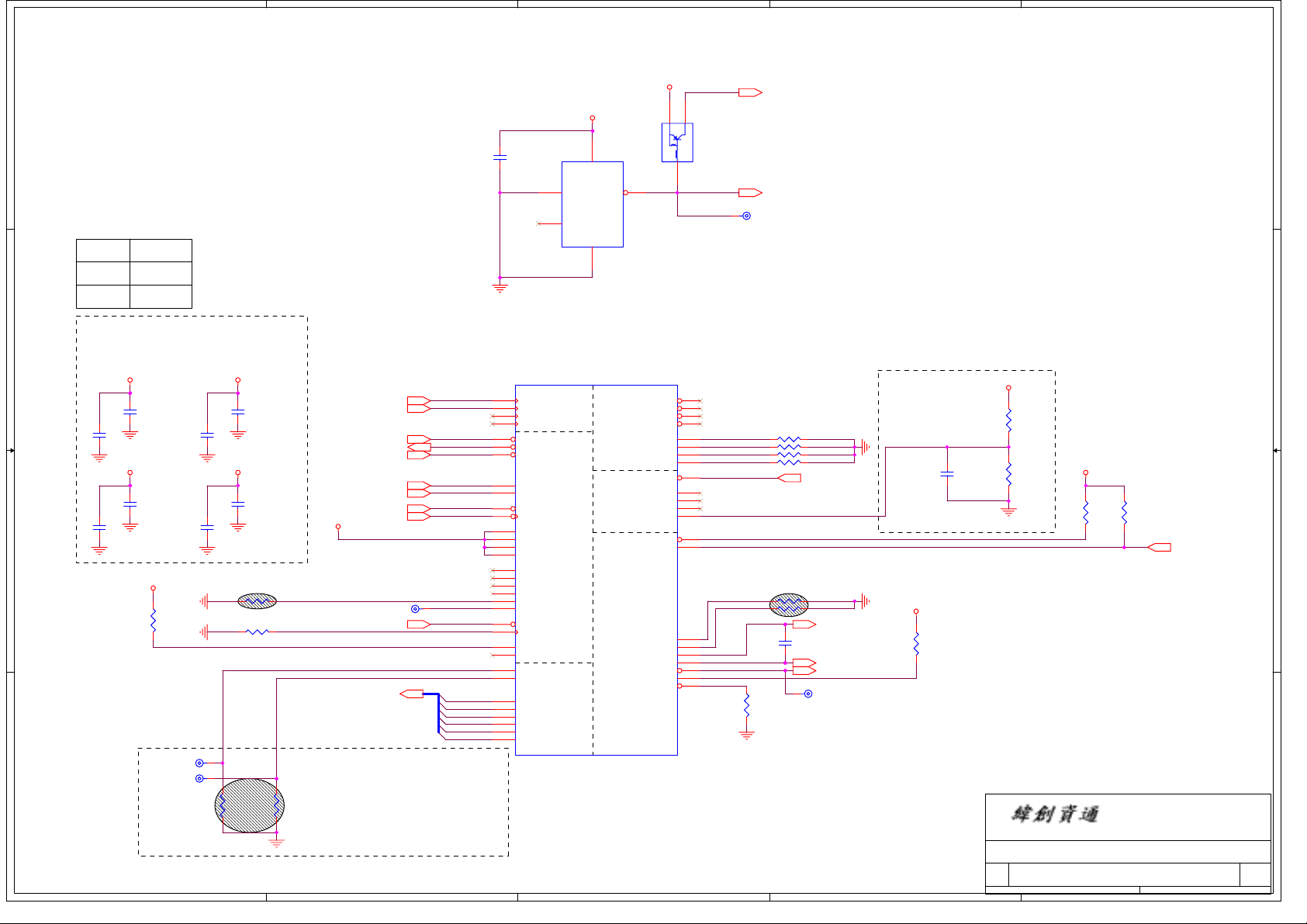

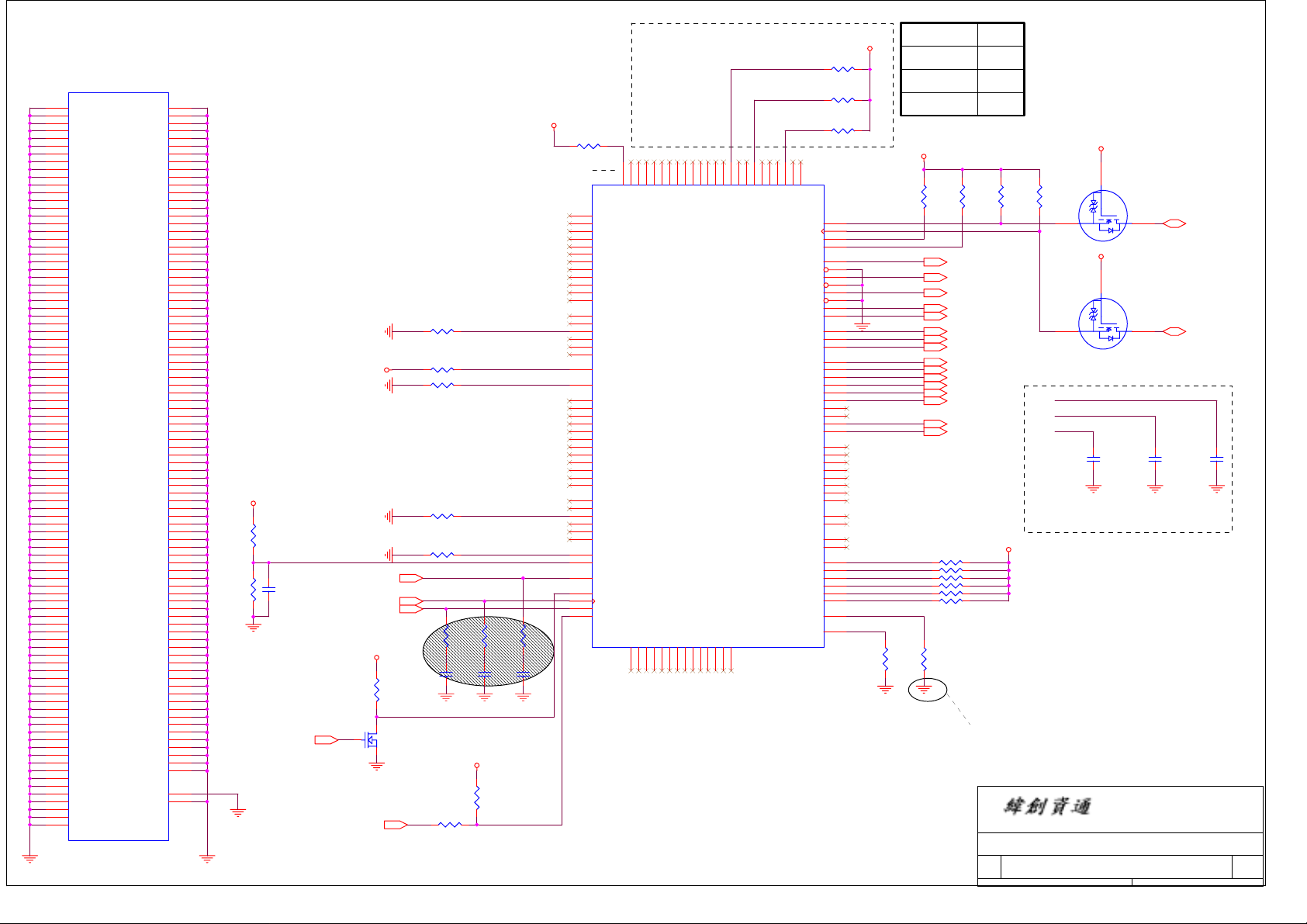

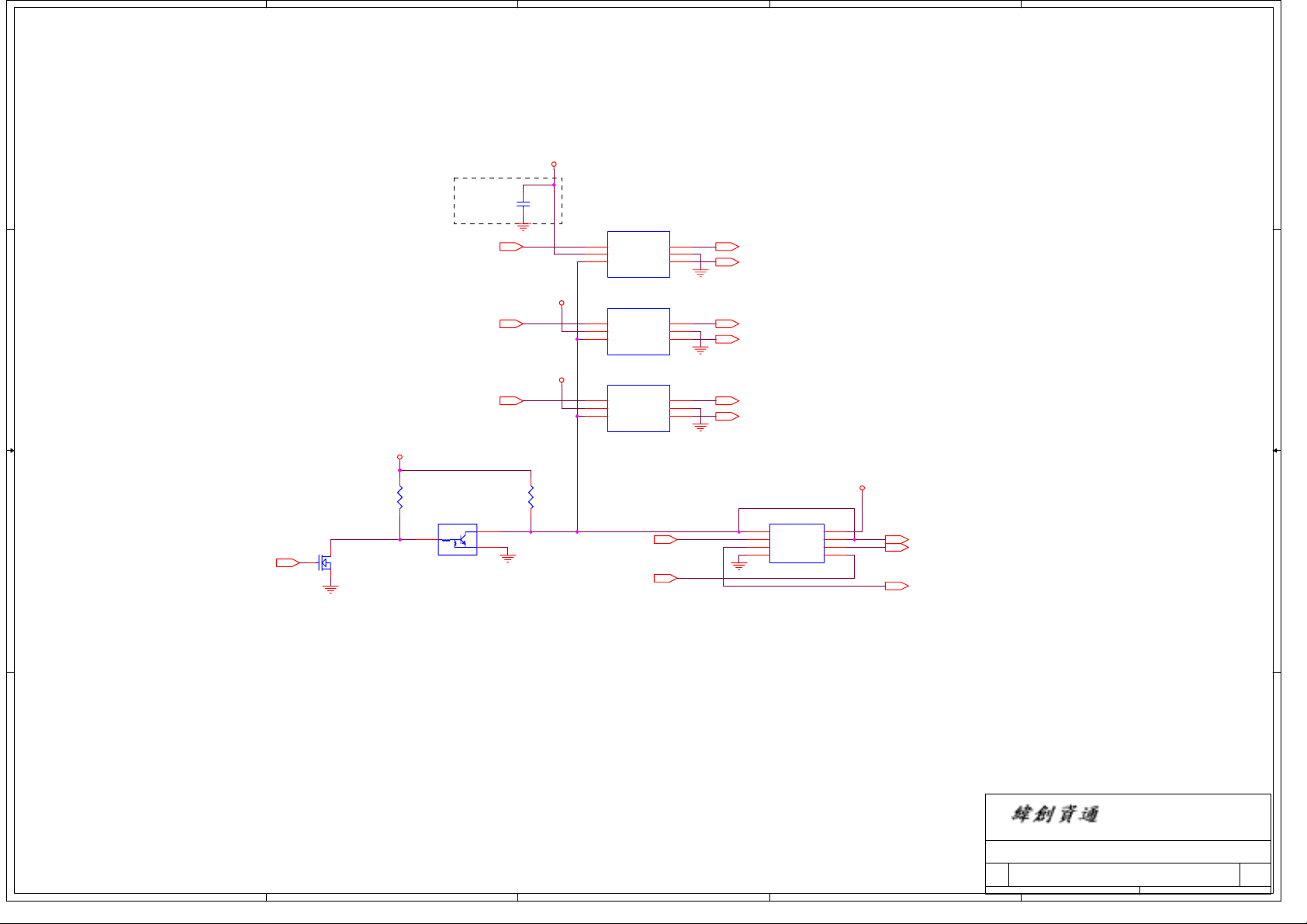

Lenovo X41 Schematics

Nov 12 '03

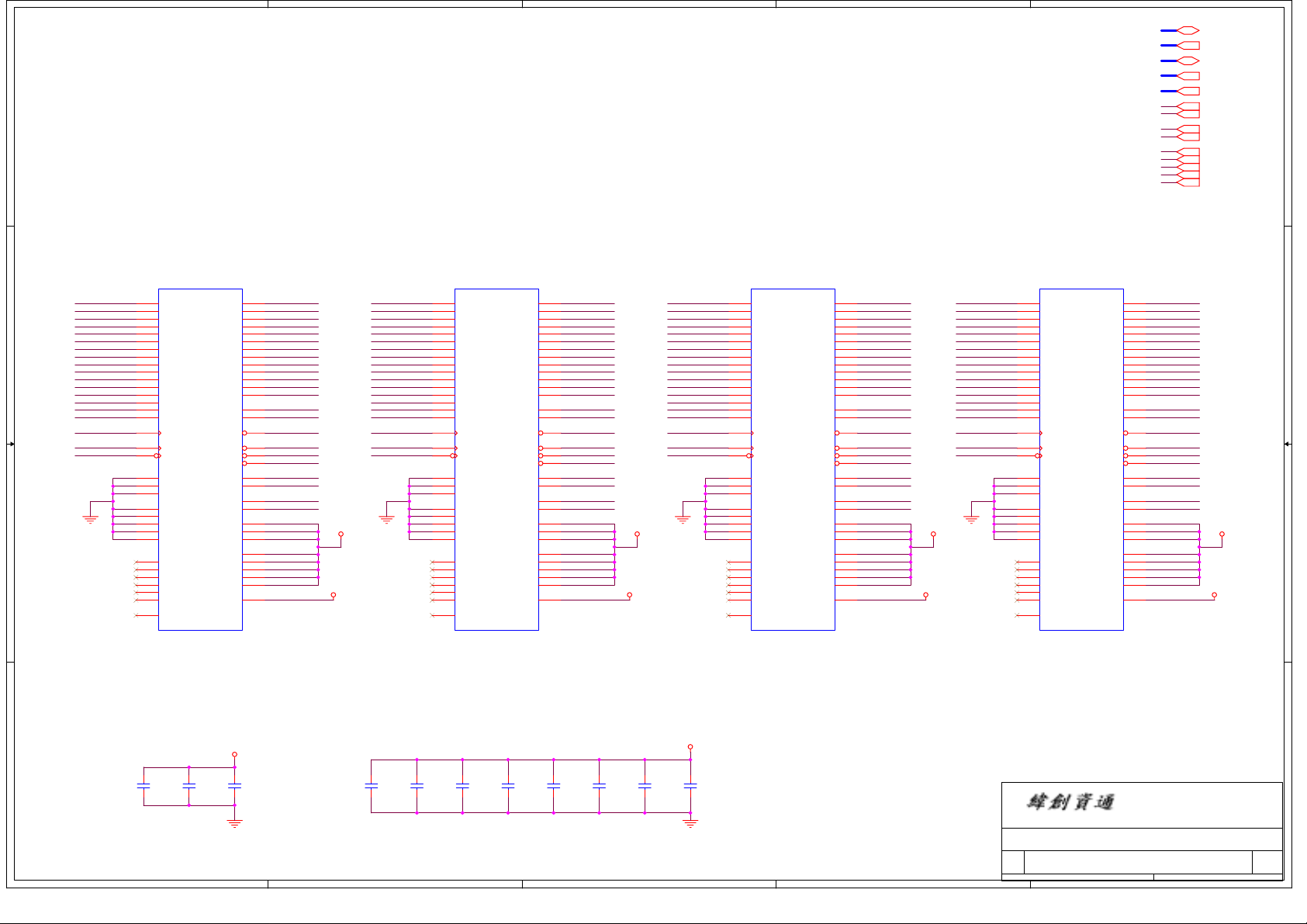

Keyboard Light

Thermal Sensor

LM83+LM26+DS75

47

ATMEL

AT24RF08CN

48

LINE OUT

Int. MIC

MIC IN

RJ11

CONN

33

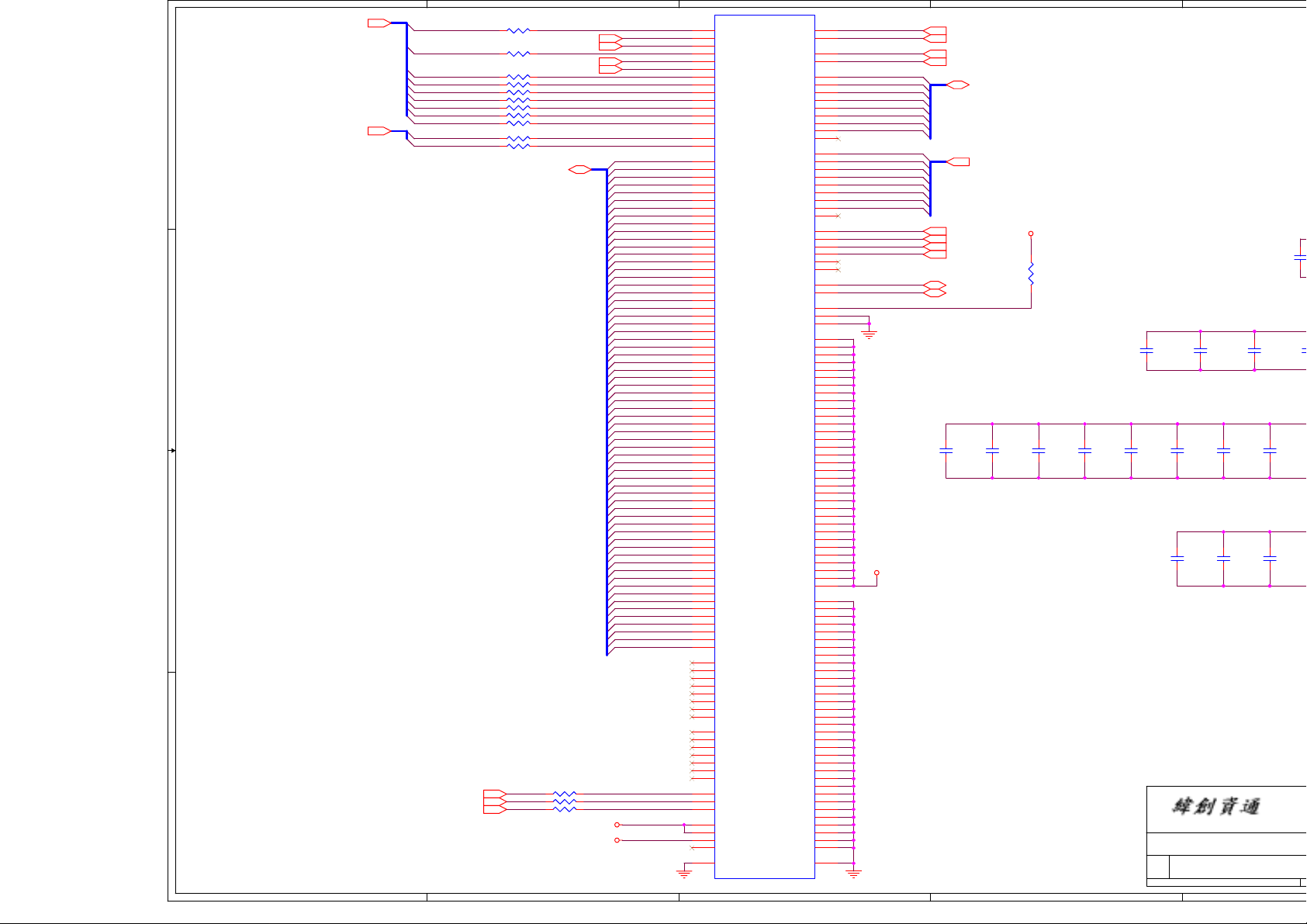

Clock Generator

ICS950813

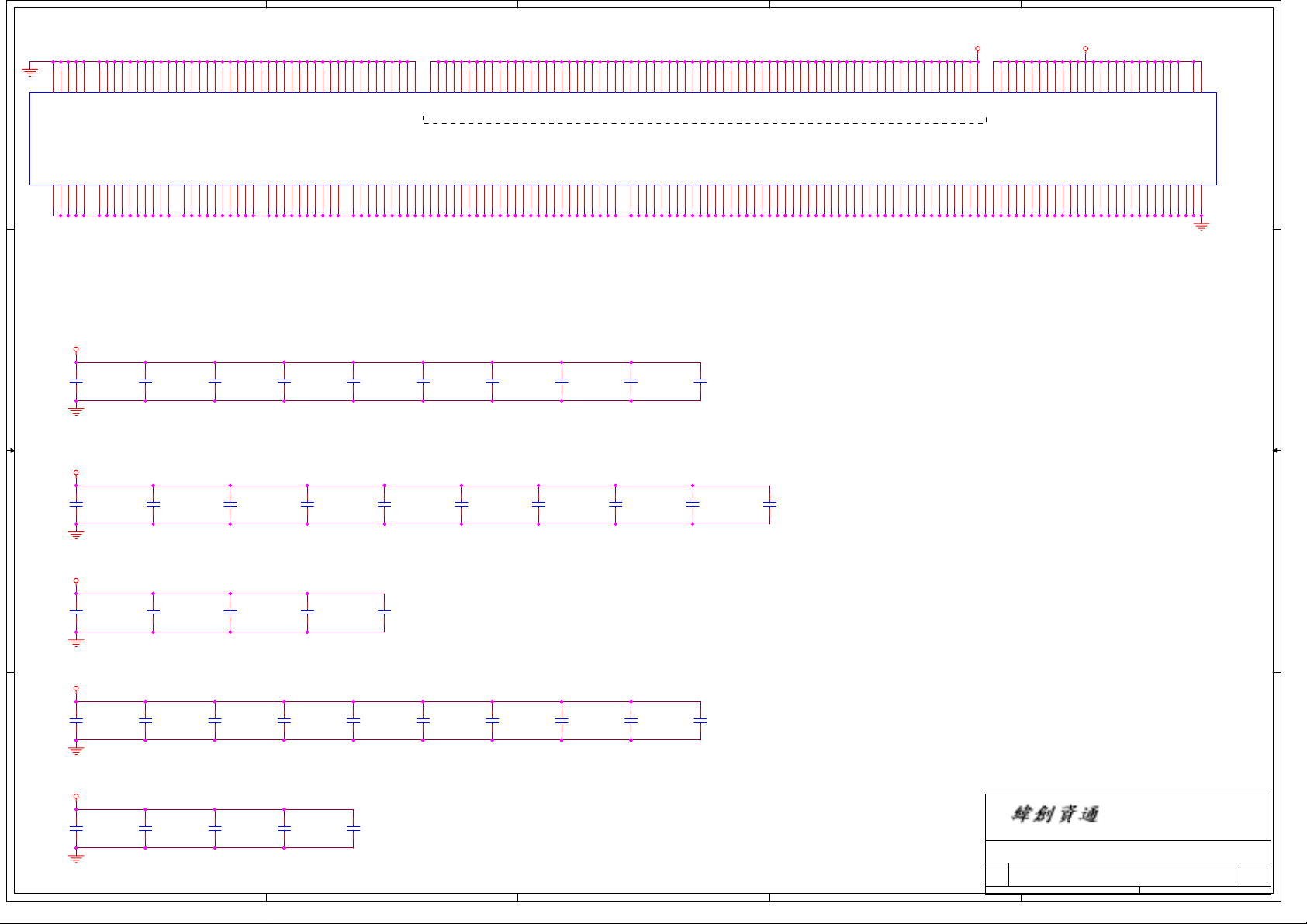

UNBUFFERED

On-Board DDR

SODIMM x 8

11,12,13,15,16

200-PIN DDR SODIMM DDR 200/266/333

UNBUFFERED

DDR SODIMM

Socket

14,15,16

SMBus

Media

Slice

HDD

46

Secondary IDE

ATA 66/100

Primary IDE

ATA 66/100

23

OP AMP

MAX9750

39

AC97 CODEC

AD1981B

36,37,38

CDC

Modem/Bluetooth

CH4

35

USB 1

USB 2

24,25

24,25

CH2,3

Secondary IDE

3

AC LINK

USB 2.0

USB Hub

SMSC

USB20H04

Intel Mobile CPU

Banias/Dothan

4,5,6

400MHzAGTL+ FSB

Intel

Motara-GM Plus

AGTL+ CPU I/F

DDR Memory I/F

INTEGRATED GRAHPICS

LVDS, CRT I/F

7,8,9,10

Hub-LINK

66MHz

Intel

ICH4-M

USB 2.0 (2+2+2)

ETHERNET (10/100Mb)

AC97 2.2

ATA 66/100

ACPI 1.1

LPC I/F

PCI/PCI BRIDGE

INT. RTC

20,21,22

KBC

H8S/2161B

Int. KB

Track point IV

42

41

LVDS

RGB CRT

PCI Bus / 33MHz

ATMEL

AT93C46

LAN MII

LPC Bus / 33MHz

NS FIR & LPC SW

PC87382

FIR

IRMS6452

39

S Note-1 Block Diagram

03209-2-Final

12.1'' XGA LCD

18

33

46

19

28

Mini-PCI

802.11a/b/g

Board Conn

SD

Socket

30

PCMCIA

SLOT

29

34

PMH-4

G/A

TCPA

Chip

41

CRT SELECTION

17

RICOH

R5C5811

Cardbus + SD Card

26,27

Intel Ethernet

Giga LAN

82541EX

31,32

OR

Intel Ethernet

10/100 PHY

82562EZ

31,32

45 40

LPC Bus

NX SIO

PC87392

Media Slice

CRT Port

MediaBay I/F

Power Switch

TPS2205

PCMCIA I/F

RJ45

CONN

FWH LPC Debug

SST-49LF008

43

44

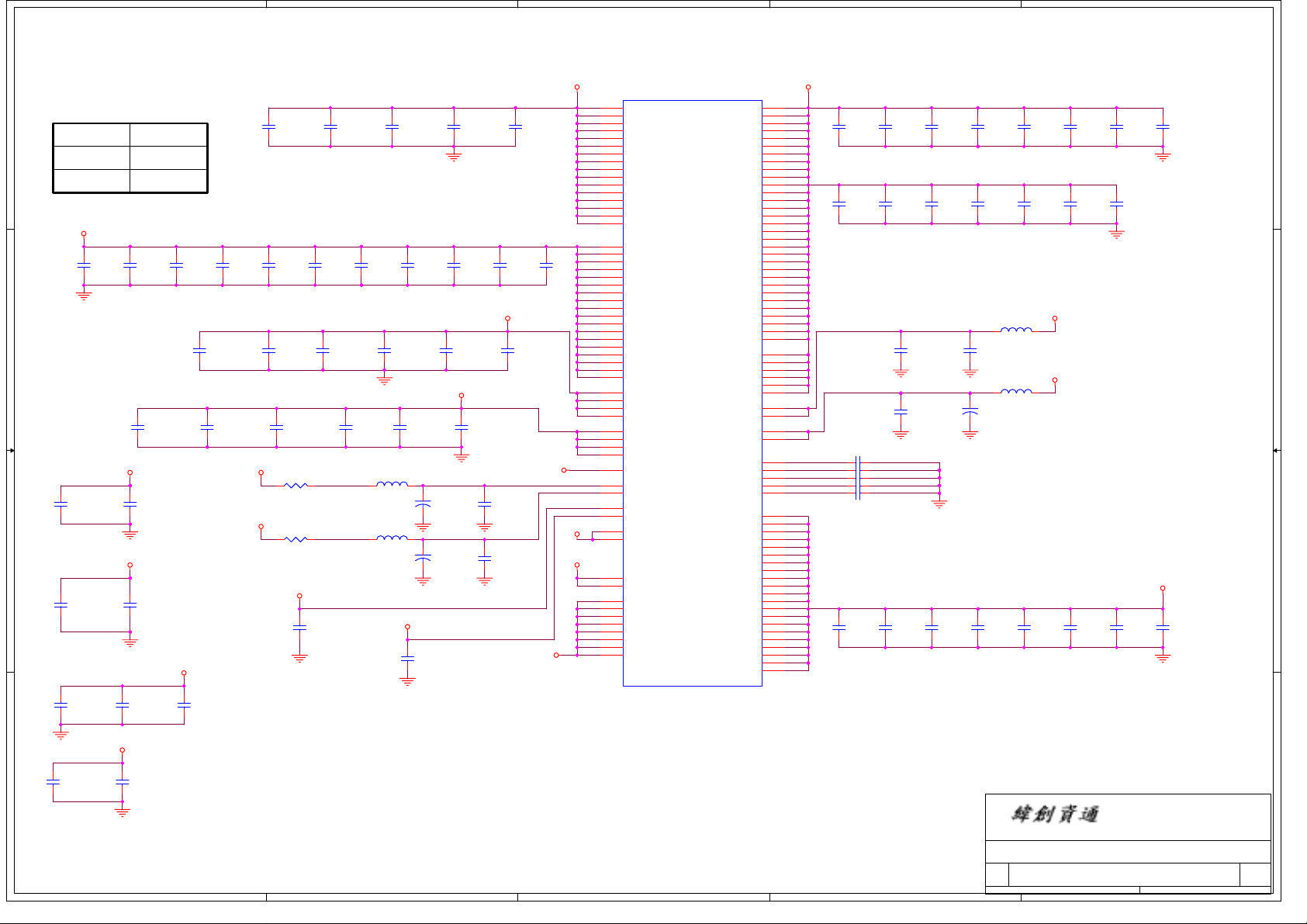

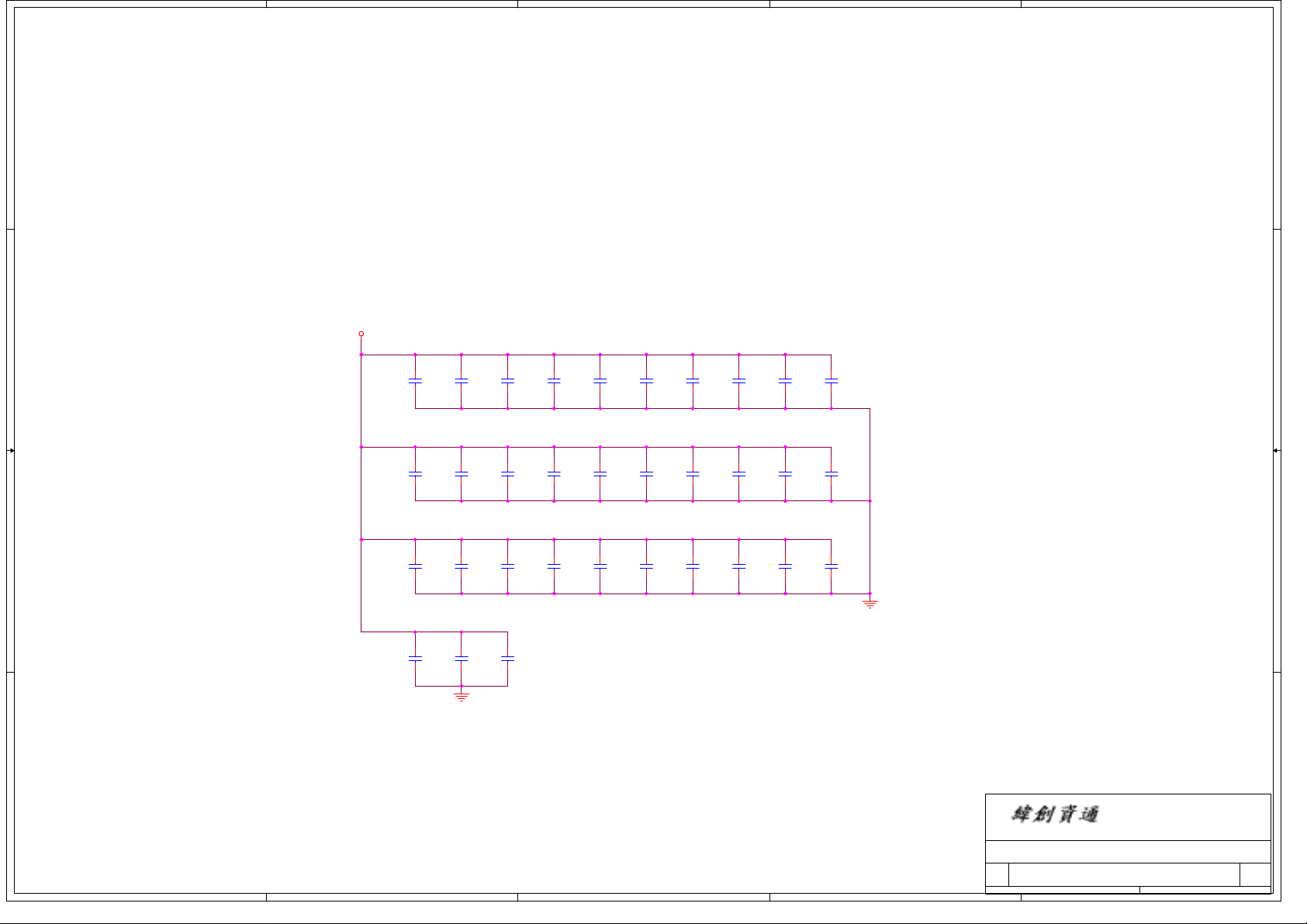

PCB Layer Stackup

L1:Component

L2:GND

L3:Signal 1

L4:VCC

L5:Signal 2

L6:Signal 3

L7:GND

L8:Component

System DC/DC

MAX1977

INPUTS

VINT16

53

OUTPUTS

VCC5M

VCC3M

Battery Charger/Selector

MAX1870

CV16 M-BAT-PWR

50

S-BAT-PWR

GMCH CORE

MAX1992

VINT16

55

VCCGMCHCORE

VCCCPUIO

CPU DC/DC

MAX1907

VINT16

54

VCCCPUCORE

VCCACPU/DDR_VREF

LP2996MR/MAX8873

VCC3M

57

DDR_VREFVCC2R5A

VCCACPU

1.5/2.5 DC/DC

MAX1845

VINT16

VCC1R5M

VCC2R5A

56

Line Out

Stereo Speaker x 2

UltraBay

HDD, Optical Drives

2nd Battery

USB x 3

Media Slice

MAX3243

RS232 Transceiver

COM Port

Parallel Port

CRTPS/2 x2Line In

RJ11

DC-IN

RJ45

Title

Size Document Number Rev

A3

46

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Block Diagram

S Note-1

166Wednesday, June 01, 2005

-2

A

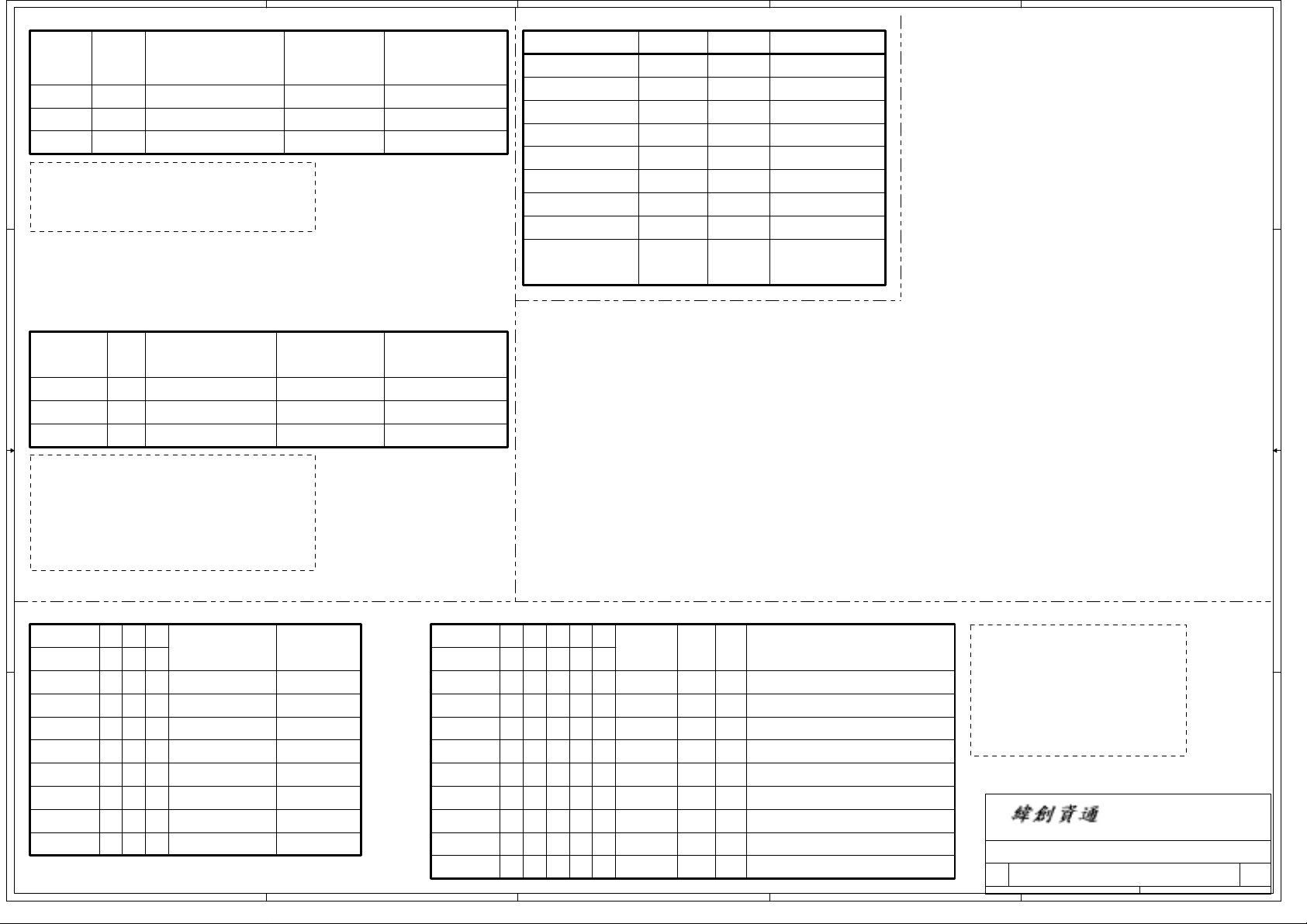

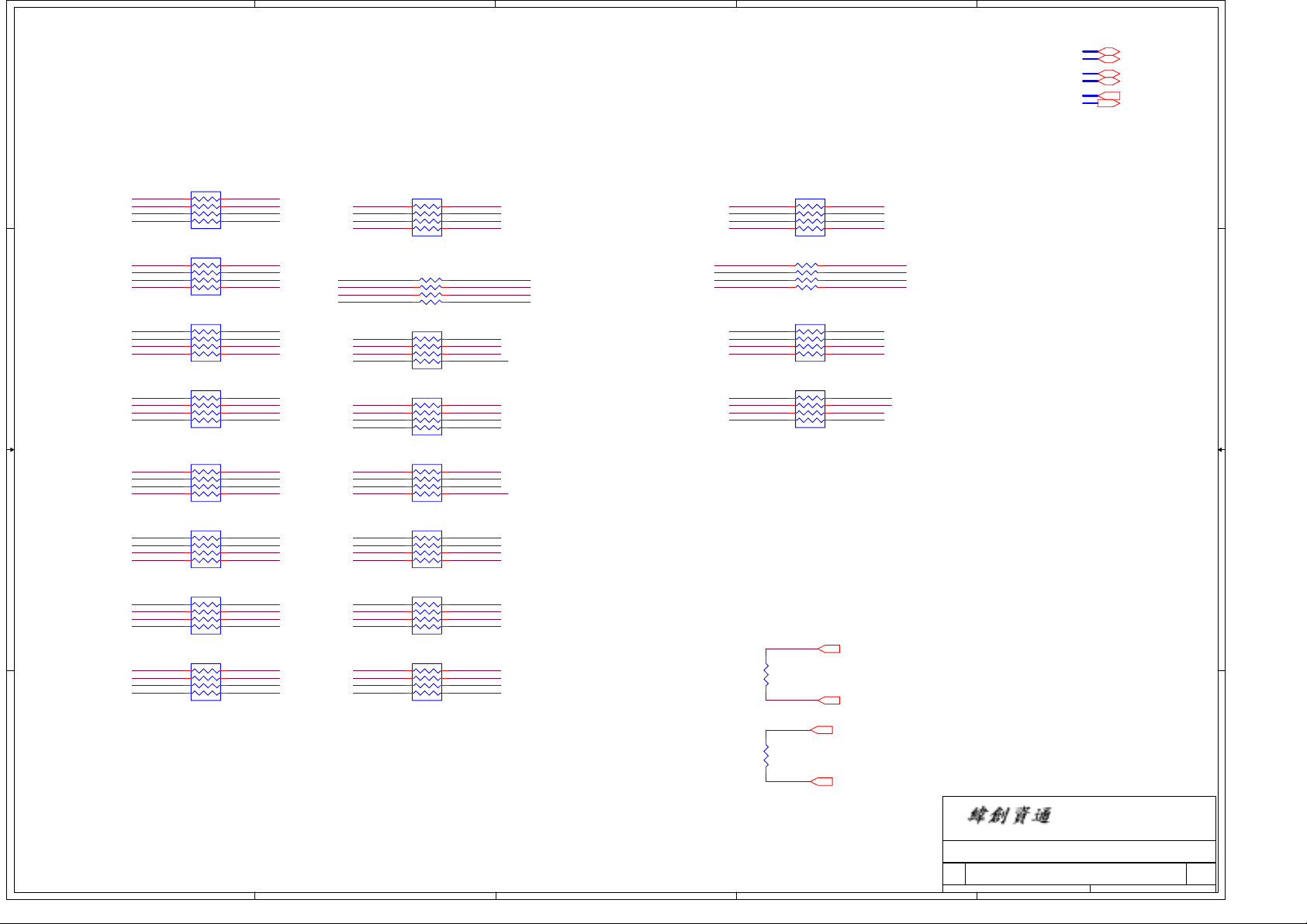

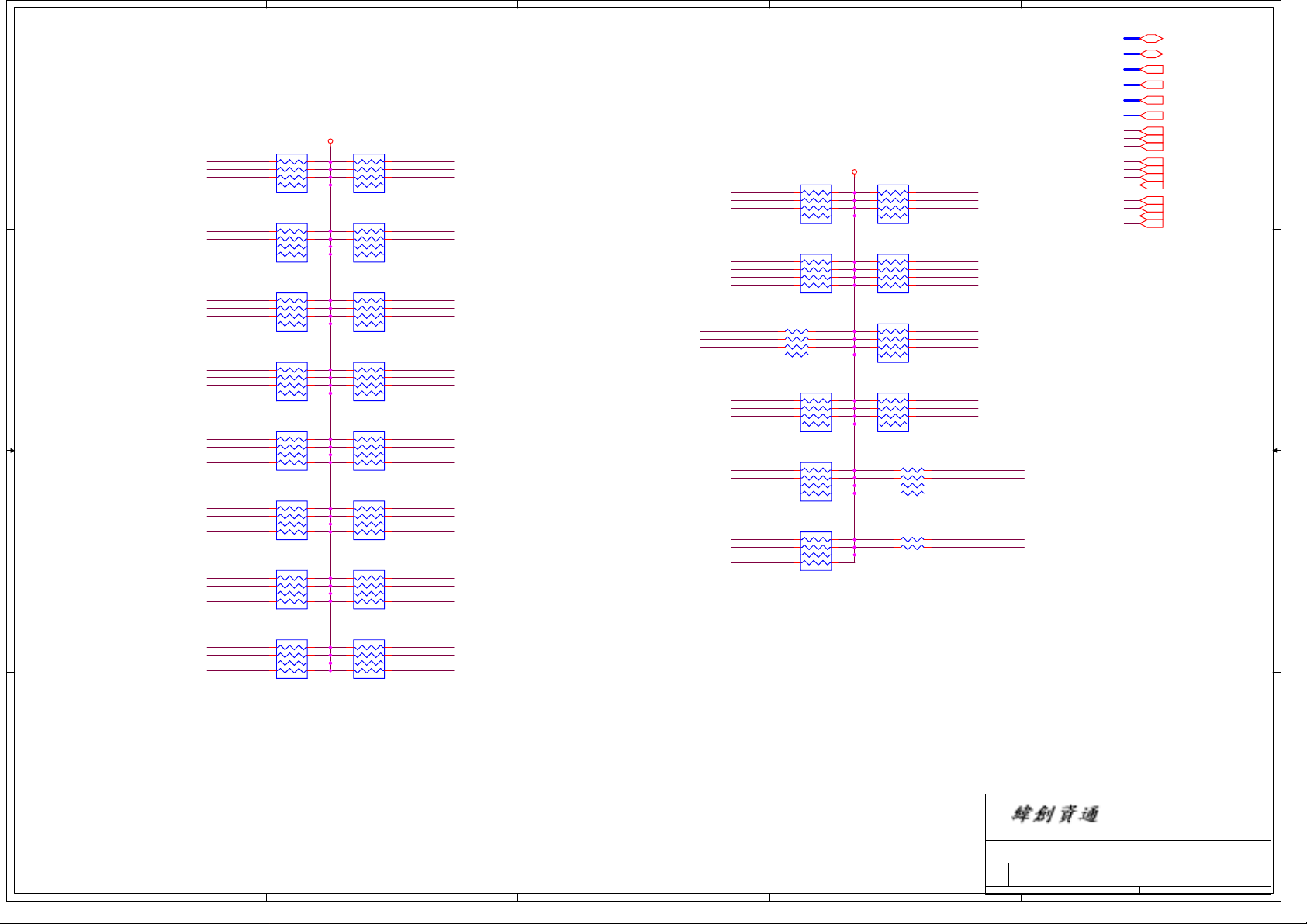

RESISTOR

Symbol name

Value

Tolerance

(J: 5%, F: 1%, D: 0.5%, B: 0.1 %)

10KR3

33D3R5

4 4

1KR3F

The naming rule is value + R + size + tolerance

For the value, it can be read by the number befor e R. (R means resistor)

For the tolerance, it can be read from the last letter.

For the rating, we don't show on the symbol name.

For the size, R2=>0402, R3=>0603, R5=>0805,....

10K Ohm

33.3 Ohm

1K Ohm

If no letter, it means J: 5%

F: 1%

Rating

0402=> 1/16W, 25V

0603 => 1/16W, 75V

0805 => 1/10W, 100V

1/16W, 75V

1/10W, 100V

1/16W, 75V

B

Size

2=>0402, 3=>0603, 5=>0805,

6=>1206, 0=>1210

0603

0805If no letter, it means J: 5%

0603

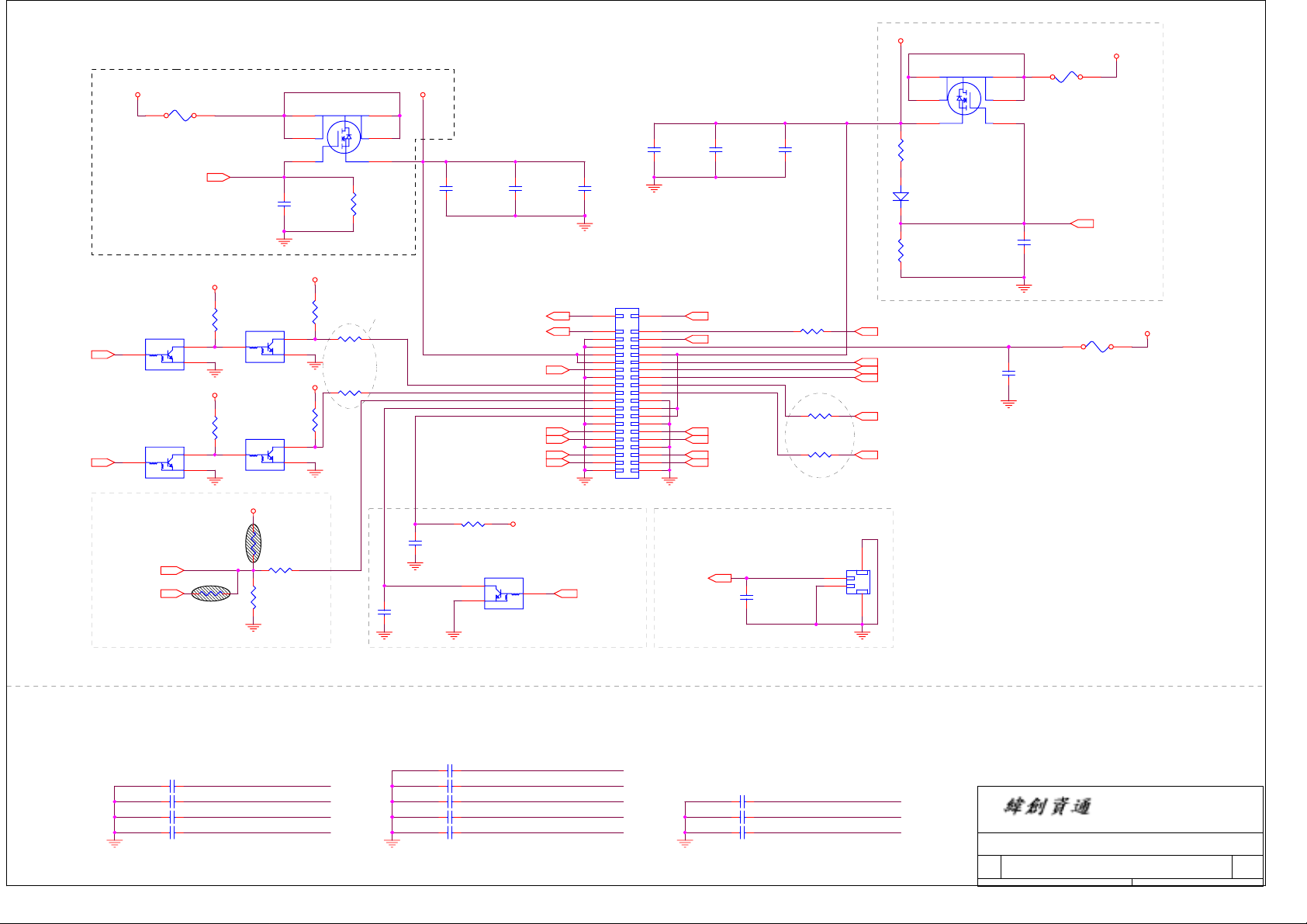

PCI TABLE

DEVICE

MINIPCI SLOT

AGP

LAN(82562EX)

LAN(82541EI)

USB UHCI

USB 2.0 EHCI

Hub-to-PCI

LPC Bridge/

IDE/AC97/

SMBus

C

AD24(Int.)

IDSEL

AD16

AD17

AD29

AD29

AD30

AD31

IRQ

F, G

SERIRQ

E

E

A, D, C

H

REQ# / GNT#

REQ# 2/ GNT#2AD18

REQ#0 / GNT#0CARDBUS R5C593

REQ#1 / GNT#1

D

E

CAPACITOR

3 3

Symbol name

SCD1U10V2MX-1

SC2D2U16V5ZY

Value

0.1uF

10uF

2.2uF

Tolerance

(M: +/-20, K: +/-10, Z: +80/-20)

M/X5R

M/X5RSC10U6D3V5MX

Z/Y5V

Rating

10V

6.3V

16V

Size

2=>0402, 3=>0603, 5=>0805,

6=>1206, 0=>1210

0402

0805

0805

The naming rule is

Capacitor type + value + ra ti ng + si z e + t ol er an c e + m a te ri al

SCD1U10V2MX-1

SC=> SMT Ceremic, TC=> POS cap or SP cap

D1U => 0.1uF

10V => the voltage rating is 1 0 V

2=> 0402, 3=>0603, 5=>0805

M=>tolerance M, K, Z

X=> X7R/X5R, Y=> Y5V

2 2

-1 => symbol version, nonsense to EE ch a racteristic

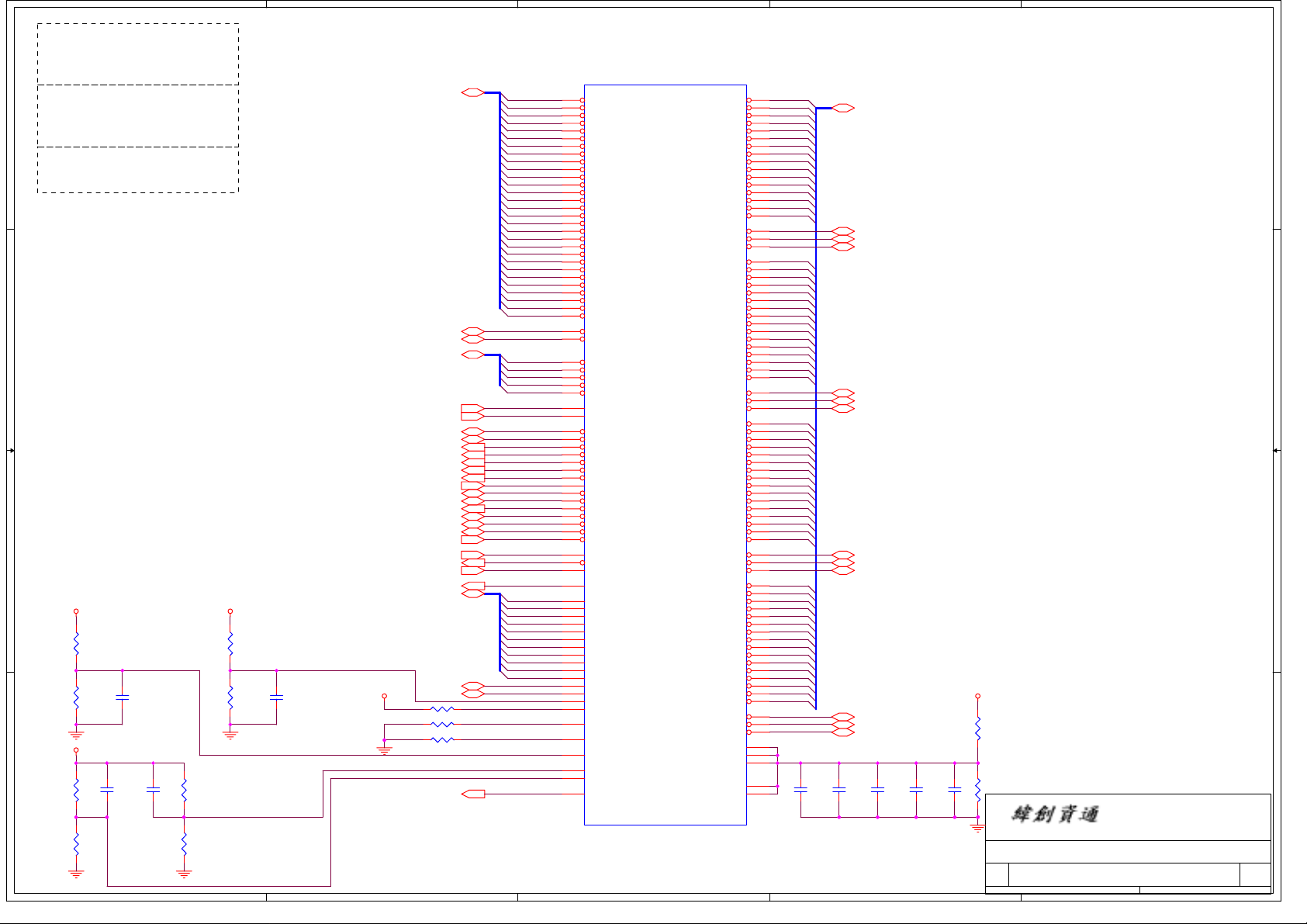

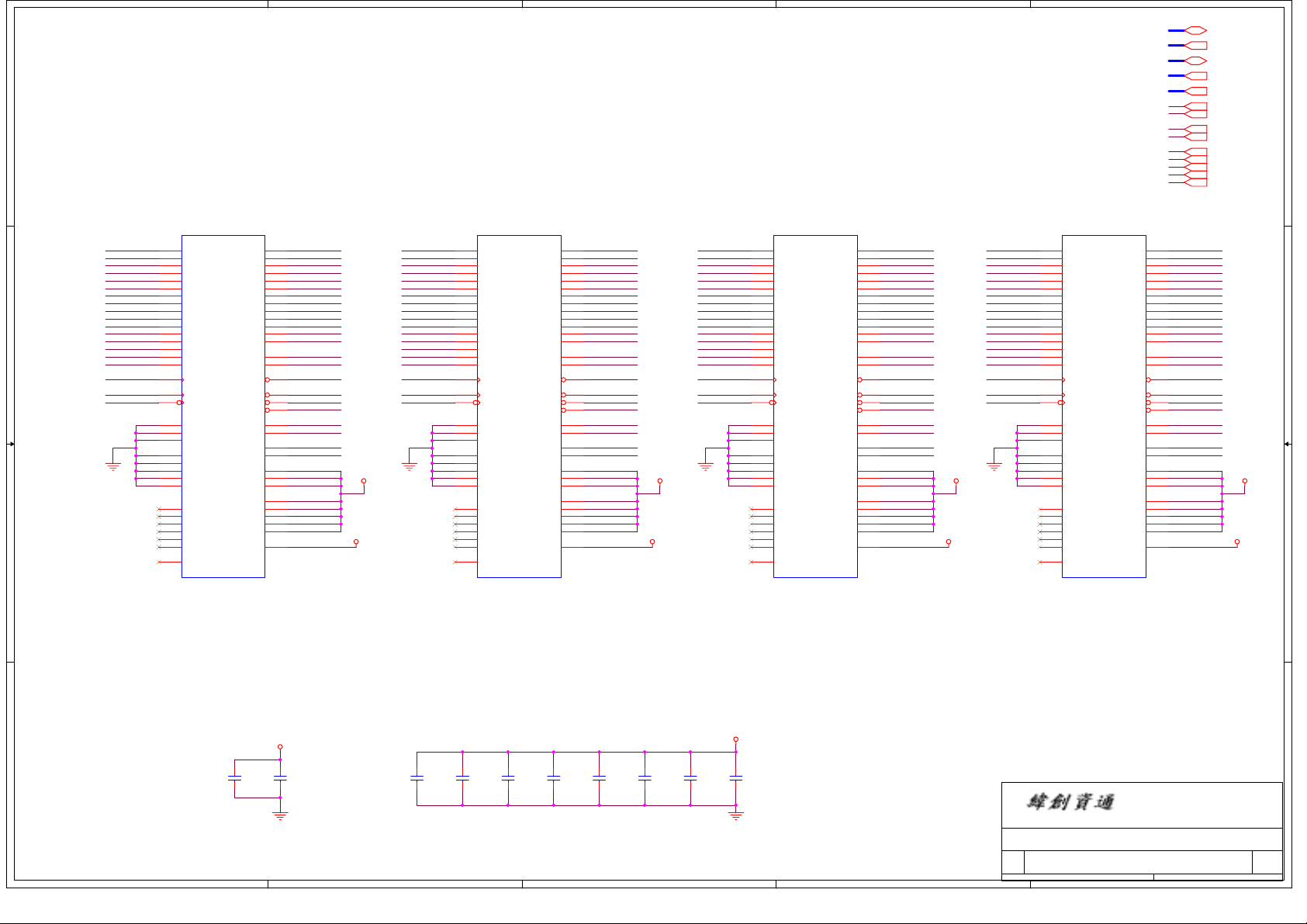

PLANAR_ID[2..0]

34

32ICH4-M GPIOn

33

PLANAR_IDn

1 1

2

0

0

0

0

1

1

1

1 03209-11

0

0

SDV-1, SVT- R 03209-SA, 03209-2

0

1

1

0

1

1

0

0

0

1

1

0

1

A

SDV-2 03209-SA

SDV-3 03209-SA

SIV

SIV-R

SIT

SIT-R

SVT

Snote-1 Planar ID Version

1

0

Planar PCB Version

03209-SB

03209-SC

03209-SD

03209-SE

MEM_BASE_ID[4..0]

ICH4-M GPIOn

BASE_MEM_IDn

B

39 38 37

00

0

01

1

100

10

11

1

210

34

1

000

1

0

0

0

011

0

100

36 35

1

1

0

1

1

0

1

Q'tyTotal Capacity

Density

0

256MB

1

256MB

0

256MB

1

256MB

1

256MB

0

256MB

1

512MB

1

512MB

0

512MB

256Mb

8

Infineon p/n HYB25D256160CT-6 (Rev D11 / 0.11um)

256Mb

8

Micron p/n MT46V16M16TG-6T C (Rev T16 / 0.13um)

256Mb

8

Samsung p/n K4H561638D-TCB3 (Rev D / 0.13um)

512Mb

4

Hynix p/n HY5DU121622AT-J (Rev PC / 0.13um)

512Mb

4

Micron p/n MT46V32M16TG-6T C (Tev T27 / 0.11um)

512Mb

4

Samsung p/n K4H511638B-TCB3 (Rev B / 0.10um)

512Mb

8

Hynix p/n HY5DU121622AT-J (Rev PC / 0.13um)

512Mb

8

Micron p/n MT46V32M16TG-6T C (Tev T27 / 0.11um)

512Mb

8

Samsung p/n K4H511638B-TCB3 (Rev B / 0.10um)

C

Chip P/N

D

MEM_BASE_ID[4..0]

ICH4 GPIO bit 39 : Memory technology bit

1 : 512Mbit technology

0 : 256Mbit technology

ICH4 GPIO bit 38 : population numbers(bank numbers)

1 : total 8pcs

0 : total 4pcs

ICH4 GPIO bit 37-35 : vendor name

0 - 1 - 1 : Hynix

0 - 1 - 0 : Samsung

0 - 0 - 1 : Micron

0 - 0 - 0 : Infiineon

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Size Document Number Rev

A3

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

Reference

S Note-1

266Wednesday, June 01, 2005

E

of

-2

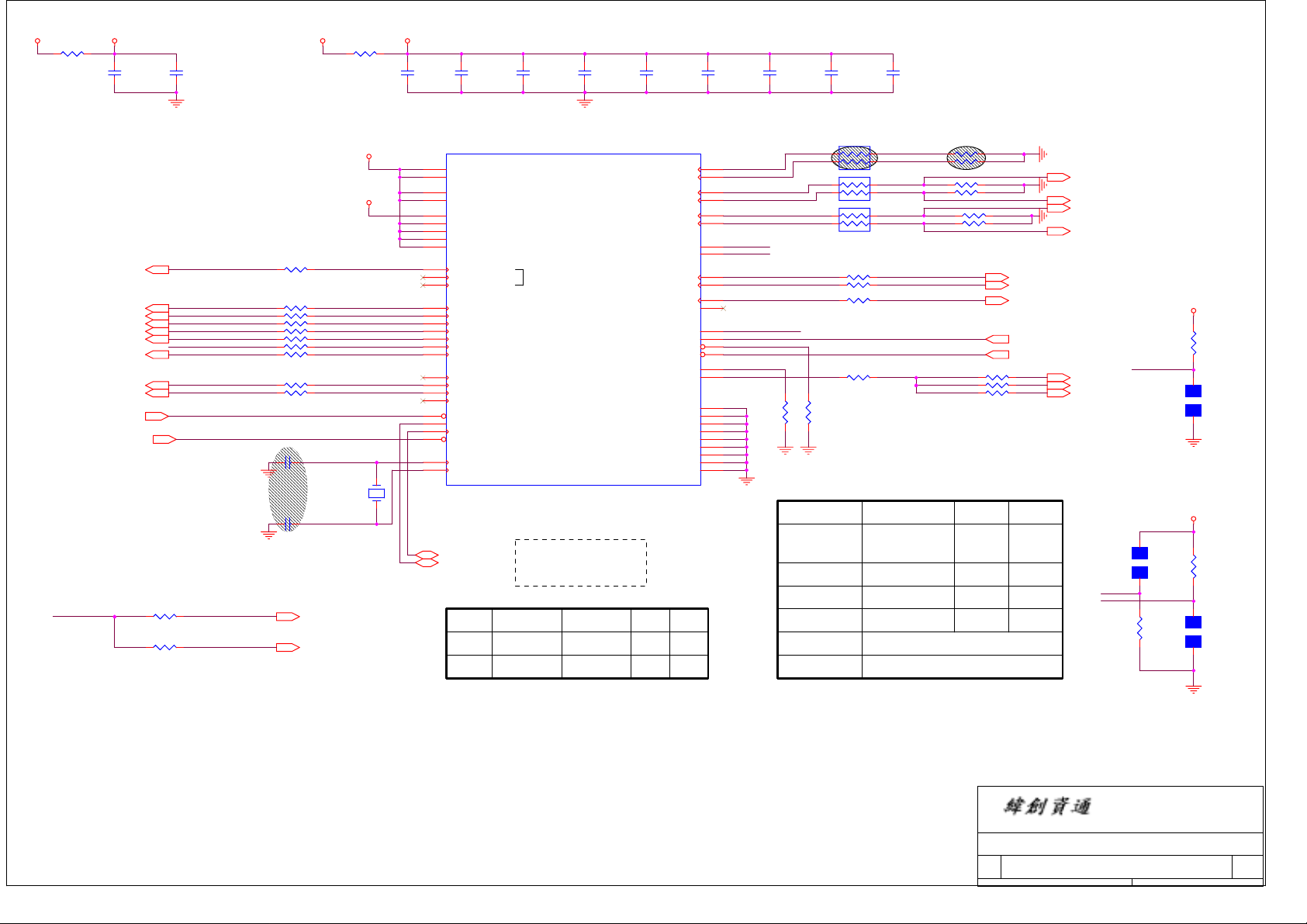

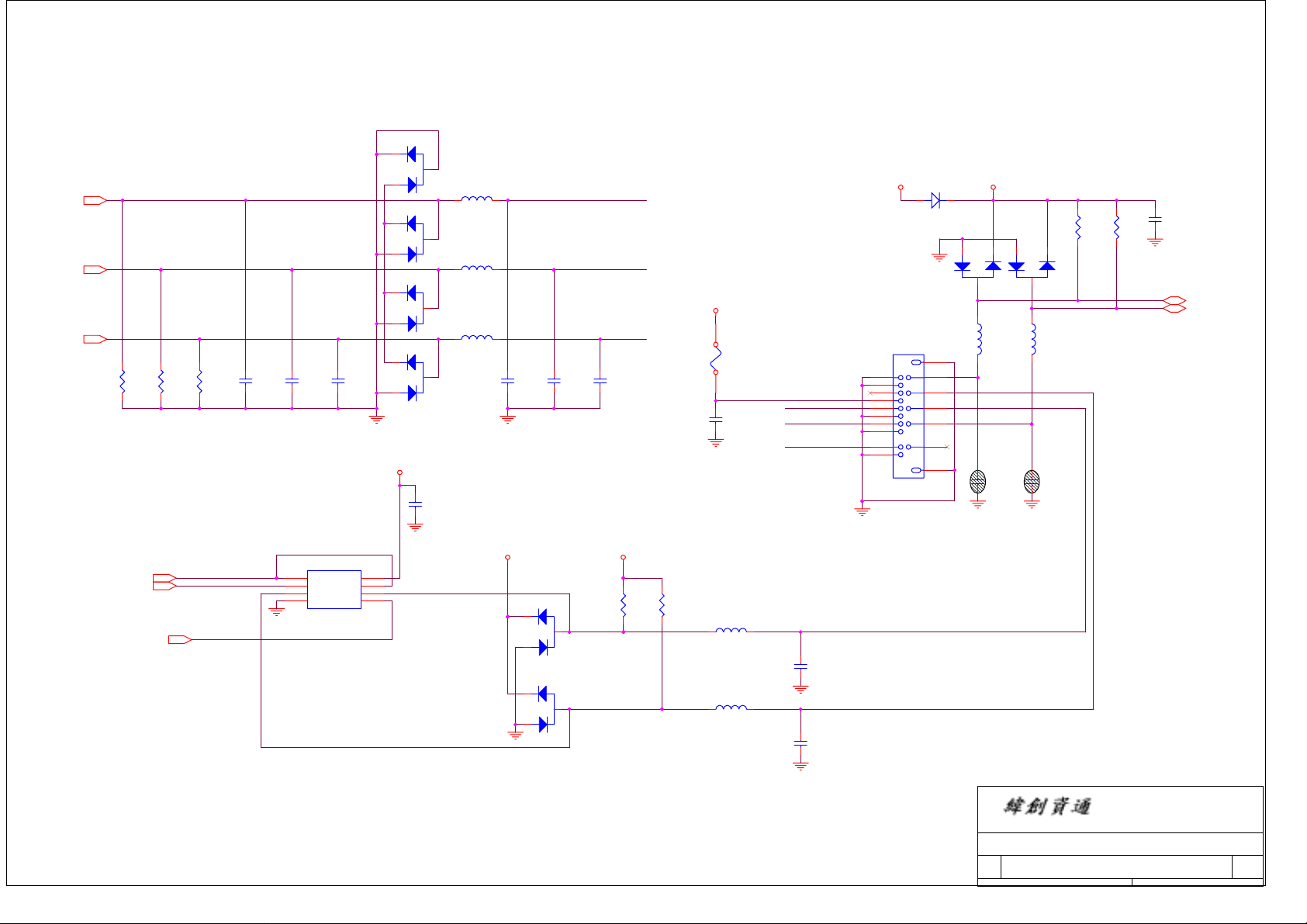

VCC3B VCC3B

R173

1 2

0R3-U

12

BC4

SC10U25V6MX

12

BC7

SCD01U25V2KX

PLACE NEAR EACH PIN PLACE NEAR EACH PIN

R232 33R2

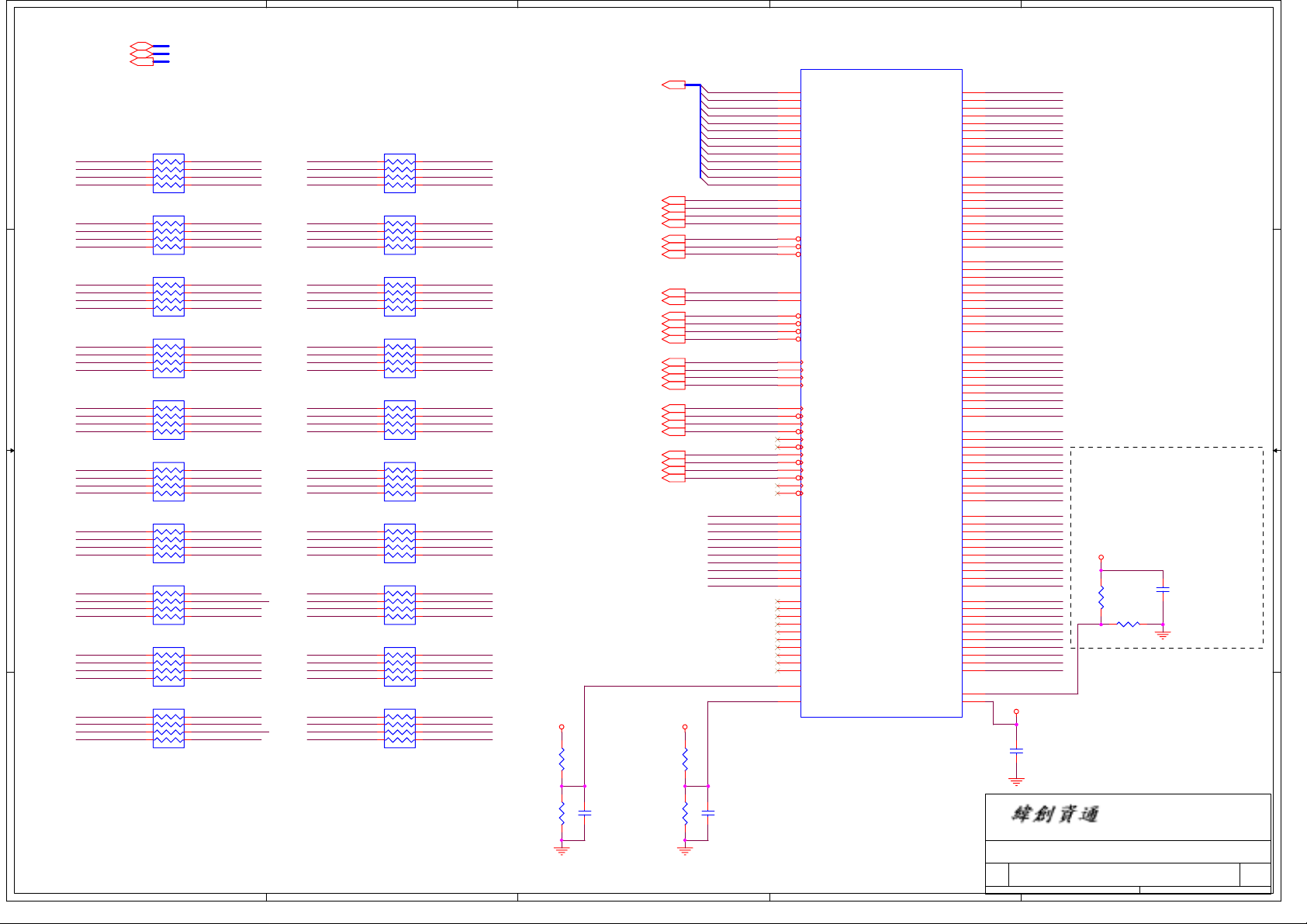

PCICLK_FR_ICH4M_33M20

1 2

1 2

PCICLK_CB_33M

PCICLK_MPCI_33M

PCICLK_GBE_33M

LPCCLK_FWH_33M

LPCCLK_SIO_33M

LPCCLK_33M

LPCCLK_CRYPT_33M

AGPCLK_MCH_66M

HLCLK_ICH4M_66M

KDS

XTAL 14.31818MHz

20P30PPM

LPCCLK_H8_33M

PCICLK_CB_33M27

PCICLK_MPCI_33M34

PCICLK_GBE_33M31

LPCCLK_FWH_33M40

LPCCLK_SIO_33M45

LPCCLK_CRYPT_33M44

AGPCLK_MCH_66M9

HLCLK_ICH4M_66M20

PM_SLP_S1#21,41

CLK_ENABLE#54

LPCCLK_33M LPCCLK_GA_33M

R592 10R2

R591 10R2

1 2

R226 33R2

1 2

R224 27R2J

1 2

R221 33R2

1 2

R219 22R2

1 2

R212 33R2

1 2

R208 0R2-0

1 2

R203 33R2

1 2

R197 33R2

1 2

R190 33R2

1 2

BC23

CK-408_GEN_X1

DY-SC10P

XTAL-14D318M-2

BC22

CK-408_GEN_X2

DY-SC10P

No stuff:

caps are

internal to

CK-TITAN.

LPCCLK_GA_33M 43

LPCCLK_H8_33M 41

3D3V_CLKGEN_S03D3V_APWR_S0

R172

1 2

0R3-U

3D3V_CLKGEN_S0

3D3V_APWR_S0

CLKPCIF_ICH_R

PCICLK_CB_33M_R

PCICLK_MPCI_33M_R

PCICLK_GBE_33M_R

LPCCLK_FWH_33M_R

LPCCLK_SIO_33M_R

LPCCLK_33M_R

LPCCLK_CRYPT_33M_R

AGPCLK_MCH_66M_R

HLCLK_ICH4M_66M_R

X4

1 2

BC3

SC10U25V6MX

U29

8

VDDPCI

14

VDDPCI

50

VDDCPU

46

VDDCPU

26

VDDA

37

VDD48

32

VDD3V66

19

VDD3V66

1

VDDREF

5

PCICLK_F0

6

PCICLK_F1

7

ASEL/PCICLK_F2

10

PCICLK0

11

E_PCICLK1/PCICLK1

12

PCICLK2

13

E_PCICLK3/PCICLK3

16

PCICLK4

17

PCICLK5

18

PCICLK6

21

3V66_2

22

3V66_3

23

3V66_4

24

3V66_5

25

PD#

29

SDATA

30

SCLK

28

VTT_PWRGD#

2

X1

3

X2

ICS950810PGT

12

BC18

SCD01U25V2KX

*

12

BC43

SCD01U25V2KX

CK-408

V1.1

Free running

*

**

**

12

BC13

SCD01U25V2KX

**

12

* These inputs have 120K internal pull-up resistor to VDD

** Internal pull-down resistors to ground

SMB_CLK_3B 14,48

SMB_DATA_3B 14,48

Vendor

ICS

CYPRESS

SNOTE-SA use the symbol of

ICS950813YGT to replace of

ICS950810PGT

Vendor's P/N

ICS950810PGT

CY28346-2ZCT

71.95810.C0W

71.28346.A0W

P/N

12

BC12

SCD01U25V2KX

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

CPUCLKT2

CPUCLKC2

FS1

FS0

**

48MHZ_USB/FS2

48MHZ_DOT

3V66_1/VCH_CLK/FS3

3V66_0/FS4

**

*

MULTSEL

*

CPU_STOP#

*

PWRSAVE#

*

PCI_STOP#

IREF

REF

GND

GND

GND

GND

GND

GND

GND

GND

GND

R179 R224

22R2 27R2J

15R2J

22R2

12

BC15

SCD01U25V2KX

CLK_ITP_R

52

CLK_ITP#_R

51

CLK_CPU_R

49

CLK_CPU#_R

48

CLK_MCH_R

45

CLK_MCH#_R

44

CKG_FS1

55

CKG_FS0

54

USBCLK_48M_R

39

DREFCLK_48M_R

38

DREFSSCLK_48M_R

35

33

CK-408_MULT0

43

53

40

34

CLKGEN_IREF

42

CLK14

56

4

9

15

20

27

47

41

36

31

12

RN40 DY-SRN33-2-U2

1

2 3

RN39 SRN33-2-U2

1

2 3

RN38 SRN33-2-U2

1

2 3

R593 33R2

R196 24R2J

R179 22R2

R235 0R2-0

12

12

R198

10KR2

BC16

SCD01U25V2KX

NO ASM

4

4

4

1 2

1 2

1 2

1 2

12

BC42

SCD01U25V2KX

CLK_ITP

CLK_ITP#

R202

475R3F

12

BC14

SCD01U25V2KX

Frequency S e t t i n g CPU PCIAGP

FS1/0 = 00

166.66MHz(ICS)

66.66MHz(CYPRESS)

FS1/0 = 01

FS1/0 = 10

FS1/0 = 11

Mult0 = 0

Mult0 = 1

100.00MHz

200.00MHz

133.33MHz

Rr=221, Iref=5mA =>Vswing=1.0 V @50ohm

Rr=475, Iref=2.32mA =>Vs w i ng= 0 .7 V@ 50ohm

NO ASM

R598 DY-49D9R2F

1 2

R597 DY-49D9R2F

1 2

R596 49D9R2F

1 2

R595 49D9R2F

1 2

R594 49D9R2F

1 2

R590 49D9R2F

1 2

CLK14_R

R248 33R2

1 2

R249 33R2

1 2

R247 33R2

1 2

66.67MHz

66.67MHz

66.67MHz

66.67MHz

USBCLK_48M 20

DREFCLK_48M 9

DREFSSCLK_48M 9

PM_CPUSTP# 21,54

PM_PCISTP# 21

33.33MHz

33.33MHz

33.33MHz

33.33MHz

CPUCLK_CPU_100M 5

CPUCLK_CPU_100M# 5

CPUCLK_MCH_100M 7

CPUCLK_MCH_100M# 7

VCC3B

12

R209

VCC3B

10KR2

12

R210

DUMMY-R2

12

R241

10KR2

12

R240

DUMMY-R2

ICH4M_14M 21

SIO_14M 45

CODEC_14M 36

CK-408_MULT0

CPU & MEMORY Freq. Selection

12

R242

DUMMY-R2

CKG_FS1

CKG_FS0

12

R243

10KR2

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Size Document Number Rev

A3

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

Clock GEN.

S Note-1

366Wednesday, June 01, 2005

of

-2

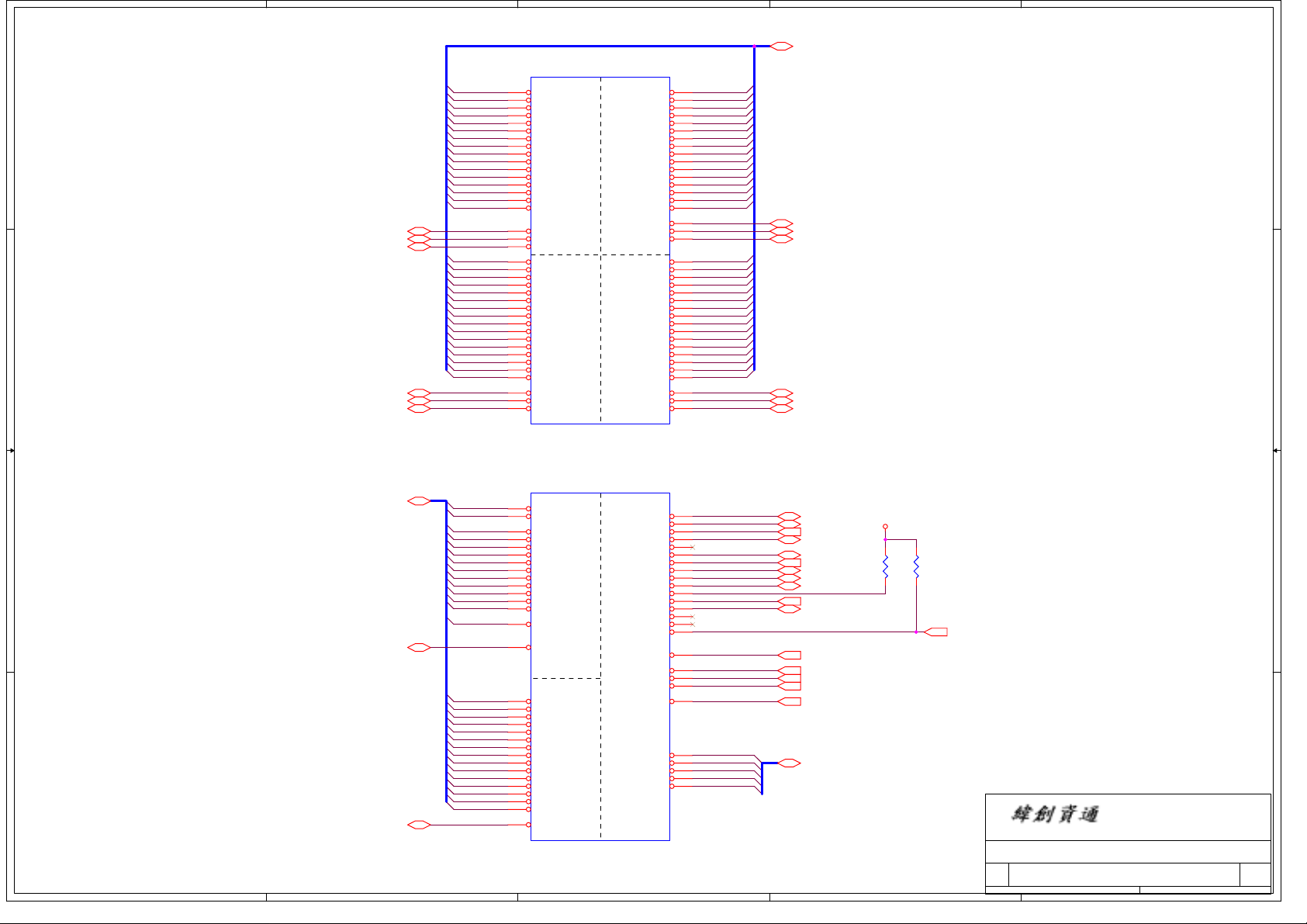

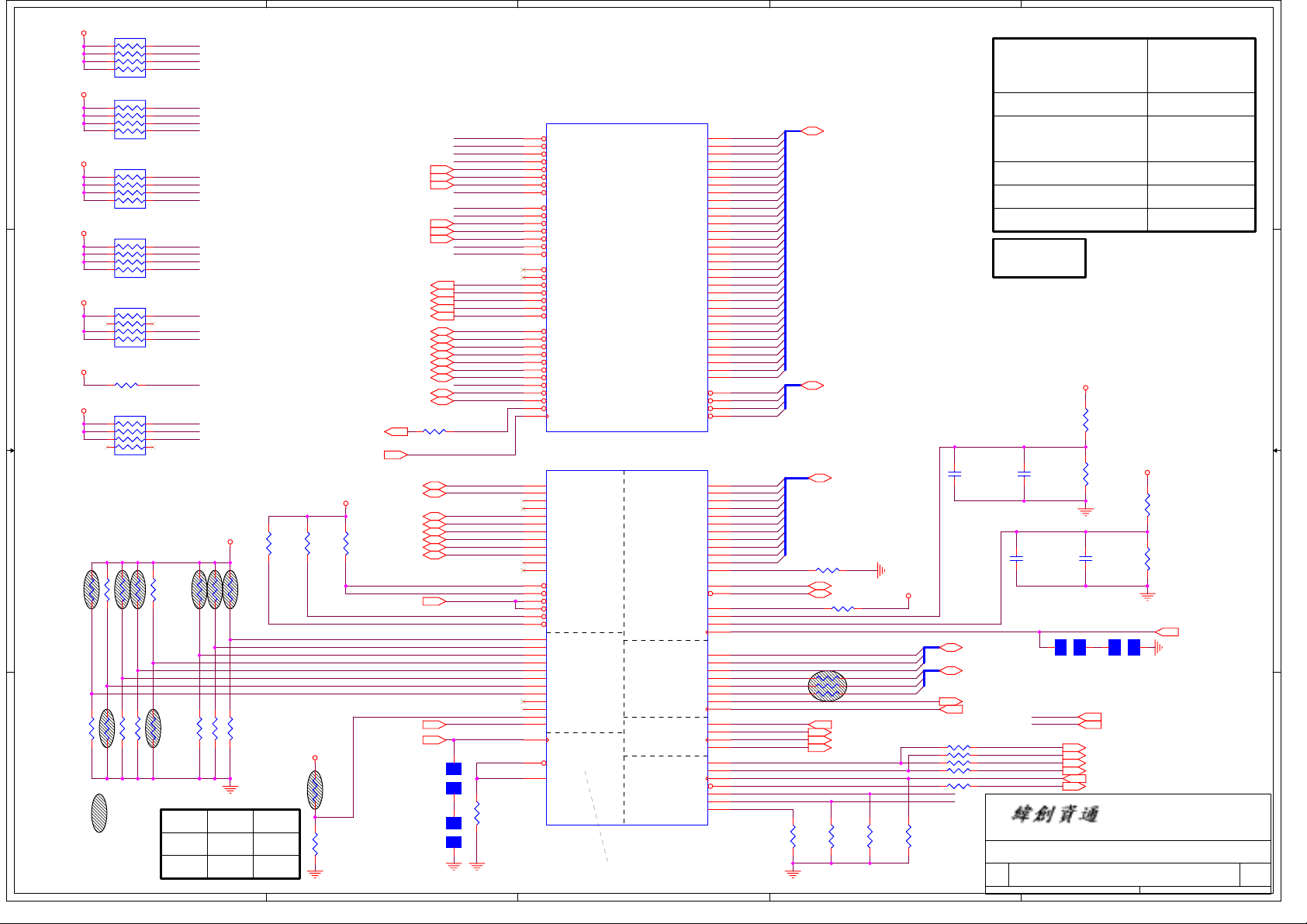

A

B

C

GTL_D#[63..0] 7

D

E

GTL_D#15

GTL_D#14

GTL_D#13

GTL_D#12

4 4

GTL_DINV#07

GTL_DSTBN#07

GTL_DSTBP#07

3 3

GTL_DINV#17

GTL_DSTBN#17

GTL_DSTBP#17

GTL_A#[31..3]7

2 2

GTL_ADSTB#07

1 1

GTL_ADSTB#17

A

B

GTL_D#11

GTL_D#9

GTL_D#8

GTL_D#7

GTL_D#6

GTL_D#5

GTL_D#4

GTL_D#3

GTL_D#2

GTL_D#1

GTL_D#0

GTL_DINV#0

GTL_DSTBN#0

GTL_DSTBP#0

GTL_D#31

GTL_D#30

GTL_D#29

GTL_D#28

GTL_D#27

GTL_D#26

GTL_D#25

GTL_D#24

GTL_D#23

GTL_D#22

GTL_D#21

GTL_D#20

GTL_D#19

GTL_D#18

GTL_D#17

GTL_D#16

GTL_DINV#1 GTL_DINV#3

GTL_DSTBP#1

GTL_A#16

GTL_A#15

GTL_A#14

GTL_A#13

GTL_A#12

GTL_A#11

GTL_A#10

GTL_A#9

GTL_A#8

GTL_A#7

GTL_A#6

GTL_A#5

GTL_A#4

GTL_A#3

GTL_ADSTB#0

GTL_A#30

GTL_A#29

GTL_A#28

GTL_A#27

GTL_A#26

GTL_A#25

GTL_A#24

GTL_A#23

GTL_A#22

GTL_A#21

GTL_A#20

GTL_A#19

GTL_A#18

GTL_A#17

GTL_ADSTB#1

U67C

C25

D15#

E23

D14#

B23

D13#

C26

D12#

E24

D11#

D24

D10#

B24

D9#

C20

D8#

B20

D7#

A21

D6#

B26

D5#

A24

D4#

B21

D3#

A22

D2#

A25

D1#

A19

D0#

D25

DINV0#

C23

DSTBN0#

C22

DSTBP0#

K25

D31#

N25

D30#

H26

D29#

M25

D28#

N24

D27#

L26

D26#

J25

D25#

M23

D24#

J23

D23#

G24

D22#

F25

D21#

H24

D20#

M26

D19#

L23

D18#

G25

D17#

H23

D16#

J26

DINV1#

K24

DSTBN1#

L24

DSTBP1#

BANIAS-1D6G-1U

U67B

AA2

A16#

Y3

A15#

AA3

A14#

U1

A13#

Y1

A12#

Y4

A11#

W2

A10#

T4

A9#

W1

A8#

V2

A7#

R3

A6#

V3

A5#

U4

A4#

P4

A3#

U3

ADSTB0#

AF1

A31#

AE1

A30#

AF3

A29#

AD6

A28#

AE2

A27#

AD5

A26#

AC6

A25#

AB4

A24#

AD2

A23#

AE4

A22#

AD3

A21#

AC3

A20#

AC7

A19#

AC4

A18#

AF4

A17#

AE5

ADSTB1#

BANIAS-1D6G-1U

DATA GROUP 0

DATA GROUP 1

ADDR GROUP 0 ADDR GROUP 1

DATA GROUP 2

DATA GROUP 3

CONTROLREQ.

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

DINV2#

DSTBN2#

DSTBP2#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

D52#

D51#

D50#

D49#

D48#

DINV3#

DSTBN3#

DSTBP3#

ADS#

BNR#

BPRI#

BR0#

DBR#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

IERR#

INIT#

LOCK#

PRDY#

PREQ#

RESET#

TRDY#

RS2#

RS1#

RS0#

DPWR#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

C

Y25

AA26

Y23

V26

U25

V24

U26

AA23

R23

R26

R24

V23

U23

T25

AA24

Y26

T24

W25

W24

AF26

AF22

AF25

AD21

AE21

AF20

AD24

AF23

AE22

AD23

AC25

AC22

AC20

AB24

AC23

AB25

AD20

AE24

AE25

N2

L1

J3

N4

A7

M2

L4

H2

K3

K4

A4

B5

J2

A10

B10

B11

M3

L2

K1

H1

C19

T1

P1

T2

P3

R2

GTL_D#47

GTL_D#46

GTL_D#45

GTL_D#44

GTL_D#43

GTL_D#42GTL_D#10

GTL_D#41

GTL_D#40

GTL_D#39

GTL_D#38

GTL_D#37

GTL_D#36

GTL_D#35

GTL_D#34

GTL_D#33

GTL_D#32

GTL_DINV#2

GTL_DSTBN#2

GTL_DSTBP#2

GTL_D#63

GTL_D#62

GTL_D#61

GTL_D#60

GTL_D#59

GTL_D#58

GTL_D#57

GTL_D#56

GTL_D#55

GTL_D#54

GTL_D#53

GTL_D#52

GTL_D#51

GTL_D#50

GTL_D#49

GTL_D#48

GTL_DSTBN#3GTL_DSTBN#1

GTL_DSTBP#3

GTL_IERR#

GTL_TRDY#

GTL_RS#2

GTL_RS#1

GTL_RS#0

GTL_DPWR#GTL_A#31

GTL_REQ#4

GTL_REQ#3

GTL_REQ#2

GTL_REQ#1

GTL_REQ#0

GTL_DINV#2 7

GTL_DSTBN#2 7

GTL_DSTBP#2 7

GTL_DINV#3 7

GTL_DSTBN#3 7

GTL_DSTBP#3 7

GTL_ADS# 7

GTL_BNR# 7

GTL_BPRI# 7

GTL_BR0# 7

GTL_DBSY# 7

GTL_DEFER# 7

GTL_DRDY# 7

GTL_HIT# 7

GTL_HITM# 7

CC_INIT# 21

GTL_LOCK# 7

GTL_TRDY# 7

GTL_RS#2 7

GTL_RS#1 7

GTL_RS#0 7

GTL_DPWR# 7

GTL_REQ#[4..0] 7

Place within 1.5" from CPU

VCCCPUIO

12

12

R632

R630

56R2F

54D9R2F

GTL_CPURST# 7

D

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Size Document Number Rev

A3

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

BANIAS CPU(1/3)

S Note-1

466Wednesday, June 01, 2005

E

of

-2

A

B

C

D

E

VCC3SW

OUT

5

BPM3#

BPM2#

BPM1#

BPM0#

COMP3

COMP2

COMP1

COMP0

DPSLP#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

PROCHOT#

PWRGOOD

TEST1

TEST2

THERMDA

THERMDC

THERMTRIP#

TMS

TRST#

C

GND

1

3

Q54

R2

DTA114EE

R1

IN

2

C9

COMP0/2: Z0=27.4 OHM TRACE

A9

B8

COMP1/3: Z0=55.0 OHM TRACE

C8

COMP3

AB1

COMP2

AB2

COMP1

P26

COMP0

P25

B7

AC1

G1

E26

H_GTLREF_0

AD26

H_PROCHOT#

B17

E4

C5

F23

B18

A18

C17

H_TMS

C11

H_TRST#

B13

TEST3

PSI#

VCC3SW

4

U24

V+

1

HYST

OS#

3

VTEMP

GND

LM26CIM5-XPA-U

2

H_CLK

ITP1

MISC

TERM

VID

4 4

12

C143

SCD1U10V2KX

VCCACPU

BANIAS

DOTHAN

For CPU VCCA[0:3] PLL

3 3

2 2

1 1

place one 0.01u & 10u

for each VCCA pin

1.80V

1.50V

VCCACPU

Pin AC26 Pin N1

12

C587

SCD01U25V2KX

12

C598

SC10U25V6MX

VCCACPU VCCACPU

Pin B1 Pin F26

12

C221

SCD01U25V2KX

12

C619

SC10U25V6MX

VCCCPUIO

12

A

R257

150R2F

TP10

TPAD30

TP9

TPAD30

12

C624

SC10U25V6MX

12

C605

SC10U25V6MX

R258 DY-1KR2

NO_ASM

VCCACPU

12

C189

SCD01U25V2KX

12

C604

SCD01U25V2KX

NO ASM

1 2

R633 27D4R2F

1 2

R544

DY-54D9R2F

12

R543

DY-54D9R2F

12

CPUCLK_CPU_100M3

CPUCLK_CPU_100M#3

CC_A20M#21

CC_FERR#21

CC_IGNNE#21

CC_INTR21

CC_NMI21

CC_SMI#21

CC_STPCLK#21

VCCACPU

TP11

TPAD30

CC_CPUSLP#21

CPU_VCCSENSE

CPU_VSSSENSE

H_VID[5..0]54

Route these two signals:

1.Equal length.(Max. length < 100mils)

2.Width/Spacing=1/3.

3.50mil away from other signals.

B

TEST3

PSI#

H_TCK

H_TDI

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

AC26

B15

B14

A16

A15

F26

AF7

C14

C16

A13

C12

A12

AE7

AF6

C2

D3

A3

D1

D4

B4

C6

N1

B1

B2

C3

E1

A6

H4

G4

G3

F3

F2

E2

U67D

BCLK0

BCLK1

ITP_CLK0

ITP_CLK1

A20M#

FERR#

IGNNE#

LINT0

LINT1

SMI#

STPCLK#

VCCA3

VCCA2

VCCA1

VCCA0

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

SLP#

TCK

TDI

TDO

VCCSENSE

VSSSENSE

VID5

VID4

VID3

VID2

VID1

VID0

BANIAS-1D6G-1U

SHUTDOWN2 49,51

SHUTDOWN2# 43,54

TP2

TPAD34

TEST PAD FOR BOARD MFG TEST

R159 54D9R2F

R139 27D4R2F

R585 54D9R2F

R582 27D4R2F

R260 DY-1KR2

TEST1

R233 DY-1KR2

TEST2

12

R631

680R2

12

1 2

1 2

1 2

CC_DPSLP# 21

NO ASM

1 2

1 2

THERMDA 47

12

C769

SC220P50V2JN

THERMDC 47

CC_THRMTRIP_S# 21

TP1

TPAD30

TEST PAD FOR BOARD MFG TEST

VCCCPUIO

GTLREF voltage

12

C568

SC1U10V3ZY

12

12

R577

1KR2F

R562

2KR2F

Close to the ball AD26, < 0.5"

VCCCPUIO

12

R256

39D2R2F

Title

Size Document Number Rev

A3

D

Date: Sheet

VCCCPUIO

12

12

R259

R634

330R2

56R2J

Place within 1.5" from CPU

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

BANIAS CPU(2/3)

S Note-1

E

CC_CPUPWRGD 21

566Wednesday, June 01, 2005

of

-2

A

A2A5A8

A11

A14

A17

A20

A23

A26B3B6B9B12

B16

B19

B22

B25C1C4

C7

C10

C13

C15

C18

C21C24

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

4 4

VSSVSS

VSS

VSS

VSS

VSS

VSS

VSS

AD25

VSS

AE3

VSS

AE6

VSS

AE8

VSS

AE10

VSS

AE12

VSS

AE14

VSS

AE16

VSS

AE18

VSS

AE20

VSS

AE23

VSS

AE26

VSS

AF2

VSS

AF5

VSS

AF9

VSS

AF11

VSS

AF13

VSS

AF15

VSS

B

AF17

VSS

AF19

VSS

AF21

AF24D6D8

VSS

VSS

VCC

VCC

D18

VCC

D20

D22E5E7E9E17

VCC

VCC

VCC

VCC

VCC

VCC

E19

VCC

E21F6F8

VCC

VCC

VCC

F18

F20

F22G5G21H6H22J5J21

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

K22U5V6

VCC

VCC

VCC

C

V22W5W21Y6Y22

VCC

VCC

VCC

VCC

VCC

VCC

AA5

VCC

AA7

VCC

AA9

VCC

AA11

VCC

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC:Core voltage for processor

AB16

VCC

AB18

VCC

AB20

VCC

AB22

VCC

AC9

VCC

AC11

VCC

AC13

VCC

AC15

VCC

AC17

VCC

AC19

VCC

AD8

VCC

AD10

VCC

AD12

VCC

AD14

VCC

AD16

VCC

AD18

VCC

AE9

D

VCC

AE11

VCC

AE13

VCC

AE15

VCC

AE17

VCC

AE19

VCC

AF8

VCC

AF10

VCC

AF12

VCC

AF14

VCC

AF16

VCC

AF18

VCC

D10

VCCP

D12

VCCP

D14

VCCP

D16

VCCP

E11

VCCP

E13

VCCP

E15

VCCP

F10

VCCP

F12

VCCP

F14

VCCCPUIOVCCCPUCORE

F16K6L5

VCCP

VCCP

L21M6M22N5N21P6P22R5R21T6T22

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

E

VCCP

VCCP

VCCP

U21

VCCP

VCCP

P23

W4

VCCQ0

U67A

VCCQ1

VCCP / VCC / VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D2D5D7D9D11

D13

D15

D17

D19

D21

D23

D26E3E6E8E10

E12

E14

E16

E18

E20

E22

E25F1F4F5F7F9F11

3 3

VCCCPUIO

F13

F15

F17

F19

F21

F24G6G2

G22

G23

G26H5H3

H21

H25J1J4J6J22

J24K2K5

K21

K23

K26L3L6

L22

L25M1M4M5M21

M24N3N6

N22

N23

N26P2P5

P21

P24R1R4R6R22

R25T3T5

T21

T23

T26U2U6

U22

U24V1V4V5V21

V25W3W6

W22

W23

W26Y2Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

BANIAS-1D6G-1U

12

12

C159

SC2D2U6D3V3MX-1

12

C210

SC2D2U6D3V3MX-1

12

B

C158

SCD1U10V2KX

C204

SC10U6D3V5MX

12

C209

SC2D2U6D3V3MX-1

12

C187

SC2D2U6D3V3MX-1

12

C176

SCD1U10V2KX

12

C205

SC10U6D3V5MX

12

C183

SC10U6D3V5MX

12

C248

SCD1U10V2KX

VCCCPUCORE

12

C206

SC2D2U6D3V3MX-1

2 2

VCCCPUCORE

12

C190

SC2D2U6D3V3MX-1

VCCCPUCORE

12

C151

SC10U6D3V5MX

1 1

VCCCPUCORE

12

C222

SC10U6D3V5MX

12

C202

SCD1U10V2KX

12

C207

SC2D2U6D3V3MX-1

12

C163

SC2D2U6D3V3MX-1

12

C203

SC10U6D3V5MX

12

C165

SC10U6D3V5MX

A

12

C185

SCD1U10V2KX

12

12

12

C192

SC10U6D3V5MX

12

C182

SC10U6D3V5MX

12

C208

SC2D2U6D3V3MX-1

C175

SC2D2U6D3V3MX-1

12

12

C181

SCD1U10V2KX

C150

SC10U6D3V5MX

C195

SC10U6D3V5MX

12

C247

SCD1U10V2KX

12

C160

SC2D2U6D3V3MX-1

2.2UF X5R 0603 X15PCS

12

C172

SC10U6D3V5MX

10UF X5R 0805 X15PCS

12

C245

SCD1U10V2KX

12

C161

SC2D2U6D3V3MX-1

12

C166

SC10U6D3V5MX

12

C246

SCD1U10V2KX

12

C162

SC2D2U6D3V3MX-1

12

C250

SC10U6D3V5MX

C

12

C196

SCD1U10V2KX

12

C164

SC2D2U6D3V3MX-1

12

C173

SC10U6D3V5MX

12

C177

SC2D2U6D3V3MX-1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Size Document Number Rev

A3

D

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

BANIAS CPU(3/3)

S Note-1

666Wednesday, June 01, 2005

E

-2

of

A

GTL_D#[63..0]

1.Be transferred at the 4x rate

2.These signals are inverted on the CPU bus

GTL_A#[31:3]

1.Be transferred at the 2x rate

4 4

2.The address inverted on the CPU bus

GTL_REQ#[4:0]

Defines the attributes of the request

3 3

2 2

VCCGMCHCOREVCCGMCHCORE

12

R610

68D1R3F

12

12

C612

R623

SCD1U10V2KX

100R2F

VCCCPUIO

R654

301R2F

R650

150R2F

12

SCD1U10V2KX

12

1 1

12

12

C630

C675

SCD1U10V2KX

A

12

12

R701

301R2F

R700

150R2F

12

12

R625

287R2F

R624

100R2F

12

1/3 VTT

1/3 VTT

350 mV +/-8%800 mV +/-8%

C614

SCD1U10V2KX

HSWING components should be placed within 0.5 inches

of their respective pins and connected with a15-mil

wide trace. Maintain at least 25 mils spacing.

B

CPUCLK_MCH_100M3

CPUCLK_MCH_100M#3

VCCGMCHCORE

B

Unless otherwise noted,the voltage level for all signal in this interface is tied

to the termination voltage of the Processor System Bus (Vtt ~ 1. 3V)

GTL_A#[31..3]4

GTL_ADSTB#04

GTL_ADSTB#14

GTL_REQ#[4..0]4

GTL_ADS#4

GTL_DRDY#4

GTL_DEFER#4

GTL_TRDY#4

GTL_RS#04

GTL_RS#14

GTL_RS#24

PCIRST#20,62

GTL_BR0#4

GTL_BNR#4

GTL_BPRI#4

GTL_DBSY#4

GTL_HITM#4

GTL_HIT#4

GTL_LOCK#4

CC_DPSLP#21

GTL_CPURST#4

BPWRG59,62

GTL_DPWR#4

HUBLINK[10..0]20

HUB_STB20

HUB_STB#20

R622 37D4R2F

1 2

R699 27D4R2F

1 2

R665 27D4R2F

1 2

AGPBUSY#21

C

U70C

GTL_A#3

GTL_A#4

GTL_A#5

GTL_A#6

GTL_A#7

GTL_A#8

GTL_A#9

GTL_A#10

GTL_A#11

GTL_A#12

GTL_A#13

GTL_A#14

GTL_A#15

GTL_A#16

GTL_A#17

GTL_A#18

GTL_A#19

GTL_A#20

GTL_A#21

GTL_A#22

GTL_A#23

GTL_A#24

GTL_A#25

GTL_A#26

GTL_A#27

GTL_A#28

GTL_A#29

GTL_A#30

GTL_A#31

GTL_REQ#0

GTL_REQ#1

GTL_REQ#2

GTL_REQ#3

GTL_REQ#4

GTL_DPWR#

HUBLINK0

HUBLINK1

HUBLINK2

HUBLINK3

HUBLINK4

HUBLINK5 GTL_D#55

HUBLINK6

HUBLINK7

HUBLINK8

HUBLINK9

HUBLINK10

HLVREF

GMCH_RCOMP1

GMCH_RCOMP0

PSWING

HYSWING

HXSWING

R27

U23

U24

R24

U28

U27

U25

W25

AA27

W24

W23

W27

AA28

W28

AB27

AB28

AA26

R28

R23

R25

AE29

AD29

N24

M28

M25

N23

M27

AD28

M23

N25

M26

N28

N27

AA22

H28

P23

T25

T28

V28

T27

V27

V26

Y24

V25

V23

Y25

Y27

Y26

T26

P25

T23

L28

P26

P28

P27

Y23

F15

B20

K28

B18

J11

U7

U4

U3

V3

W2

W6

V6

W7

T3

V5

V4

W3

V2

W1

T2

U2

F7

HA[3]#

HA[4]#

HA[5]#

HA[6]#

HA[7]#

HA[8]#

HA[9]#

HA[10]#

HA[11]#

HA[12]#

HA[13]#

HA[14]#

HA[15]#

HA[16]#

HA[17]#

HA[18]#

HA[19]#

HA[20]#

HA[21]#

HA[22]#

HA[23]#

HA[24]#

HA[25]#

HA[26]#

HA[27]#

HA[28]#

HA[29]#

HA[30]#

HA[31]#

HADSTB[0]#

HADSTB[1]#

HREQ[0]#

HREQ[1]#

HREQ[2]#

HREQ[3]#

HREQ[4]#

BCLK

BCLK#

ADS#

DRDY#

DEFER#

HTRDY#

RS[0]#

RS[1]#

RS[2]#

RSTIN#

BREQ0#

BNR#

BPRI#

DBSY#

HITM#

HIT#

HLOCK#

DPSLP#

CPURST#

PWROK

DPWR#

HL[0]

HL[1]

HL[2]

HL[3]

HL[4]

HL[5]

HL[6]

HL[7]

HL[8]

HL[9]

HL[10]

HLSTB

HLSTB#

HLVREF

HLZCOMP

HYRCOMP

HXRCOMP

PSWING

HYSWING

HXSWING

AGPBUSY#

HOST

HUB LINK

MONTARA-GM

C

HD[0]#

HD[1]#

HD[2]#

HD[3]#

HD[4]#

HD[5]#

HD[6]#

HD[7]#

HD[8]#

HD[9]#

HD[10]#

HD[11]#

HD[12]#

HD[13]#

HD[14]#

HD[15]#

HDSTBP[0]#

HDSTBN[0]#

DINV[0]#

HD[16]#

HD[17]#

HD[18]#

HD[19]#

HD[20]#

HD[21]#

HD[22]#

HD[23]#

HD[24]#

HD[25]#

HD[26]#

HD[27]#

HD[28]#

HD[29]#

HD[30]#

HD[31]#

HDSTBP[1]#

HDSTBN[1]#

DINV[1]#

HD[32]#

HD[33]#

HD[34]#

HD[35]#

HD[36]#

HD[37]#

HD[38]#

HD[39]#

HD[40]#

HD[41]#

HD[42]#

HD[43]#

HD[44]#

HD[45]#

HD[46]#

HD[47]#

HDSTBP[2]#

HDSTBN[2]#

DINV[2]#

HD[48]#

HD[49]#

HD[50]#

HD[51]#

HD[52]#

HD[53]#

HD[54]#

HD[55]#

HD[56]#

HD[57]#

HD[58]#

HD[59]#

HD[60]#

HD[61]#

HD[62]#

HD[63]#

HDSTBP[3]#

HDSTBN[3]#

DINV[3]#

HDVREF[0]

HDVREF[1]

HDVREF[2]

HAVREF

HCCVREF

K22

H27

K25

L24

J27

G28

L27

L23

L25

J24

H25

K23

G27

K26

J23

H26

K27

J28

J25

F25

F26

B27

H23

E27

G25

F28

D27

G24

C28

B26

G22

C26

E26

G23

B28

D26

C27

E25

B21

G21

C24

C23

D22

C25

E24

D24

G20

E23

B22

B23

F23

F21

C20

C21

E21

E22

B25

G18

E19

E20

G17

D20

F19

C19

C17

F17

B19

G16

E16

C16

E17

D16

C18

E18

D18

G19

K21

J21

J17

Y22

Y28

GTL_D#0

GTL_D#1

GTL_D#2

GTL_D#3

GTL_D#4

GTL_D#5

GTL_D#6

GTL_D#7

GTL_D#8

GTL_D#9

GTL_D#10

GTL_D#11

GTL_D#12

GTL_D#13

GTL_D#14

GTL_D#15

GTL_D#16

GTL_D#17

GTL_D#18

GTL_D#19

GTL_D#20

GTL_D#21

GTL_D#22

GTL_D#23

GTL_D#24

GTL_D#25

GTL_D#26

GTL_D#27

GTL_D#28

GTL_D#29

GTL_D#30

GTL_D#31

GTL_D#32

GTL_D#33

GTL_D#34

GTL_D#35

GTL_D#36

GTL_D#37

GTL_D#38

GTL_D#39

GTL_D#40

GTL_D#41

GTL_D#42

GTL_D#43

GTL_D#44

GTL_D#45

GTL_D#46

GTL_D#47

GTL_D#48

GTL_D#49

GTL_D#50

GTL_D#51

GTL_D#52

GTL_D#53

GTL_D#54

GTL_D#56

GTL_D#57

GTL_D#58

GTL_D#59

GTL_D#60

GTL_D#61

GTL_D#62

GTL_D#63

12

SCD1U10V2KX

C312

12

SCD1U10V2KX

C294

D

GTL_D#[63..0] 4

GTL_DSTBP#0 4

GTL_DSTBN#0 4

GTL_DINV#0 4

GTL_DSTBP#1 4

GTL_DSTBN#1 4

GTL_DINV#1 4

GTL_DSTBP#2 4

GTL_DSTBN#2 4

GTL_DINV#2 4

GTL_DSTBP#3 4

GTL_DSTBN#3 4

GTL_DINV#3 4

2/3 VTT

12

C313

SCD1U10V2KX

D

12

SCD1U10V2KX

HDVREF

C314

E

VCCCPUIO

12

R307

49D9R2F

12

12

R302

C340

100R2F

SC1U10V3KX

Title

Size Document Number Rev

A3

Date: Sheet

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

MONTARA GM+(1/4)

S Note-1

E

766Wednesday, June 01, 2005

-2

of

A

M_SDQ[63..0]11,14,15

M_SDQS[7..0]11,14,15

M_SDM[7..0]11,14,15

4 4

M_SDQ9

M_SDQ13

M_SDM1

M_SDQ4

M_SDM0

M_SDQ5

M_SDQ1

M_SDQ2

M_SDQ0

M_SDQS0

M_SDQ6

3 3

2 2

1 1

M_SDQ14

M_SDQ11

M_SDQ10

M_SDQ15

M_SDQ3

M_SDQ8

M_SDQ12

M_SDQ16

M_SDQ20

M_SDQ17

M_SDQS2

M_SDM2

M_SDQ21

M_SDQ19

M_SDQ22

M_SDQ23

M_SDQ24

M_SDQ25

M_SDQ26

M_SDQ27

M_SDQ30

M_SDQ31

M_SDQ28

M_SDQ29

M_SDM3

M_SDQS3

RN72

1

2

3

4 5

SRN10-1

RN69

1

2

3

4 5

SRN10-1

RN70

1

2

3

4 5

SRN10-1

RN73

1

2

3

4 5

SRN10-1

RN71

1

2

3

4 5

SRN10-1

RN74

1

2

3

4 5

SRN10-1

RN75

1

2

3

4 5

SRN10-1

RN76

1

2

3

4 5

SRN10-1

RN78

1

2

3

4 5

SRN10-1

RN77

1

2

3

4 5

SRN10-1

A

M_FR_SDQ9

8

M_FR_SDQ13

7

M_FR_SDM1

6

M_FR_SDQS1M_SDQS1

M_FR_SDQ4

8

M_FR_SDM0

7

M_FR_SDQ5

6

M_FR_SDQ1

M_FR_SDQ2

8

M_FR_SDQ0

7

M_FR_SDQS0

6

M_FR_SDQ6

M_FR_SDQ14

8

M_FR_SDQ11

7

M_FR_SDQ10

6

M_FR_SDQ15

M_FR_SDQ7M_SDQ7

8

M_FR_SDQ3

7

M_FR_SDQ8

6

M_FR_SDQ12

M_FR_SDQ16

8

M_FR_SDQ20

7

M_FR_SDQ17

6

M_FR_SDQS2

M_FR_SDM2

8

M_FR_SDQ21

7

M_FR_SDQ18M_SDQ18

6

M_FR_SDQ19

M_FR_SDQ22

8

M_FR_SDQ23

7

M_FR_SDQ24

6

M_FR_SDQ25

M_FR_SDQ26

8

M_FR_SDQ27

7

M_FR_SDQ30

6

M_FR_SDQ31

M_FR_SDQ28

8

M_FR_SDQ29

7

M_FR_SDM3

6

M_FR_SDQS3

M_SDQ33

M_SDQ32

M_SDQ36

M_SDQ37

M_SDQ38

M_SDQ34

M_SDM4

M_SDQS4

M_SDQ41

M_SDQ44

M_SDQ39

M_SDQ35

M_SDQ43

M_SDQ42

M_SDQ47

M_SDQ46

M_SDQS5

M_SDM5

M_SDQ40

M_SDQ45

M_SDQ50

M_SDM6

M_SDQ54

M_SDQS6

M_SDQ52

M_SDQ49

M_SDQ53

M_SDQ48

M_SDQ60

M_SDQ61

M_SDQ51

M_SDQ55

M_SDM7

M_SDQS7

M_SDQ56

M_SDQ57

M_SDQ63

M_SDQ59

M_SDQ58

M_SDQ62

B

RN28

1

2

3

4 5

SRN10-1

RN29

1

2

3

4 5

SRN10-1

RN30

1

2

3

4 5

SRN10-1

RN32

1

2

3

4 5

SRN10-1

RN31

1

2

3

4 5

SRN10-1

RN34

1

2

3

4 5

SRN10-1

RN33

1

2

3

4 5

SRN10-1

RN35

1

2

3

4 5

SRN10-1

RN36

1

2

3

4 5

SRN10-1

RN37

1

2

3

4 5

SRN10-1

B

M_FR_SDQ33

8

M_FR_SDQ32

7

M_FR_SDQ36

6

M_FR_SDQ37

M_FR_SDQ38

8

M_FR_SDQ34

7

M_FR_SDM4

6

M_FR_SDQS4

M_FR_SDQ41

8

M_FR_SDQ44

7

M_FR_SDQ39

6

M_FR_SDQ35

M_FR_SDQ43

8

M_FR_SDQ42

7

M_FR_SDQ47

6

M_FR_SDQ46

M_FR_SDQS5

8

M_FR_SDM5

7

M_FR_SDQ40

6

M_FR_SDQ45

M_FR_SDQ50

8

M_FR_SDM6

7

M_FR_SDQ54

6

M_FR_SDQS6

M_FR_SDQ52

8

M_FR_SDQ49

7

M_FR_SDQ53

6

M_FR_SDQ48

M_FR_SDQ60

8

M_FR_SDQ61

7

M_FR_SDQ51

6

M_FR_SDQ55

M_FR_SDM7

8

M_FR_SDQS7

7

M_FR_SDQ56

6

M_FR_SDQ57

M_FR_SDQ63

8

M_FR_SDQ59

7

M_FR_SDQ58

6

M_FR_SDQ62

C

M_SMA[12..0]12,13,14,15

M_SMAB114,15

M_SMAB214,15

M_SMAB414,15

M_SMAB514,15

M_SWE#12,13,14,15

M_SCAS#12,13,14,15

M_SRAS#12,13,14,15

M_SMBA012,13,14,15

M_SMBA112,13,14,15

M_SCS0#12,15

M_SCS1#13,15

M_SCS2#14,15

M_SCS3#14,15

M_SCKE012,15

M_SCKE113,15

M_SCKE214,15

M_SCKE314,15

DDRCLK0_133M11,12,13

DDRCLK0_133M#11,12,13

DDRCLK1_133M11,12,13

DDRCLK1_133M#11,12,13

DDRCLK3_133M14

DDRCLK3_133M#14

DDRCLK4_133M14

DDRCLK4_133M#14

VCC2R5A VCC2R5A

12

R666

604R3F

R669

150R2F

12

VCCSMx0.2

12

C643

SCD1U10V2KX

C

R659

150R2F

R655

604R3F

12

12

U70A

M_SMA0

M_SMA1

M_SMA2

M_SMA3

M_SMA4

M_SMA5

M_SMA6

M_SMA7

M_SMA8

M_SMA9

M_SMA10

M_SMA11

M_SMA12

M_FR_SDQS7

M_FR_SDM7

M_FR_SDQ56

M_FR_SDQ57

M_FR_SDQ58

M_FR_SDQ59

M_FR_SDQ60

M_FR_SDQ61

M_FR_SDQ62

M_FR_SDQ63

SMVSWINGL

SMVSWINGH

VCCSMx0.8

12

C628

SCD1U10V2KX

AC18

SMA[0]

AD14

SMA[1]

AD13

SMA[2]

AD17

SMA[3]

AD11

SMA[4]

AC13

SMA[5]

AD8

SMA[6]

AD7

SMA[7]

AC6

SMA[8]

AC5

SMA[9]

AC19

AD5

AB5

AD16

AC12

AF11

AD10

AD25

AC24

AC21

AD22

AD20

AD23

AD26

AC22

AC25

AC7

AB7

AC9

AC10

AB2

AA2

AC26

AB25

AC3

AD4

AC2

AD2

AB23

AB24

AA3

AB4

AH27

AH28

AH26

AE26

AG28

AF28

AG26

AF26

AE27

AD27

AD15

AH15

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

AJ22

SMA[10]

SMA[11]

SMA[12]

SMAB[1]

SMAB[2]

SMAB[4]

SMAB[5]

SWE#

SCAS#

SRAS#

SBA[0]

SBA[1]

SCS[0]#

SCS[1]#

SCS[2]#

SCS[3]#

SCKE[0]

SCKE[1]

SCKE[2]

SCKE[3]

SCK[0]

SCK[0]#

SCK[1]

SCK[1]#

SCK[2]

SCK[2]#

SCK[3]

SCK[3]#

SCK[4]

SCK[4]#

SCK[5]

SCK[5]#

SDQS[7]

SDM[7]

SDQ[56]

SDQ[57]

SDQ[58]

SDQ[59]

SDQ[60]

SDQ[61]

SDQ[62]

SDQ[63]

SDQS[8]

SDM[8]

SDQ[64]

SDQ[65]

SDQ[66]

SDQ[67]

SDQ[68]

SDQ[69]

SDQ[70]

SDQ[71]

SMVSWINGL

MONTARA-GM

DDR

MEMORY

Maintain a minimum of 25 mils spacing.

SMVSWINGL and SMVSWINGH components should be

placed within 0.5 inches of their respective

pins and connected with a 15-mil wide trace.

D

M_FR_SDQS0

AG2

SDQS[0]

SDM[0]

SDQ[0]

SDQ[1]

SDQ[2]

SDQ[3]

SDQ[4]

SDQ[5]

SDQ[6]

SDQ[7]

SDQS[1]

SDM[1]

SDQ[8]

SDQ[9]

SDQ[10]

SDQ[11]

SDQ[12]

SDQ[13]

SDQ[14]

SDQ[15]

SDQS[2]

SDM[2]

SDQ[16]

SDQ[17]

SDQ[18]

SDQ[19]

SDQ[20]

SDQ[21]

SDQ[22]

SDQ[23]

SDQS[3]

SDM[3]

SDQ[24]

SDQ[25]

SDQ[26]

SDQ[27]

SDQ[28]

SDQ[29]

SDQ[30]

SDQ[31]

SDQS[4]

SDM[4]

SDQ[32]

SDQ[33]

SDQ[34]

SDQ[35]

SDQ[36]

SDQ[37]

SDQ[38]

SDQ[39]

SDQS[5]

SDM[5]

SDQ[40]

SDQ[41]

SDQ[42]

SDQ[43]

SDQ[44]

SDQ[45]

SDQ[46]

SDQ[47]

SDQS[6]

SDM[6]

SDQ[48]

SDQ[49]

SDQ[50]

SDQ[51]

SDQ[52]

SDQ[53]

SDQ[54]

SDQ[55]

SMRCOMP

SMVREF_0SMVSWINGH

D

M_FR_SDM0

AE5

M_FR_SDQ0

AF2

M_FR_SDQ1

AE3

M_FR_SDQ2

AF4

M_FR_SDQ3

AH2

M_FR_SDQ4

AD3

M_FR_SDQ5

AE2

M_FR_SDQ6

AG4

M_FR_SDQ7

AH3

M_FR_SDQS1

AH5

M_FR_SDM1

AE6

M_FR_SDQ8

AD6

M_FR_SDQ9

AG5

M_FR_SDQ10

AG7

M_FR_SDQ11

AE8

M_FR_SDQ12

AF5

M_FR_SDQ13

AH4

M_FR_SDQ14

AF7

M_FR_SDQ15

AH6

M_FR_SDQS2

AH8

M_FR_SDM2

AE9

M_FR_SDQ16

AF8

M_FR_SDQ17

AG8

M_FR_SDQ18

AH9

M_FR_SDQ19

AG10

M_FR_SDQ20

AH7

M_FR_SDQ21

AD9

M_FR_SDQ22

AF10

M_FR_SDQ23

AE11

M_FR_SDQS3

AE12

M_FR_SDM3

AH12

M_FR_SDQ24

AH10

M_FR_SDQ25

AH11

M_FR_SDQ26

AG13

M_FR_SDQ27

AF14

M_FR_SDQ28

AG11

M_FR_SDQ29

AD12

M_FR_SDQ30

AF13

M_FR_SDQ31

AH13

M_FR_SDQS4

AH17

M_FR_SDM4

AD19

M_FR_SDQ32

AH16

M_FR_SDQ33

AG17

M_FR_SDQ34

AF19

M_FR_SDQ35

AE20

M_FR_SDQ36

AD18

M_FR_SDQ37

AE18

M_FR_SDQ38

AH18

M_FR_SDQ39

AG19

M_FR_SDQS5

AE21

M_FR_SDM5

AD21

M_FR_SDQ40

AH20

M_FR_SDQ41

AG20

M_FR_SDQ42

AF22

M_FR_SDQ43

AH22

M_FR_SDQ44

AF20

M_FR_SDQ45

AH19

M_FR_SDQ46

AH21

M_FR_SDQ47

AG22

M_FR_SDQS6

AH24

M_FR_SDM6

AD24

M_FR_SDQ48

AE23

M_FR_SDQ49

AH23

M_FR_SDQ50

AE24

M_FR_SDQ51

AH25

M_FR_SDQ52

AG23

M_FR_SDQ53

AF23

M_FR_SDQ54

AF25

M_FR_SDQ55

AG25

SMRCOMP

AB1

AJ24AJ19

DDR_VREF

12

C659

SCD1U10V2KX

Title

Size Document Number Rev

A3

Date: Sheet

This signa l may be option a l l y connected to

Vcc2_5 and powered off in S3.

The SMRCOMP signal should

be a minimum of 12 mils

wide and be isolated from

other signals with a

minimum of 10 mils

spacing.

VCC2R5A

MONTARA GM+(2/4)

E

12

R612

60D4R3

1 2

It's the same as Intel Reference Schematics.

Revision 1.303

S Note-1

12

C607

SCD1U10V2KX

R611

60D4R3

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

866Wednesday, June 01, 2005

E

of

-2

AA29

W29

U29

N29

G29

E29

C29

AE28

AC28

E28

D28

AJ27

AG27

AC27

F27

A27

AJ26

AB26

W26

U26

R26

N26

G26

AE25

AA25

D25

A25

AG24

AA24

V24

T24

P24

M24

K24

H24

F24

B24

AJ23

AC23

AA23

D23

A23

AE22

W22

U22

R22

N22

F22

C22

AG21

AB21

AA21

Y21

V21

T21

P21

M21

H21

D21

A21

AJ20

AC20

AA20

F20

AE19

AB19

H19

D19

A19

AJ18

AG18

AA18

F18

AC17

AB17

U17

R17

N17

H17

D17

A17

AE16

AA16

T16

P16

L29

J29

L26

J26

L22

J22

J20

J18

J16

U70E

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MONTARA-GM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSADAC

VSSALVDS

AE13

AB13

U13

R13

N13

H13

F13

D13

A13

AJ12

AG12

AA12

J12

AJ11

AC11

AB11

H11

F11

D11

AJ10

AE10

AA10

J10

C10

AG9

AB9

W9

U9

T9

R9

N9

L9

E9

AC8

Y8

V8

T8

P8

K8

H8

AJ7

AE7

AA7

R7

M7

J7

G7

E7

C7

AG6

Y6

L6

Y5

U5

B5

AE4

AC4

AA4

W4

T4

N4

K4

G4

D4

AJ3

AG3

R2

AJ1

AE1

AA1

U1

L1

G1

C1

F16

AG15

AB15

U15

R15

N15

H15

D15

AC14

AA14

T14

P14

J14

B8

B11

R618

1KR2F

R617

1KR2F

VCC1R5B

12

12

GVREF

12

C609

SCD1U10V2KX

SUSCLK_32K21,43

AGPCLK_MCH_66M3

DREFSSCLK_48M3

MEM_THRM#47

VCC1R5B

DREFCLK_48M3

VCC1R5B

1

G

R621 100KR2

1 2

R619 100KR2

1 2

R620 100KR2

1 2

R602 100KR2

1 2

R616 40D2R2F

1 2

R644

NO ASM

12

2 3

R253

1KR2

CLK48_DPMS

D

Q21

2N7002

S

C627

R601

1 2

0R2-0

VCC1R5B

L7 is DVODETECT,pull high

to 1D5V if no DVO function

DVOB_FLD/STL

DVOBC_INTR#

DVOBC_CLKINT

DVOC_FLD/STL

DVO_RCOMP

DY-10KR2

12

R265

DY-SC10P50V2JN

12

C252

MEM_THRM#_R

DY-10KR2

DY-SC10P50V2JN

DY-10KR2

12

12

R638

DY-SC10P50V2JN

12

12

C618

VCC3B

12

R600

10KR2

R604

1 2

1KR2

R3

DVOBD[0]

R5

DVOBD[1]

R6

DVOBD[2]

R4

DVOBD[3]

P6

DVOBD[4]

P5

DVOBD[5]

N5

DVOBD[6]

P2

DVOBD[7]

N2

DVOBD[8]

N3

DVOBD[9]

M1

DVOBD[10]

M5

DVOBD[11]

P3

DVOBCLK

P4

DVOBCLK#

M2

DVOBFLDSTL

T6

DVOBHSYNC

T5

DVOBVSYNC

L2

DVOBBLANK#

G2

DVOBCINTR#

M3

DVOBCCLKINT

K5

DVOCD[0]

K1

DVOCD[1]

K3

DVOCD[2]

K2

DVOCD[3]

J6

DVOCD[4]

J5

DVOCD[5]

H2

DVOCD[6]

H1

DVOCD[7]

H3

DVOCD[8]

H4

DVOCD[9]

H6

DVOCD[10]

G3

DVOCD[11]

J3

DVOCCLK

J2

DVOCCLK#

H5

DVOCFLDSTL

K6

DVOCHSYNC

L5

DVOCVSYNC

L3

DVOCBLANK#

D1

DVORCOMP

F1

GVREF

Y3

GCLKIN

D5

DPMS

B7

DREFCLK

B17

DREFSSCLK

D6

EXTTS_0

Please check Intel Montara-GM EDS

REV.NO. 1.1 REF.NO. 12716

Page 136

L7E5F5E3E2G5F4G6F6

U70B

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

F12

RSVD

D12

DVOB CRT

VIDEO

DVOC

NCNCNCNCNCNCNCNCNCNCNCNCNC

AJ29

AH29

B29

A29

AJ28

A28

AA9

AJ4

AJ2A2AH1B1AC16

B12

AA5L4C4F3D3C3B3F2D2C2B2

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

LVDS

NC

AC15

GST[0]

GST[1]

GST[2]

D7

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

DDCA_DATA

DDCA_CLK

DDCPDATA

DDCPCLK

RED#

GREEN

GREEN#

BLUE

BLUE#

HSYNC

VSYNC

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

IYAP[0]

IYAM[0]

IYAP[1]

IYAM[1]

IYAP[2]

IYAM[2]

IYAP[3]

IYAM[3]

ICLKAP

ICLKAM

IYBP[0]

IYBM[0]

IYBP[1]

IYBM[1]

IYBP[2]

IYBM[2]

IYBP[3]

IYBM[3]

ICLKBM

ICLKBP

LCLKCTLA

LCLKCTLB

MDDCCLK

MDDCDATA

MDVICLK

MDVIDATA

MI2CCLK

MI2CDATA

REFSET

LIBG

MONTARA-GM

RED

R613

1 2

1KR2

R614

1 2

1KR2

R615

1 2

1KR2

G9

B6

C5

B4

A7

A8

C8

D8

C9

D9

H10

J9

G8

F8

A5

F14

G14

E14

E15

C14

C15

B13

C13

E13

D14

G12

H12

E11

E12

C11

C12

G10

G11

E10

F10

H9

C6

P7

T7

N7

M6

K7

N6

E8

A10

VCC1R5B

DAC_SDAT

DAC_SCL

DDCPDATA

DDCPCLK

MDDCCLK

MDDCDATA

MDVICLK

MDVIDATA

MI2CCLK

MI2CDATA

REFSET

LIBG

GST[2..0]

MGM & DDR266

0 0 0

MGM+ & DDR266 0 0 0

MGM+ & DDR333

VCC3B

12

R626

2K2R2

R608 2K2R2

R609 2K2R2

R607 2K2R2

R605 2K2R2

R603 2K2R2

R606 2K2R2

12

12

R639

1K5R2F

2K2R2

1 2

1 2

1 2

1 2

1 2

1 2

R281

127R2F

1 1 1

12

R284

2K2R2

12

VCC1R5B

R627

RED 17

GREEN 17

BLUE 17

HSYNC 17,19

VSYNC 17,19

GMCH_BRIGHT 18

VGA_BLON 43

PANEL_POWER_ON 59

TXOUT_L0P 18

TXOUT_L0N 18

TXOUT_L1P 18

TXOUT_L1N 18

TXOUT_L2P 18

TXOUT_L2N 18

TXCLK_LP 18

TXCLK_LN 18

2K2R2

VSSADAC(Ground supply for the DAC)

Title

Size Document Number Rev

A3

Date: Sheet

VCC3B

R629

12

G

2

1 3

S

VCC3B

G

2

1 3

S

BLUE

GREEN

RED

C223

1 2

DY-SC33P50V2JN

For EMI recommendation:

near the output pin of RGB signal

Wide and short patte r n

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

MONTARA GM+(3/4)

S Note-1

Q68

2SK3019-N

D

Q67

2SK3019-N

D

C200

DY-SC33P50V2JN

1 2

966Wednesday, June 01, 2005

DDCDATA_ID1 19,46

DDCCLK_ID3 19,46

C212

1 2

DY-SC33P50V2JN

-2

of

A

B

C

D

E

VCC1R5B

P9

VCCDVO

VCC3B

W21

AA19

AA17

AA15

T17

P17

U16

R16

N16

T15

P15

J15

U14

R14

N14

H14

T13

P13

A12

D10

B10

B15

B14

J13

G13

A11

B16

D29

M9

K9

R8

N8

M8

L8

J8

H7

E6

M4

J4

E4

N1

J1

E1

F9

A6

Y2

B9

A9

A3

A4

V9

W8

U8

V7

U6

W5

Y1

V1

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCC

VCC

VCC

VCC

VCC

POWER

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCTXLVDS

VCCTXLVDS

VCCTXLVDS

VCCTXLVDS

VCCDLVDS

VCCDLVDS

VCCDLVDS

VCCDLVDS

VCCALVDS

VCCADPLLA

VCCADPLLB

VCCAGPLL

VCCAHPLL

VCCADAC

VCCADAC

VCCGPIO

VCCGPIO

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

C

12

SCD1U10V2KX

VCC2R5A

C264

SCD1U10V2KX

12

C617

SCD1U10V2KX

12

C626

SCD1U10V2KX

VCCGMCHCORE

12

C231

SCD1U10V2KX

C296

SCD1U10V2KX

12

C295

SCD1U10V2KX

VCC1R5B

12

C283

VCC_ADPLLAVCCADPLLA

VCC_ADPLLB

VCC1R5B

12

C233

SCD1U10V2KX

12

12

C302

SCD1U10V2KX

C285

12

SCD1U10V2KX

C297

12

C255

SC10U6D3V5MX

SCD1U10V2KX

4 4

North Bridge

MONTARA-GM

MONTARA-GM+

VCCGMCHCORE

12

SC2D2U6D3V3MX-1

C278

VCCGMCHCORE

1.20V

1.35V

C284

SC1000P50V

C286

SC1000P50V

SCD1U10V2KX

12

C606

SC10U10V-U1

12

12

C279

C259

SCD1U10V2KX

12

SCD1U10V2KX

12

C608

SC10U10V-U1

C288

Caps for VCCTXLVDS

3 3

12

C265

SCD1U10V2KX

12

C260

SCD1U10V2KX

12

C232

SCD1U10V2KX

12

For J13

C611

SCD1U10V2KX

VCCGMCHCORE

1 2

VCCGMCHCORE

1 2

VCCGMCHCORE

C267

SCD1U10V2KX

C241

SCD1U10V2KX

C276

SC10U6D3V5MX

S.B.

VCC1R5B

VCC1R5B

12

VCC3B

12

12

C610

SCD1U10V2KX

12

C268

SCD01U25V2KX

C270

SCD01U25V2KX

C251

SC10U6D3V5MX

S.B.

VCCGMCHCORE

A

12

Caps for VCCALVDS

12

2 2

Caps for VCCGPIO

12

Caps for VCCHL

12

Caps for VCCADAC

12

1 1

C263

SCD1U10V2KX

This two cap chould connect to

VSSADAC first then to GND

12

C290

SC22U10V6ZY-U

C281

SC22U10V6ZY-U

Caps for VCCDLVDS

12

C274

SCD1U10V2KX

12

C273

SC22U10V6ZY-U

For B14

R635

1R5

ESR<50mohm,ESL<2.5mH

TC19,C21 on the same si de

R641

VCCADPLLB

1R5

ESR<50mohm,ESL<2.5mH

TC20,C26 on the same side

12

C613

SCD1U10V2KX

Cap for

VCCAGPLL

L26

1 2

IND-D1UH

L27

1 2

IND-D1UH

VCCGMCHCORE

12

C266

SCD1U10V2KX

12

C258

SC22U10V6ZY-U

12

C678

SCD1U10V2KX

Cap for

VCCAHPLL

B

12

C289

SCD1U10V2KX

VCC1R5B

12

TC7

ST220U4VDM-1

12

TC9

ST220U4VDM-1

12

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCQSM

VCCQSM

VCCASM

VCCASM

VTTHF

VTTHF

VTTHF

VTTHF

VTTHF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

MONTARA-GM

U70D

AG29

AF29

AC29

AF27

AJ25

AF24

AB22

AJ21

AF21

AB20

AF18

AB18

AJ17

AB16

AF15

AB14

AJ13

AA13

AF12

AB12

AA11

AB10

AJ9

AF9

Y9

AB8

AA8

Y7

AF6

AB6

AA6

AJ5

Y4

AF3

AB3

AG1

AC1

AJ8

AJ6

AF1

AD1

V29

M29

H29

A24

A22

AB29

Y29

K29

F29

A26

V22

T22

P22

M22

H22

U21

R21

N21

L21

H20

A20

J19

H18

A18

H16

G15

VCC2R5A

12

C235

SCD1U10V2KX

12

C253

SCD1U10V2KX

VCC_QSM

VCC_ASM

Current:~440mA

C673 SCD1U10V2KX

1 2

C676 SCD1U10V2KX

1 2

C674 SCD1U10V2KX

1 2

C648 SCD1U10V2KX

1 2

C638 SCD1U10V2KX

1 2

12

C303

SCD1U10V2KX

12

C307

SCD1U10V2KX

12

C277

SCD1U10V2KX

C40,C39

should on the

same side

12

12

12

C324

SCD1U10V2KX

D

12

C272

SCD1U10V2KX

12

C333

SCD1U10V2KX

C238

SCD1U10V2KX

C615

SCD1U10V2KX

12

C301

SCD1U10V2KX

12

12

C261

SCD1U10V2KX

12

SCD1U10V2KX

C243

SC4D7U10V-U

12

12

SCD1U10V2KX

C280

SCD1U10V2KX

SCD1U10V2KX

12

C311

C334

L9

1 2

IND-D68UH-2

L10

1 2

IND-1UH-5

TC8

ST150U6D3VM-U

C41,TC36

should on the

same side

C287

Title

Size Document Number Rev

A3

Date: Sheet

SCD1U10V2KX

VCC2R5A

VCCGMCHCORE

12

C310

SCD1U10V2KX

SCD1U10V2KX

SCD1U10V2KX

12

12

C271

SCD1U10V2KX

12

C234

SCD1U10V2KX

12

C332

SCD1U10V2KX

12

C299

12

C322

12

C336

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

SC22U10V6ZY-U

VCCCPUIO

12

SCD1U10V2KX

C306

C308

MONTARA GM+(4/4)

S Note-1

10 66Wednesday, June 01, 2005

E

of

-2

A

4 4

B

C

D

E

M_SDQ[63..0] 8,14,15

M_R_SDQ[63..0] 12,13

M_SDQS[7..0] 8,14,15

M_R_SDQS[7..0] 12,13

M_SDM[7..0] 8

M_R_SDM[7..0] 12,13

M_SDQ5

M_SDQ1

M_SDM0

M_SDQ4 M_R_SDQ4

M_SDQS0 M_R_SDQS0

M_SDQ6

M_SDQ0

M_SDQ2

3 3

2 2

1 1

M_SDQ10

M_SDQ14 M_R_SDQ14

M_SDQ11

M_SDM1

M_SDQS1 M_R_SDQS1

M_SDQ9

M_SDQ13 M_R_SDQ13

M_SDQS2

M_SDQ17 M_R_SDQ17

M_SDQ20

M_SDQ16

M_SDQ19

M_SDQ18 M_R_SDQ18

M_SDQ21 M_R_SDQ21

M_SDM2

M_SDQ31

M_SDQ30

M_SDQ26

M_SDM3 M_R_SDM3

M_SDQS3

M_SDQ29

M_SDQ28

RN55

1

2

3

4 5

SRN22-2

RN56

1

2

3

4 5

SRN22-2

RN59

1

2

3

4 5

SRN22-2

RN58

1

2

3

4 5

SRN22-2

RN60

1

2

3

4 5

SRN22-2

RN61

1

2

3

4 5

SRN22-2

RN64

1

2

3

4 5

SRN22-2

RN63

1

2

3

4 5

SRN22-2

M_R_SDQ5

8

M_R_SDQ1

7

M_R_SDM0

6

8

M_R_SDQ6

7

M_R_SDQ0

6

M_R_SDQ2

M_R_SDQ15

8

M_R_SDQ10

7

6

M_R_SDQ11

M_R_SDM1

8

7

M_R_SDQ9

6

M_R_SDQS2

8

7

M_R_SDQ20

6

M_R_SDQ16

M_R_SDQ19

8

7

6

M_R_SDM2

M_R_SDQ31

8

M_R_SDQ30

7

M_R_SDQ27M_SDQ27

6

M_R_SDQ26

8

M_R_SDQS3

7

M_R_SDQ29

6

M_R_SDQ28

M_SDQ36

M_SDQ37

M_SDQ32

M_SDQ33

M_SDQ35 M_R_SDQ35

M_SDQ53 M_R_SDQ53

M_SDQ48 M_R_SDQ48

M_SDQ46

M_SDQ47

M_SDM5

M_SDQS5

M_SDQ45

M_SDQ41

M_SDQ44

M_SDQ49 M_R_SDQ49

M_SDQ52

M_SDQ54

M_SDQS6 M_R_SDQS6

M_SDQ50

M_SDM6

M_SDQ51

M_SDQ55 M_R_SDQ55

M_SDM7

M_SDQS7

M_SDQ57

M_SDQ56

M_SDQ63 M_R_SDQ63

M_SDQ59 M_R_SDQ59

M_SDQ58

M_SDQ62

RN14

1

8

2

7

3

6

4 5

SRN22-2

R109 56R2J

1 2

R108 56R2J

1 2

R111 56R2J

1 2

R110 56R2J

1 2

RN66

1

8

2

7

3

6

4 5

SRN22-2

RN65

1

8

2

7

3

6

4 5

SRN22-2

RN16

1

8

2

7

3

6

4 5

SRN22-2

RN17

1

8

2

7

3

6

4 5

SRN22-2

RN67

1

8

2

7

3

6

4 5

SRN22-2

RN68

1

8

2

7

3

6

4 5

SRN22-2

M_R_SDQ36

M_R_SDQ37

M_R_SDQ32

M_R_SDQ33

M_R_SDQ39M_SDQ39

M_R_SDQ46

M_R_SDQ47

M_R_SDM5

M_R_SDQS5

M_R_SDQ45

M_R_SDQ40

M_R_SDQ41

M_R_SDQ44

M_R_SDQ52

M_R_SDQ54

M_R_SDQ50

M_R_SDM6

M_R_SDQ51

M_R_SDM7

M_R_SDQS7

M_R_SDQ57

M_R_SDQ56

M_R_SDQ58

M_R_SDQ62

M_SDQ24 M_R_SDQ24

M_SDQ25

M_SDQ23

M_SDQ22 M_R_SDQ22

M_SDQ61

M_SDQ60

M_SDQ42

M_SDQ43

M_SDQ12

M_SDQ8

M_SDQ3 M_R_SDQ3

M_SDM4

M_SDQS4 M_R_SDQS4

M_SDQ34 M_R_SDQ34

RN62

1

8

2

7

3

6

4 5

SRN22-2

R526 56R2J

1 2

R525 56R2J

1 2

R524 56R2J

1 2

R523 56R2J

1 2

RN57

1

8

2

7

3

6

4 5

SRN22-2

RN15

1

8

2

7

3

6

4 5

SRN22-2

12

R48

120R2J

12

R451

120R2J

DDRCLK1_133M 8,12,13

DDRCLK1_133M# 8,12,13

M_R_SDQ25

M_R_SDQ23

M_R_SDQ12M_SDQ15

M_R_SDQ8

M_R_SDQ7M_SDQ7

M_R_SDM4

M_R_SDQ38M_SDQ38M_SDQ40

DDRCLK0_133M 8,12,13

DDRCLK0_133M# 8,12,13

M_R_SDQ61

M_R_SDQ60

M_R_SDQ42

M_R_SDQ43

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Size Document Number Rev

Custom

A

B

C

D

Date: Sheet

DDR DATA RESISTOR

Taipei Hsien 221, Taiwan, R.O.C.

S Note-1

11 66Wednesday, June 01, 2005

E

-2

of

A

4 4

B

C

D

E

M_R_SDQS[7..0] 11,13

M_R_SDM[7..0] 11

M_R_SDQ[63..0] 11,13

M_SMA[12..0] 8

M_SMBA[1..0] 8

DDRCLK0_133M 8,11

DDRCLK0_133M# 8,11

DDRCLK1_133M 8,11

DDRCLK1_133M# 8,11

M_SWE# 8

M_SCAS# 8

M_SRAS# 8

M_SCS0# 8

M_SCKE0 8

M_R_SDQ15

M_R_SDQ14

M_R_SDQ13

M_R_SDQ12

M_R_SDQ11

M_R_SDQ10

M_R_SDQ9

M_R_SDQ8

M_R_SDQ7

M_R_SDQ6

M_R_SDQ5

3 3

2 2

M_R_SDQ4

M_R_SDQ3

M_R_SDQ2

M_R_SDQ1

M_R_SDQ0

M_SCKE0

DDRCLK0_133M

DDRCLK0_133M#

U8

2

DQ0

4

DQ1

5

DQ2

7

DQ3

8

DQ4

10

DQ5

11

DQ6

13

DQ7

54

DQ8

56

DQ9

57

DQ10

59

DQ11

60

DQ12

62

DQ13

63

DQ14

65

DQ15

44

CKE

45

CK

46

CK#

34

VSS

48

VSS

66

VSS

6

VSSQ

12

VSSQ

52

VSSQ

58

VSSQ

64

VSSQ

14

NC

17

NC

19

NC/DNU

25

NC

43

NC

53

NC

50

DNU

MT46V32M16TG

72.46161.B09

A10/AP

BA0

BA1

CS#

RAS#

CAS#

WE#

LDM

UDM

LDQS

UDQS

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VREF

M_SMA0

29

A0

M_SMA1

30

A1

M_SMA2

31

A2

M_SMA3

32

A3

M_SMA4

35

A4

M_SMA5

36

A5

M_SMA6

37

A6

M_SMA7

38

A7

M_SMA8

39

A8

M_SMA9

40

A9

M_SMA10

28

M_SMA11

41

A11

M_SMA12

42

A12

M_SMBA0

26

M_SMBA1

27

24

M_SRAS#

23

M_SCAS#

22

M_SWE#

21

M_R_SDM1

20

M_R_SDM0

47

M_R_SDQS1

16

M_R_SDQS0

51

1

18

33

3

9

15

55

61

49

VCC2R5A

DDR_VREF

M_R_SDQ31

M_R_SDQ30

M_R_SDQ29

M_R_SDQ28

M_R_SDQ27

M_R_SDQ26

M_R_SDQ25

M_R_SDQ24

M_R_SDQ23

M_R_SDQ22

M_R_SDQ21

M_R_SDQ20

M_R_SDQ19

M_R_SDQ18

M_R_SDQ17

M_R_SDQ16

M_SCKE0

DDRCLK0_133M

DDRCLK0_133M#

U9

2

DQ0

4

DQ1

5

DQ2

7

DQ3

8

DQ4

10

DQ5

11

DQ6

13

DQ7

54

DQ8

56

DQ9

57

DQ10

59

DQ11

60

DQ12

62

DQ13

63

DQ14

65

DQ15

44

CKE

45

CK

46