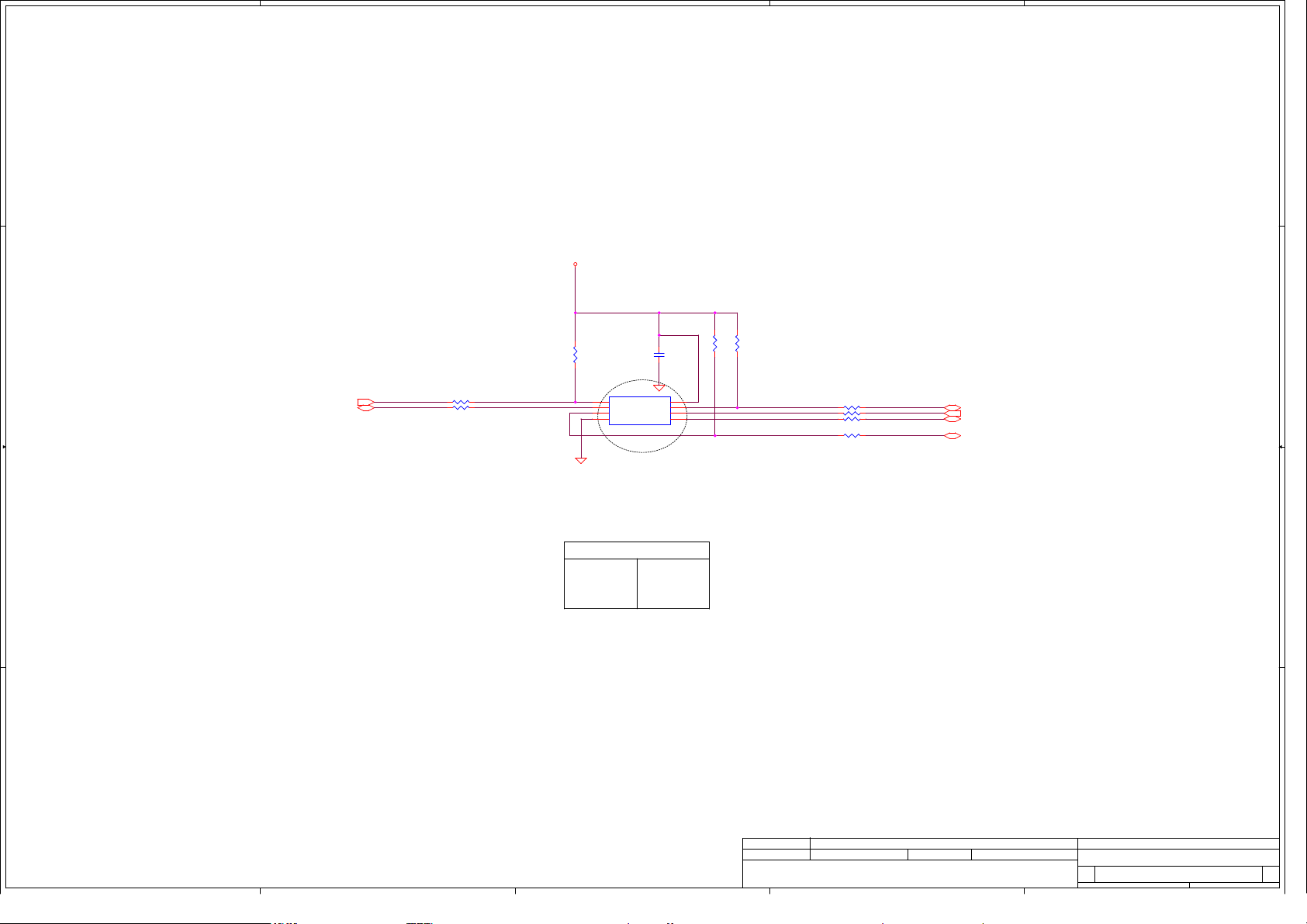

Lenovo X380 Schematic

A

1 1

B

C

D

E

Compal Confidential

2 2

STORM3 M/B Schematic

LA-F421P

Rev: 1.0_ B

2017.10.23

3 3

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/11/04 2016/12/31

2014/11/04 2016/12/31

2014/11/04 2016/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

COVER PAGE

COVER PAGE

COVER PAGE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F421P

LA-F421P

LA-F421P

Date: Sheet

Date: Sheet

Date: Sheet

E

of

of

of

1 73Monday, October 23, 2017

1 73Monday, October 23, 2017

1 73Monday, October 23, 2017

1.0

1.0

1.0

5

4

3

2

1

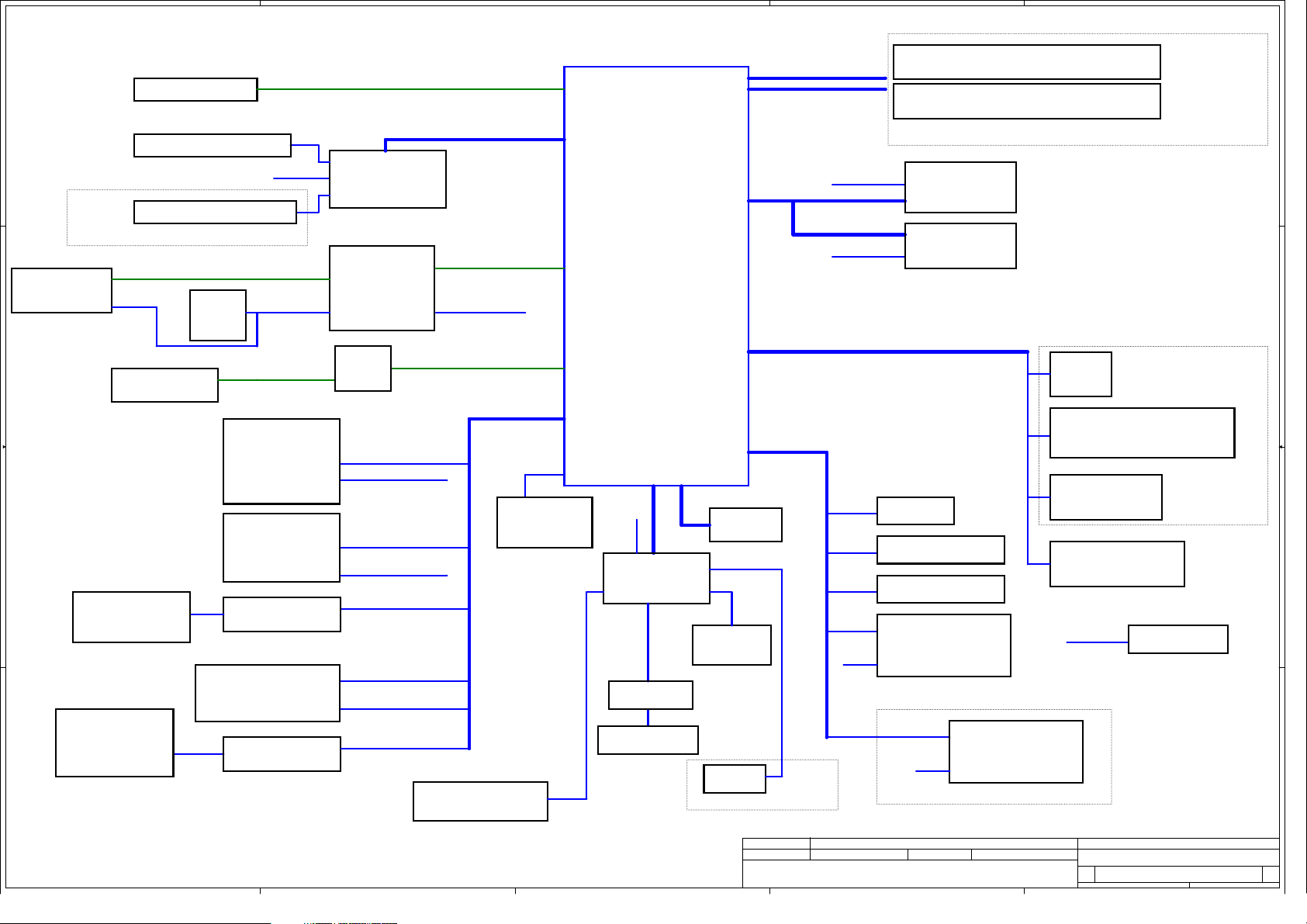

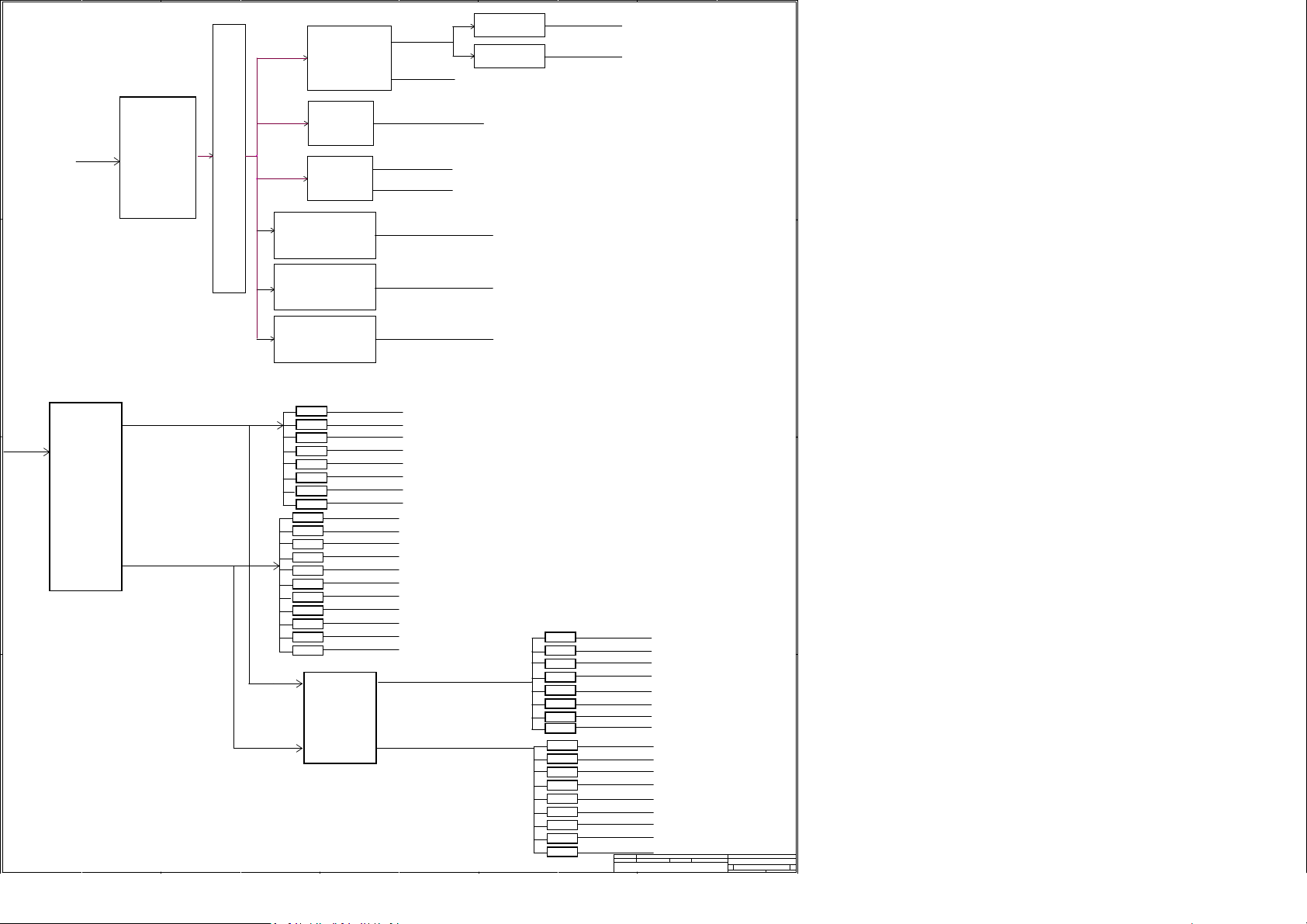

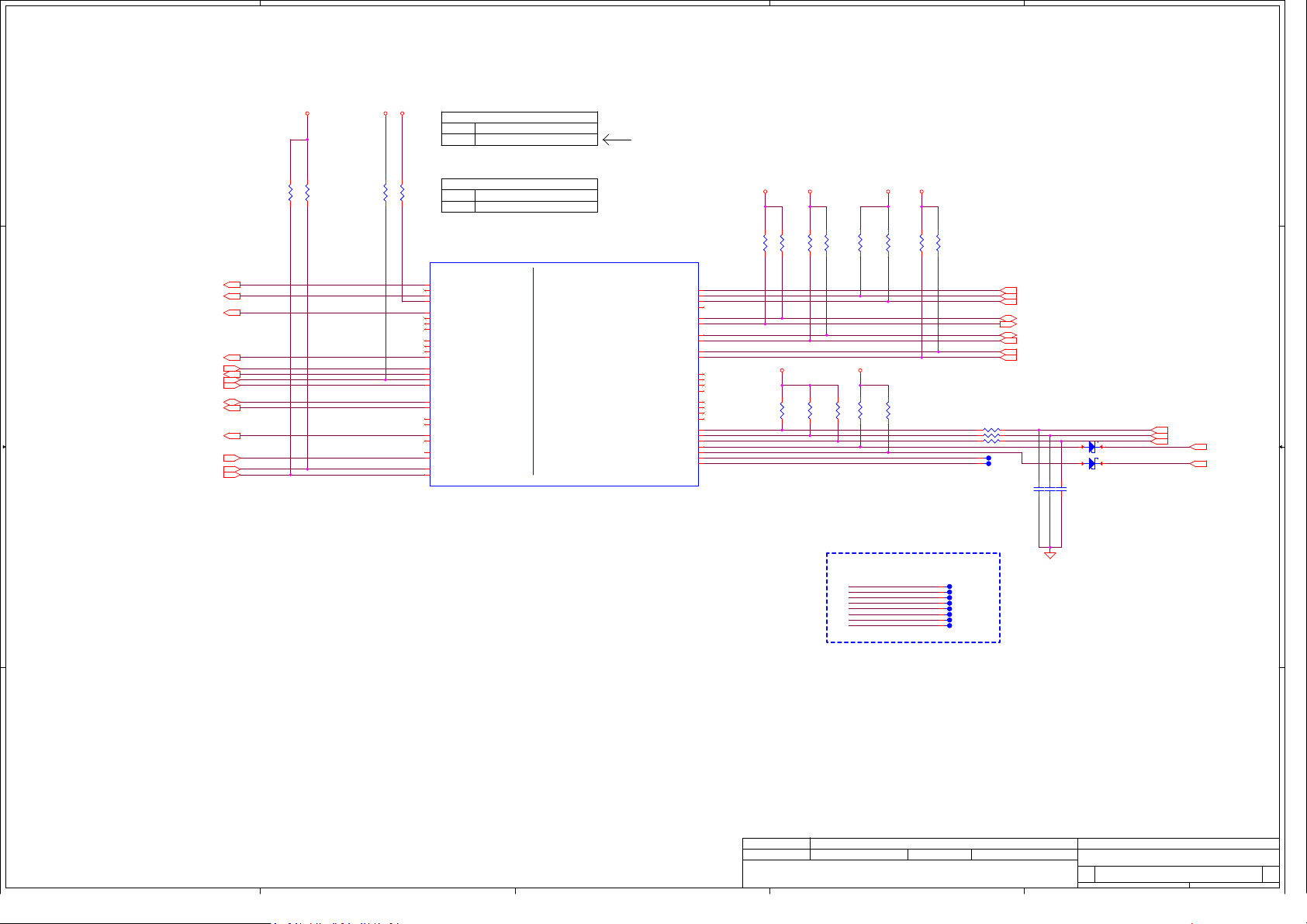

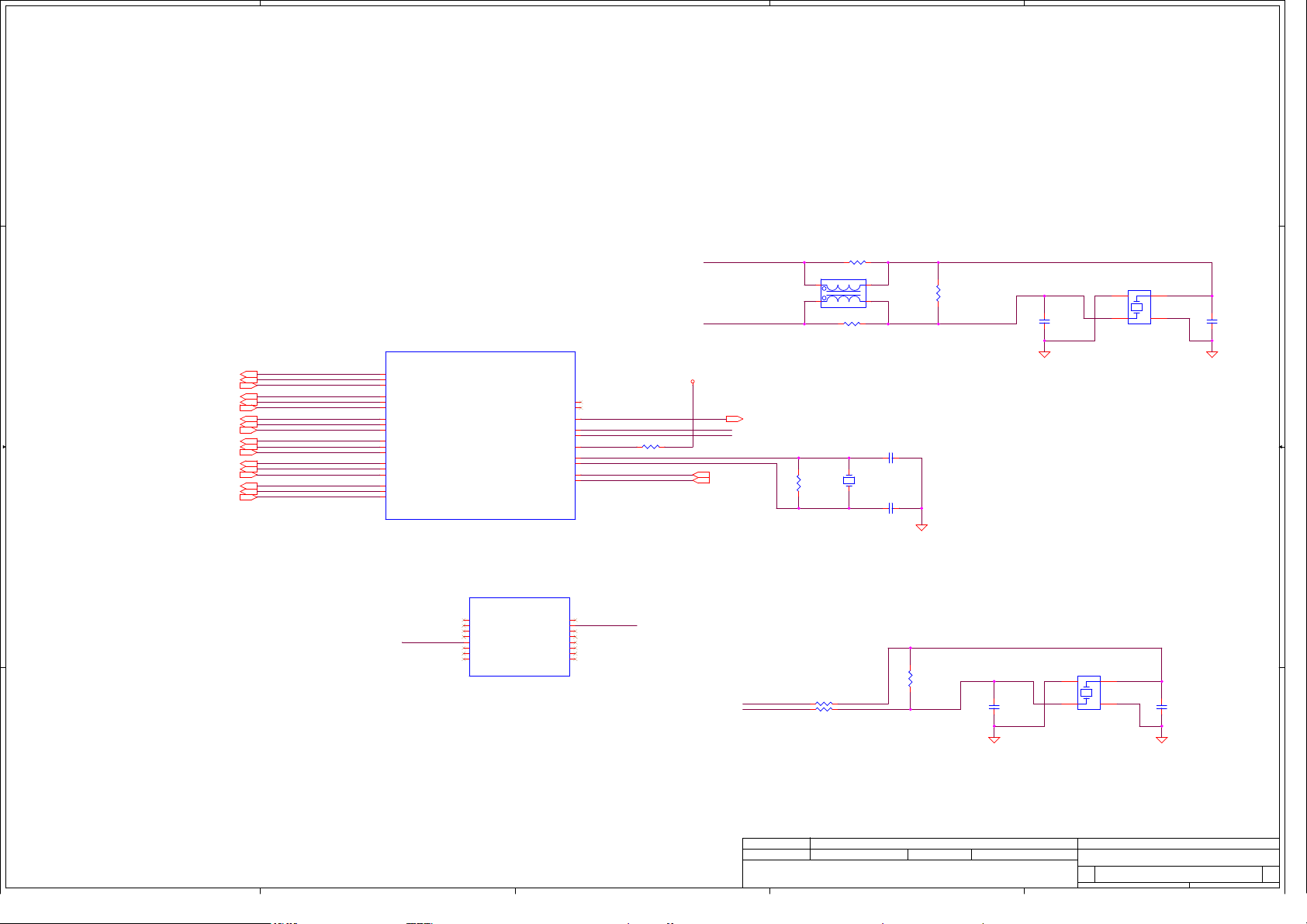

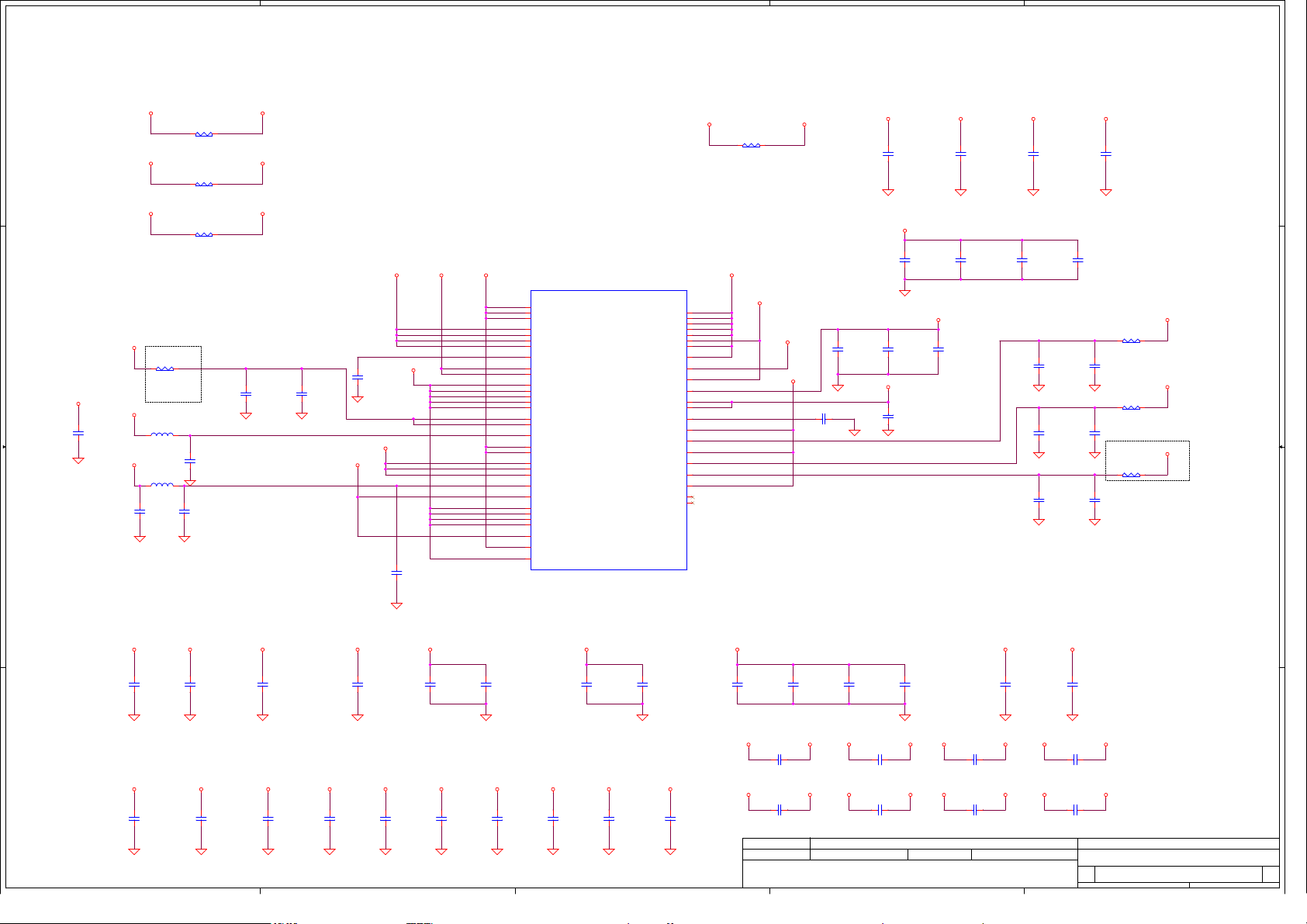

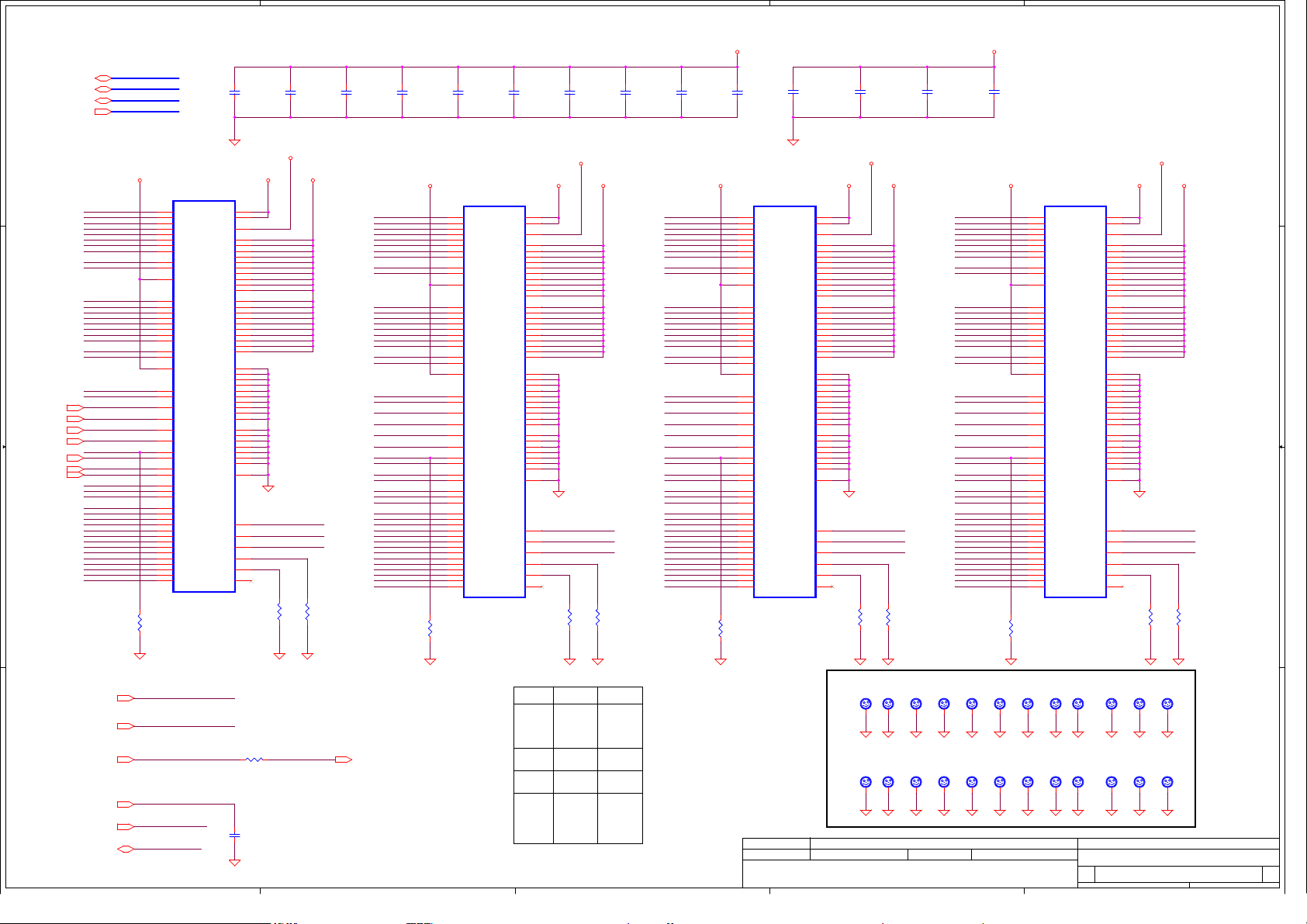

STORM 3 Block-Diagram

Two Channel

eDP Conn.

D D

P.26

2-Ch. SPK Conn.

4 Lane

P.39

DMIC

Audio Codec

P.35

eDP

HDA

USB2.0

USB3.0

Combo Jack Conn.

Sub/B

4 Lane TBT

Type C Conn.

C C

P.50

USB 2.0

HDMI Conn.

P.29

PD

P.51

USB 2.0

4 Lane

Intel

Alpine Ridge

Mux

P.28

4 Lane

PCIEx2

P.47

DDI1

Intel Kabylake

RU/U-Processor

P.4

I2C

DDI2

USB2.0

PCI-E

(A) DDR4 memory down 2400MHz

(B) DDR4 memory down 2400MHz

P.22

P.24

Maximum 16GB

USB 3.0 Conn

AOU5

P.31

USB 3.0 Conn.

P.31

ALS

Sub board

WLAN & BT

M.2 Conn.

PCIEx1

USB 2.0(BT)

P.32

(WLAN)

SPI

LPC

SPI

BIOS ROM

WWAN

P.32

P.52

PCIEx1

USB 2.0

PCIEx1

B B

Mini RJ45

P.52

M.2 Conn.

Intel LAN

16M

P.21

I2C

EC

P.53

Int.KBD

M.2 Conn.

SSD [M.2 2280/2242]

Micro SD

Card Reader

A A

Slot Conn.

P.33

Card Reader

SATA/PCIEx1

P.30

P.33

PCIEx3

PCIEx1

Click Pad

Track Point

P.43

P.42

Accelerometer(2)

P.41

5

4

3

USB2.0

FPR

TPM

P.45

P.42

LID

Sub/B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DMIC

2014/11/04 2016/12/31

2014/11/04 2016/12/31

2014/11/04 2016/12/31

P.34

Touch Panel

Smart Card

P.26

P.34

P.26

Camera & DMIC

DMIC

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

IR Camera

Accelerometer & Gyro

eCompass

Accelerometer(1)

P.41

SMBUS

P.27

NFC

Option

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F421P

LA-F421P

LA-F421P

Date: Sheet

Date: Sheet

Date: Sheet

1

P.43

1.0

1.0

1.0

of

of

of

2 73Monday, October 23, 2017

2 73Monday, October 23, 2017

2 73Monday, October 23, 2017

5

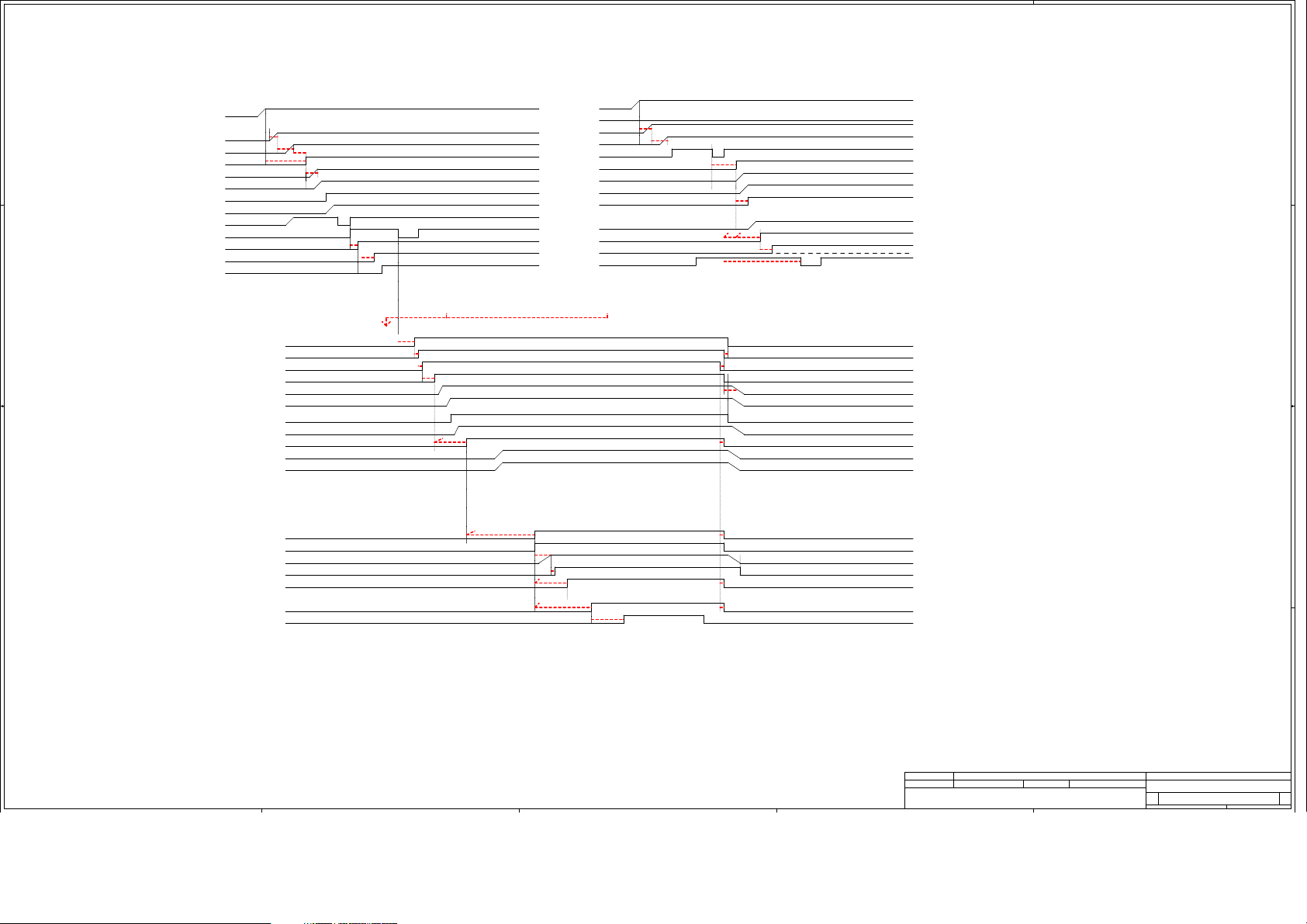

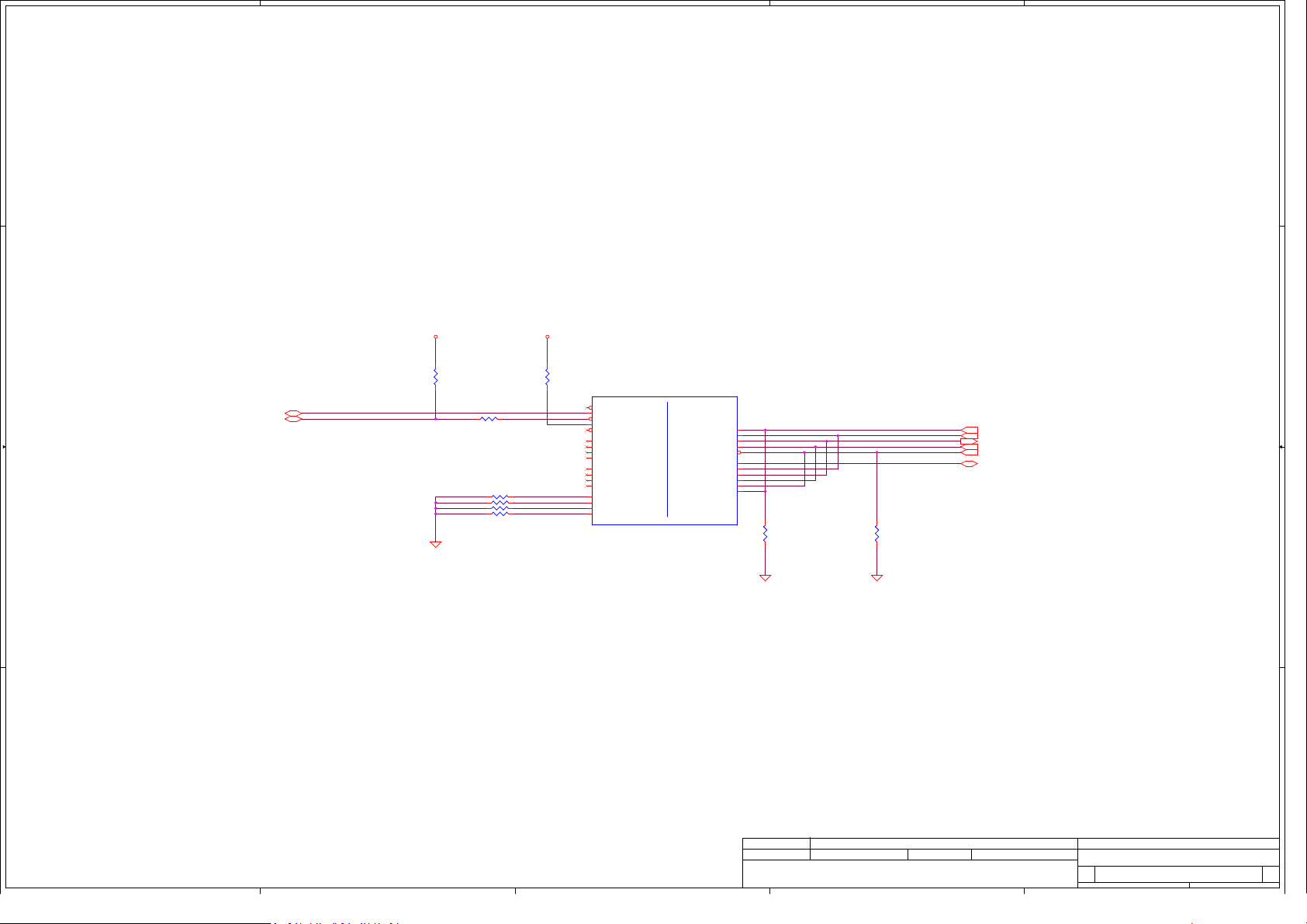

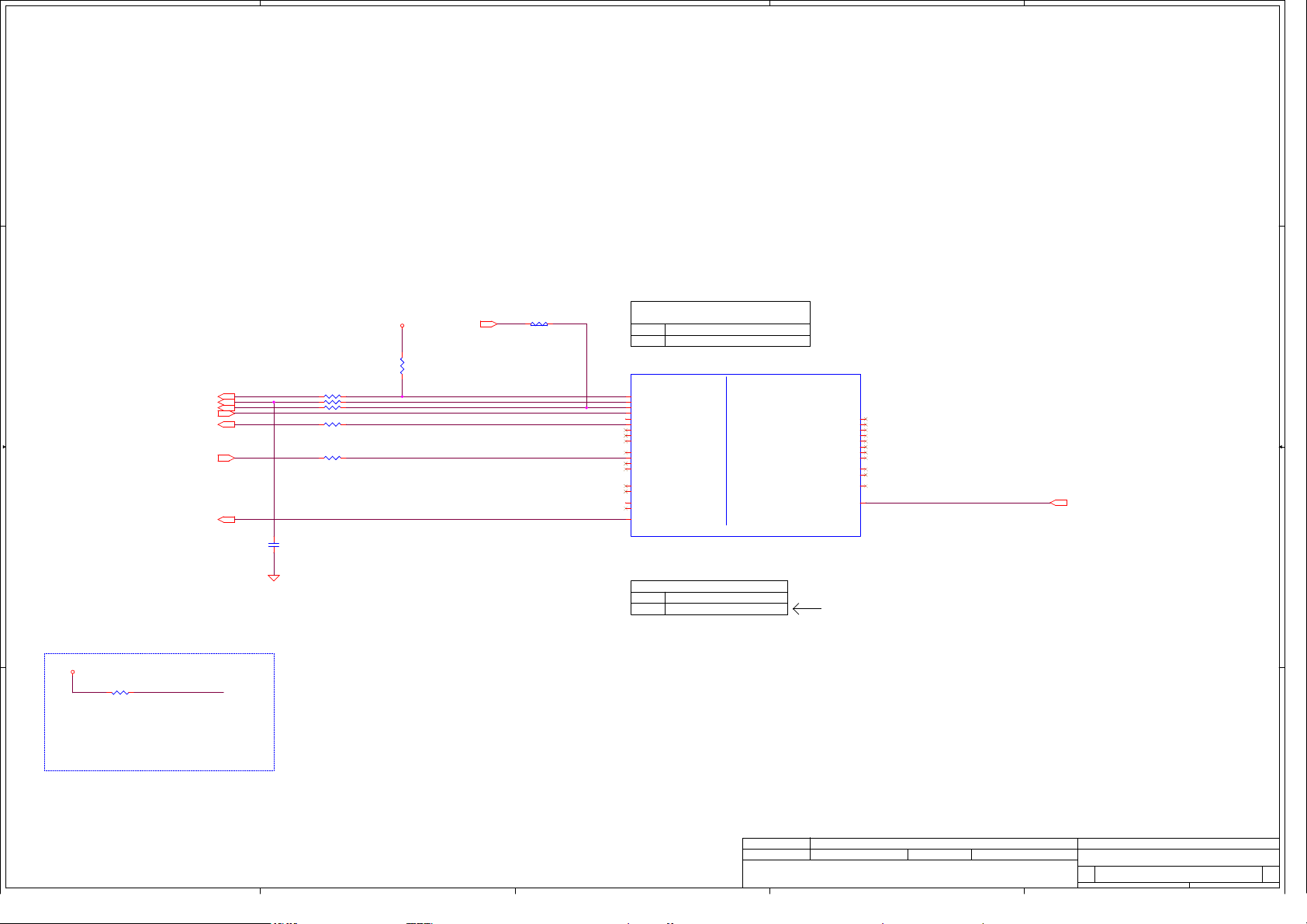

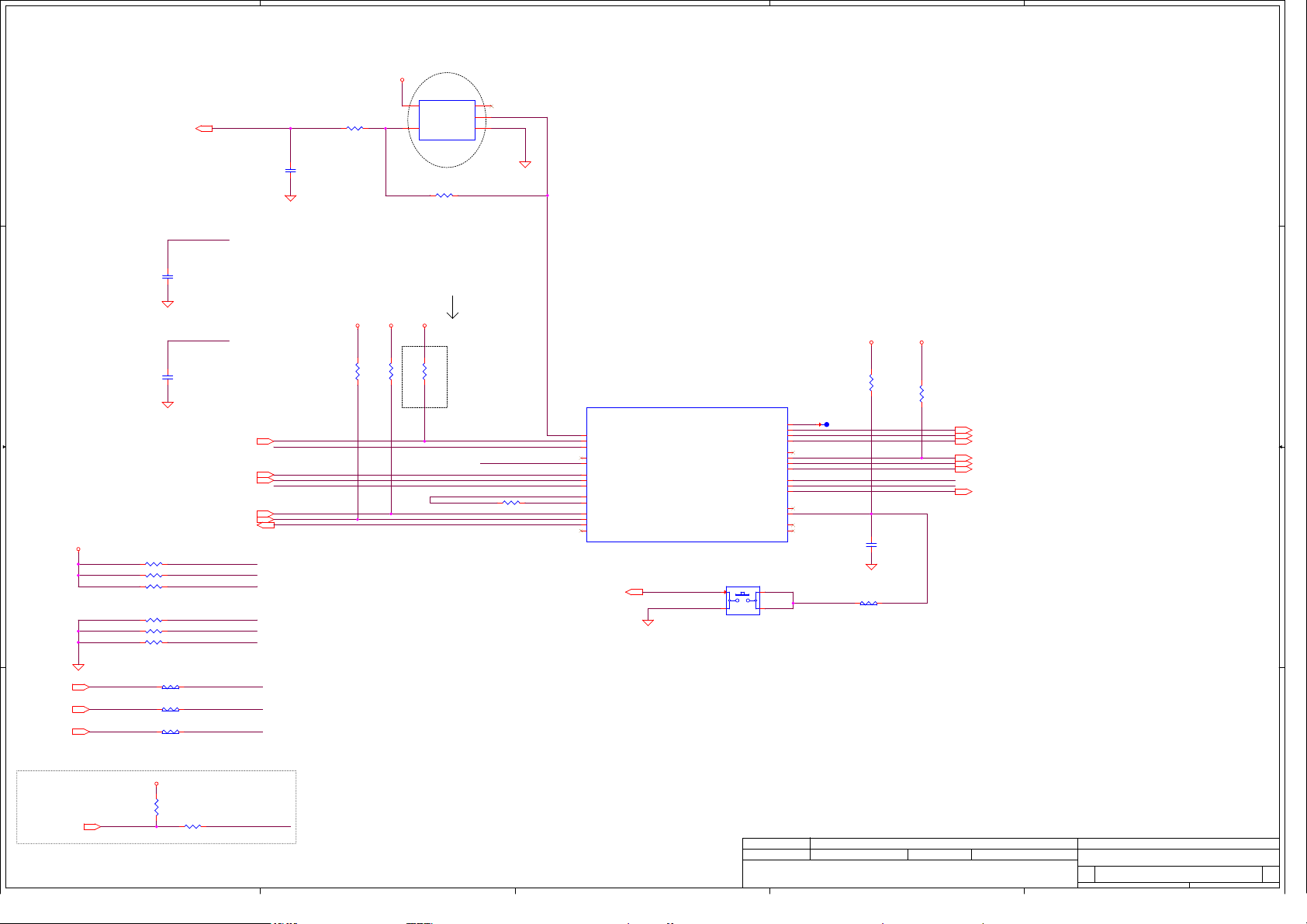

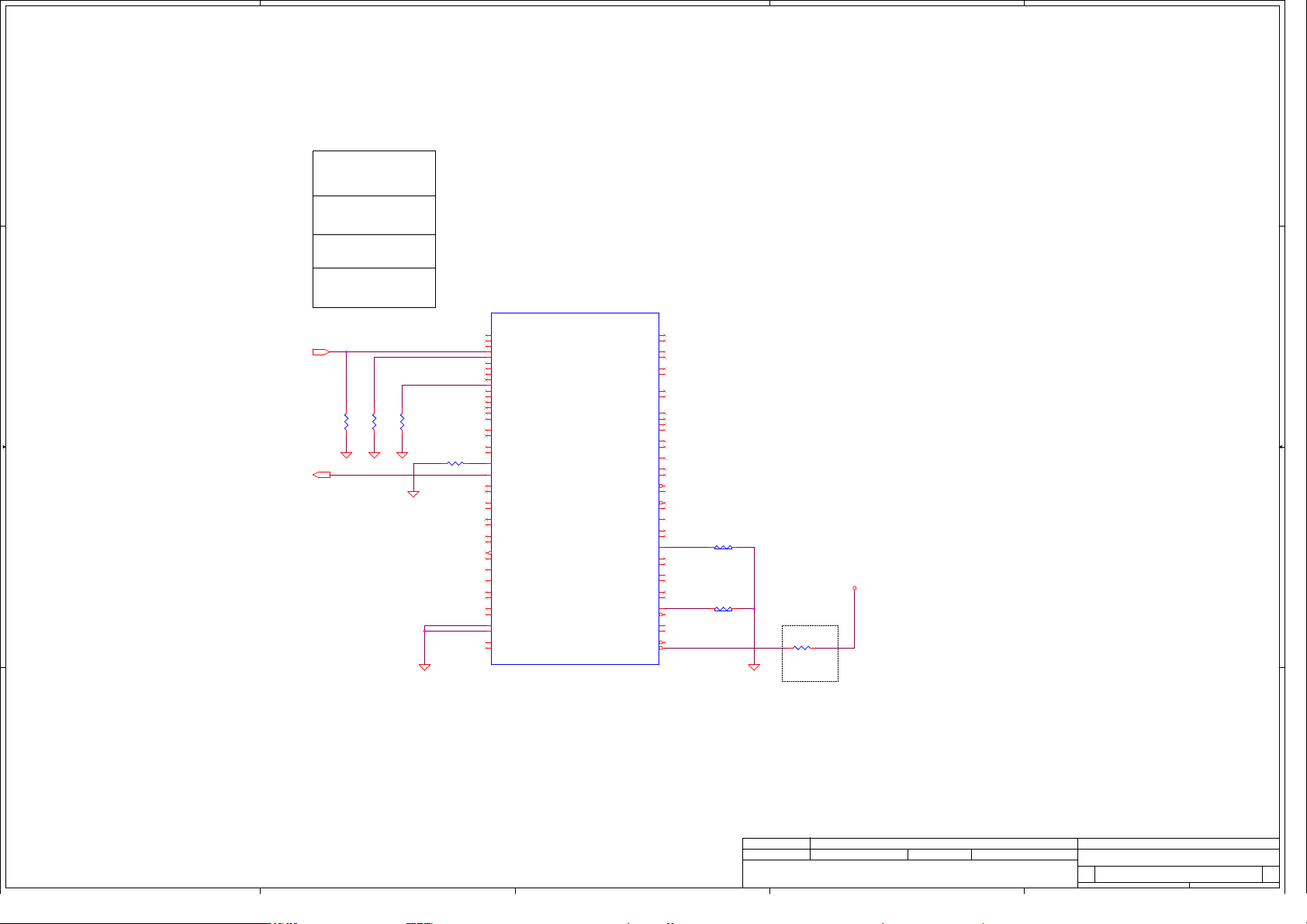

[Storm3 PWR Sequence_KBL-RU_DDR4_Non-Deep Sx]

4

3

2

1

D D

C C

B B

[AC Mode]

AC_IN

VINT12

VCC3SW

EN_3V

VCC3M/VCC5M

VCC1R0_SUS

SUS_ON1

VCC1R8_PRIM

-PWRSWITCH

-PWRSW_EC_R

-RSMRST

-SUSWARN

AC_PRESENT

moniter AC_IN (51_ON)

Moniter ON/OFFBTN# rising edge

20ms

-PCH_SLP_S5

-PCH_SLP_S4

-PCH_SLP_S3

A_ON

+VCC2R5A

+VCC1R2A

DDR_PG_CTRL

+VCC0R6B

B_ON After PM_SLP_S3# moniter SYSON rising edge.

VCC5B

VCC3B

EC_VCCST_PG

VR_ON

VCCCPUCORE

VGATE

BPWRG After VCCST_PG_EC assertion

-PLTRST

Montier PBTN_OUT# falling edge.

T=20ms

T=20ms

immediately, VCCST_PG_PWR & VCCST_PG_EC risign edge

[DC Mode]

BAT-PWR12

AC_PRESENT

VINT12

VCC3SW

-PWRSWITCH

SUS_ON2 Moniter ON/OFFBTN#

VCC3M/VCC5M

VCC1R0_SUS

SUS_ON1

VCC1R8_PRIM

-RSMRST

-SUSWARN

-PWRSW_EC_R

After SUSP# risign edge

Vboot

T=10ms

After VCCST_PG_EC rising edgePCH_PWROK

T=99ms

After CPUPWRGD/PCH_PWRGD/SYS_PWROK assertion

T=10ms

Moniter ON/OFFBTN# and EN_3/5V both of risgin edge

T=10ms

T=110ms

20ms

immediately, After PM_SLP_S4# falling edge

immediately, After PM_SLP_S3# falling edge

immediately, After SUSP# falling edge

immediately, After SUSP# falling edge

immediately, After SUSP# falling edge

Moniter ON/OFFBTN# rising edge

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

2016/03/21 2017/03/01

2016/03/21 2017/03/01

2016/03/21 2017/03/01

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Sequence

Power Sequence

Power Sequence

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

D

D

D

LA-F421P

LA-F421P

LA-F421P

Date: Sheet

Date: Sheet

Date: Sheet

1

3 73Monday, October 23, 2017

3 73Monday, October 23, 2017

3 73Monday, October 23, 2017

of

of

of

1.0

1.0

1.0

5

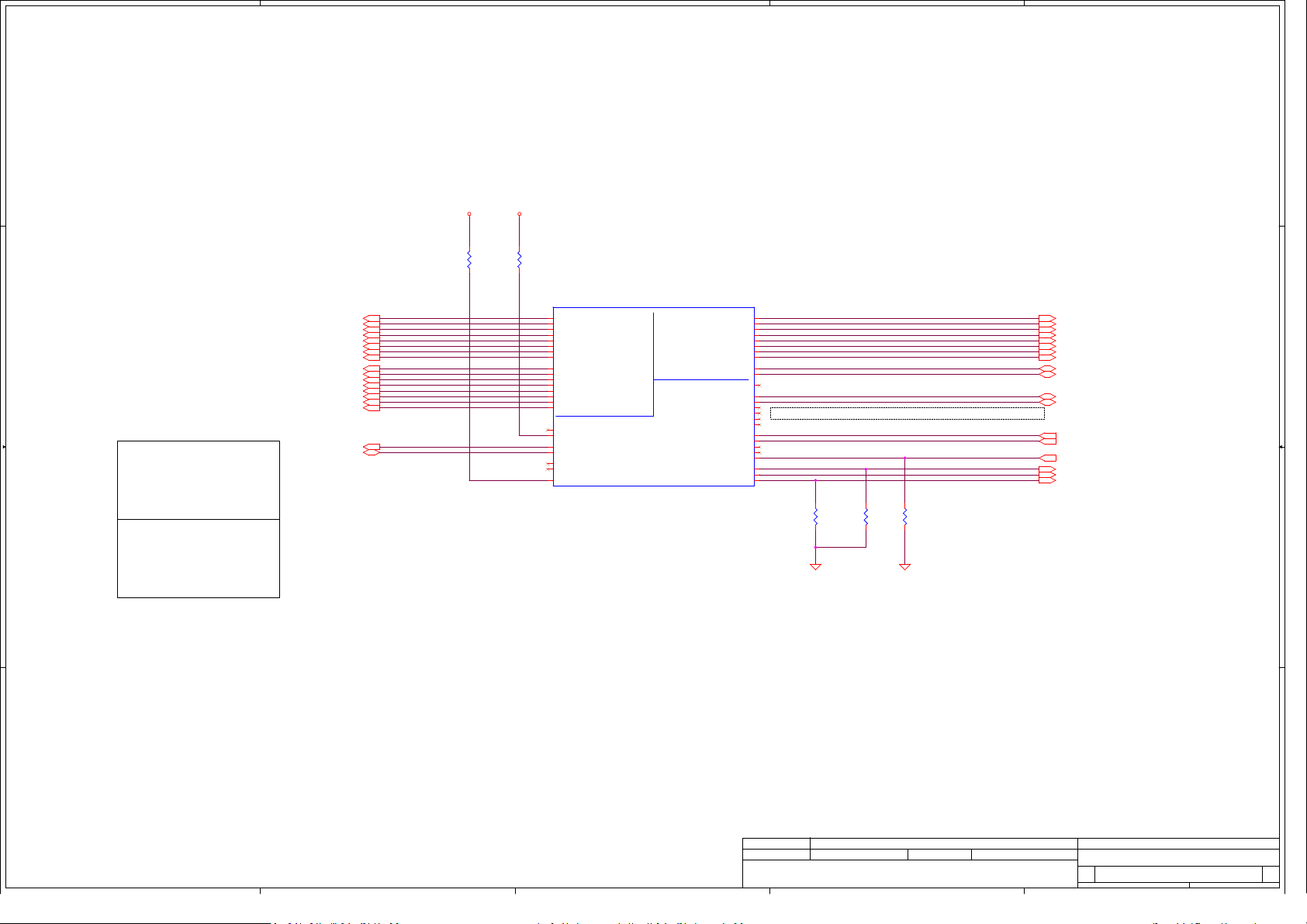

D D

4

3

2

1

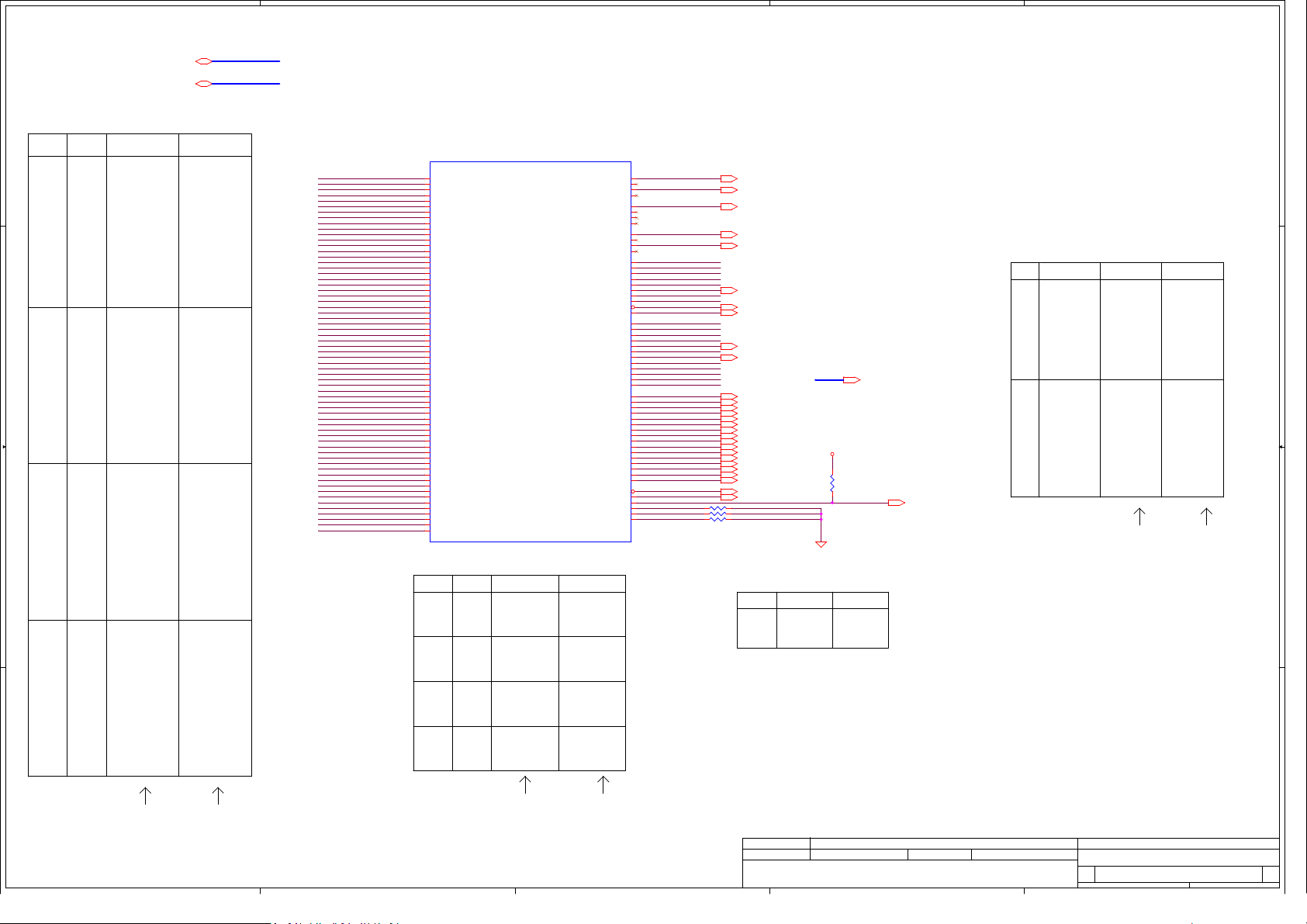

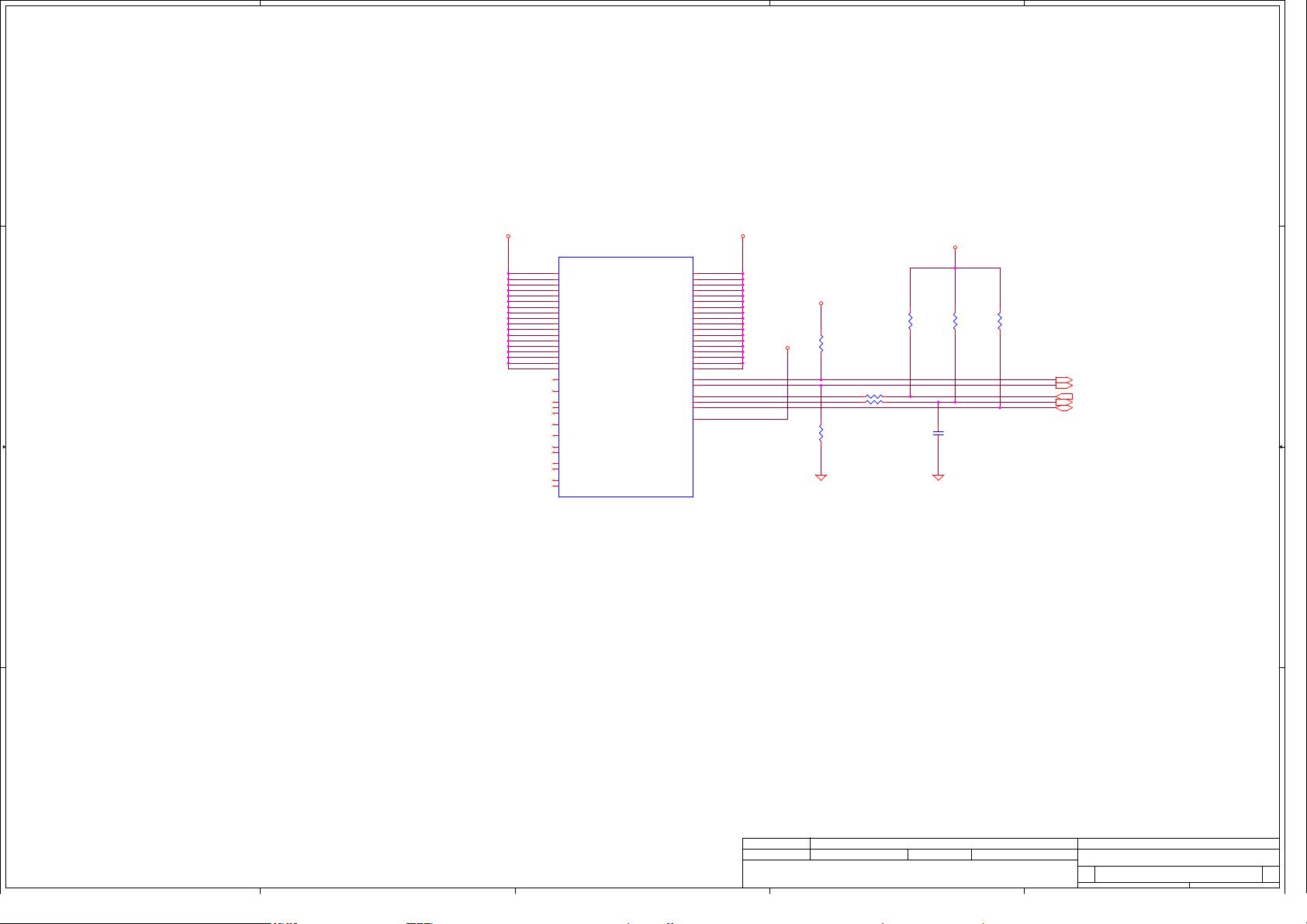

VCCCPUIO

DDIP1_0N[47]

DDIP1_0P[47]

DDIP1_1N[47]

C C

DDIP1_1P[47]

DDIP1_2N[47]

DDIP1_2P[47]

DDIP1_3N[47]

DDIP1_3P[47]

DDIP2_0N[28]

DDIP2_0P[28]

DDIP2_1N[28]

DDIP2_1P[28]

DDIP2_2N[28]

DDIP2_2P[28]

DDIP2_3N[28]

DDIP2_3P[28]

DDIP1_0N

DDIP1_0P

DDIP1_1N

DDIP1_1P

DDIP1_2N

DDIP1_2P

DDIP1_3N

DDIP1_3P

DDIP2_0N

DDIP2_0P

DDIP2_1N

DDIP2_1P

DDIP2_2N

DDIP2_2P

DDIP2_3N

DDIP2_3P

TABLE : Functional Strap

DDPB_CTRLDATA

DDIP2_CTRLCLK[28]

DDIP2_CTRLDATA[28]

DDIP2_CTRLCLK

DDIP2_CTRLDATA

HIGH Port B is detected.

LOW Port B is not detected.

DDPC_CTRLDATA

B B

HIGH Port C is detected.

R5

24.9_0201_1%

1 2

EDP_COMP

VCC3B

1 2

R9357

2.2K_0201_5%

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

U58A

@

KBL-RU_BGA1356

SKL-U

DDI

DISPLAY SIDEBANDS

1 OF 20

EDP

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

R433

100K_0201_5%

1 2

R138

100K_0201_5%

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

DDIP1_AUXN

DDIP1_AUXP

EDP_TXN0 [26]

EDP_TXP0 [26]

EDP_TXN1 [26]

EDP_TXP1 [26]

EDP_TXN2 [26]

EDP_TXP2 [26]

EDP_TXN3 [26]

EDP_TXP3 [26]

EDP_AUXN [26]

EDP_AUXP [26]

DDIP1_AUXN [47]

DDIP1_AUXP [47]

FVT_C_EC010

DDIP1_HPD

DDIP2_HPD

R8

100K_0201_5%

1 2

1 2

DDIP1_HPD [47]

DDIP2_HPD [28]

EDP_HPD [26]

VGA_BLON [53]

PANEL_BKLT_CTRL [26]

PANEL_POWER_ON [26]

LOW Port C is not detected.

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/11/04 2016/12/31

2014/11/04 2016/12/31

2014/11/04 2016/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CPU(1/16) : DDI/EDP

CPU(1/16) : DDI/EDP

CPU(1/16) : DDI/EDP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F421P

LA-F421P

LA-F421P

Date: Sheet

Date: Sheet

Date: Sheet

1

of

of

of

4 73Monday, October 23, 2017

4 73Monday, October 23, 2017

4 73Monday, October 23, 2017

1.0

1.0

1.0

5

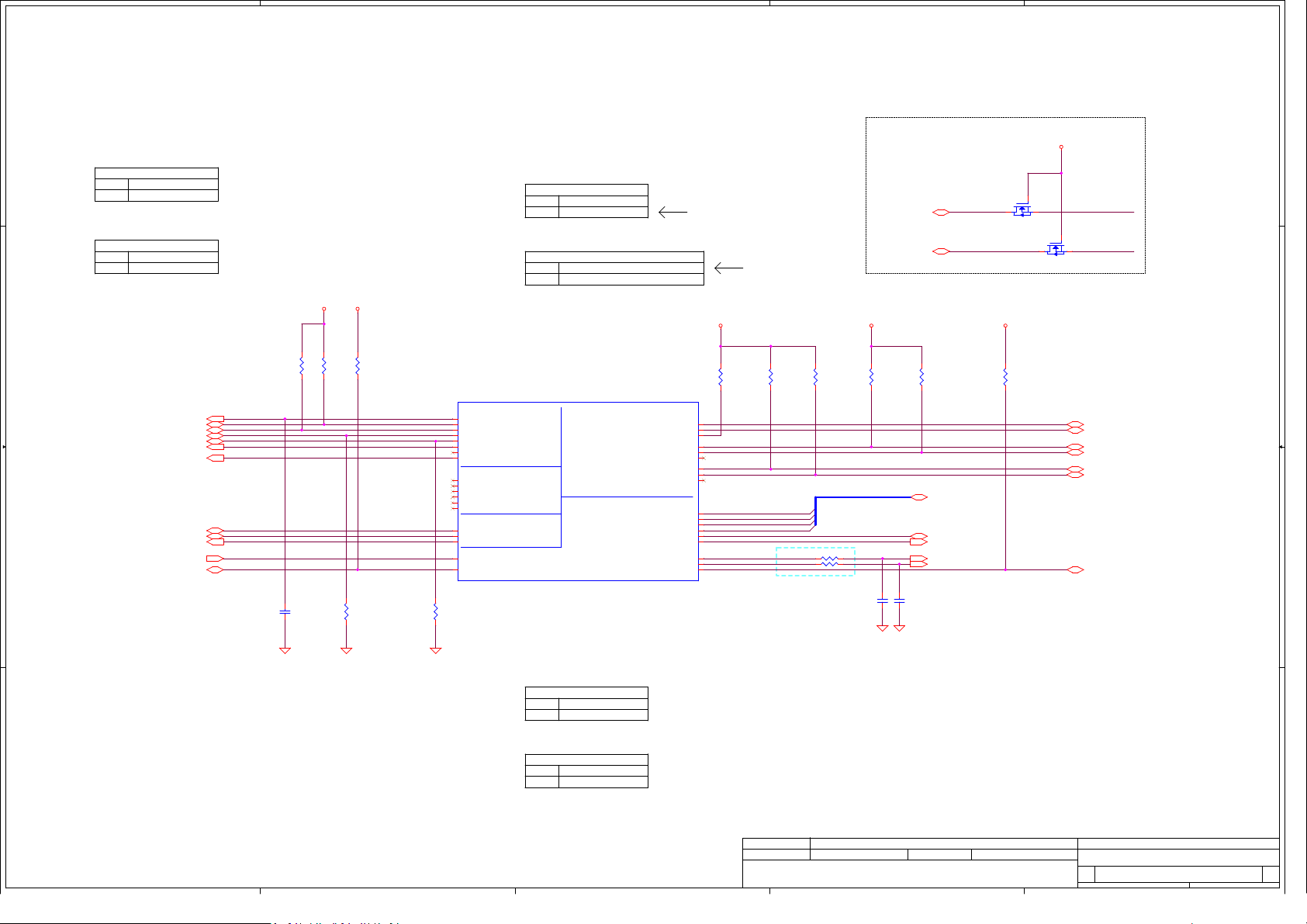

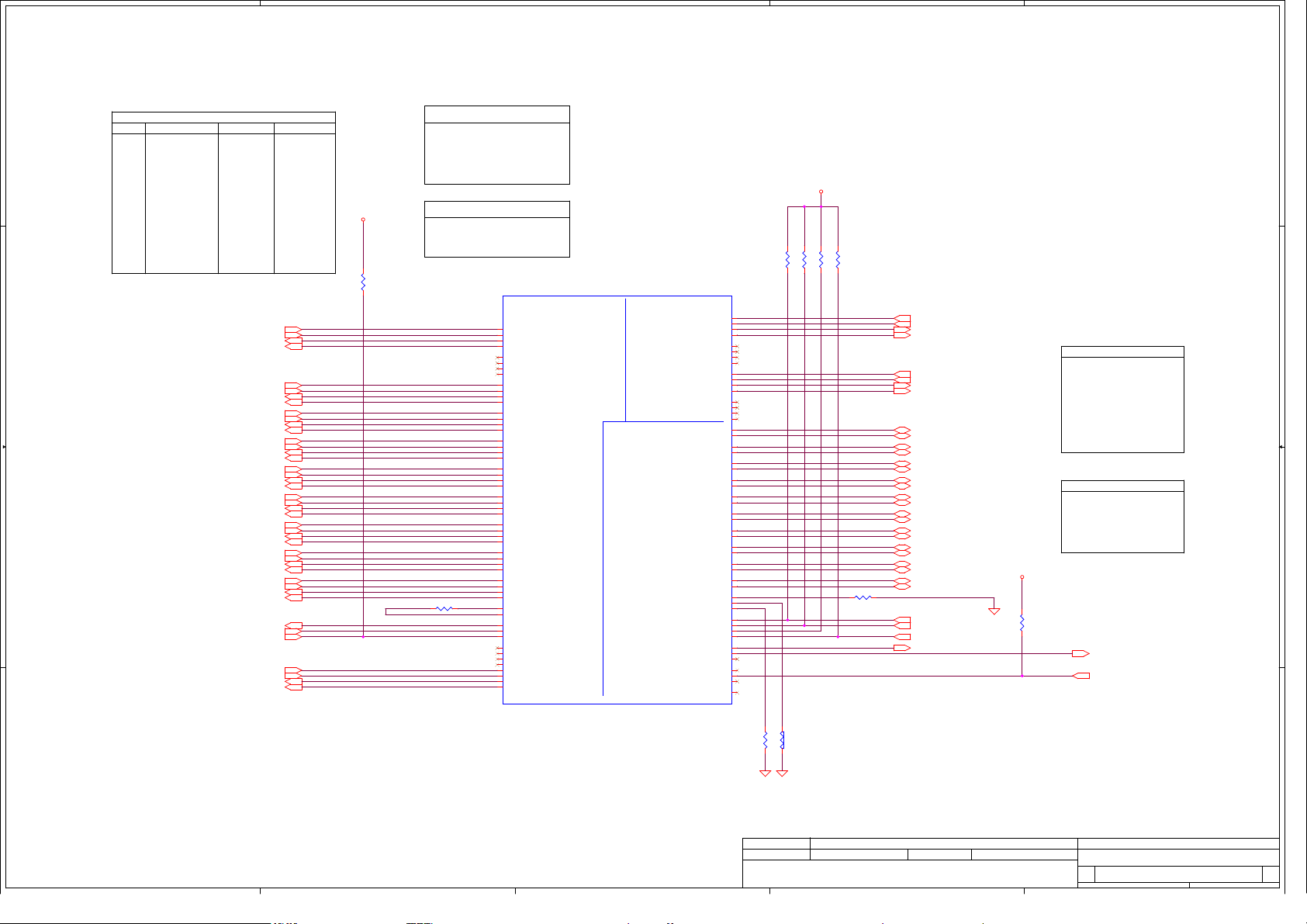

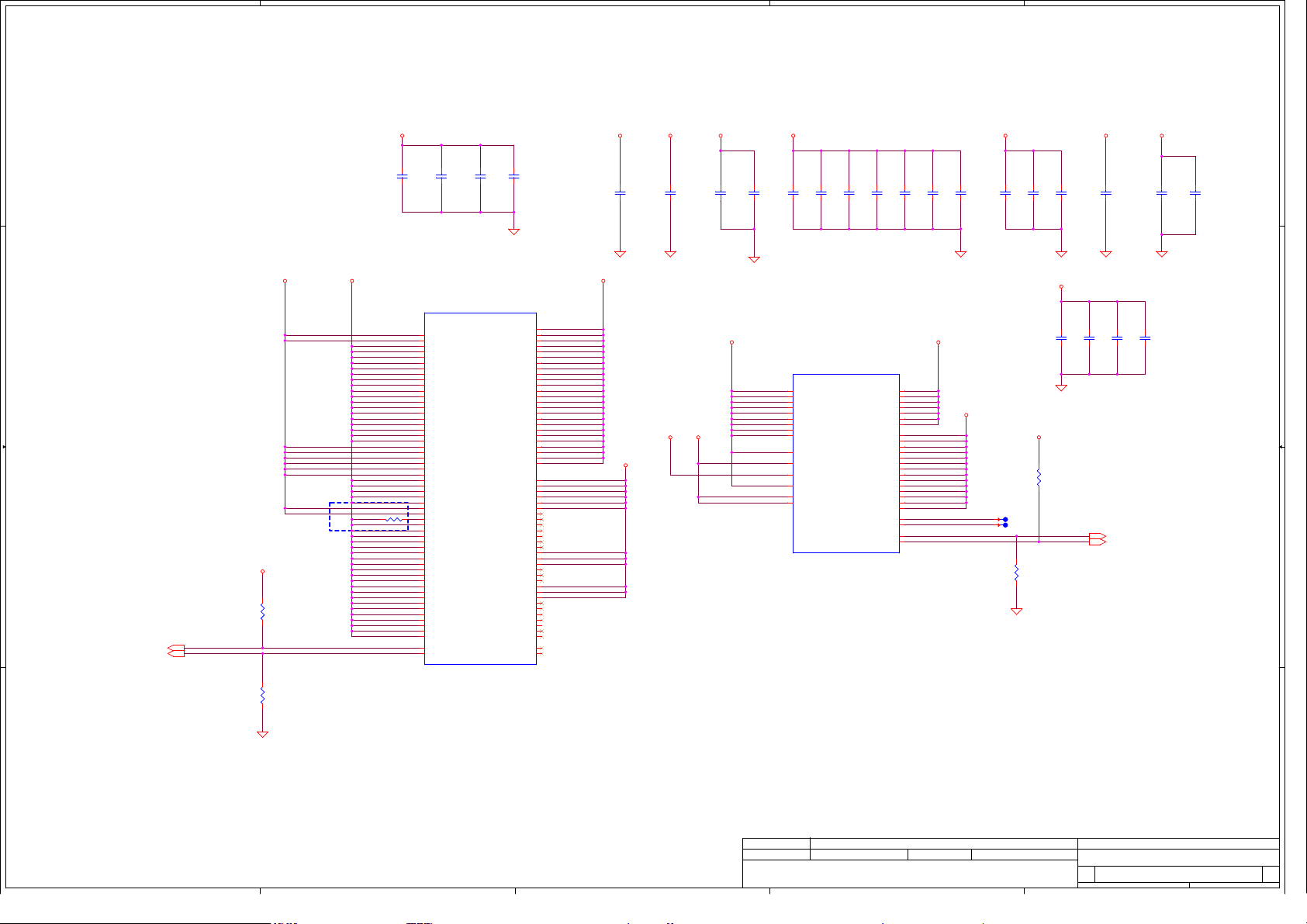

Storm3 Power tree

4

TPS51285B-1RUKR

TI

3

VCC5M / 7A

VCC3M / 7A

RT8061AZQW

Richtek

RT8061AZQW

Richtek

2

VCC2R5A / 0.8A

VCC1R8_SUS / 0.8A

1

D D

PU1

VINT20

C C

Charger (BQ25700)

VINT12

VCC5M

VINT12

PU41

B B

VCC3M

TPS51362RVER

TI

Converter

RT8207PGQW

Richtek

NCP81218MNTXG

+

NCP302045MNTWG

Dr-MOS

On-semi

NCP81218MNTXG

+

NCP302045MNTWG

Dr-MOS

On-semi

NCP81218MNTXG

+

NCP302035MNTWG

Dr-MOS

On-semi

VCCST

U143

VCC2R5A

PU151

VCC1R2A

PU118

VCC1R8_PRIM

PU145

USB_PWR_S2

U53

USB_PWR_S1

U88

VCC5M_BUTTON

R9570

VCC5M_PD

J9237

VCC3_SUS

PU154

VCC3M_PEN

F31

VCC3M_SENS_CN

F34

VCC3M_IR

F39

VCC3M_KEY_CONN

F25

VCC3M_BUTTON

R9309

VCC3M_PCH

R2485

VCC3_TBT

R9406

VCC3M_PD

RT9369

VCC3WLAN

U19

VCC3LAN

U153

U55

A A

5

4

VCC1R0_SUS_P / 7.12A

VCC1R2A / 6.4A

VCC0R6B / 0.8A

VCCCPUCORE

U22: 21A

U42: 42A

VCCGFXCORE_I / 18A

VCCSA / 4A

VCC5B

VCC3B

3

U110

F40

F35

F23

F4

F15

R2031

R2015

R2029

R2463

J9240

F24

F17

F8

F41

U9

R2472

2

VCC5B_HDMI

VCC5B_IR

VCC5B_CN

VCC5_TP

VCC5B_F4

FUSEVCC5B

VCC5B_CODEC

VCC5BA

VCC3B_PS8337B

VCC3WAN

VCC3B_TOUCH_CN

FUSEVCC3B

FUSEVCC3FP

VCC3B_IR

VCC3B_CODEC

VCC3P

VCC3B_RTS5236S

Security Classification

Security Classification

Security Classification

2015/06/09 2016/12/31

2015/06/09 2016/12/31

2015/06/09 2016/12/31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power MAP

Power MAP

Power MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F483P

LA-F483P

LA-F483P

Date: Sheet

Date: Sheet

Date: Sheet

Monday, October 23, 2017

Monday, October 23, 2017

Monday, October 23, 2017

1

of

4

of

4

of

4

0.1

0.1

0.1

44

44

44

5

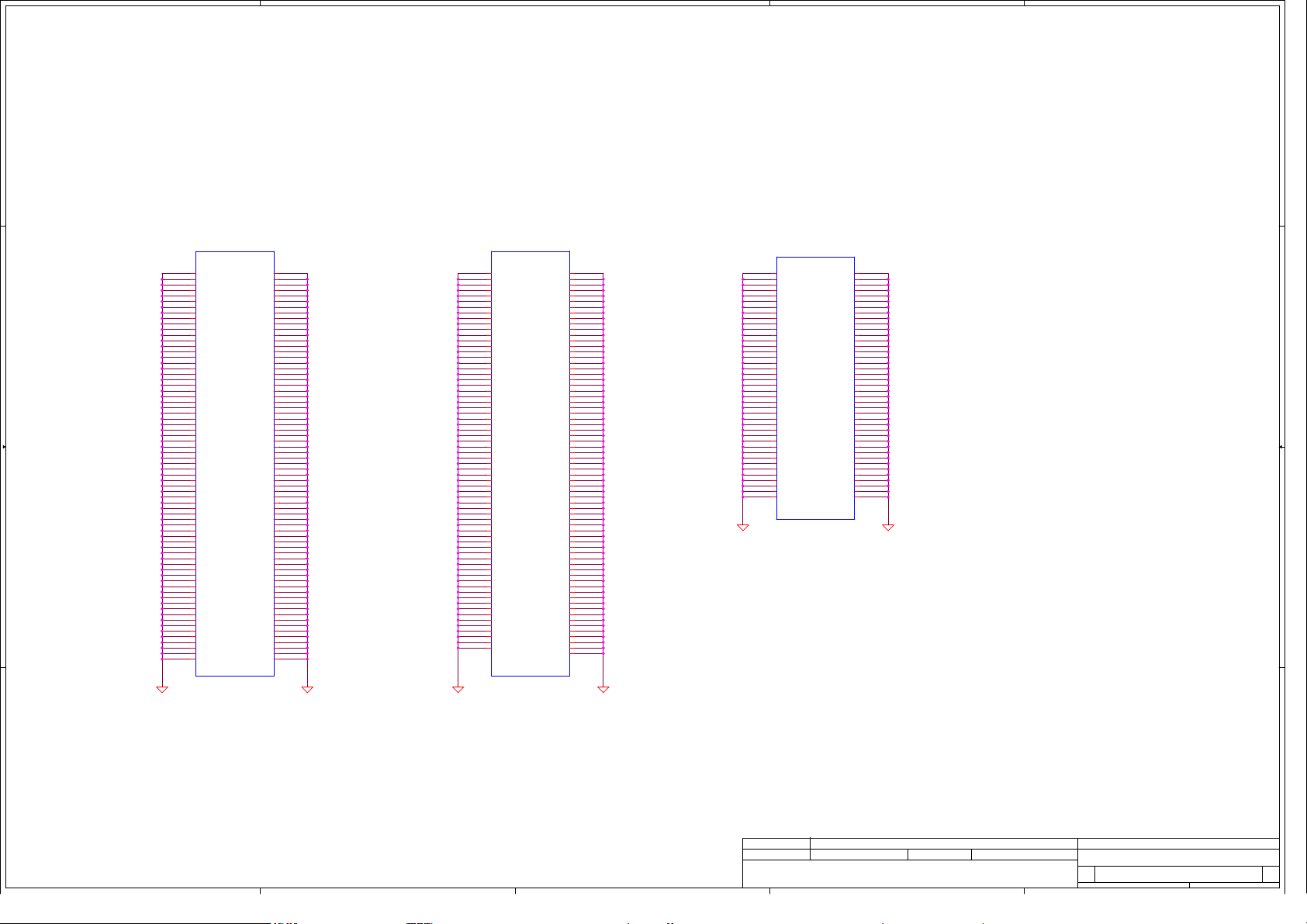

DDR_A_D[63:0][6,22]

DDR_B_D[63:0][6,24]

D D

TABLE

4

3

2

1

Pin Interleave Non-Interleave

U58B

TABLE

AL71

AL68

AN68

AN69

AL70

AL69

AN70

AN71

AR70

AR68

AU71

AU68

AR71

AR69

AU70

AU69

BB65

AW65

AW63

AY63

BA65

AY65

BA63

BB63

BA61

AW61

BB59

AW59

BB61

AY61

BA59

AY59

AY39

AW39

AY37

AW37

BB39

BA39

BA37

BB37

AY35

AW35

AY33

AW33

BB35

BA35

BA33

BB33

AY31

AW31

AY29

AW29

BB31

BA31

BA29

BB29

AY27

AW27

AY25

AW25

BB27

BA27

BA25

BB25

Block 0

Block 2

Block 4

Block 6

@

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[16]/DDR0_DQ[32]

DDR0_DQ[17]/DDR0_DQ[33]

DDR0_DQ[18]/DDR0_DQ[34]

DDR0_DQ[19]/DDR0_DQ[35]

DDR0_DQ[20]/DDR0_DQ[36]

DDR0_DQ[21]/DDR0_DQ[37]

DDR0_DQ[22]/DDR0_DQ[38]

DDR0_DQ[23]/DDR0_DQ[39]

DDR0_DQ[24]/DDR0_DQ[40]

DDR0_DQ[25]/DDR0_DQ[41]

DDR0_DQ[26]/DDR0_DQ[42]

DDR0_DQ[27]/DDR0_DQ[43]

DDR0_DQ[28]/DDR0_DQ[44]

DDR0_DQ[29]/DDR0_DQ[45]

DDR0_DQ[30]/DDR0_DQ[46]

DDR0_DQ[31]/DDR0_DQ[47]

DDR0_DQ[32]/DDR1_DQ[0]

DDR0_DQ[33]/DDR1_DQ[1]

DDR0_DQ[34]/DDR1_DQ[2]

DDR0_DQ[35]/DDR1_DQ[3]

DDR0_DQ[36]/DDR1_DQ[4]

DDR0_DQ[37]/DDR1_DQ[5]

DDR0_DQ[38]/DDR1_DQ[6]

DDR0_DQ[39]/DDR1_DQ[7]

DDR0_DQ[40]/DDR1_DQ[8]

DDR0_DQ[41]/DDR1_DQ[9]

DDR0_DQ[42]/DDR1_DQ[10]

DDR0_DQ[43]/DDR1_DQ[11]

DDR0_DQ[44]/DDR1_DQ[12]

DDR0_DQ[45]/DDR1_DQ[13]

DDR0_DQ[46]/DDR1_DQ[14]

DDR0_DQ[47]/DDR1_DQ[15]

DDR0_DQ[48]/DDR1_DQ[32]

DDR0_DQ[49]/DDR1_DQ[33]

DDR0_DQ[50]/DDR1_DQ[34]

DDR0_DQ[51]/DDR1_DQ[35]

DDR0_DQ[52]/DDR1_DQ[36]

DDR0_DQ[53]/DDR1_DQ[37]

DDR0_DQ[54]/DDR1_DQ[38]

DDR0_DQ[55]/DDR1_DQ[39]

DDR0_DQ[56]/DDR1_DQ[40]

DDR0_DQ[57]/DDR1_DQ[41]

DDR0_DQ[58]/DDR1_DQ[42]

DDR0_DQ[59]/DDR1_DQ[43]

DDR0_DQ[60]/DDR1_DQ[44]

DDR0_DQ[61]/DDR1_DQ[45]

DDR0_DQ[62]/DDR1_DQ[46]

DDR0_DQ[63]/DDR1_DQ[47]

KBL-RU_BGA1356

Pin Interleave Non-Interleave

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

DDR0_DQ[0]

AL71

DDR0_DQ[1]

AL68

DDR0_DQ[2]

AN68

DDR0_DQ[3]

AN69

DDR0_DQ[4]

AL70

DDR0_DQ[5]

AL69

DDR0_DQ[6]

AN70

DDR0_DQ[7]

AN71

DDR0_DQ[8]

AR70

DDR0_DQ[9]

AR68

Block 0

C C

Block 2

Block 4

B B

Block 6

A A

AU71

AU68

AR71

AR69

AU70

AU69

BB65

AW65

AW63

AY63

BA65

AY65

BA63

BB63

BA61

AW61

BB59

AW59

BB61

AY61

BA59

AY59

AY39

AW39

AY37

AW37

BB39

BA39

BA37

BB37

AY35

AW35

AY33

AW33

BB35

BA35

BA33

BB33

AY31

AW31

AY29

AW29

BB31

BA31

BA29

BB29

AY27

AW27

AY25

AW25

BB27

BA27

BA25

BB25

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[16]

DDR0_DQ[17]

DDR0_DQ[18]

DDR0_DQ[19]

DDR0_DQ[20]

DDR0_DQ[21]

DDR0_DQ[22]

DDR0_DQ[23]

DDR0_DQ[24]

DDR0_DQ[25]

DDR0_DQ[26]

DDR0_DQ[27]

DDR0_DQ[28]

DDR0_DQ[29]

DDR0_DQ[30]

DDR0_DQ[31]

DDR0_DQ[32]

DDR0_DQ[33]

DDR0_DQ[34]

DDR0_DQ[35]

DDR0_DQ[36]

DDR0_DQ[37]

DDR0_DQ[38]

DDR0_DQ[39]

DDR0_DQ[40]

DDR0_DQ[41]

DDR0_DQ[42]

DDR0_DQ[43]

DDR0_DQ[44]

DDR0_DQ[45]

DDR0_DQ[46]

DDR0_DQ[47]

DDR0_DQ[48]

DDR0_DQ[49]

DDR0_DQ[50]

DDR0_DQ[51]

DDR0_DQ[52]

DDR0_DQ[53]

DDR0_DQ[54]

DDR0_DQ[55]

DDR0_DQ[56]

DDR0_DQ[57]

DDR0_DQ[58]

DDR0_DQ[59]

DDR0_DQ[60]

DDR0_DQ[61]

DDR0_DQ[62]

DDR0_DQ[63]

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[32]

DDR0_DQ[33]

DDR0_DQ[34]

DDR0_DQ[35]

DDR0_DQ[36]

DDR0_DQ[37]

DDR0_DQ[38]

DDR0_DQ[39]

DDR0_DQ[40]

DDR0_DQ[41]

DDR0_DQ[42]

DDR0_DQ[43]

DDR0_DQ[44]

DDR0_DQ[45]

DDR0_DQ[46]

DDR0_DQ[47]

DDR1_DQ[0]

DDR1_DQ[1]

DDR1_DQ[2]

DDR1_DQ[3]

DDR1_DQ[4]

DDR1_DQ[5]

DDR1_DQ[6]

DDR1_DQ[7]

DDR1_DQ[8]

DDR1_DQ[9]

DDR1_DQ[10]

DDR1_DQ[11]

DDR1_DQ[12]

DDR1_DQ[13]

DDR1_DQ[14]

DDR1_DQ[15]

DDR1_DQ[32]

DDR1_DQ[33]

DDR1_DQ[34]

DDR1_DQ[35]

DDR1_DQ[36]

DDR1_DQ[37]

DDR1_DQ[38]

DDR1_DQ[39]

DDR1_DQ[40]

DDR1_DQ[41]

DDR1_DQ[42]

DDR1_DQ[43]

DDR1_DQ[44]

DDR1_DQ[45]

DDR1_DQ[46]

DDR1_DQ[47]

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

SKL-U

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR CH - A

2 OF 20

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_DQSN[2]

DDR0_DQSP[2]

DDR0_DQSN[3]

DDR0_DQSP[3]

DDR0_DQSN[4]

DDR0_DQSP[4]

DDR0_DQSN[5]

DDR0_DQSP[5]

DDR0_DQSN[6]

DDR0_DQSP[6]

DDR0_DQSN[7]

DDR0_DQSP[7]

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_DQSN[4]

DDR0_DQSP[4]

DDR0_DQSN[5]

DDR0_DQSP[5]

DDR1_DQSN[0]

DDR1_DQSP[0]

DDR1_DQSN[1]

DDR1_DQSP[1]

DDR1_DQSN[4]

DDR1_DQSP[4]

DDR1_DQSN[5]

DDR1_DQSP[5]

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

DDR_PG_CTRL

-DDR_A_CLK0

DDR_A_CLK0

DDR_A_CKE0

-DDR_A_CS0

DDR_A_ODT0

DDR_A_MA5

DDR_A_MA9

DDR_A_MA6

DDR_A_MA8

DDR_A_MA7

DDR_A_BG0

DDR_A_MA12

DDR_A_MA11

-DDR_A_ACT

DDR_A_BG1

DDR_A_MA13

DDR_A_MA15

DDR_A_MA14

DDR_A_MA16

DDR_A_BA0

DDR_A_MA2

DDR_A_BA1

DDR_A_MA10

DDR_A_MA1

DDR_A_MA0

DDR_A_MA3

DDR_A_MA4

-DDR_A_DQS0

DDR_A_DQS0

-DDR_A_DQS1

DDR_A_DQS1

-DDR_A_DQS4

DDR_A_DQS4

-DDR_A_DQS5

DDR_A_DQS5

-DDR_B_DQS0

DDR_B_DQS0

-DDR_B_DQS1

DDR_B_DQS1

-DDR_B_DQS4

DDR_B_DQS4

-DDR_B_DQS5

DDR_B_DQS5

-DDR_A_ALERT

DDR_A_PAR

+0.6V_A_VREFDQ

+0.6V_B_VREFDQ

1 2

@

R1858

10K_0201_5%

VCC1R2A

2

-DDR_A_CLK0 [22,23]

DDR_A_CLK0 [22,23]

DDR_A_CKE0 [22,23]

-DDR_A_CS0 [22,23]

DDR_A_ODT0 [22,23]

DDR_A_BG0 [22,23]

-DDR_A_ACT [22,23]

DDR_A_BG1 [22]

DDR_A_BA0 [22,23]

DDR_A_BA1 [22,23]

-DDR_A_DQS0 [22]

DDR_A_DQS0 [22]

-DDR_A_DQS1 [22]

DDR_A_DQS1 [22]

-DDR_A_DQS4 [22]

DDR_A_DQS4 [22]

-DDR_A_DQS5 [22]

DDR_A_DQS5 [22]

-DDR_B_DQS0 [24]

DDR_B_DQS0 [24]

-DDR_B_DQS1 [24]

DDR_B_DQS1 [24]

-DDR_B_DQS4 [24]

DDR_B_DQS4 [24]

-DDR_B_DQS5 [24]

DDR_B_DQS5 [24]

-DDR_A_ALERT [22,23]

DDR_A_PAR [22,23]

+0.6V_A_VREFDQ [23]

+0.6V_B_VREFDQ [25]

VCC3M

R1838

100K_0201_5%

1 2

DDR_VTT_PG_CTRL

13

Q170

DTC015TMT2L_VMT3

DDR_A_MA[16:0] [22,23]

DDR_VTT_PG_CTRL [69]

TABLE

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

DDR3L LPDDR3 DDR4

Pin

DDR0_MA[5]

DDR0_MA[9]

DDR0_MA[6]

DDR0_MA[8]

DDR0_MA[7]

DDR0_BA[2]

DDR0_MA[12]

DDR0_MA[11]

DDR0_MA[15]

DDR0_MA[14]

DDR0_MA[13]

DDR0_CAS#

DDR0_WE#

DDR0_RAS#

DDR0_BA[0]

DDR0_MA[2]

DDR0_BA[1]

DDR0_MA[10]

DDR0_MA[1]

DDR0_MA[0]

DDR0_MA[3]

DDR0_MA[4]

DDR0_CAA[0]

DDR0_CAA[1]

DDR0_CAA[2]

DDR0_CAA[3]

DDR0_CAA[4]

DDR0_CAA[5]

DDR0_CAA[6]

DDR0_CAA[7]

DDR0_CAA[8]

DDR0_CAA[9]

DDR0_CAB[0]

DDR0_CAB[1]

DDR0_CAB[2]

DDR0_CAB[3]

DDR0_CAB[4]

DDR0_CAB[5]

DDR0_CAB[6]

DDR0_CAB[7]

DDR0_CAB[8]

DDR0_CAB[9]

Not Used

Not Used

DDR0_MA[5]

DDR0_MA[9]

DDR0_MA[6]

DDR0_MA[8]

DDR0_MA[7]

DDR0_BG[0]

DDR0_MA[12]

DDR0_MA[11]

DDR0_ACT#

DDR0_BG[1]

DDR0_MA[13]

DDR0_MA[15]

DDR0_MA[14]

DDR0_MA[16]

DDR0_BA[0]

DDR0_MA[2]

DDR0_BA[1]

DDR0_MA[10]

DDR0_MA[1]

DDR0_MA[0]

DDR0_MA[3]

DDR0_MA[4]

LOGIC

LOGIC

5

LOGIC LOGIC

4

LOGIC

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/11/04 2016/12/31

2014/11/04 2016/12/31

2014/11/04 2016/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CPU(2/16) : DDR CHANNEL-A

CPU(2/16) : DDR CHANNEL-A

CPU(2/16) : DDR CHANNEL-A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F421P

LA-F421P

LA-F421P

Monday, October 23, 2017

Monday, October 23, 2017

Monday, October 23, 2017

Date: Sheet

Date: Sheet

Date: Sheet

1

73

73

73

of

of

of

5

5

5

1.0

1.0

1.0

5

DDR_A_D[63:0][5,22]

DDR_B_D[63:0][5,24]

D D

TABLE

Pin Interleave Non-Interleave

DDR1_DQ[0]

AF65

DDR1_DQ[1]

AF64

DDR1_DQ[2]

AK65

DDR1_DQ[3]

AK64

DDR1_DQ[4]

AF66

DDR1_DQ[5]

AF67

DDR1_DQ[6]

AK67

DDR1_DQ[7]

AK66

DDR1_DQ[8]

AF70

DDR1_DQ[9]

AF68

Block 1

C C

Block 3

Block 5

B B

Block 7

A A

AH71

AH68

AF71

AF69

AH70

AH69

AT66

AU66

AP65

AN65

AN66

AP66

AT65

AU65

AT61

AU61

AP60

AN60

AN61

AP61

AT60

AU60

AU40

AT40

AT37

AU37

AR40

AP40

AP37

AR37

AT33

AU33

AU30

AT30

AR33

AP33

AR30

AP30

AU27

AT27

AT25

AU25

AP27

AN27

AN25

AP25

AT22

AU22

AU21

AT21

AN22

AP22

AP21

AN21

DDR1_DQ[10]

DDR1_DQ[11]

DDR1_DQ[12]

DDR1_DQ[13]

DDR1_DQ[14]

DDR1_DQ[15]

DDR1_DQ[16]

DDR1_DQ[17]

DDR1_DQ[18]

DDR1_DQ[19]

DDR1_DQ[20]

DDR1_DQ[21]

DDR1_DQ[22]

DDR1_DQ[23]

DDR1_DQ[24]

DDR1_DQ[25]

DDR1_DQ[26]

DDR1_DQ[27]

DDR1_DQ[28]

DDR1_DQ[29]

DDR1_DQ[30]

DDR1_DQ[31]

DDR1_DQ[32]

DDR1_DQ[33]

DDR1_DQ[34]

DDR1_DQ[35]

DDR1_DQ[36]

DDR1_DQ[37]

DDR1_DQ[38]

DDR1_DQ[39]

DDR1_DQ[40]

DDR1_DQ[41]

DDR1_DQ[42]

DDR1_DQ[43]

DDR1_DQ[44]

DDR1_DQ[45]

DDR1_DQ[46]

DDR1_DQ[47]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

LOGIC

DDR0_DQ[16]

DDR0_DQ[17]

DDR0_DQ[18]

DDR0_DQ[19]

DDR0_DQ[20]

DDR0_DQ[21]

DDR0_DQ[22]

DDR0_DQ[23]

DDR0_DQ[24]

DDR0_DQ[25]

DDR0_DQ[26]

DDR0_DQ[27]

DDR0_DQ[28]

DDR0_DQ[29]

DDR0_DQ[30]

DDR0_DQ[31]

DDR0_DQ[48]

DDR0_DQ[49]

DDR0_DQ[50]

DDR0_DQ[51]

DDR0_DQ[52]

DDR0_DQ[53]

DDR0_DQ[54]

DDR0_DQ[55]

DDR0_DQ[56]

DDR0_DQ[57]

DDR0_DQ[58]

DDR0_DQ[59]

DDR0_DQ[60]

DDR0_DQ[61]

DDR0_DQ[62]

DDR0_DQ[63]

DDR1_DQ[16]

DDR1_DQ[17]

DDR1_DQ[18]

DDR1_DQ[19]

DDR1_DQ[20]

DDR1_DQ[21]

DDR1_DQ[22]

DDR1_DQ[23]

DDR1_DQ[24]

DDR1_DQ[25]

DDR1_DQ[26]

DDR1_DQ[27]

DDR1_DQ[28]

DDR1_DQ[29]

DDR1_DQ[30]

DDR1_DQ[31]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

LOGIC

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

4

U58C

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

KBL-RU_BGA1356

TABLE

Block 1

Block 3

Block 5

Block 7

@

SKL-U

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

3 OF 20

Pin Interleave Non-Interleave

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

DDR1_DQSN[0]

DDR1_DQSP[0]

DDR1_DQSN[1]

DDR1_DQSP[1]

DDR1_DQSN[2]

DDR1_DQSP[2]

DDR1_DQSN[3]

DDR1_DQSP[3]

DDR1_DQSN[4]

DDR1_DQSP[4]

DDR1_DQSN[5]

DDR1_DQSP[5]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR0_DQSN[2]

DDR0_DQSP[2]

DDR0_DQSN[3]

DDR0_DQSP[3]

DDR0_DQSN[6]

DDR0_DQSP[6]

DDR0_DQSN[7]

DDR0_DQSP[7]

DDR1_DQSN[2]

DDR1_DQSP[2]

DDR1_DQSN[3]

DDR1_DQSP[3]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

LOGIC

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

LOGIC

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

3

-DDR_B_CLK0

DDR_B_CLK0

DDR_B_CKE0

-DDR_B_CS0

DDR_B_ODT0

DDR_B_MA5

DDR_B_MA9

DDR_B_MA6

DDR_B_MA8

DDR_B_MA7

DDR_B_BG0

DDR_B_MA12

DDR_B_MA11

-DDR_B_ACT

DDR_B_BG1

DDR_B_MA13

DDR_B_MA15

DDR_B_MA14

DDR_B_MA16

DDR_B_BA0

DDR_B_MA2

DDR_B_BA1

DDR_B_MA10

DDR_B_MA1

DDR_B_MA0

DDR_B_MA3

DDR_B_MA4

-DDR_A_DQS2

DDR_A_DQS2

-DDR_A_DQS3

DDR_A_DQS3

-DDR_A_DQS6

DDR_A_DQS6

-DDR_A_DQS7

DDR_A_DQS7

-DDR_B_DQS2

DDR_B_DQS2

-DDR_B_DQS3

DDR_B_DQS3

-DDR_B_DQS6

DDR_B_DQS6

-DDR_B_DQS7

DDR_B_DQS7

1 2

R7 200_0201_1%X76@

1 2

R84 80.6_0201_1%

1 2

R576 100_0201_1%

-DDR_B_CLK0 [24,25]

DDR_B_CLK0 [24,25]

DDR_B_CKE0 [24,25]

-DDR_B_CS0 [24,25]

DDR_B_ODT0 [24,25]

DDR_B_BG0 [24,25]

-DDR_B_ACT [24,25]

DDR_B_BG1 [24]

DDR_B_BA0 [24,25]

DDR_B_BA1 [24,25]

-DDR_A_DQS2 [22]

DDR_A_DQS2 [22]

-DDR_A_DQS3 [22]

DDR_A_DQS3 [22]

-DDR_A_DQS6 [22]

DDR_A_DQS6 [22]

-DDR_A_DQS7 [22]

DDR_A_DQS7 [22]

-DDR_B_DQS2 [24]

DDR_B_DQS2 [24]

-DDR_B_DQS3 [24]

DDR_B_DQS3 [24]

-DDR_B_DQS6 [24]

DDR_B_DQS6 [24]

-DDR_B_DQS7 [24]

DDR_B_DQS7 [24]

-DDR_B_ALERT [24,25]

DDR_B_PAR [24,25]

VCC1R2A

R7 200 1% 121 1%

1 2

R1726

470_0201_5%

-DRAMRST

DDPSDP

2

DDR_B_MA[16:0] [24,25]

-DRAMRST [22,24]

TABLE

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

DDR3L LPDDR3 DDR4

Pin

DDR1_MA[5]

DDR1_MA[9]

DDR1_MA[6]

DDR1_MA[8]

DDR1_MA[7]

DDR1_BA[2]

DDR1_MA[12]

DDR1_MA[11]

DDR1_MA[15]

DDR1_MA[14]

DDR1_MA[13]

DDR1_CAS#

DDR1_WE#

DDR1_RAS#

DDR1_BA[0]

DDR1_MA[2]

DDR1_BA[1]

DDR1_MA[10]

DDR1_MA[1]

DDR1_MA[0]

DDR1_MA[3]

DDR1_MA[4]

DDR1_CAA[0]

DDR1_CAA[1]

DDR1_CAA[2]

DDR1_CAA[3]

DDR1_CAA[4]

DDR1_CAA[5]

DDR1_CAA[6]

DDR1_CAA[7]

DDR1_CAA[8]

DDR1_CAA[9]

DDR1_CAB[0]

DDR1_CAB[1]

DDR1_CAB[2]

DDR1_CAB[3]

DDR1_CAB[4]

DDR1_CAB[5]

DDR1_CAB[6]

DDR1_CAB[7]

DDR1_CAB[8]

DDR1_CAB[9]

Not Used

Not Used

LOGIC

1

DDR1_MA[5]

DDR1_MA[9]

DDR1_MA[6]

DDR1_MA[8]

DDR1_MA[7]

DDR1_BG[0]

DDR1_MA[12]

DDR1_MA[11]

DDR1_ACT#

DDR1_BG[1]

DDR1_MA[13]

DDR1_MA[15]

DDR1_MA[14]

DDR1_MA[16]

DDR1_BA[0]

DDR1_MA[2]

DDR1_BA[1]

DDR1_MA[10]

DDR1_MA[1]

DDR1_MA[0]

DDR1_MA[3]

DDR1_MA[4]

LOGIC

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/11/04 2016/12/31

2014/11/04 2016/12/31

2014/11/04 2016/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CPU(3/16) : DDR CHANNEL-B

CPU(3/16) : DDR CHANNEL-B

CPU(3/16) : DDR CHANNEL-B

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F421P

LA-F421P

LA-F421P

Monday, October 23, 2017

Monday, October 23, 2017

Monday, October 23, 2017

Date: Sheet

Date: Sheet

Date: Sheet

1

73

73

73

of

of

of

6

6

6

1.0

1.0

1.0

5

D D

4

3

2

1

C C

PECI[53]

-PROCHOT[53]

B B

A A

PECI

-PROCHOT

VCCSTG VCCST

R64

1K_0201_5%

1 2

1 2

R85 510_0402_5%

1 2

R2126 49.9_0201_1%

1 2

R2127 49.9_0201_1%

1 2

R2128 49.9_0201_1%

1 2

R2129 49.9_0201_1%

1 2

R9055

1K_0201_5%

AT16

AU16

D63

A54

C65

C63

A65

C55

D55

B54

C56

A6

A7

BA5

AY5

H66

H65

U58D

@

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

CPU MISC

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

KBL-RU_BGA1356

SKL-U

4 OF 20

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

R9397

51_0201_5%@

XDP_TCK0

XDP_TDI

XDP_TDO

XDP_TMS

-XDP_TRST

XDP_TCK0 [20]

XDP_TDI [20]

XDP_TDO [20]

XDP_TMS [20]

-XDP_TRST [20]

PCH_TCK [20]

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

R2

51_0201_5%

1 2

1 2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/11/04 2016/12/31

2014/11/04 2016/12/31

2014/11/04 2016/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CPU(4/16) : MISC/JTAG

CPU(4/16) : MISC/JTAG

CPU(4/16) : MISC/JTAG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F421P

LA-F421P

LA-F421P

Monday, October 23, 2017

Monday, October 23, 2017

Monday, October 23, 2017

Date: Sheet

Date: Sheet

Date: Sheet

1

73

73

73

of

of

of

7

7

7

1.0

1.0

1.0

5

D D

TABLE : Functional Strap

SPI0_MOSI (Boot Halt)

Disabled (Default)

HIGH

LOW Enabled

TABLE : Functional Strap

SPI0_MISO (JTAG ODT Diable)

Enabled (Default)

HIGH

LOW Disabled

VCC3_SUS

C C

@

@

1 2

1 2

R9310 1K_0201_5%

R9311 1K_0201_5%

SPI_CLK[21,45]

SPI_MISO_IO1[21,45]

SPI_MOSI_IO0[21,45]

SPI_IO2[21]

SPI_IO3[21]

-SPI_CS0[21]

-SPI_CS2[45]

CL_CLK_WLAN[32]

CL_DATA_WLAN[32]

-CL_RST_WLAN[32]

B B

-KBRC[53]

IRQSER[46,53]

CL_CLK_WLAN

CL_DATA_WLAN

-CL_RST_WLAN

2

@RF@

C264

33P_0201_25V8J

1

VCC3B

8.2K_0201_5%

@

R9308

1K_0201_5%

1 2

4

TABLE : Functional Strap

GPP_C5/SML0ALERT # (LPC or eSPI)

HIGH

eSPI is selected

LOW

LPC is selected (Default) LOGIC

TABLE : Functional Strap

GPP_C2/SMBALERT# (TLS Confidentiality)

Enable ME Crypto TLS with Confidentiality

HIGH

LOW

Disable ME Crypto TLS (Default)

1 2

R860

AV2

AW3

AV3

AW2

AU4

AU3

AU2

AU1

AW13

AY11

@

R9305

1K_0201_5%

1 2

U58E

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

KBL-RU_BGA1356

@

SPI - FLASH

SPI - TOUCH

C LINK

SKL-U

LPC

5 OF 20

3

SMBUS, SMLINK

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

2

FVT_C_EC016

EC_SMB_CK2[41,51,53]

EC_SMB_DA2[41,51,53]

LOGIC

VCC3_SUS VCC3B

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

R226

1K_0201_5%

1 2

LPCCLK_0

LPCCLK_1

R394

4.7K_0201_5%

1 2

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

R193 27_0402_1%RF@

R220 0_0402_5%

FVT_C_EC002

R397

4.7K_0201_5%

1 2

1 2

1 2

VCC3_SUS

C8609

18P_0201_50V8J

1 2

RF@

R106

499_0201_1%

2

1

2

C8610

18P_0201_50V8J

1

EC_SMB_CK2 SMB_CK2

R107

499_0201_1%

1 2

LPC_AD[3:0] [46,53]

-LPC_FRAME [46,53]

-SUS_STAT [46]

LPCCLK_EC_24M [53]

LPCCLK_DEBUG_24M [46]

@RF@

2

6 1

Q211A

SSM6N48FU 2N SC-88-6 ET88

3 4

Q211B

SSM6N48FU 2N SC-88-6 ET88

@

8.2K_0201_5%

1 2

R28

SMB_CLK

SMB_DATA

SMB0_CLK

SMB0_DATA

SMB_CK2

SMB_DA2

VCC3M

1

5

SMB_DA2EC_SMB_DA2

SMB_CLK [46]

SMB_DATA [46]

SMB0_CLK [52]

SMB0_DATA [52]

SMB_CK2 [41]

SMB_DA2 [41]

-CLKRUN [46]

TABLE : Functional Strap

SPI0_IO2 (Consent Strap)

Enabled (Default)

HIGH

LOW Disabled

TABLE : Functional Strap

SPI0_IO3 (A0 Personality Strap)

Disabled (Default)

A A

5

4

HIGH

LOW Enabled

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/11/04 2016/12/31

2014/11/04 2016/12/31

2014/11/04 2016/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CPU(5/16) : LPC/SPI/SMBUS/C-LINK

CPU(5/16) : LPC/SPI/SMBUS/C-LINK

CPU(5/16) : LPC/SPI/SMBUS/C-LINK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F421P

LA-F421P

LA-F421P

Date: Sheet

Date: Sheet

Date: Sheet

1

of

of

of

8 73Monday, October 23, 2017

8 73Monday, October 23, 2017

8 73Monday, October 23, 2017

1.0

1.0

1.0

5

10K_0201_5%

1 2

VCC1R8_SUS

@

@

10K_0201_5%

1 2

R2748

R2749

D D

NFC_DLREQ[43]

-WWAN_PWROFF[32]

-WWAN_DISABLE[32]

C C

BDC_ON[32]

-TBT_PLUG_EVENT[48]

TBT_FORCE_PWR[48]

-EC_SCI[53]

-EC_WAKE[53]

I2C0_DATA[43]

I2C0_CLK[43]

-WWAN_RESET[32]

-INT_MIC_DTCT[26,27]

WWAN_CFG0[32]

WWAN_CFG1[32]

VCC3B

4

TABLE : Functional Strap

VCC3_SUS

1K_0201_5%

10K_0201_5%

1 2

1 2

R2340

GPP_B22/GSPI1_MOSI (Boot BIOS Destination)

HIGH

Boot BIOS from LPC

LOW

Boot BIOS from SPI (Default) LOGIC

TABLE : Functional Strap

GPP_B18/GSPI0_MOSI (No Reboot)

@

HIGH

Enable "No Reboot" Mode

LOW

R65

AN8

AP7

AP8

AR7

AM5

AN7

AP5

AN5

AB1

AB2

W4

AB3

AD1

AD2

AD3

AD4

U7

U6

U8

U9

AH9

AH10

AH11

AH12

AF11

AF12

GPP_B15/GSPI0_CS#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/UART0_RXD

GPP_C9/UART0_TXD

GPP_C10/UART0_RTS#

GPP_C11/UART0_CTS#

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_F6/I2C3_SDA

GPP_F7/I2C3_SCL

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

Disable "No Reboot" Mode (Default)

U58F

@

LPSS ISH

KBL-RU_BGA1356

SKL-U

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

6 OF 20

3

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D15/ISH_UART0_RTS#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_A12/BM_BUSY#/ISH_GP6

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

VCC3B VCC3B

1K_0201_5%

1K_0201_5%

1 2

1 2

R9261

R9257

VCC3B VCC3B

R154

4.7K_0201_5%

1 2

ISH_GP0_R

ISH_GP1_R

ISH_GP2_R

ISH_GP3

ISH_GP4

ISH_GP5

ISH_GP6

2

VCC1R8_SUSVCC3B

@

1K_0201_5%

1K_0201_5%

1 2

1 2

R9263

R9262

R155

R156

4.7K_0201_5%

4.7K_0201_5%

1 2

1 2

@

10K_0201_5%

10K_0201_5%

1 2

1 2

R9375

R9565

R9259

R9260

4.7K_0201_5%

4.7K_0201_5%

1 2

1 2

@

10K_0201_5%

10K_0201_5%

1 2

1 2

R2750

R2751

1 2

R9419 0_0201_5%RF@

1 2

R9420 0_0201_5%RF@

1 2

R9421 0_0201_5%RF@

FVT_C_EC018

TP922 @

TP923 @

-NFC_DTCT [43]

-INT_IR_DTCT [27]

-TS_RESET [26]

ISH_I2C0_SDA [26,27,41]

ISH_I2C0_SCL [26,27,41]

I2C_DATA_GSENSE_SH [53]

I2C_CLK_GSENSE_SH [53]

WWAN_CFG2 [32]

WWAN_CFG3 [32]

2 1

D801 RB521CM-30T2R_SOD923-2

2 1

D802 RB521CM-30T2R_SOD923-2

C86500.1U_0201_6.3V6K

C86510.1U_0201_6.3V6K

C86490.1U_0201_6.3V6K

2

2

2

1

1

1

RF@

RF@

RF@

-LID_CLOSE

-TABLET_MODE

1

ISH_GP0 [26,27]

ISH_GP1 [26,27]

ISH_GP2 [26,27,41]

-LID_CLOSE [26,43,53]

-TABLET_MODE [43,53]

FVT_C_EC018

B B

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

For ISH debug

ISH_I2C0_SCL

ISH_I2C0_SDA

I2C_CLK_GSENSE_SH

I2C_DATA_GSENSE_SH

ISH_GP0

ISH_GP1

ISH_GP2

ISH_GP3

Compal Secret Data

Compal Secret Data

2014/11/04 2016/12/31

2014/11/04 2016/12/31

2014/11/04 2016/12/31

Compal Secret Data

2

Deciphered Date

Deciphered Date

Deciphered Date

TP924 @

TP925 @

TP926 @

TP927 @

TP928 @

TP929 @

TP930 @

TP931 @

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CPU(6/16) : LPSS/ISH

CPU(6/16) : LPSS/ISH

CPU(6/16) : LPSS/ISH

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F421P

LA-F421P

LA-F421P

Date: Sheet

Date: Sheet

Date: Sheet

1

of

of

of

9 73Monday, October 23, 2017

9 73Monday, October 23, 2017

9 73Monday, October 23, 2017

1.0

1.0

1.0

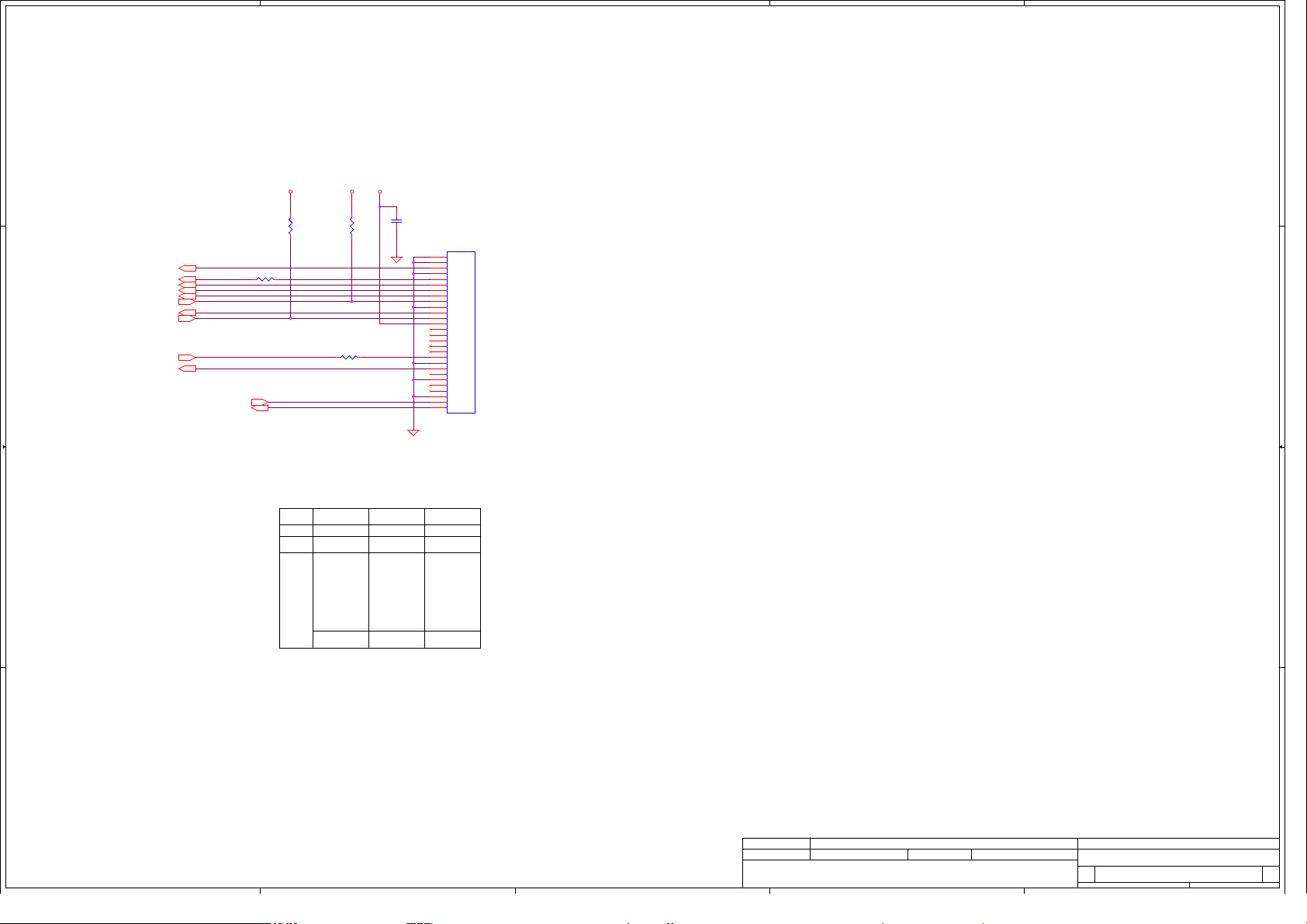

5

D D

C C

1 2

2

C38

RF@

47P_0201_25V8J

1

R423 33_0201_5%

1 2

R60 33_0201_5%

1 2

R74 33_0201_5%

1 2

R456 33_0201_5%

1 2

R9380 0_0201_5%@

PCH_SPKR

R60, C38 close to CPU

HDA_SYNC[35]

HDA_BCLK[35]

HDA_SDO[35]

HDA_SDIN0[35]

-HDA_RST[35]

NFC_ACTIVE[43]

PCH_SPKR[40]

B B

4

VCC3_SUS

@

1 2

R1009

1K_0201_5%

3

TABLE : Functional Strap

HDA_SDO/I2S0_TXD

1 2

ME_FLASH[53]

R9564 0_0201_5%@

HDA_SDOUT

Flash Descriptor Security Override

HIGH

Disable Flash Descriptor Security (Override)

LOW

Enable Flash Descriptor Security (Default)

U58G

@

AUDIO

BA22

HDA_SYNC/I2S0_SFRM

AY22

HDA_BLK/I2S0_SCLK

BB22

HDA_SDO/I2S0_TXD

BA21

HDA_SDI0/I2S0_RXD

AY21

HDA_SDI1/I2S1_RXD

AW22

HDA_RST#/I2S1_SCLK

J5

GPP_D23/I2S_MCLK

AY20

I2S1_SFRM

AW20

I2S1_TXD

AK7

GPP_F1/I2S2_SFRM

AK6

GPP_F0/I2S2_SCLK

AK9

GPP_F2/I2S2_TXD

AK10

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

AW5

GPP_B14/SPKR

KBL-RU_BGA1356

TABLE : Functional Strap

GPP_B14/SPKR (Top Swap Override)

HIGH

Enable "Top Swap" Mode

LOW

Disable "Top Swap" Mode (Default) LOGIC

SKL-U

7 OF 20

SDIO/SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

SD_RCOMP

GPP_F23

2

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

-SC_DTCT [34]

1

VCC3M

1 2

R54 1K_0201_5%@

HDA_SDOUT

ME debug mode,this signal has a weak internal PD

Low = Disabled (Default)

*

High = Enabled [Flash Descriptor Security Overide]

A A

HDA_SDOUT

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/11/04 2016/12/31

2014/11/04 2016/12/31

2014/11/04 2016/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

CPU : AUDIO/SDXC

CPU : AUDIO/SDXC

CPU : AUDIO/SDXC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-F421P

LA-F421P

LA-F421P

Date: Sheet

Date: Sheet

Date: Sheet

1

of

of

of

10 73Monday, October 23, 2017

10 73Monday, October 23, 2017

10 73Monday, October 23, 2017

1.0

1.0

1.0

5

4

3

2

1

D D

C C

B B

A A

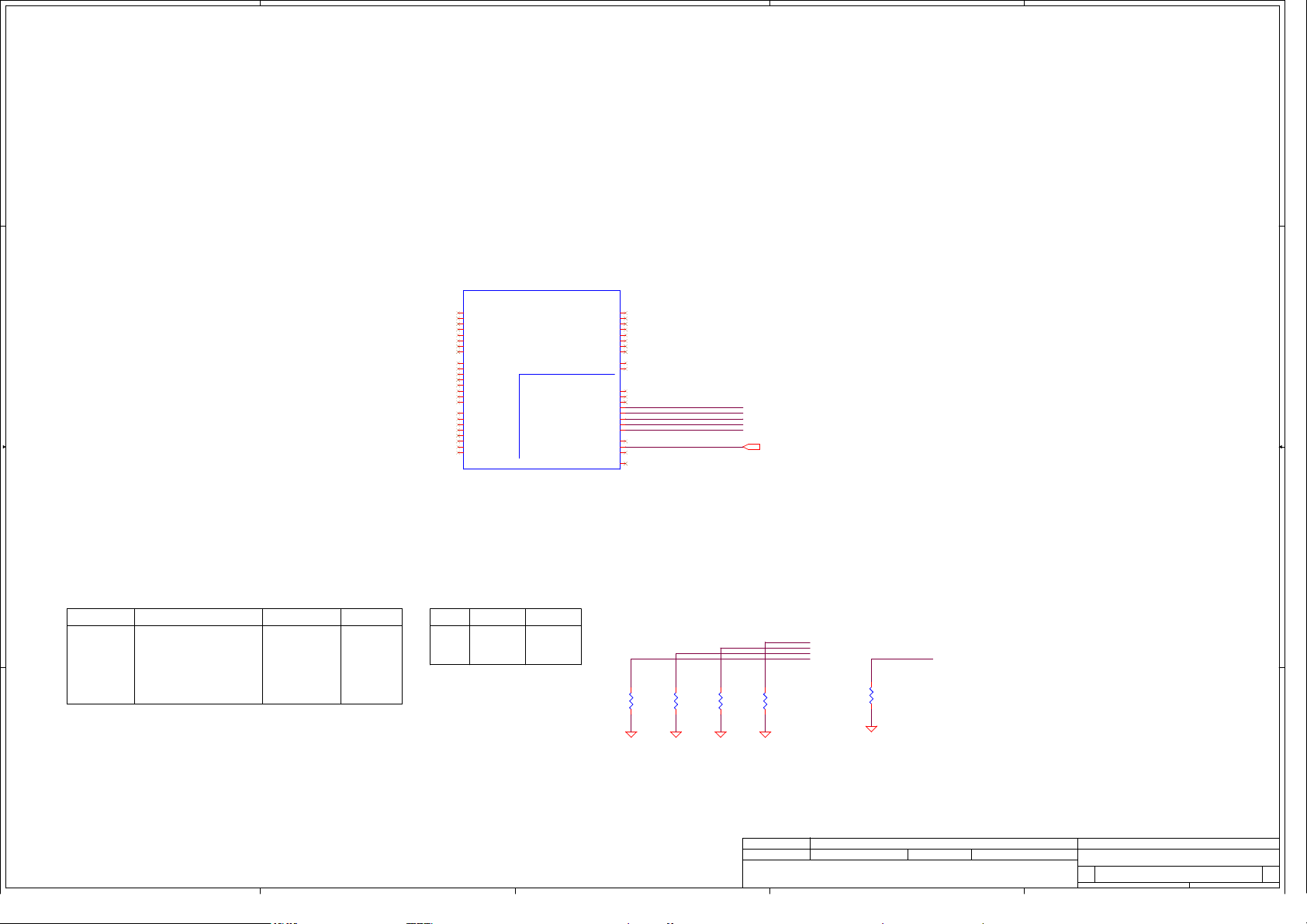

I/O High Speed Signals Configuration Net Name

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6

Port 7

Port 8

Port 9

Port 10

Port 11

Port 12

Port 13

Port 14

Port 15

Port 16

Flexible I/O Configuration PCIe Port Assignment

R8964

0

2

3

4 (x4)

8

11

0

1A

1B

2

100_0201_1%

1 2

SATA Port Assignment

(PCIE 7)

SATA SSD

NA

(PCIE 11)

USB3 1

USB3 2/SSIC

USB3 3

USB3 4

USB3 5/PCIE 1

USB3 6/PCIE 2

PCIE 3 (GbE)

PCIE 4 (GbE)

PCIE 5 (GbE)

PCIE 6

PCIE 7/SATA 0

PCIE 8/SATA 1A

PCIE 9 (GbE)

PCIE 10 (GbE)

PCIE 11/SATA 1B

PCIE 12/SATA 2

USB3 1

SSIC

USB3 3

USB3 4

PCIE 1

USB3 6

PCIE 3

PCIE 4

PCIE 5 (x4)

PCIE 6 (x4)

PCIE 7 (x4)

GPIO STRAP

PCIE 9 (x4)

PCIE 10 (x4)

PCIE 11 (x4)

PCIE 12 (x4)

PCIE4_L0_SATA1_RXN[30]

PCIE4_L0_SATA1_RXP[30]

PCIE4_L0_SATA1_TXN[30]

PCIE4_L0_SATA1_TXP[30]

USB3P0

SSIC

USB3P2

USB3P3

PCIE0

USB3P5

PCIE2

PCIE3

PCIE4_L3

PCIE4_L2

PCIE4_L1

PCIE4_L0_SATA1

PCIE5_L0

NA

NA

NA

PCIE0_RXN[33]

PCIE0_RXP[33]

PCIE0_TXN[33]

PCIE0_TXP[33]

PCIE2_RXN[32]

PCIE2_RXP[32]

PCIE2_TXN[32]

PCIE2_TXP[32]

PCIE3_RXN[52]

PCIE3_RXP[52]

PCIE3_TXN[52]

PCIE3_TXP[52]

PCIE4_L3_RXN[30]

PCIE4_L3_RXP[30]

PCIE4_L3_TXN[30]

PCIE4_L3_TXP[30]

PCIE4_L2_RXN[30]

PCIE4_L2_RXP[30]

PCIE4_L2_TXN[30]

PCIE4_L2_TXP[30]

PCIE4_L1_RXN[30]

PCIE4_L1_RXP[30]

PCIE4_L1_TXN[30]

PCIE4_L1_TXP[30]

PCIE8_L0_RXN[49]

PCIE8_L0_RXP[49]

PCIE8_L0_TXN[49]

PCIE8_L0_TXP[49]

PCIE8_L1_RXN[49]

PCIE8_L1_RXP[49]

PCIE8_L1_TXN[49]

PCIE8_L1_TXP[49]

-XDP_PRDY[20]

-XDP_PREQ[20]

-TPM_IRQ[45]

PCIE11_RXN[32]

PCIE11_RXP[32]

PCIE11_TXN[32]

PCIE11_TXP[32]

-XDP_PRDY

-XDP_PREQ

-TPM_IRQ

VCC3_SUS

1 2

R2341

10K_0201_5%

MEDIA CARD

M.2 WLAN Slot Port 0 for WLAN

GbE PHY

PCIe SSD

Thunder bolt

WWAN

U58H

@

PCIE/USB3/SATA

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20