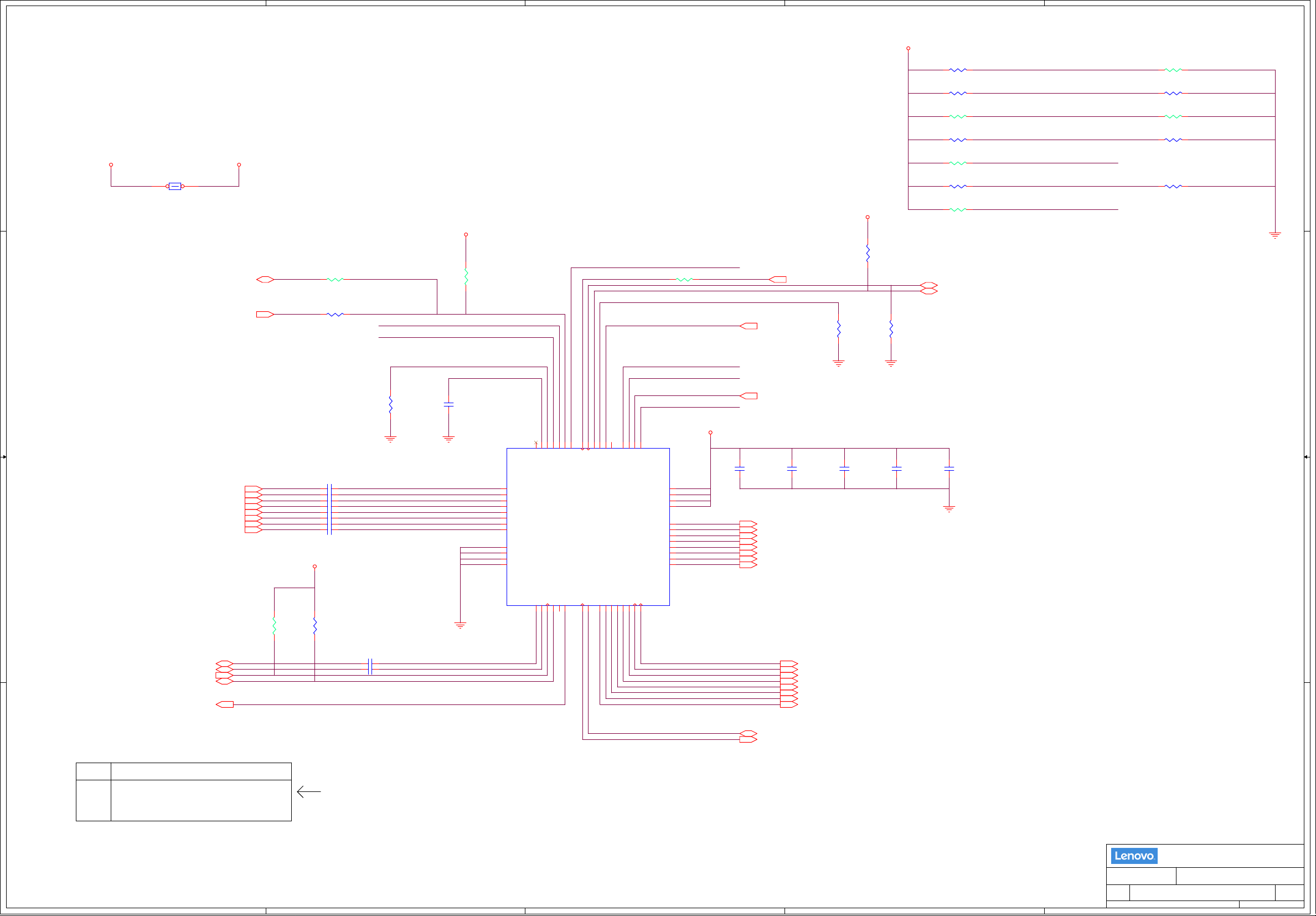

Lenovo ThinkPad X280 Schematic

5

4

3

2

1

Finn-1 SOVP Logic Schematics

1.TITLE PAGE

2.EC HISTORY

D D

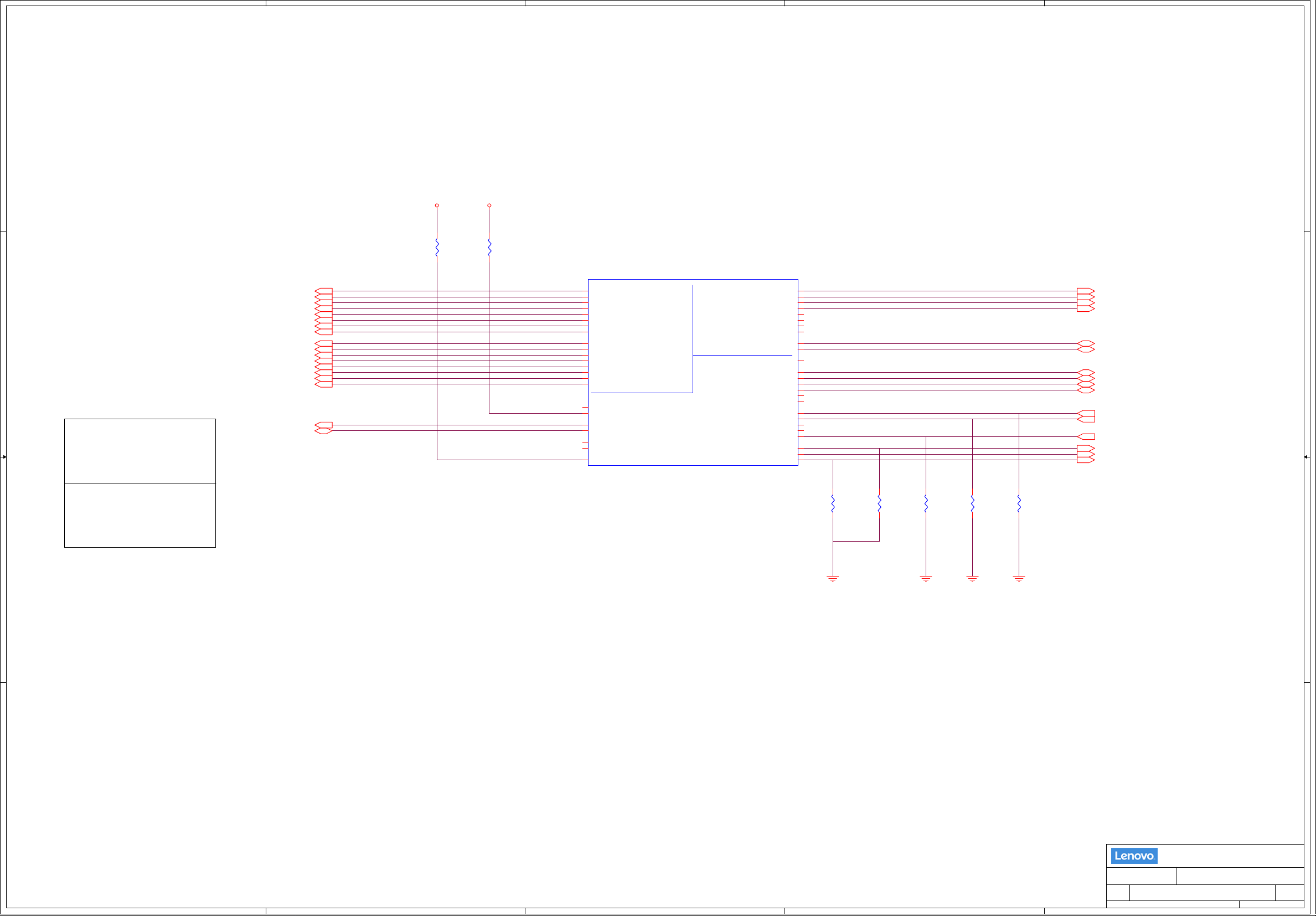

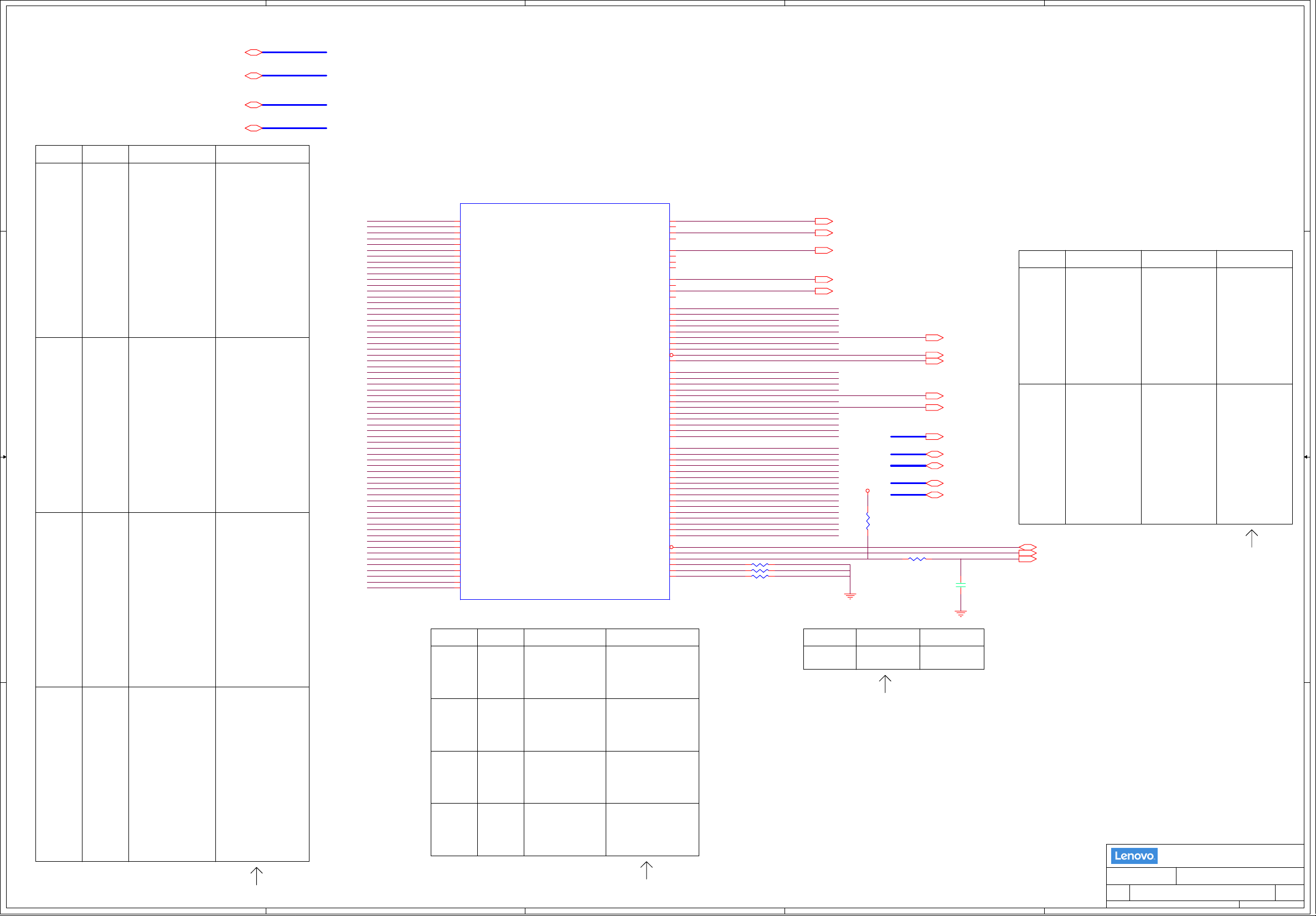

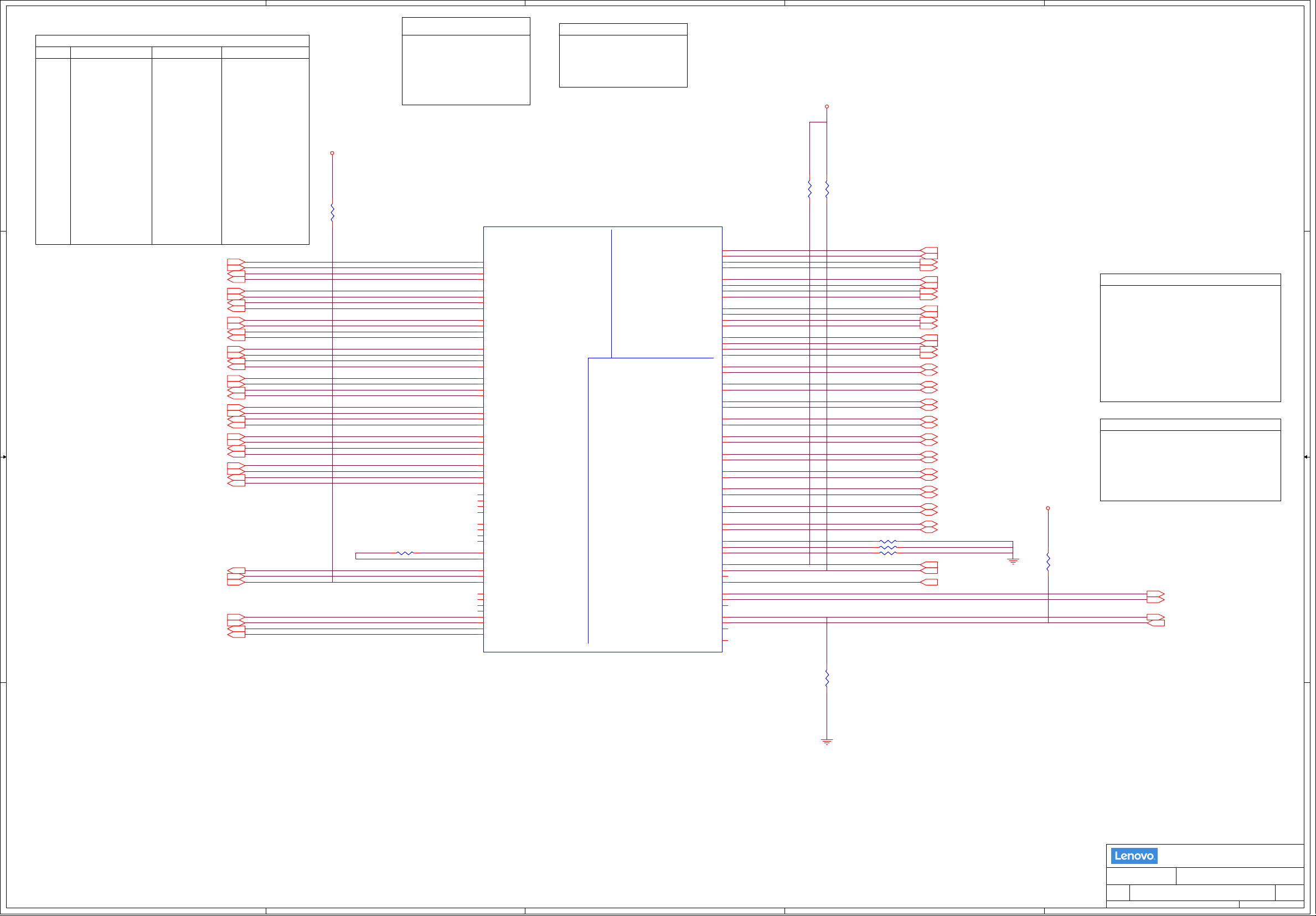

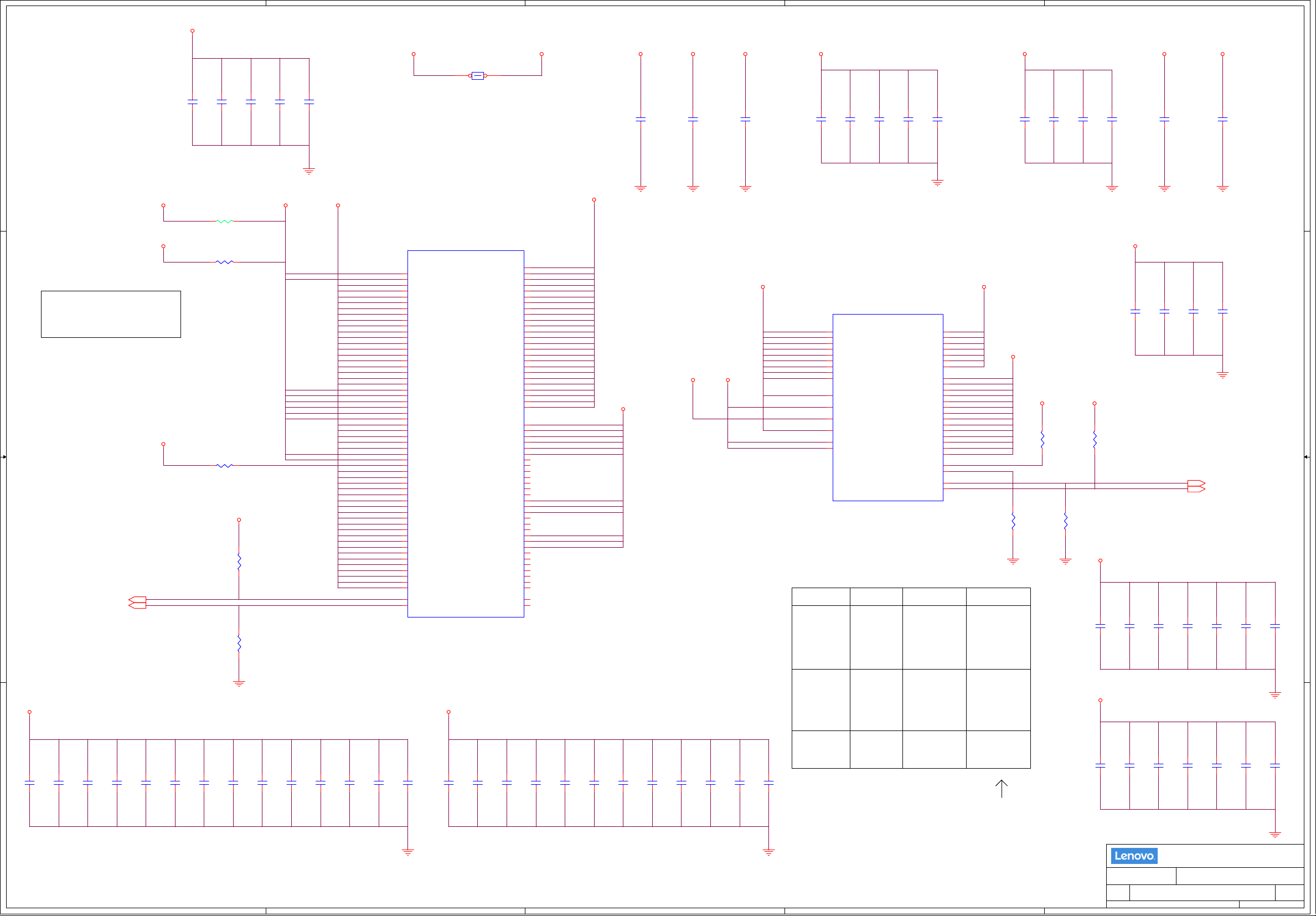

3.CPU(1/16) : DDI/EDP

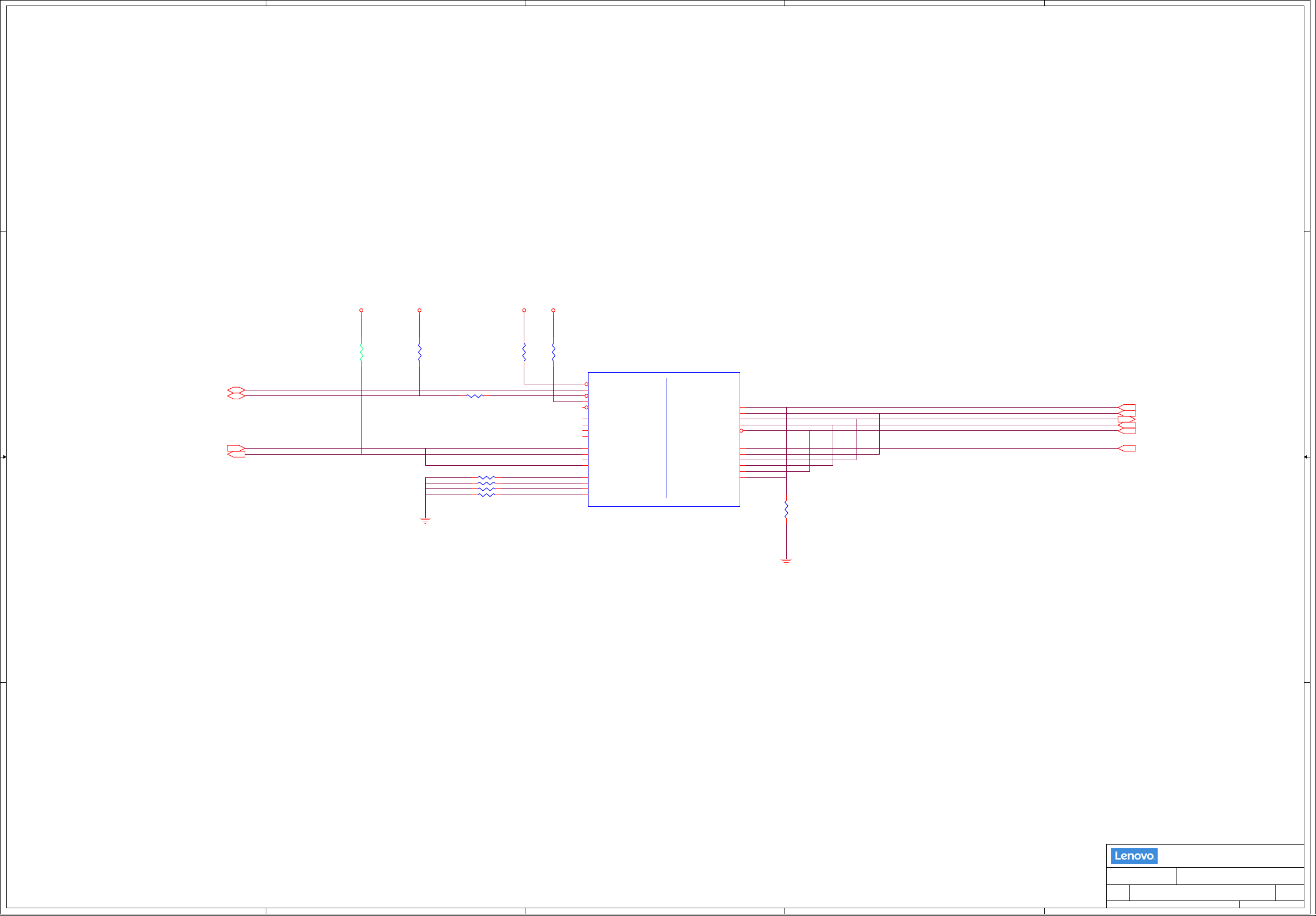

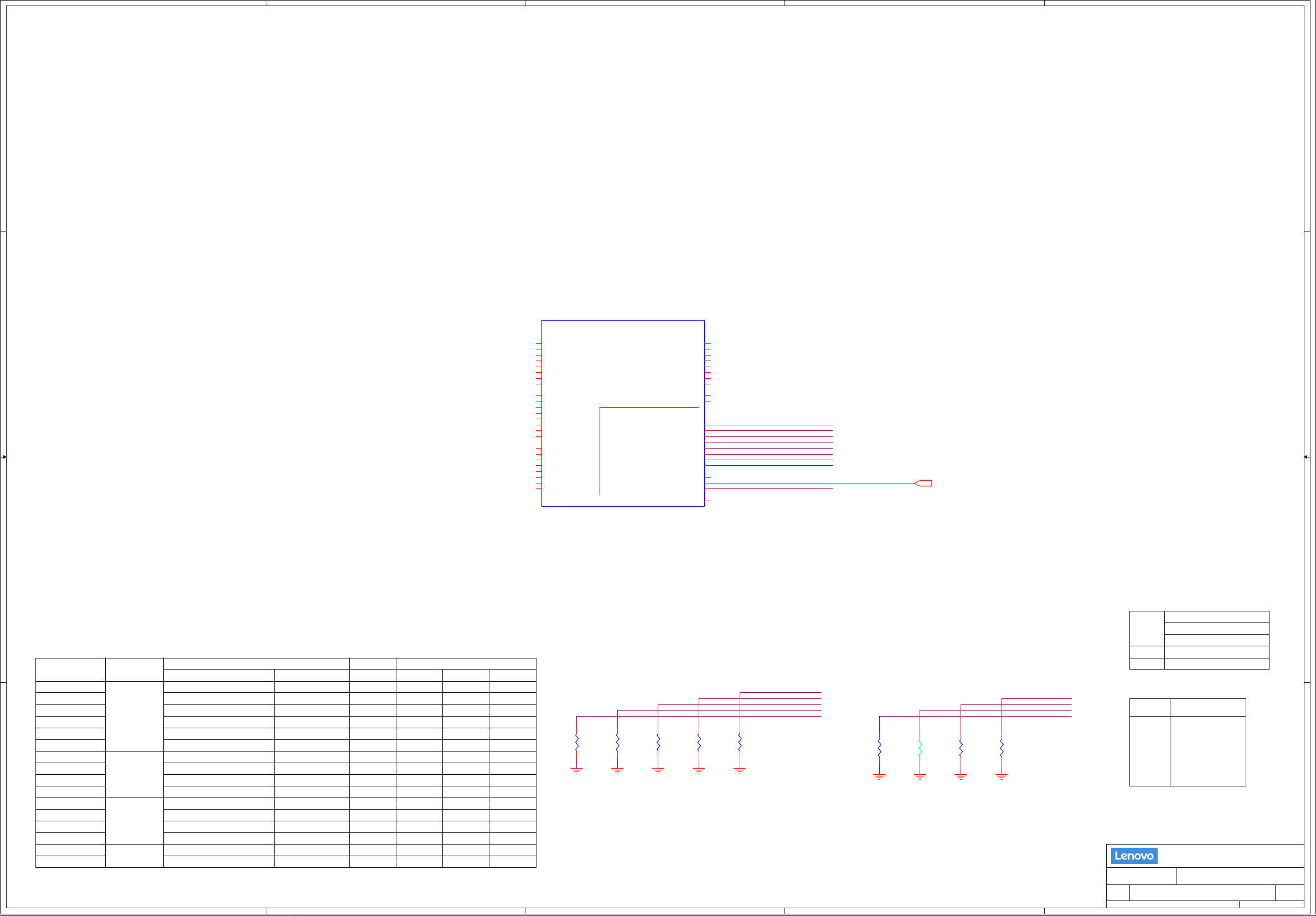

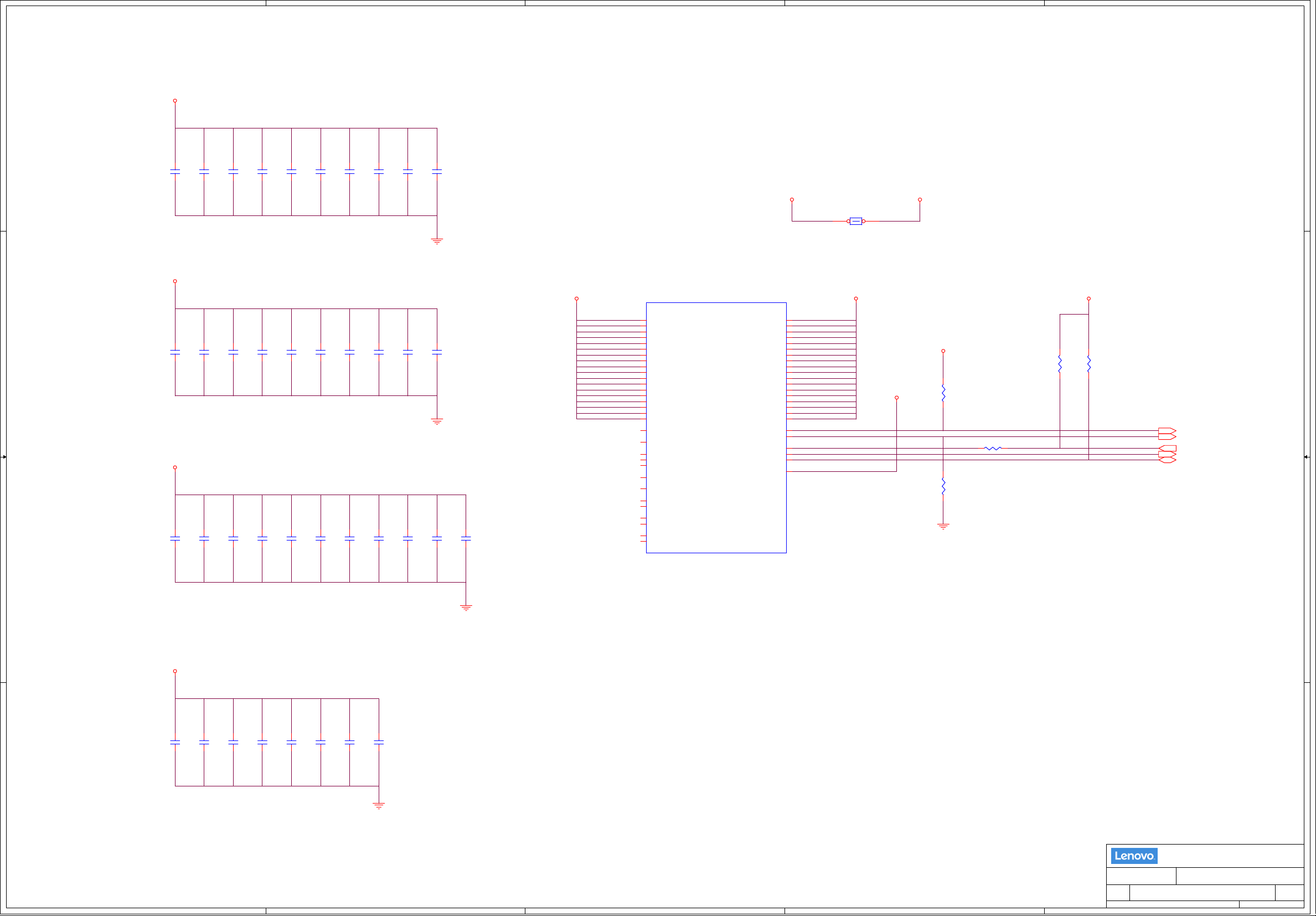

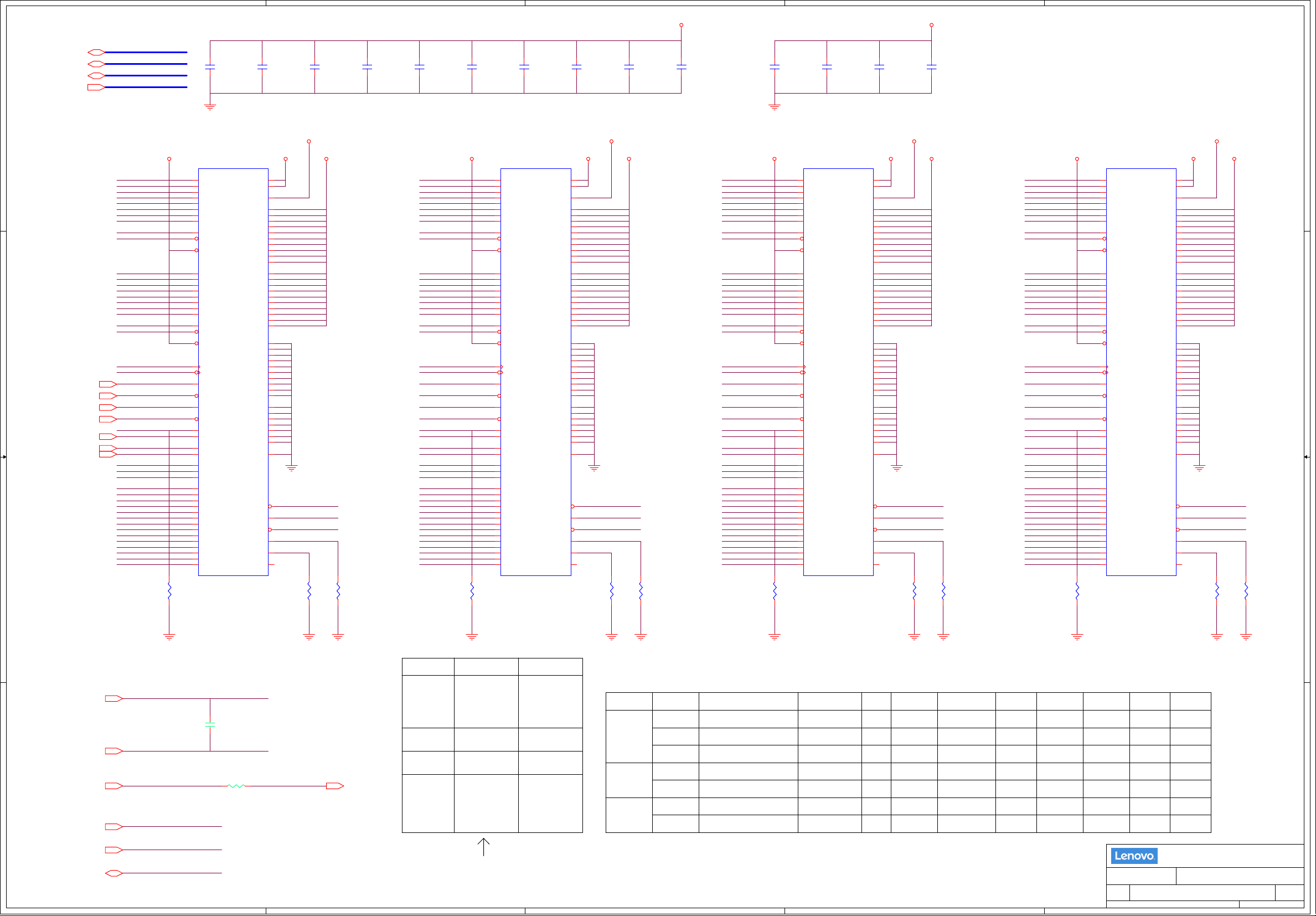

4.CPU(2/16) : DDR CHANNEL-A

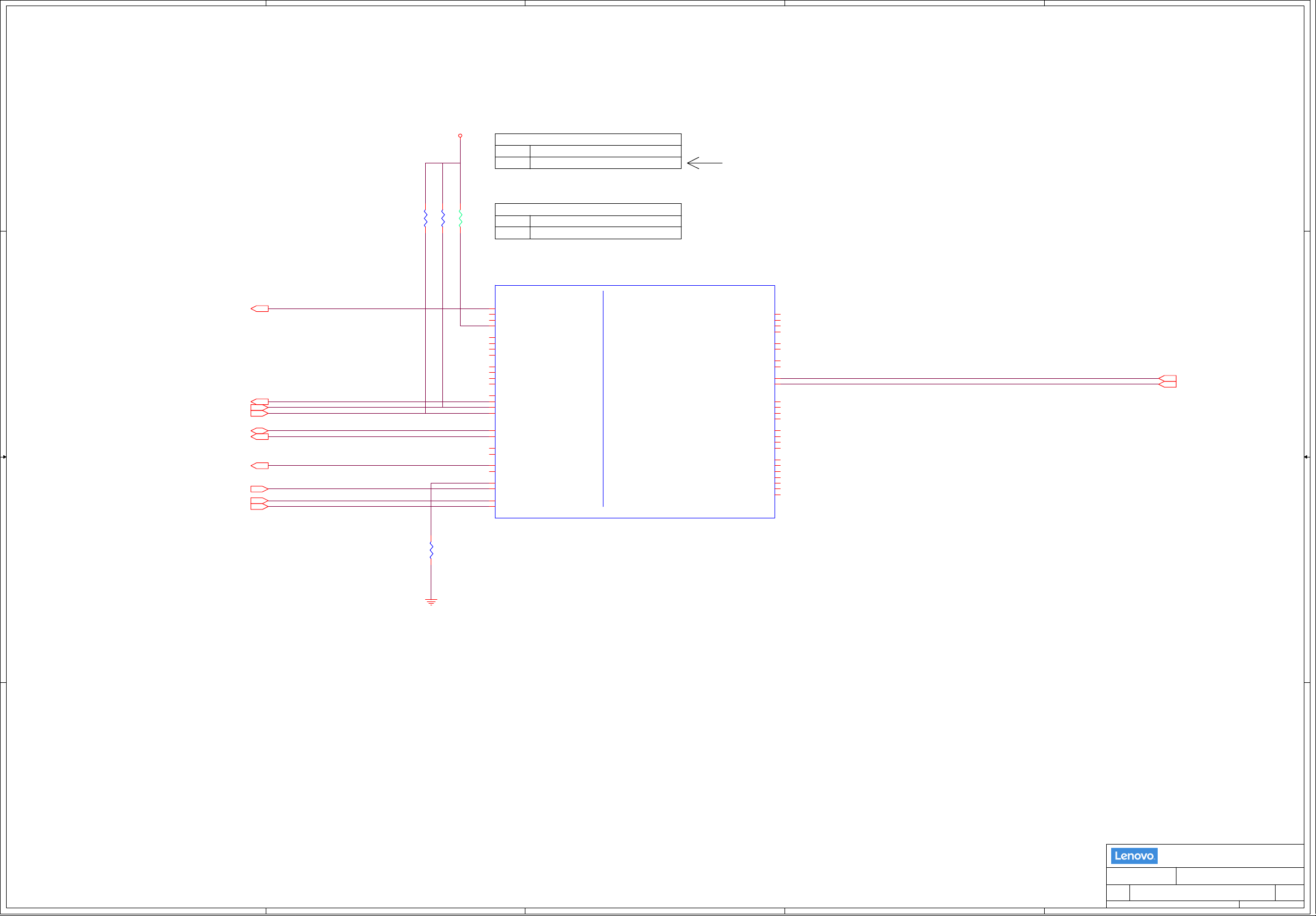

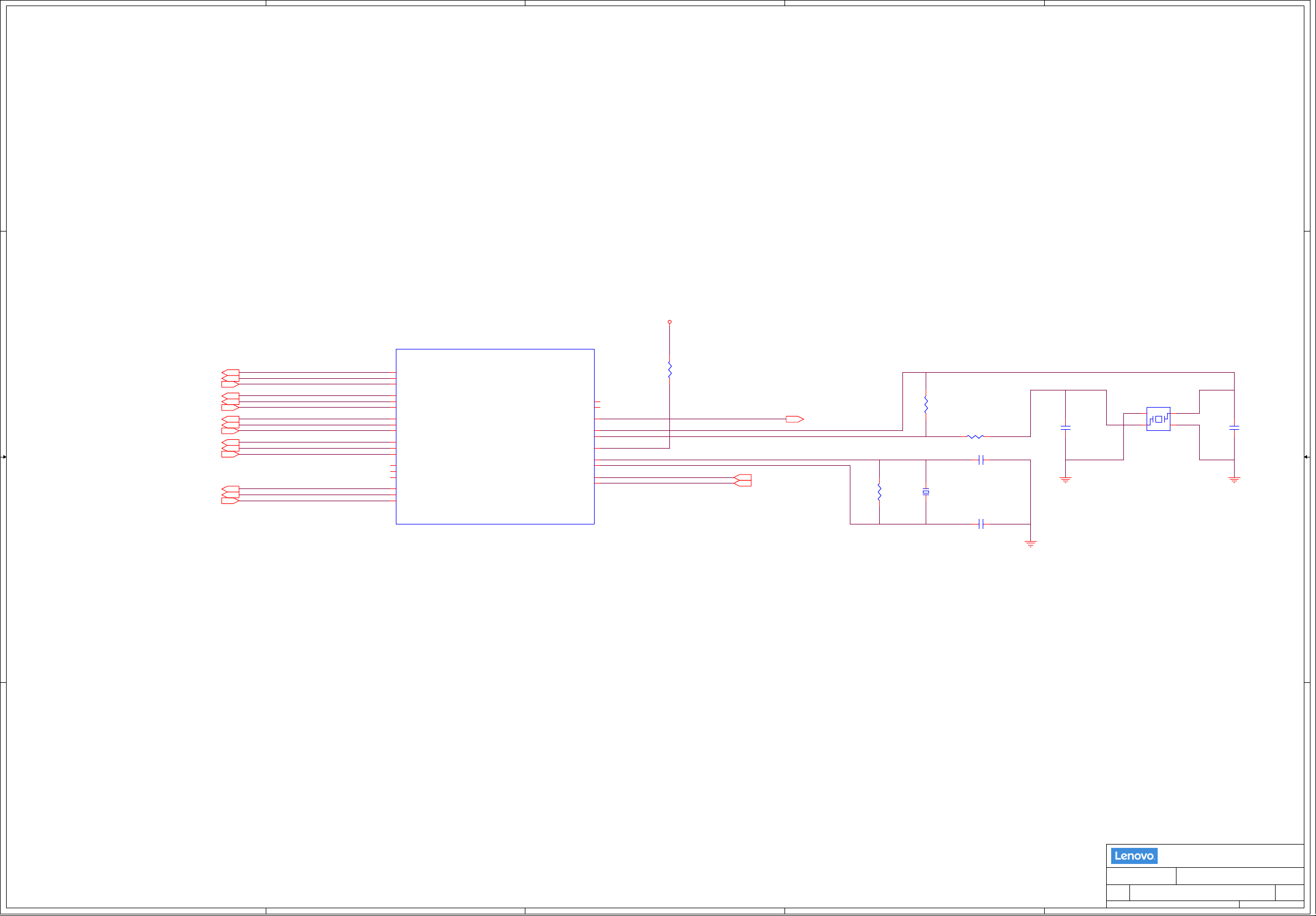

5.CPU(3/16) : DDR CHANNEL-B

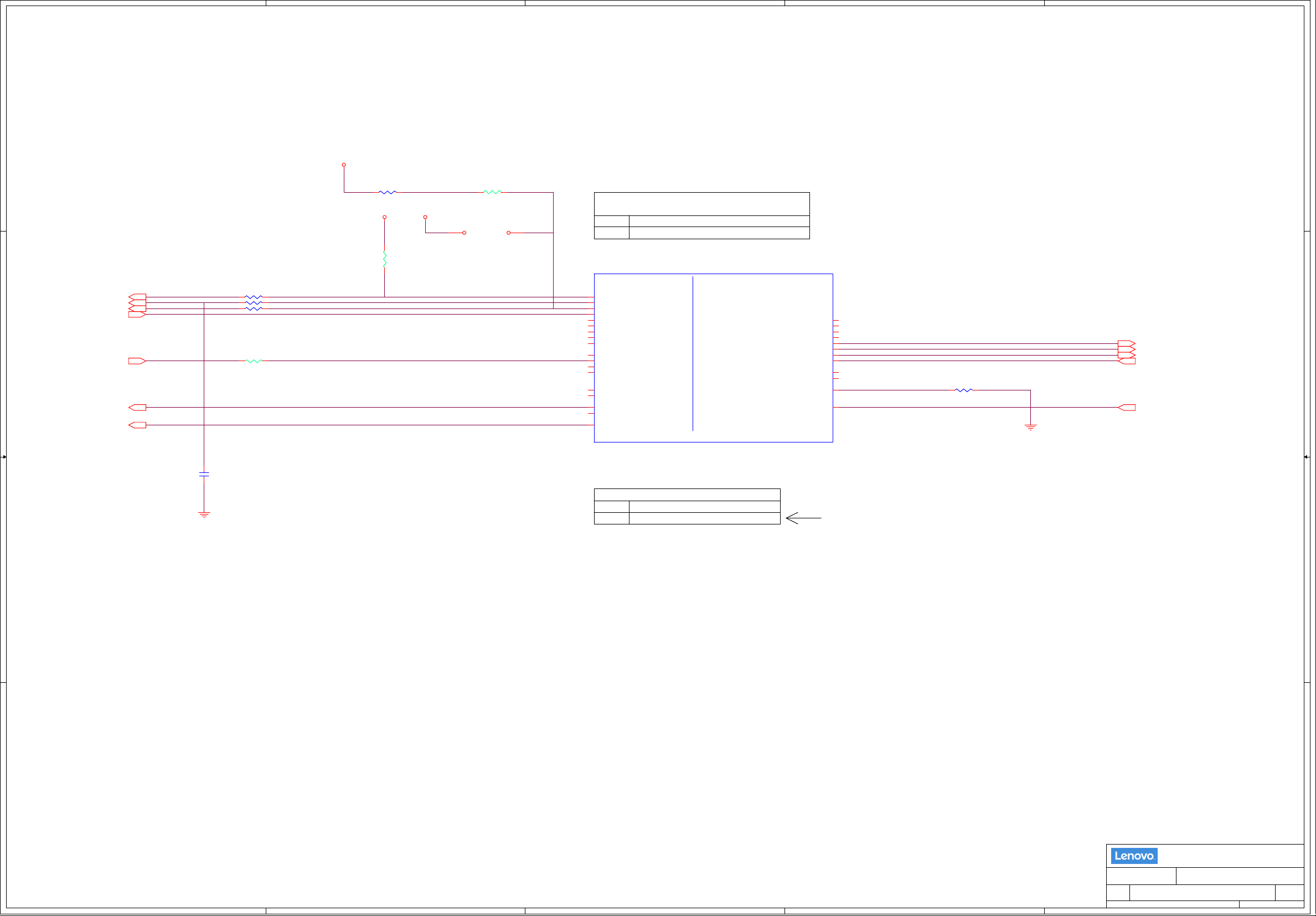

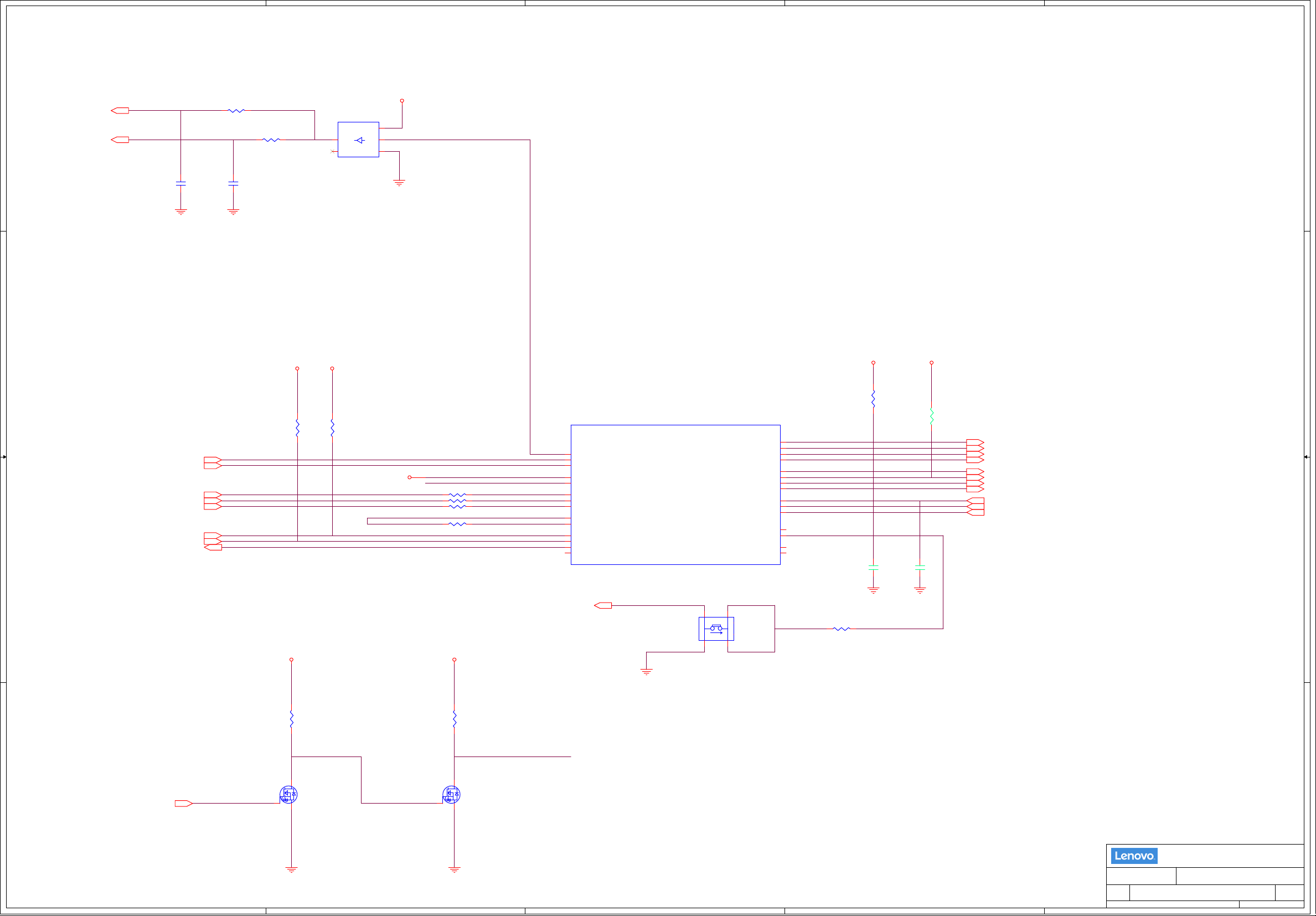

6.CPU(4/16) : MISC/JTAG

7.CPU(5/16) : LPC/SPI/SMBUS/C-LINK

8.CPU(6/16) : LPSS/ISH

9.CPU(7/16) : AUDIO/SDXC

10.CPU(8/16) : PCIE/USB/SATA

11.CPU(9/16) : CSI-2/EMMC

12.CPU(10/16) : CLOCK SIGNALS

C C

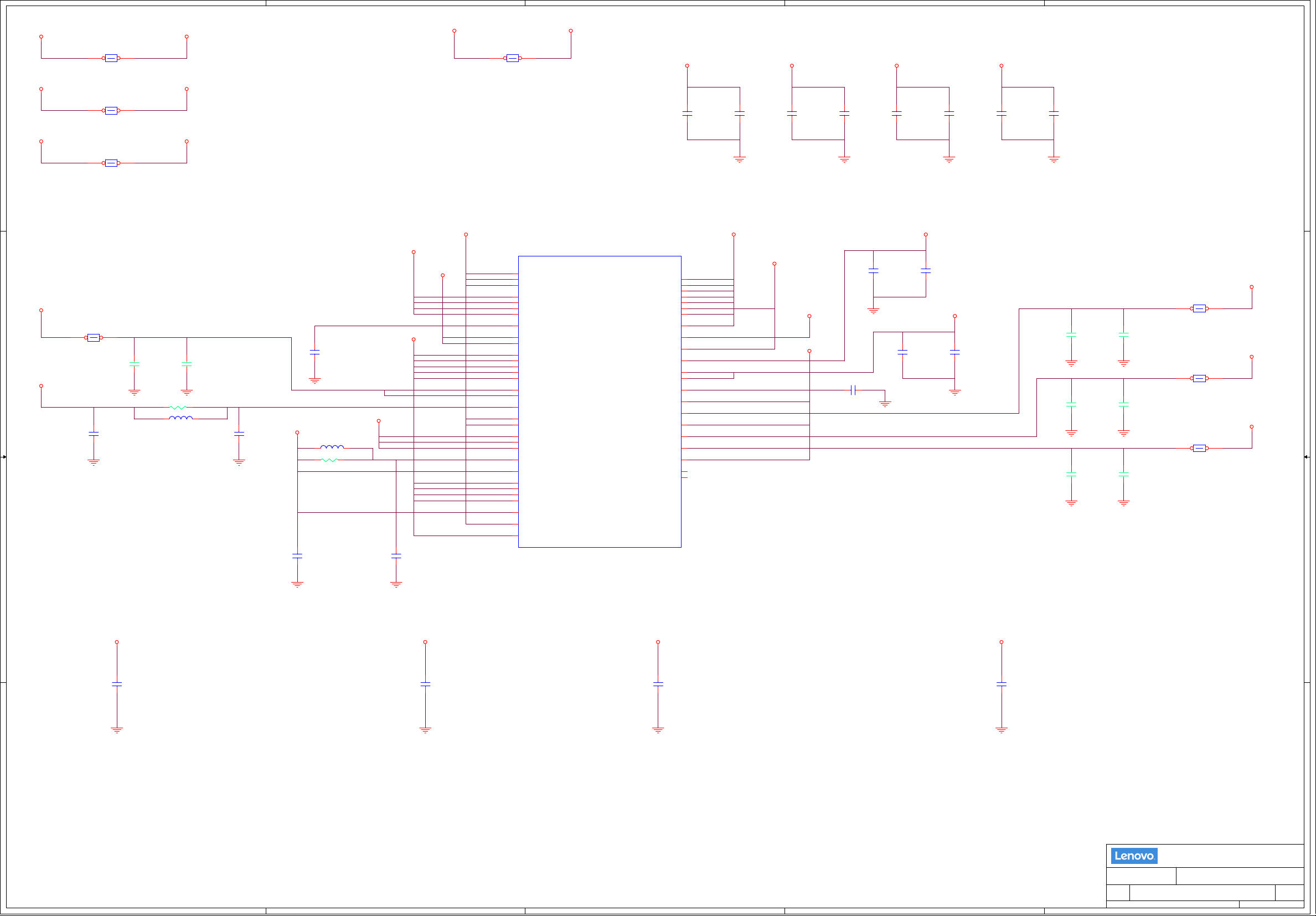

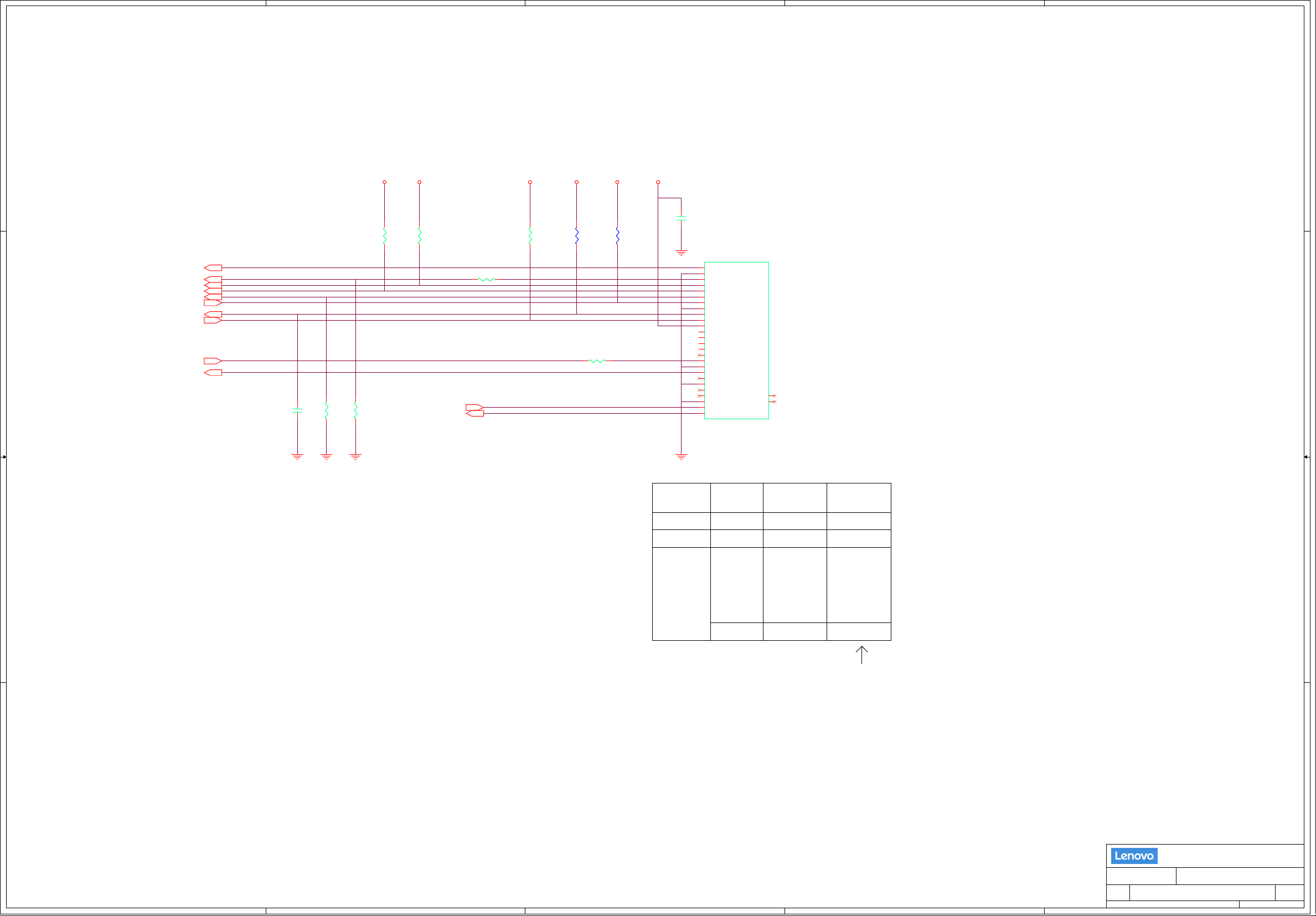

36.USB TYPE-C CONNECTOR

37.HDMI CONNECTOR

38.M.2 SOCKET 3 MODULE I/F

39.USB POWER/CONN

40.BLANK

41.GBE JACKSONVILLE

42.BLANK

43.BLANK

44.BLANK

45.M.2 SOCKET 1 MODULE I/F

46.M.2 SOCKET 2 MODULE I/F

47.MEDIA CARD CONTROLLER

FN1KR-3

VER 4.00

Dec/21/2017

71.DC/DC VCC5M/VCC3M (TPS51285B-1)

72.DC/DC IMVP8 CONTROLLER (MP2949A)

73.DC/DC VCCCPUCORE (MP86902B)

74.DC/DC VCCGFXCORE_I (MP86902B)

75.DC/DC VCCSA (MP86901A)

76.BLANK

77.DC/DC VCCCPUIO

78.DC/DC VCC1R0_SUS (NB693)

79.LOAD SW VCCST & VCCSTG

BASE LOGIC:

Finn-1 SVT VER3.11 Oct/27/2017

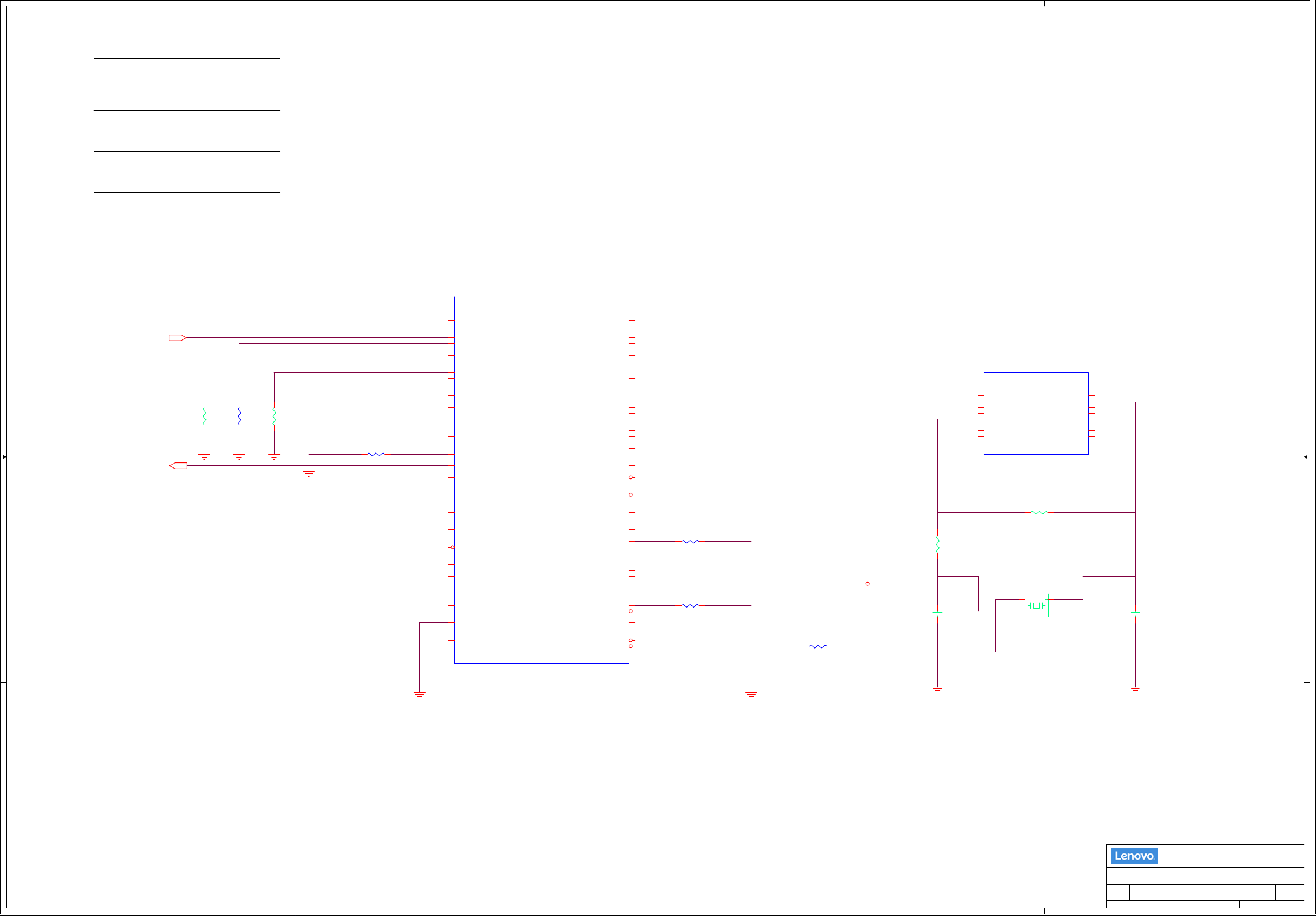

13.CPU(11/16) : SYSTEM PM

14.CPU(12/16) : CPU POWER (1/2)

15.CPU(13/16) : CPU POWER (2/2)

16.CPU(14/16) : PCH POWER

17.CPU(15/16) : GND

18.CPU(16/16) : CFG/RESERVED

19.XDP CONNECTOR

20.RTC BATTERY

21.SPI FLASH

B B

22.DDR4 BASE MEMORY CH-A (1/2)

23.DDR4 BASE MEMORY CH-A (2/2)

24.DDR4 BASE MEMORY CH-B (1/2)

25.DDR4 BASE MEMORY CH-B (2/2)

26.LCD

48.SIM/MEDIA CARD COMBO SLOT

49.AUDIO ALC3287

50.AUDIO CONNECTOR

51.AUDIO JACK SENSE

52.AUDIO EXT MIC I/F

53.AUDIO SPEAKER

54.AUDIO BEEP

55.MEC1663 (1/3)

56.MEC1663 (2/3)

57.MEC1663 (3/3)

58.KEYBOARD/TRACK POINT

59.TOUCH PAD/NFC

60.SCR/FPR/NEC LED

61.FAN CONNECTOR

80.DC/DC VCC1R2A /0R6B/2R5A (NB687)

81.BLANK

82.BLANK

83.DC/DC VCC1R8_SUS (BU90104GWZ)

84.DC/DC VCCPCHCORE

85.BLANK

86.BLANK

87.LOAD SW PCH SUS

88.LOAD SW LAN & LDO HDMI

89.LOAD SW B

90.LOAD SW WLAN

91.PTH FOR SCREW HOLES

27.LID/MIC/CAMERA/PWR SW

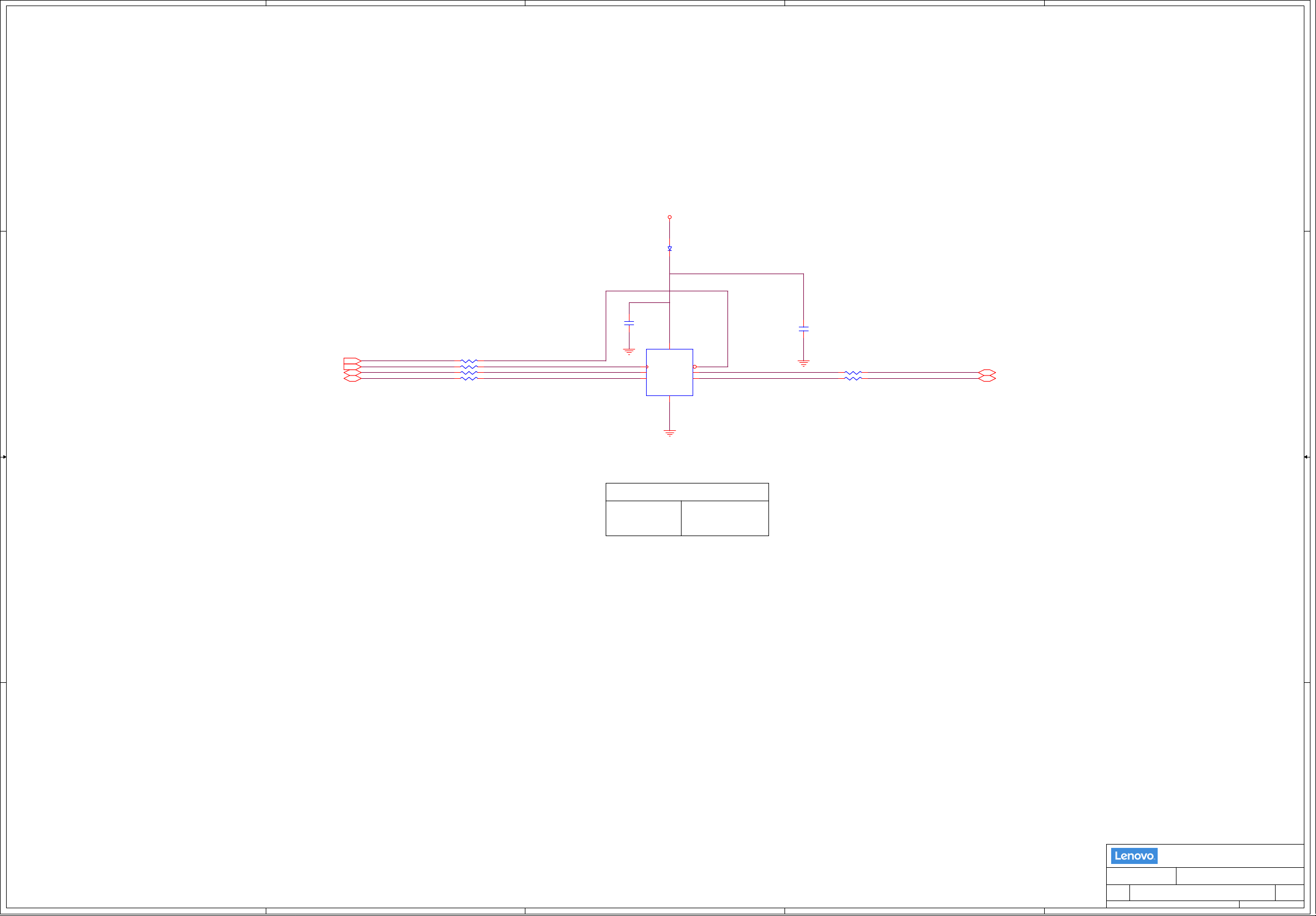

28.DDI DEMUX/HDMI LEVEL SHIFTER

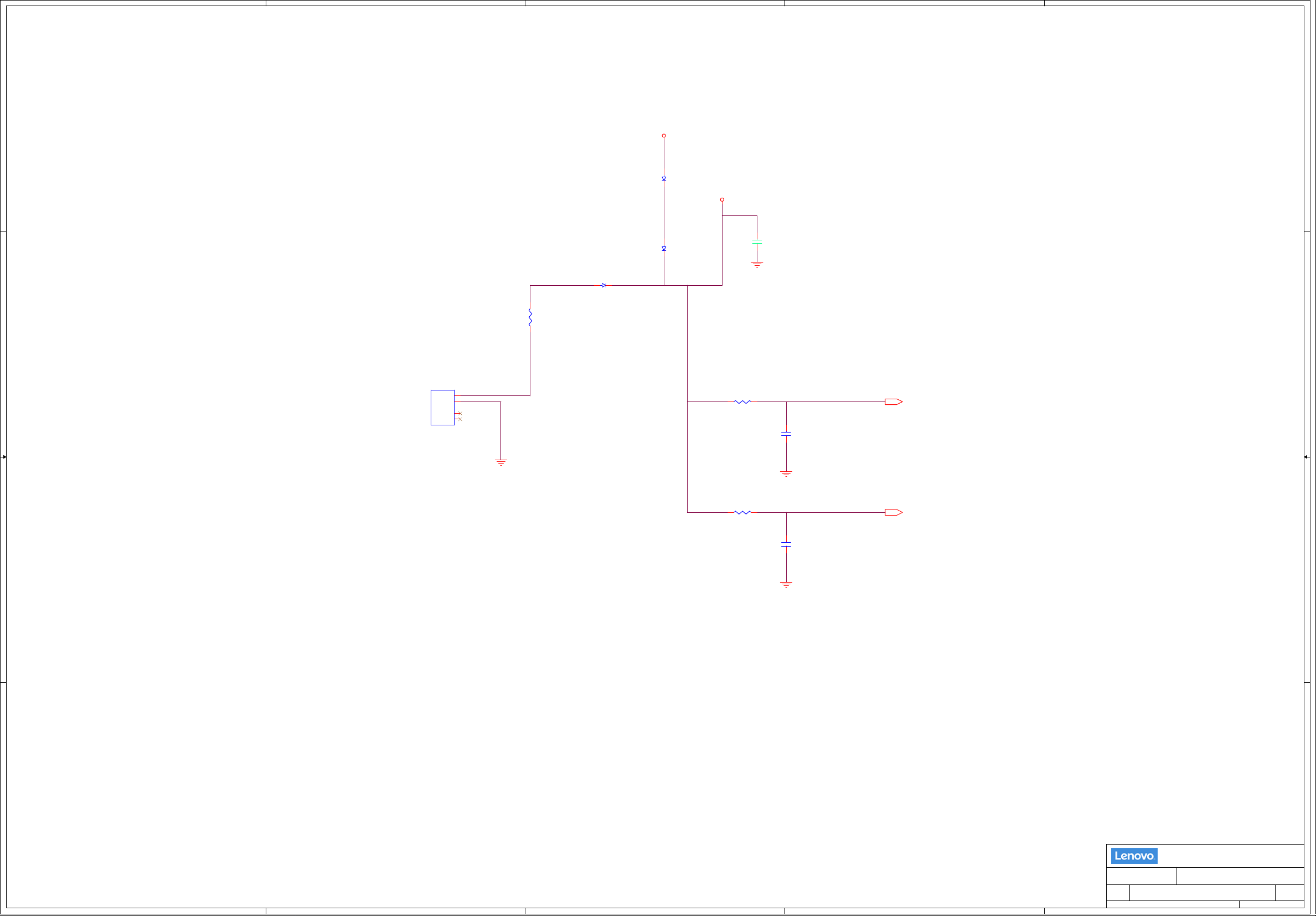

29.USB TYPE-C SWITCH

30.BLANK

31.ALPINE RIDGE(1/2)

A A

32.ALPINE RIDGE(2/2)

33.USB PD CONTROLLER(1/2)

34.USB PD CONTROLLER(2/2)

35.DOCKING CONNECTOR

5

4

62.APS G-SENSOR

63.DISCRETE TPM 2.0

64.SMBUS SWITCH/LPC DEBUG PORT

65.THINK ENGINE-3 (1/2)

66.THINK ENGINE-3 (2/2)

67.DC-IN

68.BLANK

69.BATTERY INPUT

70.BATTERY CHARGER (BQ25700A)

3

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

2

Date: Sheet :

Title :

Title :

Title :

TITLE PAGE

TITLE PAGE

TITLE PAGE

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

191Thursday, December 21, 2017

191Thursday, December 21, 2017

191Thursday, December 21, 2017

5

4

3

2

1

EC HISTORY

FN1KR-3

(BASE LOGIC: Finn-1 SVT VER3.11 Oct/27/2017)

VER.4.00 12/21/2017 APPLIED FN1_SOVP_EC001-006

D D

C C

B B

TABLE: Chip Capacitor Thermal Characteristics

-55 to 150degC

-55 to 125degC

-55 to 125degC

-55 to 105degC

-55 to 85degC

+/-30ppm/degC

+/-30ppm/degC

+/-15%

+/-22%

+/-15%

Code

NPO

C0G

X7R

X6S

X5R

TABLE: Chip Capacitor Tolerance

Tolerance Code

+/-0.25pF

+/-0.5pF

+/-5%

+/-10%

+/-20%

+80/-20%

C

D

J

K

M

Z

TABLE: Chip Part Dimension

Size [mm]

0.40 x 0.20

0.60 x 0.30

1.00 x 0.50

1.60 x 0.80

2.00 x 1.25

2.00 x 1.60

2.50 x 2.00

3.20 x 1.60

3.20 x 2.50

4.50 x 1.60

4.50 x 2.50

4.50 x 3.20

5.00 x 2.50

6.40 x 3.20

mm Size Code Inch Size Code

0402

0603

1005

1608

2125

2016

2520

3216

3225

4516

4525

4532

5025

6432

01005

0201

0402

0603

0805

0806

1008

1206

1210

1806

1810

1812

2010

2512

A A

LOGIC

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

5

4

3

2

Date: Sheet :

Title :

Title :

Title :

EC HISTORY

EC HISTORY

EC HISTORY

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

291Thursday, December 21, 2017

291Thursday, December 21, 2017

291Thursday, December 21, 2017

5

D D

4

VCCCPUIO VCC3_SUS

3

2

1

R5

24.9_1%

0603_1/20w

1 2

DDIP1_0N31

DDIP1_0P31

DDIP1_1N31

DDIP1_1P31

DDIP1_2N31

DDIP1_2P31

DDIP1_3N31

DDIP1_3P31

C C

DDIP2_0N28

DDIP2_0P28

DDIP2_1N28

DDIP2_1P28

DDIP2_2N28

DDIP2_2P28

DDIP2_3N28

DDIP2_3P28

DDIP1_0N

DDIP1_0P

DDIP1_1N

DDIP1_1P

DDIP1_2N

DDIP1_2P

DDIP1_3N

DDIP1_3P

DDIP2_0N

DDIP2_0P

DDIP2_1N

DDIP2_1P

DDIP2_2N

DDIP2_2P

DDIP2_3N

DDIP2_3P

TABLE : Functional Strap

DDIP2_CTRLCLK

DDIP2_CTRLDATA

EDP_COMP

DDPB_CTRLDATA

HIGH

LOW

Port B is detected.

Port B is not detected.

DDIP2_CTRLCLK28

DDIP2_CTRLDATA28

DDPC_CTRLDATA

HIGH

LOW

Port C is detected.

Port C is not detected.

R3069

2.2K_5%

0603_1/20w

1 2

U58A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22

N12

GPP_E23

E52

EDP_RCOMP

SKYLAKE_ULT_DDR3L_REV053F

DDI

DISPLAY SIDEBANDS

1 OF 20

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD_G46

RSVD_F46

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

R433

100K_5%

0603_1/20w

1 2

R138

100K_5%

0603_1/20w

1 2

R8

100K_5%

0603_1/20w

1 2

R2917

100K_5%

0603_1/20w

1 2

R2914

100K_5%

0603_1/20w

1 2

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_AUXN

EDP_AUXP

DDIP1_AUXN

DDIP1_AUXP

DDIP2_AUXN

DDIP2_AUXP

DDIP1_HPD

DDIP2_HPD

EDP_TXN0 26

EDP_TXP0 26

EDP_TXN1 26

EDP_TXP1 26

EDP_AUXN 26

EDP_AUXP 26

DDIP1_AUXN 31

DDIP1_AUXP 31

DDIP2_AUXN 28

DDIP2_AUXP 28

DDIP1_HPD 31

DDIP2_HPD 28

EDP_HPD 26

VGA_BLON 55

PANEL_BKLT_CTRL 26

PANEL_POWER_ON 66

B B

A A

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

5

4

3

2

Date: Sheet :

Title :

Title :

Title :

CPU(1/16) : DDI/EDP

CPU(1/16) : DDI/EDP

CPU(1/16) : DDI/EDP

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

391Thursday, December 21, 2017

391Thursday, December 21, 2017

391Thursday, December 21, 2017

5

M_A_DQ[15:0]22

M_A_DQ[47:32]22

M_B_DQ[15:0]24

D D

M_B_DQ[47:32]24

4

3

2

1

TABLE

Pin

AL71

AL68

AN68

AN69

AL70

AL69

AN70

Block 0

AN71

AR70

AR68

AU71

AU68

AR71

AR69

AU70

AU69

C C

BB65

AW65

AW63

AY63

BA65

AY65

BA63

Block 2

BB63

BA61

AW61

BB59

AW59

BB61

AY61

BA59

AY59

AY39

AW39

AY37

AW37

B B

BB39

BA39

BA37

Block 4

BB37

AY35

AW35

AY33

AW33

BB35

BA35

BA33

BB33

AY31

AW31

AY29

AW29

BB31

BA31

BA29

Block 6

A A

BB29

AY27

AW27

AY25

AW25

BB27

BA27

BA25

BB25

Interleave

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[16]

DDR0_DQ[17]

DDR0_DQ[18]

DDR0_DQ[19]

DDR0_DQ[20]

DDR0_DQ[21]

DDR0_DQ[22]

DDR0_DQ[23]

DDR0_DQ[24]

DDR0_DQ[25]

DDR0_DQ[26]

DDR0_DQ[27]

DDR0_DQ[28]

DDR0_DQ[29]

DDR0_DQ[30]

DDR0_DQ[31]

DDR0_DQ[32]

DDR0_DQ[33]

DDR0_DQ[34]

DDR0_DQ[35]

DDR0_DQ[36]

DDR0_DQ[37]

DDR0_DQ[38]

DDR0_DQ[39]

DDR0_DQ[40]

DDR0_DQ[41]

DDR0_DQ[42]

DDR0_DQ[43]

DDR0_DQ[44]

DDR0_DQ[45]

DDR0_DQ[46]

DDR0_DQ[47]

DDR0_DQ[48]

DDR0_DQ[49]

DDR0_DQ[50]

DDR0_DQ[51]

DDR0_DQ[52]

DDR0_DQ[53]

DDR0_DQ[54]

DDR0_DQ[55]

DDR0_DQ[56]

DDR0_DQ[57]

DDR0_DQ[58]

DDR0_DQ[59]

DDR0_DQ[60]

DDR0_DQ[61]

DDR0_DQ[62]

DDR0_DQ[63]

5

Non-Interleave

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[32]

DDR0_DQ[33]

DDR0_DQ[34]

DDR0_DQ[35]

DDR0_DQ[36]

DDR0_DQ[37]

DDR0_DQ[38]

DDR0_DQ[39]

DDR0_DQ[40]

DDR0_DQ[41]

DDR0_DQ[42]

DDR0_DQ[43]

DDR0_DQ[44]

DDR0_DQ[45]

DDR0_DQ[46]

DDR0_DQ[47]

DDR1_DQ[0]

DDR1_DQ[1]

DDR1_DQ[2]

DDR1_DQ[3]

DDR1_DQ[4]

DDR1_DQ[5]

DDR1_DQ[6]

DDR1_DQ[7]

DDR1_DQ[8]

DDR1_DQ[9]

DDR1_DQ[10]

DDR1_DQ[11]

DDR1_DQ[12]

DDR1_DQ[13]

DDR1_DQ[14]

DDR1_DQ[15]

DDR1_DQ[32]

DDR1_DQ[33]

DDR1_DQ[34]

DDR1_DQ[35]

DDR1_DQ[36]

DDR1_DQ[37]

DDR1_DQ[38]

DDR1_DQ[39]

DDR1_DQ[40]

DDR1_DQ[41]

DDR1_DQ[42]

DDR1_DQ[43]

DDR1_DQ[44]

DDR1_DQ[45]

DDR1_DQ[46]

DDR1_DQ[47]

LOGIC

M_A_DQ4

M_A_DQ6

M_A_DQ1

M_A_DQ7

M_A_DQ2

M_A_DQ0

M_A_DQ5

M_A_DQ3

M_A_DQ12

M_A_DQ14

M_A_DQ9

M_A_DQ13

M_A_DQ10

M_A_DQ8

M_A_DQ11

M_A_DQ15

M_A_DQ34

M_A_DQ32

M_A_DQ39

M_A_DQ35

M_A_DQ38

M_A_DQ36

M_A_DQ37

M_A_DQ33

M_A_DQ46

M_A_DQ40

M_A_DQ47

M_A_DQ45

M_A_DQ42

M_A_DQ44

M_A_DQ43

M_A_DQ41

M_B_DQ4

M_B_DQ6

M_B_DQ5

M_B_DQ1

M_B_DQ2

M_B_DQ0

M_B_DQ3

M_B_DQ7

M_B_DQ10

M_B_DQ14

M_B_DQ15

M_B_DQ13

M_B_DQ12

M_B_DQ8

M_B_DQ11

M_B_DQ9

M_B_DQ34

M_B_DQ32

M_B_DQ37

M_B_DQ33

M_B_DQ36

M_B_DQ38

M_B_DQ35

M_B_DQ39

M_B_DQ42

M_B_DQ46

M_B_DQ47

M_B_DQ45

M_B_DQ40

M_B_DQ44

M_B_DQ43

M_B_DQ41

4

AL71

AL68

AN68

AN69

AL70

AL69

AN70

AN71

AR70

AR68

AU71

AU68

AR71

AR69

AU70

AU69

BB65

AW65

AW63

AY63

BA65

AY65

BA63

BB63

BA61

AW61

BB59

AW59

BB61

AY61

BA59

AY59

AY39

AW39

AY37

AW37

BB39

BA39

BA37

BB37

AY35

AW35

AY33

AW33

BB35

BA35

BA33

BB33

AY31

AW31

AY29

AW29

BB31

BA31

BA29

BB29

AY27

AW27

AY25

AW25

BB27

BA27

BA25

BB25

TABLE

Block 0

Block 2

Block 4

Block 6

U58B

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[16]/DDR0_DQ[32]

DDR0_DQ[17]/DDR0_DQ[33]

DDR0_DQ[18]/DDR0_DQ[34]

DDR0_DQ[19]/DDR0_DQ[35]

DDR0_DQ[20]/DDR0_DQ[36]

DDR0_DQ[21]/DDR0_DQ[37]

DDR0_DQ[22]/DDR0_DQ[38]

DDR0_DQ[23]/DDR0_DQ[39]

DDR0_DQ[24]/DDR0_DQ[40]

DDR0_DQ[25]/DDR0_DQ[41]

DDR0_DQ[26]/DDR0_DQ[42]

DDR0_DQ[27]/DDR0_DQ[43]

DDR0_DQ[28]/DDR0_DQ[44]

DDR0_DQ[29]/DDR0_DQ[45]

DDR0_DQ[30]/DDR0_DQ[46]

DDR0_DQ[31]/DDR0_DQ[47]

DDR0_DQ[32]/DDR1_DQ[0]

DDR0_DQ[33]/DDR1_DQ[1]

DDR0_DQ[34]/DDR1_DQ[2]

DDR0_DQ[35]/DDR1_DQ[3]

DDR0_DQ[36]/DDR1_DQ[4]

DDR0_DQ[37]/DDR1_DQ[5]

DDR0_DQ[38]/DDR1_DQ[6]

DDR0_DQ[39]/DDR1_DQ[7]

DDR0_DQ[40]/DDR1_DQ[8]

DDR0_DQ[41]/DDR1_DQ[9]

DDR0_DQ[42]/DDR1_DQ[10]

DDR0_DQ[43]/DDR1_DQ[11]

DDR0_DQ[44]/DDR1_DQ[12]

DDR0_DQ[45]/DDR1_DQ[13]

DDR0_DQ[46]/DDR1_DQ[14]

DDR0_DQ[47]/DDR1_DQ[15]

DDR0_DQ[48]/DDR1_DQ[32]

DDR0_DQ[49]/DDR1_DQ[33]

DDR0_DQ[50]/DDR1_DQ[34]

DDR0_DQ[51]/DDR1_DQ[35]

DDR0_DQ[52]/DDR1_DQ[36]

DDR0_DQ[53]/DDR1_DQ[37]

DDR0_DQ[54]/DDR1_DQ[38]

DDR0_DQ[55]/DDR1_DQ[39]

DDR0_DQ[56]/DDR1_DQ[40]

DDR0_DQ[57]/DDR1_DQ[41]

DDR0_DQ[58]/DDR1_DQ[42]

DDR0_DQ[59]/DDR1_DQ[43]

DDR0_DQ[60]/DDR1_DQ[44]

DDR0_DQ[61]/DDR1_DQ[45]

DDR0_DQ[62]/DDR1_DQ[46]

DDR0_DQ[63]/DDR1_DQ[47]

SKYLAKE_ULT_DDR3L_REV053F

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_DQSN[2]

DDR0_DQSP[2]

DDR0_DQSN[3]

DDR0_DQSP[3]

DDR0_DQSN[4]

DDR0_DQSP[4]

DDR0_DQSN[5]

DDR0_DQSP[5]

DDR0_DQSN[6]

DDR0_DQSP[6]

DDR0_DQSN[7]

DDR0_DQSP[7]

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

2 OF 20

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_PAR

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

InterleavePin Non-Interleave

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_DQSN[4]

DDR0_DQSP[4]

DDR0_DQSN[5]

DDR0_DQSP[5]

DDR1_DQSN[0]

DDR1_DQSP[0]

DDR1_DQSN[1]

DDR1_DQSP[1]

DDR1_DQSN[4]

DDR1_DQSP[4]

DDR1_DQSN[5]

DDR1_DQSP[5]

LOGIC

3

M_A_A5

M_A_A9

M_A_A6

M_A_A8

M_A_A7

M_A_A12

M_A_A11

M_A_A13

M_A_A15

M_A_A14

M_A_A16

M_A_A2

M_A_A10

M_A_A1

M_A_A0

M_A_A3

M_A_A4

DDR_PG_CTRL

-M_A_DDRCLK0_1200M

M_A_DDRCLK0_1200M

M_A_CKE0

-M_A_CS0

M_A_ODT0

-M_A_DQS0

M_A_DQS0

-M_A_DQS1

M_A_DQS1

-M_A_DQS4

M_A_DQS4

-M_A_DQS5

M_A_DQS5

-M_B_DQS0

M_B_DQS0

-M_B_DQS1

M_B_DQS1

-M_B_DQS4

M_B_DQS4

-M_B_DQS5

M_B_DQS5

-M_A_ALERT

M_A_PARITY

VCC1R2A

NA

R1858

10K_5%

0603_1/20w

1 2

-M_A_DDRCLK0_1200M 22,23

M_A_DDRCLK0_1200M 22,23

M_A_CKE0 22,23

-M_A_CS0 22,23

M_A_ODT0 22,23

-M_A_ALERT 22,23

M_A_PARITY 22,23

M_A_VREF_CA_CPU 23

M_B_VREF_CA_CPU 25

VCC3M

R1838

100K_5%

0603_1/20w

1 2

3

1

2

Q170

DTC015TM

M_A_BG0

-M_A_ACT

M_A_BG1

M_A_BS0

M_A_BS1

DDR_VTT_PG_CTRL

2

M_A_BG0 22,23

-M_A_ACT 22,23

M_A_BG1 22

M_A_BS0 22,23

M_A_BS1 22,23

M_A_A[16:0] 22,23

-M_A_DQS[7:0] 5,22

M_A_DQS[7:0] 5,22

-M_B_DQS[7:0] 5,24

M_B_DQS[7:0] 5,24

DDR_VTT_PG_CTRL 80

TABLE

Pin

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

DDR3L LPDDR3 DDR4

DDR0_MA[5]

DDR0_MA[9]

DDR0_MA[6]

DDR0_MA[8]

DDR0_MA[7]

DDR0_BA[2]

DDR0_MA[12]

DDR0_MA[11]

DDR0_MA[15]

DDR0_MA[14]

DDR0_MA[13]

DDR0_CAS#

DDR0_WE#

DDR0_RAS#

DDR0_BA[0]

DDR0_MA[2]

DDR0_BA[1]

DDR0_MA[10]

DDR0_MA[1]

DDR0_MA[0]

DDR0_MA[3]

DDR0_MA[4]

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Size :

Size :

Size :

Date: Sheet :

Date: Sheet :

Date: Sheet :

Document Number :

Document Number :

Document Number :

C

DDR0_CAA[0]

DDR0_CAA[1]

DDR0_CAA[2]

DDR0_CAA[3]

DDR0_CAA[4]

DDR0_CAA[5]

DDR0_CAA[6]

DDR0_CAA[7]

DDR0_CAA[8]

DDR0_CAA[9]

DDR0_CAB[0]

DDR0_CAB[1]

DDR0_CAB[2]

DDR0_CAB[3]

DDR0_CAB[4]

DDR0_CAB[5]

DDR0_CAB[6]

DDR0_CAB[7]

DDR0_CAB[8]

DDR0_CAB[9]

Not Used

Not Used

Title :

Title :

Title :

CPU(2/16) : DDR CHANNEL-A

CPU(2/16) : DDR CHANNEL-A

CPU(2/16) : DDR CHANNEL-A

1

DDR0_MA[5]

DDR0_MA[9]

DDR0_MA[6]

DDR0_MA[8]

DDR0_MA[7]

DDR0_BG[0]

DDR0_MA[12]

DDR0_MA[11]

DDR0_ACT#

DDR0_BG[1]

DDR0_MA[13]

DDR0_MA[15]

DDR0_MA[14]

DDR0_MA[16]

DDR0_BA[0]

DDR0_MA[2]

DDR0_BA[1]

DDR0_MA[10]

DDR0_MA[1]

DDR0_MA[0]

DDR0_MA[3]

DDR0_MA[4]

LOGIC

491Thursday, December 21, 2017

491Thursday, December 21, 2017

491Thursday, December 21, 2017

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

5

M_A_DQ[31:16]22

M_A_DQ[63:48]22

M_B_DQ[31:16]24

D D

M_B_DQ[63:48]24

4

3

2

1

TABLE

Pin

AF65

AF64

AK65

AK64

AF66

AF67

AK67

Block 1

AK66

AF70

AF68

AH71

AH68

AF71

AF69

AH70

AH69

C C

AT66

AU66

AP65

AN65

AN66

AP66

AT65

Block 3

AU65

AT61

AU61

AP60

AN60

AN61

AP61

AT60

AU60

AU40

AT40

AT37

AU37

B B

AR40

AP40

AP37

Block 5

AR37

AT33

AU33

AU30

AT30

AR33

AP33

AR30

AP30

AU27

AT27

AT25

AU25

AP27

AN27

AN25

Block 7

A A

AP25

AT22

AU22

AU21

AT21

AN22

AP22

AP21

AN21

Interleave

DDR1_DQ[0]

DDR1_DQ[1]

DDR1_DQ[2]

DDR1_DQ[3]

DDR1_DQ[4]

DDR1_DQ[5]

DDR1_DQ[6]

DDR1_DQ[7]

DDR1_DQ[8]

DDR1_DQ[9]

DDR1_DQ[10]

DDR1_DQ[11]

DDR1_DQ[12]

DDR1_DQ[13]

DDR1_DQ[14]

DDR1_DQ[15]

DDR1_DQ[16]

DDR1_DQ[17]

DDR1_DQ[18]

DDR1_DQ[19]

DDR1_DQ[20]

DDR1_DQ[21]

DDR1_DQ[22]

DDR1_DQ[23]

DDR1_DQ[24]

DDR1_DQ[25]

DDR1_DQ[26]

DDR1_DQ[27]

DDR1_DQ[28]

DDR1_DQ[29]

DDR1_DQ[30]

DDR1_DQ[31]

DDR1_DQ[32]

DDR1_DQ[33]

DDR1_DQ[34]

DDR1_DQ[35]

DDR1_DQ[36]

DDR1_DQ[37]

DDR1_DQ[38]

DDR1_DQ[39]

DDR1_DQ[40]

DDR1_DQ[41]

DDR1_DQ[42]

DDR1_DQ[43]

DDR1_DQ[44]

DDR1_DQ[45]

DDR1_DQ[46]

DDR1_DQ[47]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

5

Non-Interleave

DDR0_DQ[16]

DDR0_DQ[17]

DDR0_DQ[18]

DDR0_DQ[19]

DDR0_DQ[20]

DDR0_DQ[21]

DDR0_DQ[22]

DDR0_DQ[23]

DDR0_DQ[24]

DDR0_DQ[25]

DDR0_DQ[26]

DDR0_DQ[27]

DDR0_DQ[28]

DDR0_DQ[29]

DDR0_DQ[30]

DDR0_DQ[31]

DDR0_DQ[48]

DDR0_DQ[49]

DDR0_DQ[50]

DDR0_DQ[51]

DDR0_DQ[52]

DDR0_DQ[53]

DDR0_DQ[54]

DDR0_DQ[55]

DDR0_DQ[56]

DDR0_DQ[57]

DDR0_DQ[58]

DDR0_DQ[59]

DDR0_DQ[60]

DDR0_DQ[61]

DDR0_DQ[62]

DDR0_DQ[63]

DDR1_DQ[16]

DDR1_DQ[17]

DDR1_DQ[18]

DDR1_DQ[19]

DDR1_DQ[20]

DDR1_DQ[21]

DDR1_DQ[22]

DDR1_DQ[23]

DDR1_DQ[24]

DDR1_DQ[25]

DDR1_DQ[26]

DDR1_DQ[27]

DDR1_DQ[28]

DDR1_DQ[29]

DDR1_DQ[30]

DDR1_DQ[31]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

LOGIC

M_A_DQ20

M_A_DQ22

M_A_DQ21

M_A_DQ17

M_A_DQ18

M_A_DQ16

M_A_DQ23

M_A_DQ19

M_A_DQ26

M_A_DQ24

M_A_DQ31

M_A_DQ29

M_A_DQ30

M_A_DQ28

M_A_DQ27

M_A_DQ25

M_A_DQ50

M_A_DQ48

M_A_DQ53

M_A_DQ49

M_A_DQ54

M_A_DQ52

M_A_DQ51

M_A_DQ55

M_A_DQ62

M_A_DQ58

M_A_DQ63

M_A_DQ61

M_A_DQ56

M_A_DQ60

M_A_DQ57

M_A_DQ59

M_B_DQ16

M_B_DQ20

M_B_DQ19

M_B_DQ23

M_B_DQ22

M_B_DQ18

M_B_DQ17

M_B_DQ21

M_B_DQ26

M_B_DQ30

M_B_DQ31

M_B_DQ29

M_B_DQ28

M_B_DQ24

M_B_DQ27

M_B_DQ25

M_B_DQ48

M_B_DQ50

M_B_DQ51

M_B_DQ55

M_B_DQ52

M_B_DQ54

M_B_DQ49

M_B_DQ53

M_B_DQ60

M_B_DQ56

M_B_DQ58

M_B_DQ62

M_B_DQ63

M_B_DQ61

M_B_DQ57

M_B_DQ59

4

AF65

AF64

AK65

AK64

AF66

AF67

AK67

AK66

AF70

AF68

AH71

AH68

AF71

AF69

AH70

AH69

AT66

AU66

AP65

AN65

AN66

AP66

AT65

AU65

AT61

AU61

AP60

AN60

AN61

AP61

AT60

AU60

AU40

AT40

AT37

AU37

AR40

AP40

AP37

AR37

AT33

AU33

AU30

AT30

AR33

AP33

AR30

AP30

AU27

AT27

AT25

AU25

AP27

AN27

AN25

AP25

AT22

AU22

AU21

AT21

AN22

AP22

AP21

AN21

TABLE

Block 1

Block 3

Block 5

Block 7

U58C

DDR1_DQ[0]/DDR0_DQ[16]

DDR1_DQ[1]/DDR0_DQ[17]

DDR1_DQ[2]/DDR0_DQ[18]

DDR1_DQ[3]/DDR0_DQ[19]

DDR1_DQ[4]/DDR0_DQ[20]

DDR1_DQ[5]/DDR0_DQ[21]

DDR1_DQ[6]/DDR0_DQ[22]

DDR1_DQ[7]/DDR0_DQ[23]

DDR1_DQ[8]/DDR0_DQ[24]

DDR1_DQ[9]/DDR0_DQ[25]

DDR1_DQ[10]/DDR0_DQ[26]

DDR1_DQ[11]/DDR0_DQ[27]

DDR1_DQ[12]/DDR0_DQ[28]

DDR1_DQ[13]/DDR0_DQ[29]

DDR1_DQ[14]/DDR0_DQ[30]

DDR1_DQ[15]/DDR0_DQ[31]

DDR1_DQ[16]/DDR0_DQ[48]

DDR1_DQ[17]/DDR0_DQ[49]

DDR1_DQ[18]/DDR0_DQ[50]

DDR1_DQ[19]/DDR0_DQ[51]

DDR1_DQ[20]/DDR0_DQ[52]

DDR1_DQ[21]/DDR0_DQ[53]

DDR1_DQ[22]/DDR0_DQ[54]

DDR1_DQ[23]/DDR0_DQ[55]

DDR1_DQ[24]/DDR0_DQ[56]

DDR1_DQ[25]/DDR0_DQ[57]

DDR1_DQ[26]/DDR0_DQ[58]

DDR1_DQ[27]/DDR0_DQ[59]

DDR1_DQ[28]/DDR0_DQ[60]

DDR1_DQ[29]/DDR0_DQ[61]

DDR1_DQ[30]/DDR0_DQ[62]

DDR1_DQ[31]/DDR0_DQ[63]

DDR1_DQ[32]/DDR1_DQ[16]

DDR1_DQ[33]/DDR1_DQ[17]

DDR1_DQ[34]/DDR1_DQ[18]

DDR1_DQ[35]/DDR1_DQ[19]

DDR1_DQ[36]/DDR1_DQ[20]

DDR1_DQ[37]/DDR1_DQ[21]

DDR1_DQ[38]/DDR1_DQ[22]

DDR1_DQ[39]/DDR1_DQ[23]

DDR1_DQ[40]/DDR1_DQ[24]

DDR1_DQ[41]/DDR1_DQ[25]

DDR1_DQ[42]/DDR1_DQ[26]

DDR1_DQ[43]/DDR1_DQ[27]

DDR1_DQ[44]/DDR1_DQ[28]

DDR1_DQ[45]/DDR1_DQ[29]

DDR1_DQ[46]/DDR1_DQ[30]

DDR1_DQ[47]/DDR1_DQ[31]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

SKYLAKE_ULT_DDR3L_REV053F

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

DDR1_DQSN[0]

DDR1_DQSP[0]

DDR1_DQSN[1]

DDR1_DQSP[1]

DDR1_DQSN[2]

DDR1_DQSP[2]

DDR1_DQSN[3]

DDR1_DQSP[3]

DDR1_DQSN[4]

DDR1_DQSP[4]

DDR1_DQSN[5]

DDR1_DQSP[5]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

3 OF 20

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

InterleavePin Non-Interleave

DDR0_DQSN[2]

DDR0_DQSP[2]

DDR0_DQSN[3]

DDR0_DQSP[3]

DDR0_DQSN[6]

DDR0_DQSP[6]

DDR0_DQSN[7]

DDR0_DQSP[7]

DDR1_DQSN[2]

DDR1_DQSP[2]

DDR1_DQSN[3]

DDR1_DQSP[3]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

LOGIC

3

-M_B_DDRCLK0_1200M

M_B_DDRCLK0_1200M

M_B_CKE0

-M_B_CS0

M_B_ODT0

M_B_A5

M_B_A9

M_B_A6

M_B_A8

M_B_A7

M_B_A12

M_B_A11

M_B_A13

M_B_A15

M_B_A14

M_B_A16

M_B_A2

M_B_A10

M_B_A1

M_B_A0

M_B_A3

M_B_A4

-M_A_DQS2

M_A_DQS2

-M_A_DQS3

M_A_DQS3

-M_A_DQS6

M_A_DQS6

-M_A_DQS7

M_A_DQS7

-M_B_DQS2

M_B_DQS2

-M_B_DQS3

M_B_DQS3

-M_B_DQS6

M_B_DQS6

-M_B_DQS7

M_B_DQS7

1 2

R7 200_1% 0603_1/20w

1 2

R84 80.6_1% 0603_1/20w

1 2

R576 100_1% 0603_1/20w

TABLE:

R7 200_1% 121_1%

-M_B_DDRCLK0_1200M 24,25

M_B_DDRCLK0_1200M 24,25

M_B_CKE0 24,25

-M_B_CS0 24,25

M_B_ODT0 24,25

M_B_BG0

-M_B_ACT

M_B_BG1

M_B_BS0

M_B_BS1

VCC1R2A

R1726

470_5%

0603_1/20w

1 2

1 2

R3271 0_5% 0603_1/20w

SDP DDP

LOGIC

2

M_B_BG0 24,25

-M_B_ACT 24,25

M_B_BG1 24

M_B_BS0 24,25

M_B_BS1 24,25

M_B_A[16:0] 24,25

-M_A_DQS[7:0] 4,22

M_A_DQS[7:0] 4,22

-M_B_DQS[7:0] 4,24

M_B_DQS[7:0] 4,24

-M_B_ALERT

M_B_PARITY

-DRAMRST

NA

C1063

0.1UF_6.3V

1 2

0603_X5R_K

TABLE

Pin

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

DDR1_MA[5]

DDR1_MA[9]

DDR1_MA[6]

DDR1_MA[8]

DDR1_MA[7]

DDR1_BA[2]

DDR1_MA[12]

DDR1_MA[11]

DDR1_MA[15]

DDR1_MA[14]

DDR1_MA[13]

DDR1_CAS#

DDR1_WE#

DDR1_RAS#

DDR1_BA[0]

DDR1_MA[2]

DDR1_BA[1]

DDR1_MA[10]

DDR1_MA[1]

DDR1_MA[0]

DDR1_MA[3]

DDR1_MA[4]

-M_B_ALERT 24,25

M_B_PARITY 24,25

-DRAMRST 22,24

DDR3L LPDDR3 DDR4

DDR1_CAA[0]

DDR1_CAA[1]

DDR1_CAA[2]

DDR1_CAA[3]

DDR1_CAA[4]

DDR1_CAA[5]

DDR1_CAA[6]

DDR1_CAA[7]

DDR1_CAA[8]

DDR1_CAA[9]

DDR1_CAB[0]

DDR1_CAB[1]

DDR1_CAB[2]

DDR1_CAB[3]

DDR1_CAB[4]

DDR1_CAB[5]

DDR1_CAB[6]

DDR1_CAB[7]

DDR1_CAB[8]

DDR1_CAB[9]

Not Used

Not Used

DDR1_MA[5]

DDR1_MA[9]

DDR1_MA[6]

DDR1_MA[8]

DDR1_MA[7]

DDR1_BG[0]

DDR1_MA[12]

DDR1_MA[11]

DDR1_ACT#

DDR1_BG[1]

DDR1_MA[13]

DDR1_MA[15]

DDR1_MA[14]

DDR1_MA[16]

DDR1_BA[0]

DDR1_MA[2]

DDR1_BA[1]

DDR1_MA[10]

DDR1_MA[1]

DDR1_MA[0]

DDR1_MA[3]

DDR1_MA[4]

LOGIC

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

Date: Sheet :

Title :

Title :

Title :

CPU(3/16) : DDR CHANNEL-B

CPU(3/16) : DDR CHANNEL-B

CPU(3/16) : DDR CHANNEL-B

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

591Thursday, December 21, 2017

591Thursday, December 21, 2017

591Thursday, December 21, 2017

5

D D

4

3

2

1

VCCSTG VCCSTVCCSTVCC3B

C C

PECI56

-PROCHOT56,70,72

-TBT_PLUG_EVENT31

-WWAN_DISABLE46

B B

PECI

-PROCHOT

-TBT_PLUG_EVENT

-WWAN_DISABLE

NA

R3316

10K_5%

0603_1/20w

1 2

R64

1K_5%

0603_1/20w

1 2

1 2

R85 510_5% 0603_1/20w

1 2

R2126 49.9_1% 0603_1/20w

1 2

R2127 49.9_1% 0603_1/20w

1 2

R2128 49.9_1% 0603_1/20w

1 2

R2129 49.9_1% 0603_1/20w

R3242

1K_5%

0603_1/20w

R9055

1K_5%

0603_1/20w

1 2

1 2

U58D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

SKYLAKE_ULT_DDR3L_REV053F

CPU MISC

4 OF 20

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

R2

51_5%

0603_1/20w

1 2

XDP_TCK0

XDP_TDI

XDP_TDO

XDP_TMS

-XDP_TRST

XDP_TCK0 19

XDP_TDI 19

XDP_TDO 19

XDP_TMS 19

-XDP_TRST 19

PCH_TCK 19

A A

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

5

4

3

2

Date: Sheet :

Title :

Title :

Title :

CPU(4/16) : MISC/JTAG

CPU(4/16) : MISC/JTAG

CPU(4/16) : MISC/JTAG

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

691Thursday, December 21, 2017

691Thursday, December 21, 2017

691Thursday, December 21, 2017

5

TABLE : Functional Strap

SPI0_MOSI (Boot Halt)

HIGH

LOW

Disabled (Default)

Enabled

4

3

2

1

TABLE : Functional Strap

SPI0_MISO (JTAG ODT Disable)

D D

HIGH

LOW

Enabled (Default)

Disabled

TABLE : Functional Strap

GPP_C5/SML0ALERT # (LPC or eSPI)

HIGH

LOW

eSPI is selected

LPC is selected (Default) LOGIC

TABLE : Functional Strap

GPP_C2/SMBALERT# (TLS Confidentiality)

HIGH

VCC3_SUSVCC3B

0603_1/20w

8.2K_5%

1 2

R860

SPI_CLK21,63

C C

SPI_MISO_IO121,63

SPI_MOSI_IO021,63

SPI_IO221

SPI_IO321

-SPI_CS021

-SPI_CS263

-NFC_DTCT59

CL_CLK_WLAN45

CL_DATA_WLAN45

-CL_RST_WLAN45

-KBRC55

IRQSER55,64

CL_CLK_WLAN

CL_DATA_WLAN

-CL_RST_WLAN

NA

R272

10K_5%

0603_1/20w

1 2

U58E

AV2

AW3

AV3

AW2

AU4

AU3

AU2

AU1

AW13

AY11

M2

M3

J4

V1

V2

M1

G3

G2

G1

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKYLAKE_ULT_DDR3L_REV053F

LOW

Enable ME Crypto TLS with Confidentiality

Disable ME Crypto TLS (Default)

SMBUS, SMLINK

GPP_B23/SML1ALERT#/PCHHOT#

LPC

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

5 OF 20

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

VCC3_SUS

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

R226

1K_5%

0603_1/20w

1 2

LOGIC

LPCCLK_0

LPCCLK_1

R106

499_1%

0603_1/20w

1 2

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

R107

499_1%

0603_1/20w

1 2

1 2

R193 33_5%0603_1/20w

1 2

R220 0_5% 0603_1/20wNA

R394

4.7K_5%

0603_1/20w

1 2

R397

4.7K_5%

0603_1/20w

1 2

LPC_AD[3:0] 55,64

-LPC_FRAME 55,64

-SUS_STAT 55,64

LPCCLK_EC_24M 55

LPCCLK_DEBUG_24M 64

VCC3B

8.2K_5%

1 2

0603_1/20w

R28

SMB_CLK

SMB_DATA

SML0_CLK

SML0_DATA

EC_SCL2

EC_SDA2

SMB_CLK 64

SMB_DATA 64

SML0_CLK 41

SML0_DATA 41

EC_SCL2 56

EC_SDA2 56

-CLKRUN 55,64

NA

R2559

1K_5%

0603_1/20w

1 2

B B

TABLE : Functional Strap

SPI0_IO2 (Consent Strap)

HIGH

LOW

Enabled (Default)

Disabled

TABLE : Functional Strap

SPI0_IO3 (A0 Personality Strap)

HIGH

LOW

A A

Disabled (Default)

Enabled

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

5

4

3

2

Date: Sheet :

Title :

Title :

Title :

CPU(5/16) : LPC/SPI/SMBUS/C-LINK

CPU(5/16) : LPC/SPI/SMBUS/C-LINK

CPU(5/16) : LPC/SPI/SMBUS/C-LINK

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

791Thursday, December 21, 2017

791Thursday, December 21, 2017

791Thursday, December 21, 2017

5

4

3

2

1

D D

NFC_DLREQ59

C C

TBT_FORCE_PWR31

-EC_SCI55

-EC_WAKE55

I2C0_DATA59

I2C0_CLK59

-WWAN_RESET46

-INT_MIC_DTCT27

WWAN_CFG046

WWAN_CFG146

10K_5%

1 2

VCC3_SUS

0603_1/20w

0603_1/20w

10K_5%

1 2

R884

R2340

-MIC_HW_EN

NA

1K_5%

1 2

TABLE : Functional Strap

GPP_B22/GSPI1_MOSI (Boot BIOS Destination)

HIGH

LOW

TABLE : Functional Strap

0603_1/20w

GPP_B18/GSPI0_MOSI (No Reboot)

HIGH

LOW

R65

U58F

AN8

GPP_B15/GSPI0_CS#

AP7

GPP_B16/GSPI0_CLK

AP8

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

AM5

GPP_B19/GSPI1_CS#

AN7

GPP_B20/GSPI1_CLK

AP5

GPP_B21/GSPI1_MISO

AN5

GPP_B22/GSPI1_MOSI

AB1

GPP_C8/UART0_RXD

AB2

GPP_C9/UART0_TXD

W4

GPP_C10/UART0_RTS#

AB3

GPP_C11/UART0_CTS#

AD1

GPP_C20/UART2_RXD

AD2

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD4

GPP_C23/UART2_CTS#

U7

GPP_C16/I2C0_SDA

U6

GPP_C17/I2C0_SCL

U8

GPP_C18/I2C1_SDA

U9

GPP_C19/I2C1_SCL

AH9

GPP_F4/I2C2_SDA

AH10

GPP_F5/I2C2_SCL

AH11

GPP_F6/I2C3_SDA

AH12

GPP_F7/I2C3_SCL

AF11

GPP_F8/I2C4_SDA

AF12

GPP_F9/I2C4_SCL

SKYLAKE_ULT_DDR3L_REV053F

Boot BIOS from LPC

Boot BIOS from SPI (Default) LOGIC

Enable "No Reboot" Mode

Disable "No Reboot" Mode (Default)

LPSS ISH

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

SX_EXIT_HOLDOFF#/GPP_A12/BM_BUSY#/ISH_GP6

6 OF 20

GPP_D15/ISH_UART0_RTS#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_D9

GPP_D10

GPP_D11

GPP_D12

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

WWAN_CFG2 46

WWAN_CFG3 46

R961

0_5%

0603_1/20w

B B

A A

1 2

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

5

4

3

2

Date: Sheet :

Title :

Title :

Title :

CPU(6/16) : LPSS/ISH

CPU(6/16) : LPSS/ISH

CPU(6/16) : LPSS/ISH

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

891Thursday, December 21, 2017

891Thursday, December 21, 2017

891Thursday, December 21, 2017

5

D D

VCC3_SUS

4

3

2

1

PLACE ON BOTTOM SIDE

1K_5%

1 2

R846

0603_1/20w

NA

R1009

1K_5%

0603_1/20w

1 2

VCC3_SUS

TP901

TESTPAD_1P0

TEST PAD

BOTTOM SIDE

DO NOT MOVE AFTER FIX

VCC3_SUS

1 2

HDA_SYNC49

HDA_BCLK49

HDA_SDO49

HDA_SDIN049

C C

NFC_ACTIVE59

DDI_PRIORITY28

PCH_SPKR54

PCH_SPKR

R423 33_5% 0603_1/20w

1 2

R60 33_5% 0603_1/20w

1 2

R74 33_5% 0603_1/20w

1 2

R3130 0_5% 0603_1/20w NA

1

NA

1 2

R566

0_5%

1608_1/10w

TP900

TESTPAD_1P0

1

TABLE : Functional Strap

HDA_SDO/I2S0_TXD

Flash Descriptor Security Override

HIGH

LOW

U58G

BA22

HDA_SYNC/I2S0_SFRM

AY22

HDA_BLK/I2S0_SCLK

BB22

HDA_SDO/I2S0_TXD

BA21

HDA_SDI0/I2S0_RXD

AY21

HDA_SDI1/I2S1_RXD

AW22

HDA_RST#/I2S1_SCLK

J5

GPP_D23/I2S_MCLK

AY20

I2S1_SFRM

AW20

I2S1_TXD

AK7

GPP_F1/I2S2_SFRM

AK6

GPP_F0/I2S2_SCLK

AK9

GPP_F2/I2S2_TXD

AK10

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

AW5

GPP_B14/SPKR

SKYLAKE_ULT_DDR3L_REV053F

Disable Flash Descriptor Security (Override)

Enable Flash Descriptor Security (Default)

AUDIO

7 OF 20

SDIO/SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

SD_RCOMP

GPP_F23

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

R2131

200_1%

1 2

0603_1/20w

TBT_RTD3_PWR_EN 31

TBT_FORCE_USB_PWR 31

-TBT_PERST 31

-TBT_PCIE_WAKE 31

-SC_DTCT 60

C38

22PF_25V

0603_C0G_J

1 2

TABLE : Functional Strap

GPP_B14/SPKR (Top Swap Override)

HIGH

LOW

B B

Enable "Top Swap" Mode

Disable "Top Swap" Mode (Default) LOGIC

A A

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

5

4

3

2

Date: Sheet :

Title :

Title :

Title :

CPU(7/16) : AUDIO/SDXC

CPU(7/16) : AUDIO/SDXC

CPU(7/16) : AUDIO/SDXC

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

991Thursday, December 21, 2017

991Thursday, December 21, 2017

991Thursday, December 21, 2017

5

4

3

2

1

PCIe Port Assignment

Flexible I/O Configuration

I/O High Speed Signals Configuration Net Name

Port 1

Port 2

Port 3

Port 4

Port 5

D D

Port 6

Port 7

Port 8

Port 9

Port 10

Port 11

Port 12

Port 13

Port 14

Port 15

Port 16

C C

B B

USB3 1

USB3 2/SSIC

USB3 3

USB3 4

USB3 5/PCIE 1

USB3 6/PCIE 2

PCIE 3 (GbE)

PCIE 4 (GbE)

PCIE 5 (GbE)

PCIE 6

PCIE 7/SATA 0

PCIE 8/SATA 1A

PCIE 9 (GbE) PCIE 9

PCIE 10 (GbE) PCIE 10

PCIE 11/SATA 1B

PCIE 12/SATA 2

USB3 1

USB3 2

USB3 3 USB3P2

USB3 4

PCIE 1

PCIE 2

PCIE 3

PCIE 4 (GbE)

PCIE 5 (x4)

PCIE 6 (x4)

PCIE 7 (x4)

GPIO STRAP

PCIE 11

PCIE 12

PCIE0_L0_RXN31

PCIE0_L0_RXP31

PCIE0_L0_TXN31

PCIE0_L0_TXP31

PCIE0_L1_RXN31

PCIE0_L1_RXP31

PCIE0_L1_TXN31

PCIE0_L1_TXP31

PCIE2_RXN45

PCIE2_RXP45

PCIE2_TXN45

PCIE2_TXP45

PCIE3_RXN41

PCIE3_RXP41

PCIE3_TXN41

PCIE3_TXP41

PCIE4_L3_RXN38

PCIE4_L3_RXP38

PCIE4_L3_TXN38

PCIE4_L3_TXP38

PCIE4_L2_RXN38

PCIE4_L2_RXP38

PCIE4_L2_TXN38

PCIE4_L2_TXP38

PCIE4_L1_RXN38

PCIE4_L1_RXP38

PCIE4_L1_TXN38

PCIE4_L1_TXP38

PCIE4_L0_SATA1_RXN38

PCIE4_L0_SATA1_RXP38

PCIE4_L0_SATA1_TXN38

PCIE4_L0_SATA1_TXP38

-XDP_PRDY19

-XDP_PREQ19

-TPM_IRQ63

PCIE11_RXN46

PCIE11_RXP46

PCIE11_TXN46

PCIE11_TXP46

USB3P0

USB3P1

USB3P3

PCIE0_L0

PCIE0_L1

PCIE2

PCIE3

PCIE4_L3

PCIE4_L2

PCIE4_L1

PCIE4_L0_SATA1

N/A

N/A

N/A

PCIE11

-XDP_PRDY

-XDP_PREQ

-TPM_IRQ

VCC3_SUS

R2341

10K_5%

0603_1/20w

1 2

R8964

100_1%

1 2

Thunderbolt

0(x2)

2

M.2 WLAN Slot Port 0

3

GbE PHY

PCIe SSD

4

M.2 WWAN Slot

11

0603_1/20w

U58H

PCIE/USB3/SATA

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKYLAKE_ULT_DDR3L_REV053F

SATA Port Assignment

0

(PCIE 7)

SATA SSD

1A

(PCIE 11)

1B

2

(PCIE 12)

8 OF 20

SSIC / USB3

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2

USB2_COMP

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_ID

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

USBCOMP

10K_5%

VCC3_SUS

0603_1/20w

1 2

R648

0603_1/20w

10K_5%

1 2

R3174

1 2

R564 113_1% 0603_1/20w

1 2

R2573 0_5% 0603_1/20w

1 2

R2580 1K_5% 0603_1/20w

R3315

10K_5%

0603_1/20w

1 2

USB3P0_RXN 39

USB3P0_RXP 39

USB3P0_TXN 39

USB3P0_TXP 39

USB3P1_RXN 39

USB3P1_RXP 39

USB3P1_TXN 39

USB3P1_TXP 39

USB3P2_RXN 47

USB3P2_RXP 47

USB3P2_TXN 47

USB3P2_TXP 47

USB3P3_RXN 29

USB3P3_RXP 29

USB3P3_TXN 29

USB3P3_TXP 29

USBP0- 39

USBP0+ 39

USBP1- 39

USBP1+ 39

USBP2- 60

USBP2+ 60

USBP3- 36

USBP3+ 36

USBP4- 27

USBP4+ 27

USBP5- 46

USBP5+ 46

USBP6- 45

USBP6+ 45

USBP7- 27

USBP7+ 27

USBP8- 60

USBP8+ 60

USBP9- 26

USBP9+ 26

-USB_PORT0_OC0 39

-USB_PORT1_OC1 39

NFC_INT 59

VCC3_SUS

0603_1/20w

10K_5%

1 2

R44

USB Port Assignment

0

USB 3.0 System Port (AOU)

1

USB 3.0 System Port

2

Smart Card Reader

3

USB Type-C

4

IR Camera

M.2 WWAN Slot

5

6

M.2 WLAN Slot (Bluetooth)

7

RGB Camera

8

Fingerprint Reader

9

Touch Panel

USB 3.0 Port Assignment

0

USB 3.0 System Port (AOU)

1

USB 3.0 System Port

2

Media Card Controller

3

USB Type-C

4 (PCIE 1)

5

(PCIE 2)

BDC_ON

-SATA1_DTCT

NFC_ON 59

SATA1_DEVSLP 38

BDC_ON 45

-SATA1_DTCT 38

A A

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

5

4

3

2

Date: Sheet :

Title :

Title :

Title :

CPU(8/16) : PCIE/USB/SATA

CPU(8/16) : PCIE/USB/SATA

CPU(8/16) : PCIE/USB/SATA

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

10 91Thursday, December 21, 2017

10 91Thursday, December 21, 2017

10 91Thursday, December 21, 2017

5

D D

C C

4

U58I

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKYLAKE_ULT_DDR3L_REV053F

9 OF 20

3

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

PLANARID1

PLANARID2

PLANARID3

MEMORYID0

MEMORYID1

MEMORYID2

MEMORYID3

MEMORYID4

PLANARID0

-TAMPER_SW_DTCT

2

-TAMPER_SW_DTCT 13

1

B B

TABLE

LEVEL

PLANAR ID

0123

R43 R47 R113 R48

TABLE: MEMORYID

MEMORYID[4:0]

Vendor

00h (00000b)

01h (00001b)

02h (00010b)

03h (00011b)

Micron

04h (00100b)

05h (00101b)

06h (00110b)

07h (00111b)

08h (01000b)

A A

09h (01001b)

0Ah (01010b)

0Bh (01011b)

0Ch (01100b)

Samsung

SK hynix

0Dh (01101b)

0Eh (01110b)

0Fh (01111b)

Micron

5

U125, U126, U127, U128, U129, U130, U131,U132

Part Number Component Qty Channel-0 Channel-1 Total

MT40A256M16GE-083E:B

MT40A512M16JY-083E:B

MT40A512M16JY-083E:B

MT40A512M16LY-075:H

MT40A512M16LY-075:H

MT40A1G16WBU-083E:B

K4A4G165WE-BCRC

K4A8G165WC-BCRC

K4A8G165WC-BCRC

K4AAG165WB-MCRC

H5AN4G6NAFR-UHC

H5AN8G6NAFR-UHC

H5AN8G6NAFR-UHC

H5ANAG6NAMR-UHC

MT40A512M16LY-075:E

MT40A512M16LY-075:E

4Gbit SDP 8pcs

8Gbit SDP

8Gbit SDP

8Gbit SDP

8Gbit SDP

16Gbit DDP

4Gbit SDP

8Gbit SDP

8Gbit SDP

16Gbit DDP

4Gbit SDP

8Gbit SDP

8Gbit SDP

16Gbit DDP

8Gbit SDP

8Gbit SDP

4pcs

8pcs

4pcs

8pcs

8pcs

8pcs

4pcs

8pcs

8pcs

8pcs

4pcs

8pcs

8pcs

4pcs

8pcs

2GB

4GB

4GB

4GB

4GB

8GB

2GB

4GB

4GB

8GB

2GB

4GB

4GB

8GB

4GB

4GB

4

Capacity

2GB

0GB

4GB

0GB

4GB

8GB

2GB

0GB

4GB

8GB

2GB

0GB

4GB

8GB

0GB

4GB

4GB

4GB

8GB

4GB

8GB

16GB

4GB

4GB

8GB

16GB

4GB

4GB

8GB

16GB

4GB

8GB

R2753

0_5%

0603_1/20w

1 2

R2754

0_5%

0603_1/20w

1 2

1 2

3

R2755

0_5%

0603_1/20w

R2756

0_5%

0603_1/20w

1 2

R2757

0_5%

0603_1/20w

1 2

MEMORYID0

MEMORYID1

MEMORYID2

MEMORYID3

MEMORYID4

R43

0_5%

0603_1/20w

1 2

1 2

2

NA

R47

0_5%

0603_1/20w

R113

0_5%

0603_1/20w

1 2

R48

0_5%

0603_1/20w

1 2

PLANARID0

PLANARID1

PLANARID2

PLANARID3

Size :

Size :

Size :

1NA

0

NA NA NA

ASM ASM ASM ASM

TABLE

LEVEL

PLANARID[3..0]

EVT 0000B

ME-FVT

0001B

FVT 0010B

SIT 0011B

SVT 0100B

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

C

Date: Sheet :

Date: Sheet :

Date: Sheet :

Title :

Title :

Title :

CPU(9/16) : CSI-2/EMMC

CPU(9/16) : CSI-2/EMMC

CPU(9/16) : CSI-2/EMMC

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

11 91Thursday, December 21, 2017

11 91Thursday, December 21, 2017

11 91Thursday, December 21, 2017

5

D D

4

3

VCC1R0_SUS

2

1

C C

-PCIE0_CLK_100M31

PCIE0_CLK_100M31

-CLKREQ_PCIE031

-PCIE2_CLK_100M45

PCIE2_CLK_100M45

-CLKREQ_PCIE245

-PCIE3_CLK_100M41

PCIE3_CLK_100M41

-CLKREQ_PCIE341

-PCIE4_CLK_100M38

PCIE4_CLK_100M38

-CLKREQ_PCIE438

-PCIE11_CLK_100M46

PCIE11_CLK_100M46

-CLKREQ_PCIE1146

U58J

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

SKYLAKE_ULT_DDR3L_REV053F

CLOCK SIGNALS

10 OF 20

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

F43

E43

BA17

E37

E35

E42

AM18

AM20

AN18

AM16

R609

2.71K_0.5%

1005_1/16w

1 2

RTCX1

RTCX2

-SRTCRST 20

-RTCRST 17,20

SUSCLK_32K 45,55

R351

10M_5%

0603_1/20w

1 2

R308

1M_1%

0603_1/20w

1 2

Y6

9H03280012

1 2

0_5%

1 2

R133

6PF_25V

1 2

C348

6PF_25V

1 2

C326

0603_1/20w

0603_C0G_D

0603_C0G_D

C205

6PF_25V

0603_C0G_D

1 2

Y5

4 3

1 2

1ZZHAE24000CC0G

24MHz 8pF 30ppm 2016

KDS 1ZZHAE24000CC0G

TXC 7R24080003

EPSON Q22FA1280055800

C206

6PF_25V

0603_C0G_D

1 2

32.768kHz 9pF 20ppm 3215

TXC 9H03280012

B B

KDS 1TJF090DJ1A000B

EPSON X1A000141000200

A A

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

5

4

3

2

Date: Sheet :

Title :

Title :

Title :

CPU(10/16) : CLOCK SIGNALS

CPU(10/16) : CLOCK SIGNALS

CPU(10/16) : CLOCK SIGNALS

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

12 91Thursday, December 21, 2017

12 91Thursday, December 21, 2017

12 91Thursday, December 21, 2017

5

4

3

2

1

U73

VCC

GND

IN

-SUSWARN

VCC3M

5

2

-PLTRST

3

NA

C3249

1 2

VCC3M

10K_5%

1 2

NA

0603_1/20w

R614

-PCH_SLP_S0 17,72,79

-PCH_SLP_S3 17,31,56,65,66

-PCH_SLP_S4 17,56,65,80

-PCH_SLP_S5 17,65

-PCH_SLP_SUS 56

-PCH_SLP_LAN 65

-PCH_SLP_WLAN 56

-PCH_SLP_M 17,65

-PWRSW_EC 56

AC_PRESENT 56

-BATLOW 31,57

1

CPU_PWRGD

VCCST_PWRGD

1 2

R21 0_5% 0603_1/20w

1 2

R617 0_5% 0603_1/20w

1 2

R203 0_5% 0603_1/20w

1 2

R1884 0_5% 0603_1/20w

U58K

SYSTEM POWER MANAGEMENT

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKYLAKE_ULT_DDR3L_REV053F

11 OF 20

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B11/EXT_PWR_GATE#

GPP_B2/VRALERT#

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

AM10

AM11

0603_1/20w

-INTRUDER

1000PF_25V

0603_X7R_K

R646

1M_5%

RTCVCC

NA

C7

1 2

1 2

0.1UF_6.3V

0603_X5R_K

33_5%

C460

100PF_25V

0603_C0G_J

1 2

R991

0603_1/20w

R993

C46

100PF_25V

0603_C0G_J

1 2

33_5%

1 2

0603_1/20w

4

1

OUT

NC

TC7SZ17FE

D D

-PLTRST_NEAR38,46,63,64

-PLTRST_FAR31,41,45,55,65

1 2

C C

VCC3MVCC3M

0603_1/20w

4.7K_5%

1 2

R19

-XDP_DBR17,19

-RSMRST19,65

BPWRG56,59,64,66

CPUCORE_PWRGD72

MPWRG66

-PCIE_WAKE31,45,46,65

-LANWAKE41

LANPHYPC41

B B

MPWRG

0603_1/20w

1K_5%

1 2

R612

TP160 TESTPAD_0P5

-TAMPER_SW_DTCT11

-TAMPER_SW_DTCT

43

12

6

S3

5

1 2

R10 0_5% 0603_1/20w

SPVR310100

VCC3_SUS VCC1R0_SUS

R2324

10K_5%

0603_1/20w

1 2

R2325

10K_5%

0603_1/20w

1 2

VCCST_PWRGD

32

Q194

A A

CPUCORE_ON65,72

5

CPUCORE_ON

1

LSK3541G1E

4

32

Q195

1

LSK3541G1E

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

3

2

Date: Sheet :

Title :

Title :

Title :

CPU(11/16) : SYSTEM PM

CPU(11/16) : SYSTEM PM

CPU(11/16) : SYSTEM PM

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

13 91Thursday, December 21, 2017

13 91Thursday, December 21, 2017

13 91Thursday, December 21, 2017

5

4

3

2

1

VCCCPUCORE

D D

0603_X5R_M

0603_X5R_M

C3324

0603_X5R_M

1UF_6.3V

1UF_6.3V

1 2

1 2

C3325

0603_X5R_M

0603_X5R_M

1UF_6.3V

1 2

C3321

1UF_6.3V

1UF_6.3V

1 2

C3322

1UF_6.3V

1 2

1 2

C3323

0603_X5R_M

C3326

0603_X5R_M

1UF_6.3V

1UF_6.3V

1 2

1 2

C3327

0603_X5R_M

C3328

0603_X5R_M

C3329

0603_X5R_M

1UF_6.3V

1 2

C3330

RJ200

SHORT1608_30MIL

1 2

VCCSTG_CPUVCCSTG

1UF_6.3V

1 2

VCCCPUCORE

VCCCPUCORE

U58L

A30

VCC_A30

A34

VCC_A34

A39

VCC_A39

A44

VCC_A44

AK33

C C

0603_X5R_M

0603_X5R_M

0603_X5R_M

C3333

0603_X5R_M

1UF_6.3V

1UF_6.3V

1 2

1 2

C3334

1UF_6.3V

1UF_6.3V

1 2

C3331

1UF_6.3V

1 2

1 2

C3332

0603_X5R_M

C3335

0603_X5R_M

0603_X5R_M

0603_X5R_M

0603_X5R_M

C3339

0603_X5R_M

1UF_6.3V

1 2

C3340

1UF_6.3V

1UF_6.3V

1UF_6.3V

1 2

1 2

C3336

C3337

1UF_6.3V

1 2

1 2

C3338

VCCCPUCORE

0603_X5R_M

C3345

0603_X5R_M

0603_X5R_M

C3347

0603_X5R_M

1UF_6.3V

1UF_6.3V

1 2

1 2

C3348

1UF_6.3V

1UF_6.3V

1 2

1 2

C3346

0603_X5R_M

0603_X5R_M

0603_X5R_M

0603_X5R_M

1UF_6.3V

1UF_6.3V

1 2

C3341

B B

1UF_6.3V

1 2

1 2

C3342

C3343

1UF_6.3V

1UF_6.3V

1 2

1 2

C3344

0603_X5R_M

C3349

0603_X5R_M

C3350

0603_X5R_M

1UF_6.3V

1 2

C3351

1UF_6.3V

1 2

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AM32

AM33

AM35

AM37

AM38

G30

K32

AK32

AB62

P62

V62

H63

G61

AC63

AE63

AE62

AG62

AL63

AJ62

VCC_AK33

VCC_AK35

VCC_AK37

VCC_AK38

VCC_AK40

VCC_AL33

VCC_AL37

VCC_AL40

VCC_AM32

VCC_AM33

VCC_AM35

VCC_AM37

VCC_AM38

VCC_G30

RSVD_K32

RSVD_AK32

VCCOPC_AB62

VCCOPC_P62

VCCOPC_V62

VCC_OPC_1P8_H63

VCC_OPC_1P8_G61

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO_1

VCCEOPIO_2

VCCEOPIO_SENSE

VSSEOPIO_SENSE

CPU POWER 1 OF 4

SKYLAKE_ULT_DDR3L_REV053F

12 OF 20

VCC_G32

VCC_G33

VCC_G35

VCC_G37

VCC_G38

VCC_G40

VCC_G42

VCC_J30

VCC_J33

VCC_J37

VCC_J40

VCC_K33

VCC_K35

VCC_K37

VCC_K38

VCC_K40

VCC_K42

VCC_K43

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG_G20

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

A63

D64

G20

VCCCPUCORE

VCCSTG_CPU

VCCCPUCORE

R9

100_5%

0603_1/20w

1 2

R70

100_5%

0603_1/20w

1 2

1 2

R781

220_5%

0603_1/20w

56_5%

1 2

0603_1/20w

R374

VCCST

100_5%

1 2

0603_1/20w

R2576

VCC_SENSE

VSS_SENSE

-SVID_ALERT

SVID_CLK

SVID_DATA

VCC_SENSE 72

VSS_SENSE 72

-SVID_ALERT 72

SVID_CLK 72

SVID_DATA 72

VCCCPUCORE

1608_X5R_M

C3354

1608_X5R_M

1 2

22UF_6.3V

1 2

22UF_6.3V

C3355

1608_X5R_M

1608_X5R_M

1 2

C3353

1 2

22UF_6.3V

1 2

22UF_6.3V

22UF_6.3V

C3352

A A

5

1608_X5R_M

C3356

1608_X5R_M

1 2

22UF_6.3V

1 2

22UF_6.3V

C3357

1608_X5R_M

C3358

1608_X5R_M

1 2

22UF_6.3V

C3429

Project Name :

Project Name :

Project Name :

Finn-1 SOVP

Finn-1 SOVP

Finn-1 SOVP

Document Number :

Document Number :

Document Number :

Size :

Size :

Size :

C

Date: Sheet :

Date: Sheet :

4

3

2

Date: Sheet :

Title :

Title :

Title :

CPU(12/16) : CPU POWER (1/2)

CPU(12/16) : CPU POWER (1/2)

CPU(12/16) : CPU POWER (1/2)

1

Rev :

Rev :

Rev :

4.00

4.00

4.00

of

of

of

14 91Thursday, December 21, 2017

14 91Thursday, December 21, 2017

14 91Thursday, December 21, 2017

5

VCCCPUCORE_GT

0603_X5R_M

0603_X5R_M

0603_X5R_M

0603_X5R_M

C3362

0603_X5R_M

1UF_6.3V

1 2

C3363

1UF_6.3V

1UF_6.3V

1UF_6.3V

1 2

D D

C3359

1 2

C3360

1UF_6.3V

1 2

1 2

C3361

4

VCCST_CPUVCCST

RJ201

SHORT1608_30MIL

1 2

3

VCCPLL

VCCST_CPU VCCSTG_CPU VCCST_CPU VCC1R2A VCC1R2A

0603_X5R_M

1UF_6.3V

1 2

C2422

0603_X5R_M

1UF_6.3V

1 2

C2423

0603_X5R_M

1UF_6.3V

1 2

C2424

VCC1R2A VCC1R2A

1005_X5R_M

1005_X5R_M

1 2

1 2

10UF_6.3V

10UF_6.3V

C3122

C1184

1 2

10UF_6.3V

1005_X5R_M

C1829

2

1

VDDQC VCCPLL_OC

1005_X5R_M

C1830

1005_X5R_M

1 2

10UF_6.3V

C1831

1 2

22UF_6.3V

1 2

10UF_6.3V

1608_X5R_M

C3123

1608_X5R_M

1 2

22UF_6.3V

1 2

22UF_6.3V

C840

1608_X5R_M

1608_X5R_M

1 2

22UF_6.3V

C844

C842

1005_X5R_M

1 2

10UF_6.3V

C2426

1UF_6.3V

1 2

0603_X5R_M

C2427

0603_X5R_M

C3373

VCCGFXCORE_I

0603_X5R_M

1UF_6.3V

1 2

C3374

U58M

CPU POWER 2 OF 4

A48

VCCGT_1

A53

VCCGT_2

A58

VCCGT_3

A62

VCCGT_4

A66

VCCGT_5

AA63

VCCGT_6

AA64

VCCGT_7

AA66

VCCGT_8

AA67

VCCGT_9

AA69

VCCGT_10

AA70

VCCGT_11

AA71

VCCGT_12

AC64

VCCGT_13

AC65

VCCGT_14

AC66

VCCGT_15

AC67

VCCGT_16

AC68

VCCGT_17

AC69

VCCGT_18

AC70

VCCGT_19

AC71

VCCGT_20

J43

VCCGT_21

J45

VCCGT_22

J46

VCCGT_23

J48

VCCGT_24

J50

VCCGT_25

J52

VCCGT_26

J53

VCCGT_27

J55

VCCGT_28

J56

VCCGT_29

J58

VCCGT_30

J60

VCCGT_31

K48

VCCGT_32

K50

VCCGT_33

K52

VCCGT_34

K53

VCCGT_35

K55

VCCGT_36

K56

VCCGT_37

K58

VCCGT_38

K60

VCCGT_39

L62

VCCGT_40

L63

VCCGT_41

L64

VCCGT_42

L65

VCCGT_43

L66

VCCGT_44

L67

VCCGT_45

L68

VCCGT_46

L69

VCCGT_47