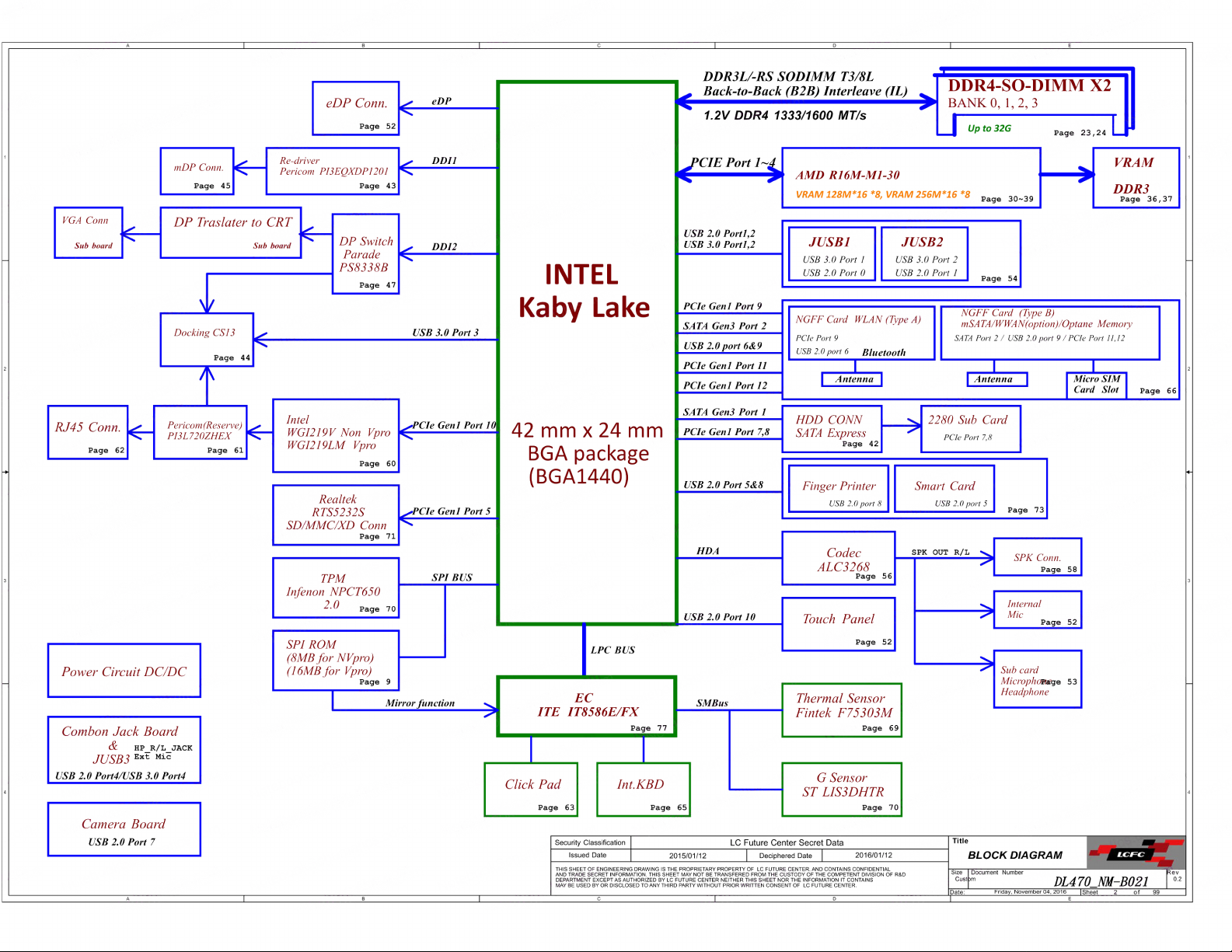

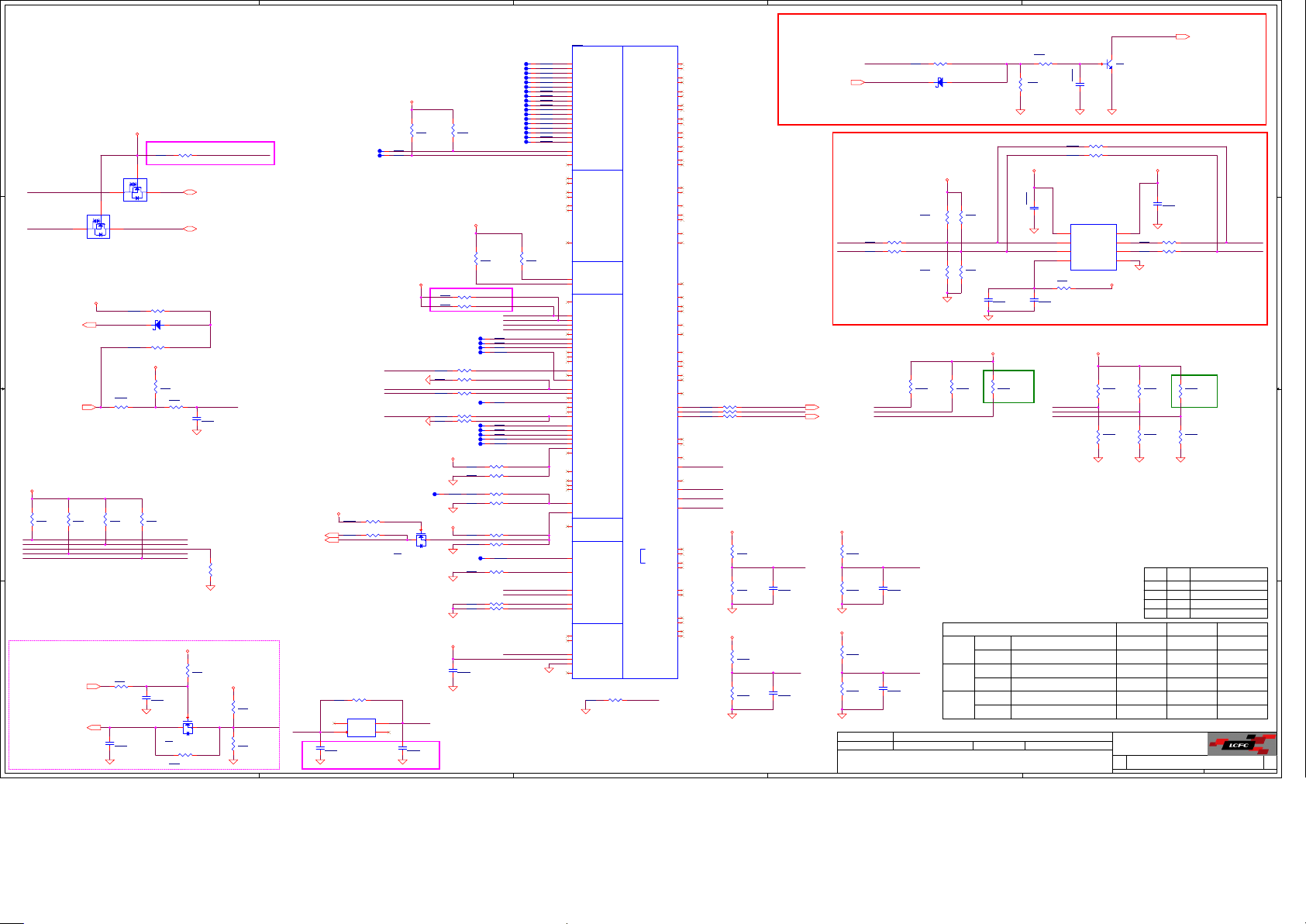

Lenovo ThinkPad L470 Schematic

5

D D

4

3

2

1

1 2

1 2

1 2

1 2

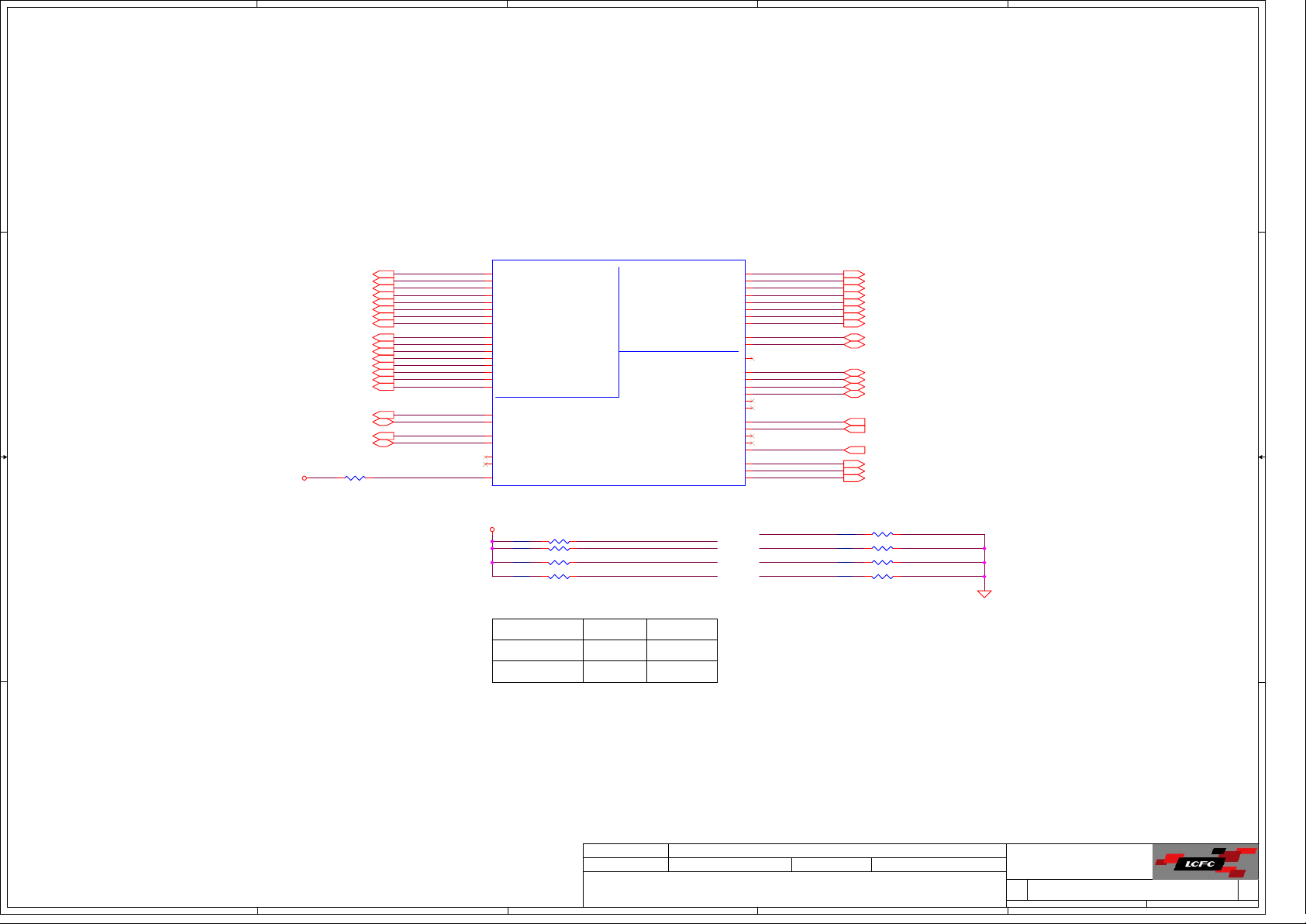

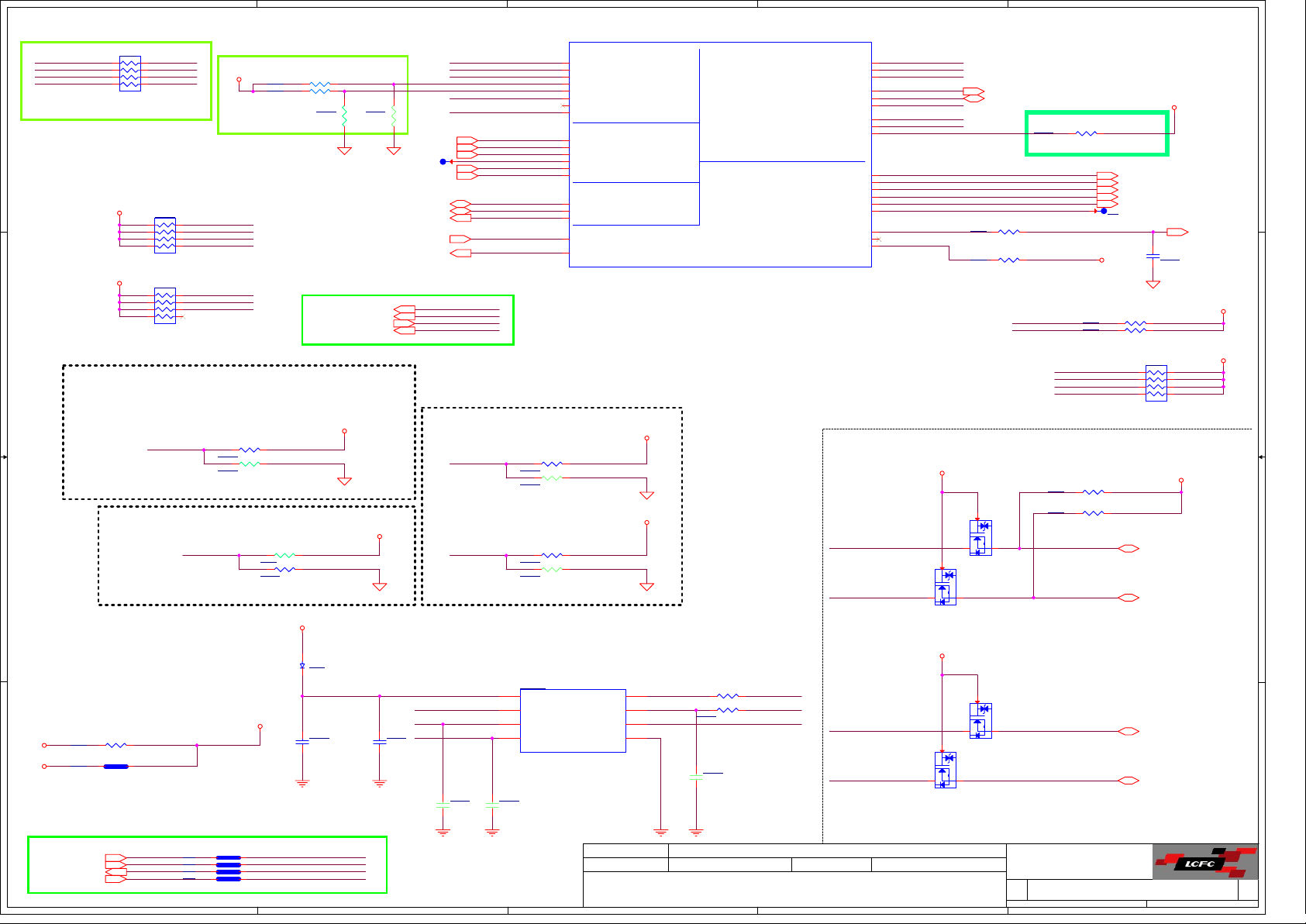

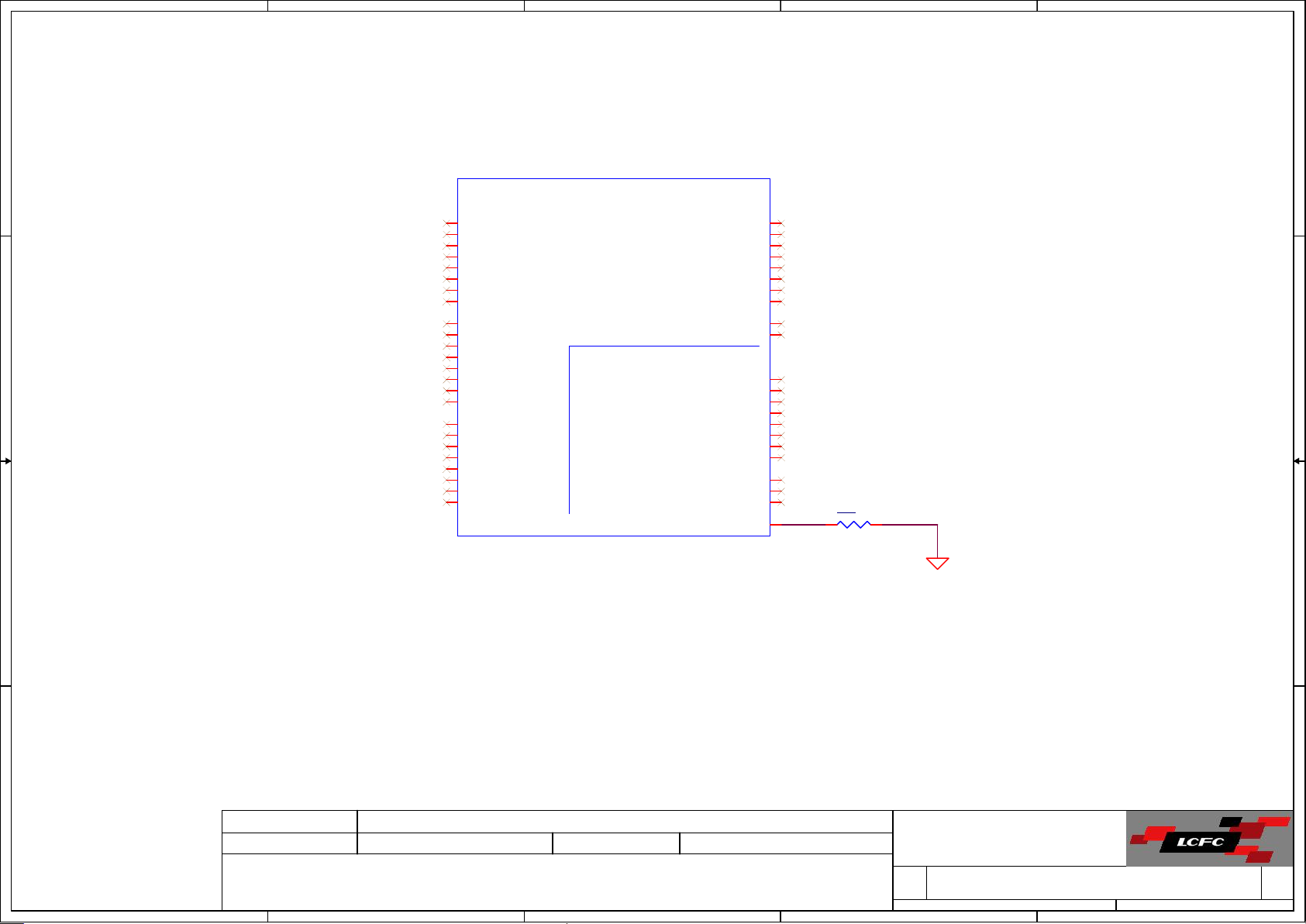

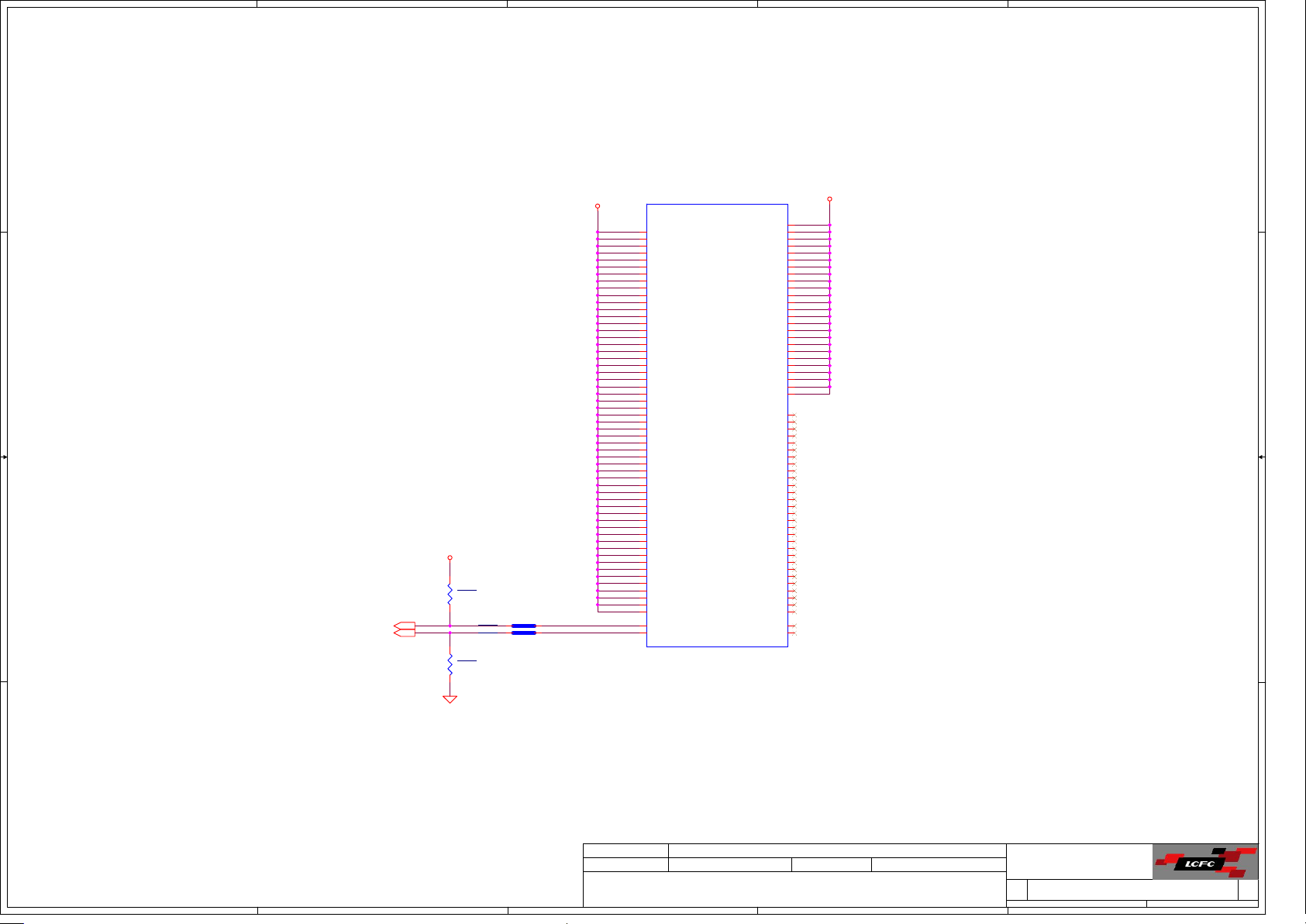

SKL_ULT

DDI

DISPLAY SIDEBANDS

1 OF 20REV = 1

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

DDIP1_CTRLCLK

DDIP1_CTRLDATA

DDIP2_CTRLCLK

DDIP2_CTRLDATA

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

MINI-DP

CPU_EDP_TX0CPU_EDP_TX0+

CPU_EDP_TX1CPU_EDP_TX1+

CPU_EDP_TX2CPU_EDP_TX2+

CPU_EDP_TX3CPU_EDP_TX3+

CPU_EDP_AUX#

CPU_EDP_AUX

DDIP1_AUXN

DDIP1_AUXP

DDIP2_AUXN

DDIP2_AUXP

DDIP1_HPD

DDIP2_HPD

CPU_EDP_HPD

ENBKL

PCH_EDP_PWM

PCH_ENVDD

DDIP1_HPD

DDIP2_HPD

CPU_EDP_HPD

ENBKL

CPU_EDP_TX0- [52]

CPU_EDP_TX0+ [52]

CPU_EDP_TX1- [52]

CPU_EDP_TX1+ [52]

CPU_EDP_TX2- [52]

CPU_EDP_TX2+ [52]

CPU_EDP_TX3- [52]

CPU_EDP_TX3+ [52]

CPU_EDP_AUX# [52]

CPU_EDP_AUX [52]

DDIP1_AUXN [43]

DDIP1_AUXP [43]

DDIP2_AUXN [46]

DDIP2_AUXP [46]

DDIP1_HPD [43,45]

DDIP2_HPD [46]

CPU_EDP_HPD [52]

ENBKL [77]

PCH_EDP_PWM [52]

PCH_ENVDD [52]

1 2

RC103 100K_0402_5%

1 2

RC57 100K_0402_5%

1 2

RC58 100K_0402_5%

1 2

RC59 100K_0402_5%

CPU_DDI1_N0[43]

CPU_DDI1_P0[43]

DDIP1_CTRLCLK[43,45]

DDIP1_CTRLDATA[43,45]

DDIP2_CTRLCLK[44]

DDIP2_CTRLDATA[44]

CPU_DDI1_N1[43]

CPU_DDI1_P1[43]

CPU_DDI1_N2[43]

CPU_DDI1_P2[43]

CPU_DDI1_N3[43]

CPU_DDI1_P3[43]

CPU_DDI2_N0[46]

CPU_DDI2_P0[46]

CPU_DDI2_N1[46]

CPU_DDI2_P1[46]

CPU_DDI2_N2[46]

CPU_DDI2_P2[46]

CPU_DDI2_N3[46]

CPU_DDI2_P3[46]

1 2

24.9_0402_1%

RC1

MINI DP

C C

B B

DOCKING & D-SUB

MINI-DP

DOCKING

+VCC_IO

EDP_RCOMP

1. Trace width=20 mils, Spacing=25mil, Max length=100mils

2. RC1 close to MCP

Trace Width=20mil, Spacing=25mil, Max length=100mil

CPU_DDI1_N0

CPU_DDI1_P0

CPU_DDI1_N1

CPU_DDI1_P1

CPU_DDI1_N2

CPU_DDI1_P2

CPU_DDI1_N3

CPU_DDI1_P3

CPU_DDI2_N0

CPU_DDI2_P0

CPU_DDI2_N1

CPU_DDI2_P1

CPU_DDI2_N2

CPU_DDI2_P2

CPU_DDI2_N3

CPU_DDI2_P3

DDIP1_CTRLCLK

DDIP1_CTRLDATA

DDIP2_CTRLCLK

DDIP2_CTRLDATA

EDP_COMP

UC1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKYLAKE-U_BGA1356

+3VS

RC12 2.2K_0402_5%@

RC13 2.2K_0402_5%

RC49 2.2K_0402_5%@

RC52 2.2K_0402_5%

DDIP2_HPD : PS8338B has Int.PD 150K

DP port

DDPB_CTRLDATA

DDPC_CTRLDATA

Enable Disable

pull-high

pull-high

no connect

no connect

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/12

2016/01/12

2016/01/12

Title

KBL_DDI/eDP

KBL_DDI/eDP

KBL_DDI/eDP

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Friday, November 04, 2016

Friday, November 04, 2016

Date: Sheet of

Date: Sheet of

Date: Sheet of

Friday, November 04, 2016

DL470_NM-B021

DL470_NM-B021

DL470_NM-B021

1

5 99

5 99

5 99

0.2

0.2

0.2

5

4

3

2

1

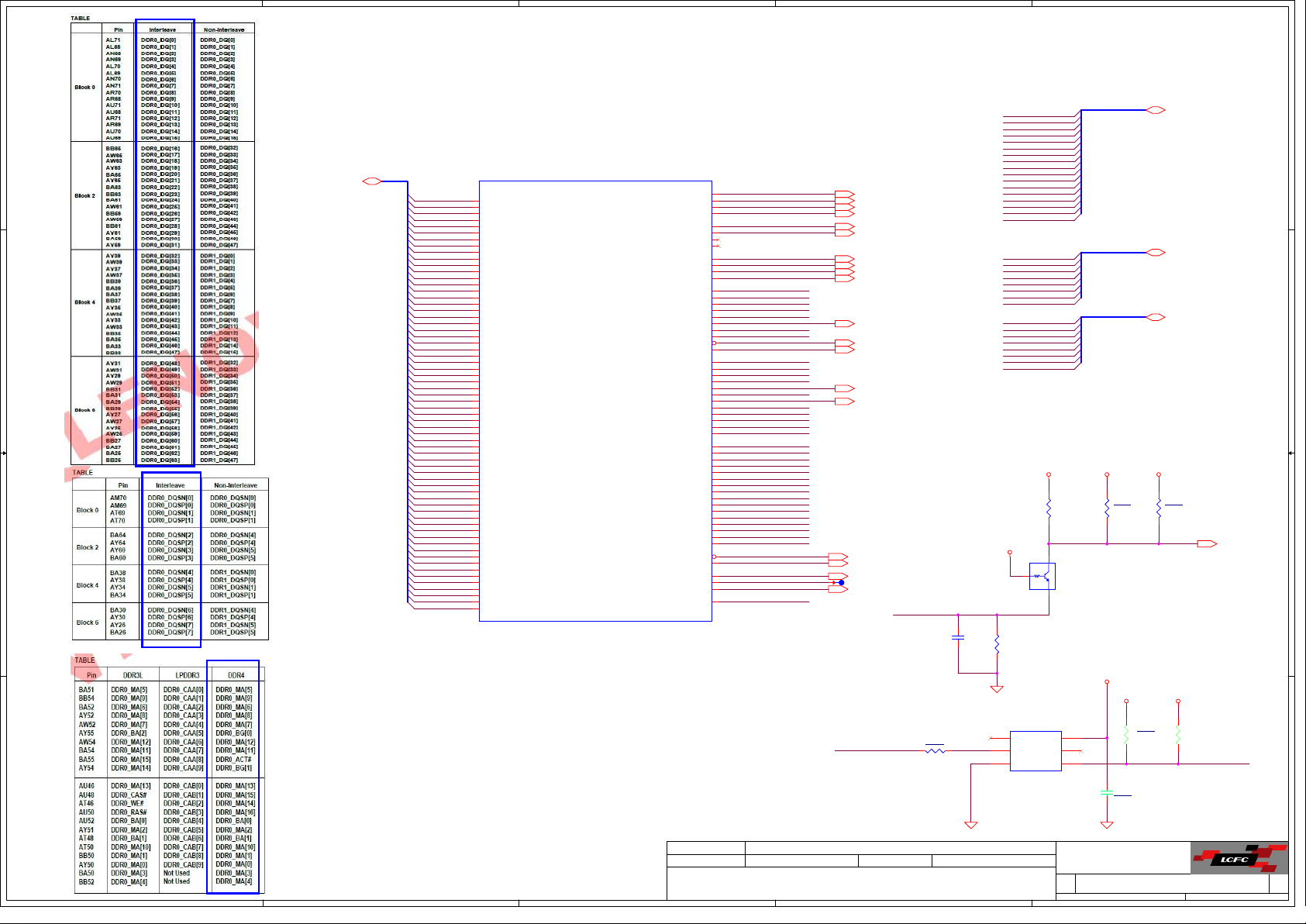

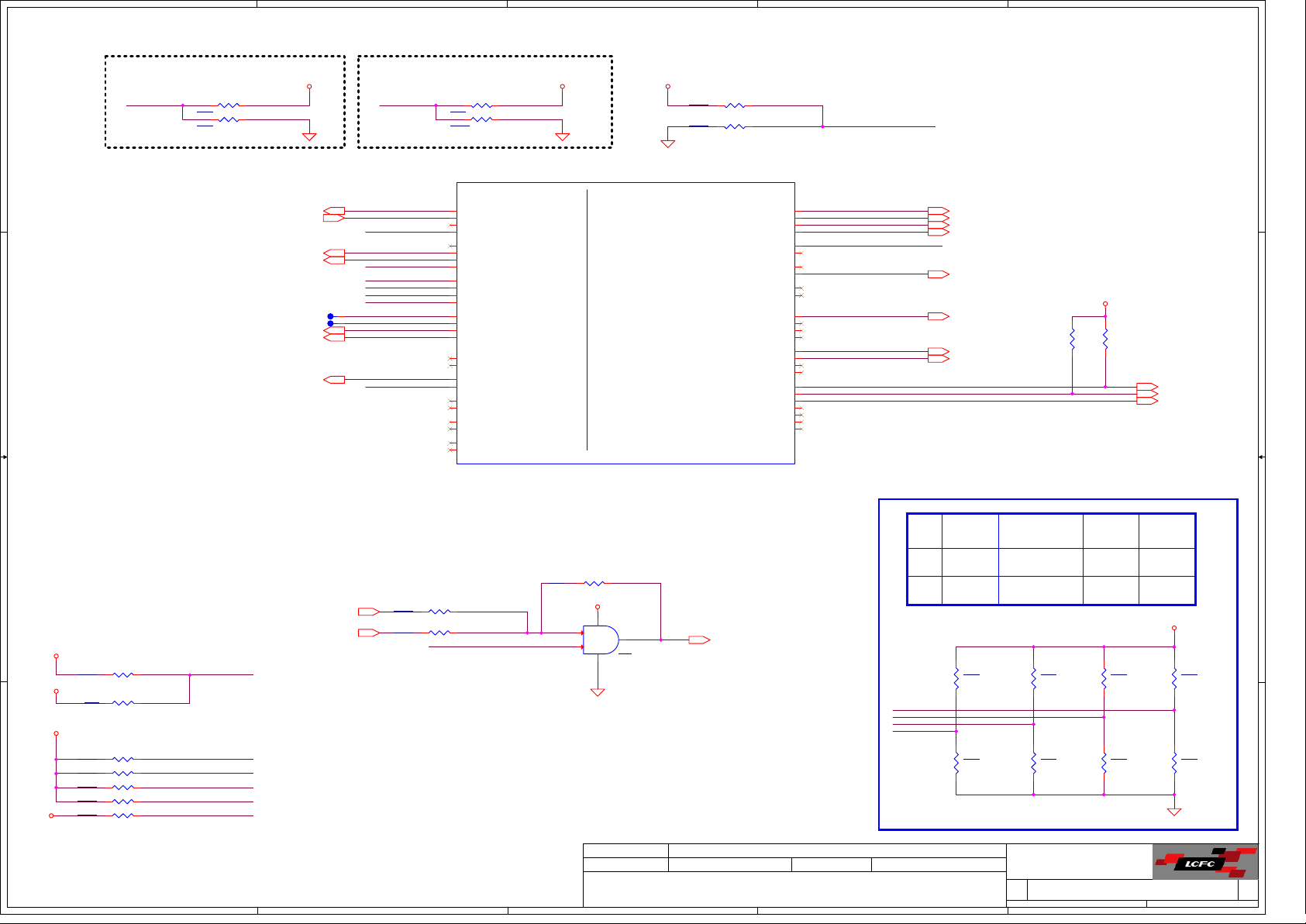

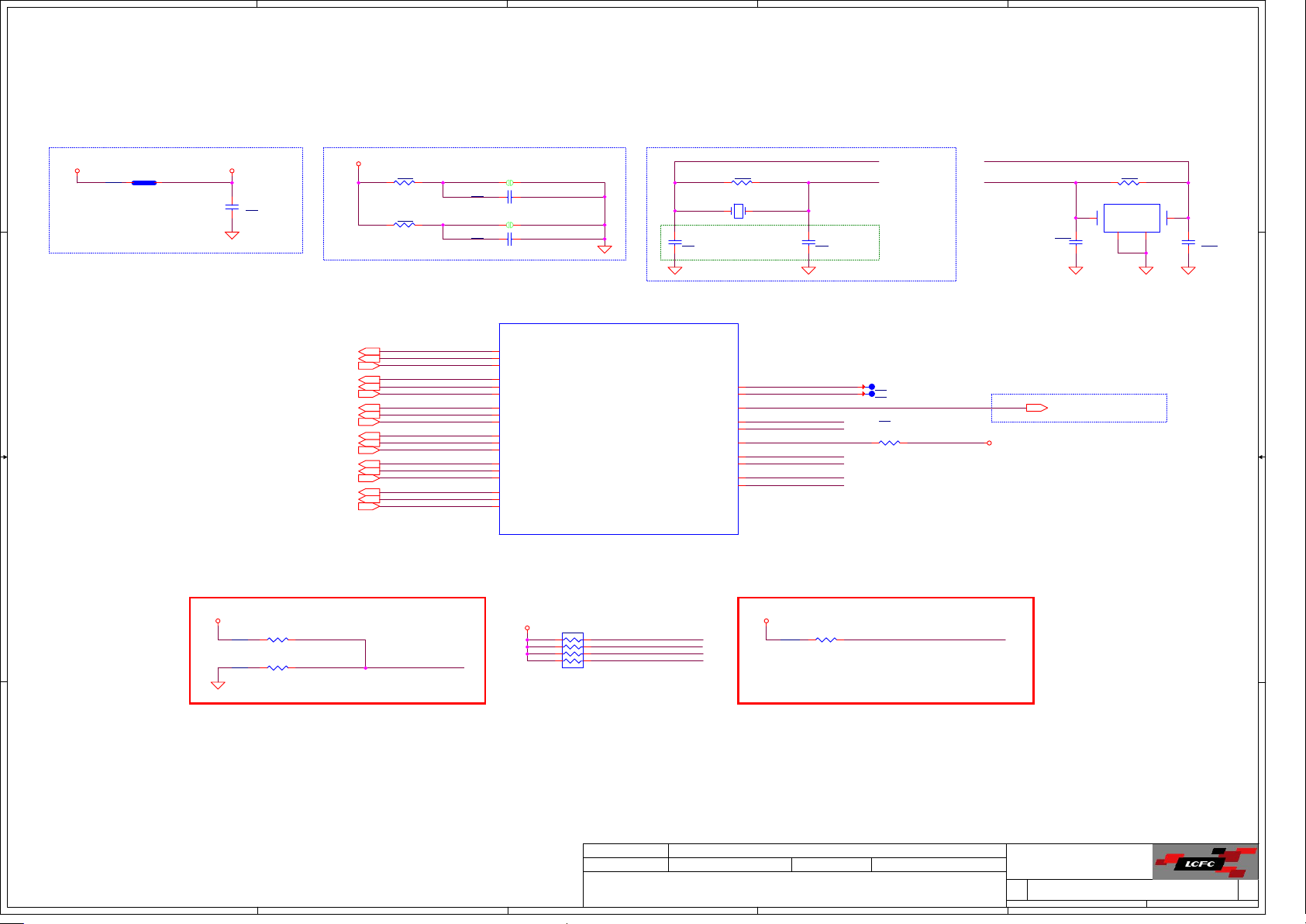

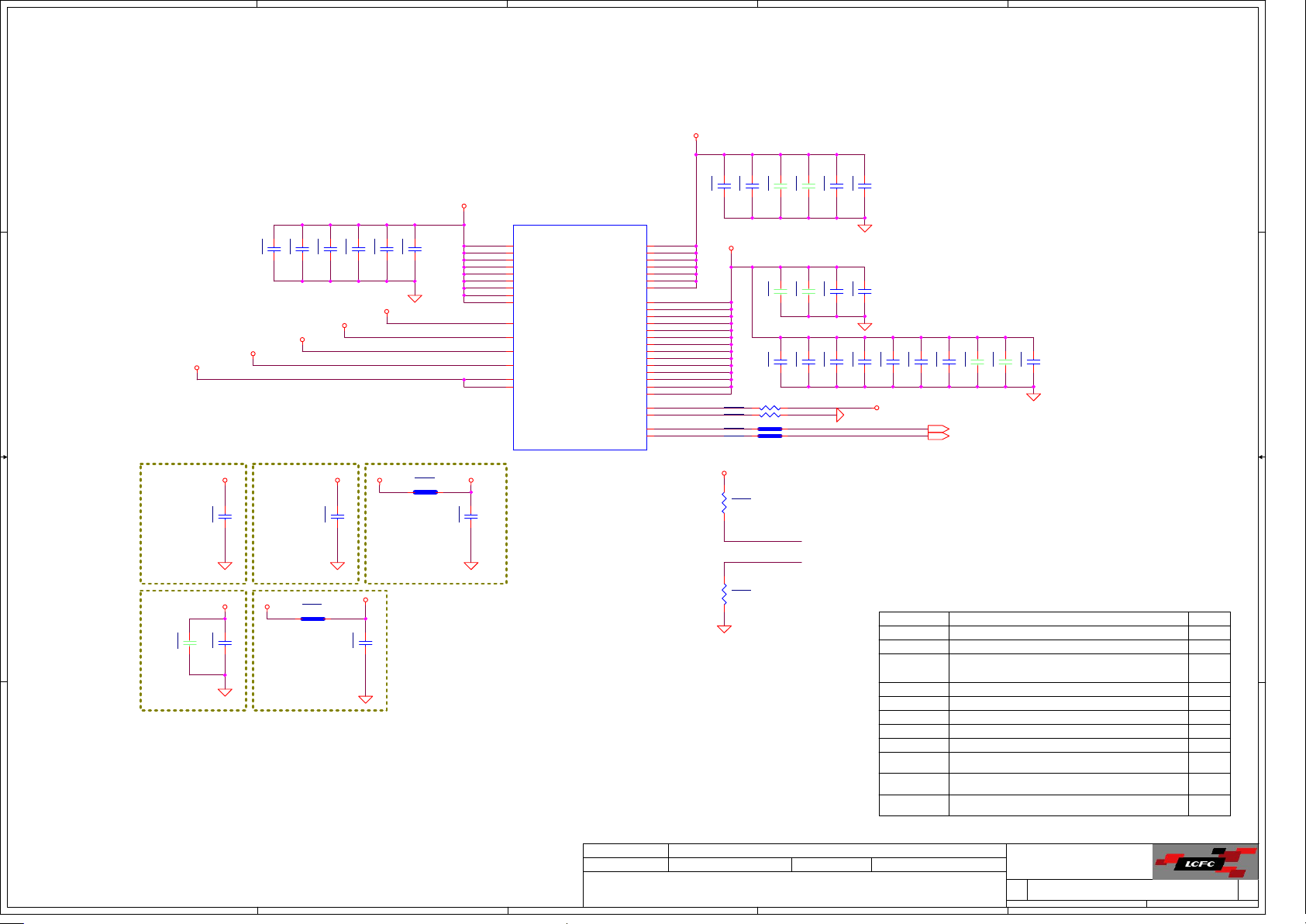

DDR_A_MA0

D D

DDR_A_D[63..0][23]

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

C C

B B

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKYLAKE-U_BGA1356

REV = 1

@

SKL_ULT

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

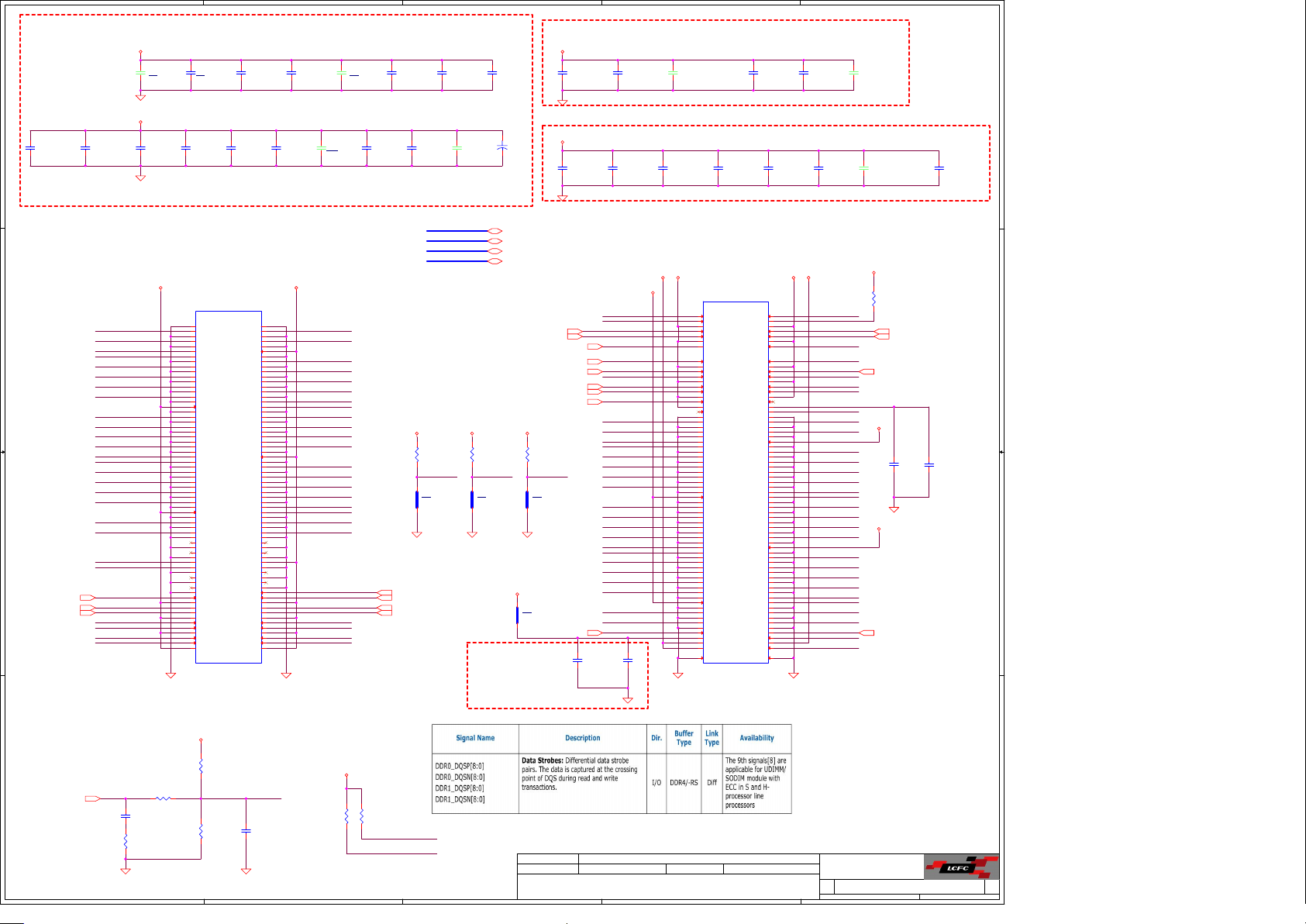

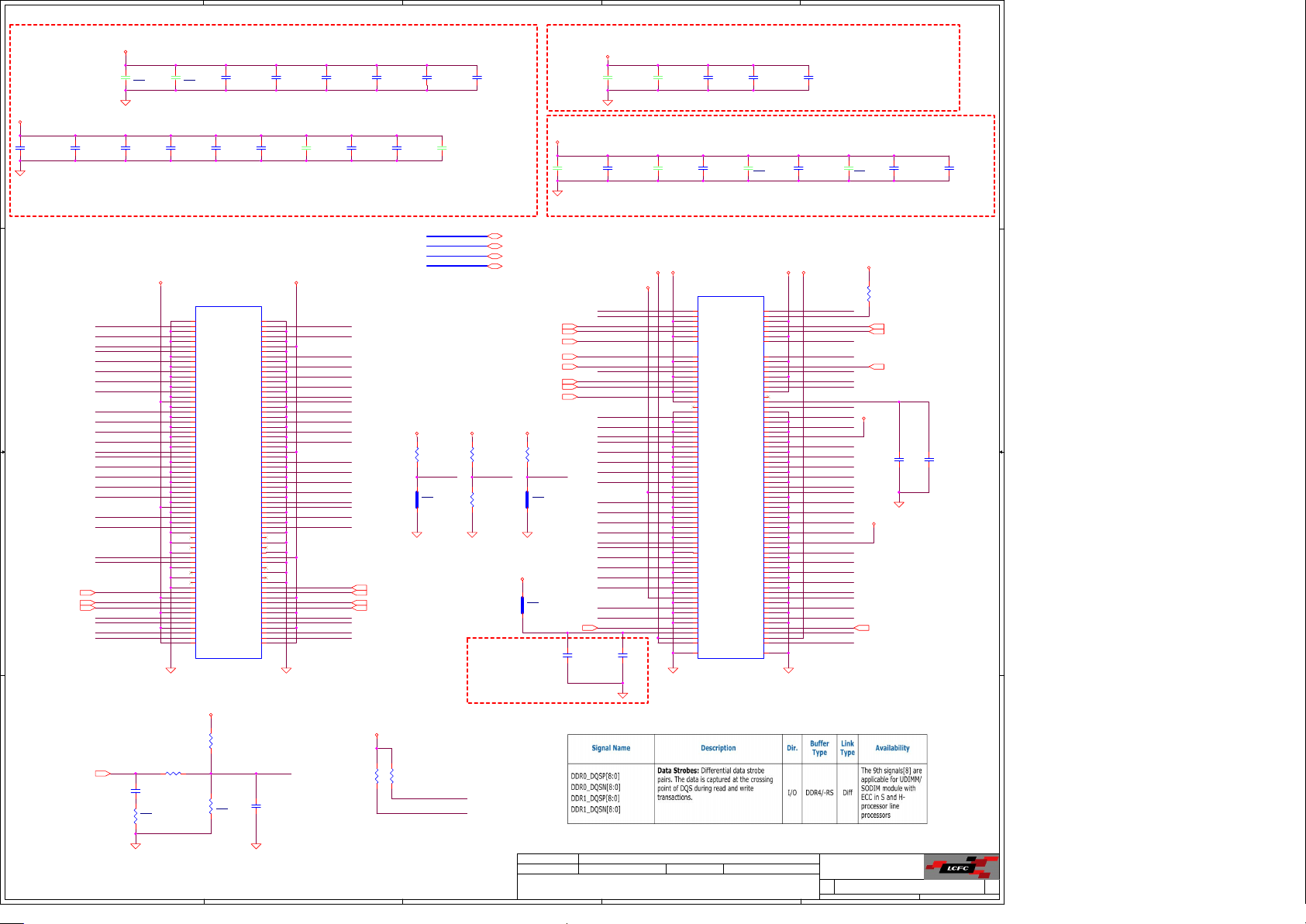

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

??2 OF 20

DDR_A_DDRCLK0_1866M#

AU53

DDR_A_DDRCLK0_1866M

AT53

DDR_A_DDRCLK1_1866M#

AU55

DDR_A_DDRCLK1_1866M

AT55

DDR_A_CKE0

BA56

DDR_A_CKE1

BB56

AW56

AY56

DDR_A_CS0#

AU45

DDR_A_CS1#

AU43

DDR_A_ODT0

AT45

DDR_A_ODT1

AT43

DDR_A_MA5

BA51

DDR_A_MA9

BB54

DDR_A_MA6

BA52

DDR_A_MA8

AY52

DDR_A_MA7

AW52

DDR_A_BG0

AY55

DDR_A_MA12

AW54

DDR_A_MA11

BA54

DDR_A_ACT_N

BA55

DDR_A_BG1

AY54

DDR_A_MA13

AU46

DDR_A_MA15

AU48

DDR_A_MA14

AT46

DDR_A_MA16

AU50

DDR_A_BA0

AU52

DDR_A_MA2

AY51

DDR_A_BA1

AT48

DDR_A_MA10

AT50

DDR_A_MA1

BB50

DDR_A_MA0

AY50

DDR_A_MA3

BA50

DDR_A_MA4

BB52

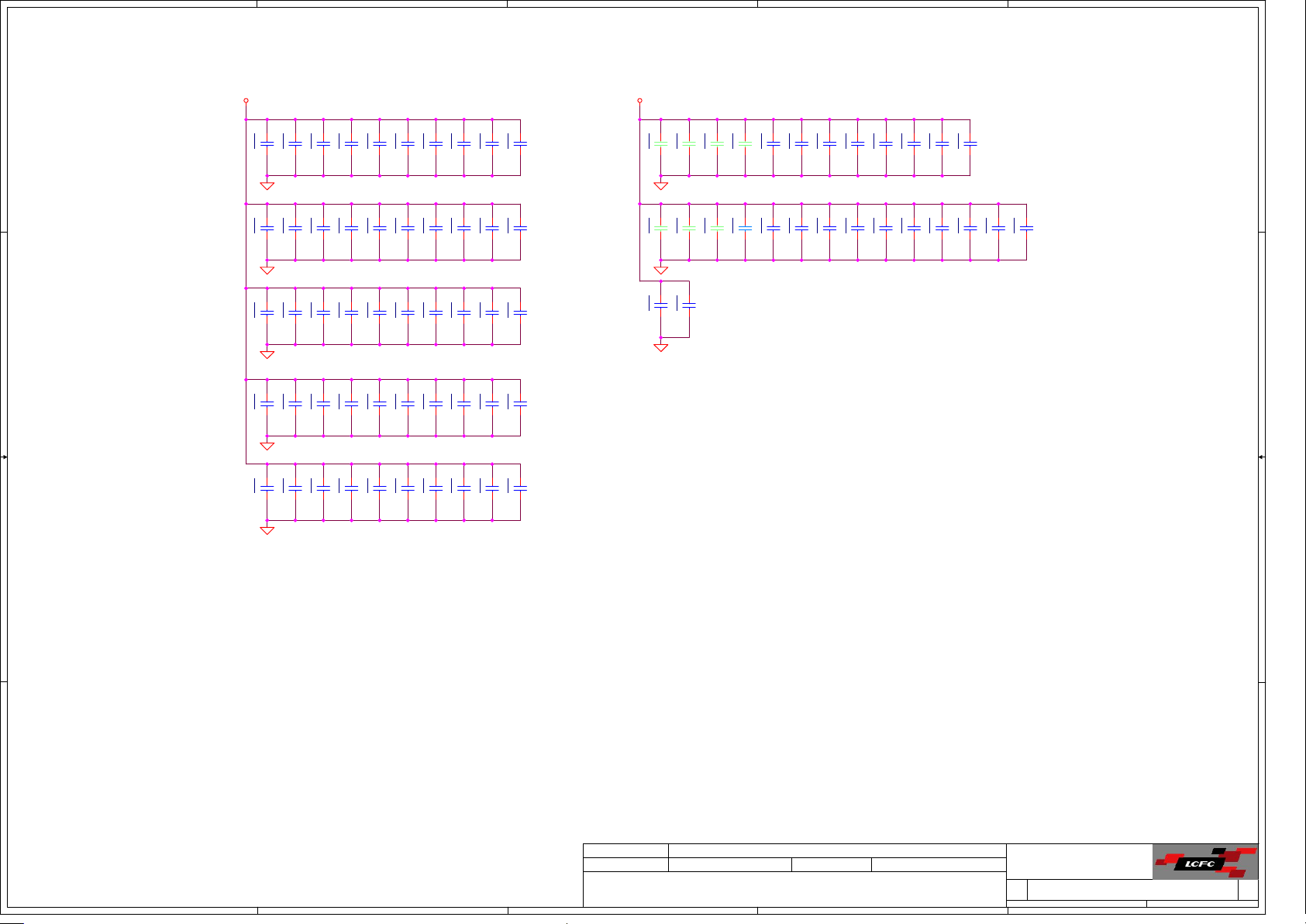

DDR_A_DQS#0

AM70

DDR_A_DQS0

AM69

DDR_A_DQS#1

AT69

DDR_A_DQS1

AT70

DDR_A_DQS#2

BA64

DDR_A_DQS2

AY64

DDR_A_DQS#3

AY60

DDR_A_DQS3

BA60

DDR_A_DQS#4

BA38

DDR_A_DQS4

AY38

DDR_A_DQS#5

AY34

DDR_A_DQS5

BA34

DDR_A_DQS#6

BA30

DDR_A_DQS6

AY30

DDR_A_DQS#7

AY26

DDR_A_DQS7

BA26

DDR_A_ALERT_N

AW50

DDR_A_PARITY

AT52

DDR4_VREF_CA_CPU_A

AY67

DDR4_VREF_DQ_CPU_A

AY68

DDR4_VREF_DQ_CPU_B

BA67

DDR_PG_CTRL

AW67

DDR_A_DDRCLK0_1866M# [23]

DDR_A_DDRCLK0_1866M [23]

DDR_A_DDRCLK1_1866M# [23]

DDR_A_DDRCLK1_1866M [23]

DDR_A_CKE0 [23]

DDR_A_CKE1 [23]

DDR_A_CS0# [23]

DDR_A_CS1# [23]

DDR_A_ODT0 [23]

DDR_A_ODT1 [23]

DDR_A_BG0 [23]

DDR_A_ACT_N [23]

DDR_A_BG1 [23]

DDR_A_BA0 [23]

DDR_A_BA1 [23]

DDR_A_ALERT_N [23]

DDR_A_PARITY [23]

DDR4_VREF_CA_CPU_A [23]

1

TC1

DDR4_VREF_DQ_CPU_B [24]

CC538

0.1U_0402_10V7-K @

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_MA16

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

+3V_DDR

12

+1.2V

DDR_PG_CTRLDDR_PG_CTRL

1

12

@

2

2

RD31

10K_0402_5%

1

3

RD32

100K_0402_5%

@

SM_PG_CTRL

QD1

DTC115TMT2L_VMT3

+3VALW

12

R0601

100K_0402_5%

DDR_A_MA[0..16] [23]

DDR_A_DQS#[0..7] [23]

DDR_A_DQS[0..7] [23]

+2.5V

12

R0602

100K_0402_5%

@

SM_PG_CTRL [87]

+1.2V

+3VALW

UC2

NC11Vcc

2

A

3

GND

74AUP1G07GF_SOT891-6_1X1

@

2

RC515

@

0_0402_5%

12

2016/12/31

2016/12/31

2016/12/31

DDR_PG_CTRL

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/09/01

2015/09/01

2015/09/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

6

5

NC2

4

Y

Title

Title

Title

KBL(3/16):DDR4 CH.A

KBL(3/16):DDR4 CH.A

KBL(3/16):DDR4 CH.A

Size

Size

Size

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

@

1 2

1

CC100

0.1U_0402_10V7-K@

2

Document Number Rev

Document Number Rev

Document Number Rev

DL470_NM-B021

DL470_NM-B021

DL470_NM-B021

Friday, November 04, 2016

Friday, November 04, 2016

Friday, November 04, 2016

RC500

100K_0402_5%

1

+3VS

@

1 2

RC516

100K_0402_5%

SM_PG_CTRL

6 99

6 99

6 99

0.2

0.2

0.2

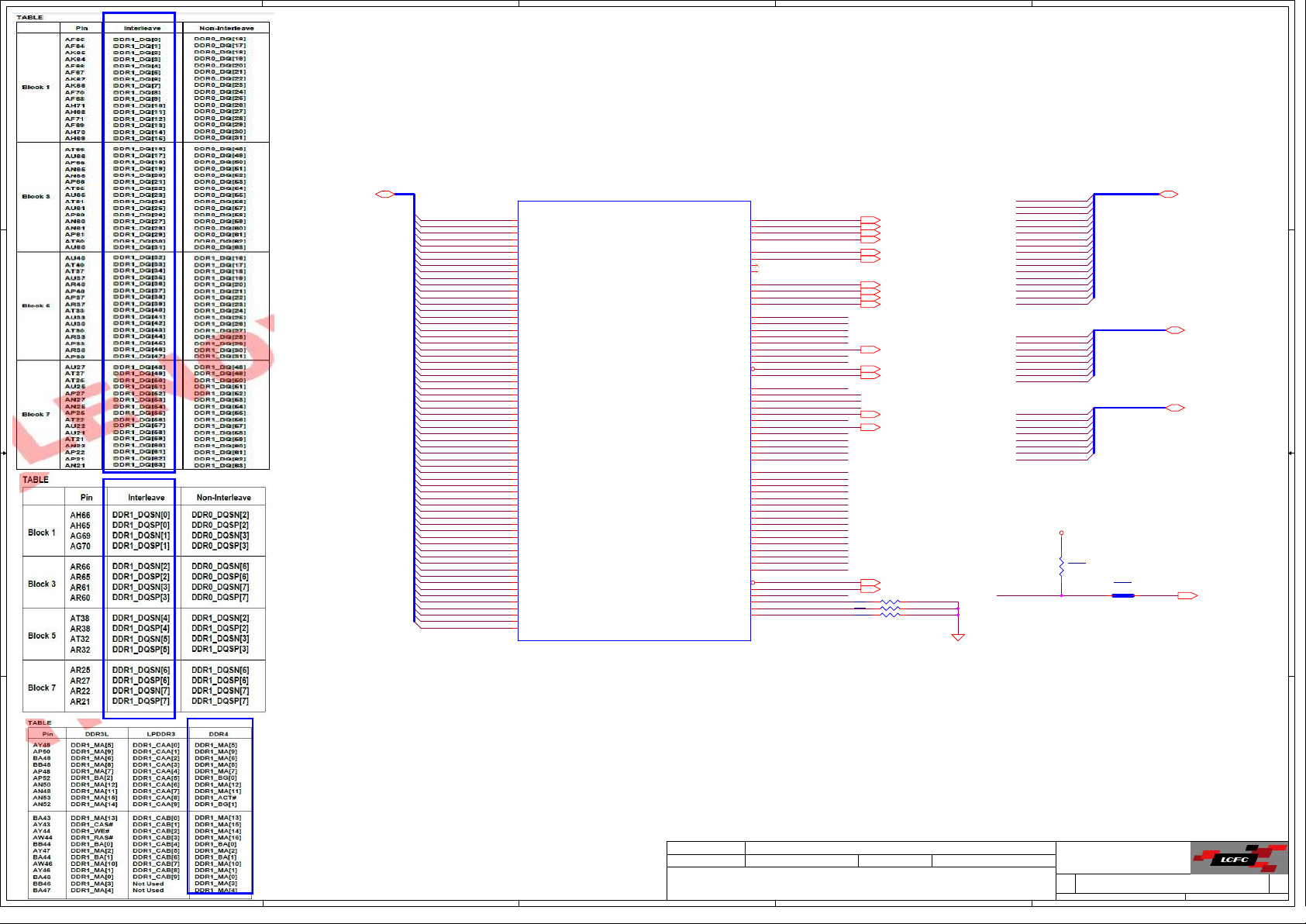

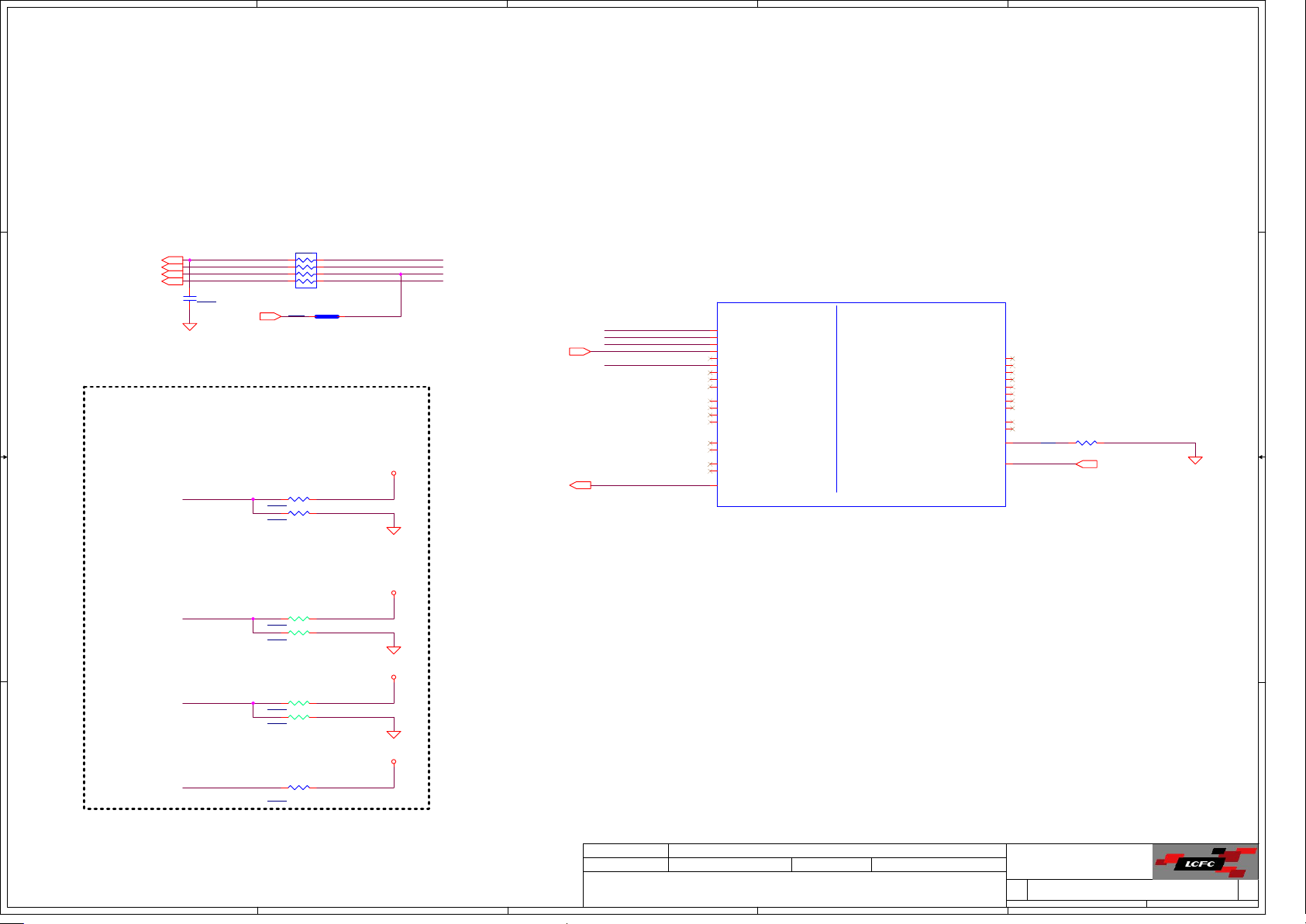

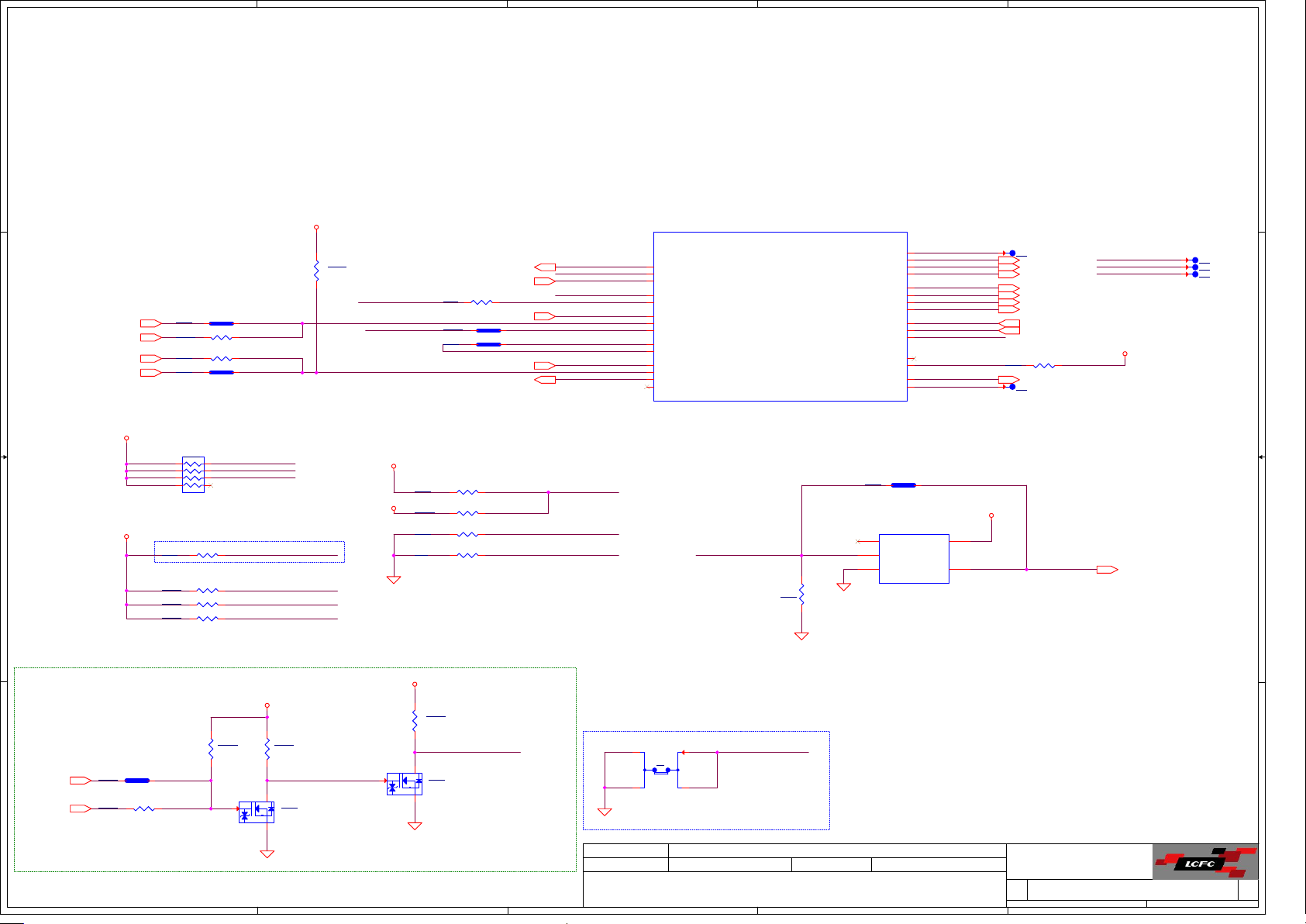

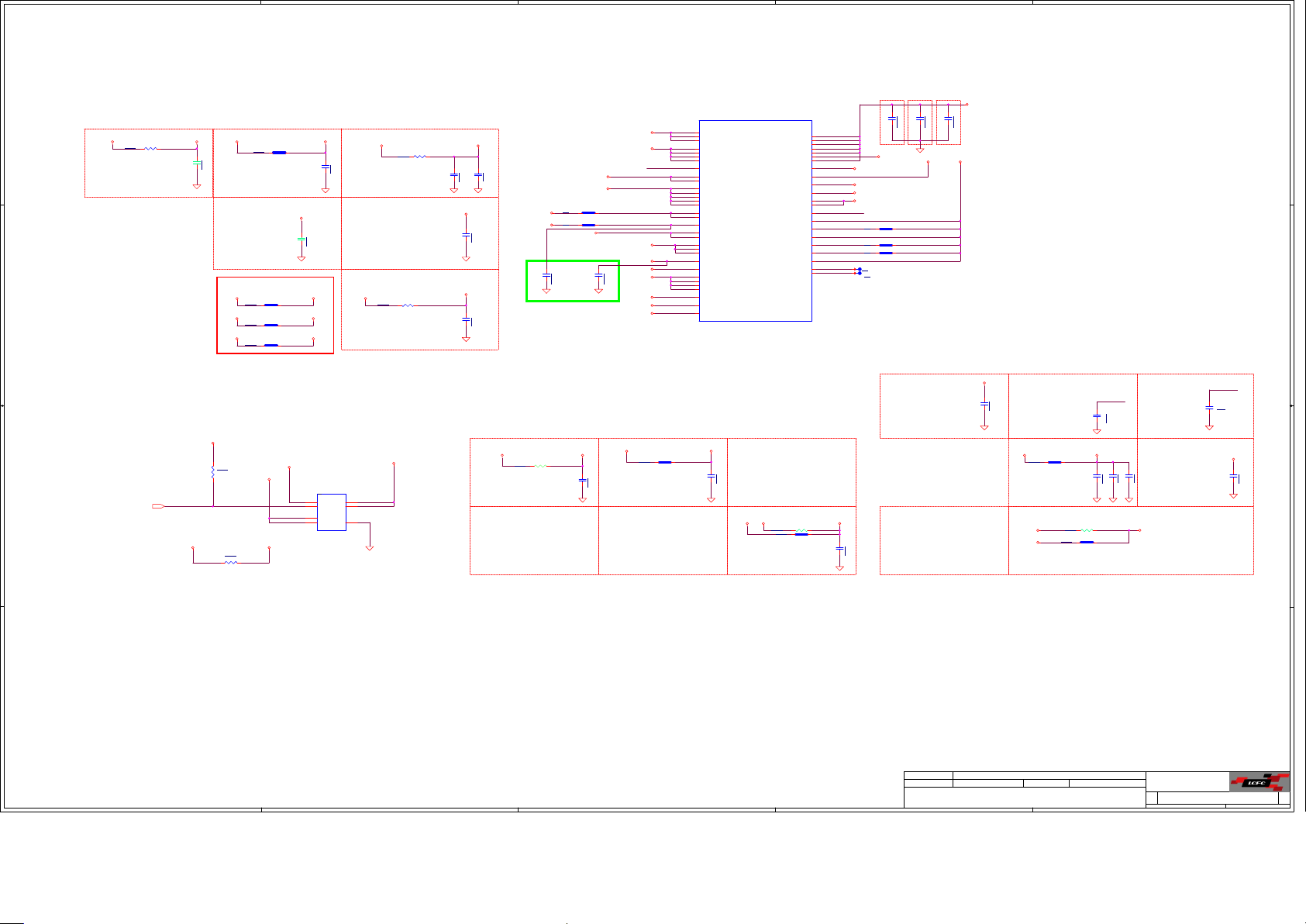

5

D D

4

3

2

1

DDR_B_D[0..63][24]

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

C C

B B

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKYLAKE-U_BGA1356

REV = 1

@

SKL_ULT

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

DDR1_PAR

??3 OF 20

DDR_B_DDRCLK0_1866M#

AN45

DDR_B_DDRCLK1_1866M#

AN46

DDR_B_DDRCLK0_1866M

AP45

DDR_B_DDRCLK1_1866M

AP46

DDR_B_CKE0

AN56

DDR_B_CKE1

AP55

AN55

AP53

DDR_B_CS0#

BB42

DDR_B_CS1#

AY42

DDR_B_ODT0

BA42

DDR_B_ODT1

AW42

DDR_B_MA5

AY48

DDR_B_MA9

AP50

DDR_B_MA6

BA48

DDR_B_MA8

BB48

DDR_B_MA7

AP48

DDR_B_BG0

AP52

DDR_B_MA12

AN50

DDR_B_MA11

AN48

DDR_B_ACT_N

AN53

DDR_B_BG1

AN52

DDR_B_MA13

BA43

DDR_B_MA15

AY43

DDR_B_MA14

AY44

DDR_B_MA16

AW44

DDR_B_BA0

BB44

DDR_B_MA2

AY47

DDR_B_BA1

BA44

DDR_B_MA10

AW46

DDR_B_MA1

AY46

DDR_B_MA0

BA46

DDR_B_MA3

BB46

DDR_B_MA4

BA47

DDR_B_DQS#0

AH66

DDR_B_DQS0

AH65

DDR_B_DQS#1

AG69

DDR_B_DQS1

AG70

DDR_B_DQS#2

AR66

DDR_B_DQS2

AR65

DDR_B_DQS#3

AR61

DDR_B_DQS3

AR60

DDR_B_DQS#4

AT38

DDR_B_DQS4

AR38

DDR_B_DQS#5

AT32

DDR_B_DQS5

AR32

DDR_B_DQS#6

AR25

DDR_B_DQS6

AR27

DDR_B_DQS#7

AR22

DDR_B_DQS7

AR21

DDR_B_ALERT_N

AN43

DDR_B_PARITY

AP43

DDR4_DRAMRST_N DDR4_DRAMRST_N

AT13

SM_RCOMP0

AR18

SM_RCOMP1

AT18

SM_RCOMP2

AU18

[KBL PDG]for DDR4 COMPENSATION

DDR_RCOMP[0] Pull down 121 ohm resistor

DDR_RCOMP[1] Pull down 80.6 ohm resistor

DDR_RCOMP[2] Pull down 100 ohm resistor

DDR_B_DDRCLK0_1866M# [24]

DDR_B_DDRCLK1_1866M# [24]

DDR_B_DDRCLK0_1866M [24]

DDR_B_DDRCLK1_1866M [24]

DDR_B_CKE0 [24]

DDR_B_CKE1 [24]

DDR_B_CS0# [24]

DDR_B_CS1# [24]

DDR_B_ODT0 [24]

DDR_B_ODT1 [24]

DDR_B_BG0 [24]

DDR_B_ACT_N [24]

DDR_B_BG1 [24]

DDR_B_BA0 [24]

DDR_B_BA1 [24]

DDR_B_ALERT_N [24]

DDR_B_PARITY [24]

1 2

RC8 121_0402_1%

1 2

RC9 80.6_0402_1%

1 2

RC10 100_0402_1%

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_MA16

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

+1.2V

RC501

470_0402_5%

1 2

RC502

0_0402_SM

1 2

DDR_B_MA[0..16] [24]

DDR_B_DQS#[0..7] [24]

DDR_B_DQS[0..7] [24]

DDR4_DRAMRST# [23,24]

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/09/01

2015/09/01

2015/09/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/12/31

2016/12/31

2016/12/31

Title

KBL(4/16):DDR4 CH.B

KBL(4/16):DDR4 CH.B

KBL(4/16):DDR4 CH.B

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

DL470_NM-B021

DL470_NM-B021

DL470_NM-B021

Friday, November 04, 2016

Friday, November 04, 2016

Friday, November 04, 2016

7 99

7 99

1

7 99

0.2

0.2

0.2

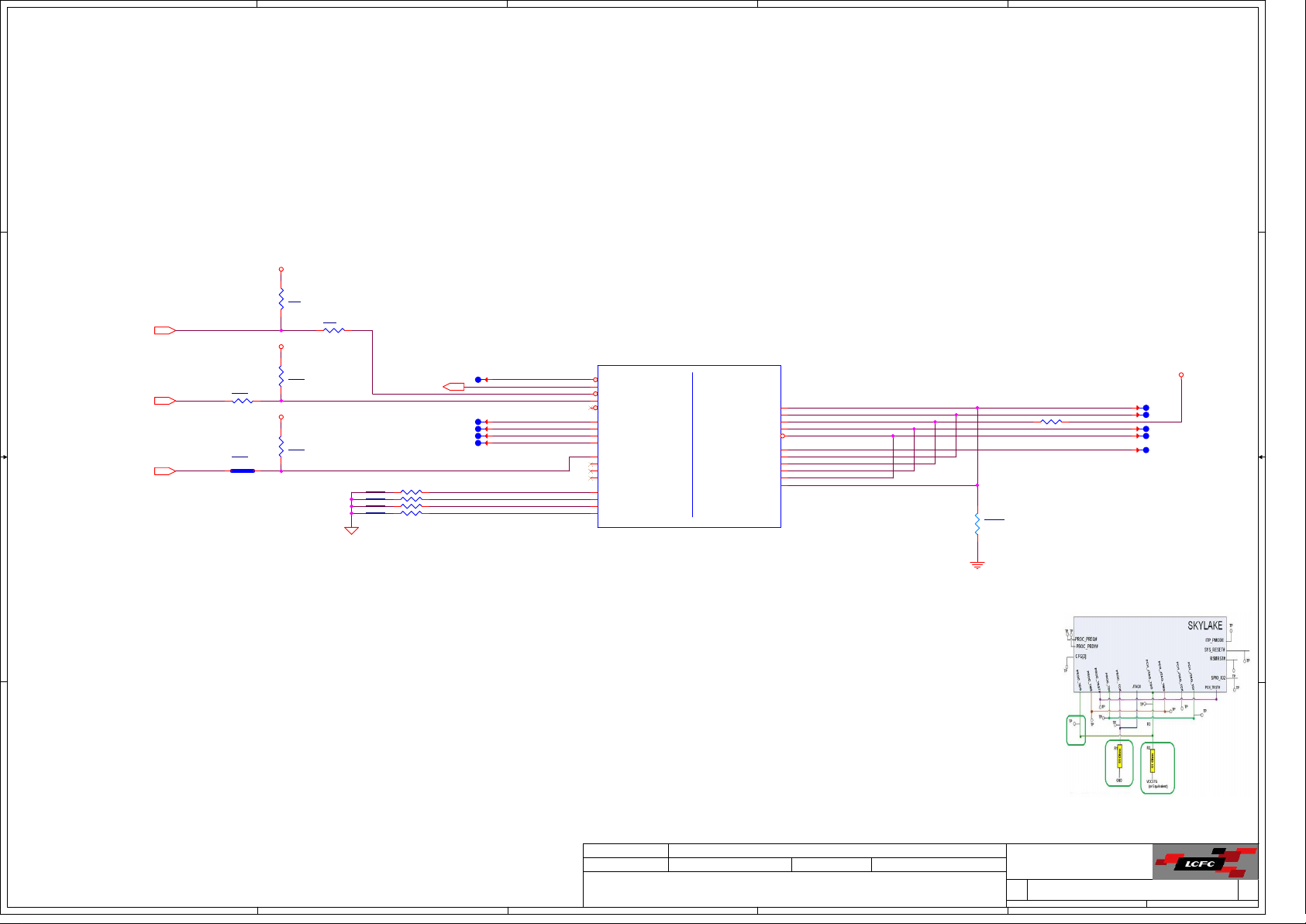

5

D D

+VCC_STG

12

RC2

1K_0402_5%

12

RC61

1K_0402_1%

12

RC51

10K_0402_5%

RC3

1 2

499_0402_1%

VR_HOT#[77,85,93]

C C

H_THERMTRIP#[30]

EC_WAKE#[30,77]

VR_HOT#

RC62

1 2

@

0_0402_5%

RC54

0_0402_SM

1 2

+VCC_ST

+3V_PCH

4

H_PECI[77]

1 2

RC151 49.9_0402_1%

1 2

RC114 49.9_0402_1%

1 2

RC200 49.9_0402_1%

1 2

RC113 49.9_0402_1%

T1

T4

T6

T8

T10

1

CATERR#

H_PECI

VR_HOT#_R

THRMTRIP#

XDP_BPM#0

1

XDP_BPM#1

1

XDP_BPM#2

1

XDP_BPM#3

1

EC_WAKE#_SUS

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

UC1D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

SKYLAKE-U_BGA1356

3

SKL_ULT

CPU MISC

4 OF 20REV = 1

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

XDP_TCLK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

2

1 2

RC517 100_0402_5%

XDP@

RC518

51_0402_5%

XDP@

1 2

1

+VCC_ST

1

T63

1

T64

1

T65

1

T66

1

T67

B B

[KBL PDG FOR DCL DEBUG]

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/12

2016/01/12

2016/01/12

Title

KBL_XDP/ JTAG

KBL_XDP/ JTAG

KBL_XDP/ JTAG

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Friday, November 04, 2016

Friday, November 04, 2016

Date: Sheet of

Date: Sheet of

Date: Sheet of

Friday, November 04, 2016

DL470_NM-B021

DL470_NM-B021

DL470_NM-B021

1

8 99

8 99

8 99

0.2

0.2

0.2

5

4

3

2

1

Near UC16M1

SPI_IO3_16MB SPI_IO3

SPI_CLK_16MB

SPI_MOSI_IO0_16MB

SPI_IO2_16MB

D D

C C

Functional Strap Definitions

RPC5

1 8

SPI_CLK

2 7

SPI_MOSI_IO0

3 6

SPI_IO2

4 5

33_0804_8P4R_5%

SD30000370T

+3V_PCH

RPC12

18

27

36

45

10K_0804_8P4R_5%

+3VS

RPC26

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

L:Disable Intel ME Crypto TLS cipher suite (no confidentiality).

*H:Enable Intel ME Crypto Transport Layer Security (TLS) cipher

suite (with confidentiality).Support Intel AMT with TLS and Intel

SBA (Small Business Advantage) with TLS.

GPP_C2, Internal PD 20K

GPP_C2

GPP_C5, Internal PD 20K

B B

Reverse internal 1K PU high

+3V_SPI

RC33 1K_0402_1%

RC34 1K_0402_1%

DOCK_ID0

DOCK_ID1

DOCK_ID2

DOCK_ID3

SERIRQ

KBRST#

EC_SCI#

1 2

RC306 1K_0402_5%

1 2

RC307 20K_0402_5%@

*L: LPC

H: eSPI

GPP_C5

RC83 1K_0402_5%

1 2

RC350 20K_0402_5%

@

@

1 2

1 2

RC399

1K_0402_1%

@

C-LINK

To TPM IC

+3V_PCH

12

1K_0402_1% @

1 2

SPI_CLK[70]

SPI_MOSI_IO0[70]

SPI_MISO_IO1[70]

SPI_CS2#_TPM[70]

+3VALW_PCH

RC392

1 2

CL_DATA_WLAN[66]

CL_RST_WLAN#[66]

CL_CLK_WLAN[66]

DOCK_ID1[44]

DOCK_ID2[44]

DOCK_ID3[44]

1

T17

DOCK_ID0[44]

EC_SCI#[77]

KBRST#[77]

SERIRQ[70,77]

SPI_CLK

SPI_MOSI_IO0

SPI_MISO_IO1

SPI_CS2#_TPM

JTAG ODT

SPI0_MOSI

SPI_MOSI_IO0

SPI_MISO_IO1

SPI_CLK

SPI_MISO_IO1

SPI_MOSI_IO0

SPI_IO2

SPI_IO3

SPI_CS0#_16MB

SPI_CS2#_TPM

DOCK_ID1

DOCK_ID2

DOCK_ID3

DOCK_CAP_ID#

DOCK_ID0

EC_SCI#

CL_CLK_WLAN

CL_DATA_WLAN

CL_RST_WLAN#

KBRST#

SERIRQ

RC298 1K_0402_5%

RC303 20K_0402_5%

RC308 1K_0402_5%

RC309 20K_0402_5%@

UC1E

AV2

AW3

AV3

AW2

AU4

AU3

AU2

AU1

M2

M3

J4

V1

V2

M1

G3

G2

G1

AW13

AY11

SKYLAKE-U_BGA1356

1 2

@

1 2

@

RGB(128,255,128)

1 2

@

1 2

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

+3V_SPI

+3V_SPI

20121218

+3V_SPI

SKL_ULT

5 OF 20REV = 1

SMBUS, SMLINK

GPP_B23/SML1ALERT#/PCHHOT#

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

R7

R8

R10

R9

W2

W1

W3

V3

AM7

PCH_SMB_CLK

PCH_SMB_DATA

GPP_C2

PCH_SML0_CLK

PCH_SML0_DAT

GPP_C5

PCH_SML1CLK

PCH_SML1DATA

GPP_B23

PCH_SML0_CLK [60]

PCH_SML0_DAT [60]

RC375 150K_0402_5%

LAN PHY

1 2

+3V_PCH

FOR DCI USE

LPC_AD0

LPC

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

SUS_STAT#

PCH_PCI_CLK_R

CLKRUN#

SMBus

PCH_SMB_CLK

PCH_SMB_DATA

EC and TPM Module debug port

1 2

RC26 22_0402_5%

1 2

RC48 8.2K_0402_5%

+3VS

2

G

6 1

S

D

QC1A

5

2N7002KDWH_SOT363-6

G

SB000013A00

3 4

S

D

QC1B

2N7002KDWH_SOT363-6

SB000013A00

PCH_SML0_DAT

PCH_SML0_CLK

PCH_SMB_CLK

PCH_SMB_DATA

PCH_SML1CLK

PCH_SML1DATA

DIMM1, DIMM2

CP, Security ROM

1 2

RC35 4.7K_0402_5%

1 2

RC36 4.7K_0402_5%

PM_SMB_CLK

PM_SMB_DAT

LPC_AD0 [77]

LPC_AD1 [77]

LPC_AD2 [77]

LPC_AD3 [77]

LPC_FRAME# [77]

1

T61

CLK_PCI_EC [77]

1

CV178

RF@

+3VS

RC30 499_0402_1%

RC29 499_0402_1%

22P_0402_50V8-J

2

1 2

1 2

RPC6

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

PM_SMB_CLK [23,24,63]

PM_SMB_DAT [23,24,63]

+3VS

+3V_PCH

+3V_PCH

M3 Support, Intel LAN PHY, (Wireless LAN)

+3VM = +3V_SPI

1. VPRO : Q6, +3VLAW To +3VM

2. NVPRO :

a. R17 and RC38, +3VALW to +3VM

+3V_SPI

1 2

+3VS

+3VM

A A

RC37 0_0402_5%@

1 2

RC38 0_0402_SM

+3V_SPI

0.085 A, 10mils

D100

RB520CM-30T2R_VMN2M2

1 2

VCC3_SUS_SPI

2

CC101

1

0.1U_0201_6.3V6-K

UC16M1

8

SPI_IO3_16MB

SPI_CLK_16MB

2

SPI_MOSI_IO0_16MB

CC102

1

0.1U_0201_6.3V6-K

2

CC103

33P_0201_25V8-J

EMC@

1

VCC

7

/HOLD/RESET(IO3)

6

CLK

5

DI(IO0)

W25Q128FVSIQ_SO8

2

CC104

33P_0201_25V8-J

EMC@

1

DO(IO1)

/WP(IO2)

GND

1

/CS

2

3

4

R530 33_0402_5%

RC504 33_0402_5%

2

CC105

33P_0201_25V8-J

EMC@

1

1 2

1 2

SPI_CS0#_16MB

SPI_MISO_IO1SPI_MISO_IO1_16MB

SPI_IO2_16MB

PCH_SML1CLK EC_SMB_CK3

PCH_SML1DATA EC_SMB_DA3

+3VS

2

6 1

D

QC2A

5

2N7002KDWH_SOT363-6

G

SB000013A00

3 4

S

D

QC2B

2N7002KDWH_SOT363-6

SB000013A00

GPU, Thermal Sendor,

Embedded Controller, G sensor

G

S

2N7002KDWH

Vth= min 1V, max 2.5V

ESD 2KV

EC_SMB_CK3 [30,69,70,77]

EC_SMB_DA3 [30,69,70,77]

Mirror Code, Close to SPI ROM (UC8M1).

Title

Title

Security Classification

Security Classification

FSCE#[77]

SPI_FMOSI#[77]

SPI_FMISO[77]

SPI_FSCK[77]

FSCE#

SPI_FMOSI#

SPI_FMISO

5

1 2

RE1 0_0402_SM

1 2

RE2 0_0402_SM

1 2

RE3 0_0402_SM

1 2

RE4 0_0402_SM

SPI_CS0#_16MB

SPI_MOSI_IO0_16MB

SPI_MISO_IO1_16MB

SPI_CLK_16MBSPI_FSCK

4

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/12

2016/01/12

2016/01/12

Title

KBL_LPC/SPI/SMBUS

KBL_LPC/SPI/SMBUS

KBL_LPC/SPI/SMBUS

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Friday, November 04, 2016

Friday, November 04, 2016

Date: Sheet of

Date: Sheet of

Date: Sheet of

Friday, November 04, 2016

DL470_NM-B021

DL470_NM-B021

DL470_NM-B021

1

9 99

9 99

9 99

0.2

0.2

0.2

5

4

3

2

1

GPP_B18, Internal PD 20K

*L: Disable “ No Reboot” mode

H: Enable “ No Reboot” mode

GPP_B18 GPP_B22

D D

FN, F1, F4 PD 100K, BIOS need output

"High" while act i ve

C C

RC98 1K_0402_5%

RC97 20K_0402_5%

12

@

12

@

To VGA_CORE IC, RPC3.7

+3VS +3VS

RF_OFF#[66]

HP_JACK_IN[57]

TRACKP_ON#[63]

BT_ON[66]

@

TP1

@

TP2

F4_LED[65]

TPNL_EN[52]

VGA_ON[30,38,39,91]

GPP_B22, Internal PD 20K

*L: SPI

H: LPC

RF_OFF#

HP_JACK_IN

GPP_B18

TRACKP_ON#

BT_ON

GPP_B22

PLANARID0

PLANARID1

PLANARID2

PLANARID3

UART2_RX

1

UART2_TX

1

F4_LED

TPNL_EN

VGA_ON

DGPU_HOLD_RST#

12

@

RC99 20K_0402_5%

1 2

@

RC100 20K_0402_5%

UC1F

LPSS ISH

AN8

GPP_B15/GSPI0_CS#

AP7

GPP_B16/GSPI0_CLK

AP8

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

AM5

GPP_B19/GSPI1_CS#

AN7

GPP_B20/GSPI1_CLK

AP5

GPP_B21/GSPI1_MISO

AN5

GPP_B22/GSPI1_MOSI

AB1

GPP_C8/UART0_RXD

AB2

GPP_C9/UART0_TXD

W4

GPP_C10/UART0_RTS#

AB3

GPP_C11/UART0_CTS#

AD1

GPP_C20/UART2_RXD

AD2

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD4

GPP_C23/UART2_CTS#

U7

GPP_C16/I2C0_SDA

U6

GPP_C17/I2C0_SCL

U8

GPP_C18/I2C1_SDA

U9

GPP_C19/I2C1_SCL

AH9

GPP_F4/I2C2_SDA

AH10

GPP_F5/I2C2_SCL

AH11

GPP_F6/I2C3_SDA

AH12

GPP_F7/I2C3_SCL

AF11

GPP_F8/I2C4_SDA

AF12

GPP_F9/I2C4_SCL

SKYLAKE-U_BGA1356

SKL_ULT

6 OF 20REV = 1

+3VS

1 2

RC505 10K_0402_5%DIS@

1 2

RC506 10K_0402_5%UMA@

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D15/ISH_UART0_RTS#

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_A12/BM_BUSY#/ISH_GP6

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

DISCRETE_PRESENCE

PCH_WWAN_RST#

CP_RESET#

CP_BYPASS

TP4RST

DISCRETE_PRESENCE

WWANRF_DISABLE#

GPP_D13

FN_LED

F1_LED

WWAN_CFG1

WWAN_CFG2

WWAN_CFG3

PCH_WWAN_RST# [66]

CP_RESET# [63]

CP_BYPASS [63]

TP4RST [63]

WWANRF_DISABLE# [66]

GPP_D13 [58]

FN_LED [65]

F1_LED [65]

+3VALW

R517

R516

1 2

1 2

10K_0402_5%

10K_0402_5%

WWAN_CFG1 [66,67]

WWAN_CFG2 [66]

WWAN_CFG3 [66,67]

Project/SKU ID

PLANARID3

(GPP_C11)

1

B B

1 2

PCH_PLT_RST#[15]

PLT_RST#[15,42,60,66,70,71,77]

+3V_PCH

+3VS

+3VS

A A

+3V_PCH

1 2

R288 4.7K_0402_5%@

1 2

RC120 10K_0402_5%

1 2

RC121 4.7K_0402_5%

1 2

RC123 10K_0402_5%

1 2

RC124 10K_0402_5%@

1 2

RC125 10K_0402_5%

5

1 2

RC119 10K_0402_5%

RF_OFF#

VGA_ON

BT_ON

CP_BYPASS

WWANRF_DISABLE#

DGPU_HOLD_RST#

RC385 0_0402_5%@

RC386 0_0402_5%DIS@

4

1 2

DGPU_HOLD_RST#

1 2

RC60 0_0402_5%@

+3VS

5

2

P

B

4

Y

1

A

G

UC5

DIS@

TC7SZ08FU SC70-5

3

SA000067X00

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

PD 10K at GPU Pin

PLT_RST_VGA# [30,35,91]

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

PLANARID0

PLANARID1

PLANARID2

PLANARID3

2016/01/12

2016/01/12

2016/01/12

1(RC65)

0

12

RC65

10K_0402_5%

12

RC69

@

10K_0402_5%

X

PLANARID2

(GPP_C10)

NVPRO SKU (RC70)

12

RC66

VPRO@

10K_0402_5%

12

RC70

NVPRO@

10K_0402_5%

Title

Title

Title

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

PLANARID1

(GPP_C9)

DIS (RC67)VPRO SKU (RC66)

UMA (RC71)

DIS@

UMA@

SKL_GPIO

SKL_GPIO

SKL_GPIO

Friday, November 04, 2016

Friday, November 04, 2016

Friday, November 04, 2016

PLANARID0

(GPP_C8)

15" (RC68)

14" (RC72)

12

RC67

10K_0402_5%

12

RC71

10K_0402_5%

DL470_NM-B021

DL470_NM-B021

DL470_NM-B021

1

+3VS

12

RC68

@

10K_0402_5%

12

RC72

10K_0402_5%

10 99

10 99

10 99

0.2

0.2

0.2

5

D D

4

3

2

1

PCH_HDA_BCLK[56]

PCH_HDA_RST#[56]

PCH_HDA_SDOUT[56]

PCH_HDA_SYNC[56]

C C

GPP_B14, Internal PD 20K

No Reboot on TCO

Timer expiration

pull-up to VCC3_3 through a 1~8.2KΩ

resistor to disable this capability

B B

Processor Strapping

543016_543016_SKL_PDG_UY_1_0_pub

P780

PCH_HDA_BCLK

PCH_HDA_RST# HDA_RST#

PCH_HDA_SDOUT

PCH_HDA_SYNC HDA_SYNC

1

CV179

RF@

22P_0402_50V8-J

2

ME_FLASH[77]

PCH_BEEP

PCH_HDA_SDIN0

HDA_SDOUT

RPC2

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

SD30000370T

1 2

RC21 0_0402_SM

1 2

@

RC376 8.2K_0402_5%

1 2

@

RC300 20K_0402_5%

1 2

@

RC297 1K_0402_5%

1 2

RC301 20K_0402_5%@

1 2

@

RC299 1K_0402_5%

1 2

RC302 20K_0402_5%@

HDA_BCLK

HDA_SDOUT

+3VS

+VCC_IO

+VCC_HDA

UC1G

HDA_SYNC

HDA_BCLK

HDA_SDOUT

PCH_HDA_SDIN0[56]

PCH_BEEP[58]

PCH_HDA_SDIN0

HDA_RST#

PCH_BEEP

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK10

AW5

J5

AK7

AK6

AK9

H5

D7

D8

C8

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

GPP_D19/DMIC_CLK0

GPP_D20/DMIC_DATA0

GPP_D17/DMIC_CLK1

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

SKYLAKE-U_BGA1356

SKL_ULT

7 OF 20REV = 1

SDIO/SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_G7/SD_WP

GPP_A16/SD_1P8_SEL

SD_RCOMP

GPP_F23

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

1 2

R111 200_0402_1%

SC_DET#

SC_DET# [73]

+3V_PCH

A A

HDA_SYNC

5

1 2

RC356

1K_0402_5%

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/12

2016/01/12

2016/01/12

Title

KBL_HDA/GPIO

KBL_HDA/GPIO

KBL_HDA/GPIO

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Friday, November 04, 2016

Friday, November 04, 2016

Date: Sheet of

Date: Sheet of

Date: Sheet of

Friday, November 04, 2016

DL470_NM-B021

DL470_NM-B021

DL470_NM-B021

1

11 99

11 99

11 99

0.2

0.2

0.2

5

4

3

2

1

8 OF 20REV = 1

SKL_ULT

SSIC / USB3

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB2

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

SATA1_DEVSLP

SSD_DEVSLP1

USB3P1_RXN

H8

USB3P1_RXP

G8

USB3P1_TXN

C13

USB3P1_TXP

D13

USB3P2_RXN

J6

USB3P2_RXP

H6

USB3P2_TXN

B13

USB3P2_TXP

A13

USB3P3_RXN_DOCK

J10

USB3P3_RXP_DOCK

H10

USB3P3_TXN_DOCK

B15

USB3P3_TXP_DOCK

A15

USB3P4_RXN

E10

USB3P4_RXP

F10

USB3P4_TXN

C15

USB3P4_TXP

D15

USB20_N0

AB9

USB20_P0

AB10

USB20_N1

AD6

USB20_P1

AD7

USB20_N2

AH3

USB20_P2

AJ3

USB20_N3

AD9

USB20_P3

AD10

USB20_N4

AJ1

USB20_P4

AJ2

USB20_N5

AF6

USB20_P5

AF7

USB20_N6

AH1

USB20_P6

AH2

USB20_N7

AF8

USB20_P7

AF9

USB20_N8

AG1

USB20_P8

AG2

USB20_N9

AH7

USB20_P9

AH8

AB6

USBCOMP

AG3

AG4

USB_OC0#

A9

USB_OC1#

C9

USB_OC2#

D9

USB_OC3#

B9

J1

SATA1_DEVSLP

J2

SSD_DEVSLP1

J3

H2

H3

G4

H1

RC377 10K_0402_5%@

RC378 10K_0402_5%@

USB3P1_RXN [54]

USB3P1_RXP [54]

USB3P1_TXN [54]

USB3P1_TXP [54]

USB3P2_RXN [54]

USB3P2_RXP [54]

USB3P2_TXN [54]

USB3P2_TXP [54]

USB3P3_RXN_DOCK [44]

USB3P3_RXP_DOCK [44]

USB3P3_TXN_DOCK [44]

USB3P3_TXP_DOCK [44]

USB3P4_RXN [53]

USB3P4_RXP [53]

USB3P4_TXN [53]

USB3P4_TXP [53]

USB20_N0 [54]

USB20_P0 [54]

USB20_N1 [54]

USB20_P1 [54]

USB20_N2 [44]

USB20_P2 [44]

USB20_N3 [53]

USB20_P3 [53]

USB20_N4 [73]

USB20_P4 [73]

USB20_N5 [66]

USB20_P5 [66]

USB20_N6 [52]

USB20_P6 [52]

USB20_N7 [73]

USB20_P7 [73]

USB20_N8 [66]

USB20_P8 [66]

USB20_N9 [52]

USB20_P9 [52]

1 2

R121 113_0402_1%

1 2

RC403 1K_0402_5%@

1 2

RC404 1K_0402_5%@

USB_OC0# [54]

USB_OC1# [53]

SATA1_DEVSLP [42]

SSD_DEVSLP1 [66]

+3VS

12

12

On Board (Right-Front)

On Board (Right-Back)

DOCKING

S/B (AOU Port)

On Board (Right-Front)

On Board (Right-Back)

DOCKING

S/B (AOU Port)

SMART CARD

BT

CAMERA

Finger Printer

WWAN

Touch Panel

On Board (Right-Front)

S/B (AOU Port)

12

12

R286

15K_0402_5%@

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

R287

15K_0402_5%@

+3VALW

R512

R2750

1 2

1 2

10K_0402_5%

RPC23

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

10K_0402_5%

-PE_DTCT [42]

-WWAN_PE_DTCT [67]

+3V_PCH

D D

PCIE_CRX_GTX_N0[35]

PCIE_CRX_GTX_P0[35]

PCIE_CTX_C_GRX_N0[35]

PCIE_CTX_C_GRX_P0[35]

PCIE_CRX_GTX_N1[35]

PCIE_CRX_GTX_P1[35]

PCIE_CTX_C_GRX_N1[35]

PCIE_CTX_C_GRX_P1[35]

PCIE_CRX_GTX_N2[35]

PCIE12_SATA2_CRX_DTX_N[66]

PCIE12_SATA2_CRX_DTX_P[66]

PCIE12_SATA2_CTX_DRX_N[66]

PCIE12_SATA2_CTX_DRX_P[66]

PCIE8_SATA1_CRX_DTX_N[42]

PCIE8_SATA1_CRX_DTX_P[42]

PCIE8_SATA1_CTX_DRX_N[42]

PCIE8_SATA1_CTX_DRX_P[42]

PCIE_CTX_C_GRX_N2[35]

PCIE_CTX_C_GRX_P2[35]

PCIE_CTX_C_GRX_N3[35]

PCIE_CTX_C_GRX_P3[35]

PCIE5_CTX_C_DRX_N[60]

PCIE5_CTX_C_DRX_P[60]

PCIE6_CTX_C_DRX_N[71]

PCIE6_CTX_C_DRX_P[71]

PCIE9_CTX_C_DRX_N[66]

PCIE9_CTX_C_DRX_P[66]

PCIE11_CRX_DTX_N[66]

PCIE11_CRX_DTX_P[66]

PCIE11_CTX_DRX_N[66]

PCIE11_CTX_DRX_P[66]

PCIE_CRX_GTX_P2[35]

PCIE_CRX_GTX_N3[35]

PCIE_CRX_GTX_P3[35]

PCIE5_CRX_DTX_N[60]

PCIE5_CRX_DTX_P[60]

PCIE6_CRX_DTX_N[71]

PCIE6_CRX_DTX_P[71]

PCIE7_CRX_DTX_N[42]

PCIE7_CRX_DTX_P[42]

PCIE7_CTX_DRX_N[42]

PCIE7_CTX_DRX_P[42]

PCIE9_CRX_DTX_N[66]

PCIE9_CRX_DTX_P[66]

DGPU_PWROK

GPU

LAN

C C

Card Reader

HDD

WLAN

+3VS

B B

1 2

RC85 10K_0402_5%

UMA@

DGPU_PWROK[38,91]

M.2 SSD

1 2

CC8 0.22U_0402_10V6-KDIS@

1 2

CC9 0.22U_0402_10V6-KDIS@

1 2

CC26 0.22U_0402_10V6-KDIS@

1 2

CC27 0.22U_0402_10V6-KDIS@

1 2

CC28 0.22U_0402_10V6-KDIS@

1 2

CC29 0.22U_0402_10V6-KDIS@

1 2

CC18 0.22U_0402_10V6-KDIS@

1 2

CC21 0.22U_0402_10V6-KDIS@

1 2

CC552 0.1U_0402_10V7-K

1 2

CC551 0.1U_0402_10V7-K

1 2

CC547 0.1U_0402_10V7-K

CC548

1 2

0.1U_0402_10V7-K

1 2

CC553 0.1U_0402_10V7-K

1 2

CC554 0.1U_0402_10V7-K

1 2

R122 100_0402_1%

TP3@

TP4@

PCIE_CRX_GTX_N0

PCIE_CRX_GTX_P0

PCIE1_CTX_DRX_N0

PCIE1_CTX_DRX_P0

PCIE_CRX_GTX_N1

PCIE_CRX_GTX_P1

PCIE2_CTX_DRX_N1

PCIE2_CTX_DRX_P1

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P2

PCIE3_CTX_DRX_N2

PCIE3_CTX_DRX_P2

PCIE_CRX_GTX_N3

PCIE_CRX_GTX_P3

PCIE4_CTX_DRX_N3

PCIE4_CTX_DRX_P3

PCIE5_CRX_DTX_N

PCIE5_CRX_DTX_P

PCIE5_CTX_DRX_N

PCIE5_CTX_DRX_P

PCIE6_CRX_DTX_N

PCIE6_CRX_DTX_P

PCIE6_CTX_DRX_N

PCIE6_CTX_DRX_P

PCIE7_CRX_DTX_N

PCIE7_CRX_DTX_P

PCIE7_CTX_DRX_N

PCIE7_CTX_DRX_P

PCIE8_SATA1_CRX_DTX_N

PCIE8_SATA1_CRX_DTX_P

PCIE8_SATA1_CTX_DRX_N

PCIE8_SATA1_CTX_DRX_P

PCIE9_CRX_DTX_N

PCIE9_CRX_DTX_P

PCIE9_CTX_DRX_N

PCIE9_CTX_DRX_P

PCIE_RCOMP

XDP_PRDY_N

1

XDP_PREQ_N

1

PCIE11_CRX_DTX_N

PCIE11_CRX_DTX_P

PCIE11_CTX_DRX_N

PCIE11_CTX_DRX_P

PCIE12_SATA2_CRX_DTX_N

PCIE12_SATA2_CRX_DTX_P

PCIE12_SATA2_CTX_DRX_N

PCIE12_SATA2_CTX_DRX_P

UC1H

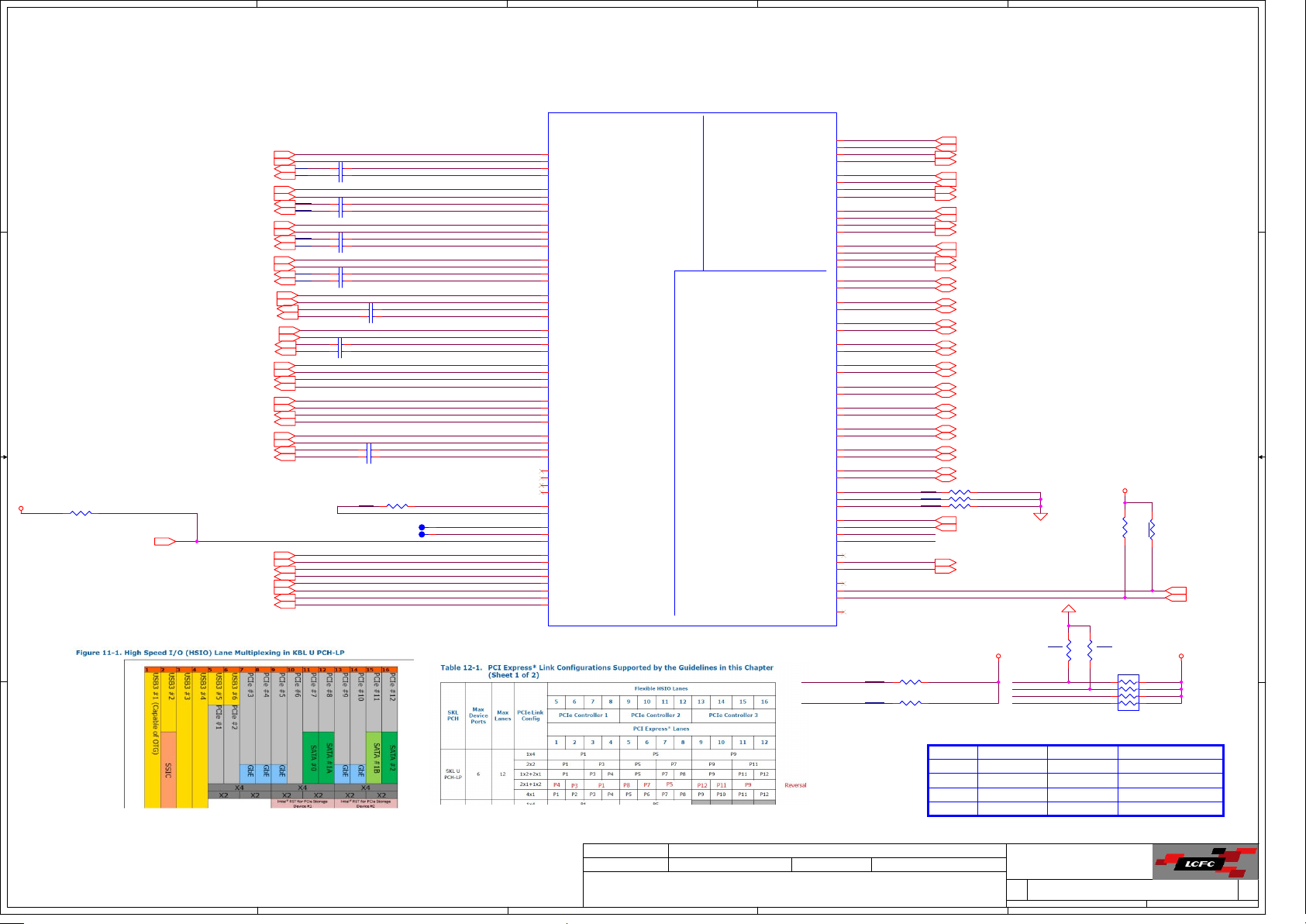

PCIE/USB3/SATA

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKYLAKE-U_BGA1356

USB_OC0#

USB_OC1#

2016/01/12

2016/01/12

2016/01/12

USB_OC2#

USB_OC3#

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Port 1, 2

Port 4

Unused. Unused.

Unused.

Date: Sheet of

Date: Sheet of

Date: Sheet of

USB3.0 Port NO.

Pin.

USB2.0 Port NO.

Port 0, 1

Port 3

Default Port Mapping

Port 0, 1

Port 2, 3

Port 4, 5

Unused.

Title

Title

Title

KBL_PCIE/ SATA/ USB

KBL_PCIE/ SATA/ USB

KBL_PCIE/ SATA/ USB

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Friday, November 04, 2016

Friday, November 04, 2016

Friday, November 04, 2016

Port 6, 7

DL470_NM-B021

DL470_NM-B021

DL470_NM-B021

1

12 99

12 99

12 99

0.2

0.2

0.2

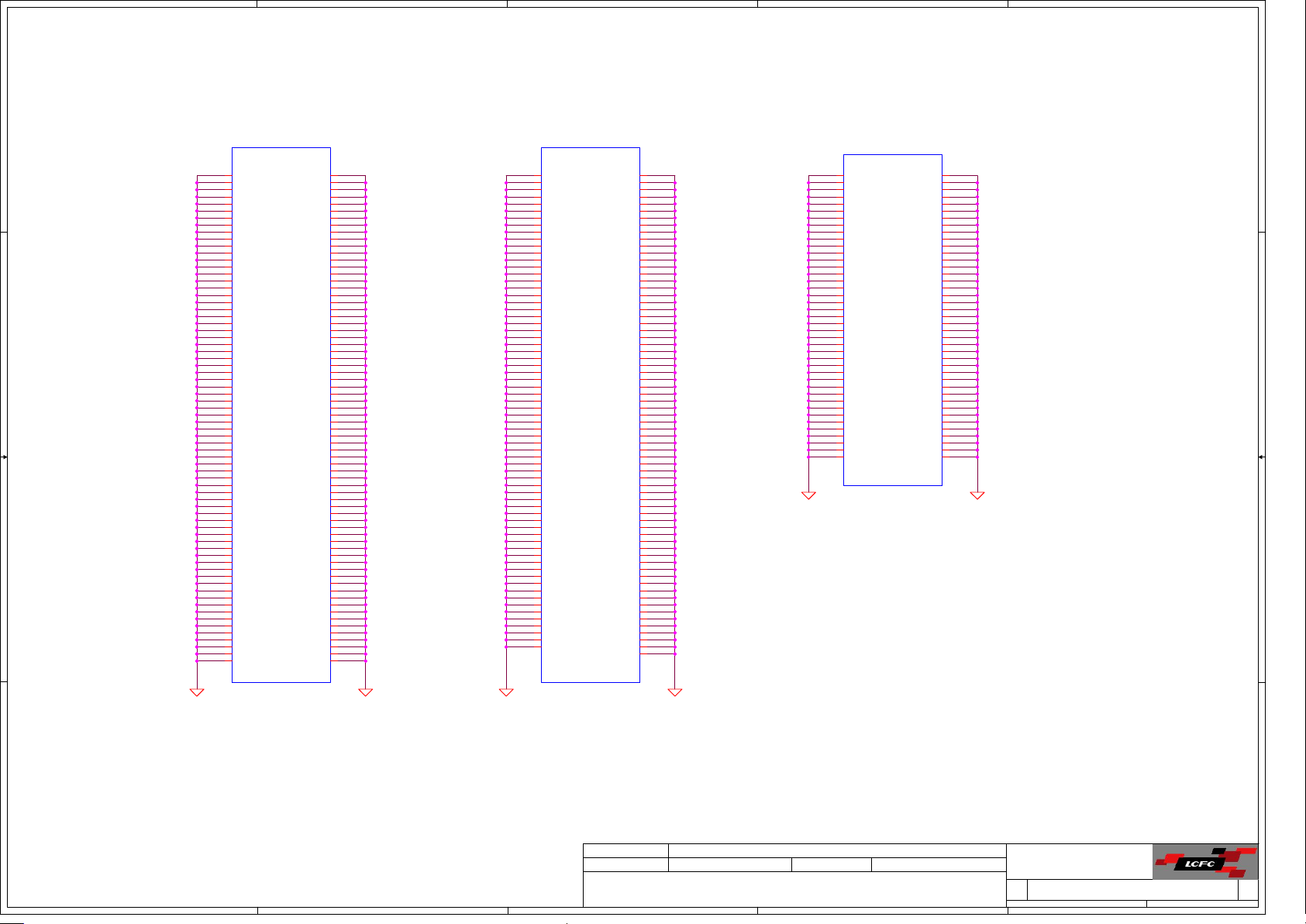

5

D D

4

3

2

1

UC1I

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

C C

D33

A31

B31

A33

B33

A29

B29

C28

D28

A27

B27

C27

D27

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

SKYLAKE-U_BGA1356

B B

SKL_ULT

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

9 OF 20REV = 1

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

R33

1 2

200_0402_1%

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

3

2016/01/12

2016/01/12

2016/01/12

Title

KBL_CS12/ EMMC

KBL_CS12/ EMMC

KBL_CS12/ EMMC

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

A4

A4

A4

Friday, November 04, 2016

Friday, November 04, 2016

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

Friday, November 04, 2016

DL470_NM-B021

DL470_NM-B021

DL470_NM-B021

13 99

13 99

13 99

1

0.2

0.2

0.2

5

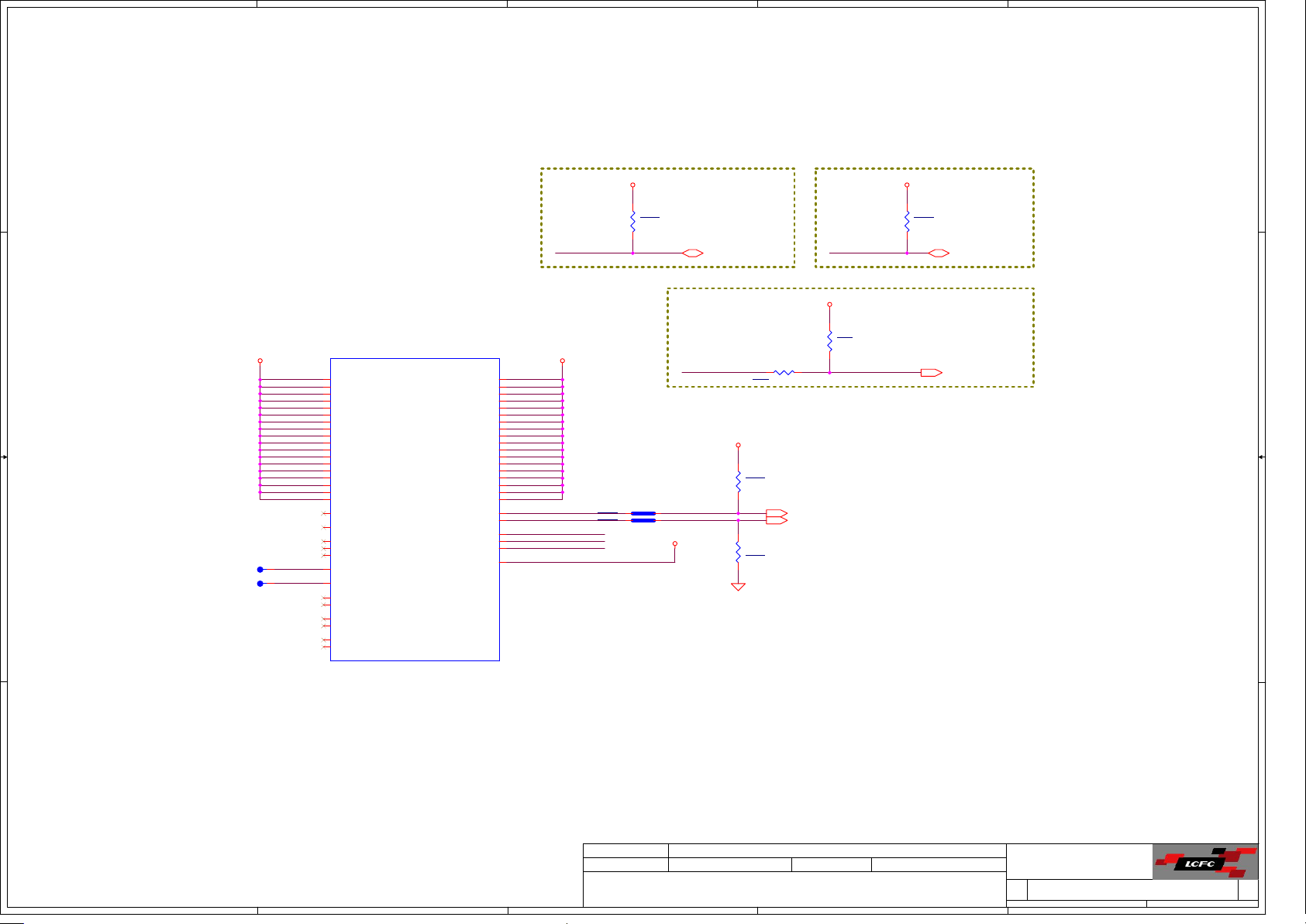

D D

RTC External Circuit

+RTCBATT

+RTCBATT, +RTCVCC

Trace width = 20mils

1 2

RC14 0_0402_SM

+RTCVCC

1

2

CC4

0.1U_0402_10V6-K

near CC59 for layout

+RTCVCC

4

RC15

1 2

20K_0402_5%

RC17

1 2

20K_0402_5%

PCH_RTCRST#

PCH_SRTCRST#

1 2

1 2

CC3 1U_0402_10V6-K

1 2

1 2

CC7 1U_0402_10V6-K

JCMOS1 @

JME1 @

3

2

1

RTC CrystalJCMOS, JME Set t i ng, Need Under DDR Door

PCH_XTAL24_IN

PCH_XTAL24_OUT

10P_0402_50V8-J

CC10

1

2

RC24

1 2

1M_0402_5%

YC2

1

1

GND1

GND2

2

24MHZ_10PF_8Y24000011

3

3

1

4

CC11

10P_0402_50V8-J

2

1 2

10M_0402_5%

YC1

1 2

32.768KHZ_9PF_9H03280012

1

CC5

5.6P_0402_50V8-D

2

RC16

PCH_RTCX1

PCH_RTCX2

1. Space > 15mils

2. No trace under crystal

3. Place on oppsosit side of

MCP for temp influence

1

CC6

5.6P_0402_50V8-D

2

UC1J

C C

HDD

M.2 SSD

WLAN

LAN

VGA

CR

B B

+3VS

CLK_PCIE_HDD#[42]

CLK_PCIE_HDD[42]

CLKREQ_PCIE0_HDD#[42]

CLK_PCIE_SSD#[66]

CLK_PCIE_SSD[66]

CLKREQ_PCIE1_SSD#[66]

CLK_PCIE_WLAN#[66]

CLK_PCIE_WLAN[66]

CLKREQ_PCIE2_WLAN#[66]

CLK_PCIE_LAN#[60]

CLK_PCIE_LAN[60]

CLKREQ_PCIE3_LAN#[60]

CLK_PCIE_VGA#[35]

CLK_PCIE_VGA[35]

CLKREQ_PCIE4_VGA#[30]

CLK_PCIE_CR#[71]

CLK_PCIE_CR[71]

CLKREQ_PCIE5_CR#[71]

UMA@

1 2

RC45 10K_0402_5%

DIS@

1 2

RC39 10K_0402_5%

CLK_PCIE_HDD#

CLK_PCIE_HDD

CLKREQ_PCIE0_HDD#

CLK_PCIE_SSD#

CLK_PCIE_SSD

CLKREQ_PCIE1_SSD#

CLK_PCIE_WLAN#

CLK_PCIE_WLAN

CLKREQ_PCIE2_WLAN#

CLK_PCIE_LAN#

CLK_PCIE_LAN

CLKREQ_PCIE3_LAN#

CLK_PCIE_VGA#

CLK_PCIE_VGA

CLKREQ_PCIE4_VGA#

CLK_PCIE_CR#

CLK_PCIE_CR

CLKREQ_PCIE5_CR#

CLKREQ_PCIE4_VGA#

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

SKYLAKE-U_BGA1356

+3VS

SKL_ULT

CLOCK SIGNALS

RPC24

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

10 OF 20REV = 1

CLKREQ_PCIE2_WLAN#

CLKREQ_PCIE3_LAN#

CLKREQ_PCIE1_SSD#

CLKREQ_PCIE5_CR#

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

CLKOUT_ITPXDP_N

F43

CLKOUT_ITPXDP_P

E43

SUSCLK_32K

BA17

PCH_XTAL24_IN

E37

PCH_XTAL24_OUT

E35

XCLK_BIASREF

E42

PCH_RTCX1

AM18

PCH_RTCX2

AM20

PCH_SRTCRST#

AN18

PCH_RTCRST#

AM16

+3VS

1 2

RC513 10K_0402_5%

1

1

1 2

T56

T57

R92

2.71K_0402_0.5%

SD00001LB1T

CLKREQ_PCIE0_HDD#

+1VALW

SUSCLK_32K [66]

to WLAN

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/01/12

2015/01/12

2015/01/12

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/01/12

2016/01/12

2016/01/12

Title

KBL_RTC/ CLK

KBL_RTC/ CLK

KBL_RTC/ CLK

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Friday, November 04, 2016

Friday, November 04, 2016

Date: Sheet of

Date: Sheet of

Date: Sheet of

Friday, November 04, 2016

DL470_NM-B021

DL470_NM-B021

DL470_NM-B021

1

14 99

14 99

14 99

0.2

0.2

0.2

5

D D

4

3

2

1

+3VALW

12

R1501

4.7K_0402_5%

VCCST_PWRGD

1 2

PCH_PWROK[77]

C C

B B

VGATE[77,93]

GPU_WAKE#[30]

PCH_LAN_WAKE#[60]

For vPRO LAN WAKE#

+3VALW

+3VALW

RC40 0_0402_SM

1 2

RC383 0_0402_5%@

1 2

RC64 0_0402_5%@

1 2

RC76 0_0402_SM

RPC9

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

SD300002P0T

RC74 10K_0402_5%

RC379 10K_0402_5%@

RC380 10K_0402_5%@

RC387 10K_0402_5%@

1 2

1 2

1 2

1 2

AC_PRESENT

BATLOW#

PCIE_WAKE#

For vPRO LAN WAKE#

EC_WAKE#_DSW

PM_SLP_S5#

PCH_SLP_WLAN#

PCH_SLP_LAN#

EC_RSMRST#

+3VS

RC47 10K_0402_5%@

+3VALW_PRIM

RC398 10K_0402_5%

RC53 10K_0402_5%

RC5 10K_0402_5%

PCH_PLT_RST#[10]

EC_RSMRST#[77]

1 2

R281 60.4_0402_1%

PCH_SYSPWROK[77]

1 2

RC382 0_0402_SM

1 2

RC55 0_0402_SM

PCIE_WAKE#[66]

LANPHYPC[60]

1 2

1 2

1 2

1 2

@

PCH_PLT_RST#

SYS_RESET#

EC_RSMRST#

H_CPUPWRGD

PCH_SYSPWROK

PWROK

DSW_PWROK

SUSWARN#

SUSACK#

PCIE_WAKE#

EC_WAKE#_DSW

LANPHYPC

SYS_RESET#

EC_RSMRST#

H_CPUPWRGDH_CPUPWRGD

UC1K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13