Lenovo ThinkPad A275 Schematic

5

Vinafix.com

WV4 AMD Schemat i c

4

3

2

1

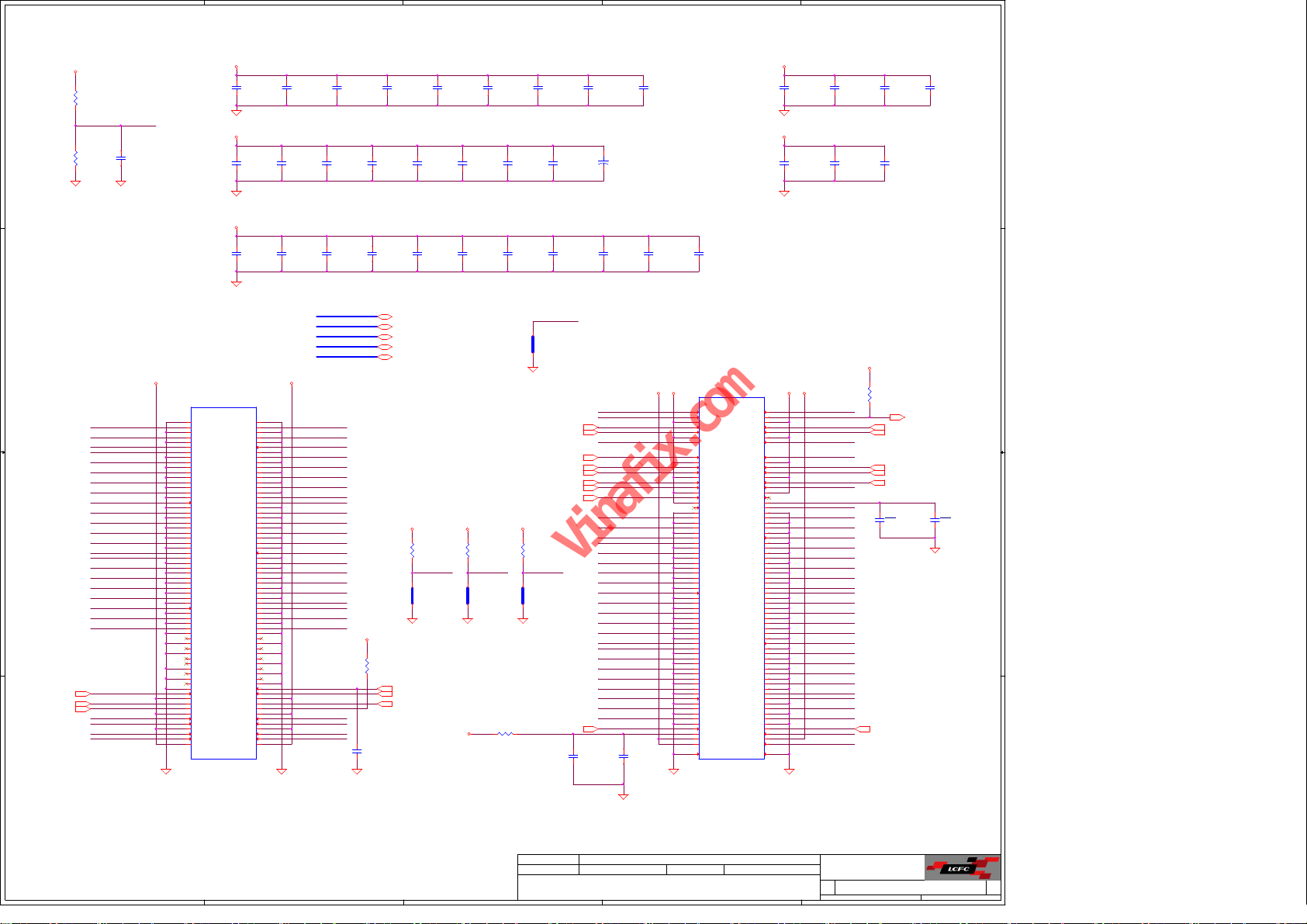

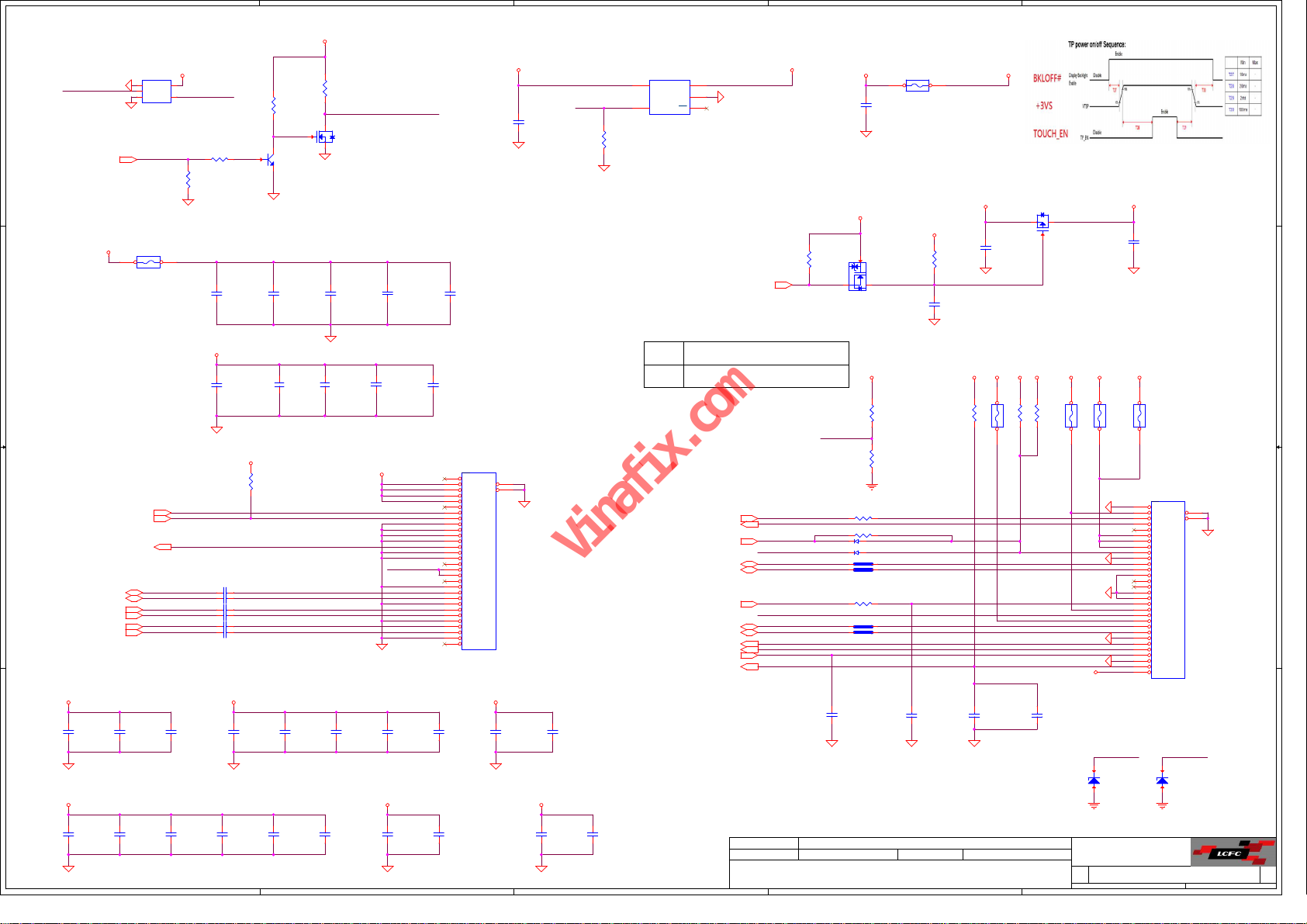

P01_TITLE PAGE

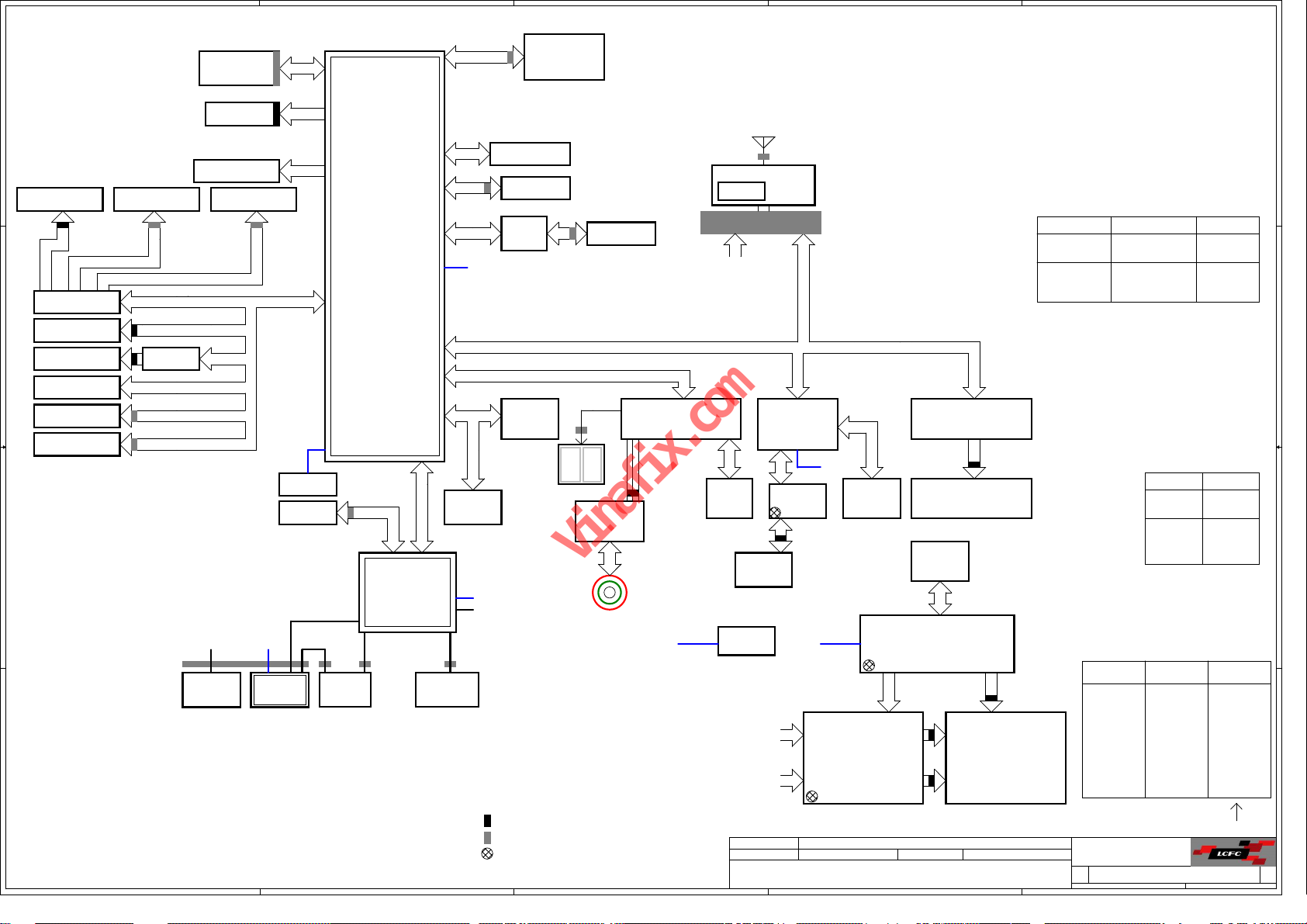

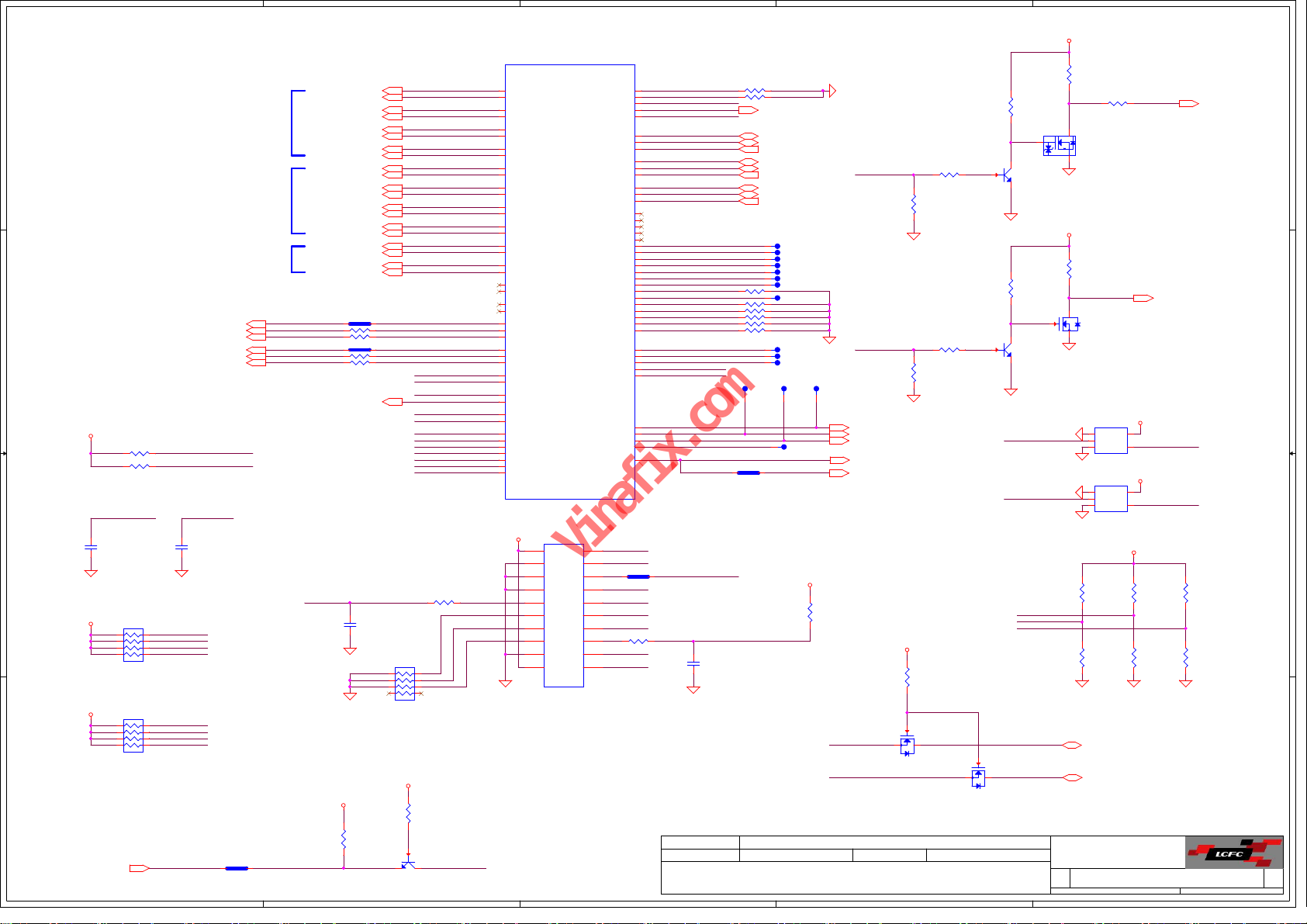

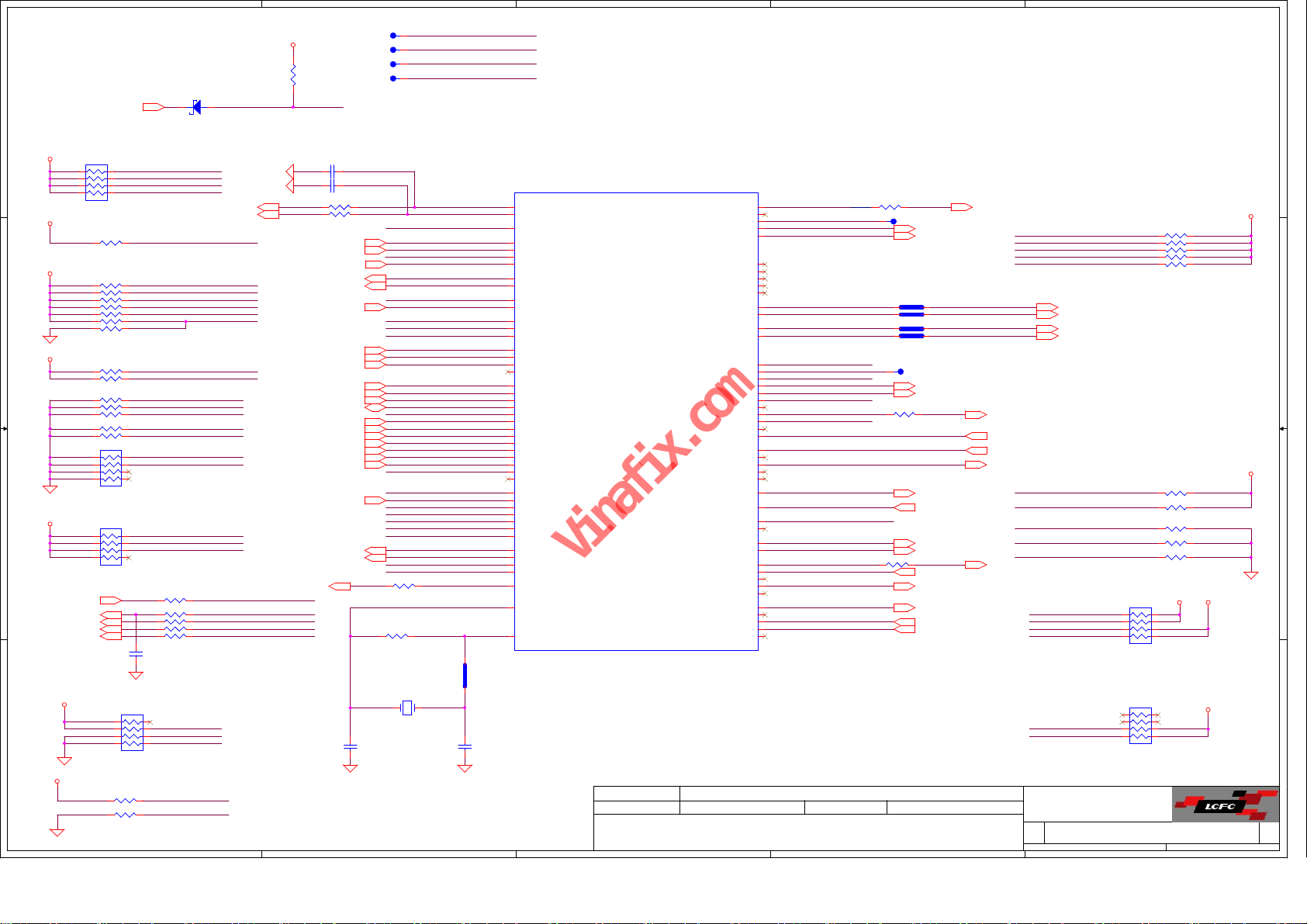

P02_BLOCK DIAGRAM

D D

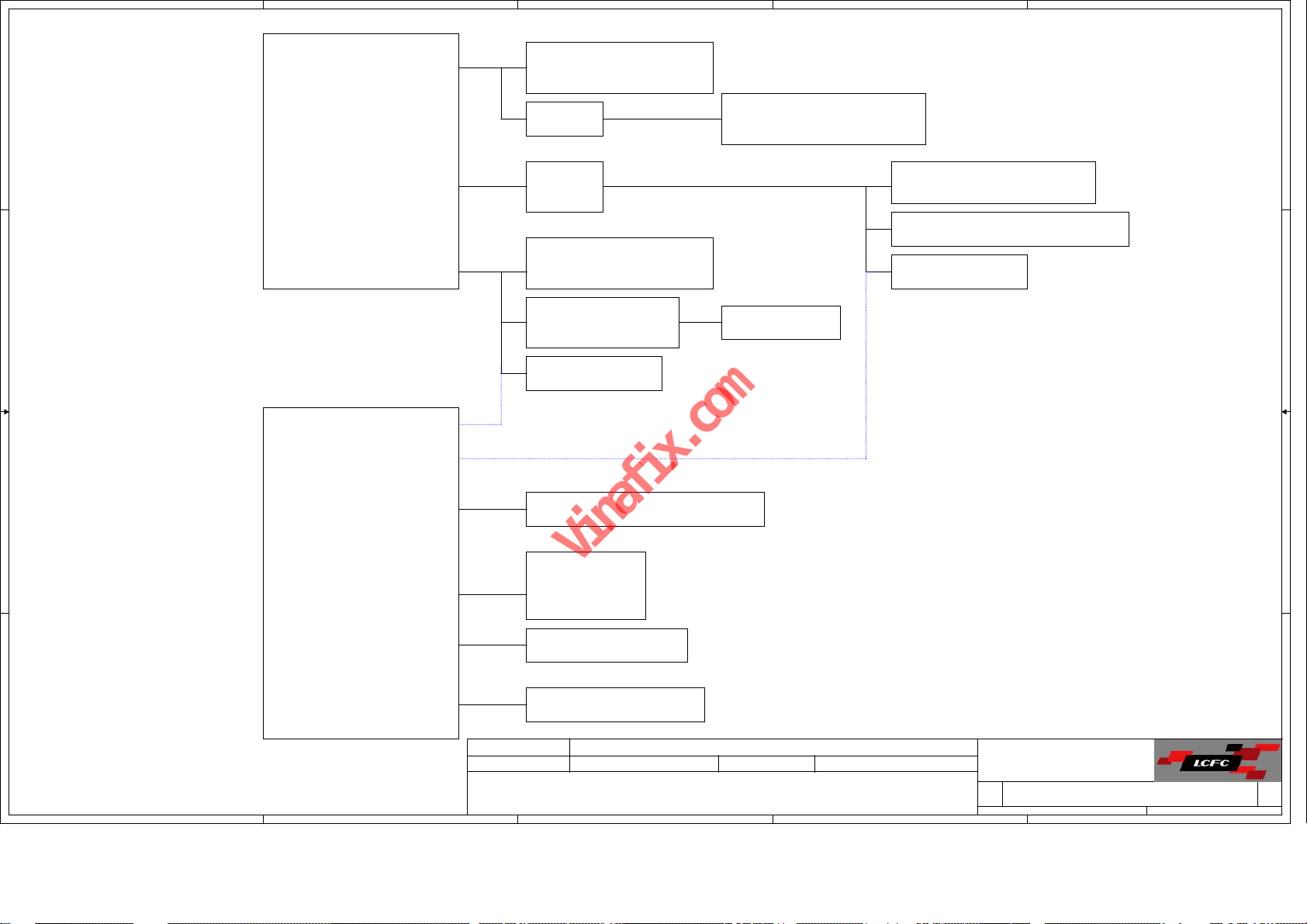

P03_BLANK

P04_SMBus Block

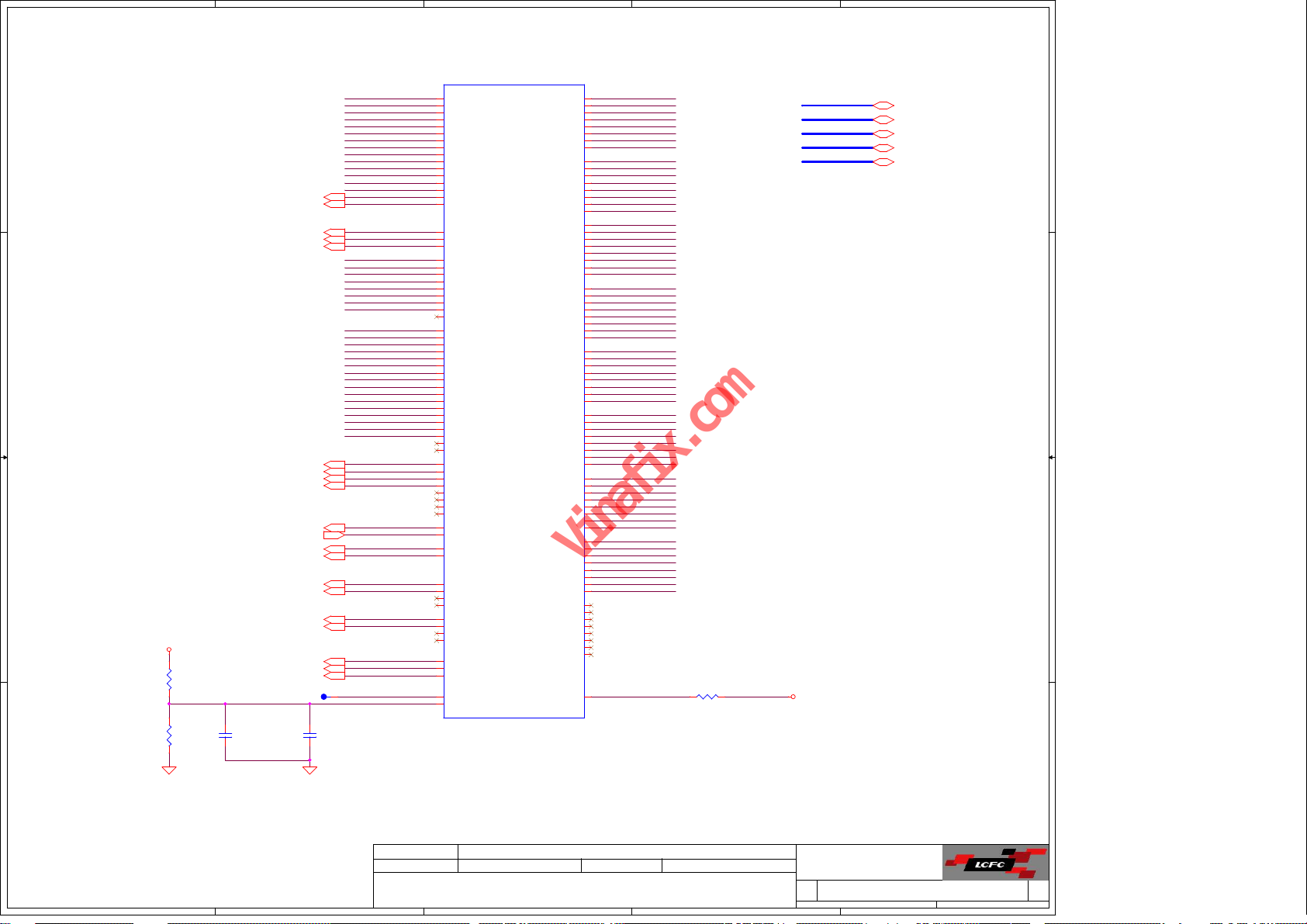

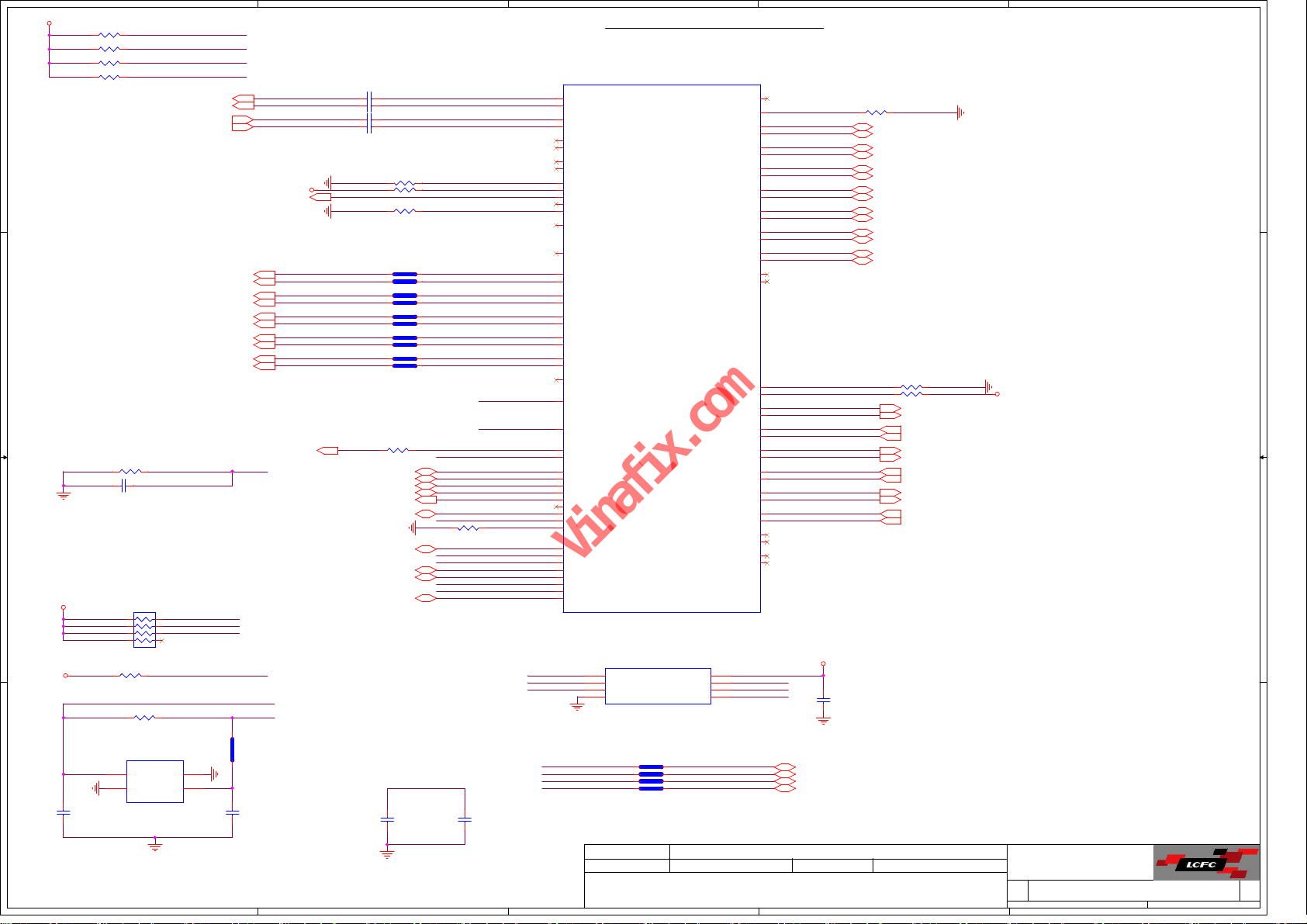

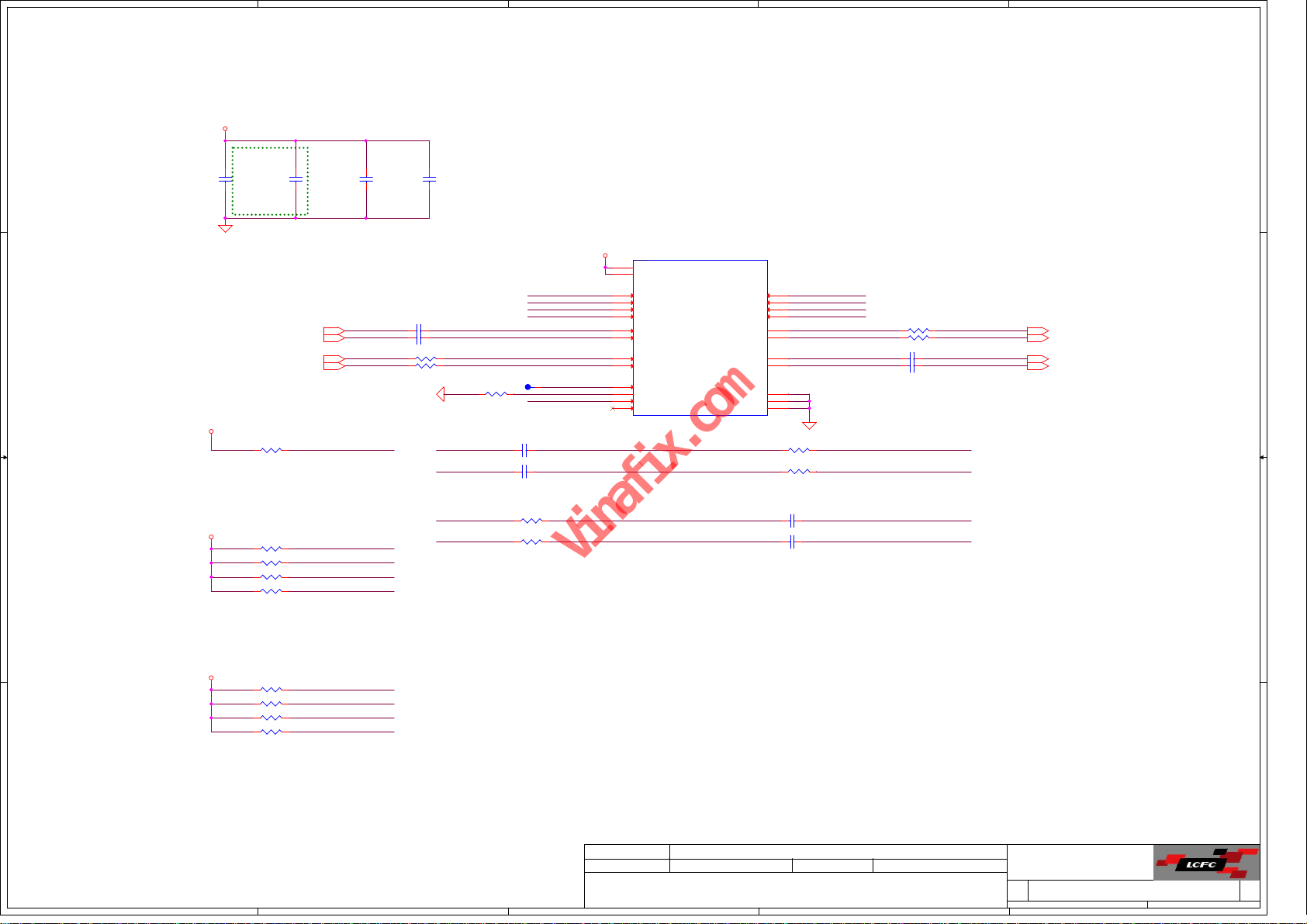

P05_APU PEG/PCIe

P06_APU DDRA/1

P07_APU DDRB/2

P08_APU DISPLAY/CLK/MISC 2

P09_APU SATA/USB/LPC/SPI

P10_APU GPIO/AZ/I2C/UARTS/ACPI

P11_APU Power

P12_APU GND

C C

P13_Switch

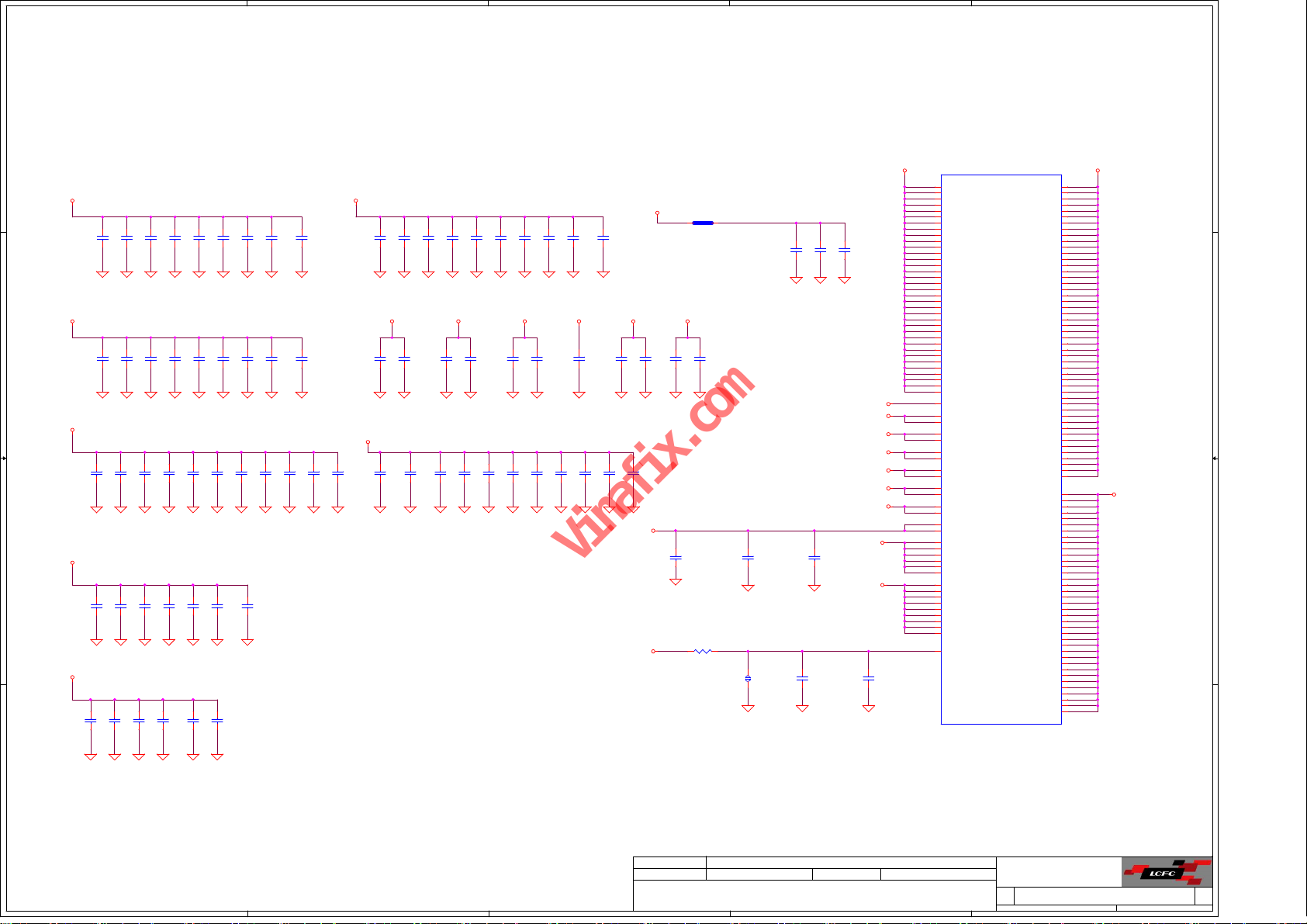

P14_DDR4 CH-A PRIMARY

P15_BLANK

P16_USB 2.0 HUB GL850G

P17_BLANK

P18_BLANK

P19_LCD/LID/MIC/CAMERA/PWR SW

P20_PCIE_SATA SWITCH

P21_HDMI Bypass

B B

P22_HDMI CONNECTOR

P23_SATA REDRIVER

P24_SATA EXPRESS CONNECTOR

P25_USB3.0 REDRIVER

P26_USB AOU POWER/CONNECTOR

P27_PCIE RE-DRIVER

P28_USB POWER/CONNECTOR

P29_GLAN-RTL8111EPV

P30_BLANK

P31_GBE MAGNETICS

A A

P32_RJ45 CONNECTOR

P33_TYPE C PD Controller

P34_TYPE-C_MUX

P35_M.2 SOCKET 1 WLAN

5

P36_M.2 SOCKET 2 WWAN

P37_CARD READER RTS5232S-GR

P38_Card Reader Connector

P39_AUDIO ALC3268

P40_AUDIO CONNECTOR

P41_AUDIO JACK SENSE

P42_AUDIO EXT MIC I/F

P43_AUDIO SPEAKER

P44_AUDIO BEEP

P45_BLANK

P46_KEYBOARD/TRACK POINT

P47_TOUCH PAD/FPR/Smart Card

P48_FAN CONNECTOR

P49_G-SENSOR

P50_TPM

P51_DEVICE_DETECT# TABLE

P52_EC_IT8186E/FX

P53_PTH FOR SCREW HOLES

P54_THERMAL SENSOR

P55_3VS/5VS/VDDP/1.8VS

P56_VDDCR_FCH_ALW/RTC/0.775VA

P57_+1.5VS

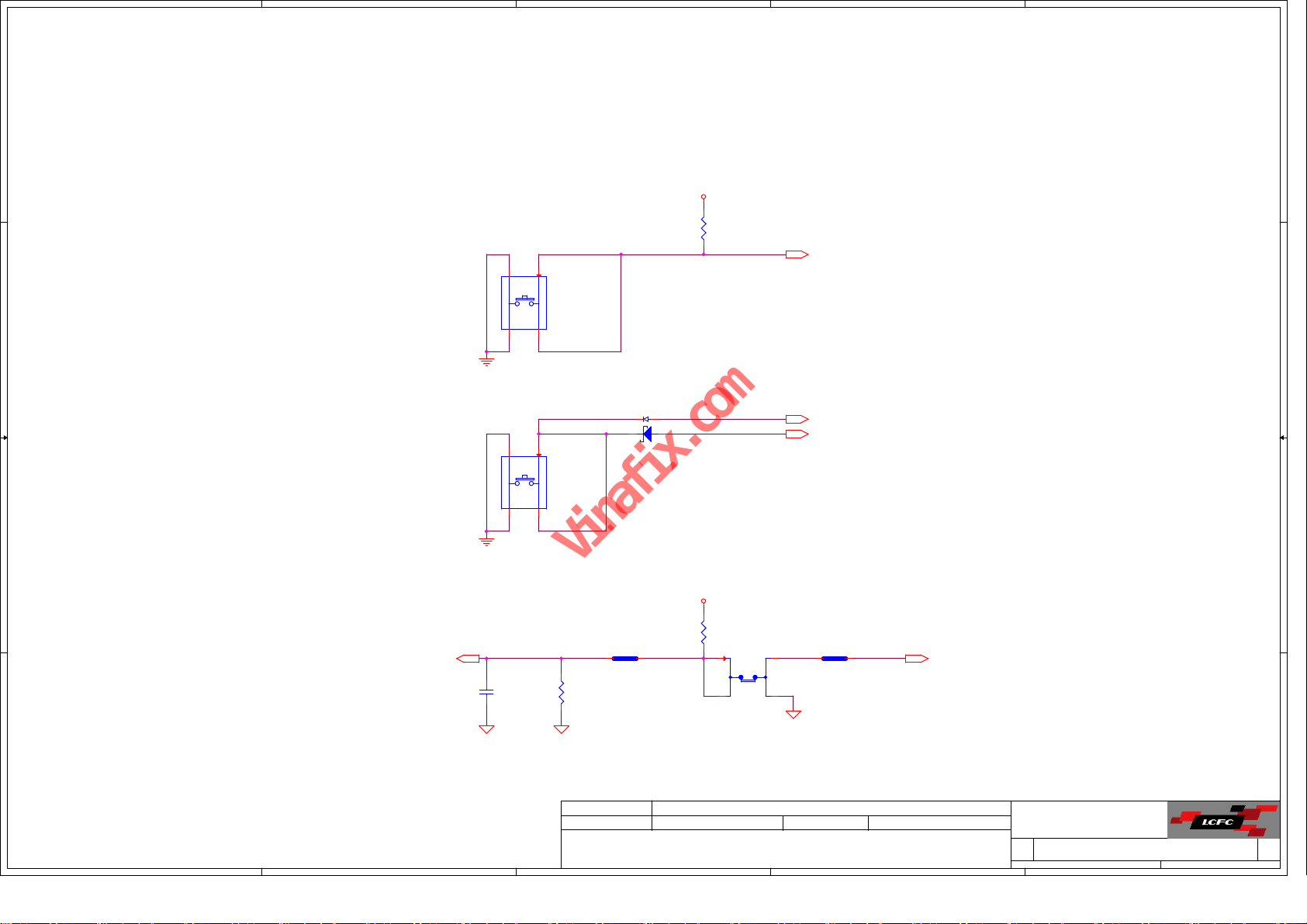

P69_OTP

P70_DC-IN

P71_TYP-C

P72_BATTERY INPUT

P73_BATTERY CHARGER(BQ25700)

P74_CHARGER SELECTOR

P75_DC/DC VCC5M/VCC3M(NB679/680

P76_DC/DC VCC1R2A(NB685A)

P77_VDD/VDDNB (ISL62771)

P78_VDD_GFX(ISL62771)

P79_SDLE DECOUPLING

P80_VDDCORE DECOUPLING

P81_+1.05VALW(NB693)

4

3

P82_+2.5V(RT8068A)

P83_+1.8VALW(RT8068A)

P84_RTC BATTERY

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2016/09/29

2016/09/29

2016/09/29

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2015/8/10

2015/8/10

2015/8/10

Title

Title

Title

TITLE PAGE

TITLE PAGE

TITLE PAGE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

Tuesday, May 09, 2017

Tuesday, May 09, 2017

Tuesday, May 09, 2017

1

1 84

1 84

1 84

SIT

SIT

SIT

5

Vinafix.com

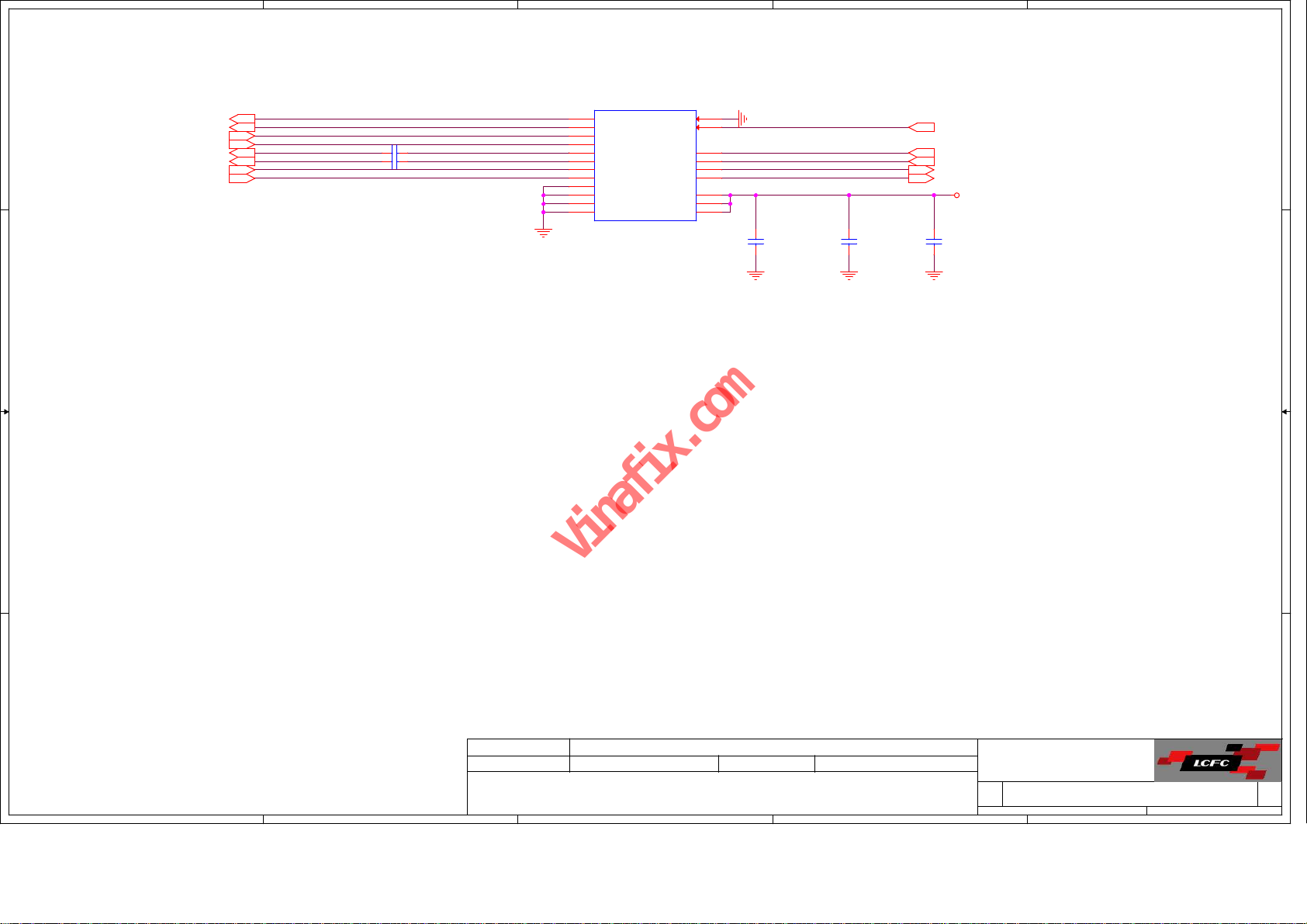

LCD CONN

eDP 14"

HD/FHD

eDPx2

23

APU

4

DDR4 / 1.2V

SM Bus

DDR4

SO-DIMMA

14

Channel A

DDR4

3

2

1

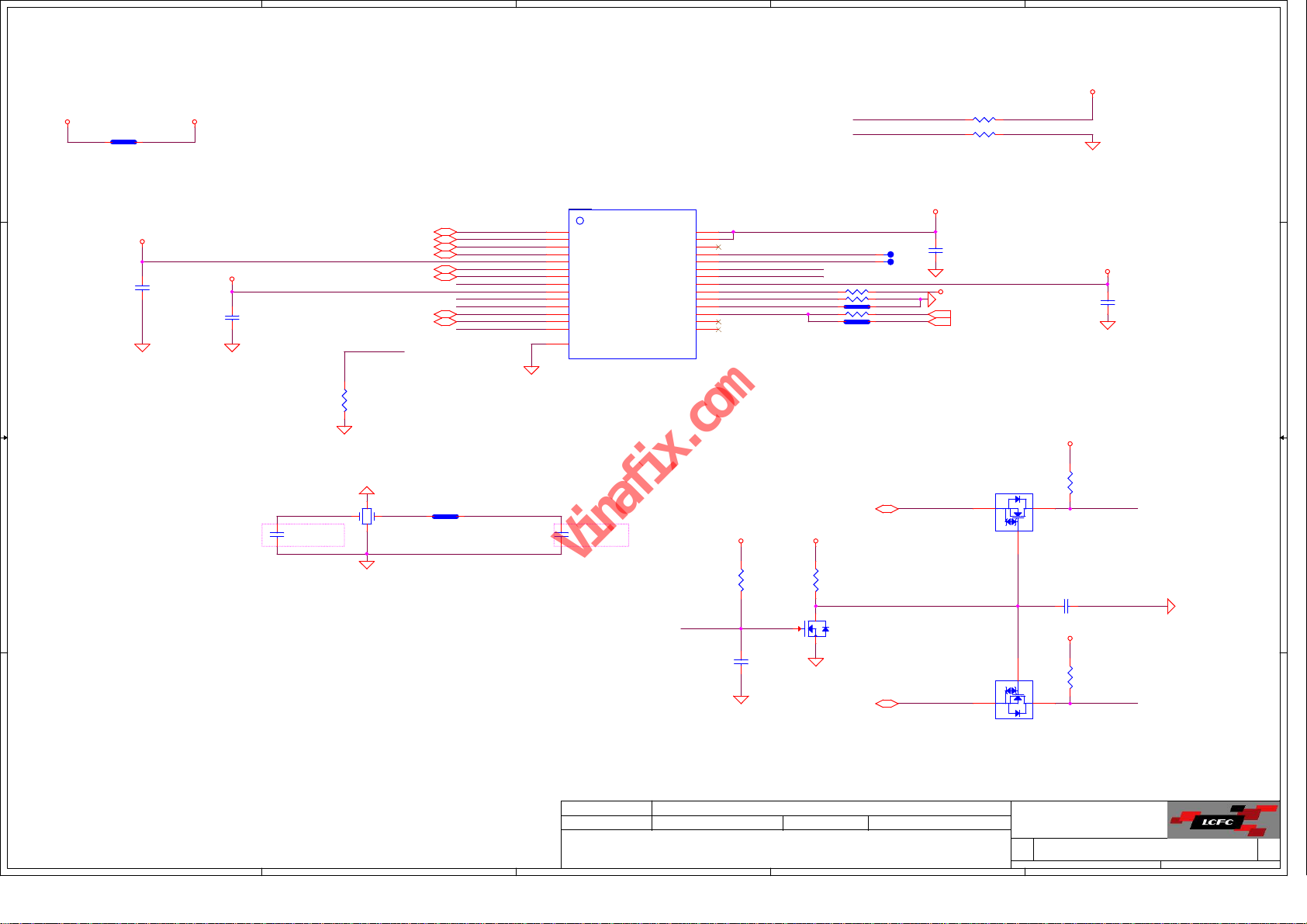

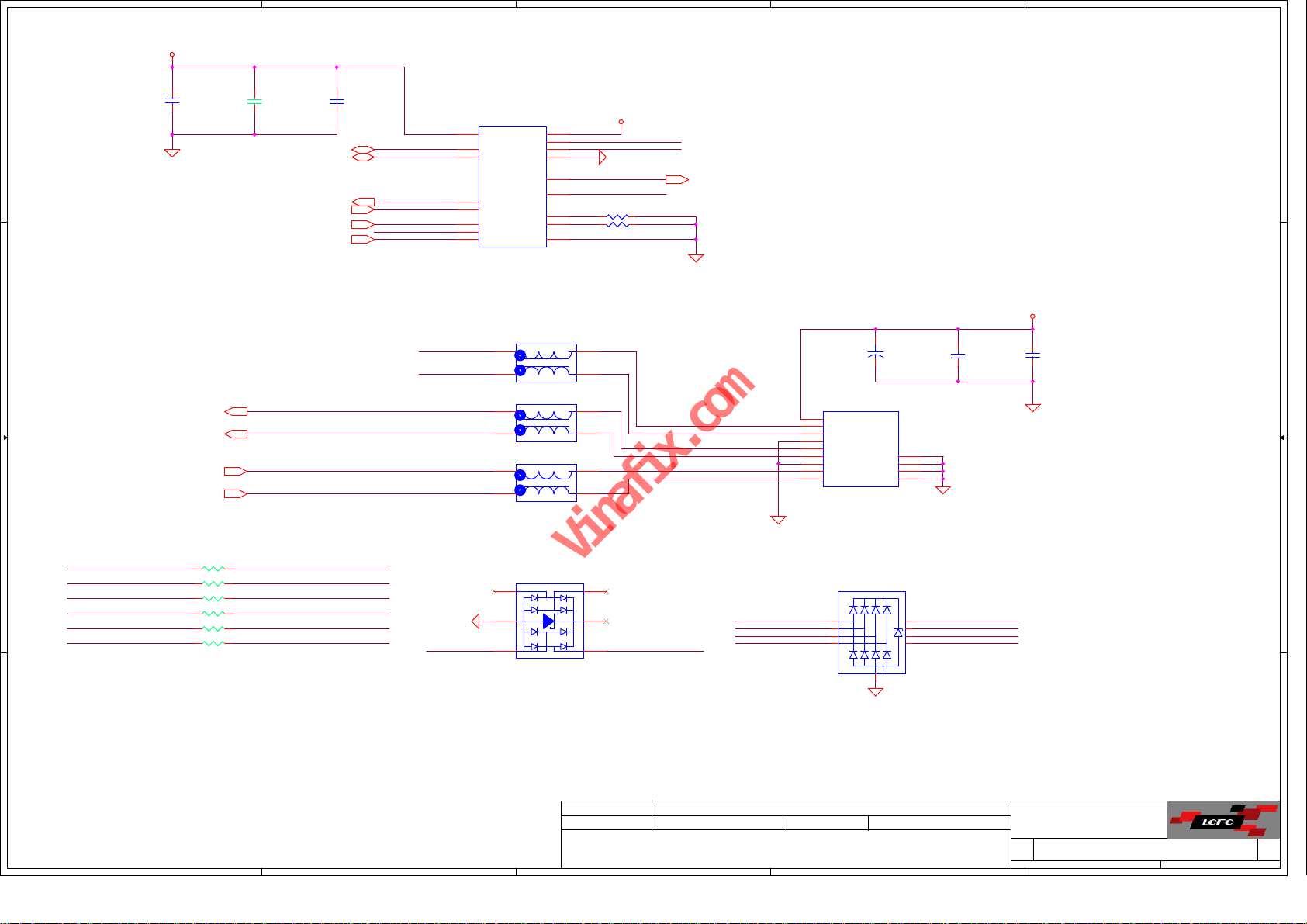

Windu Block Diagram

Project Code:

AMD

Bristol Ridge FP4

Platform

BGA968

5,6,7,8,9,10,11,12

49

Embedded

Controller

IT8186VG

Keyboard

4647

4

SATA Port

TPM

SLB9670VQ2.0

52

Power Button

HDT

(For AMD Debug)

RTC Battery

Re-Driver

PS8527C

24

SM Bus

PCI Express x8

HDA

SPI Flash

64Mbits

W25Q64FWSSIQ

50

SM Bus

LED for ThinkPad Logos

23

External Connector/Socket

Internal Connector/Socket

Internal Switch

9

8

54

Stereo

Speaker

HDD CONN

SSD

43

Microphone

Headphone

40,41,42

40

Audio

Combo Jack

24

ALC3268-CG

HDA CODEC

3

Type-A M.2 Card

USB 2.0

HUB Port 2

Internal

Mic

SM Bus

Antenna

(M.2 WLAN Card)

Bluetooth

39

23

MAGNETICS

RJ45

Thermal

Sensor

F75303M

GLAN

RealTek

RTL8111EPV-CG

31,32

51

33

LAN

SWITCH

PI3L720ZHE+CX

Por t 2

(X1)

Por t 0

(X1)

30

29

SM Bus

SM Bus

SPI Flash

8Mbits

W25X80AVSNIG

29

MUX & PD

TPS65982DAZQZR

RTS5232S-GR

Card Reader

Card Reader

CONN

SPI Flash

8Mbits

W25Q80BLSNIG

Por t 1

(X1)

17

17

Power Control

USB Type-C

USB3.0

USB2.0

Switch MUX

PS8743BQFN40GTR-B0

T y p e - C

CONN

USB DP

18

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FRO M THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FRO M THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FRO M THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED B Y LC F UTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED B Y LC F UTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED B Y LC F UTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2015/11/02

2015/11/02

2015/11/02

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2015/8/10

2015/8/10

2015/8/10

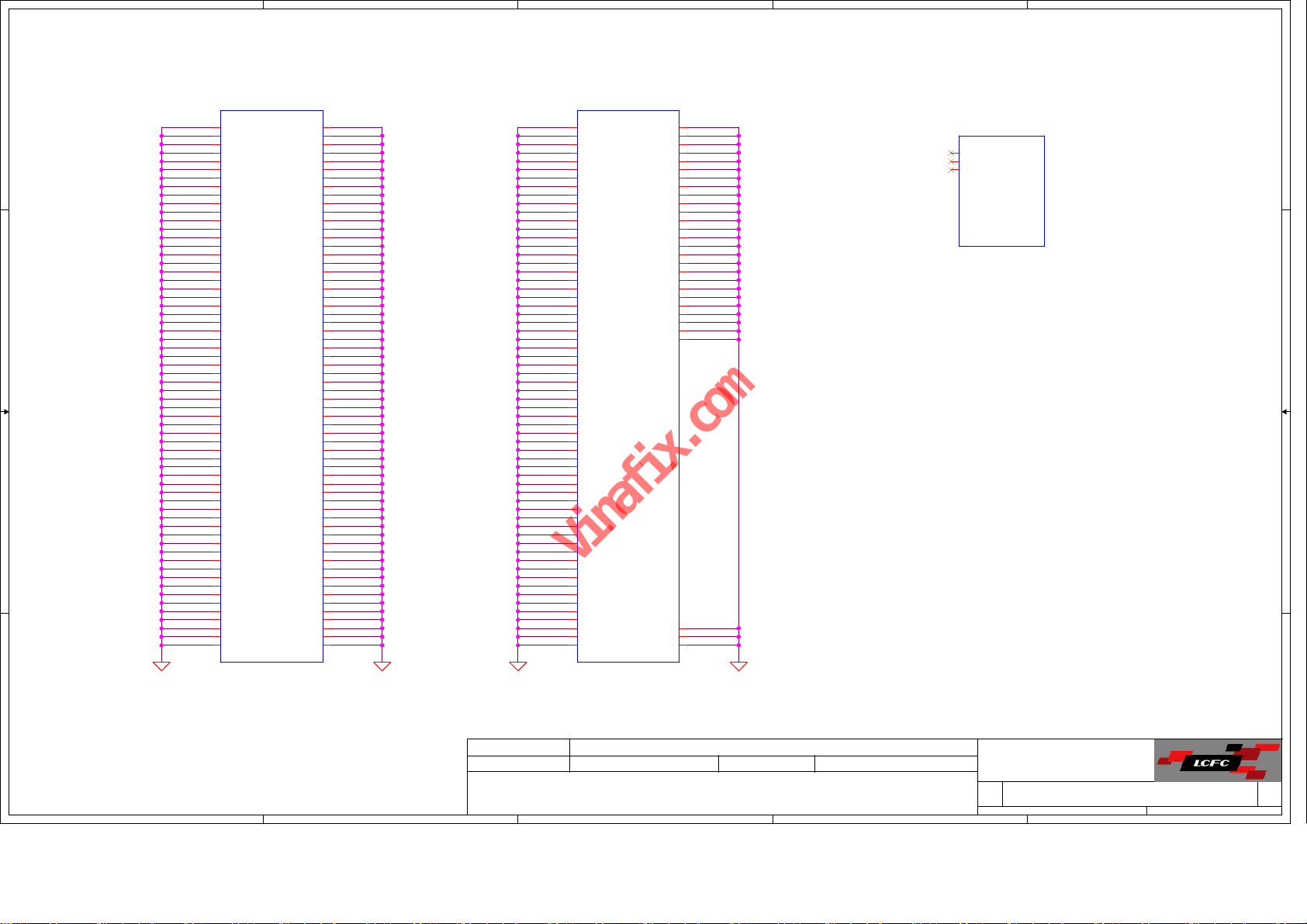

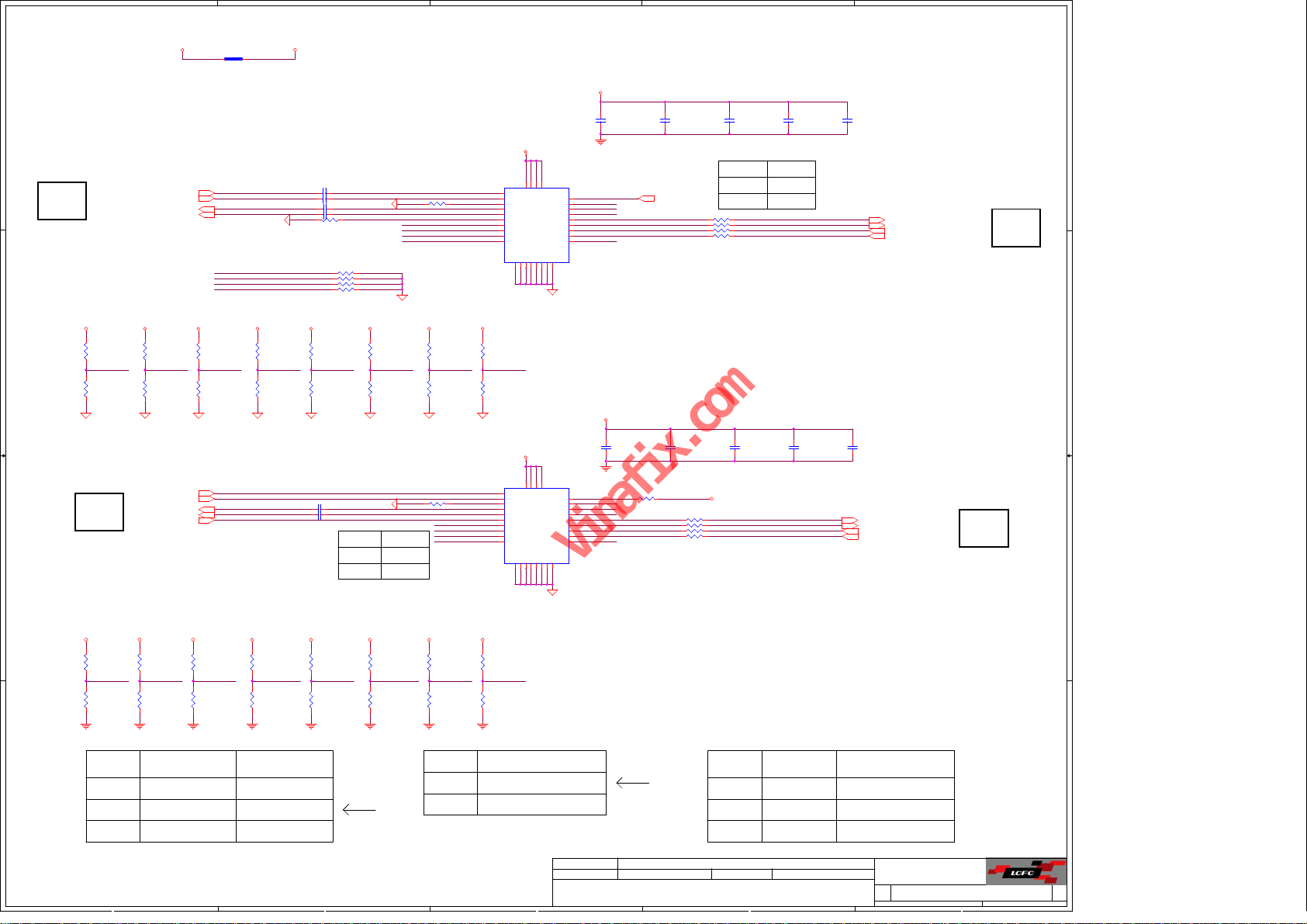

TABLE: Chip Capacitor Thermal Characteristics

35

36

-55 to 150degC

-55 to 125degC

-55 to 125degC

-55 to 105degC

-55 to 85degC

18

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

+/-30ppm/degC

+/-30ppm/degC

+/-15%

+/-22%

+/-15%

TABLE: Chip Part Dimension

Size [mm]

0.40 x 0.20

0.60 x 0.30

1.00 x 0.50

1.60 x 0.80

2.00 x 1.25

2.00 x 1.60

2.50 x 2.00

3.20 x 1.60

3.20 x 2.50

4.50 x 1.60

4.50 x 2.50

4.50 x 3.20

5.00 x 2.50

6.40 x 3.20

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

C

Tuesday, May 09, 2017

Tuesday, May 09, 2017

Tuesday, May 09, 2017

Code

NPO

C0G

X7R

X6S

X5R

TABLE: Chip Capacitor Tolerance

T o l e r a n c e

+/-0.25pF

+/-0.5pF

+/-5%

+/-10%

+/-20%

+80/-20%

mm Size Code Inch Size Code

0402

0603

1005

1608

2125

2016

2520

3216

3225

4516

4525

4532

5025

6432

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

1

Code

C

D

J

K

M

Z

01005

0201

0402

0603

0805

0806

1008

1206

1210

1806

1810

1812

2010

2512

LOGIC

2 84

2 84

2 84

SIT

SIT

SIT

USB2.0 CH1

25

HDMI Conn

DP

Type-C

USB2.0

Fingerprint

33

USB3.0 CH1

USB2.0 CH5

USB2.0

HUB Port 1

Fingerprint

Reader

47

D D

USB2.0

Smart Cart

USB2.0 CH3

USB2.0

HUB

GL850G

USB3.0

CONN (USB1)

C C

USB3.0

AOU (USB2)

USB

Type-C

USB2.0

2D Camera

USB2.0

Touch Panel

B B

47

USB2.0 CH2

16

28

26,27

17,18

23

23

USB2.0

M.2 WLAN Slot (BT)

USB2.0 CH3

USB3.0 CH3

USB2.0 CH7

USB

Redriver

PS8713BTQFN24GTR2A

USB3.0 CH2

USB2.0 CH6

USB2.0 CH3

USB2.0 CH0

25

17,18

SM Bus

ClickPad

DDI x4

DDI x4

47

USB 2.0 x8 Port

USB 3.0 x4 Port

G-Sensor

BMA255_LGA12

FAN

SM Bus

48

A A

Device Address

Thermal Sensor F75303M 1001_101xb

G Sensor BMA255 30h (W) & 31h (R)

DDR DIMM0 (JDIMM1)

CH-A

CH-B

DDR DIMM1 (JDIMM2)

32h (W) & 33h (R)

0H

2H

5

ADDR_SEL

H

L

5

Vinafix.com

D D

C C

4

3

2

1

BLANK

B B

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2016/09/29

2016/09/29

2016/09/29

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2015/08/10

2015/08/10

2015/08/10

Title

BLANK

BLANK

BLANK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, May 09, 2017

Tuesday, May 09, 2017

Date: Sheet of

Date: Sheet of

Date: Sheet of

Tuesday, May 09, 2017

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

1

3 84

3 84

3 84

SITCustom

SITCustom

SITCustom

5

Vinafix.com

4

3

2

1

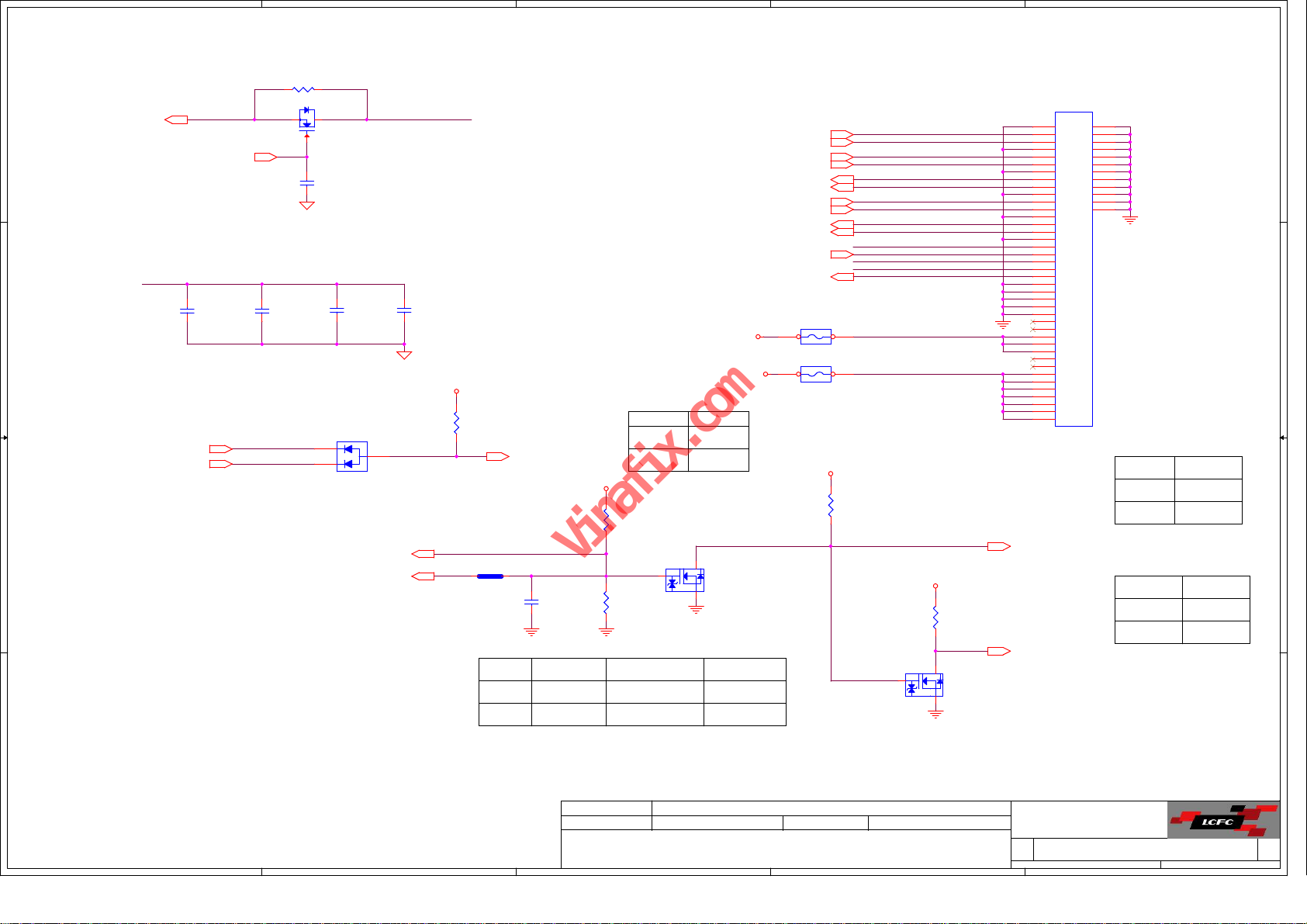

SMBus 0

D D

DDR4 SO-DIMM*2

MOSFET USB HUB GL852G-50

APU

SIC / SID

SMBus 1

C C

SMBus 3

SMBus 0

B B

SMBus 2

MOSFET

LAN - RTL8111EPV

SMBus Switch Click Pad

EC - IT8186

TYPE-C PD - TPS65982

G SENSOR - BMA255

Thermal IC - F75303M

EC - IT8186

EC

IT8186

SMBus 1

SMBus 5

A A

5

SMBus 4

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

CHARGER

BQ25700

MAIN Battery

Second Battery

2015/10/5

2015/10/5

2015/10/5

3

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2014/12/05

2014/12/05

2014/12/05

Title

Title

Title

SMBus Block

SMBus Block

SMBus Block

Size

Size

Size

Document Num ber Rev

Document Num ber Rev

Document Num ber Rev

B

B

B

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

Tuesday, May 09, 2017

Tuesday, May 09, 2017

Tuesday, May 09, 2017

1

4 84

4 84

4 84

SIT

SIT

SIT

5

Vinafix.com

4

3

2

1

PCIe Port Assignment

0

GbE PHY

1

Card Reader

2

D D

LAN

CardReader

C C

WLAN

WWAN WWAN

+1.05VS_VDDP

3

M.2 WLAN Slot

M.2 WWAN Slot

UC1B

PC IE

PCIE0_CRX_DTX_P29

PCIE0_CRX_DTX_N29

PCIE1_CRX_DTX_P37

PCIE1_CRX_DTX_N37

PCIE2_CRX_DTX_P35

PCIE2_CRX_DTX_N35

PCIE3_CRX_DTX_N27 PCIE3_CTX_DRX_N_C 27

1 2

RC1 196_0201_1%

PCIE0_CRX_DTX_P

PCIE0_CRX_DTX_N

PCIE1_CRX_DTX_P

PCIE1_CRX_DTX_N

PCIE2_CRX_DTX_P

PCIE2_CRX_DTX_N

PCIE3_CRX_DTX_P

PCIE3_CRX_DTX_N PCIE3_CTX_DRX_N PCIE3_CTX_DRX_N_C

U10

U9

T6

T5

T9

T8

P7

P6

U7

P_GPP_RXP0

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_ZVDDP

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_ZVSS/P_RX_ZVDDP

PCIE0_CTX_DRX_P

R1

PCIE0_CTX_DRX_N

R2

PCIE1_CTX_DRX_P

R4

PCIE1_CTX_DRX_N

R3

PCIE2_CTX_DRX_P

N1

PCIE2_CTX_DRX_N

N2

N4

N3

P_ZVSSP_ZVDDP

U6

1 2

CC212 0.1U_0201_16V6-K

1 2

CC213 0.1U_0201_16V6-K

1 2

CC3 0.1U_0201_16V6-K

1 2

CC4 0.1U_0201_16V6-K

1 2

CC5 0.1U_0201_16V6-K

1 2

CC6 0.1U_0201_16V6-K

1 2

CC218 0.1U_0201_16V6-K

1 2

CC219 0.1U_0201_16V6-K

1 2

RC2 196_0201_1%

PCIE0_CTX_DRX_P_C

PCIE0_CTX_DRX_N_C

PCIE1_CTX_DRX_P_C

PCIE1_CTX_DRX_N_C

PCIE2_CTX_DRX_P_C

PCIE2_CTX_DRX_N_C

PCIE3_CTX_DRX_P_CPCIE3_CTX_DRX_P

PCIE0_CTX_DRX_P_C 29

PCIE0_CTX_DRX_N_C 29

PCIE1_CTX_DRX_P_C 37

PCIE1_CTX_DRX_N_C 37

PCIE2_CTX_DRX_P_C 35

PCIE2_CTX_DRX_N_C 35

PCIE3_CTX_DRX_P_C 27PCIE3_CRX_DTX_P27

LAN

CardReader

WLAN

2

PCIE_CTX_GRX_P0_C

PCIE_CTX_GRX_N0_C

PCIE_CTX_GRX_P1_C

PCIE_CTX_GRX_N1_C

Title

Title

Title

APU PEG/PCIe

APU PEG/PCIe

APU PEG/PCIe

Size

Size

Size

Document Num ber Rev

Document Num ber Rev

Document Num ber Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

PCIE_CTX_GRX_P0_C 20

PCIE_CTX_GRX_N0_C 20

PCIE_CTX_GRX_P1_C 23

PCIE_CTX_GRX_N1_C 23

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

Tuesday, May 09, 2017

Tuesday, May 09, 2017

Tuesday, May 09, 2017

1

5 84

5 84

5 84

SIT

SIT

SIT

PCIE_CRX_GTX_P020

M.2 SSD M.2 SSD

B B

A A

5

PCIE_CRX_GTX_N020

PCIE_CRX_GTX_P123

PCIE_CRX_GTX_N123

PCIE_CRX_GTX_P0

PCIE_CRX_GTX_N0

PCIE_CRX_GTX_P1

PCIE_CRX_GTX_N1

4

P10

P_GFX_RXP0

P9

P_GFX_RXN0

N6

P_GFX_RXP1

N5

P_GFX_RXN1

N9

P_GFX_RXP2

N8

P_GFX_RXN2

L7

P_GFX_RXP3

L6

P_GFX_RXN3

L10

P_GFX_RXP4

L9

P_GFX_RXN4

K6

P_GFX_RXP5

K5

P_GFX_RXN5

K9

P_GFX_RXP6

K

8

P_GFX_RXN6

J7

P_GFX_RXP7

J6

P_GFX_RXN7

FP4 REV 0.93

AMD-BRISTOL_FP4-BGA968

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

2016/09/29

2016/09/29

2016/09/29

3

PCIE_CTX_GRX_P0

M2

PCIE_CTX_GRX_N0

M1

PCIE_CTX_GRX_P1

L1

PCIE_CTX_GRX_N1

L2

L4

L3

J1

J2

J4

J3

H2

H1

G1

G2

G4

G3

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

CC214 0.22U_0201_6.3V6-K

CC215 0.22U_0201_6.3V6-K

CC216 0.22U_0201_6.3V6-K

CC217 0.22U_0201_6.3V6-K

1 2

1 2

1 2

1 2

2014/12/05

2014/12/05

2014/12/05

1

Vinafix.com

2

3

4

5

UC1A

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

A A

DDR_A_BG114

DDR_A_ACT_N14

DDR_A_BA014

DDR_A_BA114

DDR_A_BG014

B B

SA_CLK_DDR014

SA_CLK_DDR#014

SA_CLK_DDR114

SA_CLK_DDR#114

DDR4_A_DRAMRST#14

DDR_A_EVENT#14

DDR_A_CKE014

DDR_A_CKE114

C C

+1.2V

12

RC3

@

1K_0402_1%

12

RC5

@

1K_0402_1%

1

CC7

@

0.1U_0402_10V7-K

2

DDR_A_ODT014

DDR_A_ODT114

DDR_A_CS0#14

DDR_A_CS1#14

DDR_A_RAS#14

DDR_A_CAS#14

DDR_A_WE#14

1

2

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_BG1

DDR_A_ACT_N

DDR_A_BA0

DDR_A_BA1

DDR_A_BG0

DDRA_MA_DM0

DDRA_MA_DM1

DDRA_MA_DM2

DDRA_MA_DM3

DDRA_MA_DM4

DDRA_MA_DM5

DDRA_MA_DM6

DDRA_MA_DM7

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

SA_CLK_DDR0

SA_CLK_DDR#0

SA_CLK_DDR1

SA_CLK_DDR#1

DDR4_A_DRAMRST#

DDR_A_EVENT#

DDR_A_CKE0

DDR_A_CKE1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_CS0#

DDR_A_CS1#

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

1

TPC1Test_Point_20MIL

CC8

@

1000P_0402_50V7-K

VREF_DQA

AE28

MA_ADD0

Y2 7

MA_ADD1

Y2 9

MA_ADD2

Y2 6

MA_ADD3

W28

MA_ADD4

W29

MA_ADD5

W26

MA_ADD6

U29

MA_ADD7

W25

MA_ADD8

U26

MA_ADD9

AG29

MA_ADD10

U27

MA_ADD11

T28

MA_ADD12

AK26

MA_ADD13

T26

MA_ADD14/MA_BG1

T25

MA_ADD15/MA_ACT_L

AG26

MA_BANK0

AG27

MA_BANK1

T29

MA_BANK2/MA_BG0

E19

MA_DM0

D21

MA_DM1

K21

MA_DM2

F29

MA_DM3

AP28

MA_DM4

AV26

MA_DM5

AR22

MA_DM6

BC22

MA_DM7

K29

MA_DM8

H19

MA_DQS_H0

G19

MA_DQS_L0

B22

MA_DQS_H1

A22

MA_DQS_L1

F23

MA_DQS_H2

E23

MA_DQS_L2

G27

MA_DQS_H3

F27

MA_DQS_L3

AP25

MA_DQS_H4

AP26

MA_DQS_L4

AW27

MA_DQS_H5

AV27

MA_DQS_L5

AV22

MA_DQS_H6

AU22

MA_DQS_L6

BA21

MA_DQS_H7

AY21

MA_DQS_L7

L27

MA_DQS_H8

L26

MA_DQS_L8

AE25

MA_CLK_H0

AE26

MA_CLK_L0

AD26

MA_CLK_H1

AD27

MA_CLK_L1

AB28

MA_CLK_H2

AB29

MA_CLK_L2

AB25

MA_CLK_H3

AB26

MA_CLK_L3

N29

MA_RESET_L

AE29

MA_EVENT_L

P27

MA_CKE0

P29

MA_CKE1

AK27

MA0_ODT0

AL26

MA0_ODT1

AH25

MA1_ODT0

AL25

MA1_ODT1

AH26

MA0_CS_L0

AL29

MA0_CS_L1

AH29

MA1_CS_L0

AL28

MA1_CS_L1

AG24

MA_RAS_L/MA_RAS_L_ADD16

AK29

MA_CAS_L/MA_CAS_L_ADD15

AH28

MA_WE_L/MA_WE_L_ADD14

B19

MA_VREFDQ

T32

M_VREF

MEMORY A

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_CHECK0

MA_CHECK1

MA_CHECK2

MA_CHECK3

MA_CHECK4

MA_CHECK5

MA_CHECK6

MA_CHECK7

MA_ZVDDIO_MEM_S

FP4 REV 0.93

AMD-BRISTOL_FP4-BGA968

H17

J17

F20

H20

E17

F17

K18

E20

A21

C21

C23

D23

B20

B21

B23

A23

G22

H22

E25

G25

J20

E22

H23

J23

F26

E27

J26

J27

H25

E26

G28

G29

AN26

AP29

AR26

AP24

AN29

AN27

AR29

AR27

AU26

AV29

AU25

AW25

AU29

AU28

AW26

AT25

AV23

AW23

AV20

AW20

AR23

AT23

AR20

AT20

BB23

BB22

BB20

AY19

BA23

BC23

BC21

BB21

K26

K28

N26

N28

J29

K25

L29

N25

AD29

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

MA_ZVDDIO

RC4 39.2_0402_1%

12

DDRA_MA_DM[0..7] 14

DDR_A_DQS#[0..7] 14

DDR_A_DQS[0..7] 14

DDR_A_D[0..63] 14

DDR_A_MA[0..13] 14

+1.2V

D D

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

1

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2016/09/29

2016/09/29

2016/09/29

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

3

2014/07/01

2014/07/01

2014/07/01

4

Title

APU DDRA/1

APU DDRA/1

APU DDRA/1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

Tuesday, May 09, 2017

Tuesday, May 09, 2017

Tuesday, May 09, 2017

5

6 84

6 84

6 84

SIT

SIT

SIT

1

Vinafix.com

2

3

4

5

UC1I

A A

B B

C C

AG31

MB_ADD0

AC30

MB_ADD1

AC31

MB_ADD2

AB32

MB_ADD3

AA32

MB_ADD4

AA33

MB_ADD5

AA31

MB_ADD6

Y3 3

MB_ADD7

AA30

MB_ADD8

W32

MB_ADD9

AG32

MB_ADD10

Y3 2

MB_ADD11

W33

MB_ADD12

AL31

MB_ADD13

W30

MB_ADD14/MB_BG1

V32

MB_ADD15/MB_ACT_L

AH32

MB_BANK0

AG33

MB_BANK1

W31

MB_BANK2/MB_BG0

D25

MB_DM0

D29

MB_DM1

E33

MB_DM2

J33

MB_DM3

AR30

MB_DM4

AW30

MB_DM5

BC30

MB_DM6

BC26

MB_DM7

N33

MB_DM8

B26

MB_DQS_H0

A26

MB_DQS_L0

B30

MB_DQS_H1

A30

MB_DQS_L1

F32

MB_DQS_H2

E32

MB_DQS_L2

K32

MB_DQS_H3

J32

MB_DQS_L3

AR32

MB_DQS_H4

AR33

MB_DQS_L4

AW32

MB_DQS_H5

AW33

MB_DQS_L5

BA29

MB_DQS_H6

AY29

MB_DQS_L6

BA25

MB_DQS_H7

AY25

MB_DQS_L7

P32

MB_DQS_H8

N32

MB_DQS_L8

AE33

MB_CLK_H0

AE32

MB_CLK_L0

AE30

MB_CLK_H1

AE31

MB_CLK_L1

AD32

MB_CLK_H2

AD33

MB_CLK_L2

AC33

MB_CLK_H3

AC32

MB_CLK_L3

T33

MB_RESET_L

AG30

MB_EVENT_L

U32

MB_CKE0

U33

MB_CKE1

AL30

MB0_ODT0

AM32

MB0_ODT1

AJ32

MB1_ODT0

AM33

MB1_ODT1

AJ33

MB0_CS_L0

AL32

MB0_CS_L1

AJ30

MB1_CS_L0

AL33

MB1_CS_L1

AH33

MB_RAS_L/MB_RAS_L_ADD16

AK32

MB_CAS_L/MB_CAS_L_ADD15

AJ31

MB_WE_L/MB_WE_L_ADD14

A19

MB_VREFDQ

MEMORY B

MB_ZVDDIO_MEM_S

FP4 REV 0.93

AMD-BRISTOL_FP4-BGA968

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_CHECK0

MB_CHECK1

MB_CHECK2

MB_CHECK3

MB_CHECK4

MB_CHECK5

MB_CHECK6

MB_CHECK7

A25

C25

C27

D27

B24

B25

B27

A27

A29

C29

B32

D32

B28

B29

A31

C31

E30

E31

G33

G32

C33

D33

G30

G31

J30

J31

L33

L32

H32

H33

L30

L31

AN31

AP32

AT32

AU32

AN33

AN32

AR31

AT33

AU30

AV32

BA33

AY32

AU33

AU31

AW31

AY33

BC31

BB30

BB28

AY27

BB32

BA31

BC29

BB29

BB27

BB26

BB24

AY23

BA27

BC27

BC25

BB25

N30

N31

R33

R32

M32

M33

R30

R31

AF32

D D

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

1

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2016/09/29

2016/09/29

2016/09/29

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

3

2014/07/01

2014/07/01

2014/07/01

4

Title

APU DDRB/2

APU DDRB/2

APU DDRB/2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

Tuesday, May 09, 2017

Tuesday, May 09, 2017

Tuesday, May 09, 2017

5

7 84

7 84

7 84

SIT

SIT

SIT

1

Vinafix.com

APU_MUX_TX0+21

APU_MUX_TX0-21

APU_MUX_TX1+21

A A

HDMI

DDI1 to TYPE C

eDP

APU_SVT77

APU_SVC77

B B

+1.8VS

1 2

RC31 300_0201_5%

1 2

RC32 300_0201_5%

APU_RESET#

1

CC9

@

0.1U_0201_16V6-K

+1.8VS

+1.8VS

2

H_PROCHOT#52

RPC1

1 8

2 7

3 6

4 5

1K_0804_8P4R_5%

RPC2

1 8

2 7

3 6

4 5

1K_0804_8P4R_5%

1

APU_TDI

APU_TMS

APU_TCK

APU_TRST#

APU_SIC

APU_SID

APU_ALERT#

APU_PROCHOT#

C C

D D

APU_SVD77

APU_GFX_SVT78

APU_GFX_SVC78

APU_GFX_SVD78

APU_RESET#

APU_PWROK

APU_PWROK

1

CC10

@

0.1U_0201_16V6-K

2

1 2

RC48 0_0201_SM

APU_SVT

APU_SVC

APU_SVD

APU_GFX_SVT

APU_GFX_SVC

APU_GFX_SVD

Cap close to JHDT.9

APU_MUX_TX1-21

APU_MUX_TX2+21

APU_MUX_TX2-21

APU_MUX_TX3+21

APU_MUX_TX3-21

APU_DP1_TXP034

APU_DP1_TXN034

APU_DP1_TXP134

APU_DP1_TXN134

APU_DP1_TXP234

APU_DP1_TXN234

APU_DP1_TXP334

APU_DP1_TXN334

APU_EDP_TX0+19

APU_EDP_TX0-19

APU_EDP_TX1+19

APU_EDP_TX1-19

1 2

RC21 0_0201_SM

1 2

RC23 33_0201_5%

1 2

RC25 33_0201_5%

1 2

RC27 0_0201_SM

1 2

RC28 33_0201_5%

1 2

RC29 33_0201_5%

APU_TRST#

+3VS

12

APU_PWROK77

1

CC11

0.01U_0201_25V7-K

2

RC47

10K_0201_5%

2

APU_MUX_TX0+

APU_MUX_TX0-

APU_MUX_TX1+

APU_MUX_TX1-

APU_MUX_TX2+

APU_MUX_TX2-

APU_MUX_TX3+

APU_MUX_TX3-

APU_DP1_TXP0

APU_DP1_TXN0

APU_DP1_TXP1

APU_DP1_TXN1

APU_DP1_TXP2

APU_DP1_TXN2

APU_DP1_TXP3

APU_DP1_TXN3

APU_EDP_TX0+

APU_EDP_TX0-

APU_EDP_TX1+

APU_EDP_TX1-

APU_SVT_R

APU_SVC_R

APU_SVD_R

APU_GFX_SVT_R

APU_GFX_SVC_R

APU_GFX_SVD_R

APU_SIC

APU_SID

APU_RESET#

APU_PWROK

APU_PROCHOT#

APU_ALERT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

1 2

RC42 33_0201_5%HDT@

RP1

1 8

2 7

3 6

4 5

HDT@

10K_0804_8P4R_5%

+1.8VS

12

RC46

10K_0201_5%

B

2

E

APU_PROCHOT#H_PROCHOT# H_PROCHOT#_R

3 1

C

QC7

MLMBT3904WT1G NPN SOT323-3

2

C15

D17

D19

B15

B16

A18

B18

C17

D15

C19

A15

B17

H15

H14

D13

G15

J14

C13

A11

B6

A6

D7

C7

A7

B7

D9

C9

A2

A3

B4

A4

D5

C5

A5

B5

E2

E1

E3

E4

D1

D2

C1

B1

UC1C

DP2_TXP0

DP2_TXN0

DP2_TXP1

DP2_TXN1

DP2_TXP2

DP2_TXN2

DP2_TXP3

DP2_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

SVT0

SVC0

SVD0

SVT1

SVC1

SVD1

SIC

SID

RESET_L

PWROK

PROCHOT_L

ALERT_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

+1.8VS

DISPLAY/SVI2/JTAG/TEST

DP_STEREOSYNC/TEST36

VDDCR_GFX_SENSE

VDDCR_NB_SENSE

VDDCR_CPU_SENSE

FP4 REV 0.93

AMD-BRISTOL_FP4-BGA968

JHDT1

1

1

2

3

3

4

5

5

6

7

7

8

9

9

10

11

11

12

13

13

14

15

15

16

17

17

18

19

19

20

HDT@

SAMTE_ASP-136446-07-B

A9

DP_ZVSS

DP_AUX_ZVSS

TEMPINRETURN

VDDP_SENSE

2

4

6

8

10

12

14

16

18

20

B9

G5

DP_BLON

G6

DP_DIGON

F11

DP_VARY_BL

H9

DP2_AUXP

G9

DP2_AUXN

E9

DP2_HPD

F7

DP1_AUXP

E7

DP1_AUXN

F5

DP1_HPD

F8

DP0_AUXP

E8

DP0_AUXN

G8

DP0_HPD

K24

RSVD_1

E15

TEMPIN0

E14

TEMPIN1

E12

TEMPIN2

F14

AK24

TEST410

AL24

TEST411

P24

TEST4

N24

TEST5

AN24

TEST6

AB8

TEST9

Y9

TEST10

B10

TEST14

D11

TEST15

A10

TEST16

C11

TEST17

B11

TEST11

A14

TEST18

B14

TEST19

A13

TEST28_H

B13

TEST28_L

P26

TEST31

E11

A17

TEST37

H11

J12

G12

AY18

H12

VSS_SENSE

APU_TCK

APU_TMS

1 2

RC41 0_0201_SM

APU_TDO

APU_PWROK

APU_RESET#

APU_DBRDY

1 2

RC45 33_0201_5%HDT@

APU_TEST19

APU_TEST18

3

DP_ZVSS

DP_AUX_ZVSS

APU_ENBKL_R

APU_ENVDD

APU_EDP_PWM_R

APU_HDMI_CLK

APU_HDMI_DAT

APU_HDMI_HPD

APU_DP1_AUXP

APU_DP1_AUXN

DDIP1_HPD

APU_EDP_AUX

APU_EDP_AUX#

APU_EDP_HPD

APU_TEST410

APU_TEST411

APU_TEST4

APU_TEST5

APU_TEST6

APU_TEST9

APU_TEST10

APU_TEST14

APU_TEST15

APU_TEST16

APU_TEST17

APU_TEST11

APU_TEST18

APU_TEST19

APU_TEST28_H

APU_TEST28_L

APU_TEST31

DP_STEREOSYNC

APU_TEST37

VDDCR_GFX_SENSE

VDDNB_SENSE

VDD_SENSE

VDDP_SENSE

VSS_SENSE

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXC EPT AS AUTHORI ZED BY LC FUTURE CE NTER NEITHER THIS SHEET NOR THE I NFORMATION IT CONTAINS

DEPARTMENT EXC EPT AS AUTHORI ZED BY LC FUTURE CE NTER NEITHER THIS SHEET NOR THE I NFORMATION IT CONTAINS

DEPARTMENT EXC EPT AS AUTHORI ZED BY LC FUTURE CE NTER NEITHER THIS SHEET NOR THE I NFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

1 2

RC8 2K_0201_1%

1 2

RC9 150_0201_1%

APU_ENVDD 19

APU_HDMI_CLK 21

APU_HDMI_DAT 21

APU_HDMI_HPD 21

APU_DP1_AUXP 34

APU_DP1_AUXN 34

DDIP1_HPD 33,34

APU_EDP_AUX 19

APU_EDP_AUX# 19

APU_EDP_HPD 19

1 2

RC11 1K_0201_1%@

1 2

RC16 1K_0201_1%@

1 2

RC17 1K_0201_1%@

1 2

RC18 1K_0201_1%@

1 2

RC20 1K_0201_1%

1 2

RC22 1K_0201_1%

Test_Point_12MIL

TPC13

1

1 2

RC33 0_0201_SM

APU_TDI

APU_DBREQ#

1

2

Cap close to JHDT.16

CC12

HDT@

0.01U_0201_25V7-K

1

TPC2Test_Point_12MIL

1

TPC3Test_Point_12MIL

1

TPC4Test_Point_12MIL

1

TPC5Test_Point_12MIL

1

TPC6Test_Point_12MIL

1

TPC7Test_Point_12MIL

1

TPC8Test_Point_12MIL

1

TPC9Test_Point_12MIL

1

TPC10Test_Point_12MIL

1

TPC11Test_Point_12MIL

1

TPC12Test_Point_12MIL

Test_Point_12MIL

TPC14

TPC15

1

1

1

TPC16Test_Point_12MIL

+1.8VS

12

RC43

1K_0201_1%

A. Vth = 1.5V (MAX)

B. Id = 200mA

C. RDSon = 10 ohm(MAX)

D. Vth in schematic = 0 - 1.8V

2016/09/29

2016/09/29

2016/09/29

Test_Point_12MIL

VDDCR_GFX_SENSE 78

VDDNB_SENSE 77

VDD_SENSE 77

VSS_SENSE 77

GFX_VSS_SENSE 78

APU_SIC

APU_SID

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

APU_ENBKL_R

APU_EDP_PWM_R

+1.8VS

G

S

QC5

LBSS138LT1G_SOT-23-3

Deciphered Date

Deciphered Date

Deciphered Date

4

12

12

12

RC44

1K_0201_1%

2

4

RC13

1 2

2.2K_0201_5%

RC14

@

100K_0201_5%

RC26

1 2

2.2K_0201_5%

RC30

@

4.7K_0201_5%

13

D

@

@

2014/07/01

2014/07/01

2014/07/01

12

RC10

@

100K_0201_5%

C

2

QC1

B

MLMBT3904WT1G NPN SOT323-3

E

3 1

SB000010U00

IB = 1.8V / 2.2K = 0.0008A

IB * Hfe = 0.0008 * 120 = 0.096A

IC = (Vc-Vce(sat)) / Rc = (3.3-0.25) / 100000 = 0.00000305

IB * Hfe > IC --- 飽 和 區 (OK)

12

RC6

@

47K_0201_5%

C

2

QC4

B

MLMBT3904WT1G NPN SOT323-3

E

SB000010U00

3 1

IB = 1.8V / 2.2K = 0.0008A

IB * Hfe = 0.0008 * 120 = 0.096A

IC = (Vc-Vce(sat)) / Rc = (3.3-0.25) / 47000 = 0.000065

IB * Hfe > IC --- 飽 和 區 (OK)

APU_ENBKL_R

APU_EDP_PWM_R

DP_STEREOSYNC

APU_TEST37

APU_TEST31

EC_SMB_CK3

G

2

EC_SMB_DA3

13

D

S

QC6

LBSS138LT1G_SOT-23-3

A. Vth = 1.5V (MAX)

B. Id = 200mA

C. RDSon = 10 ohm(MAX)

D. Vth in schematic = 0 - 1.8V

5

+3VS

12

RC7

@

2.2K_0201_5%

1 2

RC12 0_0201_5%@

13

A. Vth = 2.5V (MAX)

D

2

G

@

2

@

B. Id = 340 mA (MAX)

C. RDSon = 2.5 ohm(MAX)

QCC1

D. Vth in schematic = 3.3V

@

S

2N7002WT1G_SC-70-3

+3VS

12

RC15

@

4.7K_0201_5%

13

D

QC3

@

2N7002WT1G_1N_SC-70-3

A. Vth = 2.5V (MAX)

G

B. Id = 340 mA (MAX)

S

C. RDSon = 2.5 ohm(MAX)

D. Vth in schematic = 3.3V

+3VS

UC8

1

5

OE

VCC

2

A

4

ENBKL

GND3Y

SN74LV1T125DCKR_SC70-5

+3VS

UC9

1

5

OE

VCC

2

A

PANEL_BKLT_CTRL

4

GND3Y

SN74LV1T125DCKR_SC70-5

+1.8VS

12

12

EC_SMB_CK3 49,52,54

EC_SMB_DA3 49,52,54

Title

Title

Title

APU DISPLAY/CLK/MISC

APU DISPLAY/CLK/MISC

APU DISPLAY/CLK/MISC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

12

RC34

@

1K_0201_1%

RC38

@

1K_0201_1%

RC35

1K_0201_1%

12

RC39

@

1K_0201_1%

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

Tuesday, May 09, 2017

Tuesday, May 09, 2017

Tuesday, May 09, 2017

ENBKL 5 2

PANEL_BKLT_CTRL 19

12

RC36

@

39.2_0402_1%

12

RC40

@

39.2_0402_1%

8 84

8 84

5

8 84

SIT

SIT

SIT

+3VS

Vinafix.com

RC58 10K_0201_5%@

RC71 10K_0201_5%

RC72 10K_0201_5%@

RC73 10K_0201_5%

D D

C C

RC75 2K_0201_1%

CC13 10P_0201_50V8-DEMC_NS@

B B

+1.8V_SPI

RC77 10K_0201_5%

+1.8VS

A A

1

CC15

10P_0201_50V8-D

2

5

1 2

1 2

1 2

1 2

SATA_CTX_DRX_P020

SATA_CTX_DRX_N020

HDD

LAN

CR

WLAN

WWAN

1 2

1 2

RC78 1M_0201_5%

1

SATA_CRX_DTX_N020

SATA_CRX_DTX_P020

12

RPC3

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

1 2

YC 1

OSC1

NC2

NC12OSC2

48MHZ_10PF_7V48000017

5

HDD_DEVSLP0

LPC_FRAME#

PM_CLKRUN#

LPC_CLK1

CLK_PCIE_WLAN35

CLK_PCIE_WLAN#35

CLK_PCIE_WWAN36

CLK_PCIE_WWAN#36

CLK_PCIE_SSD24

CLK_PCIE_SSD#24

CLK_PCIE_LAN29

CLK_PCIE_LAN#29

CLK_PCIE_CR37

CLK_PCIE_CR#37

CLK_PCI_EC

SATA_CTX_DRX_P0 APU_SATA_CTX_DRX_P0

SATA_CTX_DRX_N0

SATA_CRX_DTX_N0

SATA_CRX_DTX_P0

+1.05VS_VDDP

HDD_DEVSLP024

CLK_PCI_EC52

CC220 0.01U_0201_25V6-K

CC221 0.01U_0201_25V6-K

CC222 0.01U_0201_25V6-K

CC223 0.01U_0201_25V6-K

CLK_PCIE_SSD

CLK_PCIE_LAN

CLK_PCIE_LAN#

CLK_PCIE_CR

CLK_PCIE_CR#

CLK_PCIE_WLAN

CLK_PCIE_WLAN#

CLK_PCIE_WWAN

CLK_PCIE_WWAN#

8MB(64Mb)

SPI_CS1#

SPI_IO3

SPI_IO2

SPI_CS2#

X48M_X1

X48M_X2

12

RC433

4

3

0_0201_SM

1

CC16

10P_0201_50V8-D

2

4

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

LPC_AD052

LPC_AD152

LPC_AD252

LPC_AD352

SERIRQ52

SPI_CLK50

SPI_SO50

SPI_SI50

SPI_CLK

1

CC229

RF@

39P_0201_50V9-J

2

4

12

12

RC76 10K_0201_5%@

RC56 1K_0201_1%

RC57 1K_0201_1%

RC60 10K_0201_5%

RC423 0_0201_SM

RC424 0_0201_SM

RC63 0_0201_SM

RC64 0_0201_SM

RC65 0_0201_SM

RC66 0_0201_SM

RC67 0_0201_SM

RC68 0_0201_SM

RC427 0_0201_SM

RC428 0_0201_SM

RC74 22_0201_5%EMC@

LPC_FRAME#52

SPI_CS2#_TPM50

APU_SATA_CTX_DRX_N0

APU_SATA_CRX_DTX_N0

APU_SATA_CRX_DTX_P0

SATA_ZVSS

SATA_ZVDDP

HDD_DEVSLP0

CLK_PCIE_SSD_R

CLK_PCIE_SSD#_RCLK_PCIE_SSD#

CLK_PCIE_LAN_R

CLK_PCIE_LAN#_R

CLK_PCIE_CR_R

CLK_PCIE_CR_R#

CLK_PCIE_WLAN_R

CLK_PCIE_WLAN#_R

CLK_PCIE_WWAN_R

CLK_PCIE_WWAN#_R

X48M_X1

X48M_X2

LPC_CLK0

LPC_CLK1

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

SERIRQ

PM_CLKRUN#

2

1

SPI_CLK

SPI_CS1#

SPI_CS2#

SPI_SO

SPI_SI

SPI_IO2

SPI_IO3

SPI_CS2#_TPM

1

CC230

RF@

27P_0201_25V8-J

2

UC1E

AU3

SATA_TX0P

AU4

SATA_TX0N

AV1

SATA_RX0N

AV2

SATA_RX0P

AY2

SATA_TX1P

AY1

SATA_TX1N

AW4

SATA_RX1N

AW3

SATA_RX1P

AW1

SATA_ZVSS

AW2

SATA_ZVDDP

AT17

DEVSLP0/EGPIO67

AT12

DEVSLP1/EGPIO70

BB15

SATA_ACT_L/AGPIO130

AU2

SATA_X1

AU1

SATA_X2

U4

GFX_CLKP

U3

GFX_CLKN

U1

GPP_CLK0P

U2

GPP_CLK0N

W4

GPP_CLK1P

W3

GPP_CLK1N

W1

GPP_CLK2P

W2

GPP_CLK2N

Y2

GPP_CLK3P

Y1

GPP_CLK3N

BC10

X25M_48M_OSC

T2

X48M_X1

T1

X48M_X2

AW14

LPCCLK0/EGPIO74

AY13

LPCCLK1/EGPIO75

BB11

LAD0

BA11

LAD1

AY11

LAD2

BA13

LAD3

AV14

LFRAME_L

BA1

ESPI_ALERT_L/LDRQ0_L

BC14

SERIRQ/AGPIO87

BC11

LPC_CLKRUN_L/AGPIO88

AE9

LPC_PD_L/AGPIO21

BC6

SPI_CLK/ESPI_CLK/EGPIO117

BB8

SPI_CS1_L/EGPIO118

AW7

SPI_CS2_L/ESPI_CS_L/EGPIO119

BA9

SPI_DI/ESPI_DATA/EGPIO120

AY7

SPI_DO/EGPIO121

AW11

SPI_WP_L/EGPIO122

BA7

SPI_HOLD_L/EGPIO133

AW12

SPI_TPM_CS_L/AGPIO76

SPI_SO

SPI_IO2

SPI_CS1#

SPI_SI

SPI_SO

SPI_CLK

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUT URE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUT URE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUT URE CENTER.

3

USB Port Assignment

0 USB 3.0 System Port (AOU)

CLK/SATA/USB/SPI/LPC

UC8M1

1

/CS

2

DO(IO1)

3

/WP(IO2)

4

GND

S IC FL 128M W25Q128FWSIQ SOIC 8P 1.8V

1 2

RC412 0_0201_SM

1 2

RC413 0_0201_SM

1 2

RC414 0_0201_SM

1 2

RC415 0_0201_SM

Issued Date

Issued Date

Issued Date

3

USBCLK/25M_48M_OSC

FP4 REV 0.93

AMD-BRISTOL_FP4-BGA968

/HOLDor/RESET(IO3)

VCC

CLK

DI(IO0)

USB_SS_ZVSS

USB_SS_ZVDDP

USB_SS_0TXP

USB_SS_0TXN

USB_SS_0RXP

USB_SS_0RXN

USB_SS_1TXP

USB_SS_1TXN

USB_SS_1RXP

USB_SS_1RXN

USB_SS_2TXP

USB_SS_2TXN

USB_SS_2RXP

USB_SS_2RXN

USB_SS_3TXP

USB_SS_3TXN

USB_SS_3RXP

USB_SS_3RXN

2016/09/29

2016/09/29

2016/09/29

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

USB_HSD6P

USB_HSD6N

USB_HSD7P

USB_HSD7N

8

7

6

5

EC_SPI_CS1#

EC_SPI_SI

EC_SPI_SO

EC_SPI_CLK

AP8

USB_ZVSS

AP5

USB20_P0

AR2

USB20_N0

AR1

USB20_P1

AR3

USB20_N1

AR4

USB20_P2

AN2

USB20_N2

AN1

USB20_P3_HUB

AN3

USB20_N3_HUB

AN4

USB20_P4

AM1

USB20_N4

AM2

USB20_P5_AOU

AL2

USB20_N5_AOU

AL1

USB20_P6

AL3

USB20_N6

AL4

AK2

AJ2

USB_SS_ZVSS

AD2

USB_SS_ZVDDP

AD1

USB3P0_TXP

AA3

USB3P0_TXN

AA4

USB3P0_RXP

W9

USB3P0_RXN

W8

USB3P1_TXP

AA2

USB3P1_TXN

AA1

USB3P1_RXP

W5

USB3P1_RXN

W6

USB3P2_TXP

AC1

USB3P2_TXN

AC2

USB3P2_RXP

Y6

USB3P2_RXN

Y7

AC4

AC3

AB5

AB6

0.085 A

+1.8V_SPISPI_CS1#

SPI_IO3

SPI_CLK

SPI_SI

+1.8V_SPI

EC_SPI_CS1# 52

EC_SPI_SI 52

EC_SPI_SO 52

EC_SPI_CLK 52

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

1 2

RC55 11.8K_0402_1%

USB20_P0 19

USB20_N0 19

USB20_P1 36

USB20_N1 36

USB20_P2 19

USB20_N2 19

USB20_P3_HUB 16

USB20_N3_HUB 16

USB20_P4 28

USB20_N4 28

USB20_P5_AOU 26

USB20_N5_AOU 26

USB20_P6 33

USB20_N6 33

1 2

RC69 1K_0201_1%

RC70 1K_0201_1%

USB3P0_TXP 28

USB3P0_TXN 28

USB3P0_RXP 28

USB3P0_RXN 28

USB3P1_TXP 25

USB3P1_TXN 25

USB3P1_RXP 25

USB3P1_RXN 25

USB3P2_TXP 34

USB3P2_TXN 34

USB3P2_RXP 34

USB3P2_RXN 34

1

CC14

0.1U_0201_16V6-K

2

2014/07/01

2014/07/01

2014/07/01

2

T o u c h Pane l

M.2 WWAN SLOT

USB Camera

USB HUB

( 1 f o r 3: FP/ SM card/ BT )

USB 3 .0 S y s t e m Por t (3rd P o rt)

USB 3 .0 S y s t e m Por t (AOU)

TYPE-C

12

+1.05VALW_VDDP

USB 3 .0 S y s t e m Por t (3rd P o rt)

USB 3 .0 S y s t e m Por t (AOU)

TYPE-C

Title

Title

Title

APU SATA/USB/LPC/SPI

APU SATA/USB/LPC/SPI

APU SATA/USB/LPC/SPI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

Tuesday, May 09, 2017

Tuesday, May 09, 2017

Tuesday, May 09, 2017

1

SIT

SIT

9 84

9 84

1

9 84

SIT

5

Vinafix.com

4

3

2

1

X32K_X1

X32K_X2

PM_SLP_S3#

PM_SLP_S5#

RSMRST#

PBTN_OUT#

BB12

AY15

BC19

BB13

BC15

BB17

BC17

BB18

BB16

BB10

RTCCLK

12

RC434

0_0201_SM

1

CC21

18P_0201_25V9-J

2

UC1D

LPC_RST_L

AN7

PCIE_RST_L/EGPIO26

AE4

RSMRST_L

AE1

PWR_BTN_L/AGPIO0

BC9

PWR_GOOD

AF2

SYS_RESET_L/AGPIO1

AG2

WAKE_L/AGPIO2

AK7

SLP_S3_L

AH5

SLP_S5_L

AE8

S0A3_GPIO/AGPIO10

AH8

S5_MUX_CTRL/EGPIO42

AH6

TEST0

AK8

TEST1/TMS

AE3

TEST2

ESPI_RESET_L/KBRST_L/AGPIO129

GA20IN/AGPIO126

AD7

LPC_PME_L/AGPIO22

LPC_SMI_L/AGPIO86

AG3

AC_PRES/USB_OC4_L/IR_RX0/AGPIO23

AD5

IR_TX0/USB_OC5_L/AGPIO13

AL8

IR_TX1/USB_OC6_L/AGPIO14

AN8

IR_RX1/AGPIO15

AE2

IR_LED_L/LLB_L/AGPIO12

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

CLK_REQ1_L/AGPIO115

CLK_REQ2_L/AGPIO116

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

CLK_REQG_L/OSCIN/EGPIO132

AH9

USB_OC0_L/TRST_L/AGPIO16

AG1

USB_OC1_L/TDI/AGPIO17

AH2

USB_OC2_L/TCK/AGPIO18

AL9

USB_OC3_L/TDO/AGPIO24

AU6

AZ_BITCLK/I2S_BCLK_MIC

AR8

AZ_SDIN0/I2S_DATA_MIC0

AP6

AZ_SDIN1/I2S_LR_PLAYBACK

AR5

AZ_SDIN2/I2S_DATA_MIC1

AU9

AZ_RST_L/I2S_LR_MIC

AT9

AZ_SYNC/I2S_BCLK_PLAYBACK

AR7

AZ_SDOUT/I2S_DATA_PLAYBACK

I2C0_SCL/EGPIO145

BB9

I2C0_SDA/EGPIO146

BB7

I2C1_SCL/EGPIO147

BC7

I2C1_SDA/EGPIO148

AG7

RTCCLK

AT1

X32K_X1

AT2

X32K_X2

ACPI/SD/AZ/GPIO/RTC/I 2C/UA RT/MIS C

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

SD0_WP/EGPIO101

SD0_PWR_CT RL/AGPIO102

SD0_CD/AGPIO25

SD0_CLK/EGPIO95

SD0_CMD/EGPIO96

SD0_DATA0/EGPIO97

SD0_DATA1/EGPIO98

SD0_DATA2/EGPIO99

SD0_DATA3/EGPIO100

SD0_LED/EGPIO93

SCL0/I2C2_SCL/EGPIO113

SDA0/I2C2_SDA/EGPIO114

SCL1/I2C3_SCL/AGPIO19

SDA1/I2C3_SDA/AGPIO20

AGPIO6/LDT_RST_L

AGPIO7/LDT_PWROK

VDDGFX_PD/AGPIO39

AGPIO66/SHUTDOWN_L

AGPIO68/SGPIO_CLK

AGPIO69/SGPIO_LOAD

AGPIO71/SGPIO_DATAOUT

AGPIO72/SGPIO_DATAIN

SPKR/AGPIO91

BLINK/USB_OC7_L/AGPIO11

GENINT1_L/AGPIO89

GENINT2_L/AGPIO90

FANIN0/AGPIO84

FANOUT0/AGPIO85

UART0_CTS_L/EGPIO135

UART0_RXD/EGPIO136

UART0_RTS_L/EGPIO137

UART0_TXD/EGPIO138

UART1_CTS_L/BT_I2S_BCLK/EGPIO140

UART1_INTR/BT_I2S_LRCLK/AGPIO144

FP4 REV 0.93

UART0_INTR/AGPIO139

UART1_RXD/BT_I2S_SDI/EGPIO141

UART1_RTS_L/EGPIO142

UART1_TXD/BT_I2S_SDO/EGPIO143

AMD-BRISTOL_FP4-BGA968

3

AGPIO3

AGPIO4

AGPIO5

AGPIO8

AGPIO9

AGPIO40

AGPIO64

AGPIO65

2016/09/29

2016/09/29

2016/09/29

APU_TOUCH_EN

BB2

BB5

BC2

APU_SSD_RST#

BB4

APU_HUB_RESET#

AY5

BC3

BA3

BC5

BA5

BB6

APU_SMB0CLK

BA15

APU_SMB0DATA

AY17

AG5

APU_SMB1_DATA_R

AG4

AL5

AGPIO3

AL6

AGPIO4

AJ1

AGPIO5

DEVSLP_GATE#

AJ3

LED_FNLOCK#

AH1

AJ4

AGPIO8

AK5

VDDGFX_PD_R

AD8

AG8

AGPIO40

AW15

AU15

IFDET

SKU_ID1

AT15

AU12

WWAN_DISABLE#

AT14

AR14

BC13

APU_SPKR

BA17

AN5

PSP_EN

BB14

BA19

RF_OFF#

BC18

BT_ON

BB19

WWAN_RESET#_R

AY9

UART0_RXD

AW8

AV5

UART0_TXD

AV8

AW9

TOUCH_PWR_ON#

AV11

AU7

LED_MICMUTE#

AT11

LED_MUTE#

AR11

AP9

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

RC437 0_0201_5%TPSC@

Deciphered Date

Deciphered Date

Deciphered Date

1 2

1

TPC34Test_Point_12MIL

APU_SSD_RST# 24

APU_HUB_RESET# 16

1 2

RC111 0_0201_SM

1 2

RC112 0_0201_SM

1 2

RC420 0_0201_SM

1 2

RC421 0_0201_SM

1

TP2Test_Point_12MIL

DEVSLP_GATE# 24

LED_FNLOCK# 46

1 2

RC105 0_0201_5%@

APU_SPKR 44

APU_DCOVER_SW 13

RF_OFF# 35

BT_ON 35

1 2

RC426 0_0201_5%@

UART0_RXD 35,40

UART0_TXD 35,40

TOUCH_PWR_ON# 19

LED_MICMUTE# 46

LED_MUTE# 46

2014/07/01

2014/07/01

2014/07/01

2

TOUCH_EN 19

PSP_EN

BT_ON

RF_OFF#

DEVSLP_GATE#

WWAN_DISABLE#

APU_SMB_CK0

APU_SMB_DA0

APU_SMB1_CLKAPU_SMB1_CLK_R

APU_SMB1_DATA

VDDGFX_PD 78

IFDET 24

SKU_ID1 29

WWAN_DISABLE# 36

AGPIO5

APU_DCOVER_SWAPU_DCOVER_SW

WWAN_DISABLE#

AGPIO3

VDDGFX_PD_R

WWAN_RESET# 36

APU_SMB1_CLK

APU_SMB1_DATA

APU_SMB0CLK

APU_SMB0DATA

Title

Title

Title

APU GPIO/AZ/I2C/SD/UARTS/ACPI

APU GPIO/AZ/I2C/SD/UARTS/ACPI

APU GPIO/AZ/I2C/SD/UARTS/ACPI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

APU_SMB_CK0 14,16

APU_SMB_DA0 14,16

APU_SMB1_CLK 29,47,52

APU_SMB1_DATA 29,47,52

AGPIO3

AGPIO8

Tuesday, May 09, 2017

Tuesday, May 09, 2017

Tuesday, May 09, 2017

2

2

2

2

1 2

1 2

1 2

12

1

1

1

12

1

12

RC88 2.2K_0201_5%

RC89 10K_0201_5%@

RC90 10K_0201_5%@

RC91 2.2K_0201_5%@

RC436 10K_0201_5%

RC96 10K_0201_5%@

RC422 10K_0201_5%

RC98 10K_0201_5%@

RC99 2K_0201_1%@

RC100 100K_0201_5%@

DIMM1, DIMM2

+3VALW

RPC10

1 8

2 7

3 6

4 5

2.2K_0804_8P4R_5%

RPC12

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

WWWOOOLLLVVVEEERRRIIINNNEEE444 AAAMMMDDD

+3VALW

1

+3VS

10 84

10 84

10 84

+3VS

+3VALW

SIT

SIT

SIT

1

+1.8VALW

12

RC80

10K_0201_5%

1 2

D D

+3VS

+3VS

+3VALW

C C

+3VS

+3VALW

B B

APU_AZ_BITCLK39

APU_AZ_SYNC39

APU_AZ_SDOUT39

+3VALW

A A

+3VALW

EC_RSMRST#52

RPC4

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

1 2

RC425 10K_0201_5%

1 2

RC418 10K_0201_5%

1 2

RC419 10K_0201_5%

1 2

RC92 10K_0201_5%@

1 2

RC93 10K_0201_5%@

1 2

RC94 10K_0201_5%

1 2

RC95 10K_0201_5%@

RC97 10K_0201_5%

1 2

RC101 10K_0201_5%@

1 2

RC102 10K_0201_5%@

RC115 15K_0201_5%

RC116 15K_0201_5%

RC117 15K_0201_5%

2

RC107 10K_0201_5%@

2

RC108 10K_0201_5%@

RPC5

10K_0804_8P4R_5%

RPC9

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

DCOVER_SW13,52

APU_AZ_RST#39

1 8

2 7

3 6

4 5

1 2

RC118 10K_0201_5%@

1 2

RC119 2K_0201_1%

RTC Coin battery implemented: Pull-up resistor

RTC Coin battery not implemented: Pull-down resistor

D1 RB751V-40_SOD323-2

SCS00008K00

CLKREQ_PCIE0_LAN#

CLKREQ_PCIE1_CR#

CLKREQ_PCIE2_WLAN#

CLKREQ_PCIE3_WWAN#

12

12

12

12

1

1

18

27

36

45

1 2

RC438 0_0201_5%@

1 2

1 2

1 2

1 2

1

CC19

EMC_NS@

10P_0402_50V8-J

2

RPC13

AGPIO40

APU_AZ_SDIN1

APU_AZ_SDIN2

10K_0804_8P4R_5%

5

LPC_RST#52

PLT_RST#16,24,29,35,37,50

CLKREQ_PCIE_SSD#

INT_MIC_DTCT#

SC_DTCT#

EC_WAKE#

AC_PRESENT

APU_S5_MUX_CTRL

BATLOW#

KBRST#

GATEA20

TEST0

TEST1

TEST2

S0A3_GPIO

APU_AZ_SDIN0

I2C1_CLK

I2C1_SDA

USB_OC1#

USB_OC0#

SYS_RESET#

APU_DCOVER_SW_R

R10396 33_0201_5%

R10397 33_0201_5%

R10398 33_0201_5%

R10399 33_0201_5%

RTCCLK

RTCCLK

RSMRST#

CC17 150P_0201_25V9-J

CC18 150P_0201_25V9-J

RC85 33_0201_5%

RC86 22_0201_5%

APU_S5_MUX_CTRL56

INT_MIC_DTCT#19

INT#_TYPEC_CPU33

CLKREQ_PCIE0_LAN#29

CLKREQ_PCIE1_CR#37

CLKREQ_PCIE2_WLAN#35

CLKREQ_PCIE3_WWAN#36

CLKREQ_PCIE_SSD#24

APU_AZ_SDIN039

RTCCLK_32K35

AZ_BITCLK

AZ_RST#

AZ_SYNC

AZ_SDOUT

TPC17 Test_Point_12MIL

TPC18 Test_Point_12MIL

TPC19 Test_Point_12MIL

TPC20 Test_Point_12MIL

1 2

1 2

1 2

1 2

PBTN_OUT#52

PWR_GOOD52

EC_WAKE#29,52

PM_SLP_S3#52

PM_SLP_S5#52

KBRST#52

GATEA2052

EC_SCI#52

AC_PRESENT52

SC_DTCT#47

USB_OC0#28

USB_OC1#26

I2C0_CLK33

I2C0_SDA33

RC113 0_0201_5%@

32.768KHZ 12.5PF 9H03200053

1

CC20

18P_0201_25V9-J

2

1

1

1

LPC_RST#_R

PLT_RST#_R

RSMRST#

PBTN_OUT#

PWR_GOOD

SYS_RESET#

EC_WAKE#

PM_SLP_S3#

PM_SLP_S5#

S0A3_GPIO

APU_S5_MUX_CTRL

TEST0

TEST1

TEST2

KBRST#

GATEA20

EC_SCI#

AC_PRESENT

INT_MIC_DTCT#

SC_DTCT#

INT#_TYPEC_CPU

BATLOW#

CLKREQ_PCIE0_LAN#

CLKREQ_PCIE1_CR#

CLKREQ_PCIE2_WLAN#

CLKREQ_PCIE3_WWAN#

CLKREQ_PCIE_SSD#

USB_OC0#

USB_OC1#

APU_DCOVER_SW_R

AZ_BITCLK

APU_AZ_SDIN0

APU_AZ_SDIN1

APU_AZ_SDIN2

AZ_RST#

AZ_SYNC

AZ_SDOUT

I2C0_CLK

I2C0_SDA

I2C1_CLK

I2C1_SDA

1 2

RC114

1 2

20M_0402_5%

YC 2

1 2

SJ10000MB00

Y_9H03200031_2P

4

5

Vinafix.com

D D

+VDD_CORE

CC23

1

2

1

2

22U_0603_6.3V6-M

0.22U_0201_10V6-K

CC108

0.22U_0201_10V6-K

0.22U_0201_10V6-M

1

2

COST@

+VDDNB_CORE

22U x 4

0.22U x 8

180P x 1

CC63

0.22U_0201_10V6-M

1

2

+1.35V_APU_VDDIO

22U x 8 + 3 (@)

0.22U x 6

180P x 1

CC81

22U_0603_6.3V6-M

1

2

CC101

0.22U_0201_10V6-K

1

2

COST@

CC109

0.22U_0201_10V6-K

1

2

CC24

CC25

0.22U_0201_10V6-M

0.22U_0201_10V6-M

1

2

COST@

CC64

CC65

0.22U_0201_10V6-M

0.22U_0201_10V6-M

1

2

CC83

CC82

22U_0603_6.3V6-M

1

2

CC102

CC103

0.22U_0201_10V6-K

1

2

COST@

Decoupling between Processor & DIMMs

across VDDIO & VSS split.

CC110

0.22U_0201_10V6-K

1

1

2

2

CC27

CC26

0.22U_0201_10V6-M

1

2

CC66

0.22U_0201_10V6-M

1

2

CC84

22U_0603_6.3V6-M

1

1

2

2

CC104

0.22U_0201_10V6-K

1

1

2

2

CC111

0.22U_0201_10V6-K

1

2

CC28

0.22U_0201_10V6-M

0.22U_0201_10V6-M

1

1

2

2

COST@

CC67

CC68

0.22U_0201_10V6-M

0.22U_0201_10V6-M

1

1

2

2

CC85

CC86

22U_0603_6.3V6-M

22U_0603_6.3V6-M

1

1

2

2

CC106

CC105

0.22U_0201_10V6-K

0.22U_0201_10V6-K

1

2

COST@

CC112

+1.35V_APU_VDDIO

180P_0402_50V8-J

180P_0402_50V8-J

0.22U x 4

1

180P x 2

2

CC30

CC29

180P_0402_50V8-J

0.22U_0201_10V6-M

0.22U_0201_10V6-M

1

2

0.22U_0201_10V6-M

1

2

22U_0603_6.3V6-M

180P_0402_50V8-J

1

2

CC87

1

2

COST@

CC69

1

2

1

2

1

2

CC70

180P_0402_50V8-J

0.22U_0201_10V6-M

1

2

@

@

CC89

CC88

22U_0603_6.3V6-M

22U_0603_6.3V6-M

1

1

2

2

CC22

COST@

+VDDNB_CORE

C C

B B

CC62

+1.2V

CC80

1

2

+1.2V

CC100

1

2

+1.2V

CC107

1

2

4

+VDD_GFX

22U x 9

0.22U x 9

180P x 1

+VDD_GFX

CC32

CC31

0.22U_0201_10V6-M

1

2

COST@

CC71

CC72

10U_0603_6.3V6-M

1

2

+1.05VS_VDDP

@

CC90

22U_0603_6.3V6-M

CC91

0.22U_0201_10V6-K

22U_0603_6.3V6-M

1

1

2

2

CC92

CC34

CC33

0.22U_0201_10V6-M

0.22U_0201_10V6-M

1

1

2

2

COST@

CC73

0.22U_0402_10V6-K

1

1

2

2

CC93

180P_0402_50V8-J

1

1

2

2

CC36

CC35

0.22U_0201_10V6-M

0.22U_0201_10V6-M

1

1

2

2

CC74

10U_0603_6.3V6-M

0.22U_0402_10V6-K

1

2

CC94

CC95

10U_0603_6.3V6-M

10U_0603_6.3V6-M

10U_0603_6.3V6-M

1

1

2

2

CC38

CC37

COST@

1

2

1

2

0.22U_0201_10V6-M

0.22U_0201_10V6-M

1

1

2

2

COST@

CC76

0.22U_0402_10V6-K

10U_0603_6.3V6-M

1

2

CC225

CC224

10U_0603_6.3V6-M

0.22U_0201_10V6-K

1

2

0.22U_0201_10V6-M

1

2

CC75

CC96

1

2

CC39

1

2

COST@

0.22U_0201_10V6-K

3

CC40

180P_0402_50V8-J

0.22U_0201_10V6-M

1

2

+1.05VS_VDDP+3VS_APU+1.8VS+1.8VALW+3VALW_APU +1.05VALW_VDDP

CC78