Lenovo T440P Schematic

5

4

3

2

1

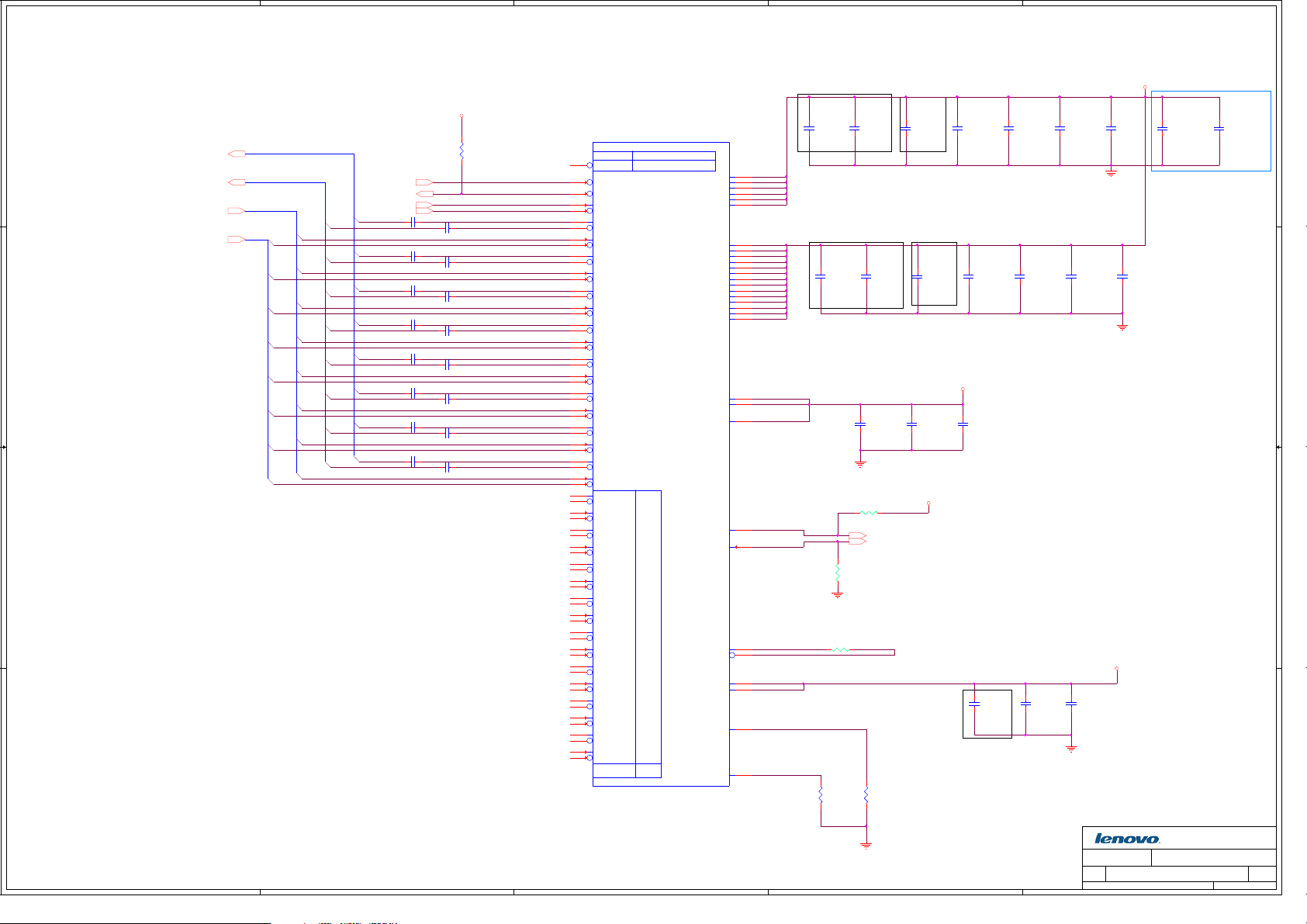

Oasis-1 SHB SOVP LOGIC SCHEMATICS

1.TITLE PAGE

2.EC HISTORY

D D

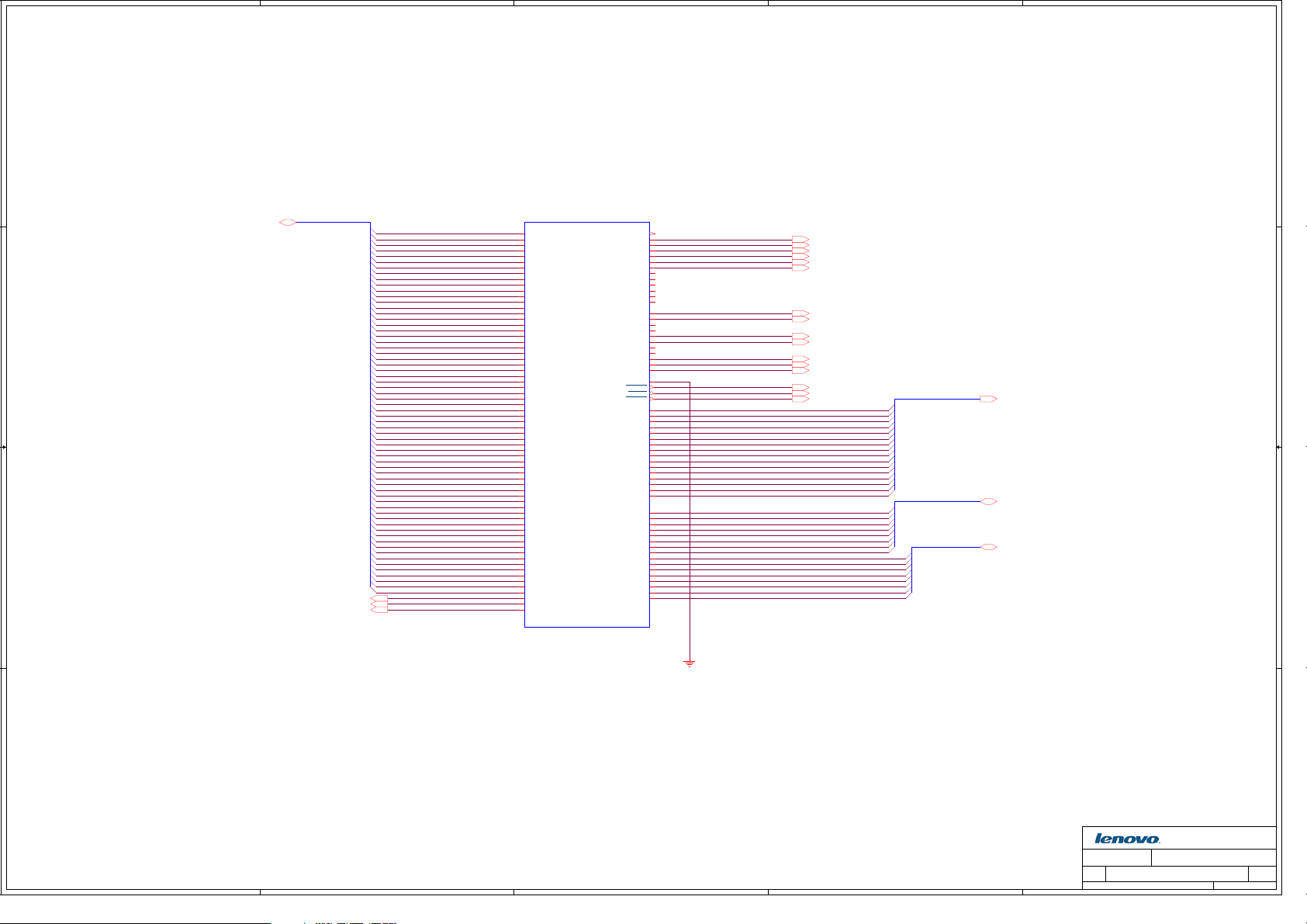

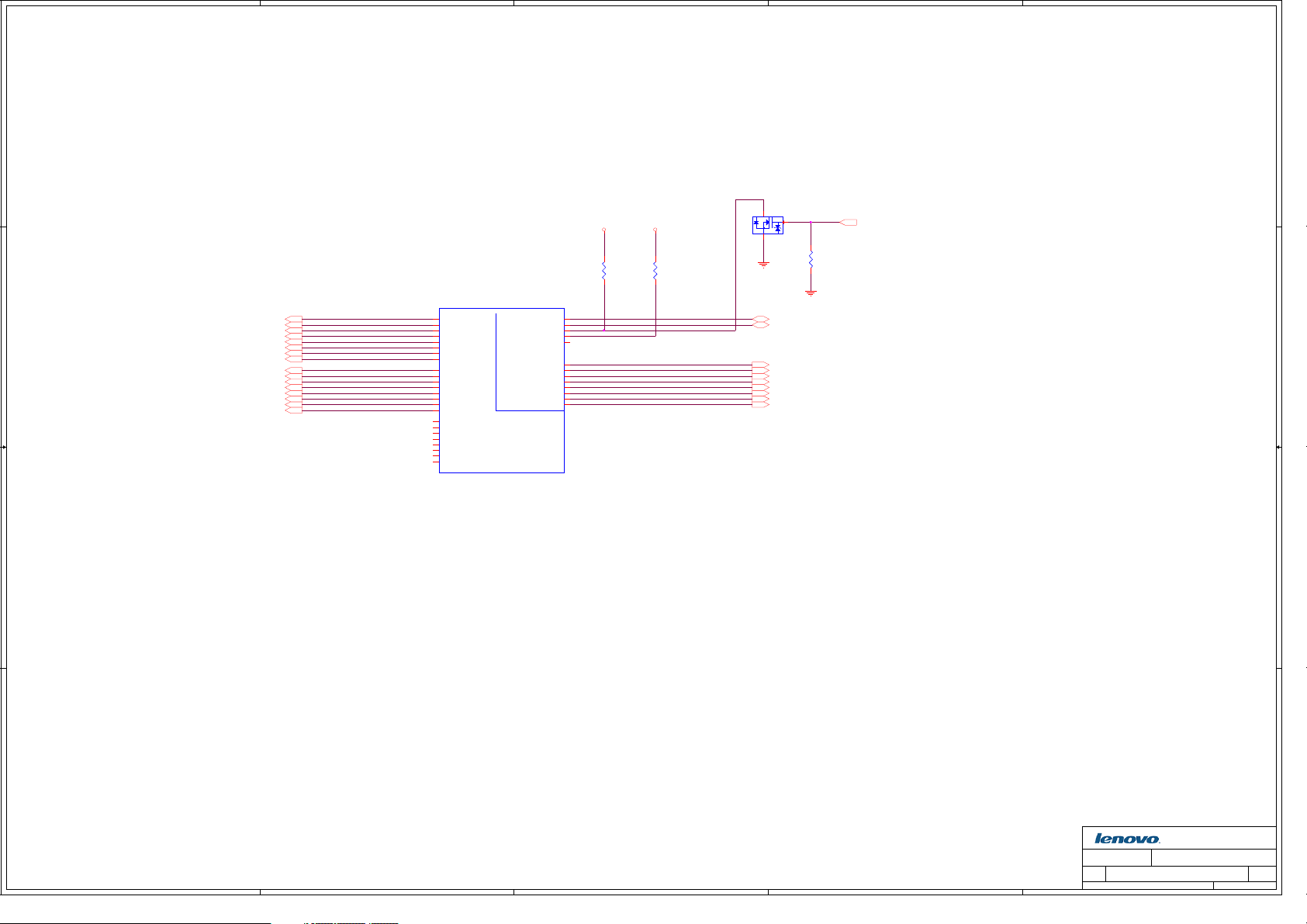

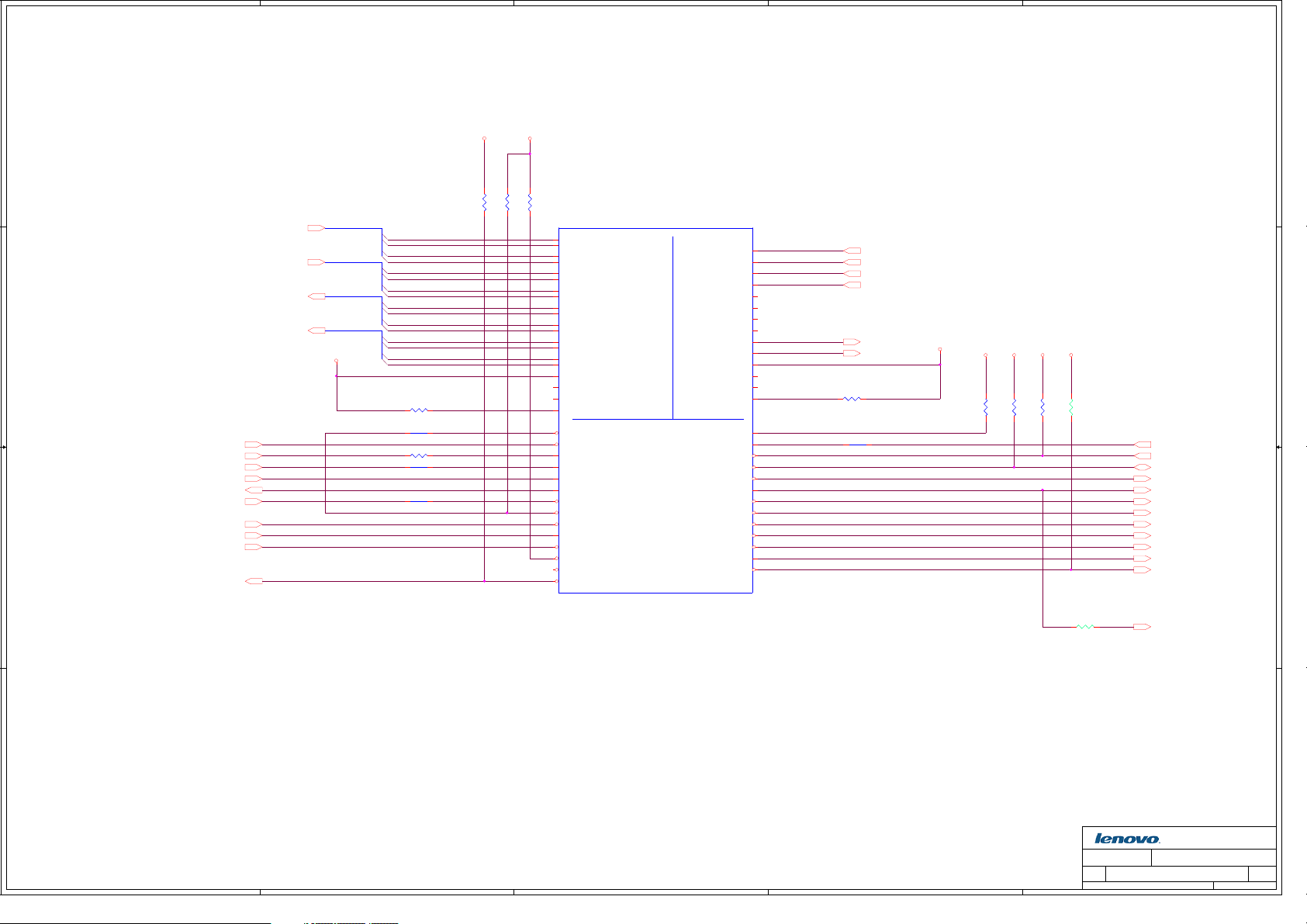

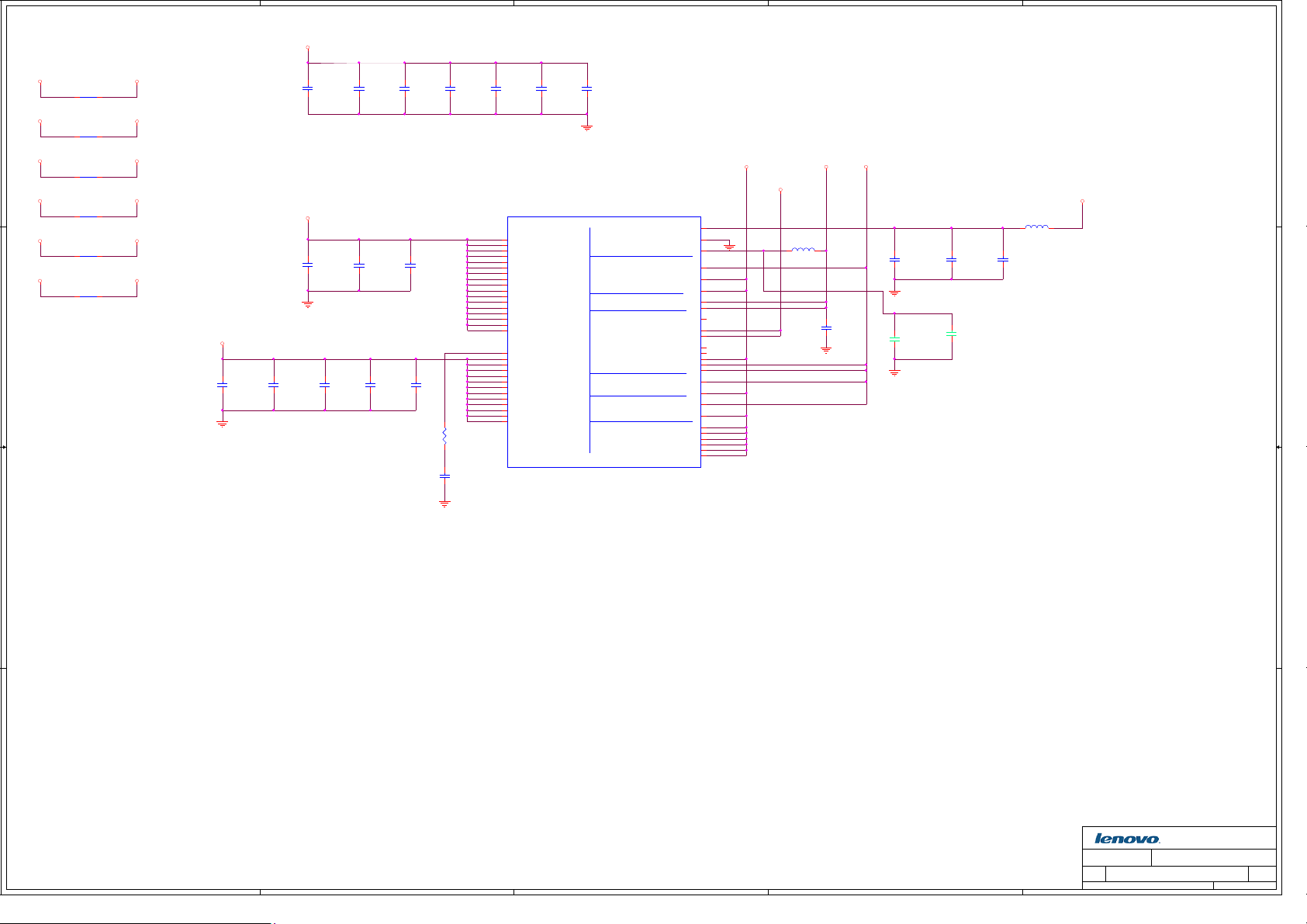

3.CPU(1/8) : DMI/FDI/PEG

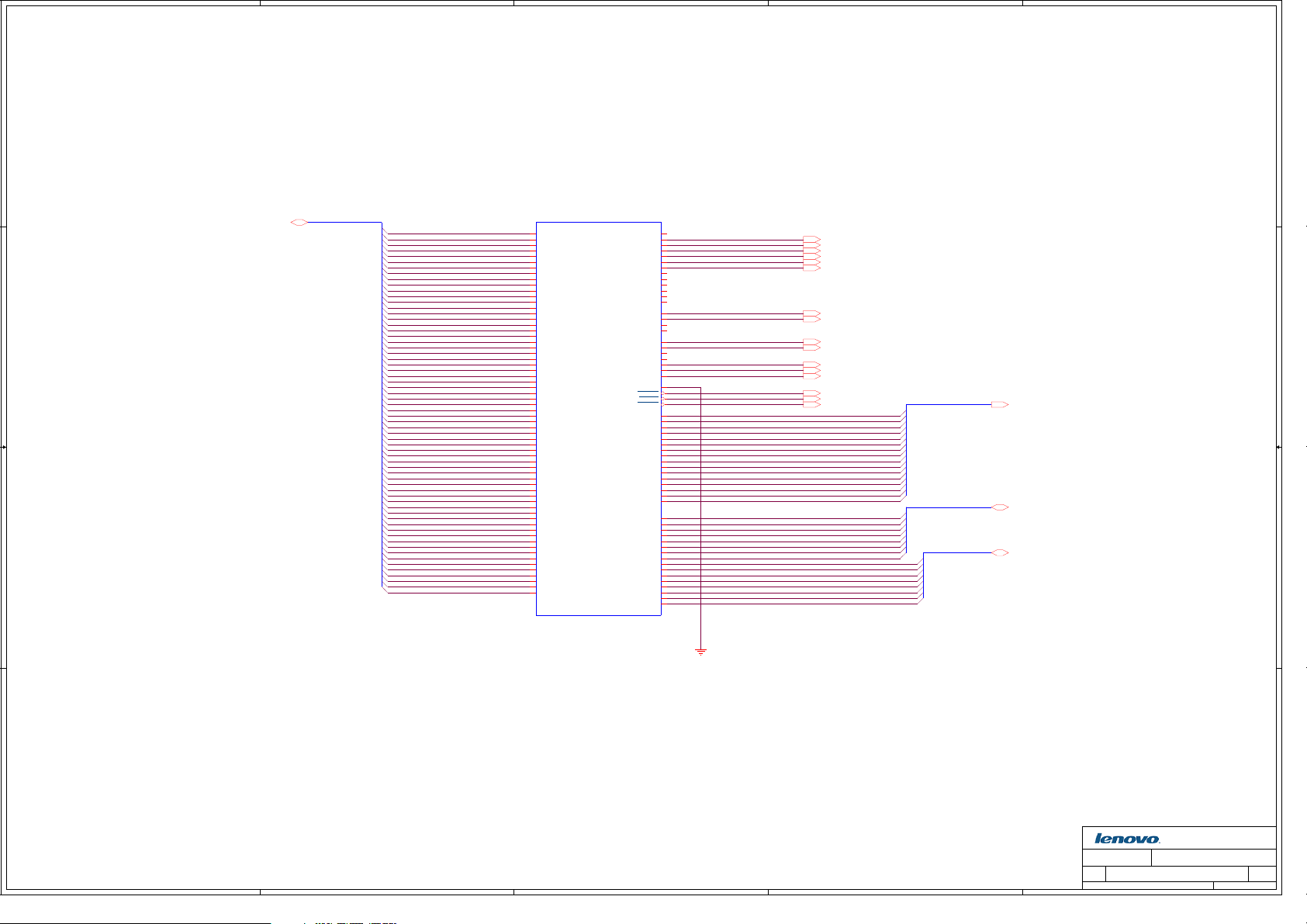

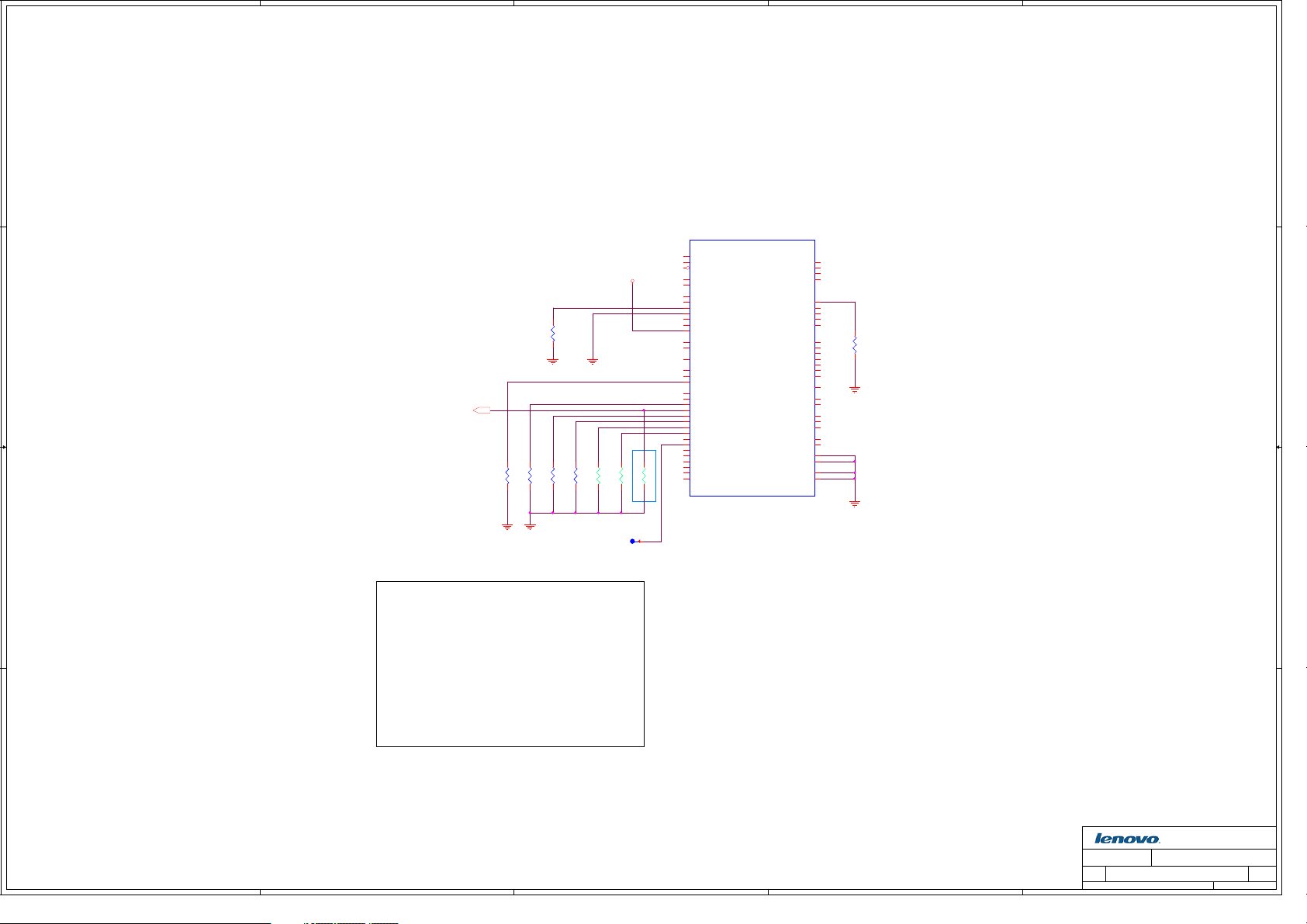

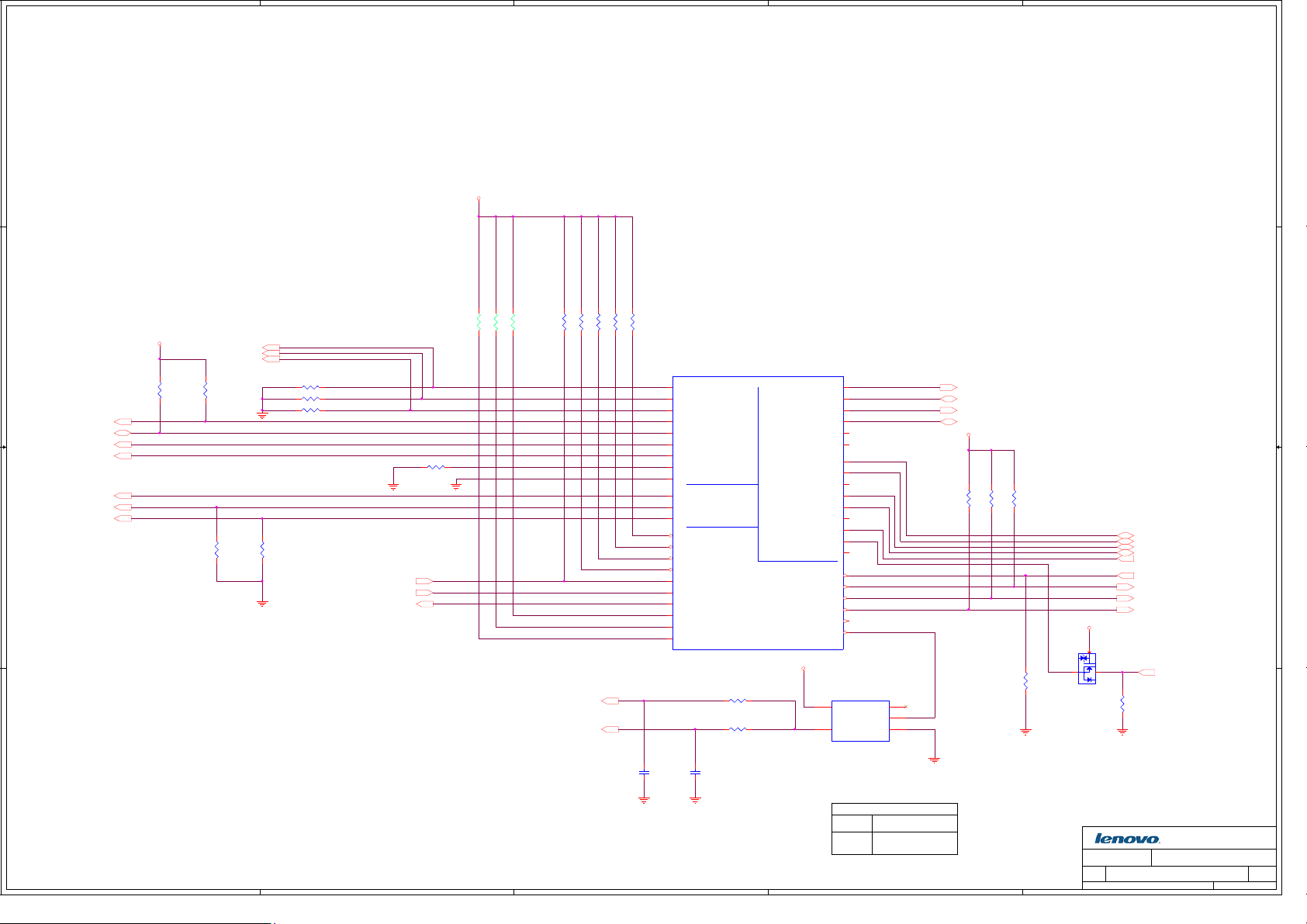

4.CPU(2/8) : MISC/JTAG/CLK

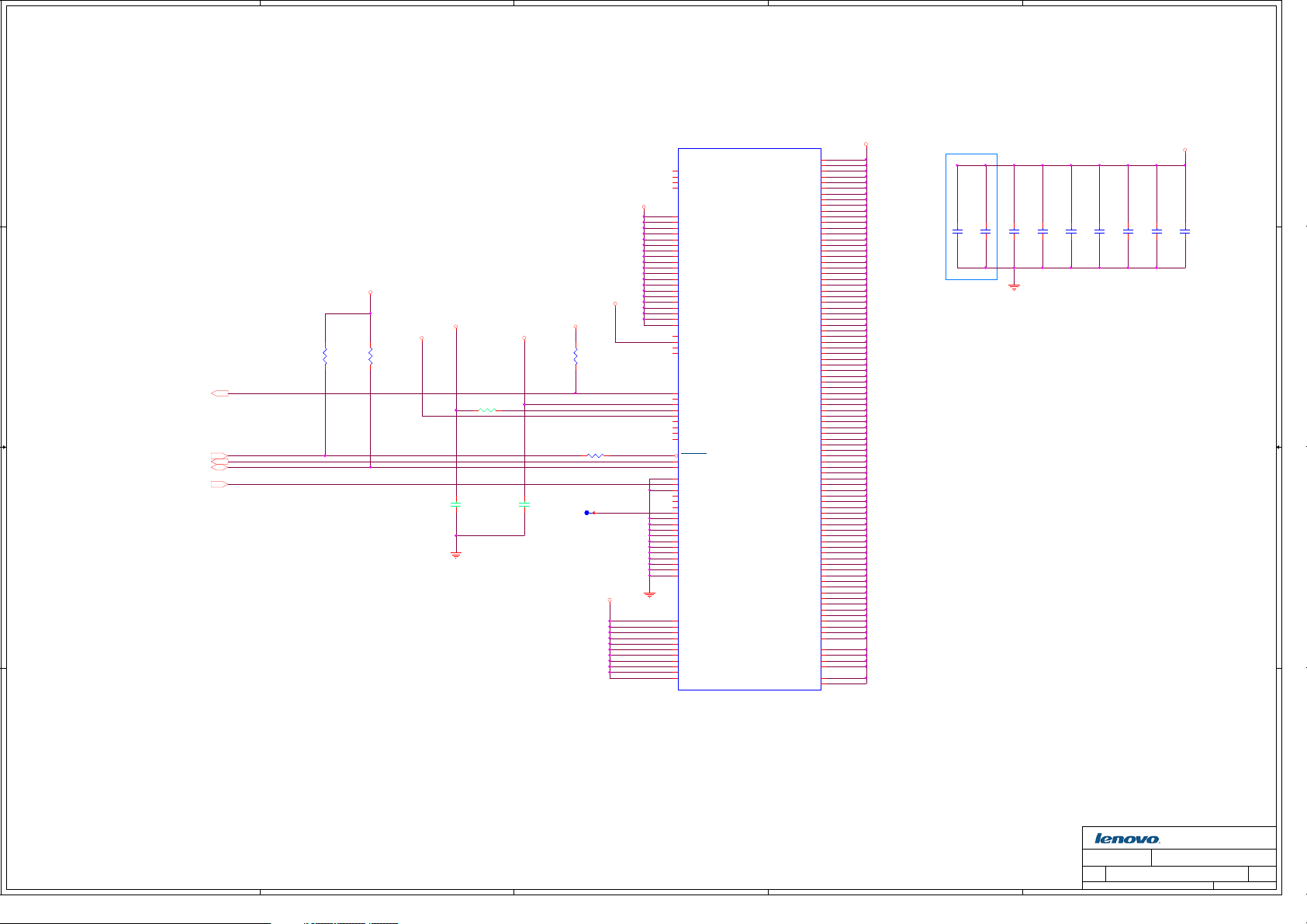

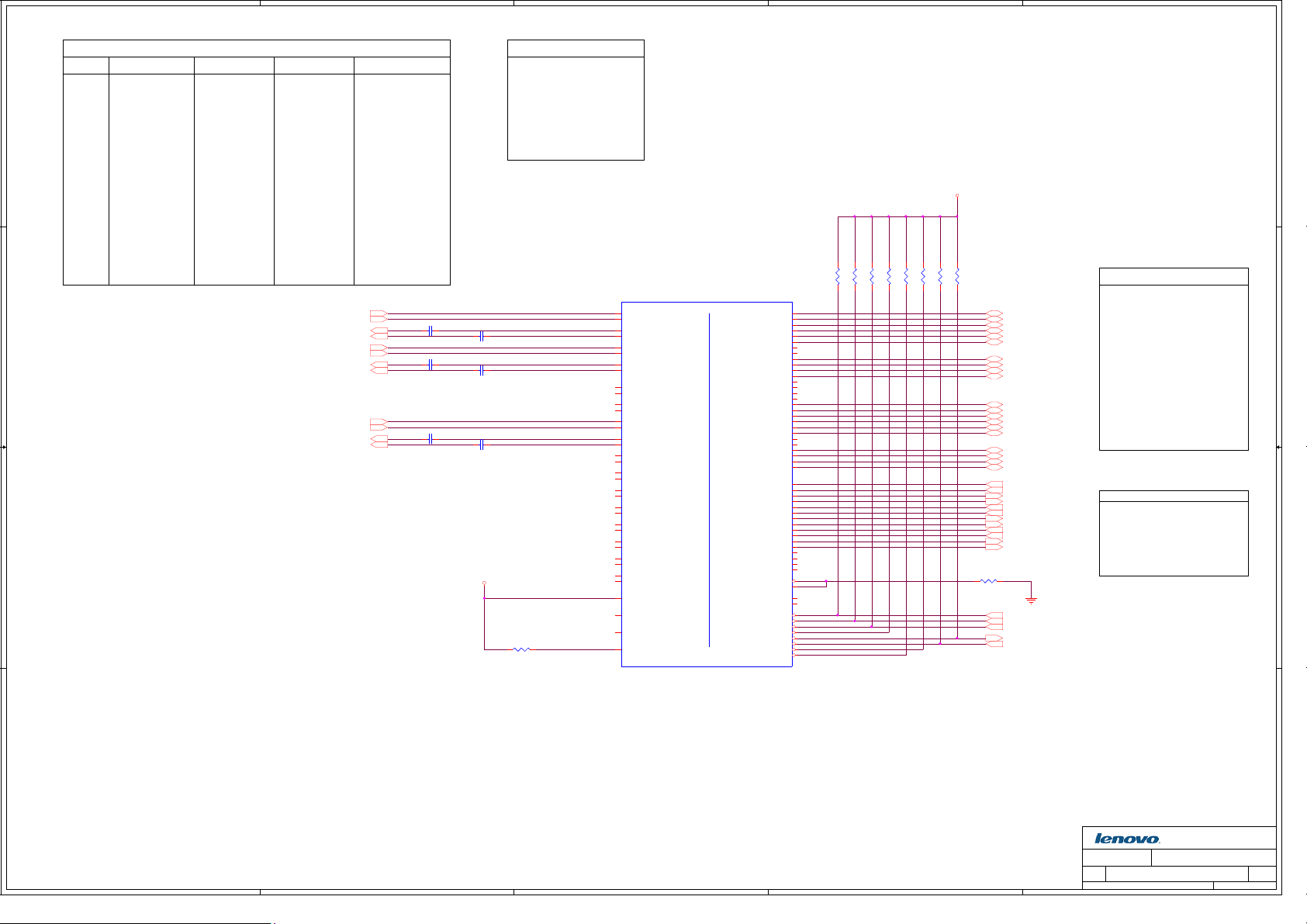

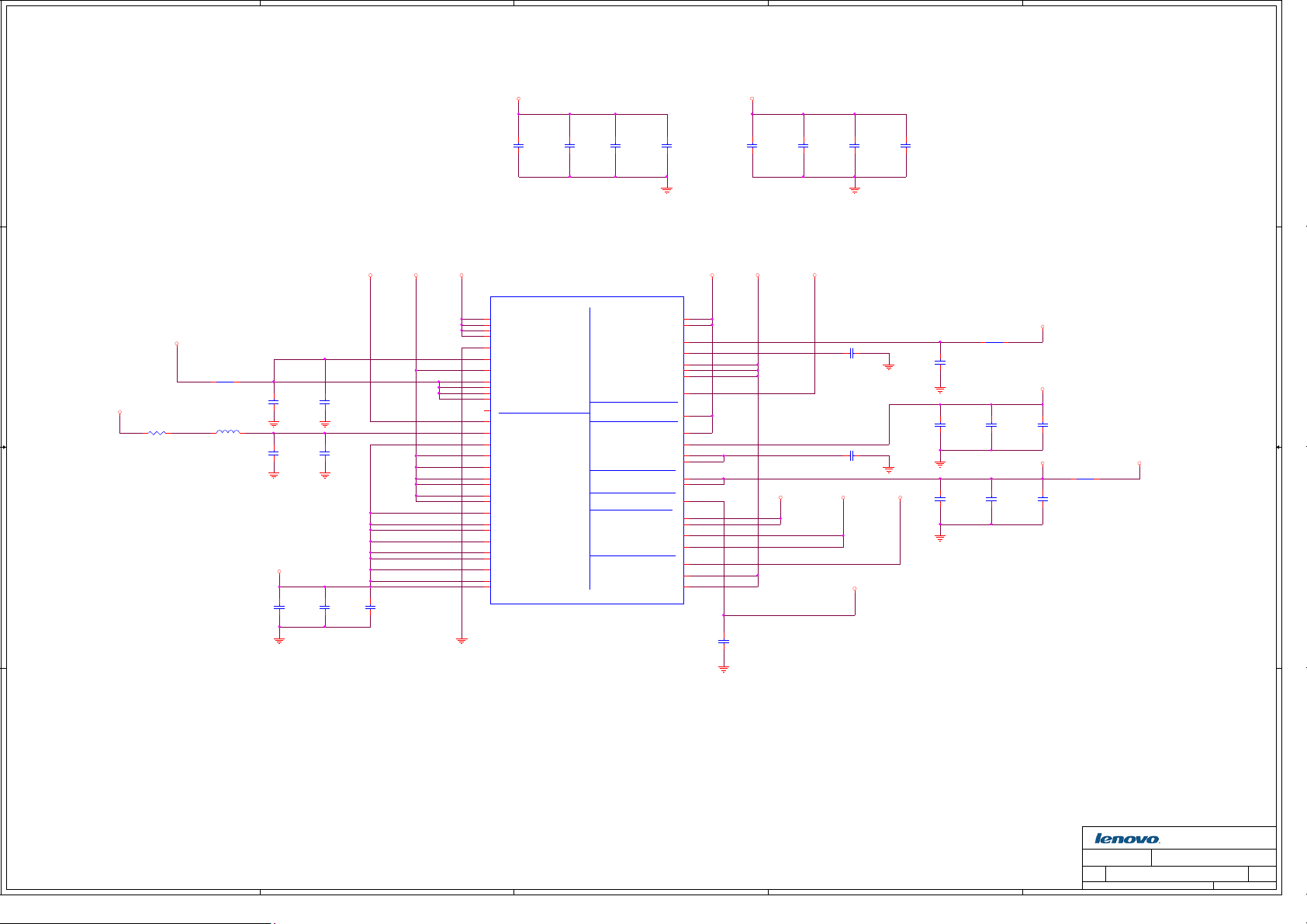

5.CPU(3/8) : DDR3L CHANNEL- A

6.CPU(4/8) : DDR3L CHANNEL- B

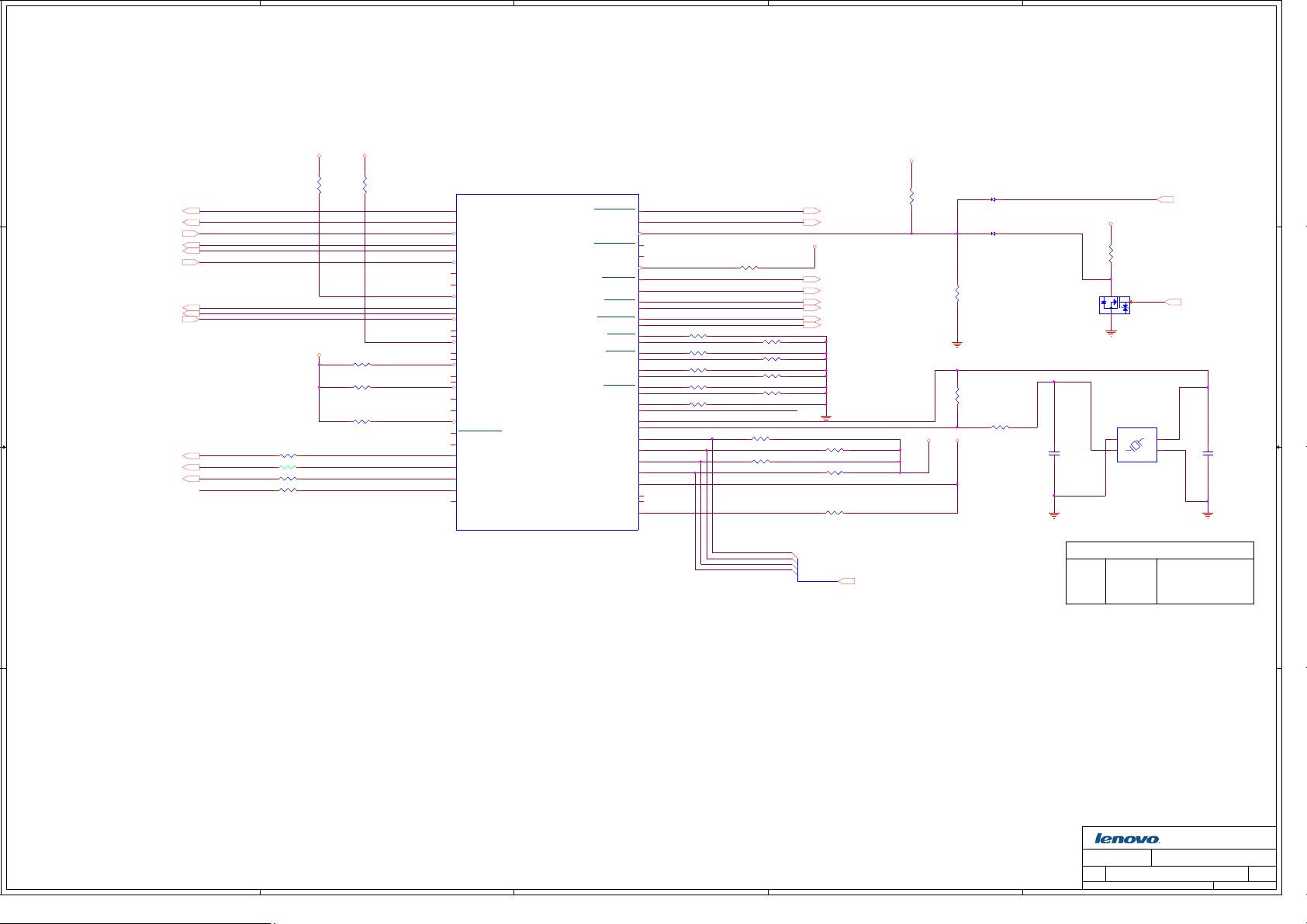

7.CPU(5/8) : POWER

8.CPU(6/8) : GND

9.CPU(7/8) : EDP/DDI

10.CPU(8/8) : CFG/RESERVED

11.PCH(1/10) : RTC/HDA/SATA/JTAG

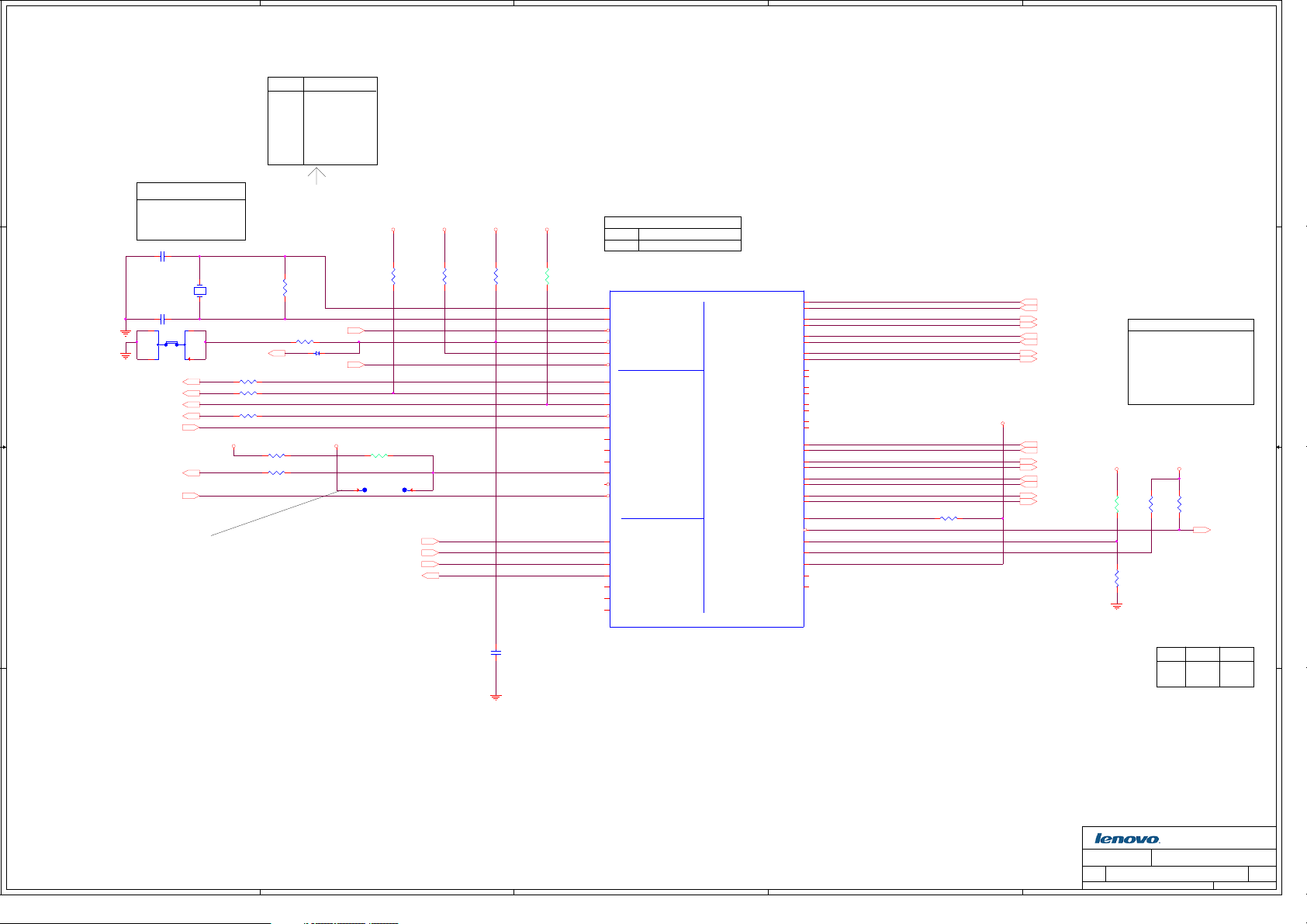

12.PCH(2/10) : LPC/SPI/SMBUS/C-LINK/THERMAL

C C

13.PCH(3/10) : DMI/FDI/PM

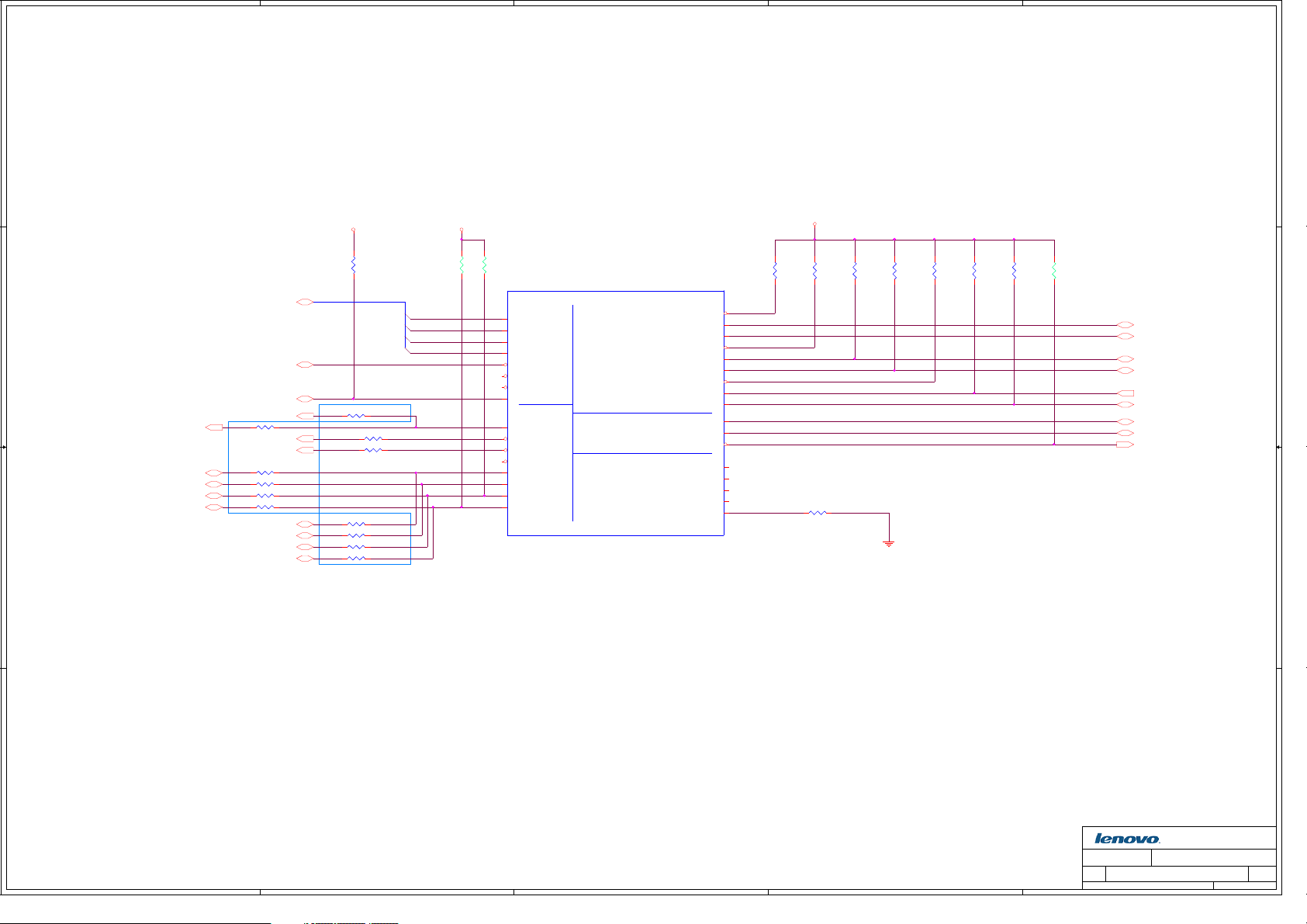

14.PCH(4/10) : LCD/CRT/PCI/DDI CONTROL

15.PCH(5/10) : GPIO/CPU/MISC/NCTF/RSVD

16.PCH(6/10) : PCIE/USB

17.PCH(7/10) : CLOCKS

18.PCH(8/10) : POWER

19.PCH(9/10) : POWER

20.PCH(10/10):GND

21.XDP CONNECTOR

B B

22.RTC BATTERY

23.SPI FLASH

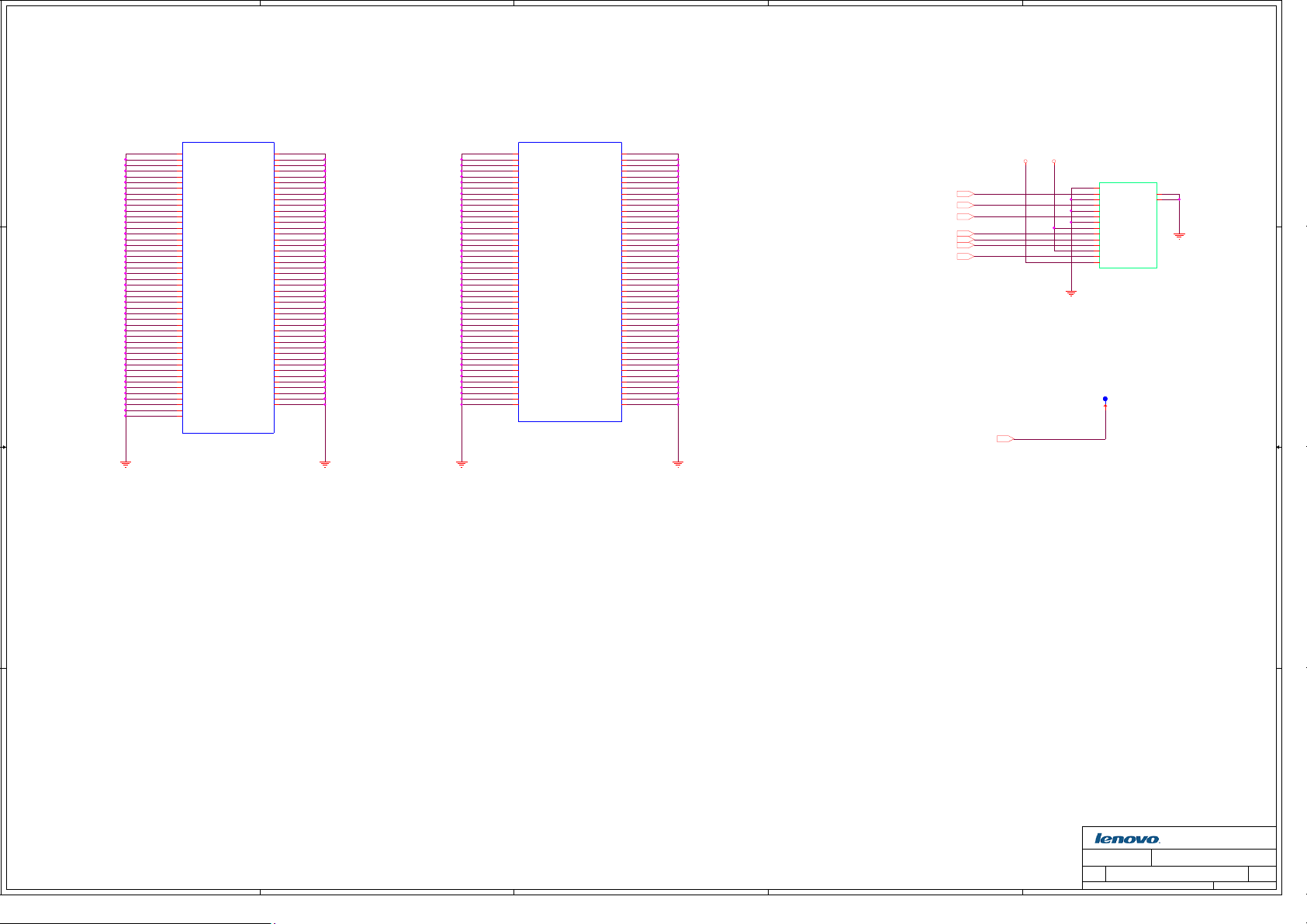

24.DDR3L SO DIMM CHANNEL-A

25.BLANK

26.DDR3L SO DIMM CHANNEL-B

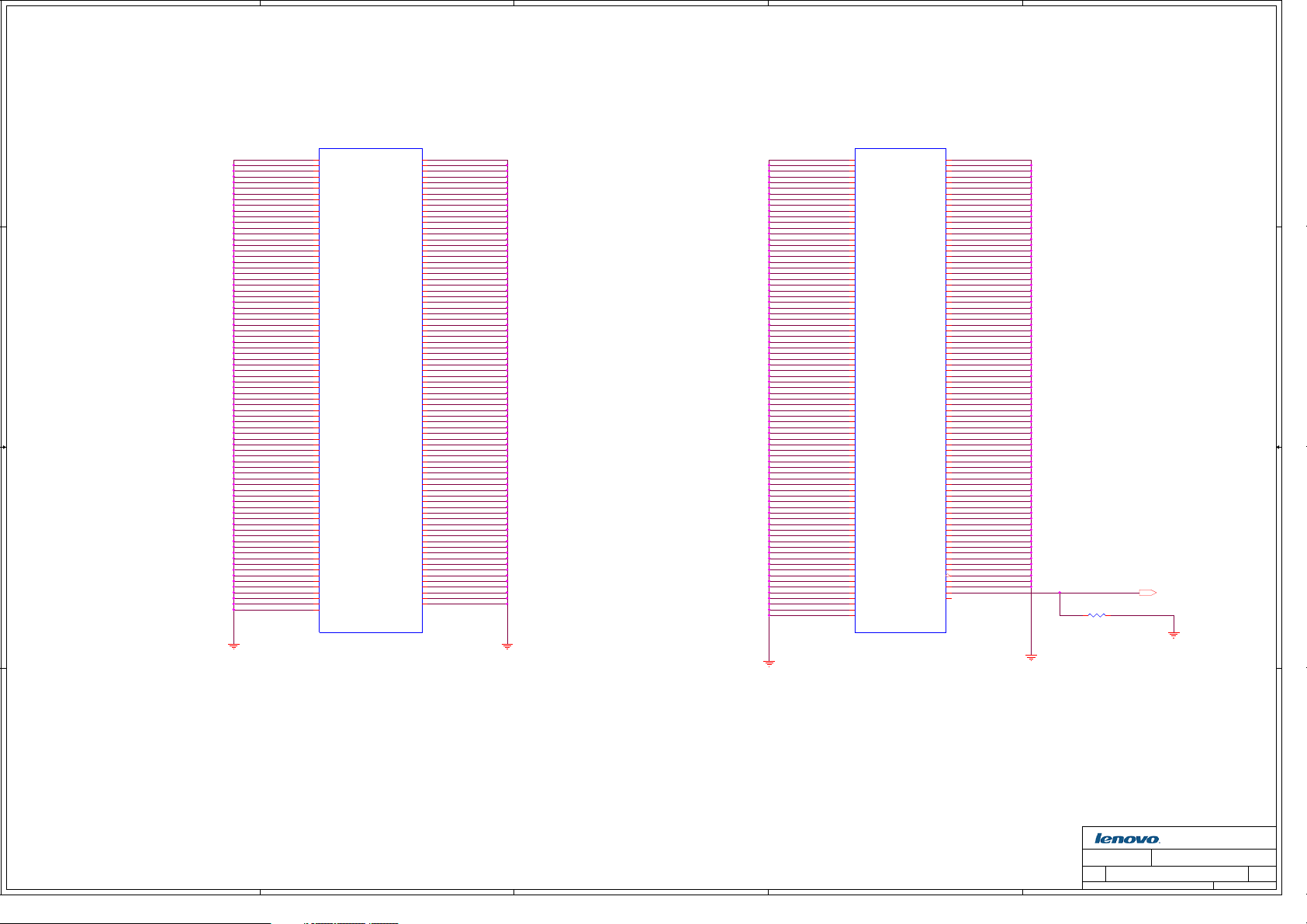

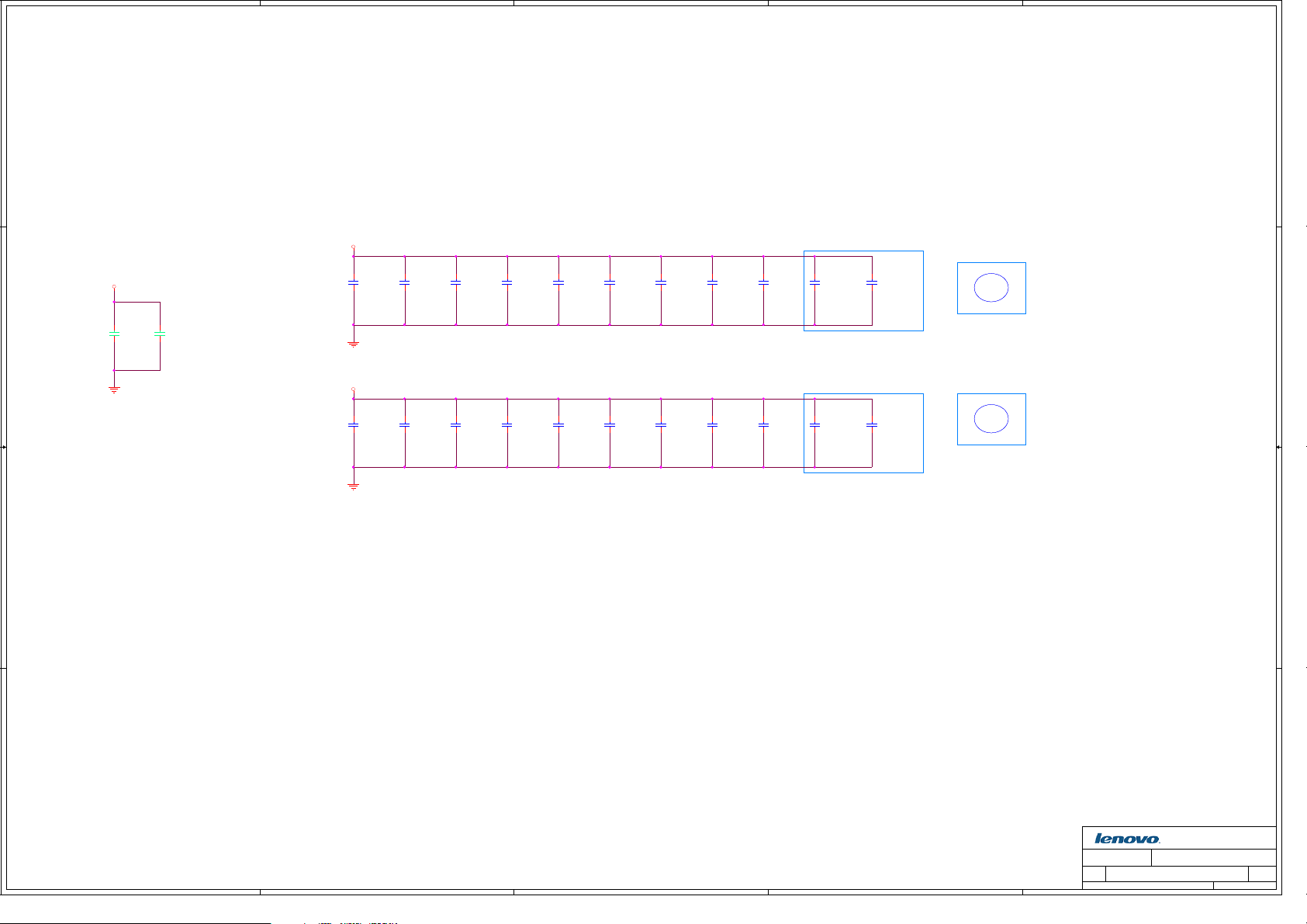

27.DDR3L DECOUPLING

28.N14M-GS(1/6) : PEG I/F

29.N14M-GS(2/6) : DIGITAL OUT I/F

30.N14M-GS(3/6) : VRAM I/F

31.N14M-GS(4/6) : GPIO

A A

32.N14M-GS(5/6) : POWER

33.N14M-GS(6/6) : GND

34.VRAM CHANNEL-A

35.BLANK

5

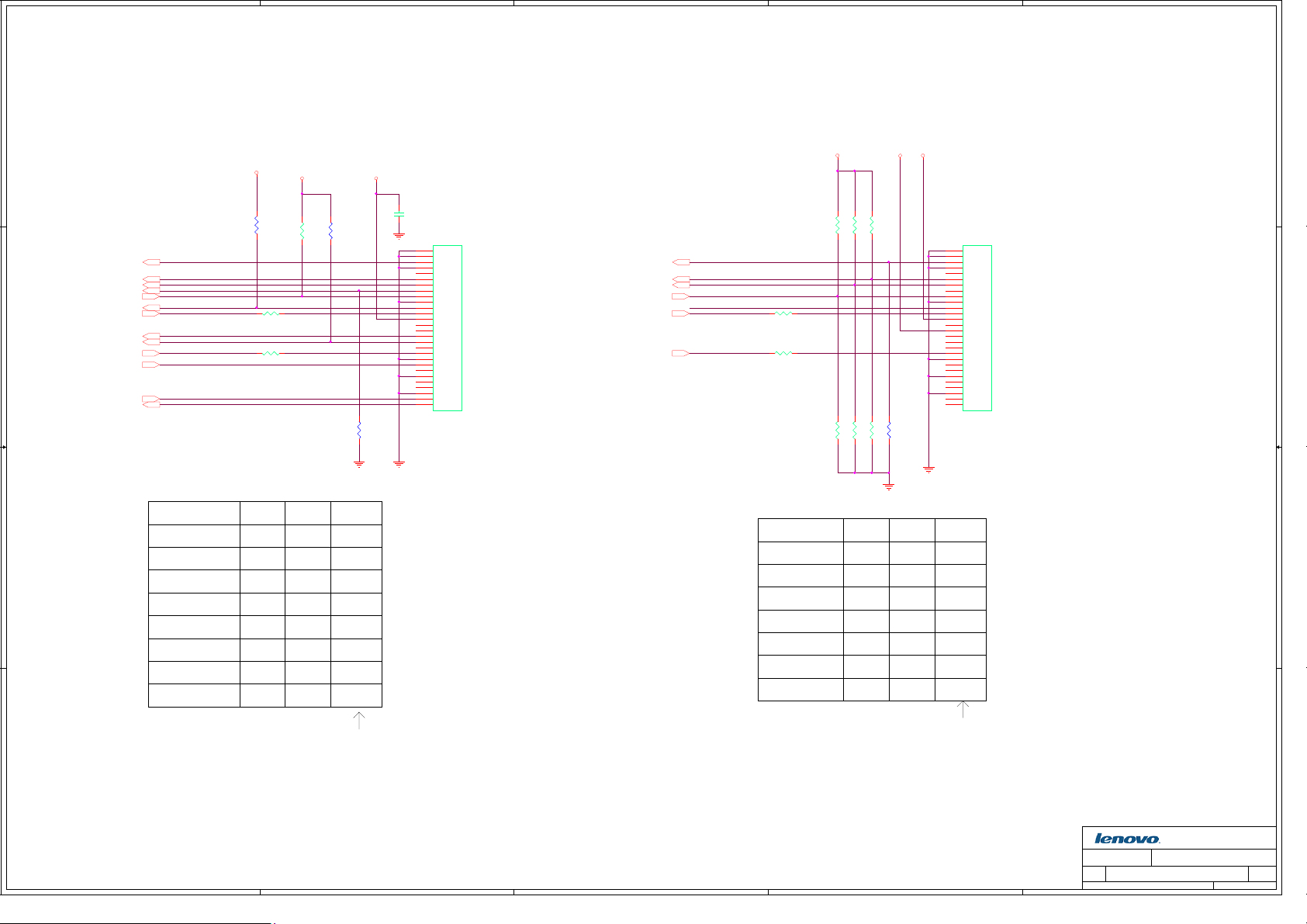

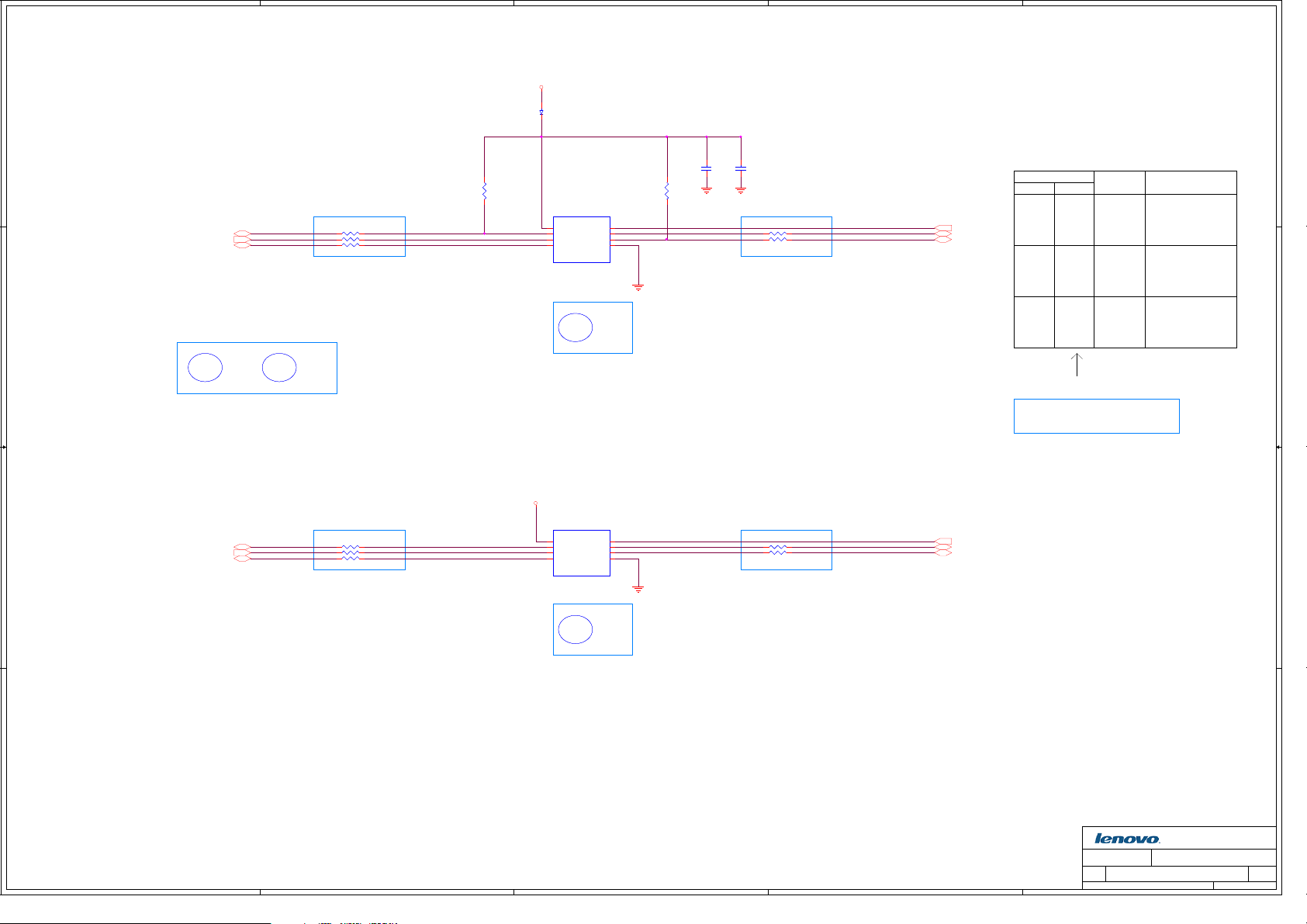

4

36.MEMORY TERMINATION

37.BLANK

38.LCD CONNECTOR

39.BLANK

40.EXT CRT INTERFACE

41.DISPLAY PORT CONNECTOR

42.BLANK

43.SATA HDD CONN

44.SATA BAY I/F CONN

45.USB CONNECTOR

46.AOU/USB POWER SWITCH

47.GBE LAN CLARKVILLE

48.GBE LAN SWITCH

49.RJ45 SUB CARD I/F

50.PCIE NGFF CARD SLOT

51.MEDIA CARD CONTROLLER

52.MEDIA CARD INTERFACE

53.SMART CARD/3rd NGFF I/F

54.AUDIO ALC3232

55.AUDIO CONNECTOR

56.AUDIO JACK SENSE

57.AUDIO EXT MIC I/F

58.AUDIO SPEAKER

59.AUDIO BEEP

60.DOCKING CONNECTOR

61.MEC1633L(1/3)

62.MEC1633L(2/3)

63.MEC1633L(3/3)

64.KEYBOARD CONNECTOR

65.CLICK PAD/NFC/FPR CONNECTOR

66.BLANK

67.FAN CONNECTOR

68.G-SENSOR

69.TPM

70.EEPROM/SMBUS SW

3

OAS1H-0

VER 1.01

Aug/08/2013

71.THINK ENGINE(1/2)

72.THINK ENGINE(2/2)

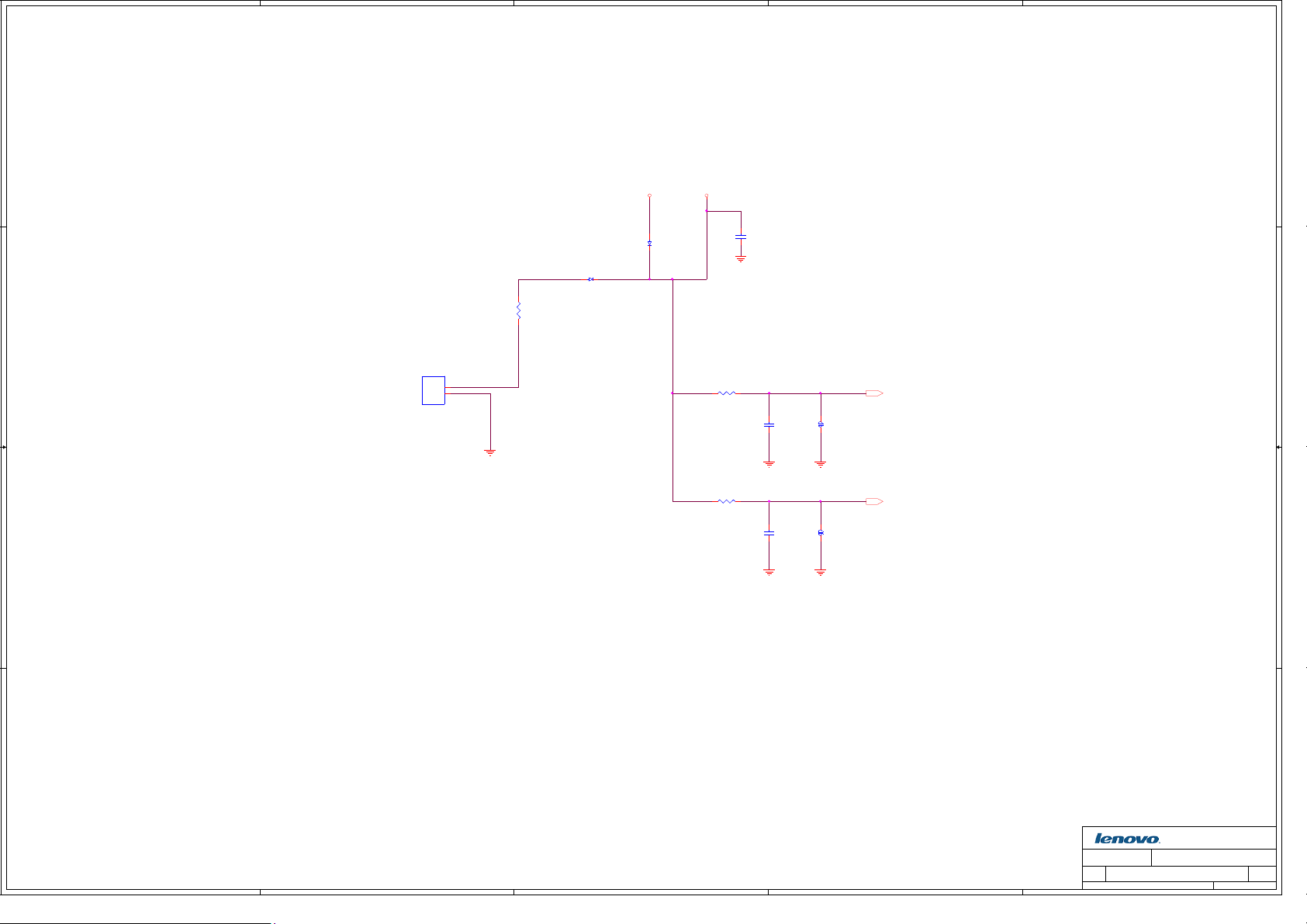

73.DC-IN

74.BATTERY INPUT

75.BATTERY CHARGER(BQ24760)

76.CHARGER SELECTOR

77.BATTERY MONITOR

78.DC/DC VCC5M/VCC3M (TPS51220A)

79.DC/DC VCCCPUCORE(TPS51631)

80.DC/DC VCCCPUCORE(CSD97374)

81.BLANK

82.VCCCPUCORE DECOUPLING

83.DC/DC VCCGFXCORE_D (TPS51219)

84.BLANK

85.DC/DC VCC1R05AMT(VT384B)

86.DC/DC VCC1R35A(VT387B)

87.DC/DC VCC0R675B(TPS51200)

88.DC/DC VCC1R5VIDEO(VT382B)

89.DC/DC VCC1R05VIDEO_PLL(TPS74801)

90.BLANK

91.BLANK

92.DC/DC VCC1R5B(BD3551)

93.LOAD SW PCH SUS

94.LOAD SW LAN

95.LOAD SW VIDEO

96.LOAD SW B

97.LOAD SW VCC5MUBAY

98.LOAD SW WWAN & WLAN

99.PTH FOR SCREW HOLES

2

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

TITLE PAGEOAS-1 SP ASSESS

TITLE PAGEOAS-1 SP ASSESS

TITLE PAGEOAS-1 SP ASSESS

1 99Monday, August 12, 2013

1 99Monday, August 12, 2013

1

1 99Monday, August 12, 2013

Rev :

Rev :

Rev :

1.01

1.01

1.01

5

4

3

2

1

EC HISTORY

Oasis-1 SP ASSESS (BASE LOGIC :NZM5H-0 VER 0.44 May/18/2012)

SDV stage

VER.0.01 05/29/2012 APPLIED OAS1_SP_EC001

VER.0.02 05/31/2012 APPLIED OAS1_SP_EC002

VER.0.03 06/05/2012 APPLIED OAS1_SP_EC003,004

VER.0.04 06/06/2012 APPLIED OAS1_SP_EC005

D D

VER.0.05 06/07/2012 APPLIED OAS1_SP_EC006-010

VER.0.06 06/08/2012 APPLIED OAS1_SP_EC011,012,014-016

VER.0.07 06/13/2012 APPLIED OAS1_SP_EC017-019

VER.0.08 06/14/2012 APPLIED OAS1_SP_EC020

VER.0.09 06/18/2012 APPLIED OAS1_SP_EC021-024

VER.0.10 06/20/2012 APPLIED OAS1_SP_EC025-027

VER.0.11 06/27/2012 APPLIED OAS1_SP_EC028-040,042

VER.0.12 06/28/2012 APPLIED OAS1_SP_EC043-055

VER.0.13 06/29/2012 APPLIED OAS1_SP_EC056,057

VER.0.14 07/02/2012 APPLIED OAS1_SP_EC058-062

VER.0.15 07/03/2012 APPLIED OAS1_SP_EC063,064

VER.0.16 07/04/2012 APPLIED OAS1_SP_EC065,066

VER.0.17 07/05/2012 APPLIED OAS1_SP_EC069-073,075,078,079

VER.0.18 07/06/2012 APPLIED OAS1_SP_EC067,068,074,076,077

VER.0.19 07/10/2012 APPLIED OAS1_SP_EC080,081

VER.0.20 07/12/2012 APPLIED OAS1_SP_EC082-087

VER.0.21 07/31/2012 APPLIED OA1_MB_SDV_EC001_0727

VER.0.22 08/03/2012 APPLIED OA1_MB_SDV_EC002_0803

VER.0.23 08/07/2012 APPLIED OA1_MB_SDV_EC003_0807

VER.0.24 08/10/2012 APPLIED OA1_MB_SDV_EC004_0810

C C

08/14/2012 APPLIED OA1_MB_SDV_EC005_0814

VER.0.25 08/15/2012 APPLIED OA1_MB_SDV_EC006_0815

VER.0.26 08/17/2012 APPLIED OA1_MB_SDV_EC007_0817

VER.0.27 08/23/2012 APPLIED OA1_MB_SDV_EC008_0823

VER.0.28 08/28/2012 APPLIED OA1_MB_SDV_EC009_0828

VER.0.29 08/29/2012 APPLIED OA1_MB_SDV_EC010_0829

VER.0.30 08/31/2012 APPLIED OA1_MB_SDV_EC011_0831

VER.0.31 09/04/2012 APPLIED OA1_MB_SDV_EC012_0904

VER.0.32 09/06/2012 APPLIED OA1_MB_SDV_EC013_0906

VER.0.33 09/10/2012 APPLIED OA1_MB_SDV_EC014_0910

09/11/2012 APPLIED OA1_MB_SDV_EC015_0911

VER.0.34 09/12/2012 APPLIED OA1_MB_SDV_EC016_0912

VER.0.35 09/14/2012 APPLIED OA1_MB_SDV_EC017_0914

VER.0.36 09/20/2012 APPLIED OA1_MB_SDV_EC018_0920

09/21/2012 APPLIED OA1_MB_SDV_EC019_0921

VER.0.37 09/24/2012 APPLIED OA1_MB_SDV_EC020_0924

VER.0.38 09/26/2012 APPLIED OA1_MB_SDV_EC021_0926

VER.0.39 09/28/2012 APPLIED OA1_MB_SDV_EC022_0928

VER.0.40 10/02/2012 APPLIED OA1_MB_SDV_EC023_1002

B B

VER.0.41 10/04/2012 APPLIED OA1_MB_SDV_EC024_1004

10/04/2012 APPLIED OA1_MB_SDV_EC025_1004a

10/05/2012 APPLIED OA1_MB_SDV_EC026_1005

VER.0.42 10/08/2012 APPLIED OA1_MB_SDV_EC027_1008

10/11/2012 APPLIED OA1_MB_SDV_EC028_1011

VER.0.43 10/16/2012 APPLIED OA1_MB_SDV_EC029_1015

VER.0.44 10/16/2012 APPLIED OA1_MB_SDV_EC030_1016

10/17/2012 APPLIED OA1_MB_SDV_EC031_1017

VER.0.45 10/18/2012 APPLIED OA1_MB_SDV_EC032_1018

VER.0.46 10/29/2012 APPLIED OA1_MB_SDV_EC033_1029

VER.0.47 11/02/2012 APPLIED OA1_MB_SDV_EC034_1102

MFVT stage

VER.1.01 11/22/2012 APPLIED OA1_MB_MFVT_EC001_1120

VER.1.02 12/03/2012 APPLIED OA1_MB_MFVT_EC002_1203

12/05/2012 APPLIED OA1_MB_MFVT_EC003_1205

VER.1.03 12/10/2012 APPLIED OA1_MB_MFVT_EC004_1210

FVT stage

VER.0.01 12/19/2012 APPLIED OA1_MB_FVT_EC001_1219

12/21/2012 APPLIED OA1_MB_FVT_EC002_1221

VER.0.02 12/21/2012 APPLIED OA1_MB_FVT_EC003_1221_R1

12/25/2012 APPLIED OA1_MB_FVT_EC004_1225

VER.0.03 12/26/2012 APPLIED OA1_MB_FVT_EC005_1226

VER.0.04 12/27/2012 APPLIED OA1_MB_FVT_EC006_1227

VER.0.05 12/28/2012 APPLIED OA1_MB_FVT_EC007_1228

VER.0.06 01/03/2012 APPLIED ECR_1R05VIDEO_PLL discharge.ppt

RF_EC_FVT_0103-oscar.ppt

VER.1.00 01/04/2012 APPLIED FVT gerber out

VER.1.01 01/08/2013 APPLIED OA1_MB_FVT_EC008_0108

OA1_MB_FVT_EC008_0108_R1

VER.1.02 01/17/2013 APPLIED OA1_MB_FVT_EC009_0117

SIT stage

VER.0.01 02/06/2013 APPLIED OA1_MB_SIT_EC001_0206

VER.0.02 02/18/2013 APPLIED OA1_MB_SIT_EC002_0218

VER.0.03 02/25/2013 APPLIED OA1_MB_SIT_EC003_0225

VER.0.04 03/07/2013 APPLIED OA1_MB_SIT_EC004_0307

VER.0.05 03/08/2013 APPLIED OA1_MB_SIT_EC005_0308

VER.0.06 03/11/2013 APPLIED OA1_MB_SIT_EC006_0311

03/12/2013 APPLIED OA1_MB_SIT_EC007_0312

VER.0.07 03/13/2013 APPLIED OA1_MB_SIT_EC008_0313

03/14/2013 APPLIED RF_EC_SIT_0305-Tony.pptx

Oasis EMC solution list on FVT stage 20130204

VER.0.08 03/14/2013 APPLIED OA1_MB_SIT_EC009_0314

VER.1.00 03/19/2013 APPLIED SIT gerber out

VER.1.01 03/25/2013 APPLIED OA1_MB_SIT_EC010_0325

VER.1.02 04/02/2013 Applied ECR_20130416

SIT-v stage

VER.0.01 04/19/2013 APPLIED OA1_MB_SITV_EC001_0419

VER.0.02 04/25/2013 APPLIED OA1_MB_SITV_EC002_0425

VER.1.00 05/02/2013 Applied ECR_20130502

VER.1.01 05/09/2013 APPLIED OA1_MB_SITV_EC003_05/09

05/10/2013 APPLIED OA1_MB_SITV_EC004_05/10

VER.1.02 05/20/2013 APPLIED ECR_20130520

06/14/2013 APPLIED ECR_20130614

SVT stage

VER.0.01 06/12/2013 APPLIED OA1_MB_SVT_EC001_0612

VER.0.02 06/18/2013 APPLIED OA1_MB_SVT_EC002_0618

06/18/2013 APPLIED OA1_MB_SVT_EC003_0618

VER.0.03 06/24/2013 APPLIED OA1_MB_SVT_EC004_0624

06/25/2013 APPLIED OA1_MB_SVT_EC005_0625

VER.1.00 06/26/2013 APPLIED OA1_MB_SVT_EC006_0626

06/26/2013 APPLIED OA1_MB_SVT_EC007_0626

VER.1.01 06/28/2013 APPLIED OA1_MB_SVT_EC008_0628

VER.1.02 07/11/2013 APPLIED OA1_MB_SVT_EC009_0711

SOVP stage

VER.1.00 08/06/2013 APPLIED ECR_20130806

VER.1.01 08/08/2013 APPLIED ECR_20130808

General BOM Structure

@ : No ASM for all model

UMA@ : ASM for UMA model, No ASM for SWG model

SWG@ : No ASM for UMA model, ASM for SWG model

CONN_ASM@ : ASM connector

CONN_NOASM@ : NO ASM connector

PLM@ : For PCB material

VRAM BOM Structure

M1G@ : ASM for SWG model with Micron 1G VRAM.

S1G@ : ASM for SWG model with Samsung 1G VRAM.

SPI ROM BOM Structure

SPI_1ST@ : ASM for Winbond SPI ROM.

SPI_2ND@ : ASM for Macronix SPI ROM.

BOM option

UMA :

PLM@ / UMA@ / CONN_ASM@

SWG + Samsung 1G VRAM :

PLM@ / SWG@ / CONN_ASM@ / X76_S1G@

SWG + Micron 1G VRAM :

PLM@ / SWG@ / CONN_ASM@ / X76_M1G@

ZZZ1

ZZZ1

NM-A131_PCB

NM-A131_PCB

DAZ0SQ00100

DAZ0SQ00100

PLM@

PLM@

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

EC HISTORYOAS-1 SP ASSESS

EC HISTORYOAS-1 SP ASSESS

EC HISTORYOAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

2 99Monday, August 12, 2013

2 99Monday, August 12, 2013

2 99Monday, August 12, 2013

5

D D

4

3

2

1

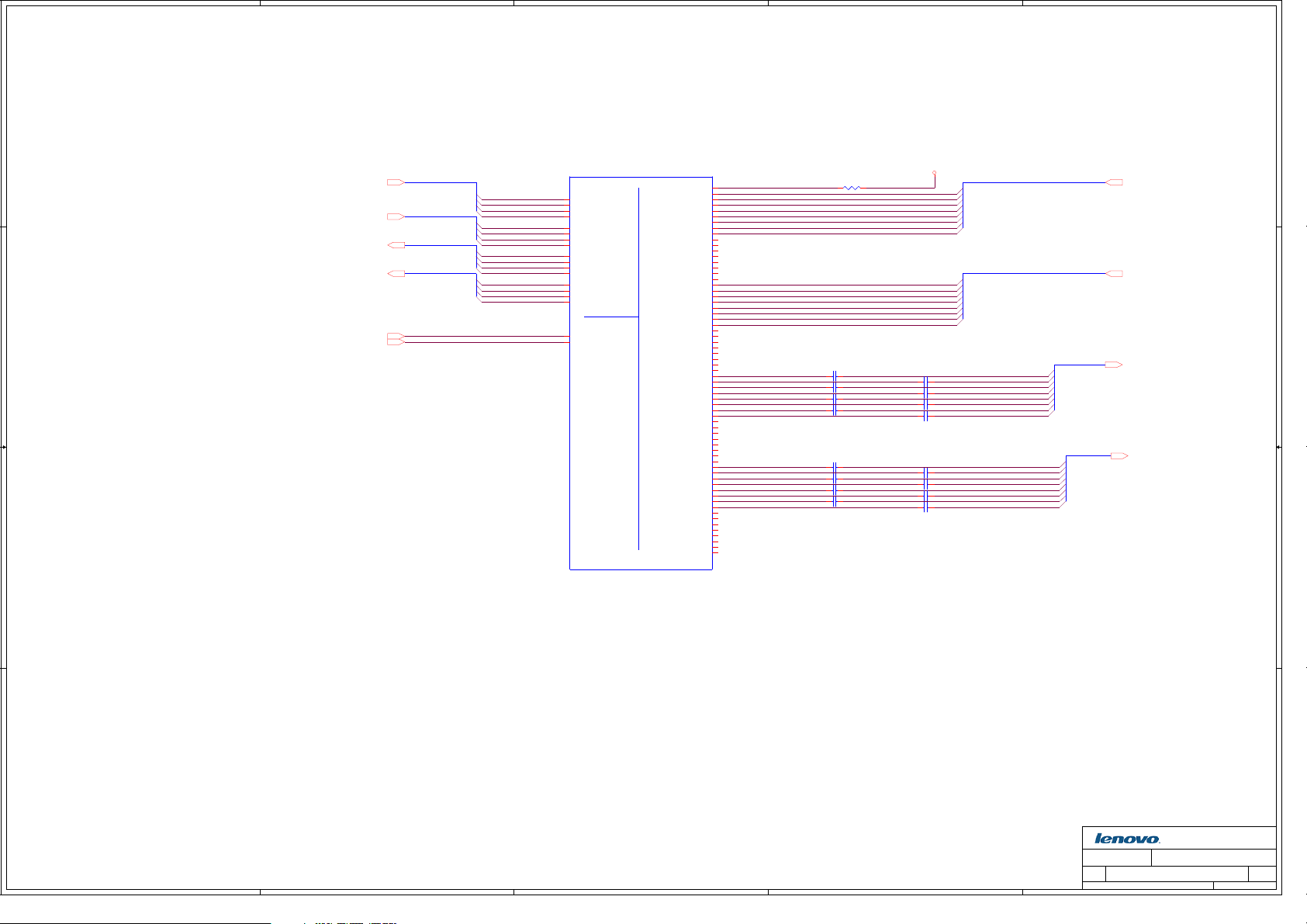

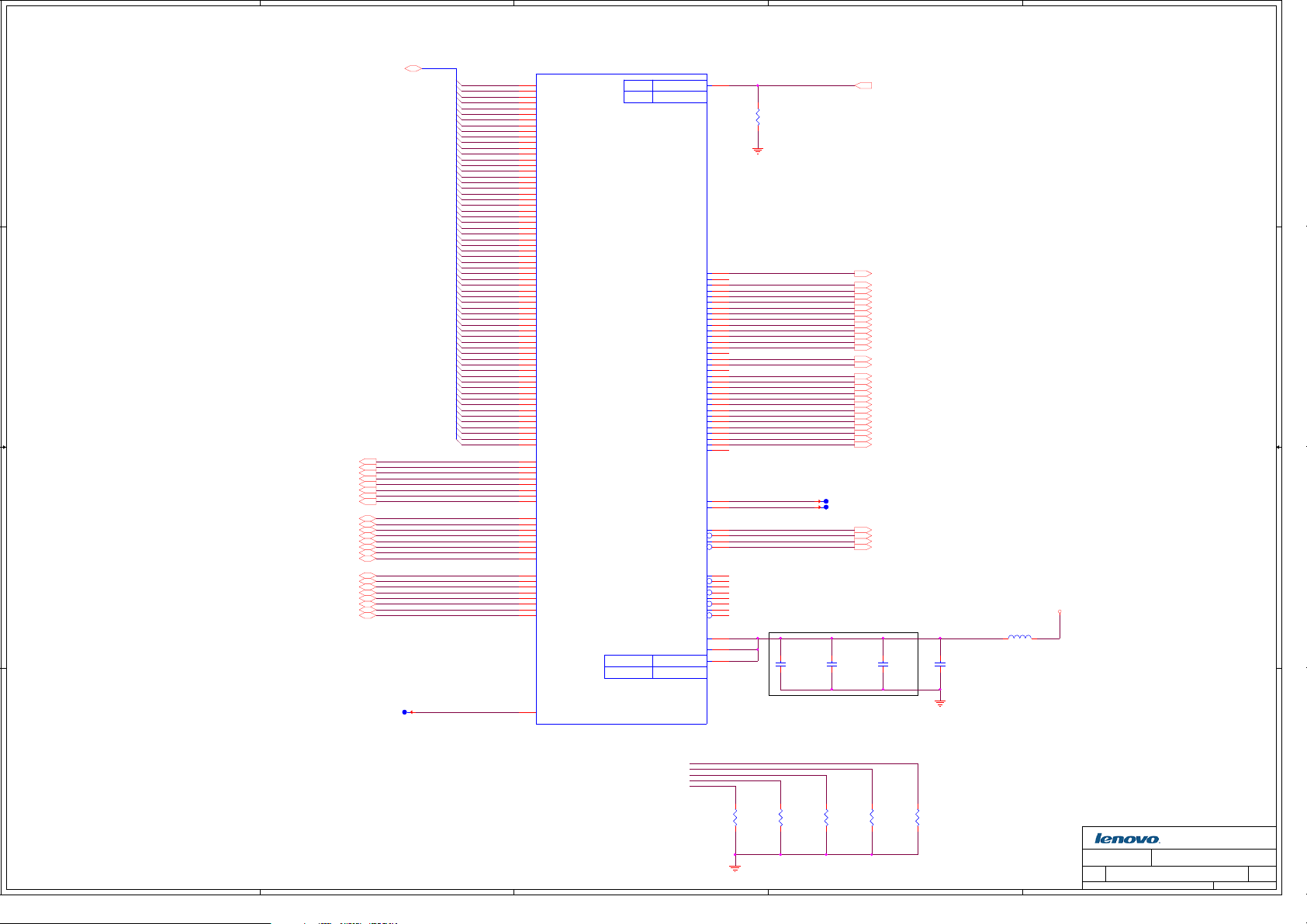

Haswell rPGA EDS

JCPU1A

DMI_TXN[3:0]13

DMI_TXP[3:0]13

DMI_RXN[3:0]13

DMI_RXP[3:0]13

C C

B B

FDI_CSYNC13

FDI_INT13

FDI_CSYNC

FDI_INT

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

JCPU1A

D21

DMI_RXN_0

C21

DMI_RXN_1

B21

DMI_RXN_2

A21

DMI_RXN_3

D20

DMI_RXP_0

C20

DMI_RXP_1

B20

DMI_RXP_2

A20

DMI_RXP_3

D18

DMI_TXN_0

C17

DMI_TXN_1

B17

DMI_TXN_2

A17

DMI_TXN_3

D17

DMI_TXP_0

C18

DMI_TXP_1

B18

DMI_TXP_2

A18

DMI_TXP_3

H29

FDI_CSYNC

J29

DISP_INT

LOTES_AZIF0012 P002B_INTELHASWEL

LOTES_AZIF0012 P002B_INTELHASWEL

CONN_ASM@

CONN_ASM@

Haswell rPGA EDS

DMI FDI

DMI FDI

1 OF 9

1 OF 9

E23

PEG_RCOM P

M29

PEG_RXN_ 0

K28

PEG_RXN_ 1

M31

PEG_RXN_ 2

L30

PEG_RXN_ 3

M33

PEG_RXN_ 4

L32

PEG_RXN_ 5

M35

PEG_RXN_ 6

PEG_RXN_ 7

PEG_RXN_ 8

PEG_RXN_ 9

PEG_RXN_ 10

PEG_RXN_ 11

PEG_RXN_ 12

PEG_RXN_ 13

PEG_RXN_ 14

PEG_RXN_ 15

PEG_RXP _0

PEG_RXP _1

PEG_RXP _2

PEG_RXP _3

PEG_RXP _4

PEG_RXP _5

PEG_RXP _6

PEG_RXP _7

PEG_RXP _8

PEG_RXP _9

PEG_RXP _10

PEG_RXP _11

PEG_RXP _12

PEG_RXP _13

PEG_RXP _14

PEG_RXP _15

PEG_TXN_0

PEG_TXN_1

PEG_TXN_2

PEG_TXN_3

PEG_TXN_4

PEG_TXN_5

PEG_TXN_6

PEG_TXN_7

PEG_TXN_8

PEG_TXN_9

PEG_TXN_1 0

PEG_TXN_1 1

PEG_TXN_1 2

PEG_TXN_1 3

PEG_TXN_1 4

PEG_TXN_1 5

PEG_TXP_ 0

PEG_TXP_ 1

PEG_TXP_ 2

PEG_TXP_ 3

PEG_TXP_ 4

PEG_TXP_ 5

PEG_TXP_ 6

PEG_TXP_ 7

PEG_TXP_ 8

PEG_TXP_ 9

PEG_TXP_ 10

PEG_TXP_ 11

PEG_TXP_ 12

PEG_TXP_ 13

PEG_TXP_ 14

PEG_TXP_ 15

L34

E29

D28

E31

D30

E35

D34

E33

E32

L29

L28

L31

K30

L33

K32

L35

K34

F29

E28

F31

E30

F35

E34

F33

D32

H35

H34

J33

H32

J31

G30

C33

B32

B31

A30

B29

A28

B27

A26

B25

A24

J35

G34

H33

G32

H31

H30

B33

A32

C31

B30

C29

B28

C27

B26

C25

B24

PEG

PEG

PEG_TXN7_C

PEG_TXN6_C

PEG_TXN5_C

PEG_TXN4_C

PEG_TXN3_C

PEG_TXN2_C

PEG_TXN1_C

PEG_TXN0_C

PEG_TXP7_C

PEG_TXP6_C

PEG_TXP5_C

PEG_TXP4_C

PEG_TXP3_C

PEG_TXP2_C

PEG_TXP1_C

PEG_TXP0_C

PEG_COMP

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_RXN4

PEG_RXN3

PEG_RXN2

PEG_RXN1

PEG_RXN0

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP4

PEG_RXP3

PEG_RXP2

PEG_RXP1

PEG_RXP0

1 2

R57 24.9_0201_1%R57 24.9_0201_1%

1 2

C649 0.22U_0201_6.3V6K

C649 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C689 0.22U_0201_6.3V6K

C689 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C789 0.22U_0201_6.3V6K

C789 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C581 0.22U_0201_6.3V6K

C581 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C684 0.22U_0201_6.3V6K

C684 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C779 0.22U_0201_6.3V6K

C779 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C330 0.22U_0201_6.3V6K

C330 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C665 0.22U_0201_6.3V6K

C665 0.22U_0201_6.3V6K

SWG@

SWG@

VCCCPUIO_A

1 2

C790 0.22U_0201_6.3V6K

C790 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C635 0.22U_0201_6.3V6K

C635 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C688 0.22U_0201_6.3V6K

C688 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C783 0.22U_0201_6.3V6K

C783 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C504 0.22U_0201_6.3V6K

C504 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C668 0.22U_0201_6.3V6K

C668 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C740 0.22U_0201_6.3V6K

C740 0.22U_0201_6.3V6K

SWG@

SWG@

1 2

C328 0.22U_0201_6.3V6K

C328 0.22U_0201_6.3V6K

SWG@

SWG@

PEG_TXN7

PEG_TXN6

PEG_TXN5

PEG_TXN4

PEG_TXN3

PEG_TXN2

PEG_TXN1

PEG_TXN0

PEG_TXP7

PEG_TXP6

PEG_TXP5

PEG_TXP4

PEG_TXP3

PEG_TXP2

PEG_TXP1

PEG_TXP0

PEG_RXN[7:0] 28

PEG_RXP[7:0] 28

PEG_TXN[7:0] 28

PEG_TXP[7:0] 28

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

CPU(1/8) : DMI/FDI/PEGOAS-1 SP ASSESS

CPU(1/8) : DMI/FDI/PEGOAS-1 SP ASSESS

CPU(1/8) : DMI/FDI/PEGOAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

3 99Monday, August 12, 2013

3 99Monday, August 12, 2013

3 99Monday, August 12, 2013

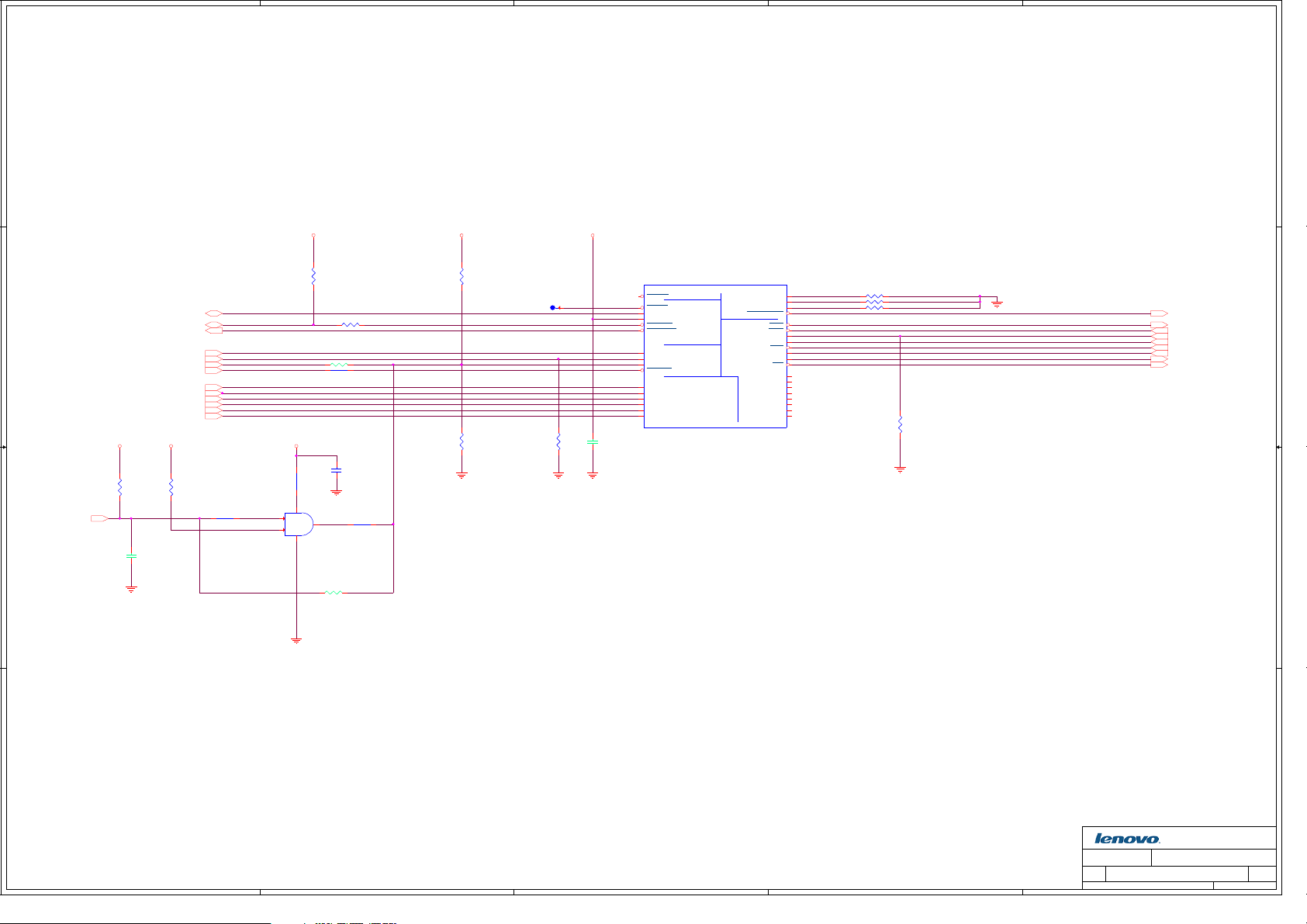

5

D D

4

3

2

1

VCCCPUIO VCCCPUIO_PCH

R64

R64

62_0201_5%

62_0201_5%

1 2

1 2

PECI

-PROCHOT

-THERMTRIP

PM_SYNC

CPUPWRGD

DRAMPWRG

-EDP_NS_CLK_135M

EDP_NS_CLK_135M

-EDP_SS_CLK_135M

EDP_SS_CLK_135M

-CPU_CLK_100M

CPU_CLK_100M

R85 56_0201_5%R85 56_0201_5%

R9243 0_0201_5%@R9243 0_0201_5%@

R8969 0_0201_5%R8969 0_0201_5%

VCC3MVCC3M

R9280

R9280

0_0402_5%

0_0402_5%

1 2

5

1

P

B

4

Y

2

A

G

U112

U112

3

MC74VHC1G09DFT2G_SC70-5

MC74VHC1G09DFT2G_SC70-5

1 2

R9249 0_0201_5%

R9249 0_0201_5%

1 2

1 2

1 2

C1901

C1901

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

@

@

R9244

R9244

1 2

0_0201_5%

0_0201_5%

PECI62

-PROCHOT62,75,79

C C

-THERMTRIP15

PM_SYNC13

CPUPWRGD15,21

DRAMPWRG13

-PLTRST_PROC15

-EDP_NS_CLK_135M17

EDP_NS_CLK_135M17

-EDP_SS_CLK_135M17

EDP_SS_CLK_135M17

-CPU_CLK_100M17

CPU_CLK_100M17

VCC3M

R9241

2

C8484

C8484

@

@

0.01U_0201_6.3V7K

0.01U_0201_6.3V7K

1

R9241

100K_0201_5%

100K_0201_5%

1 2

R9286 0_0201_5%R9286 0_0201_5%

R9240

R9240

100K_0201_5%

100K_0201_5%

1 2

DDR_VR_PWRGD86

B B

VCC1R35A

R12

R12

1K_0201_5%

1K_0201_5%

1 2

TP936TP936

-CPURST-PLTRST_PROC

R9239

R9239

2K_0201_5%

2K_0201_5%

1 2

R17

R17

1 2

10K_0201_5%

10K_0201_5%

AP32

AN32

AR27

AK31

AM30

AM35

AT28

AL34

AC10

AT26

G28

H28

F27

E27

D26

E26

@

@

2

1

C1900

C1900

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

Haswell rPGA EDS

Haswell rPGA EDS

JCPU1B

JCPU1B

MISC

MISC

SKTOCC

CATERR

PECI

FC_AK31

PROCHOT

THERMTRIP

PM_SYNC

PWRGOO D

SM_DRAMPW ROK

PLTRSTIN

DPLL_REF _CLKN

DPLL_REF _CLKP

SSC_DPLL _REF_CLKN

SSC_DPLL _REF_CLKP

BCLKN

BCLKP

LOTES_AZIF0012P002B_INTELHASWEL

LOTES_AZIF0012P002B_INTELHASWEL

CONN_ASM@

CONN_ASM@

THERMAL

THERMAL

PWR

PWR

2 OF 9

2 OF 9

DDR3

DDR3

CLOCK

CLOCK

SM_RCOMP_ 0

SM_RCOMP_ 1

SM_RCOMP_ 2

SM_DRAMRST

JTAG

JTAG

BPM_N_0

BPM_N_1

BPM_N_2

BPM_N_3

BPM_N_4

BPM_N_5

BPM_N_6

BPM_N_7

PRDY

PREQ

TRST

AP3

AR3

AP2

AN3

AR29

AT29

AM34

TCK

AN33

TMS

AM33

AM31

TDI

AL33

TDO

AP33

DBR

AR30

AN31

AN29

AP31

AP30

AN28

AP29

AP28

1 2

R7 100_0201_1%R7 100_0201_1%

1 2

R84 75_0201_1%R84 75_0201_1%

1 2

R576 100_0201_1%R576 100_0201_1%

R2

51_0201_5%R251_0201_5%

1 2

-XDP_PRDY

-XDP_PREQ

XDP_TCK

XDP_TMS

-XDP_TRST

XDP_TDI

XDP_TDO

-XDP_DBR

-DRAMRST 24,26

-XDP_PRDY 21

-XDP_PREQ 21

XDP_TCK 21

XDP_TMS 21

-XDP_TRST 21

XDP_TDI 21

XDP_TDO 21

-XDP_DBR 13,20,21

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

CPU(2/8) : MISC/JTAG/CLKOAS-1 SP ASSESS

CPU(2/8) : MISC/JTAG/CLKOAS-1 SP ASSESS

CPU(2/8) : MISC/JTAG/CLKOAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

4 99Monday, August 12, 2013

4 99Monday, August 12, 2013

4 99Monday, August 12, 2013

5

D D

M_A_DQ[63:0]24

C C

B B

DDR3_VREF_CA_M326

DDR3_VREF_DQ_SA_M324

DDR3_VREF_DQ_SB_M324

4

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

JCPU1C

JCPU1C

AR15

SA_DQ_0

AT14

SA_DQ_1

AM14

SA_DQ_2

AN14

SA_DQ_3

AT15

SA_DQ_4

AR14

SA_DQ_5

AN15

SA_DQ_6

AM15

SA_DQ_7

AM9

SA_DQ_8

AN9

SA_DQ_9

AM8

SA_DQ_1 0

AN8

SA_DQ_1 1

AR9

SA_DQ_1 2

AT9

SA_DQ_1 3

AR8

SA_DQ_1 4

AT8

SA_DQ_1 5

AJ9

SA_DQ_1 6

AK9

SA_DQ_1 7

AJ6

SA_DQ_1 8

AK6

SA_DQ_1 9

AJ10

SA_DQ_2 0

AK10

SA_DQ_2 1

AJ7

SA_DQ_2 2

AK7

SA_DQ_2 3

AF4

SA_DQ_2 4

AF5

SA_DQ_2 5

AF1

SA_DQ_2 6

AF2

SA_DQ_2 7

AG4

SA_DQ_2 8

AG5

SA_DQ_2 9

AG1

SA_DQ_3 0

AG2

SA_DQ_3 1

J1

SA_DQ_3 2

J2

SA_DQ_3 3

J5

SA_DQ_3 4

H5

SA_DQ_3 5

H2

SA_DQ_3 6

H1

SA_DQ_3 7

J4

SA_DQ_3 8

H4

SA_DQ_3 9

F2

SA_DQ_4 0

F1

SA_DQ_4 1

D2

SA_DQ_4 2

D3

SA_DQ_4 3

D1

SA_DQ_4 4

F3

SA_DQ_4 5

C3

SA_DQ_4 6

B3

SA_DQ_4 7

B5

SA_DQ_4 8

E6

SA_DQ_4 9

A5

SA_DQ_5 0

D6

SA_DQ_5 1

D5

SA_DQ_5 2

E5

SA_DQ_5 3

B6

SA_DQ_5 4

A6

SA_DQ_5 5

E12

SA_DQ_5 6

D12

SA_DQ_5 7

B11

SA_DQ_5 8

A11

SA_DQ_5 9

E11

SA_DQ_6 0

D11

SA_DQ_6 1

B12

SA_DQ_6 2

A12

SA_DQ_6 3

AM3

SM_VREF

F16

SA_DIMM_V REFDQ

F13

SB_DIMM_V REFDQ

3 OF 9

3 OF 9

LOTES_AZIF0012P002B_INTELHASWEL

LOTES_AZIF0012P002B_INTELHASWEL

CONN_ASM@

CONN_ASM@

Haswell rPGA EDS

Haswell rPGA EDS

RSVD_0

SA_CK_N_ 0

SA_CK_P _0

SA_CKE_ 0

SA_CK_N_ 1

SA_CK_P _1

SA_CKE_ 1

SA_CK_N_ 2

SA_CK_P _2

SA_CKE_ 2

SA_CK_N_ 3

SA_CK_P _3

SA_CKE_ 3

SA_CS_N_ 0

SA_CS_N_ 1

SA_CS_N_ 2

SA_CS_N_ 3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_BS_0

SA_BS_1

SA_BS_2

VSS_0

SA_RAS

SA_WE

SA_CAS

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_1 0

SA_MA_1 1

SA_MA_1 2

SA_MA_1 3

SA_MA_1 4

SA_MA_1 5

SA_DQS_ N_0

SA_DQS_ N_1

SA_DQS_ N_2

SA_DQS_ N_3

SA_DQS_ N_4

SA_DQS_ N_5

SA_DQS_ N_6

SA_DQS_ N_7

SA_DQS_ P_0

SA_DQS_ P_1

SA_DQS_ P_2

SA_DQS_ P_3

SA_DQS_ P_4

SA_DQS_ P_5

SA_DQS_ P_6

SA_DQS_ P_7

3

AC7

U4

V4

AD9

U3

V3

AC9

U2

V2

AD8

U1

V1

AC8

M7

L9

M9

M10

M8

L7

L8

L10

V5

U5

AD1

V10

U6

U7

U8

V8

AC6

V9

U9

AC5

AC4

AD6

AC3

AD5

AC2

V6

AC1

AD4

V7

AD3

AD2

AP15

AP8

AJ8

AF3

J3

E2

C5

C11

AP14

AP9

AK8

AG3

H3

E3

C6

C12

-M_A_DDRCLK0_800M

M_A_DDRCLK0_800M

M_A_CKE0

-M_A_DDRCLK1_800M

M_A_DDRCLK1_800M

M_A_CKE1

-M_A_CS0

-M_A_CS1

M_A_ODT0

M_A_ODT1

M_A_BS0

M_A_BS1

M_A_BS2

-M_A_RAS

-M_A_WE

-M_A_CAS

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

-M_A_DQS0

-M_A_DQS1

-M_A_DQS2

-M_A_DQS3

-M_A_DQS4

-M_A_DQS5

-M_A_DQS6

-M_A_DQS7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

-M_A_DDRCLK0_800M 24

M_A_DDRCLK0_800M 24

M_A_CKE0 24

-M_A_DDRCLK1_800M 24

M_A_DDRCLK1_800M 24

M_A_CKE1 24

-M_A_CS0 24

-M_A_CS1 24

M_A_ODT0 24

M_A_ODT1 24

M_A_BS0 24

M_A_BS1 24

M_A_BS2 24

-M_A_RAS 24

-M_A_WE 24

-M_A_CAS 24

2

M_A_A[15:0] 24

-M_A_DQS[7:0] 24

M_A_DQS[7:0] 24

1

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

CPU(3/8) : DDR3L CHANNEL- AOAS-1 SP ASSESS

CPU(3/8) : DDR3L CHANNEL- AOAS-1 SP ASSESS

CPU(3/8) : DDR3L CHANNEL- AOAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

5 99Monday, August 12, 2013

5 99Monday, August 12, 2013

5 99Monday, August 12, 2013

5

D D

M_B_DQ[63:0]26

C C

B B

4

Haswell rPGA EDS

Haswell rPGA EDS

JCPU1D

JCPU1D

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AR18

SB_DQ_0

AT18

SB_DQ_1

AM17

SB_DQ_2

AM18

SB_DQ_3

AR17

SB_DQ_4

AT17

SB_DQ_5

AN17

SB_DQ_6

AN18

SB_DQ_7

AT12

SB_DQ_8

AR12

SB_DQ_9

AN12

SB_DQ_1 0

AM11

SB_DQ_1 1

AT11

SB_DQ_1 2

AR11

SB_DQ_1 3

AM12

SB_DQ_1 4

AN11

SB_DQ_1 5

AR5

SB_DQ_1 6

AR6

SB_DQ_1 7

AM5

SB_DQ_1 8

AM6

SB_DQ_1 9

AT5

SB_DQ_2 0

AT6

SB_DQ_2 1

AN5

SB_DQ_2 2

AN6

SB_DQ_2 3

AJ4

SB_DQ_2 4

AK4

SB_DQ_2 5

AJ1

SB_DQ_2 6

AJ2

SB_DQ_2 7

AM1

SB_DQ_2 8

AN1

SB_DQ_2 9

AK2

SB_DQ_3 0

AK1

SB_DQ_3 1

L2

SB_DQ_3 2

M2

SB_DQ_3 3

L4

SB_DQ_3 4

M4

SB_DQ_3 5

L1

SB_DQ_3 6

M1

SB_DQ_3 7

L5

SB_DQ_3 8

M5

SB_DQ_3 9

G7

SB_DQ_4 0

J8

SB_DQ_4 1

G8

SB_DQ_4 2

G9

SB_DQ_4 3

J7

SB_DQ_4 4

J9

SB_DQ_4 5

G10

SB_DQ_4 6

J10

SB_DQ_4 7

A8

SB_DQ_4 8

B8

SB_DQ_4 9

A9

SB_DQ_5 0

B9

SB_DQ_5 1

D8

SB_DQ_5 2

E8

SB_DQ_5 3

D9

SB_DQ_5 4

E9

SB_DQ_5 5

E15

SB_DQ_5 6

D15

SB_DQ_5 7

A15

SB_DQ_5 8

B15

SB_DQ_5 9

E14

SB_DQ_6 0

D14

SB_DQ_6 1

A14

SB_DQ_6 2

B14

SB_DQ_6 3

4 OF 9

4 OF 9

LOTES_AZIF0012P002B_INTELHASWEL

LOTES_AZIF0012P002B_INTELHASWEL

CONN_ASM@

CONN_ASM@

3

RSVD_1

SB_CKN0

SB_CK0

SB_CKE_ 0

SB_CKN1

SB_CK1

SB_CKE_ 1

SB_CKN2

SB_CK2

SB_CKE_ 2

SB_CKN3

SB_CK3

SB_CKE_ 3

SB_CS_N_ 0

SB_CS_N_ 1

SB_CS_N_ 2

SB_CS_N_ 3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_BS_0

SB_BS_1

SB_BS_2

VSS_1

SB_RAS

SB_WE

SB_CAS

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_1 0

SB_MA_1 1

SB_MA_1 2

SB_MA_1 3

SB_MA_1 4

SB_MA_1 5

SB_DQS_ N_0

SB_DQS_ N_1

SB_DQS_ N_2

SB_DQS_ N_3

SB_DQS_ N_4

SB_DQS_ N_5

SB_DQS_ N_6

SB_DQS_ N_7

SB_DQS_ P_0

SB_DQS_ P_1

SB_DQS_ P_2

SB_DQS_ P_3

SB_DQS_ P_4

SB_DQS_ P_5

SB_DQS_ P_6

SB_DQS_ P_7

AG8

Y4

AA4

AF10

Y3

AA3

AG10

Y2

AA2

AG9

Y1

AA1

AF9

P4

R2

P3

P1

R4

R3

R1

P2

R7

P8

AA9

R10

R6

P6

P7

R8

Y5

Y10

AA5

Y7

AA6

Y6

AA7

Y8

AA10

R9

Y9

AF7

P9

AA8

AG7

AP18

AP11

AP5

AJ3

L3

H9

C8

C14

AP17

AP12

AP6

AK3

M3

H8

C9

C15

-M_B_DDRCLK0_800M

M_B_DDRCLK0_800M

M_B_CKE0

-M_B_DDRCLK1_800M

M_B_DDRCLK1_800M

M_B_CKE1

-M_B_CS0

-M_B_CS1

M_B_ODT0

M_B_ODT1

M_B_BS0

M_B_BS1

M_B_BS2

-M_B_RAS

-M_B_WE

-M_B_CAS

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

-M_B_DQS0

-M_B_DQS1

-M_B_DQS2

-M_B_DQS3

-M_B_DQS4

-M_B_DQS5

-M_B_DQS6

-M_B_DQS7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

-M_B_DDRCLK0_800M 26

M_B_DDRCLK0_800M 26

M_B_CKE0 26

-M_B_DDRCLK1_800M 26

M_B_DDRCLK1_800M 26

M_B_CKE1 26

-M_B_CS0 26

-M_B_CS1 26

M_B_ODT0 26

M_B_ODT1 26

M_B_BS0 26

M_B_BS1 26

M_B_BS2 26

-M_B_RAS 26

-M_B_WE 26

-M_B_CAS 26

2

M_B_A[15:0] 26

-M_B_DQS[7:0] 26

M_B_DQS[7:0] 26

1

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

CPU(4/8) : DDR3L CHANNEL- BOAS-1 SP ASSESS

CPU(4/8) : DDR3L CHANNEL- BOAS-1 SP ASSESS

CPU(4/8) : DDR3L CHANNEL- BOAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

6 99Monday, August 12, 2013

6 99Monday, August 12, 2013

6 99Monday, August 12, 2013

5

D D

C C

VCCSENSE79

-SVID_ALERT79

SVID_CLK79

SVID_DATA79

PWR_DEBUG21

B B

VCCSENSE

-SVID_ALERT

SVID_CLK

SVID_DATA

PWR_DEBUG

R374

R374

75_0201_5%

75_0201_5%

1 2

VCCCPUIO

1 2

4

R782

R782

130_0201_5%

130_0201_5%

VCCCPUIO_PCH

R1900 0_0402_5%@R1900 0_0402_5%@

2

C8296

C8296

@

@

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

1 2

VCCCPUIOVCCCPUIO_A

2

1

VCCCPUCORE

VCCIO2PCH

C8297

C8297

@

@

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

VCC1R35A

VCCCPUCORE

R9

R9

100_0201_1%

100_0201_1%

1 2

1 2

R781 43_0201_5%R781 43_0201_5%

TP941TP941

IST_TRIGGER

VCCCPUCORE

3

JCPU1E

JCPU1E

K27

RSVD_2

L27

RSVD_3

T27

RSVD_4

V27

RSVD_5

AB11

VDDQ_0

AB2

VDDQ_1

AB5

VDDQ_2

AB8

VDDQ_3

AE11

VDDQ_4

AE2

VDDQ_5

AE5

VDDQ_6

AE8

VDDQ_7

AH11

VDDQ_8

K11

VDDQ_9

N11

VDDQ_10

N8

VDDQ_11

T11

VDDQ_12

T2

VDDQ_13

T5

VDDQ_14

T8

VDDQ_15

W11

VDDQ_16

W2

VDDQ_17

W5

VDDQ_18

W8

VDDQ_19

N26

RSVD_6

K26

VCC_0

AL27

RSVD_7

AK27

RSVD_8

AL35

VCC_SENS E

E17

RSVD_9

AN35

VCCIO_OUT

A23

RSVD_10

F22

VCOMP_OU T

W32

RSVD_11

AL16

RSVD_12

J27

RSVD_13

AL13

RSVD_14

AM28

VIDALERT

AM29

VIDSCLK

AL28

VIDSOUT

AP35

VSS_2

H27

PWR_DE BUG

AP34

VSS_3

AT35

RSVD_TP_1 8

AR35

RSVD_TP_1 9

AR32

RSVD_TP_2 0

AL26

RSVD_TP_2 1

AT34

VSS_4

AL22

VSS_5

AT33

VSS_6

AM21

VSS_7

AM25

VSS_8

AM22

VSS_9

AM20

VSS_10

AM24

VSS_11

AL19

VSS_12

AM23

VSS_13

AT32

VSS_14

Y25

VCC_1

Y26

VCC_2

Y27

VCC_3

Y28

VCC_4

Y29

VCC_5

Y30

VCC_6

Y31

VCC_7

Y32

VCC_8

Y33

VCC_9

Y34

VCC_10

Y35

VCC_11

LOTES_AZIF0012P002B_INTELHASWEL

LOTES_AZIF0012P002B_INTELHASWEL

CONN_ASM@

CONN_ASM@

Haswell rPGA EDS

Haswell rPGA EDS

5 OF 9

5 OF 9

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VCC_101

VCC_102

AA26

AA28

AA34

AA30

AA32

AB26

AB29

AB25

AB27

AB28

AB30

AB31

AB33

AB34

AB32

AC26

AB35

AC28

AD25

AC30

AD28

AC32

AD31

AC34

AD34

AD26

AD27

AD29

AD30

AD32

AD33

AD35

AE26

AE32

AE28

AE30

AG28

AG34

AE34

AF25

AF26

AF27

AF28

AF29

AF30

AF31

AF32

AF33

AF34

AF35

AG26

AH26

AH29

AG30

AG32

AH32

AH35

AH25

AH27

AH28

AH30

AH31

AH33

AH34

AJ25

AJ26

AJ27

AJ28

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

G25

H25

J25

K25

L25

M25

N25

P25

R25

T25

U25

U26

V25

V26

W26

W27

2

Design note:

RF solution.

2

2

1

1

C8458 1000P_0402_25V7-KC8458 1000P_0402_25V7-K

C8459 47P_0402_25VC8459 47P_0402_25V

2

2

1

1

C835 22U_0805_6.3V6MC835 22U_0805_6.3V6M

C1184 22U_0805_6.3V6MC1184 22U_0805_6.3V6M

2

2

1

1

C838 1U_0402_6.3V6KC838 1U_0402_6.3V6K

1

VCC1R35AVCCCPUCORE

2

1

C840 1U_0402_6.3V6KC840 1U_0402_6.3V6K

C842 1U_0402_6.3V6KC842 1U_0402_6.3V6K

2

2

1

1

C846 1U_0402_6.3V6KC846 1U_0402_6.3V6K

C844 1U_0402_6.3V6KC844 1U_0402_6.3V6K

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

CPU(5/8) : POWEROAS-1 SP ASSESS

CPU(5/8) : POWEROAS-1 SP ASSESS

CPU(5/8) : POWEROAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

7 99Monday, August 12, 2013

7 99Monday, August 12, 2013

7 99Monday, August 12, 2013

5

D D

JCPU1F

JCPU1F

A10

VSS_15

A13

VSS_16

A16

VSS_17

A19

VSS_18

A22

VSS_19

A25

VSS_20

A27

VSS_21

A29

VSS_22

A3

VSS_23

A31

VSS_24

A33

VSS_25

A4

VSS_26

A7

VSS_27

AA11

VSS_28

AA25

VSS_29

AA27

VSS_30

AA31

VSS_31

AA29

VSS_32

AB1

VSS_33

AB10

VSS_34

AA33

VSS_35

AA35

VSS_36

AB3

VSS_37

AC25

VSS_38

AC27

VSS_39

AB4

VSS_40

AB6

VSS_41

AB7

VSS_42

AB9

VSS_43

AC11

VSS_44

AD11

VSS_45

AC29

C C

B B

VSS_46

AC31

VSS_47

AC33

VSS_48

AC35

VSS_49

AD7

VSS_50

AE1

VSS_51

AE10

VSS_52

AE25

VSS_53

AE29

VSS_54

AE3

VSS_55

AE27

VSS_56

AE35

VSS_57

AE4

VSS_58

AE6

VSS_59

AE7

VSS_60

AE9

VSS_61

AF11

VSS_62

AF6

VSS_63

AF8

VSS_64

AG11

VSS_65

AG25

VSS_66

AE31

VSS_67

AG31

VSS_68

AE33

VSS_69

AG6

VSS_70

AH1

VSS_71

AH10

VSS_72

AH2

VSS_73

AG27

VSS_74

AG29

VSS_75

AH3

VSS_76

AG33

VSS_77

AG35

VSS_78

AH4

VSS_79

AH5

VSS_80

AH6

VSS_81

AH7

VSS_82

AH8

VSS_83

AH9

VSS_84

AJ11

VSS_85

AJ5

VSS_86

AK11

VSS_87

AK25

VSS_88

AK26

VSS_89

AK28

VSS_90

AK29

VSS_91

AK30

VSS_92

AK32

VSS_93

E19

VSS_94

LOTES_AZIF0012P002B_INTELHASWEL

LOTES_AZIF0012P002B_INTELHASWEL

CONN_ASM@

CONN_ASM@

Haswell rPGA EDS

Haswell rPGA EDS

6 OF 9

6 OF 9

4

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_330

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

AK34

AK5

AL1

AL10

AL11

AL12

AL14

AL15

AL17

AL18

AL2

AL20

AL21

AL23

E22

AL3

AL4

AL5

AL6

AL7

AL8

AL9

AM10

AM13

AM16

AM19

E25

AM32

AM4

AM7

AN10

AN13

AN16

AN19

AN2

AN21

AN24

AN27

AN30

AN34

AN4

AN7

AP1

AP10

AP13

AP16

AP19

AP4

AP7

W25

AR10

AR13

AR16

AR19

AR2

AR22

AR25

AR28

AR31

AR34

AR4

AR7

AT10

AT13

AT16

AT19

AT21

AT24

AT27

AT3

AT30

AT4

AT7

B10

B13

B16

B19

B2

B22

3

B34

B4

B7

C1

C10

C13

C16

C19

C2

C22

C24

C26

C28

C30

C32

C34

C4

C7

D10

D13

D16

D19

D22

D25

D27

D29

D31

D33

D35

D4

D7

E1

E10

E13

E16

E4

E7

F10

F11

F12

F14

F15

F17

F18

F20

F21

F23

F24

F26

F28

F30

F32

F34

F4

F6

F7

F8

F9

G1

G11

G2

G27

G29

G3

G31

G33

G35

G4

G5

H10

H26

H6

H7

J11

J26

J28

J30

J32

J34

J6

K1

2

Haswell rPGA EDS

Haswell rPGA EDS

JCPU1G

JCPU1G

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

LOTES_AZIF0012P002B_INTELHASWEL

LOTES_AZIF0012P002B_INTELHASWEL

CONN_ASM@

CONN_ASM@

7 OF 9

7 OF 9

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_SEN SE

RSVD_15

K10

K2

K29

K3

K31

K33

K35

K4

K5

K7

K8

K9

L11

L26

L6

M11

M26

M28

M30

M32

M34

M6

N1

N10

N2

N29

N3

N31

N33

N35

N4

N5

N6

N7

N9

P11

P26

P5

R11

R26

R28

R30

R32

R34

R5

T1

T10

T29

T3

T31

T33

T35

T4

T6

T7

T9

U11

U27

V11

V28

V30

V32

V34

W1

W10

W3

W35

W4

W6

W7

W9

Y11

H11

AL24

F19

T26

AK35

AK33

VSSSENSE

1 2

R70 100_0201_1%R70 100_0201_1%

1

VSSSENSE 79

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

CPU(6/8) : GNDOAS-1 SP ASSESS

CPU(6/8) : GNDOAS-1 SP ASSESS

CPU(6/8) : GNDOAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

8 99Monday, August 12, 2013

8 99Monday, August 12, 2013

8 99Monday, August 12, 2013

5

D D

DPB_0N41

DPB_0P41

DPB_1N41

C C

DPB_1P41

DPB_2N41

DPB_2P41

DPB_3N41

DPB_3P41

DPC_0N60

DPC_0P60

DPC_1N60

DPC_1P60

DPC_2N60

DPC_2P60

DPC_3N60

DPC_3P60

4

VCCCPUIO VCCCPUIO_A

Haswell rPGA EDS

Haswell rPGA EDS

JCPU1H

JCPU1H

T28

DDIB_TXBN_0

U28

DDIB_TXBP_ 0

T30

DDIB_TXBN_1

U30

DDIB_TXBP_ 1

U29

DDIB_TXBN_2

V29

DDIB_TXBP_ 2

U31

DDIB_TXBN_3

V31

DDIB_TXBP_ 3

T34

DDIC_TXCN_0

U34

DDIC_TXCP_0

U35

DDIC_TXCN_1

V35

DDIC_TXCP_1

U32

DDIC_TXCN_2

T32

DDIC_TXCP_2

U33

DDIC_TXCN_3

V33

DDIC_TXCP_3

P29

DDID_TXDN_0

R29

DDID_TXDP_0

N28

DDID_TXDN_1

P28

DDID_TXDP_1

P31

DDID_TXDN_2

R31

DDID_TXDP_2

N30

DDID_TXDN_3

P30

DDID_TXDP_3

LOTES_AZIF0012P002B_INTELHASWEL

LOTES_AZIF0012P002B_INTELHASWEL

CONN_ASM@

CONN_ASM@

eDP

eDP

EDP_DISP _UT IL

EDP_AUXN

EDP_AUXP

EDP_HPD

EDP_RCOMP

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

FDI_TXN_0

FDI_TXP_0

FDI_TXN_1

FDI_TXP_1

DDI

DDI

8 OF 9

8 OF 9

M27

N27

P27

E24

R27

P35

R35

N34

P34

P33

R33

N32

P32

R10

R10

10K_0201_5%

10K_0201_5%

1 2

EDP_COMP

3

R5

R5

24.9_0201_1%

24.9_0201_1%

1 2

EDP_AUXN

EDP_AUXP

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

FDI_TXN0

FDI_TXP0

FDI_TXN1

FDI_TXP1

13

D

D

Q1

Q1

2

G

G

LSK3541G1ET2L_VMT3

LSK3541G1ET2L_VMT3

S

S

EDP_AUXN 38

EDP_AUXP 38

EDP_TXN0 38

EDP_TXP0 38

EDP_TXN1 38

EDP_TXP1 38

FDI_TXN0 13

FDI_TXP0 13

FDI_TXN1 13

FDI_TXP1 13

R8

R8

100K_0201_5%

100K_0201_5%

1 2

EDP_HPD 38

2

1

B B

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

CPU(7/8) : EDP/DDIOAS-1 SP ASSESS

CPU(7/8) : EDP/DDIOAS-1 SP ASSESS

CPU(7/8) : EDP/DDIOAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

9 99Monday, August 12, 2013

9 99Monday, August 12, 2013

9 99Monday, August 12, 2013

5

D D

C C

B B

4

R8898

R8898

49.9_0201_1%

49.9_0201_1%

1 2

CFG321

@

1 2

1 2

R8900 49.9_0201_1%R8900 49.9_0201_1%

1 2

1 2

R14 1K_0201_5%R14 1K_0201_5%

1 2

R8965 1K_0201_5%R8965 1K_0201_5%

R8966 1K_0201_5%R8966 1K_0201_5%

Table 10-1

CFG2 : PEG Static Lane Reversal

1 : Normal Operation

0 : Lane Reversal

CFG4 : Display Port Presence

1 : Disabled

0 : Enabled

CFG[6:5] : PEG Bifurcation

11 : Func 1 Disabled, Func 2 Disabled (x16,---,---)

10 : Func 1 Enabled, Func 2 Disabled (x8,x8,---)

01 : Func 1 Disabled, Func 2 Enabled

00 : Func 1 Enabled, Func 2 Enabled (x8,x4,x4)

CFG7 : PEG Defer Training

1 : PEG Train Immediately Following XXRESETB Deassertion

0 : PEG Wait for BIOS for Training

R8967 1K_0201_5%@R8967 1K_0201_5%

TP940TP940

VCCCPUCORE

@

@

1 2

R8968 1K_0201_5%@R8968 1K_0201_5%

3

Haswell rPGA EDS

Haswell rPGA EDS

JCPU1I

JCPU1I

AT1

RSVD_TP_0

AT2

RSVD_TP_1

AD10

RSVD_16

A34

RSVD_TP_2

A35

RSVD_TP_3

W29

RSVD_TP_4

W28

RSVD_TP_5

G26

TESTLO_G26

W33

RSVD_17

AL30

RSVD_18

AL29

RSVD_19

F25

VCC_103

C35

RSVD_TP_6

B35

RSVD_TP_7

AL25

RSVD_TP_8

W30

RSVD_TP_9

W31

RSVD_TP_1 0

W34

TESTLO

AT20

CFG_0

AR20

CFG_1

AP20

CFG_2

AP22

CFG_3

AT22

CFG_4

AN22

CFG_5

AT25

CFG_6

AN23

CFG_7

AR24

CFG_8

AT23

CFG_9

AN20

CFG_10

AP24

CFG_11

AP26

CFG_12

AN25

CFG_13

AN26

CFG_14

AP25

1 2

CFG_15

LOTES_AZIF0012P002B_INTELHASWEL

LOTES_AZIF0012P002B_INTELHASWEL

R9231 1K_0201_5%@R9231 1K_0201_5%

CONN_ASM@

CONN_ASM@

Layout note:

Trace length between Pin AP22 to R9231.2 as short as possible.

RSVD_TP_1 1

RSVD_TP_1 2

RSVD_TP_1 3

RSVD_TP_1 4

CFG_RCOMP

CFG_16

CFG_18

CFG_17

CFG_19

RSVD_29

FC_G6

RSVD_30

RSVD_31

RSVD_20

RSVD_21

RSVD_22

RSVD_23

RSVD_24

RSVD_25

RSVD_26

RSVD_TP_1 5

RSVD_TP_1 6

RSVD_TP_1 7

RSVD_27

RSVD_28

VSS_330

VSS_331

9 OF 9

9 OF 9

C23

B23

D24

D23

AT31

AR21

AR23

AP21

AP23

AR33

R8963

R8963

G6

AM27

49.9_0201_1%

49.9_0201_1%

AM26

1 2

F5

AM2

K6

E18

U10

P10

B1

NC

A2

AR1

E21

E20

AP27

AR26

AL31

AL32

2

1

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

CPU(8/8) : CFG/RESERVEDOAS-1 SP ASSESS

CPU(8/8) : CFG/RESERVEDOAS-1 SP ASSESS

CPU(8/8) : CFG/RESERVEDOAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

10 99Monday, August 12, 2013

10 99Monday, August 12, 2013

10 99Monday, August 12, 2013

5

4

3

2

1

Table 11-4

Tamper Dis ableEnable

SW1 ASM NO_ASM

D D

C8486

D255

R9291

ASM

ASM

NO_ASMR9248

NO_ASMASM

NO_ASMASM

NO_ASM

Table 11-1

32.768KHz 9pF 20ppm:

KDS 1TJF090DP1A0004

TXC 9H03200033

Epson Q13FC1350000300

1 2

C348 10P_0201_25V8DC348 10P_0201_25V8D

Y6

Y6

32.768KHZ_9PF_9H03200033

32.768KHZ_9PF_9H03200033

1 2

1 2

C326 10P_0201_25V8DC326 10P_0201_25V8D

C C

HDA_BCLK54

HDA_SYNC54

PCH_SPKR59

-HDA_RST54

HDA_SDIN054

B B

1

4

SW1

SW1

2

3

SPVR310100_4P

SPVR310100_4P

R60 33_0201_5%R60 33_0201_5%

R423 33_0201_5%R423 33_0201_5%

R456 33_0201_5%R456 33_0201_5%

HDA_SDO54

-EC_WAKE61

TEST PAD

BOTTOM SIDE

DO NOT MOVE AFTER FIX

-INTRUDER_EC63

1 2

1 2

1 2

VCC3_SUS

1 2

R846 1K_0201_5%R846 1K_0201_5%

1 2

R74 33_0201_5%R74 33_0201_5%

SIT

R351

R351

10M_0201_5%

10M_0201_5%

1 2

1 2

R9248 0_0201_5%R9248 0_0201_5%

D255 RB520CS-30GT2RA_VMN2-2D255 RB520CS-30GT2RA_VMN2-2

-SRTCRST22

12

-RTCRST20,22

VCC3_SUS

R566 0_0603_5%

R566 0_0603_5%

RTCX1

RTCX2

PLACE ON TOP SIDE

1 2

TP901TP901

VCC3_SUS

@

@

R1009

R1009

1K_0201_5%

1K_0201_5%

1 2

TP900TP900

PCH_TCK21

PCH_TMS21

PCH_TDI21

PCH_TDO21

R408

R408

330K_0201_5%

330K_0201_5%

1 2

RTCVCCRTCVCC

1 2

2

1

R646

R646

1M_0201_5%

1M_0201_5%

-INTRUDER

C8486

C8486

1000P_0201_25V7K

1000P_0201_25V7K

VCC3B

1 2

R65

R65

@

@

1K_0201_5%

1K_0201_5%

Table 11-2

SPKR TCO TIMER SYSTEM REBOOT

HIGH

DISABLED (NO REBOOT)

LOW

ENABLED

LPT_PCH_M_EDS

U5A

U5A

B5

RTCX1

B4

RTCX2

B9

SRTCRST#

A8

INTRUDER#

G10

INTVRMEN

D9

RTCRST#

B25

HDA_BCLK

A22

HDA_SYNC

AL10

SPKR

C24

HDA_RST#

L22

HDA_SDI0

K22

HDA_SDI1

G22

HDA_SDI2

F22

HDA_SDI3

A24

HDA_SDO

B17

DOCKEN#/G PIO33

C22

HDA_DOCK_ RST#/GPIO13

AB3

JTAG_TCK

AD1

JTAG_TMS

AE2

JTAG_TDI

AD3

JTAG_TDO

F8

TP25

C26

TP22

AB6

TP20

DH82QM87-SR17C-C2_FCBGA695

DH82QM87-SR17C-C2_FCBGA695

LPT_PCH_M_EDS

JTAGRTC AZALIA

JTAGRTC AZALIA

1 OF 11

1 OF 11

SATA

SATA

SATA_RXN4 /PERN1

SATA_RXP4 /PERP1

SATA_RXN5 /PERN2

SATA_RXN_ 0

SATA_RXP_ 0

SATA_TXN_0

SATA_TXP_0

SATA_RXN_ 1

SATA_RXP_ 1

SATA_TXN_1

SATA_TXP_1

SATA_RXN_ 2

SATA_RXP_ 2

SATA_TXN_2

SATA_TXP_2

SATA_RXN_ 3

SATA_RXP_ 3

SATA_TXN_3

SATA_TXP_3

SATA_TXN4/P ETN1

SATA_TXP4/P ETP1

SATA_RXP5 /PERP2

SATA_TXN5/P ETN2

SATA_TXP5/P ETP2

SATA_RCOMP

SATALED#

SATA0GP/G PIO21

SATA1GP/G PIO19

SATA_IREF

BC8

BE8

AW8

AY8

BC10

BE10

AV10

AW10

BB9

BD9

AY13

AW13

BC12

BE12

AR13

AT13

BD13

BB13

AV15

AW15

BC14

BE14

AP15

AR15

AY5

AP3

AT1

AU2

BD4

BA2

TP9

BB2

TP8

SATA_RCOMP

1 2

R604 7.5K_0201_1%R604 7.5K_0201_1%

VCC1R5B

SATA0_HDD_RXN 43

SATA0_HDD_RXP 43

SATA0_HDD_TXN 43

SATA0_HDD_TXP 43

SATA1_WWAN_RXN 50

SATA1_WWAN_RXP 50

SATA1_WWAN_TXN 50

SATA1_WWAN_TXP 50

SATA4_3RD_RXN 53

SATA4_3RD_RXP 53

SATA4_3RD_TXN 53

SATA4_3RD_TXP 53

SATA5_ODD_RXN 44

SATA5_ODD_RXP 44

SATA5_ODD_TXN 44

SATA5_ODD_TXP 44

-DISCRETE_PRESENCE

UMA@R996

UMA@

1 2

R996

SWG@R239

SWG@

1 2

R239

Table 11-3

0

1

2

3

4

5

10K_0201_5%

10K_0201_5%

10K_0201_5%

10K_0201_5%

SATA Port Assignment

HDD Connector

NGFF WWAN Slot

Reserved

Reserved

NGFF Slot at Palmrest

Bay Connector

VCC3BVCC3B

10K_0201_5%

10K_0201_5%

1 2

1 2

100K_0201_5%

100K_0201_5%

R99

R99

R9247

R9247

Table 11-4

GFX SWG UMA

R239

ASM

R996

No-ASM

-DASPHDD 71

No-ASM

ASM

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

PCH(1/10) : RTC/HDA/SATA/JTAGOAS-1 SP ASSESS

PCH(1/10) : RTC/HDA/SATA/JTAGOAS-1 SP ASSESS

PCH(1/10) : RTC/HDA/SATA/JTAGOAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

11 99Monday, August 12, 2013

11 99Monday, August 12, 2013

11 99Monday, August 12, 2013

5

D D

4

3

2

1

VCC3B VCC3LAN_SPI

R860

R860

8.2K_0201_5%

8.2K_0201_5%

1 2

LPC_AD[3:0]61,69,70

C C

-LPC_FRAME61,69, 70

IRQSER61,69,70

SPI2_CLK23

12

SPI_CLK23

SPI_MOSI_IO023

SPI_MISO_IO123

SPI_IO223

SPI_IO323

B B

R9268 33_0201_5%R9268 33_0201_5%

-SPI_CS023

-SPI_CS123

12

R9269 33_0201_5%R9269 33_0201_5%

12

R9270 33_0201_5%R9270 33_0201_5%

12

R9271 33_0201_5%R9271 33_0201_5%

12

R9272 33_0201_5%R9272 33_0201_5%

SPI2_MOSI_IO023

SPI2_MISO_IO123

SPI2_IO223

SPI2_IO323

R9267 33_0201_5%R9267 33_0201_5%

R9273 33_0201_5%R9273 33_0201_5%

R9274 33_0201_5%R9274 33_0201_5%

R9275 33_0201_5%R9275 33_0201_5%

R9276 33_0201_5%R9276 33_0201_5%

Layout note:

Put on below resistors near PCH (U5):

R9268,R9269,R9270,R9271,R9272

R9267,R9273,R9274,R9275,R9276

INTEGRATED PULL UP

INTEGRATED PULL UP

1 2

R9287 33_0201_5%R9287 33_0201_5%

R9288 33_0201_5%R9288 33_0201_5%

1 2

1 2

1 2

1 2

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

12

12

@

@

@

@

1 2

1 2

R9266

R9266

R9265

R9265

3.3K_0201_5%

3.3K_0201_5%

3.3K_0201_5%

3.3K_0201_5%

A20

C20

A18

C18

B21

D21

G20

AL11

AJ11

AJ7

AL7

AJ10

AH1

AH3

AJ4

AJ2

U5D

U5D

LAD_0

LAD_1

LAD_2

LAD_3

LFRAME#

LDRQ0#

LDRQ1#/G PIO23

SERIRQ

SPI_CLK

SPI_CS0#

SPI_CS1#

SPI_CS2#

SPI_MOSI

SPI_MISO

SPI_IO2

SPI_IO3

DH82QM87-SR17C-C2_FCBGA695

DH82QM87-SR17C-C2_FCBGA695

LPT_PCH_M_EDS

LPT_PCH_M_EDS

SMBCLK

SMBDATA

SML0CLK

SML0DATA

CL_CLK

CL_DATA

CL_RST#

TD_IREF

N7

R10

U11

N8

U8

R7

H6

K6

N11

AF11

AF10

AF7

BA45

TP1

BC45

TP2

BE43

TP4

BE44

TP3

AY43

SMBus

SMBus

LPC

LPC

C-Link

C-Link

SPI

SPI

Thermal

Thermal

3 OF 11

3 OF 11

SMBALERT# /GPIO11

SML0ALE RT#/GPIO60

SML1ALE RT#/PCHHOT#/GPIO 74

SML1CLK/ GPIO58

SML1DATA/G PIO75

VCC3_SUS

R9282

R9282

R359

R359

10K_0201_5%

10K_0201_5%

10K_0201_5%

1 2

10K_0201_5%

1 2

1 2

R8971 8.25K_0201_1%R8971 8.25K_0201_1%

R106

R106

499_0201_1%

499_0201_1%

1 2

R107

R107

499_0201_1%

499_0201_1%

1 2

R389

R389

10K_0201_5%

10K_0201_5%

1 2

R394

R394

4.7K_0201_5%

4.7K_0201_5%

1 2

R397

R397

4.7K_0201_5%

4.7K_0201_5%

1 2

R272

R272

@

@

10K_0201_5%

10K_0201_5%

1 2

SMB_CLK

SMB_DATA

SML0_CLK

SML0_DATA

EC_SCL2

EC_SDA2

CL_CLK_WLAN

CL_DATA_WLAN

-CL_RST_WLAN

SMB_CLK 70

SMB_DATA 70

SML0_CLK 47

SML0_DATA 47

EC_SCL2 62

EC_SDA2 62

CL_CLK_WLAN 50

CL_DATA_WLAN 50

-CL_RST_WLAN 50

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

PCH(2/10) : LPC/SPI/SMBUS/C-LINK/THERMALOAS-1 SP ASSESS

PCH(2/10) : LPC/SPI/SMBUS/C-LINK/THERMALOAS-1 SP ASSESS

PCH(2/10) : LPC/SPI/SMBUS/C-LINK/THERMALOAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

12 99Monday, August 12, 2013

12 99Monday, August 12, 2013

12 99Monday, August 12, 2013

5

D D

DMI_RXN[3:0]3

DMI_RXP[3:0]3

DMI_TXN[3:0]3

C C

-XDP_DBR20,21,4

BPWRG21,62,70,72

CPUCORE_PWRGD21,79

MEPWRG85 -SUS_STAT 61,70

DRAMPWRG4

-RSMRST21,71

-PWRSW_EC62

AC_PRESENT20,71

B B

-BATLOW71

-PCH_SLP_WLAN62

DMI_TXP[3:0]3

VCC1R5B

-SUSWARN

4

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

1 2

R201 7.5K_0201_1%R201 7.5K_0201_1%

1 2

R9059 0_0201_5%R9059 0_0201_5%

1 2

R21 0_0201_5%R21 0_0201_5%

1 2

R617 0_0201_5%R617 0_0201_5%

1 2

R9250 0_0201_5%R9250 0_0201_5%

VCC3M

1 2

3

VCC3_SUS

1 2

1 2

R161 10K_0201_5%R161 10K_0201_5%

R9177 100K_0201_5%R9177 100K_0201_5%

U5B

U5B

R502 10K_0201_5%R502 10K_0201_5%

AW22

DMI_RXN_0

AR20

DMI_RXN_1

AP17

DMI_RXN_2

AV20

DMI_RXN_3

AY22

DMI_RXP_0

AP20

DMI_RXP_1

AR17

DMI_RXP_2

AW20

DMI_RXP_3

BD21

DMI_TXN_0

BE20

DMI_TXN_1

BD17

DMI_TXN_2

BE18

DMI_TXN_3

BB21

DMI_TXP_0

BC20

DMI_TXP_1

BB17

DMI_TXP_2

BC18

DMI_TXP_3

BE16

DMI_IREF

AW17

TP12

AV17

TP7

AY17

DMI_RCOMP

R6

SUSACK#

AM1

SYS_RESE T#

AD7

SYS_PW ROK

F10

PWROK

AB7

APWROK

H3

DRAMPWR OK

J2

RSMRST#

J4

SUSWAR N#/SUSPWR NACK/GPIO30

K1

PWRBTN#

E6

ACPRESEN T/GPIO31

K7

BATLOW# /GPIO72

N4

RI#

AB10

TP21

D2

SLP_W LAN#/GPIO2 9

DH82QM87-SR17C-C2_FCBGA695

DH82QM87-SR17C-C2_FCBGA695

LPT_PCH_M_EDS

LPT_PCH_M_EDS

DMI

DMI

System Power

System Power

Management

Management

4 OF 11

4 OF 11

FDI

FDI

SUS_STAT#/G PIO61

SUSCLK/G PIO62

SLP_S5# /GPIO63

FDI_RXN_0

FDI_RXN_1

FDI_RXP_0

FDI_RXP_1

FDI_CSYNC

FDI_INT

FDI_IREF

FDI_RCOMP

DSWVRME N

DPWROK

WAKE#

CLKRUN#

SLP_S4#

SLP_S3#

SLP_A#

SLP_SUS #

PMSYNCH

SLP_LAN #

AJ35

FDI_TXN0

AL35

FDI_TXN1

AJ36

FDI_TXP0

AL36

FDI_TXP1

AV43

TP16

AY45

TP5

AV45

TP15

AW44

TP10

AL39

FDI_CSYNC

AL40

FDI_INT

AT45

AU42

TP17

AU44

TP13

AR44

C8

L13

K3

AN7

U7

Y6

Y7

C6

H1

F3

F1

AY3

G5

1 2

R8970 7.5K_0201_1%R8970 7.5K_0201_1%

1 2

R203 0_0201_5%R203 0_0201_5%

FDI_TXN0 9

FDI_TXN1 9

FDI_TXP0 9

FDI_TXP1 9

FDI_CSYNC 3

FDI_INT 3

2

VCC1R5B

1 2

R164 330K_0201_5%R164 330K_0201_5%

VCC3B VCC3M

1 2

1 2

R28 8.2K_0201_5%R28 8.2K_0201_5%

VCC3MRTCVCC

@

1 2

R612 10K_0201_5%R612 10K_0201_5%

R614 10K_0201_5%@R614 10K_0201_5%

1

MPWRG 72

-PCIE_WAKE 50,61,71

-CLKRUN 61,69,70

SUSCLK_32K 61,71

-PCH_SLP_S5 20,71

-PCH_SLP_S4 20,62,71

-PCH_SLP_S3 20,62,71,78

-PCH_SLP_M 20,71

-PCH_SLP_SUS 62

PM_SYNC 4

-PCH_SLP_LAN 71

1 2

R9251 0_0201_5%@R9251 0_0201_5%@

Design Note :

Put R9251 near PCH (U5) in order to shorten

the stub of SUSCLK_32K.

A A

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

5

4

3

2

Date: Sheet : of

Document Number :

Document Number :

Document Number :

SUSCLK_32K_R 50

Title :

Title :

Title :

PCH(3/10) : DMI/FDI/PMOAS-1 SP ASSESS

PCH(3/10) : DMI/FDI/PMOAS-1 SP ASSESS

PCH(3/10) : DMI/FDI/PMOAS-1 SP ASSESS

1

Rev :

Rev :

Rev :

1.01

1.01

1.01

13 99Monday, August 12, 2013

13 99Monday, August 12, 2013

13 99Monday, August 12, 2013

5

D D

C C

DDCCLK40

DDCDATA40

HSYNC40

VSYNC40

PANEL_BKLT_CTRL38

VGA_BLON71

PANEL_POWER_ON72

B B

A A

VCC3B

1 2

R40

R40

2.2K_0201_5%

2.2K_0201_5%

R38

R38

2.2K_0201_5%

2.2K_0201_5%

1 2

1 2

BLUE40

GREEN40

RED40

R138

R138

100K_0201_5%

100K_0201_5%

1 2

R513 150_0201_1%R513 150_0201_1%

1 2

R242 150_0201_1%R242 150_0201_1%

1 2

R527 150_0201_1%R527 150_0201_1%

R433

R433

100K_0201_5%

100K_0201_5%

1 2

4

VCC3B

1 2

1 2

1 2

1 2

R663 8.2K_0201_5%@R663 8.2K_0201_5%

R160 8.2K_0201_5%@R160 8.2K_0201_5%

@

@

@

R140

R140

1 2

649_0201_0.5%

649_0201_0.5%

-SC_DTCT53

PLANARID115

NFC_REG_ON65

1 2

R550 8.2K_0201_5%R 550 8.2K_0201_5%

R669 8.2K_0201_5%@R669 8.2K_0201_5%

R465 8.2K_0201_5%R 465 8.2K_0201_5%

-PLTRST_NEAR21,51,61,69,70,71

-PLTRST_FAR47,50,70

3

1 2

1 2

1 2

R545 8.2K_0201_5%R 545 8.2K_0201_5%

R546 8.2K_0201_5%R 546 8.2K_0201_5%

R542 8.2K_0201_5%R 542 8.2K_0201_5%

LPT_PCH_M_EDS

U5E

U5E

T45

VGA_BLU E

U44

VGA_GRE EN

V45

VGA_RED

M43

VGA_DDC_ CLK

M45

VGA_DDC_ DATA

N42

VGA_HSYNC

N44

VGA_VSYN C

U40

DAC_IREF

U39

VGA_IRTN

N36

EDP_BKL TCTL

K36

EDP_BKL TEN

G36

EDP_VDDE N

H20

PIRQA#

L20

PIRQB#

K17

PIRQC#

M20

PIRQD#

A12

GPIO50

B13

GPIO52

C12

GPIO54

C10

GPIO51

A10

GPIO53

AL6

GPIO55

DH82QM87-SR17C-C2_FCBGA695

DH82QM87-SR17C-C2_FCBGA695

2

C460

C460

100P_0201_25V8J

100P_0201_25V8J

1

LPT_PCH_M_EDS

LVDSCRT

LVDSCRT

PCI

PCI

5 OF 11

5 OF 11

1 2

R991 33_0201_5%R991 33_0201_5%

1 2

R993 33_0201_5%R993 33_0201_5%

2

C46

C46

100P_0201_25V8J

100P_0201_25V8J

1

DDPB_CTRLCL K

DDPB_CTRLDA TA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPD_CTRLCLK

DDPD_CTRLDATA

DDPB_AUX N

DDPC_AUXN

DISPLAY

DISPLAY

DDPD_AUXN

DDPB_AUX P

DDPC_AUXP

DDPD_AUXP

DDPB_HPD

DDPC_HPD

DDPD_HPD

PIRQE#/G PIO2

PIRQF#/GP IO3

PIRQG#/G PIO4

PIRQH#/GP IO5

PME#

PLTRST#

VCC3M

5

4

R40

R39

R35

R36

N40

N38

H45

K43

J42

H43

K45

J44

K40

K38

H39

G17

F17

L15

M15

AD10

Y11

U73

U73

VCC

OUT_Y

TC7SG17FE_SON5

TC7SG17FE_SON5

Table 14-1

2

INTEGRATED PULL UP

1

NC

2

IN_A

3

GND

DPB_CTRLCLK 41

DPB_CTRLDATA 41

DOCK_DP_CLK 60

DOCK_DP_DATA 60

VCC3B

1 2

1 2

R430 8.2K_0201_5%R430 8.2K_0201_5%

R432 8.2K_0201_5%R432 8.2K_0201_5%

1 2

R435 8.2K_0201_5%R435 8.2K_0201_5%

1 2

R438

R438

10K_0201_5%

10K_0201_5%

VCC5B

G

G

2

13

D

D

S

S

Q186

Q186

LSK3541G1ET2L_VMT3

LSK3541G1ET2L_VMT3

1

DPB_AUXN 41

DOCK_DPC_AUXN 60

DPB_AUXP 41

DOCK_DPC_AUXP 60

DPB_HPD 41

NFC_INT 65

-SATA0_DEVSLP 43

-SATA1_DEVSLP 50

-SATA4_DEVSLP 53

R9210

R9210

100K_0201_5%

100K_0201_5%

1 2

DOCK_HPD 60

Buffer (U73)

TC7SG17FEToshiba

NL17SZ17XV5T2GONsemi

5

4

3

2

Project Name :

Project Name :

Project Name :

Size :

Size :

Size :

C

Date: Sheet : of

Date: Sheet : of

Date: Sheet : of

Document Number :

Document Number :

Document Number :

Title :

Title :

Title :

PCH(4/10) : LCD/CRT/PCI/DDI CONTROLOAS-1 SP ASSESS

PCH(4/10) : LCD/CRT/PCI/DDI CONTROLOAS-1 SP ASSESS

PCH(4/10) : LCD/CRT/PCI/DDI CONTROLOAS-1 SP ASSESS

14 99Monday, August 12, 2013

14 99Monday, August 12, 2013

1

14 99Monday, August 12, 2013

Rev :

Rev :

Rev :

1.01

1.01

1.01

5

4

3

2

1

Table 15-1

GPIO8

D D

Table 15-2

-FB_CLAMP_TGL_REQ31

C C

B B

HIGH

LOW

GPIO37

HIGH

LOW

DGFX_PWRGD17,83

-NFC_DTCT65

-INT_MIC_DTCT38

-WWAN_DTCT50

-NGFF_DTCT53

-EC_SCI61

FB_CLAMP30,31

LANPHYPC47

-LANWAKE47

INTEGRATED CLOCKING

DISABLED(BTM)

ENABLED(FCIM)

ME CRYPTO STRAP

WITH CONFIDENTIALITY

NO CONFIDENTIALITY

1 2

R9140 0_0201_5%@R9140 0_0201_5%@

@

@

1 2

R9141 0_0201_5%

R9141 0_0201_5%

SATA_BAY_DTCT

VCC3B

R690

R690

10K_0201_5%

10K_0201_5%

1 2

10K_0201_5%

10K_0201_5%

R689

R689

10K_0201_5%

10K_0201_5%

1 2

VCC3_SUSVCC3BVCC3_SUS

VCC3M

R226

R226

R610

@

@

1 2

R686

R686

@

@

10K_0201_5%

10K_0201_5%

R961

R961

10K_0201_5%

10K_0201_5%

R610

10K_0201_5%

10K_0201_5%

1 2

R685

R685

10K_0201_5%

10K_0201_5%

1 2

R360

R360

R280

R280

10K_0201_5%

10K_0201_5%

10K_0201_5%

10K_0201_5%

10K_0201_5%

1 2

VCC3_SUS

10K_0201_5%

R212

R212

10K_0201_5%

10K_0201_5%

1 2

1 2

FOR SOLDER CRACK DETECTION

R9198

R9198

R9199

R9199

10K_0201_5%

10K_0201_5%

1 2

1 2

1 2

R543 1K_0201_5%R543 1K_0201_5%

VCC3B

-MIC_HW_EN

R933

R933

@

@

10K_0201_5%

10K_0201_5%

1 2

1 2

1 2

R544

R544

10K_0201_5%

10K_0201_5%

10K_0201_5%

10K_0201_5%

1 2

1 2

R320 10K_0201_5%R320 10K_0201_5%

R547 1K_0201_5%R547 1K_0201_5%

PLANARID2

PLANARID3

PLANARID0

SATA_BAY_DTCT

R9057

R9057

1 2

1 2

TP108TP108

TP109TP109

TP110TP110

TP111TP111

Design Note :

Size : 1.55mm x 0.6mm

R8951

R8951

10K_0201_5%

10K_0201_5%

1 2

R684

R684

@

@

10K_0201_5%

10K_0201_5%

1 2

U5F

U5F