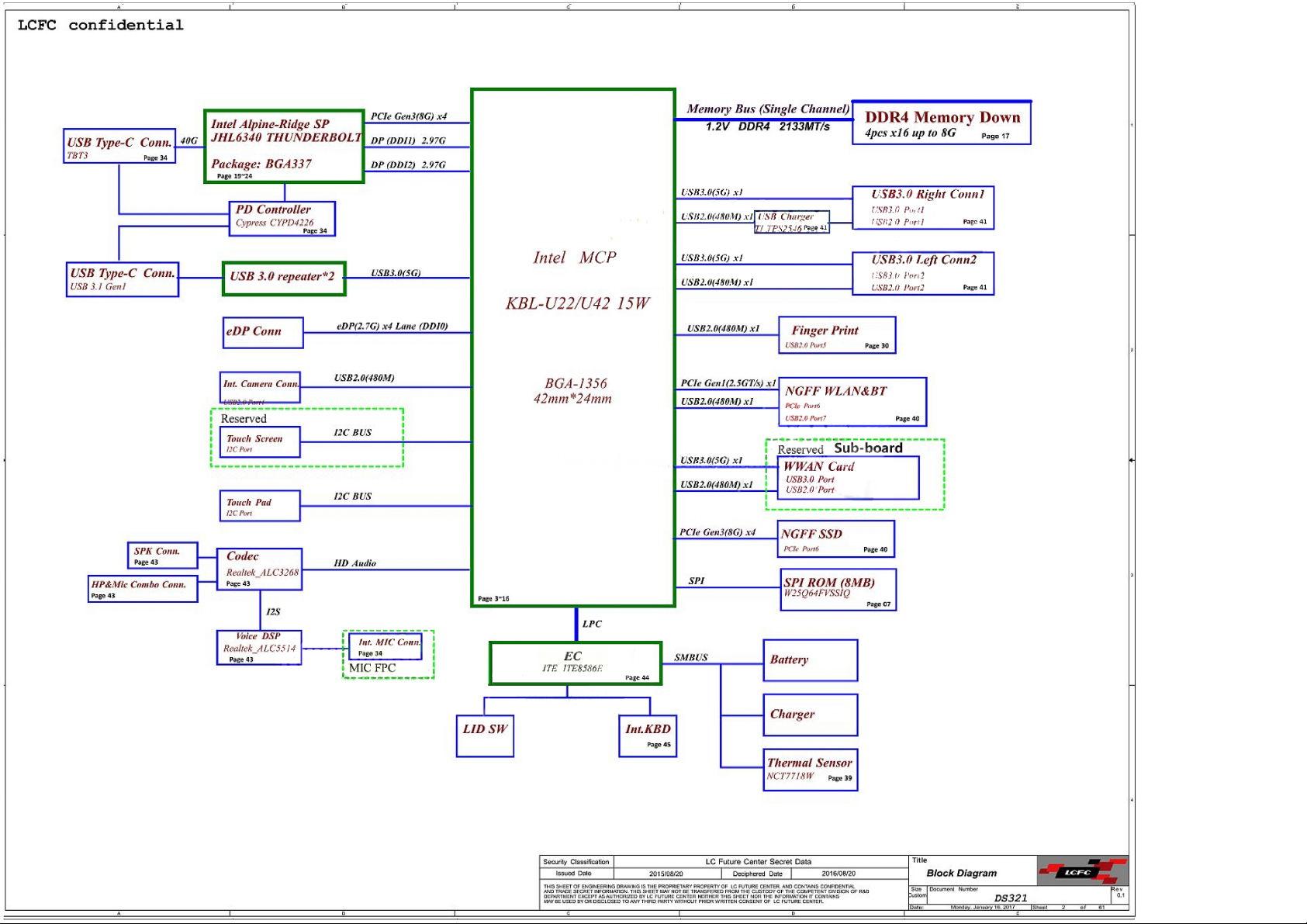

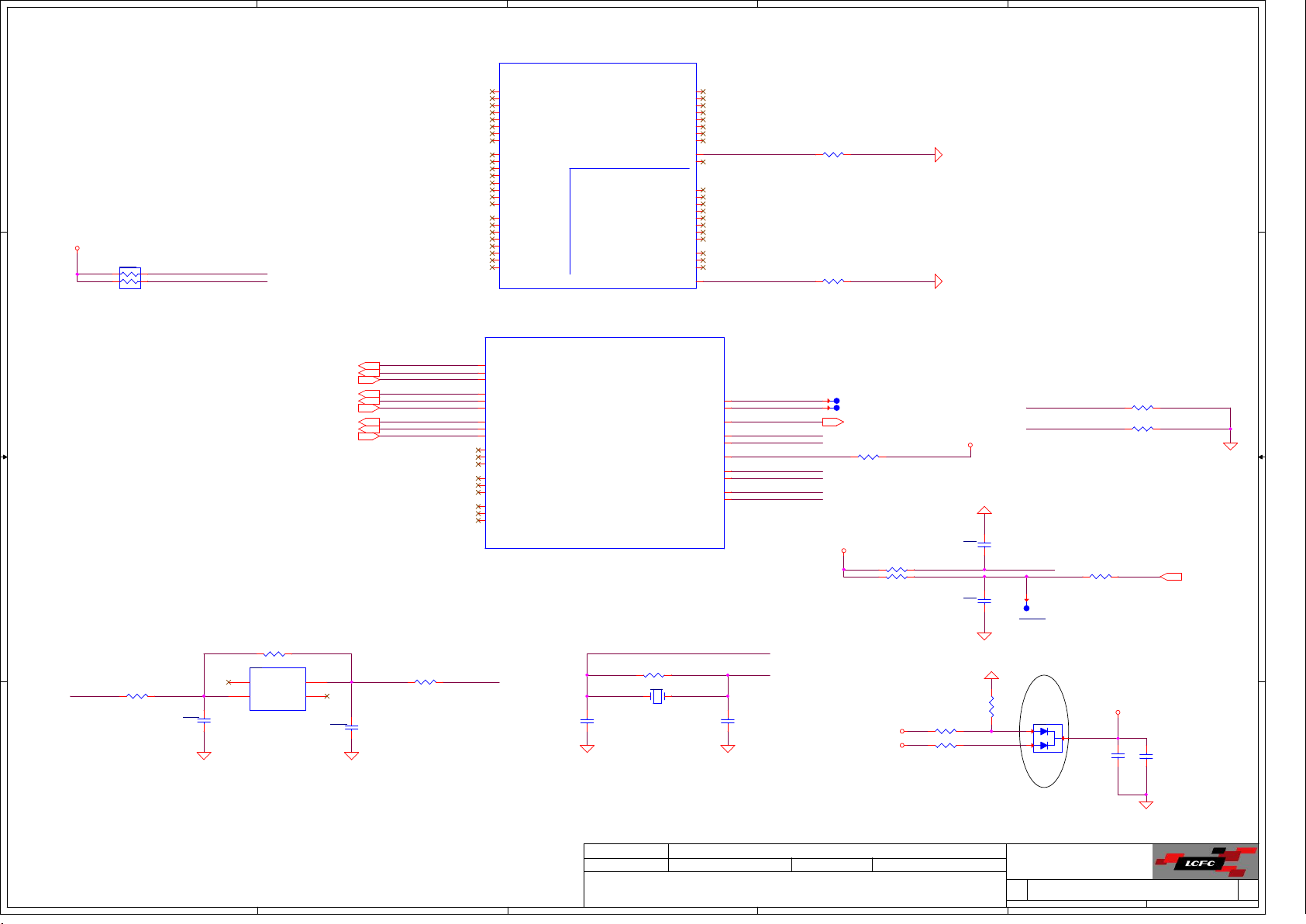

LENOVO Legion Y920-17IKB Schematics

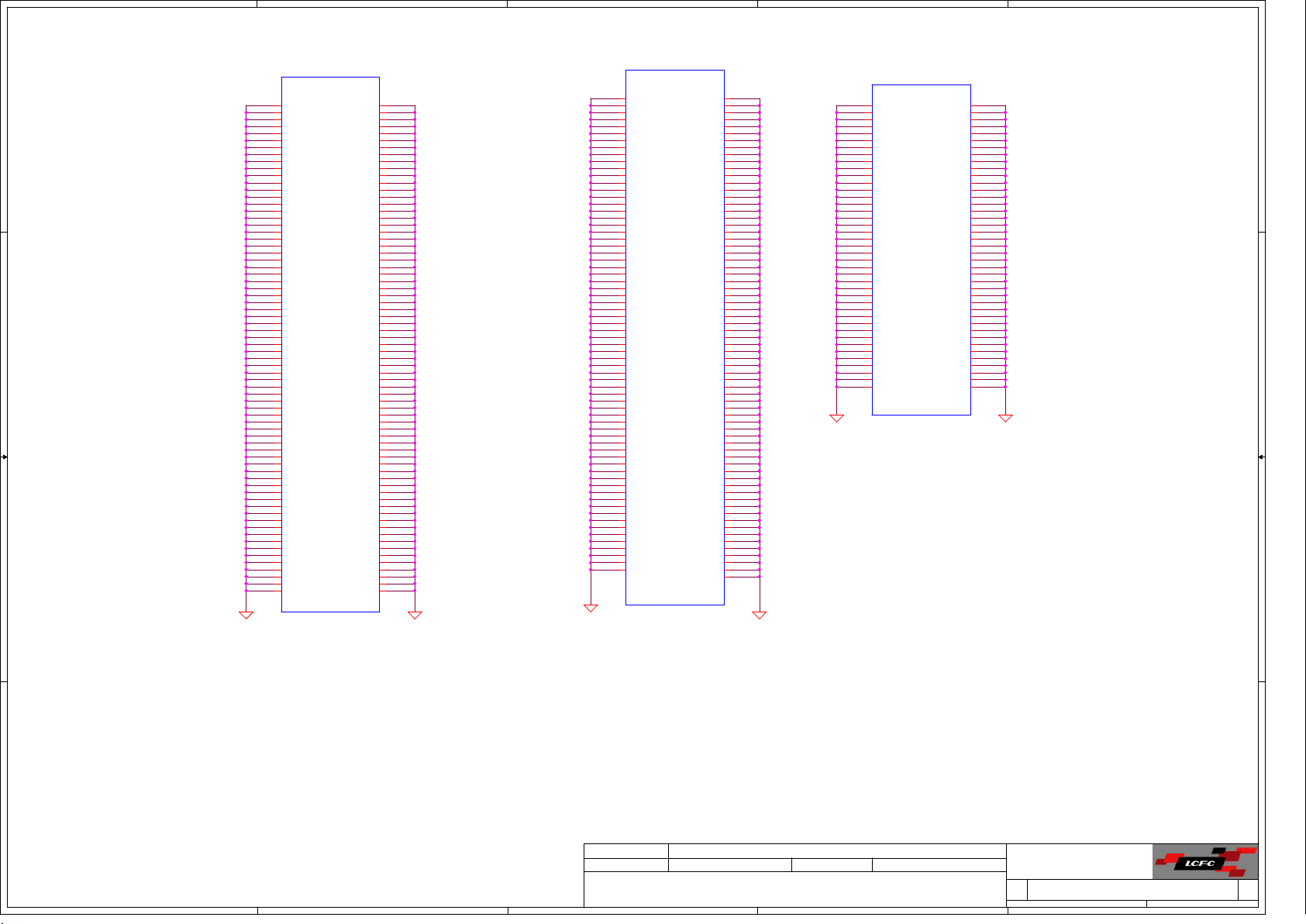

5

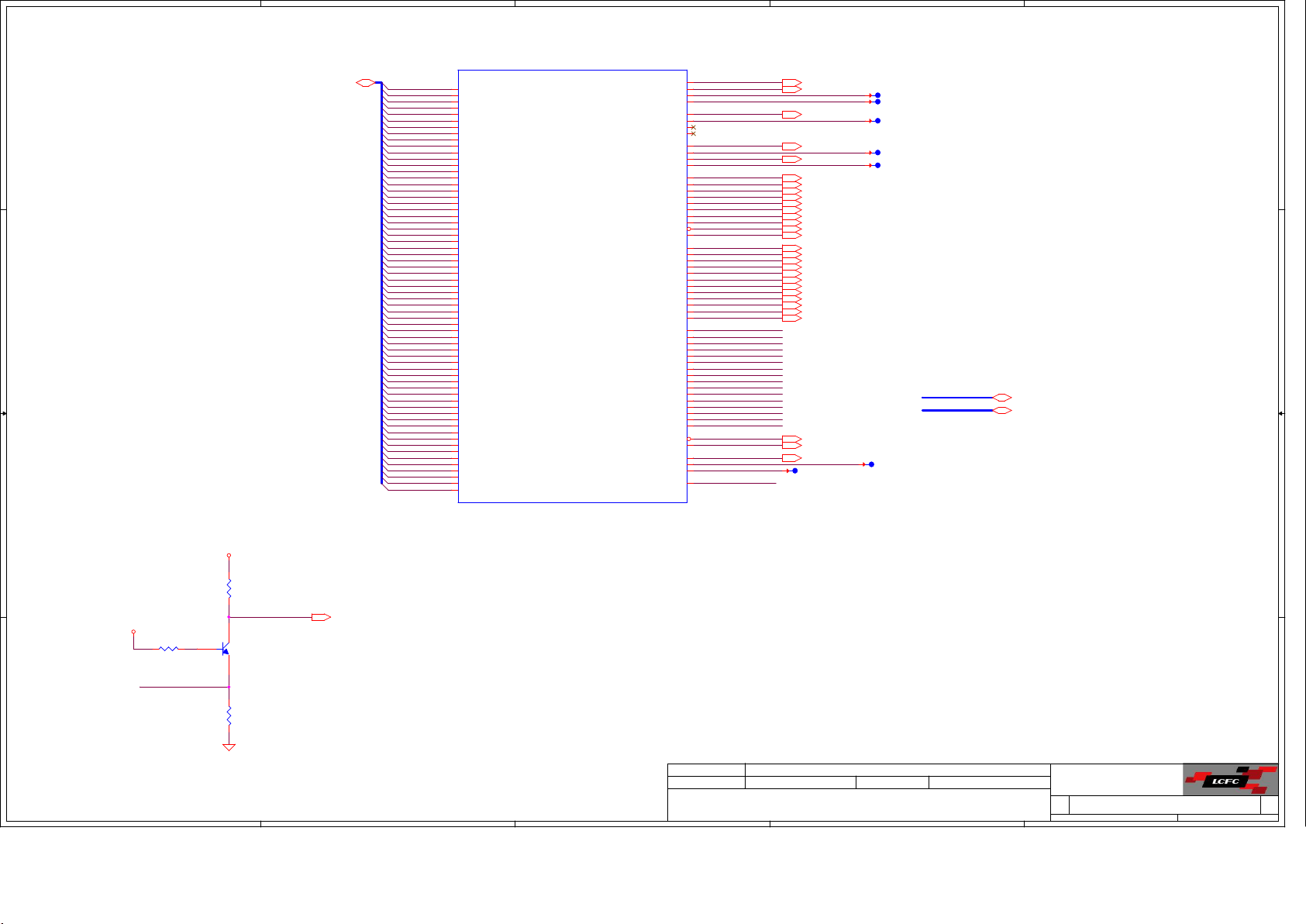

CPU_DDIA_TXN029

D D

+VCCIO

C C

check PROCHOT# circuit with PWR

H_PROCHOT#44

+VCCST_CPU

check H_THRMTRIP# if need to connector to EC

B B

CPU_DDIA_TXP029

CPU_DDIA_TXN129

CPU_DDIA_TXP129

CPU_DDIA_TXN229

CPU_DDIA_TXP229

CPU_DDIA_TXN329

CPU_DDIA_TXP329

CPU_DDIB_TXN029

CPU_DDIB_TXP029

CPU_DDIB_TXN129

CPU_DDIB_TXP129

CPU_DDIB_TXN229

CPU_DDIB_TXP229

CPU_DDIB_TXN329

CPU_DDIB_TXP329

RC4 24.9_0402_1%

+VCCSTG

12

RC19

1K_0402_5%

1 2

RC20 499 +-1% 0402

12

RC143

1K_0402_5%

+3VS

12

H_PECI44

RC155 49.9_0402_1%

RC156 49.9_0402_1%

RC157 49.9_0402_1%U23E@

RC170 49.9_0402_1%U23E@

RPC19

23

14

2.2K_0404_4P2R_5%

RPC38

23

14

@

2.2K_0404_4P2R_5%

CPU_DDIA_TXN0

CPU_DDIA_TXP0

CPU_DDIA_TXN1

CPU_DDIA_TXP1

CPU_DDIA_TXN2

CPU_DDIA_TXP2

CPU_DDIA_TXN3

CPU_DDIA_TXP3

CPU_DDIB_TXN0

CPU_DDIB_TXP0

CPU_DDIB_TXN1

CPU_DDIB_TXP1

CPU_DDIB_TXN2

CPU_DDIB_TXP2

CPU_DDIB_TXN3

CPU_DDIB_TXP3

DDPB_CLK

DDPB_DATA

DDPC_CLK

DDPC_DATA

EDP_COMP PCH_ENVDD

+VCCIO&EDP_COMP :

Trace Width: 20mil

Isolation Spa cing: 25mil

Max length: 100mil

1 2

1 2

1 2

1 2

DDPC_DATA

DDPB_DATA

DDPC_CLK

DDPB_CLK

4

?

DDI

DISPLAY SIDEBANDS

UC1D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

SKYLAKE-U_BGA1356

REV = 1

@

SKL_ULT

EDP

1 OF 20

SKL_ULT

CPU MISC

UC1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[ 0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[ 1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[ 2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[ 3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[ 0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[ 1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[ 2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[ 3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKYLAKE-U_BGA1356

12

RC1625

49.9_0402_1%

REV = 1

@

CATERR#

H_PROCHOT#_R

H_THRMTRIP#

XDP_BPM0#

1

XDP_BPM1#

1

XDP_BPM2#

1

XDP_BPM3#

1

GPP_E3

1

GPP_E7

1

PCH_TP_INT#

PROC_OPI_RCOMP

PCH_OPI_RCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

+VCCST_CPU

@

RC3048

1 2

@

100K_0402_5%

H_PECI

TC11PAD @

TC12PAD @

TC13PAD @

TC14PAD @

TC162@PAD

TC163@PAD

PCH_TP_INT#45

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

?

1 OF 20

3

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

?

JTAGX

?

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

CPU_EDP_TX0CPU_EDP_TX0+

CPU_EDP_TX1CPU_EDP_TX1+

CPU_EDP_TX2CPU_EDP_TX2+

CPU_EDP_TX3CPU_EDP_TX3+

CPU_EDP_AUX#

CPU_EDP_AUX

CPU_DDIA_AUXN

CPU_DDIA_AUXP

CPU_DDIB_AUXN

CPU_DDIB_AUXP

CPU_DDIA_HPD

CPU_DDIB_HPD

GPP_E15

CPU_EDP_HPD

PCH_ENBKL

PCH_EDP_PWM

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_TRST#

JTAGX

2

CPU_EDP_TX0- 34

CPU_EDP_TX0+ 34

CPU_EDP_TX1- 34

CPU_EDP_TX1+ 34

CPU_EDP_TX2- 34

CPU_EDP_TX2+ 34

CPU_EDP_TX3- 34

CPU_EDP_TX3+ 34

CPU_EDP_AUX# 34

CPU_EDP_AUX 34

CPU_DDIA_AUXN 29

CPU_DDIA_AUXP 29

CPU_DDIB_AUXN 29

CPU_DDIB_AUXP 29

CPU_DDIA_HPD 29

CPU_DDIB_HPD 29

PCH_ENBKL 34

PCH_EDP_PWM 34

PCH_ENVDD 34

1

PAD @

TC29

1 2

RC181 0_0402_5%

XDP_TCK

XDP_TDO

confirmed with ITE, the HPD

pull down resistor should follow

ITE recommended resistor 4.7k~10Kohm

GPP_E15

EC_SCI# 44

12

RC13

100K_0402_5%

1 2

RC1546 0_0402_5%

1 2

RC1547 0_0402_5%

XDP_TDI PCH_JTAG_TDI

1 2

RC1548 0_0402_5%

1 2

RC1549 0_0402_5%

1 2

RC1550 0_0402_5%

CPU_EDP_HPD 34

JTAGX

PCH_JTAG_TDO

RC1551 51_0402_5%

RC1543 51_0402_5%

PCH_JTAG_TMSXDP_TMS

PCH_JTAG_TRST#XDP_TRST#

1 2

RC1601 10K_0402_5%@

1 2

1 2

1

+3VS

+VCCSTG

DDP*_CTRLDATA strapping sam pled on the rising edge of PWROK

Port

Strap Enable Disable

Port 1

DDPB_CTRLDATA

Port 2

DDPC_CTRLDATA

Pull up to 3.3 V

with 2.2Kohm

Pull up to 3.3 V

with 2.2Kohm

NC

NC

A A

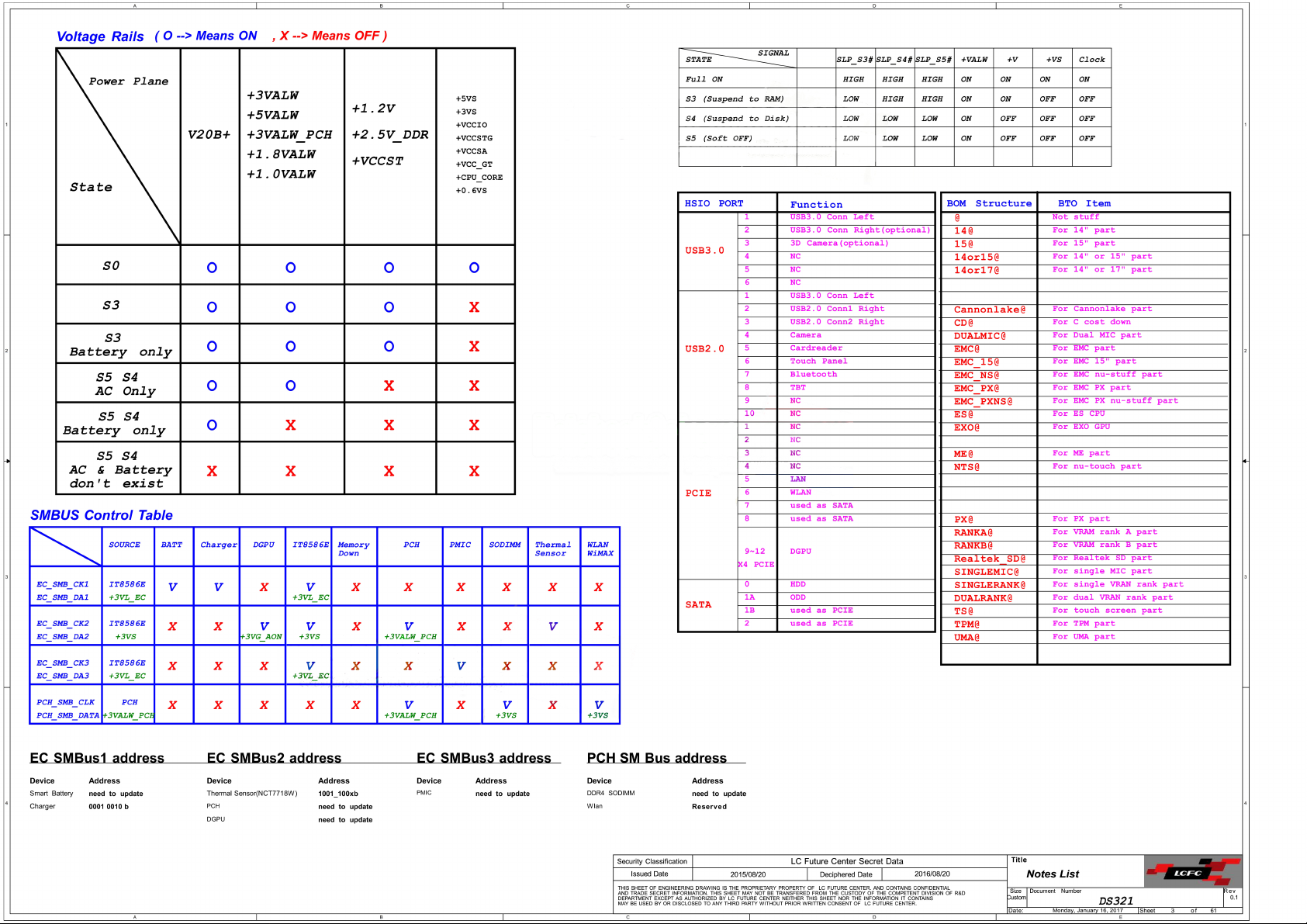

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DR AWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DR AWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DR AWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET I NFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

AND TRADE SECRET I NFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/08/20

2016/08/20

2016/08/20

Title

MCP (DDI,EDP)

MCP (DDI,EDP)

MCP (DDI,EDP)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

DS321

DS321

DS321

Monday, January 16, 2017

Monday, January 16, 2017

Monday, January 16, 2017

461

461

1

461

0.1

0.1

0.1

5

4

3

2

1

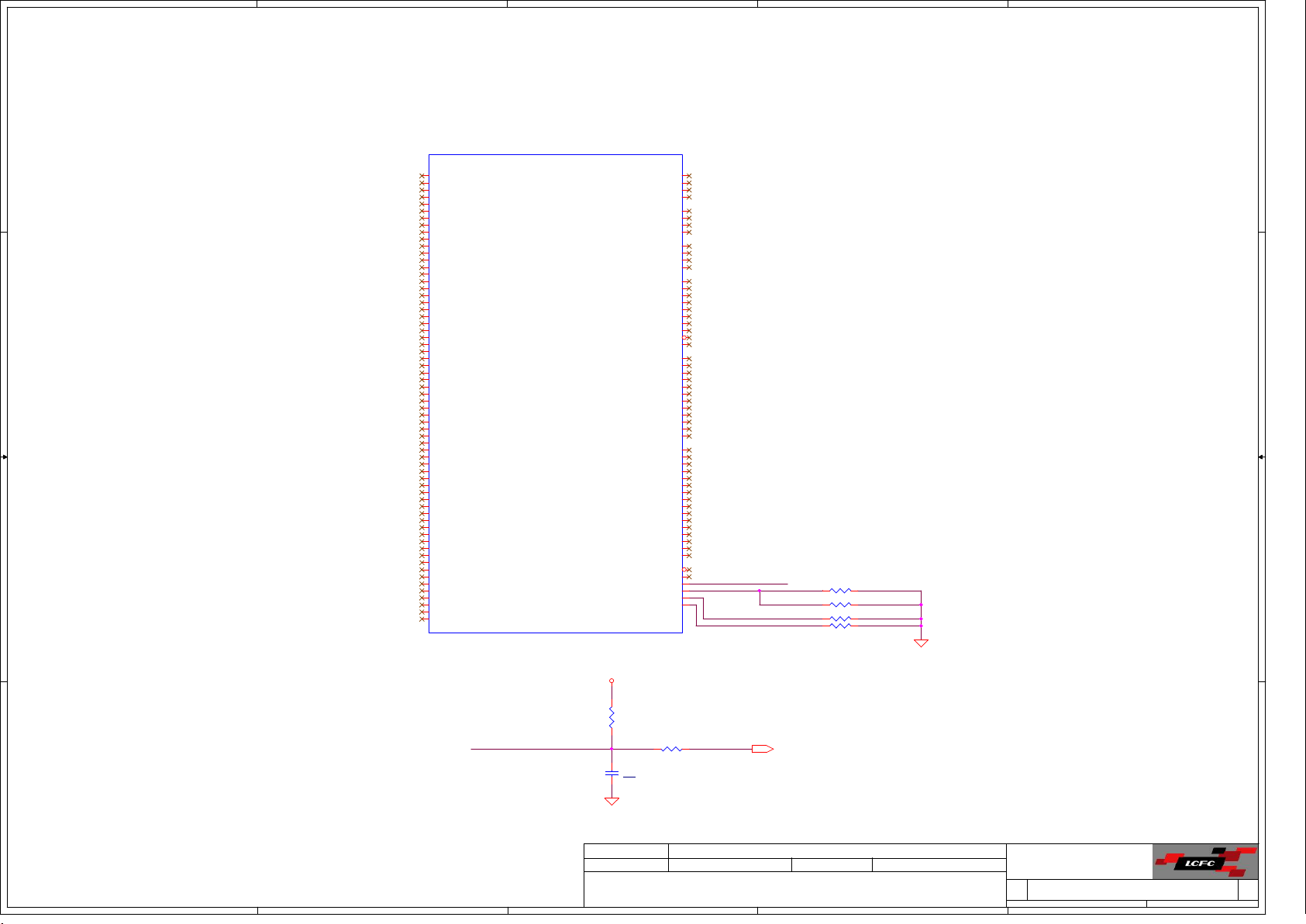

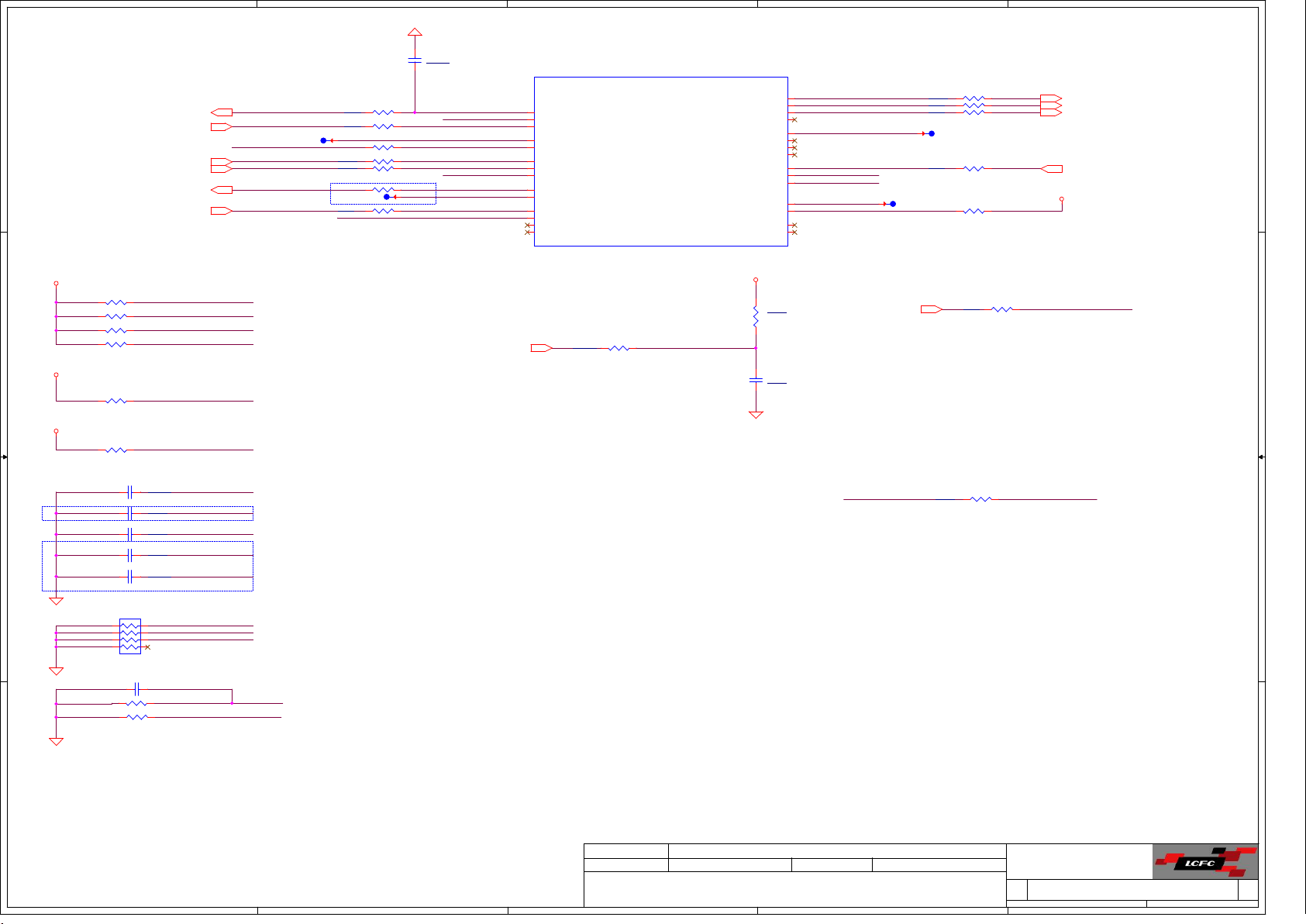

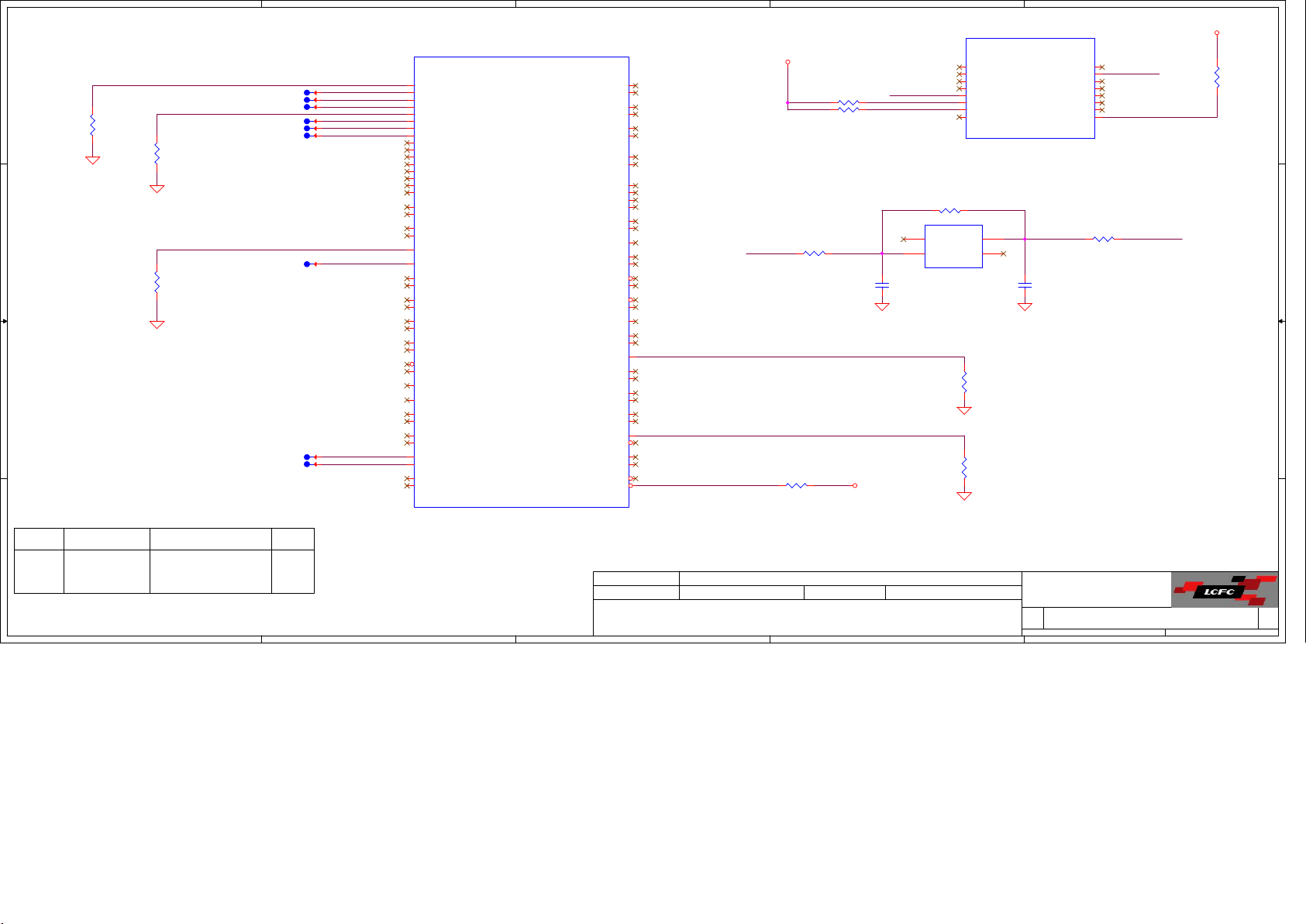

UC1B

DDRA_DQ[0..63]17

D D

C C

B B

DDRA_DQ0

DDRA_DQ1

DDRA_DQ2

DDRA_DQ3

DDRA_DQ4

DDRA_DQ5

DDRA_DQ6

DDRA_DQ7

DDRA_DQ8

DDRA_DQ9

DDRA_DQ10

DDRA_DQ11

DDRA_DQ12

DDRA_DQ13

DDRA_DQ14

DDRA_DQ15

DDRA_DQ16

DDRA_DQ17

DDRA_DQ18

DDRA_DQ19

DDRA_DQ20

DDRA_DQ21

DDRA_DQ22

DDRA_DQ23

DDRA_DQ24

DDRA_DQ25

DDRA_DQ26

DDRA_DQ27

DDRA_DQ28

DDRA_DQ29

DDRA_DQ30

DDRA_DQ31

DDRA_DQ32

DDRA_DQ33

DDRA_DQ34

DDRA_DQ35

DDRA_DQ36

DDRA_DQ37

DDRA_DQ38

DDRA_DQ39

DDRA_DQ40

DDRA_DQ41

DDRA_DQ42

DDRA_DQ43

DDRA_DQ44

DDRA_DQ45

DDRA_DQ46

DDRA_DQ47

DDRA_DQ48

DDRA_DQ49

DDRA_DQ50

DDRA_DQ51

DDRA_DQ52

DDRA_DQ53

DDRA_DQ54

DDRA_DQ55

DDRA_DQ56

DDRA_DQ57

DDRA_DQ58

DDRA_DQ59

DDRA_DQ60

DDRA_DQ61

DDRA_DQ62

DDRA_DQ63

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/ DDR0_DQ[32]

AW65

DDR0_DQ[17]/ DDR0_DQ[33]

AW63

DDR0_DQ[18]/ DDR0_DQ[34]

AY63

DDR0_DQ[19]/ DDR0_DQ[35]

BA65

DDR0_DQ[20]/ DDR0_DQ[36]

AY65

DDR0_DQ[21]/ DDR0_DQ[37]

BA63

DDR0_DQ[22]/ DDR0_DQ[38]

BB63

DDR0_DQ[23]/ DDR0_DQ[39]

BA61

DDR0_DQ[24]/ DDR0_DQ[40]

AW61

DDR0_DQ[25]/ DDR0_DQ[41]

BB59

DDR0_DQ[26]/ DDR0_DQ[42]

AW59

DDR0_DQ[27]/ DDR0_DQ[43]

BB61

DDR0_DQ[28]/ DDR0_DQ[44]

AY61

DDR0_DQ[29]/ DDR0_DQ[45]

BA59

DDR0_DQ[30]/ DDR0_DQ[46]

AY59

DDR0_DQ[31]/ DDR0_DQ[47]

AY39

DDR0_DQ[32]/ DDR1_DQ[0]

AW39

DDR0_DQ[33]/ DDR1_DQ[1]

AY37

DDR0_DQ[34]/ DDR1_DQ[2]

AW37

DDR0_DQ[35]/ DDR1_DQ[3]

BB39

DDR0_DQ[36]/ DDR1_DQ[4]

BA39

DDR0_DQ[37]/ DDR1_DQ[5]

BA37

DDR0_DQ[38]/ DDR1_DQ[6]

BB37

DDR0_DQ[39]/ DDR1_DQ[7]

AY35

DDR0_DQ[40]/ DDR1_DQ[8]

AW35

DDR0_DQ[41]/ DDR1_DQ[9]

AY33

DDR0_DQ[42]/ DDR1_DQ[10]

AW33

DDR0_DQ[43]/ DDR1_DQ[11]

BB35

DDR0_DQ[44]/ DDR1_DQ[12]

BA35

DDR0_DQ[45]/ DDR1_DQ[13]

BA33

DDR0_DQ[46]/ DDR1_DQ[14]

BB33

DDR0_DQ[47]/ DDR1_DQ[15]

AY31

DDR0_DQ[48]/ DDR1_DQ[32]

AW31

DDR0_DQ[49]/ DDR1_DQ[33]

AY29

DDR0_DQ[50]/ DDR1_DQ[34]

AW29

DDR0_DQ[51]/ DDR1_DQ[35]

BB31

DDR0_DQ[52]/ DDR1_DQ[36]

BA31

DDR0_DQ[53]/ DDR1_DQ[37]

BA29

DDR0_DQ[54]/ DDR1_DQ[38]

BB29

DDR0_DQ[55]/ DDR1_DQ[39]

AY27

DDR0_DQ[56]/ DDR1_DQ[40]

AW27

DDR0_DQ[57]/ DDR1_DQ[41]

AY25

DDR0_DQ[58]/ DDR1_DQ[42]

AW25

DDR0_DQ[59]/ DDR1_DQ[43]

BB27

DDR0_DQ[60]/ DDR1_DQ[44]

BA27

DDR0_DQ[61]/ DDR1_DQ[45]

BA25

DDR0_DQ[62]/ DDR1_DQ[46]

BB25

DDR0_DQ[63]/ DDR1_DQ[47]

@

SKYLAKE-U_BGA1356

SKL_ULT

DDR0_MA[5]/DD R0_CAA[0]/DDR0_ MA[5]

DDR0_MA[9]/DD R0_CAA[1]/DDR0_ MA[9]

DDR0_MA[6]/DD R0_CAA[2]/DDR0_ MA[6]

DDR0_MA[8]/DD R0_CAA[3]/DDR0_ MA[8]

DDR0_MA[7]/DD R0_CAA[4]/DDR0_ MA[7]

DDR0_BA[2]/ DDR0_CAA[5]/ DDR0_BG[0]

DDR0_MA[12]/ DDR0_CAA[6]/DDR0 _MA[12]

DDR0_MA[11]/ DDR0_CAA[7]/DDR0 _MA[11]

DDR0_MA[15]/ DDR0_CAA[8]/DDR0 _ACT#

DDR0_MA[14]/ DDR0_CAA[9]/DDR0 _BG[1]

DDR0_MA[13]/ DDR0_CAB[0]/DDR0 _MA[13]

DDR0_CAS#/DDR0_C AB[1]/DDR0_MA[ 15]

DDR0_WE#/ DDR0_CAB[2]/ DDR0_MA[14]

DDR0_RAS#/DDR0_C AB[3]/DDR0_MA[ 16]

DDR0_BA[0]/ DDR0_CAB[4]/ DDR0_BA[0]

DDR0_MA[2]/DD R0_CAB[5]/DDR0_ MA[2]

DDR0_BA[1]/ DDR0_CAB[6]/ DDR0_BA[1]

DDR0_MA[10]/ DDR0_CAB[7]/DDR0 _MA[10]

DDR0_MA[1]/DD R0_CAB[8]/DDR0_ MA[1]

DDR0_MA[0]/DD R0_CAB[9]/DDR0_ MA[0]

DDR0_DQSN[2]/ DDR0_DQSN[4]

DDR0_DQSP[2] /DDR0_DQSP[4]

DDR0_DQSN[3]/ DDR0_DQSN[5]

DDR0_DQSP[3] /DDR0_DQSP[5]

DDR0_DQSN[4]/ DDR1_DQSN[0]

DDR0_DQSP[4] /DDR1_DQSP[0]

DDR0_DQSN[5]/ DDR1_DQSN[1]

DDR0_DQSP[5] /DDR1_DQSP[1]

DDR0_DQSN[6]/ DDR1_DQSN[4]

DDR0_DQSP[6] /DDR1_DQSP[4]

DDR0_DQSN[7]/ DDR1_DQSN[5]

DDR0_DQSP[7] /DDR1_DQSP[5]

DDR CH - A

2 OF 20

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

DDRA_DQS#0

AM70

DDRA_DQS0

AM69

DDRA_DQS#1

AT69

DDRA_DQS1

AT70

DDRA_DQS#2

BA64

DDRA_DQS2

AY64

DDRA_DQS#3

AY60

DDRA_DQS3

BA60

DDRA_DQS#4

BA38

DDRA_DQS4

AY38

DDRA_DQS#5

AY34

DDRA_DQS5

BA34

DDRA_DQS#6

BA30

DDRA_DQS6

AY30

DDRA_DQS#7

AY26

DDRA_DQS7

BA26

AW50

AT52

AY67

AY68

BA67

DDR_VTT_CNTL

AW67

VREFCA

VREFDQ

Width -->2 0mil

Space-->20mil

1

@

TP313

DDRA_CLK0# 17

DDRA_CLK0 17

DDRA_CKE0 17

DDRA_CS0# 17

DDRA_ODT0 17

DDRA_MA5 17

DDRA_MA9 17

DDRA_MA6 17

DDRA_MA8 17

DDRA_MA7 17

DDRA_BG0 17

DDRA_MA12 17

DDRA_MA11 17

DDRA_ACT# 17

DDRA_BG1 17

DDRA_MA13 17

DDRA_MA15_CAS# 17

DDRA_MA14_WE# 17

DDRA_MA16_RAS# 17

DDRA_BA0 17

DDRA_MA2 17

DDRA_BA1 17

DDRA_MA10_AP 17

DDRA_MA1 17

DDRA_MA0 17

DDRA_MA3 17

DDRA_MA4 17

DDRA_ALERT# 17

DDRA_PAR 17

DDR_VREFCA 17

1

1

@

TP33

1

@

TP34

1

@

TP32

1

@

TP274

1

@

TP35

DDRA_DQS#[0..7]

DDRA_DQS[0..7]

@

TP31

DDRA_DQS#[0..7] 17

DDRA_DQS[0..7] 17

+3VALW

12

RC422

100K_0402_5%

+1.2V

RC452

1 2

1K_0402_5%

DDR_VTT_CNTL

A A

5

10K_0402_5%

RC432

B2

E3 1C

@

1 2

QC142

LMBT3904WT1G_SOT323-3

CPU_DRAMPG_CNTL 57

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FU TURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FU TURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FU TURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/08/20

2016/08/20

2016/08/20

Title

Title

Title

MCP (DDR4)

MCP (DDR4)

MCP (DDR4)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

DS321

DS321

DS321

Monday, January 16, 2017

Monday, January 16, 2017

Monday, January 16, 2017

561

561

1

561

0.1

0.1

0.1

5

D D

C C

B B

4

UC1C

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

@

SKYLAKE-U_BGA1356

SKL_U LT

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

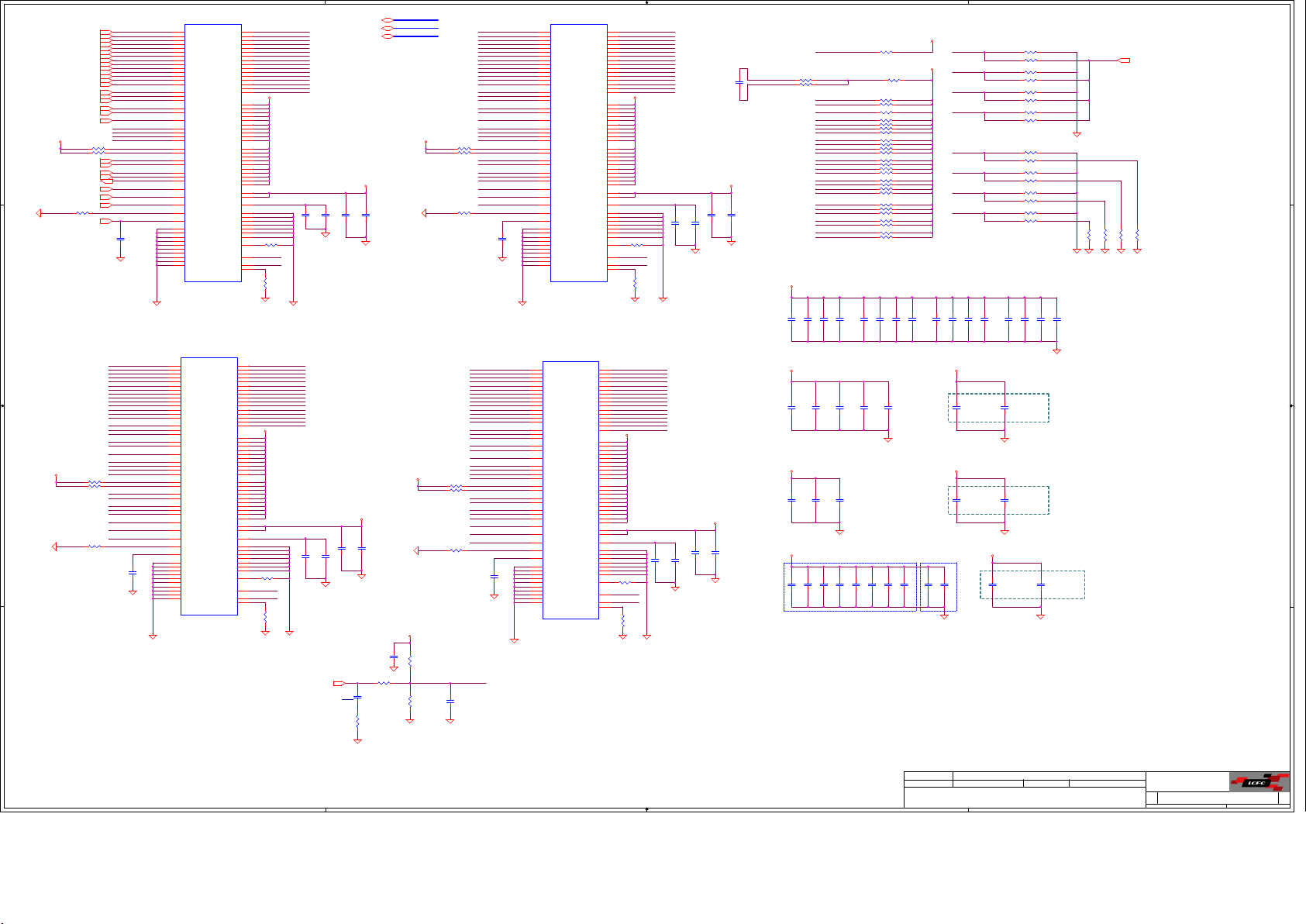

DDR CH - B

3 OF 20

3

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

CPU_DRAMRST#

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

2

1 2

RC2545 200_0402_1%SDP@

1 2

RC2543 121_0402_1%DDP@

1 2

RC2546 80.6_0402_1%

1 2

RC2544 100_0402_1%

1

+1.2V

RD91

470_0402_5%

CPU_DRAMRST#

A A

5

4

1 2

1 2

RC2542 0_0402_5%

1

CC1

0.01U_0201_10V6K

2

EMC_NS@

Security Cl assification

Security Cl assification

Security Cl assification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

3

2015/08/20

2015/08/20

2015/08/20

CPU_DRAMRST#_R 17

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/08/20

2016/08/20

2016/08/20

Title

Title

Title

MCP (DDR4)

MCP (DDR4)

MCP (DDR4)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Monday, January 16, 2017

Monday, January 16, 2017

Monday, January 16, 2017

Date: Sheet of

Date: Sheet of

Date: Sheet of

DS321

DS321

DS321

661

661

1

661

0.1

0.1

0.1

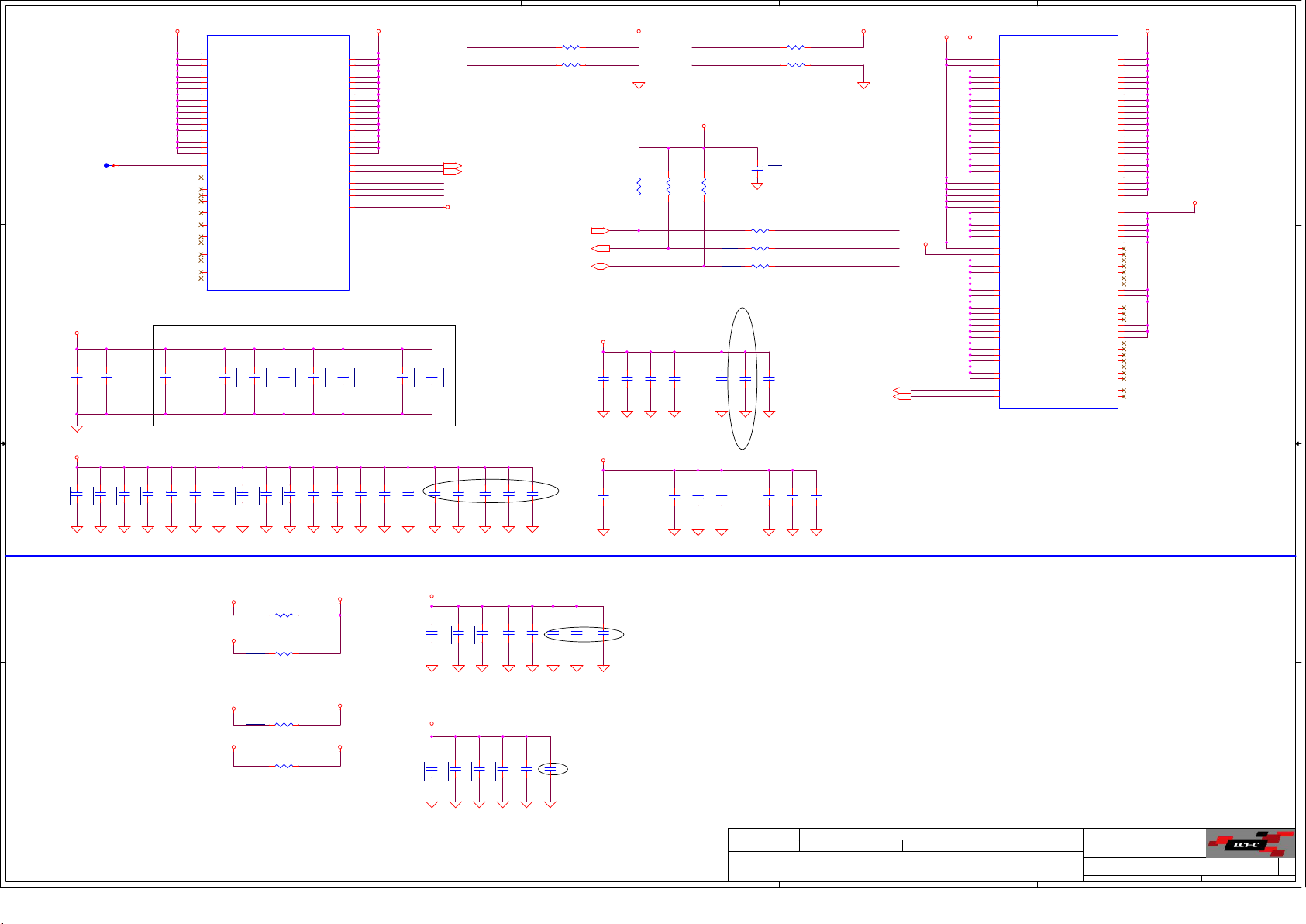

5

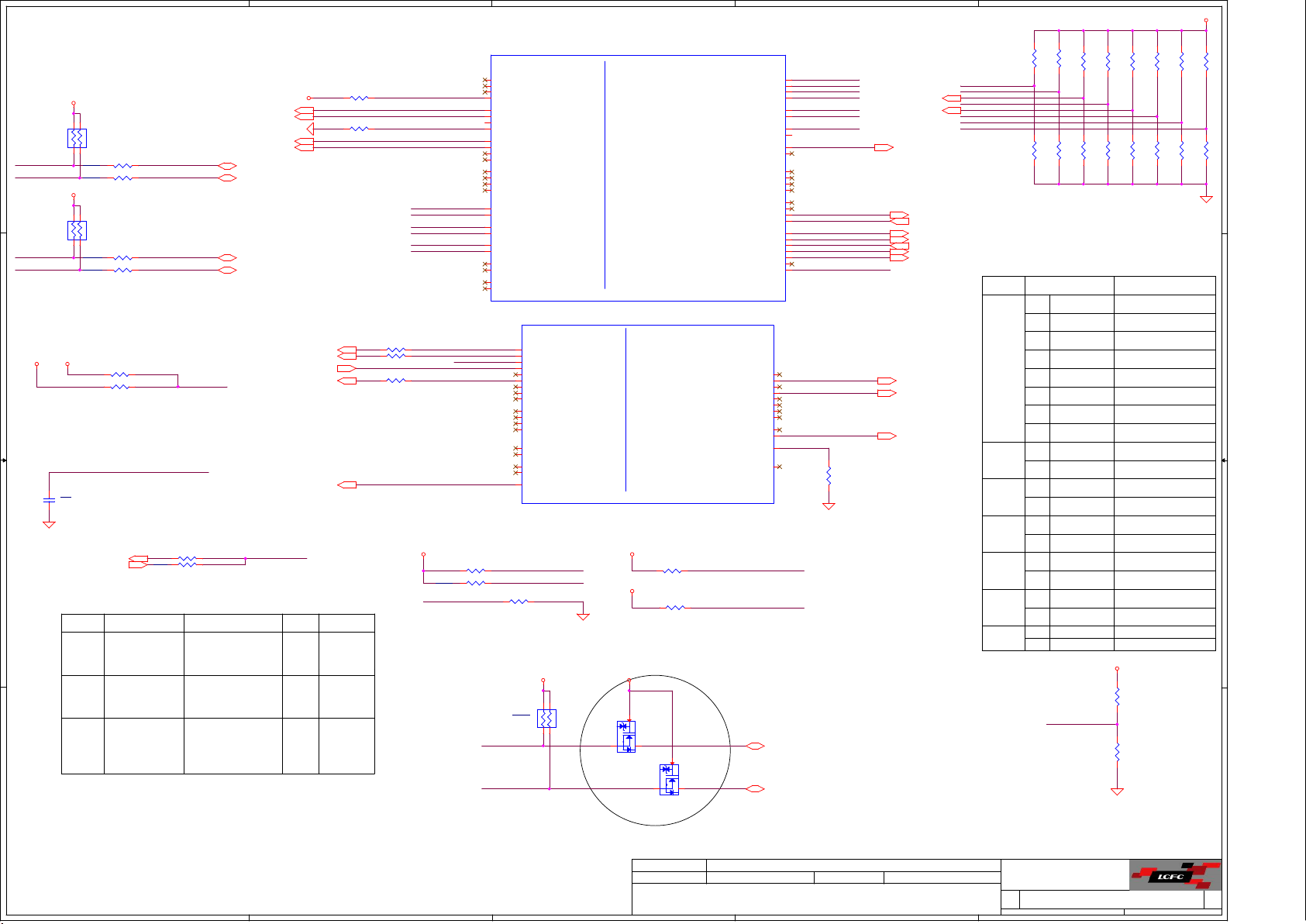

1 2

SPI_CLK44

SPI_SO44

D D

SPI_SI44

SPI_CS0#44

Check with BIOS, SPI is Dual mode or quad mode

SPI_WP#_R

SPI_HOLD#_R

RC54 15_0402_5%@

RC55 15_0402_5%@

C C

B B

RC1539 15_0402_5%

SPI_SO

SPI_SI

SPI_CS0# SPI_CS0#_R

1 2

RC53 15_0402_5%

1 2

RC52 15_0402_5%

1 2

RC51 0_0402_5%

RC60

1K_0402_5%

1 2

1 2

SPI_SO_R

SPI_SI_R

+3V_SPI

12

12

RC61

1K_0402_5%

SPI_WP#

SPI_HOLD#

SPI_CS0#

SPI_SO

SPI_WP#

TBT_FORCE_PW R29

BOARD_ID48

KBRST#44

SERIRQ44

+3VALW_PCH

RC171 0_0402_5%

1

2

3

SPI_CLK_RSPI_CLK SPI_CLK_R

SPI_SO_R

SPI_SI_R

SPI_WP#_R

SPI_HOLD#_R

SPI_CS0#_R

BOARD_ID4

KBRST#

SERIRQ

1 2

UC3

/CS

DO (IO1)

IO2

GND4DI (IO0)

W25Q64JVSSIQ_SO8

4

?

1

CC8

0.1u_0201_10V6K

2

SKL_ULT

SMBUS, SMLINK

GPP_B23/S ML1ALERT#/PCH HOT#

LPC

GPP_A5/LFR AME#/ESPI_C S#

GPP_A14/S US_STAT#/ESPI_RE SET#

GPP_A9/CLK OUT_LPC0/ESPI_ CLK

1 OF 20

check CLKRUN# / SUS_STAT# signal if need to connect

PM_CLKRUN#_R

SERIRQ

KBRST#

KBRST#

GPP_C2/SMB ALERT#

GPP_C5/SML 0ALERT#

GPP_A1/LA D0/ESPI_IO0

GPP_A2/LA D1/ESPI_IO1

GPP_A3/LA D2/ESPI_IO2

GPP_A4/LA D3/ESPI_IO3

GPP_A10/CL KOUT_LPC1

RC11 8.2K_0402_ 5%

RC12 10K_0402_5%

RC10 10K_0402_5%

CC1255 1000P_0201_50V7-K

UC1E

SPI - FLASH

AV2

SPI0_CLK

AW3

SPI0_MISO

AV3

SPI0_MOSI

AW2

SPI0_IO2

AU4

SPI0_IO3

AU3

SPI0_CS0#

AU2

SPI0_CS1#

AU1

SPI0_CS2#

SPI - TOUCH

M2

GPP_D1/SP I1_CLK

M3

GPP_D2/SP I1_MISO

J4

GPP_D3/SP I1_MOSI

V1

GPP_D21/SP I1_IO2

V2

GPP_D22/SP I1_IO3

M1

GPP_D0/SP I1_CS#

C LINK

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

AW13

GPP_A0/RCIN#

AY11

GPP_A6/SE RIRQ

SKYLAKE-U_BGA1356

REV = 1

@

+3V_SPI

+3V_SPI

8

VCC

SPI_HOLD#

7

IO3

SPI_CLK

6

CLK

SPI_SI

5

GPP_C0/SMB CLK

GPP_C1/SMB DATA

GPP_C3/SML 0CLK

GPP_C4/SML 0DATA

GPP_C6/SML 1CLK

GPP_C7/SML 1DATA

GPP_A8/CLK RUN#

1 2

1 2

1 2

1 2

EMC_NS@

3

PCH_SMB_CLK

R7

PCH_SMB_DATA

R8

SMB_ALERT#

R10

SML0_CLK

R9

SML0_DATA

W2

SML0_ALERT#

W1

PCH_SML1_CLK

W3

PCH_SML1_DAT

V3

SML1_ALERT#

AM7

AY13

BA13

BB13

AY12

BA12

SUS_STAT#

BA11

CLK_PCI_EC_R

AW9

AY9

PM_CLKRUN#_R

AW11

?

RC173 22_0402_5%

RC3033 0_0402_5%

+3VS

LPC_AD0 44

LPC_AD1 44

LPC_AD2 44

LPC_AD3 44

LPC_FRAME# 44

1 2

1

12

TC81@

CLK_PCI_EC 44

PM_CLKRUN# 44

2

PCH_SMB_CLK

PCH_SMB_DATA

PCH_SML1_CLK

PCH_SML1_DAT

SMB_ALERT#

SML0_CLK

SML0_DATA

SML0_ALERT#

This signal has a w eak internal pull-down.

0 = LPC Is selected for EC . (Default)

1 = eSPI Is selected for EC.

Notes:

1. The internal pull-do wn is disabled after RSMRST#

de-asserts .

2. This signal is in the primary wel

Rising edge of RSMRST#

SML1_ALERT#

To enable Direct Connect Interface (DCI), a 150K pull up resistor will need to be

added to PCHHOT# pin. This pin must be low during the rising edge of RSMRST#.

(Refer to WW52_MOW)

RPC20

14

23

2.2K_0404_4P2R_5%

RPC25

23

14

2.2K_0404_4P2R_5%

12

RC1562

2.2K_0402_5%

RPC23

14

23

2.2K_0404_4P2R_5%

12

RC1564 2.2K_0402_5%@

1 2

RC1569 150K_0402_5%@

1 2

RC1655 150K_0402_5%

1

+3VALW_PCH

+3VALW_PCH

+3VALW_PCH

+3VALW_PCH

+3VALW_PCH

+3VS

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF L C FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF L C FUTURE CENTER.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF L C FUTURE CENTER.

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

2

Deciphered Date

Deciphered Date

Deciphered Date

2016/08/20

2016/08/20

2016/08/20

Title

MCP (MISC,JTAG,SPI,LPC,SMB)

MCP (MISC,JTAG,SPI,LPC,SMB)

MCP (MISC,JTAG,SPI,LPC,SMB)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

DS321

DS321

DS321

Monday, January 16, 2017

Monday, January 16, 2017

Monday, January 16, 2017

1

761

761

761

0.1

0.1

0.1

5

RC1561 2.2K_0402_5%@

UART_RX_DEBUG40

UART_TX_DEBUG40

HDA_SDOUT

*

+3VS

RC1563 2.2K_0402_5%@

HDA_SYNC_AUDIO43

HDA_BITCLK_AUDIO43

HDA_SDIN043

HDA_RST_AUDIO#43

PCH_BEEP43

Default

When

Value

Sampled

0*Rising edge

of PCH_PWROK

0*Rising edge

of PCH_PWROK

Rising edge

0

of PCH_PWROK

+3VS

D D

PCH_I2C_SCL0

PCH_I2C_SDA0

PCH_I2C_SCL1

PCH_I2C_SDA1

C C

+3VALW_PCH

B B

A A

14

23

RPC26

2.2K_0404_4P2R_5%

1 2

RC147 0_0402_5%

1 2

RC148 0_0402_5%

+3VS

14

23

RPC27

2.2K_0404_4P2R_5%

1 2

RC2552 0_0402_5%

1 2

RC2553 0_0402_5%

+3VS

1 2

RC1600 1K_0402_5%@

1 2

RC47 1K_0402_5%@

*

HDA_SDO This signal has a w eak internal pull-down.

0 = Enable security measures def ined in the Flash Descriptor.

1 = Disable Flash Descriptor Security(override). This strap

should only be asserted high during external pull-up in

manufacturing/debug environments ONLY.

For EMI

1

CC7

10P_0201_50V8F

EMC_NS@

2

HDA_SDOUT_AUDIO43

ME_FLA SH44

Pin Name Strap Description Configuration

SPKR /

Top Swap

GPP_B14

Override

GSPI0_MOSI

No Reboot

/GPP_B18

GSPI1_MOSI

Boot BIOS

/GPP_B22

Strap Bit

BBS

5

PM_I2C_SCL0

PM_I2C_SDA0

PM_I2C_SCL1

PM_I2C_SDA1

HDA_SDOUT

HDA_SDIN0

1 2

RC45 33_0402_5%

1 2

RC46 0_0402_5%

Internal PD

0 = Disable “ Top Swap”

mode. (Default)

1 = Enable “ Top Swap”

mode.

Internal PD

0 = Disable “ No Reboot”

mode. (Default)

1 = Enable “ No Reboot”

mode

Internal PD

0 = SPI (Default)

1 = LPC

PCH_WLAN_OFF#9,40

PCH_BT_OFF#9,40

PM_I2C_SCL0 34

PM_I2C_SDA0 34

PM_I2C_SCL1 45

PM_I2C_SDA1 45

4

1 2

1 2

touch panel

touch pad

CCG4

RC43 33_0402_5%

RC42 33_0402_5%

RC44 33_0402_5%

4

1 2

1 2

1 2

AN8

AP7

GPP_B18

PCH_WLAN_OFF#

GPP_B22

PCH_I2C_SDA0

PCH_I2C_SCL0

PCH_I2C_SDA1

PCH_I2C_SCL1

PCH_I2C_SDA2

PCH_I2C_SCL2

+3VS

PCH_THS_RST#

AP8

AR7

AM5

AN7

AP5

AN5

AB1

AB2

W4

AB3

AD1

AD2

AD3

AD4

U7

U6

U8

U9

AH9

AH10

AH11

AH12

AF11

AF12

HDA_SYNC

HDA_BCLK

HDA_SDOUT

HDA_SDIN0

HDA_RST#

PCH_BEEP

1 2

RC14 2.2K_0402_5%@

1 2

RC514 10K_0402_5%

2.2K_0404_4P2R_5%

3

?

UC1F

LPSS ISH

GPP_B15/GSPI0_CS#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/UART0_R XD

GPP_C9/UART0_T XD

GPP_C10/UART0_ RTS#

GPP_C11/UART0_ CTS#

GPP_C20/UART2_ RXD

GPP_C21/UART2_ TXD

GPP_C22/UART2_ RTS#

GPP_C23/UART2_ CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_F6/I2C3_SDA

GPP_F7/I2C3_SCL

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

SKYLAKE-U_BGA1356

REV = 1

@

UC1G

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK10

1 2

RC513 10K_0402_5%

PCH_I2C_SCL2

PCH_I2C_SDA2

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

J5

GPP_D23/I2S_MCLK

I2S1_ SFRM

I2S1_ TXD

AK7

GPP_F1/I2S2_SFRM

AK6

GPP_F0/I2S2_SCLK

AK9

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

AW5

GPP_B14/SPKR

SKYLAKE-U_BGA1356

REV = 1

@

PCH_BEEP

THS_IRQ

@

+1.8VALW +1.8VALW

RPC36

1 4

2 3

@

SKL_ULT

SKL_ULT

+1.8VS

+3VALW_PCH

G

S

@

2N7002KDWH_SOT3 63-6

Need change to SB000019A00

S TR DMN5L06DWK-7 2N SOT363-6

Vgs(th) max1.0V

3

2

BOARD_ID0

P2

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SD A

GPP_F11/I2C5_SCL/ISH_I2C2 _SCL

GPP_D13/ISH_UART0_ RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_ TXD/SML0BCLK/I2C4B_SCL

1 OF 20

?

1 OF 20

10K_0402_5%

1 2

10K_0402_5%

2

61

QC10A

D

S

@

2N7002KDWH_SOT3 63-6

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF T HE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF T HE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF T HE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR TH E INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR TH E INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR TH E INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

GPP_D15/ISH_UART0_ RTS#

GPP_D16/ISH_UART0_ CTS#/SML0BALERT#

GPP_C12/UART1_ RXD/ISH_UART1_RXD

GPP_C13/UART1_ TXD/ISH_UART1_TXD

GPP_C14/UART1_ RTS#/ISH_UART1_RTS#

GPP_C15/UART1_ CTS#/ISH_UART1_CTS#

GPP_A17/SD_PWR _EN#/ISH_GP7

WWAN@

12

G

5

34

D

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_A12/BM_BUSY#/ISH_GP6

SDIO/SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A16/SD_1P8_SE L

SD_RCOMP

?

PCH_GNSS_DISABLE#

RC3030

BM_BUSY#

RC3038

QC10B

GPP_F23

2015/08/20

2015/08/20

2015/08/20

BOARD_ID1

P3

BOARD_ID8

P4

BOARD_ID3

P1

BOARD_ID6

M4

BOARD_ID5PCH_BT_OFF#

N3

BOARD_ID7 BOARD_ID7

N1

N2

PCH_GNSS_DISABLE#

AD11

AD12

U1

U2

U3

U4

AC1

AC2

PCH_THS_RST#

AC3

THS_IRQ

AB4

FP_PWR_EN

AY8

TOUCHPAD_PWR_EN

BA8

TBT_CIO_PLUG_EVENT#

BB7

CAMERA_PWR_EN

BA7

TOUCHPANEL_PWR_EN

AY7

AW7

BM_BUSY#

AP13

?

AB11

TBT_USB_PWR_EN

AB13

AB12

TBT_CIO_PWR_EN

W12

W11

W10

W8

W7

BA9

PCH_WW AN_OFF#

BB9

SD_RCOMP

AB7

AF13

CCG4_I2C_PCH_SCL 31

CCG4_I2C_PCH_SDA 31

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

12

RC49

200_0402_1%

Deciphered Date

Deciphered Date

Deciphered Date

2

TBT_USB_PWR_EN 29

TBT_CIO_PWR_EN 29

PCH_WW AN_OFF# 38

BOARD_ID29

BOARD_ID47

PCH_GNSS_DISABLE# 38

PCH_THS_RST# 34

THS_IRQ 34

FP_PWR_EN 45

TOUCHPAD_PWR_EN 45

TBT_CIO_PLUG_EVENT# 29

CAMERA_PWR_EN 34

TOUCHPANEL_PWR_EN 34

2016/08/20

2016/08/20

2016/08/20

1

NOTOUCH@

NOMS@

U42@

@

@

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

BOARD_ID5

BOARD_ID6

@

Board ID

Board_ID

[2,1,0]

Board_ID3

Board_ID4

Board_ID5

Board_ID6

Board_ID7

Board_ID8

Title

Title

Title

MCP (LPSS,ISH,AUDIO,SDIO)

MCP (LPSS,ISH,AUDIO,SDIO)

MCP (LPSS,ISH,AUDIO,SDIO)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

@

RC1613

RC1615

1 2

1 2

10K_0402_5%

10K_0402_5%

@

@

RC1616

RC1614

1 2

1 2

10K_0402_5%

10K_0402_5%

Description

Samsung 8Gb

000

2400 MT/s

Hynix 8Gb

010

2400 MT/s

Micron 8Gb

100

2400 MT/s

Reserved

110

Samsung 16Gb

001

2400 MT/s

Hynix 16Gb

011

2400 MT/s

Micron 16Gb

101

2400 MT/s

Reserved111

U22

U42

1

MS

0

1NON-MS

0Touch

1

NON-Touch

01FHD Panel

UHD Panel

01WWAN

NON-WWAN

0

1FPNon-FP

BOARD_ID8

Monday, January 16, 2017

Monday, January 16, 2017

Monday, January 16, 2017

RC1611

1 2

10K_0402_5%

U22@

RC1612

1 2

10K_0402_5%

DS321

DS321

DS321

RC1609

1 2

10K_0402_5%

MS@

RC1610

1 2

10K_0402_5%

+3VS

RC3045

1 2

RC3046

1 2

1

RC1608

1 2

10K_0402_5%

TOUCH@

RC1607

1 2

10K_0402_5%

Stuff R

RC1612

RC1611 RC1614 RC1616

RC1611 RC1613 RC1616

RC1612 RC1614 RC1615

RC1612 RC1613 RC1615

RC1611 RC1614 RC1615

RC1611 RC1613 RC1615

RC16100

RC1609

RC1607

RC1608

RC123

RC1606

RC1634

RC1631

RC1635

RC1632

RC3046

RC3045

Non-FP@

10K_0402_5%

FP@

10K_0402_5%

+3VS

NOWWAN@

UHD@

12

12

RC1606

RC1631

10K_0402_5%

FHD@

10K_0402_5%

WWAN@

12

RC1634

RC1616

RC1616

RC1632

10K_0402_5%

12

RC1635

10K_0402_5%

0.1

0.1

0.1

1 2

RC123

1 2

RC1614RC1612

RC1613

861

861

861

10K_0402_5%

10K_0402_5%

5

4

3

2

1

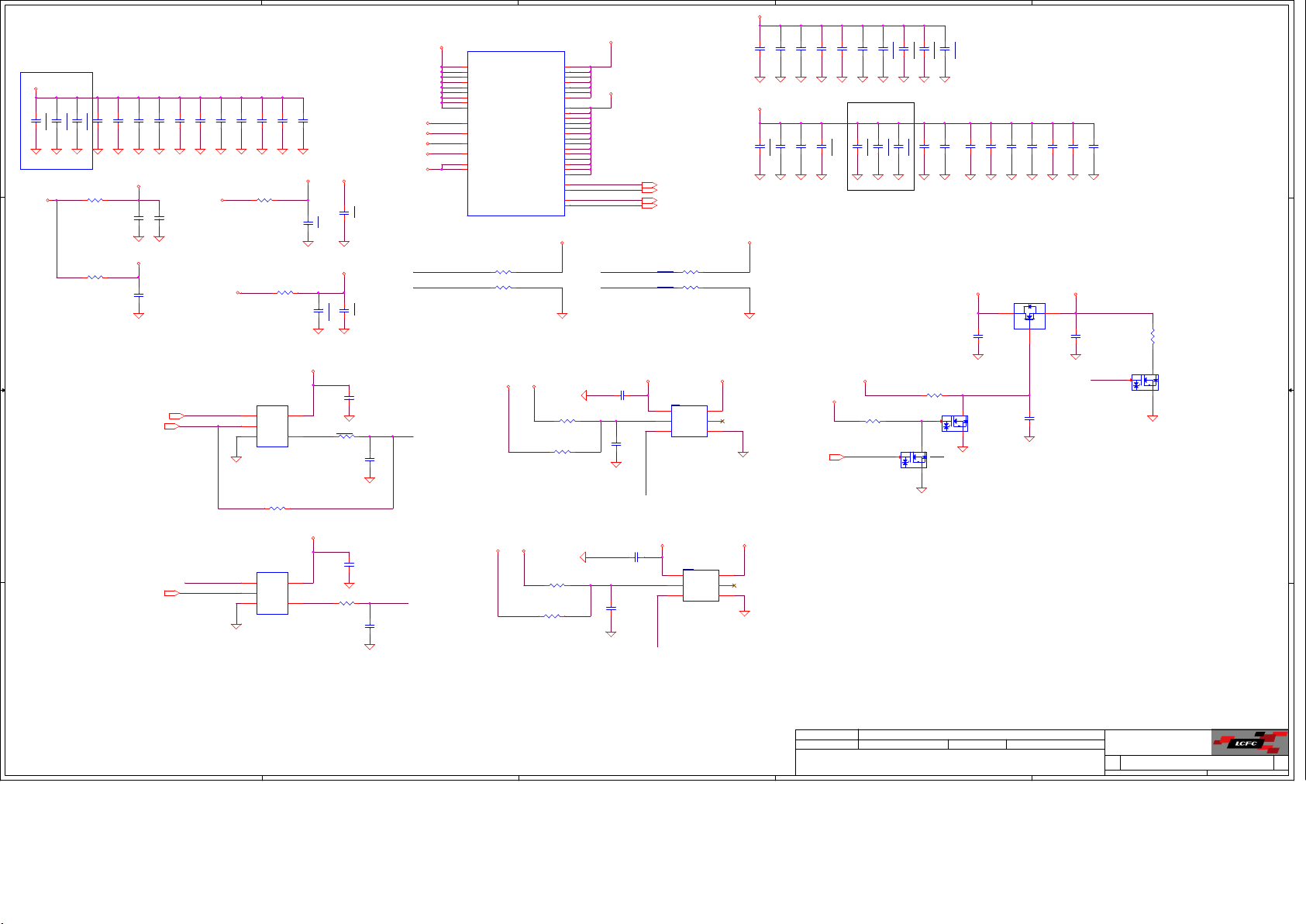

D D

UC1H

PCIE/USB3/SATA

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE_PRX_DTX_N440

WLAN

C C

SSD

TBT

B B

A A

GPP_E4

PM_SLP_S0IX#_R

5

PCIE_PRX_DTX_P440

PCIE_PTX_C_DRX_N440

PCIE_PTX_C_DRX_P440

PCIE_PRX_DTX_N542

PCIE_PRX_DTX_P542

PCIE_PTX_DRX_N542

PCIE_PTX_DRX_P542

PCIE_PRX_DTX_N642

PCIE_PRX_DTX_P642

PCIE_PTX_DRX_N642

PCIE_PTX_DRX_P642

PCIE_PRX_DTX_N742

PCIE_PRX_DTX_P742

PCIE_PTX_DRX_N742

PCIE_PTX_DRX_P742

PCIE_PRX_DTX_N842

PCIE_PRX_DTX_P842

PCIE_PTX_DRX_N842

PCIE_PTX_DRX_P842

PCIE_PRX_DTX_N929

PCIE_PRX_DTX_P929

PCIE_PTX_DRX_N929

PCIE_PTX_DRX_P929

PCIE_PRX_DTX_N1029

PCIE_PRX_DTX_P1029

PCIE_PTX_DRX_N1029

PCIE_PTX_DRX_P1029

PCIE_RCOMPN and PCIE_RCOMPP

Trace Width: 12-15mil

Differential between RCOMPP/RCOMPN

PM_SLP_S0#9,11,13,44,54

PCIE_PRX_DTX_N1129

PCIE_PRX_DTX_P1129

PCIE_PTX_DRX_N1129

PCIE_PTX_DRX_P1129

PCIE_PRX_DTX_N1229

PCIE_PRX_DTX_P1229

PCIE_PTX_DRX_N1229

PCIE_PTX_DRX_P1229

+3VS

RC1617 10K_0402_5%@

RC3032 10K_0402_5%

RC119 100_0402_1%

RPC2

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

12

12

1 2

CC1279 0.1u_0201_10V6K

1 2

CC1280 0.1u_0201_10V6K

PCIE_PRX_DTX_N9

PCIE_PRX_DTX_P9

PCIE_PTX_DRX_N9

PCIE_PTX_DRX_P9

PCIE_PRX_DTX_N10

PCIE_PRX_DTX_P10

PCIE_PTX_DRX_N10

PCIE_PTX_DRX_P10

1 2

TC20PAD@

TC19PAD@

1 2

PCIE_PRX_DTX_N11

PCIE_PRX_DTX_P11

PCIE_PTX_DRX_N11

PCIE_PTX_DRX_P11

PCIE_PRX_DTX_N12

PCIE_PRX_DTX_P12

PCIE_PTX_DRX_N12

PCIE_PTX_DRX_P12

PCH_WLAN_OFF#

SATA0GP

SATA2GP

PCH_BT_OFF#

+3VS

4

PCIE_PRX_DTX_N4

PCIE_PRX_DTX_P4

PCIE_PTX_DRX_N4

PCIE_PTX_DRX_P4

PCIE_PRX_DTX_N5

PCIE_PRX_DTX_P5

PCIE_PTX_DRX_N5

PCIE_PTX_DRX_P5

PCIE_PRX_DTX_N6

PCIE_PRX_DTX_P6

PCIE_PTX_DRX_N6

PCIE_PTX_DRX_P6

PCIE_PRX_DTX_N7

PCIE_PRX_DTX_P7

PCIE_PTX_DRX_N7

PCIE_PTX_DRX_P7

PCIE_PRX_DTX_N8

PCIE_PRX_DTX_P8

PCIE_PTX_DRX_N8

PCIE_PTX_DRX_P8

PCIE_RCOMPN

PCIE_RCOMPP

XDP_PRDY#

1

XDP_PREQ#

1

PM_SLP_S0IX#_R

RC30310_0402_5% @

PCH_WLAN_OFF# 8,40

PCH_BT_OFF# 8,40

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKYLAKE-U_BGA1356

REV = 1

@

USB_OC0#

USB_OC1#

PRIM_CORE_OPT_DIS#

TYPE_C_OCP#

Security Cl assification

Security Cl assification

Security Cl assification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

SKL_U LT

3

?

USB2

GPP_E0/SATAXP CIE0/SATAGP0

GPP_E1/SATAXP CIE1/SATAGP1

GPP_E2/SATAXP CIE2/SATAGP2

1 OF 20

RPC17

18

27

36

10K_0804_8P4R_5%

45

SSIC / USB3

2015/08/20

2015/08/20

2015/08/20

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB2_VBUSSENSE

GPP_E9/USB2_OC 0#

GPP_E10/USB2_OC 1#

GPP_E11/USB2_OC 2#

GPP_E12/USB2_OC 3#

GPP_E4/DEVSLP 0

GPP_E5/DEVSLP 1

GPP_E6/DEVSLP 2

GPP_E8/SATALED #

+3VALW_PCH

USB30_RX_N1

H8

USB30_RX_P1

G8

USB30_TX_N1

C13

USB30_TX_P1

USB3_1_TXP

USB3_4_TXP

USB2_COMP

D13

USB30_RX_N2

J6

USB30_RX_P2

H6

USB30_TX_N2

B13

USB30_TX_P2

A13

USB30_RX_N3

J10

USB30_RX_P3

H10

USB30_TX_N3

B15

USB30_TX_P3

A15

USB30_RX_N4

E10

USB30_RX_P4

F10

USB30_TX_N4

C15

USB30_TX_P4

D15

USB20_N1

AB9

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_ID

?

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

USB20_P1

AB10

USB20_N2

AD6

USB20_P2

AD7

USB20_N3

AH3

USB20_P3

AJ3

USB20_N4

AD9

USB20_P4

AD10

USB20_N5

AJ1

USB20_P5

AJ2

USB20_N6

AF6

USB20_P6

AF7

USB20_N7

AH1

USB20_P7

AH2

USB20_N8

AF8

USB20_P8

AF9

AG1

AG2

AH7

AH8

USB2_COMP

AB6

USB2_ID

AG3

USB2_VBUSSENSE

AG4

USB_OC0#

A9

USB_OC1#

C9

TYPE_C_OCP#

D9

PRIM_CORE_OPT_DIS#

B9

GPP_E4

J1

J2

J3

H2

SATA0GP

SSD_SATA_PCIE_DET#

H3

G4

SATA2GP

BOARD_ID2

H1

VCCIO_LPM#54

+3VALW

Deciphered Date

Deciphered Date

Deciphered Date

USB30_RX_N1 41

USB30_RX_P1 41

USB30_TX_N1 41

USB30_TX_P1 41

USB30_RX_N2 41

USB30_RX_P2 41

USB30_TX_N2 41

USB30_TX_P2 41

USB30_RX_N3 33

USB30_RX_P3 33

USB30_TX_N3 33

USB30_TX_P3 33

USB30_RX_N4 33

USB30_RX_P4 33

USB30_TX_N4 33

USB30_TX_P4 33

USB20_N1 41

USB20_P1 41

USB20_N2 41

USB20_P2 41

USB20_N3 45

USB20_P3 45

USB20_N4 34

USB20_P4 34

USB20_N5 38

USB20_P5 38

USB20_N6 33

USB20_P6 33

USB20_N7 40

USB20_P7 40

USB20_N8 32

USB20_P8 32

RC118 113_0402_1%

1 2

RC1626 0_0402_5%

1 2

RC1627 1K_0402_5%

USB_OC0# 41

USB_OC1# 41

TYPE_C_OCP# 33

PRIM_CORE_OPT_DIS# 9

PCH_SATA_DEVSLP 42

FULL_CARD_POWER_OFF# 38

SSD_SATA_PCIE_DET# 42

BOARD_ID2 8

RC3047

1 2

0_0402_5%

12

C8654

0.1U_0402_10V6-K

MS@

2016/08/20

2016/08/20

2016/08/20

2

Right USB (3.0)

LEFT USB (3.0)

Type-C

Type-C

RIGHT USB (2.0)

LEFT USB (2.0)

Finger Print

Camera

WWAN

Type-C

BT

TBT

12

1 2

RC1628 0_0402_5%

2016/05/03: Implement as Power Button

function for Windows RedStone support

TBT_C_OCP32

NOMS@

U3313

4

5

MC74VHC1G32DFT1G_SOT353-5

MS@

3

GND

OUT Y

2

INA

1

INB

VCC

Title

Title

Title

MCP (PCIE,SATA,USB3,USB2)

MCP (PCIE,SATA,USB3,USB2)

MCP (PCIE,SATA,USB3,USB2)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

USBRBIAS

Width 20Mil

Space 15Mil

Length 500Mil

PM_SLP_S0#

PRIM_CORE_OPT_DIS#

DS321

DS321

Monday, January 16, 2017

Monday, January 16, 2017

Monday, January 16, 2017

DS321

EC_SMI# 44

1 2

@

RC3044 0_0402_5%

PM_SLP_S0# 9,11,13,44,54

PRIM_CORE_OPT_DIS# 9

1

TYPE_C_OCP#TBT_C_OCP

0.1

0.1

961

961

961

0.1

5

D D

check the Pull up resistor

+3VS

RPC4

1 4

2 3

10K_0404_4P2R_5%

C C

PCIE CLK0

PCIE CLK1

PCIE CLK2 WLAN

B B

XTAL24_IN

RC3035

1 2

0_0402_5%

U22@

XTAL24_IN_R

CC12

SSD_CLKREQ#

WLAN_CLKREQ#

TBT

SSD

RC71 1M_0402_5%

YC2

U22@

GND12OSC2

1

1

2.2P_0402_50V8-C

2

U22@

OSC1

24MHZ_6PF_7V24000032

U22@

CLK_PCIE_SSD#42

CLK_PCIE_SSD42

SSD_CLKREQ#42

12

GND2

CLK_PCIE_TBT#29

CLK_PCIE_TBT29

TBT_CLKREQ0#29

CLK_PCIE_WLAN#40

CLK_PCIE_WLAN40

WLAN_CLKREQ#40

3

4

CC11

need to use 38.4MHz (30ohm) for Cannonlake-u

A A

4

XTAL24_OUT_R

1

2.2P_0402_50V8-C

U22@

2

CLK_PCIE_TBT#

CLK_PCIE_TBT

TBT_CLKREQ0#

CLK_PCIE_SSD#

CLK_PCIE_SSD

SSD_CLKREQ#

CLK_PCIE_WLAN#

CLK_PCIE_WLAN

WLAN_CLKREQ#

RC3034

1 2

0_0402_5%

U22@

D42

C42

AR10

B42

A42

AT7

D41

C41

AT8

D40

C40

AT10

B40

A40

AU8

E40

E38

AU7

XTAL24_OUT

UC1I

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKYLAKE-U_BGA1356

REV = 1

@

UC1J

CLKOUT_PCIE_N0

CLKOUT_PCIE_P0

GPP_B5/S RCCLKREQ0#

CLKOUT_PCIE_N1

CLKOUT_PCIE_P1

GPP_B6/S RCCLKREQ1#

CLKOUT_PCIE_N2

CLKOUT_PCIE_P2

GPP_B7/S RCCLKREQ2#

CLKOUT_PCIE_N3

CLKOUT_PCIE_P3

GPP_B8/S RCCLKREQ3#

CLKOUT_PCIE_N4

CLKOUT_PCIE_P4

GPP_B9/S RCCLKREQ4#

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

GPP_B10/S RCCLKREQ5#

SKYLAKE-U_BGA1356

REV = 1

@

SKL_U LT

SKL_U LT

3

?

GPP_D4/FLASHT RIG

EMMC

GPP_F13/EMMC _DATA0

GPP_F14/EMMC _DATA1

GPP_F15/EMMC _DATA2

GPP_F16/EMMC _DATA3

GPP_F17/EMMC _DATA4

GPP_F18/EMMC _DATA5

GPP_F19/EMMC _DATA6

GPP_F20/EMMC _DATA7

GPP_F21/E MMC_RCLK

GPP_F22/EMMC _CLK

GPP_F12/EMMC _CMD

1 OF 20

?

CLOCK SIGNALS

1 OF 20

RC32 10M_0402_5%

32.768KHZ_9PF_X1A0001410002

2

CC4

7P_0402_50V8J

1

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

EMMC_RCOMP

?

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

XCLK_BIASREF

12

YC1

1 2

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

RTCX1

RTCX2

SRTCRST#

RTCRST#

?

CSI2_COMP

EMMC_RCOMP

CLK_PCIE_XDP#

F43

CLK_PCIE_XDP

E43

BA17

SUSCLK

XTAL24_IN

E37

XTAL24_OUT

E35

DIFFCLK_BIASREF

E42

RTC_X1

AM18

RTC_X2

AM20

SRTC_RST#

AN18

RTC_RST#

AM16

RTC_X1

RTC_X2

2

CC5

7P_0402_50V8J

1

2

1 2

RC73 100_0402_1%

1 2

RC50 200_0402_1%

1

TC85 @

1

TC87 @

SUSCLK 35,40

1 2

RC72 2.7K_0402_1%

VCCRTC

1 2

RC33 20K_0402_1%

1 2

RC34 20K_0402_1%

+3VL

RTC_VCC

check RTC_VCC voltage spec come from battery

RC1491

+VCCCLK5

1U_0402_6.3V6K

1U_0402_6.3V6K

RC35

1 2

1.5K_0402_5%

1 2

1K_0402_5%

CC3

CC6

1

2

1

2

BAT_D

SUSCLK

DIFFCLK_BIASREF

SRTC_RST#

RTC_RST#

1

JCMOS1

@

change to main source SCS00007D00 01/16 JT

45.3K_0402_1%

RC36

DC5

1 2

2

3

LBAT54CWT1G_SOT323-3

RC95 1K_0402_5%@

RC1555 60.4_0402_1%

1 2

RC1624

@

VCCRTC

1

1

1 2

1 2

Cannonlake@

0_0402_5%

CC17

1U_0402_10V6K

1

2

CC26

2

1

@

EC_RTC_RST# 44

.1U_0402_ 10V6-K

Title

Title

Security Cl assification

Security Cl assification

Security Cl assification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

3

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/08/20

2016/08/20

2016/08/20

Title

MCP (CSI2,EMMC,CLOCK)

MCP (CSI2,EMMC,CLOCK)

MCP (CSI2,EMMC,CLOCK)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Monday, January 16, 2017

Monday, January 16, 2017

Monday, January 16, 2017

Date: Sheet of

Date: Sheet of

Date: Sheet of

DS321

DS321

DS321

10 61

10 61

1

10 61

0.1

0.1

0.1

5

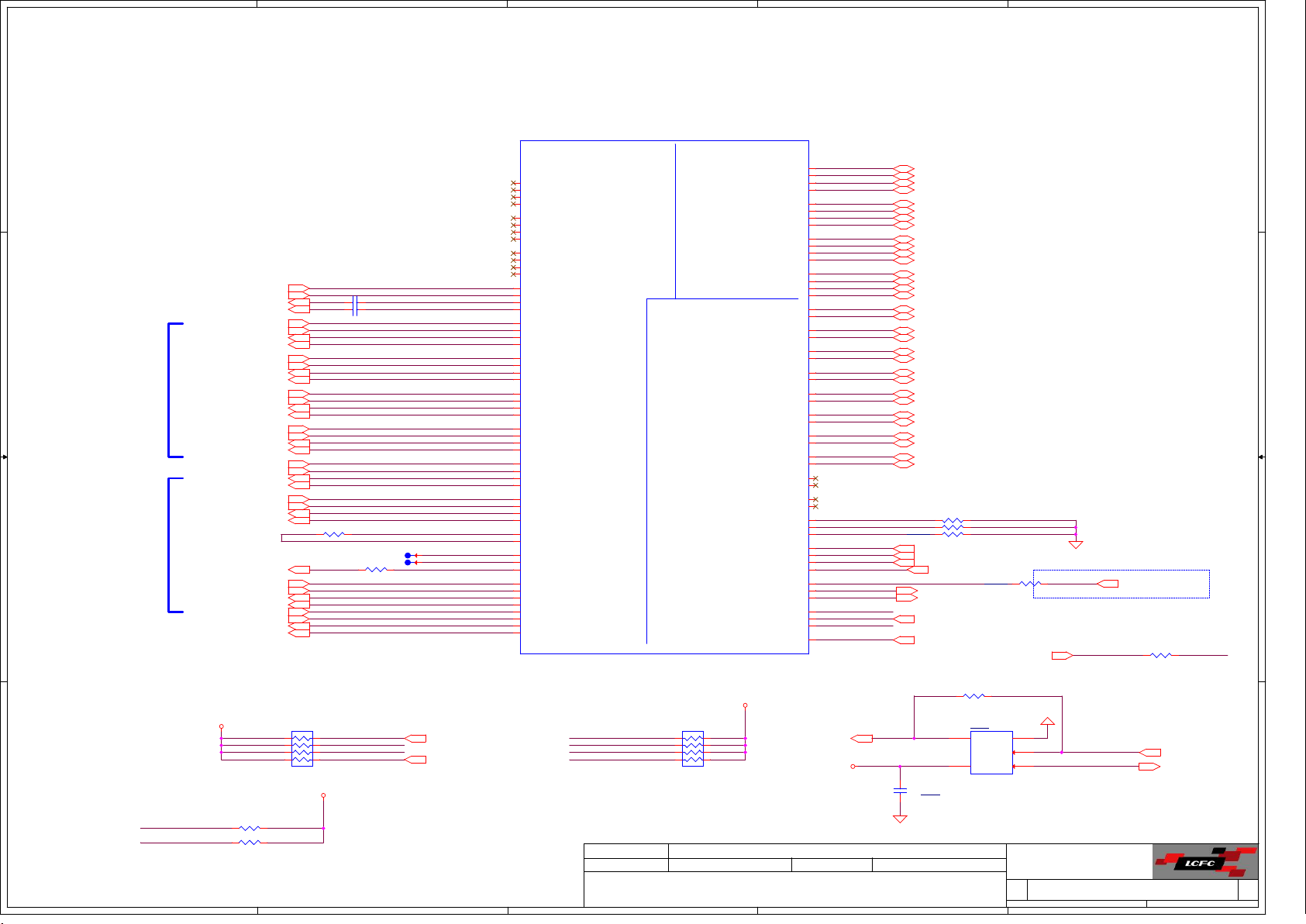

D D

+3VALW

1 2

RC74 10K_0402_5%

1 2

RC75 8.2K_0402_5%

RC76 1K_0402_5%

1 2

C C

RC90 10K_0402_5%

+3VALW_PCH

1 2

RC78 10K_0402_5%@

+3VS

1 2

RC80 10K_0402_5%

PLT_RST#29,40,42,44

EC_RSMRST#44

SYS_PWROK44

PCH_PWROK44

SUSWARN#44

PCIE_WAKE#29,38,40

AC_PRESENT_R

12

BATLOW#

WAKE#

PCH_LAN_WAKE#

SUSWARN#_R

SYS_RESET#

VCCST_PWRGD_R

Follow CRB change to 1kohm

TC21PAD@

4

CC1322

0.1U_0402_25V6

1 2

EMC@

1 2

RC84 0_0402_5%

1 2

RC85 0_0402_5%

1

1 2

RC93 60.4_0402_1%

1 2

RC139 0_0402_5%

1 2

RC126 0_0402_5%

1 2

RC86 0_0402_5%

RC91 0_0402_5%

1

TC207 PAD@

1 2

PLT_RST#_R

SYS_RESET#

PCH_RSMRST#_R

CPU_PROCPWRGD

VCCST_PWRGD

SYS_PWROK_R

PCH_PWROK_R

PCH_DPWROK_R

SUSWARN#_R

SUSACK#_R

WAKE#

PCH_LAN_WAKE#

EC_VCCST_PWRGD44

UC1K

SYSTEM POWE R MANAGEMENT

AN10

GPP_B13/PLTRST #

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSW ARN#/SUSPWRD NACK

AP11

GPP_A15/SUSAC K#

BB15

WAKE#

AM15

GPD2/LAN_W AKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKYLAKE-U_BGA1356

REV = 1

@

RC1599 0_0402_5%

1 2

3

SKL_U LT

?

1 OF 20

GPP_B12/SLP_S0 #

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WL AN#

GPD6/SLP_A#

GPD3/PWRBT N#

GPD1/ACP RESENT

GPD0/BATLOW #

GPP_A11/PME#

GPP_B11/EXT_PW R_GATE#

VCCST_PWRGD_R

INTRUDER#

GPP_B2/VRALER T#

+VCCST_CPU

1 2

2

1

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

AM10

AM11

?

RC137

1K_0402_5%

CC140

1000P_0402_50V7K

EMC_NS@

PM_SLP_S0#_R

PM_SLP_S3#_R

PM_SLP_S4#_R

PM_SLP_SUS#

PBTN_OUT#_R

AC_PRESENT_R

BATLOW#

PME#

INTVRMEN

2

MS@

1 2

RC138 0_0402_5%

1 2

RC96 0_0402_5%

1 2

RC97 0_0402_5%

1

TC206@

1 2

RC87 0_0402_5%

1

TC89@

RC41 330K_0402_5%

AC_PRESENT44

12

1 2

RC88 0_0402_5%

PM_SLP_S0# 9,13,44,54

PM_SLP_S3# 29,44

PM_SLP_S4# 44

PBTN_OUT# 44

VCCRTC

AC_PRESENT_R

1

1 2

1 2

1 2

1 2

B B

1 2

PCH_RSMRST#_R

CC12541000P_0201_50V7-K

EMC_NS@

Stuff to fix Reset&PWRGD test fail issue

PCH_PWROK

CC1040.01U_0201_10V6K

PCH_DPWROK_R

CC1031000P_0201_50V7-K

EMC_NS@

SYS_PWROK

CC10147P_0201_25V8-J

EC_RSMRST#

CC12780.01U_0201_10V6K

1 2

RC182 0_0402_5%

EC_RSMRST#PCH_DPWROK_R

Add to fix Reset&PWRGD test fail issue

RPC21

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

1 2

CC200 330P_0402_50V7K

A A

5

12

12

RC92100K_0402_5%

RC94100K_0402_1% @

PCH_RSMRST#_R

PCH_PWROK

SYS_PWROK

PCH_DPWROK_R

PLT_RST#_R

Title

Title

Security Cl assification

Security Cl assification

Security Cl assification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

3

2015/08/20

2015/08/20

2015/08/20

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2016/08/20

2016/08/20

2016/08/20

Title

MCP (SYSTEM PWR MANAGEMENT)

MCP (SYSTEM PWR MANAGEMENT)

MCP (SYSTEM PWR MANAGEMENT)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Monday, January 16, 2017

Monday, January 16, 2017

Monday, January 16, 2017

Date: Sheet of

Date: Sheet of

Date: Sheet of

DS321

DS321

DS321

11 61

11 61

1

11 61

0.1

0.1

0.1

5

+CPU_CORE +CPU_CORE

D D

1

TC90@

C C

+CPU_CORE

13x10uF 0402, SIT update to 0603 package

1

1

CC1086

CC1085

2

2

10U_0402_6.3V6M

10U_0402_6.3V6M

1

2

CC1080

10U_0402_6.3V6M

UC1L

A30

VCC_A30

A34

VCC_A34

A39

VCC_A39

A44

VCC_A44

AK33

VCC_AK33

AK35

VCC_AK35

AK37

VCC_AK37

AK38

VCC_AK38

AK40

VCC_AK40

AL33

VCC_AL33

AL37

VCC_AL37

AL40

VCC_AL40

AM32

VCC_AM32

AM33

VCC_AM33

AM35

VCC_AM35

AM37

VCC_AM37

AM38

VCC_AM38

G30

VCC_G30

K32

RSVD_K32

AK32

RSVD_AK32

AB62

VCCOPC_AB62

P62

VCCOPC_P62

V62

VCCOPC_V62

H63

VCC_OPC_1P8_H63

G61

VCC_OPC_1P8_G61

AC63

VCCOPC_SENSE

AE63

VSSOPC_SENSE

AE62

VCCEOPIO_AE62

AG62

VCCEOPIO_AG62

AL63

VCCEOPIO_SENSE

AJ62

VSSEOPIO_SENSE

SKYLAKE-U_BGA1356

REV = 1

@

1

2

SKL_ULT

CPU POWER 1 OF 4

CC1236

10U_0402_6.3V6M

1

2

U42@

?

1 OF 20

1

CC1237

2

10U_0402_6.3V6M

VCC_G32

VCC_G33

VCC_G35

VCC_G37

VCC_G38

VCC_G40

VCC_G42

VCC_J30

VCC_J33

VCC_J37

VCC_J40

VCC_K33

VCC_K35

VCC_K37

VCC_K38

VCC_K40

VCC_K42

VCC_K43

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG_G20

?

Change to 0402 Size 07/13

1

1

CC1092

CC1093

2

2

10U_0402_6.3V6M

10U_0402_6.3V6M

@

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

A63

D64

G20

CC1091

10U_0402_6.3V6M

4

VCORE_VCC_SEN

VCORE_VSS_SEN

CPU_SVID_ALERT#_R

CPU_SVID_CLK_R

CPU_SVID_DAT_R

1

CC1089

2

10U_0402_6.3V6M

+CPU_CORE +VCC_GT

VCORE_VCC_SEN

VCORE_VSS_SEN VCCGT_VSS_SEN

1 2

RC77 100_0402_1%

1 2

RC82 100_0402_1%

SVID

VCORE_VCC_SEN 61

VCORE_VSS_SEN 61

RC131

+VCCSTG

VR_SVID_ALRT#61

VR_SVID_CLK61

VR_SVID_DAT61

+VCC_GT

1

CC1238

2

10U_0402_6.3V6M

1 2

1, Alert# Route Between CLK and Data

Backside Cap 8x10uF 0402, SIT update

1

1

CC1123

CC1122

2

2

10U_0402_6.3V6M

10U_0402_6.3V6M

@

@

3

VCCGT_VCC_SEN

+VCCST_CPU

12

12

RC132

RC1544

56_0402_5%

100_0402_1%

@

1

CC1124

2

10U_0402_6.3V6M

@

100_0402_1%

RC133 220_04 02_1%

RC134 0_0402_5%

RC1545 0_0402_5%

change CC1128 mount,CC1122 unmount

1

2

@

1

CC1125

2

10U_0402_6.3V6M

CD@

CC1127

1 2

RC83 100_0402_1%

1 2

RC98 100_0402_1%

1

CC42

0.1u_0201_10V6K

@

2

1 2

1 2

1 2

1

1

CC1128

CC1129

2

2

10U_0402_6.3V6M

10U_0402_6.3V6M

10U_0402_6.3V6M

CPU_SVID_ALERT#_R

CPU_SVID_CLK_R

CPU_SVID_DAT_R

VCCGT_VCC_SEN61

VCCGT_VSS_SEN61

2

+VCCCORE_GT2

+VCCCOREG2_G T

VCCGT_VCC_SEN

VCCGT_VSS_SEN

+VCC_GT

UC1M

A48

VCCGT_A48

A53

VCCGT_A53

A58

VCCGT_A58

A62

VCCGT_A62

A66

VCCGT_A66

AA63

VCCGT_AA63

AA64

VCCGT_AA64

AA66

VCCGT_AA66

AA67

VCCGT_AA67

AA69

VCCGT_AA69

AA70

VCCGT_AA70

AA71

VCCGT_AA71

AC64

VCCGT_AC64

AC65

VCCGT_AC65

AC66

VCCGT_AC66

AC67

VCCGT_AC67

AC68

VCCGT_AC68

AC69

VCCGT_AC69

AC70

VCCGT_AC70

AC71

VCCGT_AC71

J43

VCCGT_J43

J45

VCCGT_J45

J46

VCCGT_J46

J48

VCCGT_J48

J50

VCCGT_J50

J52

VCCGT_J52

J53

VCCGT_J53

J55

VCCGT_J55

J56

VCCGT_J56

J58

VCCGT_J58

J60

VCCGT_J60

K48

VCCGT_K48

K50

VCCGT_K50

K52

VCCGT_K52

K53

VCCGT_K53

K55

VCCGT_K55

K56

VCCGT_K56

K58

VCCGT_K58

K60

VCCGT_K60

L62

VCCGT_L62

L63

VCCGT_L63

L64

VCCGT_L64

L65

VCCGT_L65

L66

VCCGT_L66

L67

VCCGT_L67

L68

VCCGT_L68

L69

VCCGT_L69

L70

VCCGT_L70

L71

VCCGT_L71

M62

VCCGT_M62

N63

VCCGT_N63

N64

VCCGT_N64

N66

VCCGT_N66

N67

VCCGT_N67

N69

VCCGT_N69

J70

VCCGT_SENSE

J69

VSSGT_SENSE

SKYLAKE-U_BGA1356

REV = 1

@

SKL_ULT

CPU POWER 2 OF 4

?

1 OF 20

VCCGT_N70

VCCGT_N71

VCCGT_R63

VCCGT_R64

VCCGT_R65

VCCGT_R66

VCCGT_R67

VCCGT_R68

VCCGT_R69

VCCGT_R70

VCCGT_R71

VCCGT_T62

VCCGT_U65

VCCGT_U68

VCCGT_U71

VCCGT_W63

VCCGT_W64

VCCGT_W65

VCCGT_W66

VCCGT_W67

VCCGT_W68

VCCGT_W69

VCCGT_W70

VCCGT_W71

VCCGT_Y62

VCCGTX_AK42

VCCGTX_AK43

VCCGTX_AK45

VCCGTX_AK46

VCCGTX_AK48

VCCGTX_AK50

VCCGTX_AK52

VCCGTX_AK53

VCCGTX_AK55

VCCGTX_AK56

VCCGTX_AK58

VCCGTX_AK60

VCCGTX_AK70

VCCGTX_AL43

VCCGTX_AL46

VCCGTX_AL50

VCCGTX_AL53

VCCGTX_AL56

VCCGTX_AL60

VCCGTX_AM48

VCCGTX_AM50

VCCGTX_AM52

VCCGTX_AM53

VCCGTX_AM56

VCCGTX_AM58

VCCGTX_AU58

VCCGTX_AU63

VCCGTX_BB57

VCCGTX_BB66

VCCGTX_SENSE

VSSGTX_SENSE

1

+VCC_GT

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

?

+VCCCORE_GT1

+CPU_CORE

CC1108

1U_0201_6.3V6-M

4

1

CC1109

2

1U_0201_6.3V6-M

U42@

+VCCCORE_GT2

1

CC1126

2

10U_0402_6.3V6M

+VCCCORE_GT1

1

CC1105

2

1U_0201_6.3V6-M

U42@

1

2

U42@

1

1

CC1095

CC1096

2

2

1U_0201_6.3V6-M

1U_0201_6.3V6-M

B B

A A

1

1

CC1097

2

1U_0201_6.3V6-M

1

CC1098

CC1099

2

2

1U_0201_6.3V6-M

1U_0201_6.3V6-M

5

1

1

CC1102

2

1U_0201_6.3V6-M

1

CC1296

2

1U_0201_6.3V6-M

1 2

RC1068 0.0002_0805U42@

1 2

RC1069 0.0002_0805U22@

1 2

RC1070 0.0002_0805U42@

1 2

RC3029 0_040 2_5%U22@

1

CC1101

CC1100

2

2

1U_0201_6.3V6-M

1U_0201_6.3V6-M

+CPU_CORE

+VCC_GT

+CPU_CORE

1

CC1304

1U_0201_6.3V6-M

1

CC1305

2

2

1U_0201_6.3V6-M

+VCCCORE_GT2

+VCCCORE_GT1

+VCCCOREG2_G T+VCC_GT

1

1

CC1306

2

2

1U_0201_6.3V6-M

U42@

1

CC1104

2

1U_0201_6.3V6-M

1

1

CC1318

CC1317

2

2

1U_0201_6.3V6-M

1U_0201_6.3V6-M

U42@

U42@

1

1

CC1241

CC1303

2

2

1U_0201_6.3V6-M

1U_0201_6.3V6-M

1

1

CC1294

CC1295

2

2

1U_0201_6.3V6-M

1U_0201_6.3V6-M

U42@

U42@

1

1