LENOVO K610D Schematics

1

www.schematic-x.blogspot.com

2

3

4

5

6

7

8

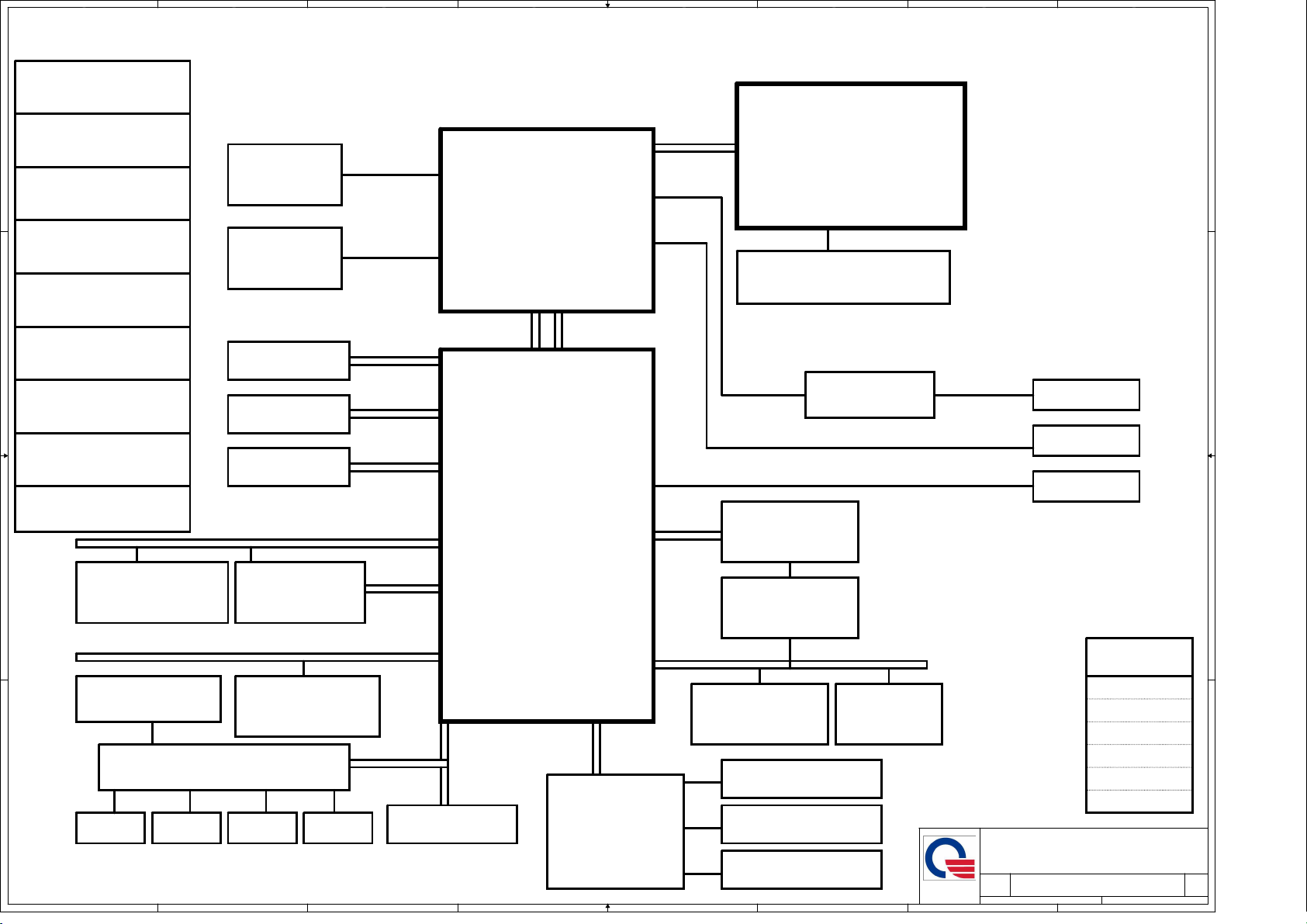

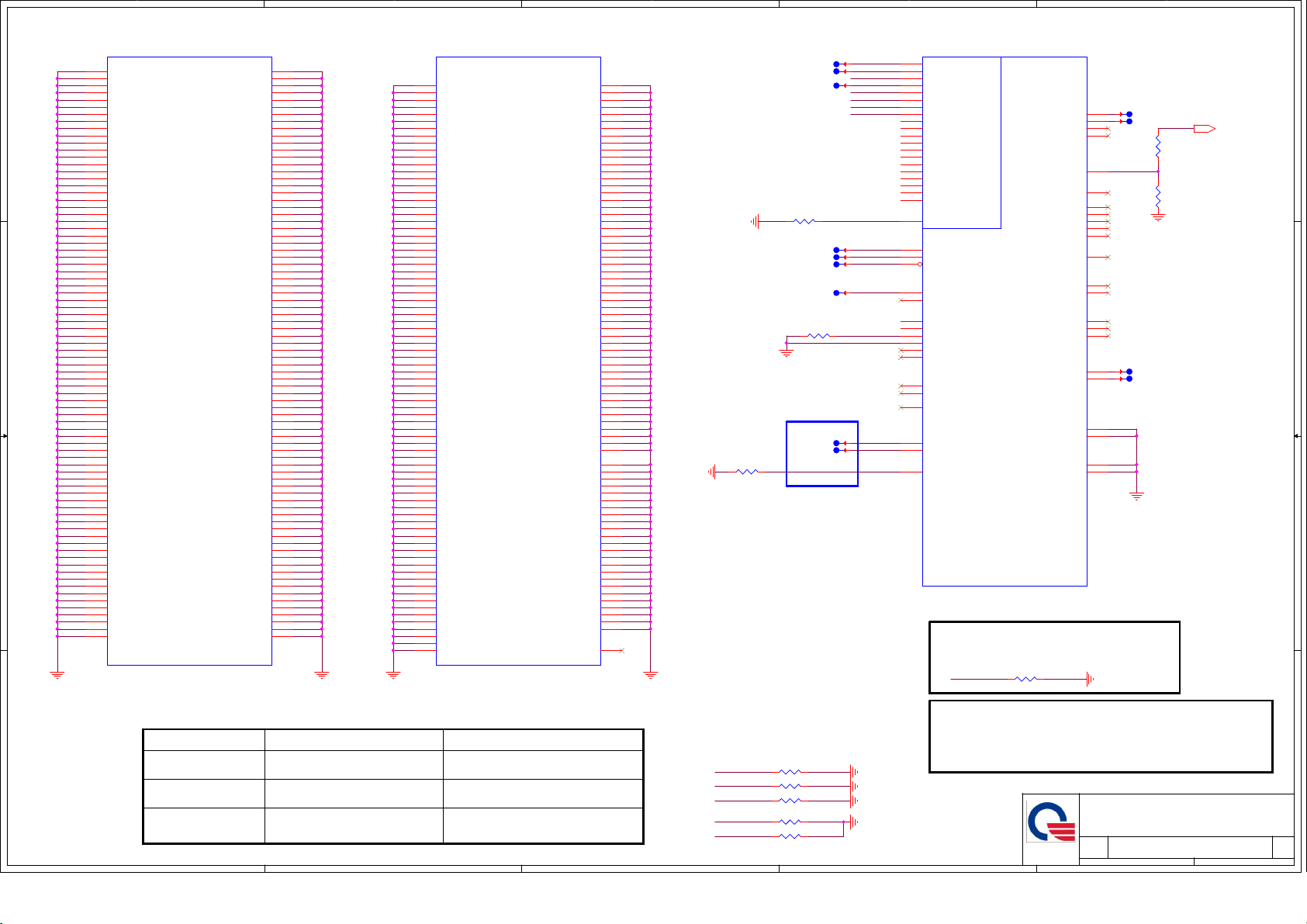

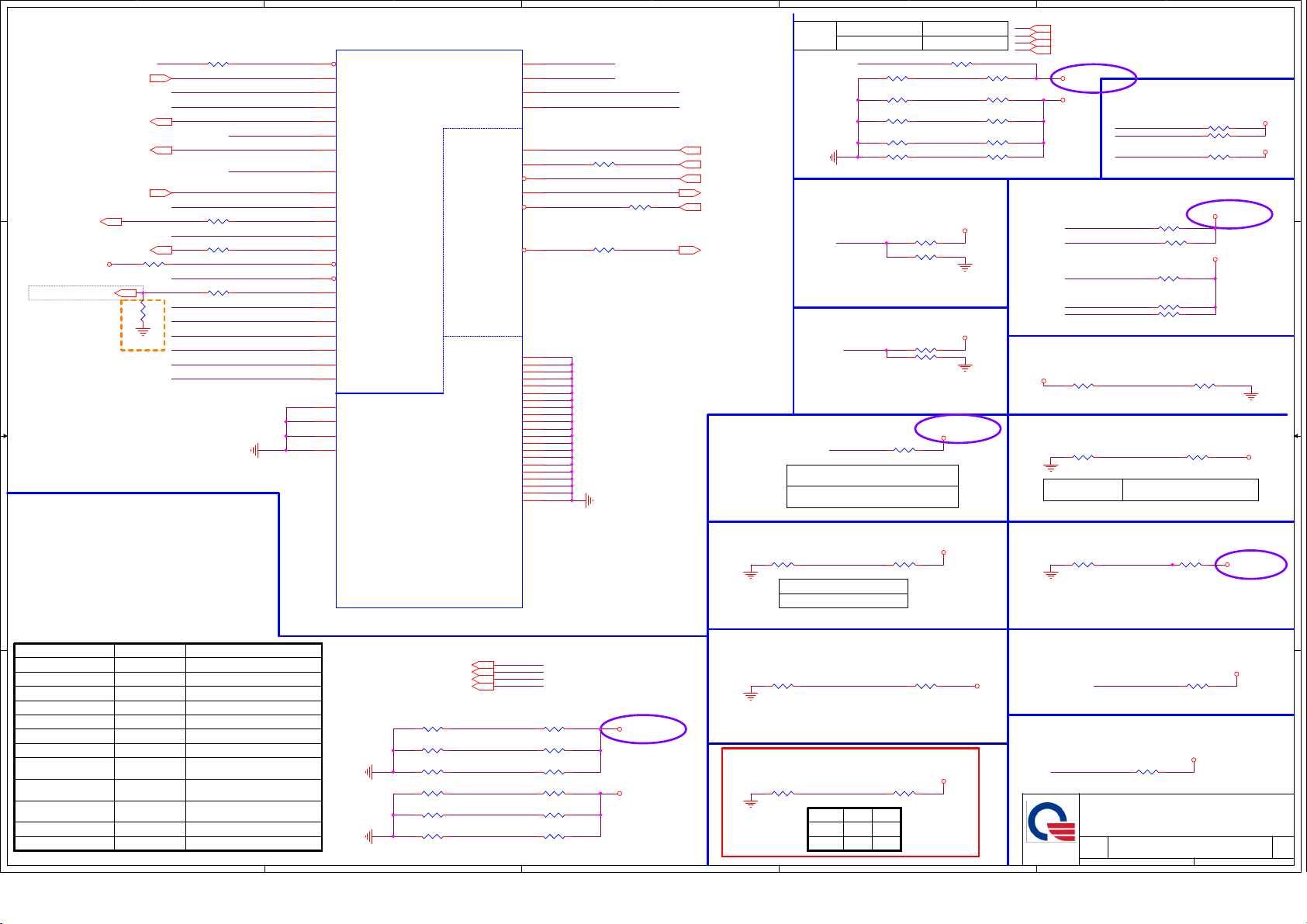

TWS Shark Bay DIAGRAM

01

+3V/+5V S5

A A

+1.05V

CPU Core

DDR3L

Charge

B B

Dis-Charge

+VGACORE

+1.5V_GFX

+1.05V_GFX/3V_GFX

C C

D D

PG.34

PG.35

PG.38~39

PG.36

PG.33

PG.37

PG.40

PG.41

PG.42

LANE2 LANE1

LAN

RTL8111GS-CG

GbE

Accelerometer

PG.24

SMBUS

KBC

IT8528E

TPKB

PG.32PG.27 PG.32PG.31

SODIMM1

Max. 4GB

PG.12

SODIMM2

Max. 4GB

PG.13

HDD

ODD

PG.32

PG.32

mSATA

PG.32

PCI-E x 1

WLAN

BT COMBO

PG.29PG.30

PCI-E x 1

LANE3

Card Reader

5227-GRT

PG.31

FANROM

1600MT/s

DDR3 L

Channel A

1600MT/s

DDR3 L

Channel B

SATA0 6GB/s

SATA0

SATA4 3GB/s

SATA4

SATA1 6GB/s

SATA1

USB 2.0

PORT10

PG.25

TPM

SLB9635TT1.2

LPC

INTEL

Haswell

Processor : Daul / Quad Core

Power : 37 / 47 (Watt)

Package : rPGA947

Size : 37.5 x 37.5 (mm)

PG.2~5

FDI

DMI

INTEL PCH

Lynx Point

Power : 3.5 Watt

Package : FCBGA695

Size : 20 x 20 (mm)

PG.6~11

AUDIO

CODEC

PCI-E x8

eDP (5.4Gb/s)

DDI (5.4Gb/s)

CRT

USB 3.0

PORT1

USB 2.0

USB2.0

Ports X2

DP Port B

USB3.0 Ports

X1

USB Charge

SLG55583A

Speaker

HP/MIC

ALC282-CG

Analog MIC

1

2

PG.26

3

4

5

nVIDIA

N14P-GS

GB4128

FCBGA908

29mm X 29mm

PG.14~18

DDR3 900MHz

VRAM

128Mx16x8,128bit

eDP

PORT0

RTD 2136S

DP to LVDS Converter

PG.27

DRE rof

DRE rof

PORT9,11

PG.26

PG.27

Webcam

DRE rof

PG.26

PG.26

PG.26

6

PG.19~20

PAGE 22

PORT4

PG.23

LVDS Interface

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Custom

Custom

NB5

NB5

NB5

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

LVDS

HDMI

CRT

PG.23

PG.21

PG.21

Stackup

TOP

GND

IN1

IN2

VCC

BOT

PROJECT : TWS

PROJECT : TWS

PROJECT : TWS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

DRE rof

1 43Friday, August 16, 2013

1 43Friday, August 16, 2013

1 43Friday, August 16, 2013

8

DRE rof

1A

1A

1A

5

4

3

2

1

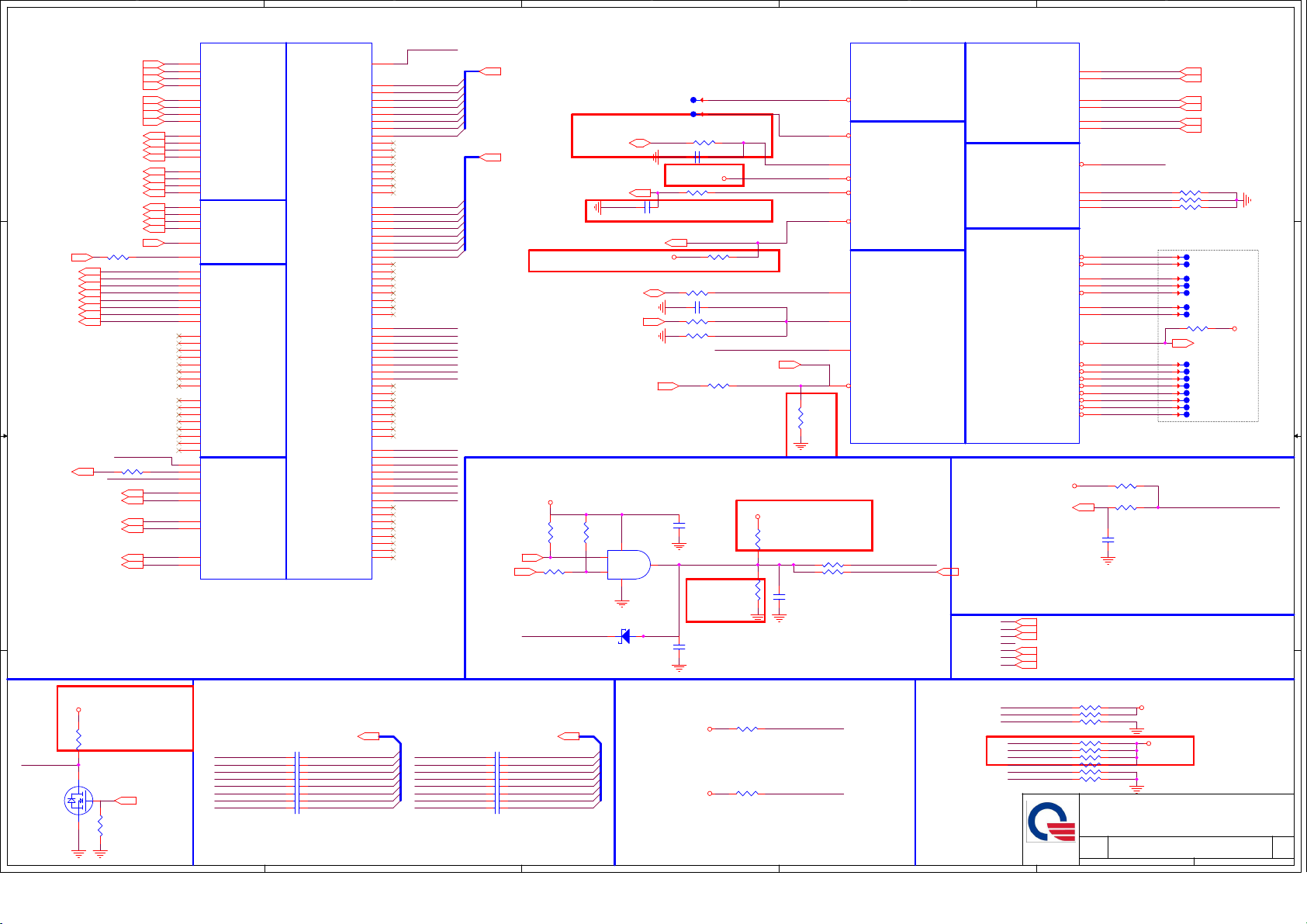

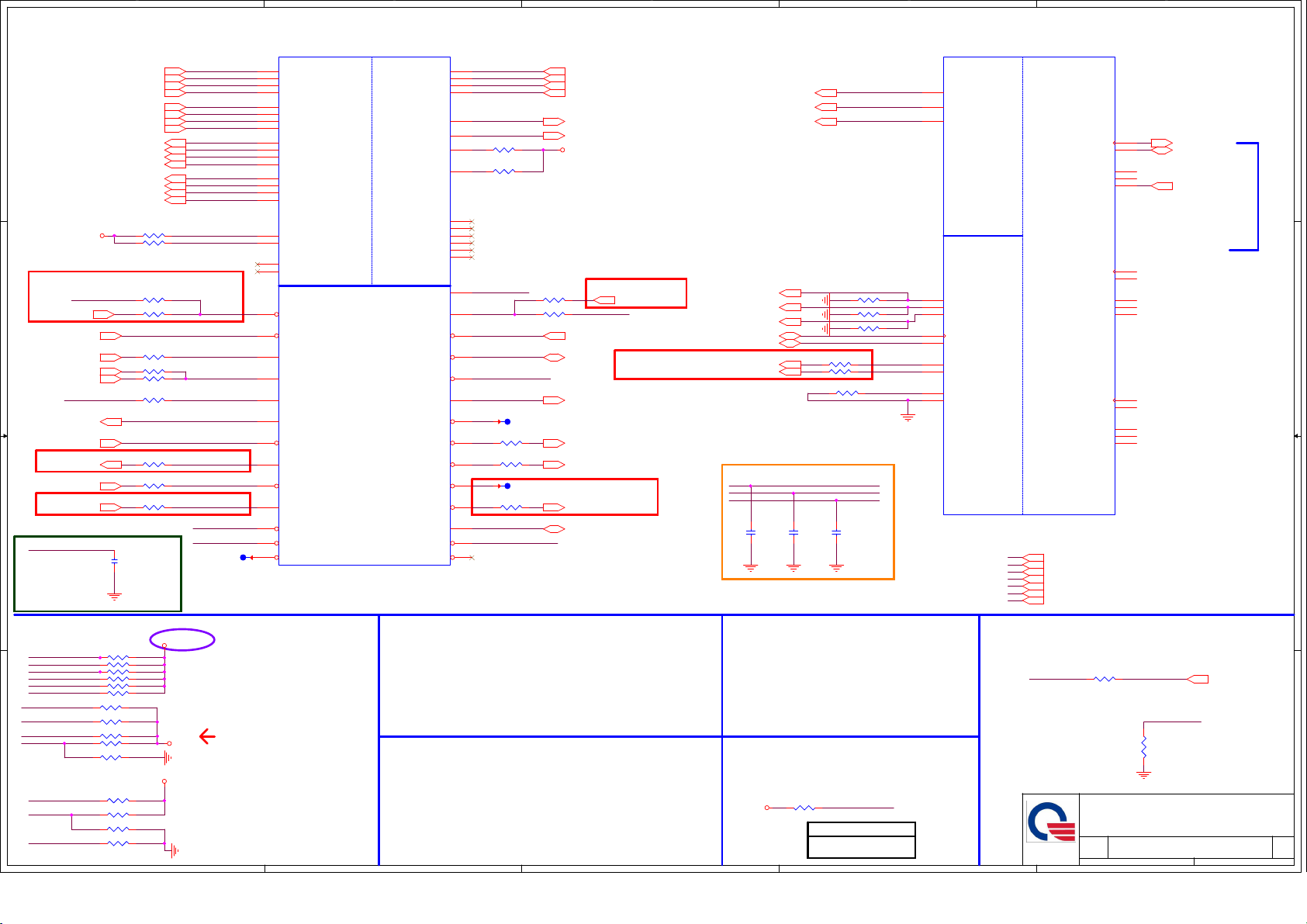

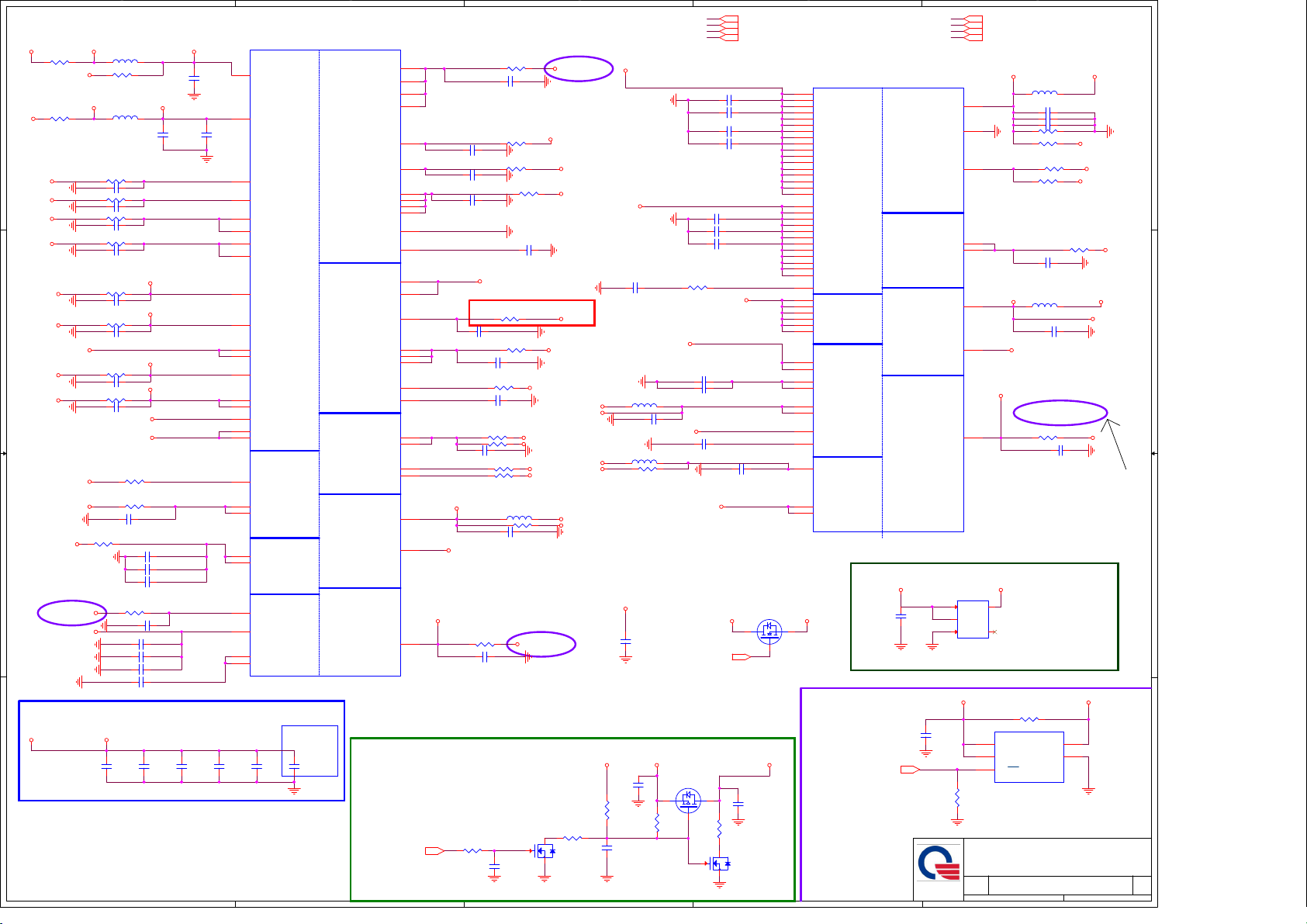

Haswell Processor (DMI,PEG,FDI) Haswell Processor (CLK,MISC,JTAG)

DRE rof

U23A

DMI_TXN 06

DMI_TXN 16

DMI_TXN 26

DMI_TXN 36

DMI_TXP 06

DMI_TXP 16

D D

FDI_CSYNC6

IN_D2#21

IN_D1#21

IN_D0#21

IN_CLK#21

IN_D221

IN_D121

IN_D021

C C

B B

A A

IN_CLK21

FDI_CSYN C & FDI_I NT

Trace len gth < 10000 Mils

Impenda nce = 50 ohm

EDP_DIS P_UTIL

+VCCIO_O UT

INT_eDP_H PD_Q

Q7

2N7002

DMI_TXP 26

DMI_TXP 36

DMI_RX N06

DMI_RX N16

DMI_RX N26

DMI_RX N36

DMI_RX P06

DMI_RX P16

DMI_RX P26

DMI_RX P36

FDI_TXN 06

FDI_TXN 16

FDI_TXP 06

FDI_TXP 16

FDI_INT6

R102 *0_4/S

DPB_LA NE0_N

DPB_LA NE1_N

DPB_LA NE2_N

DPB_LA NE3_N

DPB_LA NE0_P

DPB_LA NE1_P

DPB_LA NE2_P

DPB_LA NE3_P

eDP_RCO MP

R71 *0_4

INT_eDP_H PD_Q

EDP_AU XP22

EDP_AU XN22

EDP_TX P022

EDP_TX P122

EDP_TX N022

EDP_TX N122

4/30 C RB V1.0 -> 10K

R75

10K_4

3

2

R68

1

100K_4

5

D21

C21

B21

A21

D20

C20

B20

A20

D18

C17

B17

A17

D17

C18

B18

A18

P33

N32

R33

P32

J29

H29

FDI_CSYNC _R

T28

T30

U29

U31

U28

U30

V29

V31

T34

U35

U32

U33

U34

V35

T32

V33

P29

N28

P31

N30

R29

P28

R31

P30

E24

R27

P27

N27

EDP_AU XP

M27

EDP_AU XN

R35

EDP_TX P0

P34

EDP_TX P1

P35

EDP_TX N0

N34

EDP_TX N1

EDP_HP D 22,23

DMI_RX #[0]

DMI_RX #[1]

DMI_RX #[2]

DMI_RX #[3]

DMI_RX [0]

DMI_RX [1]

DMI_RX [2]

DMI_RX [3]

DMI_TX #[0]

DMI_TX #[1]

DMI_TX #[2]

DMI_TX #[3]

DMI_TX [0]

DMI_TX [1]

DMI_TX [2]

DMI_TX [3]

FDI_TX# [0]

FDI_TX# [1]

FDI_TX[ 0]

FDI_TX[ 1]

FDI_INT

FDI_CSY NC

DDIB_TX #[0]

DDIB_TX #[1]

DDIB_TX #[2]

DDIB_TX #[3]

DDIB_TX [0]

DDIB_TX [1]

DDIB_TX [2]

DDIB_TX [3]

DDIC_TX #[0]

DDIC_TX #[1]

DDIC_TX #[2]

DDIC_TX #[3]

DDIC_TX [0]

DDIC_TX [1]

DDIC_TX [2]

DDIC_TX [3]

DDID_TX #[0]

DDID_TX #[1]

DDID_TX #[2]

DDID_TX #[3]

DDID_TX [0]

DDID_TX [1]

DDID_TX [2]

DDID_TX [3]

eDP_RCO MP

EDP_DIS P_UTIL

eDP_HPD

eDP_AUX

eDP_AUX #

eDP_TX[ 0]

eDP_TX[ 1]

eDP_TX# [0]

eDP_TX# [1]

HSW_ RPGA_EDS_P GA

PEG_R COMPO

PEG_R X#[0]

PEG_R X#[1]

PEG_R X#[2]

PEG_R X#[3]

PEG_R X#[4]

PEG_R X#[5]

PEG_R X#[6]

PEG_R X#[7]

PEG_R X#[8]

DMI

Intel(R) DDI FDI

eDP

PEG_R X#[10]

PEG_R X#[11]

PEG_R X#[12]

PEG_R X#[13]

PEG_R X#[14]

PEG_R X#[15]

PEG_TX #[10]

PEG_TX #[11]

PEG_TX #[12]

PEG_TX #[13]

PEG_TX #[14]

PEG_TX #[15]

PCI EXPRESS* - GRAPHICS

PEG_R X#[9]

PEG_R X[0]

PEG_R X[1]

PEG_R X[2]

PEG_R X[3]

PEG_R X[4]

PEG_R X[5]

PEG_R X[6]

PEG_R X[7]

PEG_R X[8]

PEG_R X[9]

PEG_R X[10]

PEG_R X[11]

PEG_R X[12]

PEG_R X[13]

PEG_R X[14]

PEG_R X[15]

PEG_TX #[0]

PEG_TX #[1]

PEG_TX #[2]

PEG_TX #[3]

PEG_TX #[4]

PEG_TX #[5]

PEG_TX #[6]

PEG_TX #[7]

PEG_TX #[8]

PEG_TX #[9]

PEG_TX [0]

PEG_TX [1]

PEG_TX [2]

PEG_TX [3]

PEG_TX [4]

PEG_TX [5]

PEG_TX [6]

PEG_TX [7]

PEG_TX [8]

PEG_TX [9]

PEG_TX [10]

PEG_TX [11]

PEG_TX [12]

PEG_TX [13]

PEG_TX [14]

PEG_TX [15]

PEG x8 disable (UMA only remove)

PEG_TX[0 ..7]14 PEG_TX# [0..7]14

C_PEG_T X0

C_PEG_T X1

C_PEG_T X2

C_PEG_T X3

C_PEG_T X4

C_PEG_T X5

C_PEG_T X6

C_PEG_T X7

C146 0.22U/10V_4

C135 0.22U/10V_4

C144 0.22U/10V_4

C137 0.22U/10V_4

C133 0.22U/10V_4

C147 0.22U/10V_4

C138 0.22U/10V_4

C149 0.22U/10V_4

0.22uF AC couplin g Caps fo r PCIE GEN1/2/3 0.22uF AC couplin g Caps for PCIE GEN1/2/3

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

E23

M29

K28

M31

L30

M33

L32

M35

L34

E29

D28

E31

D30

E35

D34

E33

E32

L29

L28

L31

K30

L33

K32

L35

K34

F29

E28

F31

E30

F35

E34

F33

D32

H35

H34

J33

H32

J31

G30

C33

B32

B31

A30

B29

A28

B27

A26

B25

A24

J35

G34

H33

G32

H31

H30

B33

A32

C31

B30

C29

B28

C27

B26

C25

B24

PEG_RX# 0

PEG_RX# 1

PEG_RX# 2

PEG_RX# 3

PEG_RX# 4

PEG_RX# 5

PEG_RX# 6

PEG_RX# 7

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

C_PEG_T X#0

C_PEG_T X#1

C_PEG_T X#2

C_PEG_T X#3

C_PEG_T X#4

C_PEG_T X#5

C_PEG_T X#6

C_PEG_T X#7

C_PEG_T X0

C_PEG_T X1

C_PEG_T X2

C_PEG_T X3

C_PEG_T X4

C_PEG_T X5

C_PEG_T X6

C_PEG_T X7

4

PEG_COM P

C_PEG_T X#0

C_PEG_T X#1

C_PEG_T X#2

C_PEG_T X#3

C_PEG_T X#4

C_PEG_T X#5

C_PEG_T X#6

C_PEG_T X#7

PEG_RX# [0..7] 14

H_PECI (5 0ohm)

Route o n microstri p only

Spacing > 18 mil s

Trace Le ngth: 15 inch

HPECI Ra,Ca need placement clos e to EC.

PEG_RX[0 ..7] 14

THERMT RIP# (50ohm)

Trace Le ngth: 1. 1~12 inch es

Rb need placment near PCH

4/30 CRB 1.0 Add

PM_SYNC (50ohm)

Trace Le ngth: 1~ 11.25 inches

H_PWRGO OD (50oh m)

Trace Le ngth: 1~ 11.25 inches

EC_PEC I9,3 1

PROCHOT # (50ohm)

Trace Le ngth < 11 inches

H_PROC HOT#31,38

C73

Cb

47P/50V_4

PM_THR MTRIP#R9,31

PM_SYNC6

H_PW RGOOD9

CPU RESET#

PLTRST #8,14,24,25,29 ,30,31

CPU_PLT RST# (50ohm)

Trace Le ngth: 10~ 17 inches

SM_DRAMPWROK Processor Input.

DDR_VR _PWRGD36

SYS_PW ROK6

PM_DRAM_P WRGD (50o hm)

Trace Le ngth: 2~ 7 inches

DDR_VR_PW RGD (50oh m)

Trace Le ngth: 2~ 7 inches

C145 0.22U/10V_4

C134 0.22U/10V_4

C143 0.22U/10V_4

C136 0.22U/10V_4

C132 0.22U/10V_4

C148 0.22U/10V_4

C131 0.22U/10V_4

C139 0.22U/10V_4

R141 *0_4

R141

DDR_VR _PWRGD

+3VS5

R143

100K_4

2013/02/ 20

PEG_TX# 0

PEG_TX# 1

PEG_TX# 2

PEG_TX# 3

PEG_TX# 4

PEG_TX# 5

PEG_TX# 6

PEG_TX# 7

PM_DRAM_P WRGD_C (50o hm)

Trace Le ngth: < 1 inches

R142

100K_4

U7

2

1

74AHC1 G09GW

3 5

D11 *MEK500 V-40

Ra

Ca

+VCCST

SKTOCC #

TP_CAT ERR#

H_PECI

H_PROC HOT#_R

TP70

TP62

R514 43_4

C602 *47P/50V_4

4/30 CRB 1.0 Add

R124 56.2/F_4

Cb need placment near VR

PM_THR MTRIP#_R

R196 *1K/F_4

+1.05V

R512 *0_4/S

C214 *0.1U/10V_4

R106 *0_4/S

R101 10K_4

R517 *750/F_4

To cha nge the resistor va lues in the DRAMPWROK logic to red uce the

leakage on VDD PWRGO OD

C265

0.1U/10V_ 4

4

PM_DR AM_PWRG D_C

DG 498 556 -> 3.3K

C269

*0.1U/10V_ 4

Rb

PM_SYNC _R

H_PW RGOOD_R

PM_DR AM_PWRG D_R

CPU_PL TRST#R9,31

CPU_PL TRST#R

+1.35VSU S

R133

1.8K/F_4

R132

3.3K_4

DG 498 556 -> 1.8K

R134 0_4

R137 *0_4

C271

*0.1U/10V_ 4

DP & PEG Compensation

+VCCIOA _OUT

+VCCIOA _OUT

3

R112 24.9/F_4

eDP_RCOM P

Trace len gth < 100 Mils

Trace Wid th 20 Mils Trac e Spacing 25 Mils

R118 24.9/F_4

PEG_RCO MP

Trace len gth < 400 MILS

Trace wi dth = 12 MILS

Trace sp acing = 15 MILS

eDP_RCO MP

PEG_COM P

U23B

AP32

SKTOC C#

AN32

CATER R#

AR27

PECI

AK31

FC_AK3 1

AM30

PROCH OT#

AM35

THERM TRIP#

AT28

PM_SY NC

AL34

UNCOR EPWRG OOD

AC10

SM_DR AMPWR OK

AT26

RESET#

R516

*1.5K/F_4

HSW_ RPGA_EDS_P GA

PM_DR AM_PWRG D_R

PM_DR AM_PWRG D

PM_DRAM_P WRGD_R (50o hm)

Trace Le ngth: 0. 5~1 inche s

DRE rof

SSC_DP LL_REF_CLK

MISC

SSC_DP LL_REF_CLK #

DPLL_R EF_CLK

DPLL_R EF_CLK#

CLOCKS

SM_DR AMRST#

SM_RC OMP[0]

SM_RC OMP[1]

SM_RC OMP[2]

DDR3

MISC

THERMALPWR MANAGEMENT

JTAG & BPM

DDR3_DRAMRS T#_R (50ohm)

Trace Le ngth < 6 inches

PM_DR AM_PWRG D 6

Processor pull-up (CPU)

2

+1.35VSU S

DDR3_D RAMRST#12,13

+VCCIO_O UT 4,38

+VCCIOA _OUT 4

+1.05V 4 ,9,10,27,35,42

+1.35VSU S 4,12,13,36

+3VS5 6,7,9,1 0,24,27,28,29,31,34,3 6,37,42

+3V 6,7,8,9,10,1 2,13,14,17,21,22,23,2 4,25,26,28,29,30,31 ,32,37,38,40

H_PROC HOT#

CLK_DP LL_SSCLKP

CLK_DP LL_SSCLKN

XDP_TD O

XDP_TM S

XDP_TD I_R

XDP_PR EQ#

XDP_TC LK

XDP_TR ST#

NB5

NB5

NB5

Host CLK :

Trace len gth < 11000 MIL S

Trace sp acing = 15 ,20 MIL S, Impendence 9 0 ohm

E26

BCLK

BCLK#

PRDY#

PREQ#

TRST#

DBR#

BPM#[0 ]

BPM#[1 ]

BPM#[2 ]

BPM#[3 ]

BPM#[4 ]

BPM#[5 ]

BPM#[6 ]

BPM#[7 ]

CLK_CP U_BCLKP

D26

CLK_CP U_BCLKN

E27

CLK_DP LL_SSCLKP

F27

CLK_DP LL_SSCLKN

H28

CLK_DP LL_NSCCLKP

G28

CLK_DP LL_NSCCLKN

AN3

CPU_DR AMRST#

AP3

SM_RC OMP_0

AR3

SM_RC OMP_1

AP2

SM_RC OMP_2

SM_RCOM P[0] W:12mils/S:15mi ls/L: 500mils,

SM_RCOM P[1] W:12mils/S:15mi ls/L: 500mils,

SM_RCOM P[2] W:12mils/S:15mi ls/L: 500mils,

AR29

XDP_PR DY#

AT29

XDP_PR EQ#

AM34

XDP_TC LK

TCK

AN33

XDP_TM S

TMS

AM33

XDP_TR ST#

AM31

XDP_TD I_R

TDI

AL33

XDP_TD O

TDO

AP33

XDP_DB RST#

AR30

XDP_BP M0

AN31

XDP_BP M1

AN29

XDP_BP M2

AP31

XDP_BP M3

AP30

XDP_BP M4

AN28

XDP_BP M5

AP29

XDP_BP M6

AP28

XDP_BP M7

R153 100/F_4

R157 75/F_4

R158 100/F_4

R582 *1K_4

DDR3 DRAM RESET

R160 *1K_4

R159 *0_4/S

C289

*0.1U/10V_ 4

DRE rof

R123 62_4

R105 *10K_4

R99 *10K_4

R115 51_4

R110 *51_4

R120 *51_4

R519 *51_4

R90 51_ 4

R97 51_ 4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

+VCCIO_O UT

+1.05V

check

PROJECT : TWS

PROJECT : TWS

PROJECT : TWS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

HAS 1/4 (PCIE& DMI&FDI )

HAS 1/4 (PCIE& DMI&FDI )

HAS 1/4 (PCIE& DMI&FDI )

1

02

CLK_CP U_BCLKP 8

CLK_CP U_BCLKN 8

CLK_DP LL_SSCLKP 8

CLK_DP LL_SSCLKN 8

CLK_DP LL_NSCCLKP 8

CLK_DP LL_NSCCLKN 8

TP73

CPU XDP

TP72

TP7

TP10

TP9

TP12

TP11

+3V

XDP_DB RST# 6

TP64

TP71

TP74

TP63

TP66

TP75

TP69

TP67

CPU_DR AMRST#

DRE rof

2 43Friday, August 16, 201 3

2 43Friday, August 16, 201 3

2 43Friday, August 16, 201 3

1A

1A

1A

5

4

3

2

1

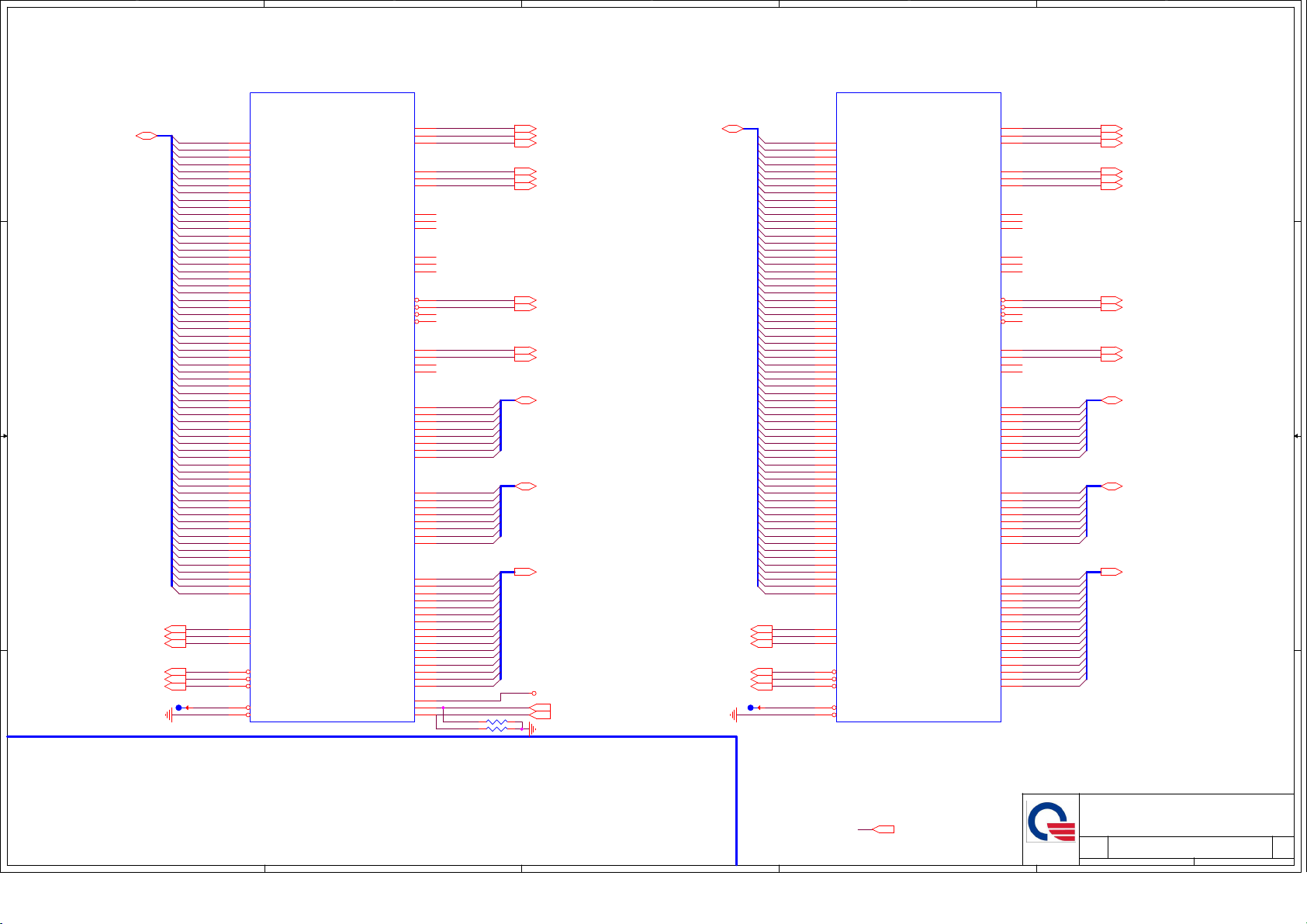

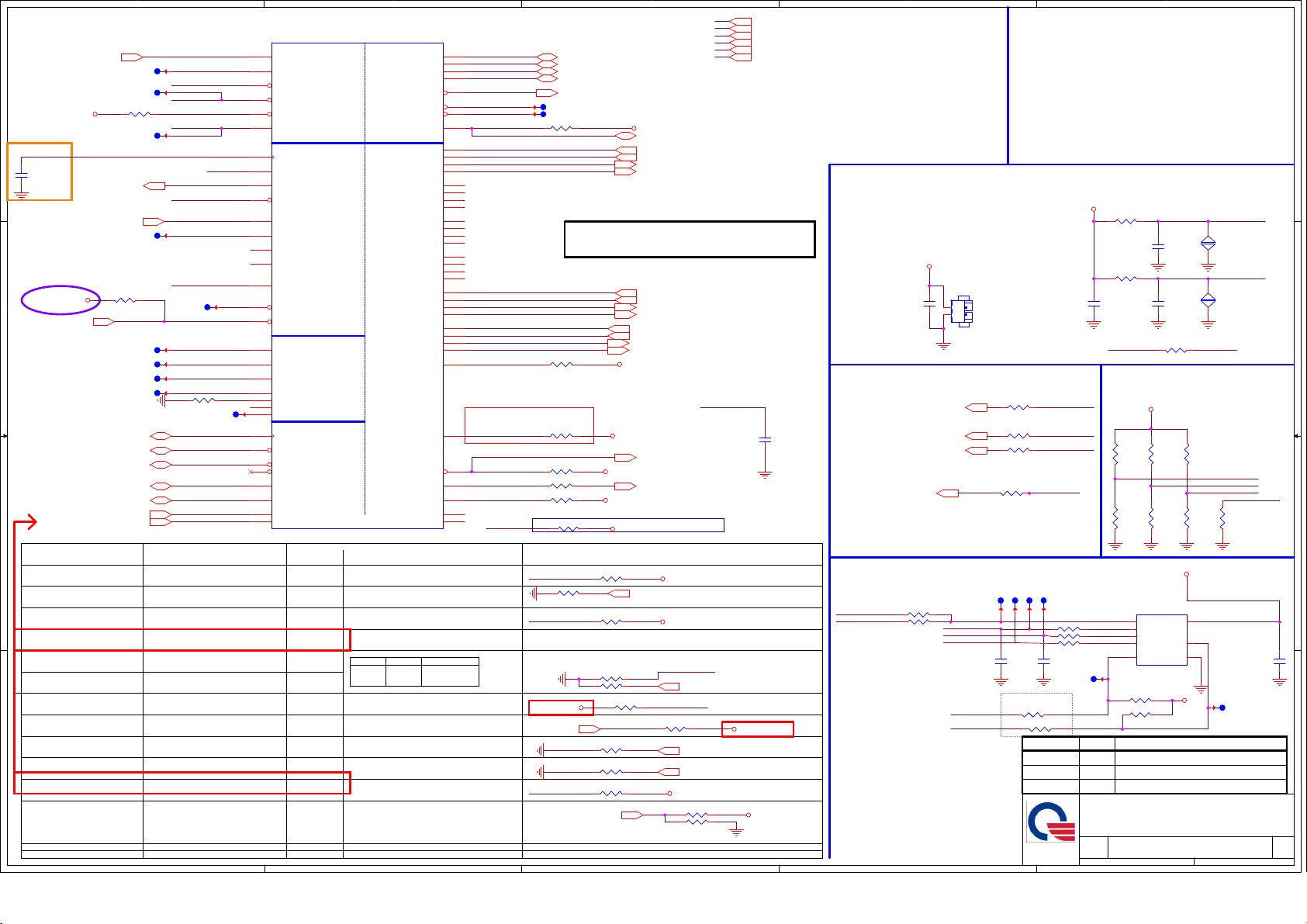

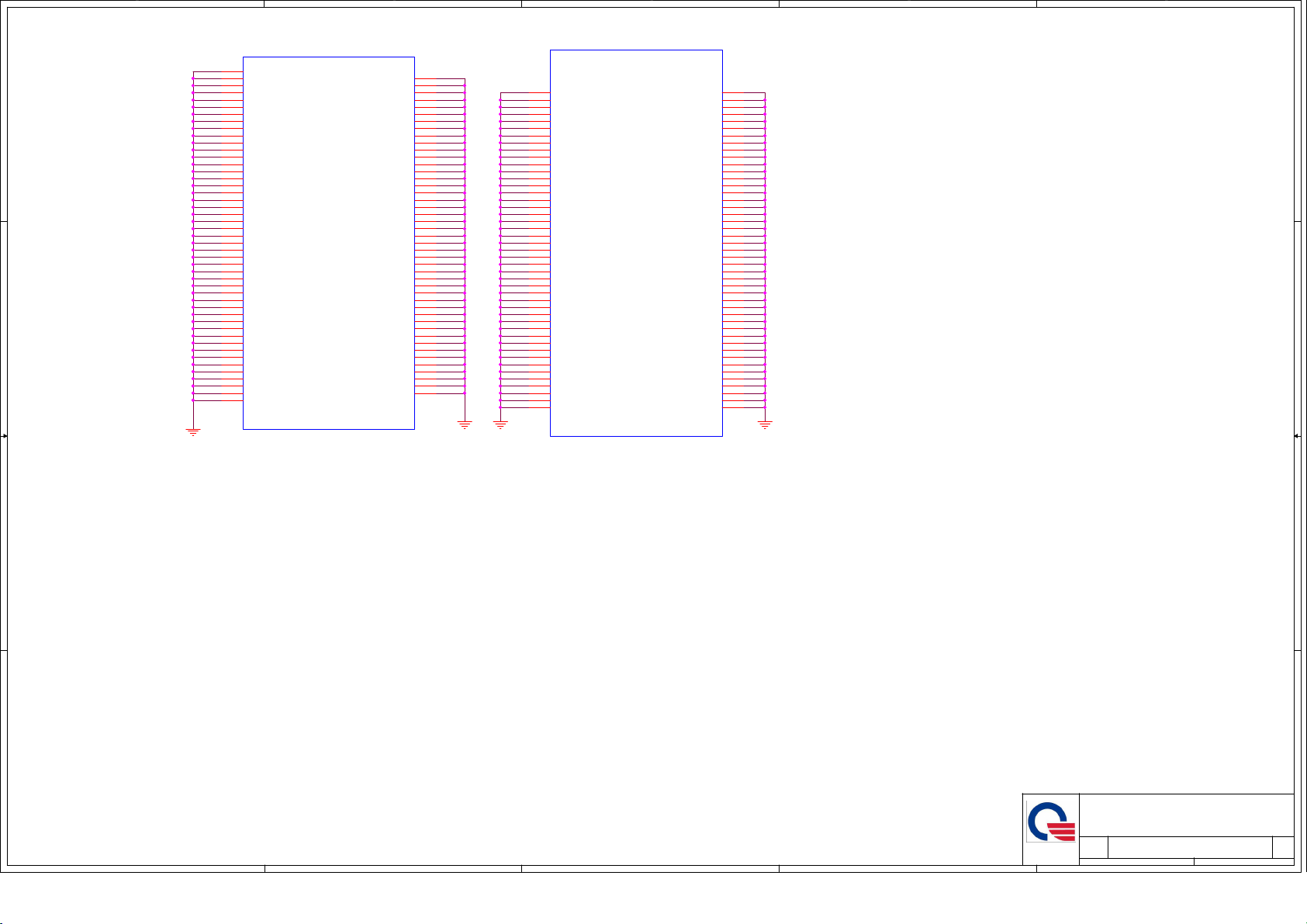

Haswell Processor (DDR3)

U23C

D D

M_A_DQ [63:0]12

C C

B B

M_A_BS #012

M_A_BS #112

M_A_BS #212

M_A_CA S#12

M_A_RA S#12

M_A_W E#12

TP16

RSVD_V 10 must be groun ded

CPU SM_VREF

A A

M_A_DQ 0

M_A_DQ 1

M_A_DQ 2

M_A_DQ 3

M_A_DQ 4

M_A_DQ 5

M_A_DQ 6

M_A_DQ 7

M_A_DQ 8

M_A_DQ 9

M_A_DQ 10

M_A_DQ 11

M_A_DQ 12

M_A_DQ 13

M_A_DQ 14

M_A_DQ 15

M_A_DQ 16

M_A_DQ 17

M_A_DQ 18

M_A_DQ 19

M_A_DQ 20

M_A_DQ 21

M_A_DQ 22

M_A_DQ 23

M_A_DQ 24

M_A_DQ 25

M_A_DQ 26

M_A_DQ 27

M_A_DQ 28

M_A_DQ 29

M_A_DQ 30

M_A_DQ 31

M_A_DQ 32

M_A_DQ 33

M_A_DQ 34

M_A_DQ 35

M_A_DQ 36

M_A_DQ 37

M_A_DQ 38

M_A_DQ 39

M_A_DQ 40

M_A_DQ 41

M_A_DQ 42

M_A_DQ 43

M_A_DQ 44

M_A_DQ 45

M_A_DQ 46

M_A_DQ 47

M_A_DQ 48

M_A_DQ 49

M_A_DQ 50

M_A_DQ 51

M_A_DQ 52

M_A_DQ 53

M_A_DQ 54

M_A_DQ 55

M_A_DQ 56

M_A_DQ 57

M_A_DQ 58

M_A_DQ 59

M_A_DQ 60

M_A_DQ 61

M_A_DQ 62

M_A_DQ 63

AR15

SA_DQ [0]

AT14

SA_DQ [1]

AM14

SA_DQ [2]

AN14

SA_DQ [3]

AT15

SA_DQ [4]

AR14

SA_DQ [5]

AN15

SA_DQ [6]

AM15

SA_DQ [7]

AM9

SA_DQ [8]

AN9

SA_DQ [9]

AM8

SA_DQ [10]

AN8

SA_DQ [11]

AR9

SA_DQ [12]

AT9

SA_DQ [13]

AR8

SA_DQ [14]

AT8

SA_DQ [15]

AJ9

SA_DQ [16]

AK9

SA_DQ [17]

AJ6

SA_DQ [18]

AK6

SA_DQ [19]

AJ10

SA_DQ [20]

AK10

SA_DQ [21]

AJ7

SA_DQ [22]

AK7

SA_DQ [23]

AF4

SA_DQ [24]

AF5

SA_DQ [25]

AF1

SA_DQ [26]

AF2

SA_DQ [27]

AG4

SA_DQ [28]

AG5

SA_DQ [29]

AG1

SA_DQ [30]

AG2

SA_DQ [31]

J1

SA_DQ [32]

J2

SA_DQ [33]

J5

SA_DQ [34]

H5

SA_DQ [35]

H2

SA_DQ [36]

H1

SA_DQ [37]

J4

SA_DQ [38]

H4

SA_DQ [39]

F2

SA_DQ [40]

F1

SA_DQ [41]

D2

SA_DQ [42]

D3

SA_DQ [43]

D1

SA_DQ [44]

F3

SA_DQ [45]

C3

SA_DQ [46]

B3

SA_DQ [47]

B5

SA_DQ [48]

E6

SA_DQ [49]

A5

SA_DQ [50]

D6

SA_DQ [51]

D5

SA_DQ [52]

E5

SA_DQ [53]

B6

SA_DQ [54]

A6

SA_DQ [55]

E12

SA_DQ [56]

D12

SA_DQ [57]

B11

SA_DQ [58]

A11

SA_DQ [59]

E11

SA_DQ [60]

D11

SA_DQ [61]

B12

SA_DQ [62]

A12

SA_DQ [63]

V5

SA_BS[ 0]

U5

SA_BS[ 1]

AD1

SA_BS[ 2]

U8

SA_CAS #

U6

SA_RAS #

U7

SA_W E#

AC7

RSCD_ AC7

V10

RSCD_ V10

HSW_ RPGA_EDS_P GA

DDR SYSTEM MEMORY A

SA_DIM M_VREFDQ

SB_DIM M_VREFDQ

SA_CLK [0]

SA_CLK #[0]

SA_CKE [0]

SA_CLK [1]

SA_CLK #[1]

SA_CKE [1]

SA_CLK [2]

SA_CLK #[2]

SA_CKE [2]

SA_CLK [3]

SA_CLK #[3]

SA_CKE [3]

SA_CS# [0]

SA_CS# [1]

SA_CS# [2]

SA_CS# [3]

SA_OD T[0]

SA_OD T[1]

SA_OD T[2]

SA_OD T[3]

SA_DQ S#[0]

SA_DQ S#[1]

SA_DQ S#[2]

SA_DQ S#[3]

SA_DQ S#[4]

SA_DQ S#[5]

SA_DQ S#[6]

SA_DQ S#[7]

SA_DQ S[0]

SA_DQ S[1]

SA_DQ S[2]

SA_DQ S[3]

SA_DQ S[4]

SA_DQ S[5]

SA_DQ S[6]

SA_DQ S[7]

SA_MA [0]

SA_MA [1]

SA_MA [2]

SA_MA [3]

SA_MA [4]

SA_MA [5]

SA_MA [6]

SA_MA [7]

SA_MA [8]

SA_MA [9]

SA_MA [10]

SA_MA [11]

SA_MA [12]

SA_MA [13]

SA_MA [14]

SA_MA [15]

SM_VR EF

V4

U4

AD9

V3

U3

AC9

V2

U2

AD8

V1

U1

AC8

M7

L9

M9

M10

M8

L7

L8

L10

AP15

M_A_DQ SN0

AP8

M_A_DQ SN1

AJ8

M_A_DQ SN2

AF3

M_A_DQ SN3

J3

M_A_DQ SN4

E2

M_A_DQ SN5

C5

M_A_DQ SN6

C11

M_A_DQ SN7

AP14

M_A_DQ SP0

AP9

M_A_DQ SP1

AK8

M_A_DQ SP2

AG3

M_A_DQ SP3

H3

M_A_DQ SP4

E3

M_A_DQ SP5

C6

M_A_DQ SP6

C12

M_A_DQ SP7

V8

M_A_A0

AC6

M_A_A1

V9

M_A_A2

U9

M_A_A3

AC5

M_A_A4

AC4

M_A_A5

AD6

M_A_A6

AC3

M_A_A7

AD5

M_A_A8

AC2

M_A_A9

V6

M_A_A1 0

AC1

M_A_A1 1

AD4

M_A_A1 2

V7

M_A_A1 3

AD3

M_A_A1 4

AD2

M_A_A1 5

AM3

+VREF_ CA_CPU

F16

SMDDR _VREF_DQ0_ M3

F13

SMDDR _VREF_DQ1_ M3

R536*1K_4

R540*1K_4

M_A_CL KP0 12

M_A_CL KN0 12

M_A_CK E0 12

M_A_CL KP1 12

M_A_CL KN1 12

M_A_CK E1 12

M_A_CS #0 12

M_A_CS #1 12

M_A_OD T0 12

M_A_OD T1 12

M_A_DQ SN[7:0] 12

M_A_DQ SP[7:0] 12

M_A_A[1 5:0] 12

+VREF_ CA_CPU

SMDDR _VREF_DQ0_ M3 12

SMDDR _VREF_DQ1_ M3 13

M_B_DQ [63:0]13

M_B_BS #013

M_B_BS #113

M_B_BS #213

M_B_CA S#13

M_B_RA S#13

M_B_W E#13

TP17

RSVD_R 10 must b e ground ed

M_B_DQ 0

M_B_DQ 1

M_B_DQ 2

M_B_DQ 3

M_B_DQ 4

M_B_DQ 5

M_B_DQ 6

M_B_DQ 7

M_B_DQ 8

M_B_DQ 9

M_B_DQ 10

M_B_DQ 11

M_B_DQ 12

M_B_DQ 13

M_B_DQ 14

M_B_DQ 15

M_B_DQ 16

M_B_DQ 17

M_B_DQ 18

M_B_DQ 19

M_B_DQ 20

M_B_DQ 21

M_B_DQ 22

M_B_DQ 23

M_B_DQ 24

M_B_DQ 25

M_B_DQ 26

M_B_DQ 27

M_B_DQ 28

M_B_DQ 29

M_B_DQ 30

M_B_DQ 31

M_B_DQ 32

M_B_DQ 33

M_B_DQ 34

M_B_DQ 35

M_B_DQ 36

M_B_DQ 37

M_B_DQ 38

M_B_DQ 39

M_B_DQ 40

M_B_DQ 41

M_B_DQ 42

M_B_DQ 43

M_B_DQ 44

M_B_DQ 45

M_B_DQ 46

M_B_DQ 47

M_B_DQ 48

M_B_DQ 49

M_B_DQ 50

M_B_DQ 51

M_B_DQ 52

M_B_DQ 53

M_B_DQ 54

M_B_DQ 55

M_B_DQ 56

M_B_DQ 57

M_B_DQ 58

M_B_DQ 59

M_B_DQ 60

M_B_DQ 61

M_B_DQ 62

M_B_DQ 63

U23D

AR18

SB_DQ [0]

AT18

SB_DQ [1]

AM17

SB_DQ [2]

AM18

SB_DQ [3]

AR17

SB_DQ [4]

AT17

SB_DQ [5]

AN17

SB_DQ [6]

AN18

SB_DQ [7]

AT12

SB_DQ [8]

AR12

SB_DQ [9]

AN12

SB_DQ [10]

AM11

SB_DQ [11]

AT11

SB_DQ [12]

AR11

SB_DQ [13]

AM12

SB_DQ [14]

AN11

SB_DQ [15]

AR5

SB_DQ [16]

AR6

SB_DQ [17]

AM5

SB_DQ [18]

AM6

SB_DQ [19]

AT5

SB_DQ [20]

AT6

SB_DQ [21]

AN5

SB_DQ [22]

AN6

SB_DQ [23]

AJ4

SB_DQ [24]

AK4

SB_DQ [25]

AJ1

SB_DQ [26]

AJ2

SB_DQ [27]

AM1

SB_DQ [28]

AN1

SB_DQ [29]

AK2

SB_DQ [30]

AK1

SB_DQ [31]

L2

SB_DQ [32]

M2

SB_DQ [33]

L4

SB_DQ [34]

M4

SB_DQ [35]

L1

SB_DQ [36]

M1

SB_DQ [37]

L5

SB_DQ [38]

M5

SB_DQ [39]

G7

SB_DQ [40]

J8

SB_DQ [41]

G8

SB_DQ [42]

G9

SB_DQ [43]

J7

SB_DQ [44]

J9

SB_DQ [45]

G10

SB_DQ [46]

J10

SB_DQ [47]

A8

SB_DQ [48]

B8

SB_DQ [49]

A9

SB_DQ [50]

B9

SB_DQ [51]

D8

SB_DQ [52]

E8

SB_DQ [53]

D9

SB_DQ [54]

E9

SB_DQ [55]

E15

SB_DQ [56]

D15

SB_DQ [57]

A15

SB_DQ [58]

B15

SB_DQ [59]

E14

SB_DQ [60]

D14

SB_DQ [61]

A14

SB_DQ [62]

B14

SB_DQ [63]

R7

SB_BS[ 0]

P8

SB_BS[ 1]

AA9

SB_BS[ 2]

P7

SB_CAS #

R6

SB_RAS #

P6

SB_W E#

AG8

RSVD_A G8

R10

RSVD_R 10

HSW_ RPGA_EDS_P GA

AA4

SB_CLK [0]

Y4

SB_CLK #[0]

AF10

SB_CKE [0]

AA3

SB_CLK [1]

Y3

SB_CLK #[1]

AG10

SB_CKE [1]

AA2

SB_CLK [2]

Y2

SB_CLK #[2]

AG9

SB_CKE [2]

AA1

SB_CLK [3]

Y1

SB_CLK #[3]

AF9

SB_CKE [3]

P4

SB_CS# [0]

R2

SB_CS# [1]

P3

SB_CS# [2]

P1

SB_CS# [3]

R4

SB_OD T[0]

R3

SB_OD T[1]

R1

SB_OD T[2]

P2

SB_OD T[3]

AP18

AP11

AP5

AJ3

L3

H9

C8

C14

AP17

AP12

AP6

AK3

M3

H8

C9

C15

R8

Y5

Y10

AA5

Y7

AA6

Y6

AA7

Y8

AA10

R9

Y9

AF7

P9

AA8

AG7

M_B_DQ SN0

M_B_DQ SN1

M_B_DQ SN2

M_B_DQ SN3

M_B_DQ SN4

M_B_DQ SN5

M_B_DQ SN6

M_B_DQ SN7

M_B_DQ SP0

M_B_DQ SP1

M_B_DQ SP2

M_B_DQ SP3

M_B_DQ SP4

M_B_DQ SP5

M_B_DQ SP6

M_B_DQ SP7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A1 0

M_B_A1 1

M_B_A1 2

M_B_A1 3

M_B_A1 4

M_B_A1 5

SB_DQ S#[0]

SB_DQ S#[1]

SB_DQ S#[2]

SB_DQ S#[3]

SB_DQ S#[4]

SB_DQ S#[5]

SB_DQ S#[6]

SB_DQ S#[7]

SB_DQ S[0]

SB_DQ S[1]

SB_DQ S[2]

SB_DQ S[3]

SB_DQ S[4]

SB_DQ S[5]

SB_DQ S[6]

SB_DQ S[7]

DDR SYSTEM MEMORY B

SB_MA [0]

SB_MA [1]

SB_MA [2]

SB_MA [3]

SB_MA [4]

SB_MA [5]

SB_MA [6]

SB_MA [7]

SB_MA [8]

SB_MA [9]

SB_MA [10]

SB_MA [11]

SB_MA [12]

SB_MA [13]

SB_MA [14]

SB_MA [15]

M_B_CL KP0 13

M_B_CL KN0 13

M_B_CK E0 13

M_B_CL KP1 13

M_B_CL KN1 13

M_B_CK E1 13

M_B_CS #0 13

M_B_CS #1 13

M_B_OD T0 13

M_B_OD T1 13

M_B_DQ SN[7:0] 13

M_B_DQ SP[7:0] 13

M_B_A[1 5:0] 13

03

PROJECT : TWS

PROJECT : TWS

PROJECT : TWS

Quanta Computer Inc.

Quanta Computer Inc.

+VREF_ CA_CPU 12

NB5

NB5

NB5

5

4

3

2

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

HAS 2/4 (DDR3 I/ F)

HAS 2/4 (DDR3 I/ F)

HAS 2/4 (DDR3 I/ F)

1

3 43Friday, August 16, 201 3

3 43Friday, August 16, 201 3

3 43Friday, August 16, 201 3

1A

1A

1A

5

4

3

2

1

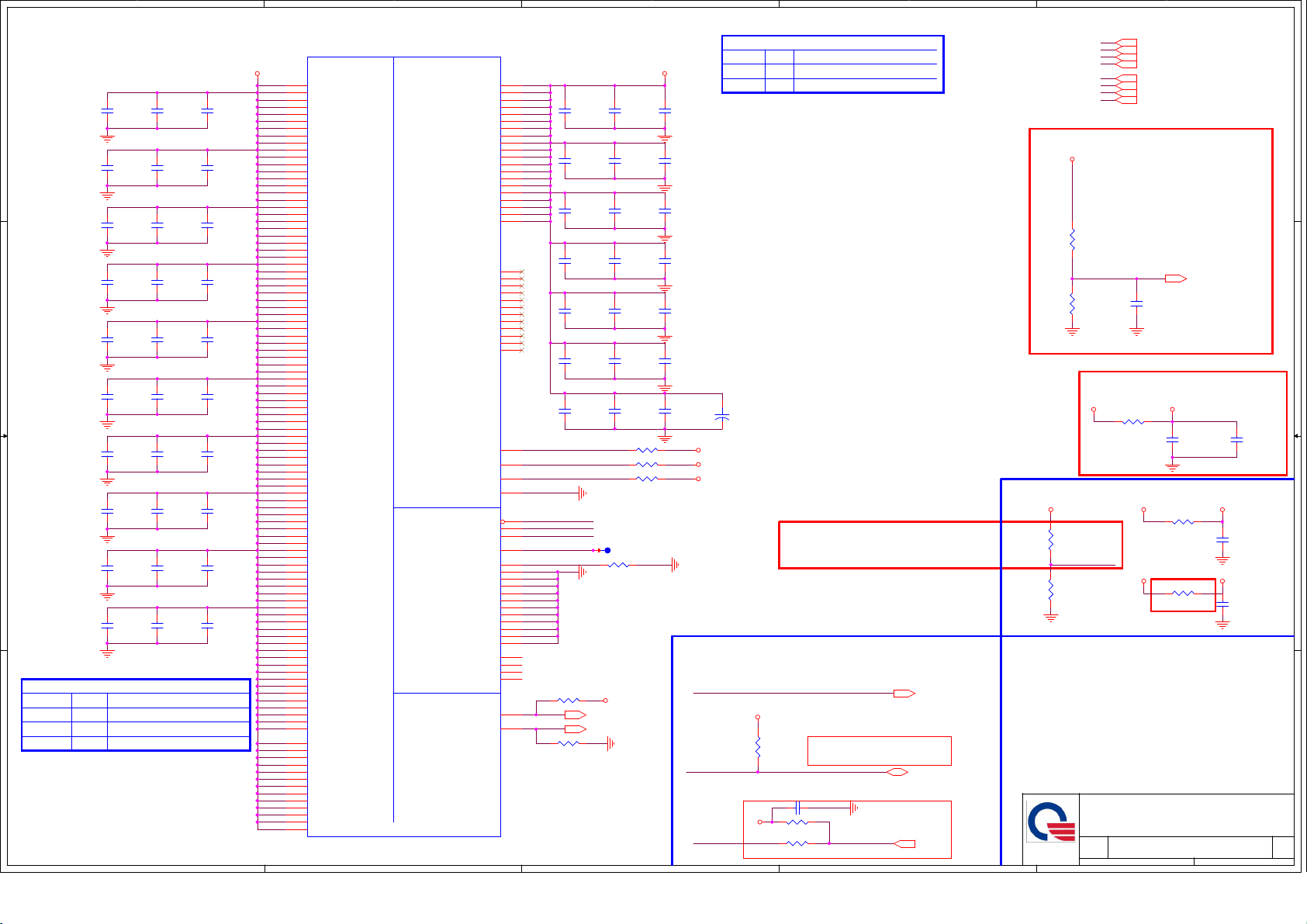

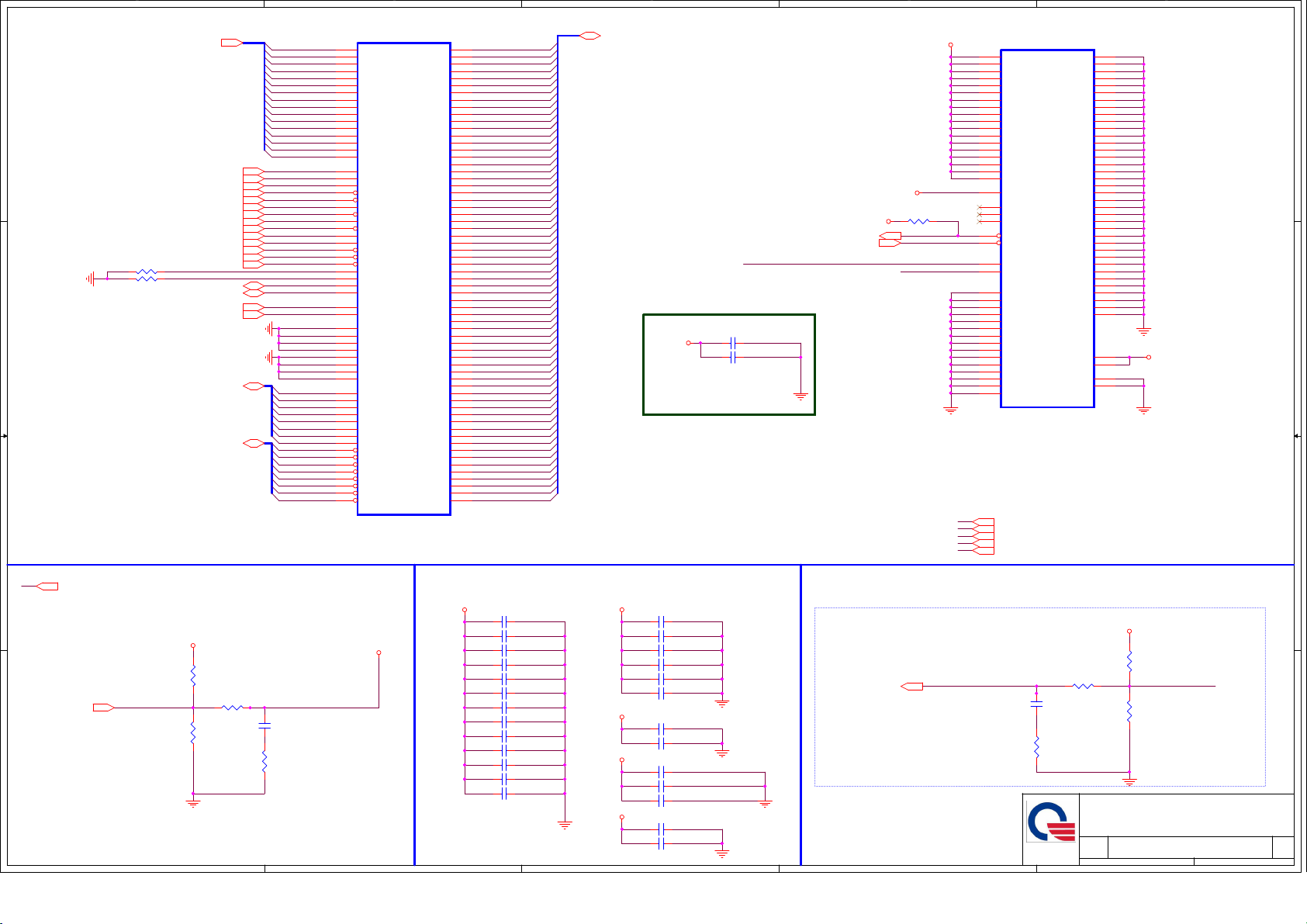

Haswell Processor (POWER)

U23F

+VCC_C ORE

D D

C C

B B

C615

22U/6.3VS _6

C236

22U/6.3VS _6

C606

22U/6.3VS _6

C622

22U/6.3VS _6

C607

22U/6.3VS _6

C611

22U/6.3VS _6

C237

22U/6.3VS _6

C621

*22U/6.3VS _6

C612

22U/6.3VS _6

C620

10U/6.3V_ 6

C241

22U/6.3VS _6

C617

22U/6.3VS _6

C235

22U/6.3VS _6

C233

22U/6.3VS _6

C619

22U/6.3VS _6

C239

22U/6.3VS _6

C242

22U/6.3VS _6

C238

*22U/6.3VS _6

C243

22U/6.3VS _6

C613

10U/6.3V_ 6

C604

22U/6.3VS _6

C229

22U/6.3VS _6

C234

22U/6.3VS _6

C603

22U/6.3VS _6

C608

22U/6.3VS _6

C230

22U/6.3VS _6

C605

22U/6.3VS _6

C610

22U/6.3VS _6

C618

10U/6.3V_ 6

C614

10U/6.3V_ 6

VCC Out put Deco upling Recommend ations

470uFx4 7343

22uFx8

22uFx11

10uFx11

A A

TOP socke t side

4 on TOP , 4 on BO T near socket edge

0805

0805

TOP, i nside socket c avity

0805

BOT, i nside socket c avity

5

AA26

VCC1

AA28

VCC2

AA34

VCC3

AA30

VCC4

AA32

VCC5

AB26

VCC6

AB29

VCC7

AB25

VCC8

AB27

VCC9

AB28

VCC10

AB30

VCC11

AB31

VCC12

AB33

VCC13

AB34

VCC14

AB32

VCC15

AC26

VCC16

AB35

VCC17

AC28

VCC18

AD25

VCC19

AC30

VCC20

AD28

VCC21

AC32

VCC22

AD31

VCC23

AC34

VCC24

AD34

VCC25

AD26

VCC26

AD27

VCC27

AD29

VCC28

AD30

VCC29

AD32

VCC30

AD33

VCC31

AD35

VCC32

AE26

VCC33

AE32

VCC34

AE28

VCC35

AE30

VCC36

AG28

VCC37

AG34

VCC38

AE34

VCC39

AF25

VCC40

AF26

VCC41

AF27

VCC42

AF28

VCC43

AF29

VCC44

AF30

VCC45

AF31

VCC46

AF32

VCC47

AF33

VCC48

AF34

VCC49

AF35

VCC50

AG26

VCC51

AH26

VCC52

AH29

VCC53

AG30

VCC54

AG32

VCC55

AH32

VCC56

AH35

VCC57

AH25

VCC58

AH27

VCC59

AH28

VCC60

AH30

VCC61

AH31

VCC62

AH33

VCC63

AH34

VCC64

AJ25

VCC65

AJ26

VCC66

AJ27

VCC67

AJ28

VCC68

AJ29

VCC69

AJ30

VCC70

AJ31

VCC71

AJ32

VCC72

AJ33

VCC73

AJ34

VCC74

AJ35

VCC75

G25

VCC76

H25

VCC77

J25

VCC78

K25

VCC79

L25

VCC80

M25

VCC81

N25

VCC82

P25

VCC83

R25

VCC84

T25

VCC85

U25

VCC86

U26

VCC87

V25

VCC88

V26

VCC89

W2 6

VCC90

W2 7

VCC91

Y25

VCC92

Y26

VCC93

Y27

VCC94

Y28

VCC95

Y29

VCC96

Y30

VCC97

Y31

VCC98

Y32

VCC99

Y33

VCC100

Y34

VCC101

Y35

VCC102

K26

VCC103

F25

VCC104

HSW_ RPGA_EDS_P GA

POWER

CORE SUPPLY

4

+1.35VS US 4.2A+VCCIN 9 5A

C259

22U/6.3VS _6

C258

22U/6.3VS _6

C255

22U/6.3VS _6

C262

22U/6.3VS _6

C641

10U/6.3V_ 6

C636

10U/6.3V_ 6

C642

10U/6.3V_ 6

R5070_4

+VCC_C ORE

+1.35VSU S

C640

22U/6.3VS _6

C632

22U/6.3VS _6

C630

22U/6.3VS _6

C261

10U/6.3V_ 6

C252

10U/6.3V_ 6

C260

10U/6.3V_ 6

C263

10U/6.3V_ 6

R91*0_1206/S

R513*0.0 02/F_1206

R522*0_ 1206/S

Layout n ote: It is recomm ended to shield V IDSOUT signal by

routing it in b etween th e VIDSCLK and V IDALERT# signals.

Place PU resistor

close to CPU

Place PU resistor clo se to CPU

The VI DALERT# signal mu st have a dampin g resistor to prevent

overshoo t

PEG AND DDR

AB11

VDDQ1

AB2

VDDQ2

AB5

VDDQ3

AB8

VDDQ4

AE11

VDDQ5

AE2

VDDQ6

AE5

VDDQ7

AE8

VDDQ8

AH11

VDDQ9

K11

VDDQ1 0

N11

VDDQ1 1

N8

VDDQ1 2

T11

VDDQ1 3

T2

VDDQ1 4

T5

VDDQ1 5

T8

VDDQ1 6

W1 1

VDDQ1 7

W2

VDDQ1 8

W5

VDDQ1 9

W8

VDDQ2 0

K27

RSVD

L27

RSVD

T27

RSVD

V27

RSVD

N26

RSVD

AL27

RSVD

AK27

RSVD

E17

RSVD

W3 2

RSVD

AL16

RSVD

AL13

RSVD

J27

RSVD

AN35

VCCIO_ OUT

VCCIO2 PCH

VCOMP _OUT

VSS_AP 35

VIDALER T#

VIDSCLK

VIDSOU T

PW R_DEBUG

RSVD_T P

RSVD_T P

RSVD_T P

RSVD_T P

VCC_SE NSE

VSS_SE NSE

+VCCIO_O UT_R

A23

+VCCIO_P CH_R

F22

+VCCIOA _OUT_R

AP35

AM28

H_CPU_ SVIDALRT#

AM29

H_CPU_ SVIDCLK

AL28

H_CPU_ SVIDDAT

H27

PWR_ DEBUG_R

AP34

VSS

AT34

VSS

AL22

VSS

AT33

VSS

AM21

VSS

AM25

VSS

AM22

VSS

AM20

VSS

AM24

VSS

AL19

VSS

AM23

VSS

AT32

VSS

AT35

AR35

AR32

AL26

R72 100_4

AL35

AK35

R73 100_4

Sense resis tor shou ld be p laced wit hin 2

inches (5 0.8 mm) o f the pro cessor socke t

Trace Im pendence 50 ohm

C633

22U/6.3VS _6

C253

22U/6.3VS _6

C639

22U/6.3VS _6

C631

22U/6.3VS _6

C637

10U/6.3V_ 6

C254

10U/6.3V_ 6

C644

10U/6.3V_ 6

TP8

VCC_SE NSE 3 8

VSS_SE NSE 38

SENSE LINES SVID

3

VDDQ Ou tput Decouplin g Recommendatio ns

330uFx2 7343

22uFx11

10uFx10

+

C298

*330U/2V_ 7343

+VCCIO_O UT

+VCCIO_P CH

+VCCIOA _OUT

H_CPU_ SVIDCLK

H_CPU_ SVIDDAT

+VCCIO_O UT

H_CPU_ SVIDALRT#

+VCCIO_O UT

BOT socke t side

5 onTOP, 6 on BOT inside socket cav ity

0805

5 onTOP, 5 on BOT inside socket cav ity0805

300mA

300mA

4/30: DG 498550

Haswell PWR_DEBUG requir es a 150-Ohm pull-up resistor to PCH 1.05- V VCC

Core when routed to XDP

R129

130/F_4

C218 *0.1U/10V_4

R126 75/F_4

R128 43_4

SVID CLK

VR_SVID _CLK 38

SVID DATA

DG V0 .7 -> 1 10 Ohm

SCH V0. 7 -> 130 Ohm

VR_SVID _DATA 38

DG V0 .7 -> 4 4 Ohm

SCH V0. 7 -> 43 Ohm

SVID ALERT

VR_SVID _ALERT# 38

2

+3VPCU

R492

20K/F_4

R495

100K_6 N TC

4/30: CRB 1.0 add

Power Test Propose

+1.05V +VCCIO_O UT+1.05V

R94

150/F_4

PWR_ DEBUG_R

R92

*10K_4

CPU VDDQ

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

+VCCIOA _OUT 2

+VCCIO_O UT 2,3 8

+VCCIO_P CH 10

+1.5V 6,7,8 ,10,26,29,32,36

+1.05V 2 ,9,10,27,35,42

+VCC_C ORE 38,39

+VCCST 2

+1.35VSU S 2,12,13,36

HW Thrm Protect

For 65 d egree, 1.8v limit, (SW)

For 75 d egree, 1.2v limit, (HW)

R119 *0_8

PROJECT : TWS

PROJECT : TWS

PROJECT : TWS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

HAS 3/4 (POWER )

HAS 3/4 (POWER )

HAS 3/4 (POWER )

C598

*0.1U/10V_ 4

+VCCST+1.05V

C240

*10U/6.3V_ 6

R109 *0_8

R515 0_6

CRB 1.0 st uff

1

THRM_ MOINTOR1 31

+VCCIO_P CH+1.0 5V

04

C245

*10U/6.3V_ 6

C217

*4.7U/6.3V_ 6

C600

*4.7U/6.3V_ 6

4 43Friday, August 16, 201 3

4 43Friday, August 16, 201 3

4 43Friday, August 16, 201 3

P

1A

1A

1A

5

4

3

2

1

Haswell Processor (GND)

U23G

A10

VSS1

A13

VSS2

A16

VSS3

A19

VSS4

A22

VSS5

A25

VSS6

A27

D D

C C

B B

VSS7

A29

VSS8

A3

VSS9

A31

VSS10

A33

VSS11

A4

VSS12

A7

VSS13

AA11

VSS14

AA25

VSS15

AA27

VSS16

AA31

VSS17

AA29

VSS18

AB1

VSS19

AB10

VSS20

AA33

VSS21

AA35

VSS22

AB3

VSS23

AC25

VSS24

AC27

VSS25

AB4

VSS26

AB6

VSS27

AB7

VSS28

AB9

VSS29

AC11

VSS30

AD11

VSS31

AC29

VSS32

AC31

VSS33

AC33

VSS34

AC35

VSS35

AD7

VSS36

AE1

VSS37

AE10

VSS38

AE25

VSS39

AE29

VSS40

AE3

VSS41

AE27

VSS42

AE35

VSS43

AE4

VSS44

AE6

VSS45

AE7

VSS46

AE9

VSS47

AF11

VSS48

AF6

VSS49

AF8

VSS50

AG11

VSS51

AG25

VSS52

AE31

VSS53

AG31

VSS54

AE33

VSS55

AG6

VSS56

AH1

VSS57

AH10

VSS58

AH2

VSS59

AG27

VSS60

AG29

VSS61

AH3

VSS62

AG33

VSS63

AG35

VSS64

AH4

VSS65

AH5

VSS66

AH6

VSS67

AH7

VSS68

AH8

VSS69

AH9

VSS70

AJ11

VSS71

AJ5

VSS72

AK11

VSS73

AK25

VSS74

AK26

VSS75

AK28

VSS76

AK29

VSS77

AK30

VSS78

AK32

VSS79

E19

VSS80

HSW_ RPGA_EDS_P GA

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AK34

AK5

AL1

AL10

AL11

AL12

AL14

AL15

AL17

AL18

AL2

AL20

AL21

AL23

E22

AL3

W9

AL4

AL5

AL6

AL7

AL8

AL9

AM10

AM13

AM16

AM19

E25

AM32

AM4

AM7

AN10

AN13

AN16

AN19

AN2

AN21

AN24

AN27

AN30

AN34

AN4

AN7

AP1

AP10

AP13

AP16

AP19

AP4

AP7

W2 5

Y11

AR13

AR16

AR19

AR2

AR22

AR25

AR28

AR31

AR34

AR4

AR7

AT10

AT13

AT16

AT19

AT21

AT24

AT27

AT3

AT30

AT4

AT7

B10

B13

B16

B19

B2

B22

U23H

B34

VSS161

B4

VSS162

B7

VSS163

C1

VSS164

C10

VSS165

C13

VSS166

C16

VSS167

C19

VSS168

C2

VSS169

C22

VSS170

C24

VSS171

C26

VSS172

C28

VSS173

C30

VSS174

C32

VSS175

C34

VSS176

C4

VSS177

C7

VSS178

D10

VSS179

D13

VSS180

D16

VSS181

D19

VSS182

D22

VSS183

D25

VSS184

D27

VSS185

D29

VSS186

D31

VSS187

D33

VSS188

D35

VSS189

D4

VSS190

D7

VSS191

E1

VSS192

E10

VSS193

E13

VSS194

E16

VSS195

E4

VSS196

E7

VSS197

F10

VSS198

F11

VSS199

F12

VSS200

F14

VSS201

F15

VSS202

F17

VSS203

F18

VSS204

F20

VSS205

F21

VSS206

F23

VSS207

F24

VSS208

F26

VSS209

F28

VSS210

F30

VSS211

F32

VSS212

F34

VSS213

F4

VSS214

F6

VSS215

F7

VSS216

F8

VSS217

F9

VSS218

G1

VSS219

G11

VSS220

G2

VSS221

G27

VSS222

G29

VSS223

G3

VSS224

G31

VSS225

G33

VSS226

G35

VSS227

G4

VSS228

G5

VSS229

H10

VSS230

H26

VSS231

H6

VSS232

H7

VSS233

J11

VSS286

J26

VSS287

J30

VSS288

J32

VSS289

J34

VSS290

J6

VSS291

K1

VSS292

HSW_ RPGA_EDS_P GA

VSS

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

VSS301

VSS302

VSS303

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS310

VSS311

VSS312

VSS313

VSS314

VSS315

VSS316

RSVD

K10

K2

K29

K3

K31

K33

K35

K4

K5

K7

K8

K9

L11

L26

L6

M11

M26

M28

M30

M32

M34

M6

N1

N10

N2

N29

N3

N31

N33

N35

N4

N5

N6

N7

N9

P11

P26

P5

R11

R26

R28

R30

R32

R34

R5

T1

T10

T29

T3

T31

T33

T35

T4

T6

T7

T9

U11

U27

V11

V28

V30

V32

V34

W1

W1 0

W3

W3 5

W4

W6

W7

AR10

J28

H11

AL24

F19

T26

AK33

R74 49.9/F_4

Haswell Processor (RESERVED, CFG)

U23E

AT20

R50649.9/F_4

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG_RC OMP

RSVD30

RSVD38

RSVD39

TESTLO

CFG[0]

AR20

CFG[1]

AP20

CFG[2]

AP22

CFG[3]

AT22

CFG[4]

AN22

CFG[5]

AT25

CFG[6]

AN23

CFG[7]

AR24

CFG[8]

AT23

CFG[9]

AN20

CFG[10 ]

AP24

CFG[11 ]

AP26

CFG[12 ]

AN25

CFG[13 ]

AN26

CFG[14 ]

AP25

CFG[15 ]

AR21

CFG[16 ]

AP21

CFG[17 ]

AR23

CFG[18 ]

AP23

CFG[19 ]

AT31

CFG_R COMP

AT1

RSVD_T P

AT2

RSVD_T P

AD10

RSVD_T P

A34

RSVD_T P

A35

RSVD_T P

W2 9

RSVD_T P

W2 8

RSVD_T P

G26

TESTLO _G26

W3 3

RSVD

AL30

RSVD

AL29

RSVD

C35

RSVD_T P

B35

RSVD_T P

AL25

RSVD_T P

W3 0

RSVD_T P

W3 1

RSVD_T P

W3 4

TESTLO

HSW_ RPGA_EDS_P GA

CFG

RESERVED

RSVD_T P

RSVD_T P

RSVD_T P

RSVD_T P

FC_G6

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD_T P

RSVD_T P

RSVD_T P

RSVD

RSVD

RSVD

RSVD

C23

B23

D24

D23

G6

AR33

AM27

AM26

F5

AM2

K6

E18

U10

P10

B1

NC

A2

AR1

E21

E20

AP27

AR26

AL31

AL32

CFG[3] (P HYSICAL_DEBUG_E NABLED (DFX PR IVACY))

0 Enable; SET DF X ENAB LED BIT IN DEBUG

1 , Disable;

CFG3

R524 *1K_4

TP80

TP79

TP77

TP19

TP20

TP18

TP61

R100 49.9/F_4

For CPU debug.

TP4

TP5

TP65

TP68

TP76

TP78

R154

*2K_4

R149

*1K_4

05

EC_PW ROK 6,3 1

Processor Strapping

The CFG signals hav e a default v alue of '1 ' if not te rminated on the board.

1 0

A A

CFG2

(PEG Static Lane R eversal)

CFG4

(DP Pres ence Strap)

CFG7

(PEG Defer Traini ng)

5

Normal O peration Lane Re versed

Disable ; No physical DP a ttached to e DP

PEG train immediately following

xxRESE TB de assertion

4

Enable; An ext DP device is connected to eDP

PEG wa it for BIO S training

CFG2

R534 *1K_4

CFG4

R533 1K_4

CFG7

R523 *1K_4

CFG5

R530 1K_4

CFG6

R518 *1K_4

3

CFG[6:5] (PCIE Port Bifurc ation Straps)

11: ( Defau lt) x 16 - Devic e 1 f uncti ons 1 and 2 dis abled

10: x 8, x8 - De vice 1 fun ction 1 en abled ; fu nctio n 2 disa bled

01: R eserv ed - (Devi ce 1 funct ion 1 disa bled ; fun ction 2 enabl ed)

00: x 8,x4, x4 - Devic e 1 f uncti ons 1 and 2 ena bled

PROJECT : TWS

PROJECT : TWS

PROJECT : TWS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

HAS 4/4 (GND)

HAS 4/4 (GND)

HAS 4/4 (GND)

1

1A

1A

5 43Friday, August 16, 201 3

5 43Friday, August 16, 201 3

5 43Friday, August 16, 201 3

1A

5

4

3

2

1

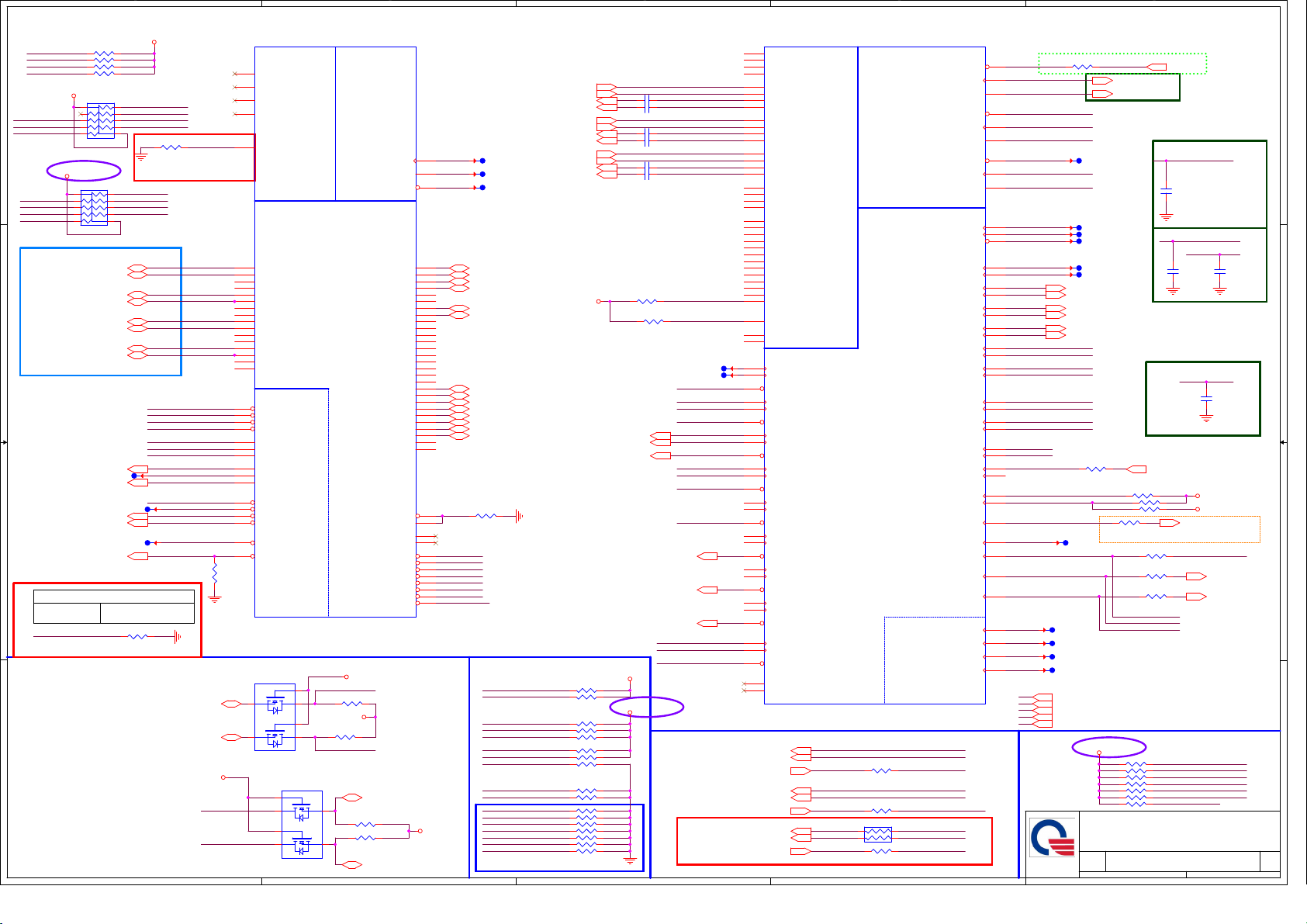

Lynx Point (DMI,FDI,PM)

U25C

TP30

AW 22

DMI0RX N

AR20

DMI1RX N

AP17

DMI2RX N

AV20

DMI3RX N

AY22

DMI0RX P

AP20

DMI1RX P

AR17

DMI2RX P

AW 20

DMI3RX P

BD21

DMI0TX N

BE20

DMI1TX N

BD17

DMI2TX N

BE18

DMI3TX N

BB21

DMI0TX P

BC20

DMI1TX P

BB17

DMI2TX P

BC18

DMI3TX P

BE16

DMI_IRE F

AY17

DMI_IRC OMP

AW 17

TP12

AV17

TP7

R6

SUSAC K#

AM1

SYS_RE SET#

AD7

SYS_PW ROK

F10

PW ROK

AB7

APW ROK

H3

DRAMP WROK

J2

RSMRS T#

J4

SUSW ARN#/SU SPWRD NACK/GPIO 30 (SUS)

(+3VS5)

K1

PW RBTN#

E6

ACPRE SENT / GP IO31(DSW )

(DSW)

K7

BATLOW # / G PIO72 (SUS)

(+3VS5)

N4

RI#

AB10

TP21

LPT_PC H_M_EDS/BGA

System Powe r Management

DMI

FDI

DSW VRMEN

SUS_ST AT# / GPIO 61 (SUS)

SUSCLK / GPIO62 (SUS)

SLP_S5# / GPIO63 ( SUS)

(+3VS5)

SLP_W LAN#/ G PIO29 ( DS W)

DMI_RX N02

DMI_RX N12

DMI_RX N22

DMI_RX N32

DMI_RX P02

D D

+1.5V

DMI_RX P12

DMI_RX P22

DMI_RX P32

DMI_TXN 02

DMI_TXN 12

DMI_TXN 22

DMI_TXN 32

DMI_TXP 02

DMI_TXP 12

DMI_TXP 22

DMI_TXP 32

R570 *0_4/S

R571 7.5K/F_4

DMI_IRE F

DMI_COM P

5/16 for D S3

SUSW ARN#

SUSAC K#EC31

C C

B B

XDP_DB RST#2

SYS_PW ROK2

IMVP_PW RGD6,38

PM_DR AM_PWRG D2

5/16 for D S3

SUSW ARN#EC31

DNBSW ON#31

5/16 for D S3 5/16 for D S3

AC_PRE SENT31

SYS_PW ROK_R

R273

EC_PW ROK5,31

EC_PW ROK_R

RSMRS T#31

short pad 2013/02/2 0

R273 0_4

R434 *0_4

R432 0_4

R431 *0_4/S

R410 *0_4/S

R393 *0_4/S

R652 *0_4/S

C398

*0.1U/10V_ 4

R345*0_4

R328*0_4/S

SUSAC K#

XDP_DB RST#

SYS_PW ROK_R

EC_PW ROK_R

APWR OK_R

PM_DR AM_PWRG D

RSMRS T#

SUSW ARN#

DNBSW ON#_R

AC_PRE SENT_R

PM_BAT LOW#

PM_RI#

Reserve fo r power on sequence

PCH Pull-high/low(CLG)

SUS_ST AT#

PM_RI#

SLP_LAN #

SUSAC K#

SUSW ARN#

PM_DR AM_PWRG D

PM_BAT LOW#

PCIE_W AKE#

DNBSW ON#_R

AC_PRE SENT_R

A A

CLKRUN #

XDP_DB RST#

RSMRS T#

R302 *10K_4

R604 10K_4

R660 *10K_4

R335 *10K_4

R413 *10K_4

R661 *200_4

R368 8.2K_4

R605 1K_4

R392 *10K_4

R365 10K_4

R399 *100K_4

R245 10K_4

R218 1K_4

R583 *1K_4

R397 100K_4

5

+3V_DE EP_SUS

+3VS5

+3V

for DS3

EDS V0.7 -> BATLOW# is i n SUS w ell

SCH V0.7 -> BATLO W# pull up to DS3 power

DG V0.7 say that PW RBTN# is internal

pulled- up in P CH to 3.3 V DSW through

a weak pu ll-up resistor (24 kΩ nomin al)

INT HDMI Detect Function

4

FDI_RXN 0

FDI_RXN 1

FDI_RXP 0

FDI_RXP 1

FDI_CSY NC

FDI_INT

FDI_IREF

FDI_RCO MP

TP16

TP5

TP15

TP10

TP17

TP13

DPW ROK

WA KE#

(+3V)

CLKRU N#

(+3VS5)

(+3VS5)

(+3VS5)

SLP_S4#

SLP_S3#

SLP_A#

SLP_SU S#

PMSYN CH

SLP_LAN #

AJ35

AL35

AJ36

AL36

AL39

AL40

AT45

R212 *0_4/S

AR44

R211 7.5K/F_4

AV43

AY45

AV45

AW 44

AU42

AU44

C8

DSWV REN

L13

DPWR OK

K3

PCIE_W AKE#

AN7

CLKRUN #

U7

Y6

PCH_SU SCLK_L

Y7

C6

H1

F3

F1

AY3

G5

D2

R382 0_4

R398 *0_4

SUS_ST AT#

TP33

R636 *0_4/S

R645 *0_4/S

TP51

R644 *0_4/S

SLP_LAN #

FDI_TXN 0 2

FDI_TXN 1 2

FDI_TXP 0 2

FDI_TXP 1 2

FDI_CSYNC 2

FDI_INT 2

+1.5V

for DS3

DPWR OK_EC 31

RSMRS T#

PCIE_W AKE# 25,30

CLKRUN # 2 4,31

PCH_SU SCLK_L 7

SUSC# 31

SUSB# 31

SLP_SU S#EC 31

PM_SYNC 2

DG V0. 7 -> 33 o hm

SCH V0.7 -> 0 ohm

LVDS_B LON23

DISP_ON23

DPST_P WM2,22,23

PD Res pl ace close to PCH

PCH to R es routein g 37.5 ohm Imp edance.

Res to co nnector f ilter route ing 50oh m Impedance.

CRT_B21

CRT_G21

CRT_R21

DDCCL K21

DDCDA TA21

HSYNC_C OM21

VSYNC_C OM21

DAC_IREF ( 50ohm)

Trace len gth < 500 MILS

Trace sp acing = 30 MILS

R298 150/F_4

R291 150/F_4

R285 150/F_4

R314 33_4

R307 33_4

R292 649/F_4

Reserv e from EMI req uest

CRT_B

CRT_G

C446

C434

*5.6P/16V_ 4

*5.6P/16V_ 4

PCH Nut: QCI P/N: MBUL1001010 (Location:H13,H14)

R380 330K_4

+3V_RTC

On Die DSW VR En able

High = Enable ( Default)

Low = Disabl e

3

Lynx Point ( DDI)

U25D

K36

EDP_BK LTEN

G36

EDP_VD D_EN

N36

EDP_BK LTCTL

T45

CRT_BL UE

U44

CRT_G REEN

V45

CRT_RE D

M43

CRT_DD C_CLK

M45

CRT_DD C_DATA

DAC_IRE F

2

N42

CRT_HS YNC

N44

CRT_VS YNC

U40

DAC_IRE F

U39

CRT_IRT N

LPT_PC H_M_EDS/BGA

CRT_R

C423

*5.6P/16V_ 4

DSWV REN

PCH_HS YNC_R

PCH_VS YNC_R

DDPB_H PD

R40

R39

H45

H43

K40

DDPB_C TRLCLK

DDPB_C TRLDATA

DDPB_A UXN

DDPB_A UXP

LVDS

DDPC_ HPD

DDPD_ HPD

R35

R36

K43

K45

K38

N40

N38

J42

J44

H39

DDPC_ CTRLCLK

DDPC_ CTRLDATA

DDPD_ CTRLCLK

DDPD_ CTRLDATA

Digital Dis play Interface

DDPC_ AUXN

DDPC_ AUXP

DDPD_ AUXN

DDPD_ AUXP

CRT

+3V_DE EP_SUS 7,8 ,9,10,29

+3V_RTC 7,10,27

+1.05V 2 ,4,9,10,27,35,42

+3VPCU 4,27,29,31 ,32,33,34

+3VS5 2,7,9,10 ,24,27,28,29,31,34,36,3 7,42

+3V 2,7,8,9,10,12 ,13,14,17,21,22,23,24,2 5,26,28,29,30,31,3 2,37,38,40

+5V 21,26,28,29 ,32,37,40

System PWR_OK(CLG)

R435 *0_4/S

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

IMVP_PW RGDSYS_PW ROK

EC_PW ROK

R429

10K_4

PROJECT : TWS

PROJECT : TWS

PROJECT : TWS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PCH 1/6 (DMI/FDI/ VIDEO)

PCH 1/6 (DMI/FDI/ VIDEO)

PCH 1/6 (DMI/FDI/ VIDEO)

1

06

SDVO_C LK 21

SDVO_D ATA 21

HDMI_H PD_CON 21

IMVP_PW RGD 6,38

6 43Friday, August 16, 201 3

6 43Friday, August 16, 201 3

6 43Friday, August 16, 201 3

INT. HDMI

1A

1A

1A

5

Lynx Point (HDA,JTAG,SATA)

CLKGEN _RTC_X127

D D

+3V_RTC

Reser ve fo r EMI

C693

*10P/50V_ 4

for DS3

+3V_DE EP_SUS

SIO_EXT_ SCI#31

C C

check

PCH Strap Table

B B

Pin Nam e Strap de scription Sampled Configuration

SPKR

GNT3# / GPIO55 Top-Block Swap Ov erride

TP45

TP86

R378 1M_4

TP42

ACZ_SP KR26

ACZ_SD IN026

TP38

R618 10K_4

SIO_EXT_ SCI#

TP84

TP83

TP82

TP23

PCH_SP I_CLK31

PCH_SP I_CS0#31

PCH_SP I_CS1#31

PCH_SP I_SI31

PCH_SP I_SO31

PCH_SP I_IO231

PCH_SP I_IO331

RTC_RS T#

SRTC_R ST#

SM_INTR UDER#

PCH_INV RMEN

ACZ_BC LK

ACZ_SYNC

ACZ_SP KR

ACZ_RS T#

ACZ_SD OUT

GPIO33

TP91

PCH_JT AG_TCK_R

PCH_JT AG_TMS

PCH_JT AG_TDI_R

PCH_JT AG_TDO_R

R317 *0_4/S

TP31

PCH_SP I_CLK

PCH_SP I_CS0#

PCH_SP I_CS1#

PCH_SP I_SI

PCH_SP I_SO

PCH_SP I_IO2

PCH_SP I_IO3

No reboot mode set ting PWRO K

U25A

B5

RTCX1

B4

RTCX2

D9

RTCRS T#

B9

SRTCR ST#

A8

INTRUD ER#

G10

INTVRM EN

B25

HDA_BC LK

A22

HDA_SY NC

AL10

SPKR

C24

HDA_R ST#

L22

HDA_SD IN0

K22

HDA_SD IN1

G22

HDA_SD IN2

F22

HDA_SD IN3

A24

HDA_SD O

(+3V)

B17

HDA_D OCK_EN# / GPIO33

(+3VS5)

C22

HDA_D OCK_RST# / GPIO13

AB3

JTAG_ TCK

AD1

JTAG_ TMS

AE2

JTAG_ TDI

AD3

JTAG_ TDO

F8

TP25

C26

TP22

AB6

TP20

AJ11

SPI_CLK

AJ7

SPI_CS0 #

AL7

SPI_CS1 #

AJ10

SPI_CS2 #

AH1

SPI_MO SI

AH3

SPI_MISO

AJ4

SPI_IO2

AJ2

SPI_IO3

LPT_PC H_M_EDS/BGA

PWRO K

INTVRME N Integrated 1.05V VRM enable ALW AYS

HDA_DOCK _EN#/GP IO33

GNT1# / GPIO51

GPIO19

Flash Des criptor Se curity

Only for Int erposer

Boot BI OS Se lection 1 [bit-1]

Boot BI OS Selec tion 0 [bit-0]

PWRO K

PWRO K

PWRO K

HDA_SYN C On-Die PLL VR Voltage Select RSMRST

HDA_SDO PWRO KFlash De scriptor S ecurity

GPIO8

A A

GPIO28 0 = Disable

RSVD Internel P URSMRST#

On-die PLL Voltage R egulator RSMRS T#

SPI_MOSI iTPM fun ction Disable APW ROK 0 = Default (weak pull-down 20K )

SUSCLK / GPIO6 2

On-die PLL Voltage R egulator PWR OK

5

4

A20

LAD0

C20

LAD1

A18

LAD2

C18

LAD3

B21

LFRAM E#

D21

LDRQ0#

RTCIHDA

LDRQ1# / GPIO23

SATA 6G LPC

SATA4R XN / PERN 1

SATA4R XP / PER P1

SATA4T XN / PETN 1

SATA4T XP / PETP 1

SATA5R XN / PERN 2

SATA5R XP / PER P2

SATA5T XN / PETN 2

SATA5T XP / PETP 2

SATA_R COMP

SATA0G P / GPIO21

SATA1G P / GPIO19

SPI JTAG

0 = Default (weak pull-down 20K)

1 = Set ting to No -Reboot mode

0 = "top-block swap " mode

1 = Default (Int PU)

0 = Disabl e

1 = Enabl e

0 = Ov erride

1 = Default (weak pull-up 20K)

GNT0#GNT 1#

11

00

0 = Support b y 1.8V (weak pull-down)

1 = Support b y 1.5V

0 = Sec urity Effec t (Int PD)

1 = Can be Overridden

(+3V)

SERIRQ

SATA0R XN

SATA0R XP

SATA0T XN

SATA0T XP

SATA1R XN

SATA1R XP

SATA1T XN

SATA1T XP

SATA2R XN

SATA2R XP

SATA2T XN

SATA2T XP

SATA3R XN

SATA3R XP

SATA3T XN

SATA3T XP

SATA_IR EF

SATALE D#

(+3V)

(+3V)

TP9

TP8

G20

AL11

BC8

BE8

AW 8

AY8

BC10

BE10

AV10

AW 10

BB9

BD9

AY13

AW 13

BC12

BE12

AR13

AT13

BD13

BB13

AV15

AW 15

BC14

BE14

AP15

AR15

AY5

SATA_RCOMP

Impedanc e = 50 ohm

Trace length < 500 mils

Trace spacing = 15 mils

DG V0 .7 -> 7 50 ohm

SCH V0. 7 -> 0 o hm

BD4

AP3

AT1

AU2

BA2

BB2

Boot Locat ion

SPI

LPC

1 = Ena ble (Int P U)

1 = Ena ble

0 = Disable

1 = Ena ble (Int P U)

4

LAD0 24 ,29,31

LAD1 24 ,29,31

LAD2 24 ,29,31

LAD3 24 ,29,31

PCH_DR Q#0

PCH_DR Q#1

SERIRQ

LFRAME # 24,29,31

TP85

TP41

R249 8.2K_4

Port 1 Disable

DG recom mended that AC couplin g capacitors should be

close to the connector (< 100 mils) for optimal signal quali ty.

Port 3 Disable

SATA_R COMP

SATA_IR EF

DGT_STO P#

BBS_BIT 0

R223 7.5K/F_4

R224 *0_4/S

R243 10K_4

R577 0_4

R559 *10K_4

DGT_STO P#

R562 10K_4

Circuit

ACZ_SP KR

PCH_INV RMEN

[Need ext ernal pull -down for LP C BIOS]

Default weak pull-up on GNT0/1 #

+VCC_H DA_IO

PCH_SP I_SI

R267 *1K_4

GPIO33_E31

PCH_SU SCLK_L6

R269 *1K_4

R346 330K_4

R565 *1K_4

R622 *1K_4

R595 *1K_4

R598 *1K_4

R256 *1K_4

+3V

SERIRQ 24 ,31

SATA_R XN0 32

SATA_R XP0 32

SATA_T XN0 32

SATA_T XP0 32

SATA_R XN4 32

SATA_R XP4 32

SATA_T XN4 32

SATA_T XP4 32

SATA_R XN5 32

SATA_R XP5 32

SATA_T XN5 32

SATA_T XP5 32

+1.5V

+1.5V

SATA_LE D# 29

+3V

DGPU_H OLD_RST# 9,14

+3V

9/21 Inst all for In tel DG

+3V

PCI_GNT3 # 8

R619 *1K_4

ACZ_SD OUT

3

ODD (SATA1 1.5Gb/s)

HDD0 (SATA3 6.0Gb/s)

mSATA (SATA3 6.0Gb/s)

BIT_CLK _AUDIO

EMI

+3V

+3V_RTC

BBS_BIT 0

BBS_BIT 1 8

ACZ_SYNC

R617 *1K_4

3

+3V power leakage i n S3 AC m ode: Pleas e always r emove pull high .

(Intel re lease docu ment:

BT_OFF# 9,29

PLL_ODV R_EN 9

+3V

R315 *1K_4

R310 *1K_4

2

+1.05V 2 ,4,9,10,27,35,42

+3V_RTC 6,10,27

+3VPCU 4,27,29,31 ,32,33,34

+3V 2,6,8,9,10,1 2,13,14,17,21,22,23,2 4,25,26,28,29,30,31 ,32,37,38,40

+3V_DE EP_SUS 6 ,8,9,10,29

+5V 21,26,28,29 ,32,37,40

RTC Circuitry(RTC)

RTC Power trac e wi dth 2 0mils .

C307

0.1U/10V_ 4

BIT_CLK _AUDIO26

C527

*33P/50V_ 4

ACZ_RS T#_AUDIO26

ACZ_SD OUT_AUDIO26

ACZ_SYNC _AUDIO26

PCH SPI ROM(CLG)

+VCC_H DA_IO

+3V

PCH_SP I_CS1#

PCH_SP I_CS0#

strap pin ) 2012/12 /17

R447 *0_4

R448 0_4

2

+3V_RTC _0

RTC CON N

1

2

BT1

HDA Bus(CLG)

PCH_SP I_CS0#R

PCH_SP I_CLK

PCH_SP I_SI

PCH_SP I_SO

C707

*22P/50V_ 4

PCH_SP I_IO2

PCH_SP I_IO3

RTC Clock 32.768KHz

CB USE GREEN CLK

30mils

+3V_RTC

R177 20K/F_4

R178 20K/F_4

C312

1U/6.3V_4

PCH JTAG Debug(CLG)

+3VS5

R590

*210/F_4

R589

*100/F_4

U27

1

CE#

6

SCK

5

SPI_SI_R

SI

2

SPI_SO_R

SO

3

WP #

A25QE16M -F/Q (QE)

R443 1K_4

R651 1K_4

P/N

AKE38ZN0803 ( A25QE16M-F /Q (QE))

AKE38FP 0N03 (W 25Q16DVS SIQ)WIN

DFHS08F S023

PROJECT : TWS

PROJECT : TWS

PROJECT : TWS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PCH 2/6 (SATA/H DA/SPI)

PCH 2/6 (SATA/H DA/SPI)

PCH 2/6 (SATA/H DA/SPI)

TP59

C708

ACZ_SYNC

TP50

ACZ_BC LK

ACZ_RS T#

ACZ_SD OUT

TP48

R658 0_4

R659 0_4

R449 0_4

TP57

SPI_CLK _R

R616 33_4

R632 33_4

R631 33_4

R411 0_6

If EC supp ort embedde d flash , SPI

power must be used S5 _0N power rail

for EC loa d code.

TP58

*22P/50V_ 4

Close to PC H

R450 0_4

R655 0_4

Vender

AMIC

Size

2MB

2MB

Socket

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

C314

1U/6.3V_4

C315

1U/6.3V_4

R180 *0_6

R588

*210/F_4

R587

*100/F_4

+3V

VDD

HOLD#

VSS

1

07

RTC_RS T#

12

J2

*SOLDER JUMPER-2

SRTC_R ST#

12

J1

*SOLDER JUMPER-2

SRTC_R ST#RTC_RS T#

R592

*210/F_4

PCH_JT AG_TMS

PCH_JT AG_TDI_R

PCH_JT AG_TDO_R

PCH_JT AG_TCK_R

R591

R593

*100/F_4

*51_4

8

7

4

+3V

TP53

7 43Friday, August 16, 201 3

7 43Friday, August 16, 201 3

7 43Friday, August 16, 201 3

C705

0.1U/10V_ 4

1A

1A

1A

5

PCI/USBOC# Pull-up(CLG)

PCI_PIRQ A#

R384 8.2K_4

PCI_PIRQ B#

R404 8.2K_4

PCI_PIRQ C#

R402 8.2K_4

PCI_PIRQ D#

R386 8.2K_4

+3V

RP7

10

9

for DS3

8

7 4

10K_10P 8R_6

+3V_DEEP _SUS

RP6

10

9

8

7 4

10K_10P 8R_6

USB30_RX 1-27

USB30_RX 2-27

USB30_RX 1+27

USB30_RX 2+27

USB30_TX1 -27

USB30_TX2 -27

USB30_TX1 +27

USB30_TX2 +27

BOARD_ID 39

ACCEL_IN TH#2 4

BBS_BIT17

PCI_GNT3 #7

PLTRST#2,14,24 ,25,29,30,31

ACCEL_IN TH#

D D

LCD_BK

MPC_PW R_CTRL#

USB_OC4 #

USB_OC1 #

USB_OC3 #

USB3.0

C C

B B

+3V

1

ACC_LED#

2

EDID_SEL ECT#

3

BT_COMB O_EN#

DGPU_SEL ECT#

56

4/30: CRB 1.0 =>rename PCH_TP26

1

USB_OC6 #

2

USB_OC0 #

3

RF_PW R_OFF#

USB_OC5 #USB_OC2 #

56

Port 5,6 D isabl e

Port 5,6 D isabl e

Port 5,6 D isabl e

Port 5,6 D isabl e

TP89

TP49

TP29

check

MPC Sw itch Control

MPC_PW R_CTRL#

MPC_PW R_CTRL#

Low = MPC ON

High = M PC OFF (Defa ult)

R338 *1K_4

SMBus/Pull-up(CLG)

A A

5

Lynx Point (PCI,USB,NVRAM)

U25E

BA45

TP1

BC45

TP2

BE44

TP3

BE43

TP4

AY43

PCH_TP26

R2478. 2K_4

PCI_PIRQ A#

PCI_PIRQ B#

PCI_PIRQ C#

PCI_PIRQ D#

BT_COMB O_EN#

DGPU_SEL ECT#

EDID_SEL ECT#

BBS_BIT1

ACC_LED#

PCI_GNT3 #

MPC_PW R_CTRL#

LCD_BK

ACCEL_IN TH#

PCI_PME#

PLTRST#

MBCLK213,17,22, 24,31

MBDATA213,17,22,24,31

+3V

SMB_PCH _DAT

SMB_PCH _CLK

R287

100K_4

AR26

AW26

AW29

AR29

AP26

AV26

AV29

AP29

BE24

BD25

BE26

BD27

BD23

BC24

BC26

BE28

M20

M15

AD10

H20

L20

K17

A12

B13

C12

C10

A10

AL6

G17

F17

L15

Y11

TD_IREF

USB3RXN1

USB3RXN2

USB3RXN5

USB3RXN6

USB3RXP1

USB3RXP2

USB3RXP5

USB3RXP6

USB3TXN1

USB3TXN2

USB3TXN5

USB3TXN6

USB3TXP1

USB3TXP2

USB3TXP5

USB3TXP6

PIRQA#

PIRQB#

PIRQC#

PIRQD#

(+3V)

GPIO50

(+3V)

GPIO52

(+3V)

GPIO54

(+3V)

GPIO51

(+3V)

GPIO53

(+3V)

GPIO55

PIRQE# / GPIO2

PIRQF# / GPIO3

PIRQG# / GPIO4

PIRQH# / GPIO5

PME#

PLTRST#

LPT_PCH_ M_EDS/BGA

Q17

4 3

1

*2N7002 DW

5

2

6

2N7002 DW

Therma l

PCI

(+3V)

(+3V)

(+3V)

(+3V)

5

+3V_DEEP _SUS

2

6

Q16

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

SMB_ME1 _CLK

R389 2.2K_4

R379 2.2K_4

SMB_ME1 _DAT

43

R361 4.7K_4

R376 4.7K_4

1

4

C- Lin k

CL_CLK1

CL_DATA1

CL_RST1#

USBP0N

USBP0P

USBP1N

USBP1P

USBP2N

USBP2P

USBP3N

USBP3P

USBP4N

USBP4P

USBP5N

USBP5P

USBP6N

USBP6P

USBP7N

USBP7P

USBP8N

USBP8P

USBP9N

USBP9P

USBP10N

USBP10P

USBP11N

USBP11P

USBP12N

USBP12P

USBP13N

USBP13P

USB

USBRBIAS#

USBRBIAS

TP24

TP23

OC0# / G PIO59

OC1# / G PIO40

OC2# / G PIO41

OC3# / G PIO42

OC4# / G PIO43

OC5# / G PIO9

OC6# / G PIO10

OC7# / G PIO14

+3V

SMB_RUN _DAT 12,1 3,22,32

SMB_RUN _CLK 12 ,13,22,32

4

LAN

Cardrea der

AF11

CL_CLK_ R

AF10

CL_DAT_R

AF7

CL_RST#_ R

B37

D37

A38

C38

A36

C36

A34

C34

B33

D33

F31

G31

K31

L31

G29

H29

A32

C32

A30

C30

B29

D29

A28

C28

G26

F26

F24

G24

K24

K26

M33

L33

P3

V1

U2

P1

M3

T1

N2

M1

7/4: GPIO1 4 cha nge n etnam e

to RF _PWR_ OFF# for C B

USB_BIAS

R330

22.6/F_ 4

USB_OC0 #

USB_OC1 #

USB_OC2 #

USB_OC3 #

USB_OC4 #

USB_OC5 #

USB_OC6 #

RF_PW R_OFF#

TP26

WLAN

TP25

TP28

USBP0- 27

USBP0+ 27

USBP1- 26

USBP1+ 26

USBP3- 23

USBP3+ 23

USBP9- 26

USBP9+ 26

USBP10- 29

USBP10+ 29

USBP11- 24

USBP11+ 24

USBP12- 32

USBP12+ 32

Camera

TV Ca rd

CLK_REQ/Strap Pin(CLG)

CLK_PCIE _REQ1#

PCIE_CLK REQ_CR#

CLK_PCIE _REQ0#

CLK_PCIE _REQ3#

CLK_PCIE _REQ4#

CLK_PEGB _REQ#

CLK_PEGA _REQ#

CLK_PEGA _REQ#

CLK_BUF _BCLK_N

CLK_BUF _BCLK_P

CLK_BUF _PCIE_3GPLL #

CLK_BUF _PCIE_3GPLL

CLK_BUF _DREFCLK#

+3V

CLK_BUF _DREFCLK

CLK_BUF _DREFSSCLK#

CLK_BUF _DREFSSCLK

CLK_PCH_ 14M

CLOCK TE RMINATIO N for FCI M

PCIE_RXN2 _LAN30

PCIE_TXN2 _LAN30

PCIE_TXP2_ LAN30

PCIE_RXN3 _CARD25

PCIE_RXP3 _CARD2 5

PCIE_TXN3 _CARD25

PCIE_TXP3_ CARD25

PCIE_RXN429

PCIE_RXP429

PCIE_TXN42 9

PCIE_TXP429

USB2.0/U SB3.0 COMBO 1s t

USB3.0

Right_USB_ up

+1.5V

Right_USB_ down

WLAN

FP

CLK_PCIE _CRN2 5

CLK_PCIE _CRP25

PCIE_CLK REQ_CR#25

R251 10K_4

R268 10K_4

R301 10K_4

R602 10K_4

R601 10K_4

R312 10K_4

R255 10K_4

Ra

R254 *10K_4

Rb

SG : Rb ; UMA/ OPT : Ra

R253 10K_4

R248 10K_4

R240 10K_4

R244 10K_4

R323 10K_4

R331 10K_4

R573 10K_4

R572 10K_4

R329 10K_4

3

C688 0.1U/10V _4

C687 0.1U/10V _4

C686 0.1U/10V _4

C685 0.1U/10V _4

C344 0.1U/10V _4

C337 0.1U/10V _4

R568 *0_4/S

R569 7.5K/F_4

BOARD_ID 09

BOARD_ID 19

BOARD_ID 29

+3V

for DS3

+3V_DEEP _SUS

3

2

Lynx Point (PCI-E,SMBUS,CLK)

PCIE_TXN2 _LAN_C

PCIE_TXP2_ LAN_C

PCIE_TXN3 _CARD_C

PCIE_TXP3_ CARD_C

PCIE_TXN4 _C

PCIE_TXP4_ C

PCIE_IREF

PCIE_RCO MP

TP92

TP93

CLK_PCIE _REQ0#

CLK_PCH_ SRC2N

CLK_PCH_ SRC2P

CLK_PCIE _REQ1#

CLK_PCH_ CARD2N

CLK_PCH_ CARD2P

PCIE_CLK REQ_CR#

CLK_PCH_ SRC3N

CLK_PCH_ SRC3P

CLK_PCIE _REQ3#

CLK_PCIE _REQ4#

CLK_PCH_ PEGAN

CLK_PCH_ PEGAP

CLK_PEGA _REQ#_R

PCIE Clock

WLAN

LAN

GPU

Remov e for UMA on ly.

AW31

AY31

BE32

BC32

AT31

AR31

BD33

BB33

AW33

AY33

BE34

BC34

AT33

AR33

BE36

BC36

AW36

AV36

BD37

BB37

AY38

AW38

BC38

BE38

AT40

AT39

BE40

BC40

AN38

AN39

BD42

BD41

BE30

BD29

BC30

BB29

Y43

Y45

AB1

AA44

AA42

AF1

AB43

AB45

AF3

AD43

AD45

AF43

AF45

AE44

AE42

AA2

AB40

AB39

AE4

AJ44

AJ42

AB35

AB36

AF6

AD39

AD38

CLK_PCIE _WLANN29

CLK_PCIE _WLANP29

PCIE_CLK REQ_WLAN #29

CLK_PCIE _LANP30

CLK_PCIE _LANN30

PCIE_CLK REQ_LAN#3 0

CLK_PCIE _VGA#14

CLK_PCIE _VGA14

CLK_PEGA _REQ#14

U25B

PERN1 / U SB3RN3

PERP1 / U SB3RP3

PETN1 / US B3TN3

PETP1 / USB 3TP3

PERN2/ US B3RN4

PERP2/ US B3RP4

PETN2/ USB 3TN4

PETP2/ USB 3TP4

PERN3

PERP3

PETN3

PETP3

PERN4

PERP4

PETN4

PETP4

PERN5

PERP5

PETN5

PETP5

PERN6

PERP6

PETN6

PETP6

PERN7

PERP7

PETN7

PETP7

PERN8

PERP8

PETN8

PETP8

PCIE_IREF

PCIE_RCO MP

TP11

TP6

CLKOUT_P CIE0N

CLKOUT_P CIE0P

PCIECLKRQ 0# / GPIO73

CLKOUT_P CIE1N

CLKOUT_P CIE1P

PCIECLKRQ 1# / GPIO18

CLKOUT_P CIE2N

CLKOUT_P CIE2P

PCIECLKRQ 2# / GPIO20 / SMI#

CLKOUT_P CIE3N

CLKOUT_P CIE3P

T3

PCIECLKRQ 3# / GPIO25

CLKOUT_P CIE4N

CLKOUT_P CIE4P

V3

PCIECLKRQ 4# / GPIO26

CLKOUT_P CIE5N

CLKOUT_P CIE5P

PCIECLKRQ 5# / GPIO44

CLKOUT_P CIE6N

CLKOUT_P CIE6P

PCIECLKRQ 6# / GPIO45

CLKOUT_P CIE7N

CLKOUT_P CIE7P

Y3

PCIECLKRQ 7# / GPIO46

CLKOUT_P EG_A_N

CLKOUT_P EG_A_P

PEG_A_CL KRQ# / GPIO 47

TP19

TP18

LPT_PCH_ M_EDS/BGA

PCI-E*

(+3VS5)

(+3V)

(+3V)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

RP5

0_4P2R_ 4

SML1ALE RT# / PCHHOT# / GPIO74

SMBUS

PEG_B_CL KRQ# / GPIO 56

CLOCKS

FLEX CLO CKS

CLK_PCH_ SRC3N

R295 *0_4/S

R266 *0_4/S

2

4

R275 *0_4/S

CLK_PCH_ SRC3P

CLK_PCH_ SRC2P

CLK_PCH_ SRC2N

1

CLK_PCH_ PEGAN

3

CLK_PCH_ PEGAP

2

SMBALERT # / GPIO11

SML0ALE RT# / GPIO60

SML1DATA / GPIO75

CLKIN_PC ILOOPBACK

CLKOUTF LEX0 / GPIO64

CLKOUTF LEX1 / GPIO65

CLKOUTF LEX2 / GPIO66

CLKOUTF LEX3 / GPIO67

CLK_PCIE _REQ3#

CLK_PCIE _REQ1#

CLK_PEGA _REQ#_R

(+3VS5)

SMBCLK

SMBDATA

(+3VS5)

SML0CL K

SML0DATA

(+3VS5)

(+3VS5)

SML1CL K / GPIO58

(+3VS5)

CLKOUT_P EG_B_N

CLKOUT_P EG_B_P

(+3VS5)

CLKOUT_I TPXDP_N

CLKOUT_I TPXDP_P

CLKOUT_D PNS_N

CLKOUT_D PNS_P

CLKOUT_D P_N

CLKOUT_D P_P

CLKOUT_D MI_N

CLKOUT_D MI_P

CLKIN_DM I_N

CLKIN_DM I_P

CLKIN_G ND1_N

CLKIN_G ND1_P

CLKIN_DO T_96N

CLKIN_DO T_96P

CLKIN_SA TA_N

CLKIN_SA TA_P

REFCLK1 4IN

XTAL25_IN

XTAL25_O UT

ICLK_IREF

DIFFCL K_BIASREF

CLKOUT_3 3MHZ0

CLKOUT_3 3MHZ1

CLKOUT_3 3MHZ2

CLKOUT_3 3MHZ3

CLKOUT_3 3MHZ4

(+3V)

(+3V)

(+3V)

(+3V)

N7

SMBALERT #

R10

SMB_PCH _CLK

U11

SMB_PCH _DAT

N8

DRAMRST_ CNTRL_PCH

U8

SMB_ME0 _CLK

R7

SMB_ME0 _DAT

H6

SML1ALE RT#_R

K6

SMB_ME1 _CLK

N11

SMB_ME1 _DAT

Y39

Y38

U4

CLK_PEGB _REQ#

AH43

CLK_PCH_ ITPN

AH45

CLK_PCH_ ITPP

AF35

AF36

AJ40

AJ39

AF39

AF40

AY24

CLK_BUF _PCIE_3GPLL #

AW24

CLK_BUF _PCIE_3GPLL

AR24

CLK_BUF _BCLK_N

AT24

CLK_BUF _BCLK_P

H33

CLK_BUF _DREFCLK#

G33

CLK_BUF _DREFCLK

BE6

CLK_BUF _DREFSSCLK#

BC6

CLK_BUF _DREFSSCLK

F45

CLK_PCH_ 14M

D17

CLK_PCI_ FB

AM43

XTAL25_IN

AL44

AM45

ICLK_IREF

AN44

ICLK_BIAS

D44

CLK_PCI_ TPM_R

E44

CLK_PCI_ CARD_R

B42

CLK_PCH_ PCI2

F41

CLK_PCH_ PCI3

A40