NGEF(KEY E)

WIFI/BT MODULE

PCle X4

USB2.0

GSPI

12C

gerprint connector

Fin

FPC to touch panel

Changer

Power LED

Hall sensor

<XR_PAGE_TITLE>

TABLE OF CONTENTS

6

3

287 54 1

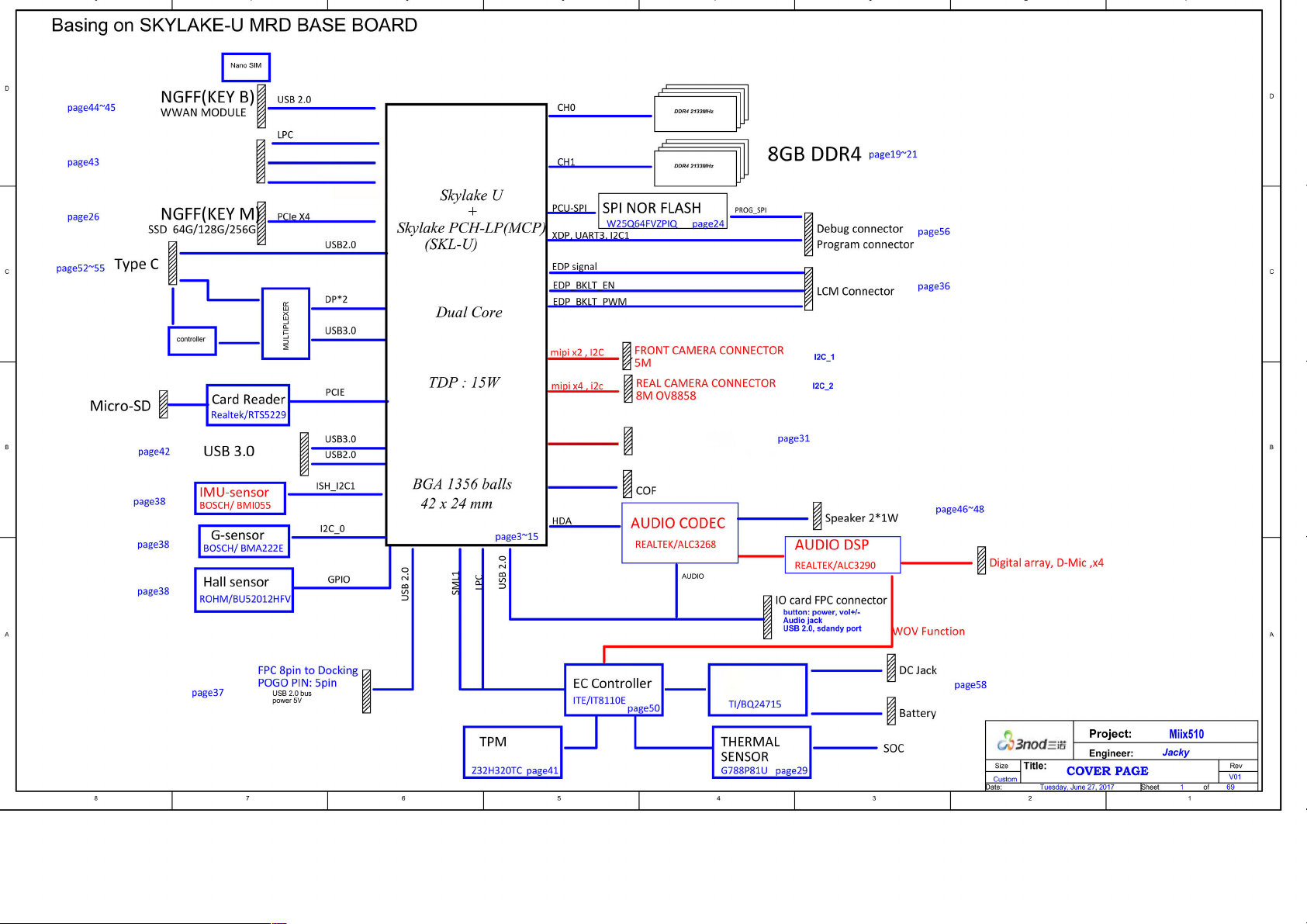

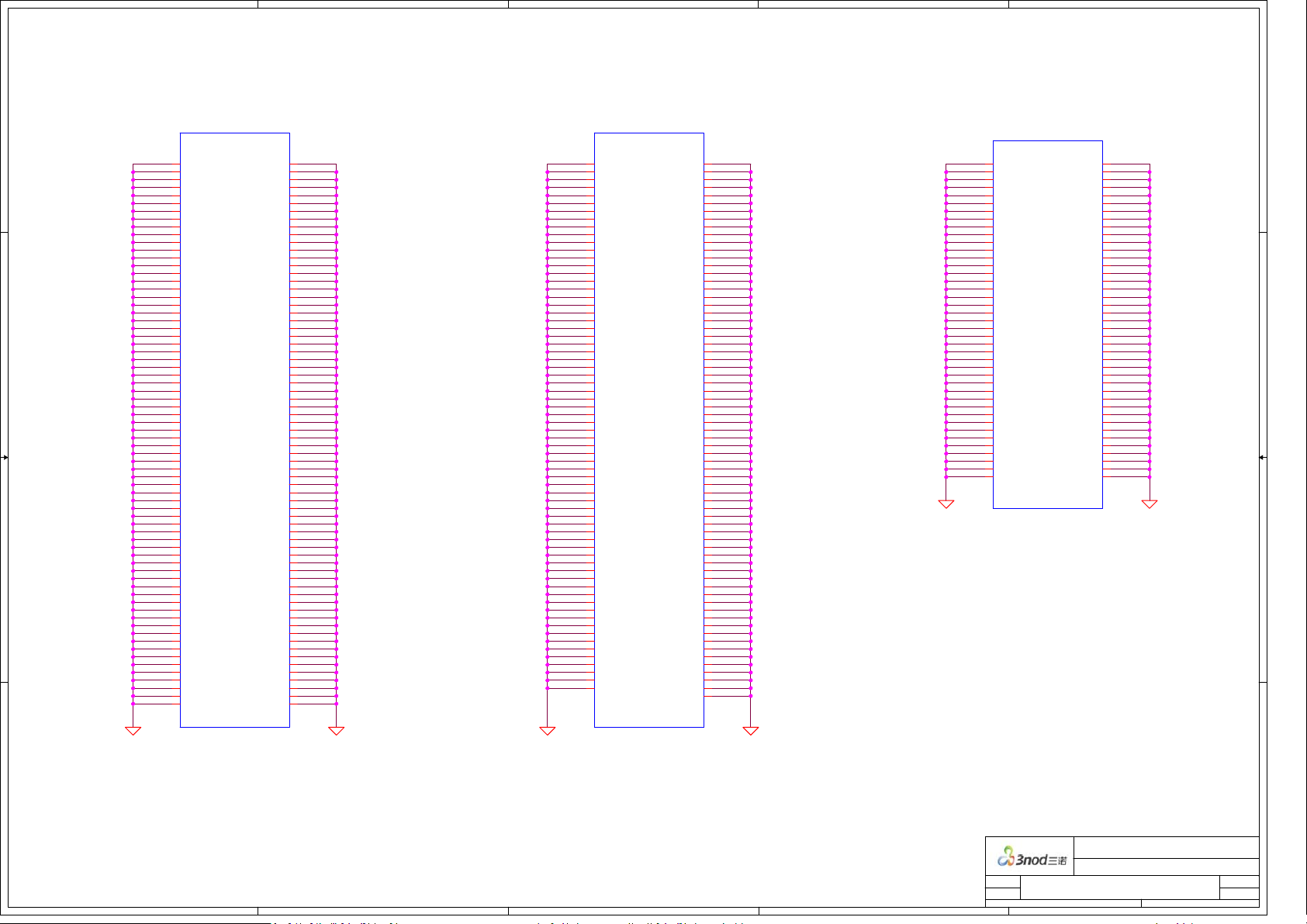

01 -- COVER PAGE

D

02 -- TABLE OF CONTENTS

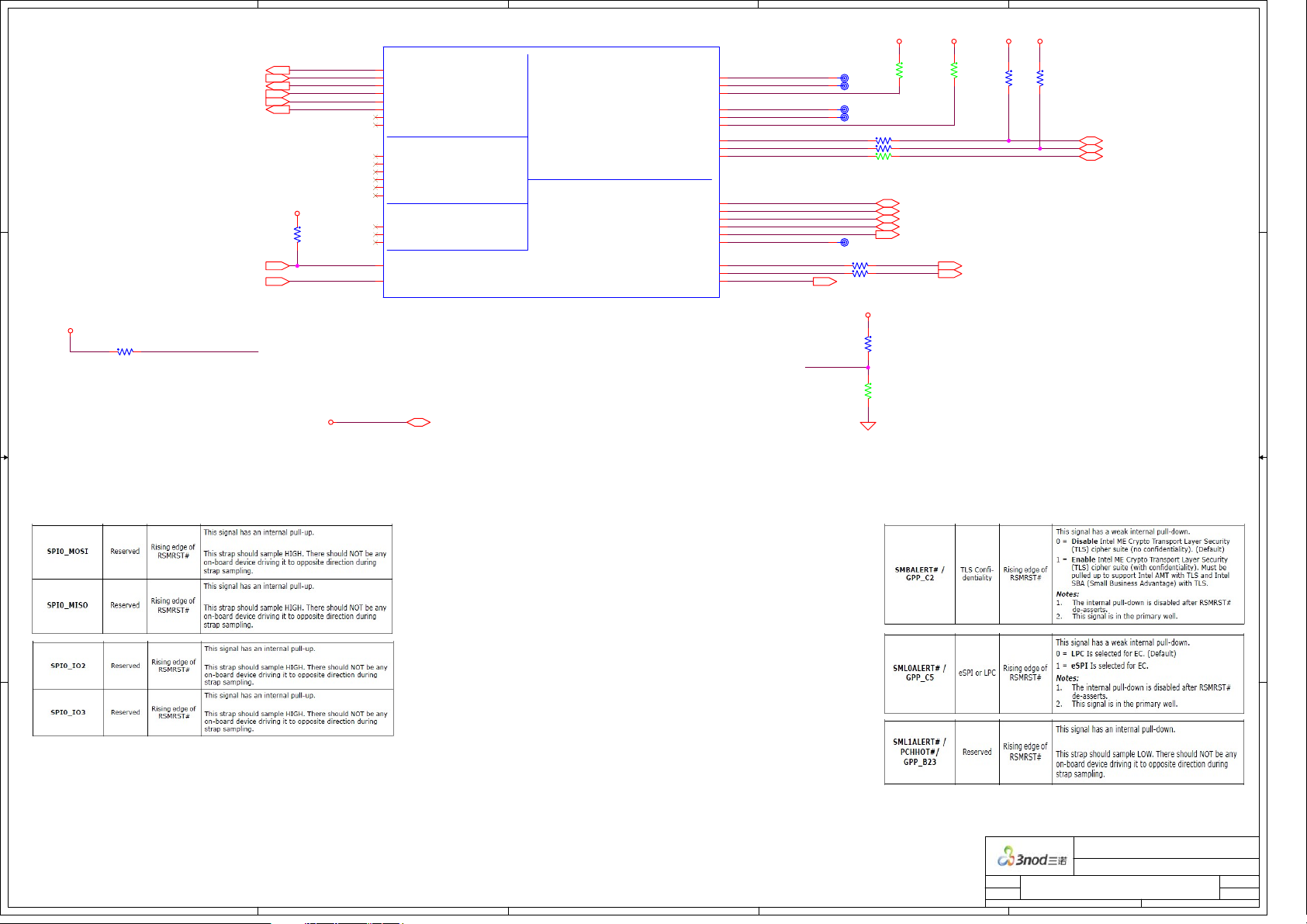

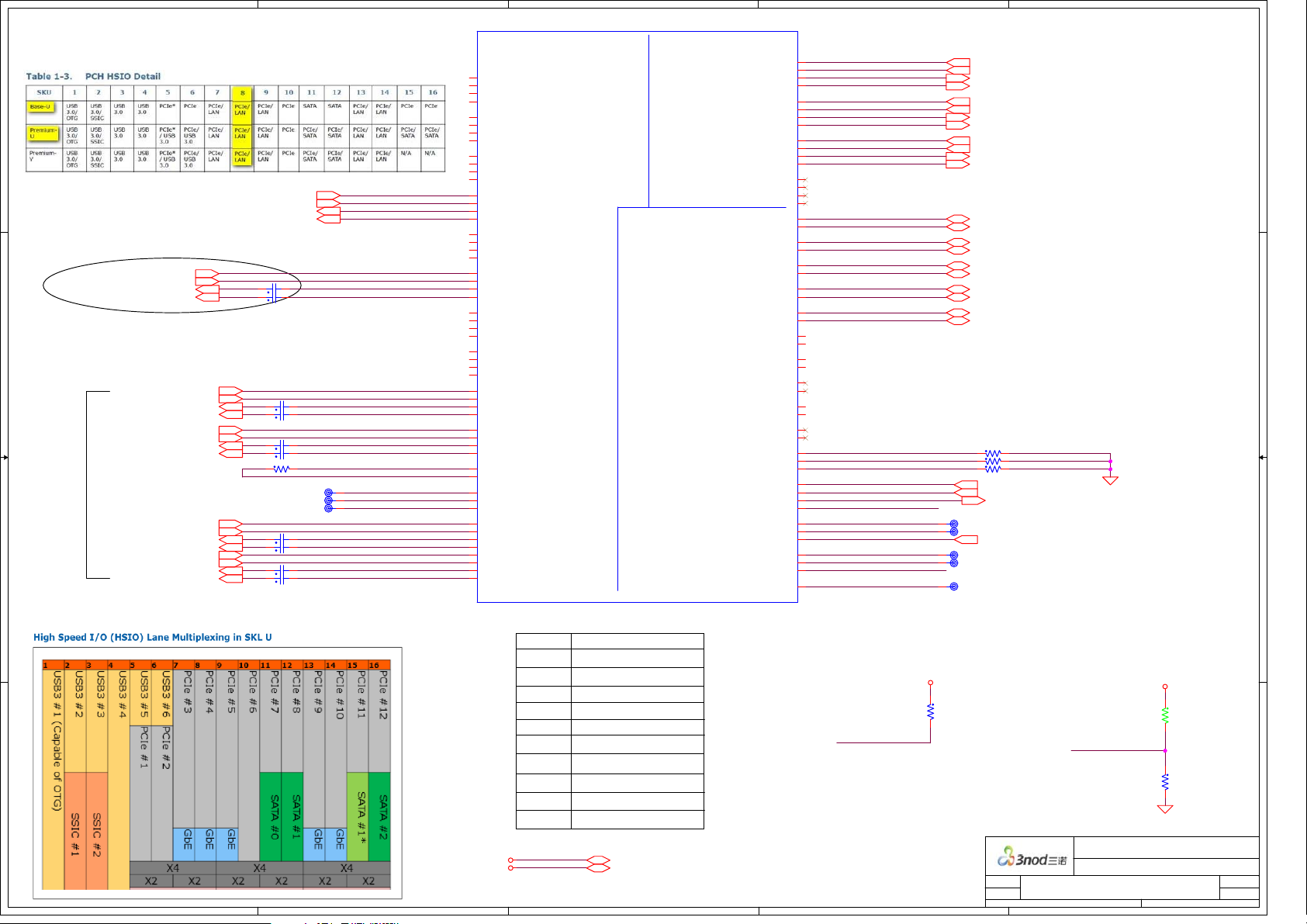

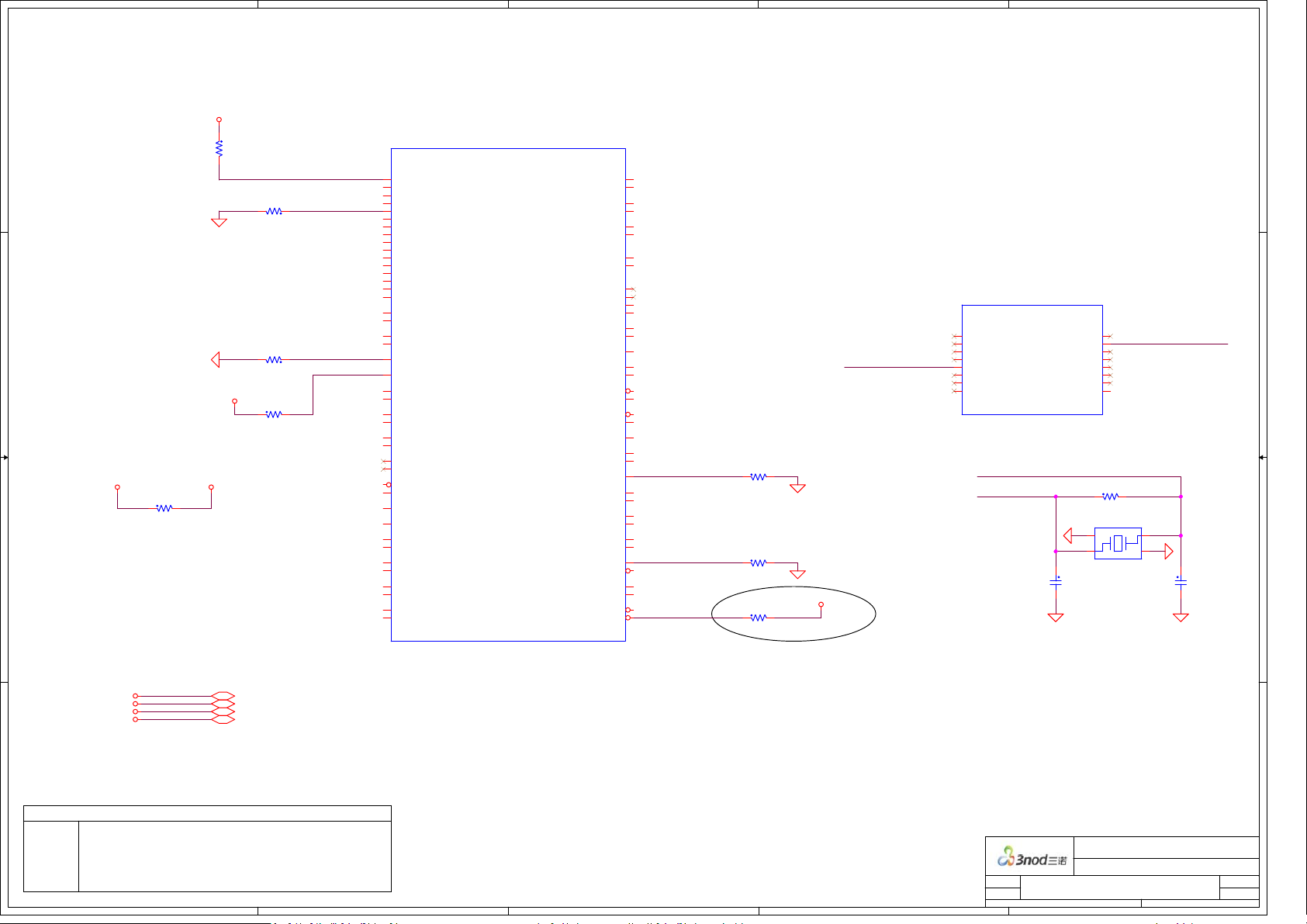

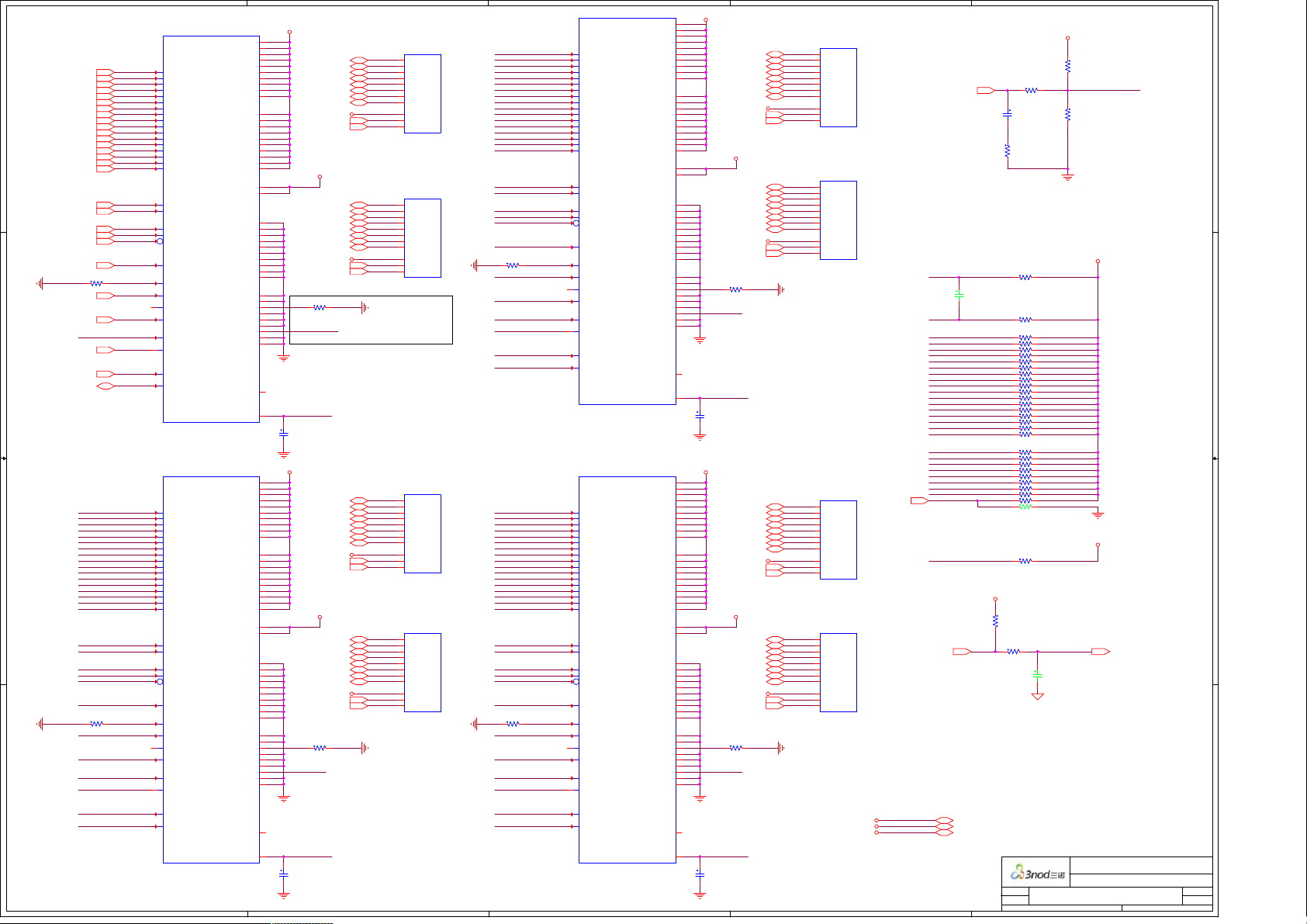

03--SKL-U(1/12)DDI,MISC,XDP,EDP

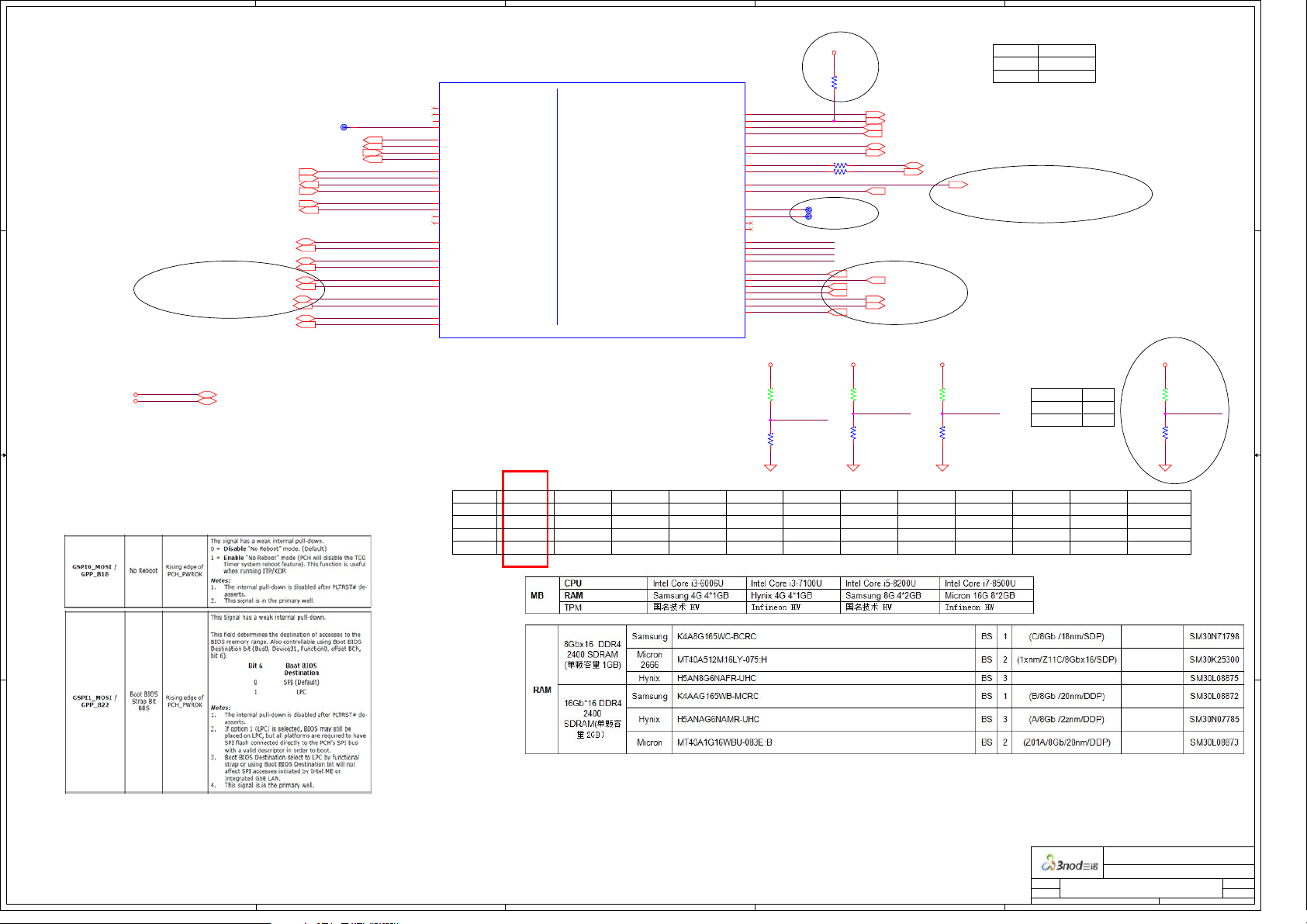

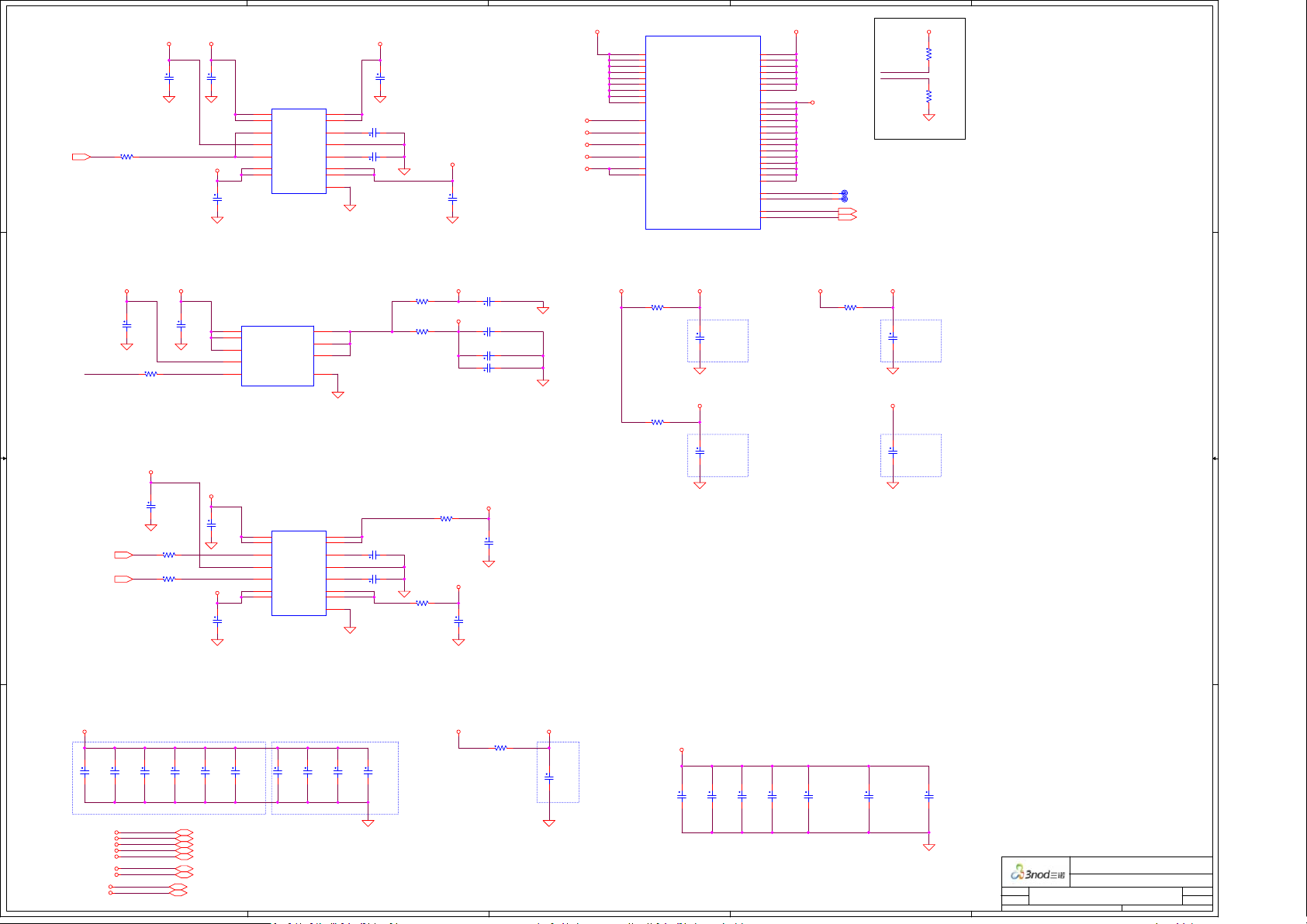

04--SKL-U(2/12)DDR4

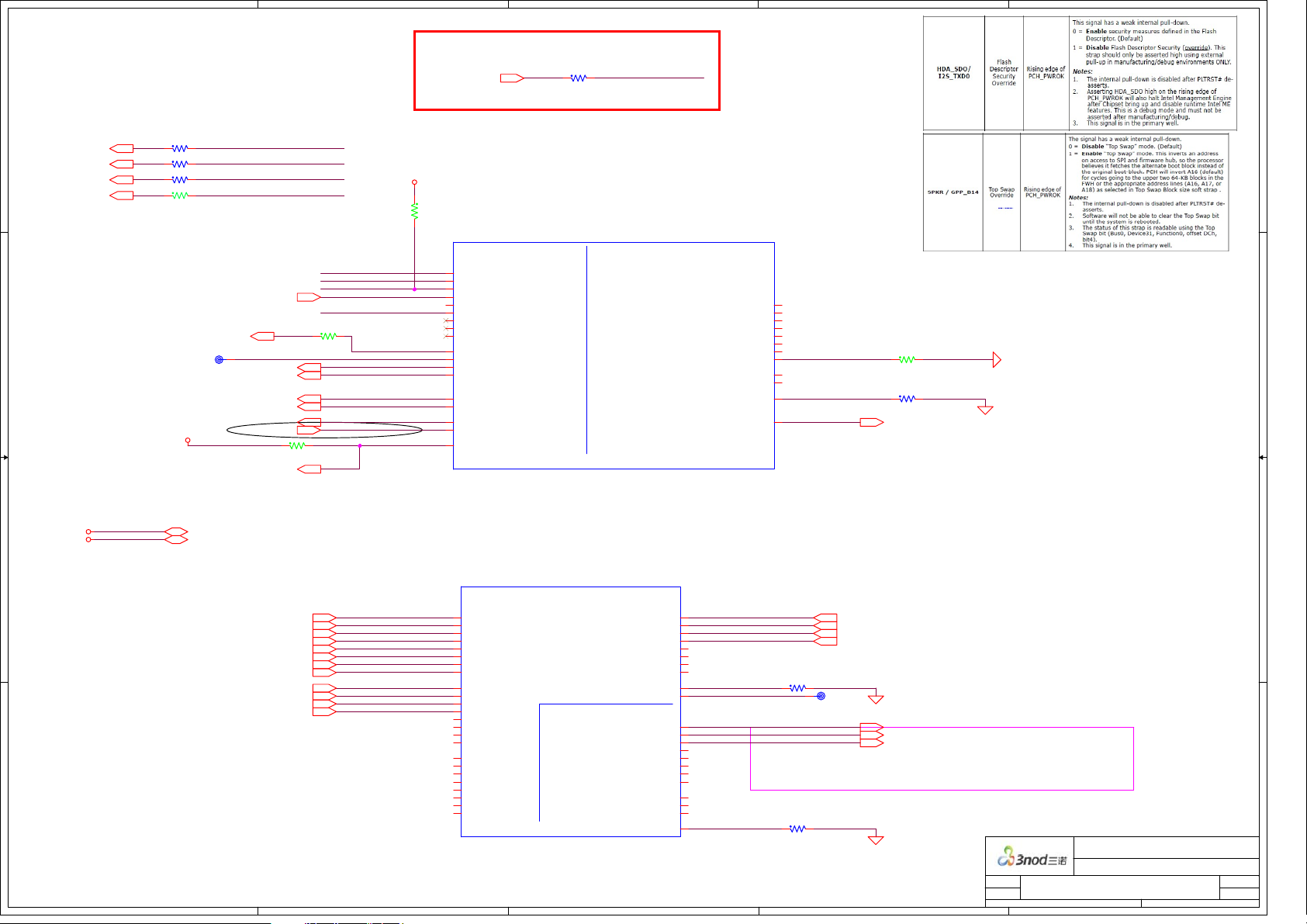

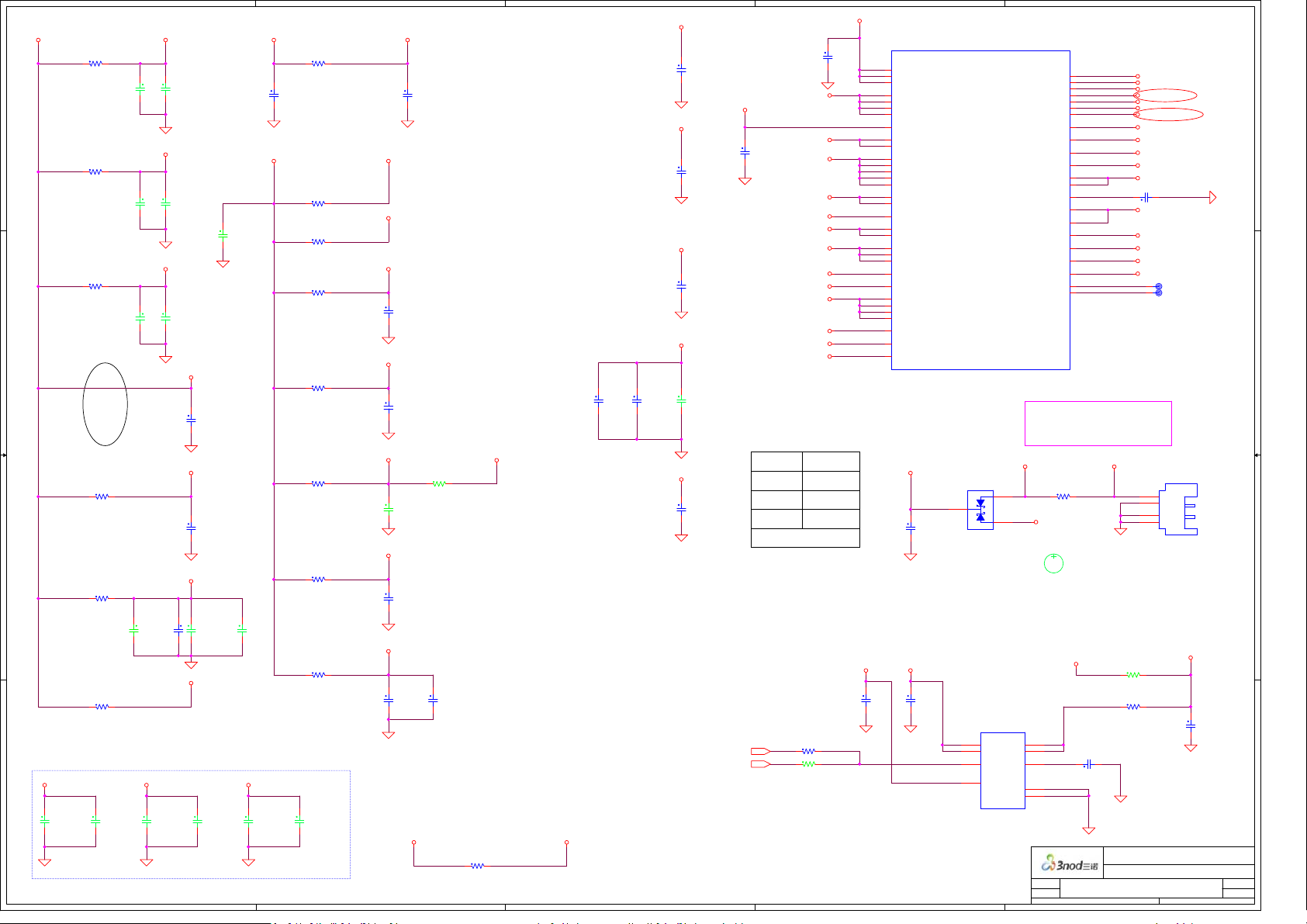

05--SKL-U(3/12)SPI,ESPI,SMB,LPC

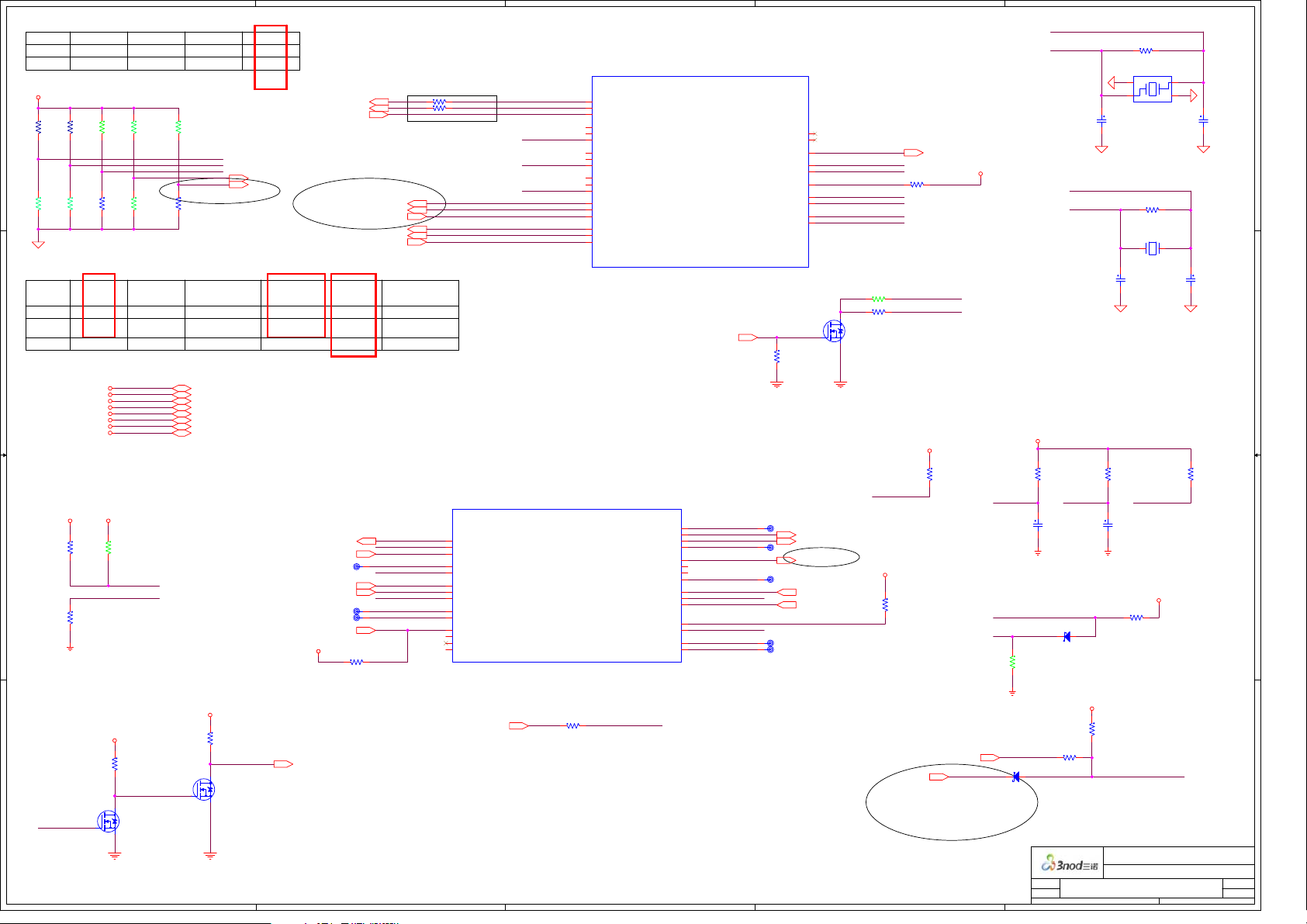

06--SKL-U(4/12)HDA,EMMC,SD

07--SKL-U(5/12)CLK,GPIO

08--SKL-U(6/12)GPIO

09--SKL-U(7/12)PCIE,USB,SATA

C

10--SKL-U(8/12)Power

11--SKL-U(9/12)Power

12--SKL-U(10/12)Power,SVID

13--SKL-U(11/12)GND

14--SKL-U(12/12)RSVD

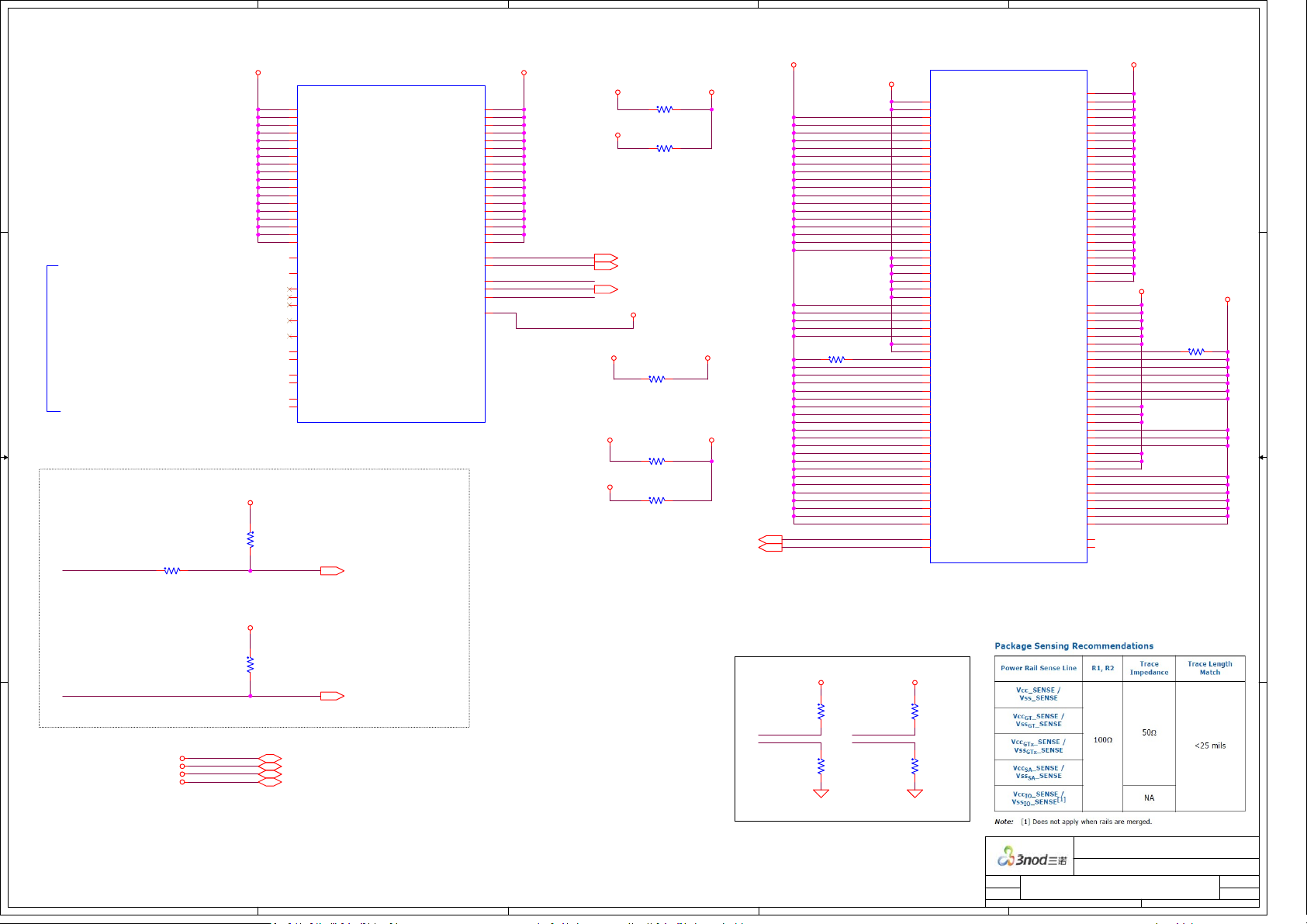

15--SOC (DECOUPLING)

16--NA

17--NA

18--NA

B

19--DDR4_CHA

20--DDR4_CHB

21--DDR4 Decoupling

22--NA

23--RF / EMC Solution

24 -- SYSTEM FLASH

25 -- NC_EMMC

26 -- PCIE SSD MODULE

27 -- NC_MICRO-SD CARD

A A

28 -- NC_SD CARD POWER

29 -- CPU THERMAL SENSOR

30 -- FAN conn

31 -- Finger print

32 -- NA

33 -- NA

34 -- NC_HDMI LEVEL SHIFTERS

35 -- NC_HDMI CONNECTOR

36 -- DISPLAY

37 -- TOUCH PANEL AND DOCK

38 -- SENSORS & LID

39 -- FRONT AND REAR CAMERA CON

40 -- CAMERA DISCRETE CONTROLL

41 -- TPM

42 -- USB3.0 CONN

43 -- WLAN WIFI BT MODULE

44 -- WWAN MODULE

45 -- MICRO SIM

46 -- AUDIO CODEC

47 -- AUDIO-MIC AND SPKRS

48 -- IO board CONN

49 -- DC JACK

50 -- EMBEDDED CONTROLLER

51 -- BUTTON & LED

52 -- TYPE-C MULTIPLEXER

53 -- TYPE-C PD CONTROLLER

54 -- NC_TYPE-C BOOST VR

55 -- TYPE-C CONNECTOR

56 -- UART CONN & HOLE & CLIP

57 -- HW Change list

58--PWR_DCIN/BATT CONN

59--PWR_CHARGER(OZ8690)

60--PWR-+V5P0A / +V3P3A

61--PWR-DDR

62--PWR-+V2P5U_VPP

63--PWR-+1.0V_PRIM

64--PWR-NA

65--PWR-+1.8V_PRIM

66--PWR-CPU VR IC

67--PWR-VCC_CORE/GT/SA

68--PWR-Block Diagram

69--PWR_Change list

D

C

B

87

INTERNAL ONLY

BPAGE DRAWING

sky_y_mrd._

Wed Jun 03 11:22:42 2015

Project:

Project:

Project:

Engineer:

Engineer:

Size

Size

Size

Title:

Title:

Title:

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

34

2

Engineer:

TABLE OF CONTENTS

TABLE OF CONTENTS

TABLE OF CONTENTS

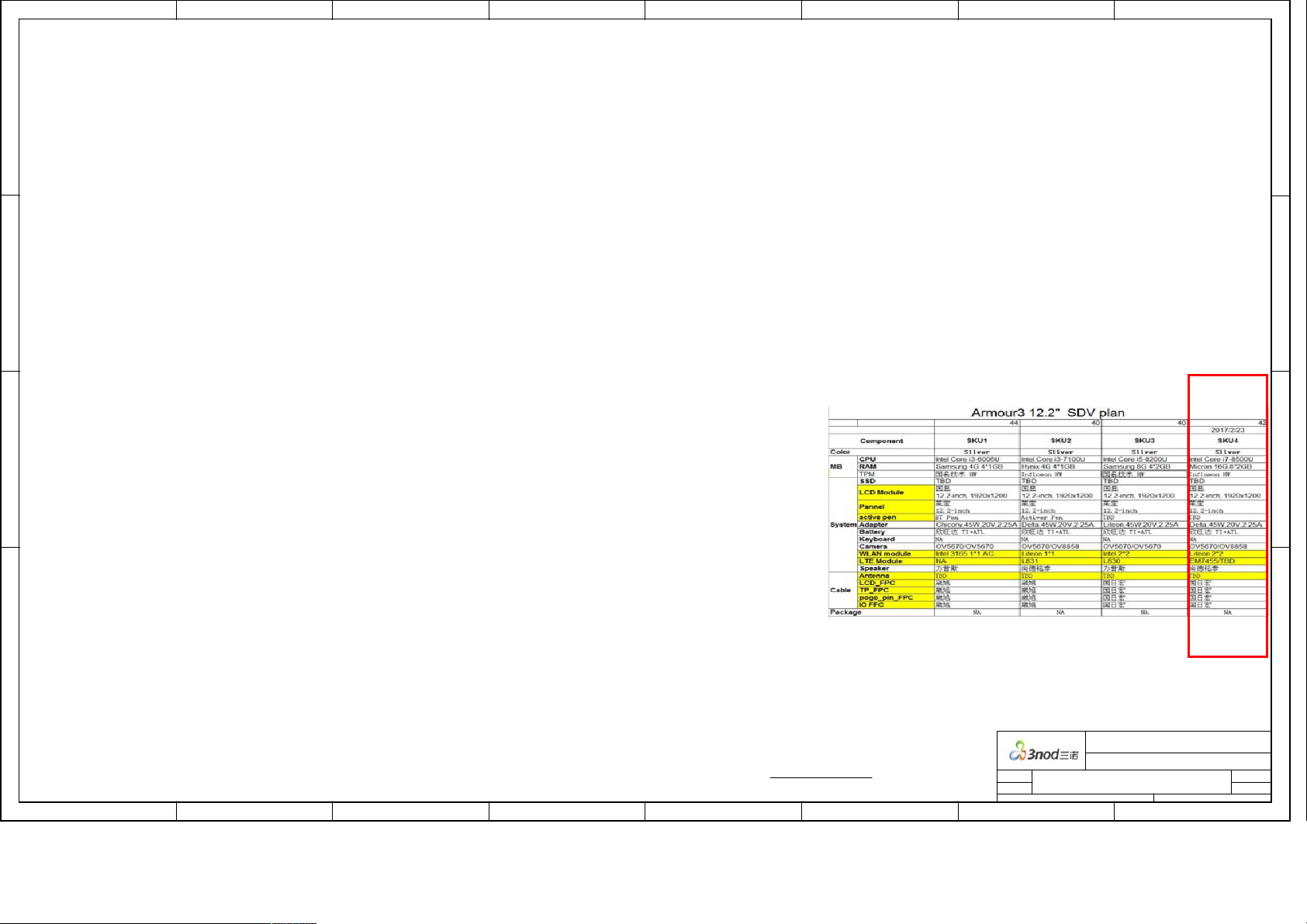

Miix510

Miix510

Miix510

Jacky

Jacky

Jacky

Rev

Rev

Rev

V01

V01

2 69Tuesday, June 27, 2017

2 69Tuesday, June 27, 2017

2 69Tuesday, June 27, 2017

V01

156

A

1 1

B

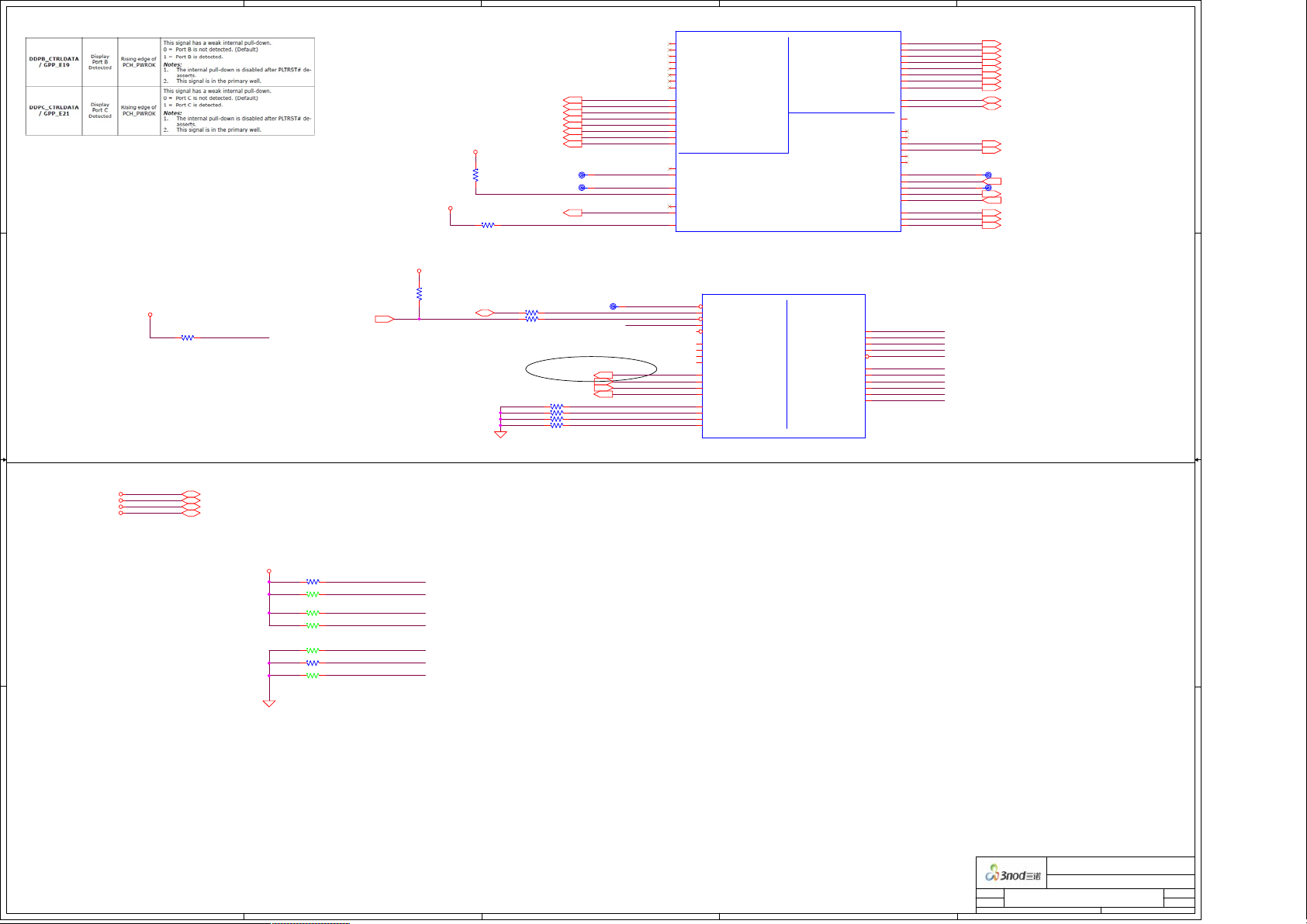

DDI2_TX0_DN52

DDI2_TX0_DP52

DDI2_TX1_DN52

DDI2_TX1_DP52

R1092

2.2K

5%

R0402_N

I

DDI2_TX2_DN52

DDI2_TX2_DP52

DDI2_TX3_DN52

DDI2_TX3_DP52

No need HDMI

TOUCH_PANEL_RESET_N37

24.9R

IR0402 1%

<Type-c>

+V3P3A

+1.0VS_VCCIO

R1009

C

<No need HDMI>

DDI1_DDC_SDA

TP_DDI2_DDC_SCL

DDI2_DDC_SDA

EDP_COMP

UC1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKL-U_BGA1356

@

SKL-U

DDI

DISPLAY SIDEBANDS

1 OF 20

D

Rev_0.53

C47

EDP_TXN[0]

C46

EDP_TXP[0]

D46

EDP_TXN[1]

C45

EDP_TXP[1]

A45

EDP_TXN[2]

B45

EDP_TXP[2]

A47

EDP_TXN[3]

B47

EDP_TXP[3]

E45

EDP

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

F45

B52

G50

F50

E48

F48

G46

F46

DDI1_HPD

L9

DDI2_HPD

L7

TP_SMC_EXTSMI_N

L6

SMC_RUNTIME_SCI_N

N9

EDP_HPD

L10

R12

R11

U13

EDP_TX0_SOC_DN 36

EDP_TX0_SOC_DP 36

EDP_TX1_SOC_DN 36

EDP_TX1_SOC_DP 36

EDP_TX2_SOC_DN 36

EDP_TX2_SOC_DP 36

EDP_TX3_SOC_DN 36

EDP_TX3_SOC_DP 36

EDP_AUX_SOC_DN 36

EDP_AUX_SOC_DP 36

DDI2_AUX_DN 52

DDI2_AUX_DP 52

TP9991TP1064

DDI2_HPD 50,53

TP1049TP1063

SMC_RUNTIME_SCI_N 50

EDP_HPD 36

EDP_BKLT_EN 36

EDP_BKLT_PWM 36

EDP_VDD_EN 36

E

<eDP>

No need HDMI

From eDP

+1.0VS_VCCSTG

R1024

1K

R0402

+1.0V_VCCST

2 2

R1021 1K

THERMTRIP_SOC_N

IR0402_N 1%

PROCHOT_N50,66

5%

I

PECI_EC50

CRB install 499R,ARMOUR install 0R

R1022 43R

R1023 499R

TOUCH_PANEL_INT_N37

HW_ID37,31

R1025 49.9R

R1026 49.9R

RC7 49.9R

RC8 49.9R

5/17 update

WOV_KILL_N47

BT_RF_KILL_N43

TP1019

IR0402_N1%

IR0402 1%

IR0402 1%

IR0402 1%

IR0402 1%

IR0402 1%

CATERR_SOC_N

PECI_SOC

H_PROCHOT#_R

THERMTRIP_SOC_N

CPU_POPIRCOMP

PCH_OPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

D63

A54

C65

C63

A65

C55

D55

B54

C56

A6

A7

BA5

AY5

AT16

AU16

H66

H65

UC1D

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

SKL-U_BGA1356

@

CPU MISC

SKL-U

4 OF 20

JTAG

Rev_0.53

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

XDP_TCK0

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST_N

XDP_TCK1_PCH

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST_N

XDP_TCK0

+V3P3A

+1.0VS_VCCIO

+1.0VS_VCCSTG

+1.0V_VCCST

3 3

4 4

A

+V3P3A 4,5,6,7,9,10,11,23,24,29,31,37,38,42,47,49,50,51,52,53,56,60,62,65,66,67

+1.0VS_VCCIO 10,14

+1.0VS_VCCSTG 10,12

+1.0V_VCCST 7,10,12,14,66

+1.0VS_VCCSTG

IR0402 5%

R1028 51R

R1029 51R

R1027 51R

R1031 51R

R1034 51R

R1032 51R

R1033 51R

NIR0402 5%

NIR0402 5%

NIR0402 5%

NIR0402 5%

IR0402 5%

NIR0402 5%

B

XDP_TDO

XDP_TMS

XDP_TDI

XDP_TCK0

XDP_TCK1_PCH

XDP_TCK0

XDP_TRST_N

Project:

Project:

Project:

Miix510

Miix510

Miix510

Jacky

Jacky

Engineer:

Engineer:

Size

Size

Size

Title:

Title:

Title:

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

C

D

Date: Sheet of

Engineer:

SKL-U(1/12)DDI,MISC,XDP,EDP

SKL-U(1/12)DDI,MISC,XDP,EDP

SKL-U(1/12)DDI,MISC,XDP,EDP

Jacky

E

Rev

Rev

Rev

V01

V01

V01

3 69Tuesday, June 27, 2017

3 69Tuesday, June 27, 2017

3 69Tuesday, June 27, 2017

5

4

3

2

1

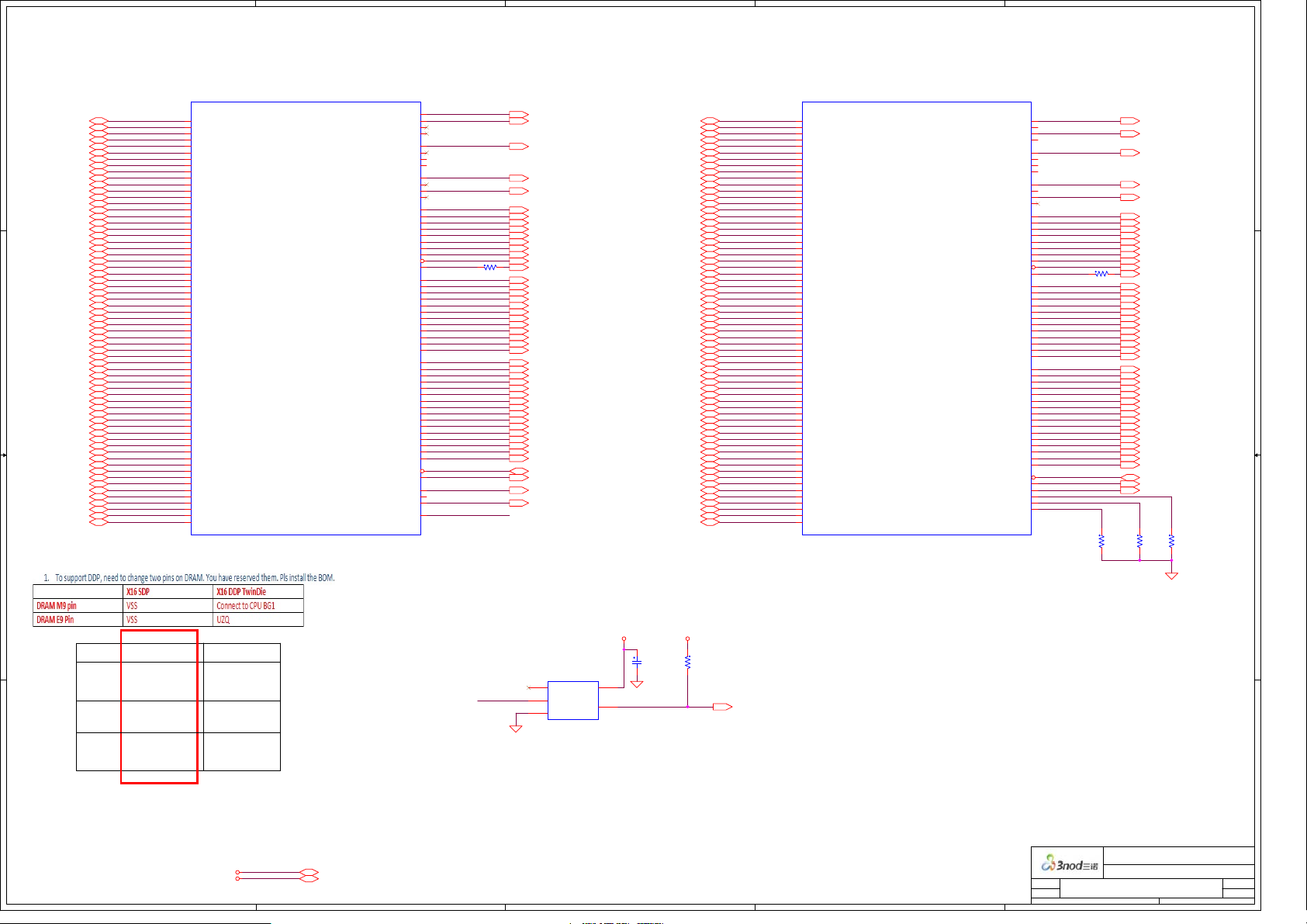

Non‐Interleaved

UC1B

D D

C C

B B

M_A_DQ<0>19

M_A_DQ<1>19

M_A_DQ<2>19

M_A_DQ<3>19

M_A_DQ<4>19

M_A_DQ<5>19

M_A_DQ<6>19

M_A_DQ<7>19

M_A_DQ<8>19

M_A_DQ<9>19

M_A_DQ<10>19

M_A_DQ<11>19

M_A_DQ<12>19

M_A_DQ<13>19

M_A_DQ<14>19

M_A_DQ<15>19

M_A_DQ<32>19

M_A_DQ<33>19

M_A_DQ<34>19

M_A_DQ<35>19

M_A_DQ<36>19

M_A_DQ<37>19

M_A_DQ<38>19

M_A_DQ<39>19

M_A_DQ<40>19

M_A_DQ<41>19

M_A_DQ<42>19

M_A_DQ<43>19

M_A_DQ<44>19

M_A_DQ<45>19

M_A_DQ<46>19

M_A_DQ<47>19

M_B_DQ<0>20

M_B_DQ<1>20

M_B_DQ<2>20

M_B_DQ<3>20

M_B_DQ<4>20

M_B_DQ<5>20

M_B_DQ<6>20

M_B_DQ<7>20

M_B_DQ<8>20

M_B_DQ<9>20

M_B_DQ<10>20

M_B_DQ<11>20

M_B_DQ<12>20

M_B_DQ<13>20

M_B_DQ<14>20

M_B_DQ<15>20

M_B_DQ<32>20

M_B_DQ<33>20

M_B_DQ<34>20

M_B_DQ<35>20

M_B_DQ<36>20

M_B_DQ<37>20

M_B_DQ<38>20

M_B_DQ<39>20

M_B_DQ<40>20

M_B_DQ<41>20

M_B_DQ<42>20

M_B_DQ<43>20

M_B_DQ<44>20

M_B_DQ<45>20

M_B_DQ<46>20

M_B_DQ<47>20

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

@

SKL-U

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR CH - A

2 OF 20

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

M_A_BG1_SOC

R0402_N 0R

RM97

DDR_VTT_CTRL

M_A_DIM0_CK_DDR0_DN 19

M_A_DIM0_CK_DDR0_DP 19

M_A_DIM0_CKE0 19

M_A_DIM0_CS0_N 19

M_A_DIM0_ODT0 19

M_A_A5 19

M_A_A9 19

M_A_A6 19

M_A_A8 19

M_A_A7 19

M_A_BG0 19

M_A_A12 19

M_A_A11 19

M_A_ACT_N 19

5%

M_A_A13 19

M_A_A15_CAS_N 19

M_A_A14_WE_N 19

M_A_A16_RAS_N 19

M_A_BA0 19

M_A_A2 19

M_A_BA1 19

M_A_A10_AP 19

M_A_A1 19

M_A_A0 19

M_A_A3 19

M_A_A4 19

M_A_DQS_DN<0> 19

M_A_DQS_DP<0> 19

M_A_DQS_DN<1> 19

M_A_DQS_DP<1> 19

M_A_DQS_DN<4> 19

M_A_DQS_DP<4> 19

M_A_DQS_DN<5> 19

M_A_DQS_DP<5> 19

M_B_DQS_DN<0> 20

M_B_DQS_DP<0> 20

M_B_DQS_DN<1> 20

M_B_DQS_DP<1> 20

M_B_DQS_DN<4> 20

M_B_DQS_DP<4> 20

M_B_DQS_DN<5> 20

M_B_DQS_DP<5> 20

DDR0_A_ALERT_N 19

DDR0_A_PARITY 19

M_A_BG1 19

NI

2/2 add 0R

+V_DDR_CA_VREF 19

+V_DDR_VREFDQ02_CHB 20

M_A_DQ<16>19

M_A_DQ<17>19

M_A_DQ<18>19

M_A_DQ<19>19

M_A_DQ<20>19

M_A_DQ<21>19

M_A_DQ<22>19

M_A_DQ<23>19

M_A_DQ<24>19

M_A_DQ<25>19

M_A_DQ<26>19

M_A_DQ<27>19

M_A_DQ<28>19

M_A_DQ<29>19

M_A_DQ<30>19

M_A_DQ<31>19

M_A_DQ<48>19

M_A_DQ<49>19

M_A_DQ<50>19

M_A_DQ<51>19

M_A_DQ<52>19

M_A_DQ<53>19

M_A_DQ<54>19

M_A_DQ<55>19

M_A_DQ<56>19

M_A_DQ<57>19

M_A_DQ<58>19

M_A_DQ<59>19

M_A_DQ<60>19

M_A_DQ<61>19

M_A_DQ<62>19

M_A_DQ<63>19

M_B_DQ<16>20

M_B_DQ<17>20

M_B_DQ<18>20

M_B_DQ<19>20

M_B_DQ<20>20

M_B_DQ<21>20

M_B_DQ<22>20

M_B_DQ<23>20

M_B_DQ<24>20

M_B_DQ<25>20

M_B_DQ<26>20

M_B_DQ<27>20

M_B_DQ<28>20

M_B_DQ<29>20

M_B_DQ<30>20

M_B_DQ<31>20

M_B_DQ<48>20

M_B_DQ<49>20

M_B_DQ<50>20

M_B_DQ<51>20

M_B_DQ<52>20

M_B_DQ<53>20

M_B_DQ<54>20

M_B_DQ<55>20

M_B_DQ<56>20

M_B_DQ<57>20

M_B_DQ<58>20

M_B_DQ<59>20

M_B_DQ<60>20

M_B_DQ<61>20

M_B_DQ<62>20

M_B_DQ<63>20

Non‐Interleaved

UC1C

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

@

SKL-U

DDR CH - B

3 OF 20

Rev_0.53Rev_0.53

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_B_BG1_SOC

R0402_N 0R

RM98

5%

DDR4_DRAMRST_N

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

RM1

100R

R0402_N

M_B_DIM0_CK_DDR0_DN 20

M_B_DIM0_CK_DDR0_DP 20

M_B_DIM0_CKE0 20

M_B_DIM0_CS0_N 20

M_B_DIM0_ODT0 20

M_B_A5 20

M_B_A9 20

M_B_A6 20

M_B_A8 20

M_B_A7 20

M_B_BG0 20

M_B_A12 20

M_B_A11 20

M_B_ACT_N 20

M_B_BG1 20

NI

M_B_A13 20

M_B_A15_CAS_N 20

M_B_A14_WE_N 20

M_B_A16_RAS_N 20

M_B_BA0 20

M_B_A2 20

M_B_BA1 20

M_B_A10_AP 20

M_B_A1 20

M_B_A0 20

M_B_A3 20

M_B_A4 20

M_A_DQS_DN<2> 19

M_A_DQS_DP<2> 19

M_A_DQS_DN<3> 19

M_A_DQS_DP<3> 19

M_A_DQS_DN<6> 19

M_A_DQS_DP<6> 19

M_A_DQS_DN<7> 19

M_A_DQS_DP<7> 19

M_B_DQS_DN<2> 20

M_B_DQS_DP<2> 20

M_B_DQS_DN<3> 20

M_B_DQS_DP<3> 20

M_B_DQS_DN<6> 20

M_B_DQS_DP<6> 20

M_B_DQS_DN<7> 20

M_B_DQS_DP<7> 20

DDR1_B_ALERT_N 20

DDR1_B_PARITY 20

DDR4_DRAMRST_N 19

RM2

RM3

1%

80.6R

1%

R0402_N

I

I

R0402_N

200R

2/2 add 0R

1%

I

4Gb or 8GbMemory size

RM95,RM96,RM97,RM98

need uninstall

DRAM M9 pin

RM99,RM100

need install

DRAM E9 pin RM79,RM81,RM83,RM85,

RM87,RM89,RM91,RM93

need install 0 ohm

RM3 200R

DDR_RCOMP0

A A

2/2 Add (4Gb 8Gb) & (16Gb) BOM option table

need install

Default

5

DDPSDP

8G or 16Gb

RM95,RM96,RM97,RM98

need install

RM99,RM100

need uninstall

RM79,RM81,RM83,RM85,

RM87,RM89,RM91,RM93

need install 240 ohm

RM3 121R

need install page04

+V3P3A

+V1P2U_VDDQ

page4,19,20

page19,20

+V3P3A 3,5,6,7,9,10,11,23,24,29,31,37,38,42,47,49,50,51,52,53,56,60,62,65,66,67

+V1P2U_VDDQ 10,19,20,21,61

4

DDR_VTT_CTRL

NC1VCC

2

A

3

GND

74AUP1G07GW

sot_353

UM10

5

4

Y

I

CM1

0.1uF 10V 10%

C0402

X5R

I

3

+V3P3A+V1P2U_VDDQ

RM4

100K

5%

R0402

I

SM_PG_CTRL 61

Project:

Project:

Project:

Miix510

Miix510

Miix510

Jacky

Jacky

Engineer:

Engineer:

Size

Size

Size

Title:

Title:

Title:

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Engineer:

SKL-U(2/12)DDR4

SKL-U(2/12)DDR4

SKL-U(2/12)DDR4

1

Jacky

Rev

Rev

Rev

V01

V01

V01

4 69Tuesday, July 25, 2017

4 69Tuesday, July 25, 2017

4 69Tuesday, July 25, 2017

5

4

3

2

1

UC1E

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL-U_BGA1356

@

SPI - FLASH

SPI - TOUCH

C LINK

FLASH_SPI_CLK24,50

FLASH_SPI_MISO24,50

SPI Flash

D D

FLASH_SPI_MOSI24,50

FLASH_SPI_IO224

FLASH_SPI_IO324

FLASH_SPI_CS0_N24,50

AV2

AW3

AV3

AW2

AU4

AU3

AU2

AU1

M2

M3

V1

V2

M1

+V3P3SX

AW13

AY11

G3

G2

G1

5/9 EC_KBRST# Add PU R1066 10Kohm +V3P3SX

EC_KBRST#50

To EC

LPC_SERIRQ50

R1066

10K

5%

R0402_N

I

LPC Mode

+V3P3A

IR0402 5%

C C

R1059 10K

LPC_SERIRQ

5/9 Page50 EC pin24 BAT_CHGOK_LED_N change to EC_KBRST#,connect to SOC pin AW13(RCIN)

+V3P3A

+V3P3A 3,4,6,7,9,10,11,23,24,29,31,37,38,42,47,49,50,51,52,53,56,60,62,65,66,67

SKL-U

LPC

5 OF 20

SMBUS, SMLINK

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

Rev_0.53

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A8/CLKRUN#

TP_SMB_CLK

R7

TP_SMB_DATA

R8

STRAP_GPP_C2

R10

SML0_CLK

R9

SML0_DATA

W2

STRAP_GPP_C5

W1

SML1_CLK_R

W3

SML1_DATA_R

V3

THERMAL_ALERT#_R

AM7

AY13

BA13

BB13

AY12

BA12

TP_PM_SUS_STAT_N

BA11

LPC_CLK_EC_R

AW9

LPC_CLK_PRT80_R

AY9

AW11

R1064

R1065

PM_CLKRUN_N 50

PM_CLKRUN_N

+V3P3A +V3P3A

R1055

1K

TP1053

TP1054

TP9998

TP9999

R9861 0R

R9862 0R

R9863 0R

R0402

5%

NI

3/2 R9863 change to NI,THERMAL HW shutdown

LPC_AD0 41,43,50

LPC_AD1 41,43,50

LPC_AD2 41,43,50

LPC_AD3 41,43,50

I

R0402 5%

22R

I

R0402 5%

22R

LPC_FRAME_N 41,43,50

TP1052

+V3P3A

R1061

8.2K

R0402

5%

I

R1073

1K

R0402

5%

NI

+V3P3A +V3P3A

R1053

100K

R0402

5%

NI

IR0402_N 5%

IR0402_N 5%

NIR0402_N 5%

R9872

10K

5%

R0402_N

I

TPM/WLAN/EC

LPC_CLK_EC 50

LPC_CLK_PRT80 41,43

R9873

10K

5%

R0402_N

I

Difference with armour

connect to thermal sensor

SML1_CLK 29

SML1_DATA 29

THERMAL_ALERT# 29

B B

A A

Project:

Project:

Project:

Engineer:

Engineer:

Size

Size

Size

Title:

Title:

Title:

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

Miix510

Miix510

Miix510

1

Jacky

Jacky

Jacky

Rev

Rev

Rev

V01

V01

5 69Tuesday, June 27, 2017

5 69Tuesday, June 27, 2017

5 69Tuesday, June 27, 2017

V01

5

4

3

2

1

To Enable ME Override

ME_Flash_EN37,50

R9848 0R

STRAP_HDA_SDO_SOC

IR0402_N 5%

D D

IR0402 5%

HDA_SYNC46

HDA_BCLK_R46

STRAP_HDA_SDO46

HDA_RST_N46

RC393 33R

R1086 33R

RC395 33R

RC394 33R

HDA for AUDIO

C C

FCAM_RST_N39

TP10034

+V3P3SX

HDA_SYNC_SOC

IR0402 5%

HDA_BCLK

IR0402 5%

STRAP_HDA_SDO_SOC

NIR0402 5%

HDA_RST_N_SOC

HDA_SYNC_SOC

HDA_BCLK

STRAP_HDA_SDO_SOC

HDA_SDI046

HDA_SDI0

HDA_RST_N_SOC

R10086 0R

FCAM_RST_N_CPU

FCAM_CLK_EN40

RCAM_CLK_EN40

WWAN_DISABLE_N44

WIFI_DISABLE_N43

PCH_AUDIO_PWREN46 FCAM_PD_N 39

HW_ID47

R1052 100K

NIR0402 5%

6/27 update

HDA_SPKR46

1/4 Connect codec

+V3P3A

+V3P3SX

+V3P3A 3,4,5,7,9,10,11,23,24,29,31,37,38,42,47,49,50,51,52,53,56,60,62,65,66,67

+V3P3SX 5,7,9,10,23,26,30,31,36,37,38,39,40,41,43,44,45,46,47

Difference with armour

Add EC to enable ME override

+V3P3A

NIR0402_N 5%

RCAM_RST_N

R1054

1K

R0402

5%

NI

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK10

AW5

UC1G

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

J5

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

AK7

GPP_F1/I2S2_SFRM

AK6

GPP_F0/I2S2_SCLK

AK9

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

SKL-U_BGA1356

@

AUDIO

5/23 R9848 install,BIOS request

SKL-U

7 OF 20

SDIO/SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

Rev_0.53

SD_RCOMP

GPP_F23

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

TP_SD_WP

SDMMC_RCOMP

R9864 0R

R1015 200R

Non-Micro SD

NIR0402_N 5%

IR0402 1%

Difference with armour

Add 0ohm NI

B B

CSI2_RCAM_DATA0_DN39

Rear Camera1

8M

Front Camera

5M

A A

5

CSI2_RCAM_DATA0_DP39

CSI2_RCAM_DATA1_DN39

CSI2_RCAM_DATA1_DP39

CSI2_RCAM_DATA2_DN39

CSI2_RCAM_DATA2_DP39

CSI2_RCAM_DATA3_DN39

CSI2_RCAM_DATA3_DP39

CSI2_FCAM_DATA0_DN39

CSI2_FCAM_DATA0_DP39

CSI2_FCAM_DATA1_DN39

CSI2_FCAM_DATA1_DP39

4

A36

B36

C38

D38

C36

D36

A38

B38

C31

D31

C33

D33

A31

B31

A33

B33

A29

B29

C28

D28

A27

B27

C27

D27

@

UC1I

CSI-2

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

SKL-U_BGA1356

SKL_ULT

9 OF 20

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

3

Rev_0.53

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

C37

D37

C32

D32

C29

D29

B26

A26

CSI2_COMP

E13

CSI2_FLASH_STROBE

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

EMMC_RCOMP

AT1

R1013 100R

3/18 Add TP1061

R1014 200R

CSI2_RCAM_CLK_DN 39

CSI2_RCAM_CLK_DP 39

CSI2_FCAM_CLK_DN 39

CSI2_FCAM_CLK_DP 39

TP1061

1/4 check PDG

IR0402 1%

Non-EMMC

IR0402 1%

2

RCAM_PD_N 39

FCAM_ALLPWR_EN 39

RCAM_ALLPWR_EN 40

4/24 update

Project:

Project:

Project:

Engineer:

Engineer:

Size

Size

Size

Title:

Title:

Title:

SKL-U(4/12)HDA,EMMC,SD

SKL-U(4/12)HDA,EMMC,SD

SKL-U(4/12)HDA,EMMC,SD

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

Miix510

Miix510

Miix510

1

Jacky

Jacky

Jacky

6 69Wednesday, July 05, 2017

6 69Wednesday, July 05, 2017

6 69Wednesday, July 05, 2017

Rev

Rev

Rev

V01

V01

V01

5

SDV SIV SIT SVT

HW_ID0

HW_ID1

+3V_PRIM

R9865

D D

10K

5%

R0402_N

I

R1088

10K

5%

R0402_N

NI

HW_ID2

HW_ID3

C C

HW_ID4

B B

A A

PLT_RST_N

0

00

R9866

R9867

10K

10K

5%

5%

R0402_N

R0402_N

I

NI

R1090

R1089

10K

10K

5%

5%

R0402_N

R0402_N

I

NI

Difference with armour

Modify HW_ID

TPM

U9505

01

+V1P0A_VCCPRIM

+V3P3A

+V3P3SX

+1.8V_PRIM

+V3.3AL

+RTCVCC

+3V_PRIM

+1.0V_VCCST

+V3P3SX+V3P3A

R1093

2.2K

5%

R0402_N

I

R1079

100K

5%

R0402_N

I

Difference with armour

Del U1201 Low-power buffer(74AUP1G07GW)

and add Dual MOS to change level

+V3.3AL

G1

10

R9868

10K

5%

R0402_N

NI

R1091

10K

5%

R0402_N

NI

non-TPM

U9505

R1071

2.2K

5%

R0402_N

NI

PM_SYSRST_N

RSMRST_N

R9849

100K

5%

R0402_N

I

PLT_RST_N_Q

QX1A

D1

S1

2N7002KDW 115mA 60V

SOT363V

I

5

11

1

PCIE_REFCLK_SSD_DN26

PCIE_REFCLK_SSD_DP26

have

FP sensor

SSD_CLK_REQ_N26

PCIE_REFCLK_SD_DN_R45

PCIE_REFCLK_SD_DP_R45

PCIE_REFCLK_WLAN_DN_R43

PCIE_REFCLK_WLAN_DP_R43

R10126

10K

5%

R0402_N

DSP

HW_ID0

HW_ID1

HW_ID2

HW_ID3

HW_ID4

R10127

6/27 update

10K

5%

R0402_N

NONDSP

non FP sensor

HW_ID3 3

HW_ID4 6

01

+V1P0A_VCCPRIM 14

+V3P3A 3,4,5,6,9,10,11,23,24,29,31,37,38,42,47,49,50,51,52,53,56,60,62,65,66,67

+V3P3SX 5,6,9,10,23,26,30,31,36,37,38,39,40,41,43,44,45,46,47

+1.8V_PRIM 10,11,31,39,40,44,47,56,65

+V3.3AL 11,50,51,58,60,66

+RTCVCC 11

+3V_PRIM 8,11

+1.0V_VCCST 3,10,12,14,66

PLT_RST_N26,41,43,45,50

RSMRST_N50

TP1021

SYS_PWROK50

IMVP_PCH_PWRGD50

TP1081

TP1048

PCIE_WAKE_PCH_N26,43

+V3P3A

R1041 10K

+1.8V_PRIM

R9850

2.2K

5%

R0402_N

I

QX1B

D2

S2

G2

2N7002KDW 115mA 60V

SOT363V

I

BUF_PLT_RST_N_V1P8S 44

to WWAN reset pin

4

R9887 0R

R9888 0R

Close to SOC

SSD

2016/10/07

SD

SD_CLK_REQ_N45

WLAN_CLK_REQ_N43

WLAN

non DSP Have DSP

01

PM_SYSRST_N

TP_CPUPWRGD

H_VCCST_PWRGD

RSMRST_N

TP_SUS_PWR_DN_ACK

TP_SUSACK_N

IR0402_N 5%

4

UC1K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL-U_BGA1356

@

VR_PWRGD29,66

UC1J

IR0402_N5%

PCIE_REFCLK_SSD_DN_R

IR0402_N5%

PCIE_REFCLK_SSD_DP_R

HW_ID0

HW_ID1

HW_ID2

PCIE_REFCLK_WLAN_DN_R

PCIE_REFCLK_WLAN_DP_R

SYSTEM POWER MANAGEMENT

D42

C42

AR10

B42

A42

AT7

D41

C41

AT8

D40

C40

AT10

B40

A40

AU8

E40

E38

AU7

SKL-U

11 OF 20

R1042 0R

CLKOUT_PCIE_N0

CLKOUT_PCIE_P0

GPP_B5/SRCCLKREQ0#

CLKOUT_PCIE_N1

CLKOUT_PCIE_P1

GPP_B6/SRCCLKREQ1#

CLKOUT_PCIE_N2

CLKOUT_PCIE_P2

GPP_B7/SRCCLKREQ2#

CLKOUT_PCIE_N3

CLKOUT_PCIE_P3

GPP_B8/SRCCLKREQ3#

CLKOUT_PCIE_N4

CLKOUT_PCIE_P4

GPP_B9/SRCCLKREQ4#

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

GPP_B10/SRCCLKREQ5#

SKL-U_BGA1356

@

IR0402_N 5%

2/24 Add R1042,VR_PWRGD connect to SOC and EC

3

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

GPD9/SLP_WLAN#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

GPP_B11/EXT_PWR_GATE#

GPP_B2/VRALERT#

IMVP_PCH_PWRGD

3

Rev_0.53

SLP_SUS#

SLP_LAN#

GPD6/SLP_A#

INTRUDER#

SKL_ULT

CLOCK SIGNALS

10 OF 20

SRTCRST_EC50

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

AM10

AM11

1/13 Add RTC reset circuit.

SLP_S0_N

SLP_S5_N

SLP_SUS_N

SLP_A_N

AC_PRESENT_R

PME_N

SM_INTRUDER_N

EXT_PWR_GATEB

R200_PWR_EN

Rev_0.53

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

R9883

10K

5%

R0402_N

I

TP9996

TP9988

TP9997

TP1025

TP1022

F43

E43

BA17

XTAL_24M_SOC_IN

E37

XTAL_24M_SOC_OUT

E35

XCLK_BIASREF

E42

XTAL_32K_SOC_IN

AM18

XTAL_32K_SOC_OUT

AM20

SRTC_RST_N

AN18

RTC_RST_N

AM16

R9885 0R

R9884 0R

D

Q8209

2N7002 250mA 60V

sot_323_dgs

S

G

I

SLP_S3_N 10,50,60

SLP_S4_N 10,42,47,50,60

SLP_SUS_N 11

PM_PWRBTN_R_N 50

PM_BATLOW_N 50

2

R1019 2.7K

SRTC_RST_N

NIR0402_N 5%

RTC_RST_N

IR0402_N 5%

+V3P3A

PM_BATLOW_N

Difference with armour

SLP_SUS_N open +3V_PRIM

+3V_PRIM

R1020

10K

5%

R0402_N

I

AC_PRESENT50

ACPRES50,59

CHG_ACOK change to ACPRES

from Charger IC

2

SUS_CLK 43

R1072

10K

5%

R0402_N

I

+V1P0A_VCCPRIM

IR0402 1%

RTC_RST_N

H_VCCST_PWRGD

IMVP_PCH_PWRGD

1

XTAL_24M_SOC_IN

XTAL_24M_SOC_OUT

8.2pF 50V 0.1pF

C1250

C0402_N

R1057 1M

Y1001

GND

Y12Y2

3

Y34Y4

24MHZ 10PPM

X4S32X25

NPO

U22,U22F

U22,U22F

3/10 Change C1249,C1250 from 22pF to 8.2pF

XTAL_32K_SOC_OUT

XTAL_32K_SOC_IN

C1251

15pF 50V 5%

NPO

C0402_N

I

R1056 10M

Y1000

1 2

32.768KHz +/-20ppm

CRY2_3215

I

3/10 Change Y1000 from seiko to HOSONIC

3/10 Change C1251,C1252 from 18pF to 12pF

3/21 Change C1251,C1252 from 12pF to 15pF,

hosonic & seiko share

+RTCVCC

R1058

20K

5%

R0402_N

I

SRTC_RST_N SM_INTRUDER_N

C1254

1uF 6.3V 10%

X5R

C0402_N

I

R1060

20K

5%

R0402_N

I

C1253

1uF 6.3V 10%

X5R

C0402_N

I

+1.0V_VCCST

R1044 1K

IR0402_N 5%

R9886

100K

5%

R0402_N

NI

AC

CR1003

RB521C30 100mA 30v

SOD-923

I

+V3P3A

R1048

100K

5%

R0402_N

R1046 0R

AC

CR9052

RB521C30 100mA 30v

SOD-923

I

Size

Size

Size

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

I

NIR0402_N 5%

AC_PRESENT_R

Project:

Project:

Project:

Engineer:

Engineer:

Title:

Title:

Title:

Engineer:

SKL-U(5/12)CLK,GPIO

SKL-U(5/12)CLK,GPIO

SKL-U(5/12)CLK,GPIO

1

Miix510

Miix510

Miix510

GND

U22,U22FR0402 5%

1

IR0402 5%

Jacky

Jacky

Jacky

7 69Monday, September 04, 2017

7 69Monday, September 04, 2017

7 69Monday, September 04, 2017

R1062

1M

5%

R0402_N

I

C1249

8.2pF 50V 0.1pF

NPO

C0402_N

U22,U22F

C1252

15pF 50V 5%

NPO

C0402_N

I

Rev

Rev

Rev

V01

V01

V01

5

4

3

2

1

+3V_PRIM

Add the GPIO for control CAM 5M/8M

UC1F

AN8

AP7

D D

FP_SPI_CS0_N31

FP_SPI_CLK31

FP_SPI_MISO31

Add the GPIO for Hall sensor

UART for debug

G-sensor

Touch panel

Camera 8M

Camera 5M

4/20 update

C C

+V3P3A

+1.8V_PRIM

LID_INT_N38,47,50

DOCK_DET37,50

WLAN_RST43

LID_INT_N149,50

UART2_RXD56

UART2_TXD56

TP_I2C0_SDA_EDP2DSI38

TP_I2C0_SCL_EDP2DSI38

TOUCH_I2C_SDA37

TOUCH_I2C_CLK37

I2C_2_RCAM_SDA39

I2C_2_RCAM_SCL39

I2C_3_FCAM_SDA39

I2C_3_FCAM_SCL39

WWAN_HOST_WAKE_N44

GPS_DISABLE_N44

+V3P3A 3,4,5,6,7,9,10,11,23,24,29,31,37,38,42,47,49,50,51,52,53,56,60,62,65,66,67

+1.8V_PRIM 7,10,11,31,39,40,44,47,56,65

FP_SPI_MOSI31

TP1009

TP_STRAP_GPP_B18

AP8

AR7

AM5

AN7

AP5

AN5

AB1

AB2

W4

AB3

AD1

AD2

AD3

AD4

U7

U6

U8

U9

AH9

AH10

AH11

AH12

AF11

AF12

LPSS ISH

GPP_B15/GSPI0_CS#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/UART0_RXD

GPP_C9/UART0_TXD

GPP_C10/UART0_RTS#

GPP_C11/UART0_CTS#

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_F6/I2C3_SDA

GPP_F7/I2C3_SCL

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

SKL-U_BGA1356

@

SKL-U

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

6 OF 20

GPP_D15/ISH_UART0_RTS#

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

GPP_A12/BM_BUSY#/ISH_GP6

Memory Dectection

3/2 Change memory ID PU from +1.8V_PRIM to +3V_PRIM

Rev_0.53

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

P2

P3

P4

P1

M4

N3

IMU_I2C_SDA

N1

IMU_I2C_SCL

N2

CRD_PWR_OFF_N_SOC

AD11

AD12

U1

U2

U3

U4

MEM_DEC0

AC1

MEM_DEC1

AC2

MEM_DEC2

AC3

MEM_DEC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

+3V_PRIM +3V_PRIM +3V_PRIM

R9803

10K

1%

R0402_N

NI

R9804

10K

1%

R0402_N

I

R10089

10K

1%

03/22 Modify

R0402_N

I

SH9515 0R

SH9516 0R

TP10014

TP10015

DOCK_DET_SOC 37

CAM_8M 39

VOLUME_UP 49,50

VOLUME_DOWN 49,50

WWAN_GNSS_3P3_SDA 44

WWAN_GNSS_3P3_SCL 44

WWAN_GNSS_INT 44

2/17 Modify

IR0402_N 5%

IR0402_N 5%

Add the GPIO for control docking power

IMU_I2C_SDA_HUB 38

IMU_I2C_SCL_HUB 38

3/1 Modify

CRD_PWR_OFF_N_SOC 44

WWAN

Memory detection

3/1 Modify

IMU_INT1 38

ACCEL_INT 38

IMU_INT2 38

IMU_INT3 38

FP_SLEEP_N 31

FP_DRDY 31

IMU_INT4 38

6/24 SAR_PROX_RST,reserved R1096 connect to GPP_A12,add R1095 connect to GPP_A22,BIOS request

R9806

10K

1%

R0402_N

NI

R9807

10K

1%

R0402_N

I

MEM_DEC0

R9801

10K

1%

R0402_N

NI

MEM_DEC1 MEM_DEC2

R9802

10K

1%

R0402_N

I

GPP_D10

8M CAM 0

5M CAM

Difference with armour

WWAN_SAR_DET AD11 move to BA7

follow Intel MRD

1

IMU Sensor

Mem_DEC3 Voltage

One Channel

Two Channel

+3V_PRIM

R10090

10K

1%

0V

3.3V

R0402_N

NI

MEM_DEC3

R10091

10K

1%

R0402_N

I

3/29 add memory ID

MEM_DEC0

MEM_DEC1

MEM_DEC2

MEM_DEC3 0 0 0 0 0 0 1 1 1 1 1

B B

A A

5

4

0

0

1

0

00

Default

0

1

0

3

1

1

0

Samsung_4GB SDP Samsung_8GB SDPMicron_4GB SDP Micron_8GB DDPHynix_4GB SDP Hynix_16GB DDP Samsung_16GB DDPMicron_16GB DDP

0

0

1

Samsung_8GB DDP

1

0

1

Micron_8GB SDPHynix_8GB SDPHynix_8GB DDP

0

0

0

1

0

0

0

1

0

1

0

01

0

1

1

0

1

1

Project:

Project:

Project:

Miix510

Miix510

Miix510

Jacky

Jacky

Engineer:

Engineer:

Size

Size

Size

Title:

Title:

Title:

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Engineer:

SKL-U(6/12)GPIO

SKL-U(6/12)GPIO

SKL-U(6/12)GPIO

1

Jacky

Rev

Rev

Rev

V01

V01

V01

8 69Monday, September 04, 2017

8 69Monday, September 04, 2017

8 69Monday, September 04, 2017

5

D D

PCIE_WLAN_LN0_RX_SOC_DN43

NGFF WIFI Module

PCIE_WLAN_LN0_RX_SOC_DP43

PCIE_WLAN_LN0_TX_SOC_DN43

PCIE_WLAN_LN0_TX_SOC_DP43

5/4 WIFI PCIE port 8 change to port 4,because PCH HSIO 8 can use PCIe interface (for Base-U)

PCIE_SD_LN0_RX_SOC_DN45

PCIE_SD_LN0_RX_SOC_DP45

PCIE_SD_LN0_TX_SOC_DN45

PCIE_SD_LN0_TX_SOC_DP45

C9586 0.22uF 10V 10%

C9587 0.22uF 10V 10%

2016/10/07

C C

PCIE9_SSD_RX_DN26

PCIE9_SSD_RX_DP26

PCIE9_SSD_TX_DN_C26

PCIE9_SSD_TX_DP_C26

PCIE10_SSD_RX_DN26

PCIE10_SSD_RX_DP26

PCIE10_SSD_TX_DN_C26

PCIE10_SSD_TX_DP_C26

NGFF SSD

PCIE11_SSD_RX_DN26

PCIE11_SSD_RX_DP26

PCIE11_SSD_TX_DN_C26

PCIE11_SSD_TX_DP_C26

PCIE12_SSD_RX_DN26

PCIE12_SSD_RX_DP26

B B

Difference with armour

SSD interface SATA change to PCIE

SATA1A change to PCIE port 9,10,11,12

A A

PCIE12_SSD_TX_DN_C26

PCIE12_SSD_TX_DP_C26

C0600 0.22uF 10V 10%

C0601 0.22uF 10V 10%

C0602 0.22uF 10V 10%

C0603 0.22uF 10V 10%

R1063 100R

C0604 0.22uF 10V 10%

C0605 0.22uF 10V 10%

C0606 0.22uF 10V 10%

C0607 0.22uF 10V 10%

Checklist:

Gen1 and Gen2=100nF

Gen3=220nF

TP1051

TP1062

TP1050

IR0402 1%

4

IX5RC0402_N

CPU_SD_TX_DN

IX5RC0402_N

CPU_SD_TX_DP

IX5RC0402_N

PCIE9_SSD_TX_DN

IX5RC0402_N

PCIE9_SSD_TX_DP

IX5RC0402_N

PCIE10_SSD_TX_DN

IX5RC0402_N

PCIE10_SSD_TX_DP

PCIE_RCOMP_N

PCIE_RCOMP_P

XDP_PRDY_N

XDP_PREQ_N

TP_EC_CS_WAKE

IX5RC0402_N

PCIE11_SSD_TX_DN

IX5RC0402_N

PCIE11_SSD_TX_DP

IX5RC0402_N

PCIE12_SSD_TX_DN

IX5RC0402_N

PCIE12_SSD_TX_DP

UC1H

PCIE/USB3/SATA

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKL-U_BGA1356

@

GPIO

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

DEVSLP0

DEVSLP1

DEVSLP2

SATA_GP0

SATA_GP1

SATA_GP2

3

SKL-U

8 OF 20

DEVICE CONTROL

Type C

USB2 Port 2

NA

WWAN_PWR_ON

NA

NA

NGFF SSD KEY M

NA

NA

SSD_SATA_PCIE_DET_N

SSIC / USB3

USB2

Rev_0.53

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

USB2_COMP

AB6

USB2_P1_WP1_OTG_ID

AG3

USB2_VBUSSENSE

AG4

A9

C9

D9

USB2_P2_WP3_OC_N

B9

TP_SATA0_DEVSLP

J1

SATA1_DEVSLP

J2

J3

TP_SSD_SATA0_PCIE_DET_N

H2

H3

SSD_SATA_PCIE_DET_N

G4

TP_EDP2DSI_CORE_PWR_EN

H1

USB2_P2_WP3_OC_N

1/7 Add PU +V3P3A

2

USB3_P1_RX_DN 42

USB3_P1_RX_DP 42

USB3_P1_TX_DN 42

USB3_P1_TX_DP 42

USB3_P2_WP2_RX_DN 52

USB3_P2_WP2_RX_DP 52

USB3_P2_WP2_TX_DN 52

USB3_P2_WP2_TX_DP 52

USB3_P3_WWAN_SSIC_RX_DN 44

USB3_P3_WWAN_SSIC_RX_DP 44

USB3_P3_WWAN_SSIC_TX_DN 44

USB3_P3_WWAN_SSIC_TX_DP 44

USB2_P1_WP1_DN 42

USB2_P1_WP1_DP 42

USB2_P2_WP2_DN 55

USB2_P2_WP2_DP 55

USB2_P3_WWAN_DN 44

USB2_P3_WWAN_DP 44

USB2_P4_BT_DN 43

USB2_P4_BT_DP 43

USB2_P5_DOCK_DN 37

USB2_P5_DOCK_DP 37

R1012 113R

R1084 1K

R1085 1K

USB2_P1_WP1_OC_N 42

USB2_P2_WP2_OC_N 53

WWAN_PWR_ON 44

TP1079

TP8201

SATA2_DEVSLP 26

TP1080

TP1082

IR0402 1%

IR0402_N 5%

IR0402_N 5%

TP8213

+V3P3A

R9882

10K

5%

R0402_N

I

Difference with armour

R1050 install,R1087 uninstall

1

USB3.0 CONN

Type-c

WWAN

USB3.0 connector

Type-c

NGFF WWAN Module

BT

USB 2.0 docking

Difference with armour

B9 modify to WWAN_PWR_ON

Difference with armour

modify SATA2_DEVSLP

Difference with armour

SSD_SATA_PCIE_DET_N connect to G4 pin

+V3P3SX

R1087

100K

5%

R0402_N

NI

SSD_SATA_PCIE_DET_N

NOTE:

USE FITC TO ALLOW SELECTION OF

PCIE VS SATA BASED ON STRAPPING:

GPP_E_2 FOR SATA2/PCIE:

1 - SATA2, 0 - PCIE P9,P10,P11,P12

R1050

10K

5%

R0402_N

I

Project:

Project:

+V3P3A

+V3P3SX

5

4

+V3P3A 3,4,5,6,7,10,11,23,24,29,31,37,38,42,47,49,50,51,52,53,56,60,62,65,66,67

+V3P3SX 5,6,7,10,23,26,30,31,36,37,38,39,40,41,43,44,45,46,47

3

Size

Size

Size

Title:

Title:

Title:

SKL-U(7/12)PCIE,USB,SATA

SKL-U(7/12)PCIE,USB,SATA

SKL-U(7/12)PCIE,USB,SATA

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Project:

Engineer:

Engineer:

Engineer:

Miix510

Miix510

Miix510

1

Jacky

Jacky

Jacky

Rev

Rev

Rev

V01

V01

9 69Tuesday, June 27, 2017

9 69Tuesday, June 27, 2017

9 69Tuesday, June 27, 2017

V01

5

+V5P0A

+V5P0A +V5P0S

CC98

1uF 6.3V 10%

X5R

C0402

I

D D

SLP_S3_N7,10,50,60

RC420 0R

IR0402 5%

1/4 modify OK

+V5P0A to +V5P0S

CC97

1uF 6.3V 10%

X5R

C0402

I

+V3P3A

1/13 新 增 +V5P0S

UC5

1

2

3

4

5

6

7

CC164

1uF 6.3V 10%

X5R

C0402

I

EM5209VF

dfn14p_ph0p4_3x2_h0p8

I

+V3P3A to +V3P3SX

12/22 新 增+V3P3SX

VIN1

VIN1-1

ON1

VBIAS

ON2

VIN2

VIN2-1

VOUT1

VOUT1-1

VOUT2-1

VOUT2

GPAD

CT1

GND

CT2

4

CC96

0.1uF 10V 10%

X5R

C0402

I

11/17_Follow 543977_SKL_PDDG_Rev0_91

14

CC95 10PF ->22us(Spec:<= 65us)

13

12

CC95 10pF 50V 0.5pF

11

10

CC94 1000pF 50V 10%

9

8

15

INPOC0402

IX7RC0402

+V3P3SX

CC165

0.1uF 10V 10%

X5R

C0402

I

+1.2V_VDDQC

+1.0V_VCCST

+1.0VS_VCCSTG

+1.2V_VCCSFR_OC

+1.0V_VCCSFR

+V1P2U_VDDQ

3

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

A18

A22

AL23

K20

K21

UC1N

CPU POWER 3 OF 4

VDDQ_AU23

VDDQ_AU28

VDDQ_AU35

VDDQ_AU42

VDDQ_BB23

VDDQ_BB32

VDDQ_BB41

VDDQ_BB47

VDDQ_BB51

VDDQC

VCCST

VCCSTG_A22

VCCPLL_OC

VCCPLL_K20

VCCPLL_K21

SKL-U_BGA1356

@

14 OF 20

SKL-U

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

Rev_0.53

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

VCCSA9

VCCSA10

VCCSA11

VCCSA12

VCCSA13

VCCSA14

+1.0VS_VCCIO

AK28

AK30

AL30

AL42

AM28

AM30

AM42

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

+VCC_SA

2

VCCSA_SENSE

VSSSA_SENSE

12/2 Close to CPU

T124

T125

VSSSA_SENSE 66

VCCSA_SENSE 66

+VCC_SA

RC421

100R

R0402

I

RC422

100R

R0402

I

1

1%

1%

+V5P0A

C C

SLP_S3_N

CC88

0.1uF 10V 10%

X5R

C0402

I

RC187 0R

+1.0V_PRIM

2/24 pin9 connect GND,need change to +1.0V_PRIM

CC117

1uF 6.3V 10%

X5R

C0402

I

UC6

1

VIN1

2

VIN2

9

VIN thermal

3

VBIAS

IR0402 5%

4

ON

TPS22961DNYR

tps22961_8P_h0p8

I

VOUT3

VOUT2

VOUT1

GND

+1.0VS_VCCSTG_IO

8

7

6

5

RC188 0R

RC189 0R

Imax : 2.73 A

+1.0VS_VCCSTG

CC89 0.1uF 10V 10%

IR0402 5%

+1.0VS_VCCIO

CC90 0.1uF 10V 10%

IR0805_N 5%

CC99 10uF 6.3V 20%

CC100 10uF 6.3V 20%

1/27 Intel Add 10uF x2

IX5RC0402

IX5RC0402

IX5RC0402_N

IX5RC0402_N

+1.0V_PRIM to +1.0VS_VCCSTG / +1.0VS_VCCIO

+V5P0A

+1.0V_PRIM

CC380

0.1uF 10V 10%

X5R

C0402

I

SLP_S4_N7,42,47,50,60

B B

SLP_S3_N7,10,50,60

RC142 0R

RC431 0R

EN_1.0V_VCCSTU

IR0402 5%

+1.8V_PRIM

+1.0V_PRIM to +1.0V_VCCSTU

CC376

1uF 6.3V 10%

X5R

C0402

I

IR0402 5%

EN_1.8VS

CC398

1uF 6.3V 10%

X5R

C0402

I

UC8

1

VIN1

2

VIN1-1

3

ON1

4

VBIAS

5

ON2

6

VIN2

7

VIN2-1

EM5209VF

dfn14p_ph0p4_3x2_h0p8

I

VOUT1

VOUT1-1

VOUT2-1

VOUT2

GPAD

14

13

12

CT1

11

GND

10

CT2

9

8

15

+1.0V_VCCSTU_IO

CC392 10pF 50V 0.5pF

CC394 1000pF 50V 10%

INPOC0402

IX7RC0402

RC432 0R

RC430 0R

+V1P8S

IR0402 5%

+1.0V_VCCSTU

IR0402 5%

CC397

0.1uF 10V 10%

X5R

C0402

I

CC379

0.1uF 10V 10%

X5R

C0402

I

+1.0V_VCCSTU +1.0V_VCCST

RC140 0R

IR0402 5%

+1.0V_VCCSFR

RC143 0R

IR0402 5%

PSC Side

CC48

1uF 6.3V 10%

X5R

C0402

I

RC208 Follow 544669_SKL_U__DDR3L_RVP7_Schematic_Rev1.0

CC55

1uF 6.3V 10%

X5R

C0402

I

+V1P2U_VDDQ

RC141 0R

+1.2V_VCCSFR_OC

BSC Side

IR0402 5%

CC49

1uF 6.3V 10%

X5R

C0402

I

+1.0VS_VCCSTG

BSC SidePSC Side

CC142

1uF 6.3V 10%

X5R

C0402

I

+1.8V_PRIM to +V1P8S

RC208 Follow 544669_SKL_U__DDR3L_RVP7_Schematic_Rev0_53

+1.0VS_VCCIO

10uF 6.3V 20%

10uF 6.3V 20%

1uF 6.3V 10%

CC28

X5R

C0603

I

CC29

X5R

C0402

I

5

CC27

X5R

C0603

I

A A

+V5P0S

+V5P0A

+1.0V_PRIM

+V3P3SX

+V1P2U_VDDQ

+1.0VS_VCCSTG

+1.0VS_VCCIO

+V1P8S

+1.8V_PRIM

1uF 6.3V 10%

CC31

X5R

C0402

I

CC32

X5R

C0402

I

1uF 6.3V 10%

1uF 6.3V 10%

CC30

X5R

C0402

I

+V5P0S 30,46

+V5P0A 11,23,37,39,40,42,53,60,61,62,63,65

+1.0V_PRIM 11,14,63

+V3P3SX 5,6,7,9,23,26,30,31,36,37,38,39,40,41,43,44,45,46,47

+V1P2U_VDDQ 4,19,20,21,61

+1.0VS_VCCSTG 3,12

+1.0VS_VCCIO 3,14

+V1P8S 31,38,46

+1.8V_PRIM 7,11,31,39,40,44,47,56,65

CC33

X5R

C0402

I

PSC SideBSC Side

CC34

X5R

C0402

I

1uF 6.3V 10%

CC35

X5R

C0402

I

1uF 6.3V 10%

CC36

X5R

C0402

I

4

1uF 6.3V 10%

1uF 6.3V 10%

+V1P2U_VDDQ

RC208 0R

CC47 Follow 543016_SKL_U_Y_PDG_0_9

+1.2V_VDDQC

IR0603 5%

BSC Side

10uF 6.3V 20%

CC47

X5R

C0603

I

+V1P2U_VDDQ

10uF 6.3V 20%

10uF 6.3V 20%

10uF 6.3V 20%

CC38

CC37

X5R

X5R

C0603

C0603

I

I

+V1P2U_VDDQ: 10UF/6.3V/0603 *4

22UF/6.3V/0402 *3

3

CC39

X5R

C0603

I

CC40

X5R

C0603

I

10uF 6.3V 20%

CC41

22uF6.3V20%

X5R

C0603_N

I

2

CC42

22uF6.3V20%

X5R

C0603_N

I

CC43

22uF6.3V20%

X5R

C0603_N

I

Project:

Project:

Project:

Miix510

Miix510

Miix510

Jacky

Jacky

Engineer:

Engineer:

Size

Size

Size

Title:

Title:

Title:

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

SKL-U(8/12)Power

SKL-U(8/12)Power

SKL-U(8/12)Power

Jacky

10 69Tuesday, June 27, 2017

10 69Tuesday, June 27, 2017

1

10 69Tuesday, June 27, 2017

Rev

Rev

Rev

V01

V01

V01

5

+1.0V_PRIM

RC148 0R

22uF 6.3V 20%

D D

Follow 543016_SKL_U_Y_PDG_1_0

RC152 0R

22uF 6.3V 20%

IR0603 5%

CC123

C0603_N

IR0603 5%

CC135

C0603_N

X5R

X5R

+1.0V_APLL

NI

+1.0V_CLK5_F24NS

NI

CC134

22uF 6.3V 20%

X5R

C0603_N

NI

CC130

22uF 6.3V 20%

X5R

C0603_N

NI

CC67

1uF 6.3V 10%

X7R

C0402

NI

+3V_PRIM

+3V_PRIM

RC150 0R

CC72

1uF 6.3V 10%

X7R

C0402

I

RC197 0R

RC154 0R

+1.0V_CLK4_F100OC

RC190 0R

C C

CC136

22uF 6.3V 20%

C0603_N

IR0603 5%

CC137

22uF 6.3V 20%

X5R

X5R

C0603_N

NI

NI

RC161 0R

+1.0V_PRIM

RC163 0R

Imax : 2.57A

near pin AF18,

AF19, V20, V21

CC76

1uF 6.3V 10%

X7R

C0402

I

+1.0V_MPHYAON

RC172 0R

RC175 0R

B B

RC169 0R

RC162 0R

CC86

1uF 6.3V 10%

X7R

C0402

IR0402 5%

NI

IR0402 5%

IR0603 5%

CC75

1uF 6.3V 10%

X7R

C0402

NI

CC87

1uF 6.3V 10%

X7R

C0402

I

+1.0V_CLK6_24TBT

CC138

22uF 6.3V 20%

X5R

C0603_N

NI

+1.0V_DTS

CC139

22uF 6.3V 20%

X5R

C0603_N

NI

RC167 0R

RC171 0R

Follow 543016_SKL_U_Y_PDG_0_9

+1.0V_PRIM +3V_PRIM +1.8V_PRIM

A A

CC111

22uF 6.3V 20%

X5R

C0603_N

NI

CC112

22uF 6.3V 20%

X5R

C0603_N

NI

5

CC113

22uF 6.3V 20%

X5R

C0603_N

NI

CC114

22uF 6.3V 20%

X5R

C0603_N

NI

CC115

22uF 6.3V 20%

X5R

C0603_N

NI

CC116

22uF 6.3V 20%

X5R

C0603_N

NI

IR0402 5%

IR0402 5%

IR0402 5%

IR0402 5%

IR0402 5%

IR0402 5%

IR0402 5%

IR0402 5%

4

+3V_HDA

+3V_PGPPA

+3V_SPI

+3V_PGPPB

CC102

1uF 6.3V 10%

X7R

C0402

I

+3V_PGPPC

CC73

1uF 6.3V 10%

X7R

C0402

I

+3V_1.8V_PGPPD

CC103

1uF 6.3V 10%

X7R

C0402

NI

+3V_PGPPE

CC74

1uF 6.3V 10%

X7R

C0402

I

+3V_PRIM_RTC

CC140

1uF 6.3V 10%

X7R

C0402

I

4

CC163

1uF 6.3V 10%

X7R

C0402

I

+1.8V_PRIM

RC206 0R

CC141

1uF 6.3V 10%

X7R

C0402

I

NIR0402 5%

+V3P3A

RC173 0R

Follow 543016_SKL_U_Y_PDG_0_9

near pin K15, L15

near pin AF20,

AF21, T19, T20

near pin N15, N16

N17, P15, P16

Intel review: need close to pin AA1

+3VALW_DSW

IR0603 5%

3

near pin N18

CC81

CC80

22uF 6.3V 20%

1uF 6.3V 10%

X5R

X7R

C0603_N

C0402

I

I

3

+1.0V_PRIM

+1.0V_PRIM

+1.0V_PRIM

+1.0V_PRIM

+1.8V_PRIM

CC61

1uF 6.3V 10%

X7R

C0402

I

CC68

1uF 6.3V 10%

X7R

C0402

I

CC122

1uF 6.3V 10%

X7R

C0402

I

CC82

22uF 6.3V 20%

X5R

C0603_N

NI

CC389

1uF 6.3V 10%

X7R

C0402

I

+V5A_+V3.3A_PWRGD50,60

CC85

1uF 6.3V 10%

X7R

C0402

I

+1.0V_PRIM

+1.0V_MPHYAON

+1.0V_PRIM

+1.0VO_DSW

+1.0V_PRIM

+1.0V_APLL

+1.0V_PRIM

+3VALW_DSW

+1.0V_PRIM

+1.0V_PRIM

+1.0V_PRIM

Per 543016_SKL_U_Y_PDG_0_9

VCCRTC does not exceed 3.2 V From PDG

Power Rail Voltage

+CHGRTC

BAT54C(VF)

+3VL_RTC

Result : Pass

RC428 0R

SLP_SUS_N7

RC191 0R

1/4 Modify OK

+3V_HDA

+3V_SPI

+3V_PRIM

3.383V(MAX)

240 mV

3.143V

+1.0V_PRIM

CC91

1uF 6.3V 10%

X7R

C0402

I

For DS3

IR0402 5%

NIR0402 5%

2

UC1O

AB19

VCCPRIM_1P0_1

AB20

VCCPRIM_1P0_2

P18

VCCPRIM_1P0_3

AF18

VCCPRIM_CORE_1

AF19

VCCPRIM_CORE_2

V20

VCCPRIM_CORE_3

V21

VCCPRIM_CORE_4

AL1

DCPDSW_1P0

K17

VCCMPHYAON_1P0_1

L1

VCCMPHYAON_1P0_2

N15

VCCMPHYGT_1P0_N15

N16

VCCMPHYGT_1P0_N16

N17

VCCMPHYGT_1P0_N17

P15

VCCMPHYGT_1P0_P15

P16

VCCMPHYGT_1P0_P16

K15

VCCAMPHYPLL_1P0_1

L15

VCCAMPHYPLL_1P0_2

V15

VCCAPLL_1P0

AB17

VCCPRIM_1P0_AB17

Y18

VCCPRIM_1P0_Y18

AD17

VCCDSW_3P3_AD17

AD18

VCCDSW_3P3_AD18

AJ17

VCCDSW_3P3_AJ17

AJ19

VCCHDA

AJ16

VCCSPI

AF20

VCCSRAM_1P0_1

AF21

VCCSRAM_1P0_2

T19

VCCSRAM_1P0_3

T20

VCCSRAM_1P0_4

AJ21

VCCPRIM_3P3_AJ21

AK20

VCCPRIM_1P0_AK20

N18

VCCAPLLEBB

SKL-U_BGA1356

@

RTC Battery

CC7 Close UC1.AK19.

+RTCVCC

CC7

1uF 6.3V 10%

X7R

C0402

I

+V3P3A+V5P0A

CC52

CC50

1uF 6.3V 10%

1uF 6.3V 10%

X7R

X7R

C0402

C0402

I

I

EN_3V_PRIM

2

SKL-U

CPU POWER 4 OF 4

VCCPRIM_3P3_V19

VCCPRIM_1P0_T1

VCCRTCPRIM_3P3

GPP_B0/CORE_VID0

GPP_B1/CORE_VID1

15 OF 20

1/11 reserve to BATT conn

3/9 Del RC429,don't connect to BATT_RTC

+RTCBATT_R

DC1

3

BAT54C 200mA 30V

SOT_23

I

2

1

15mils

+V3P3A to +3V_PRIM

UC4

1

2

3

4

AOZ1336DI

WDFN8p_PH0p5_2X2_H0p8

I

VIN1

VIN2

ON

VBIAS

For DS3

7

VOUT1

8

VOUT2

6

CT

5

GND

9

EPAD

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Rev_0.53

AK15

VCCPGPPA

AG15

VCCPGPPB

Y16

VCCPGPPC

Y15

VCCPGPPD

T16

VCCPGPPE

AF16

VCCPGPPF

AD15

VCCPGPPG

12/9_change to +3V_PRIM, follow #543016

V19

T1

AA1

VCCATS_1P8

AK17

AK19

VCCRTC_AK19

BB14

VCCRTC_BB14

BB10

DCPRTC

A14

VCCCLK1

K19

VCCCLK2

L21

VCCCLK3

N20

VCCCLK4

L19

VCCCLK5

A10

VCCCLK6

AN11

AN13

RC19

1K

R0402

5%

I

15mils15mils

CC71 0.1uF 10V 10%

PRIMCORE_VID0

PRIMCORE_VID1

+RTCBATT

+3V_PGPPA

+3V_PGPPB

+3V_PGPPC

+3V_1.8V_PGPPD

+3V_PGPPE

+1.8V_PRIM

+3V_PRIM

+3V_PRIM

+1.0V_DTS

+1.8V_PRIM

+3V_PRIM_RTC

+RTCVCC

+1.0V_CLK6_24TBT

+1.0V_APLL

+1.0V_CLK4_F100OC

+1.0V_CLK5_F24NS

+1.0V_CLK6_24TBT

+V3.3AL

@RTC

SHUNWO

LITHIUM BATT

CR2032

Battery_3V_75mAh

CR1216

NI

CIS ok

+V3P3A

R153 0R

For NON-DS3

+3V_PRIMJP

R159 0R

For DS3

CC53 1000pF 50V 10%

Size

Size

Size

Title:

Title:

Title:

Custom

Custom

Custom

IX7RC0402

Project:

Project:

Project:

Engineer:

Engineer:

Engineer:

SKL-U(9/12)Power

SKL-U(9/12)Power

SKL-U(9/12)Power

1

IX5RC0402

T130

T131

JRTC1

1

1

2

2

G1

PAD1

G2

PAD2

11255W90-2P-S-5A-HF-R

wtb_2p_1p25_90_BAT

I

CIS ok

+3V_PRIM

NIR0805_N 5%

IR0805_N 5%

Miix510

Miix510

Miix510

Jacky

Jacky

Jacky

For SD CARD

CC51

0.1uF 10V 10%

X5R

C0402

I

11 69Tuesday, June 27, 2017

11 69Tuesday, June 27, 2017

11 69Tuesday, June 27, 2017

Rev

Rev

Rev

V01

V01

V01

5

4

3

2

1

+VCC_CORE +VCC_CORE

UC1L

A30

VCC_A30

A34

VCC_A34

D D

For CPU2+3e SKU

C C

+1.0V_VCCST

SVID ALERT

B B

SOC_SVID_ALERT#

RC180 220R

IR0402 1%

A39

VCC_A39

A44

VCC_A44

AK33

VCC_AK33

AK35

VCC_AK35

AK37

VCC_AK37

AK38

VCC_AK38

AK40

VCC_AK40

AL33

VCC_AL33

AL37

VCC_AL37

AL40

VCC_AL40

AM32

VCC_AM32

AM33

VCC_AM33

AM35

VCC_AM35

AM37

VCC_AM37

AM38

VCC_AM38

G30

VCC_G30

K32

RSVD_K32

AK32

RSVD_AK32

AB62

VCCOPC_AB62

P62

VCCOPC_P62

V62

VCCOPC_V62

H63

VCC_OPC_1P8_H63

G61

VCC_OPC_1P8_G61

AC63

VCCOPC_SENSE

AE63

VSSOPC_SENSE

AE62

VCCEOPIO_1

AG62

VCCEOPIO_2

AL63

VCCEOPIO_SENSE

AJ62

VSSEOPIO_SENSE

SKL-U_BGA1356

@

Place the PU

resistors close to CPU

RC179

56R

1%

R0402

I

SKL-U

CPU POWER 1 OF 4

12 OF 20

SOC_SVID_ALERT#_R 66

(To VR)

Rev_0.53

VCC_G32

VCC_G33

VCC_G35

VCC_G37

VCC_G38

VCC_G40

VCC_G42

VCC_J30

VCC_J33

VCC_J37

VCC_J40

VCC_K33

VCC_K35

VCC_K37

VCC_K38

VCC_K40

VCC_K42

VCC_K43

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG_G20

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

A63

D64

G20

SOC_SVID_ALERT#

SOC_SVID_CLK

SOC_SVID_DAT

+VCC_GT

+VCC_CORE

RC448 0R

R0805_N

RC449 0R

R0805_N

5%

U22,U22F

5%

U42

Trace Length < 25 mils

VCCSENSE 66

VSSSENSE 66

SOC_SVID_CLK 66

+1.0VS_VCCSTG

+VCC_GT

+VCC_GTX

+VCC_CORE

RC452 0R

R0805_N

RC446 0R

R0805_N

RC447 0R

R0805_N

5%

U22F

5%

U22,U22F

5%

U42

VCC_VCCGT

+VCC_GTX

VCC_VCCGTX

VCCGT_SENSE66

VSSGT_SENSE66

Trace Length < 25 mils

+VCC_GT

U22,U22F

RC451 0R

R0402 5%

VCCGT_SENSE

VSSGT_SENSE

VCC_VCCGT

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

A48

A53

A58

A62

A66

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

M62

N63

N64

N66

N67

N69

J70

J69

UC1M

VCCGT1

VCCGT2

VCCGT3

VCCGT4

VCCGT5

VCCGT6

VCCGT7

VCCGT8

VCCGT9

VCCGT10

VCCGT11

VCCGT12

VCCGT13

VCCGT14

VCCGT15

VCCGT16

VCCGT17

VCCGT18

VCCGT19

VCCGT20

VCCGT21

VCCGT22

VCCGT23

VCCGT24

VCCGT25

VCCGT26

VCCGT27

VCCGT28

VCCGT29

VCCGT30

VCCGT31

VCCGT32

VCCGT33

VCCGT34

VCCGT35

VCCGT36

VCCGT37

VCCGT38

VCCGT39

VCCGT40

VCCGT41

VCCGT42

VCCGT43

VCCGT44

VCCGT45

VCCGT46

VCCGT47

VCCGT48

VCCGT49

VCCGT50

VCCGT51

VCCGT52

VCCGT53

VCCGT54

VCCGT55

VCCGT_SENSE1

VSSGT_SENSE

SKL-U_BGA1356

@

CPU POWER 2 OF 4

SKL-U

13 OF 20

Rev_0.53

VCCGT56

VCCGT57

VCCGT58

VCCGT59

VCCGT60

VCCGT61

VCCGT62

VCCGT63