Lenovo Ideapad 700S-14ISK - Schematic

A

1 1

B

C

D

E

Compal Confidential

2 2

BIZ00 M/B Schematic Document

Intel Skylake Y Processor

LA-D341P

3 3

2015-09-01

REV:0.3

4 4

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-D341PR03

LA-D341PR03

LA-D341PR03

1 42Tuesday, September 01, 2 015

1 42Tuesday, September 01, 2 015

1 42Tuesday, September 01, 2 015

E

0.3

0.3

0.3

of

of

of

A

B

C

D

E

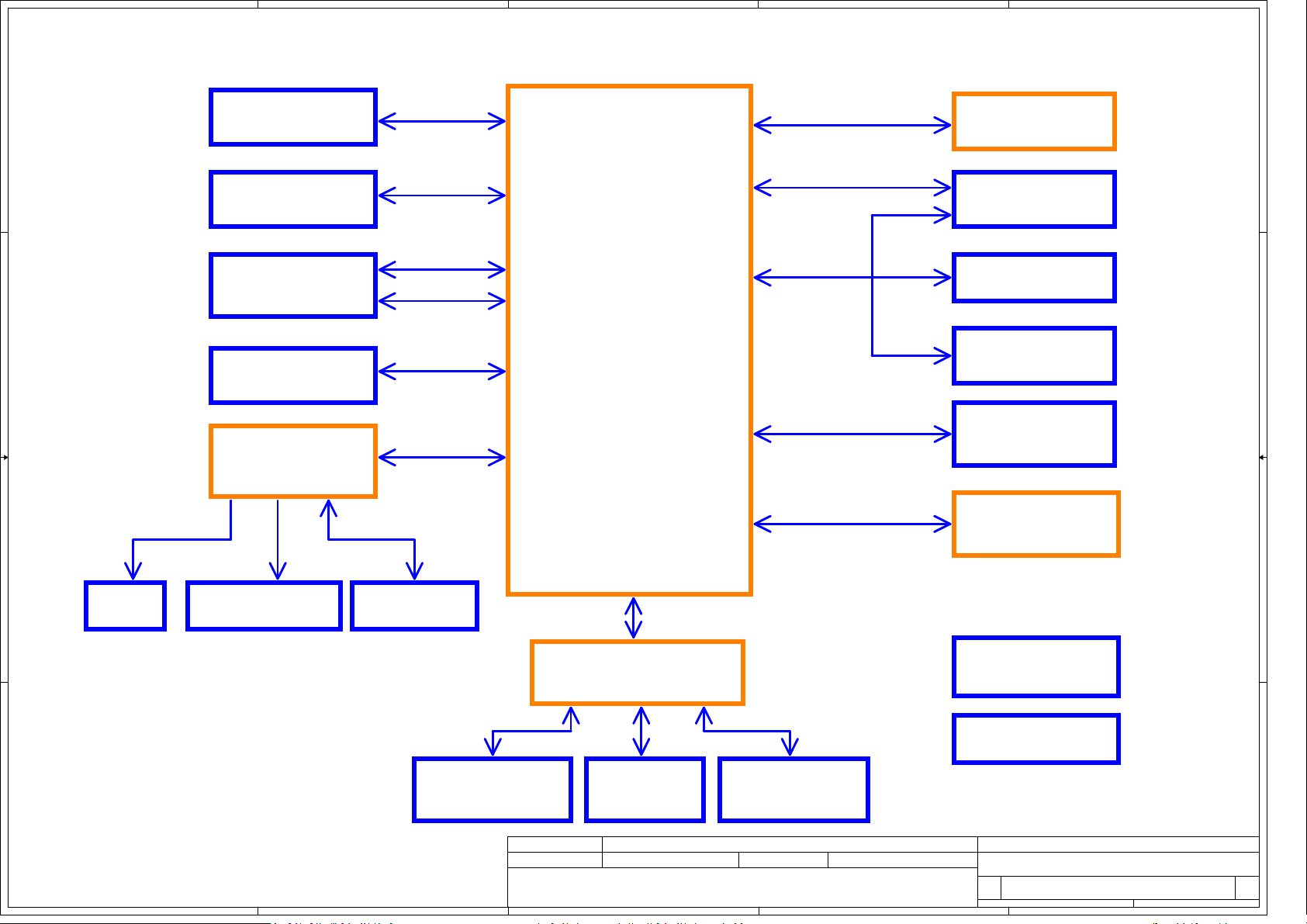

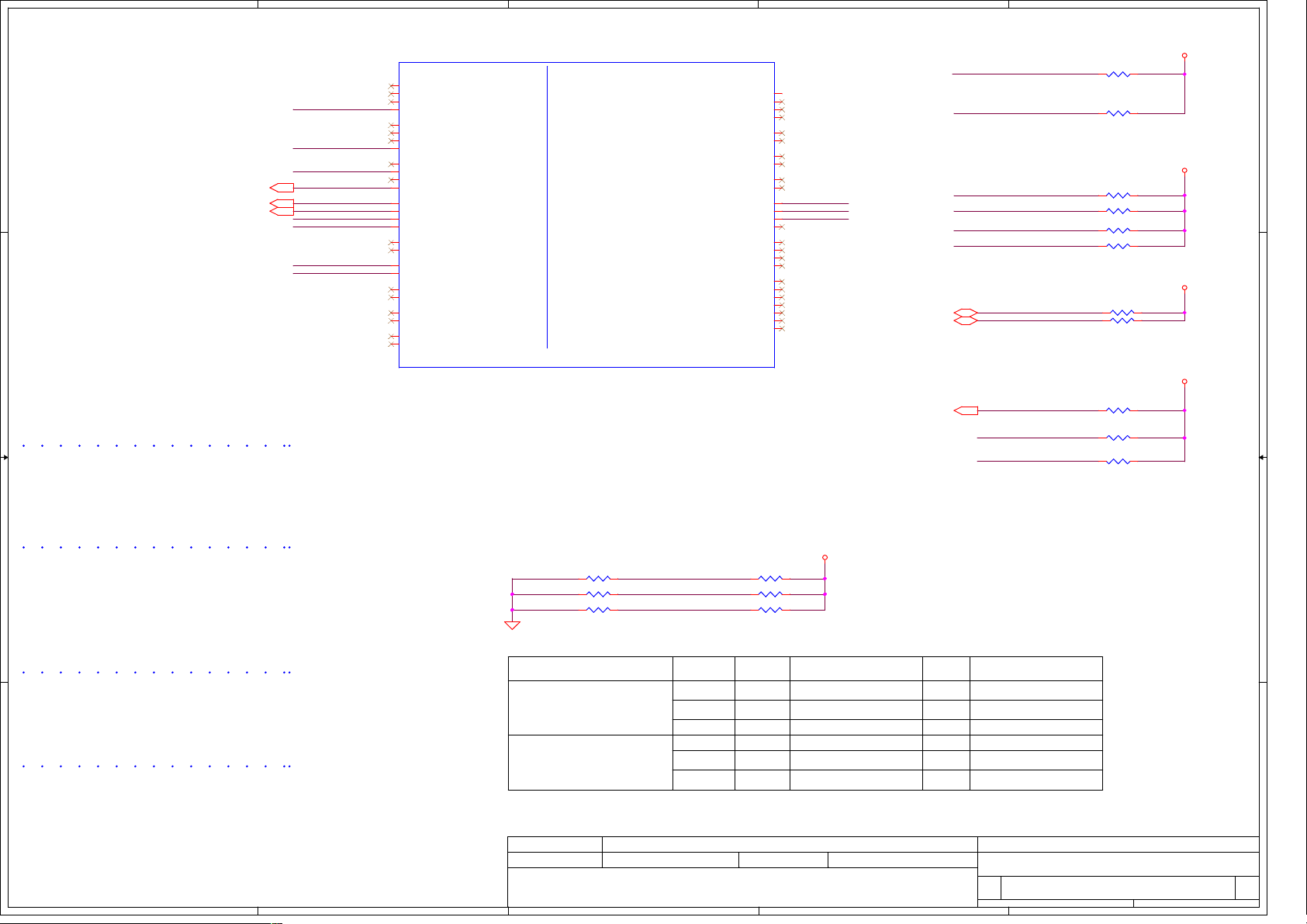

Intel Skylake Y Block Diagram

1 1

1920 * 1080

P.20

uHDMI Connector

P.21

eDP Connector

eDP

DDI1

Ch0, Ch1

USB3.0

LPDDR3 *4pcs

4GB / 8G

P.18~P.19

USB3.0 Connector

P.24

Skylake Y

WIFI+BT combo

NGFF Half

P.23

2 2

Click Pad

P.28

Audio Codec

PCIe

USB2.0

I2C_1

HDA

Realtek ALC233-VB2

P.25

3 3

Speaker

P.25

Digital Array Mic *2

Combo Jack

IO BD

+

Skylake PCH-LP(MCP)

20 x 16.5 mm

BGA1515

P.04~P17

LPC

USB2.0

SATA

SPI

Camera 1M HD

P.20

USB2.0 + DC in

SSD 128GB / 256GB

NGFF Full

SPI ROM (8MB)

W25Q64FVSSIQ

P.27

P.22

P.06

EC

Nuvoton NPCE388

P.26

DC / DC

Interface CKT

P.29

Power Circuit

P.30~P.39

Thermal Sensor

4 4

A

Nuvoton NCT7718W

B

P.28 P.28

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Int. KBD

C

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

Hall Sensor

Toshiba TCS20DLR

PWR BD

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Block Diagram

Block Diagram

Block Diagram

LA-D341PR03

LA-D341PR03

LA-D341PR03

2 42Tuesday, September 01, 2 015

2 42Tuesday, September 01, 2 015

2 42Tuesday, September 01, 2 015

E

0.3

0.3

0.3

of

of

of

A

B

C

D

E

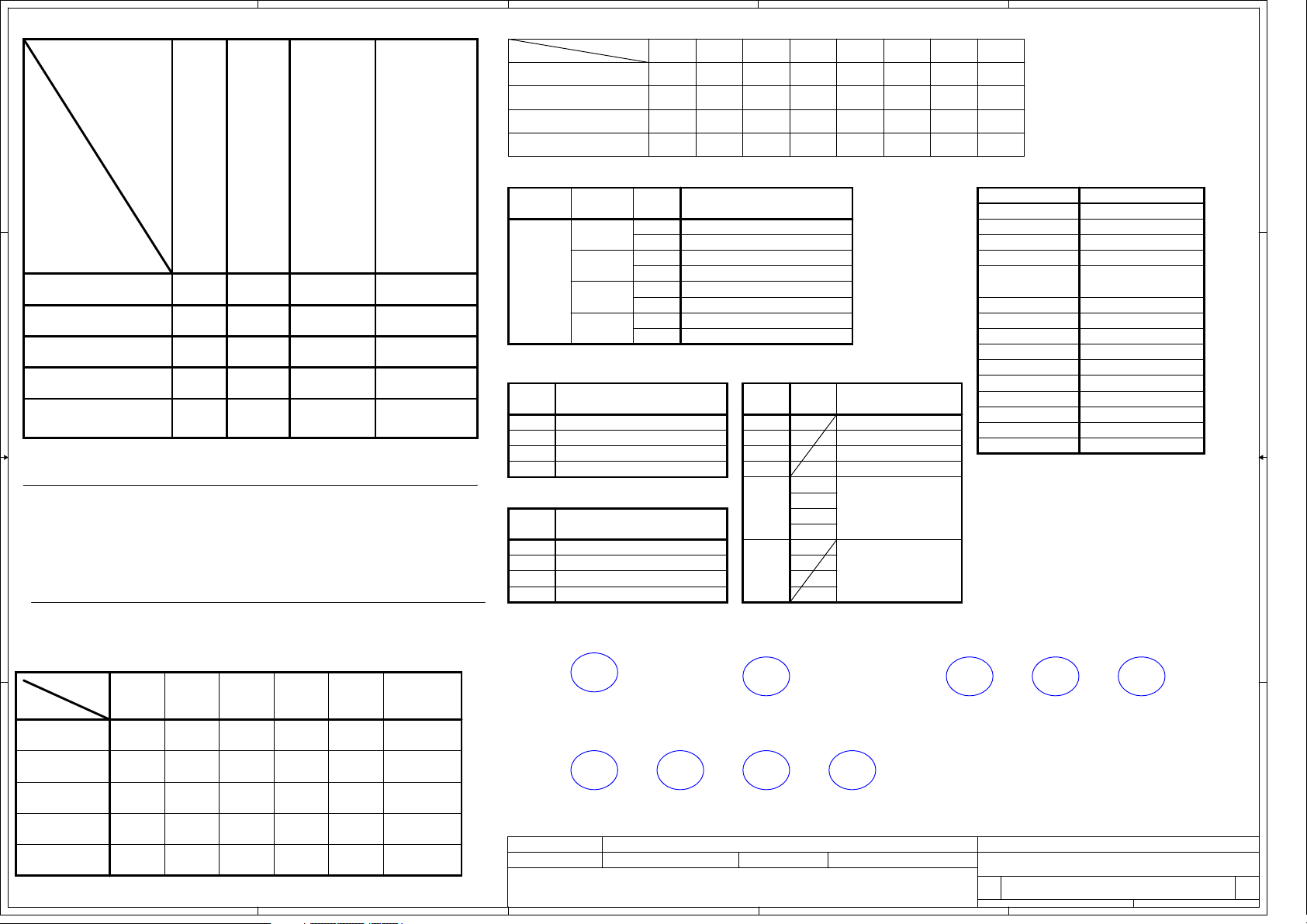

Voltage Rails

STATE

Full ON

power

1 1

State

2 2

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

plane

+5VALW

B+

S0

S3

+3VALW

+1.8VALW

+1.0VALW

O

O

O

X

X

O

O

O

X

X X X

+1.8V_MEM

O

X X

X

+5VS

+3VS

+1.8VS+1.2V_VDDQ

+1.0VS_VCCSTG

+1.0VS_VCCIO+1.0VS_VCCST

+VCC_CORE

+VCC_GT

+VCC_SA

+0.6VS_VTT

OO

X

X

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

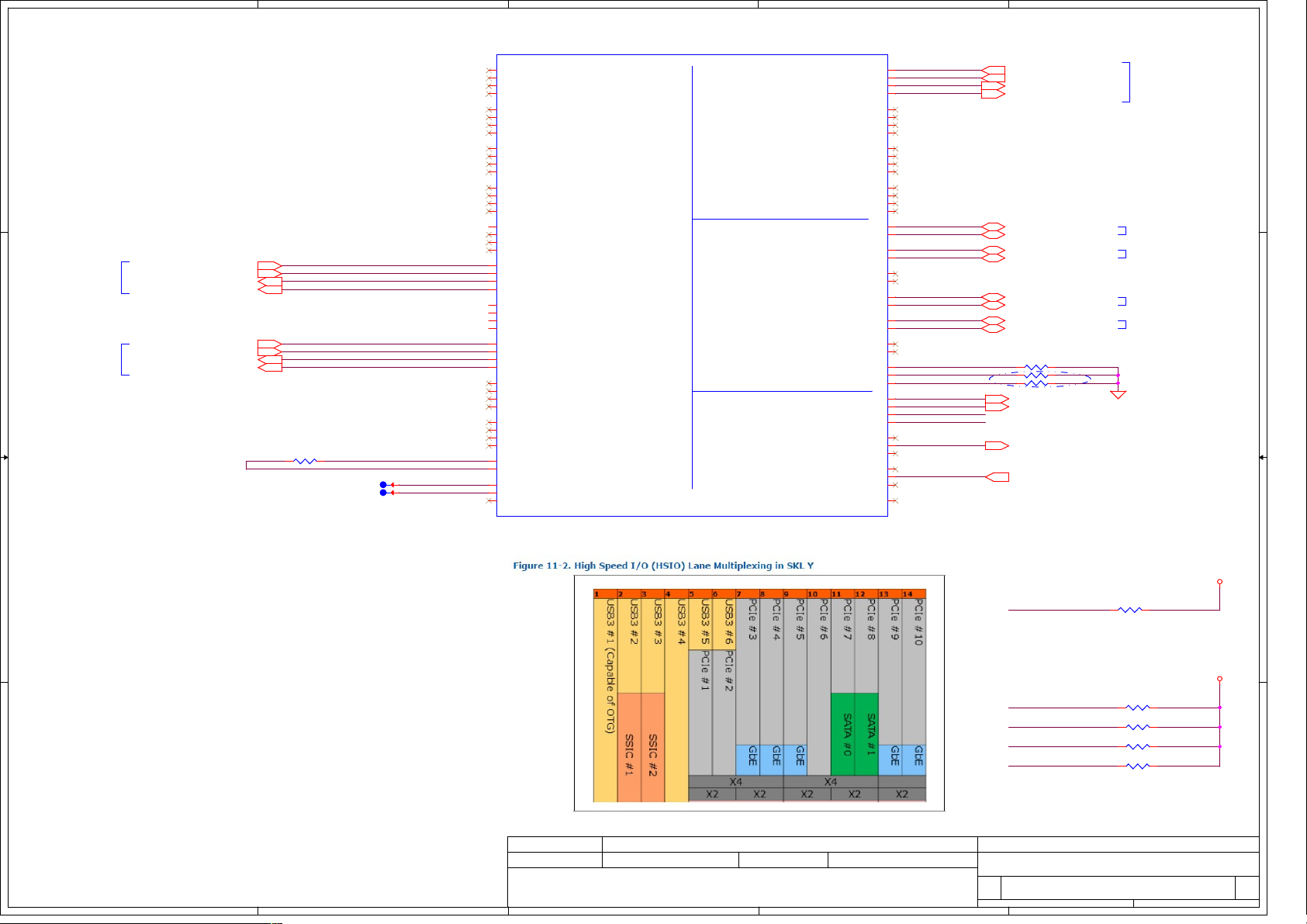

USB 2.0 Port Table

USB 3.0 Port Table

Port

1

2

3

EC SM Bus1 address

Device

Smart Batte ry

Charger

Address Address

EC SM Bus2 address

Device

Thermal Sen sor NCT7718 W

Skylake Y SML1

1001100x

4

SATA Port Table

Port

0

3 3

CPU SM Bus address

Device Address

NA NA

CPU SML0 Bus address

AddressDevice

1

2

3

SMBUS Control Table

Thermal

X

V

X

X

sensor

NCT7718W

XV

V

+3VS

X

X

VX

+3VS

B

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

HOST

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

SMBCLK

4 4

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

NPCE388

+3VLP

NPCE388

+3VS

CPU

+3VALW

CPU

+3VALW

CPU

+3VS

Changer

+3VLP

X

X

X

X V

A

BATT NPCE388

V

+3VLP

X

X

X

X

+3VS

X

X

X

X

CPU

+3VS

SIGNAL

SLP_S0# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS

USB 2.0 Port

USB 3.0 Port (MB)

NGFF SSD(SATA)

HDMI Logo

ZZZ

45@

HDMI Logo

RO00000 03HM

DRAM

ZZZ

M4G@

MICRON

X766553 8L01

EDF8132A3MA-JD-F-R

SA00008PF00

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

C

HIGH HIGH HIGH HIGH

LOW LOW

HIGH

LOWLOWLOW

HIGH

HIGH

3 External

USB Port

1

USB 3.0/2.0 Port (MB)

2

3

Camera

5

BT

7

9

DCIN-USB

PCIE Port Table

Port

Lane

1

2

3

4

5

6

PCB part CPU part

ZZZ

PCB 1I3 LA-D3 41P REV0 M/B

DA80015 8000

ZZZ

S4G@

SAMSUNG

X766553 8L02

K4E8E304EE-EGCFT00

SA00008PQ00

ZZZ

M8G@

MICRON

X766553 8L03

EDFA232A2MA-JD-F-R

SA00008Q100

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

0

1

2

3

NGFF WLAN

ZZZ

SAMSUNG

X766553 8L04

K4E6E304EE-EGCF

SA00008QV00

ON

ON

ON

ON

ON ON ON

ON

OFF

OFFLOW LOW LOW LOW

S8G@

D

Clock

OFF

OFF

OFF

OFF

OFF

OFF

BOM Structure Table

BTO Item BOM Structure

Connector ME@

76 LEVEL X76@

UNPOP

CPU OPTION

DRAM Option

EMI POP EMI@

ESD POP ESD@

RF POP RF@

ESD UNPOP @ESD@

45 LEVEL 45@

UC1

CPU1@

SR2EN D1 0 .9G

SA00009 2Y40

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

UC1

SR2EM D1 1.1 G

SA00009 2Z40

@

S4G@ H4G@ M4G@

M8G@H8G@S8G@

@EMI@EMI UNPOP

UC1

CPU2@

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Note List

Note List

Note List

LA-D341PR03

LA-D341PR03

LA-D341PR03

CPU3@

SR2EH D1 1 .2G

SA00009 2V40

E

0.3

0.3

0.3

3 42Tuesday, September 01, 2 015

3 42Tuesday, September 01, 2 015

3 42Tuesday, September 01, 2 015

of

of

of

A

B

C

D

E

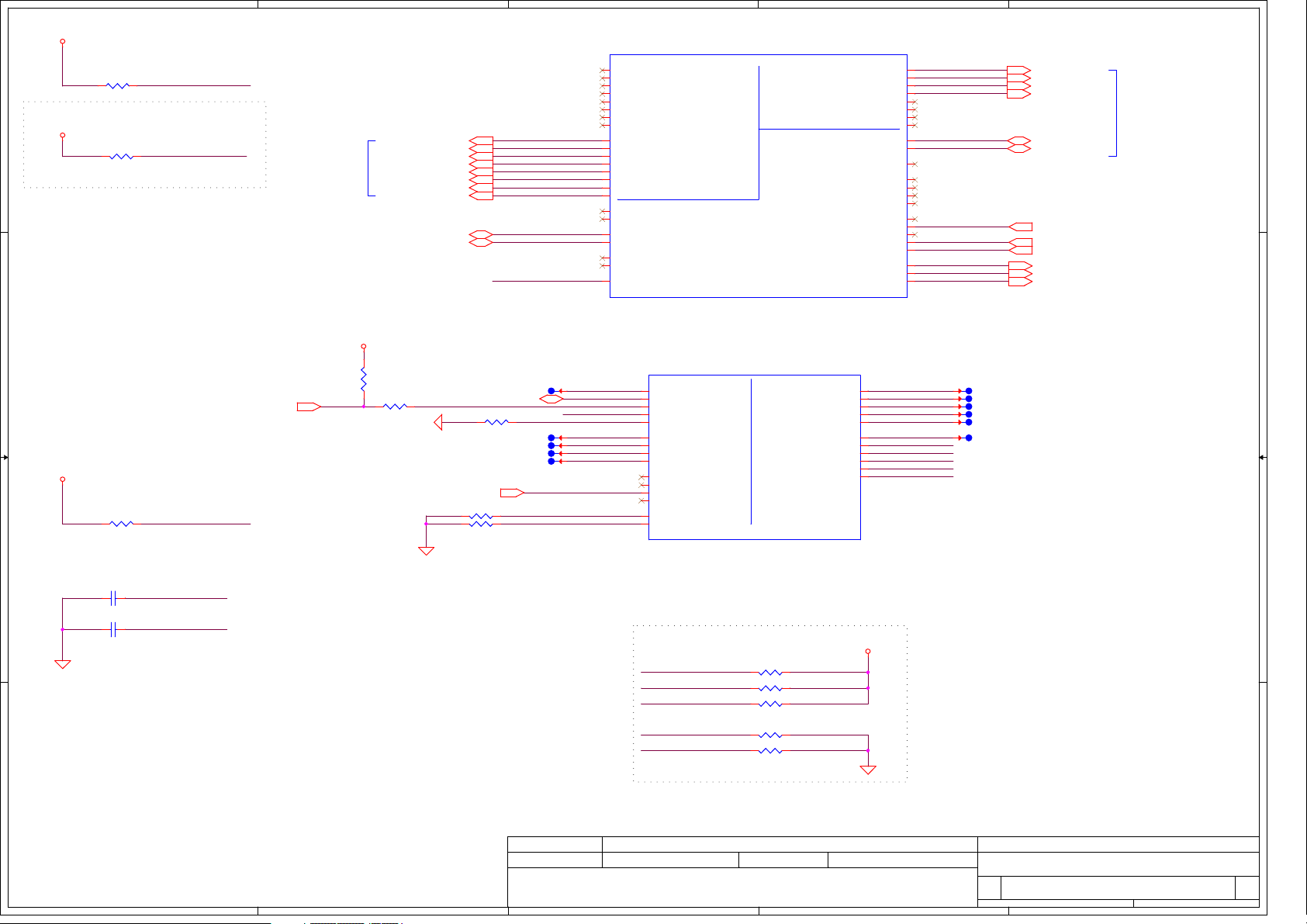

+3VS

UC1A

A46

DDI1_TXN[0]

C46

1 2

RC138 10K_040 2_5%

COMPENSATION PU FOR eDP

1 1

+1.0VS_V CCIO

1 2

RC2 24.9_0402_1 %

CAD note:

Trace width=20 mils,Spacing=25mil,Max length=100mils

SOC_DP2_CTRL_DATA(Internal Pull Down):

Display Port C Detected

0 = Port C is not detected.

1 = Port C is detected.

2 2

+1.0V_VC CST

1 2

RC5 1K_0402 _5%

3 3

ESD@

1 2

CC196

100P_04 02_50V8J

1 2

CC197

100P_04 02_50V8J

near to chipset

ESD@

EC_SCI#

EDP_COM P

H_THERM TRIP#

H_PROCH OT#_R

H_THERM TRIP#

HDMI DDC (Port C)

H_PROCH OT#<26,32>

<HDMI>

2.2K,3VS

2.2K,3VS

+1.0VS_V CCSTG

RC3

1K_0402 _5%

499_040 2_1%

1 2

1 2

RC4

CPU_DP2 _N0<21>

CPU_DP2 _P0<21>

CPU_DP2 _N1<21>

CPU_DP2 _P1<21>

CPU_DP2 _N2<21>

CPU_DP2 _P2<21>

CPU_DP2 _N3<21>

CPU_DP2 _P3<21>

DDI2_CTRL _CK<21>

DDI2_CTRL _DATA<2 1>

DDI2_CTRL _CK

DDI2_CTRL _DATA

EDP_COM P

To EC thermal

RC51 0_0402_5 %

10K,3VS

RC6 49.9_040 2_1%

RC7 49.9_040 2_1%

TC36 TP@

H_PECI<26>

12

@

TC35 TP@

TC43 TP@

TC12 TP@

TC13 TP@

TP_INT#<28>

TP_INT#

12

12

CPU_POP IRCOMP

PCH_OPIRC OMP

DDI1_TXP[0]

C48

DDI1_TXN[1]

A48

DDI1_TXP[1]

B45

DDI1_TXN[2]

D45

DDI1_TXP[2]

B47

DDI1_TXN[3]

D47

DDI1_TXP[3]

A42

DDI2_TXN[0]

C42

DDI2_TXP[0]

A44

DDI2_TXN[1]

C44

DDI2_TXP[1]

B41

DDI2_TXN[2]

D41

DDI2_TXP[2]

B43

DDI2_TXN[3]

D43

DDI2_TXP[3]

L6

GPP_E18/DDPB_CTRLCLK

H6

GPP_E19/DDPB_CTRLDATA

H4

GPP_E20/DDPC_CTRLCLK

F4

GPP_E21/DDPC_CTRLDATA

M5

GPP_E22/DDPD_CTRLCLK

L4

GPP_E23/DDPD_CTRLDATA

A50

EDP_RCOMP

SKL-Y_BGA15 15 @

UC1D

CATERR#

H_PECI

H_PROCH OT#_R

H_THERM TRIP#

SKTOCC#

XDP_BPM #0

XDP_BPM #1

XDP_BPM #2_R

XDP_BPM #3_R

H49

CATERR#

F49

PECI

J48

PROCHOT#

H47

THERMTRIP#

B62

SKTOCC#

H51

BPM#[0]

J50

BPM#[1]

F51

BPM#[2]

G50

BPM#[3]

E11

GPP_E3/CPU_GP0

M9

GPP_E7/CPU_GP1

BD8

GPP_B3/CPU_GP2

BC11

GPP_B4/CPU_GP3

BN17

PROC_POPIRCOMP

BP16

PCH_OPIRCOMP

SKL-Y_BGA15 15

< PU/PD for Dual Scan Chain Debug >

SOC_XDP _TMS

SOC_XDP _TDI

SOC_XDP _TDO

DDI

CPU MISC

SKYLAKE_ULX

DISPLAY

<DDI1>

<DDI2>

DISPLAY SIDEBANDS

SKYLAKE_ULX

1 2

RC11 51_0 402_5%@

1 2

RC12 51_0 402_5%@

1 2

RC13 51_0 402_5%@

JTAG

<DDI1>

<DDI2>

PCH_JTAG_TCK

PCH_JTAG_TDO

PCH_JTAG_TMS

eDP

<DDI1>

<DDI2>

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TDI

PCH_TRST#

JTAGX

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

EDP_BKLEN

EDP_BKLCTL

EDP_VDDEN

D53

C54

G48

C59

F47

B53

C50

B51

A52

C52

B49

@

+1.0VS_V CCIO

H45

F45

J44

G44

J46

G46

H43

F43

J42

G42

A40

H41

F41

J40

G40

C11

L10

M7

F6

A7

D4

B6

D3

CPU_XDP _TCK0

SOC_XDP _TDI

SOC_XDP _TDO

SOC_XDP _TMS

SOC_XDP _TRST#

PCH_JTA G_TCK1

SOC_XDP _TDI

SOC_XDP _TDO

SOC_XDP _TMS

SOC_XDP _TRST#

CPU_XDP _TCK0

DDI2_HDMI_HP D

EC_SCI#

EDP_HPD

ENBKL

SOC_BKL _PWM

SOC_ENV DD

TC45TP@

TC46TP@

TC47TP@

TC48TP@

TC49TP@

TC50TP@

EDP_TXN 0 <20>

EDP_TXP 0 <20>

EDP_TXN 1 <20>

EDP_TXP 1 <20>

EDP_AUX N <20>

EDP_AUX P <2 0>

DDI2_HDMI_HP D <21 >

EC_SCI# < 26>

EDP_HPD <20>

ENBKL <26>

SOC_BKL _PWM <2 0>

SOC_ENV DD <20>

10K,3VS

PD 100K

<eDP>

1M,3VS

From HDMI

From eDP

H active

CPU_XDP _TCK0

PCH_JTA G_TCK1

4 4

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

C

1 2

RC14 51_0 402_5%@

1 2

RC15 51_0 402_5%@

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SKL Y(1/13) DDI,MSIC,XDP

SKL Y(1/13) DDI,MSIC,XDP

SKL Y(1/13) DDI,MSIC,XDP

LA-D341PR03

LA-D341PR03

LA-D341PR03

4 42Tuesday, September 01, 2 015

4 42Tuesday, September 01, 2 015

4 42Tuesday, September 01, 2 015

E

0.3

0.3

0.3

of

of

of

A

Vinafix.com

B

C

D

E

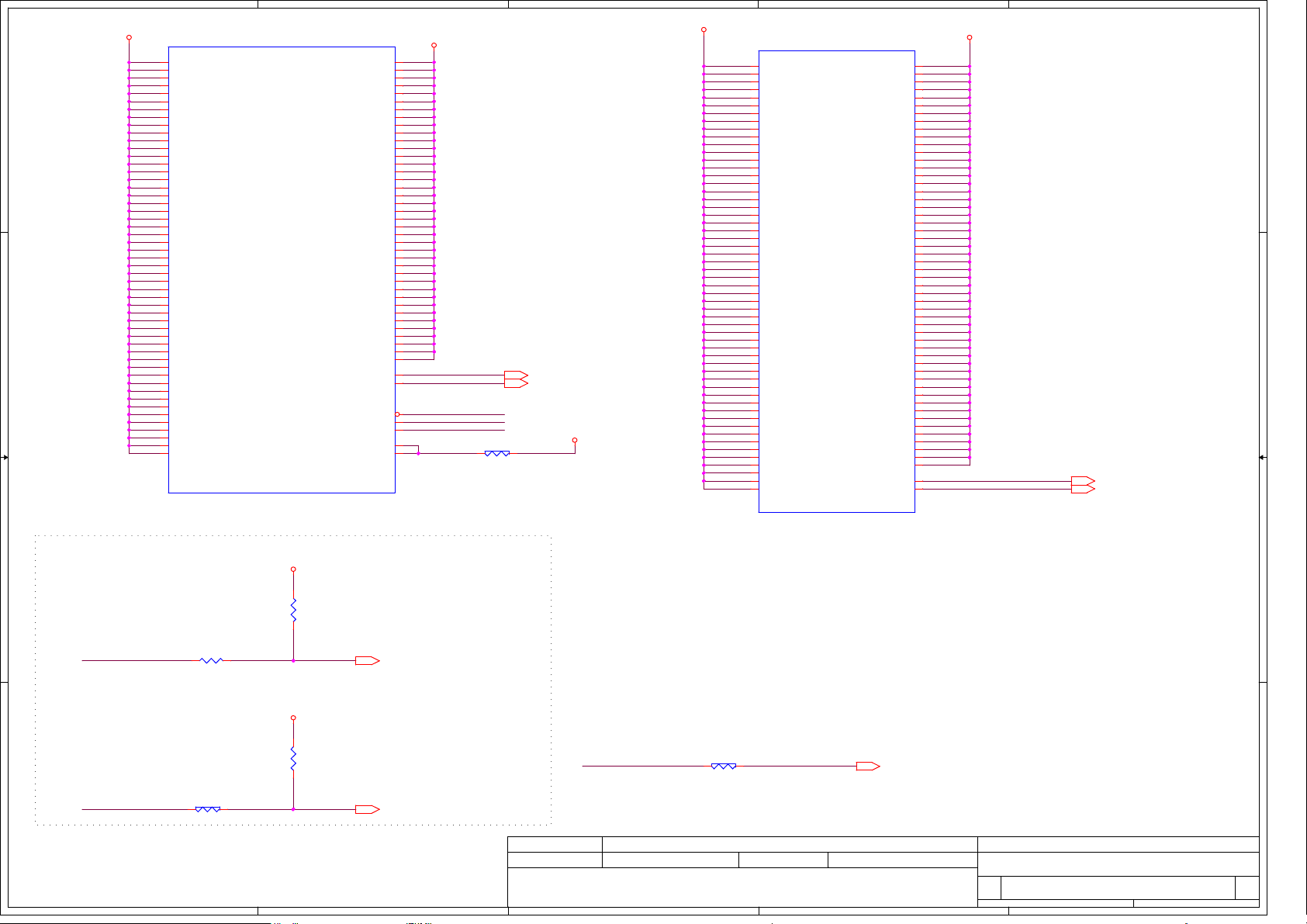

Non-Interleaved Memory

1 1

DDR_A_D[0..15]<18>

DDR_A_D[16..31 ]<18>

2 2

DDR_A_D[32..47 ]<18>

DDR_A_D[48..63 ]<18>

3 3

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1B

AG61

DDR0_DQ[0]

AH60

DDR0_DQ[1]

AK62

DDR0_DQ[2]

AK60

DDR0_DQ[3]

AH62

DDR0_DQ[4]

AG63

DDR0_DQ[5]

AL61

DDR0_DQ[6]

AL63

DDR0_DQ[7]

AM60

DDR0_DQ[8]

AM62

DDR0_DQ[9]

AT60

DDR0_DQ[10]

AR61

DDR0_DQ[11]

AN61

DDR0_DQ[12]

AN63

DDR0_DQ[13]

AR63

DDR0_DQ[14]

AT62

DDR0_DQ[15]

AT56

DDR1_DQ[0]/DDR0_DQ[16]

AR55

DDR1_DQ[1]/DDR0_DQ[17]

AN57

DDR1_DQ[2]/DDR0_DQ[18]

AN55

DDR1_DQ[3]/DDR0_DQ[19]

AR57

DDR1_DQ[4]/DDR0_DQ[20]

AT58

DDR1_DQ[5]/DDR0_DQ[21]

AM58

DDR1_DQ[6]/DDR0_DQ[22]

AM56

DDR1_DQ[7]/DDR0_DQ[23]

AL55

DDR1_DQ[8]/DDR0_DQ[24]

AL57

DDR1_DQ[9]/DDR0_DQ[25]

AH58

DDR1_DQ[10]/DDR0_DQ[26]

AH56

DDR1_DQ[11]/DDR0_DQ[27]

AK58

DDR1_DQ[12]/DDR0_DQ[28]

AK56

DDR1_DQ[13]/DDR0_DQ[29]

AG55

DDR1_DQ[14]/DDR0_DQ[30]

AG57

DDR1_DQ[15]/DDR0_DQ[31]

BE55

DDR0_DQ[16]/DDR0_DQ[32]

BC55

DDR0_DQ[17]/DDR0_DQ[33]

BG53

DDR0_DQ[18]/DDR0_DQ[34]

BE53

DDR0_DQ[19]/DDR0_DQ[35]

BC53

DDR0_DQ[20]/DDR0_DQ[36]

BG55

DDR0_DQ[21]/DDR0_DQ[37]

BD52

DDR0_DQ[22]/DDR0_DQ[38]

BF52

DDR0_DQ[23]/DDR0_DQ[39]

BC51

DDR0_DQ[24]/DDR0_DQ[40]

BE51

DDR0_DQ[25]/DDR0_DQ[41]

BC49

DDR0_DQ[26]/DDR0_DQ[42]

BE49

DDR0_DQ[27]/DDR0_DQ[43]

BG51

DDR0_DQ[28]/DDR0_DQ[44]

BG49

DDR0_DQ[29]/DDR0_DQ[45]

BF48

DDR0_DQ[30]/DDR0_DQ[46]

BD48

DDR0_DQ[31]/DDR0_DQ[47]

BJ55

DDR1_DQ[16]/DDR0_DQ[48]

BL55

DDR1_DQ[17]/DDR0_DQ[49]

BJ53

DDR1_DQ[18]/DDR0_DQ[50]

BL53

DDR1_DQ[19]/DDR0_DQ[51]

BN55

DDR1_DQ[20]/DDR0_DQ[52]

BN53

DDR1_DQ[21]/DDR0_DQ[53]

BM52

DDR1_DQ[22]/DDR0_DQ[54]

BK52

DDR1_DQ[23]/DDR0_DQ[55]

BL51

DDR1_DQ[24]/DDR0_DQ[56]

BJ51

DDR1_DQ[25]/DDR0_DQ[57]

BL49

DDR1_DQ[26]/DDR0_DQ[58]

BJ49

DDR1_DQ[27]/DDR0_DQ[59]

BN49

DDR1_DQ[28]/DDR0_DQ[60]

BN51

DDR1_DQ[29]/DDR0_DQ[61]

BK48

DDR1_DQ[30]/DDR0_DQ[62]

BM48

DDR1_DQ[31]/DDR0_DQ[63]

SKL-Y_BGA1515

SKYLAKE_ULX

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR CH - A

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

@

BC62

BC60

BA60

BA62

BB57

BC58

BE57

AW61

AW63

BJ57

BN61

AW59

AW55

BF62

AV56

AW57

AV58

BA56

BD59

BD61

BG61

BK59

BL62

BJ61

AV60

BN62

BB61

BL61

BM59

BN58

AV62

BB63

BL57

AJ61

AJ63

AP62

AP60

AP56

AP58

AJ57

AJ55

BD54

BF54

BF50

BD50

BM54

BK54

BK50

BM50

BG57

BM56

AR53

AN53

AW53

BN47

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_CAA0

DDR_A_CAA1

DDR_A_CAA2

DDR_A_CAA3

DDR_A_CAA4

DDR_A_CAA5

DDR_A_CAA6

DDR_A_CAA7

DDR_A_CAA8

DDR_A_CAA9

DDR_A_CAB0

DDR_A_CAB1

DDR_A_CAB2

DDR_A_CAB3

DDR_A_CAB4

DDR_A_CAB5

DDR_A_CAB6

DDR_A_CAB7

DDR_A_CAB8

DDR_A_CAB9

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

+0.6V_VREFCA

+0.6V_A_VREFDQ

+0.6V_B_VREFDQ

DDR_PG_CT RL

DDR_A_CLK#0 <18>

DDR_A_CLK0 <18>

DDR_A_CLK#1 <18>

DDR_A_CLK1 <18>

DDR_A_CKE0 <18>

DDR_A_CKE1 <18>

TC14TP@

TC15TP@

DDR_A_CS#0 <18>

DDR_A_CS#1 <18>

DDR_A_ODT0 <18>

DDR_A_CAA0 <18>

DDR_A_CAA1 <18>

DDR_A_CAA2 <18>

DDR_A_CAA3 <18>

DDR_A_CAA4 <18>

DDR_A_CAA5 <18>

DDR_A_CAA6 <18>

DDR_A_CAA7 <18>

DDR_A_CAA8 <18>

DDR_A_CAA9 <18>

DDR_A_CAB0 <18>

DDR_A_CAB1 <18>

DDR_A_CAB2 <18>

DDR_A_CAB3 <18>

DDR_A_CAB4 <18>

DDR_A_CAB5 <18>

DDR_A_CAB6 <18>

DDR_A_CAB7 <18>

DDR_A_CAB8 <18>

DDR_A_CAB9 <18>

DDR_A_DQS#0 <18>

DDR_A_DQS0 <18>

DDR_A_DQS#1 <18>

DDR_A_DQS1 <18>

DDR_A_DQS#2 <18>

DDR_A_DQS2 <18>

DDR_A_DQS#3 <18>

DDR_A_DQS3 <18>

DDR_A_DQS#4 <18>

DDR_A_DQS4 <18>

DDR_A_DQS#5 <18>

DDR_A_DQS5 <18>

DDR_A_DQS#6 <18>

DDR_A_DQS6 <18>

DDR_A_DQS#7 <18>

DDR_A_DQS7 <18>

+0.6V_VREFCA

+0.6V_A_VREFDQ

+0.6V_B_VREFDQ

DDR_B_D[0..15 ]<19>

DDR_B_D[16 ..31]<19>

DDR_B_D[32 ..47]<19>

DDR_B_D[48 ..63]<19>

Trace width/Spacing >= 20mils

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

BC41

DDR0_DQ[32]/DDR1_DQ[0]

BC39

DDR0_DQ[33]/DDR1_DQ[1]

BG41

DDR0_DQ[34]/DDR1_DQ[2]

BE39

DDR0_DQ[35]/DDR1_DQ[3]

BF42

DDR0_DQ[36]/DDR1_DQ[4]

BD42

DDR0_DQ[37]/DDR1_DQ[5]

BG39

DDR0_DQ[38]/DDR1_DQ[6]

BE41

DDR0_DQ[39]/DDR1_DQ[7]

BC43

DDR0_DQ[40]/DDR1_DQ[8]

BD46

DDR0_DQ[41]/DDR1_DQ[9]

BG43

DDR0_DQ[42]/DDR1_DQ[10]

BG45

DDR0_DQ[43]/DDR1_DQ[11]

BC45

DDR0_DQ[44]/DDR1_DQ[12]

BE43

DDR0_DQ[45]/DDR1_DQ[13]

BE45

DDR0_DQ[46]/DDR1_DQ[14]

BF46

DDR0_DQ[47]/DDR1_DQ[15]

BM28

DDR1_DQ[32]/DDR1_DQ[16]

BN27

DDR1_DQ[33]/DDR1_DQ[17]

BK28

DDR1_DQ[34]/DDR1_DQ[18]

BL25

DDR1_DQ[35]/DDR1_DQ[19]

BN25

DDR1_DQ[36]/DDR1_DQ[20]

BL27

DDR1_DQ[37]/DDR1_DQ[21]

BJ25

DDR1_DQ[38]/DDR1_DQ[22]

BJ27

DDR1_DQ[39]/DDR1_DQ[23]

BM24

DDR1_DQ[40]/DDR1_DQ[24]

BK24

DDR1_DQ[41]/DDR1_DQ[25]

BN21

DDR1_DQ[42]/DDR1_DQ[26]

BJ23

DDR1_DQ[43]/DDR1_DQ[27]

BL23

DDR1_DQ[44]/DDR1_DQ[28]

BN23

DDR1_DQ[45]/DDR1_DQ[29]

BJ21

DDR1_DQ[46]/DDR1_DQ[30]

BL21

DDR1_DQ[47]/DDR1_DQ[31]

BN45

DDR0_DQ[48]/DDR1_DQ[32]

BM46

DDR0_DQ[49]/DDR1_DQ[33]

BL43

DDR0_DQ[50]/DDR1_DQ[34]

BK46

DDR0_DQ[51]/DDR1_DQ[35]

BN43

DDR0_DQ[52]/DDR1_DQ[36]

BL45

DDR0_DQ[53]/DDR1_DQ[37]

BJ45

DDR0_DQ[54]/DDR1_DQ[38]

BJ43

DDR0_DQ[55]/DDR1_DQ[39]

BM42

DDR0_DQ[56]/DDR1_DQ[40]

BN41

DDR0_DQ[57]/DDR1_DQ[41]

BJ41

DDR0_DQ[58]/DDR1_DQ[42]

BN39

DDR0_DQ[59]/DDR1_DQ[43]

BK42

DDR0_DQ[60]/DDR1_DQ[44]

BL41

DDR0_DQ[61]/DDR1_DQ[45]

BL39

DDR0_DQ[62]/DDR1_DQ[46]

BJ39

DDR0_DQ[63]/DDR1_DQ[47]

BF28

DDR1_DQ[48]

BD28

DDR1_DQ[49]

BG25

DDR1_DQ[50]

BC27

DDR1_DQ[51]

BG27

DDR1_DQ[52]

BE27

DDR1_DQ[53]

BE25

DDR1_DQ[54]

BC25

DDR1_DQ[55]

BF24

DDR1_DQ[56]

BD24

DDR1_DQ[57]

BG21

DDR1_DQ[58]

BC23

DDR1_DQ[59]

BE23

DDR1_DQ[60]

BG23

DDR1_DQ[61]

BC21

DDR1_DQ[62]

BE21

DDR1_DQ[63]

SKL-Y_BGA1515 @

SKYLAKE_ULX

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[4]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - B

DDR1_CKN[0]

DDR1_CKP[0]

DDR1_CKN[1]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

BK36

BM36

BD32

BF32

BN33

BK32

BG33

BH30

BM30

BJ33

BC35

BK30

BN31

BM32

BL37

BG31

BN37

BJ37

BJ35

BM34

BN35

BG37

BE37

BC37

BF34

BC33

BF30

BD36

BG35

BC31

BF36

BJ31

BK34

BD40

BF40

BD44

BF44

BK26

BM26

BM22

BK22

BK44

BM44

BM40

BK40

BD26

BF26

BF22

BD22

BD34

BD30

BP20

BF64

BJ64

BC64

DDR_B_CLK #0

DDR_B_CLK 0

DDR_B_CLK #1

DDR_B_CLK 1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS# 0

DDR_B_CS# 1

DDR_B_ODT 0

DDR_B_CAA0

DDR_B_CAA1

DDR_B_CAA2

DDR_B_CAA3

DDR_B_CAA4

DDR_B_CAA5

DDR_B_CAA6

DDR_B_CAA7

DDR_B_CAA8

DDR_B_CAA9

DDR_B_CAB0

DDR_B_CAB1

DDR_B_CAB2

DDR_B_CAB3

DDR_B_CAB4

DDR_B_CAB5

DDR_B_CAB6

DDR_B_CAB7

DDR_B_CAB8

DDR_B_CAB9

DDR_B_DQS# 0

DDR_B_DQS0

DDR_B_DQS# 1

DDR_B_DQS1

DDR_B_DQS# 2

DDR_B_DQS2

DDR_B_DQS# 3

DDR_B_DQS3

DDR_B_DQS# 4

DDR_B_DQS4

DDR_B_DQS# 5

DDR_B_DQS5

DDR_B_DQS# 6

DDR_B_DQS6

DDR_B_DQS# 7

DDR_B_DQS7

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR_B_CLK #0 <19>

DDR_B_CLK 0 <19>

DDR_B_CLK #1 <19>

DDR_B_CLK 1 <19>

DDR_B_CKE0 <19>

DDR_B_CKE1 <19>

TC16TP@

TC17TP@

DDR_B_CS# 0 <19>

DDR_B_CS# 1 <19>

DDR_B_ODT 0 <1 9>

DDR_B_CAA0 <19>

DDR_B_CAA1 <19>

DDR_B_CAA2 <19>

DDR_B_CAA3 <19>

DDR_B_CAA4 <19>

DDR_B_CAA5 <19>

DDR_B_CAA6 <19>

DDR_B_CAA7 <19>

DDR_B_CAA8 <19>

DDR_B_CAA9 <19>

DDR_B_CAB0 <19>

DDR_B_CAB1 <19>

DDR_B_CAB2 <19>

DDR_B_CAB3 <19>

DDR_B_CAB4 <19>

DDR_B_CAB5 <19>

DDR_B_CAB6 <19>

DDR_B_CAB7 <19>

DDR_B_CAB8 <19>

DDR_B_CAB9 <19>

DDR_B_DQS# 0 <19>

DDR_B_DQS0 <19>

DDR_B_DQS# 1 <19>

DDR_B_DQS1 <19>

DDR_B_DQS# 2 <19>

DDR_B_DQS2 <19>

DDR_B_DQS# 3 <19>

DDR_B_DQS3 <19>

DDR_B_DQS# 4 <19>

DDR_B_DQS4 <19>

DDR_B_DQS# 5 <19>

DDR_B_DQS5 <19>

DDR_B_DQS# 6 <19>

DDR_B_DQS6 <19>

DDR_B_DQS# 7 <19>

DDR_B_DQS7 <19>

1 2

RC36 200_0402_ 1%

1 2

RC37 80.6_0402_ 1%

1 2

RC38 162_0402_ 1%

+3VALW

RC206

100K_0402_ 5%

1 2

DDR_VTT_PG_ CTRL<34>

4 4

DDR_VTT_PG_ CTRL

A

B

+1.2V_VDDQ_CPU

CC1

1 2

0.1U_0201_ 10V6K

UC9

5

NC

VCC

4

Y

GND

74AUP1G07GW _TSSOP5

SA00007UR00

1

2

DDR_PG_CT RL

A

3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2015/04/28 2016/04/28

2015/04/28 2016/04/28

2015/04/28 2016/04/28

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SKL Y(2/13) DDRIII

SKL Y(2/13) DDRIII

SKL Y(2/13) DDRIII

LA-D341PR03

LA-D341PR03

LA-D341PR03

E

5 4 2Tuesday, September 01, 2015

5 4 2Tuesday, September 01, 2015

5 4 2Tuesday, September 01, 2015

0.3

0.3

0.3

of

of

of

A

B

C

D

E

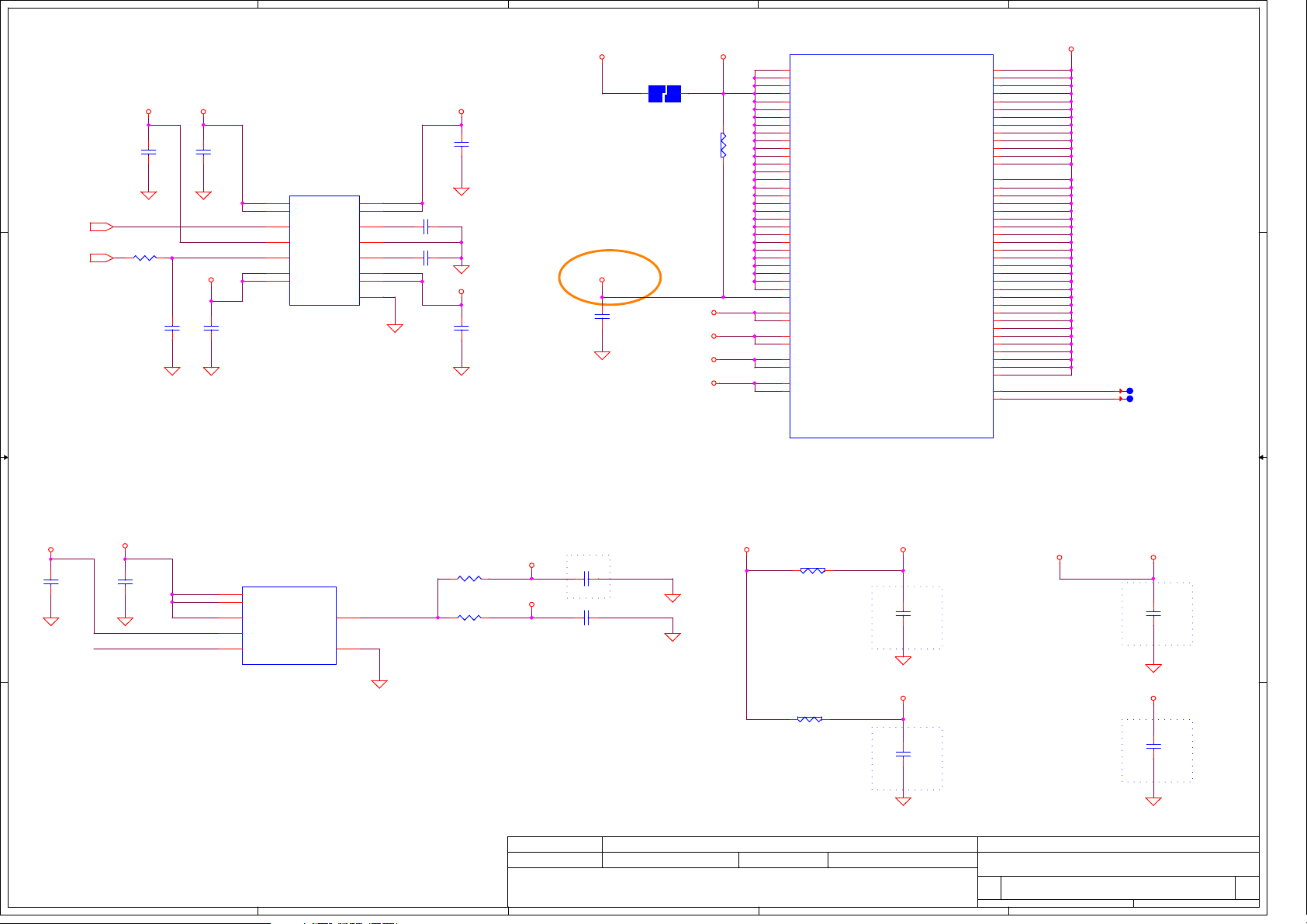

UC1E

SOC_SPI_C LK

1 1

10K,3VS

10K,3VS

KB_RST#<26>

SERIRQ<26>

SOC_SPI_S O

SOC_SPI_S I

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SPI_C S#0

KB_RST#

SERIRQ

LPC Mode

2 2

AU10

SPI0_CLK

AU12

SPI0_MISO

AT3

SPI0_MOSI

AV11

SPI0_IO2

AV13

SPI0_IO3

AU4

SPI0_CS0#

AU6

SPI0_CS1#

AU8

SPI0_CS2#

P9

GPP_D1/SPI1_CLK

N8

GPP_D2/SPI1_MISO

P3

GPP_D3/SPI1_MOSI

W12

GPP_D21/SPI1_IO2

V7

GPP_D22/SPI1_IO3

N6

GPP_D0/SPI1_CS#

F12

CL_CLK

D12

CL_DATA

B12

CL_RST#

BL10

GPP_A0/RCIN#

BN8

GPP_A6/SERIRQ

SKL-Y_BGA15 15

SPI - FLASH SMBUS, SMLINK

SPI - TOUCH

RPC2, RPC3 and RC30 are close to UC7

RPC2

SOC_SPI_S O

SOC_SPI_C LK

SOC_SPI_S I

From SOC

3 3

From EC

EC_SPI_CL K<26 >

EC_SPI_MO SI<26>

EC_SPI_CS 0#<26>

EC_SPI_MISO<26>

SOC_SPI_IO3

SOC_SPI_IO2

EC_SPI_CL K

EC_SPI_MO SI SOC_SPI_S I_0_R

EC_SPI_CS 0#

EC_SPI_MISO

1 8

2 7

3 6

4 5

33_0804 _8P4R_5%

EMI@

RC30

1 2

RPC3

1 8

2 7

3 6

4 5

33_0804 _8P4R_5%

EMI@

SOC_SPI_S O_0_R

SOC_SPI_C LK_0_R

SOC_SPI_S I_0_R

SOC_SPI_IO3_ 0_R

SOC_SPI_IO2_ 0_R

33_0402 _5%E MI@

SOC_SPI_C LK_0_R

SOC_SPI_C S#0

SOC_SPI_S O_0_R

C LINK

SKYLAKE_ULX

LPC

< SPI ROM - 8M >

SOC_SPI_C S#0

SOC_SPI_IO2_ 0_R

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

@

UC7

1

/CS

2

DO(IO1)

3

4

/HOLD(IO3)

/WP(IO2)

GND

W25 Q64FVSSIQ_SO8

SA00007 LA10

S IC FL 64M GD 25B64CSIGR SOP 8 P SPI ROM

VCC

CLK

DI(IO0)

8

7

6

5

AC12

SOC_SMB CLK

W6

SOC_SMB DATA

W8

SOC_SMB ALERT#

W4

SOC_SML 0CLK

AC10

SOC_SML 0DATA

AA6

SOC_SML 0ALERT#

AA4

EC_SMB_ CK2

W10

EC_SMB_ DA2

BB6

SOC_SML 1ALERT#

BK11

BJ8

BG10

BP5

BP7

BJ6

BJ10

CK_LPC_ KBC_R

BF5

BH11

PM_CLKR UN#

+3VALW

@

1 2

CC2 0.1U_020 1_10V6K

SOC_SPI_IO3_ 0_RSOC_SPI_S O_0_R

SOC_SPI_C LK_0_R

SOC_SPI_S I_0_R

1K,3VALW @

1K,3VALW @

2.2K,3VALW @

1K,3VALW @

1K,3VALW @

150K,3VALW @

EC_SMB_ CK2 <26,2 8>

EC_SMB_ DA2 <26,2 8>

150K,3VALW @

LPC_AD0 <2 6>

LPC_AD1 <2 6>

LPC_AD2 <2 6>

LPC_AD3 <2 6>

LPC_FRA ME# < 26>

RC44 22_0402 _5%

1

CC3

10P_040 2_50V8J

2

@EMI@

12

8.2K,3VS

499,3VS

(Link to EC)

499,3VS

ESPI / LPC Bus

ESPI : +1.8V

LPC : +3.3V

CK_LPC_ KBC <26>

follow MOW 6 & 9 rev 1.0

omit any PU/PD

default internal PD for LPC, PU for eSPI

To EC

EC_SMB_ CK2

EC_SMB_ DA2

PM_CLKR UN#

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SML 0ALERT#

SOC_SMB ALERT#

SOC_SML 1ALERT#

1 2

RC48 499_0402 _1%

1 2

RC49 499_0402 _1%

1 2

RC56 8.2K_04 02_5%

@

1 2

RC46 1K_0402_ 1%

@

1 2

RC47 1K_0402_ 1%

12

RC54

1K_0402 _1%

@

@

1 2

RC116 150K_04 02_1%

@

@

2.2K_040 2_5%

150K_04 02_1%

RC123

RC124

1 2

1 2

+3VS

+3V_SPI

+3VALW

+3VALW

RPC7

E

1 8

2 7

3 6

4 5

1K_0804 _8P4R_5%

@

6 42Tuesday, September 01, 2 015

6 42Tuesday, September 01, 2 015

6 42Tuesday, September 01, 2 015

of

of

of

0.3

0.3

0.3

SOC_SMB CLK

SOC_SMB DATA

SOC_SML 0CLK

SOC_SML 0DATA

4 4

Security Class ification

Security Class ification

Security Class ification

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/04/ 28 2016/04/ 28

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SKL Y(3/13) SPI,ESPI,SMB

SKL Y(3/13) SPI,ESPI,SMB

SKL Y(3/13) SPI,ESPI,SMB

LA-D341PR03

LA-D341PR03

LA-D341PR03

A

B

C

D

E

UC1G

HDA_SYNC

HDA_BIT_C LK

HDA_SDO UT

HDA_SDIN0

1 1

100K, 3VS @

2 2

SPKR<9,25>

HDA_RST #

SPKR

BJ19

HDA_SYNC/I2S0_SFRM

BK18

HDA_BLK/I2S0_SCLK

BK16

HDA_SDO/I2S0_TXD

BL15

HDA_SDI0/I2S0_RXD

BL17

HDA_SDI1/I2S1_RXD

BL19

HDA_RST#/I2S1_SCLK

V5

GPP_D23/I2S_MCLK

BL12

I2S1_SFRM

BK14

I2S1_TXD

AT13

GPP_F1/I2S2_SFRM

AT11

GPP_F0/I2S2_SCLK

AP11

GPP_F2/I2S2_TXD

AT5

GPP_F3/I2S2_RXD

V3

GPP_D19/DMIC_CLK0

V11

GPP_D20/DMIC_DATA0

U12

GPP_D17/DMIC_CLK1

U8

GPP_D18/DMIC_DATA1

AV3

GPP_B14/SPKR

SKL-Y_BGA15 15

HDA for AUDIO

HDA_BIT_C LK_R< 25>

HDA_SYNC_ R<25>

HDA_RST #_R<25>

HDA_SDO UT_R<25>

HDA_SDIN0<25>

AUDIO

<+3V_1.8V_PGPPD>

ME_EN<26>

SKYLAKE_ULX

SDIO/SDXC

GPP_A17/SD_PWR_EN#/ISH_GP7

RPC9

1 8

2 7

3 6

4 5

33_0804 _8P4R_5%

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A16/SD_1P8_SEL

SD_RCOMP

HDA_BIT_C LK

HDA_SYNC

HDA_RST #

HDA_SDO UT

HDA_SDIN0

GPP_F23

AH9

AH11

AG12

AF9

AF11

AG8

AG10

AE12

BL4

BN4

BF1

SD_RCOM P

AJ8

@

RC67 200_0402 _1%

12

UC1I

H29

CSI2_DN0

F29

CSI2_DP0

F33

CSI2_DN1

H33

CSI2_DP1

J30

3 3

4 4

A

G30

J32

G32

D29

B29

C32

A32

C30

A30

D33

B33

D35

B35

C36

A36

D37

B37

C38

A38

SKL-Y_BGA15 15

B

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

SKYLAKE_ULX

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI-2

eMMC

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

H31

F31

D31

B31

C34

A34

D39

B39

A11

MCSI_2_CO MP

N4

AN12

AP9

AN10

AJ10

AM9

AL12

AJ12

AN8

AL10

AL8

AM11

BC1

EMMC_RC OMP

@

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

C

RC69 100 _0402_1%

RC78 200_0402 _1%

Compal Secret Data

Compal Secret Data

Compal Secret Data

12

12

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SKL Y(4/13) HDA,EMMC,SDIO

SKL Y(4/13) HDA,EMMC,SDIO

SKL Y(4/13) HDA,EMMC,SDIO

LA-D341PR03

LA-D341PR03

LA-D341PR03

7 42Tuesday, September 01, 2 015

7 42Tuesday, September 01, 2 015

7 42Tuesday, September 01, 2 015

of

of

E

of

0.3

0.3

0.3

A

+3VS

RPC10

18

CLKREQ_PCIE#0

27

CLKREQ_PCIE#1

36

WLAN_CLKR EQ#

45

RPC11

@

ESD@

ESD@

ESD@

ESD@

ESD@

18

27

36

45

CLKREQ_PCIE#3

CLKREQ_PCIE#4

CLKREQ_PCIE#5

SYS_RESET#

EC_RSMRST#

SYS_PWROK

SOC_PLTRST #

H_CPUPW RGD_R

SYS_RESET#

near to chipset

EC_RSMRST#

near to chipset

PCH_PWR OK

WLAN(Mini-PCIE)

Only For Power Sequence Debug

SUSWARN#

PM_BATLOW#

WAKE#

AC_PRESENT

1 1

2 2

3 3

+3VALW_DSW

10K_0804_8 P4R_5%

+3VALW

10K_0804_8 P4R_5%

1 2

CC200

1000P_0402 _50V7K

1 2

CC194

100P_0402_ 50V8J

1 2

CC188

100P_0402_ 50V8J

1 2

CC198

100P_0402_ 50V8J

1 2

CC199

100P_0402_ 50V8J

1 2

RC95

10K_0402_5 %

+3V_1.8V_PGPPA

1 2

RC101 10K_0402 _5%

1 2

RC97 8.2K_0402_ 5%

1 2

RC98 1K_0402_5 %

1 2

RC100 10K_0402 _5%

B

10K,3VS

CLK_PCIE_WLAN#<23>

CLK_PCIE_WLAN< 23>

WLAN_CLKR EQ#<23>

PD 10K

TC83 TP@

PD 10K

EC_RSMRST#<26>

SYS_PWROK<26>

PCH_PWR OK<26>

10K,3VS

10K,3VS

10K,3VS

10K,3VS

10K,3VS

CLKREQ_PCIE#1

CLK_PCIE_WL AN#

CLK_PCIE_WL AN

WLAN_CLKR EQ#

CLKREQ_PCIE#3

CLKREQ_PCIE#4

CLKREQ_PCIE#5

CLKREQ_PCIE#0

10K,3VALW

1K, +1.0V_VCCST

10K,3VALW @

1K,3VALW

H35

F35

AV9

J36

G36

BD10

J38

G38

AV5

H37

F37

AV7

H39

F39

BC5

BB10

PCH PLTRST Buffer

SOC_PLTRST #

SYS_RESET#

EC_RSMRST#

H_CPUPW RGD_R

EC_VCCST_PG

SYS_PWROK

PCH_PWR OK

EC_RSMRST#

SUSWARN#

WAKE#

C

UC1J

CLKOUT_PCIE_N1

CLKOUT_PCIE_P1

GPP_B6/SRCCLKREQ1#

CLKOUT_PCIE_N2

CLKOUT_PCIE_P2

GPP_B7/SRCCLKREQ2#

CLKOUT_PCIE_N3

CLKOUT_PCIE_P3

GPP_B8/SRCCLKREQ3#

CLKOUT_PCIE_N4

CLKOUT_PCIE_P4

GPP_B9/SRCCLKREQ4#

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

GPP_B10/SRCCLKREQ5#

GPP_B5/SRCCLKREQ0#

SKL-Y_BGA1515

RC90 0_0402_5%

SOC_PLTRST #

SN74AHC1G08D CKR_SC70-5

UC1K

BB8

GPP_B13/PLTRST#

H2

SYS_RESET#

BJ12

RSMRST#

A62

PROCPWRGD

B61

VCCST_PWRGD

J1

SYS_PWROK

BP14

PCH_PWROK

BN15

DSW_PWROK

BL6

GPP_A13/SUSWARN#/SUSPWRDNACK

BF9

GPP_A15/SUSACK#

BP9

WAKE#

BE15

GPD2/LAN_WAKE#

BC15

GPD11/LANPHYPC

BB16

GPD7/RSVD

SKL-Y_BGA1515

SKYLAKE_ULX

CLOCK SIGNALS

1 2

+3VS

CC10

1 2

5

0.1U_0201_ 10V6K

UC3

1

P

IN1

O

2

IN2

G

3

@

SKYLAKE_ULX

SYSTEM POWER MANAGEMENT

4

CLKOUT_ITPXDP_P

@

CLKOUT_ITPXDP

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

PLT_RST#

12

RC16

100K_0402_ 5%

@

GPP_B11/EXT_PWR_GATE#

J34

G34

BA15

SUSCLK_W LAN

M1

SOC_XTAL24_IN

L2

SOC_XTAL24_OUT

P1

XCLK_BIASREF

BN19

SOC_RTCX1

BP18

SOC_RTCX2

BH18

SOC_SRTCRS T#

BN12

SOC_RTCRST #

@

PLT_RST# <23 ,26>

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B2/VRALERT#

D

1 2

RC85 2.7K_0402_ 1%

20K,3VL_RTC

20K,3VL_RTC

EC/ WLAN

BC9

PM_SLP_S0#

AY14

PM_SLP_S3#

BF16

PM_SLP_S4#

BH14

PM_SLP_S5#

BN10

BP11

BH16

BE17

BF14

PBTN_OUT#

BD14

AC_PRESENT

BD16

PM_BATLOW#

BF7

BG19

SM_INTRUDER#

BC7

BD6

SOC_VRALERT#

@

SUSCLK_W LAN <23>

PM_SLP_S3# <2 6>

PM_SLP_S4# <2 6>

8.2K,3VALW

1M,3VL_RTC

10K,3VALW @

+1.0V_CLK5_F2 4NS

Change to 2.71K_0.5% (SD00001F80)

SOC_XTAL24_IN

TC80T P@

TC81T P@

TC84T P@

TC82T P@

PBTN_OUT# <26>

100K,3VALW

10K,3VALW

SOC_XTAL24_OUT

RC89 1M_0402_5 %

15P_0402_50V8J

1

CC8

2

SOC_RTCX2

SOC_RTCX1

RC93 1 0M_0402_5%

32.768KHZ_9P F_X1A000141000200

8.2P_0402_50V8D

12

E

1 2

YC1

24MHZ_12PF_7 V24000020

SJ10000DI00

3

3

GND

4

1 2

YC2

1 2

SJ10000Q400

CC11

GND

1

1

15P_0402_50V8J

1

2

CC9

2

8.2P_0402_50V8D

12

CC12

+3VALW

@

1 2

RC102 10K_0402 _5%

RC105 100K_040 2_5%

4 4

From EC(open-drain)

EC_VCCST_PG_ R<26>

12

A

SOC_VRALERT#

PBTN_OUT#

+1.0V_VCCST

12

RC109

1K_0402_5%

1 2

RC110 60.4_0402 _1%

EC_VCCST_PG

B

+3VL_RTC

1 2

RC87 20K_0402_ 5%

1 2

CC21 1U_0402_ 6.3V6K

@

1 2

CLRP4 SHORT PADS

1 2

RC83 20K_0402_ 5%

1 2

CC30 1U_0402_ 6.3V6K

@

1 2

CLRP3 SHORT PADS

1 2

RC86 1M_0402_5 %

SOC_SRTCRS T#

CLR ME

SOC_RTCRST #

CLR CMOS

SM_INTRUDER#

1 2

RC10 0_ 0402_5%

@

13

QC7

D

2N7002K_SOT 23-3

2

G

S

CRB : 330K PDG : 1M

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2015/04/28 2016/04/28

2015/04/28 2016/04/28

2015/04/28 2016/04/28

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

12

RC8

10K_0402_5 %

EC_CLEAR_CMO S <26>

Title

Title

Title

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SKL Y(5/13) CLK,GPIO

SKL Y(5/13) CLK,GPIO

SKL Y(5/13) CLK,GPIO

LA-D341PR03

LA-D341PR03

LA-D341PR03

E

8 4 2Tuesday, September 01, 2015

8 4 2Tuesday, September 01, 2015

8 4 2Tuesday, September 01, 2015

0.3

0.3

0.3

of

of

of

A

B

C

D

E

UC1F

BC3

GPP_B15/GSPI0_CS#

AW10

GPP_B16/GSPI0_CLK

AW6

GPP_B17/GSPI0_MISO

GSPI0_MOS I

1 1

10K,3VS

49.9K,3VS

49.9K,3VS

UART_2_ CRXD_DTXD<23>

UART_2_ CTXD_DRXD<23>

<Touch Pad>

2 2

4.7K,3VS @

150K,3VS @

49.9K,3VS @

BT_OFF#<23>

49.9K,3VS @

49.9K,3VS @

1K,3VS

1K,3VS

GSPI1_MOS I

NGFF_SS D_PRESENT#

BT_OFF#

UART_2_ CRXD_DTXD

UART_2_ CTXD_DRXD

UART_2_ CRTS_DCTS

UART_2_ CCTS_DRTS

I2C1_SDA_ TP

I2C1_SCL_ TP

BB4

GPP_B18/GSPI0_MOSI

BB2

GPP_B19/GSPI1_CS#

AW12

GPP_B20/GSPI1_CLK

AW4

GPP_B21/GSPI1_MISO

AW8

GPP_B22/GSPI1_MOSI

AC8

GPP_C8/UART0_RXD

AA8

GPP_C9/UART0_TXD

AA10

GPP_C10/UART0_RTS#

AA12

GPP_C11/UART0_CTS#

AD5

GPP_C20/UART2_RXD

AD7

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD9

GPP_C23/UART2_CTS#

AD11

GPP_C16/I2C0_SDA

AB3

GPP_C17/I2C0_SCL

AB9

GPP_C18/I2C1_SDA

AB11

GPP_C19/I2C1_SCL

AP3

GPP_F4/I2C2_SDA

AP7

GPP_F5/I2C2_SCL

AP5

GPP_F6/I2C3_SDA

AT7

GPP_F7/I2C3_SCL

AN4

GPP_F8/I2C4_SDA

AN6

GPP_F9/I2C4_SCL

SKL-Y_BGA15 15

3.3V

Functional Strap Definitions

SPKR (Internal Pull Down):

SKYLAKE_ULX

ISHLPSS

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA

GPP_D14/ISH_UART0_TXD/SML0BCLK

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_D15/ISH_UART0_RTS#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_A12/BM_BUSY#/ISH_GP6

BT_OFF#

P11

T7

T5

T11

P7

P5

T9

T3

AM7

AT9

U10

RAM_ID0

U4

RAM_ID1

U6

RAM_ID2

V9

AC6

AC4

AB7

AB5

BF11

BD2

BJ1

BL3

BJ3

BD4

BJ4

@

I2C1_SDA_ TP<2 8>

I2C1_SCL_ TP<28>

NGFF_SS D_PRESENT#

UART_2_ CRXD_DTXD

UART_2_ CTXD_DRXD

UART_2_ CRTS_DCTS

UART_2_ CCTS_DRTS

SPKR<7,25>

I2C1_SDA_ TP

I2C1_SCL_ TP

SPKR

GSPI0_MOS I

GSPI1_MOS I

1 2

@

1 2

@

@

1 2

1 2

@

@

@

+3VS

RC9610K_0402_5%

RC20349.9K_04 02_1%

+3VS

12

RC8849.9K_04 02_1%

12

RC12249.9K_04 02_1%

12

RC12749.9K_04 02_1%

12

RC13149.9K_04 02_1%

+3VS

RC1791K_0402 _1%

RC1801K_0402 _1%

+3VS

12

RC113100K_04 02_5%

12

RC1144.7K_0402_5%

12

RC115150K_04 02_5%

TOP Swap Override

0 = Disable TOP Swap mode.---> Use

1 = Enable TOP Swap Mode.

+3V_1.8V _PGPPD

GSPI0_MOSI (Internal Pull Down):

3 3

No Reboot

0 = Disable No Reboot mode. --> Use

1 = Enable No Reboot Mode. (PCH will disable the TCO

Timer system reboot feature). This function is useful

when running ITP/XDP.

GSPI1_MOSI (Internal Pull Down):

Boot BIOS Strap Bit

8Gb x32 LPDDR3 1866

0 = SPI Mode --> Use

1 = LPC Mode

16Gb x32 LPDDR3 1866

SML0ALERT# (Internal Pull Down):

4 4

X76@

1 2

X76@

1 2

X76@

1 2

Capacity

X76@

RAM_ID0

RC2151K_0402 _1%

RAM_ID1

RC2171K_0402 _1%

RAM_ID2

RC2191K_0402 _1%

Vendor

SAMSUNG

Hynix

Micron

SAMSUNG

Hynix

Micron

1 2

X76@

1 2

X76@

1 2

RAM_ID

000

001

010

011

100

101

RC2161K_0402 _1%

RC2181K_0402 _1%

RC2201K_0402 _1%

Description

K4E8E304EE-EGCF

H9CCNNN8GTMLAR-NUD

EDF8132A3MA-JD-F

K4E6E304EE-EGCF

H9CCNNNBJTMLAR-NUD

EDFA232A2MA-JD-F

Channel Stuf f R

A/B

RC215,RC217,RC219

RC216,RC217,RC219

A/B

RC215,RC218,RC219

A/B

RC216,RC218,RC219

A/B

A/B

RC215,RC217,RC220

A/B

RC216,RC217,RC220

eSPI or LPC

0 = LPC is selected for EC --> Use

1 = eSPI is selected for EC

A

B

Security Class ification

Security Class ification

Security Class ification

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/04/ 28 2016/04/ 28

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SKL Y(6/13) GPIO,LPIO,I2C

SKL Y(6/13) GPIO,LPIO,I2C

SKL Y(6/13) GPIO,LPIO,I2C

LA-D341PR03

LA-D341PR03

LA-D341PR03

9 42Tuesday, September 01, 2 015

9 42Tuesday, September 01, 2 015

9 42Tuesday, September 01, 2 015

E

of

of

of

0.3

0.3

0.3

A

B

C

D

E

UC1H

C20

PCIE1_RXN/USB3_5_RXN

A20

PCIE1_RXP/USB3_5_RXP

G20

PCIE1_TXN/USB3_5_TXN

J20

PCIE1_TXP/USB3_5_TXP

B19

PCIE2_RXN/USB3_6_RXN

D19

PCIE2_RXP/USB3_6_RXP

1 1

PCIE_PRX_ DTX_N6<23>

WLAN(NGFF card)

2 2

NGFF SSD

PCIE_PRX_ DTX_P6<23>

PCIE_PTX_ DRX_N6<23>

PCIE_PTX_ DRX_P6<23>

SATA_PR X_DTX_N1<22>

SATA_PR X_DTX_P1<22>

SATA_PT X_DRX_N1<22>

SATA_PT X_DRX_P1<22>

1 2

RC118 100_040 2_1%

TC197 TP@

TC196 TP@

PCIE_RCOM PN

PCIE_RCOM PP

F19

PCIE2_TXN/USB3_6_TXN

H19

PCIE2_TXP/USB3_6_TXP

C22

PCIE3_RXN

A22

PCIE3_RXP

G22

PCIE3_TXN

J22

PCIE3_TXP

B21

PCIE4_RXN

D21

PCIE4_RXP

F21

PCIE4_TXN

H21

PCIE4_TXP

C24

PCIE5_RXN

A24

PCIE5_RXP

G24

PCIE5_TXN

J24

PCIE5_TXP

B23

PCIE6_RXN

D23

PCIE6_RXP

F23

PCIE6_TXN

H23

PCIE6_TXP

C26

PCIE7_RXN/SATA0_RXN

A26

PCIE7_RXP/SATA0_RXP

G26

PCIE7_TXN/SATA0_TXN

J26

PCIE7_TXP/SATA0_TXP

B25

PCIE8_RXN/SATA1A_RXN

D25

PCIE8_RXP/SATA1A_RXP

F25

PCIE8_TXN/SATA1A_TXN

H25

PCIE8_TXP/SATA1A_TXP

C28

PCIE9_RXN

A28

PCIE9_RXP

G28

PCIE9_TXN

J28

PCIE9_TXP

B27

PCIE10_RXN

D27

PCIE10_RXP

F27

PCIE10_TXN

H27

PCIE10_TXP

A9

PCIE_RCOMPN

B10

PCIE_RCOMPP

D51

PROC_PRDY#

B55

PROC_PREQ#

BF3

GPP_A7/PIRQA#

SKL-Y_BGA15 15

PCIE/USB3/SATA

SKYLAKE_ULX

SSIC / USB3

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB2

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_5

USB2P_5

USB2N_7

USB2P_7

USB2N_3

USB2P_3

USB2N_9

USB2P_9

USB2N_2

USB2P_2

USB2_COMP

USB2_ID

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E8/SATALED#

C16

A16

G16

J16

B15

D15

F15

H15

C18

A18

G18

J18

B17

D17

F17

H17

AJ6

AJ4

AH5

AH3

AF5

AF3

AL6

AL4

AG6

AG4

AM3

AM5

N2

AF7

AE6

N12

M11

F8

B8

F10

H10

L8

G11

J11

N10

H8

@

USB20_N 1

USB20_P 1

USB20_N 2

USB20_P 2

USB20_N 4

USB20_P 4

USB20_N 5

USB20_P 5

USB2_CO MP

USB_OC0 #

USB_OC1 #

USB_OC2 #

USB_OC3 #

DEVSLP1

NGFF_SS D_PEDET

USB3_RX 1_N <24>

USB3_RX 1_P <24>

USB3_TX 1_N <24 >

USB3_TX 1_P <24>

USB20_N 1 <24 >

USB20_P 1 <24>

USB20_N 2 <23 >

USB20_P 2 <23>

USB20_N 4 <20 >

USB20_P 4 <20>

USB20_N 5 <27 >

USB20_P 5 <27>

1 2

RC117 113_0 402_1%

1 2

RC134 1K_0402 _5%

1 2

RC185 1K_0402 _5%

USB_OC0 # <24>

USB_OC1 # <27>

10K,3VALW

10K,3VALW

DEVSLP1 <22>

NGFF_SS D_PEDET <22>

10K,3VALW

To NGFF SSD

USB 3.0 MB

USB 2.0 MB

BT

Camera

DCIN-USB

OTG is not in u se

To USB 3.0

To USB SW

10K,3VS @

3 3

@

NGFF_SS D_PEDET

USB_OC0 #

USB_OC1 #

USB_OC2 #

USB_OC3 #

4 4

Security Class ification

Security Class ification

Security Class ification

2015/04/ 28 2016/04/ 28

2015/04/ 28 2016/04/ 28

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/04/ 28 2016/04/ 28

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

1 2

RC130 10K_040 2_5%

1 2

RC121 10K_0 402_5%

1 2

RC125 10K_0 402_5%

1 2

RC142 10K_0 402_5%

1 2

RC128 10K_0 402_5%

SKL Y(7/13) PCIE,USB

SKL Y(7/13) PCIE,USB

SKL Y(7/13) PCIE,USB

LA-D341PR03

LA-D341PR03

LA-D341PR03

E

+3VS

+3VALW

0.3

0.3

0.3

10 42Tuesday, Septemb er 01, 2015

10 42Tuesday, Septemb er 01, 2015

10 42Tuesday, Septemb er 01, 2015

of

of

of

A

B

C

D

E

AH64

BA27

BA37

BA49

BP32

BP50

AK64

BA29

BA41

BA51

BP34

BP56

AT64

BA31

BA43

BN64

BP40

BP58

AV64

BA33

BA45

BP24

BP42

BP64

BA25

BA35

BA47

BP26

BP48

BA39

V26

Y26

R26

AE27

AF27

R27

T26

T27

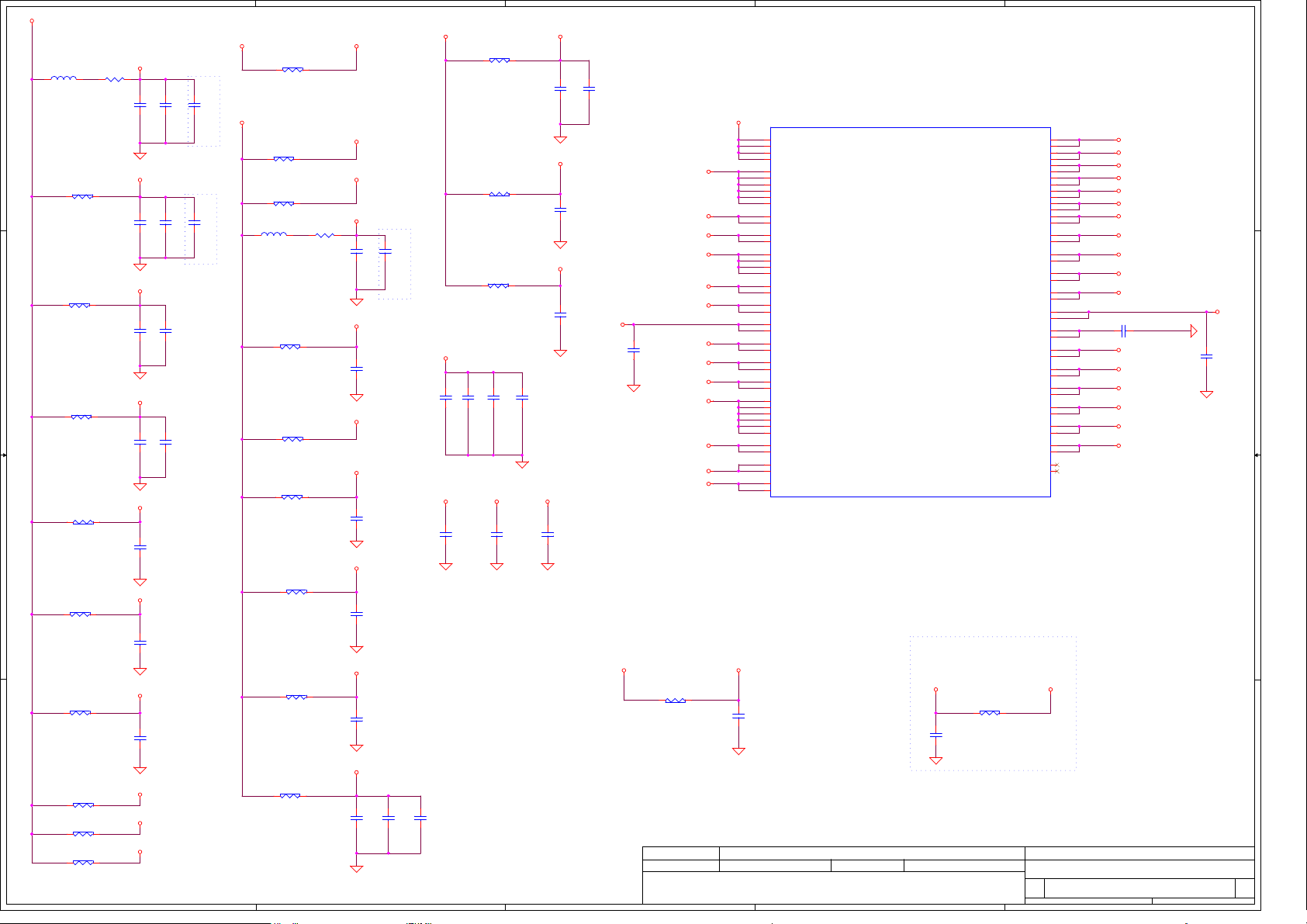

UC1N

SKL-Y_BGA15 15

+1.2V_VD DQ

+1.0VALW TO +1.0V_VCCSTU

+1.0VALW

1 1

SYSON<26,29,34>

SUSP#<2 6,29,34>

2 2

100K_04 02_1%

1

2

RC223

1 2

1U_0402_6.3V6K

CC15

1

CC29

2

@

+1.8VALW

0.1U_0201_10V6K

1U_0402_6.3V6K

CC13

1

2

UC4

1

VIN1

2

VIN1

3

ON1

4

VBIAS

5

ON2

6

VIN2

7

VIN2

1U_0402_6.3V6K

1

CC20

@

2

EM5209V F_DFN14_2X3

VOUT1

VOUT1

CT1

GND

CT2

VOUT2

VOUT2

GPAD

14

13

12

CC16

1000P_0 402_50V7K

11

10

CC17

1000P_0 402_50V7K

9

8

15

1 2

1 2

+1.0V_VC CSTU+5VALW

@

@

+1.8VS

JUMP_43 X118

0.1U_0201_10V6K

CC14

1

@

2

VDDQC trace

filter width = 6mm

Total etch length

= 186.94mils

PDG P597

+VDDQ_C PU_CLK

0.1U_0201_10V6K

1U_0402_6.3V6K

CC19

1

@

2

CC18

1

2

+1.0VS_V CCSTG

+1.2V_VC CSFR_OC

+1.8VALW TO +1.8VS

J503

@

2

112

0_0402_ 5%

+1.0V_VC CST

+1.0V_VC CSFR

+1.2V_VD DQ_CPU

RC209

1 2

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VCCST

VCCST

VCCSTG

VCCSTG

VCCPLL_OC

VCCPLL_OC

VCCPLL

VCCPLL

SKYLAKE_ULX

CPU POWER 3 OF 4

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_DDR

VCCIO_SENSE

VSSIO_SENSE

@

AC23

AF24

AN26

AC24

AF26

AR26

AE23

AH26

AT26

AE24

AK26

AE26

AL26

AV26

AV36

AV46

AW31

AW41

AW51

AV28

AV38

AV48

AW33

AW43

AV30

AV40

AV50

AW35

AW45

AV32

AV42

AW27

AW37

AW47

AV34

AV44

AW29

AW39

AW49

AT24

AR24

+1.0VS_V CCIO

VCCIO_SEN SE

VSSIO_SEN SE

TC139TP @

TC140TP @

+1.0VALW TO +1.0VS_VCCSTG / +1.0VS_VCCIO

+5VALW

CC22

3 3

4 4

1

@

2

+1.0VALW

0.1U_0201_10V6K

SUSP#

1U_0402_6.3V6K

1

CC28

@

2

A

UC6

1

VIN1

2

VIN2

7

VIN thermal

3

VBIAS

4

ON

TPS2296 1DNYR_WSON8

Total_ON=15us @1V

9.8 mOHM/6 A

VOUT

GND

6

+1.0VS_V CCSTG_IO

5

B