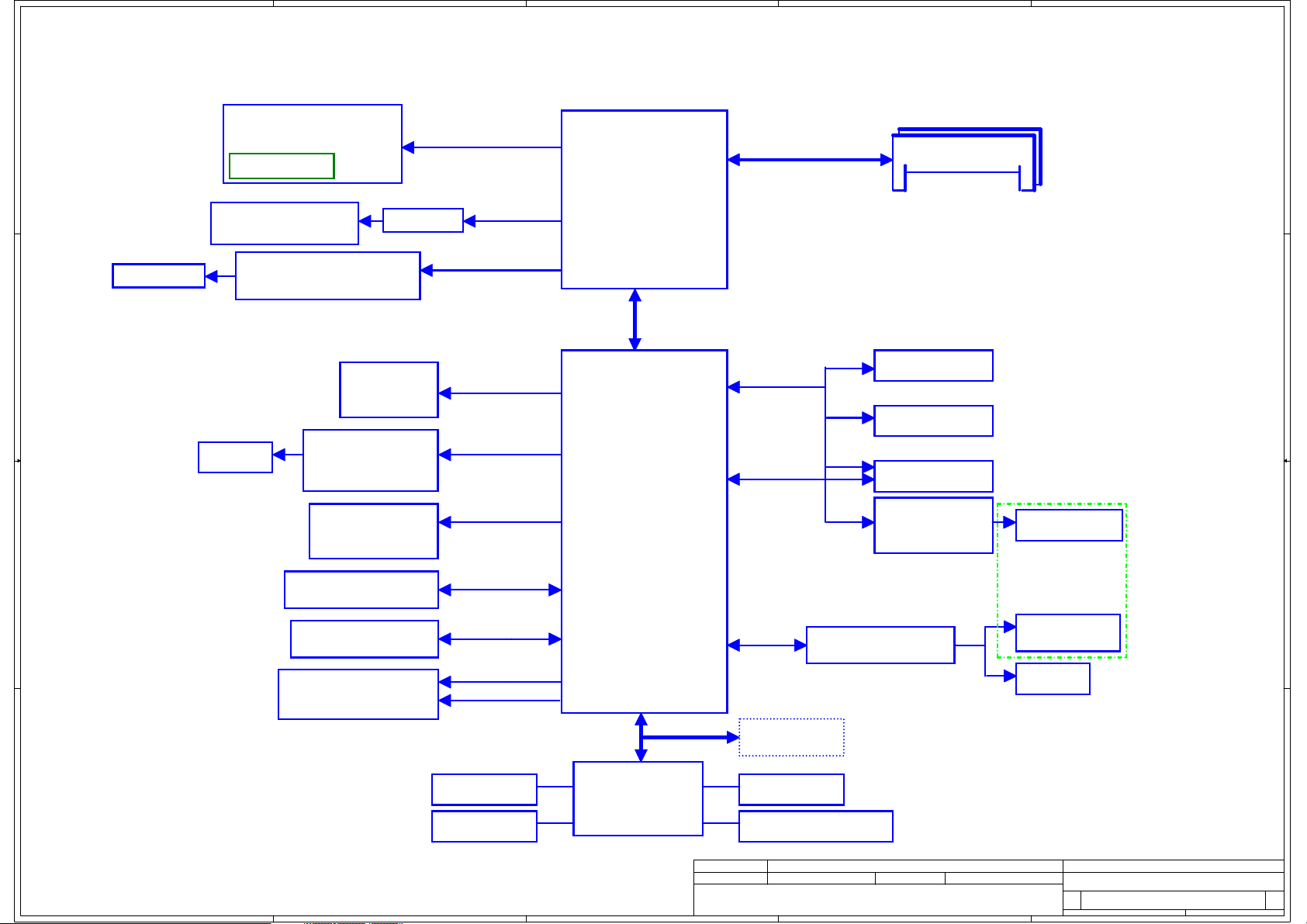

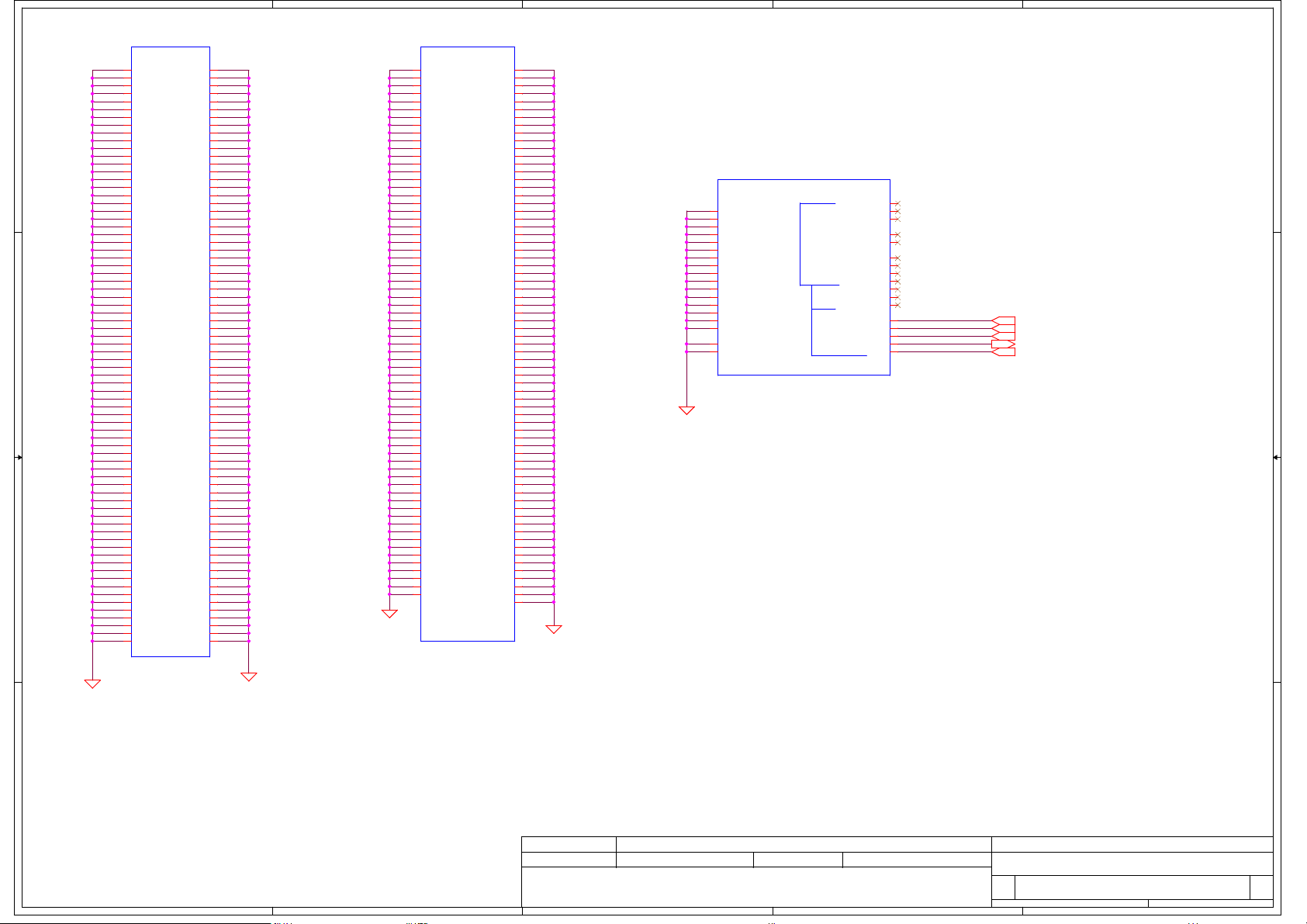

Lenovo ideapad 700-14ISK Schematic

1

A A

2

3

4

5

Compal Confidential

M/B Schematics Document

B B

Intel Skylake-H 4+2 + AMD Tropo XT2

C C

LA-C951P

2015-08-14

REV:1.0

D D

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

For DFT ONLY

1

2

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/08/ 10 2016/12/ 31

2015/08/ 10 2016/12/ 31

2015/08/ 10 2016/12/ 31

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

4

Date : Sheet o f

Compal Electronics, Inc.

Cover Sheet

Cover Sheet

Cover Sheet

LA-C951P

LA-C951P

LA-C951P

1 6 2Friday, August 14, 20 15

1 6 2Friday, August 14, 20 15

1 6 2Friday, August 14, 20 15

5

1.0

1.0

1.0

1

Compal Confidential

Model Name : AIPY6

Project Name : LA-C951P

2

3

4

5

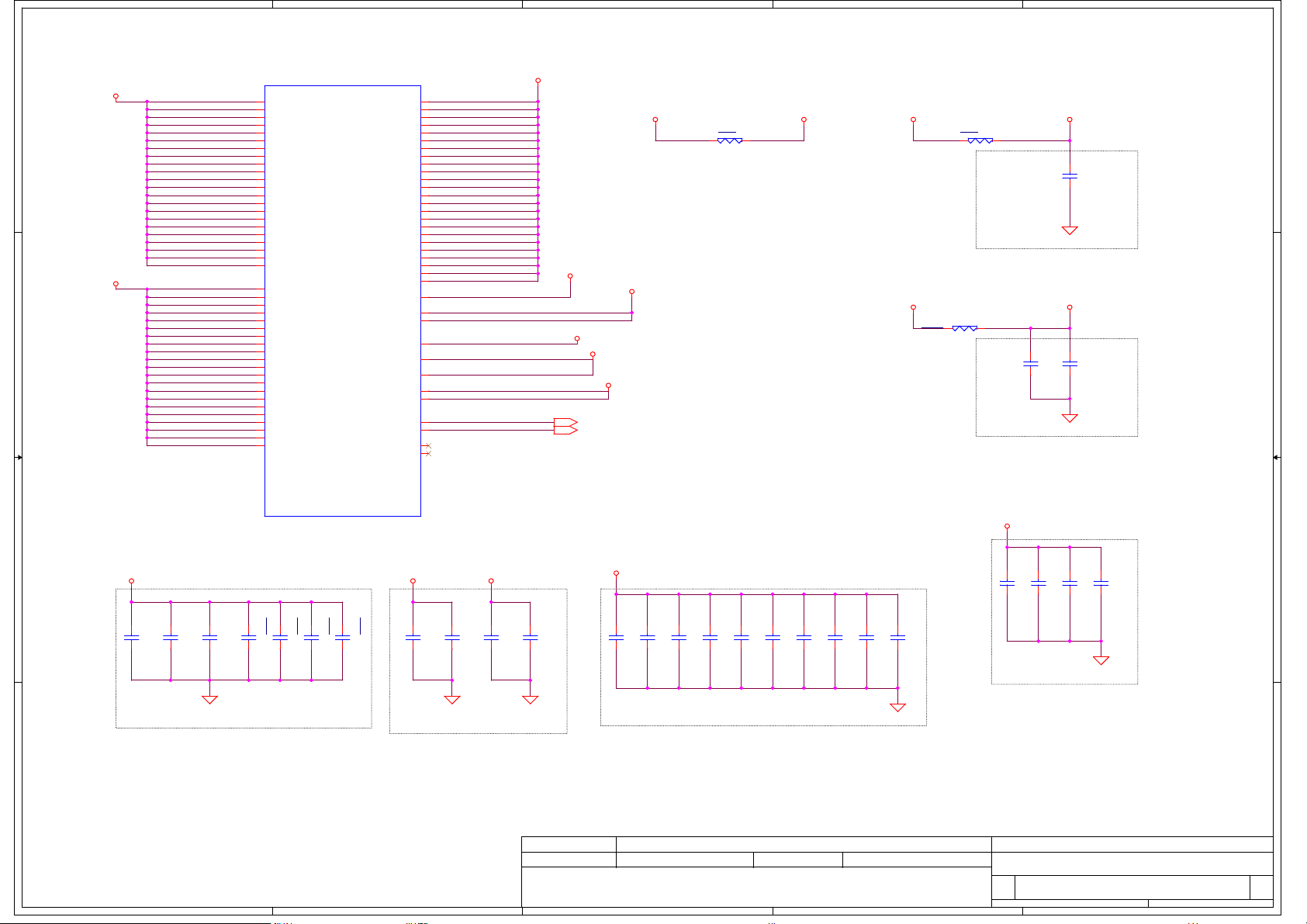

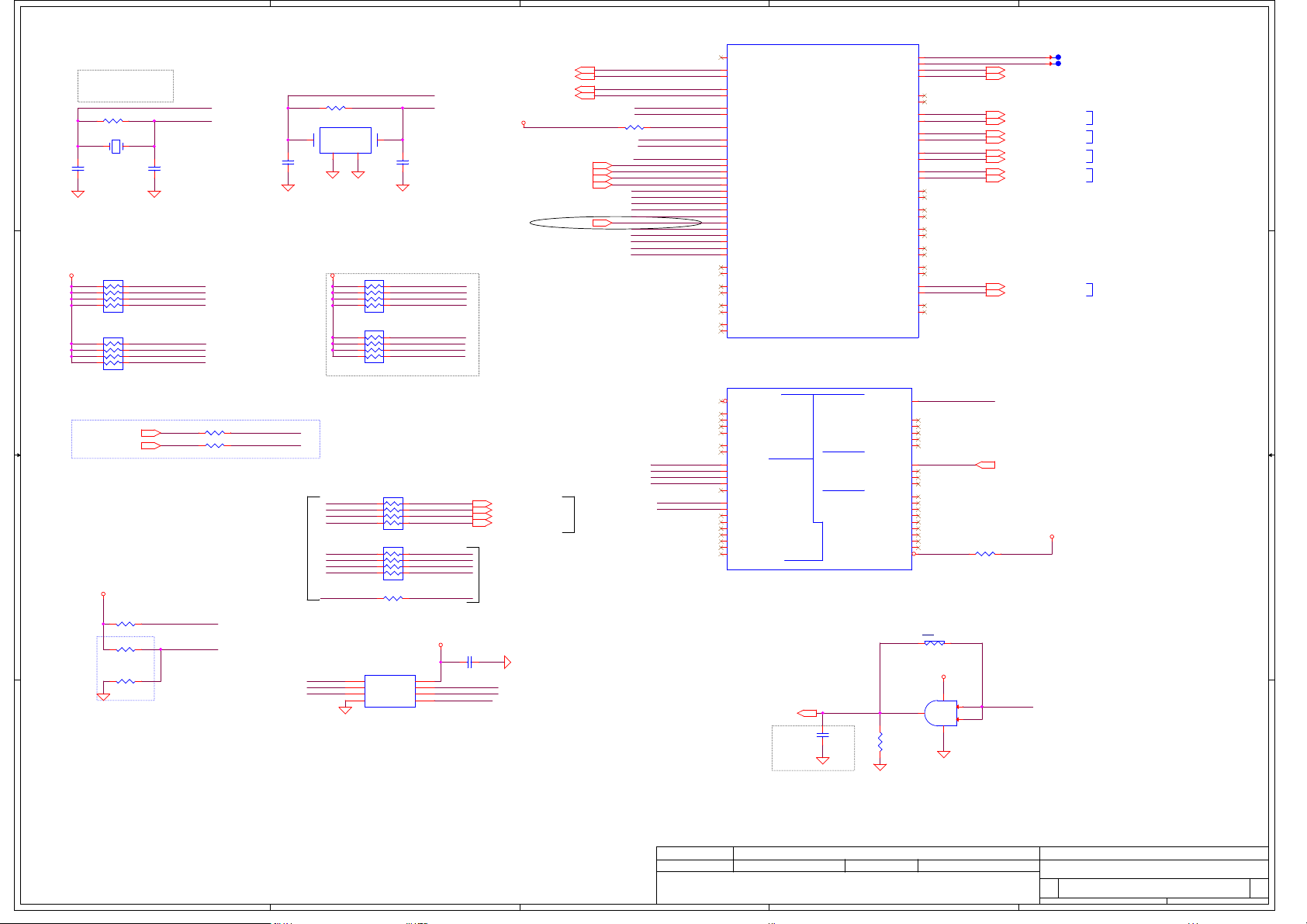

Skylake-H

A A

ATI

Tropo XT2 (R9-M375)

VRAM 256X16, 128X16

gDDR5 x 8

14.0" FHD (1920x1080)

HDMI Conn.

B B

C C

p.32

HDMI level shifter 2.97G

Parade PS8407A

RJ45

p.36

SPI ROM

GD25B64BSIGR

8MB

+VGA_C ORE

+3VS G

+1.8V SG

+1.5V SG

45W DDR4-SO-DIMM X 2

+0.95 VSG

p.22~p .31

IPS/TN

LCD conn

PEG X 8

eDPx1

p.33

DDI x 4 lanes

p.32

NGFF (TYPE E)

2230 Conn.

WLAN/BT4.0

p.34

LAN (10/100/1000GbE)

PCIE x 1

PCIE x 1

Realtek GbE

RTL8111H-CG

Card Reader

p.36

PCIE x 1

Realtek

RTS5249S-GR

p.35

Intel

Processor

Skylake-H

4+2

45W

BGA

42mmX 28mm

DMI x4

Gen3

Intel

Skylake

PCH-H

FCBGA

p.6~p .12

DDR4 2133MHz

1.2V, 2.5V

Dual Channel

USB2.0 x 5

USB3.0 x 2

BT (NGFF)

Camera

USB 3.0 conn x2

USB Charger

TI

TPS2546RTER

p.34

720p HD

p.33

p.43

p.43

p.20~p .21

HM 170

SPI

p.16

23mmX23mm

USB 2.0 conn x1

IO Board

LS-B952P

2.5" SATA HDD

NGFF (TYPE M)

M.2 SATA/PCIE SSD(Gen3)

p.42

p.42

SATA 3.0 x 1

SATA 3.0 x 1

PCIE x 4

p.13~p .19

LPC BUS

Touch Pad CONN.

D D

Thermal Sensor

F75397M

For DFT ONLY

1

2

p.40 p.40

p.40

NPCE388NA0DX

p.38

3

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

HDA

TPM2.0

Z32H320TC

Int. KBDNuvoton

LID switch

Toshiba TCS20DLR

Issued Date

Issued Date

Issued Date

Audio Codec

Realtek ALC3248-CG

p.39

Reser ve

p.41

Compal Secret Data

Compal Secret Data

2015/08/10 2016/12/31

2015/08/10 2016/12/31

2015/08/10 2016/12/31

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4

p.37

Combo Jack

JBL Speaker

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet of

Date: Sheet of

Date: Sheet of

Block Diagram

Block Diagram

Block Diagram

LA-C951P

LA-C951P

LA-C951P

5

1.0

1.0

2 62Friday, August 14, 2015

2 62Friday, August 14, 2015

2 62Friday, August 14, 2015

1.0

A

Funct i on

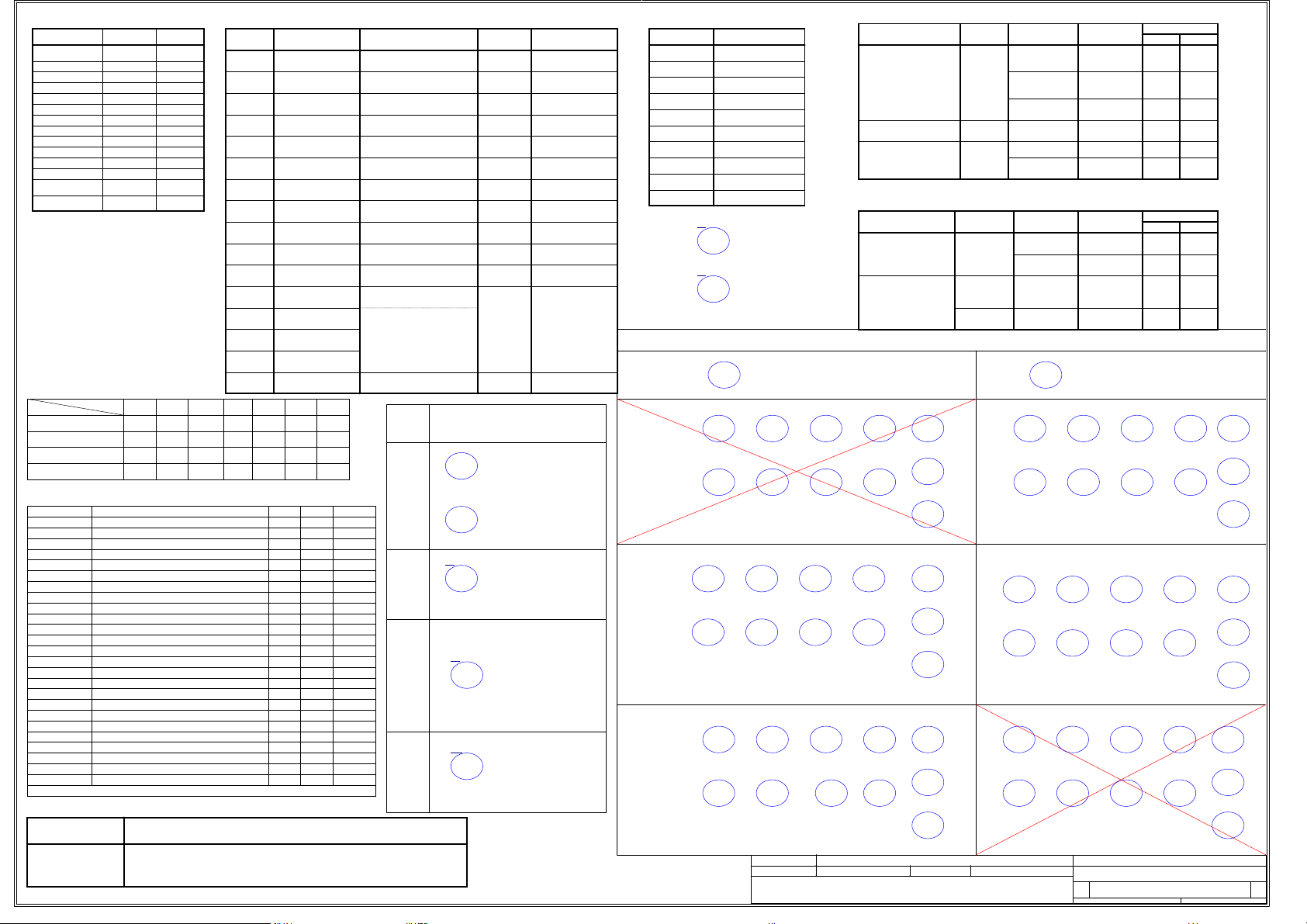

BOM Structure Table

Un-Stuf f

Stuf f

DGPU SKU DIS@

SPI_IO3(MOW36)

2G VRAM

4G VRAM

NC Components

QS@

V2G@

V4G@

CMC

EMI

ESD

RF

ISCT

MPHY_EXT

CPU

KB ID

Power State

STATE

EMI@

ESD@

RF@

NOISCT@

NOEXTMPHY@ EXTMPHY@

CPU5@/CPU6@

NOKBL@/KBL@

SIGNAL

S0 (Full ON)

S3 (Suspend to RAM)

1 1

S4 (Suspend to Disk)

@DIS@

ES@

@

CMC@

TPM@TPM

@EMI@

@ESD@

@RF@

ISCT@

SLP_S4#

SLP_S3#

HIGH HIGH HIGH

HIGH

LOW

LOWLOW

S5 (Sof t OFF)

Voltage Rails

Power Plane Descript i on

VIN

BATT+

+19VB

+VCC_CO RE

+VCC_GT Sliced graphics power rail

+0.6VS_VTT

+1VALW System +1VALW power rail ON*ONON

+1V_PRIM

+VCCIO +1.0VS IO power rail

+VGA_PCIE

+MEM_GFX +1.5VS power rail for GPU

+1VS_VCCST

+1VS_VCCSTG

+3VALW System +3VALW always on power rail

+3VLP +19VB to +3VLP power rail for suspend power

+3VALW_DSW +3VALW power for PCH DSW rails

+3V_LAN

+3VS

+1.8VGS +1.8VS power rail for GPU

+5VALW

+5VS System +5VS power rail

+3VL_RTC RTC power

+VCC_SA System Agent power rail

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF

Adapter power supply

Bat t ery po wer suppl y

AC or bat t ery po wer r ail f or po wer circ uit

Core voltage for CPU

DDR +0.6VS power rail for DDR terminator

System +1VALW power rail ON*

+1.0VS power rail for GPU

DDR-IV +1.2V power rail+1.2V_VDDQ

+1.0V power rail for CPU

+1.0VS power rail for CPU

+3VALW power for LAN power rails

System +3VS power rail

+3VS power rail for GPU+3VGS

System +5VALW power rail

Load BOM Opt i on Tabl e

BOM Number Load BOM Opt i on

4519YS38L09

4519YS38L12

DIS@/QS@/EMI@/ESD@/RF@/NOEXTMPHY@/HM170@ /NOISCT@

DIS@/QS@/EMI@/ESD@/RF@/NOEXTMPHY@/HM170@ /NOISCT@

For DFT ONLY

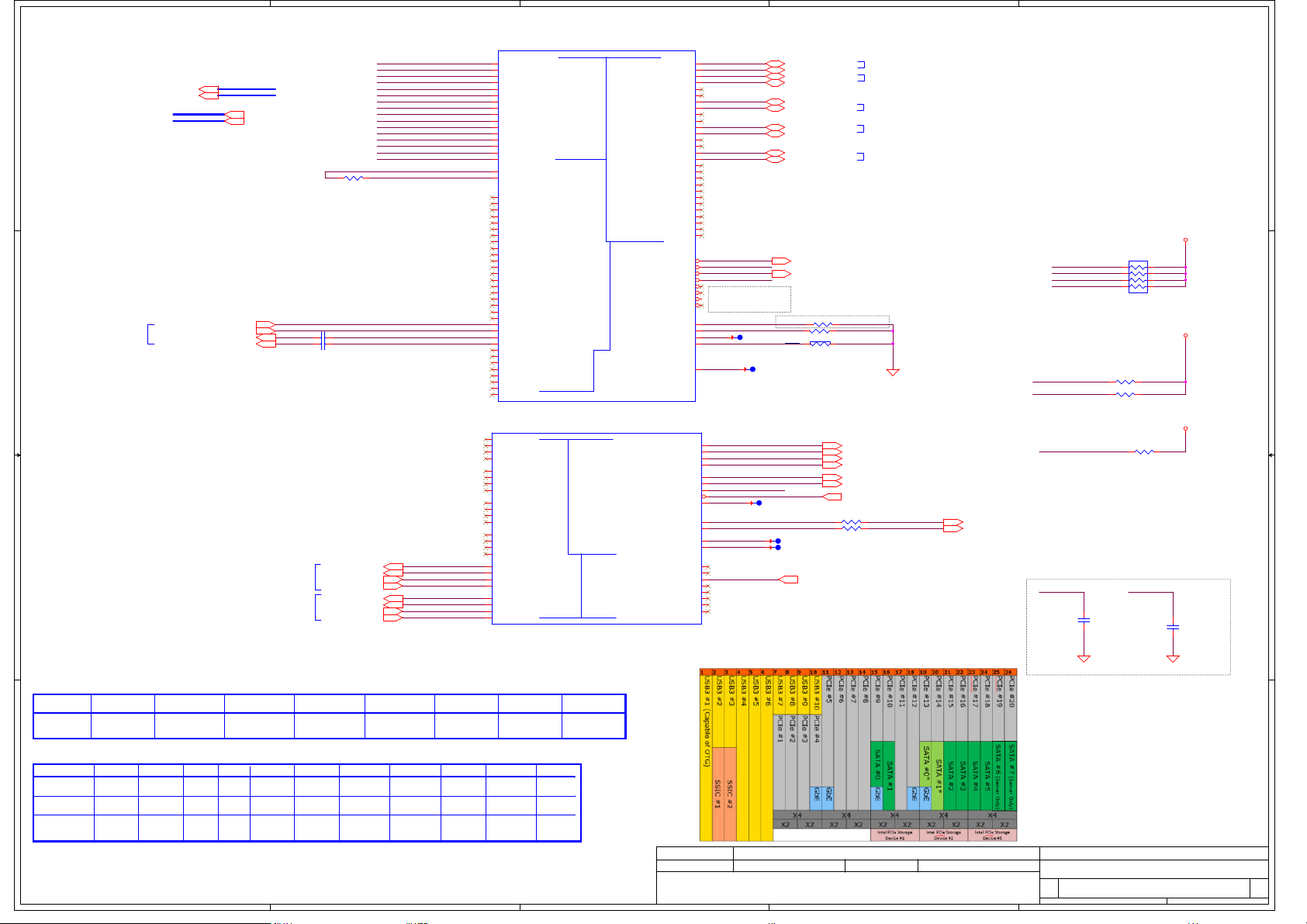

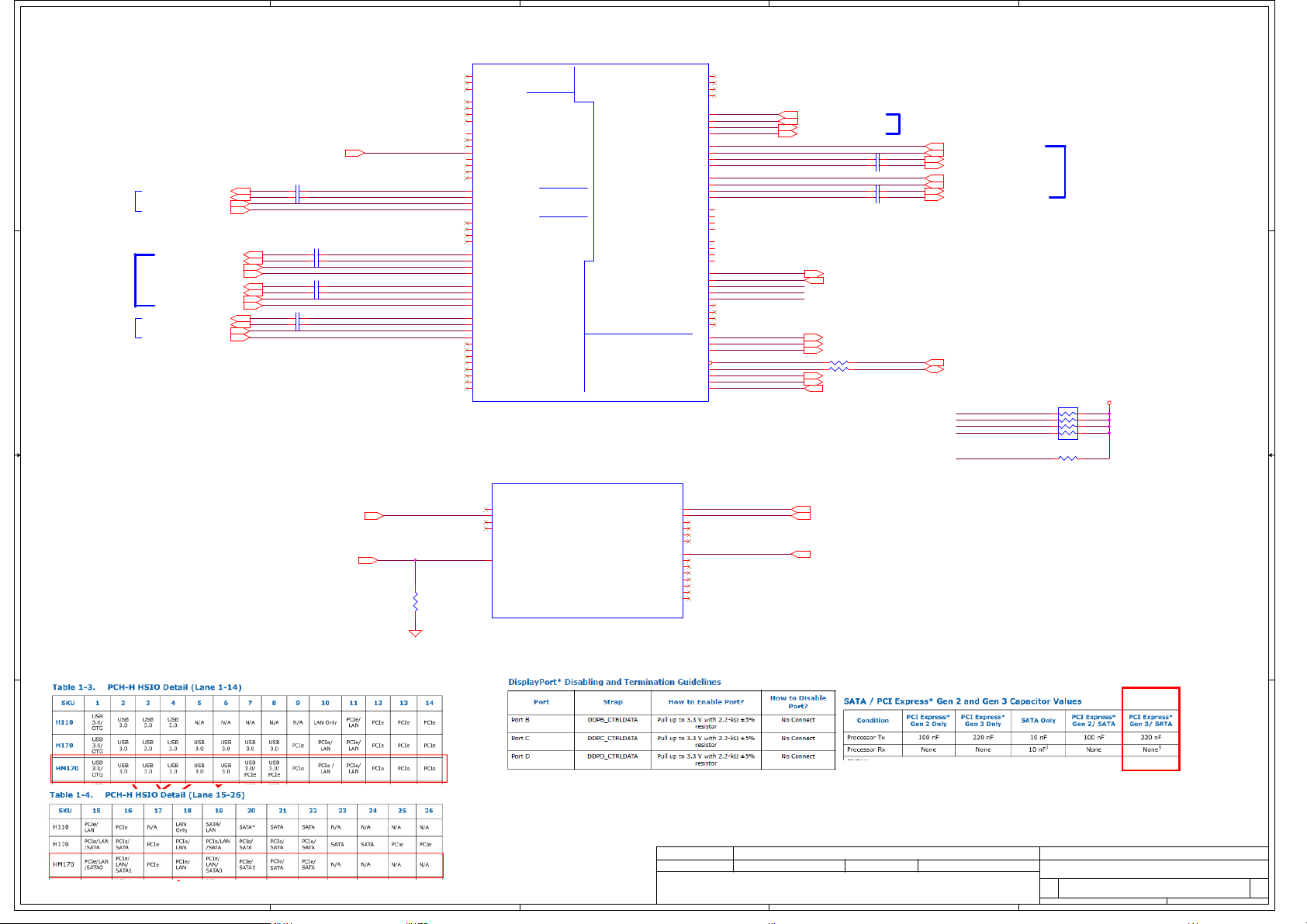

HSIO Port Table

HSIO Port Capable

.... .... .... ....

12 PCI E_6

.... .... .... ....

16 PCI E_10 / SATA_1A HDD_SATA

1718PCIE_11

19

20

21

22

.... .... .... ....

+VALW

SLP_S5#

ON ON ON ON

HIGH

ONONON

HIGH

ON

USB3.0_1 / OTG

1

USB3.0_2 / SSIC_1

2

USB3.0_3 / SSIC_2

3

USB3.0_4

4

5 USB3.0_5 / PCIE_1

PCIE_12

PCIE_13 / SATA_0B

PCIE_14 / SATA_1B

PCIE_15 / SATA_2

PCIE_16 / SATA_3

+VS Clock

+V

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFFLOW LOW LOW

S3

S0

N/A

N/A

N/A

N/A

N/A

N/A

OFF

ON

OFF

ON

OFF

ON

ON

ON

OFF

ON

OFF

ON

OFF

ON

ON

ON

ON

ON

OFF

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

ON

OFF

ON

OFF

ON

ON

ON

OFF

ON

ON

ON

NA

NA

USB3.0 (MB_UP)

USB3.0 (MB_DOWN)

NA

WLAN(NGFF_KEY E)

Card Reader

LAN

S4/S5

N/A

N/A

N/A

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON*

ON

ON*

ON*

OFF

OFF

OFF

ON*

OFF

ON

OFFOFFON

/CPU5@/KBL@

/CPU6@/KBL@

Device PCIE CLK

SSD_SATA

SSD_PCIe x 4

CPU/PCH part

UC1

S IC CL8066202194632 SR2FP R0 2.3G C38!

SA000096Q30

SKL-H

UC1

S IC CL8066202194635 SR2FQ R0 2.6G C38!

SA000095Z50

UH1

PCH-H

S IC GLHM170 SR2C4 D1 BGA 837P PCH C38 !

SA000096J60

UV1

VGA

HDMI

S IC 216-0866000 A1 TROPO XT2 962P C38!

SA00008B310

HDMI

HDMI_ROYALTY

RO0000003HM

ROYALTY HDMI W/LOGO+HDCP

45@

CPU5@

CPU6@

HM170@

DIS@

CLK3

CLK2

CLK1

CLK4

QS-R3

QS-R3

QS-R3

R3

NOTE

Opt i on SSD ty pe

USB2.0 Port Table

USB2.0 Port Devi ce

USB3.0 (MB_UP)

1

2

USB3.0 (MB_DOWN)

NA

3

4

BT (NGFF)

NA

5

6

USB2.0 (IO_Charge Port)

NA

7

8 Camera

NA

9

NA

10

ZZZ

@

PCB 1F6 LA-C951P REV1 M/B 2

DA80013R010

ZZZ

PCB AIPY6 LA-C951P LS-C951P/C952P 02

DAZ1F600100

ZZZ

V2G@

EDW2032BBBG-6A-F-R

UV3

HYN2@

H5TC2G63FFR-11C

UV7

HYN2@

H5TC2G63FFR-11C

SA00006H410

UV3

MIC2@

EDW2032BBBG-6A-F-R

EDW2032BBBG-6A-F-R

Micron_X7663138L01

Samsung_X7663138L02

A

EDW2032BBBG-6A-F-R

UV7

MIC2@

EDW2032BBBG-6A-F-R

SA00007HS10

UV3

SAM2@

K4G20325FD-FC03

UV7

SAM2@

K4G20325FD-FC03

SA000066I10

2G

X7663138L01

UV4

HYN2@

UV5

H5TC2G63FFR-11C

H5TC2G63FFR-11C

UV4

UV8

K4G20325FD-FC03

K4G20325FD-FC03

H5TC2G63FFR-11C

UV8

UV8

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

UV9

HYN2@

H5TC2G63FFR-11C

MIC2@

UV5

EDW2032BBBG-6A-F-R

MIC2@ UV10

UV9

EDW2032BBBG-6A-F-R

SAM2@

UV5

K4G20325FD-FC03

SAM2@

K4G20325FD-FC03

Issued Date

Issued Date

Issued Date

SOC SMBUS Address Table

SOC_SMBUS Net Name

SMBCLK

SMBD ATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

EC SMBUS Address Table

EC_SMBUS Port

SMBUS Port 1

SMBUS Port 2

gDDR5 VRAM * 8

RV6

HYN2@ UV6

HYN2@

MIC2@

EDW2032BBBG-6A-F-R

MIC2@

EDW2032BBBG-6A-F-R

SAM2@

UV9

SAM2@

HYN2@

H5TC2G63FFR-11C

UV10

HYN2@

H5TC2G63FFR-11C

UV6

MIC2@

MIC2@

UV6

SAM2@

K4G20325FD-FC03

UV10

SAM2@

K4G20325FD-FC03

2015/08/10 2016/12/31

2015/08/10 2016/12/31

2015/08/10 2016/12/31

HYN2@

10K_0402_5%

RV8

HYN2@

10K_0402_5%

RV10

HYN2@

10K_0402_5%

RV6

MIC2@

10K_0402_5%

RV8

MIC2@

10K_0402_5%

RV9

MIC2@

10K_0402_5%

RV6

SAM2@

10K_0402_5%

RV7

SAM2@

10K_0402_5%

RV10

SAM2@

10K_0402_5%

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Power R ail

+3VS

+3VS

+3VS

Power R ail Device Address (7 bit)

+3VLP

+3VLP TP (reserve) TBC TBCTBC

+3VLP

(TBC)

Device

DIMM1

DIMM2

TP TBC TBC TBC

EC

Thermal sensor

Address (7 bit)

TBC

TBC

TBC TBC

TBC

1001100

(TBC)

BAT

CHGR TBC TBC

Thermal sensor

ZZZ

V4G@

EDW4032BABG-50-F

UV3

HYN4@ UV6

H5GC4H24AJR-T2C

UV7

HYN4@

H5GC4H24AJR-T2C

SA000085V40

1001100

UV4

HYN4@

H5GC4H24AJR-T2C

UV8

HYN4@

H5GC4H24AJR-T2C

TBC

TBC

Hynix_X7663138L04Hynix_X76xxx38Lxx

UV3

MIC4@

UV4

MIC4@

EDW4032BABG-50-F

UV7

MIC4@

EDW4032BABG-50-F

SA00008VF10

EDW4032BABG-50-F

EDW4032BABG-50-F

UV8

EDW4032BABG-50-F

MIC4@

EDW4032BABG-50-F

Micron_X7663138L03

UV4

UV3

SAM4@

K4W4G1646E-BC1A

UV7

SAM4@

K4W4G1646E-BC1A

SA000076P10

SAM4@

K4W4G1646E-BC1A

UV8

SAM4@ UV9

K4W4G1646E-BC1A

K4W4G1646E-BC1A

K4W4G1646E-BC1A

Samsung_X76xxx38Lxx

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

LA-C951P

LA-C951P

LA-C951P

Date : Sheet of

Date : Sheet of

Date : Sheet of

Address (8bit)

Write Read

TBC

TBC

TBC

TBC TBC

Address (8bit)

Write Read

TBC TBC

TBC

4G

X7663138L03

UV5

HYN4@

H5GC4H24AJR-T2C

UV9

HYN4@

H5GC4H24AJR-T2C

UV5

MIC4@

EDW4032BABG-50-F

UV9

MIC4@

EDW4032BABG-50-F

UV5

SAM4@

K4W4G1646E-BC1A

SAM4@

K4W4G1646E-BC1A

0xA0

0xA4

TBCTBC

TBC

HYN4@

H5GC4H24AJR-T2C

UV10

HYN4@

H5GC4H24AJR-T2C

UV6

MIC4@

UV10

MIC4@

UV6

SAM4@UV4

UV10

SAM4@

RV6

10K_0402_5%

RV7

10K_0402_5%

RV9

10K_0402_5%

RV5

10K_0402_5%

RV8

10K_0402_5%

RV10

10K_0402_5%

RV5

10K_0402_5%

RV7

10K_0402_5%

RV10

10K_0402_5%

3 62Friday, August 14, 2015

3 62Friday, August 14, 2015

3 62Friday, August 14, 2015

SAM4@

SAM4@

SAM4@

HYN4@

HYN4@

HYN4@

MIC4@

MIC4@

MIC4@

1.0

1.0

1.0

5

D D

C C

4

3

2

1

B B

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

For DFT ONLY

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

2015/08/10 2016/12/31

2015/08/10 2016/12/31

2015/08/10 2016/12/31

4

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Document Number Re v

Size

Document Number Re v

Size

Document Number Re v

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

3

Date: Sheet of

2

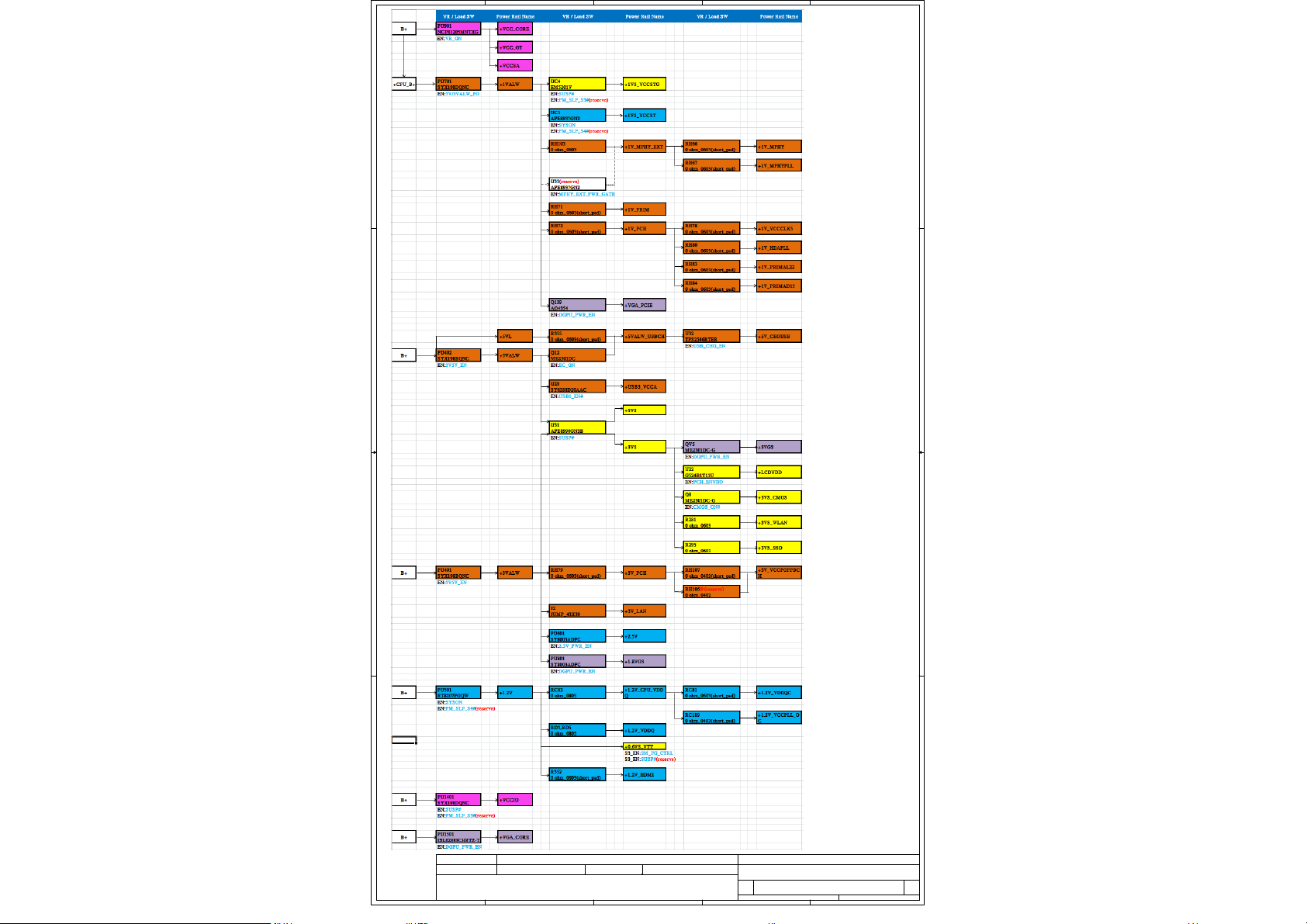

Power map

Power map

Power map

LA-C951P

LA-C951P

LA-C951P

1.0

1.0

1.0

4 62Friday, August 14, 2015

4 62Friday, August 14, 2015

4 62Friday, August 14, 2015

1

5

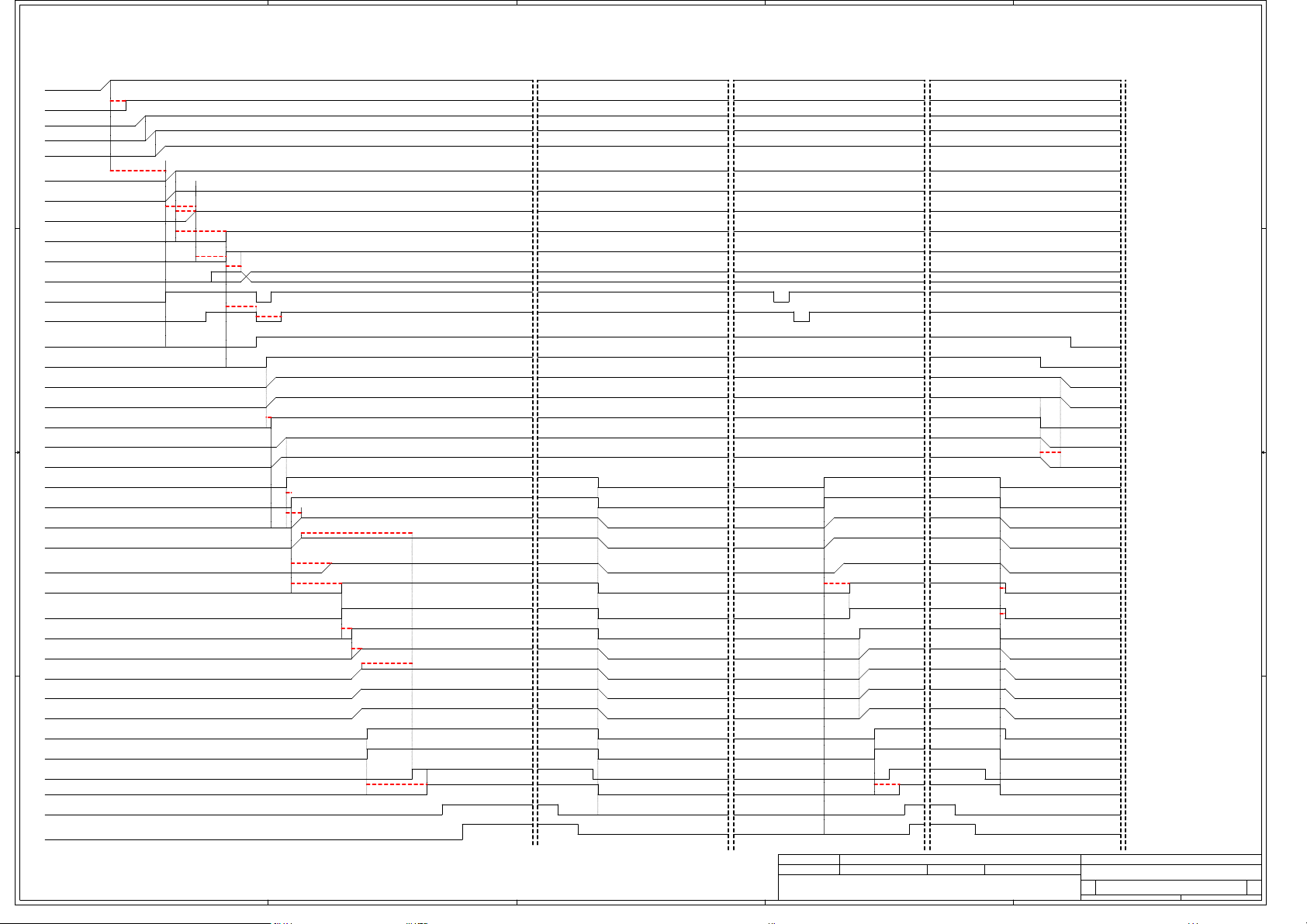

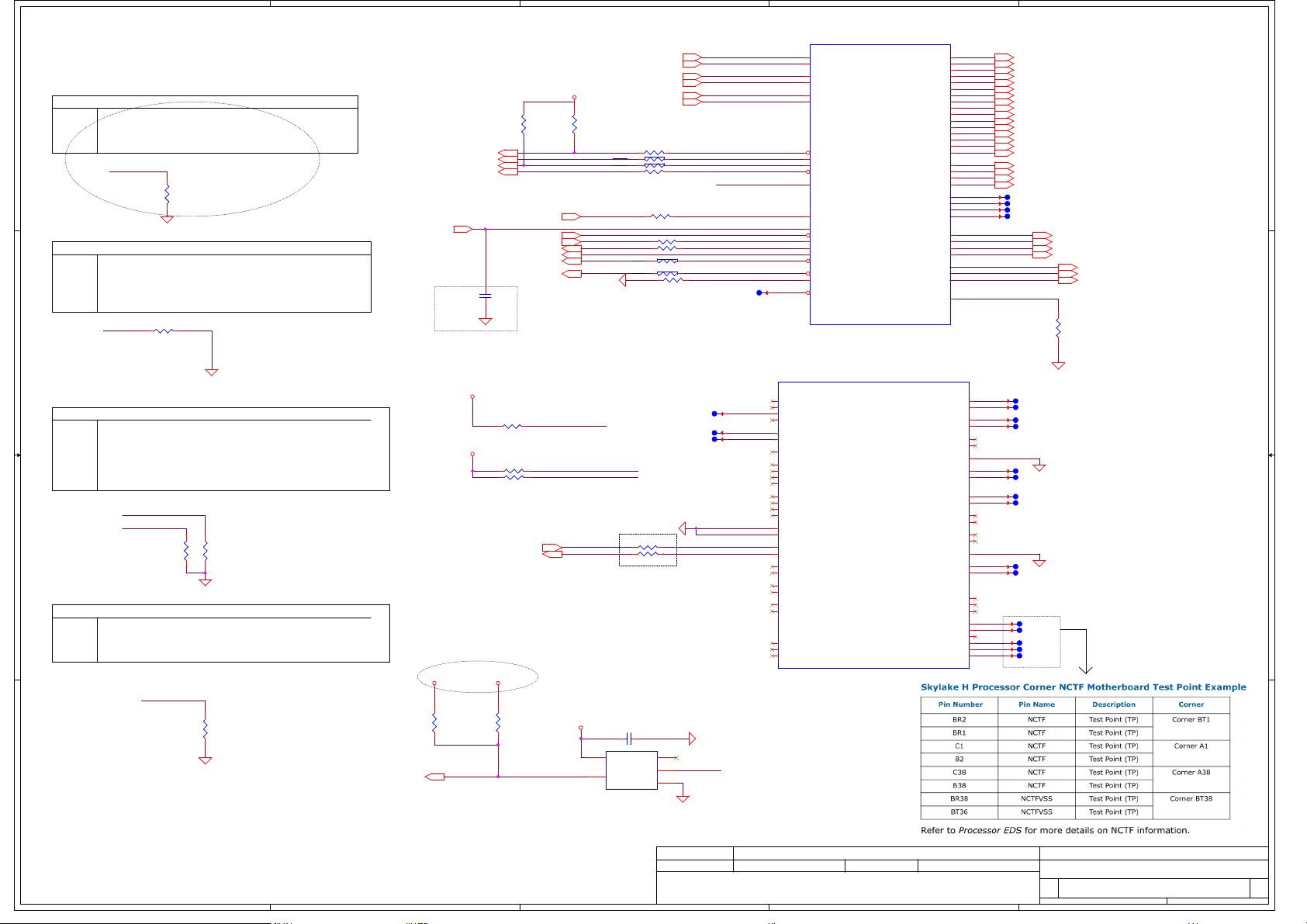

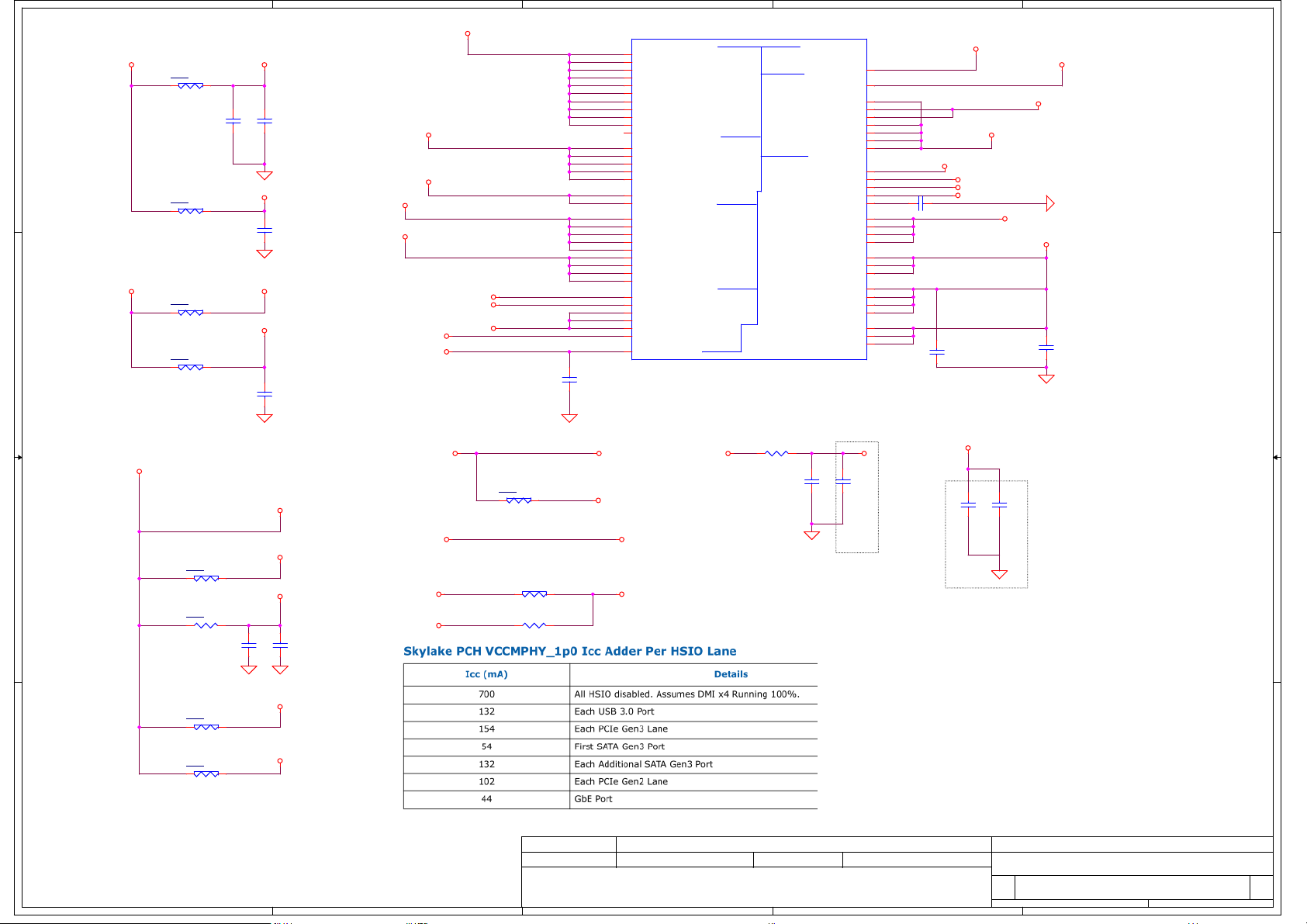

[AIPY6-PWR Sequence_SKL-H 4+2_DDR4]

4

3

2

1

G3->S0 S0->S3 ->S0

+3VL_RTC

RTCRST#

D D

+19VB

+3VLP/+5V LP

EC_ON (PIN112)

+5VALW/+ 3VALW

+3VALW_DSW

SUSACK#

+1V_PRIM

DSW_PWROK

EC_RSMRST# (PIN100)

AC_PRESENT (PIN74)

ON/OFF#

PBTN_OUT# (PIN122)

PM_SLP_S5#

C C

PM_SLP_S4#

2.5V_PWR_EN (PIN15) 2.5V_PWR_EN (PIN66)

+2.5V(VPP) +2.5V(VPP)

SYSON (PIN95)

+1.0V_VCCST/+1.0V_VCCSFR

+1.2V_VDDQ/+1.2V_VCCPLL_OC

PM_SLP_S3#

SUSP# (PIN116)

+1VS_VCCSTG

+VCCIO

+5VS/+3V S

B B

H_VCCST_PWRGD (PIN21)

VR_ON (PIN108)

SM_PG_CTRL

+0.6VS_VTT

+VCC_SA

+VCC_C ORE

+VCC_GT

VGATE

(PIN107)

PCH_PWROK (PIN32)

H_CPUPWRGD

SYS_PWROK (PIN98)

A A

SUS_STAT#

PLTRST#

(PIN13)

(PIN123)

(PIN106)

tPCH01_Min : 9 ms

tPCH04_Min : 9 ms

tPCH34_Max : 20 ms

tPCH06_Min : 200 us

tPCH02_Min : 10 ms

tPCH03_Min : 10 ms (VccPrimary stable to RSMRST# high)

tPLT02_Min : 0 ms Max : 90 ms

tPCH43_Min : 95 ms

Minimum duration of PWRBTN# assertion = 16mS. PWRBTN# can assert before or after RSMRST#

T = 30msec

T = 40msec

tCPU04 Min : 100 ns

tCPU10 Min : 1 ms

T <=10msec

T = 20msec

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

tCPU09 Min : 1 ms

T = 100msec

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

For DFT ONLY

5

4

3

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

T = 20msec

T = 100msec

Compal Secret Data

Compal Secret Data

2015/08/10 2016/12/31

2015/08/10 2016/12/31

2015/08/10 2016/12/31

Compal Secret Data

2

Deciphered Date

Deciphered Date

Deciphered Date

S0->S5S3

+3VL_RTC

SOC_RTCRST#

+19VB

+3VLP/+5V LP

EC_ON

+5VALW/+ 3VALW

+3VALW_DSW

SUSACK#

+1.0V_PRIM

DSW_PWROK

EC_RSMRST#

AC_PRESE NT

ON/OFF

PBTN_OUT#

PM_SLP_S5#

PM_SLP_S4#

SYSON (PIN95)

+1V_VCCST/+1V_VCCSFR

+1.2V_VDDQ/+1.2V_VCCPLL_OC

PM_SLP_S3#

SUSP#

+1VS_VCCSTG

+VCCIO

+5VS/+3V S

H_VCCST_PG (PIN107)

VR_ON (PIN70)

SM_PG_CTRL

+0.6VS_VTT

+VCC_SA

+VCC_C ORE

+VCC_GT

VGATE

PCH_PWROK

H_CPUPWRGD

SYS_PWROK (PIN98)

SUS_STAT#

SOC_PLTRST#

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Power Sequence

Power Sequence

Power Sequence

Document Number Re v

Document Number Re v

Document Number Re v

1

5 62Friday, August 14, 2015

5 62Friday, August 14, 2015

5 62Friday, August 14, 2015

1.0

1.0

1.0

tCPU28< 1us

tPLT17< 1us

tPLT16_Min : 30 ms

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

D D

+VCCIO

C C

RC7 24.9_0402_1%

Note :

Trace width=12 mils ,Spacing=15mils

Max length= 400 mils.

1 2

PEG_RCOMP

DMI_CRX_PTX_P[0..3]<13>

DMI_CRX_PTX_N[0..3]<13>

4

PEG_CRX_GTX_P[0..7]<22> PEG_CTX_C_GRX_P [0..7] <22>

PEG_CRX_GTX_N[0..7]<22> PEG_CTX_C_GRX_N[0..7] <22>

UC1C

@

E25

PEG_RXP[0]

D25

PEG_RXN[0]

E24

PEG_RXP[1]

F24

PEG_RXN[1]

E23

PEG_RXP[2]

D23

PEG_RXN[2]

E22

PEG_RXP[3]

F22

PEG_RXN[3]

E21

PEG_RXP[4]

D21

PEG_RXN[4]

E20

PEG_RXP[5]

F20

PEG_RXN[5]

E19

PEG_RXP[6]

D19

PEG_RXN[6]

E18

Reverse

PEG_CRX_GTX_P7

PEG_CRX_GTX_N7

PEG_CRX_GTX_P6

PEG_CRX_GTX_N6

PEG_CRX_GTX_P5

PEG_CRX_GTX_N5

PEG_CRX_GTX_P4

PEG_CRX_GTX_N4

PEG_CRX_GTX_P3

PEG_CRX_GTX_N3

PEG_CRX_GTX_P2

PEG_CRX_GTX_N2

PEG_CRX_GTX_P1

PEG_CRX_GTX_N1

PEG_CRX_GTX_P0

PEG_CRX_GTX_N0

PEG_RCOMP

DMI_CRX_PTX_P0

DMI_CRX_PTX_N0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_N2

DMI_CRX_PTX_P3 DM I_CTX_PRX_P3

DMI_CRX_PTX_N3 DMI_CTX_PRX_N3

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

D11

E11

F10

E10

G2

D8

E8

E6

F6

D5

E5

J8

J9

SKL-H_BGA1440

PEG_RXP[7]

PEG_RXN[7]

PEG_RXP[8]

PEG_RXN[8]

PEG_RXP[9]

PEG_RXN[9]

PEG_RXP[10]

PEG_RXN[10]

PEG_RXP[11]

PEG_RXN[11]

PEG_RXP[12]

PEG_RXN[12]

PEG_RXP[13]

PEG_RXN[13]

PEG_RXP[14]

PEG_RXN[14]

PEG_RXP[15]

PEG_RXN[15]

PEG_RCOMP

DMI_RXP[0]

DMI_RXN[0]

DMI_RXP[1]

DMI_RXN[1]

DMI_RXP[2]

DMI_RXN[2]

DMI_RXP[3]

DMI_RXN[3]

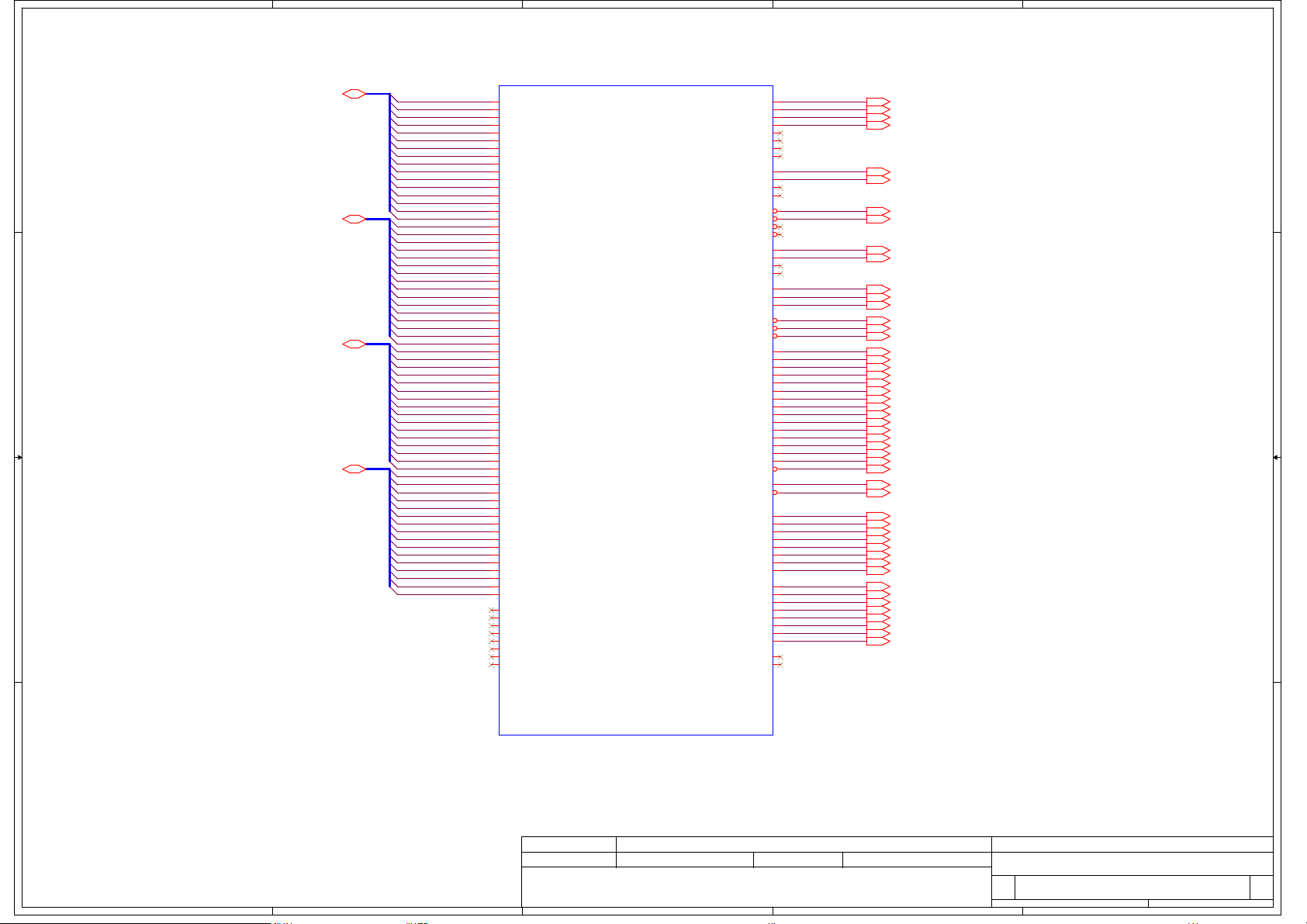

SKYLAKE_HALO

BGA1440

3 OF 14

3

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

B25

A25

B24

C24

B23

A23

B22

C22

B21

A21

B20

C20

B19

A19

B18

C18

PEG_CTX_GRX_P7 PEG_CTX_C_GRX_P 7

A17

B17

C16

PEG_CTX_GRX_N6

B16

PEG_CTX_GRX_P5

A15

PEG_CTX_GRX_N5

B15

PEG_CTX_GRX_P4

C14

PEG_CTX_GRX_N4

B14

PEG_CTX_GRX_P3 PEG_CTX_C_GRX_P 3

A13

B13

C12

PEG_CTX_GRX_N2

B12

PEG_CTX_GRX_P1 PEG_CTX_C_GRX_P 1

A11

PEG_CTX_GRX_N1

B11

PEG_CTX_GRX_P0 PEG_CTX_C_GRX_P 0

C10

B10

DMI_CTX_PRX_P0

B8

DMI_CTX_PRX_N0

A8

DMI_CTX_PRX_P1

C6

DMI_CTX_PRX_N1DMI_CRX_PTX_N1

B6

DMI_CTX_PRX_P2

B5

DMI_CTX_PRX_N2

A5

D4

B4

Reverse

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

CC30.22U_0402 _10V6K DIS@

CC40.22U_0402 _10V6K DIS@

CC50.22U_0402 _10V6K DIS@

CC60.22U_0402 _10V6K DIS@

CC70.22U_0402 _10V6K DIS@

CC80.22U_0402 _10V6K DIS@

CC90.22U_0402 _10V6K DIS@

CC100.22U_0402 _10V6K DIS@

CC120.22U_0402 _10V6K DIS@

CC130.22U_0402 _10V6K DIS@

CC150.22U_0402 _10V6K DIS@

CC140.22U_0402 _10V6K DIS@

CC160.22U_0402 _10V6K DIS@

CC170.22U_0402 _10V6K DIS@

CC180.22U_0402 _10V6K DIS@

CC200.22U_0402 _10V6K DIS@

DMI_CTX_PRX_P[0..3] <13>

DMI_CTX_PRX_N[0..3] <13>

2

PEG_CTX_C_GRX_N 7PEG_CTX_GRX_N7

PEG_CTX_C_GRX_P 6PEG_CTX_GR X_P6

PEG_CTX_C_GRX_N 6

PEG_CTX_C_GRX_P 5

PEG_CTX_C_GRX_N 5

PEG_CTX_C_GRX_P 4

PEG_CTX_C_GRX_N 4

PEG_CTX_C_GRX_N 3PEG_CTX_GRX_N3

PEG_CTX_C_GRX_P 2PEG_CTX_GR X_P2

PEG_CTX_C_GRX_N 2

PEG_CTX_C_GRX_N 1

PEG_CTX_C_GRX_N 0PEG_CTX_GRX_N0

1

B B

TMDS_B_DATA2_ C

12

TMDS_B_DATA2<32>

TMDS_B_DATA2#<32>

TMDS_B_DATA1<32>

TMDS_B_DATA1#<32>

TMDS_B_DATA0<32>

HDMI

A A

TMDS_B_DATA0#<32>

TMDS_B_CL K<32>

TMDS_B_CL K#<32>

12

12

12

12

12

12

12

C2300.1U_0201_ 10V6K

C2310.1U_0201_ 10V6K

C2320.1U_0201_ 10V6K

C2330.1U_0201_ 10V6K

C2340.1U_0201_ 10V6K

C2350.1U_0201_ 10V6K

C2360.1U_0201_ 10V6K

C2370.1U_0201_ 10V6K

TMDS_B_DATA2# _C

TMDS_B_DATA1_ C

TMDS_B_DATA1# _C

TMDS_B_DATA0_ C

TMDS_B_DATA0# _C

TMDS_B_CL K_C

TMDS_B_CL K#_C

K36

K37

J35

J34

H37

H36

J37

J38

D27

E27

H34

H33

F37

G38

F34

F35

E37

E36

F26

E26

C34

D34

B36

B34

F33

E33

C33

B33

A27

B27

For DFT ONLY

5

4

UC1D

@

DDI1_TXP[0]

DDI1_TXN[0]

DDI1_TXP[1]

DDI1_TXN[1]

DDI1_TXP[2]

DDI1_TXN[2]

DDI1_TXP[3]

DDI1_TXN[3]

DDI1_AUXP

DDI1_AUXN

DDI2_TXP[0]

DDI2_TXN[0]

DDI2_TXP[1]

DDI2_TXN[1]

DDI2_TXP[2]

DDI2_TXN[2]

DDI2_TXP[3]

DDI2_TXN[3]

DDI2_AUXP

DDI2_AUXN

DDI3_TXP[0]

DDI3_TXN[0]

DDI3_TXP[1]

DDI3_TXN[1]

DDI3_TXP[2]

DDI3_TXN[2]

DDI3_TXP[3]

DDI3_TXN[3]

DDI3_AUXP

DDI3_AUXN

SKL-H_BGA1440

SKYLAKE_HALO

BGA1440

4 OF 14

D29

EDP_TXP[0]

E29

EDP_TXN[0]

F28

EDP_TXP[1]

E28

EDP_TXN[1]

B29

EDP_TXN[2]

A29

EDP_TXP[2]

B28

EDP_TXN[3]

C28

EDP_TXP[3]

C26

EDP_AUXP

B26

EDP_AUXN

CPU_INV_PWM

EDP_DISP_UTIL

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

3

A33

EDP_COMP

D37

EDP_RCOMP

G27

G25

CPU_DISPA_SDI

G29

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

EDP_TXP0 <33>

EDP_TXN0 <33>

EDP_TXP1 <33>

EDP_TXN1 <33>

EDP_AUXP < 33>

EDP_AUXN <33>

@

T215

EDP_COMP

Note :

Trace width=20 mils ,Spacing=25mils

Max length= 100 mils.

CPU_DISPA_BCLK_R <15>

RC25 20_0402_1 %

12

2015/08/10 2016/12/31

2015/08/10 2016/12/31

2015/08/10 2016/12/31

CPU_DISPA_SDO_R <15>

CPU_DISPA_SDI_R <15>

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+VCCIO

12

RC824.9_0402_1%

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Re v

Size Document N umber R ev

Size Document N umber R ev

Custom

Custom

Custom

Date : Sh eet o f

Date : Sh eet o f

Date : Sh eet o f

Compal Electronics, Inc.

DMI,PEG,DDI,EDP

DMI,PEG,DDI,EDP

DMI,PEG,DDI,EDP

LA-C951P

LA-C951P

LA-C951P

1

6 62Friday, August 14, 2015

6 62Friday, August 14, 2015

6 62Friday, August 14, 2015

1.0

1.0

1.0

5

4

3

2

1

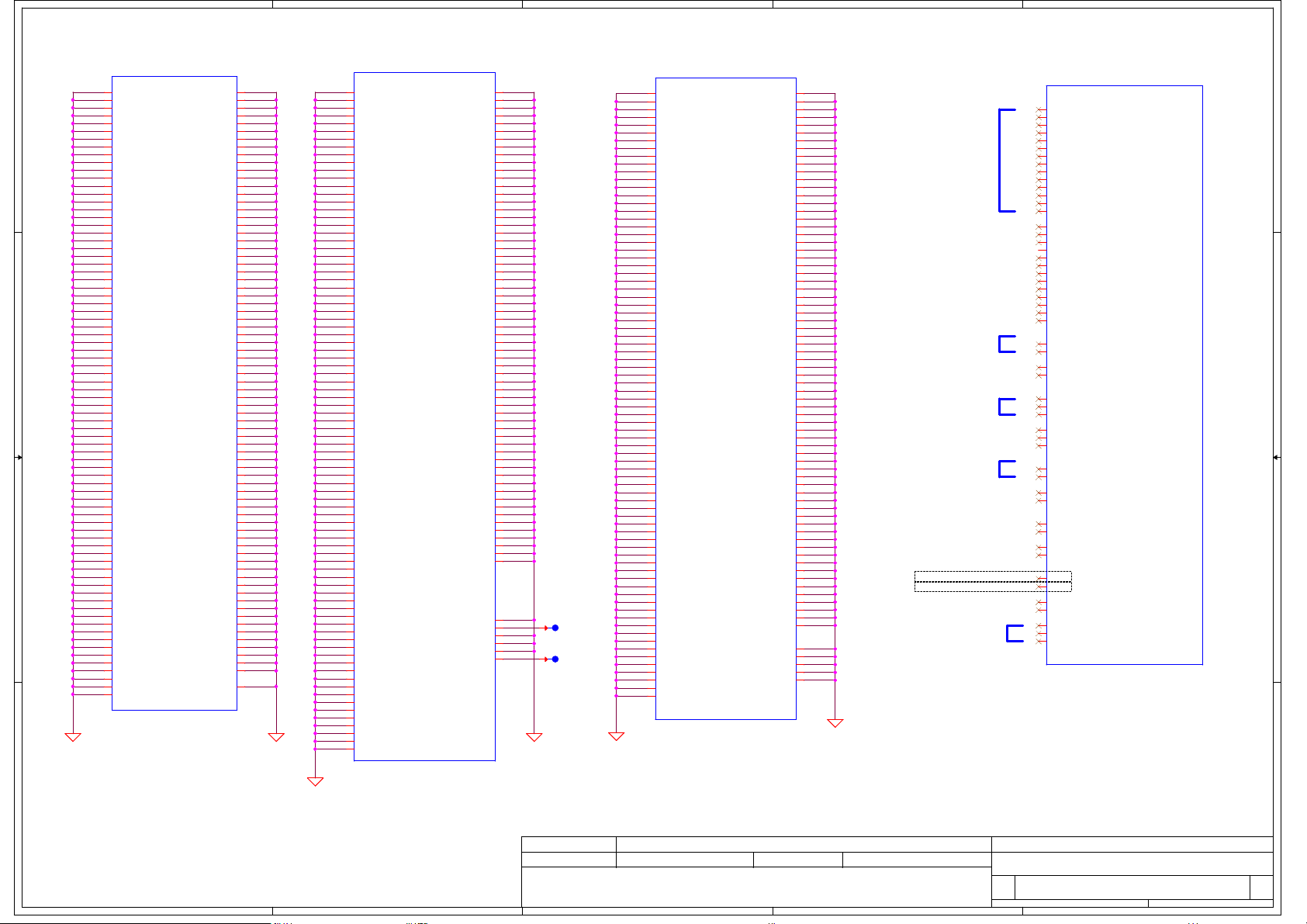

UC1A

DDR_A_D [0..15]<20>

D D

DDR_A_D [16..31]<20>

C C

B B

DDR_A_D [32..47]<20>

DDR_A_D [48..63]<20>

DDR_A_D 0

DDR_A_D 1

DDR_A_D 2

DDR_A_D 3

DDR_A_D 4

DDR_A_D 5

DDR_A_D 6

DDR_A_D 7

DDR_A_D 8

DDR_A_D 9

DDR_A_D 10

DDR_A_D 11

DDR_A_D 12

DDR_A_D 13

DDR_A_D 14

DDR_A_D 15

DDR_A_D 16

DDR_A_D 17

DDR_A_D 18

DDR_A_D 19

DDR_A_D 20

DDR_A_D 21

DDR_A_D 22

DDR_A_D 23

DDR_A_D 24

DDR_A_D 25

DDR_A_D 26

DDR_A_D 27

DDR_A_D 28

DDR_A_D 29

DDR_A_D 30

DDR_A_D 31

DDR_A_D 32

DDR_A_D 33

DDR_A_D 34

DDR_A_D 35

DDR_A_D 36

DDR_A_D 37

DDR_A_D 38

DDR_A_D 39

DDR_A_D 40

DDR_A_D 41

DDR_A_D 42

DDR_A_D 43

DDR_A_D 44

DDR_A_D 45

DDR_A_D 46

DDR_A_D 47

DDR_A_D 48

DDR_A_D 49

DDR_A_D 50

DDR_A_D 51

DDR_A_D 52

DDR_A_D 53

DDR_A_D 54

DDR_A_D 55

DDR_A_D 56

DDR_A_D 57

DDR_A_D 58

DDR_A_D 59

DDR_A_D 60

DDR_A_D 61

DDR_A_D 62

DDR_A_D 63

BR6

BT6

BP3

BR3

BN5

BP6

BP2

BN3

BL4

BL5

BL2

BM1

BK4

BK5

BK1

BK2

BG4

BG5

BF4

BF5

BG2

BG1

BF1

BF2

BD2

BD1

BC4

BC5

BD5

BD4

BC1

BC2

AB1

AB2

AA4

AA5

AB5

AB4

AA2

AA1

BA2

BA1

AY4

AY5

BA5

BA4

AY1

AY2

M4

M1

M5

M2

@

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[16]/DDR0_DQ[32]

DDR0_DQ[17]/DDR0_DQ[33]

DDR0_DQ[18]/DDR0_DQ[34]

DDR0_DQ[19]/DDR0_DQ[35]

DDR0_DQ[20]/DDR0_DQ[36]

DDR0_DQ[21]/DDR0_DQ[37]

DDR0_DQ[22]/DDR0_DQ[38]

DDR0_DQ[23]/DDR0_DQ[39]

DDR0_DQ[24]/DDR0_DQ[40]

DDR0_DQ[25]/DDR0_DQ[41]

DDR0_DQ[26]/DDR0_DQ[42]

DDR0_DQ[27]/DDR0_DQ[43]

DDR0_DQ[28]/DDR0_DQ[44]

DDR0_DQ[29]/DDR0_DQ[45]

DDR0_DQ[30]/DDR0_DQ[46]

DDR0_DQ[31]/DDR0_DQ[47]

DDR0_DQ[32]/DDR1_DQ[0]

DDR0_DQ[33]/DDR1_DQ[1]

DDR0_DQ[34]/DDR1_DQ[2]

DDR0_DQ[35]/DDR1_DQ[3]

DDR0_DQ[36]/DDR1_DQ[4]

DDR0_DQ[37]/DDR1_DQ[5]

DDR0_DQ[38]/DDR1_DQ[6]

DDR0_DQ[39]/DDR1_DQ[7]

V5

DDR0_DQ[40]/DDR1_DQ[8]

V2

DDR0_DQ[41]/DDR1_DQ[9]

U1

DDR0_DQ[42]/DDR1_DQ[10]

U2

DDR0_DQ[43]/DDR1_DQ[11]

V1

DDR0_DQ[44]/DDR1_DQ[12]

V4

DDR0_DQ[45]/DDR1_DQ[13]

U5

DDR0_DQ[46]/DDR1_DQ[14]

U4

DDR0_DQ[47]/DDR1_DQ[15]

R2

DDR0_DQ[48]/DDR1_DQ[32]

P5

DDR0_DQ[49]/DDR1_DQ[33]

R4

DDR0_DQ[50]/DDR1_DQ[34]

P4

DDR0_DQ[51]/DDR1_DQ[35]

R5

DDR0_DQ[52]/DDR1_DQ[36]

P2

DDR0_DQ[53]/DDR1_DQ[37]

R1

DDR0_DQ[54]/DDR1_DQ[38]

P1

DDR0_DQ[55]/DDR1_DQ[39]

DDR0_DQ[56]/DDR1_DQ[40]

DDR0_DQ[57]/DDR1_DQ[41]

L4

DDR0_DQ[58]/DDR1_DQ[42]

L2

DDR0_DQ[59]/DDR1_DQ[43]

DDR0_DQ[60]/DDR1_DQ[44]

DDR0_DQ[61]/DDR1_DQ[45]

L5

DDR0_DQ[62]/DDR1_DQ[46]

L1

DDR0_DQ[63]/DDR1_DQ[47]

DDR0_ECC[0]

DDR0_ECC[1]

DDR0_ECC[2]

DDR0_ECC[3]

DDR0_ECC[4]

DDR0_ECC[5]

DDR0_ECC[6]

DDR0_ECC[7]

SKYLAKE_HA LO

BGA1440

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CLKP[2]

DDR0_CLKN[2]

DDR0_CLKP[3]

DDR0_CLKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN[0]

DDR0_DQSN[1]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[8]

DDR0_DQSN[8]

AG1

AG2

AK1

AK2

AL3

AK3

AL2

AL1

AT1

AT2

AT3

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

AH5

AH1

AU1

AH4

AG4

AD1

AH3

AP4

AN4

AP5

AP2

AP1

AP3

AN1

AN3

AT4

AH2

AN2

AU4

AE3

AU2

AU3

AG3

AU5

BR5

BL3

BG3

BD3

AB3

V3

R3

M3

BP5

BK3

BF3

BC3

AA3

U3

P3

L3

AY3

BA3

DDR_A_C LK0

DDR_A_C LK#0

DDR_A_C LK#1

DDR_A_C LK1

DDR_A_C KE0

DDR_A_C KE1

DDR_A_C S#0

DDR_A_C S#1

DDR_A_O DT0

DDR_A_O DT1

DDR_A_B A0

DDR_A_B A1

DDR_A_B G0

DDR_A_R AS#

DDR_A_W E#

DDR_A_C AS#

DDR_A_M A0

DDR_A_M A1

DDR_A_M A2

DDR_A_M A3

DDR_A_M A4

DDR_A_M A5

DDR_A_M A6

DDR_A_M A7

DDR_A_M A8

DDR_A_M A9

DDR_A_M A10

DDR_A_M A11

DDR_A_M A12

DDR_A_M A13

DDR_A_B G1

DDR_A_A CT#

DDR_A_D QS#0

DDR_A_D QS#1

DDR_A_D QS#2

DDR_A_D QS#3

DDR_A_D QS4

DDR_A_D QS5

DDR_A_D QS6

DDR_A_D QS7

DDR_A_D QS0

DDR_A_D QS1

DDR_A_D QS2

DDR_A_D QS3

DDR_A_D QS#4

DDR_A_D QS#5

DDR_A_D QS#6

DDR_A_D QS#7

DDR_A_C LK0 <20>

DDR_A_C LK#0 <20>

DDR_A_C LK#1 <20>

DDR_A_C LK1 <20>

DDR_A_C KE0 <20>

DDR_A_C KE1 <20>

DDR_A_C S#0 <20>

DDR_A_C S#1 <20>

DDR_A_O DT0 <20>

DDR_A_O DT1 <20>

DDR_A_B A0 <20>

DDR_A_B A1 <20>

DDR_A_B G0 <20>

DDR_A_R AS# <20>

DDR_A_W E# <20>

DDR_A_C AS# <20>

DDR_A_M A0 < 20>

DDR_A_M A1 < 20>

DDR_A_M A2 < 20>

DDR_A_M A3 < 20>

DDR_A_M A4 < 20>

DDR_A_M A5 < 20>

DDR_A_M A6 < 20>

DDR_A_M A7 < 20>

DDR_A_M A8 < 20>

DDR_A_M A9 < 20>

DDR_A_M A10 <20>

DDR_A_M A11 <20>

DDR_A_M A12 <20>

DDR_A_M A13 <20>

DDR_A_B G1 <20>

DDR_A_A CT# <20>

DDR_A_P AR <20>

DDR_A_A LERT# <20>

DDR_A_D QS#0 <20 >

DDR_A_D QS#1 <20 >

DDR_A_D QS#2 <20 >

DDR_A_D QS#3 <20 >

DDR_A_D QS4 <20>

DDR_A_D QS5 <20>

DDR_A_D QS6 <20>

DDR_A_D QS7 <20>

DDR_A_D QS0 <20>

DDR_A_D QS1 <20>

DDR_A_D QS2 <20>

DDR_A_D QS3 <20>

DDR_A_D QS#4 <20 >

DDR_A_D QS#5 <20 >

DDR_A_D QS#6 <20 >

DDR_A_D QS#7 <20 >

DDR CHANNEL A

SKL-H_BG A1440

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

For DFT ONLY

5

4

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1 OF 14

Compal Secret Data

Compal Secret Data

2015/08/ 10 2016/12/ 31

2015/08/ 10 2016/12/ 31

2015/08/ 10 2016/12/ 31

3

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

2

Date : Sheet o f

Compal Electronics, Inc.

DDR4_CHA

DDR4_CHA

DDR4_CHA

LA-C951P

LA-C951P

LA-C951P

7 6 2Friday, August 14, 20 15

7 6 2Friday, August 14, 20 15

7 6 2Friday, August 14, 20 15

1

1.0

1.0

1.0

5

4

3

2

1

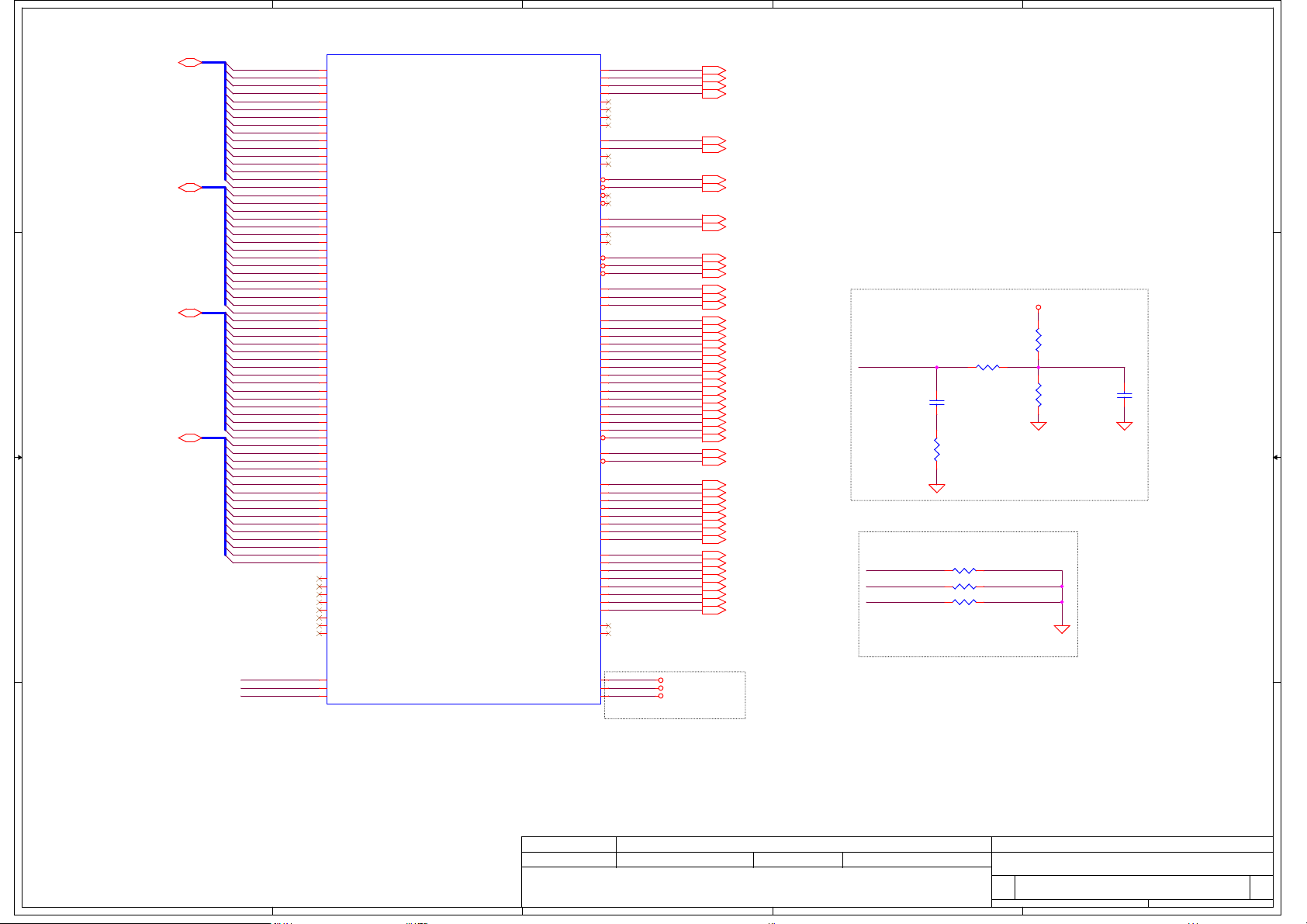

@

DDR_B_D [0..15]<21>

D D

DDR_B_D [16..31]<21>

DDR_B_D [32..47]<21>

C C

DDR_B_D [48..63]<21>

B B

DDR_B_D 0

DDR_B_D 1

DDR_B_D 2

DDR_B_D 3

DDR_B_D 4

DDR_B_D 5

DDR_B_D 6

DDR_B_D 7

DDR_B_D 8

DDR_B_D 9

DDR_B_D 10

DDR_B_D 11

DDR_B_D 12

DDR_B_D 13

DDR_B_D 14

DDR_B_D 15

DDR_B_D 16

DDR_B_D 17

DDR_B_D 18

DDR_B_D 19

DDR_B_D 20

DDR_B_D 21

DDR_B_D 22

DDR_B_D 23

DDR_B_D 24

DDR_B_D 25

DDR_B_D 26

DDR_B_D 27

DDR_B_D 28

DDR_B_D 29

DDR_B_D 30

DDR_B_D 31

DDR_B_D 32

DDR_B_D 33

DDR_B_D 34

DDR_B_D 35

DDR_B_D 36

DDR_B_D 37

DDR_B_D 38

DDR_B_D 39

DDR_B_D 40

DDR_B_D 41

DDR_B_D 42

DDR_B_D 43

DDR_B_D 44

DDR_B_D 45

DDR_B_D 46

DDR_B_D 47

DDR_B_D 48

DDR_B_D 49

DDR_B_D 50

DDR_B_D 51

DDR_B_D 52

DDR_B_D 53

DDR_B_D 54

DDR_B_D 55

DDR_B_D 56

DDR_B_D 57

DDR_B_D 58

DDR_B_D 59

DDR_B_D 60

DDR_B_D 61

DDR_B_D 62

DDR_B_D 63

DDR_RCO MP0

DDR_RCO MP1

DDR_RCO MP2

UC1B

BT11

DDR1_DQ[0]/DDR0_DQ[16]

BR11

DDR1_DQ[1]/DDR0_DQ[17]

BT8

DDR1_DQ[2]/DDR0_DQ[18]

BR8

DDR1_DQ[3]/DDR0_DQ[19]

BP11

DDR1_DQ[4]/DDR0_DQ[20]

BN11

DDR1_DQ[5]/DDR0_DQ[21]

BP8

DDR1_DQ[6]/DDR0_DQ[22]

BN8

DDR1_DQ[7]/DDR0_DQ[23]

BL12

DDR1_DQ[8]/DDR0_DQ[24]

BL11

DDR1_DQ[9]/DDR0_DQ[25]

BL8

DDR1_DQ[10]/DDR0_DQ[26]

BJ8

DDR1_DQ[11]/DDR0_DQ[27]

BJ11

DDR1_DQ[12]/DDR0_DQ[28]

BJ10

DDR1_DQ[13]/DDR0_DQ[29]

BL7

DDR1_DQ[14]/DDR0_DQ[30]

BJ7

DDR1_DQ[15]/DDR0_DQ[31]

BG11

DDR1_DQ[16]/DDR0_DQ[48]

BG10

DDR1_DQ[17]/DDR0_DQ[49]

BG8

DDR1_DQ[18]/DDR0_DQ[50]

BF8

DDR1_DQ[19]/DDR0_DQ[51]

BF11

DDR1_DQ[20]/DDR0_DQ[52]

BF10

DDR1_DQ[21]/DDR0_DQ[53]

BG7

DDR1_DQ[22]/DDR0_DQ[54]

BF7

DDR1_DQ[23]/DDR0_DQ[55]

BB11

DDR1_DQ[24]/DDR0_DQ[56]

BC11

DDR1_DQ[25]/DDR0_DQ[57]

BB8

DDR1_DQ[26]/DDR0_DQ[58]

BC8

DDR1_DQ[27]/DDR0_DQ[59]

BC10

DDR1_DQ[28]/DDR0_DQ[60]

BB10

DDR1_DQ[29]/DDR0_DQ[61]

BC7

DDR1_DQ[30]/DDR0_DQ[62]

BB7

DDR1_DQ[31]/DDR0_DQ[63]

AA11

DDR1_DQ[32]/DDR1_DQ[16]

AA10

DDR1_DQ[33]/DDR1_DQ[17]

AC11

DDR1_DQ[34]/DDR1_DQ[18]

AC10

DDR1_DQ[35]/DDR1_DQ[19]

AA7

DDR1_DQ[36]/DDR1_DQ[20]

AA8

DDR1_DQ[37]/DDR1_DQ[21]

AC8

DDR1_DQ[38]/DDR1_DQ[22]

AC7

DDR1_DQ[39]/DDR1_DQ[23]

W8

DDR1_DQ[40]/DDR1_DQ[24]

W7

DDR1_DQ[41]/DDR1_DQ[25]

V10

DDR1_DQ[42]/DDR1_DQ[26]

V11

DDR1_DQ[43]/DDR1_DQ[27]

W11

DDR1_DQ[44]/DDR1_DQ[28]

W10

DDR1_DQ[45]/DDR1_DQ[29]

V7

DDR1_DQ[46]/DDR1_DQ[30]

V8

DDR1_DQ[47]/DDR1_DQ[31]

R11

DDR1_DQ[48]

P11

DDR1_DQ[49]

P7

DDR1_DQ[50]

R8

DDR1_DQ[51]

R10

DDR1_DQ[52]

P10

DDR1_DQ[53]

R7

DDR1_DQ[54]

P8

DDR1_DQ[55]

L11

DDR1_DQ[56]

M11

DDR1_DQ[57]

L7

DDR1_DQ[58]

M8

DDR1_DQ[59]

L10

DDR1_DQ[60]

M10

DDR1_DQ[61]

M7

DDR1_DQ[62]

L8

DDR1_DQ[63]

AW11

DDR1_ECC[0]

AY11

DDR1_ECC[1]

AY8

DDR1_ECC[2]

AW8

DDR1_ECC[3]

AY10

DDR1_ECC[4]

AW10

DDR1_ECC[5]

AY7

DDR1_ECC[6]

AW7

DDR1_ECC[7]

G1

DDR_RCOMP[0]

H1

DDR_RCOMP[1]

J2

DDR_RCOMP[2]

SKL-H_BG A1440

DDR CHANNEL B

SKYLAKE_HA LO

BGA1440

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

2 OF 14

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[1]

DDR1_CLKP[2]

DDR1_CLKN[2]

DDR1_CLKP[3]

DDR1_CLKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_B_C LK0

AM9

DDR_B_C LK#0

AN9

DDR_B_C LK#1

AM8

DDR_B_C LK1

AM7

AM11

AM10

AJ10

AJ11

DDR_B_C KE0

AT8

DDR_B_C KE1

AT10

AT7

AT11

DDR_B_C S#0

AF11

DDR_B_C S#1

AE7

AF10

AE10

DDR_B_O DT0

AF7

DDR_B_O DT1

AE8

AE9

AE11

DDR_B_R AS#

AH10

DDR_B_W E#

AH11

DDR_B_C AS#

AF8

DDR_B_B A0

AH8

DDR_B_B A1

AH9

DDR_B_B G0

AR9

DDR_B_M A0

AJ9

DDR_B_M A1

AK6

DDR_B_M A2

AK5

DDR_B_M A3

AL5

DDR_B_M A4

AL6

DDR_B_M A5

AM6

DDR_B_M A6

AN7

DDR_B_M A7

AN10

DDR_B_M A8

AN8

DDR_B_M A9

AR11

DDR_B_M A10

AH7

DDR_B_M A11

AN11

DDR_B_M A12

AR10

DDR_B_M A13

AF9

DDR_B_B G1

AR7

DDR_B_A CT#

AT9

AJ7

AR8

DDR_B_D QS#0

BP9

DDR_B_D QS#1

BL9

DDR_B_D QS#2

BG9

DDR_B_D QS#3

BC9

DDR_B_D QS#4

AC9

DDR_B_D QS#5

W9

DDR_B_D QS#6

R9

DDR_B_D QS#7

M9

DDR_B_D QS0

BR9

DDR_B_D QS1

BJ9

DDR_B_D QS2

BF9

DDR_B_D QS3

BB9

DDR_B_D QS4

AA9

DDR_B_D QS5

V9

DDR_B_D QS6

P9

DDR_B_D QS7

L9

AW9

AY9

BN13

BP13

BR13

Trace width/Spacing >= 20mils

+0.6V_VR EFCA

+0.6V_A_ VREFDQ

+0.6V_B_ VREFDQ

DDR_B_C LK0 <21>

DDR_B_C LK#0 <21>

DDR_B_C LK#1 <21>

DDR_B_C LK1 <21>

DDR_B_C KE0 <21>

DDR_B_C KE1 <21>

DDR_B_C S#0 <21>

DDR_B_C S#1 <21>

DDR_B_O DT0 <21>

DDR_B_O DT1 <21>

DDR_B_R AS# <21>

DDR_B_W E# <21>

DDR_B_C AS# <21>

DDR_B_B A0 <21>

DDR_B_B A1 <21>

DDR_B_B G0 <21>

DDR_B_M A0 < 21>

DDR_B_M A1 < 21>

DDR_B_M A2 < 21>

DDR_B_M A3 < 21>

DDR_B_M A4 < 21>

DDR_B_M A5 < 21>

DDR_B_M A6 < 21>

DDR_B_M A7 < 21>

DDR_B_M A8 < 21>

DDR_B_M A9 < 21>

DDR_B_M A10 <21>

DDR_B_M A11 <21>

DDR_B_M A12 <21>

DDR_B_M A13 <21>

DDR_B_B G1 <21>

DDR_B_A CT# <21>

DDR_B_P AR <21>

DDR_B_A LERT# <21>

DDR_B_D QS#0 <21 >

DDR_B_D QS#1 <21 >

DDR_B_D QS#2 <21 >

DDR_B_D QS#3 <21 >

DDR_B_D QS#4 <21 >

DDR_B_D QS#5 <21 >

DDR_B_D QS#6 <21 >

DDR_B_D QS#7 <21 >

DDR_B_D QS0 <21>

DDR_B_D QS1 <21>

DDR_B_D QS2 <21>

DDR_B_D QS3 <21>

DDR_B_D QS4 <21>

DDR_B_D QS5 <21>

DDR_B_D QS6 <21>

DDR_B_D QS7 <21>

+1.2V_VDDQ

@

+0.6V_A_ VREFDQ

@

@

R5

1 2

2_0402_ 1%

1

CC2

0.022U_0 402_25V7K

2

RC6

24.9_040 2_1%

1 2

Refer Doc.546884_SKL_H_PDG_Rev1_2_pub.

Figure 4-25

RC2

1K_0402 _1%

DDR4 COMPENSATION SIGNALS

DDR_RCO MP0

DDR_RCO MP1

DDR_RCO MP2

Note:

Trace width=12~15 mil, Spcing=20 mils

Max trace length= 500 mils

1 2

RC3 121_0402_ 1%

1 2

RC4 75_0402_1 %

1 2

RC5 100_0402_ 1%

RC1

1K_0402 _1%

1 2

@

1 2

@

CC1

0.1U_020 1_10V6K

2

@

1

A A

Security Classification

Security Classification

Security Classification

2015/08/ 10 2016/12/ 31

2015/08/ 10 2016/12/ 31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

For DFT ONLY

5

4

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/08/ 10 2016/12/ 31

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

2

Date : Sheet o f

Compal Electronics, Inc.

DDR4_CHB

DDR4_CHB

DDR4_CHB

LA-C951P

LA-C951P

LA-C951P

8 6 2Friday, August 14, 20 15

8 6 2Friday, August 14, 20 15

8 6 2Friday, August 14, 20 15

1

1.0

1.0

1.0

5

4

3

2

1

+VCC_CO RE +VCC_ CORE

AA13

AA31

AA32

D D

C C

B B

AA33

AA34

AA35

AA36

AA37

AA38

AB29

AB30

AB31

AB32

AB35

AB36

AB37

AB38

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF35

AF36

AF37

AF38

K13

K14

L13

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13

SKYLAKE_HA LO

UC1G

@

BGA1440

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SKL-H_BG A1440

7 OF 14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC_SENSE

VSS_SENSE

V32

V33

V34

V35

V36

V37

V38

W13

W14

W29

W30

W31

W32

W35

W36

W37

W38

Y29

Y30

Y31

Y32

Y33

Y34

Y35

Y36

L14

P29

P30

P31

P32

P33

P34

P35

P36

R13

R31

R32

R33

R34

R35

R36

R37

R38

T29

T30

T31

T32

T35

T36

T37

T38

U29

U30

U31

U32

U33

U34

U35

U36

V13

V14

V31

P14

AG37

AG38

+VCC_GT

@

SKYLAKE_HA LO

UC1H

BG34

BG35

BG36

BH33

BH34

BH35

BH36

BH37

BH38

BJ37

BJ38

BL36

BL37

BM36

BM37

BN36

BN37

BN38

BP37

BP38

BR37

BT37

BE38

BF13

BF14

BF29

BF30

BF31

BF32

BF35

BF36

BF37

BF38

BG29

BG30

BG31

BG32

BG33

BC36

BC37

BC38

BD13

BD14

BD29

BD30

BD31

BD32

BD33

BD34

BD35

BD36

BE31

BE32

BE37

VCCCORE _SENSE <54>

VSSCORE _SENSE <54 >

BGA1440

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

SKL-H_BG A1440

8 OF 14

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BE33

BE34

BE35

BE36

+VCC_GT

+VCC_GT

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

AJ36

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK38

AL13

AL29

AL30

AL31

AL32

AL35

AL36

AL37

AL38

AM13

AM14

AM29

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AN13

AN14

AN31

AN32

AN33

AN34

AN35

AN36

AN37

AN38

AP13

AP14

AP29

AP30

AP31

AP32

AP35

AP36

AP37

AP38

AR29

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AT14

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AU14

AU29

AU30

AU31

AU32

AU35

AU36

AU37

AU38

@

UC1N

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

SKL-H_BG A1440

REV = 1

?

SKYLAKE_HA LO

BGA1440

14 OF 14

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGT_SENSE

VSSGTX_SENSE

VSSGT_SENSE

VCCGTX_SENSE

AF29

AF30

AF31

AF32

AF33

AF34

AG13

AG14

AG31

AG32

AG33

AG34

AG35

AG36

AH13

AH14

AH29

AH30

AH31

AH32

AJ13

AJ14

AH38

AH35

AH37

AH36

?

VCCGT_S ENSE <54>

VSSGT_S ENSE <54>

A A

Security Classification

Security Classification

Security Classification

2015/08/ 10 2016/12/ 31

2015/08/ 10 2016/12/ 31

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

For DFT ONLY

5

4

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/08/ 10 2016/12/ 31

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

2

Date : Sheet o f

Compal Electronics, Inc.

VCC/VCCGT

VCC/VCCGT

VCC/VCCGT

LA-C951P

LA-C951P

LA-C951P

9 6 2Friday, August 14, 20 15

9 6 2Friday, August 14, 20 15

9 6 2Friday, August 14, 20 15

1

1.0

1.0

1.0

5

4

3

2

1

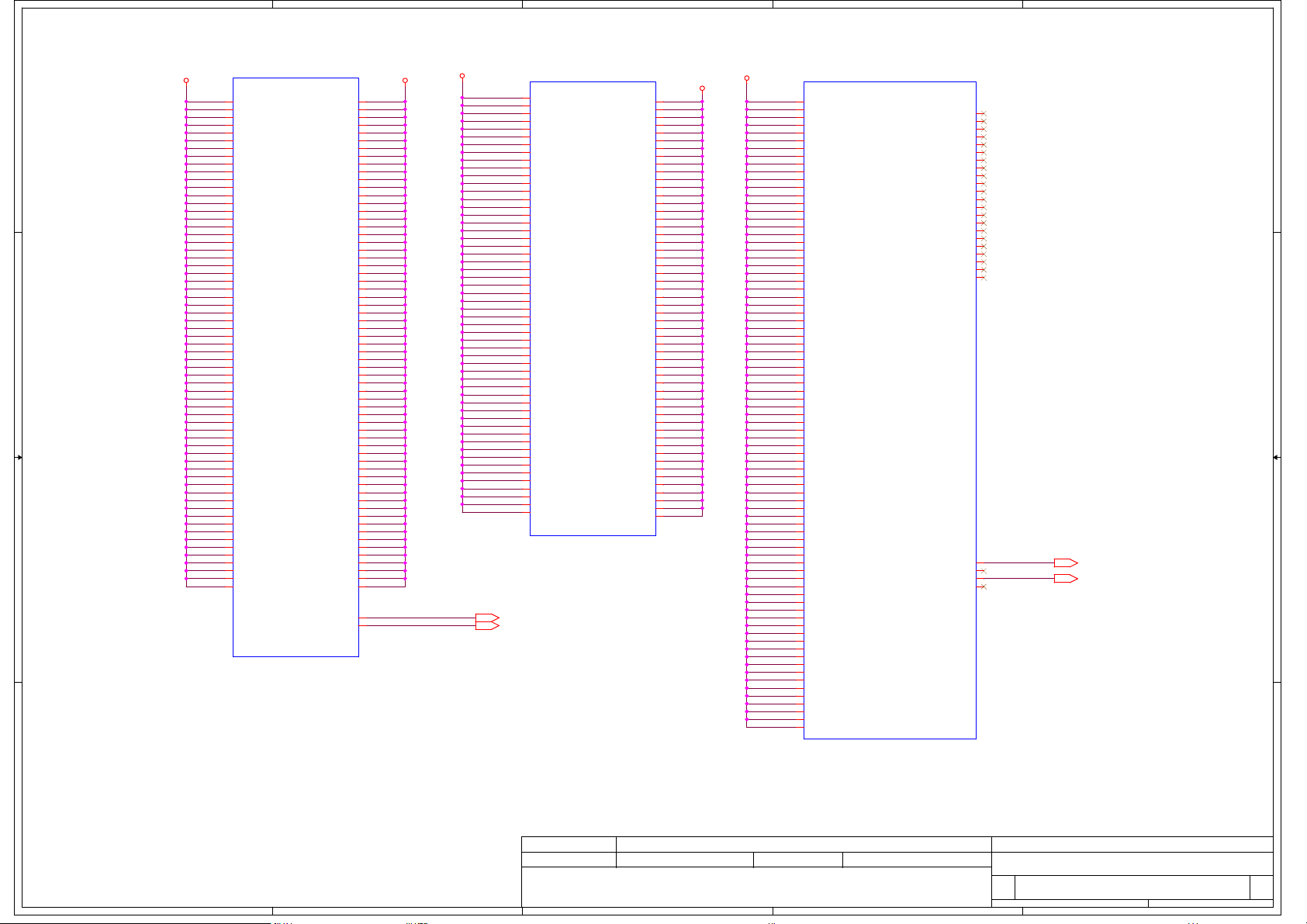

SKYLAKE_HA LO

UC1I

+VCCSA

D D

+VCCIO

C C

K29

K30

K31

K32

K33

K34

K35

M29

M30

M31

M32

M33

M34

M35

M36

AG12

G15

G17

G19

G21

H15

H16

H17

H19

H20

H21

H26

H27

J30

L31

L32

L35

L36

L37

L38

J15

J16

J17

J19

J20

J21

J26

J27

@

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

SKL-H_BG A1440

BGA1440

9 OF 14

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VCCPLL_OC

VCCPLL_OC

VCCST

VCCSTG

VCCSTG

VCCPLL

VCCPLL

VCCSA_SENSE

VSSSA_SENSE

VCCIO_SENSE

VSSIO_SENSE

AA6

AE12

AF5

AF6

AG5

AG9

AJ12

AL11

AP6

AP7

AR12

AR6

AT12

AW6

AY6

J5

J6

K12

K6

L12

L6

R6

T6

W6

Y12

BH13

G11

H30

H29

G30

H28

J28

M38

M37

H14

J14

+1.2V_CP U_VDDQ

+1.2V_VD DQC

2.8A

+1V_VCC ST

+1.2V_VC CPLL_OC

+1VS_VC CSTG

+1V_VCC ST

VCCSA_S ENSE <54>

VSSSA_S ENSE < 54>

+1.2V +1.2V_ CPU_VDDQ

RC83

@

1 2

0_0805_ 5%

RC189 0_0402_ 5%@

RC81

@

1 2

0_0603_ 5%

PLACE CAP BACKSIDE

1 2

PLACE CAP BACKSIDE

+1.2V_CPU_VDDQ

+1.2V_VD DQC+1.2V_CP U_VDDQ

2.8A

10U_0603_6.3V6M

CC58

2

1

+1.2V_VC CPLL_OC+1.2V_CP U_VDDQ

1U_0402_6.3V6K

1U_0402_6.3V6K

CC21

2

1

CC22

2

1

10U_0603_6.3V6M

2

1

CC23

22uF *4

CC45

+1.2V_CPU_VDDQ

10U_0603_6.3V6M

CC27

2

2

1

1

10U_0603_6.3V6M

CC28

@

10U_0603_6.3V6M

10U_0603_6.3V6M

CC30

CC29

2

2

1

1

10U_0603_6.3V6M

10U_0603_6.3V6M

CC32

CC31

2

2

1

1

10U_0603_6.3V6M

10U_0603_6.3V6M

CC34

CC33

2

2

@

@

1

1

10U_0603_6.3V6M

10U_0603_6.3V6M

CC36

CC35

2

2

@

@

1

1

B B

10U_0603_6.3V6M

10U_0603_6.3V6M

CC41

2

2

1

1

10U_0603_6.3V6M

10U_0603_6.3V6M

CC43

CC42

2

@

1

10U_0603_6.3V6M

CC40

2

1

CC39

2

@

1

10U_0603_6.3V6M

10U_0603_6.3V6M

CC38

2

2

1

1

+1VS_VC CSTG +1V_ VCCST+VCCIO

1U_0402_6.3V6K

1U_0402_6.3V6K

CC37

1U_0402_6.3V6K

2

1

CC47

CC46

2

2

@

1

1

1U_0402_6.3V6K

CC44

2

1

10U_0603_6.3V6M

10U_0603_6.3V6M

CC24

2

1

10U_0603_6.3V6M

CC25

2

1

CC26

2

1

PLACE CAP BACKSIDE

22uF*4/1 0uF*3

PLACE CAP BACKSIDE

A A

For DFT ONLY

5

PLACE CAP BACKSIDE

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/08/ 10 2016/12/ 31

2015/08/ 10 2016/12/ 31

2015/08/ 10 2016/12/ 31

3

10uF*10

PLACE CAP BACKSIDE

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

2

Date : Sheet o f

Compal Electronics, Inc.

VDDQ/VCCSA/VCCIO

VDDQ/VCCSA/VCCIO

VDDQ/VCCSA/VCCIO

LA-C951P

LA-C951P

LA-C951P

10 62F riday, August 14, 2 015

10 62F riday, August 14, 2 015

10 62F riday, August 14, 2 015

1

1.0

1.0

1.0

5

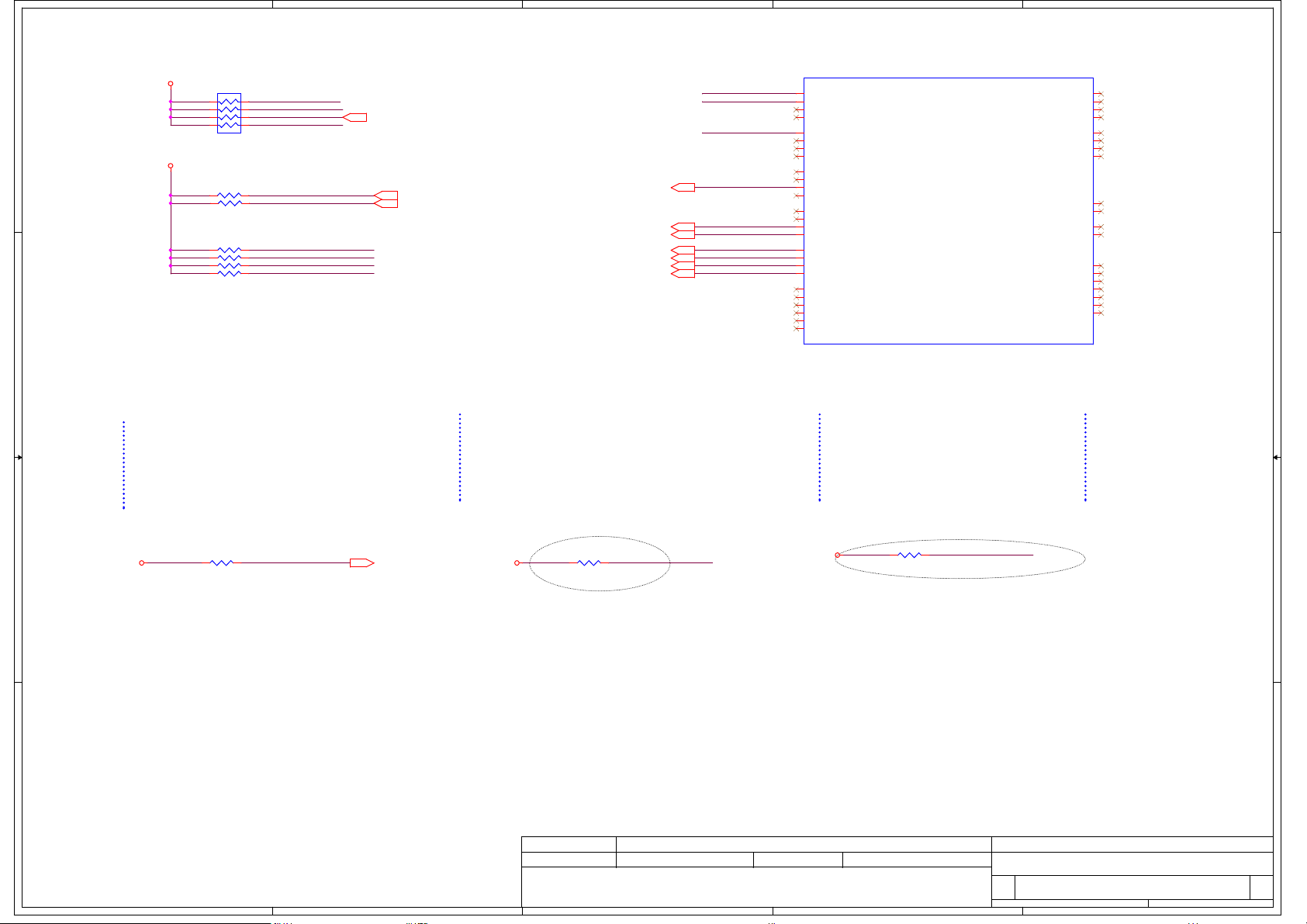

CFG Straps for Processor

PEG Static Lane Reversal - CFG2 is for the 16x

D D

CFG2

Display Port Presence Strap

CFG4

C C

PCIE Port Bifurcation Straps

CFG[6:5 ]

B B

PEG DEFER TRAINING

CFG7

A A

1: Normal Operation; Lane # definition matches

socket pin map definition

0:Lane Reversed

*

CFG2

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

*

1 2

CFG4

RC47 1K_040 2_5%

RC20

1K_0402_1%

1 2

check GPU PEG

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

*

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG5

CFG6

RC56

RC58

@

1K_0402_1%

1: (Default) PEG Train immediately following xxRESETB

de assertion

*

1K_0402_1%

1 2

1 2

0: PEG Wait for BIOS for training

CFG7

RC40

@

1K_0402_1%

1 2

4

SM_PG_CTRL< 50>

H_CPUPWR GD<15>

100P_0402_5 0V8J

20141230, ESD require

+3VS

CRB

1 2

VR_SVID_ALERT#_R<54>

VR_SVID_SCLK_R<54>

VR_SVID_SDIO_R<54>

H_PROCHOT#_ EC<38,4 8>

EMI@

+1VS_VCCSTG

+1V_VCCST

RC55

330K_0402_5 %

SM_PG_CTRL

CC271

+1V_VCCST

RC53

100_0402_1 %

1 2

H_PROCHOT#_ EC

H_VCCST_PW RGD<38,45>

PLTRST_CPU #<14>

H_PM_SYNC<14>

H_PM_DOWN<14>

H_PECI<14,38>

THERMTRIP#_R<14>

H_SKTOCC#_R<14>

1

2

@

RC52

100K_0402_5 %

H_PROCHOT#_ EC

1 2

RC38 1K_0 402_5%

1 2

RH25 1K_0402_5 %

1 2

RC46 1K_0402_5 %

PCH_TRIGGER<19>

CPU_TRIGGER<19>

+3VALW

ORB

1 2

3

TC87 TP@

TC91 TP@

TC92 TP@

DDR_PG_CTR L

PCH_CPU_BCL K_P

PCH_CPU_BCL K_N

PCH_CPU_PCIBCL K_P

PCH_CPU_PCIBCL K_N

PCH_CPU_NSS C_P

PCH_CPU_NSS C_N

VR_SVID_ALERT#

VR_SVID_CLK

VR_SVID_DATA

H_PROCHOT#_ R

DDR_PG_CTR L

VCCST_PWRGD _CPUH_VCCST_PW RGD

H_PM_SYNC_R

H_PM_DOWN _R

H_PECI