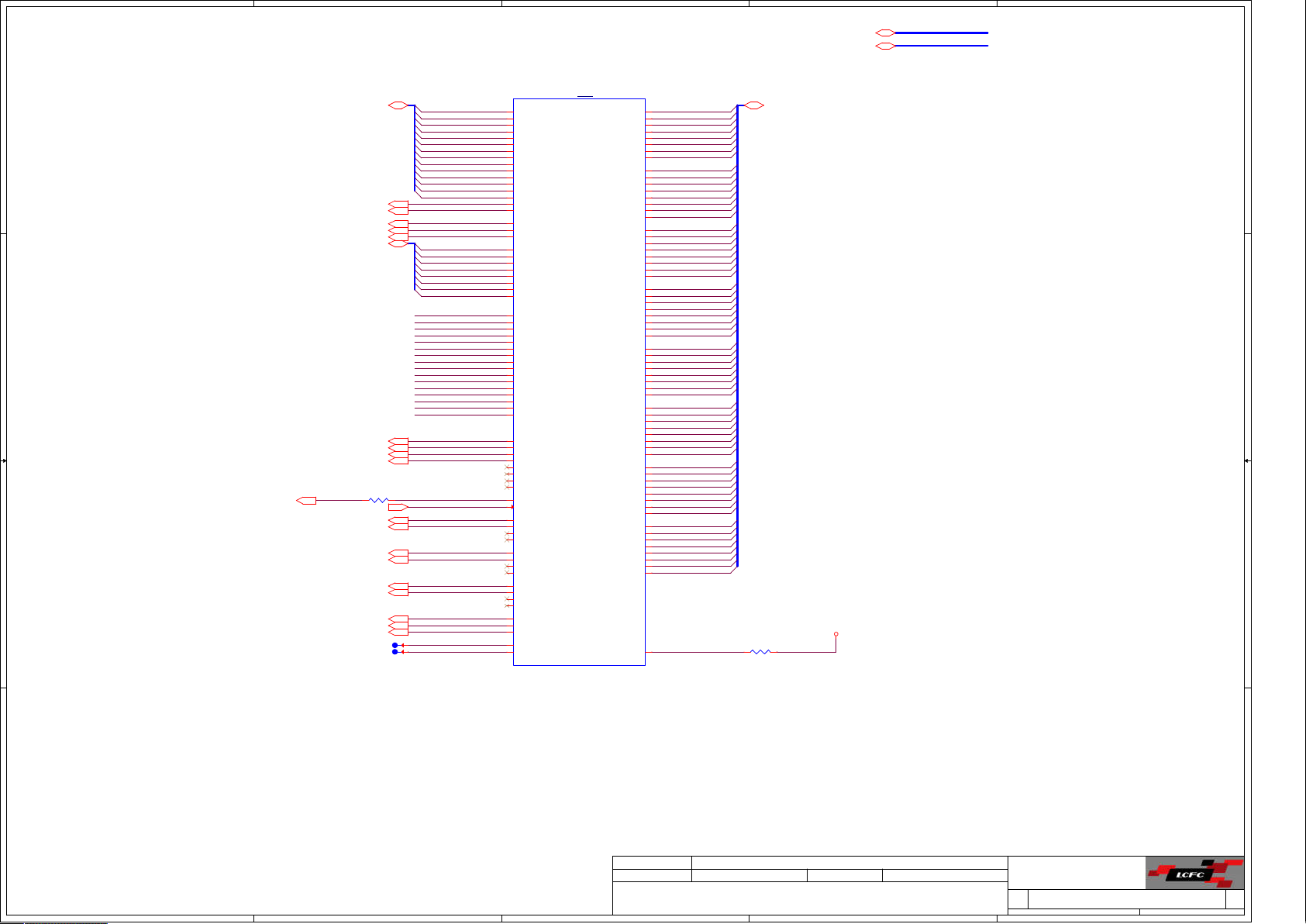

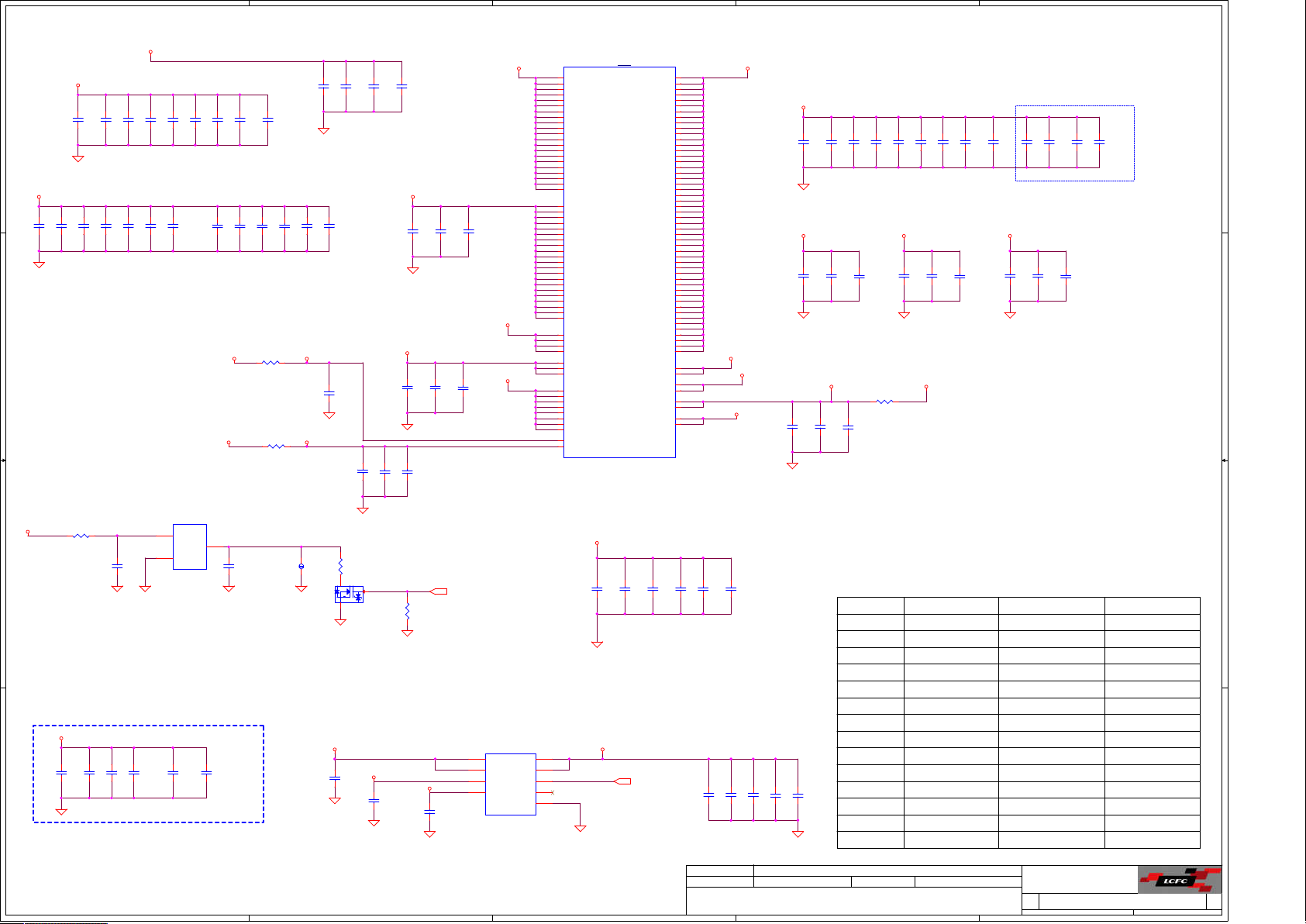

Lenovo Ideapad 320-14IKB Schematic

A

1 1

B

C

D

E

LCFC Confidential

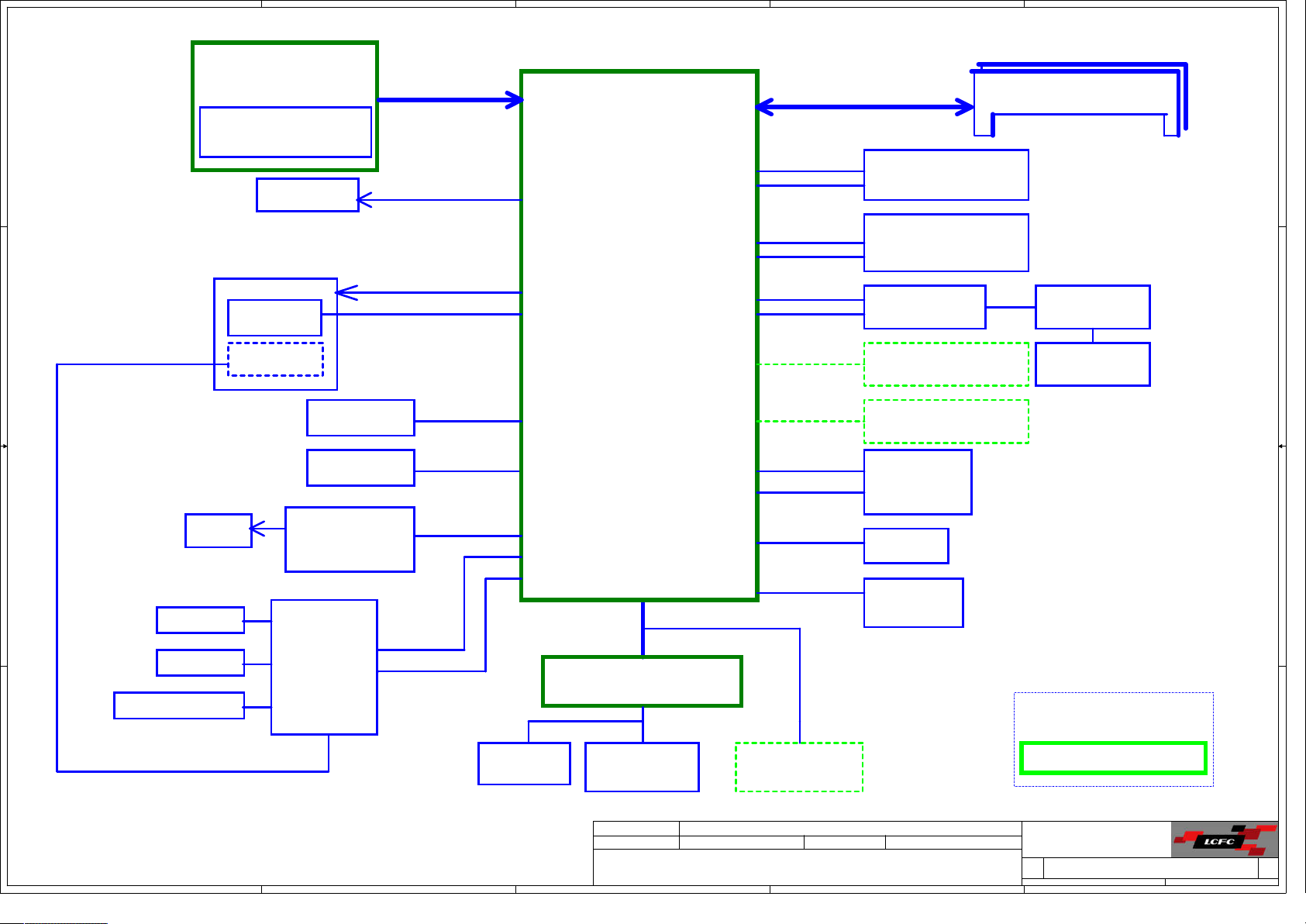

G 320 AST M/B Schematics Document

2 2

NM_B321 REV:0.2

AMD FT4 Stoney SOC with DDRIIII

AMD R17M-M1-70

2017-02-04

3 3

4 4

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFE RED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFE RED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFE RED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT ASAU THORIZED BY LC FUTURE CENTER NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT ASAU THORIZED BY LC FUTURE CENTER NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT ASAU THORIZED BY LC FUTURE CENTER NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANYTHIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTU RE CENTER.

MAY BE USED BY OR DISCLOSED TO ANYTHIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTU RE CENTER.

MAY BE USED BY OR DISCLOSED TO ANYTHIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTU RE CENTER.

A

B

2017/02/04

2017/02/04

2017/02/04

C

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2017/02/04

2017/02/04

2017/02/04

D

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Saturday, February 04, 2017

Saturday, February 04, 2017

Date: Sheet of

Date: Sheet of

Date: Sheet of

Saturday, February 04, 2017

320AST

320AST

320AST

E

1 50

1 50

1 50

0.2

0.2

0.2

A

LCFC confidential

File Name : German

B

C

D

E

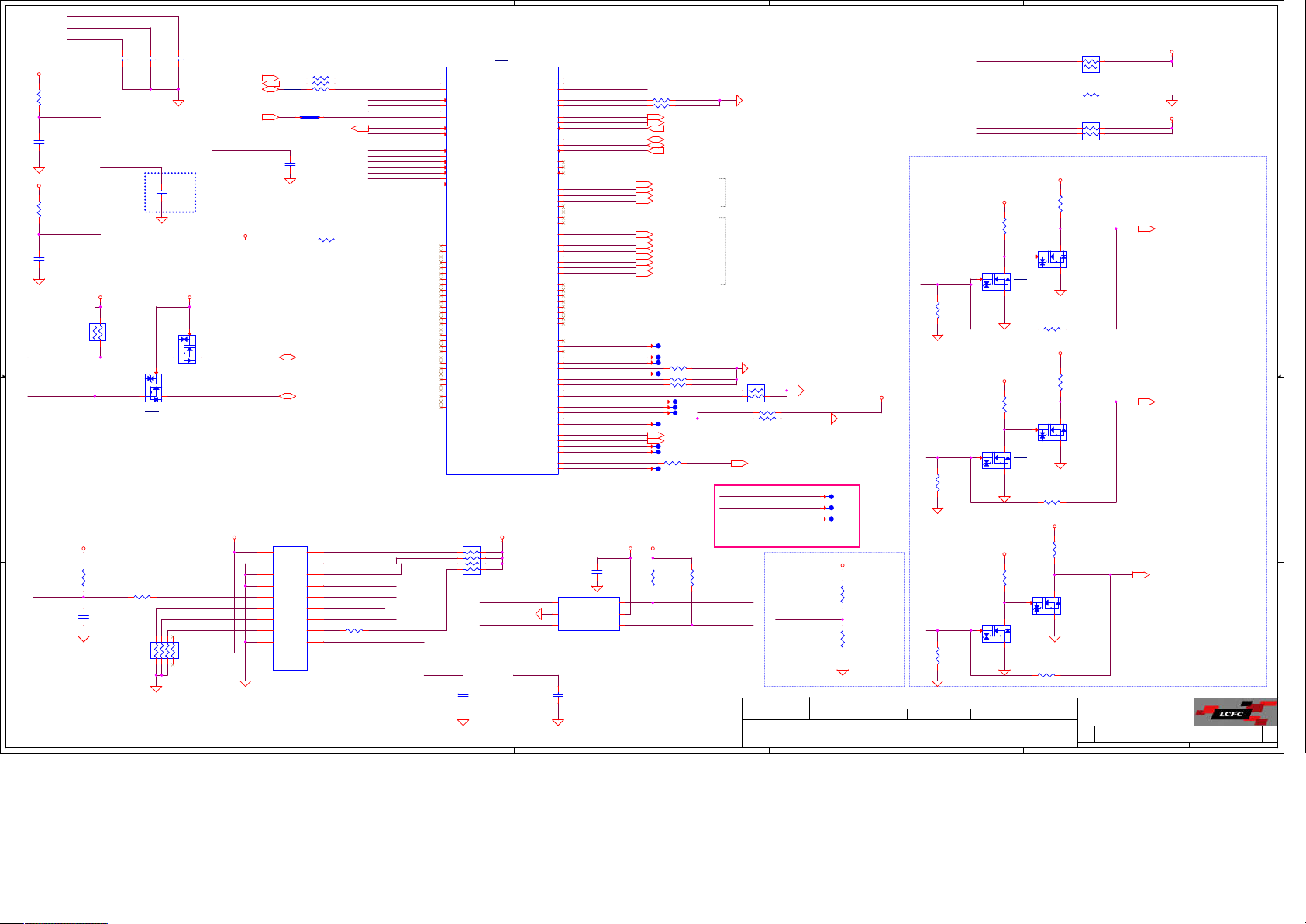

AMD: R17M-M1-70

Package: S3

Page 15~19

1 1

VRAM: 512/256*16

GDDR5*4: 4GB/2GB

Page 20~23

HDMI Conn.

Page 25

PCIe Port 1~4

PCI-Express

4x Gen3

HDMI x4 Lane Port1

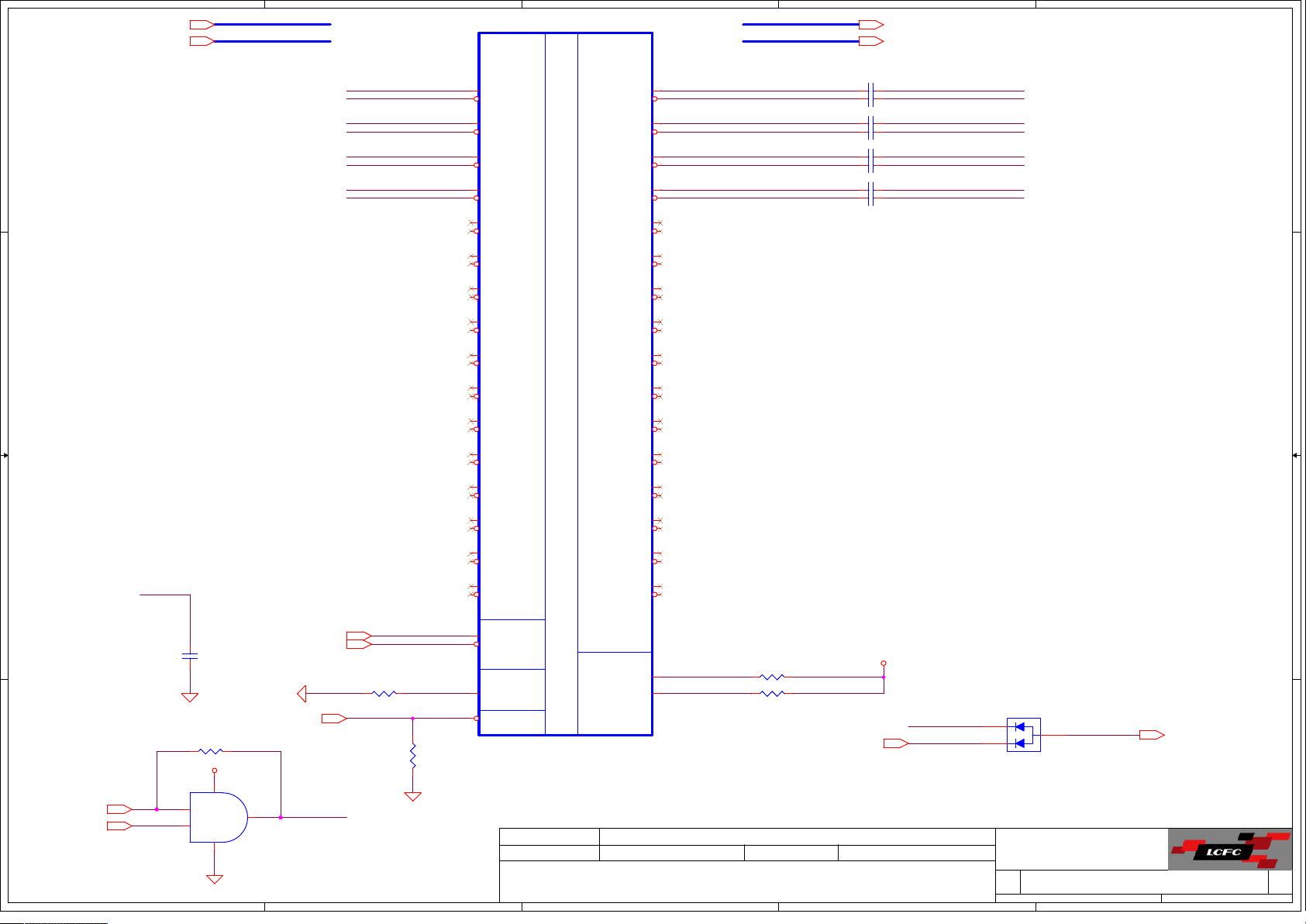

AMD FT4 APU

Stoney 15W

Page 26

eDP Conn

Int. Camera

2 2

USB2.0 Port3

eDP x2 Lane

USB2.0 1x

Int. MIC Conn.

Page 23

Page 33

SATA Port0

SATA Gen3SATA HDD

(Integrated FCH)

BGA-769

Memory BUS (DDR4)

Single Channel B

1.2V DDR4 2133 MT/s

1866 MT/s

USB3.0 x1

USB2.0 x1

USB3.0 x1

USB2.0 x1

USB3.0 x1

USB2.0 x1

USB2.0 x1

USB2.0 x1

USB3.0 Left Conn

USB3.0 Port1

USB2.0 Port5

USB3.0 Left Conn

USB3.0 Port3

USB2.0 Port7

USB3.0 Redriver

Parade PS8713

Touch Screen (Optional)

USB2.0 Port8

Finger Print (Optional)

USB2.0 Port1

DDR4-SO-DIMM X1

UP TO 8G

Page 41

Page 41

Type-C IC

Page 43

Page 33

Page 45

Realtek RTS5449

Type-C Conn

Page 12

Page 43

Page 43

24mm*24mm

Page 33

RJ45 Conn.

Page 29

3 3

LAN Realtek

Realtek_RTL8111GUL

Page 28

SATA Port1

PCIe Port2

SATA Gen1SATA ODD

PCIe 1x

USB 2.0 1x

PCIe 1x

SPI BUS

NGFF Card

WLAN&BT

Key E

Page 31

SPI ROM

8MB

Page 08

PCIe Port1

USB2.0 Port2

Page 4~11

SD/MMC Conn.

Page 24

SPK Conn.

Page 34

HP&Mic Combo Conn.

Page 34

4 4

A

Codec & C/R

Realtek RTS5119

USB2.0 Port4

Page 30

USB2.0 x1

HD Audio

B

Int.KBD

Page 36

EC

ITE IT8586E-LQFP

Page 35

Thermal Sensor

NCT7718W

Page 30

reserve

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUT URE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUT URE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUT URE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENTER.

C

TPM (Reserved)

Z32H320TC

2017/02/04

2017/02/04

2017/02/04

Page 30

LC

LC

LC

Future Center Secret Data

Future Center Secret Data

Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Touch Pad

Page 36

2017/02/04

2017/02/04

2017/02/04

D

Sub-board ( for 15")

ODD Board

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

stom

stom

stom

Cu

Cu

Cu

Saturday, February 04, 2017

Saturday, February 04, 2017

Date: Sheet

Date: Sheet

Date: Sheet

Saturday, February 04, 2017

320AST

320AST

320AST

E

f

2 50

f

2 50

f

2 50

o

o

o

0.2

0.2

0.2

A

Vinafix

B

C

D

E

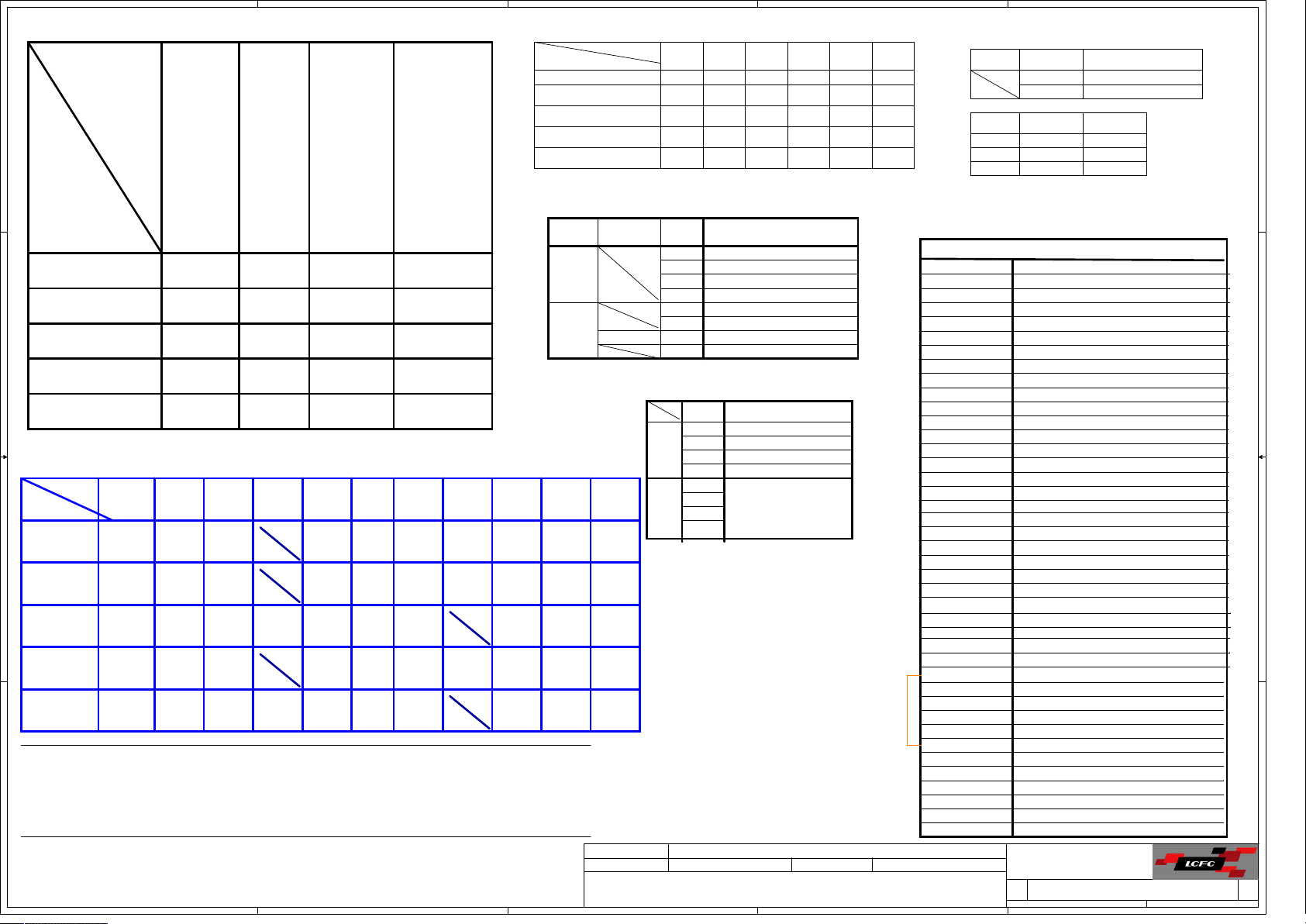

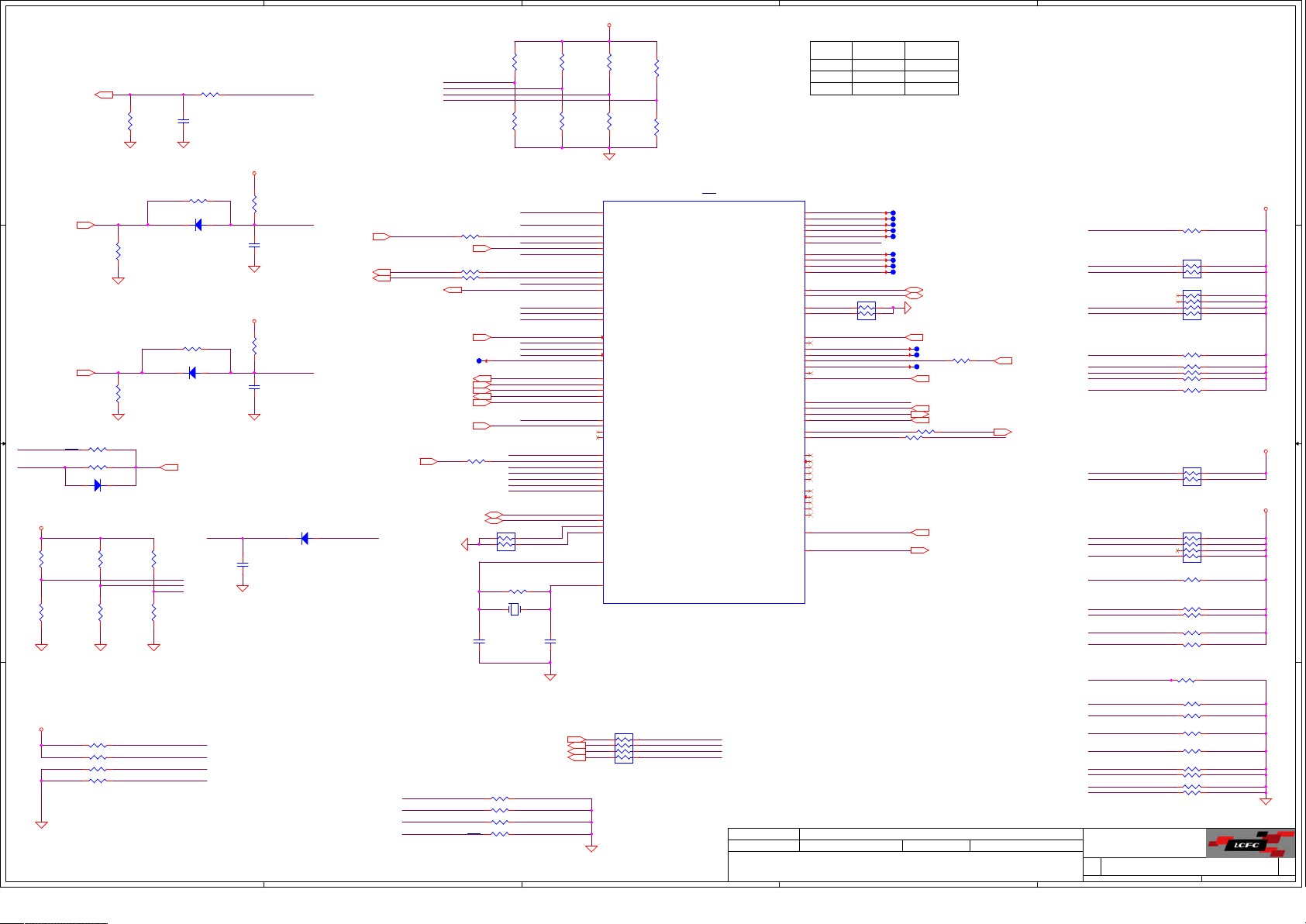

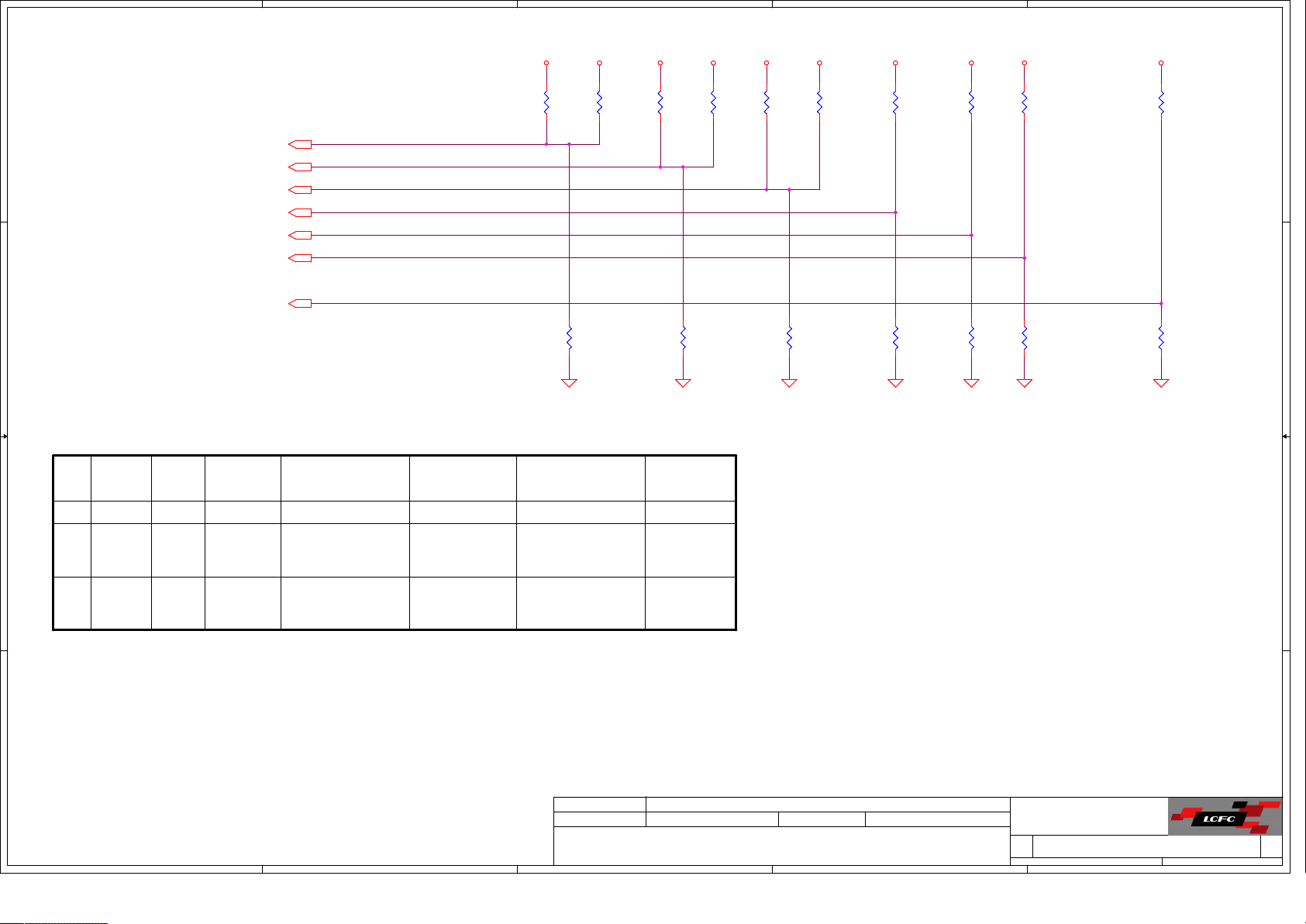

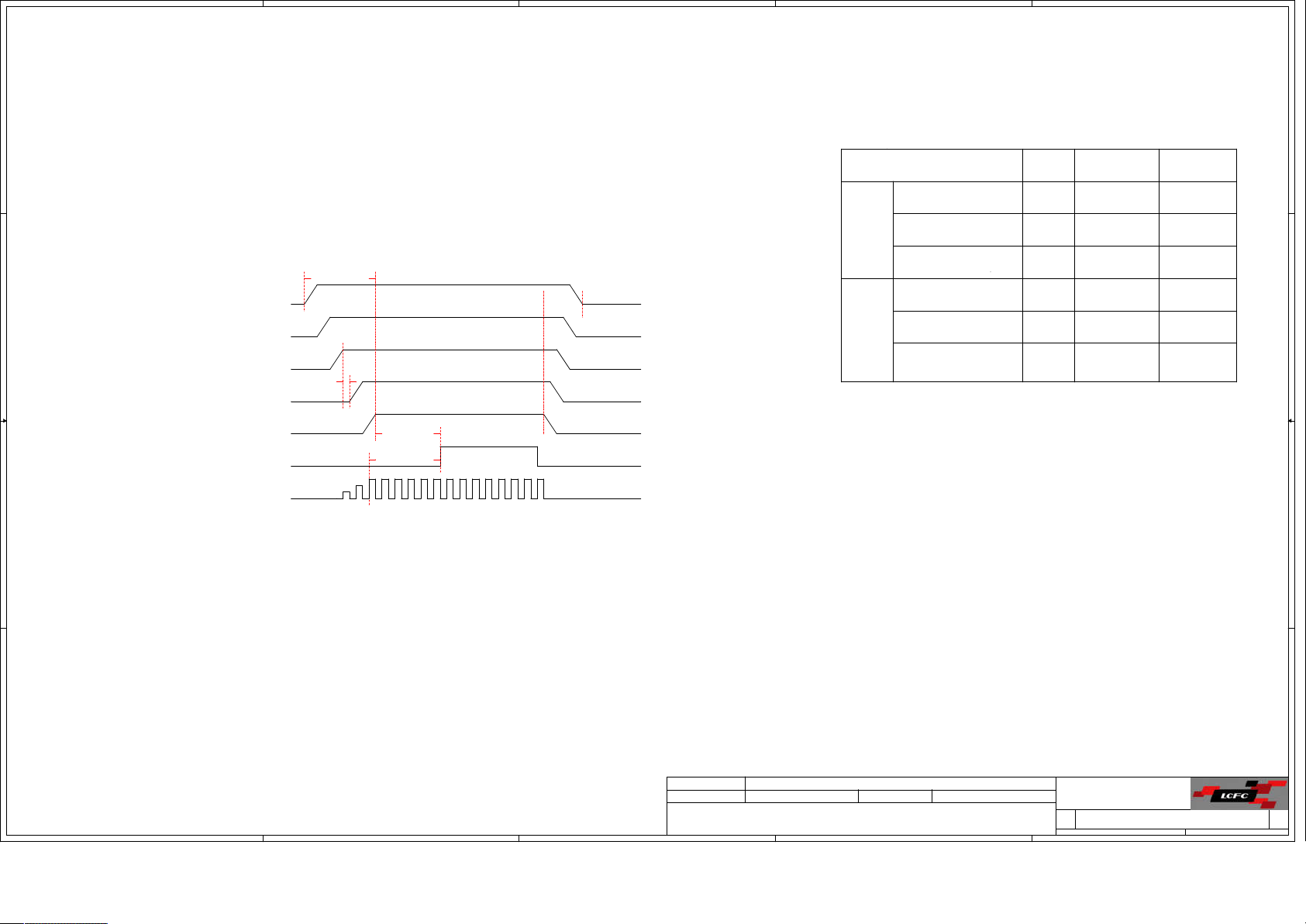

Voltage Rails

power

plane

1 1

State

S0

S3

2 2

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

SMBUS Control Table

EC_SMB_CK1

EC_SMB_DA1

3 3

EC_SMB_CK3

EC_SMB_DA3

APU_SMB_CLK

APU_SMB_DATA

EC_SMB_CK2

EC_SMB_DA2

TP_I2C0_SCL_R

TP_I2C0_SDA_R

IT8586E

+3VL_EC

IT8586E

IT8586E

+3VL_EC

EC SM Bus1 address

Device

Battery

Charger

4 4

APU SM Bus1 address

ce

Devi

ouch pad

T

( O --> Means ON , X --> Means OFF )

SOURCE

B+

(+20VSB)

+3VL

+5VLP

O

O

O

O

X

GPU BATT SODIMM WLAN Thermal

+5VALW

+3VALW

(+3VALW_APU)

+1.8VALW

+0.95VALW

+0.775VALW

O

O

O

X

XX X

X

+3VS

APU

+3VS

V

+3VS_VGA

XXX X

X

XX XXXX XXV

APU

+1.8VS

XXXXXX XX

EC SM Bus2 address

Address

0X16

0001 0010 b

Device

PMIC

APU SM Bus2

Address

0x15

A

No use

+5VS

+3VS

+1.8VS

+2.5V

+1.2V

(+VSYSMEM_APU)

+1.5VS

+0.95VS

+0.6VS

+APU_CORE

+APU_CORE_NB

+APU_GFX

+VGA_CORE

+3VGS

+1.8VGS

+1.35VGS

+0.95VGS

OO

O

X

X X

X

X

STATE

S0 (Full ON)

S1 (Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

USB Port Table for Stoney FT4

EHCI

xHCI 2

SIGNAL

SLP_S3# SLP_S5# +VALW +V +VS Clock

HIGH HIGH

LOW

LOW LOW

USB 3.0USB 2.0 Port

0

1

2

3

4

5

6

7

PCIE PORT LIST

ON

ON

HIGHHIGH

ON

HIGHLOW

ON

LOW

ON

Port device

Finger print

Blue Tooth

Camera

Card Reader

LEFT USB (3.0)

Typ e- C

RighT USB (3.0) upper

Touch screen

Port Device

0

N/A

1

WLAN

2

LAN

3

N/A

0

1

DIS GPU

2

Sensor

GPP

APUIT8586E

Charger

PMIC

Touch

Pad

GFX

3

X

X

X

X

VV

XV

V

X

V

APU_SIC

APU_SID

1.8VS for AST

V

X

X

X

X

X

X

X

X

V

EC SM Bus3 address

Address

0X34

Device

Thermal Sensor

GPU

APU SB-TSI

APU SM Bus3 address

ce

Devi

DD

W

R DIMM

LAN

Address

A0h

0x

B

RSVD

Address

1001_100xb(reserve)

0x41(def ault)

releate to F3x1E4[SbiAddr] or

Address Select Pins setting

APU SM Bus4

No use

Secu

Secu

Secu

rity Classification

rity Classification

rity Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

AY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

AY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

AY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

M

M

M

C

2017/02/04

2017/02/04

2017/02/04

Future Center Secret Data

Future Center Secret Data

Future Center Secret Data

LC

LC

LC

ONONON ON

ON

ON

OFF

OFF

OFF

OFF

OFF

VRAM

Deciphered Date

Deciphered Date

Deciphered Date

LOW

OFF

OFF

OFF

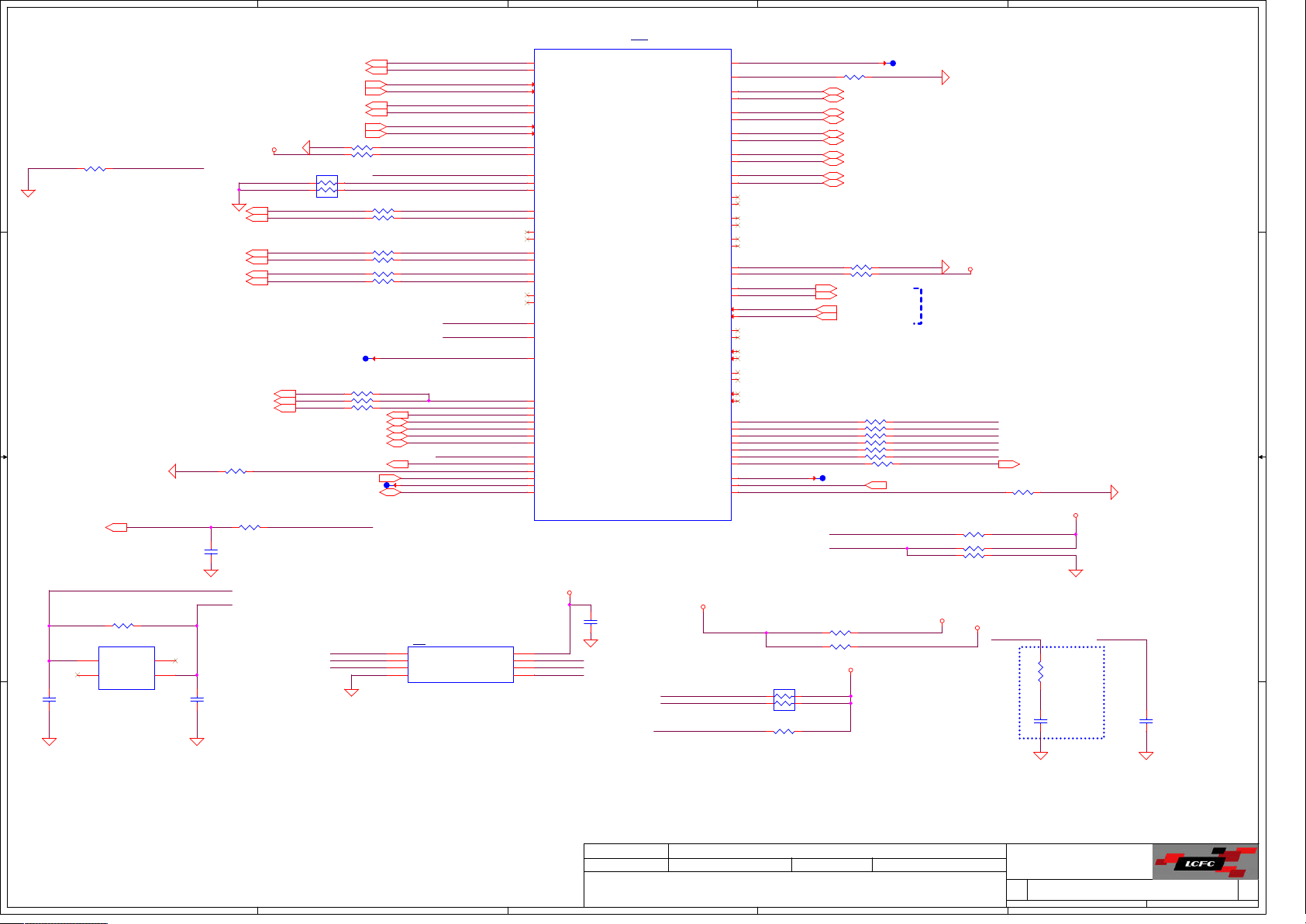

BOM Structure Table

@

ME@

14@

15@

EMC@

EMC_NS@

EMC_PX@

EMC_CZ@

EMC_15@

RF_NS@

RF_PXNS@

UMA@

PX@

EXO@

TOPAZ@

TPM@

AOAC@

HDT@

TS@

CZ@

CZL@

CZPX@

CZLPX@

S4GX4@

M4GX4@

H4GX4@

S2GX4@

M2GX4@

H2GX4@

S2G@

M2G@

H2G@

S1G@

M1G@

H1G@

CZLUMA@

CZUMA@

SIVCD@

HDMI@

STN@

KBL@

2017/02/04

2017/02/04

2017/02/04

D

BOARD

Config.

BOARD

Config.

14''

15''

17''

BOARD_ID1

0: Dis

1: UMA

BOARD_ID0 BOARD_ID3

0

0 1

1 0

BOARD_ID2 reserve

0: No KBL

1: KBL

0

BTO ItemBOM Structure

Not stuff

Connector

For 14" part

For 15" part

EMC Part

EMC reserve Part

EMC GPU part

EMC Carrizo APU part

EMC 15 part

RF reserve Part

RF GPU reserve part

UMA SKU ID part

Discrete GPU SKU part

EXO GPU Part

TOPAZ GPU Part

TPM part

AOAC support part

HDT Debug part

Touch screen part

Carrizo Part

CarrizoL part

Carrizo Discrete Part

CarrizoL Discrete Part

X76 SAMSUNG 2G

X76 MICRON 2G

X76 HYNIX 2G

X76 SAMSUNG 1G

X76 MICRON 1G

X76 HYNIX 1G

SAMSUNG 2G

MICRON 2G

HYNIX 2G

SAMSUNG 1G

MICRON 1G

HYNIX 1G

CarrizoL UMA Part

Carrizo UMA Part

SIV COST down material

HDMI Logo

Stoney part

Key board backlight part

itle

itle

itle

T

T

T

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Saturday, February 04, 2017

Saturday, February 04, 2017

Date: Sheet

Date: Sheet

Date: Sheet

Saturday, February 04, 2017

320AST

320AST

320AST

E

o

o

o

f

3 50

f

3 50

f

3 50

0.2

0.2

0.2

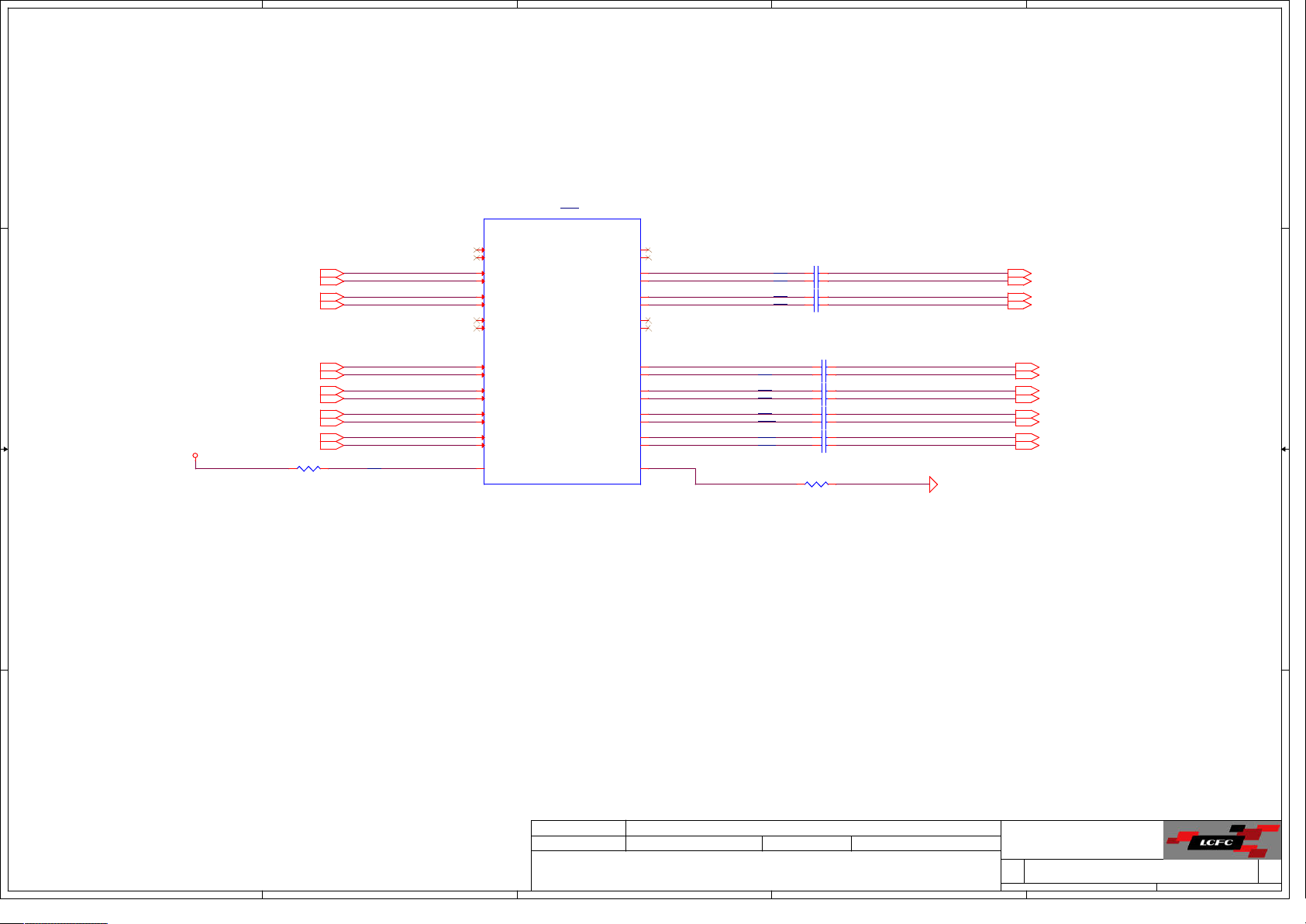

5

D D

PCIE_PRX_DTX_P131

WLAN

LAN

C C

GPU

+0.95VS

PCIE_PRX_DTX_N131

PCIE_PRX_DTX_P228

PCIE_PRX_DTX_N228

PCIE_CRX_GTX_P015

PCIE_CRX_GTX_N015

PCIE_CRX_GTX_P115

PCIE_CRX_GTX_N115

PCIE_CRX_GTX_P215

PCIE_CRX_GTX_N215

PCIE_CRX_GTX_P315

PCIE_CRX_GTX_N315

1 2

with BOM strcture control, RC1 change to 196_0402_1% for Stoney and Carrizo

CarrizoL not support GFX4-GFX7

4

PCIE_PRX_DTX_P1

PCIE_PRX_DTX_N1

PCIE_PRX_DTX_P2

PCIE_PRX_DTX_N2

PCIE_CRX_GTX_P0

PCIE_CRX_GTX_N0

PCIE_CRX_GTX_P1

PCIE_CRX_GTX_N1

PCIE_CRX_GTX_P2

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P3

PCIE_CRX_GTX_N3

P_TX_ZVDD

RC1196_0402_1% STN@

R10

U4

U5

R8

R5

R4

N4

N5

L5

L4

J5

J4

G5

G4

D7

E7

U8

P_GPP_RXP0

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_GFX_RXP0

P_GFX_RXN0

P_GFX_RXP1

P_GFX_RXN1

P_GFX_RXP2

P_GFX_RXN2

P_GFX_RXP3

P_GFX_RXN3

P_ZVDDP

@

UC2B

PCIE

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

FT4 REV 0.93

AMD-STON EY-FT4_BGA769

P_ZVSS

3

D2

D1

C2

C1

B2

B1

A3

B3

A4

B4

A5

B5

A6

B6

A7

B7

W8

P_RX_ZVDD

PCIE_PTX_DRX_P1

PCIE_PTX_DRX_N1

PCIE_PTX_DRX_P2

PCIE_PTX_DRX_N2

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_N3

1 2

CC1 0.1U_020 1_6.3V6-K

1 2

CC2 0.1U_020 1_6.3V6-K

1 2

CC3 0.1U_020 1_6.3V6-K

1 2

CC4 0.1U_020 1_6.3V6-K

CC5 0.22U_02 01_6.3V6-KPX@

CC6 0.22U_02 01_6.3V6-KPX@

CC7 0.22U_02 01_6.3V6-KPX@

CC8 0.22U_02 01_6.3V6-KPX@

CC9 0.22U_02 01_6.3V6-KPX@

CC10 0.22U_02 01_6.3V6-KPX@

CC11 0.22U_02 01_6.3V6-KPX@

CC12 0.22U_02 01_6.3V6-KPX@

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

2

RC3196_0402_1% STN@

PCIE_PTX_C_DRX_P1

PCIE_PTX_C_DRX_N1

PCIE_PTX_C_DRX_P2

PCIE_PTX_C_DRX_N2

PCIE_CTX_C_GRX_P0

PCIE_CTX_C_GRX_N0

PCIE_CTX_C_GRX_P1

PCIE_CTX_C_GRX_N1

PCIE_CTX_C_GRX_P2

PCIE_CTX_C_GRX_N2

PCIE_CTX_C_GRX_P3

PCIE_CTX_C_GRX_N3

PCIE_PTX_C_DRX_P1 31

PCIE_PTX_C_DRX_N1 31

PCIE_PTX_C_DRX_P2 28

PCIE_PTX_C_DRX_N2 28

PCIE_CTX_C_GRX_P0 15

PCIE_CTX_C_GRX_N0 15

PCIE_CTX_C_GRX_P1 15

PCIE_CTX_C_GRX_N1 15

PCIE_CTX_C_GRX_P2 15

PCIE_CTX_C_GRX_N2 15

PCIE_CTX_C_GRX_P3 15

PCIE_CTX_C_GRX_N3 15

1

WLAN

LAN

GPU

B B

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

017/02/0 4

017/02/0 4

017/02/0 4

2

2

2

3

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2017/02/0 4

2017/02/0 4

2017/02/0 4

2

Title

FT4 (PCIE I/F)

FT4 (PCIE I/F)

FT4 (PCIE I/F)

Si

Si

Si

ze Document Number Rev

ze Document Number Rev

ze Document Number Rev

C

C

C

ustom

ustom

ustom

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

Saturday, February 04, 2017

Saturday, February 04, 2017

Saturday, February 04, 2017

320AST

320AST

320AST

4 50

4 50

4 50

1

0

0

0

.2

.2

.2

5

D D

C C

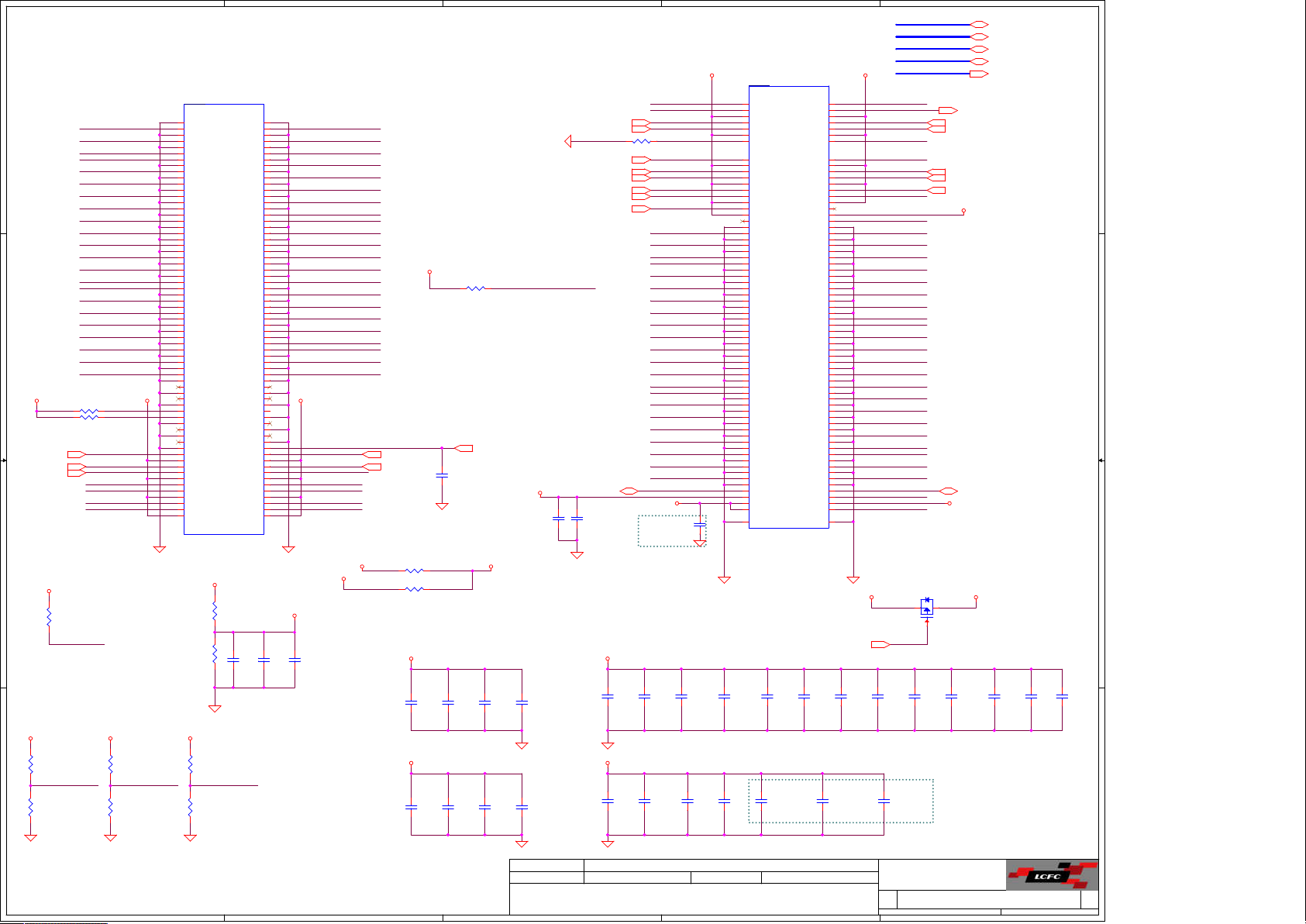

MEM_MB_RST#12

B B

MEM_MB_EVENT#12

DDRB_MA16_RAS#12

DDRB_MA15_CAS#12

DDRB_MA14_WE#12

4

DDRB_MA[13..0]12

DDRB_BG112

DDRB_ACT#12

DDRB_BA012

DDRB_BA112

DDRB_BG012

DDRB_DM[7..0]12

DDRB_CLK012

DDRB_CLK0#12

DDRB_CLK112

DDRB_CLK1#12

1 2

RC240 10_0402_5%

DDRB_CKE012

DDRB_CKE112

DDRB_ODT012

DDRB_ODT112

DDRB_CS0#12

DDRB_CS1#12

TC86@

1

1

TC70@

DDRB_MA0

DDRB_MA1

DDRB_MA2

DDRB_MA3

DDRB_MA4

DDRB_MA5

DDRB_MA6

DDRB_MA7

DDRB_MA8

DDRB_MA9

DDRB_MA10

DDRB_MA11

DDRB_MA12

DDRB_MA13

DDRB_BG1

DDRB_ACT#

DDRB_BA0

DDRB_BA1

DDRB_BG0

DDRB_DM0

DDRB_DM1

DDRB_DM2

DDRB_DM3

DDRB_DM4

DDRB_DM5

DDRB_DM6

DDRB_DM7

DDRB_DQS0

DDRB_DQS#0

DDRB_DQS1

DDRB_DQS#1

DDRB_DQS2

DDRB_DQS#2

DDRB_DQS3

DDRB_DQS#3

DDRB_DQS4

DDRB_DQS#4

DDRB_DQS5

DDRB_DQS#5

DDRB_DQS6

DDRB_DQS#6

DDRB_DQS7

DDRB_DQS#7

DDRB_CLK0

DDRB_CLK0#

DDRB_CLK1

DDRB_CLK1#

MEM_MB_RST#_R

MEM_MB_EVENT#

DDRB_CKE0

DDRB_CKE1

DDRB_ODT0

DDRB_ODT1

DDRB_CS0#

DDRB_CS1#

DDRB_MA16_RAS#

DDRB_MA15_CAS#

DDRB_MA14_WE#

+MEM_VREF

APU_M_VREFDQ

AG38

M_ADD0

W35

M_ADD1

W38

M_ADD2

W34

M_ADD3

U38

M_ADD4

U37

M_ADD5

U34

M_ADD6

R35

M_ADD7

R38

M_ADD8

N38

M_ADD9

AG34

M_ADD10

R34

M_ADD11

N37

M_ADD12

AN35

M_ADD13

L38

M_ADD14/M_BG1

L35

M_ADD15/M_ACT_L

AJ38

M_BANK0

AG35

M_BANK1

N34

M_BANK2/M_BG0

B35

M_DM0

D40

M_DM1

K40

M_DM2

T41

M_DM3

AE41

M_DM4

AL40

M_DM5

AU40

M_DM6

BA37

M_DM7

B36

M_DQS_H0

A36

M_DQS_L0

E40

M_DQS_H1

D41

M_DQS_L1

L40

M_DQS_H2

K41

M_DQS_L2

U41

M_DQS_H3

U40

M_DQS_L3

AF41

M_DQS_H4

AE40

M_DQS_L4

AM40

M_DQS_H5

AM41

M_DQS_L5

AV40

M_DQS_H6

AV41

M_DQS_L6

BA36

M_DQS_H7

AY36

M_DQS_L7

AC35

M_CLK_H0

AC34

M_CLK_L0

AA34

M_CLK_H1

AA32

M_CLK_L1

AE38

M_CLK_H2

AE37

M_CLK_L2

AA37

M_CLK_H3

AA38

M_CLK_L3

G38

M_RESET_L

AA41

M_EVENT_L

J38

M0_CKE0

J34

M0_CKE1

L34

M1_CKE0

J37

M1_CKE1

AN37

M0_ODT0

AU38

M0_ODT1

AL34

M1_ODT0

AN34

M1_ODT1

AL35

M0_CS_L0

AR37

M0_CS_L1

AJ34

M1_CS_L0

AR38

M1_CS_L1

AJ37

M_RAS_L/M_RAS_L_ADD16

AN38

M_CAS_L/M_CAS_L_ADD15

AL38

M_WE_L/M_W E_L_ADD14

AA40

M_VREF

Y41

M_VREFDQ

@

UC2A

MEMORY

M_ZVDDIO_MEM_S3

FT4 REV 0.93

AMD-STONEY-FT4_BGA769

3

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

A34

B34

A38

B38

A33

B33

A37

B37

B41

C40

F41

G40

A40

B40

E41

F40

J40

J41

N40

N41

H40

H41

M40

M41

R40

T40

W40

Y40

P40

P41

V40

V41

AD41

AD40

AH41

AH40

AB40

AC40

AF40

AG40

AK41

AK40

AP41

AP40

AJ41

AJ40

AN41

AN40

AT40

AU41

AY40

BA40

AR40

AT41

AW40

AY41

BA38

AY37

BA34

BA33

AY39

AY38

AY35

AY34

AB41

DDRB_DQ0

DDRB_DQ1

DDRB_DQ2

DDRB_DQ3

DDRB_DQ4

DDRB_DQ5

DDRB_DQ6

DDRB_DQ7

DDRB_DQ8

DDRB_DQ9

DDRB_DQ10

DDRB_DQ11

DDRB_DQ12

DDRB_DQ13

DDRB_DQ14

DDRB_DQ15

DDRB_DQ16

DDRB_DQ17

DDRB_DQ22

DDRB_DQ23

DDRB_DQ20

DDRB_DQ21

DDRB_DQ19

DDRB_DQ18

DDRB_DQ24

DDRB_DQ25

DDRB_DQ26

DDRB_DQ27

DDRB_DQ29

DDRB_DQ28

DDRB_DQ30

DDRB_DQ31

DDRB_DQ36

DDRB_DQ32

DDRB_DQ39

DDRB_DQ35

DDRB_DQ33

DDRB_DQ37

DDRB_DQ34

DDRB_DQ38

DDRB_DQ41

DDRB_DQ44

DDRB_DQ43

DDRB_DQ47

DDRB_DQ45

DDRB_DQ40

DDRB_DQ46

DDRB_DQ42

DDRB_DQ54

DDRB_DQ53

DDRB_DQ50

DDRB_DQ52

DDRB_DQ49

DDRB_DQ48

DDRB_DQ51

DDRB_DQ55

DDRB_DQ60

DDRB_DQ57

DDRB_DQ58

DDRB_DQ59

DDRB_DQ61

DDRB_DQ56

DDRB_DQ63

DDRB_DQ62

MB_ZVDDIO

DDRB_DQ[63..0] 12

1 2

RC10 39.2_0402_1%

2

DDRB_DQS[0..7]12

DDRB_DQS#[0..7]12

DDRB_DQS[0..7]

DDRB_DQS#[0..7]

1

DATA16--DATA23 Byte internal swap

DATA24--DATA31 Byte internal swap

DATA32--DATA39 Byte internal swap

DATA40--DATA47 Byte internal swap

DATA48--DATA55 Byte internal swap

DATA56--DATA63 Byte internal swap

+1.2V

A A

Ti

Ti

Ti

tle

tle

curity Classification

curity Classification

curity Classification

Se

Se

Se

Issue

Issue

Issue

d Date

d Date

d Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENTER.

3

20

20

20

17/02/04

17/02/04

17/02/04

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2017/02/04

2017/02/04

2017/02/04

tle

FT4 (MEM)

FT4 (MEM)

FT4 (MEM)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ustom

ustom

ustom

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

rday, February 04, 2017

rday, February 04, 2017

rday, February 04, 2017

Satu

Satu

Satu

320AST

320AST

320AST

1

f

5 50

f

5 50

f

5 50

o

o

o

.2

.2

.2

0

0

0

RPC10

1K_0404_4P2R_5%

1 4

2 3

1

CC1286

2

@

APU_PWROK

STN@

5

0.01U_0201_25V6-K

1

1

CC1287

CC1288

2

2

@

@

0.01U_0201_25V6-K

0.01U_0201_25V6-K

1

CC1276

0.01U_0201_25V6-K

EMC@

2

+1.8VS+1.8VS

5

G

S

G

2

QC6B

DMN5L06DWK-7 2N SOT363-6

S

61

D

STN@

QC6A

DMN5L06DWK-7 2N SOT363-6

D

STN@

34

APU_SVT50

APU_SVC50

APU_SVD50

H_PROCHOT#35,47

1000P_0402_25V7-K

+3VALW_APU

EC_SMB_DA3APU_SID

RC249 0_0402_5%

RC213 22_0402_5%

RC215 22_0402_5%

RC31 0_0402_5%@

APU_SVT_L

12

CC210

@

1 2

1 2

1 2

1 2

APU_PWROK50

EC_SMB_CK3 16,30,35

EC_SMB_DA3 16,30,35

12

APU_SVT

APU_SVC

APU_SVD

+1.8VS

12

RC18

300_0402_5%

D D

C C

B B

APU_RST#

PLACE CC16 CAPS CLOSE TO APU,CRB reserve 27pf

1

CC16

150P_0402_50V8-J

@

2

+1.8VS

12

RC19

300_0402_5%

APU_PWROK

PLACE CC17 CAPS CLOSE TO APU,CRB reserve 27pf

1

CC17

150P_0402_50V8-J

@

2

APU_SIC EC_SMB_CK3

With HDT+ Header

+1.8VS

RC7

1K_0402_5%

1 2

APU_TRST#

A A

2

CC84

0.01U_0201_10V6K

1

1 2

RC76 33_0402_5%HDT@

5

1 8

2 7

RPC17

10K_0804_8P4R_5%

HDT@

3 6

4 5

APU_TRST#_R

JHDT1

@

1

1

2

3

3

4

5

5

6

7

7

8

9

9

10

11

11

12

13

13

14

15

15

16

17

17

18

19

19

20

SAMTE_ASP-136446-07-B

2

4

6

8

10

12

14

16

RC273 33_0402_5%HDT@

18

20

APU_TCK

APU_TMS

APU_TDI

APU_TDO

APU_PWROK_BUF

APU_RST#_BUF

APU_DBRDY

1 2

APU_TEST19_PLLTEST0

APU_TEST18_PLLTEST1

RC239100K_0402_5% @

4

APU_SVT_L

APU_SVC_L

APU_SVD_L

APU_SIC

APU_SID

ALERT#

APU_PROCHOT#_R

APU_PWROK

APU_RST#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

Core_type

4

AM15

AM17

AM19

AR13

AR15

AR17

APU_DBREQ#

H27

E27

D27

B30

B29

A30

A31

G25

D29

B25

A27

B27

B26

A29

A26

A25

D9

D11

D13

E4

E31

H11

H13

L11

AE34

AN8

AP13

AP15

AP17

AU4

AU13

AU15

AU17

AV7

AV9

AV11

AV13

AV15

AV17

AY3

AY7

@

1K_0804_8P4R_5%

SVT

SVC

SVD

SIC

SID

ALERT_L

PROCHOT_L

PWROK

RESET_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

RSVD_16

RSVD_17

RSVD_18

RSVD_19

RSVD_20

RSVD_21

RSVD_22

RSVD_23

RSVD_24

RSVD_25

RSVD_26

RSVD_27

RSVD_28

RSVD_29

RSVD_30

RSVD_31

RPC5

2

1

UC2C

DISPLAY/SVI2/JTAG/TEST

DP_STEREOSYNC/TEST36

VDDIO_MEM_S3_SENSE

FT4 REV 0.93

AMD-STONEY-FT4_BGA769

+1.8VS+1.8VS

18

27

36

45

APU_PWROK

APU_RST#

CC213

0.01U_0201_10V6K

HDT@

DP_BLON

DP_DIGON

DP_VARY_BL

DP_AUX_ZVSS

DP_ZVSS

DP0_AUXP

DP0_AUXN

DP0_HPD

DP1_AUXP

DP1_AUXN

DP1_HPD

DP2_AUXP

DP2_AUXN

DP2_HPD

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP2_TXP0

DP2_TXN0

DP2_TXP1

DP2_TXN1

DP2_TXP2

DP2_TXN2

DP2_TXP3

DP2_TXN3

TEST4

TEST5

TEST6

TEST9

TEST10

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST28_H

TEST28_L

TEST31

TEST41

VDDCR_CPU_SENSE

VDDCR_NB_SENSE

VDDP_SENSE

VSS_SENSE_A

VSS_SENSE_B

0.1U_0201_6.3V6-K

APU_TDIAPU_DBREQ#

B23

B24

A24

D21

B18

G15

H15

D15

G17

H17

D17

G19

H19

D19

A9

B9

A10

B10

A11

B11

A12

B12

A14

B14

A15

B15

A16

B16

A17

B17

A19

B19

A20

B20

A21

B21

A22

B22

H29

G29

H25

R32

N32

G21

H21

D23

E23

A28

B28

N8

N10

H31

D25

B31

D31

E33

D35

AM21

D33

AM23

UC6

3

2A

2

GND

1

1A

2

CC212

0.01U_0201_10V6K

1

@

CC25

HDT@

DP_ENBKL

DP_ENVDD

DP_EDP_PWM

DP_150_ZVSS

DP_2K_ZVSS

APU_EDP_AUX

APU_EDP_AUX#

APU_EDP_HPD

APU_DDC_CLK

APU_DDC_DATA

APU_HDMI_HPD

TEST5

TEST9

TEST10

APU_TEST14_BP0

APU_TEST15_BP1

APU_TEST16_BP2

APU_TEST17_BP3

APU_TEST18_PLLTEST1

APU_TEST19_PLLTEST0

APU_TEST28_H_PLLCHARZ

APU_TEST28_L_PLLCHARZ

APU_TEST31_MEM_TEST

APU_TEST36_STEREOSYNC

TEST41

APU_VDDCORE_SEN_H

APU_VDDNB_SEN_H

VDDIO_MEM_S3_SENSE

VDD_095_FB_H

APU_VSS_SEN_L

VSS_SENSE_B

APU_EDP_TX0+

APU_EDP_TX0APU_EDP_TX1+

APU_EDP_TX1-

APU_HDMI_TX2+

APU_HDMI_TX2APU_HDMI_TX1+

APU_HDMI_TX1APU_HDMI_TX0+

APU_HDMI_TX0APU_HDMI_CLK+

APU_HDMI_CLK-

1

2

2Y

VCC

1Y

SN74LVC2G07YZPR_WCSP6HDT@

RC12 150_0402_1%

RC55 2K_0402_1%

+1.8VS+1.8VS

4

5

6

3

1 2

1 2

APU_EDP_AUX 23

APU_EDP_AUX# 23

APU_EDP_HPD 23

APU_DDC_CLK 24

APU_DDC_DATA 24

APU_HDMI_HPD 24

APU_EDP_TX0+ 23

APU_EDP_TX0- 23

APU_EDP_TX1+ 23

APU_EDP_TX1- 23

APU_HDMI_TX2+ 24

APU_HDMI_TX2- 24

APU_HDMI_TX1+ 24

APU_HDMI_TX1- 24

APU_HDMI_TX0+ 24

APU_HDMI_TX0- 24

APU_HDMI_CLK+ 24

APU_HDMI_CLK- 24

1

TC14@

1

TC80@

1

TC81@

1 2

RC21 1K_0402_5%@

1

TC18@

1 2

RC23 1K_0402_5%@

1 2

RC24 1K_0402_5%@

1

TC21@

1

TC23@

1

TC25@

1

TC78@

APU_VDDCORE_SEN_H 50

APU_VDDNB_SEN_H 50

1

@

TC76

1

@

TC26

1 2

RC236 0_0402_5%

1

@

TC77

12

12

RC32

RC36

300_0402_5%

300_0402_5%

APU_PWROK_BUF

APU_RST#_BUF

3

2

APU_DDC_CLK

APU_DDC_DATA

APU_EDP_HPD

eDP

ALERT#

APU_PROCHOT#_R

HDMI

To EDP pan el

eDP

HDMI

DP_EDP_PWM

12

RC11

100K_0402_5%

RPC141K_0404_4P2R_5%

14

23

1 2

RC28 1K_0402_5%

1 2

RC27 1K_0402_5%

@

APU_VDD_SEN_L 50

APU_VDDNB_SEN_H

APU_VDDCORE_SEN_H

APU_VDD_SEN_L

1

1

1

APU_TEST31_MEM_TEST

+1.8VS

Reserve follow CRB

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTU RE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTU RE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTU RE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

TC27@

TC28@

TC29@

1 2

@

1 2

@

2017/02/04

2017/02/04

2017/02/04

RC274

39.2_0402_1%

RC275

39.2_0402_1%

+1.8VS

DP_ENVDD

12

RC13

100K_0402_5%

@

DP_ENBKL

12

RC14

100K_0402_5%

@

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

+3VALW_APU

RC71

10K_0402_5%

1 2

61

D

2

G

S

+3VALW_APU

RC73

10K_0402_5%

@

1 2

61

D

2

G

S

LCD Power IC can change for PCH_ENVDD for cost down

+3VALW_APU

RC75

10K_0402_5%

@

1 2

61

D

2

G

S

@

PCH_ENBKL con EC 1.8V level GPI pin cost down

2017/02/04

2017/02/04

2017/02/04

1 4

2 3

1 2

RC35 100K_0402_5%

+3VS_APU

12

RC70

4.7K_0402_5%

34

D

5

QC8B

G

DMN5L06DWK-7 2N SOT363-6

S

QC8A

DMN5L06DWK-7 2N SOT363-6

1 2

RC205 0_0402_5%@

+3VS_APU

12

RC74

4.7K_0402_5%

@

34

D

5

QC9B

G

DMN5L06DWK-7 2N SOT363-6

@

S

QC9A

DMN5L06DWK-7 2N SOT363-6

@

1 2

RC206 0_0402_5%

+3VS_APU

RC77

2.2K_0402_5%

@

1 2

34

D

5

QC10B

G

DMN5L06DWK-7 2N SOT363-6

@

S

QC10A

DMN5L06DWK-7 2N SOT363-6

1 2

RC207 0_0402_5%

1

RPC18

2.2K_0404_4P2R_5%

RPC11

23

14

1K_0404_4P2R_5%

Title

Title

Title

FT4 (DISPLAY/CLK/MISC)

FT4 (DISPLAY/CLK/MISC)

FT4 (DISPLAY/CLK/MISC)

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

Custom

Custom

Custom

Saturday, February 04, 2017

Saturday, February 04, 2017

Saturday, February 04, 2017

Date: Shee t o f

Date: Shee t o f

Date: Shee t o f

+3VS_APU

+1.8VS

PCH_EDP_PWM 23

PCH_ENVDD 23

PCH_ENBKL 23

320AST

320AST

320AST

1

6 50

6 50

6 50

0.2

0.2

0.2

5

1 2

PLT_RST#15,28,30 ,31,35

D D

EC_RSMRST#35

12

RC43

100K_0402_5%@

12

RC66

100K_0402_5%@

RC38 33_0402_5%

1

CC19

150P_04 02_50V8-J

2

RC247

0_0402_5%

DC1

1 2

LRB751V -40T1G_SOD32 3-2

12

@

with QC16,QC17, EC must set EC_RSMRST# a nd EC_SYS_PWRGD reversed compare to DC1 and DC2

C C

EC_SYS_P WRGD35

PCIE_W AKE#_RA

RC88 0_0402_5%

AGPIO5

SDM10U45 LP-7_DFN1006 -2-2

+3VALW_APU

B B

RC84

2.2K_04 02_5%

@

1 2

RC195

15K_0402_5%

1 2

+3VS_APU

RC98 10K_0402_5%PX@

RC100 10K_0402_5%@

A A

RC101 100K_0402_5%@

RC104 2K_0402_5%UMA@

0_0402_5%

2 1

@

1 2

1 2

1 2

1 2

1 2

1 2

12

RC82

100K_0402_5%@

12

12

RC92

DC3

RC85

1K_0402_5%

@

RC196

15K_0402_5%

LRB751V -40T1G_SOD32 3-2

1 2

1 2

RC95

0_0402_5%

DC2

1 2

PCIE_W AKE# 28,31,3 5

RC20

2.2K_04 02_5%

@

TEST0

TEST1

TEST2

RC197

15K_0402_5%

PXS_PW REN_R

VR_VGA_ PWRGD

PXS_PW REN_R

VR_VGA_ PWRGD

12

@

PCIE_RST#_R

+1.8VALW

Connected to 10-ms RC-delay circuit on VDD_18_S5 powe r rail.

(CRB PWR Dea ly: 22K/0.1uF)

12

RC53

10K_0402_5%

RSMRST#_R

1

2

+3VS_APU

12

1

2

CC21

0.1U_020 1_6.3V6-K

RC72

10K_0402_5%

@

SYS_PW RGD_R

CC22

0.1U_020 1_6.3V6-K

PBTN_OUT#35

PM_SLP_ S3#35

PM_SLP_ S5#35

Connect TouchPad to I2C port0 following CRB 10/28

DC4

1 2

LRB751V -40T1G_SOD32 3-2

1

CC38

0.1U_020 1_6.3V6-K

2

SYS_PW RGD_RSYS_RESET#

@

PXS_PWREN_R/PXS_RST#_R/VR_VGA_PWRGD internal pull up 40k

5

4

SYS_RESE T#11

PM_SLP_ S3#

PM_SLP_ S5#

APU_S5_ MUX_CTRL9

AC_PRESE NT35

PCH_WL AN_OFF#31

WLAN_CL KREQ#31

LAN_CLKRE Q#28

PCH_BT_OFF#31

GPU_CLKRE Q#16

HDA_SDIN032

TP_I2C0_S DA_R36

Max ESR < 65K ohm !!

HDA_RST#

HDA_SYNC

HDA_SDOUT

HDA_BITCLK

4

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

1 2

1 2

12

RC191

0_0402_5%

12

RC193

12

0_0402_5%

RC194

0_0402_5%

APU_S5_ MUX_CTRL

1

TC90 @

USB_OC1#25

1 2

RC201 0_0402_5%

TP_I2C0_S CL_R36

RPC3

1 4

2 3

10K_040 4_4P2R_5%

RC102

1 2

20M_040 2_5%

YC1

1 2

32.768K HZ_12.5PF_2 02740-PG14

1

CC23

2

20P_0402_50V8

HDA_RST_AUD IO#32

HDA_SYNC_A UDIO32

HDA_BITCLK_ AUDIO32

HDA_SDOUT_A UDIO32

1 2

RC282 1K_0402_5%

1 2

RC283 1K_0402_5%

1 2

RC284 1K_0402_5%

1 2

RC90 1K_0402_5%

RC39

10K_0402_5%

@

RC47

2K_0402_5%

@

PCIE_RST#_R

RSMRST#_R

PWRBTN#_ RPBTN_OUT#

SYS_PW RGD_R

SYS_RESE T#

PCIE_W AKE#_RA

PM_SLP_ S3#_R

PM_SLP_ S5#_R

AGPIO10

TEST0

TEST1

TEST2

AC_PRESE NT

BOARD_ID0

BOARD_ID1

BOARD_ID3

ODD_EN

PCH_WL AN_OFF#

WLAN_CL KREQ#

LAN_CLKRE Q#

PCH_BT_OFF#

GPU_CLKRE Q#

BOARD_ID2

USB_OC1#

HDA_BITCLK

HDA_SDIN0 _R

HDA_SDIN1

HDA_SDIN2

HDA_RST#

HDA_SYNC

HDA_SDOUT

TP_I2C0_S CL_R

TP_I2C0_S DA_R

I2C1SCL

I2C1SDA

1

CC24

2

1 2

1 2

32K_X1

32K_X2

20P_0402_50V8

3

+3VALW_APU

RC40

10K_0402_5%

UMA@

RC48

2K_0402_5%

PX@

RC41

10K_0402_5%

NOKBL@

1 2

RC49

2K_0402_5%

KBL@

1 2

AE4

PCIE_RST_L/EGPIO26

AG1

RSMRST_L

AD2

PWR_BTN_L/AGPIO0

AE2

PWR_GOOD

AF1

SYS_RESET_L/AGPIO1

AE7

WAKE_L/AGPIO2

AC2

SLP_S3_L

AG4

SLP_S5_L

AB1

S0A3_GPIO/AGPIO10

AA7

S5_MUX_CTRL/EGPIO42

AF2

TEST0

AE1

TEST1/TMS

AC8

TEST2

AH2

AC_PRES/USB_OC4_L/IR_RX0/AGPIO23

AA4

IR_TX0/USB_OC5_L/AGPIO13

AG8

IR_TX1/USB_OC6_L/AGPIO14

AL5

IR_RX1/AGPIO15

AE8

IR_LED_L/LLB_L/AGPIO12

AY32

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

AY31

CLK_REQ1_L/AGPIO115

AV29

CLK_REQ2_L/AGPIO116

AP31

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

AV35

CLK_REQG_L/OSCIN/EGPIO132

AB2

USB_OC0_L/TRST_L/AGPIO16

AG2

USB_OC1_L/TDI/AGPIO17

AJ1

USB_OC2_L/TCK/AGPIO18

AH1

USB_OC3_L/TDO/AGPIO24

AY6

AZ_BITCLK/I2S_BCLK_MIC

BA6

AZ_SDIN0/I2S_DATA_MIC0

AY5

AZ_SDIN1/I2S_LR_PLAYBACK

BA5

AZ_SDIN2/I2S_DATA_PLAYBACK

AY4

AZ_RST_L/I2S_LR_MIC

BA3

AZ_SYNC/I2S_BCLK_PLAYBACK

BA4

AZ_SDOUT/I2S_DATA_MIC1

AY22

I2C0_SCL/EGPIO145

BA22

I2C0_SDA/EGPIO146

AU19

I2C1_SCL/EGPIO147

AV19

I2C1_SDA/EGPIO148

BA2

X32K_X1

AY2

X32K_X2

@

RPC4

1 8

2 7

3 6

4 5

33_0804 _8P4R_5%

3

RC1660

10K_0402_5%

@

1 2

RC1659

2K_0402_5%

@

1 2

ACPI/SD/AZ/GPIO/RTC/MI SC

FT4 REV 0.93

HDA_RST#

HDA_SYNC

HDA_BITCLK

HDA_SDOUT

2

BOARD

BOARD_ID 0 BOARD_ID3

Config.

14''

15''

17''

UC2D

AGPIO3

AGPIO4

AGPIO5

AGPIO8

AGPIO9

AGPIO40

SPKR/AGPIO91

HVBEN_L

RTCCLK

BA28

AY29

AY13

BA14

AY15

BA29

AY14

BA13

BA16

AY16

AY33

BA32

AC5

AC4

AJ7

AK2

AK1

AL4

AJ2

AJ4

AG5

AD1

AJ8

AR29

AP29

AU35

AV33

AU33

AP23

AP25

AR25

AV25

AU23

AP21

AV21

AP19

AV23

AR21

AP27

AN4

SD_WP/EGPIO101

SD_PWR_CTRL/AGPIO102

SD_CD/AGPIO25

SD_CLK/EGPIO95

SD_CMD/EGPIO96

SD_LED/EGPIO93

SD_DATA0/EGPIO97

SD_DATA1/EGPIO98

SD_DATA2/EGPIO99

SD_DATA3/EGPIO100

SCL0/I2C2_SCL/EGPIO113

SDA0/I2C2_SDA/EGPIO114

SCL1/I2C3_SCL/AGPIO19

SDA1/I2C3_SDA/AGPIO20

AGPIO6/LDT_RST_L

AGPIO7/LDT_PWROK

BLINK/USB_OC7_L/AGPIO11

GENINT2_L/AGPIO90

GA20IN/AGPIO126

FANIN0/AGPIO84

FANOUT0/AGPIO85

UART0_CTS_L/EGPIO135

UART0_RXD/EGPIO136

UART0_RTS_L/EGPIO137

UART0_TXD/EGPIO138

UART0_INTR/AGPIO139

UART1_CTS_L/BT_I2S_BCLK/EGPIO140

UART1_RXD/BT_I2S_SDI/EGPIO141

UART1_RTS_L/EGPIO142

UART1_TXD/BT_I2S_SDO/EGPIO143

UART1_INTR/BT_I2S_LRCLK/AGPIO144

AMD-STONEY-FT4_B GA769

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

0

0 1

1 0

@

SD_PWR_ CNTL

ODD_DETECT#

SD_LED

SD_DATA0_R

SD_DATA1_R

SD_DATA2_R

SD_DATA3_R

APU_SMB_ CLK

APU_SMB_ DATA

SCL1

SDA1

AGPIO5

LDT_RST_L

PCH_TP_INT#_ L

AGPIO8

PCH_PW RBT#

BLINK

VR_VGA_ PWRGD

PXS_PW REN_R

PCH_TP_INT#_ R PCH_TP_INT#

@

@

@

@

RPC2

1 4

2 3

@

10K_040 4_4P2R_5%

RC1662

1

TC61

1

TC44

1

TC89

1

TC45

1

TC59

1

TC62@

1

TC63@

1

TC64@

1

TC65@

1

1

1

RC109 1K_0402_5%PX@

0_0402_5%

0

APU_SMB_ CLK 1 2,31

APU_SMB_ DATA 12 ,31

AGPIO3 11

TC83@

TC67@

RC1663

TC84@

PCH_PW RBT# 35

VR_VGA_ PWRGD 1 5,49

PCH_BEEP 32

GATEA20 35

1 2

12

@

0_0402_5%

delete APU_SHUTDOWN# signal for Stoney FT4

HVB_EN

APU_S5_MUX_CTRL 100K pull high follow CRB

BLINK isn't strap pin, don't need pull high

CRB: CARRIZO NEED 10K PD ON UNUSED SDIN

DG: 10K PD

2017/02/04

2017/02/04

2017/02/04

HVB_EN 11,3 5

SUSCLK 11,3 1

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

12

PCH_TP_INT# 36

PXS_PW REN 19,4 8,49

2017/02/04

2017/02/04

2017/02/04

1

+3VS_APU

PCH_TP_INT#

APU_SMB_ CLK

APU_SMB_ DATA

PCH_BT_OFF#

PCH_WL AN_OFF#

PCH_PW RBT#

LAN_CLKRE Q#

WLAN_CL KREQ#

GPU_CLKRE Q#

GATEA20

TP_I2C0_S CL_R

TP_I2C0_S DA_R

PCIE_W AKE#_RA

AC_PRESE NT

PBTN_OUT#

USB_OC1#

PM_SLP_ S3#

PM_SLP_ S5#

APU_S5_ MUX_CTRL

BLINK

PCH_TP_INT#

SD_LED

AGPIO10

GPU_CLKRE Q#

HDA_SDIN0 _R

RSMRST#_R

SYS_PW RGD_R

HDA_SDIN2

HDA_SDIN1

Title

Title

Title

FT4 (GEVENT/GPIO/SD/AZ)

FT4 (GEVENT/GPIO/SD/AZ)

FT4 (GEVENT/GPIO/SD/AZ)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Saturday, February 04, 2017

Saturday, February 04, 2017

Saturday, February 04, 2017

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

1 2

RC1655 10K_0402_5%

RPC9

23

14

2.2K_04 04_4P2R_5 %

RPC6

18

27

36

45

10K_080 4_8P4R_5%

1 2

RC287 10K_0402_5%@

1 2

RC67 10K_0402_5%

1 2

RC78 10K_0402_5%

1 2

RC64 10K_0402_5%UMA@

1 2

RC276 10K_0402_5%

RPC19

1 4

2 3

2.2K_04 04_4P2R_5 %

RPC15

1 8

2 7

3 6

4 5

10K_080 4_8P4R_5%

1 2

RC285 10K_0402_5%

1 2

RC203 2.2K_ 0402_5%@

1 2

RC208 2.2K_ 0402_5%@

1 2

RC248 100K_0402_5%

STN@

1 2

RC277 10K_0402_5%@

1 2

RC1661 10K_0402_5%@

1 2

RC97 10K_0402_5%@

1 2

RC80 10K_0402_5%

1 2

RC65 2K_0402_5%PX@

1 2

RC91 10K_0402_5%@

1 2

RC87 100K_0402_5%

1 2

RC89 100K_0402_5%

1 2

RC241 10K_0402_5%

1 2

RC242 10K_0402_5%

320AST

320AST

320AST

1

7 50

7 50

7 50

+1.8VS

+3VALW_APU

0.2

0.2

0.2

5

SATA_PTX_DRX_P034

SATA_PTX_DRX_N034

HDD

SATA_PRX_DTX_N034

SATA_PRX_DTX_P034

SATA_PTX_DRX_P134

SATA_PTX_DRX_N134

D D

NC2

APU_TS_ON#

CLK_PCIE_GPU15

CLK_PCIE_GPU#15

CLK_PCIE_WLAN31

CLK_PCIE_WLAN#31

CLK_PCIE_LAN28

CLK_PCIE_LAN#28

RC149 10K _0402_5%

48M_X1

48M_X2

4

3

1

2

1 2

RC147 10K _0402_5%

C C

APU_LPC_RST#35

B B

1 2

RC140 1M_0402_5%

YC2

1

OSC1

1

2

NC12OSC2

48MHZ 10PF X1E000021083400

CC28

12P_0402_50V8-J

ODD

SATA_PRX_DTX_N134

SATA_PRX_DTX_P134

+0.95VS

CLK_PCIE_GPU#

CLK_PCIE_WLAN#

CLK_PCIE_LAN# CLK_PCIE_LAN#_R

TPM_CLK30

CLK_PCI_EC11,35

LPC_CLK111

1 2

1 2

RC46 33_0402_5%

1

CC20

150P_0402_50V8-J

2

CC29

12P_0402_50V8-J

RC113 1K_ 0402_1%

RC114 1K_ 0402_1%

RPC13

10K_0404_4P2R_5%

STN@

RC125 22_04 02_5%TPM@

RC126 3.3_0402_1 %

RC127 0_040 2_5%

LPC_CLKRUN#30

LPC_RST#_R

8M ROM

with BOM strcture control, UC3 change to 1.8V SPI ROM for CZ

4

SATA_PTX_DRX_P0

SATA_PTX_DRX_N0

SATA_PRX_DTX_N0

SATA_PRX_DTX_P0

SATA_PTX_DRX_P1

SATA_PTX_DRX_N1

SATA_PRX_DTX_N1

SATA_PRX_DTX_P1

SATA0_DEVSLP_R

EGPIO70

1

UC3

1

/CS

2

DO(IO1)

3

/WP(IO2)

4

GND

W25Q64FWSSIQ_SO8

SATA_CALRN

SATA_CALRP

APU_TS_ON#

CLK_PCIE_GPU_RCLK_PCIE_GPU

CLK_PCIE_GPU#_R

CLK_PCIE_WLAN_RCLK_PCIE_WLAN

CLK_PCIE_WLAN#_R

CLK_PCIE_LAN_RCLK_PCIE_LAN

48M_X1

48M_X2

LPCCLK0

LPCCLK1

LPC_RST#_R

AGPIO21

ODD_DA#

/HOLDor/RESET(IO3)

1 2

1 2

23

14

1 2

RC117 0_040 2_5%

1 2

RC118 0_040 2_5%

1 2

RC119 0_040 2_5%

1 2

RC120 0_040 2_5%

1 2

RC121 0_040 2_5%

1 2

RC122 0_040 2_5%

X14M_25M_48M_OSC

1

TC53 @

1 2

1 2

1 2

LPC_FRAME#11,30,35

LPC_AD030,35

LPC_AD130,35

LPC_AD230,35

LPC_AD330,35

EC_SCI#35

TC91 @

SERIRQ30,35

SPI_CS0#

SPI_SO SPI_HOLD#

VCC

DI(IO0)

CLK

BA10

AY10

AY12

BA12

AY9

BA9

BA8

AY8

AU11

AP11

AY30

AV31

AU31

AU27

BA25

BA24

AY24

BA26

AY28

AY25

AY23

AY27

AY26

AC1

AA8

BA27

AV27

H2

H1

M2

M1

L2

L1

K2

K1

J2

J1

F2

F1

8

7

6

5

SATA_TX0P

SATA_TX0N

SATA_RX0N

SATA_RX0P

SATA_TX1P

SATA_TX1N

SATA_RX1N

SATA_RX1P

SATA_ZVSS

SATA_ZVDDP

SATA_ACT_L/AGPIO130

DEVSLP0/EGPIO67

DEVSLP1/EGPIO70

GFX_CLKP

GFX_CLKN

GPP_CLK0P

GPP_CLK0N

GPP_CLK1P

GPP_CLK1N

GPP_CLK2P

GPP_CLK2N

GPP_CLK3P

GPP_CLK3N

X48M_X1

X48M_X2

X25M_48M_OSC

LPCCLK0/EGPIO74

LPCCLK1/EGPIO75

LFRAME_L

LAD0

LAD1

LAD2

LAD3

LPC_RST_L

LPC_CLKRUN_L/AGPIO88

LPC_PD_L/AGPIO21

LPC_PME_L/AGPIO22

LPC_SMI_L/AGPIO86

SERIRQ/AGPIO87

@

SPI_CLKSPI_WP#

SPI_SI

+VCC_SPI

3

UC2E

CLK/SATA/USB/SPI /LPC

USBCLK/25M_48M_OSC

SPI_CLK/ESPI_CLK/EGPIO117

SPI_DO/ESPI_DAT0/EGPIO121

SPI_DI/ESPI_DAT1/EGPIO120

SPI_HOLD_L/ESPI_DAT3/EGPIO133

SPI_WP_L/ESPI_DAT2/EGPIO122

SPI_TPM_CS_L/AGPIO76

ESPI_ALERT_L/LDRQ0_L

ESPI_RESET_L/KBRST_L/AGPIO129

SPI_CS2_L/ESPI_CS_L/EGPIO119

FT4 REV 0.93

AMD-STONEY-FT4_BGA769

1

CC27

0.1U_0201_6.3V6-K

2

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

USB_HSD6P

USB_HSD6N

USB_HSD7P

USB_HSD7N

USB_SS_ZVSS

USB_SS_ZVDDP

USB_SS_0TXP

USB_SS_0TXN

USB_SS_0RXP

USB_SS_0RXN

USB_SS_1TXP

USB_SS_1TXN

USB_SS_1RXP

USB_SS_1RXN

USB_SS_2TXP

USB_SS_2TXN

USB_SS_2RXP

USB_SS_2RXN

SPI_CS1_L/EGPIO118

+VCC_SPI

SPI_WP#

SPI_HOLD#

SPI_CS0#

CLK_USB48M

AL8

USB_RCOMP

AN7

USB20_P7

AW1

USB20_N7

AW2

USB20_P4

AV1

USB20_N4

AV2

USB20_P5

AU1

USB20_N5

AU2

USB20_P3

AT1

USB20_N3

AT2

USB20_P2

AR1

USB20_N2

AR2

AP1

AP2

AN1

AN2

AM1

AM2

USBSS_CALRN

W4

USBSS_CALRP

W5

USB30_TX_P1

T1

USB30_TX_N1

T2

USB30_RX_P1

V2

USB30_RX_N1

V1

R1

R2

W2

W1

P1

P2

Y2

Y1

SPI_CLK_R

AY17

SPI_SI_R

AY20

SPI_SO_R

BA17

SPI_HOLD#_R

BA18

SPI_WP#_R

BA20

SPI_CS0#_R

AY21

BA21

AGPIO76

AY18

BA30

AY19

EGPIO119

+VCC_SPI

RC138 10K_0402_5%

RC112 11.8K_04 02_1%

1

RC135 0_0402_5%@

RC192 0_0402_5%STN@

RPC8

1 4

2 3

10K_0404_4P2R_5%

1 2

2

1

1 2

USB20_P7 25

USB20_N7 25

USB20_P4 31

USB20_N4 31

USB20_P5 23

USB20_N5 23

USB20_P3 32

USB20_N3 32

USB20_P2 25

USB20_N2 25

1 2

RC123 1K_ 0402_1%

1 2

RC124 1K_ 0402_1%

USB30_TX_P1 25

USB30_TX_N1 25

USB30_RX_P1 25

USB30_RX_N1 25

TC54@

KBRST#

KBRST#

PXS_RST#

1 2

1 2

+VCC_SPI

TC69@

RighT USB (2.0) upper

Blue Tooth

Camera

Card Reader

LEFT USB (3.0) upper

12

RC2090_0402_5%

12

RC1980_0402_5%

12

RC1990_0402_5%

12

RC1330_0402_5%

12

RC1320_0402_5%

12

RC2020_0402_5%

12

RC2430_0402_5%

KBRST# 35

1

USB3.0 port0 must map to USB2.0 port4,

USB3.0 port1 must map to USB2.0 port5,

USB3.0 port2 must map to USB2.0 port6

Remove Finger print

Remove Touch Screen

+0.95VALW

Connect the four USB 3.0 ports to onboard devices first

starting from the lower ports and then the remaining

ports can be used for routing to USB 3.0 connectors.

Less than four USB 3.0 ports can be utilized provided

the unused ports are higher-numbered consecutive

LEFT USB (3.0) upper

ports.

None of the four USB 3.0 ports can be configured

as USB 2.0 external ports.

SPI_CLK

SPI_SI

SPI_SO

SPI_HOLD#

SPI_WP#

SPI_CS0#

1 2

RC279 10K_0402_5%

+3VALW_APU

+1.8VS

12

12

SPI_CLK

RC28010K_0402_5% @

RC28110K_0402_5%

PXS_RST# 15

12

RC14410K_0402_5% STN@

RC139

10_0402_5%

EMC_NS@

1 2

2

CC26

10P_0402_50V8J

EMC_NS@

1

+3VS_APU

EMC

KBRST#

CC1274

EMC_NS@

1 2

1000P_0402_25V7-K

A A

itle

itle

itle

T

T

Secu

Secu

Secu

rity Classification

rity Classification

rity Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

AY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

AY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

AY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

M

M

5

4

M

3

2017/02/04

2017/02/04

2017/02/04

Future Center Secret Data

Future Center Secret Data

Future Center Secret Data

LC

LC

LC

Deciphered Date

Deciphered Date

Deciphered Date

2

2017/02/04

2017/02/04

2017/02/04

T

FT4 (SATA/USB/LPC/SPI)

FT4 (SATA/USB/LPC/SPI)

FT4 (SATA/USB/LPC/SPI)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Saturday, February 04, 2017

Saturday, February 04, 2017

Saturday, February 04, 2017

320AST

320AST

320AST

1

o

o

o

f

8 50

f

8 50

f

8 50

0.2

0.2

0.2

5

+1.2V

+1.2V

D D

+0.95VS

CC221

C C

VCCRTC

B B

A A

1

CC42

CC54

2

22U_0603_6.3V6-M

SIVCD@

1

1

1

CC223

CC222

2

22U_0603_6.3V6-M

RC231 10K_0402_5%

+1.2V

CC224

2

2

22U_0603_6.3V6-M

22U_0603_6.3V6-M

SIVCD@

SIVCD@

1 2

1

1

CC169

CC168

CC170

2

2

0.22U_0201_6.3V6-K

0.22U_0201_6.3V6-K

SIVCD@

SIVCD@

DECOUPLING BETWEEN PROCESSOR AND DIMMs

ACROSS VDDIO AND VSS SPLIT

1

2

1

2

CC37

1

2

CC55

22U_0603_6.3V6-M

CC225

22U_0603_6.3V6-M

SIVCD@

1

2

0.22U_0201_6.3V6-K

1

1

CC56

2

2

22U_0603_6.3V6-M

22U_0603_6.3V6-M

1

1

CC174

2

2

10U_0603_6.3V6M

22U_0603_6.3V6-M

AP2138N-1.5TRG1_SOT23-3

1U_0402_6.3V6K

1

CC172

2

0.22U_0201_6.3V6-K

1

CC57

2

1

CC226

2

UC5

1

Vin

2

GND

1

CC179

2

1

CC58

CC59

2

22U_0603_6.3V6-M

22U_0603_6.3V6-M

SIVCD@

CC227

10U_0603_6.3V6M

SIVCD@

3

Vout

1

CC176

2

180P_0402_50V8-J

SIVCD@

1

2

1 2

+1.8VS

CC194

180P_0402_50V8-J

1

CC53

CC60

2

22U_0603_6.3V6-M

22U_0603_6.3V6-M

SIVCD@

CC228

CC229

1 2

1 2

1000P_0402_25V7-K

1000P_0402_25V7-K

SIVCD@

1 2

RC6

1K_0402_5%

1 2

RC212

0_0402_5%

+RTCBATT

1

2

1U_0402_6.3V6K

1

2

CC258

22U_0603_6.3V6-M

1

CC230

CC203

1 2

2

1000P_0402_25V7-K

1000P_0402_25V7-K

180P_0402_50V8-J

+RTCBATT_APU+RTCBATT

+VDDIO_AZ_APU

12

JCMOS1

SHORT PADS

@

L2N7002KWT1G_SOT323-3

CC192

SDVCD@

1

1

CC185

2

2

1U_0402_6.3V6K

1

CC220

47P_0402_50V8J

RF@

2

1

2

1U_0402_6.3V6K

12

RC8

470_0603_5%

13

D

S

@

+APU_CORE_NB

12

CC207

10U_0603_6.3V6M

1U_0402_6.3V6K

CC236

QC7

4

1

CC214

2

SIVCD@

1

CC234

2

1U_0402_6.3V6K

@

EC_RTCRST#_ON

2

G

+0.775VALW

12

CC208

SDVCD@

1

CC165

2

1U_0402_6.3V6K

+APU_CORE

+0.95VALW

CC182

CC235

1 2

1000P_0402_25V7-K

SIVCD@

10U_0603_6.3V6M

180P_0402_50V8-J

1

CC215

CC216

2

1U_0402_6.3V6K

1

CC219

2

10U_0603_6.3V6M

1 2

1000P_0402_25V7-K

12

RC15

100K_0402_5%

@

+5VALW

1

CC209

2

SDVCD@

1

CC137

2

1U_0402_6.3V6K

SIVCD@

1

CC231

1 2

2

1U_0402_6.3V6K

SIVCD@

EC_RTCRST#_ON 35

1U_0402_6.3V6K

+1.2V

1

2

180P_0402_50V8-J

+VDDCR_FCH_S5

+0.95VS

1000P_0402_25V7-K

UC7

1

VIN1_1

2

VIN1_2

3

VIN2

VCC4EN

G5018RD1U_TDFN8_3X3

STN@

VOUT_1

VOUT_2

3

UC2F

+0.95VALW

2

1

2.2U_0402_6.3V6M

EMC@

+VDDCR_FCH_S5

POWER

VDDCR_NB_1

VDDCR_NB_2

VDDCR_NB_3

VDDCR_NB_4

VDDCR_NB_5

VDDCR_NB_6

VDDCR_NB_7

VDDCR_NB_8

VDDCR_NB_9

VDDCR_NB_10

VDDCR_NB_11

VDDCR_NB_12

VDDCR_NB_13

VDDCR_NB_14

VDDCR_NB_15

VDDCR_NB_16

VDDCR_NB_17

VDDCR_NB_18

VDDCR_NB_19

VDDCR_NB_20

VDDCR_NB_21

VDDCR_NB_22

VDDCR_NB_23

VDDCR_NB_24

VDDCR_NB_25

VDDCR_NB_26

VDDCR_NB_27

VDDCR_NB_28

VDDCR_NB_29

VDDCR_NB_30

VDDCR_NB_31

VDDCR_NB_32

VDDCR_NB_33

VDDCR_NB_34

VDDCR_NB_35

VDDCR_NB_36

VDDCR_NB_37

VDDCR_NB_38

VDDCR_NB_39

VDDCR_NB_40

VDDCR_NB_41

VDDCR_NB_42

VDDCR_NB_43

VDDCR_NB_44

VDDCR_NB_45

VDDCR_NB_46

VDDCR_NB_47

VDDCR_NB_48

VDDCR_NB_49

VDDCR_NB_50

VDD_18_1

VDD_18_2

VDD_18_S5_1

VDD_18_S5_2

VDD_33_1

VDD_33_2

VDD_33_S5_1

VDD_33_S5_2

FT4 REV 0.93

AMD-STONEY-FT4_BGA769

2

2

CC1280

CC1281

1

1

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

EMC_NS@

EMC@

APU_S5_MUX_CTRL 7

CC1282

E9

E11

E13

E15

E17

E19

G7

J7

K11

K13

K15

K17

K19

L7

L10

L15

L17

N7

N11

N13

N15

N17

N19

R7

U7

U11

U13

U15

U17

U19

U21

W7

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AE25

AE27

AE29

AE31

AJ15

AL17

AJ13

AL15

AJ19

AL21

AJ17

AL19

2

1

2.2U_0402_6.3V6M

EMC_NS@

J35

3A

VDDIO_MEM_S3_1

L32

VDDIO_MEM_S3_2

L37

VDDIO_MEM_S3_3

N35

VDDIO_MEM_S3_4

R37

VDDIO_MEM_S3_5

U32

VDDIO_MEM_S3_6

U35

VDDIO_MEM_S3_7

W32

VDDIO_MEM_S3_8

W37

VDDIO_MEM_S3_9

AA35

VDDIO_MEM_S3_10

AC32

VDDIO_MEM_S3_11

AC37

VDDIO_MEM_S3_12

AE32

VDDIO_MEM_S3_13

AE35

VDDIO_MEM_S3_14

AG32

VDDIO_MEM_S3_15

AG37

VDDIO_MEM_S3_16

AJ32

VDDIO_MEM_S3_17

AJ35

VDDIO_MEM_S3_18

AL32

VDDIO_MEM_S3_19

AL37

VDDIO_MEM_S3_20

AR35

VDDIO_MEM_S3_21

K21

VDDCR_CPU_1

K23

VDDCR_CPU_2

K25

VDDCR_CPU_3

K27

VDDCR_CPU_4

K29

VDDCR_CPU_5

K31

VDDCR_CPU_6

N21

VDDCR_CPU_7

N23

VDDCR_CPU_8

N25

VDDCR_CPU_9

N27

VDDCR_CPU_10

N29

VDDCR_CPU_11

N31

VDDCR_CPU_12

U23

VDDCR_CPU_13

U25

VDDCR_CPU_14

U27

VDDCR_CPU_15

U29

VDDCR_CPU_16

U31

VDDCR_CPU_17

AA25

VDDCR_CPU_18

AA27

VDDCR_CPU_19

AA29

VDDCR_CPU_20

AA31

VDDCR_CPU_21

AR4

VDDCR_FCH_S5_1

AR5

VDDCR_FCH_S5_2

AR7

VDDCR_FCH_S5_3

AU7

VDDCR_FCH_S5_4

AJ11

VDDP_S5_1

AL11

VDDP_S5_2

AL13

VDDP_S5_3

AJ21

VDDP_1

AJ23

VDDP_2

AJ25

VDDP_3

AJ27

VDDP_4

AL23

VDDP_5

AL25

VDDP_6

AL27

VDDP_7

AL29

VDDP_8

AM11

VDDBT_RTC_G

AM13

VDDIO_AUDIO

@

8

7

APU_S5_MUX_CTRL

6

SEL

5

9

GND

2

CC1283

1

2.2U_0402_6.3V6M

EMC_NS@

CC162

STN@

CC1284

1

2

+APU_CORE_NB

+1.8VS

+1.8VALW

+3VALW_APU

2

1

2.2U_0402_6.3V6M

EMC@

1

CC217

2

10U_0603_6.3V6M

STN@

1U_0402_6.3V6K

CC1285

1

CC218

2

SIVCD@

1U_0402_6.3V6K

CC232

1 2

SIVCD@

+APU_CORE_NB

1

CC237

2

SIVCD@

+1.8VS

1

CC246

2

1

CC252

2

10U_0603_6.3V6M

CC233

1 2

1000P_0402_25V7-K

1000P_0402_25V7-K

STN@

22U_0603_6.3V6-M

10U_0603_6.3V6M

CC253

CC238

SIVCD@

OK

CC247

1

2

1

1

CC239

2

2

22U_0603_6.3V6-M

1

CC245

2

1U_0402_6.3V6K

SIVCD@

CC251

1 2

1U_0402_6.3V6K

SIVCD@

VDDCR_CPU

VDDCR_NB

VDDCR_GFX

VDDIO_MEM_S3

VDDCR_FCH_S5

VDDP

VDDP_GFX

VDDP_S5

VDD_18

VDD_18_S5

VDD_33

VDD_33_S5

VDDIO_AUDIO

VDDBT_RTC_G

2

1

CC240

CC241

2

22U_0603_6.3V6-M

22U_0603_6.3V6-M

1 2

1000P_0402_25V7-K

RC214

1 2

0_0402_5%

1000P_0402_25V7-K

1

1

1

1

CC242

CC244

CC243

2

2

2

2

22U_0603_6.3V6-M

SIVCD@

+1.8VALW

1

CC249

CC250

2

10U_0603_6.3V6M

+3VS+3VS_APU

Design Guide CRBG FT4

7*22uf 0603

2*1uf 0402

1*180pf 0402

11*22uf 0603

1*1uf 0402

1*180pf 0402

9*22uf 0603

3*1uf 0402

3*180pf 0402

1*10uf 0402

2*1uf 0402

2*1000pf 0402

5*22uf 0603 2*10uf 0603 5*22uf 0603 2*10uf 0603

4*1000pf 0402

1*180pf 0402

1*10uf 0402

1*1uf 0402

1*1000pf 0402

1*10uf 0402

1*1uf 0402

1*1000pf 0402

1*10uf 0402

1*1uf 0402

1*1000pf 0402

1*10uf 0402

1*1uf 0402

1*1000pf 0402

1*10uf 0402

1*1uf 0402

1*1000pf 0402

1*10uf 0402

2*1000pf 0402

22U_0603_6.3V6-M

1

2

1U_0402_6.3V6K

22U_0603_6.3V6-M

CC248

1 2

1000P_0402_25V7-K

SIVCD@

1U_0402_6.3V6K

1*1000pf 0402

1

1

CC195

CC145

2

2

@

180P_0402_50V8-J

+3VALW_APU

1

CC255

2

10U_0603_6.3V6M

11*22uf 0805

2*1uf 0402

1*180pf 0402

11*22uf 0603

1*1uf 0402

1*180pf 0402

9*22uf 0603 2*1uf 0402

split*4 0.22uf 0402

1*180pf 0402 split*2

1*10uf 0402

2*1uf 0402

2*1000pf 0402

4*1000pf 0402

1*180pf 0402

1*10uf 0402

1*1uf 0402

1*1000pf 0402

1*10uf 0402

1*1uf 0402

1*1000pf 0402

1*10uf 0402

1*1uf 0402

1*1000pf 0402

1*10uf 0402

1*1uf 0402

1*1000pf 0402

1*10uf 0402

1*1uf 0402

1*1000pf 0402

1*10uf 0402

2*1000pf 0402

1*1000pf 0402

CC196

@

0.22U_0201_6.3V6-K

follow CRB reserve

1

CC256

2

1

2

1U_0402_6.3V6K

1

CC199

2

@

0.22U_0201_6.3V6-K

CC254

1 2

1000P_0402_25V7-K

SIVCD@

1

1

CC200

2

@

0.22U_0201_6.3V6-K

0.22U_0201_6.3V6-K

11*22uf 0603

1*1uf 0402

1*180pf 0402

15*22uf 0603

8*0.22uf 0402 split *5

1*180pf 0402

9*22uf 0603 2*1uf 0402

split*4 0.22uf 0402

1*180pf 0402 split*2

2*10uf 0603

1*0.22uf 0402

4*10uf 0603

1*0.22uf 0402

1*180pf 0402

1*10uf 0603

1*0.22uf 0402

1*22uf 0603

1*10uf 0603

1*10uf 0603

1*0.22uf 0402

1*10uf 0603

1*10uf 0603

1*0.22uf 0402

3*1uf 0402

1*0.22uf 0402

T

T

T

itle

itle

LC Future Center Secret Data

LC Future Center Secret Data

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS

THIS

THIS

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTU RE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTU RE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTU RE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2017/02/04

2017/02/04

2017/02/04