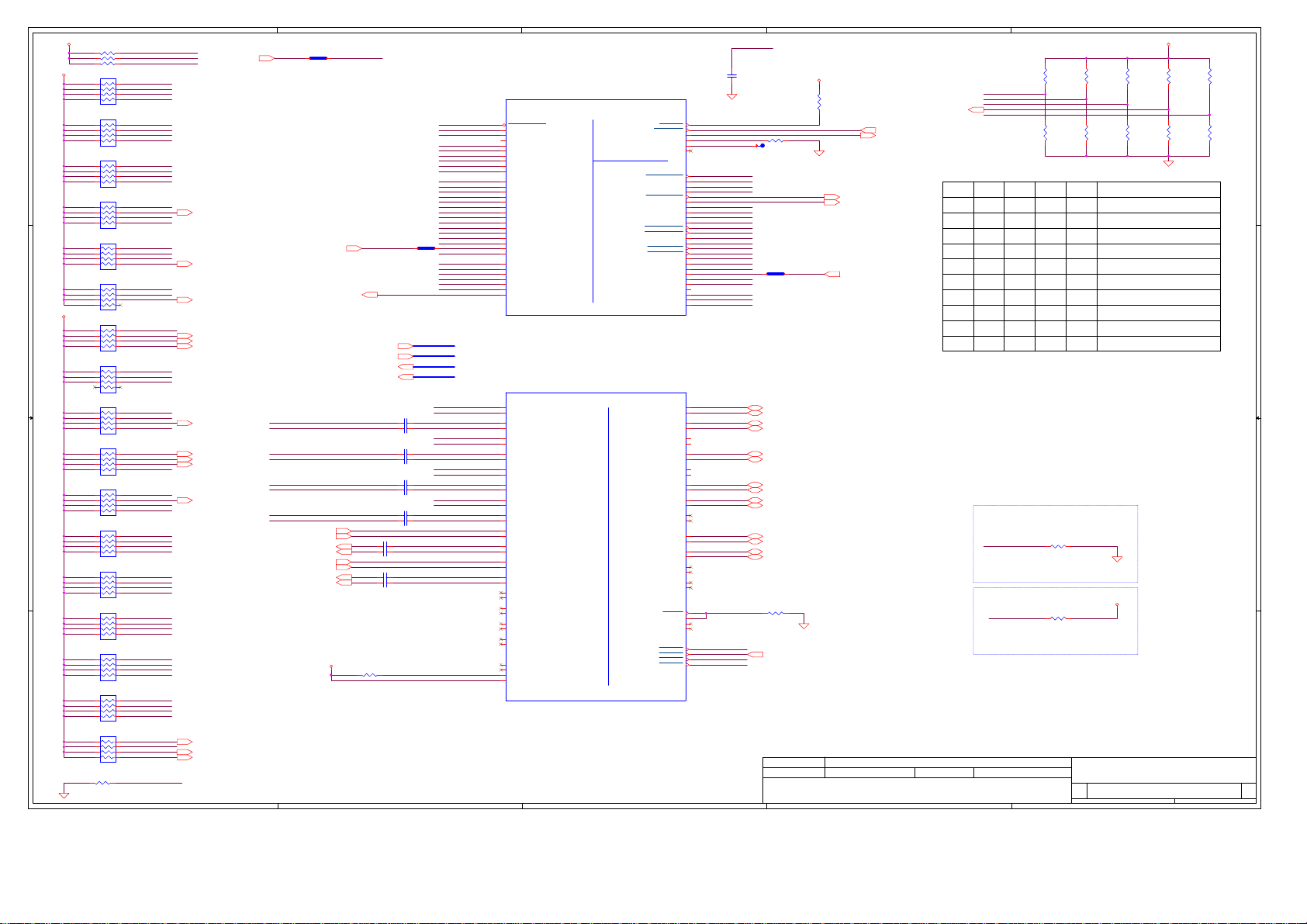

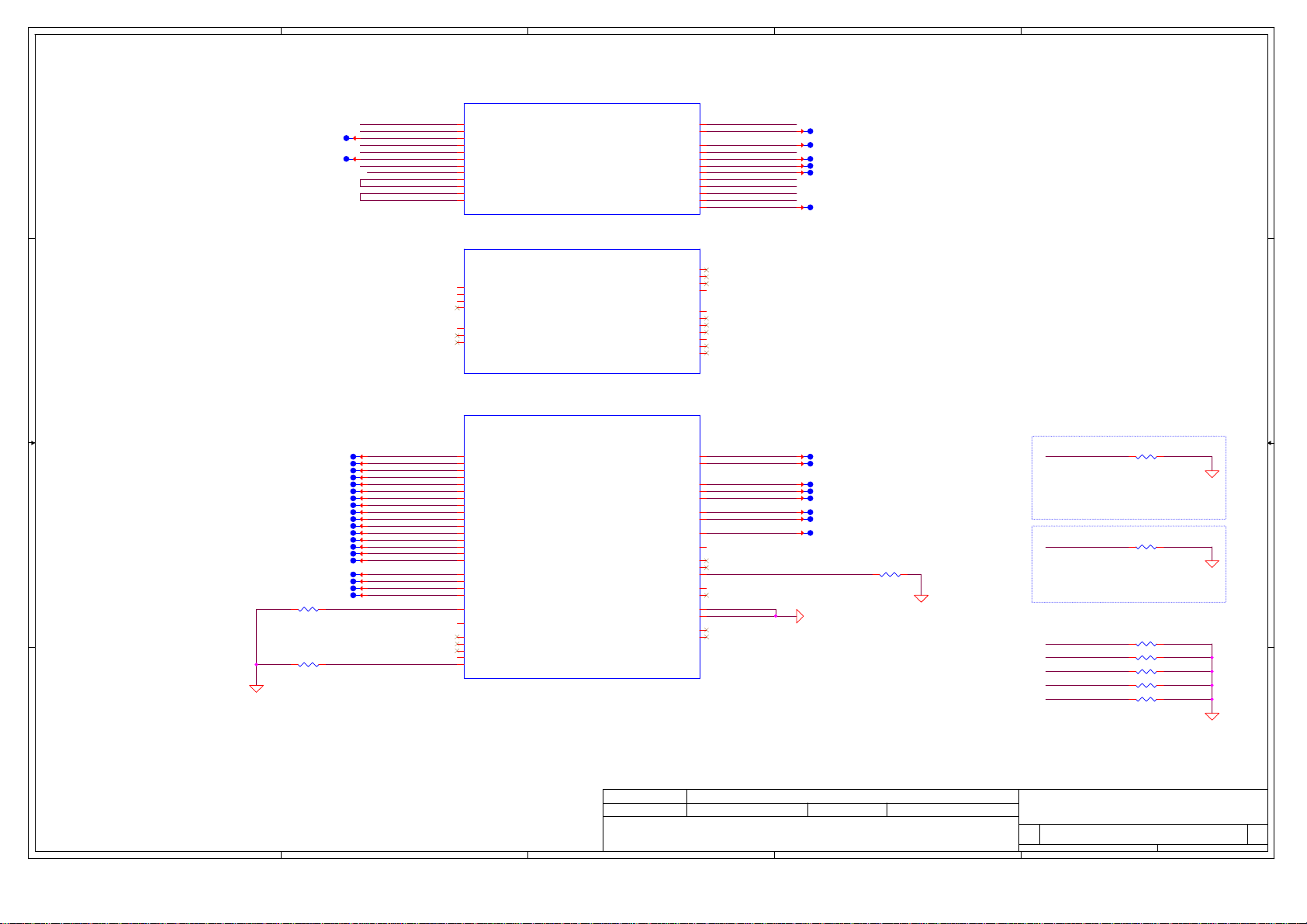

Lenovo IdeaPad 100 series Schematic

A

1 1

B

C

D

E

LCFC Confidential

CG510 M/B Schematics Document

2 2

Intel Broadwell U-Processor with DDRIIIL + NV920

2015-05-09

3 3

4 4

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

REV:0.2

Issued Date

Issued Date

Issued Date

C

2015/02/27

2015/02/27

2015/02/27

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2013/08/05

2013/08/05

2013/08/05

D

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Saturday, May 09, 2015

Saturday, May 09, 2015

Date: Sheet of

Date: Sheet of

Date: Sheet of

Saturday, May 09, 2015

CG510

CG510

CG510

E

1 59

1 59

1 59

0.2

0.2

0.2

A B C

LCFC confidential

File Name : CG510

D

E

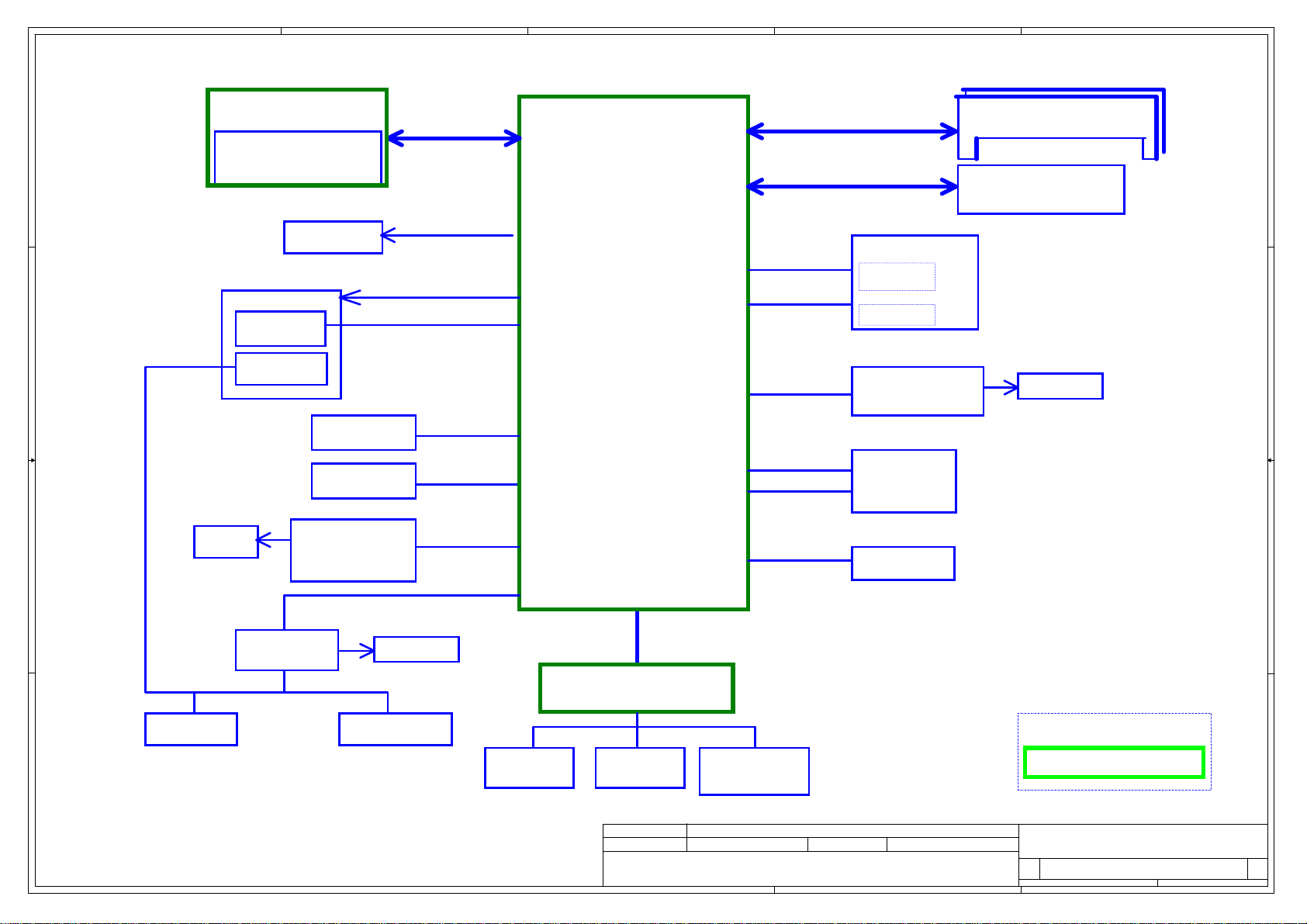

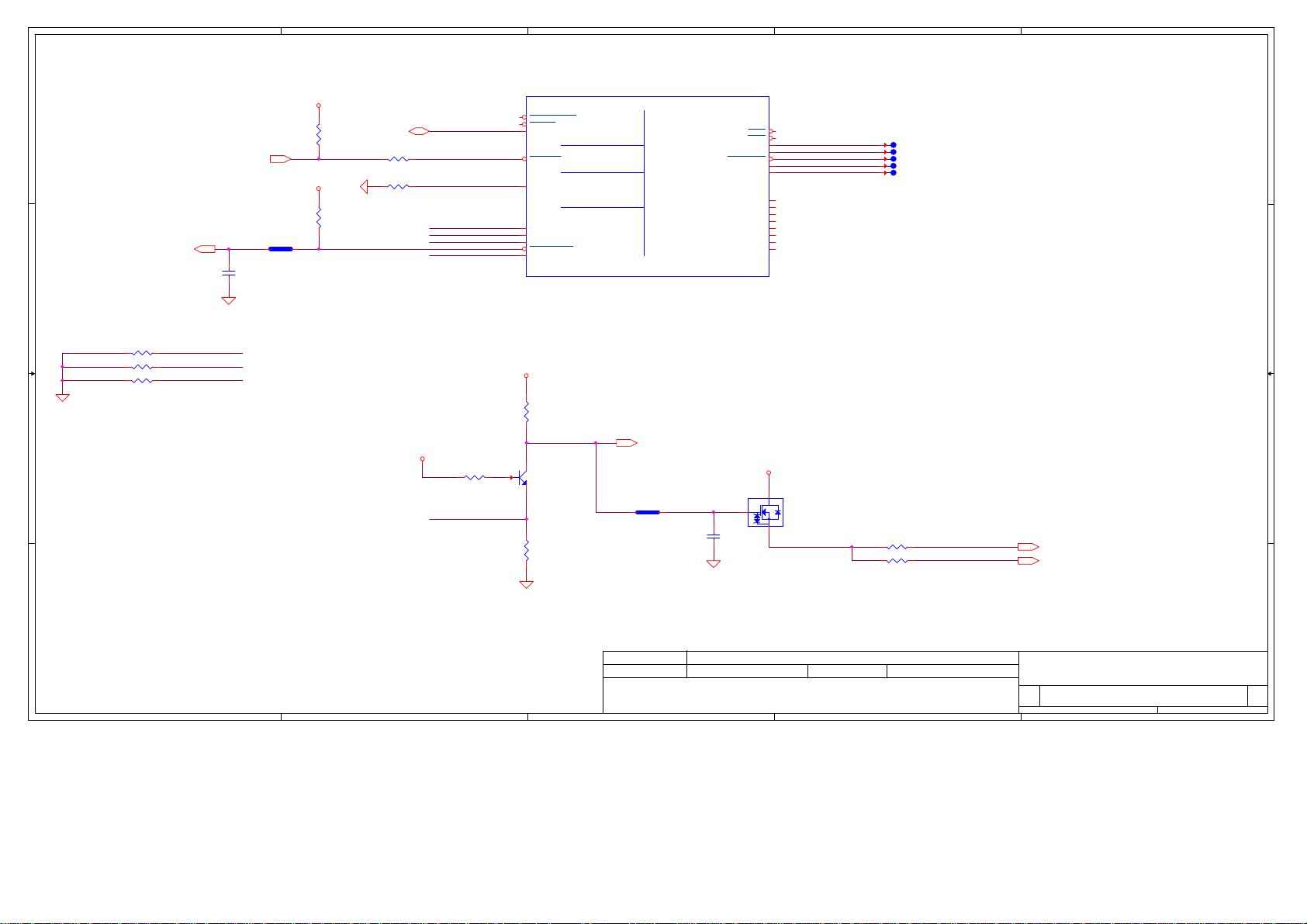

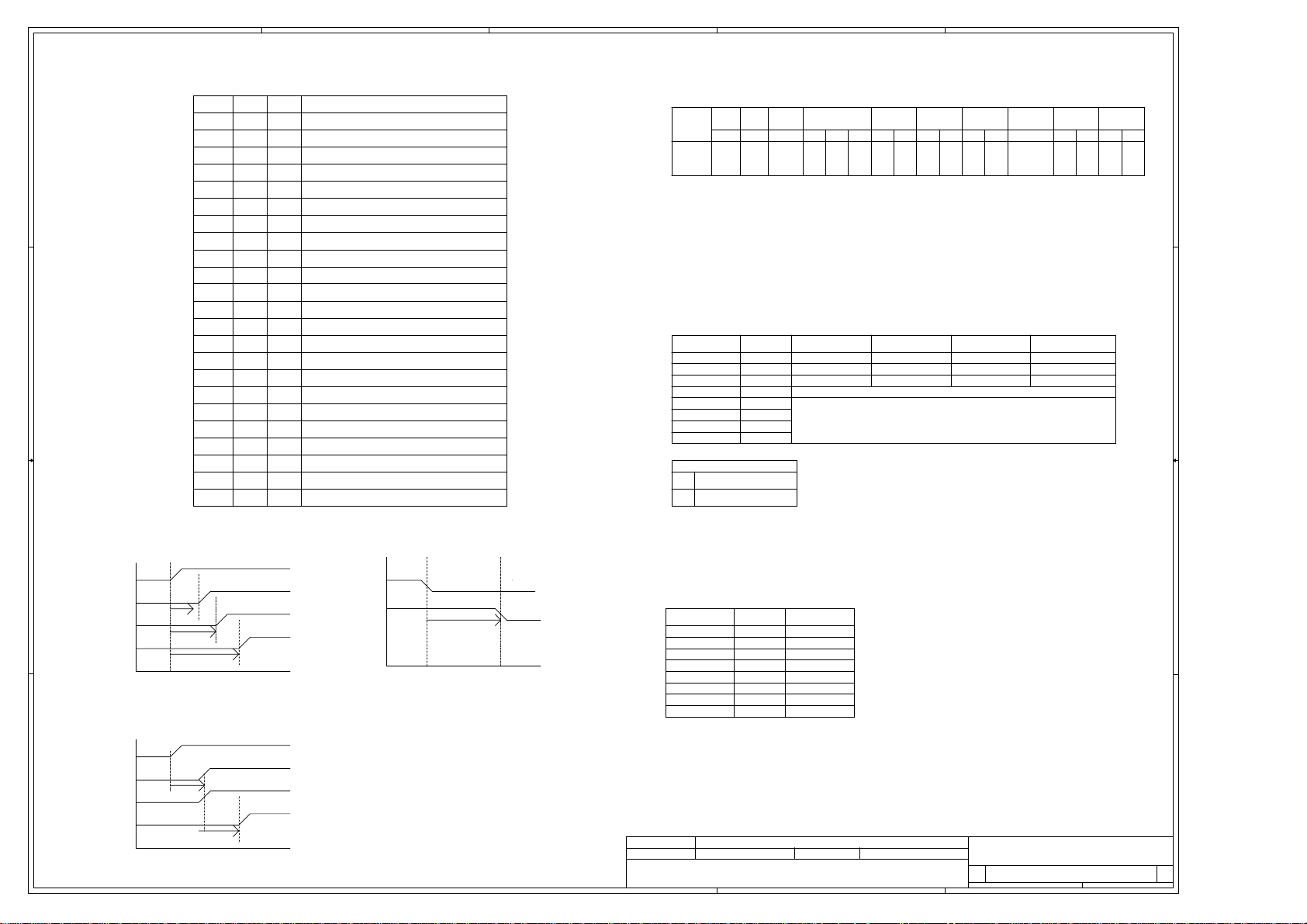

NV (N16V-GM)

GB2B-64 Package

Page 18~28

1 1

VRAM 256/128*16

DDR3L*4 2GB/1GB

Page 19~28

HDMI Conn.

Page 34

PCIe Port5

eDP Conn

Int. Camera

USB2.0 Port5

2 2

3 3

Page 33

RJ45 Conn.

Page 38

Int. MIC Conn.

Page 42

Page 42

LAN Realtek

RTL8106EUL (10M/100M)

Page 37

SATA Port0

SATA Port1

PCIe Port3

PCI-Express

4x Gen2

HDMI

eDP x2 Lane

USB2.0 1x

SATA Gen3SATA HDD

SATA Gen1SATA ODD

PCIe 1x

HD Audio

Intel MCP

Haswell U 15W /

Broadwell U 15W

BGA-1168

40mm*24mm

Page 3~13

Memory BUS (CHA)

1.35V DDR3L 1600 MT/s

Memory BUS (CHB)

1.35V DDR3L 1600 MT/s

USB Left

USB 3.0 1x

USB 2.0 2x

USB2.0 1x

USB 2.0 1x

PCIe 1x

SPI BUS

USB 3.0 Port1

USB 2.0 Port1

USB 2.0 Port2

Cardreader Realtek

RTS5170

NGFF Card

WLAN&BT

Page 40

SPI ROM

8MB

USB2.0 Port3

PCIe Port4

USB2.0 Port6

Page 07

DDR3L-SO-DIMM X1

Page 14,15

UP TO 4G

Memory down 256/128*16

DDR3L*8 4G/2G

Page 41

SD/MMC Conn.

Codec

Conexant CX11802

Page 43

SPK Conn.

Page 43

EC

ITE IT8586E-LQFP

Page 44

Mic

Page 44

4 4

HP&Mic Combo Conn.

Touch Pad Int.KBD

Page 45 Page 45

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

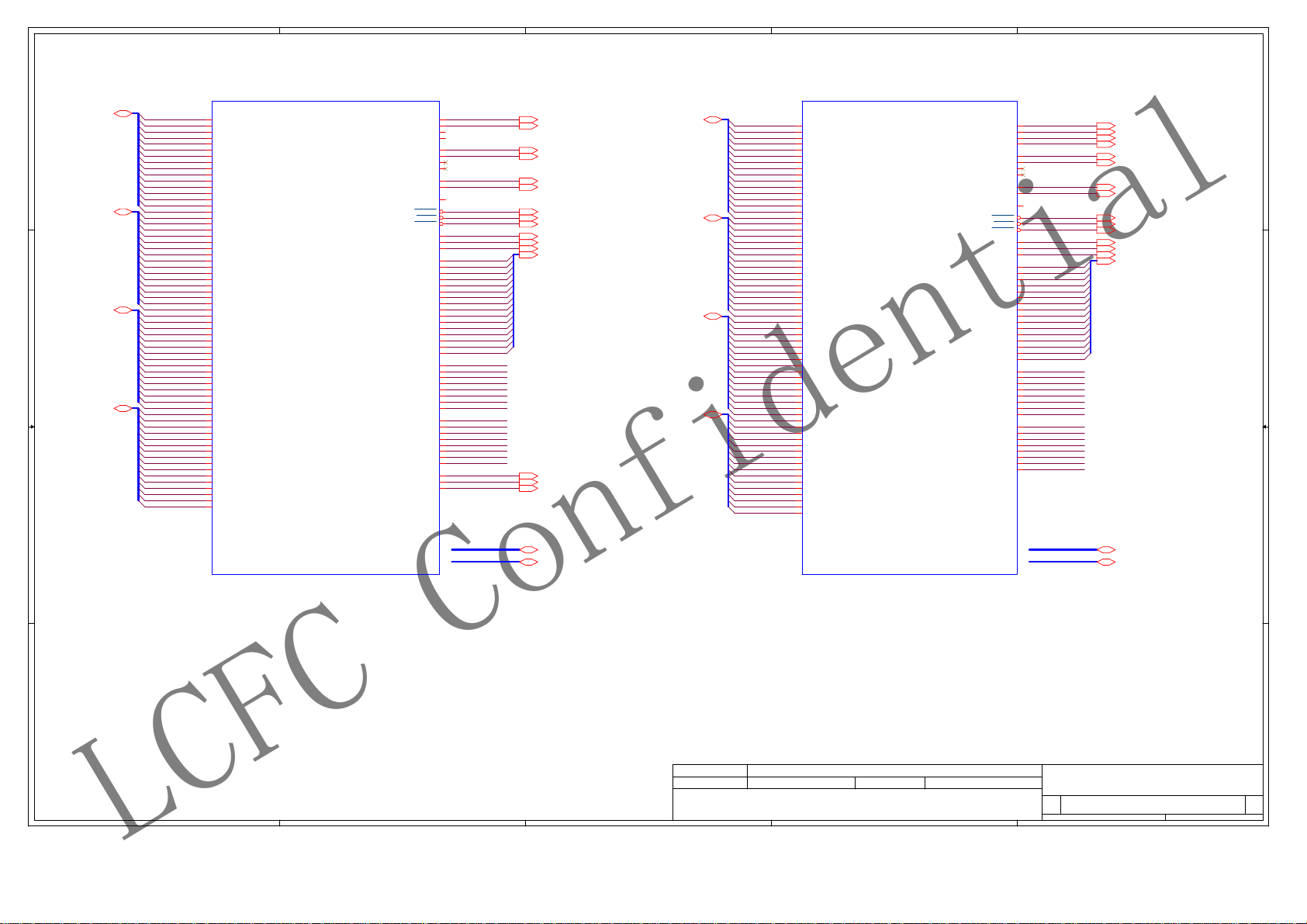

Sub-board ( for 15")

Thermal Sensor

NCT7718W

Page 39

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

2015/02/27

2015/02/27

2015/02/27

C

Deciphered Date

Deciphered Date

Deciphered Date

D

2013/08/05

2013/08/05

2013/08/05

ODD Board

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Saturday, May 09, 2015

Saturday, May 09, 2015

Saturday, May 09, 2015

Date: Sheet of

Date: Sheet of

Date: Sheet of

CG510

CG510

CG510

E

2 59

2 59

2 59

0.2

0.2

0.2

A

B

C

D

E

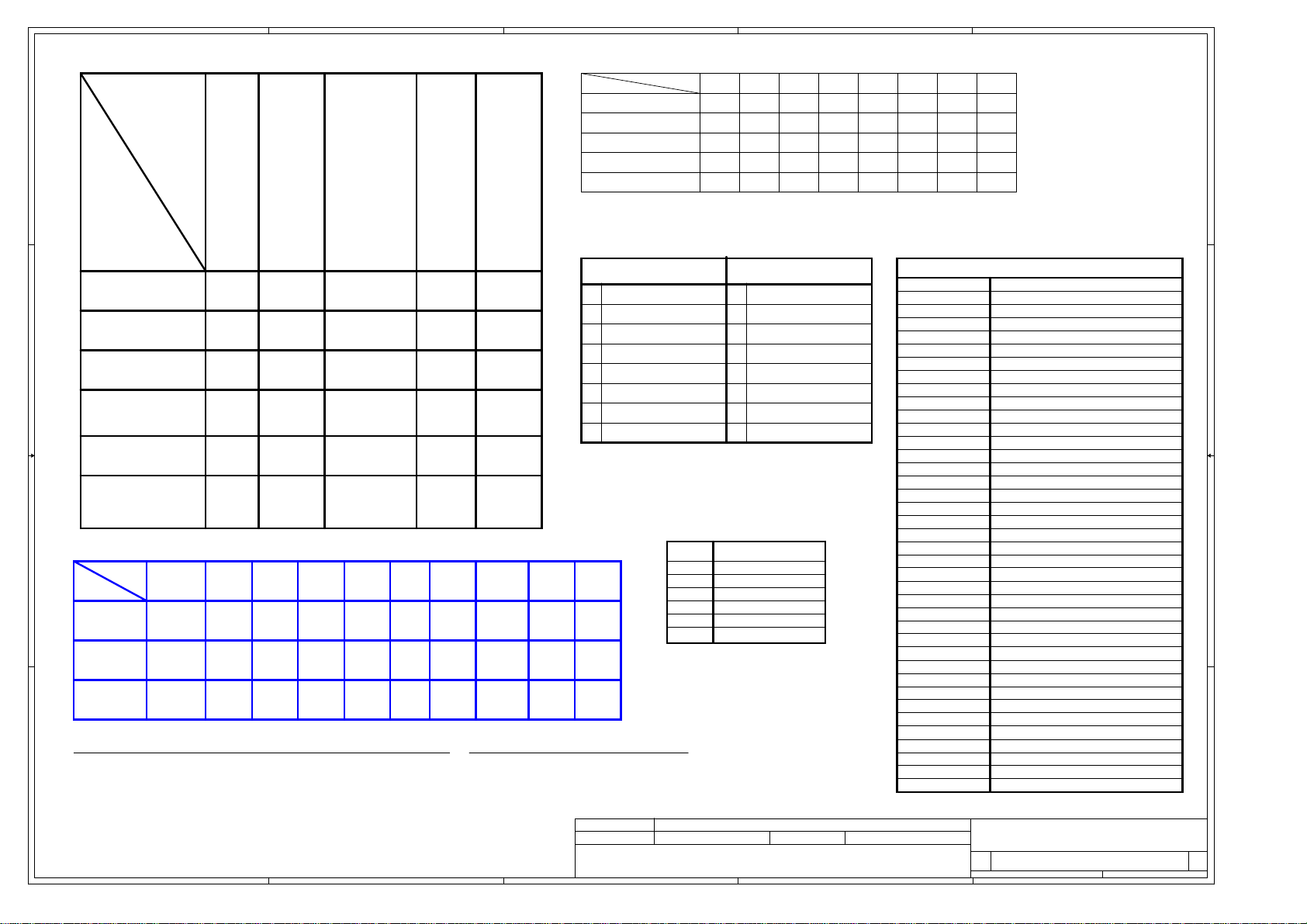

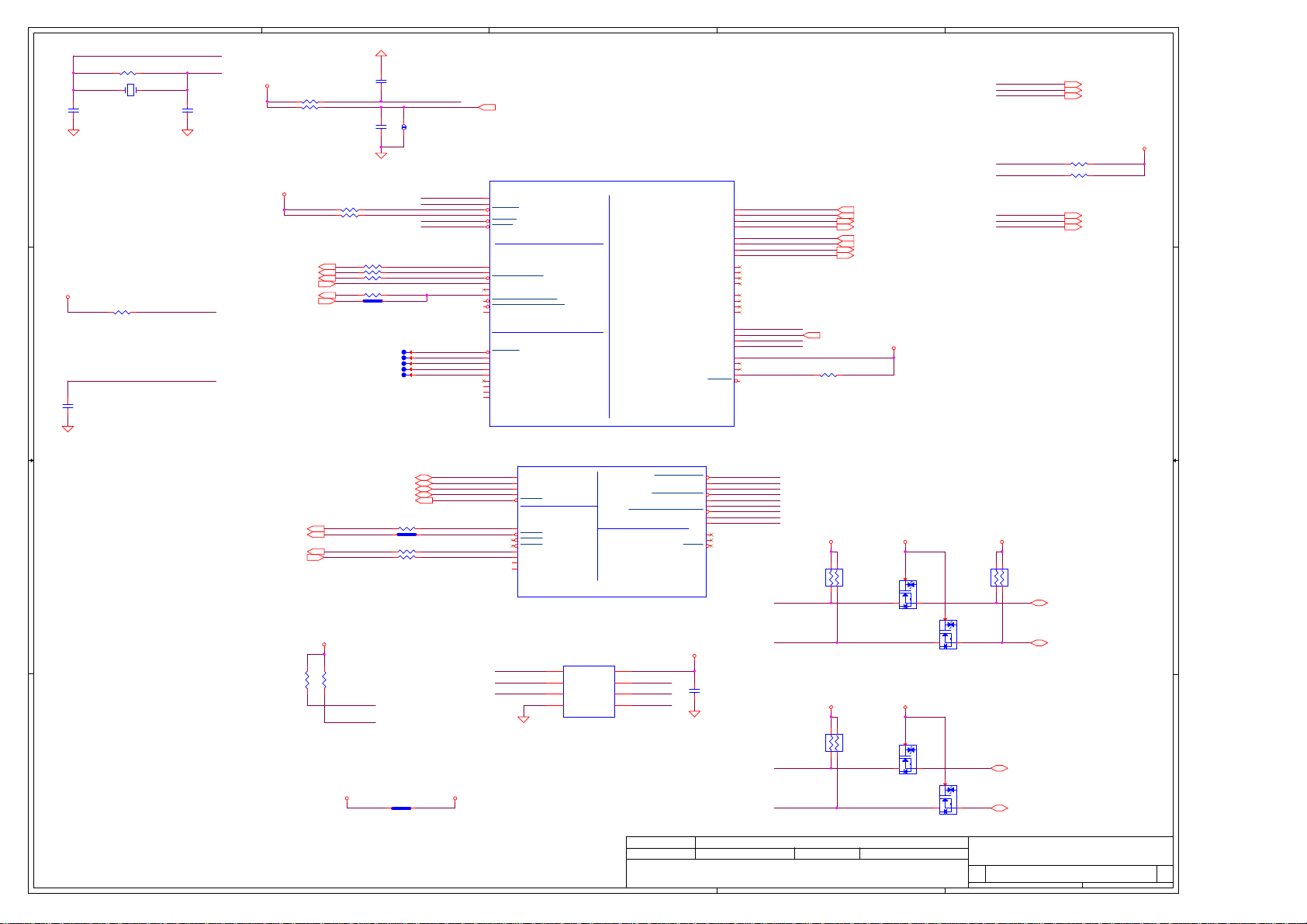

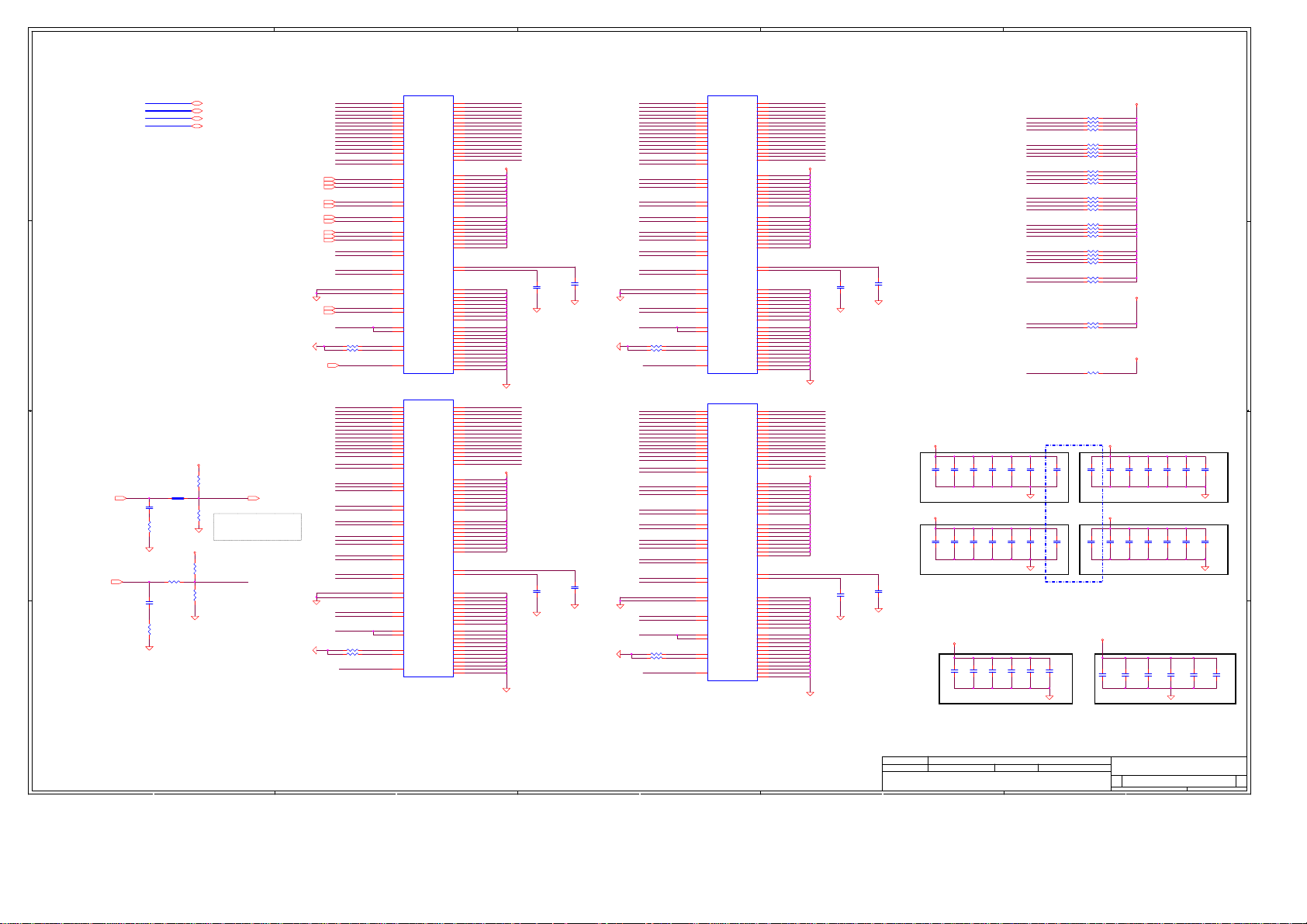

Voltage Rails

Power Plane

1 1

State

S0

S3

2 2

S3

Battery only

S5 S4/AC Only

S5 S4

Battery only

S5 S4

AC & Battery

don't exist

3 3

SMBUS Control Table

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_SMB_CLK

PCH_SMB_DATA

EC SM Bus1 address

4 4

Device

Smart Battery

Charger

( O --> Means ON , X --> Means OFF )

+3VALW

B+

+3VALW_PCH

+5VALW

O

O O O

O

O

O X

O

O

O

X X

X X

SOURCE

IT8586EEC_SMB_CK1

+3VALW

IT8586E

+3VS

PCH

+3VALW_PCH

0X16

0001 0010 b

A

VGA BATT SODIMM

X

V

+3VGS

X

IT8586E

V

+3VALW

X

V

+3VS

X X X

EC SM Bus2 address

Device

Thermal Sensor NCT7718W

VGA

PCH

+1.35V

O

OO

O

O

O

O

X

X

X

X

V V

+3VS +3VS

Address

1001_100xb

0x41(default)

need to update

B

WLAN

WiMAX

X

X

V

X

Thermal

Sensor

X XV

V

+3VS

+3VALW_PCH

+3VALW_PCH

PCH SM Bus address

+5VS

+3VS

+1.5VS

+1.35VS

+1.05VS

+0.675VS

CPU_CORE

+VGA_CORE

+3VGS

+1.8VGS

+1.35VGS

+0.95VGS

X

X

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

USB Port Table

0

USB Port (Right Side)

1

USB Port1 (Left Side)

2

USB Port2 (Left Side)

3

Cardreader

4

TOUCH PANEL

5

Camera

6

NGFF(WLAN)

7

X

X

TP

PCH

X

Device Address

DDR DIMMA

DDR DIMMB

Wlan

charger

Module

XX

V

X

X

X

X

1010 000Xb

1010 010Xb

Rsvd

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THISSHEET MAY NOT BE TRANSFERED FROMTHECUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THISSHEET MAY NOT BE TRANSFERED FROMTHECUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THISSHEET MAY NOT BE TRANSFERED FROMTHECUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT ASAUTHORIZED BY LC FUTURE CENTER NEITHER THISSHEETNOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT ASAUTHORIZED BY LC FUTURE CENTER NEITHER THISSHEETNOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT ASAUTHORIZED BY LC FUTURE CENTER NEITHER THISSHEETNOR THE INFORMATION IT CONTAINS

MAY BE USEDBY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIORWRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USEDBY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIORWRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USEDBY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIORWRITTEN CONSENT OF LC FUTURE CENTER.

SIGNAL

SLP_S1#SLP_S3#SLP_S4#SLP_S5#+VALW +V +VS Clock

ON

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

USB 3.0USB 2.0

XHCI

1

XHCI

USB Port1 (Left Side)

2

3

4

PCIE PORT LIST

Port

1

2

3

4

5

6

2015/02/27

2015/02/27

2015/02/27

C

Device

LAN

WLAN

Discrete GPU

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

ONONON ON

ON

ON

ON

ON

ON

OFF

OFF

ON

OFF

OFF

OFF

BOM Structure Table

@

14@

15@

UMA@

PX@

100M@

GIGA@

JET@

TOPAZ@

RANKA@

RANKB@

ME@

TS@

AOAC@

H2@

H4@

M2@

M4@

S2@

S4@

H2GX4@

M2GX4@

S2GX4@

H4GX4@

M4GX4@

S4GX4@

H2GX8@

M2GX8@

S2GX8@

H4GX8@

M4GX8@

S4GX8@

CD@

BCD@

SINGLE@

DUAL@

2013/08/05

2013/08/05

2013/08/05

LOW

OFF

OFF

OFF

BTO ItemBOM Structure

Not stuff

For 14" part

For 15" part

UMA SKU part

Discrete GPU SKU part

100M LAN Part

GIGA LAN Part

For AMD Jet GPU part

For AMD Topaz GPU part

For VRAM RankA part

For VRAM RankB part

ME part(connector, hole)

For support touch panel sku part

AOAC support part

Hynix 128Mx16 VRAM part

Hynix 256Mx16 VRAM part

Micron 128Mx16 VRAM part

Micron 256Mx16 VRAM part

Samsung 128Mx16 VRAM part

Samsung 256Mx16 VRAM part

Hynix 128Mx16 VRAM x4pcs sku

Micron 128Mx16 VRAM x4pcs sku

Samsung 128Mx16 VRAM x4pcs sku

Hynix 256Mx16 VRAM x4pcs sku

Micron 256Mx16 VRAM x4pcs sku

Samsung 256Mx16 VRAM x4pcs sku

Hynix 128Mx16 VRAM x8pcs sku

Micron 128Mx16 VRAM x8pcs sku

Samsung 128Mx16 VRAM x8pcs sku

Hynix 256Mx16 VRAM x8pcs sku

Micron 256Mx16 VRAM x8pcs sku

Samsung 256Mx16 VRAM x8pcs sku

Cost down part

Cost down part for BDW project

Single Rank VRAM sku

Dual Rank VRAM sku

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Saturday, May 09, 2015

Saturday, May 09, 2015

Saturday, May 09, 2015

Date: Sheet of

Date: Sheet of

Date: Sheet of

CG510

CG510

CG510

E

3 59

3 59

3 59

0.2

0.2

0.2

5 4 3

2

1

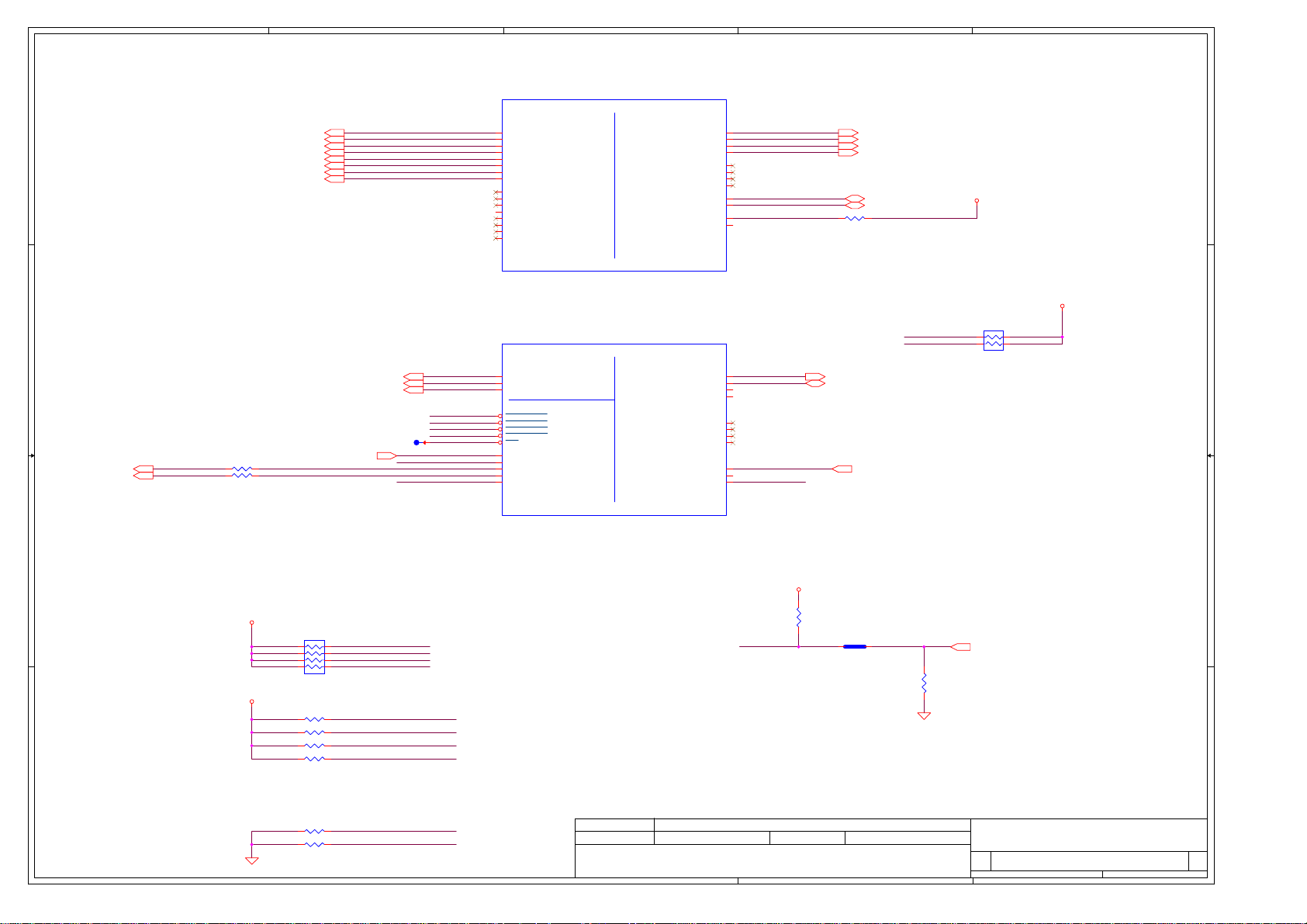

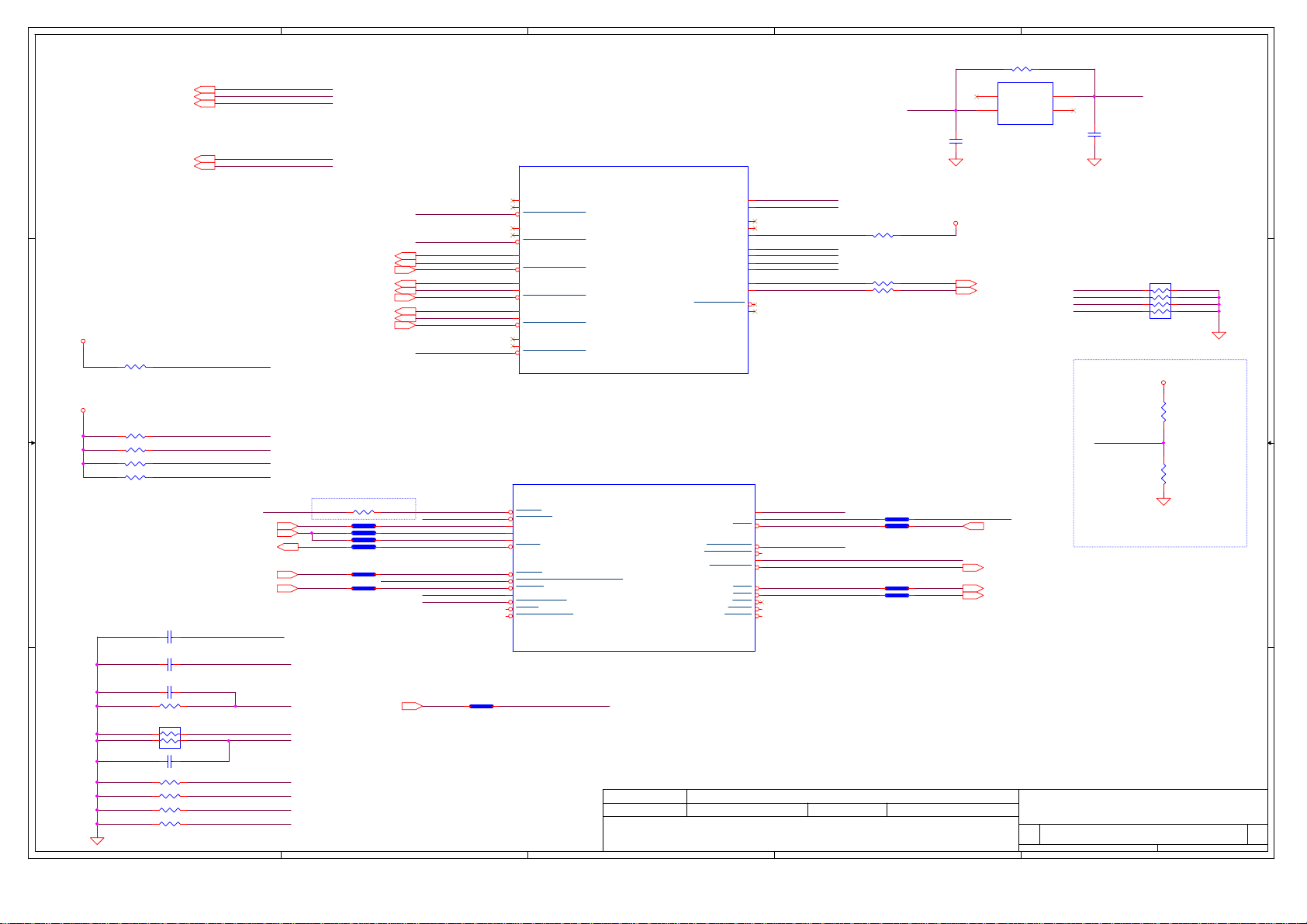

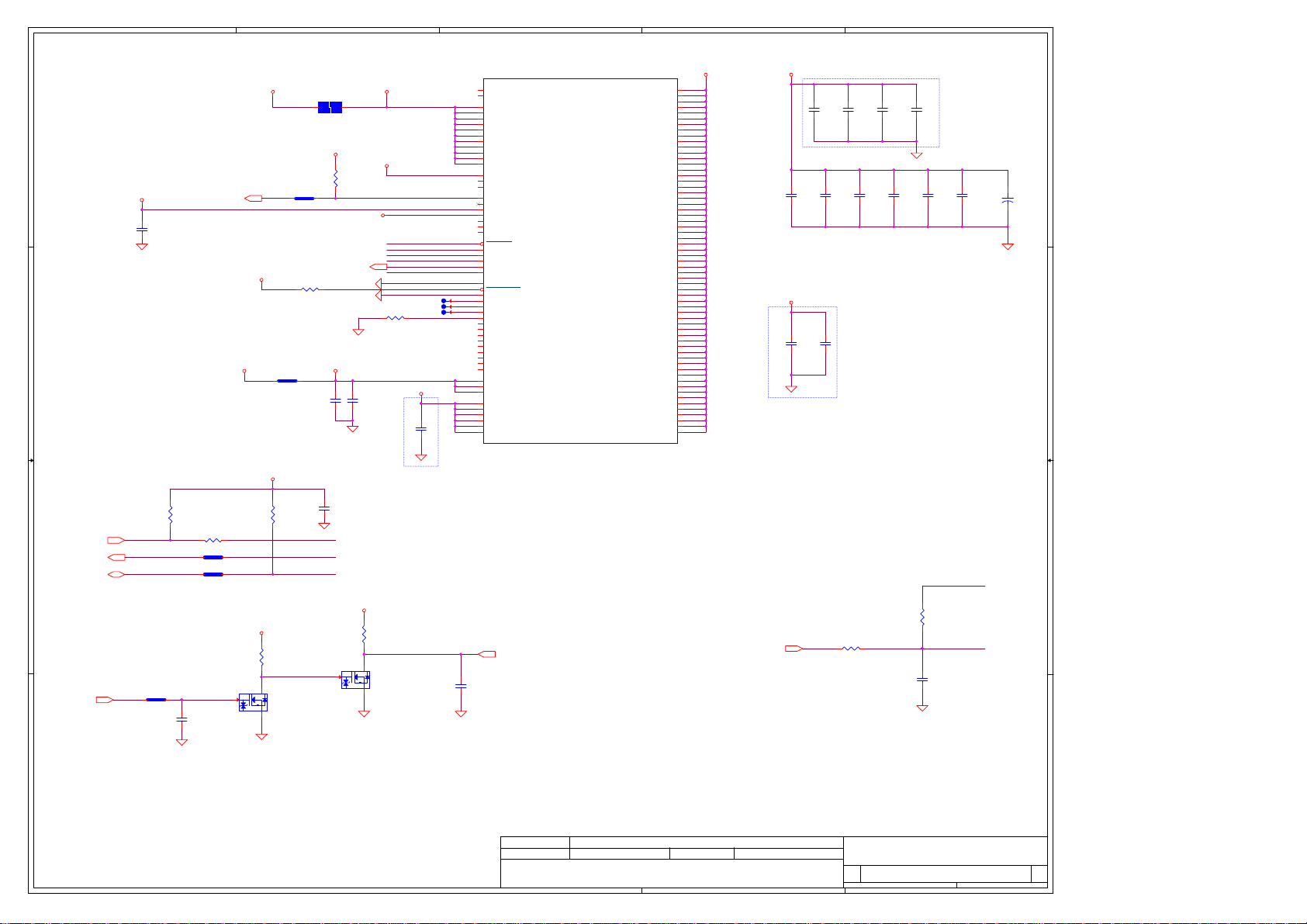

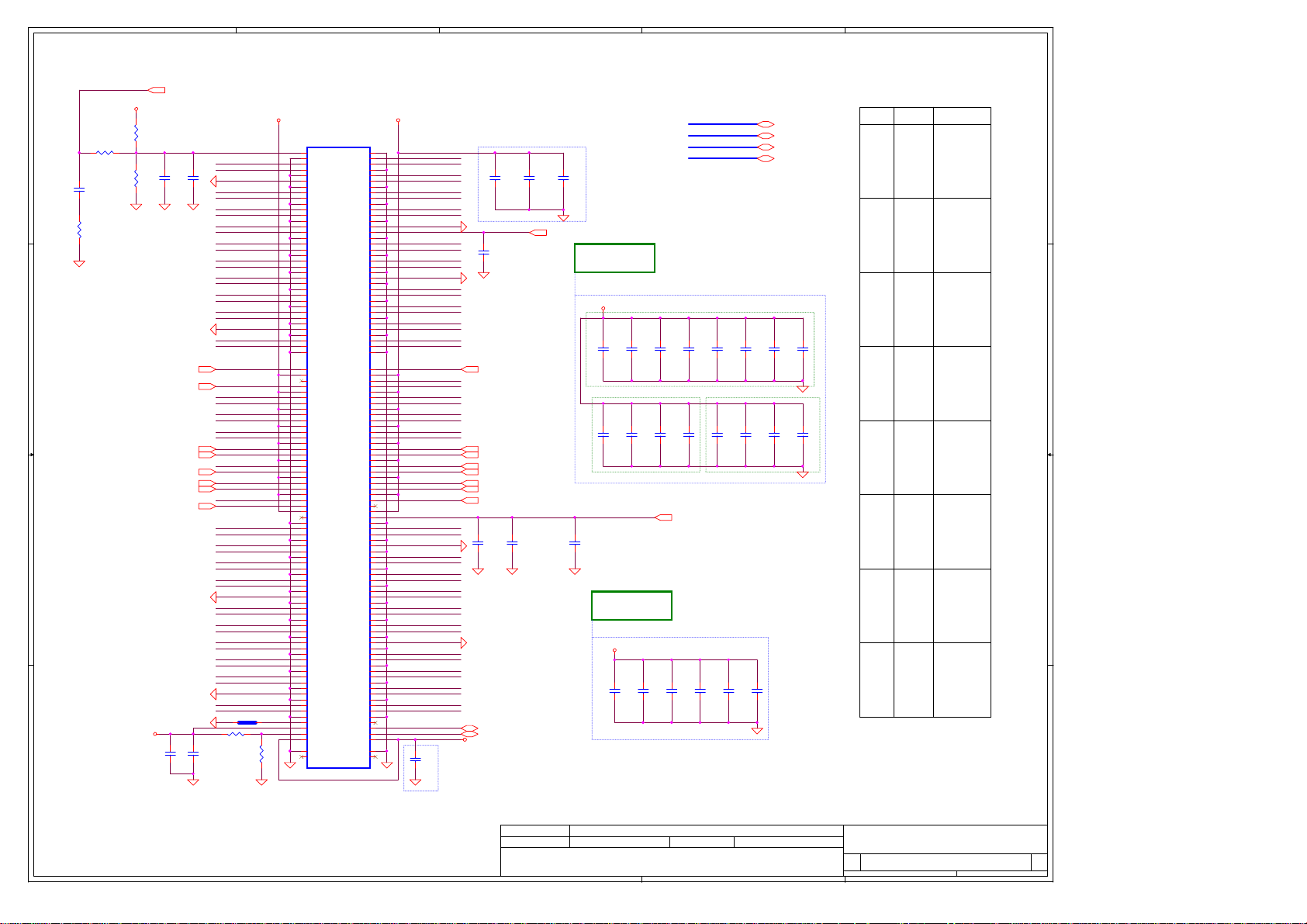

eDP SIDEBAND

PCIE

HSW_ULT_DDR3L

1 OF 19

HSW_ULT_DDR3L

9 OF 19

EDPDDI

DISPLAY

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

CPU_EDP_TX0CPU_EDP_TX0+

CPU_EDP_TX1CPU_EDP_TX1+

CPU_EDP_AUX#

CPU_EDP_AUX

EDP_COMP

DDPB_CLK

DDPB_DATA

HDMI_HPD

EDP_HPD

CPU_EDP_TX0- 33

CPU_EDP_TX0+ 33

CPU_EDP_TX1- 33

CPU_EDP_TX1+ 33

CPU_EDP_AUX# 33

CPU_EDP_AUX 33

1 2

RC1 24.9_0402_1%

DDPB_CLK 34

DDPB_DATA 34

*

HDMI_HPD 34

+VCCIOA_OUT

DDPB_DATA

DDPB_CLK

DDPx_CTRLDATA

The signal has a weak internal pull-down.

H Port is detected.

L Port is not detected.

+VCCIOA_OUT & EDP_COMP :

Trace Width: 20mil

Space: 25mil

Max length: 100mil

RPC19

23

14

2.2K_0404_4P2R_5%

+3VS

UC1A

D D

HDMI D2

HDMI D1

HDMI D0

HDMI CLK

C C

PXS_PWREN21,58

PXS_RST#19

PXS_PWREN

PXS_RST#

1 2

RC7 1K_0402_5%OPT@

RC8 0_0402_5%OPT@1 2

HDMI_TX2-34

HDMI_TX2+34

HDMI_TX1-34

HDMI_TX1+34

HDMI_TX0-34

HDMI_TX0+34

HDMI_CLK-34

HDMI_CLK+34

HDMI_TX2HDMI_TX2+

HDMI_TX1HDMI_TX1+

HDMI_TX0HDMI_TX0+

HDMI_CLKHDMI_CLK+

TC1

BOARD_ID3

GPIO52

PXS_PWREN_R

PXS_RST#_R

GPIO53

PCH_EDP_PWM

PCH_ENBKL

PCH_ENVDD

PCI_PIRQA#

PCI_PIRQB#

PCI_PIRQC#

PCI_PIRQD#

PCH_EDP_PWM33

PCH_ENBKL33

PCH_ENVDD33

PAD@ 1

BOARD_ID39

C54

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

DDI1_TXP2

A57

DDI1_TXN3

B57

DDI1_TXP3

C51

DDI2_TXN0

C50

DDI2_TXP0

C53

DDI2_TXN1

B54

DDI2_TXP1

C49

DDI2_TXN2

B50

DDI2_TXP2

A53

DDI2_TXN3

B53

DDI2_TXP3

BROADWELL-ULT-DDR3L_BGA1168

@

UC1I

B8

EDP_BKLCTL

A9

EDP_BKLEN

C6

EDP_VDDEN

U6

PIRQA/GPIO77

P4

PIRQB/GPIO78

N4

PIRQC/GPIO79

N2

PIRQD/GPIO80

AD4

PME

U7

GPIO55

L1

GPIO52

L3

GPIO54

R5

GPIO51

L4

GPIO53

BROADWELL-ULT-DDR3L_BGA1168

@

B B

+3VS

12

+3VS

RPC1

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

+3VS

RC10 10K_0402_5%1 2

1 2

RC11 10K_0402_5%

1 2

RC14 10K_0402_5%

1 2

RC15 10K_0402_5%@

A A

RC17 100K_0402_5%@

1 2

RC18 10K_0402_5%

PCI_PIRQA#

PCI_PIRQB#

PCI_PIRQC#

PCI_PIRQD#

GPIO52

GPIO53

PXS_PWREN_R

PXS_RST#_R

Security Classification

Security Classification

12

PXS_PWREN_R

PXS_RST#_R

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THISSHEET MAY NOT BE TRANSFERED FROMTHECUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THISSHEET MAY NOT BE TRANSFERED FROMTHECUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THISSHEET MAY NOT BE TRANSFERED FROMTHECUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT ASAUTHORIZED BY LC FUTURE CENTER NEITHER THISSHEETNOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT ASAUTHORIZED BY LC FUTURE CENTER NEITHER THISSHEETNOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT ASAUTHORIZED BY LC FUTURE CENTER NEITHER THISSHEETNOR THE INFORMATION IT CONTAINS

MAY BE USEDBY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIORWRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USEDBY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIORWRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USEDBY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIORWRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/02/27

2015/02/27

2015/02/27

RC9

1M_0402_5%

@

EDP_HPD

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

RC16

1 2

0_0402_5%

@

12

RC13

100K_0402_5%

2013/08/05

2013/08/05

2013/08/05

2

CPU_EDP_HPD 33

Title

Title

Title

MCP (DDI,EDP)

MCP (DDI,EDP)

MCP (DDI,EDP)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Saturday, May 09, 2015

Saturday, May 09, 2015

Saturday, May 09, 2015

Date: Sheet of

Date: Sheet of

Date: Sheet of

CG510

CG510

CG510

4 59

4 59

4 59

1

0.2

0.2

0.2

5

4

3

2

1

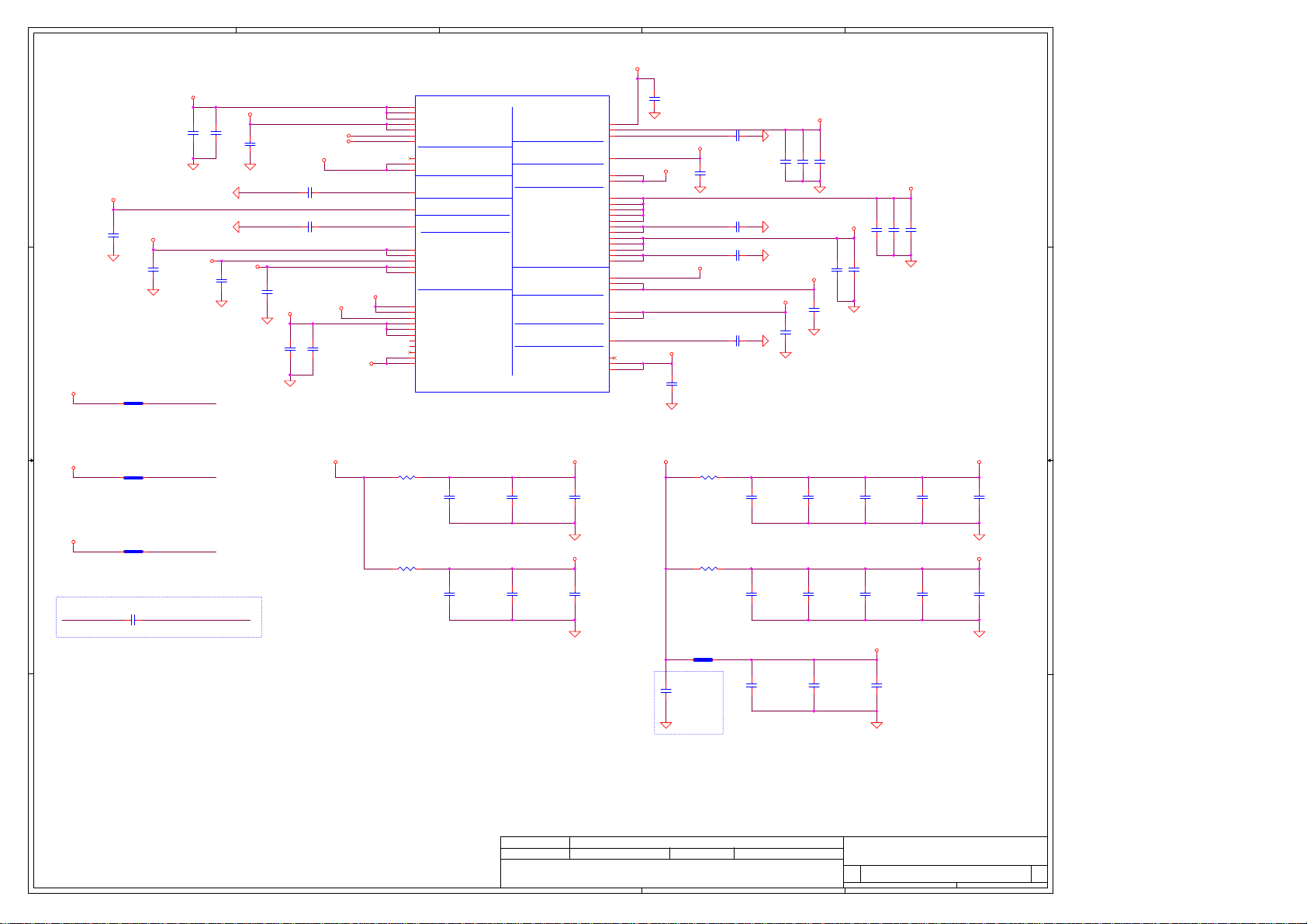

+1.05V_VCCST

D D

H_PROCHOT#44

1 2

CPU_DRAMRST#14,15

C C

SM_RCOMP_2

12

RC24100_0402_1%

SM_RCOMP_1

12

RC25121_0402_1%

SM_RCOMP_0

12

RC26200_0402_1%

B B

RC23

1

CC1

0.1U_0402_25V6

2

EMC@

0_0402_5%

RC19

62_0402_1%

@

+1.35V

12

12

RC22

470_0402_5%

H_PECI44

1 2

1 2

10K_0402_5%

+1.35V

H_PROCHOT#_R

RC2056_0402_5%

CPU_PROCPWRGD

RC21

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

CPU_DRAMRST#_R

SM_PG_CNTL1

RC3

SM_PG_CNTL1

H_PECI

1 2

1K_0402_5%

10K_0402_5%

UC1B

D61

PROC_DETECT

K61

CATERR

N62

PECI

K63

PROCHOT

C61

PROCPWRGD

AU60

SM_RCOMP0

AV60

SM_RCOMP1

AU61

SM_RCOMP2

AV15

SM_DRAMRST

AV61

SM_PG_CNTL1

BROADWELL-ULT-DDR3L_BGA1168

@

+3VALW

12

RC28

100K_0402_5%

C

2

QC14

B

E

3 1

MMBT3904WH_SOT323-3

RC29

@

1 2

HSW_ULT_DDR3L

MISC

THERMAL

PWR

DDR3L

CPU_DRAMPG_CNTL 55

1 2

RC31 0_0402_5%

@

.1U_0402_10V6-K

JTAG

2 OF 19

CD1

@

1

2

PRDY

PREQ

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

2

G

J62

K62

XDP_TCLK

E60

XDP_TMS

E61

XDP_TRST#

E59

XDP_TDI

F63

XDP_TDO

F62

J60

H60

H61

H62

K59

H63

K60

J61

+1.35V

1

QC5

D

S

PJA138K_SOT23-3

3

DDR_ODT DDRB_ODT0

1

TC6

1

TC7

1

TC8

1

TC9

1

TC10

1 2

RD3 66.5_0402_1%

1 2

RD4 66.5_0402_1%

PAD @

PAD @

PAD @

PAD @

PAD @

DDRB_ODT1

DDRB_ODT0 15

DDRB_ODT1 15

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/02/27

2015/02/27

2015/02/27

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2013/08/05

2013/08/05

2013/08/05

Title

MCP (MISC,THERMAL,JATG)

MCP (MISC,THERMAL,JATG)

MCP (MISC,THERMAL,JATG)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Saturday, May 09, 2015

Saturday, May 09, 2015

Saturday, May 09, 2015

Date: Sheet of

Date: Sheet of

Date: Sheet of

CG510

CG510

CG510

5 59

5 59

1

5 59

0.2

0.2

0.2

5

4

3

2

1

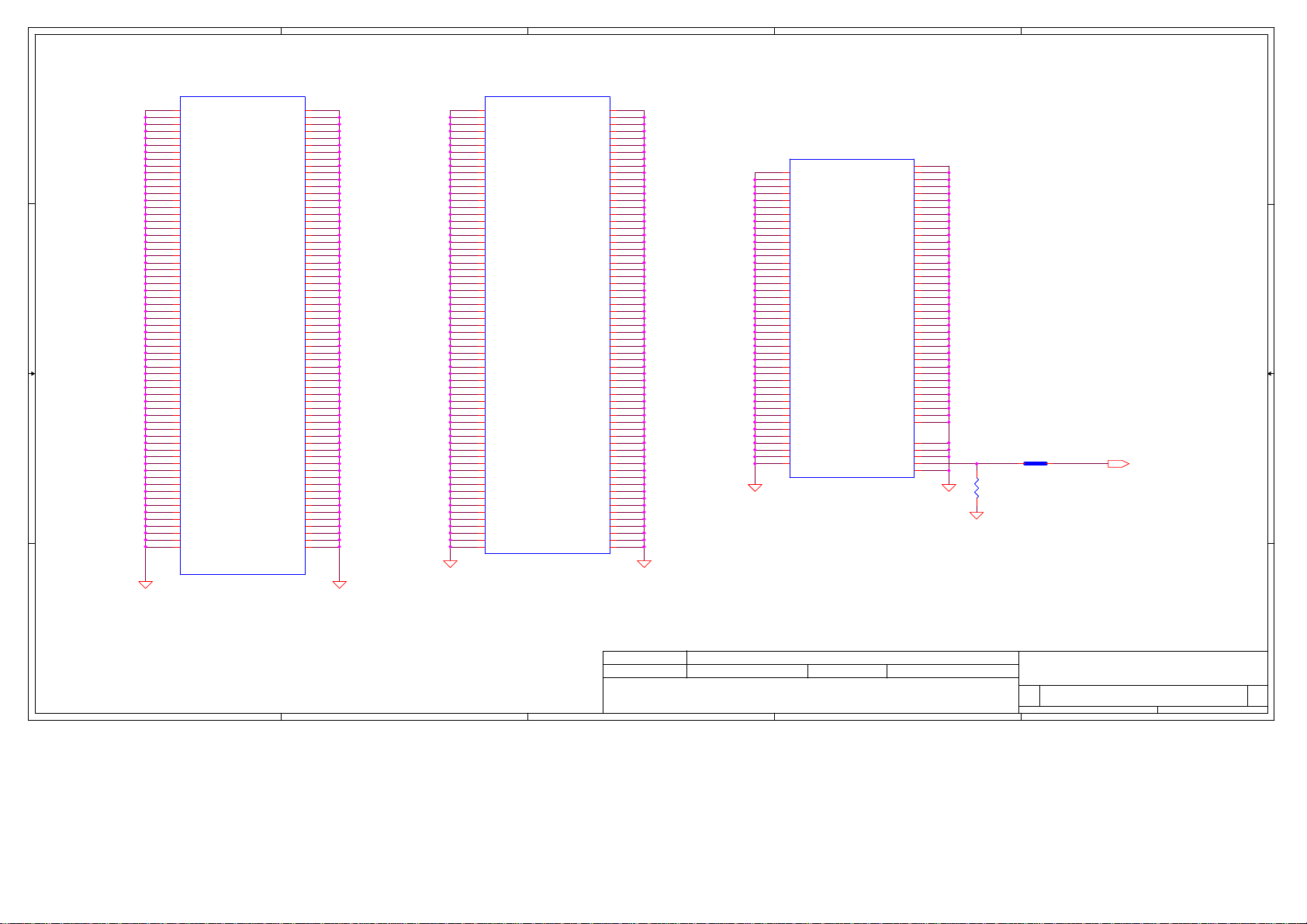

UC1C

DDRA_DQ[0..15]14

D D

DDRB_DQ[0..15]15

DDRA_DQ[16..31]14

C C

DDRB_DQ[16..31]15

B B

DDRA_DQ2

DDRA_DQ4

DDRA_DQ7

DDRA_DQ6

DDRA_DQ1

DDRA_DQ3

DDRA_DQ0

DDRA_DQ5

DDRA_DQ15

DDRA_DQ10

DDRA_DQ9

DDRA_DQ8

DDRA_DQ14

DDRA_DQ11

DDRA_DQ13

DDRA_DQ12

DDRB_DQ0

DDRB_DQ1

DDRB_DQ2

DDRB_DQ3

DDRB_DQ4

DDRB_DQ5

DDRB_DQ6

DDRB_DQ7

DDRB_DQ8

DDRB_DQ9

DDRB_DQ10

DDRB_DQ11

DDRB_DQ12

DDRB_DQ13

DDRB_DQ14

DDRB_DQ15

DDRA_DQ19

DDRA_DQ20

DDRA_DQ18

DDRA_DQ17

DDRA_DQ23

DDRA_DQ22

DDRA_DQ21

DDRA_DQ16

DDRA_DQ28

DDRA_DQ25

DDRA_DQ26

DDRA_DQ27

DDRA_DQ24

DDRA_DQ29

DDRA_DQ31

DDRA_DQ30

DDRB_DQ16

DDRB_DQ17

DDRB_DQ18

DDRB_DQ19

DDRB_DQ20

DDRB_DQ21

DDRB_DQ22

DDRB_DQ23

DDRB_DQ24

DDRB_DQ25

DDRB_DQ26

DDRB_DQ27

DDRB_DQ28

DDRB_DQ29

DDRB_DQ30

DDRB_DQ31

AH63

SA_DQ0

AH62

SA_DQ1

AK63

SA_DQ2

AK62

SA_DQ3

AH61

SA_DQ4

AH60

SA_DQ5

AK61

SA_DQ6

AK60

SA_DQ7

AM63

SA_DQ8

AM62

SA_DQ9

AP63

SA_DQ10

AP62

SA_DQ11

AM61

SA_DQ12

AM60

SA_DQ13

AP61

SA_DQ14

AP60

SA_DQ15

AP58

SA_DQ16

AR58

SA_DQ17

AM57

SA_DQ18

AK57

SA_DQ19

AL58

SA_DQ20

AK58

SA_DQ21

AR57

SA_DQ22

AN57

SA_DQ23

AP55

SA_DQ24

AR55

SA_DQ25

AM54

SA_DQ26

AK54

SA_DQ27

AL55

SA_DQ28

AK55

SA_DQ29

AR54

SA_DQ30

AN54

SA_DQ31

AY58

SA_DQ32

AW58

SA_DQ33

AY56

SA_DQ34

AW56

SA_DQ35

AV58

SA_DQ36

AU58

SA_DQ37

AV56

SA_DQ38

AU56

SA_DQ39

AY54

SA_DQ40

AW54

SA_DQ41

AY52

SA_DQ42

AW52

SA_DQ43

AV54

SA_DQ44

AU54

SA_DQ45

AV52

SA_DQ46

AU52

SA_DQ47

AK40

SA_DQ48

AK42

SA_DQ49

AM43

SA_DQ50

AM45

SA_DQ51

AK45

SA_DQ52

AK43

SA_DQ53

AM40

SA_DQ54

AM42

SA_DQ55

AM46

SA_DQ56

AK46

SA_DQ57

AM49

SA_DQ58

AK49

SA_DQ59

AM48

SA_DQ60

AK48

SA_DQ61

AM51

SA_DQ62

AK51

SA_DQ63

BROADWELL-ULT-DDR3L_BGA1168

@

HSW_ULT_DDR3L

DDR CHANNEL A

3 OF 19

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

DDRA_MA0

AU36

DDRA_MA1

AY37

DDRA_MA2

AR38

DDRA_MA3

AP36

DDRA_MA4

AU39

DDRA_MA5

AR36

DDRA_MA6

AV40

DDRA_MA7

AW39

DDRA_MA8

AY39

DDRA_MA9

AU40

DDRA_MA10

AP35

DDRA_MA11

AW41

DDRA_MA12

AU41

DDRA_MA13

AR35

DDRA_MA14

AV42

DDRA_MA15

AU42

DDRA_DQS#0

AJ61

AN62

DDRB_DQS#0

AM58

DDRB_DQS#1

AM55

DDRA_DQS#2

AV57

DDRA_DQS#3

AV53

DDRB_DQS#2

AL43

AL48

DDRA_DQS0

AJ62

DDRA_DQS1

AN61

DDRB_DQS0

AN58

DDRB_DQS1

AN55

DDRA_DQS2

AW57

DDRA_DQS3

AW53

DDRB_DQS2

AL42

DDRB_DQS3

AL49

AP49

AR51

AP51

SMVREF

WIDTH:20MIL

SPACING: 20MIL

DDRA_DQS#[0..7]

DDRA_DQS[0..7]

DDRA_CLK0# 14

DDRA_CLK0 14

DDRA_CKE0 14

DDRA_CKE1 14

DDRA_CS0# 14

DDRA_CS1# 14

DDRA_RAS# 14

DDRA_WE# 14

DDRA_CAS# 14

DDRA_BS0# 14

DDRA_BS1# 14

DDRA_BS2# 14

DDRA_MA[0..15] 14

DDR_SM_VREFCA 14

DDR_SA_VREFDQ 14

DDR_SB_VREFDQ 15

DDRA_DQS#[0..7] 14

DDRA_DQS[0..7] 14

UC1D

DDRA_DQ[32..47]14

DDRB_DQ[32..47]15

DDRA_DQ[48..63]14

DDRB_DQ[48..63]15

DDRA_DQ37

DDRA_DQ36

DDRA_DQ38

DDRA_DQ35

DDRA_DQ32

DDRA_DQ33

DDRA_DQ34

DDRA_DQ39

DDRA_DQ41

DDRA_DQ47

DDRA_DQ44

DDRA_DQ43

DDRA_DQ45

DDRA_DQ40

DDRA_DQ42

DDRA_DQ46

DDRB_DQ32

DDRB_DQ33

DDRB_DQ34

DDRB_DQ35

DDRB_DQ36

DDRB_DQ37

DDRB_DQ38

DDRB_DQ39

DDRB_DQ40

DDRB_DQ41

DDRB_DQ42

DDRB_DQ43

DDRB_DQ44

DDRB_DQ45

DDRB_DQ46

DDRB_DQ47

DDRA_DQ53

DDRA_DQ50

DDRA_DQ51

DDRA_DQ55

DDRA_DQ54

DDRA_DQ48

DDRA_DQ49

DDRA_DQ52

DDRA_DQ58

DDRA_DQ62

DDRA_DQ60

DDRA_DQ57

DDRA_DQ59

DDRA_DQ63

DDRA_DQ56

DDRA_DQ61

DDRB_DQ48

DDRB_DQ49

DDRB_DQ50

DDRB_DQ51

DDRB_DQ52

DDRB_DQ53

DDRB_DQ54

DDRB_DQ55

DDRB_DQ56

DDRB_DQ57

DDRB_DQ58

DDRB_DQ59

DDRB_DQ60

DDRB_DQ61

DDRB_DQ62

DDRB_DQ63

AY31

SB_DQ0

AW31

SB_DQ1

AY29

SB_DQ2

AW29

SB_DQ3

AV31

SB_DQ4

AU31

SB_DQ5

AV29

SB_DQ6

AU29

SB_DQ7

AY27

SB_DQ8

AW27

SB_DQ9

AY25

SB_DQ10

AW25

SB_DQ11

AV27

SB_DQ12

AU27

SB_DQ13

AV25

SB_DQ14

AU25

SB_DQ15

AM29

SB_DQ16

AK29

SB_DQ17

AL28

SB_DQ18

AK28

SB_DQ19

AR29

SB_DQ20

AN29

SB_DQ21

AR28

SB_DQ22

AP28

SB_DQ23

AN26

SB_DQ24

AR26

SB_DQ25

AR25

SB_DQ26

AP25

SB_DQ27

AK26

SB_DQ28

AM26

SB_DQ29

AK25

SB_DQ30

AL25

SB_DQ31

AY23

SB_DQ32

AW23

SB_DQ33

AY21

SB_DQ34

AW21

SB_DQ35

AV23

SB_DQ36

AU23

SB_DQ37

AV21

SB_DQ38

AU21

SB_DQ39

AY19

SB_DQ40

AW19

SB_DQ41

AY17

SB_DQ42

AW17

SB_DQ43

AV19

SB_DQ44

AU19

SB_DQ45

AV17

SB_DQ46

AU17

SB_DQ47

AR21

SB_DQ48

AR22

SB_DQ49

AL21

SB_DQ50

AM22

SB_DQ51

AN22

SB_DQ52

AP21

SB_DQ53

AK21

SB_DQ54

AK22

SB_DQ55

AN20

SB_DQ56

AR20

SB_DQ57

AK18

SB_DQ58

AL18

SB_DQ59

AK20

SB_DQ60

AM20

SB_DQ61

AR18

SB_DQ62

AP18

SB_DQ63

BROADWELL-ULT-DDR3L_BGA1168

@

HSW_ULT_DDR3L

4 OF 19

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

DDRB_MA0

DDRB_MA1

DDRB_MA2

DDRB_MA3

DDRB_MA4

DDRB_MA5

DDRB_MA6

DDRB_MA7

DDRB_MA8

DDRB_MA9

DDRB_MA10

DDRB_MA11

DDRB_MA12

DDRB_MA13

DDRB_MA14

DDRB_MA15

DDRA_DQS#4DDRA_DQS#1

DDRA_DQS#5

DDRB_DQS#4

DDRB_DQS#5

DDRA_DQS#6

DDRA_DQS#7

DDRB_DQS#6DDRB_DQS#3

DDRB_DQS#7

DDRA_DQS4

DDRA_DQS5

DDRB_DQS4

DDRB_DQS5

DDRA_DQS6

DDRA_DQS7

DDRB_DQS6

DDRB_DQS7

DDRB_DQS#[0..7]

DDRB_DQS[0..7]

DDRB_CLK0# 15

DDRB_CLK0 15

DDRB_CLK1# 15

DDRB_CLK1 15

DDRB_CKE0 15

DDRB_CKE1 15

DDRB_CS0# 15

DDRB_CS1# 15

DDRB_RAS# 15

DDRB_WE# 15

DDRB_CAS# 15

DDRB_BS0# 15

DDRB_BS1# 15

DDRB_BS2# 15

DDRB_MA[0..15] 15

DDRB_DQS#[0..7] 15

DDRB_DQS[0..7] 15

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THISSHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THISSHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THISSHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THISSHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THISSHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THISSHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/02/27

2015/02/27

2015/02/27

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2013/08/05

2013/08/05

2013/08/05

Title

MCP (DDR3L)

MCP (DDR3L)

MCP (DDR3L)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Saturday, May 09, 2015

Saturday, May 09, 2015

Saturday, May 09, 2015

CG510

CG510

CG510

1

6 59

6 59

6 59

0.2

0.2

0.2

LCFC Confidential

5 4 3

RTC_X1

HDA_SDOUT

HDA_SDIN0

RTC_X2

2

CC5

18P_0402_50V8J

1

VCCRTC

1 2

RC33 20K_0402_1%

1 2

RC34 20K_0402_1%

VCCRTC

RC39 1M_0402_5%

RC41 330K_0402_5%

INTVRMEN

HIntegrated VRM enable (Default)

*

LIntegrated VRM disable

(INTVRMEN should always be pull high.)

HDA_BITCLK_AUDIO43

HDA_SYNC_AUDIO43

HDA_RST_AUDIO#43

HDA_SDIN043

HDA_SDOUT_AUDIO43

ME_FLASH44

1U_0402_10V6K

1U_0402_10V6K

2

1

CC6

2

12

12

1 2

RC42 33_0402_5%

1 2

RC43 33_0402_5%

1 2

RC44 33_0402_5%

1 2

RC45 33_0402_5%

1 2

RC46 0_0402_5%

@

TC24 @

TC25 @

TC26 @

TC28 @

TC30 @

1

CC3

12

JCMOS1

SHORT PADS

@

1

1

1

1

1

SRTC_RST#

RTC_RST#

RTC_X1

RTC_X2

SM_INTRUDER#

INTVRMEN

SRTC_RST#

RTC_RST#

HDA_BCLK

HDA_SYNC

HDA_RST#

HDA_SDIN0

HDA_SDOUT

PCH_JTAG_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

RTC_RST# 44

UC1E

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD1

AC4

RSVD2

AE63

JTAGX

AV2

RSVD0

BROADWELL-ULT-DDR3L_BGA1168

@

HSW_ULT_DDR3L

RTC

AUDIO SATA

JTAG

5 OF 19

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

RSVD3

RSVD4

SATA_RCOMP

SATALED

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

K10

C12

U3

SATA_RCOMP

SATA_PRX_DTX_N0

SATA_PRX_DTX_P0

SATA_PTX_DRX_N0

SATA_PTX_DRX_P0

SATA_PRX_DTX_N1

SATA_PRX_DTX_P1

SATA_PTX_DRX_N1

SATA_PTX_DRX_P1

SATA0GP

ODD_DETECT#

SATA2GP

SATA3GP

RC32 10M_0402_5%

2

CC4

15P_0402_50V8J

1

D D

CRYSTAL

1, Space 15MIL

2, No trace under crystal

3, Place on oppsosit side of MCP for temp influence

+3VALW_PCH

RC47 1K_0402_5%@

HDA_SDO This signal has a weak internal pull-down.

0 = Enable security measures defined in the Flash Descriptor.

*

1 = Disable Flash Descriptor Security(override). This strap

should only be asserted high during external pull-up in

manufacturing/debug environments ONLY.

C C

12

YC1

1 2

32.768KHZ_12.5PF_202740-PG14

1 2

For EMI

1

CC7

10P_0402_50V8J

2

EMC_NS@

2

SATA_PRX_DTX_N0 42

SATA_PRX_DTX_P0 42

SATA_PTX_DRX_N0 42

SATA_PTX_DRX_P0 42

SATA_PRX_DTX_N1 42

SATA_PRX_DTX_P1 42

SATA_PTX_DRX_N1 42

SATA_PTX_DRX_P1 42

ODD_DETECT# 9,42

RC48 3.01K_0402_1%

+1.05VS_PSATA3PLL

12

HDD

ODD

IREF&RCOMP

Width: 12-15Mil

Space:12Mil

Length: 500Mil

SATA0GP

SATA2GP

SATA3GP

SML0_CLK

RC35 2.2K_0402_5%

SML0_DATA

RC36 2.2K_0402_5%

SMB_ALERT#

SML0_ALERT#

SML1_ALERT#

1

1 2

1 2

SATA0GP 9

SATA2GP 9

SATA3GP 9

+3VALW_PCH

SMB_ALERT# 9

SML0_ALERT# 9

SML1_ALERT# 9

UC1G

SPI_CS0#_R

SPI_SI_R

SPI_SO_R

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

BROADWELL-ULT-DDR3L_BGA1168

@

SPI_CS0#

SPI_SO

SPI_WP#

LPC_AD032,44

LPC_AD132,44

LPC_AD232,44

LPC_AD332,44

LPC_FRAME#32,44

SPI_CLK44

SPI_CS0#44

SPI_SI44

B B

A A

SPI_SO44

1K_0402_5%

SPI_CLK SPI_CLK_R

SPI_CS0#

SPI_SI

SPI_SO

+3V_SPI

12

12

RC61

RC60

1K_0402_5%

SPI_WP#

SPI_HOLD#

+3VALW_PCH

+3V_SPI

1. If support DS3, connect to +3VS and don't support EC mirror code;

2. If don't support DS3, connect to +3VALW_PCH and support EC mirror code.

*

1 2

RC50 15_0402_5%

1 2

RC51 0_0402_5%

@

1 2

RC52 15_0402_5%

1 2

RC53 15_0402_5%

1 2

RC171

@

0_0402_5%

+3V_SPI

HSW_ULT_DDR3L

LPC

UC3

1

CS#

2

DO

3

WP#

GND4DI

W25Q64FVSSIQ_SO8

SMBCLK

SMBDATA

SML0CLK

SML0DATA

CL_CLK

CL_DATA

CL_RST

+3V_SPI

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

1

CC8

.1U_0402_10V6-K

2

PCH_SMB_CLK

PCH_SMB_DATA

SML0_ALERT#

SML0_CLK

SML0_DATA

SML1_ALERT#

PCH_SML1_CLK

PCH_SML1_DAT

2015/02/27

2015/02/27

2015/02/27

+3VALW_PCH +3VS +3VS

RPC20

2.2K_0404_4P2R_5%

1 4

PCH_SMB_CLK

PCH_SMB_DATA

PCH_SML1_CLK

PCH_SML1_DAT

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

2 3

+3VALW_PCH +3VS

RPC25

2.2K_0404_4P2R_5%

1 4

2 3

Deciphered Date

Deciphered Date

Deciphered Date

2

SMBALERT/GPIO11

SMBUS

SML0ALERT/GPIO60

SML1ALERT/PCHHOT/GPIO73

SML1CLK/GPIO75

SML1DATA/GPIO74

C-LINKSPI

7 OF 19

8

VCC

SPI_HOLD#

7

HOLD#

SPI_CLK

6

CLK

SPI_SI

5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

SMB_ALERT#

2

G

6 1

QC2A

D

2N7002KDWH_SOT363-6

QC2B

2

G

6 1

QC3A

D

2N7002KDWH_SOT363-6

QC3B

2013/08/05

2013/08/05

2013/08/05

DIMM1, DIMM2, NGFF

S

5

G

3 4

S

D

2N7002KDWH_SOT363-6

@

S

5

G

3 4

S

D

2N7002KDWH_SOT363-6

RPC24

2.2K_0404_4P2R_5%

1 4

2 3

SMB_CLK_S3 15,40

SMB_DATA_S3 15,40

GPU, EC, Thermal Sensor

EC_SMB_CK2 19,44

@

EC_SMB_DA2 19,44

Title

Title

Title

MCP (RTC&AUDIO&SATA&SMBUS)

MCP (RTC&AUDIO&SATA&SMBUS)

MCP (RTC&AUDIO&SATA&SMBUS)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

CG510

CG510

CG510

Saturday, May 09, 2015

Saturday, May 09, 2015

Saturday, May 09, 2015

7 59

7 59

1

7 59

0.2

0.2

0.2

5

4

3

2

1

RC71 1M_0402_5%

SUSWARN#_R

PCH_PWROK

PCH_DPWROK_R

PCH_PWROK

PCH_RSMRST#_R

PLT_RST#_R

PCH_DPWROK_R

SUSCLK

GPU_CLKREQ#

PCIE_CLKREQ1#

PCIE_CLKREQ0#

PCIE_CLKREQ5#

SYS_RESET#

PM_CLKRUN#

LAN

WLAN

CLK_PCIE_LAN#37

CLK_PCIE_LAN37

LAN_CLKREQ#9,37

CLK_PCIE_WLAN#40

CLK_PCIE_WLAN40

WLAN_CLKREQ#9,40

CLK_PCIE_GPU#19

CLK_PCIE_GPU19

GPU_CLKREQ#19

Reserve for DS3

1 2

RC79 0_0402_5%@

1 2

RC139 0_0402_5%@

1 2

RC126 0_0402_5%@

1 2

RC83 0_0402_5%@

1 2

RC84 0_0402_5%@

1 2

RC85 0_0402_5%@

1 2

RC87 0_0402_5%@

AC_PRESENT44

4

PCIE_CLKREQ0#

PCIE_CLKREQ1#

CLK_PCIE_LAN#

CLK_PCIE_LAN

LAN_CLKREQ#

CLK_PCIE_WLAN#

CLK_PCIE_WLAN

WLAN_CLKREQ#

CLK_PCIE_GPU#

CLK_PCIE_GPU

GPU_CLKREQ#

PCIE_CLKREQ5#

SUSACK#_R

SYS_RESET#

SYS_PWROK_R

PCH_PWROK_R

APWROK

PLT_RST#_R

PCH_RSMRST#_R

SUSWARN#_R

PBTN_OUT#_R

AC_PRESENT_R

PCH_GPIO72

1 2

RC88 0_0402_5%@

UC1F

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

BROADWELL-ULT-DDR3L_BGA1168

@

UC1H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

BROADWELL-ULT-DDR3L_BGA1168

@

AC_PRESENT_RSYS_PWROK

XTAL24_IN

CC12

4.7P_0402_50V8B

HSW_ULT_DDR3L

XTAL24_IN

A25

XTAL24_IN

XTAL24_OUT

RSVD5

RSVD6

DIFFCLK_BIASREF

CLOCK

SIGNALS

6 OF 19

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

8 OF 19

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

DSWVRMEN

DPWROK

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_SUS

SLP_LAN

2015/02/27

2015/02/27

2015/02/27

WAKE

SLP_A

XTAL24_OUT

B25

K21

M21

DIFFCLK_BIASREF

C26

MCP_TESTLOW1

C35

MCP_TESTLOW2

C34

MCP_TESTLOW3

AK8

MCP_TESTLOW4

AL8

CLK_PCI_EC_R

AN15

CLK_PCI_TPM_R

AP15

B35

A35

AW7

DSWODVREN

AV5

AJ5

WAKE#

PM_CLKRUN#

V5

AG4

AE6

SUSCLK

PM_SLP_S5#

AP5

PM_SLP_S4#_R

AJ6

PM_SLP_S3#_R

AT4

AL5

AP4

AJ7

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+1.05VS_PLPTCLKPLL

RC72 3.01K_0402_1%

RC73 22_0402_5%

RC183 22_0402_5%

RC182 0_0402_5%@

RC82 0_0402_5%@

RC140 0_0402_5%@

RC141 0_0402_5%@

12

12

12

TPM@

1 2

1 2

1 2

1 2

2

2013/08/05

2013/08/05

2013/08/05

1

1

2

DIFFCLK_BIASREF

Width: 12-15Mil

Space:12Mil

Length: 500Mil

CLK_PCI_EC 44

CLK_PCI_TPM 32

EC_RSMRST#PCH_DPWROK_R

PCIE_WAKE# 44

PM_SLP_S5# 44

PM_SLP_S4# 44

PM_SLP_S3# 44

PCIE_CLKREQ1#9

PCIE_CLKREQ0#9

PCIE_CLKREQ5#9

D D

SYS_RESET#9

PM_CLKRUN#9

PCIE CLK2

PCIE CLK3

PCIE CLK4 GPU

+3VS

C C

1 2

RC120 10K_0402_5%

+3VALW_PCH

1 2

RC74 10K_0402_5%

1 2

RC76 10K_0402_5%

1 2

RC78 10K_0402_5%

1 2

RC90 10K_0402_5%

B B

1 2

CC104

1 2

CC103

1 2

CC101 1000P_0402_50V7K

EMC@

1 2

RC91 10K_0402_5%

RPC21

1 4

A A

2 3

CC142

1 2

10K_0404_4P2R_5%

1 2

5

GPU_CLKREQ#

AC_PRESENT_R

WAKE#

SUSWARN#_R

PCH_GPIO72

SYS_PWROK44

PCH_PWROK10,44

PLT_RST#19,32,37,40,44

EC_RSMRST#44

PBTN_OUT#44

1000P_0402_50V7KEMC_NS@

1000P_0402_50V7KEMC_NS@

1000P_0402_50V7KEMC_NS@

12

RC92100K_0402_5%

12

RC94100K_0402_1% @

RC951K_0402_5% @

12

RC10510K_0402_5% @

12

YC2

GND12OSC2

OSC1

GND2

24MHZ_6PF_7V24000032

Title

Title

Title

MCP (Clock,PM)

MCP (Clock,PM)

MCP (Clock,PM)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

XTAL24_OUT

3

4

1

CC11

3.3P_0402_50V8-C

2

10K_0804_8P4R_5%

CG510

CG510

CG510

1

RPC5

VCCRTC

MCP_TESTLOW1

MCP_TESTLOW2

MCP_TESTLOW3

MCP_TESTLOW4

DSWODVREN

DSWODVREN - On Die DSW VR Enable

H Enable

*

L Disable

Monday, May 11, 2015

Monday, May 11, 2015

Monday, May 11, 2015

18

27

36

45

12

RC77

330K_0402_5%

12

RC80

330K_0402_5%

@

8 59

8 59

8 59

0.2

0.2

0.2

5

1 2

RC97 10K_0402_5%@

RC98 10K_0402_5%1 2

RC99 10K_0402_5%1 2

+3VALW_PCH

D D

C C

B B

A A

+3VS

RC181 10K_0402_5%1 2

RPC6

10K_0804_8P4R_5%

RPC7

10K_0804_8P4R_5%

RPC8

10K_0804_8P4R_5%

RPC9

10K_0804_8P4R_5%

RPC17

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

RPC22

10K_0804_8P4R_5%

RPC2

10K_0804_8P4R_5%

RPC3

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

RPC4

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

RPC10

10K_0804_8P4R_5%

RPC11

10K_0804_8P4R_5%

RPC12

10K_0804_8P4R_5%

RPC13

10K_0804_8P4R_5%

RPC14

10K_0804_8P4R_5%

RPC15

10K_0804_8P4R_5%

RPC16

10K_0804_8P4R_5%

RPC18

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

PCH_GPIO12

DS3_WAKE#

PCH_GPIO25

PCH_GPIO13

18

PCH_GPIO57

27

PCH_GPIO26

36

PCH_GPIO9

45

PCH_GPIO45

18

PCH_GPIO46

27

USB_OC2#

36

PCH_GPIO14

45

PCH_GPIO47

18

PCH_GPIO28

27

ODD_EN

36

PCH_GPIO56

45

PCH_GPIO10

18

SML0_ALERT#

27

USB_OC0#

36

PCH_GPIO44

45

PCH_GPIO8

USB_OC3#

USB_OC1#

SMB_ALERT#

PCH_GPIO58

18

PCH_GPIO59

27

SML1_ALERT#

36

45

18

SERIRQ

PCIE_CLKREQ0#

27

36

SATA0GP

ODD_DETECT#

45

PCH_GPIO83

PCH_GPIO92

PCH_GPIO85

PCH_GPIO38

PCH_BT_OFF#

WLAN_CLKREQ#

PCH_GPIO33

LAN_CLKREQ#

18

SYS_RESET#

27

36

SATA3GP

PCH_GPIO71

45

ODD_DA#

18

PCIE_CLKREQ5#

27

PCH_GPIO50

36

PCH_GPIO76

45

PCH_GPIO90

18

PCH_GPIO2

27

PCH_GPIO93

36

PCH_GPIO91

45 CC23 .1U_0402_10V6-K1 2

PCH_GPIO3

18

PCH_GPIO1

27

PCH_GPIO94

36

PCH_GPIO4

45

PCH_GPIO5

18

PCH_GPIO69

27

CMOS_ON#

36

PCH_GPIO70

45

PCH_GPIO7

18

PCH_GPIO65

27

PCH_GPIO0

36

PCH_GPIO89

45

PCH_GPIO67

18

PCH_GPIO64

27

PCH_GPIO6

36

PCH_WLAN_OFF#

45

PCIE_CLKREQ1#

KBRST#

SATA2GP

PM_CLKRUN#

VGA_PWRGD

5

EC_LID_OUT#44

SML0_ALERT# 7

SMB_ALERT# 7

SML1_ALERT# 7

PCIE_CLKREQ0# 8

SATA0GP 7

ODD_DETECT# 7,42

WLAN_CLKREQ# 8,40

LAN_CLKREQ# 8,37

SYS_RESET# 8

SATA3GP 7

PCIE_CLKREQ5# 8

LAN PCIE3

WLAN

PCIE4

PCIE_CLKREQ1# 8

SATA2GP 7

PM_CLKRUN# 8

RC96

PCIE5

GPU

PCIE_PRX_DTX_N337

PCIE_PRX_DTX_P337

PCIE_PTX_C_DRX_N337

PCIE_PTX_C_DRX_P337

PCIE_PRX_DTX_N440

PCIE_PRX_DTX_P440

PCIE_PTX_C_DRX_N440

PCIE_PTX_C_DRX_P440

@1 2

0_0402_5%

EC_SMI#44

PCH_BEEP43

PCIE_CRX_GTX_N[0..3]19

PCIE_CTX_C_GRX_N[0..3]19

PCIE_CTX_C_GRX_P[0..3]19

+1.05VS_PUSB3PLL

RC119 3.01K_0402_1%12

PCIE_RCOMP&PCIE_IREF

Width 12~15Mil

Space >12Mil

Length 500Mil

PCH_GPIO14

PCIE_CRX_GTX_P[0..3]19

4

EC_SMI#

1 2

RC111

0_0402_5%

CC16.1U_0402_10V6-K OPT@ 1 2

1 2

CC14.1U_0402_10V6-K OPT@

1 2

CC15.1U_0402_10V6-K OPT@

CC17.1U_0402_10V6-K OPT@ 1 2

CC18.1U_0402_10V6-K OPT@ 1 2

1 2

CC19.1U_0402_10V6-K OPT@

1 2

CC20.1U_0402_10V6-K OPT@

CC21.1U_0402_10V6-K OPT@ 1 2

CC22 .1U_0402_10V6-K1 2

CC24 .1U_0402_10V6-K1 2

1 2

CC25 .1U_0402_10V6-K

4

@

PCH_GPIO76

PCH_GPIO8

PCH_GPIO12

BOARD_ID0

ODD_DA#

ODD_EN

DS3_WAKE#

PCH_GPIO28

PCH_GPIO26

PCH_GPIO56

PCH_GPIO57

PCH_GPIO58

PCH_GPIO59

PCH_GPIO44

PCH_GPIO47

VGA_PWRGD

BOARD_ID4

PCH_GPIO71

PCH_GPIO13

PCH_GPIO14

PCH_GPIO25

PCH_GPIO45

PCH_GPIO46

PCH_GPIO9

PCH_GPIO10

PCH_GPIO33

PCH_GPIO70

PCH_GPIO38

BOARD_ID2

PCH_BEEP

PCIE_CRX_GTX_N0

PCIE_CRX_GTX_P0

PCIE_CTX_GRX_N0PCIE_CTX_C_GRX_N0

PCIE_CTX_GRX_P0PCIE_CTX_C_GRX_P0

PCIE_CRX_GTX_N1

PCIE_CRX_GTX_P1

PCIE_CTX_GRX_N1PCIE_CTX_C_GRX_N1

PCIE_CTX_GRX_P1PCIE_CTX_C_GRX_P1

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P2

PCIE_CTX_GRX_N2PCIE_CTX_C_GRX_N2

PCIE_CTX_GRX_P2PCIE_CTX_C_GRX_P2

PCIE_CRX_GTX_N3

PCIE_CRX_GTX_P3

PCIE_CTX_GRX_N3PCIE_CTX_C_GRX_N3

PCIE_CTX_GRX_P3PCIE_CTX_C_GRX_P3

PCIE_PRX_DTX_N3

PCIE_PRX_DTX_P3

PCIE_PTX_DRX_N3

PCIE_PTX_DRX_P3

PCIE_PRX_DTX_N4

PCIE_PRX_DTX_P4

PCIE_PTX_DRX_N4

PCIE_PTX_DRX_P4

PCIE_RCOMP

UC1J

P1

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12

AD6

GPIO15

Y1

GPIO16

T3

GPIO17

AD5

GPIO24

AN5

GPIO27

AD7

GPIO28

AN3

GPIO26

AG6

GPIO56

AP1

GPIO57

AL4

GPIO58

AT5

GPIO59

AK4

GPIO44

AB6

GPIO47

U4

GPIO48

Y3

GPIO49

P3

GPIO50

Y2

HSIOPC/GPIO71

AT3

GPIO13

AH4

GPIO14

AM4

GPIO25

AG5

GPIO45

AG3

GPIO46

AM3

GPIO9

AM2

GPIO10

P2

DEVSLP0/GPIO33

C4

SDIO_POWER_EN/GPIO70

L2

DEVSLP1/GPIO38

N5

DEVSLP2/GPIO39

V2

SPKR/GPIO81

BROADWELL-ULT-DDR3L_BGA1168

@

UC1K

F10

PERN5_L0

E10

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PETN5_L1

A23

PETP5_L1

H10

PERN5_L2

G10

PERP5_L2

B21

PETN5_L2

C21

PETP5_L2

E6

PERN5_L3

F6

PERP5_L3

B22

PETN5_L3

A21

PETP5_L3

G11

PERN3

F11

PERP3

C29

PETN3

B30

PETP3

F13

PERN4

G13

PERP4

B29

PETN4

A29

PETP4

G17

PERN1/USB3RN3

F17

PERP1/USB3RP3

C30

PETN1/USB3TN3

C31

PETP1/USB3TP3

F15

PERN2/USB3RN4

G15

PERP2/USB3RP4

B31

PETN2/USB3TN4

A31

PETP2/USB3TP4

E15

RSVD9

E13

RSVD10

A27

PCIE_RCOMP

B27

PCIE_IREF

BROADWELL-ULT-DDR3L_BGA1168

@

HSW_ULT_DDR3L

GPIO

10 OF 19

HSW_ULT_DDR3L

PCIE USB

11 OF 19

CPU/

MISC

SERIAL IO

3

THRMTRIP

RCIN/GPIO82

SERIRQ

PCH_OPI_RCOMP

RSVD7

RSVD8

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

RSVD11

RSVD12

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

3

D60

V4

T4

AW15

AF20

AB21

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4

F2

F3

G4

F1

E3

F4

D3

E4

C3

E2

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

CC102

@

H_THRMTRIP#_R

KBRST#

SERIRQ

OPI_COMP

PCH_GPIO83

BOARD_ID1

PCH_GPIO85

PCH_GPIO86

PCH_BT_OFF#

PCH_WLAN_OFF#

PCH_GPIO89

PCH_GPIO90

PCH_GPIO91

PCH_GPIO92PCH_GPIO50

PCH_GPIO93

PCH_GPIO94

PCH_GPIO0

PCH_GPIO1

PCH_GPIO2

PCH_GPIO3

PCH_GPIO4

PCH_GPIO5

PCH_GPIO6

PCH_GPIO7

PCH_GPIO64

PCH_GPIO65

PCH_GPIO67

CMOS_ON#

PCH_GPIO69

USB20_N0

USB20_P0

USB20_N1

USB20_P1

USB20_N3

USB20_P3

USB20_N5

USB20_P5

USB20_N6

USB20_P6

USB30_RX_N1

USB30_RX_P1

USB30_TX_N1

USB30_TX_P1

USBRBIAS

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

H_THRMTRIP#_R

.01U_0402_16V7-K

1

2

+1.05V_VCCST

RC104

1K_0402_5%

1 2

RC106 49.9_0402_1%12

1

@

TC41

1 2

RC112 0_0402_5%

@

USB20_N0 41

USB20_P0 41

USB20_N1 41

USB20_P1 41

USB20_N3 30

USB20_P3 30

USB20_N5 33

USB20_P5 33

USB20_N6 40

USB20_P6 40

USB30_RX_N1 41

USB30_RX_P1 41

USB30_TX_N1 41

USB30_TX_P1 41

RC118

12

22.6_0402_1%

USB_OC1# 41

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

EC_SCI# 44

LEFT USB (2.0)

LEFT USB (3.0)

Card reader

Camera

BT

LEFT USB (3.0)

USBRBIAS

Width 20Mil

Space 15Mil

Length 500Mil

2

KBRST# 44

SERIRQ 32,44

OPI_RCOMP

Width 20Mil

Space 15Mil

Length 500Mil

PCH_BT_OFF# 40

PCH_WLAN_OFF# 40

2015/02/27

2015/02/27

2015/02/27

2

BOARD_ID34

BOARD_ID0X1BOARD_ID1

0

X

X

X

X

X

X

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

X

X

X

X

X

X

PCH_GPIO86

GPIO86, Internal PD

1: LPC

*0: SPI

PCH_BEEP

GPIO81, No Reboot, Internal PD

1: Enabled No Reboot Mode

*0: Disable No Reboot Mode

2013/08/05

2013/08/05

2013/08/05

1

RC101

10K_0402_5%

15@

1 2

RC108

10K_0402_5%

14@

1 2

DIS SKU

UMA SKU

15" SKU1

14" SKU0

MH2G@: H5TC4G63CFR-PBA

MS4G@: K4B8G1646Q-MYK01

MM4G@: MT41K512M16HA-125:A

+3VS

Saturday, May 09, 2015

Saturday, May 09, 2015

Saturday, May 09, 2015

RC102

10K_0402_5%

@

RC109

10K_0402_5%

@

Description

CG510

CG510

CG510

1

RC100

10K_0402_5%

OPT@

1 2

1 2

RC107

10K_0402_5%

UMA@

1 2

1 2

BOARD_ID3BOARD_ID2

RC116 1K_0402_5%@ 12

RC117 1K_0402_5%@

BOARD_ID4

X

X

XXX

X

XXX

X

0 0

1

00

0

1

0 MH4G@: H5TC8G63AMR-PBA

12

Title

Title

Title

MCP (GPIO,USB,PCIE)

MCP (GPIO,USB,PCIE)

MCP (GPIO,USB,PCIE)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

X X

X XX

0 MS2G@: K4B4G1646Q-HYK0

0 MM2G@: MT41K256M16LY-107:N1

100

1 0 1

+3VS+3VALW_PCH

1 2

1 2

RC121

10K_0402_5%

@

RC123

10K_0402_5%

@

RC184

10K_0402_5%

@

1 2

RC185

10K_0402_5%

@

1 2

9 59

9 59

9 59

0.2

0.2

0.2

5 4 3 2

1

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

CPU_CORE

UC1L

+1.35V

Need short

JC1

112

JUMP_43X79

D D

VCC_SENSE

Length Match: <25Mil

Space: More Than 25Mil

1

2

RC131

75_0402_1%

1 2

RC133 43_0402_5%

RC134 0_0402_5%@

RC135 0_0402_5%@

12

@

0_0402_5%

1

2

GND Reference

CPU_VCC_SENSE59

12

1 2

1 2

CC46

0.01U_0402_16V7K

@

+1.05VS

2

G

+VCCIO_OUT

CC36

4.7U_0603_10V6-K

@

C C

SVID

1, Stripline Line, No More Than 6000Mil

2, Alert# Route Between CLK and Data

3, CLK Length<Data Length<CLK Length + 2000Mil

4, Space at least 18Mil

CPU_SVID_ALERT#59

CPU_SVID_CLK59

B B

CPU_SVID_DAT59

PCH_PWROK

RC138

RC128

+1.05VS

RC129 150_0402_1%@

1 2

LC1

0_0402_5%

+1.05VS

12

+3VALW

RC136

10K_0402_5%

@

1 2

61

D

QC6A

2N7002KDWH_SOT363-6

@

S

1 2

@

0_0402_5%

@

CC39

22U_0805_6.3V6M

BCD@

RC132

130_0402_1%

CPU_SVID_ALERT#_R

CPU_SVID_CLK_R

CPU_SVID_DAT_R

+1.05V_VCCST

@

2

CPU_CORE

RC127

100_0402_1%

1 2

+VCCIOA_OUT

CPU_VR_ON59

12

1

2

12

CC42

.1U_0402_10V6-K

@

5

G

+1.35V_CPU

RC130

VCCST(0.1A)

1

CC40

1U_0402_10V6K

2

BCD@

+1.05V_VCCST

1 2

34

D

S

CPU_CORE

CPU_SVID_ALERT#_R

CPU_SVID_CLK_R

CPU_SVID_DAT_R

VCCST_PWRGD

CPU_VR_ON

CPU_VR_READY

PWR_DEBUG

12

10K_0402_5%

CPU_CORE

33P_0402_50V8J

For RF

RC137

1K_0402_5%

VCCST_PWRGD

QC6B

2N7002KDWH_SOT363-6

@

CC2

1

2

@

L59

RSVD13

J58

RSVD14

AH26

VDDQ1

AJ31

VDDQ2

AJ33

VDDQ3

AJ37

VDDQ4

AN33

VDDQ5

AP43

VDDQ6

AR48

VDDQ7

AY35

VDDQ8

AY40

VDDQ9

AY44

VDDQ10

AY50

VDDQ11

F59

VCC1

N58

RSVD15

AC58

RSVD16

E63

VCC_SENSE

AB23

RSVD17

A59

VCCIO_OUT

E20

VCCIOA_OUT

AD23

RSVD18

AA23

RSVD19

AE59

RSVD20

L62

VIDALERT

N63

VIDSCLK

L63

VIDSOUT

B59

VCCST_PWRGD

F60

VR_EN

C59

VR_READY

D63

VSS344

H59

PWR_DEBUG

P62

VSS345

P60

1

TC53@

TC54@

TC55@

1

P61

1

N59

N61

T59

AD60

AD59

AA59

AE60

AC59

AG58

U59

V59

AC22

AE22

AE23

AB57

AD57

AG57

C24

C28

C32

2

CC140

1000P_0402_50V7K

@

1

RSVD_TP1

RSVD_TP2

RSVD_TP3

RSVD_TP4

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

VCCST1

VCCST2

VCCST3

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

BROADWELL-ULT-DDR3L_BGA1168

@

VCCST_PWRGD 8,44

HSW_ULT_DDR3L

HSW ULT POWER

12 OF 19

+1.35V_CPU

2.2U_0603_10V6-K

2.2U_0603_10V6-K

2.2U_0603_10V6-K

CC27

CC26

1

1

2

2

CD@

For cost down, change to X5R.

10U_0603_6.3V6M

10U_0603_6.3V6M

CC34

CC30

1

2

1.35V_CPU(1.4A)

HW 4PCS 2.2UF CAP Mounted

HW 6PCS 10UF CAP Mounted

PWR 2PCS 470U Near VR Output

+1.35V_CPU

CC37

33P_0402_50V8J

1

2

@

1

2

CD@

CC38

33P_0402_50V8J

1

2

@

1

2

10U_0603_6.3V6M

CC35

1

2

BCD@

2.2U_0603_10V6-K

CC28

CC29

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

CC31

CC32

1

1

1

2

2

@

2

BCD@

330U_2.5V_M

CC33

1

CC41

+

2

@

For RF

CPU_VR_ON

RC146

10K_0402_5%

1 2

1 2

VR_CPU_PWROK44,59

RC155 0_0402_5%

CPU_VR_READY

1

CC141

100P_0402_50V8J

@

2

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2015/02/27

2015/02/27

2015/02/27

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2013/08/05

2013/08/05

2013/08/05

2

Title

MCP (Power)

MCP (Power)

MCP (Power)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

CG510

CG510

CG510

Saturday, May 09, 2015

Saturday, May 09, 2015

Saturday, May 09, 2015

10 59

10 59

10 59

1

0.2

0.2

0.2

5 4 3 2

+3VALW_PCH

2

CC50

1U_0402_10V6K

1

AH11

AG10

AE7

+DCPRTC

VCCSPI 18mA

Y8

+1.05VS

AG14

AG13

VCCASW[1:5] 658mA

J11

H11

H15

AE8

AF22

+PCH_DCPSUSBYP+1.05VS_DCPSUS2

AG19

AG20

AE9

AF9

AG8

+1.05VS_DCPSUS1

AD10

AD8

VCCTS1_5 3mA

J15

K14

K16

VCCSDIO 17mA

U8

T9

+1.05VS_DCPSUS4

AB8

AC20

AG16

AG17

+1.05VS

2

1

VCCSPI

+1.5VS

1U_0402_10V6K

CC77

CC52

0.1U_0402_10V7K

CC58

2

@

1

CC61

CC66

CC73

VCCRTC 1mA

12

0.1U_0402_10V7K

1U_0402_10V6K

12

12

1U_0402_10V6K

1U_0402_10V6K

12

VCCRTC

CC57

CC56

CC55

0.1U_0402_10V7K

0.1U_0402_10V7K

1U_0402_10V6K

2

2

2

1

1

1

CD@

CC64