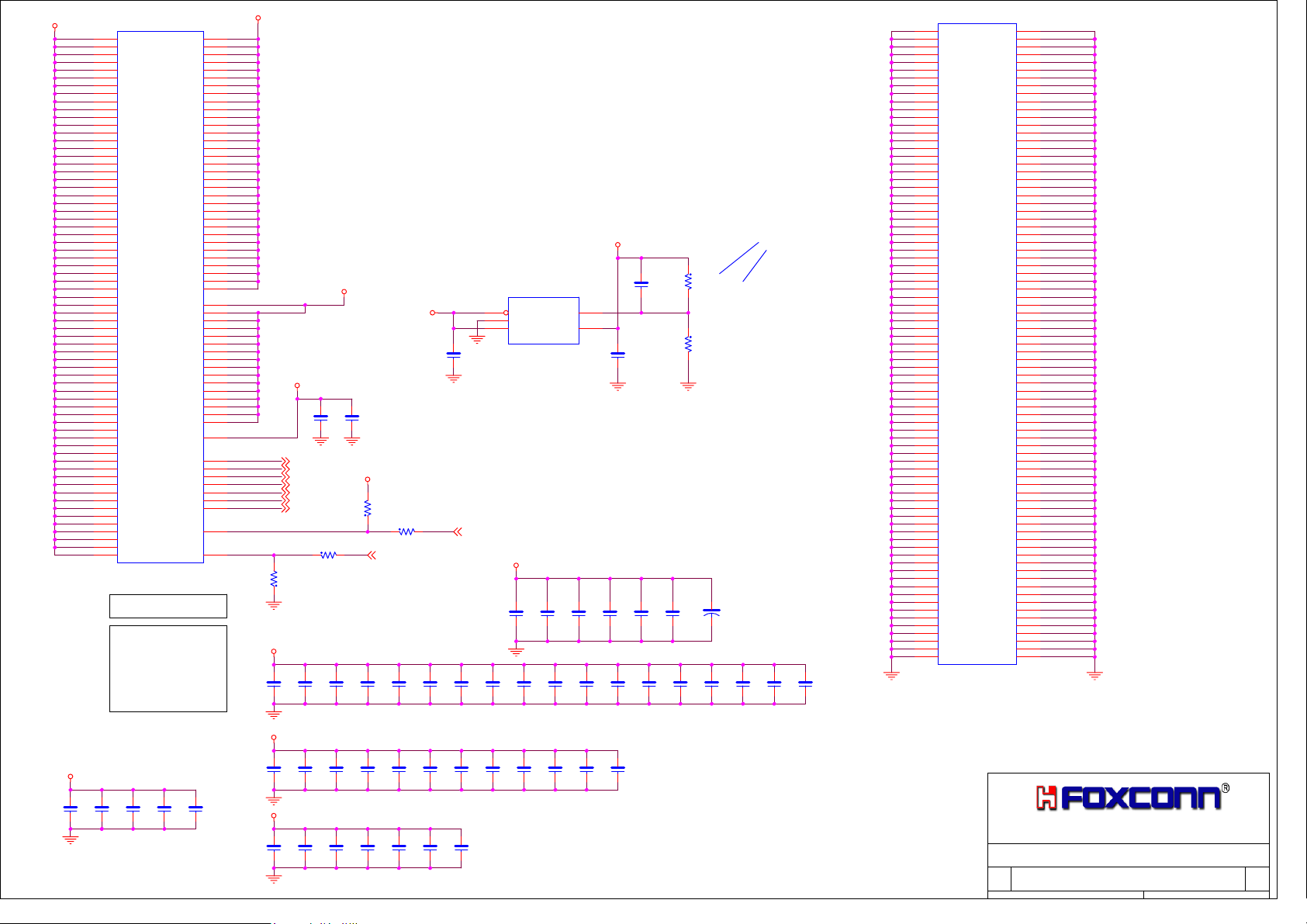

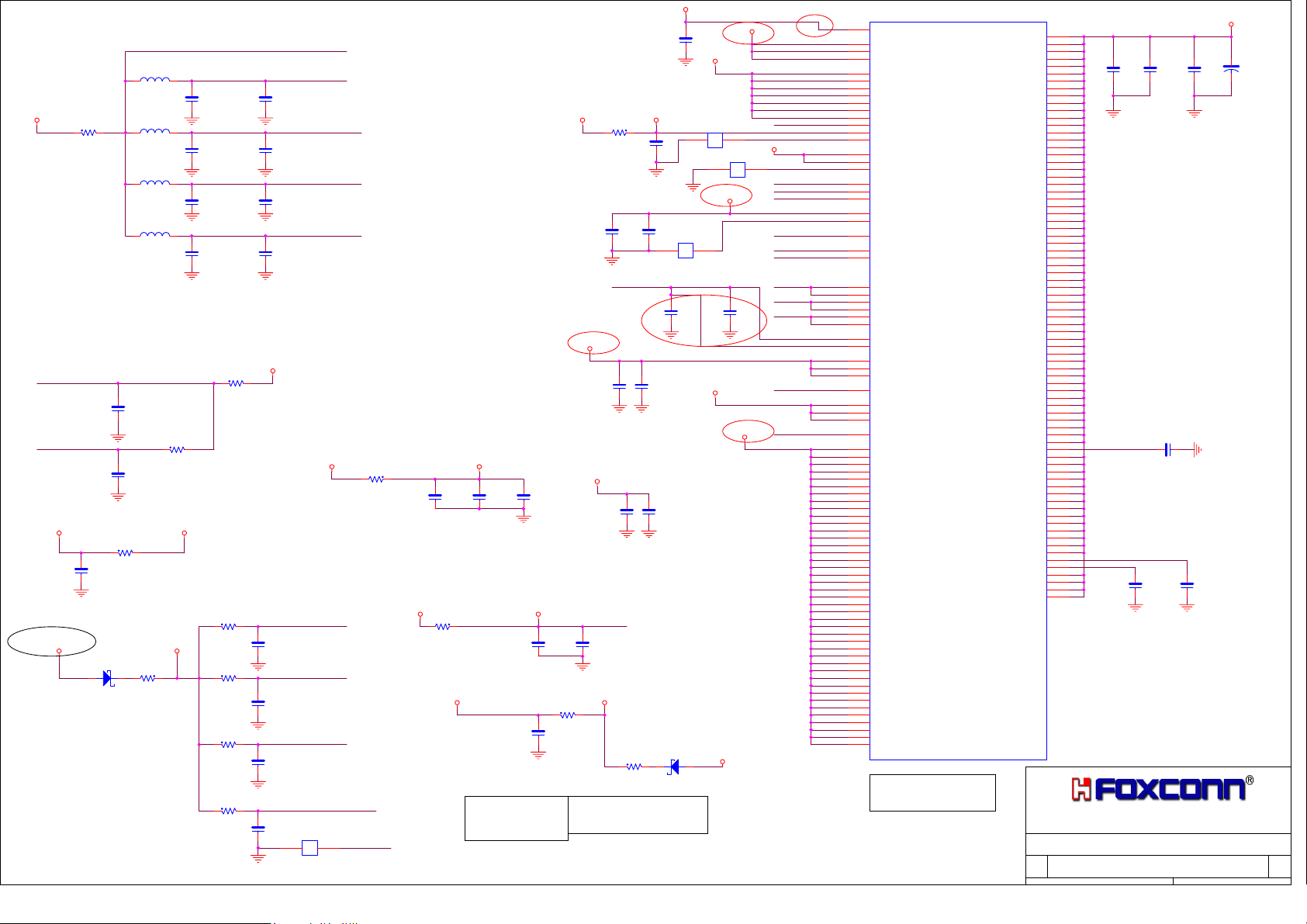

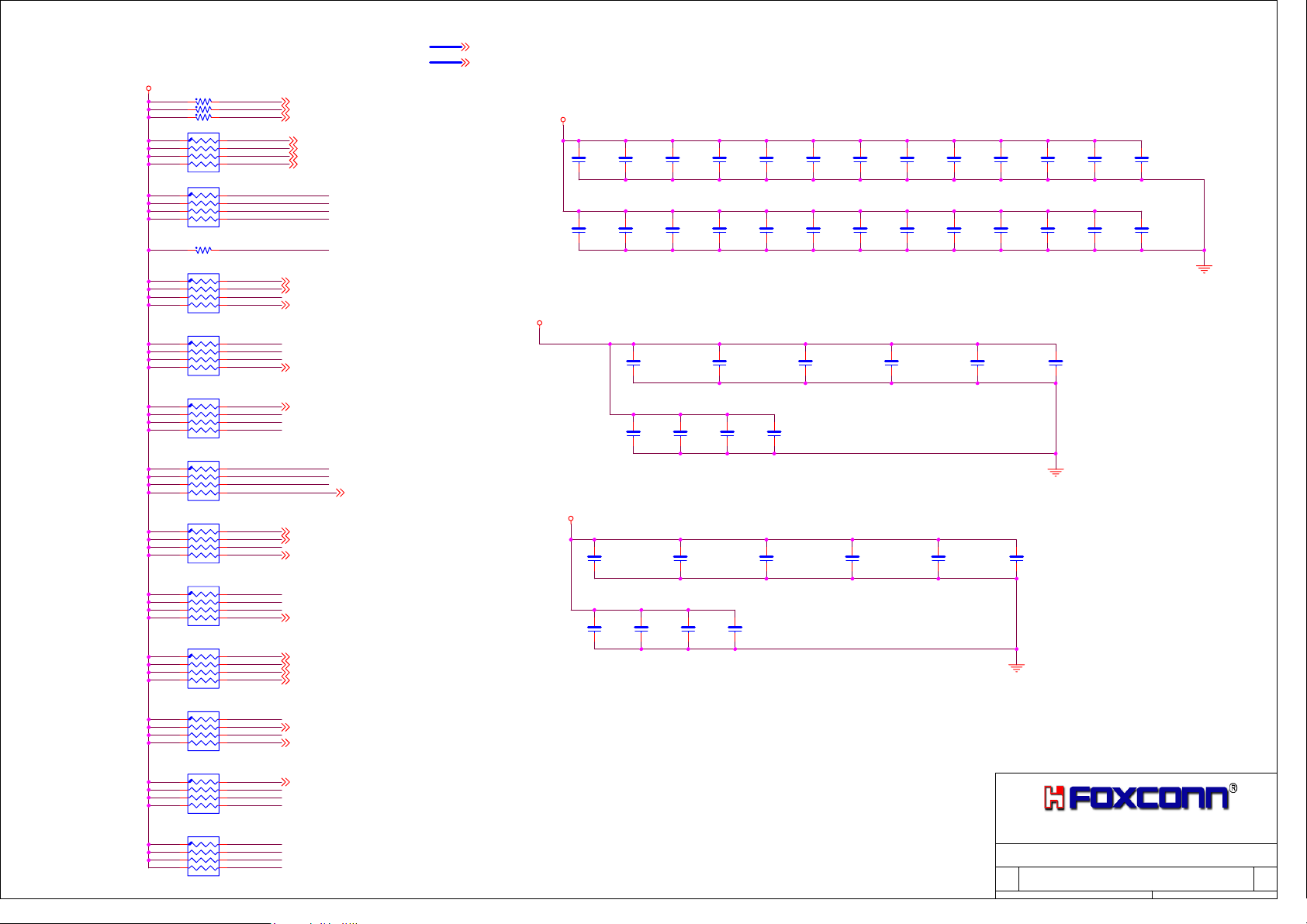

Page 1

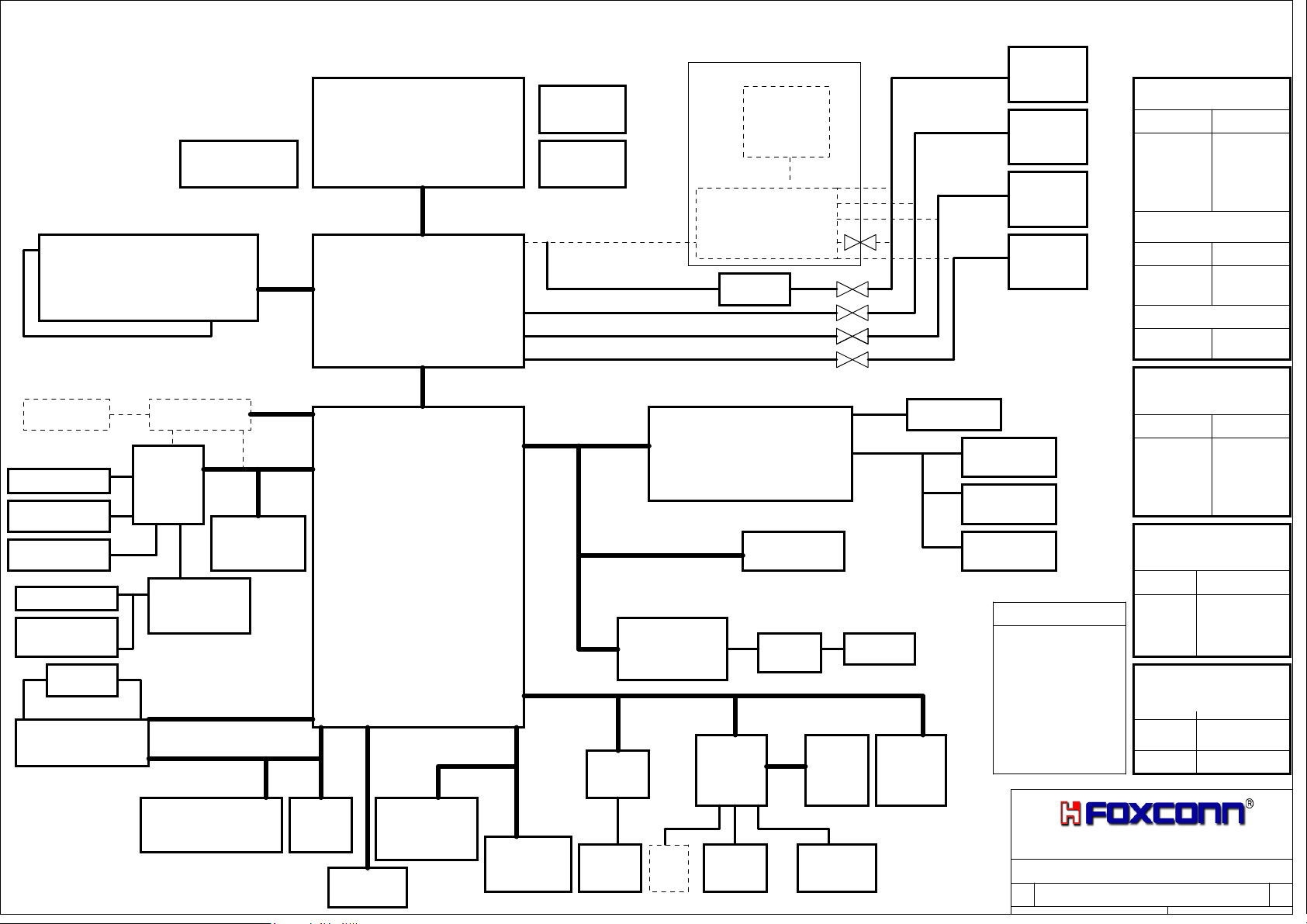

CLK GEN

www.hocnghetructuyen.vn

ICS954226

DDR2

400/533/667Mhz

LCD/BTN

S/P DIF

Line In

MIC In

LineOut

Speaker

PWR SW

30

30

30

30

30

22

Audio DJ

AC'97

CODEC

ALC655

29

OP AMP

GMT1421b

PCI Express

PCI-E Card

22

BlueTooth

W06N Block Diagram

Thermal

G768D

21

T8

MAX6510

21

PCI Express

SDVO

RGB

LVDS

S-Video

PCI BUS

LAN

RTL8100CL

LPC BUS

NS

87381

PATA

22

FIR

34

34

03

11,12

LPC

31

AC-Link

MODEM

MDC Card

23

30

Mobile CPU

Yonah

C1 Stepping

Calistoga

B1 Stepping

ICH7-M

B2 Stepping

SATA

HDD

(master)

USB

4 PORT

HDD

Reserve

USB*6

DB

04.05

533 / 667 MHzHOST BUS

PM

GM

GML

06,07,08,09,10

100MHzDMI I/F

17.18.19.20

ODD

22

(slave)

MXM VGA Card

VRAM*4

M24-P/NV43

DB

CH7307

15

Cardbus/1394/

CardReader

ENE CB810

Mini-PCI

802.11A/B/G

TXFM

27

KBC

ENE

PS2

KB3910

Touch

Pad

32

33 33

DB

XD

INT_KB

24,25

BIOS

4Mb

Switch

28

RJ45

LPC

DEBUG

CONN.

35 35

TMDS

RGB

LVDS

PWR SW

CP2211

DB

S-Video

25

CARDBUS

ONE SLOT

CardReader

7 in 1

1394*1

DVI

CONN

15

CRT

CONN

14

LCD

XGA/SXGA+

16

TV-OUT

DB

SYSTEM DC/DC

MAX1999

INPUTS

DCBATOUT

SYSTEM DC/DC

MAX1845

INPUTS OUTPUTS

DCBATOUT

Maxim 8550

DCBATOUT

OUTPUTS

5V_S5

3V_S5

5V_AUX

3D3V_AUX

1D05V_S0

1D5V_S0

1D8V_S3

0D9V_S0

MAXIM CHARGER

MAX1645B

OUTPUTSINPUTS

BT+

26

26

DCBATOUT

18V 4.0A

5V_AUX

5V 100mA

CPU DC/DC

26

PCB LAYER

L1:

Signal 1

GND

L2:

L3: Signal 2

Signal 3

L4:

VCCL5:

L6:

Signal 4

INPUTS

DCBATOUT

SYSTEM DC/DC

MAX1993

(external VGA Core)

INPUTS

DCBATOUT

SC452

OUTPUTS

VCC_CORE

0.844~1.3V

27A

OUTPUTS

1D2V_S0

FOXCONN ND2

Title

Size Document Number Rev

<Doc>

A3

Date: Sheet of

Block Diagram

W06N

144Saturday, February 19, 2005

40

38

39

DB

37

DB

SA

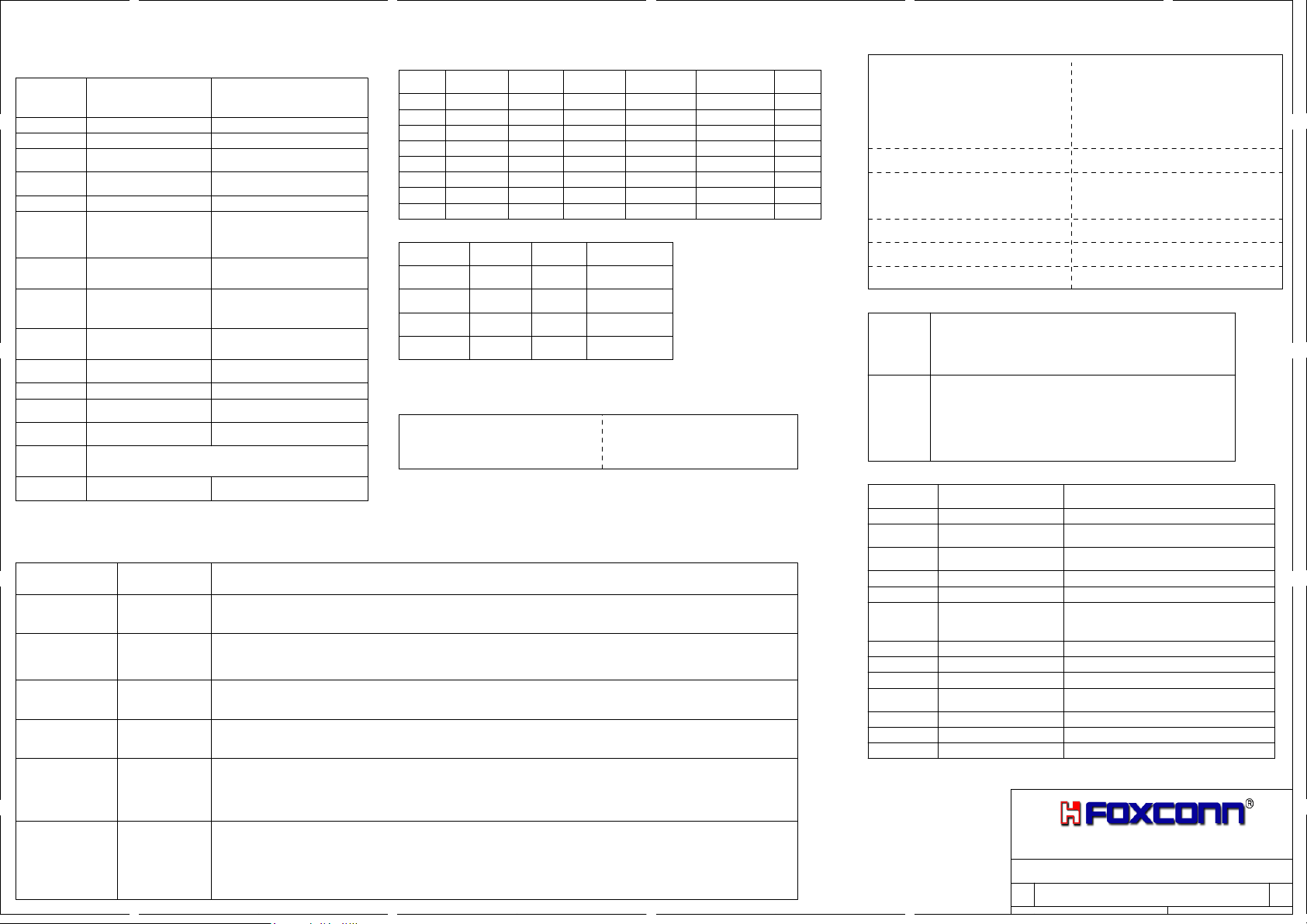

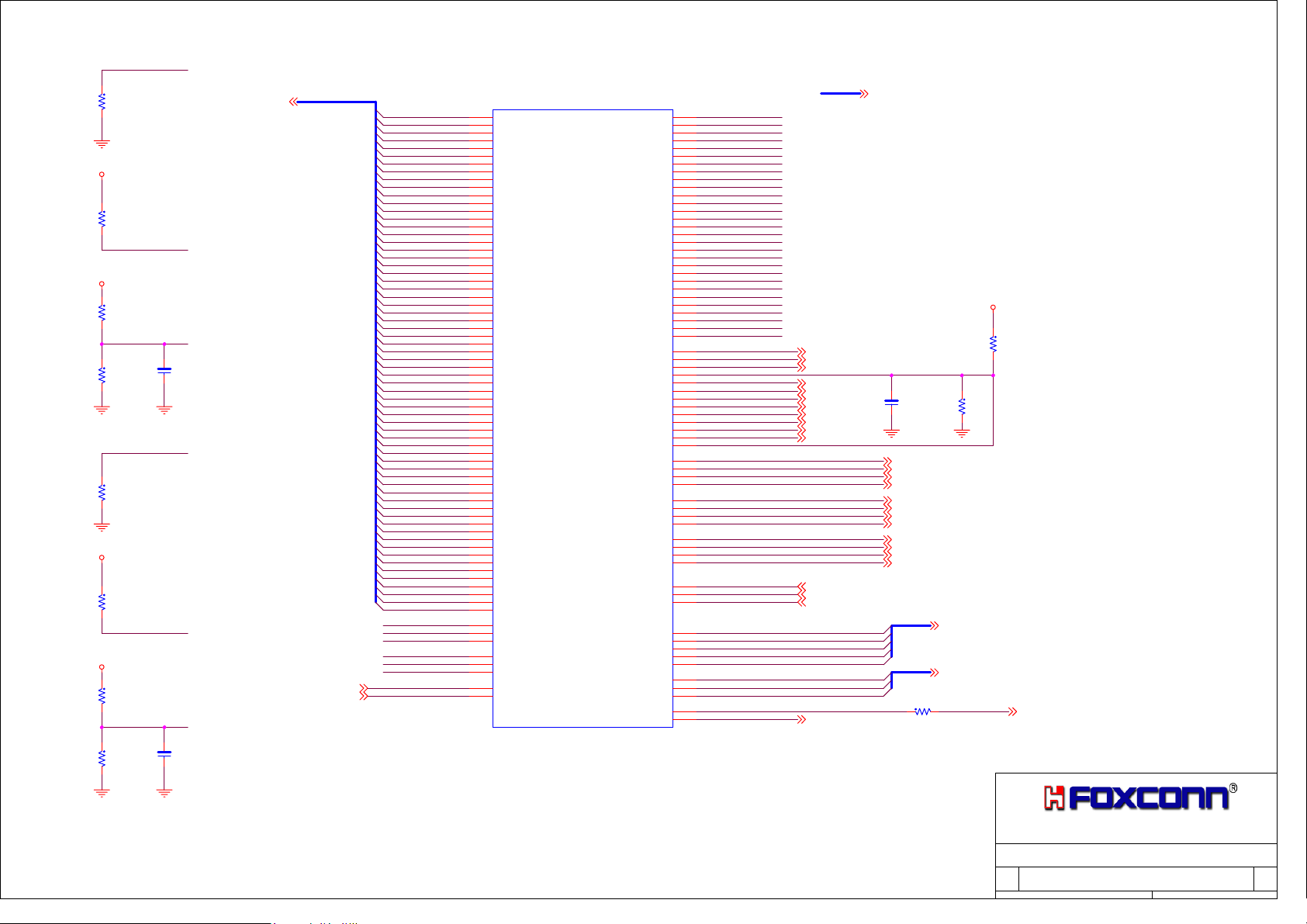

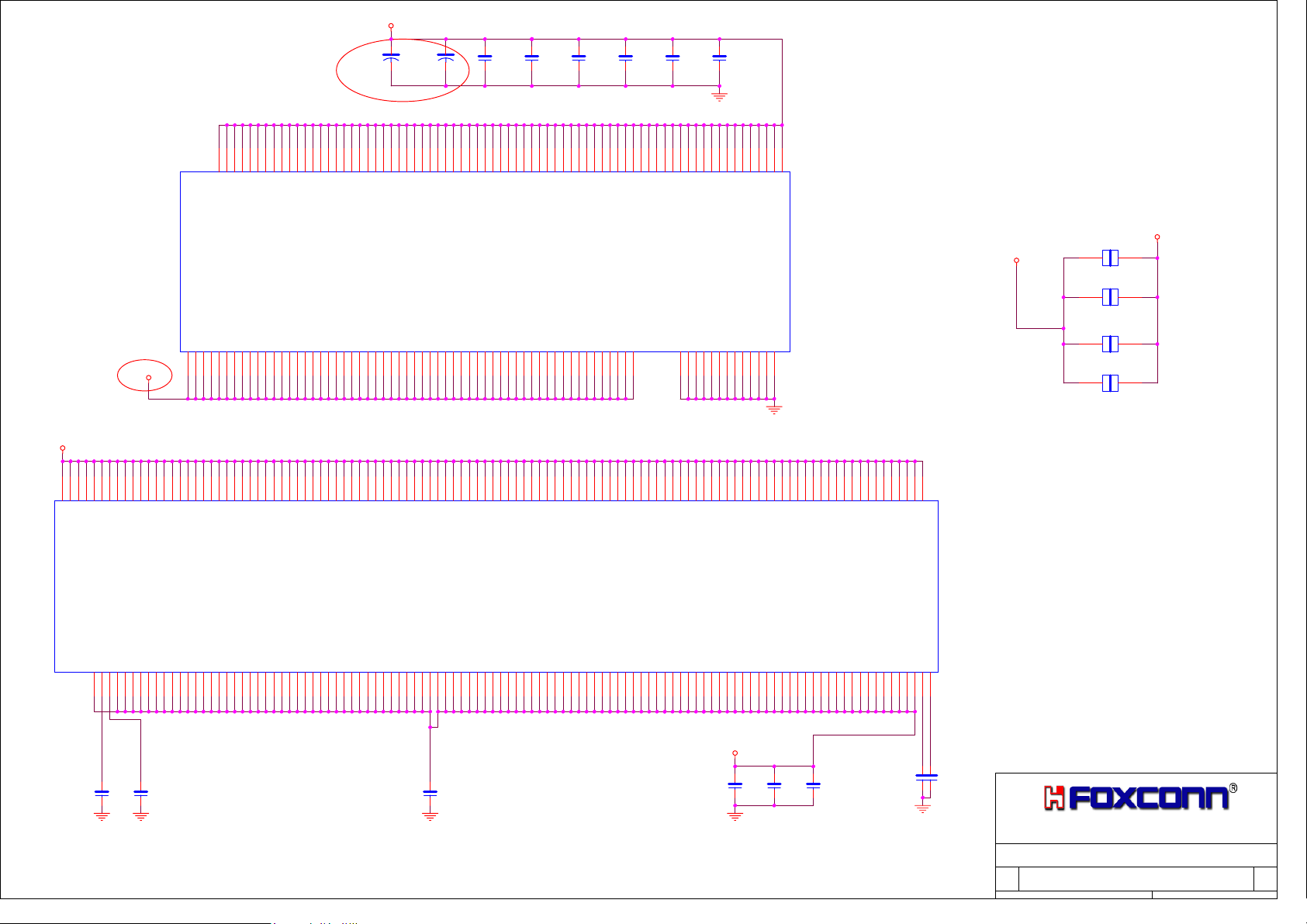

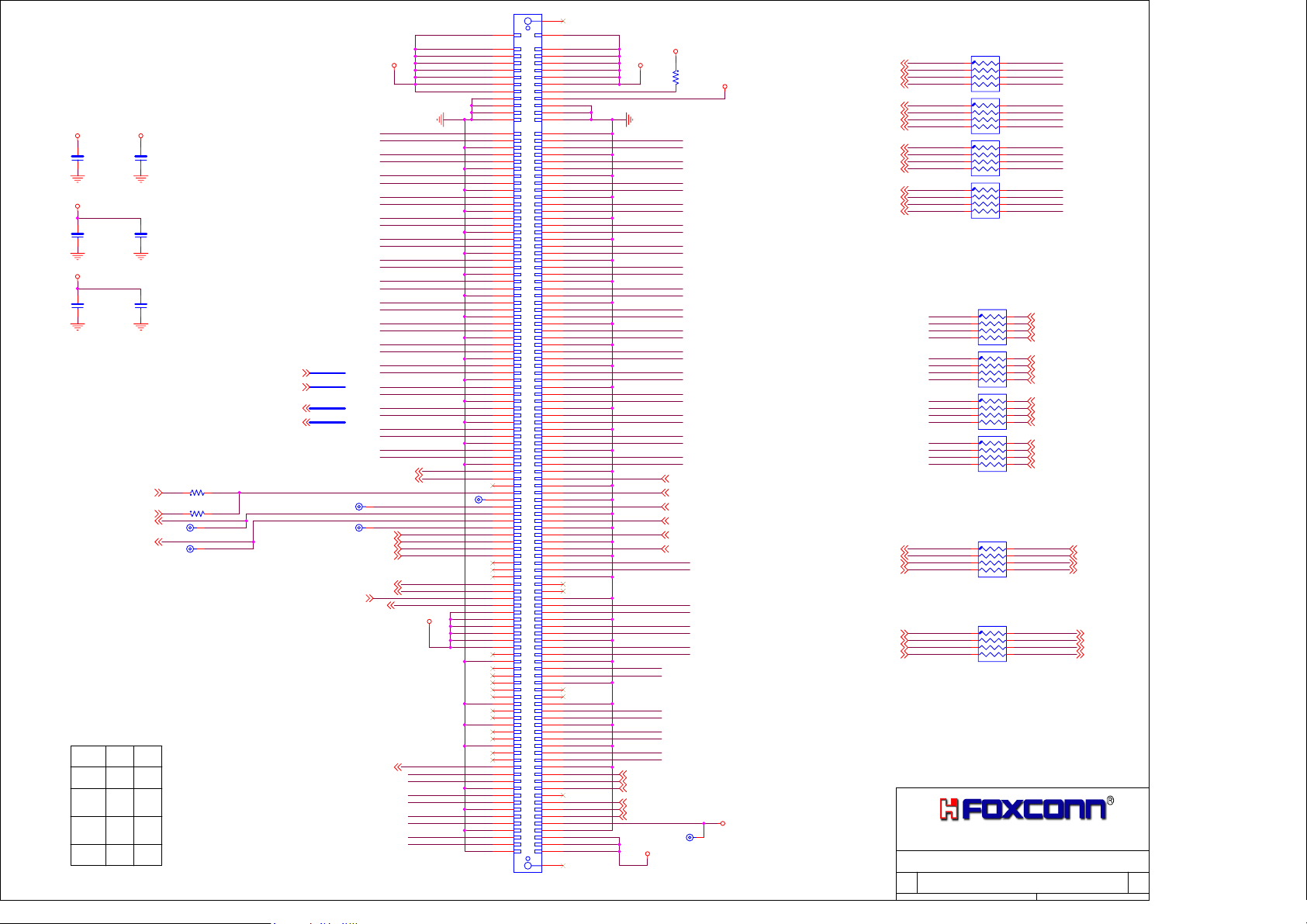

Page 2

Calistoga Strapping Signals

www.hocnghetructuyen.vn

A

and Configuration

Pin Name Strap Description Configuration

CFG[2:0]

CFG[3:4]

4 4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG[13:12]

CFG[14:15]

3 3

CFG16

CFG17

CFG18

CFG19

CFG20

SDVO

CRTL_DATA

All strap signals are sampled with respect to the leading

NOTE:

edge of the Alviso GMCH PWORK In signal.

FSB Frequency Select

Reversed

DMI x2 Select

NB strap

CPU Strap

Reversed

PCI Express Graphics

Lane reverse option

for layout convenience

Reversed

Reversed

Reversed

Reversed

Reversed

Reversed

FSB Dynamic ODT 0 = Dynamic ODT Disabled

Reversed

GMCH core VCC

Select

DMI Lane Reversal

0= Only SDVO or PCIEx1 is operational ( default)

1= SDVO and PCIE x1 are operating

simultaneously via the PEG port

SDVO Present

001 = FSB533

011 = FSB667

Others = Reversed

0 = DMI x2

1 = DMI x4

0 = Moby Dick

1 = Calistoga

0= Reserved

1=Mobility

0=Reverse Lanes

1=Normal Operation

1 = Dynamic ODT Enabled

(Default)

0 = 1.05V

1 = 1.5V

0 = Normal

1 = Lanes Reversal

0 = No SDVO device present

1= SDVO device present

(Default)

(Default)

(Default)

(Default)

(Default)

(Default)

(Default)

KBC Hardware Strap

PinNumber PinName Function

2 2

125

128

131

11

A1

A4

A5

GPIO05

High:Enable the internal pull-up resistors on XIOCS [F:0] pins

Low:Disable the internal pull-up resistors on XIOCS [F:0]

High: Diasble DMPP(Recommended)

Low : Enable DMPP

High:Enable EMWB(Recommended for application using shared BIOS

Low:Disable EMWB

High:Test Mode

Low:32KHz clock in normal running(Recommend)

page 7

B

ICS954226 Spread Spectrum

C

Select

Byte 6b7

1

1

1

1

1

1

1

1

Byte 6b6

byte 6b5 Byte 6b4 Spread Mode Spread Amount%

00 0

00

00

1

0

11

00

1

0

11

11

11 1

1

0

Down

Down

Down

Down

Center

Center

Center

Center

PCI Routing

IRQ

CB810

MiniPCI

LAN

25

21

23

1394 19 3E

E

G

F

REQ/GNTIDSEL

0

1

2

ICH7-M IDE Integrated Series

Termination Resistors

DD[15:0],

DDACK#,

DCS3#,

IORDY,

IDEIRQ

DIOR#, DREQ,DIOW#,

DA[2:0],

DCS1#,

approximately 33 ohm

page 3

0.8

1.25

1.75

2.5

+-0.3

+-0.5

+-0.8

+-1.25

Pin17/18

Mhz

100

100

100

100

100

100

100

100

D

ICH7-M Integrated Pull-up

and Pull-down Resistors

GNT[3:0]

GNT[5]#/GPO[17],

GPIO[25]

LAN_RXD[2:0],

TP[3]

ACZ_RST#, ACZ_SDIN[2:0],

ACZ_SYNC,ACZ_SDOUT,

EE_CS,

DDREQ

DPRSTP#

SPI_ARB, SPI_CLK,

SPKR,

(Default)

EE_DIN,EE_DOUT,

GNT[4]#/GPO[48],

GNT[6]#/GPO[16],

LAD[3:0]#/FB[3:0]#,

LDRQ[0], LDRQ[1]/GPI[41],PME#,

PWRBTN#,

SATALED#

ACZ_BITCLK,

DPRSLPVR,

USB[7:0][P,N]

DD[7],

LAN_CLK

ICH7-M Strapping Options

This signal enables the internal VccSus1_5V suspend

regulator when connected to VccRTC. When connected to

GND, the internal regulator is disabled.

INVTVRMEN

SPKR

Pin Name Strap Description Configuration

GNT3#

LINKALERT#

SPKR

INTVRMEN

GPIO25

EE_CS

GNT5#

/GPIO17#.

GNT4#

/GPIO48.

EE_DOUT

ACZ_SDOUT

ACZ_SYNC

GPIO16/

DPRSLPVR

SATALED# Reversed

REQ[4:1]# XOR Chain Selection

TP3 XOR Chain Entrance

To enable internla VccSus1_5V VRM pull signal to

VccRTC via 330Kohm

The signal has a weak internal pull-down. If the

signal is sampled high, this indicates that the

system is strapped to the "No Reboot" mode (ICH7M

will disable the TCO Timer system reboot feature).

The status of this strap is readable via the NO

REBOOT bit. NOTE: Please refer to ICH7M EDS Rev0.5

(or latest) for all ICH7M Strap details.

Top-Block Swap

Override

Reversed

No Reboot

VccSus1_05 VRM

Enable/Disable.

Reserved

Reversed

Boot BIOS

Destination

Selection

Reversed

XOR Chain Entrance

PCI-E Port CFG Bit 0 Reversed

Reversed

E

ICH7-M EDS 16971 1.0V1

ICH7 internal 20K pull-ups

ICH7 internal 15K pull-ups

ICH7 internal 20K pull-downs

ICH7 internal 15K pull-downs

ICH7 internal 11.5K pull-downs

ICH7 internal 100K pull-downs

Internal Pull-up for

top-block swap mode.

Internal pull-down to indicate system

is strapped to the no reboot more.

0 = Disable

1 = Enable

01 = SPI

10 = PCI

11 = LPC

0 = Allow XOR Testing

1 = Not Allow

Not available in Datasheet Yet

Not available in Datasheet Yet

(Default)

(Default)

(Default)

12

GPIO06

High:Test Mode(KSOUT0~15 become DPLL internal data outputs,

KSO16 becomes internal power-on reset output

1 1

105

GPIO20

Low:Normal operation(Recommended)

High:Normal operation(Recommended)

Low:Enable ISP mode during which the RD#,WR#,MEMSEL#,A[20:0]

andD[7:0}will be controlled by ISP COntriller

Title

Size Document Number Rev

<Doc>

A3

Date: Sheet of

Table of content

W06N

244Saturday, February 19, 2005

SA

FOXCONN ND2

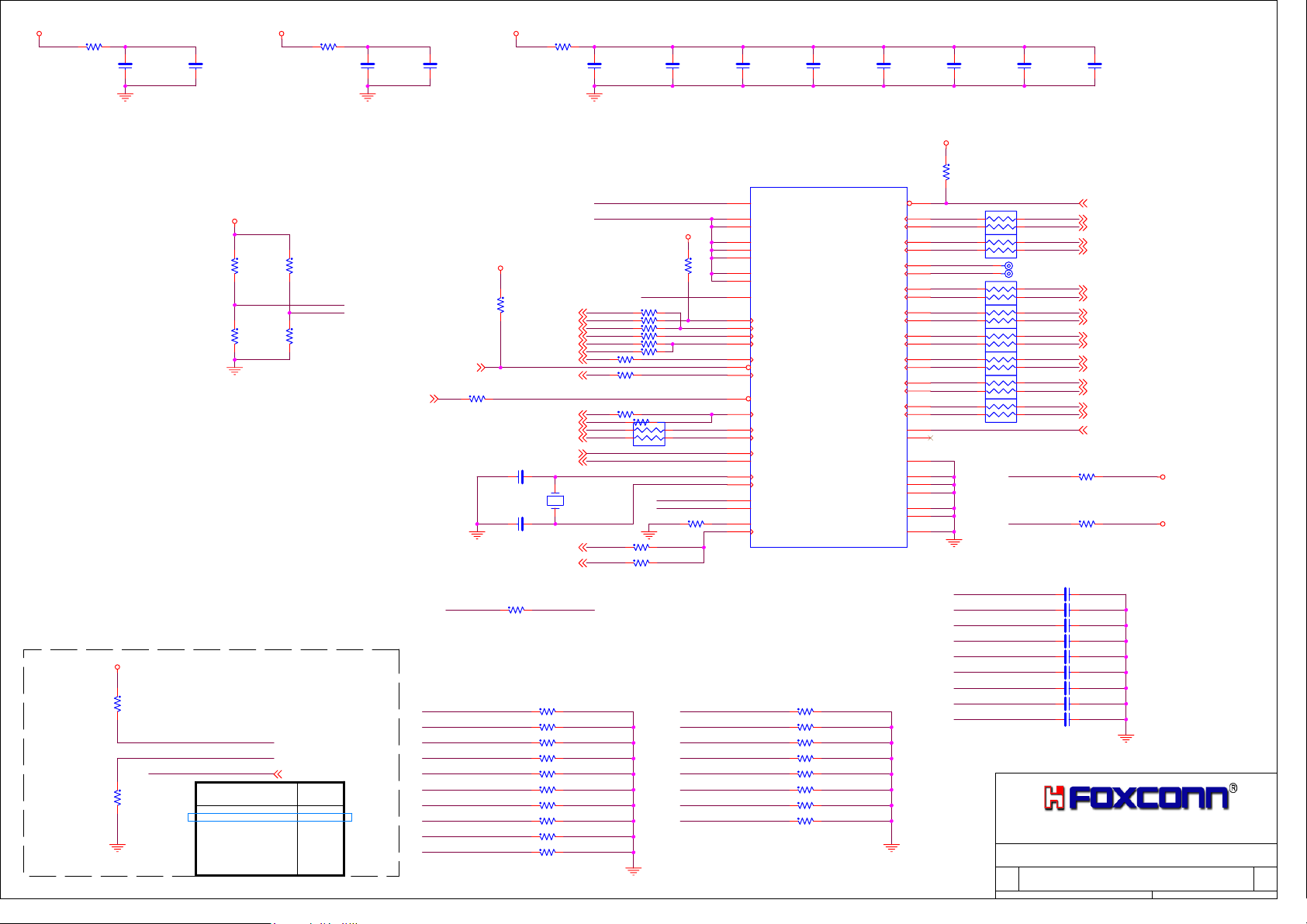

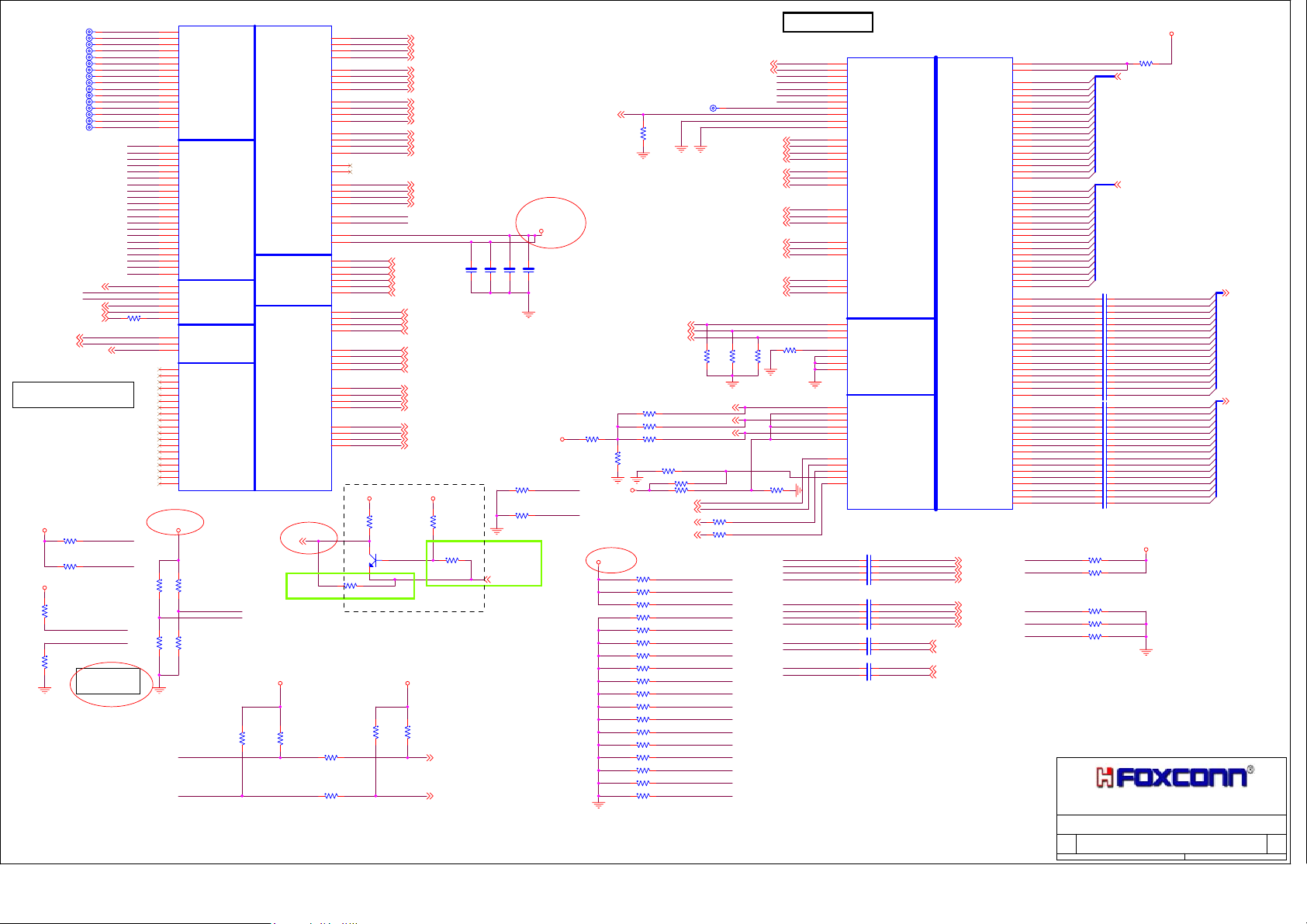

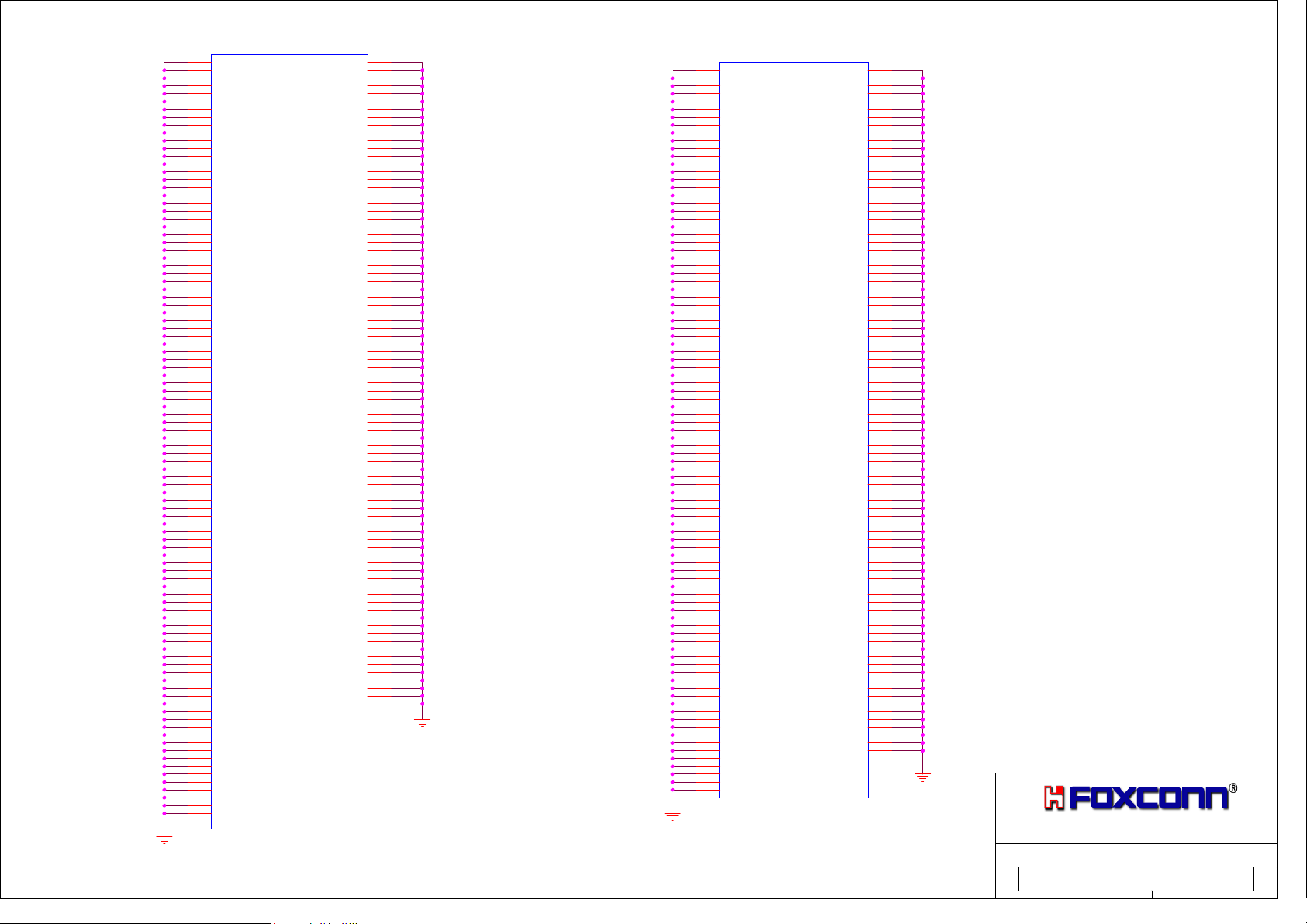

Page 3

3D3V_S0 3D3V_S03D3V_S0

www.hocnghetructuyen.vn

0 R0603

+/-5%

R93

*

3D3V_CLKGEN_S0

R515

1K

+/-5%

R0402

R42

1K

+/-5%

R0402

3D3V_APWR_S0 3D3V_CLKGEN_S03D3V_48MPWR_S0

C101

4.7uF

C0805

10V, Y5V, +80%/-20%

ITP_EN 0=PCIEX_6 1=CPU_2_ITP

SS_SEL 0=LCDCLK 1=PCIEX/free running

3.3V PCI clock output

C93

0.1uF

*

16V, Y5V, +80%/-20%

C0402

3D3V_S0

FS_A

FS_C

CFG1

FS_B

FS_C

0

0

0

1

1 100M

1

1

R30

10K

+/-5%

R0402

DUMMY

R34

10K

+/-5%

R0402

0

0

1

1

0

0

1

1

CFG1 7

FS_A

0

01200M

1

00333M

1

0

1 200M

R519

10K

+/-5%

R0402

R35

10K

+/-5%

R0402

DUMMY

CPU

266M

133M

166M

400M

0 R0603

+/-5%

R521

ITP_EN

SS_SEL

C415

4.7uF

*

C0805

10V, Y5V, +80%/-20%

CLKEN#38

(Default)

C90

0.1uF

*

16V, Y5V, +80%/-20%

C0402

3D3V_S0

R39

10K

R0402

+/-5%

DUMMY

PM_STPPCI#19

R51

0 R0402 +/-5%

C66

C65

CFG1 FS_B

CLK_PCIE_ICH

CLK_PCIE_ICH#

DREFSSCLK#

DREFSSCLK

CLK_PCIE_NEW

CLK_PCIE_NEW#

DREFCLK

DREFCLK#

SATA_CLKP

SATA_CLKN

0 R0603

+/-5%

R77

*

PCLK_FWH36

PCLK_MINI29

PCLK_PCM25

PCLK_KBC33

CLK33_AUDIODJ32

PCLK_SIO35

PCLK_LAN28

CLK_ICHPCI19

VTT_PWRGD#

CLK48_ICH19

CLK48_CARDBUS25

DREFCLK7

DREFCLK#7

SMBC_ICH12,21,23

SMBD_ICH12

*

33pF

*

33pF

R517

0

R0402+/-5%

R59 49.9R0402 +/-1%

R60 49.9R0402 +/-1%

R62 49.9R0402 +/-1%

R61 49.9R0402 +/-1%

R63 49.9R0402 +/-1%

R64 49.9R0402 +/-1%

R53 49.9R0402 +/-1%

R55 49.9R0402 +/-1%

R69 49.9R0402 +/-1%

R70 49.9R0402 +/-1%

X2

X-14D318MHz

1 2

CLK_ICH1419

SIO_14M35

C97

10uF

6.3V, X5R, +/-10%

C0805

3D3V_APWR_S0

3D3V_CLKGEN_S0

R511 33 R0402 +/-5%

R37 33 R0402 +/-5%

R514 33 R0402 +/-5%

R509 33 R0402 +/-5%

R510 33 R0402 +/-5% DUMMY

R512 33 R0402 +/-5%

R36 33 R0402 +/-5%

R33 33R0402 +/-5%

H/L : CPU_ITP/SRC7

R518 22R0402 +/-5%

R516 22R0402 +/-5%

RN14

1

33

2 3

R46 47R0402 +/-5%

R49 47R0402 +/-5%

C94

0.1uF

*

C0402

16V, Y5V, +80%/-20%

3D3V_S0

R38

10K

R0402

+/-5%

DUMMY

3D3V_48MPWR_S0

SS_SEL

ITP_EN

FS_A

4P2R0402V

4

+/-5%

X2_ICS

X1_ICS

FS_C

FS_B

R58

475 R0402 +/-1%

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_PCIE_PEG

CLK_PCIE_PEG#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

C83

0.1uF

*

C0402

16V, Y5V, +80%/-20%

U3

37

VDDA

1

VDDPCI

7

VDDPCI

21

VDDPCIEX

28

VDDPCIEX

34

VDDPCIEX

42

VDDCPU

48

VDDREF

11

VDD_48

56

PCICLK2/REQ_SEL

3

PCICLK3

4

PCICLK4

5

PCICLK5

9

SELPCIEX_LCDCLK#/PCICLK_F1

55

PCI/SRC_STP#

8

ITP_EN/PCICLK_F0

10

VTT_PWRGD#/PD

12

USB_48/FS_A

14

DOT96T

15

DOT96C

46

SCLK

47

SDATA

49

XOUT

50

XIN

53

REF1/FS_C/TEST_SEL

16

FS_B/TEST_MODE

39

IREF

52

REF0

ICS954226

*internal Pull-Up resistors

**internal Pull-Down resistor

R52 49.9R0402 +/-1%

R54 49.9R0402 +/-1%

R56 49.9R0402 +/-1%

R57 49.9R0402 +/-1%

R67 49.9R0402 +/-1%

R68 49.9R0402 +/-1%

R66 49.9R0402 +/-1%

R65 49.9R0402 +/-1%

C78

0.1uF

*

C0402

16V, Y5V, +80%/-20%

CPUT2_ITP/PCIEXT6

CPUC2_ITP/PCIEXC6

LCDCLK_SS/PCIEX0T

LCDCLK_SS/PCIEX0C

**

H/L: 100/96MHz

**

PEREQ2#/PCIEXC5

*

PEREQ1#/PCIEXT5

*

*

16V, Y5V, +80%/-20%

CPU_STP#

CPUT0

CPUC0

CPUT1

CPUC1

PCIEXT1

PCIEXC1

PCIEXT2

PCIEXC2

PCIEXT3

PCIEXC3

SATACLKT

SATACLKC

PCIEXC4

PCIEXT4

GND

GND

GND

GND

GND

GND

GNDA

C95

0.1uF

C0402

*

16V, Y5V, +80%/-20%

3D3V_S0

54

44

43

41

40

CLK_XDP_CPU

36

CLK_XDP_CPU#

35

17

18

19

20

22

23

24

25

26

27

30

31

32

33

13

51

45

29

2

6

38

C81

0.1uF

C0402

R41

10K

+/-5%

R0402

DUMMY

RN13

33

RN15

33

RN17

33

RN18

33

RN19

33

RN20

33

RN21

33

RN16

33

16V, Y5V, +80%/-20%

1

2 3

1

2 3

1

1

2 3

1

2 3

1

2 3

1

2 3

1

2 3

1

2 3

1

DREFSSCLK

DREFCLK

C92

0.1uF

*

C0402

4P2R0402V

4

+/-5%

4P2R0402V

4

+/-5%

TP8

TP9

4P2R0402V

+/-5%

4

4P2R0402V

+/-5%

4

4P2R0402V

+/-5%

4

4P2R0402V

+/-5%

4

4P2R0402V

+/-5%

4

4P2R0402V

+/-5%

4

NEWCARD_DET#

C91

0.1uF

*

C0402

16V, Y5V, +80%/-20%

PM_STPCPU# 19

CLK_CPU_BCLK 4

CLK_CPU_BCLK# 4

CLK_MCH_BCLK 6

CLK_MCH_BCLK# 6

DREFSSCLK 7

DREFSSCLK# 7

CLK_PCIE_NEW 23

CLK_PCIE_NEW# 23

CLK_MCH_3GPLL 7

CLK_MCH_3GPLL# 7

CLK_PCIE_PEG 14

CLK_PCIE_PEG# 14

SATA_CLKP 18

SATA_CLKN 18

CLK_PCIE_ICH# 19

CLK_PCIE_ICH 19

NEWCARD_DET# 23

R174 0

R0603 +/-5% DUMMY

R513 0

R0603 +/-5% DUMMY

1D5V_S0

1D5V_S0

EMI capacitor

CLK_ICH14

CLK33_AUDIODJ

PCLK_PCM

PCLK_MINI

PCLK_KBC

CLK_ICHPCI

CLK48_ICH

PCLK_SIO

SIO_14M

C80 10pF C0402 50V, NPO, +/-5% DUMMY

*

C405 10pF C0402 50V, NPO, +/-5% DUMMY

*

C413 10pF C0402 50V, NPO, +/-5% DUMMY

*

C77 10pF C0402 50V, NPO, +/-5% DUMMY

*

C404 10pF C0402 50V, NPO, +/-5% DUMMY

*

C64 10pF C0402 50V, NPO, +/-5% DUMMY

*

C414 10pF C0402 50V, NPO, +/-5% DUMMY

*

C411 10pF C0402 50V, NPO, +/-5% DUMMY

*

C82 10pF C0402 50V, NPO, +/-5% DUMMY

*

FOXCONN ND2

Title

Size Document Number Rev

<Doc>

A3

Date: Sheet

Clock Generator

W06N

SA

of

344Saturday, February 19, 2005

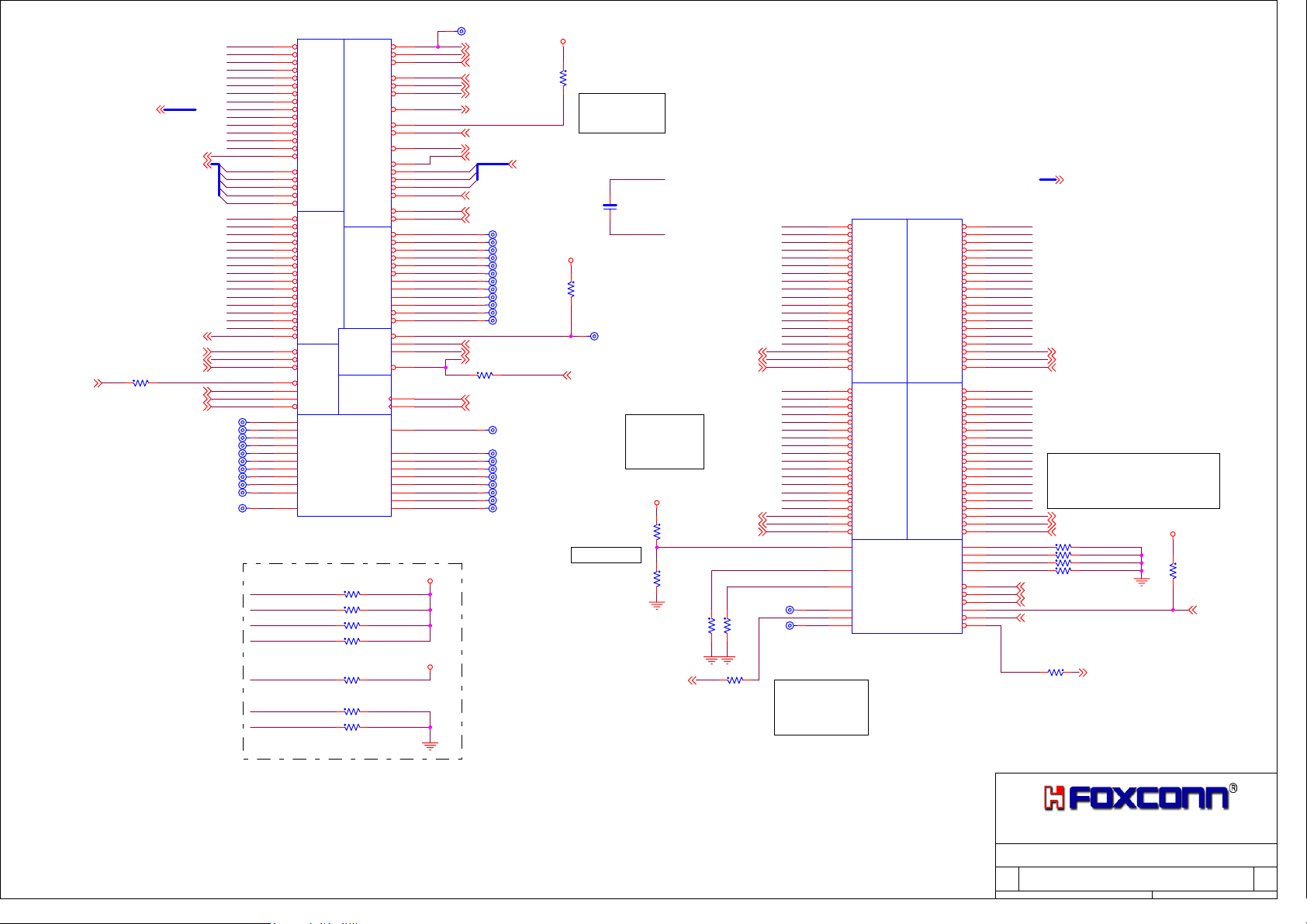

Page 4

TP48

www.hocnghetructuyen.vn

H_RS#0

H_RS#1

H_RS#2

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_DBRESET#

CPU_PROCHOT#

1D05V_S0

3D3V_S0

1

B_H_ADS# 6

B_H_BNR# 6

H_BPRI# 6

H_DEFER# 6

B_H_DRDY# 6

B_H_DBSY# 6

B_H_BREQ#0 6

H_INIT# 18

B_H_LOCK# 6

H_CPURST# 6

H_TRDY# 6

B_H_HIT# 6

B_H_HITM# 6

1

1

1

1

1

1

1

1

1

1

1

1

THERMDP1 22

THERMDN 22

PM_THRMTRIP-A# 7

R186 0 R0402+/-5%

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

1

1

1

1

1

1

1

1

1

TP16

TP15

TP17

TP19

TP21

TP25

TP20

TP28

TP24

TP23

TP26

TP61

TP34

TP53

TP51

TP55

TP54

TP12

TP57

TP58

TP62

J4

L4

M3

K5

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

1

AA1

1

AA4

1

AB2

1

AA3

1

M4

1

N5

1

T2

1

V3

1

B2

1

C3

1

B25

XDP_TDI

XDP_TMS

XDP_TDO

H_CPURST#

XDP_DBRESET#

XDP_TCK

XDP_TRST#

U40A

A[3]#

A[4]#

A[5]#

ADDR GROUP 0

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

ADDR GROUP 1

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

RSVD[10]

RSVD[11]

Yonah Ball-out Rev 1.0

PROCHOT#

THERM

THERMTRIP#

RESERVED

R112 150 R0603 +/-1%

R113 39.2 R 0402 +/-1%

R111 54.9R0402 +/-1%

DUMMY

R147 54.9R0402 +/-1%

DUMMY

R211 150 R0603 +/-1%

R104 27.4R0402 +/-1%

R109 680 R0603 +/-1%

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALSH CLK

THERMDA

THERMDC

BCLK[0]

BCLK[1]

RSVD[12]

RSVD[13]

RSVD[14]

RSVD[15]

RSVD[16]

RSVD[17]

RSVD[18]

RSVD[19]

RSVD[20]

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

TDI

AB3

AB5

AB6

C20

D21

A24

A25

C7

A22

A21

T22

D2

F6

D3

C1

AF1

D22

C23

C24

B_H_A#3

B_H_A#4

B_H_A#5

B_H_A#6

B_H_A#7

B_H_A#8

B_H_A#9

B_H_A#10

B_H_REQ#0

B_H_REQ#1

B_H_REQ#2

B_H_REQ#3

B_H_REQ#4

H_STPCLK_R

TP31

TP29

TP27

TP30

TP39

TP38

TP36

TP32

TP67

TP59

TP64

B_H_A#11

B_H_A#12

B_H_A#13

B_H_A#14

B_H_A#15

B_H_A#16

B_H_A#17

B_H_A#18

B_H_A#19

B_H_A#20

B_H_A#21

B_H_A#22

B_H_A#23

B_H_A#24

B_H_A#25

B_H_A#26

B_H_A#27

B_H_A#28

B_H_A#29

B_H_A#30

B_H_A#31

B_H_A#[31..3]6

B_H_ADSTB#06

B_H_REQ#[4..0]6

B_H_ADSTB#16

H_A20M#18

H_FERR#18

H_IGNNE#18

+/-5%

H_STPCLK#18

R185 0 R0402

H_INTR18

H_NMI18

H_SMI#18

H_IERR#

H_RS#[2..0] 6

1D05V_S0

R173

56

+/-5%

R0402

Place testpoint on

H_IERR# with a GND

0.1" away

Put thes e tw o Caps near the the rmal diode.

THERMDP1

BC34

470pF

*

50V. X7R, +/-10%

C0402

THERMDN

1D05V_S0

R177

56

+/-5%

R0402

TP56

1

PM_THRMTRIP-I# 18

PM_THRMTRIP#

should connect to

ICH6 and Alviso

without T-ing

( No stub)

1D05V_S0

R100

1K

+/-1%

Layout Note:

0.5" max length.

R0603

R102

2K

+/-1%

R0603

R178

1K

+/-5%

R0402

DUMMY

CPU_SEL17

B_H_DSTBN#06

B_H_DSTBP#06

B_H_DSTBN#16

B_H_DSTBP#16

R210

0

+/-5%

R0402

B_H_DINV#06

B_H_DINV#16

TEST1

TEST2

R171

1K

+/-5%

R0402

DUMMY

GTLREF0

TP65

TP60

CPU_SEL1_1

BSEL[2:0] Freq.(MHz)

L L L Reserve

L L H 133

L H L Reserve

L H H 166

B_H_D#0

B_H_D#1

B_H_D#2

B_H_D#3

B_H_D#4

B_H_D#5

B_H_D#6

B_H_D#7

B_H_D#8

B_H_D#9

B_H_D#10

B_H_D#11

B_H_D#12

B_H_D#13

B_H_D#14

B_H_D#15

B_H_D#16

B_H_D#17

B_H_D#18

B_H_D#19

B_H_D#20

B_H_D#21

B_H_D#22

B_H_D#23

B_H_D#24

B_H_D#25

B_H_D#26

B_H_D#27

B_H_D#28

B_H_D#29

B_H_D#30

B_H_D#31

1

1

U40B

E22

D[0]#

F24

D[1]#

E26

D[2]#

H22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H26

D[12]#

F26

D[13]#

K22

D[14]#

H25

D[15]#

H23

DSTBN[0]#

G22

DSTBP[0]#

J26

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L25

D[20]#

L22

D[21]#

L23

D[22]#

M23

D[23]#

P25

D[24]#

P22

D[25]#

P23

D[26]#

T24

D[27]#

R24

D[28]#

L26

D[29]#

T25

D[30]#

N24

D[31]#

M24

DSTBN[1]#

N25

DSTBP[1]#

M26

DINV[1]#

AD26

GTLREF

C26

TEST1

D25

TEST2

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

Yonah Ball-out Rev 1.0

DATA GRP 0 DATA GRP 1

MISC

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

DATA GRP 2

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

DATA GRP 3

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

B_H_D#[63..0] 6

B_H_D#32

AA23

B_H_D#33

AB24

B_H_D#34

V24

B_H_D#35

V26

B_H_D#36

W25

B_H_D#37

U23

B_H_D#38

U25

B_H_D#39

U22

B_H_D#40

AB25

B_H_D#41

W22

B_H_D#42

Y23

B_H_D#43

AA26

B_H_D#44

Y26

B_H_D#45

Y22

B_H_D#46

AC26

B_H_D#47

AA24

W24

Y25

V23

B_H_D#48

AC22

B_H_D#49

AC23

B_H_D#50

AB22

B_H_D#51

AA21

B_H_D#52

AB21

B_H_D#53

AC25

B_H_D#54

AD20

B_H_D#55

AE22

B_H_D#56

AF23

B_H_D#57

AD24

B_H_D#58

AE21

B_H_D#59

AD21

B_H_D#60

AE25

B_H_D#61

AF25

B_H_D#62

AF22

B_H_D#63

AF26

AD23

AE24

AC20

COMP0

R26

COMP1

U26

COMP2

U1

COMP3

V1

E5

B5

D24

D6

D7

AE6

B_H_DSTBN#2 6

B_H_DSTBP#2 6

B_H_DINV#2 6

Layout Note:

Comp0, 2 connect with Zo=27.4 ohm, make

trace length shorter than 0.5" .

Comp1, 3 connect with Zo=55 ohm, make

trace length shorter than 0.5" .

B_H_DSTBN#3 6

B_H_DSTBP#3 6

B_H_DINV#3 6

R121 27.4R0402 +/-1%

R118 54.9R0402 +/-1%

R119 27.4R0402 +/-1%

R114 54.9R0402 +/-1%

H_DPRSLP# 18

H_DPSLP# 18

H_DPWR# 6

H_CPUSLP# 6,18

R97

0

+/-5%

R0402

DUMMY

PSI# 38

1D05V_S0

R150

200

+/-1%

R0402

DUMMY

H_PWRGD 18

All place within 2" to CPU

Title

Size Document Number Rev

<Doc>

A3

Date: Sheet of

CPU(1/2)

W06N

444Monday, February 21, 2005

SA

FOXCONN ND2

Page 5

VCC_CORE_S0

www.hocnghetructuyen.vn

Layout Note:

U40C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

Yonah Ball-out Rev 1.0

VCCSENSE and VSSSENSE lines

should be of equal length.

Layout Note:

Provide a test point (with

no stub) to connect a

differential probe

between VCCSENSE and

VSSSENSE at the location

where the two 54.9ohm

resistors terminate the

55 ohm transmission line.

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCSENSE

VSSSENSE

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

VCC_CORE_S0

1D5V_VCCA_S0

R106

100

R0402

+/-1%

DUMMY

VCC_CORE_S0

*

1D05V_S0

C221

10nF

*

C0402

H_VID0 38

H_VID1 38

H_VID2 38

H_VID3 38

H_VID4 38

H_VID5 38

H_VID6 38

10V, Y5V, +80%/-20%

C113

R105

0 R0402 +/-5%

*

10uF C0805

*

C110

10uF C0805

VCC_CORE_S0

10V, Y5V, +80%/-20%

C194

10uF

*

6.3V, X5R, +/-10%

C0805

R96

100

R0402

+/-1%

DUMMY

FB- 38

*

C109

10uF C0805

3D3V_S0

0 R0402 +/-5%

*

C108

10uF C0805

U40D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

A26

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

Place these

12.7K 1.56V

11K 1.52V

*

C154

C229

10uF C0805

and dummy

12K7R3F for

1D8V_VCCA_S0

*

*

C165

10uF C0805

10uF C0805

C127

10uF C0805

1D5V_VCCA_S0

BC32

I max = 120 mA

U11

1

SHDN#

2

GND

3

FB+ 38

1D05V_S0

*

C115

10uF C0805

IN

G913C

*

C187

C148

*

10uF C0805

BC33

1uF

*

C0603

R95

*

*

C112

C226

10uF C0805

10uF C0805

SET

OUT

10V, X5R, +/-10%

*

*

C184

0.1uF C0402

0.1uF C0402

*

C176

C114

10uF C0805

*

10uF C0805

5

4

BC29

*

C158

0.1uF C0402

C188

*

50V, NPO, +/-5%

1uF

*

C060310V, Y5V, +80%/-20%

*

C142

0.1uF C0402

*

C111

10uF C0805

*

10uF C0805

22pF

C0402

R170

11K

+/-1%

R0402

R176

49.9K

+/-1%

R0603

TC8

150uF

*

*

C182

0.1uF C0402

*

C126

10uF C0805

6.3V, +/-20%

C163

CTX

DUMMY

0.1uF C0402

*

C125

10uF C0805

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Yonah Ball-out Rev 1.0

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

VCC_CORE_S0

*

*

*

*

C228

10uF C0805

DUMMY

C175

*

10uF C0805

DUMMY

DUMMY

C225

10uF C0805

DUMMY

C223

10uF C0805

DUMMY

C227

10uF C0805

VCC_CORE_S0

10V, Y5V, +80%/-20%

*

C191

VCC_CORE_S0

*

C130

*

10uF C0805

*

10uF C0805

*

*

C222

C192

10uF C0805

10uF C0805

*

*

C193

C189

10uF C0805

10uF C0805

*

*

C146

C155

10uF C0805

10uF C0805

*

*

C131

10uF C0805

*

*

C145

10uF C0805

C164

C169

10uF C0805

10uF C0805

C230

10uF C0805

FOXCONN ND2

*

*

C129

10uF C0805

*

C128

C107

10uF C0805

10uF C0805

*

*

C170

10uF C0805

C190

C224

10uF C0805

10uF C0805

Title

Size Document Number Rev

<Doc>

A3

Date: Sheet of

CPU(2/2)

W06N

544Saturday, February 19, 2005

SA

Page 6

H_XRCOMP

www.hocnghetructuyen.vn

R543

24.9

+/-1%

R0402

Place them near to the chip

1D05V_S0

R544

54.9

+/-1%

R0402

H_XSCOMP

Place them near to the chip

1D05V_S0

R545

221

+/-1%

R0402

H_XSWING

R546

100

+/-1%

R0603

*

Place them near to the chip

H_YRCOMP

R539

24.9

+/-1%

R0402

Place them near to the chip

1D05V_S0

R542

54.9

+/-1%

R0402

H_YSCOMP

1D05V_S0

Place them near to the chip

R541

221

+/-1%

R0402

H_YSWING

R540

100

+/-1%

R0603

*

C449

0.1uF

10V, X7R, +/-10%

C0402

C438

0.1uF

10V, X7R, +/-10%

C0402

B_H_D#[63..0]4

CLK_MCH_BCLK3

CLK_MCH_BCLK#3

B_H_D#0

B_H_D#1

B_H_D#2

B_H_D#3

B_H_D#4

B_H_D#5

B_H_D#6

B_H_D#7

B_H_D#8

B_H_D#9

B_H_D#10

B_H_D#11

B_H_D#12

B_H_D#13

B_H_D#14

B_H_D#15

B_H_D#16

B_H_D#17

B_H_D#18

B_H_D#19

B_H_D#20

B_H_D#21

B_H_D#22

B_H_D#23

B_H_D#24

B_H_D#25

B_H_D#26

B_H_D#27

B_H_D#28

B_H_D#29

B_H_D#30

B_H_D#31

B_H_D#32

B_H_D#33

B_H_D#34

B_H_D#35

B_H_D#36

B_H_D#37

B_H_D#38

B_H_D#39

B_H_D#40

B_H_D#41

B_H_D#42

B_H_D#43

B_H_D#44

B_H_D#45

B_H_D#46

B_H_D#47

B_H_D#48

B_H_D#49

B_H_D#50

B_H_D#51

B_H_D#52

B_H_D#53

B_H_D#54

B_H_D#55

B_H_D#56

B_H_D#57

B_H_D#58

B_H_D#59

B_H_D#60

B_H_D#61

B_H_D#62

B_H_D#63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

W11

U11

T11

AB7

AA9

Y10

AB8

AA4

AA7

AA2

AA6

AA10

AA1

AB4

AC9

AB11

AC11

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD10

AD4

AC8

AG2

AG1

K11

T10

W9

W7

W6

W4

W3

W5

W2

W1

F1

J1

H1

J6

H3

K2

G1

G2

K9

K1

K7

J8

H4

J3

G4

T3

U7

U9

T1

T8

T4

U5

T9

T5

Y3

Y7

Y8

E1

E2

E4

Y1

U1

U39A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_CLKIN

H_CLKIN#

CALISTOGA_1p0

H_ADSTB#_0

H_ADSTB#_1

HOST

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_VREF_0

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_VREF_1

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_SLPCPU#

H_TRDY#

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

E8

B9

C13

J13

C6

F6

C7

B7

A7

C3

J9

H8

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

B_H_A#3

B_H_A#4

B_H_A#5

B_H_A#6

B_H_A#7

B_H_A#8

B_H_A#9

B_H_A#10

B_H_A#11

B_H_A#12

B_H_A#13

B_H_A#14

B_H_A#15

B_H_A#16

B_H_A#17

B_H_A#18

B_H_A#19

B_H_A#20

B_H_A#21

B_H_A#22

B_H_A#23

B_H_A#24

B_H_A#25

B_H_A#26

B_H_A#27

B_H_A#28

B_H_A#29

B_H_A#30

B_H_A#31

H_VREF

B_H_DINV#0

B_H_DINV#1

B_H_DINV#2

B_H_DINV#3

B_H_DSTBN#0

B_H_DSTBN#1

B_H_DSTBN#2

B_H_DSTBN#3

B_H_DSTBP#0

B_H_DSTBP#1

B_H_DSTBP#2

B_H_DSTBP#3

B_H_REQ#0

B_H_REQ#1

B_H_REQ#2

B_H_REQ#3

B_H_REQ#4

H_RS#0

H_RS#1

H_RS#2

B_H_ADS# 4

B_H_ADSTB#0 4

B_H_ADSTB#1 4

B_H_BNR# 4

H_BPRI# 4

B_H_BREQ#0 4

H_CPURST# 4

B_H_DBSY# 4

H_DEFER# 4

H_DPWR# 4

B_H_DRDY# 4

B_H_HIT# 4

B_H_HITM# 4

B_H_LOCK# 4

H_TRDY# 4

B_H_A#[31..3] 4

Place them near to the chip

C171

0.1uF

*

10V, X7R, +/-10%

C0402

B_H_DINV#0 4

B_H_DINV#1 4

B_H_DINV#2 4

B_H_DINV#3 4

B_H_DSTBN#0 4

B_H_DSTBN#1 4

B_H_DSTBN#2 4

B_H_DSTBN#3 4

B_H_DSTBP#0 4

B_H_DSTBP#1 4

B_H_DSTBP#2 4

B_H_DSTBP#3 4

B_H_REQ#[4..0] 4

H_RS#[2..0] 4

R159 0 R0402 +/-5%

R136

200

+/-1%

R0402

1D05V_S0

R131

100

+/-1%

R0603

H_CPUSLP# 4,18

Place them near to the chip

Title

Size Document Number Rev

<Doc>

A3

Date: Sheet of

Calistoga (1 of 6)

W06N

644Monday, February 21, 2005

SA

FOXCONN ND2

Page 7

TP43

www.hocnghetructuyen.vn

1

TP35

1

TP37

1

TP44

1

TP46

1

TP18

1

TP22

1

TP45

1

TP42

1

TP40

1

TP41

1

TP52

1

TP106

1

TP107

1

TP47

1

TP49

1

PM_BMBUSY#19

PM_THRMTRIP-A#4

FOR DVI

SDVOB_CTRLCLK16

SDVOB_CTRLDATA16

Alviso will provide SDVO_CTRLCLK

and CTRLDATA pulldowns on-die

3D3V_S0

R0402 +/-5%

R160 10K

R0402 +/-5%

R144 10K

1D8V_S3

R89

80.6

+/-1%

R0402

DUMMY

R92

80.6

+/-1%

R0402

DUMMY

PWROK19,22

PLT_RST1#14,19,21,23,33,35,36

MCH_SYNC#19

PM_EXTTS#0

PM_EXTTS#1

M_RCOMPN

M_RCOMPP

CFG[2:0] Freq.(MHz)

011 667

001 533

PM_EXTTS#0

PM_EXTTS#1

SDVOB_CTRLCLK

SDVOB_CTRLDATA

R108

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

R126

1K

+/-5%

R0402

R125

+/-5%

4.7K

R0402

DUMMY

LCTLA_CLK

LCTLB_DATA

LDDC_NB_CLK

B_LDDC_NB_DATA

LIBG

4.99K

R0402

+/-1%

CRTIREF

R554

0 R0402 +/-5%

HSYNC

VSYNC

SDVOB_CLKN_1

SDVOB_RP_1

SDVOB_GP_1

SDVOB_BP_1CFG3

SDVOB_CLKP_1

When SDVO no use

SDVOCTRL_DATA PL

U39C

D32

J30

H30

H29

G26

G25

B38

L_LVBG

C35

F32

L_VREFH

C33

L_VREFL

C32

A33

A32

E27

E26

C37

B35

A37

B37

B34

A36

G30

D30

F29

F30

D29

F28

A16

C18

A19

J20

B16

B18

B19

E23

D23

C22

B22

A21

B21

C26

C25

G23

J22

H23

CALISTOGA_1p0

SDVOB_RN_1

C216 0.1uF C0402

SDVOB_GN_1

C196 0.1uF C0402

SDVOB_BN_1

C214 0.1uF C0402

C207 0.1uF C0402

C215 0.1uF C0402

C195 0.1uF C0402

C211 0.1uF C0402

C206 0.1uF C0402

PEG_RXN1

C210 0.1uF C0402

PEG_RXN2

C212 0.1uF C0402

PEG_RXP1

C209 0.1uF C0402

PEG_RXP2

C213 0.1uF C0402

L_BKLTCTL

L_BKLTEN

L_CLKCTLA

L_CLKCTLB

L_DDC_CLK

L_DDC_DATA

L_IBG

L_VBG

L_VDDEN

L_VREFH

L_VREFL

LA_CLK#

LA_CLK

LB_CLK#

LB_CLK

LA_DATA#_0

LA_DATA#_1

LA_DATA#_2

LA_DATA_0

LA_DATA_1

LA_DATA_2

LB_DATA#_0

LB_DATA#_1

LB_DATA#_2

LB_DATA_0

LB_DATA_1

LB_DATA_2

TV_DACA_OUT

TV_DACB_OUT

TV_DACC_OUT

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_IREF

CRT_VSYNC

*

*

*

*

for GM DVI function

*

*

*

*

*

*

*

*

LVDS

TV

VGA

EXP_A_COMPI

EXP_A_COMPO

EXP_A_RXN_0

EXP_A_RXN_1

EXP_A_RXN_2

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_0

EXP_A_RXP_1

EXP_A_RXP_2

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_0

EXP_A_TXN_1

EXP_A_TXN_2

EXP_A_TXN_3

EXP_A_TXN_4

EXP_A_TXN_5

EXP_A_TXN_6

EXP_A_TXN_7

EXP_A_TXN_8

EXP_A_TXN_9

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

PCI-EXPRESS GRAPHICS

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_0

EXP_A_TXP_1

EXP_A_TXP_2

EXP_A_TXP_3

EXP_A_TXP_4

EXP_A_TXP_5

EXP_A_TXP_6

EXP_A_TXP_7

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

SDVOB_RN 16

SDVOB_GN 16

SDVOB_BN 16

SDVOB_CLKN 16

SDVOB_RP 16

SDVOB_GP 16

SDVOB_BP 16

SDVOB_CLKP 16

SDVOB_INTN 16

SDVOB_STALLN 16

SDVOB_INTP 16

SDVOB_STALLP 16

1D5V_PCIE_S0

24.9

PEG_COMP

D40

PEG_COMP

D38

PEG_RXN0

F34

PEG_RXN1

G38

PEG_RXN2

H34

PEG_RXN3

J38

PEG_RXN4

L34

PEG_RXN5

M38

PEG_RXN6

N34

PEG_RXN7

P38

PEG_RXN8

R34

PEG_RXN9

T38

PEG_RXN10

V34

PEG_RXN11

W38

PEG_RXN12

Y34

PEG_RXN13

AA38

PEG_RXN14

AB34

PEG_RXN15

AC38

PEG_RXP0

D34

PEG_RXP1

F38

PEG_RXP2

G34

PEG_RXP3

H38

PEG_RXP4

J34

PEG_RXP5

L38

PEG_RXP6

M34

PEG_RXP7

N38

PEG_RXP8

P34

PEG_RXP9

R38

PEG_RXP10

T34

PEG_RXP11

V38

PEG_RXP12

W34

PEG_RXP13

Y38

PEG_RXP14

AA34

PEG_RXP15

AB38

SDVOB_RN_1

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

LCTLA_CLK

LCTLB_DATA

GMCH_BL_ON

LBKLT_CRTL

LIBG

C179 0.1uF C0402

SDVOB_GN_1

C448 0.1uF C0402

SDVOB_BN_1

C172 0.1uF C0402

SDVOB_CLKN_1

C446 0.1uF C0402

C167 0.1uF C0402

C444 0.1uF C0402

C159 0.1uF C0402

C442 0.1uF C0402

C151 0.1uF C0402

C440 0.1uF C0402

C144 0.1uF C0402R137

C437 0.1uF C0402

C137 0.1uF C0402

C434 0.1uF C0402

C123 0.1uF C0402

C431 0.1uF C0402

SDVOB_RP_1

C183 0.1uF

SDVOB_GP_1

C450 0.1uF

SDVOB_BP_1

C174 0.1uF C0402

SDVOB_CLKP_1

C447 0.1uF C0402

C168 0.1uF C0402

C445 0.1uF C0402

C166 0.1uF C0402

C443 0.1uF C0402

C157 0.1uF C0402

C441 0.1uF C0402

C147 0.1uF C0402

C439 0.1uF C0402

C141 0.1uF C0402

C436 0.1uF C0402

C132 0.1uF C0402

C433 0.1uF C0402

R143

DUMMY

R142

DUMMY

R146 100KR0402 +/-5%

R156 100KR0402 +/-5%

R175 1.5KR0603 +/-1%

Title

Size Document Number Rev

<Doc>

Custom

Date: Sheet

+/-1%

R161

R0402

PEG_RXN[15..0] 14

PEG_RXP[15..0] 14

16V, Y5V, +80%/-20%

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

C0402

C0402

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

3D3V_S0

2.2KR0402 +/-5%

2.2KR0402 +/-5%

FOXCONN ND2

Calistoga (2 of 6)

W06N

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

PEG_TXN[15..0] 14

PEG_TXP[15..0] 14

of

744Monday, February 21, 2005

SA

U39B

H32

CLK_REQ#

T32

RSVD_1

R32

RSVD_2

F3

RSVD_3

F7

RSVD_4

AG11

RSVD_5

AF11

RSVD_6

H7

RSVD_7

J19

RSVD_8

K30

TV_DCONSEL0

J29

TV_DCONSEL1

A41

RSVD_11

A35

RSVD_12

A34

RSVD_13

D28

RSVD_14

D27

RSVD_15

K16

CFG_0

K18

CFG_1

J18

CFG_2

F18

CFG_3

E15

CFG_4

F15

CFG_5

E18

CFG_6

D19

CFG_7

D16

CFG_8

G16

CFG_9

E16

CFG_10

D15

CFG_11

G15

CFG_12

K15

CFG_13

C15

CFG_14

H16

CFG_15

G18

CFG_16

H15

CFG_17

J25

CFG_18

K27

CFG_19

J26

CFG_20

G28

PM_BMBUSY#

F25

PM_EXTTS#_0

H26

PM_EXTTS#_1

G6

PM_THRMTRIP#

AH33

PWROK

AH34

RSTIN#

100R0402+/-5%

H28

SDVO_CTRLCLK

H27

SDVO_CTRLDATA

K28

LT_RESET#

D1

NC0

C41

NC1

C1

NC2

BA41

NC3

BA40

NC4

BA39

NC5

BA3

NC6

BA2

NC7

BA1

NC8

B41

NC9

B2

NC10

AY41

NC11

AY1

NC12

AW41

NC13

AW1

NC14

A40

NC15

A4

NC16

A39

NC17

A3

3D3V_S0

NC18

R127

1K

+/-5%

R0402

DUMMY

R128

4.7K

+/-5%

R0402

LDDC_NB_CLK

CALISTOGA_1p0

CFG2

CFG0

SM_OCDCOMP_0

SM_OCDCOMP_1

CFGRSVD

DDR MUXINGCLKDMI

D_REFCLKIN#

D_REFSSCLKIN#

PM

D_REFSSCLKIN

MISC

NC

CFG13

3D3V_S0 3D3V_S0

R148

R153

2.2K

2.2K

+/-5%

+/-5%

R0402

R0402

AY35

SM_CK_0

AR1

SM_CK_1

AW7

SM_CK_2

AW40

SM_CK_3

AW35

SM_CK#_0

AT1

SM_CK#_1

AY7

SM_CK#_2

AY40

SM_CK#_3

AU20

SM_CKE_0

AT20

SM_CKE_1

BA29

SM_CKE_2

AY29

SM_CKE_3

AW13

SM_CS#_0

AW12

SM_CS#_1

AY21

SM_CS#_2

AW21

SM_CS#_3

AL20

AF10

M_ODT0

BA13

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP#

SM_RCOMP

SM_VREF_0

SM_VREF_1

G_CLKIN#

G_CLKIN

D_REFCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

FOR CFG2 abnormal output 14.318Mhz

BA12

AY20

AU21

AV9

AT9

AK1

AK41

AF33

AG33

A27

A26

C40

D41

AE35

AF39

AG35

AH39

AC35

AE39

AF35

AG39

AE37

AF41

AG37

AH41

AC37

AE41

AF37

AG41

R548

1K

+/-5%

R0402

CFG1

DUMMY

R181 0 R0402 +/-5%

R166

0

R0402

+/-5%

R165

0

R0402

+/-5%

M_ODT1

M_ODT2

M_ODT3

M_RCOMPN

M_RCOMPP

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

E C

R488

2.2K

+/-5%

LDDC_CLK

CLK_DDR0 12

CLK_DDR1 12

CLK_DDR2 12

CLK_DDR3 12

CLK_DDR0# 12

CLK_DDR1# 12

CLK_DDR2# 12

CLK_DDR3# 12

M_CKE0_R# 12,13

M_CKE1_R# 12,13

M_CKE2_R# 12,13

M_CKE3_R# 12,13

M_CS0_R# 12,13

M_CS1_R# 12,13

M_CS2_R# 12,13

M_CS3_R# 12,13

M_ODT0 12,13

M_ODT1 12,13

M_ODT2 12,13

M_ODT3 12,13

CLK_MCH_3GPLL# 3

CLK_MCH_3GPLL 3

DREFCLK# 3

DREFCLK 3

DREFSSCLK# 3

DREFSSCLK 3

DMI_TXN0 19

DMI_TXN1 19

DMI_TXN2 19

DMI_TXN3 19

DMI_TXP0 19

DMI_TXP1 19

DMI_TXP2 19

DMI_TXP3 19

DMI_RXN0 19

DMI_RXN1 19

DMI_RXN2 19

DMI_RXN3 19

DMI_RXP0 19

DMI_RXP1 19

DMI_RXP2 19

DMI_RXP3 19

1D05V_S02D5V_S0

R204

330

+/-5%

R0402

FWH_INIT_Q

DUMMY

DUMMY

R205 0 R0402 +/-5%

Q14

MMBT3904

DUMMY

B

For pull high 1.05V 11/08

R487

2.2K

+/-5%

R0402

R0402

DUMMY

DUMMY

LDDC_CLK 14,17

LDDC_DATAB_LDDC_NB_DATA

LDDC_DATA 14,17

BC110

*

0.1uF C0402

C426

2.2uFC0805

*

*

0.1uF C0402

BC109

R141

0 R0402 +/-5%

R149

0 R0402 +/-5%

CPU_SEL1 4

DDR_VREF_S3

2.2uFC0805

*

6.3V, X5R, +/-10%

C425

NB_CORE_S0

DUMMY

DUMMY

LBKLT_CRTL17

GMCH_BL_ON33

TP50

GMCH_LCDVDD_ON17

DUMMY

R183

0

R189

R0402

0

R0402

+/-5%

VSYNC

NB_CORE_S0

HSYNC

CFG[19:18] have internal pull-down

CFG[17:3] have internal up

CFG[2:0] have no internal pull-up or pull-down

R151

100K

+/-5%

R0402

GMCH_TV_COM15

GMCH_TV_LUMA15

GMCH_TV_CRMA15

R168 150 R0603 +/-1%

R547 150 R0603 +/-1%

R556 150 R0603 +/-1%

+/-5%

R139 255 R0402 +/-1%

GMCH_DDCCLK15

B_GMCH_DDCDATA15

GMCH_HSYNC15

GMCH_VSYNC15

When High 1K Ohm

3D3V_S0

R1292.2K

R1352.2K

R1342.2K

R1552.2K

R5492.2K

R1822.2K

R1632.2K

R1692.2K

R1622.2K

R5572.2K

R2022.2K

R5502.2K

R2032.2K

R1322.2K

R1722.2K

R1382.2K

R2132.2K

R1452.2K

DUMMY

R1400 R0402 +/-5%

R5550R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

R0402 +/-5%

DUMMY

When Low choice

lower than 3.5K

Ohm

1

150

150

+/-1%

+/-1%

R0603

R0603

R561

R553

GMCH_BLUE15

GMCH_GREEN15

GMCH_RED15

R222 39R0402 +/-5%

R224 39R0402 +/-5%

CFG18

CFG19

CFG20

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

GMCH_TXAOUT0-14

GMCH_TXAOUT1-14

GMCH_TXAOUT2-14

GMCH_TXAOUT0+14

GMCH_TXAOUT1+14

GMCH_TXAOUT2+14

GMCH_TXBOUT0-14

GMCH_TXBOUT1-14

GMCH_TXBOUT2-14

GMCH_TXBOUT0+14

GMCH_TXBOUT1+14

GMCH_TXBOUT2+14

GMCH_TXACLK-14

GMCH_TXACLK+14

GMCH_TXBCLK-14

GMCH_TXBCLK+14

150

+/-1%

R0603

R552

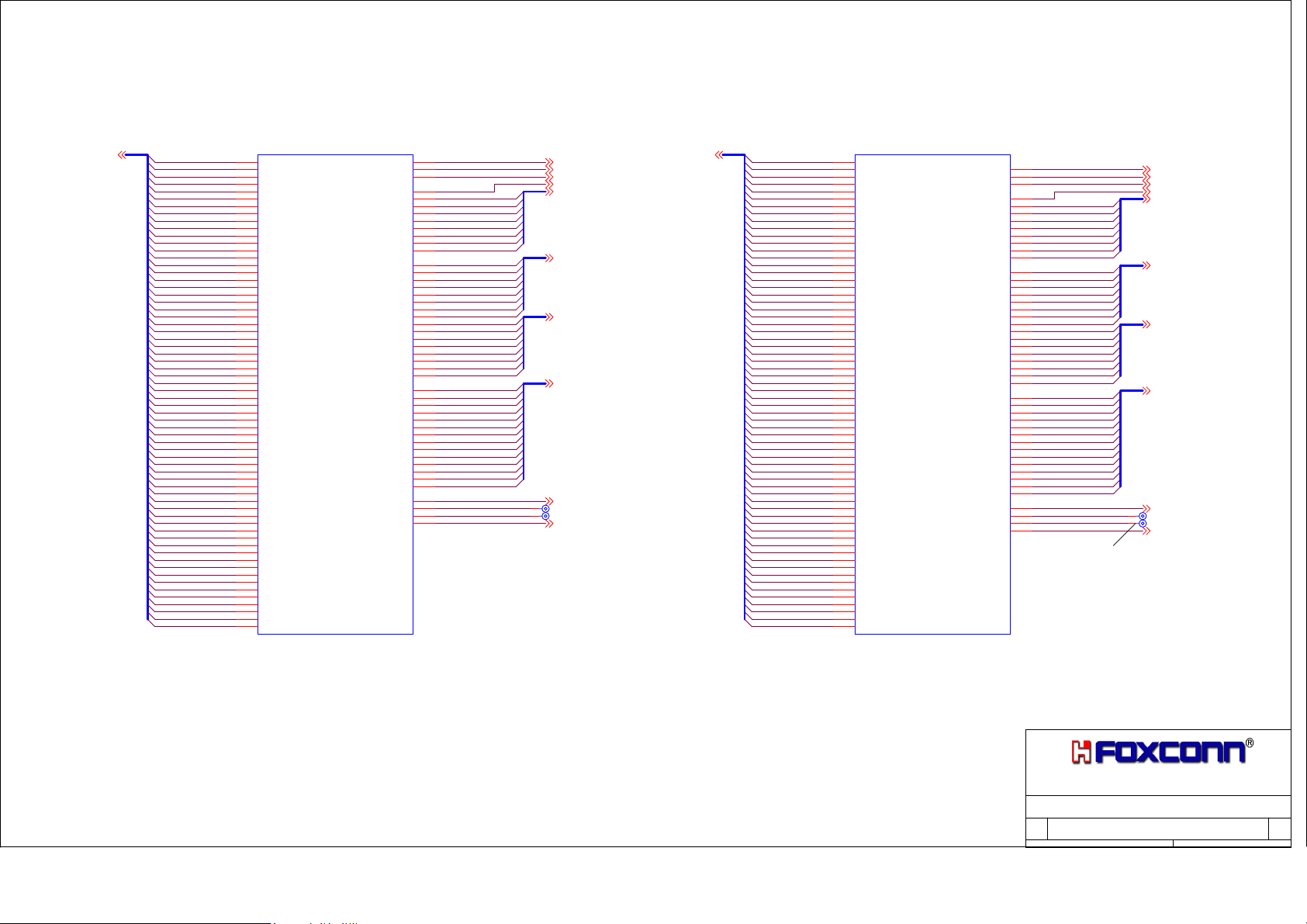

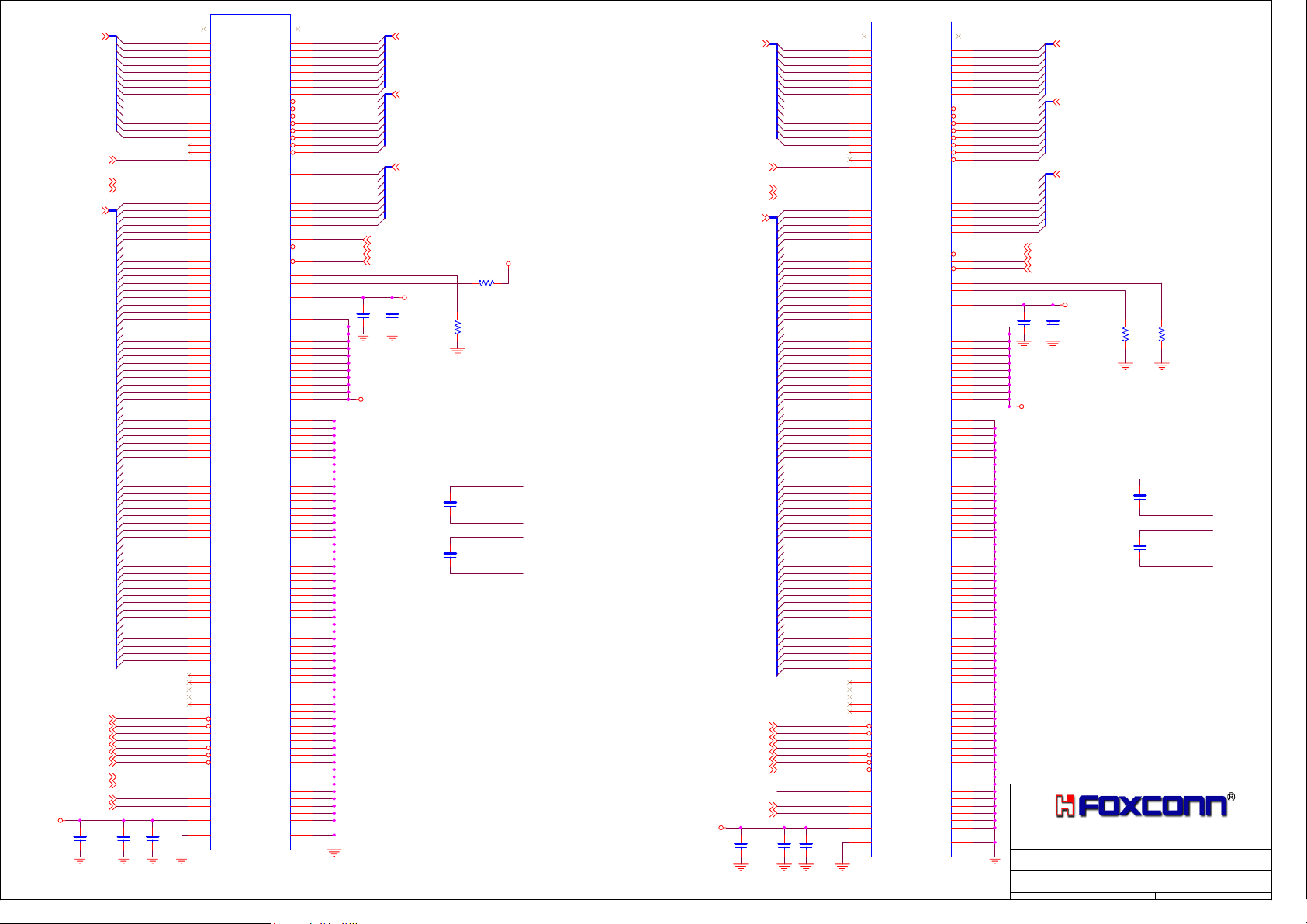

Page 8

M_A_DQ[63..0]12

www.hocnghetructuyen.vn

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AY2

AW2

AP1

AN2

AV2

AN1

AG7

AG4

AG9

AH6

AT5

AL5

AT3

AL2

AF9

AF6

AF4

AF8

U39D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

CALISTOGA_1p0

AU12

SA_BS_0

AV14

SA_BS_1

BA20

SA_BS_2

AY13

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

DDR SYSTEM MEMORY A

SA_WE#

AJ33

AM35

AL26

AN22

AM14

AL9

AR3

AH4

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AW14

AK23

AK24

AY14

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

GMCH_TP48

GMCH_TP49

M_A_BS0# 12,13

M_A_BS1# 12,13

M_A_BS2# 12,13

M_A_CAS# 12,13

M_A_DM[7..0] 12

M_A_DQS[7..0] 12

M_A_DQS#[7..0] 12

M_A_A[13..0] 12,13

M_A_RAS# 12,13

TP14

1

TP13

1

M_A_WE# 12,13

M_B_DQ[63..0]12

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AN10

AK13

AH11

AK10

BA10

AW10

AW4

AY10

AW5

AR5

AK4

AK3

AT4

AK5

AJ9

AJ8

BA4

AY9

AY5

AV4

AJ5

AJ3

U39E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

CALISTOGA_1p0

AT24

SB_BS_0

AV23

SB_BS_1

AY28

SB_BS_2

AR24

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

DDR SYSTEM MEMORY B

SB_WE#

M_B_DM0

AK36

M_B_DM1

AR38

M_B_DM2

AT36

M_B_DM3

BA31

M_B_DM4

AL17

M_B_DM5

AH8

M_B_DM6

BA5

M_B_DM7

AN4

M_B_DQS0

AM39

M_B_DQS1

AT39

M_B_DQS2

AU35

M_B_DQS3

AR29

M_B_DQS4

AR16

M_B_DQS5

AR10

M_B_DQS6

AR7

M_B_DQS7

AN5

M_B_DQS#0

AM40

M_B_DQS#1

AU39

M_B_DQS#2

AT35

M_B_DQS#3

AP29

M_B_DQS#4

AP16

M_B_DQS#5

AT10

M_B_DQS#6

AT7

M_B_DQS#7

AP5

M_B_A0

AY23

M_B_A1

AW24

M_B_A2

AY24

M_B_A3

AR28

M_B_A4

AT27

M_B_A5

AT28

M_B_A6

AU27

M_B_A7

AV28

M_B_A8

AV27

M_B_A9

AW27

M_B_A10

AV24

M_B_A11

BA27

M_B_A12

AY27

M_B_A13

AR23

AU23

AK16

AK18

AR27

Place Test PAD Near to Chip

ascould as possible

M_B_BS0# 12,13

M_B_BS1# 12,13

M_B_BS2# 12,13

M_B_CAS# 12,13

M_B_DM[7..0] 12

M_B_DQS[7..0] 12

M_B_DQS#[7..0] 12

M_B_A[13..0] 12,13

M_B_RAS# 12,13

TP11

1

TP10

1

M_B_WE# 12,13

Title

Size Document Number R ev

<Doc>

Custom

Date: Sheet

Calistoga (3 of 6)

W06N

844Saturday, Febr uary 19, 2005

SA

of

FOXCONN ND2

Page 9

1D5V_S0

www.hocnghetructuyen.vn

1D5V_TVDAC_S0

1D5V_QTVDAC_S0

1D5V_S0

R179

0

R0805

+/-5%

0

C116

*

0.1uF

C0402

10V, X5R, +/-10%

D11

SSM5818

C180

0.1uF

*

10V, X5R, +/-10%

C0402

C173

0.1uF

*

10V, X5R, +/-10%

C0402

R107

21

R0402

+/-5%

L5

*

L0805 1uH

L4

*

L0805 1uH

L3

*

L0805 1uH

L2

*

L0805 1uH

+/-5%

R0805

R215

1K

*

*

*

*

0 R0603 +/-5%R154

1D5V_S01D5V_NB_S0

3D3V_S0

C208

10uF

10V, Y5V, +80%/-20%

C0805

C197

10uF

10V, Y5V, +80%/-20%

C0805

C120

10uF

10V, Y5V, +80%/-20%

C0805

C432

10uF

10V, Y5V, +80%/-20%

C0805

R191 0 R0603 +/-5%

R192 0 R0603 +/-5%

0 R0603 +/-5%R164

0 R0603 +/-5%R193

0 R0603 +/-5%R194

*

C205

*

C185

*

C119

*

C430

1D5V_S0

C201

0.1uF

*

10V, X5R, +/-10%

C0402

C202

0.1uF

*

10V, X5R, +/-10%

C0402

C203

0.1uF

*

10V, X5R, +/-10%

C0402

C204

0.1uF

*

10V, X5R, +/-10%

C0402

1D5V_HMPLL_S0

1D5V_DPLLA_S0

0.1uFC0402

10V, X5R, +/-10%

1D5V_DPLLB_S0

0.1uFC0402

10V, X5R, +/-10%

1D5V_HPLL_S0

0.1uFC0402

10V, X5R, +/-10%

1D5V_MPLL_S0

0.1uFC0402

10V, X5R, +/-10%

1D5V_S0 1D5V_PCIE_S0

3D3V_TVDACA_S0 VCCA_3GPLL_S0

3D3V_TVDACB_S0

3D3V_TVDACC_S0

3D3V_ATVBG_S0

G6

1 2

Close-Power-Gap-3050

R0805

+/-5%

VSSA_TVBG

R158

0

10uFC0805

10V, Y5V, +80%/-20%

1D5V_S0

*

C122

10V, Y5V, +80%/-20%

0R0603+/-5% R110

2D5V_CRTDAC_S0

*

10uFC0805

*

10uFC0805

C162

C143

10V, Y5V, +80%/-20%

1D5V_3GPLL_S0

*

10uFC0805

C135

10V, Y5V, +80%/-20%

*

C181

Layout Notes: VSSA_CRTDAC

Route caps within 250mil

of Alviso. Route FB

within 3" of Alviso.

0.1uFC0402

10V, X5R, +/-10%

0R0603+/-5% R152

10V, X5R, +/-10%

C199

0.1uF

*

C0402

10V, X5R, +/-10%

1D5V_HMPLL_S0 3D3V_TVDACA_S0

1D5V_S0

*

10uFC0805

10V, Y5V, +80%/-20%

3D3V_S0

*

10uFC0805

10V, Y5V, +80%/-20%

C133

*

0.1uF

C0402

10V, X5R, +/-10%

2D5V_S0

R167 0

R0603+/-5%

Route VSSA_CRTDAC gnd from GMCH to

decoupling cap ground lead and then

connect to the gnd plane.

C186

0.1uF

C0402

10V, X5R, +/-10%

2D5V_3GBG_S02D5V_S0

C177

*

0.1uF

C0402

C178

10nF

*

C0402

1 2

Close-Power-Gap-3050

25V, X7R, +/-10%

*

10V, X5R, +/-10%

C233

*

0.1uF

C0402

C234

10V, X5R, +/-10%

C200

*

0.1uF

C0402

C231

10V, X5R, +/-10%

R184

2 1

1K

SSM5818

R0402

+/-5%

2D5V_S0

*

1D5V_PCIE_S0

G7

1 2

Close-Power-Gap-3050

Close-Power-Gap-3050

2D5V_S0

G8

C429

0.1uF

C0402

3D3V_S0

NB_CORE_S0

D12

2D5V_S0

G5

1 2

C428

*

0.1uF

C0402

10V, X5R, +/-10%

1D5V_NB_S0

VCCA_3GPLL_S0

2D5V_CRTDAC_S0

VSSA_CRTDAC

1D5V_DPLLA_S0

1D5V_DPLLB_S0

1D5V_HPLL_S0

1D5V_MPLL_S0

3D3V_ATVBG_S0

VSSA_TVBG

3D3V_TVDACB_S0

3D3V_TVDACC_S0

1D5V_TVDAC_S0

1D5V_QTVDAC_S0

H22

VCCSYNC

C30

VCC_TXLVDS0

B30

VCC_TXLVDS1

A30

VCC_TXLVDS2

AJ41

VCC3G0

AB41

VCC3G1

Y41

VCC3G2

V41

VCC3G3

R41

VCC3G4

N41

VCC3G5

L41

VCC3G6

AC33

VCCA_3GPLL

G41

VCCA_3GBG

H41

VSSA_3GBG

F21

VCCA_CRTDAC0

E21

VCCA_CRTDAC1

G21

VSSA_CRTDAC

B26

VCCA_DPLLA

C39

VCCA_DPLLB

AF1

VCCA_HPLL

A38

VCCA_LVDS

B39

VSSA_LVDS

AF2

VCCA_MPLL

H20

VCCA_TVBG

G20

VSSA_TVBG

E19

VCCA_TVDACA0

F19

VCCA_TVDACA1

C20

VCCA_TVDACB0

D20

VCCA_TVDACB1

E20

VCCA_TVDACC0

F20

VCCA_TVDACC1

AH1

VCCD_HMPLL0

AH2

VCCD_HMPLL1

A28

VCCD_LVDS0

B28

VCCD_LVDS1

C28

VCCD_LVDS2

D21

VCCD_TVDAC

A23

VCC_HV0

B23

VCC_HV1

B25

VCC_HV2

H19

VCCD_QTVDAC

AK31

VCCAUX0

AF31

VCCAUX1

AE31

VCCAUX2

AC31

VCCAUX3

AL30

VCCAUX4

AK30

VCCAUX5

AJ30

VCCAUX6

AH30

VCCAUX7

AG30

VCCAUX8

AF30

VCCAUX9

AE30

VCCAUX10

AD30

VCCAUX11

AC30

VCCAUX12

AG29

VCCAUX13

AF29

VCCAUX14

AE29

VCCAUX15

AD29

VCCAUX16

AC29

VCCAUX17

AG28

VCCAUX18

AF28

VCCAUX19

AE28

VCCAUX20

AH22

VCCAUX21

AJ21

VCCAUX22

AH21

VCCAUX23

AJ20

VCCAUX24

AH20