Page 1

5

hocnghetructuyen.vn

4

3

2

1

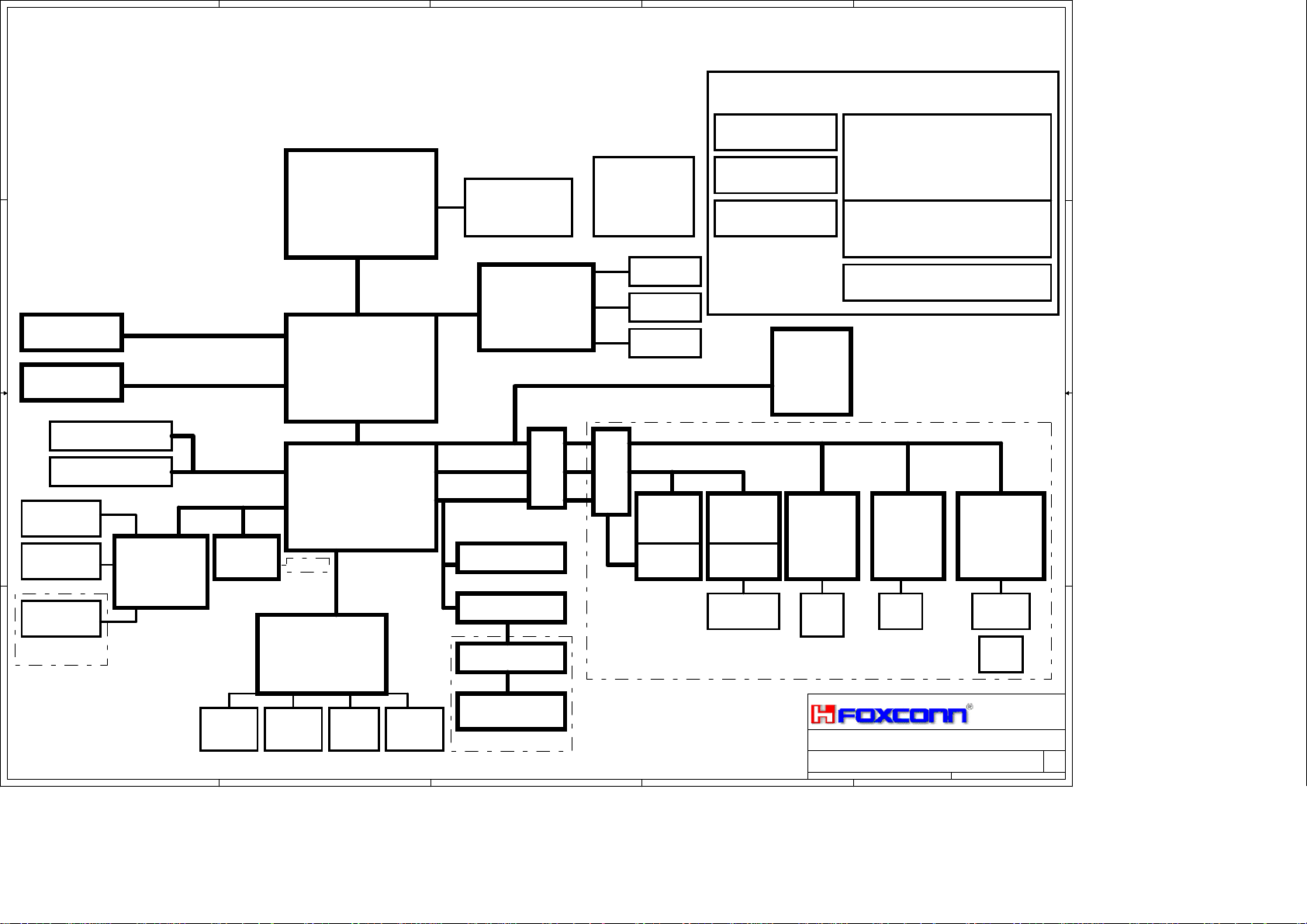

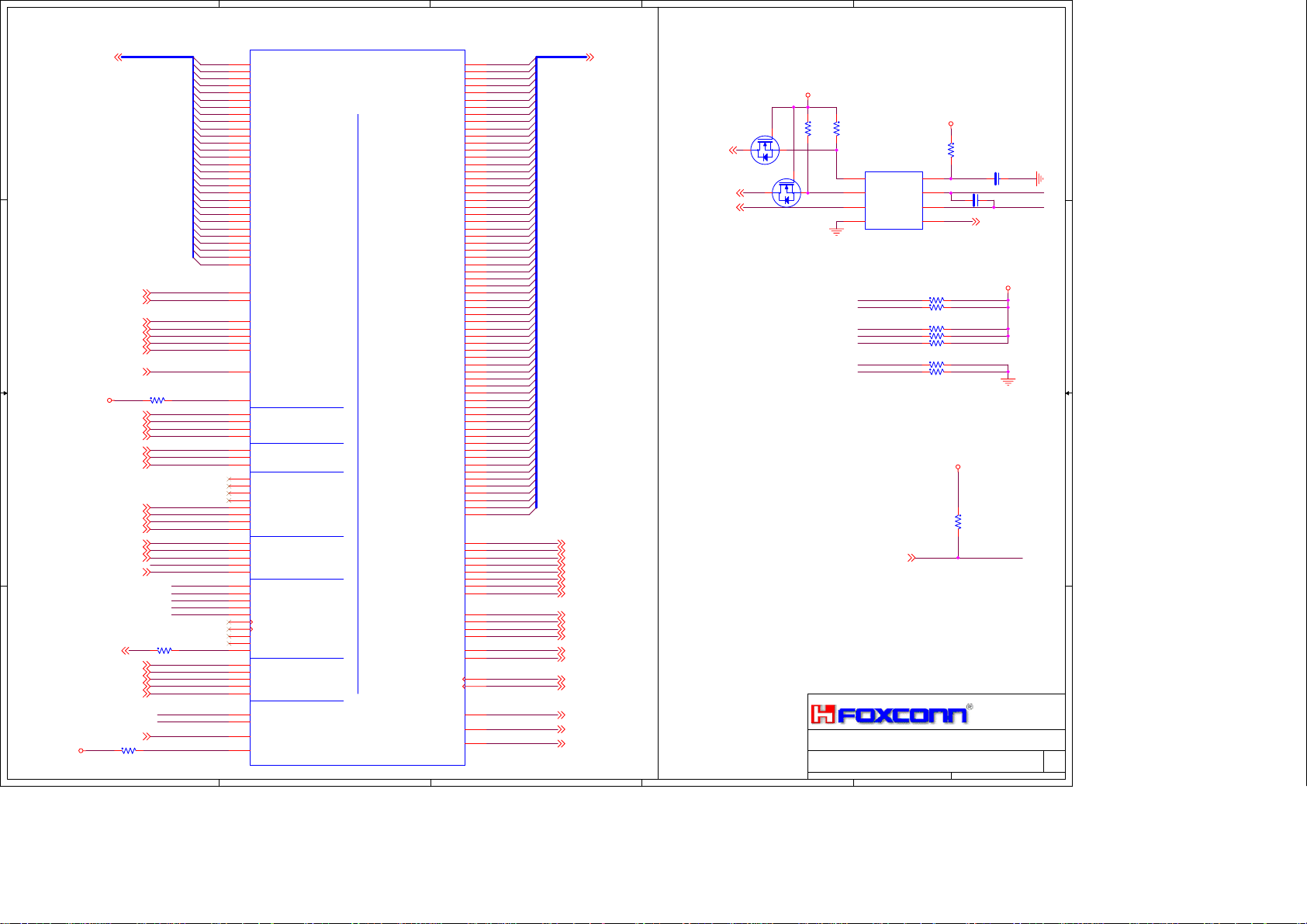

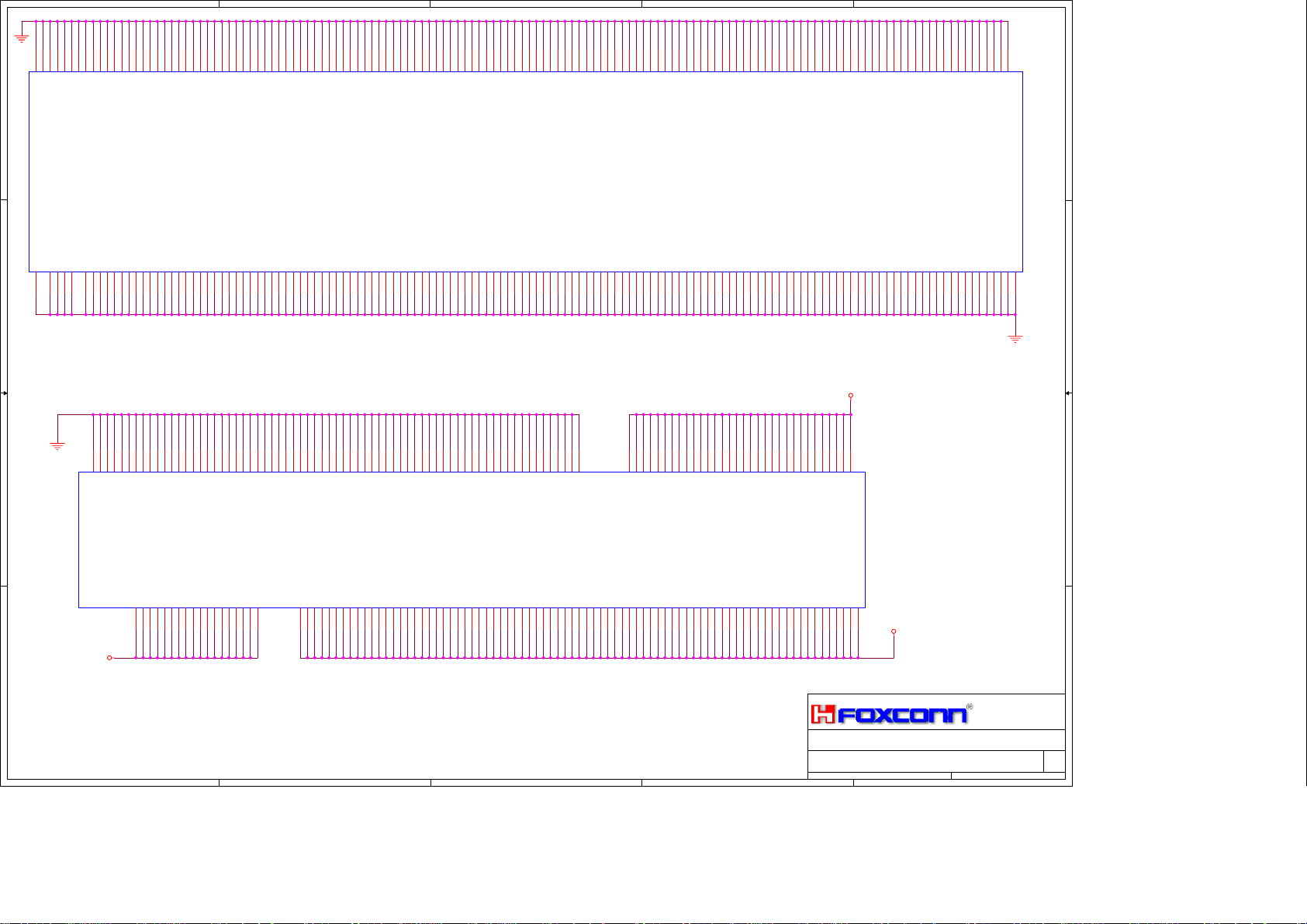

S04

BLOCK DIAGRAM

D D

Dothan(Yonah)/Alviso

+1.8V

+1.5V

Dothan/Yonah

+VCCP

FSB

C C

VTT_MEM

DDR-SODIMM1

DDR-SODIMM2

VDIMM

DDR SDRAM 2.5V, 400/500MHz

P:12

DDR SDRAM 2.5V, 400/500MHz

P:13

4X100MHZ

4X133MHZ

+VCCP(1.05V)

VDIMM(2.5V)

+2.5V

VCORE_CPU

478 Pins

(Micro-FCPGA)

P:5,6

PCI-Express x16(GFX)

+1.5V

( 915PM )

Alviso

1257 PCBGA

+3V

+3V

CPU Thermal

Sensor

MAX6648

VCORE_VGA

Video Controller

+1.5V

+1.8V

+1.2V

+2.5V

+3V

P:5

ATI-M24CSP

P:21,22,23

P:7,8,9,10,11

Primary IDE - HDD

+5V

Master

DVD/CDRW/CD/COMBO

+5V

Slave

B B

Headphone

P:27

External

P:27

MIC

P:17

P:17

+5V

+3V

AUDIO

ALC202A(Codec)

ATA 66/100

AC-LINK

+5V

+3VAUX

MDC1.0

+3V

P:20

VCCRTC

+VCCP(1.05V)

+2.5V

+1.5V

+5V

+5VSUS

+3VSUS

RJ11

DMI

ICH6-M

609 BGA

P:14,15,16

+1.5VSUS

+3V

33MHZ, 3.3V PCI

PCI-Express x1

USB 2.0

USB PORT -->2,6

+5VSUS

CON

P:38

P:17

TPA0312(Amp)

P:26

Internal

P:1

MIC

PCI Board

A A

+5V

Touchpad

P:29

5

+3VALW

+5V

+3V

PC87591

176 Pins LQFP

+5V

Keyboard

P:29

+3VALW

FLASH

4

VCCRTC

P:28

P:28

+5V

FAN 1

P:30

CON

CON

USB --> 1

+5VSUS

USB BOARD

P:38

3

+3V

Clocks

CK410

CYPRESS:

CY28411

IDT CV125

LVDS

R.G,B

P:4

LCD Panel

CRT port

S-VIDEO

CON

P:1

+1.5V

+3VSUS 3VAUX

+3V

NewCard

USB --> 7

PCI Board

P:25

P:24

P:24

P:5

DC/DC & Charger

CPU VR

MAX1987

AC/BATT

Connector

RTC

Battery

PIRQCJ,DJ

AD20

REQ1J

+3V

CardReader

P:5

USB -->0

SD&MMC&MS

Slot

2

P:31

P:39

P:33

+5V

+3VSUS

MINI-PCI

Intel

Calexico II

33MHZ, 3.3V PCI

PIRQEJ

CardBus

OZ711

Switching

+VCCP,1.5V

3V,5V

VGA CORE

VDIMM,VTT_MEM

LDO

1.2V(ATI)

+1.8V

+2.5V

+3V

MAX1715

MAX1999

MAX1993

MAX8550

MAX8527

L1087_ADJ

P:20

AD25

REQ3J

PIRQBJ

+3V

AD23

REQ2J

PIRQAJ

+3V

1394

VT6307

P:5 P:4

CARD

BUS

SLOT

Title

Document Number Re v

Date: Sheet

1394

CONN

S04 MAINBOARD

10/100/1G

RTL8110S-32

RJ45

TECHNOLOGY COPR.

1

+3VAUX

LAN

P:2

P:3

RJ11

140Monday, June 14, 2004

P:36

P:33

P:35

P:34

P:37

P:37

P:37

AD22

REQ0J

of

A

BLOCK DIAGRAM

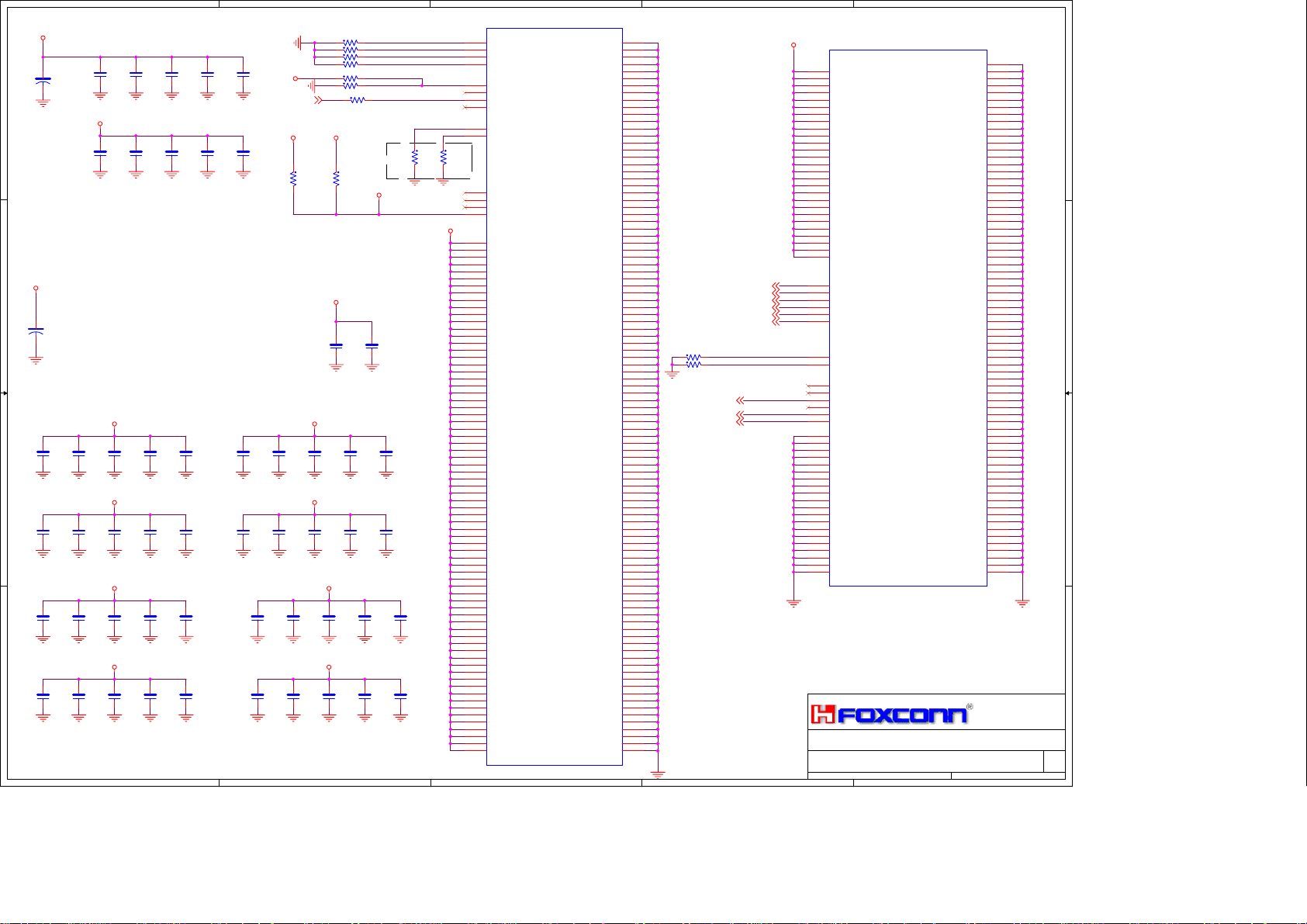

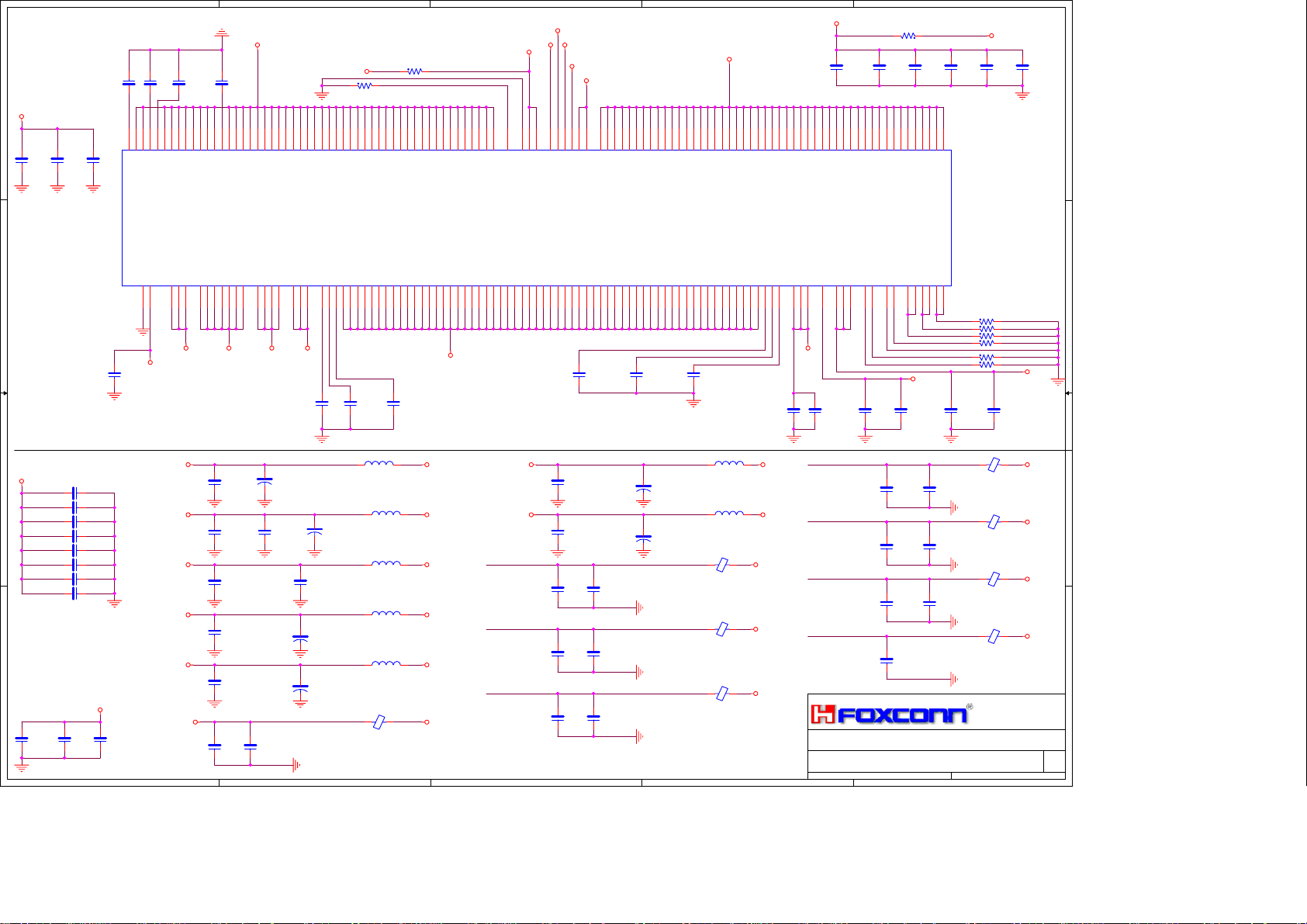

Page 2

5

hocnghetructuyen.vn

4

3

2

1

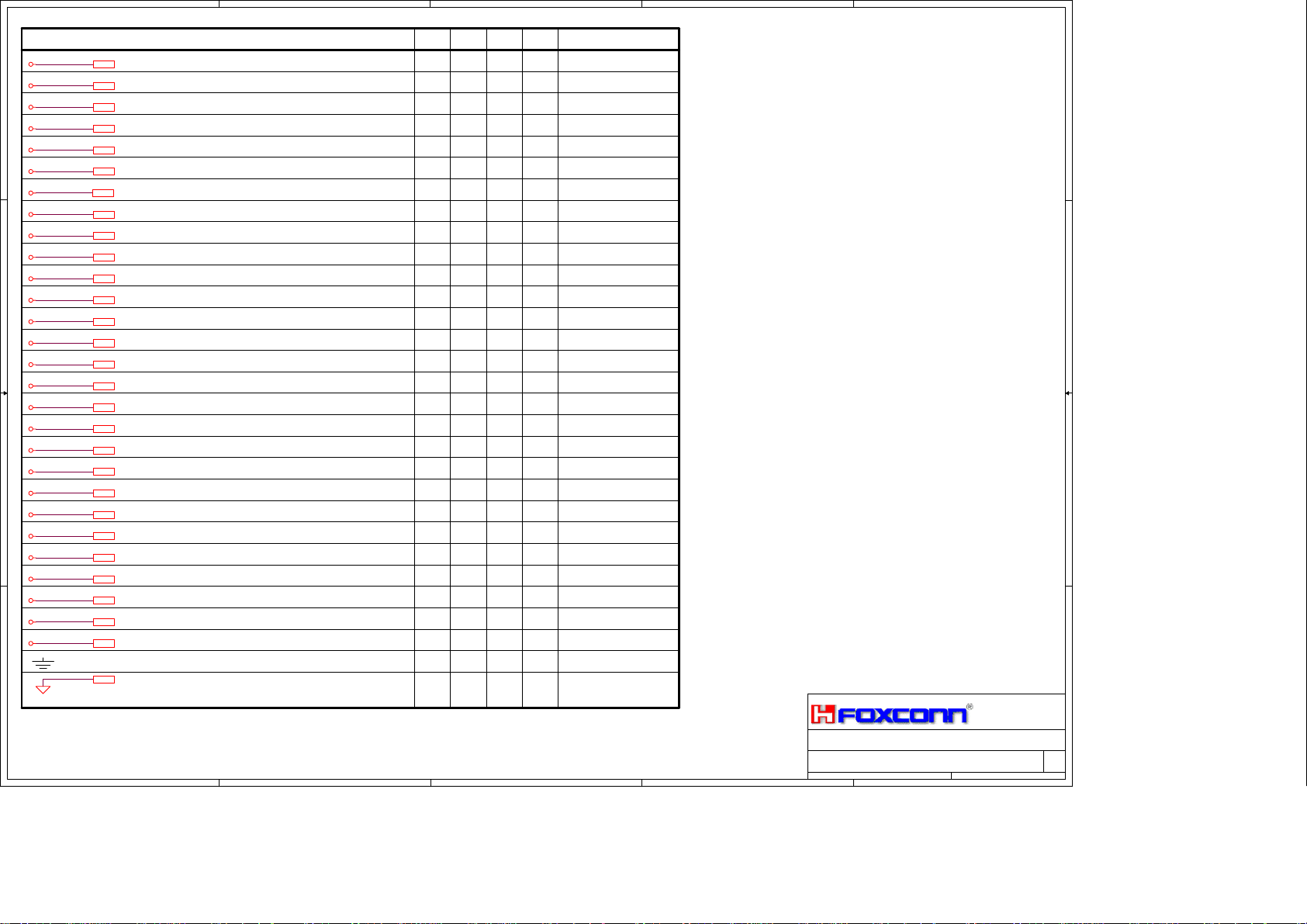

Power & Ground

Label

MBATA+

VIN

VCCRTC

D D

+3VALW

+5VALW

3VAUX

+1.5VSUS

VDIMM

+3VSUS

+5VSUS

+1.5V

+1.8V

C C

VCORE_VGA

VMEM_VGA

+3V

+5V

+5VA

+5VAA

+5V_FAN

M_VREF

VCORE_CPU

B B

+VCCP

+1.2V

+2.5V

5VAUX

VTT_MEM

MOSVCC

MOSVCC_RUN

GND

A A

AUDGND

Pg#

MBATA+ 39

VIN 25,31,33,34,35,36,39

VCCRTC 14,16,28,33

+3VALW 19 ,25,28,29, 33,39

+5VALW 32 ,33

3VAUX 20,33, 38

+1.5VSUS 16,36,37

VDIMM 7,9 ,10,12,13 ,34,37

+3VSUS 15,16,19,20,32,33,34,35

+5VSUS 16,17,32,33,36,38

+1.5V 6,10,11,15,16,23,32,36,37,38

+1.8V 6,22,23,32,37

VCORE_VGA 23,35

VMEM_VGA 22,23

+3V 4,5,10,12,13,14,15,16,17,18,19,20,21,23,24,25,26,28,29,30,31,32,33,35,37,38

+5V 16,17,20,24,25,26,27,28,29,30,31,32,33,38

+5VA 26

+5VAA 26,27

+5V_FAN 30

M_VREF 7,12,13,34

VCORE_CPU 6,31

+VCCP 4,5,6,7,9,10,14,16,36

+1.2V 23,37

+2.5V 7,8,10,11,16,23,32,37

5VAUX 33,34 ,35,36,38

VTT_MEM 12,13,34

MOSVCC 32,33

MOSVCC_RUN 25,30,32,33,38

ALL PAGES

AUDGND 26,27,38

5

4

S0 S3 S4 S5

YYYY

YYYY

YYYY

YYYY

YYY

YY

YY

YY

YY

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

YYY

Y

YYY

Y

Control Signal

9V-12.6V,3X2 cells

20V-9V

3V

3VAUXEN

3VAUXEN

YYYY

3VAUXEN

SUSD

SUSON

SUSD

SUSD

MAIND

+3V

MAIND

+1.8V

MAIND

MAIND

+5V

+5V

VFAN,+5V

MAINON

VRON

VRON

MAIND

MAIND

3VAUXEN

MAINON

5VAU X

MAINON

3

Title

Frontpage

Document Number Re v

2

Date: Sheet

S04 MAINBOARD

TECHNOLOGY COPR.

240Monday, June 14, 2004

1

A

of

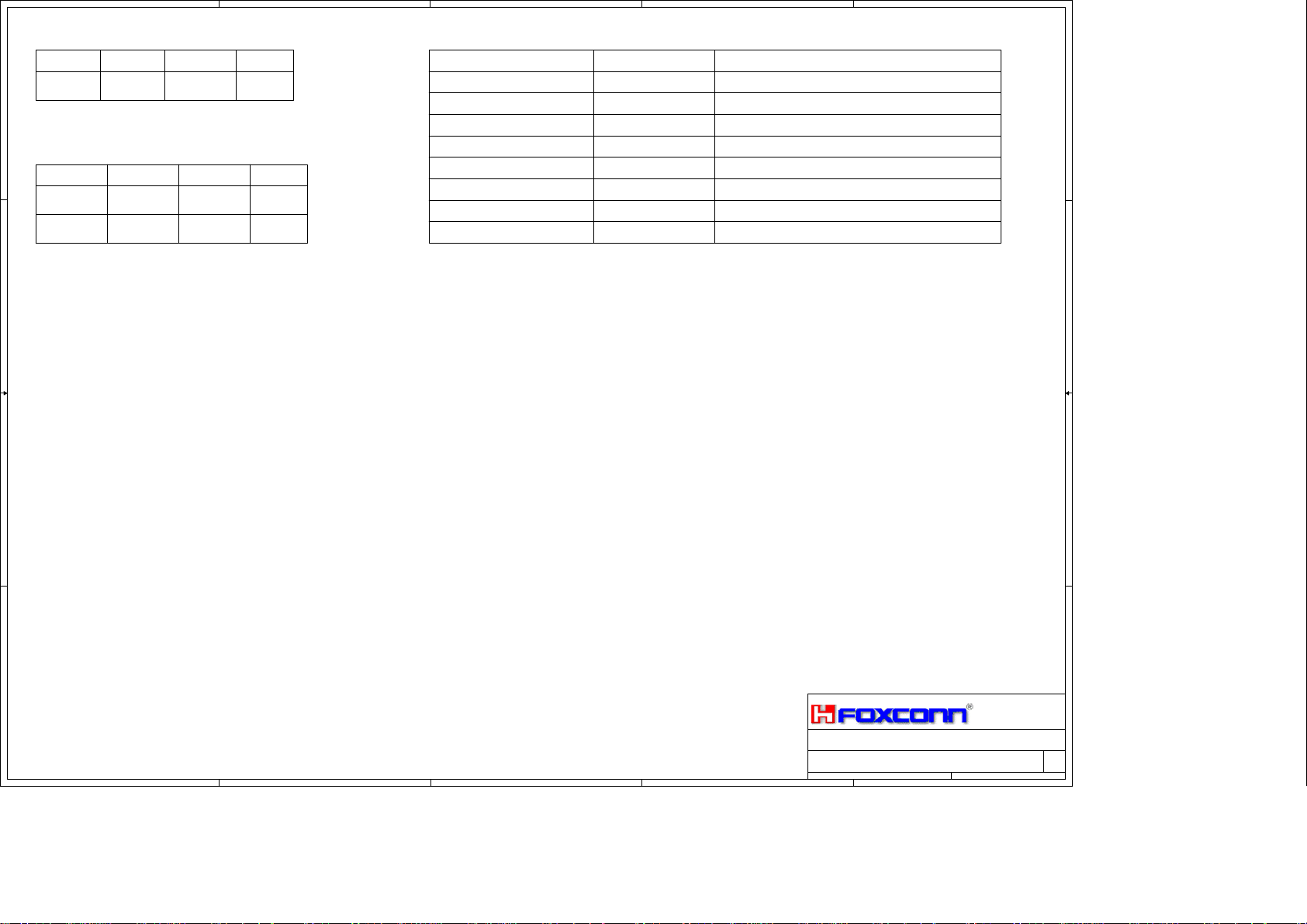

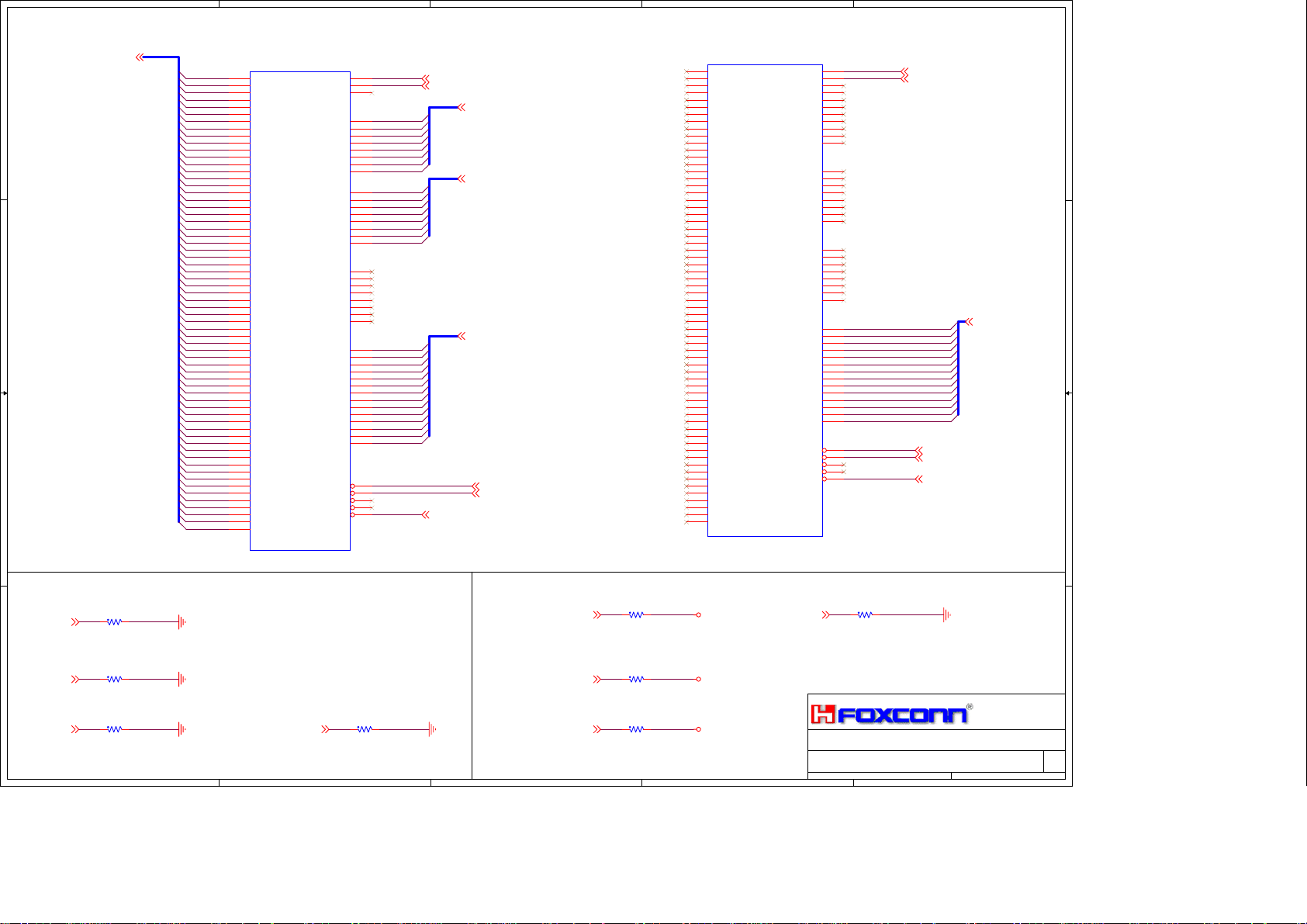

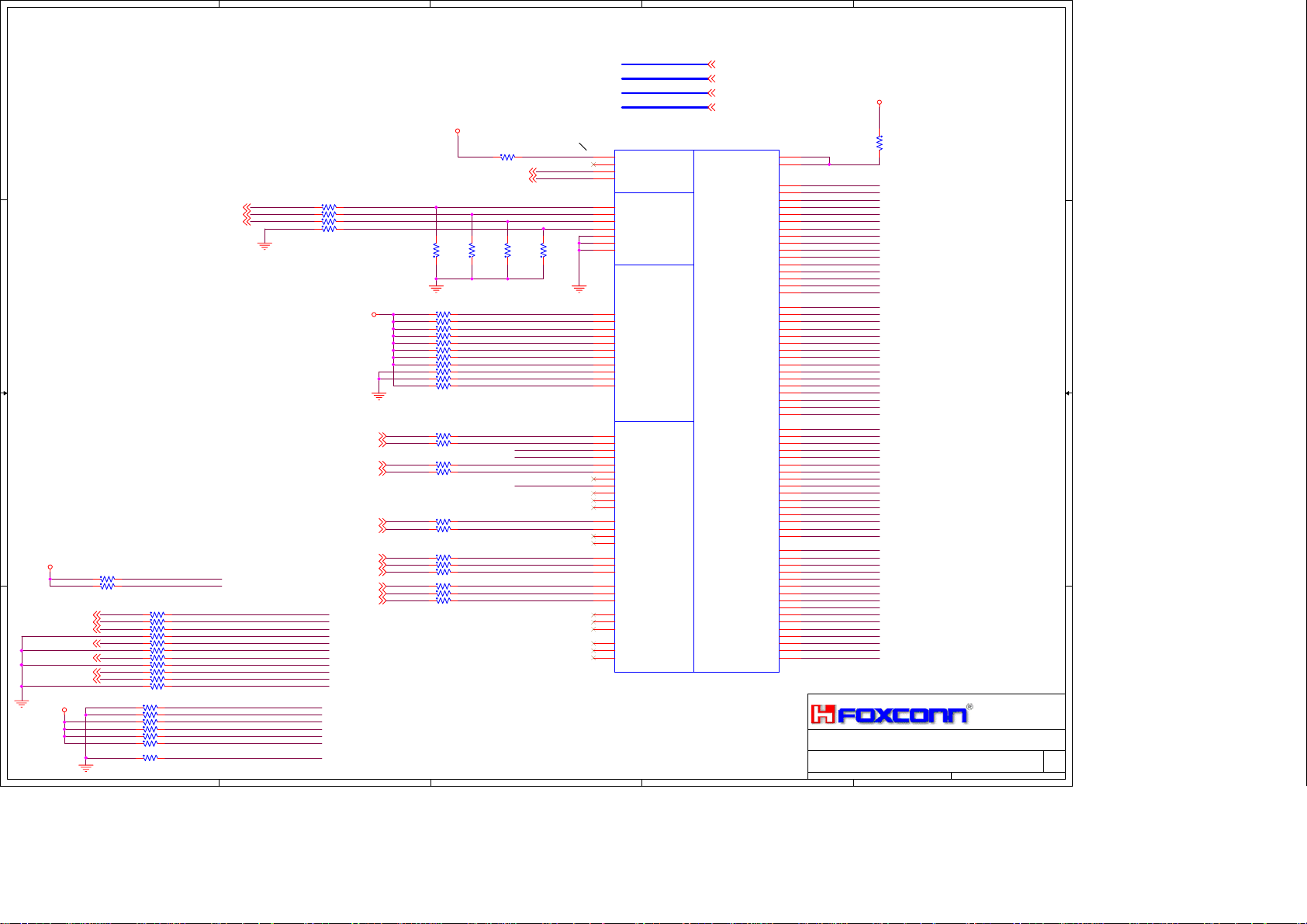

Page 3

5

hocnghetructuyen.vn

4

3

2

1

PWR_LED STATUS

S0 S1&S3 S4&S5

PWR_LED

D D

ON Blinking OFF

LAN LED STATUS

Green Amber Yellow

10M/100M

1000M

C C

Blinking

Blinking

OFF

BlinkingONON

WAKE UP EVENT

POWER BUTTON

RTC ALARM

LAN (PCI LAN)

USB

TOUCH PAD/INTERNAL KB

MODEM WAKEUP

1394

WIRELESS LAN

WAKE UP EVENT

FROM ACPI STATE

S1,S3,*S4,S5

S5

S1,S3,*S4

S1,S3

S1,S3

S3 Default support

COMMENTS

Default set all support by BIOS

Default set all support by BIOS

*S4 support set by BIOS,or not support

S3 set by BIOS,or not support

Default support

not support

not support

B B

A A

Title

Table of contects

Document Number Re v

5

4

3

2

Date: Sheet

S04 MAINBOARD

TECHNOLOGY COPR.

340Monday, June 14, 2004

1

A

of

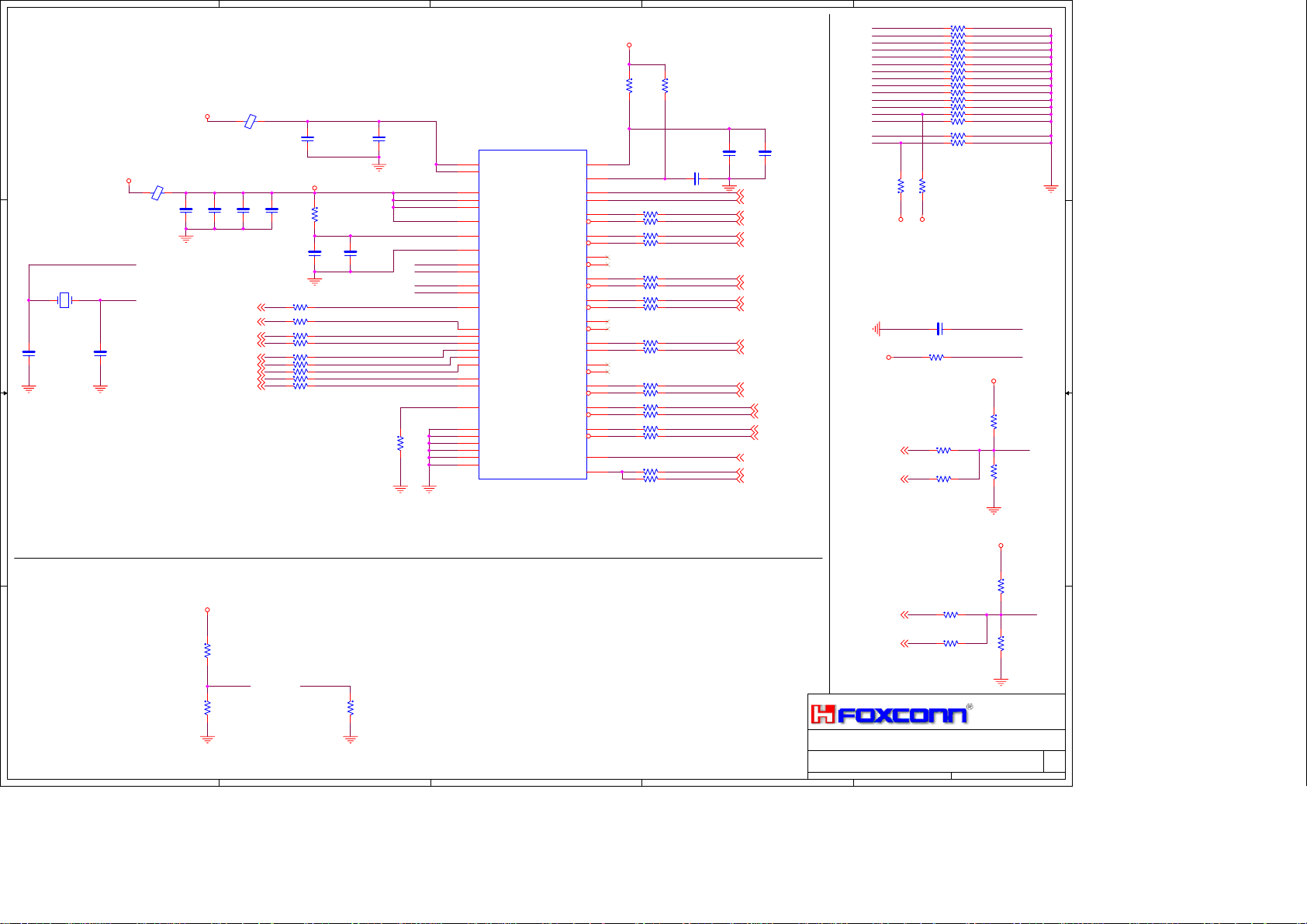

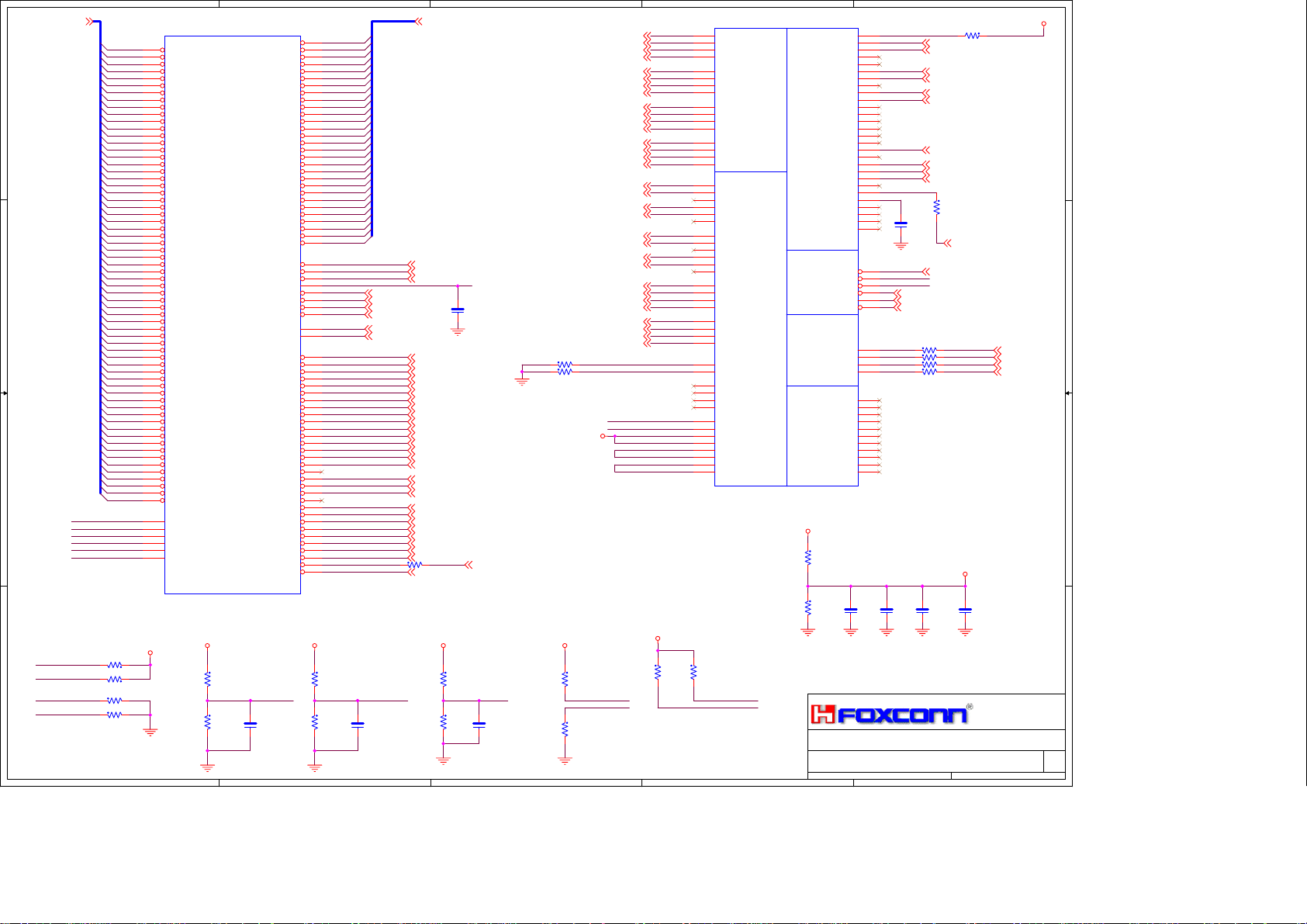

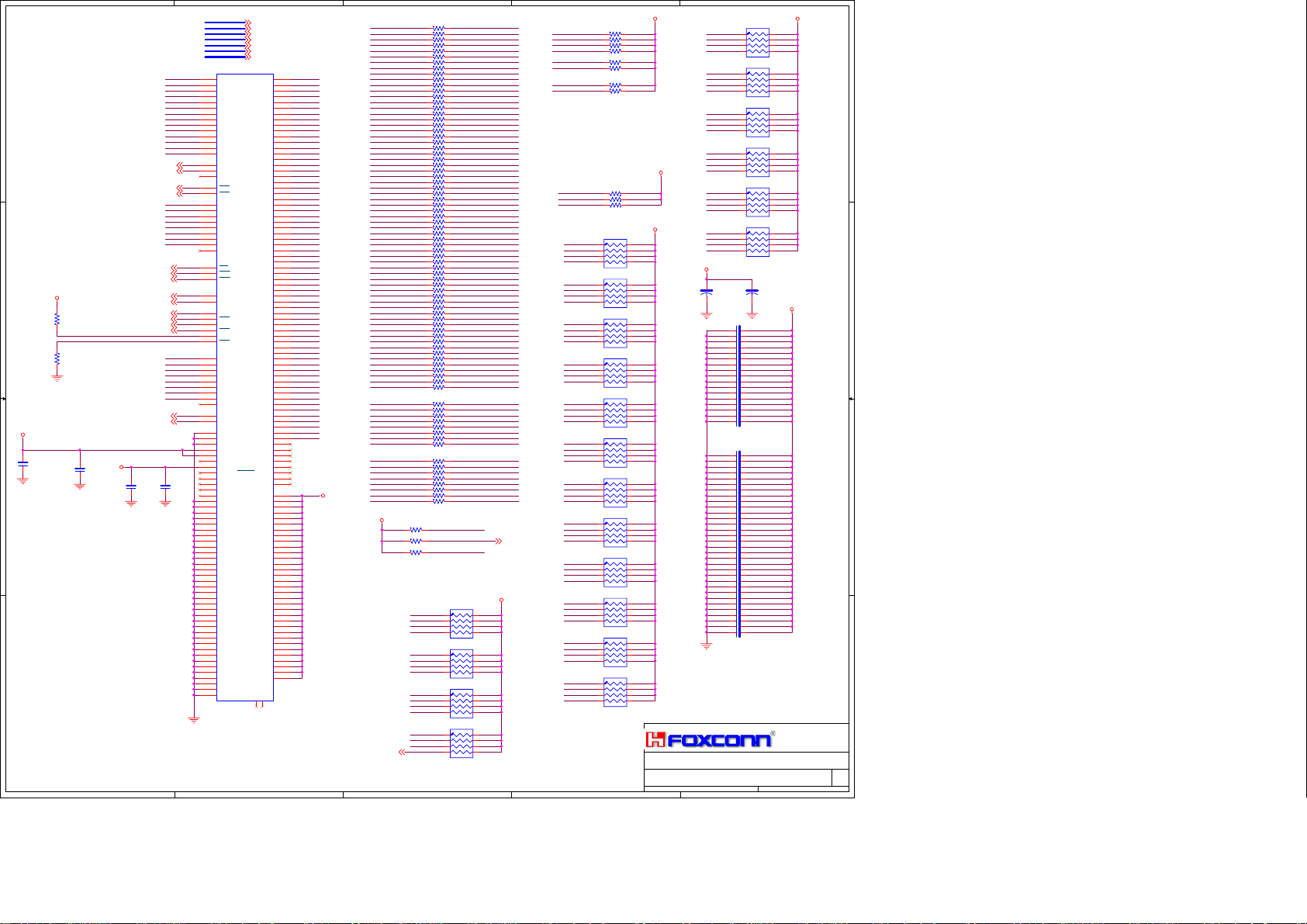

Page 4

5

hocnghetructuyen.vn

*

CLK48_USB15

PCLK_139438

PCLK_MINI20

PCLK_59128

PCLK_LAN38

PCLK_OZ38

PCLK_ICH615

SMB_CLK12,13,15,16,38

SMB_DATA12,13,15,16,38

FB1

FB L0805 180 Ohm

2 1

BC7

*

0.1uF

C0402

BC8

0.1uF

C0402

*

D D

+3V

FB2

FB L0805 180 Ohm

2 1

CLK_XTAL_OUT

CLK_XTAL_IN

X1

XTAL-14.318MHz

BC13

33pF

C0603

12

BC14

*

33pF

C0603

C C

*

B B

BC6

*

0.1uF

C0402

4

+V3.3S_CLKVDD1

BC1

*

47nF

C0603

VCC3_CLK

BC9

R20

0.1uF

2.2

C0402

+/-5%

R0603

BC10

*

47nF

C0603

R30 33 R0402+/-5%

R32 33 R0402+/-5%

R36 33 R0402+/-5%

R38 33 R0402+/-5%

R42 33 R0402+/-5%

R43 33 R0402+/-5%

R45 33 R0402+/-5%

R48 0 R0402+/-5%

R50 0 R0402+/-5%

*

*

CLK_VDD_A

BC11

10uF

C0805

R0402

+/-1%

R54

475

BC2

10uF

C0805

100_96_sel

PCIF0

CGCLK_SMB

CGDAT_SMB

CLK_XTAL_OUT

CLK_XTAL_IN

BSEL0

BSEL1

FSA

CLK_IREF

U1

1

VDD_PCI0

7

VDD_PCI1

21

VDD_SRC0

28

VDD_SRC1

34

VDD_SRC2

42

VDD_CPU

37

VDD_A

38

VSS_A

49

XTAL_OUT

50

XTAL_IN

53

FSC/TEST_SEL

16

FSB/TEST_MODE

12

FSA/USB_48

3

PCI3

4

PCI4

5

PCI5

56

PCI2

9

PCIF1

8

PCIF0/ITP_EN

46

SCLOCK

47

SDATA

39

IREF

13

VSS_48

51

VSS_REF

45

VSS_CPU

29

VSS_SRC

6

VSS_PCI1

2

VSS_PCI0

CV125

3

VDD_48

VDD_REF

CPU_STOP#

PCI_STOP#

CPU1

CPU1#

CPU0

CPU0#

CPU_2_ITP/SRC_7

CPU2_ITP/SRC7#

SRC6

SRC6#

SRC5

SRC5#

SRC4_SATA

SRC4_SATA#

SRC3

SRC3#

SRC2

SRC2#

SRC1

SRC1#

SRC0

SRC0#

DOT96

DOT96#

VTT_PWRGD#/PD

REF

+V3.3S_CLKVDD1

R9

2.2

+/-5%

R0603

11

48

54

55

R21 33 R0402+/-5%

41

R23 33 R0402+/-5%

40

R24 33 R0402+/-5%

44

R25 33 R0402+/-5%

43

36

35

R27 33 R0402+/-5%

33

R28 33 R0402+/-5%

32

R29 33 R0402+/-5%

31

R31 33 R0402+/-5%

30

26

27

R39 33 R0402+/-5%

24

R41 33 R0402+/-5%

25

22

23

R47 33 R0402+/-5%

19

R49 33 R0402+/-5%

20

R950 33 R0402+/-5% @GM

17

R951 33 R0402+/-5% @GM

18

R52 33 R0402+/-5% @GM

14

R53 33 R0402+/-5% @GM

15

CKGEN_ENJ

10

R56 12.1 R0402+/-1%

52

R58 12.1 R0402+/-1%

R10

1

+/-5%

R0603

CLK_PWR

BC5 47nF

Dummy

2

CLK_MCH_BCLK

CLK_MCH_BCLKJ

CLK_CPU_BCLK

CLK_CPU_BCLKJ

CLK_NEWCARD

CLK_NEWCARDJ

CLK_PCIE_VGA

CLK_PCIE_VGAJ

CLK_PCIE_ICH

CLK_PCIE_ICHJ

CLK_PCIE_MCH

CLK_PCIE_MCHJ

DREFCLK+3V

DREFCLKJ

DREFssCLKJ

BC3

*

C0603

*

BC4

*

47nF

10uF

C0603

C0805

STP_CPUJ 15

STP_PCIJ 15

CLK_MCH_BCLK 7

CLK_MCH_BCLKJ 7

CLK_CPU_BCLK 5

CLK_CPU_BCLKJ 5

CLK_NEWCARD 38

CLK_NEWCARDJ 38

CLK_PCIE_VGA 21

CLK_PCIE_VGAJ 21

CLK_PCIE_ICH 15

CLK_PCIE_ICHJ 15

CLK_PCIE_MCH 11

CLK_PCIE_MCHJ 11

DREFssCLK 7

DREFssCLKJ 7

DREFCLK 7

DREFCLKJ 7

CKGEN_ENJ 31

CLK14_ICH6 15

CLK14_AUDIO 26

DREFssCLK

@M24

CPU_BSEL16

MCH_BSEL17

R957

0

+/-5%

R0402

+1.5V +1.5V

BC12 10pF

C0603 50V, N PO, +/-5%

R37 10K

+3V

1

R1 49.9 R0402+/-1%

R2 49.9 R0402+/-1%

R3 49.9 R0402+/-1%

R4 49.9 R0402+/-1%

R5 49.9 R0402+/-1%

R6 49.9 R0402+/-1%

R7 49.9 R0402+/-1%

R8 49.9 R0402+/-1%

R13 49.9 R0402+/-1%

R14 49.9 R0402+/-1%

R17 49.9 R0402+/-1%

R18 49.9 R0402+/-1%

R838 49.9 R0402+/-1% @GM

R839 49.9 R0402+/-1%

R949 49.9 R0402+/-1%

R948 49.9 R0402+/-1% @GM

R958

0

+/-5%

R0402

@M24

PCLK_MINI

*

PCIF0

R0402+/-5%

+VCCP

R51

1K

+/-1%

R0402

R0402+/-5%

R0402+/-1%

Dummy

Dummy

R57

2.2K

+/-5%

R0402

R55 0

R821 1K

BSEL1

+VCCP

R60

1K

+/-1%

+3V

R63

10K

+/-5%

R0402

A A

5

R64

10K

+/-5%

R0402

Dummy

FSA

100_96_sel

4

R952

10K

R0402

+/-5%

Title

Document Number Re v

3

2

Date: Sheet

CPU_BSEL06

MCH_BSEL07

Clock Generator

R61 0

R822 1K

S04 MAINBOARD

1

R0402

Dummy

R0402+/-5%

R62

2.2K

R0402+/-1%

+/-5%

R0402

Dummy

TECHNOLOGY COPR.

of

440Monday, June 14, 2004

BSEL0

A

Page 5

5

hocnghetructuyen.vn

4

3

2

1

AA3

AA2

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

A13

A12

C12

C11

B13

A16

A15

B10

A10

B18

A18

C17

B17

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

Y3

U3

R2

P3

T2

P1

T1

N2

A4

N4

J3

L1

J2

K3

K4

L4

C8

B8

A9

C9

M3

H1

K1

L2

C2

D3

A3

E4

B4

A7

D1

D4

C6

A6

B7

U2A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB0#

ADSTB1#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADS#

IERR#

BR0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

BPM0#

BPM1#

BPM2#

BPM3#

TRDY#

RS0#

RS1#

RS2#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

TCK

TDO

TDI

TMS

TRST#

ITP_CLK0

ITP_CLK1

PREQ#

PRDY#

DBR#

LINT0

LINT1

STPCLK#

SLP#

DPSLP#

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

Banias-Processor

Dothan

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

4

1 OF 3

DATA

PHASE

SIGNALS

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN0#

DSTBP0#

DSTBN1#

DSTBP1#

DSTBN2#

DSTBP2#

DSTBN3#

DSTBP3#

DINV0#

DINV1#

DINV2#

DINV3#

DBSY#

DRDY#

BCLK1

BCLK0

INIT#

RESET#

DPWR#

HDJ0

A19

D0#

HDJ1

A25

D1#

HDJ2

A22

D2#

HDJ3

B21

D3#

HDJ4

A24

D4#

HDJ5

B26

D5#

HDJ6

A21

D6#

HDJ7

B20

D7#

HDJ8

C20

D8#

HDJ9

B24

D9#

HDJ10

D24

HDJ11

E24

HDJ12

C26

HDJ13

B23

HDJ14

E23

HDJ15

C25

HDJ16

H23

HDJ17

G25

HDJ18

L23

HDJ19

M26

HDJ20

H24

HDJ21

F25

HDJ22

G24

HDJ23

J23

HDJ24

M23

HDJ25

J25

HDJ26

L26

HDJ27

N24

HDJ28

M25

HDJ29

H26

HDJ30

N25

HDJ31

K25

HDJ32

Y26

HDJ33

AA24

HDJ34

T25

HDJ35

U23

HDJ36

V23

HDJ37

R24

R26

HDJ39

R23

HDJ40

AA23

HDJ41

U26

HDJ42

V24

HDJ43

U25

HDJ44

V26

HDJ45

Y23

HDJ46

AA26

HDJ47H_IERRJ

Y25

HDJ48

AB25

HDJ49

AC23

HDJ50

AB24

HDJ51

AC20

HDJ52

AC22

HDJ53

AC25

HDJ54

AD23

HDJ55

AE22

HDJ56

AF23

HDJ57

AD24

HDJ58

AF20

HDJ59

AE21

HDJ60

AD21

HDJ61

AF25

HDJ62

AF22

HDJ63

AF26

C23

C22

K24

L24

W25

W24

AE24

AE25

D25

J26

T24

AD20

M2

H2

B14

B15

B5

H_CPURSTJ

B11

C19

+VCCP

H_A20MJ14

H_FERRJ14

H_IGNNEJ14

H_SMIJ14

H_INTR14

H_NMI14

H_STPCLKJ14

H_CPUSLPJ7,14

H_DPSLPJ14,31

PM_THRMTRIPJ7,14

R78 56

HADSTBJ07

HADSTBJ17

HREQJ07

HREQJ17

HREQJ27

HREQJ37

HREQJ47

ADSJ7

HBREQJ07

BPRIJ7

BNRJ7

HLOCKJ7

HITJ7

HITMJ7

DEFERJ7

HTRDYJ7

RSJ07

RSJ17

RSJ27

5

HAJ[3..31]

R75 56

Dummy

R77 220

PM_THRMTRIPJ

R0603+/-5%

R0603+/-5%

H_PWRGD

TCK_H

TDO_H

TDI_H

TMS_H

TRSTJ

DBRJ

R0402+/-5%

THERMDA

THERMDC

CPU_PROCHOTJ

HAJ3

HAJ4

HAJ5

HAJ6

HAJ7

HAJ8

HAJ9

HAJ10

HAJ11

HAJ12

HAJ13

HAJ14

HAJ15

HAJ16

HAJ17

HAJ18

HAJ19

HAJ20

HAJ21

HAJ22

HAJ23

HAJ24

HAJ25

HAJ26

HAJ27

HAJ28

HAJ29

HAJ30

HAJ31

HAJ[3..31]7 HDJ[0..63] 7

D D

C C

B B

PM_SYSRSTJ15,16

A A

+VCCP

HDJ[0..63]

3

HDSTBNJ0 7

HDSTBPJ0 7

HDSTBNJ1 7

HDSTBPJ1 7

HDSTBNJ2 7

HDSTBPJ2 7

HDSTBNJ3 7

HDSTBPJ3 7

HDBIJ0 7

HDBIJ1 7

HDBIJ2 7

HDBIJ3 7

DBSYJ 7

DRDYJ 7

CLK_CPU_BCLKJ 4

CLK_CPU_BCLK 4

H_INITJ 14

H_CPURSTJ 7

DPWRJ 7

+3V

R66

R65

8.2K

Q2

2N7002

D S

MBCLK28,39

Q3

2N7002

MBDATA28,39

TEMP_ALERTJ28

D S

8.2K

G

G

+/-5%

R0402

6648CLK

6648DAT

+/-5%

R0402

U3 MAX6648

8

7

6

5

H_CPURSTJ

TDO_H

TMS_H

TDI_HHDJ38

DBRJ

TCK_H

TRSTJ

SMCLK

SMDATA

-ALT

GND

H_PWRGD14

+3V

6648VCC

1

VCC

2

DXP

BC16 2.2nF C0603

3

DXN

4

-OVT

Dummy

R68 54.9 R0603+/-1%

R69 54.9 R0603+/-1%

Dummy

R70 39.2 R0603+/-1%

R71 150 R0603+/-5%

R72 150 R0603+/-5%

R73 27.4 R0402+/-1%

R74 680 R0603+/-5%

+VCCP

R67

100

+/-1%

R0603

R76

200

+/-1%

R0603

*

*

TEMP_OVTJ 30

+VCCP

H_PWRGD

BC15

0.1uF

C0603

THERMDA

THERMDC

TECHNOLOGY COPR.

Title

Dothan CPU-1

Document Number Re v

2

Date: Sheet

S04 MAINBOARD

1

540Monday, June 14, 2004

A

of

Page 6

5

hocnghetructuyen.vn

+VCCP

BC18

EC1

150uF

*

2.5V, +/-20%

CTB

D D

VCORE_CPU

C C

EC2

150uF

*

2.5V, +/-20%

CTB

BC29

*

10uF

C0805

B B

BC39

*

10uF

C0805

BC49

*

10uF

C0805

A A

BC59

*

0.1uF

C0603

BC17

*

*

0.1uF

C0603

+VCCP

BC22

*

*

0.1uF

C0603

VCORE_CPU

BC30

*

*

*

*

BC31

*

10uF

10uF

C0805

C0805

BC40

BC41

*

10uF

10uF

C0805

C0805

VCORE_CPU VCORE_CPU

BC50

BC51

*

10uF

10uF

C0805

C0805

VCORE_CPU VCORE_CPU

BC60

BC61

*

0.1uF

0.1uF

C0603

C0603

5

BC19

*

0.1uF

C0603

BC23

0.1uF

C0603

*

*

*

*

*

0.1uF

C0603

BC24

*

*

0.1uF

C0603

10U/6.3V/X5R(CC0805)

5 mOhm*35

BC32

BC33

*

10uF

10uF

C0805

C0805

BC42

BC43

*

10uF

10uF

C0805

C0805

BC52

BC53

*

10uF

10uF

C0805

C0805

BC62

BC63

*

0.1uF

0.1uF

C0603

C0603

BC20

0.1uF

C0603

BC25

0.1uF

C0603

BC21

*

0.1uF

+VCCP

C0603

H_DPRSLPJ14

BC26

*

0.1uF

C0603

BC34

*

*

10uF

C0805

BC44

*

*

10uF

C0805

BC54

*

10uF

C0805

BC64

*

10uF

C0805

+1.5V

R88

0

+/-5%

R0805

VCORE_CPU

BC35

10uF

C0805

VCORE_CPUVCORE_CPU

BC45

10uF

C0805

BC55

*

10uF

C0805

BC65

*

10uF

C0805

4

R79 27.4 R0402+/-1%

R80 54.9 R0402+/-1%

R81 27.4 R0402+/-1%

R82 54.9 R0402+/-1%

R83 1K R0603+/-1%

R84 2K R0603+/-1%

R85 0

+1.8V

+1.8V_R

*

BC36

*

10uF

C0805

BC46

*

10uF

C0805

*

*

4

BC56

10uF

C0805

BC66

10uF

C0805

R89

0

+/-5%

R0805

Dummy

BC27

10nF

C0402

*

*

*

BC37

10uF

C0805

BC47

10uF

C0805

*

*

R0402+/-5%

+1.8V_R

BC28

10uF

C0805

*

*

BC57

10uF

C0805

BC67

10uF

C0805

Dummy

R86

1K

+/-1%

R0603

BC38

10uF

C0805

BC48

10uF

C0805

*

*

DPRSLPJ

BC58

10uF

C0805

BC68

10uF

C0805

COMP0

COMP1

COMP2

COMP3

GTLREF0

TEST1

TEST2

Dummy

R87

1K

+/-1%

R0603

VCORE_CPU

AD26

AC26

W21

AA11

AA13

AA15

AA17

AA19

AA21

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC11

AC13

AC15

AC17

AC19

AD10

AD12

AD14

AD16

AD18

AE11

AE13

AE15

AE17

AE19

AF10

AF12

AF14

AF16

AF18

P25

P26

AB2

AB1

E26

AC1

D18

D20

D22

E17

E19

E21

G21

H22

K22

V22

Y22

AA5

AA7

AA9

AB6

AB8

AC9

AD8

AE9

AF8

G1

C5

F23

N1

B1

F26

D6

D8

E5

E7

E9

F6

F8

F18

F20

F22

G5

H6

J5

J21

U5

V6

W5

Y6

U2B

COMP0

COMP1

COMP2

COMP3

GTLREF0

RSVD

DPRSLP#

RSVD

TEST1

TEST2

VCCA3

VCCA2

VCCA1

VCCA0

VCC00

VCC01

VCC02

VCC03

VCC04

VCC05

VCC06

VCC07

VCC08

VCC09

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

Banias-Processor

3

Dothan

2 OF 3

POWER,

GROUND,

RESERVED

SIGNALS

3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A2

A5

A8

A11

A14

A17

A20

A23

A26

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

Dummy

R90 54.9 R0603+/-1%

R91 54.9 R0603+/-1%

Dummy

CPU_BSEL14

CPU_BSEL04

PSIJ31

2

+VCCP

CPU_VID031

CPU_VID131

CPU_VID231

CPU_VID331

CPU_VID431

CPU_VID531

VCCSEN

VSSSEN

U2C

D10

VCCP0

D12

VCCP1

D14

VCCP2

D16

VCCP3

E11

VCCP4

E13

VCCP5

E15

VCCP6

F10

VCCP7

F12

VCCP8

F14

VCCP9

F16

VCCP10

K6

VCCP11

L5

VCCP12

L21

VCCP13

M6

VCCP14

M22

VCCP15

N5

VCCP16

N21

VCCP17

P6

VCCP18

P22

VCCP19

R5

VCCP20

R21

VCCP21

T6

VCCP22

T22

VCCP23

U21

VCCP24

P23

VCCP25

W4

VCCP26

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AE7

VCCSENSE

AF6

VSSSENSE

B2

RSVD

AF7

RSVD

C14

BSE[1]

C3

RSVD

C16

BSE[0]

E1

PSI#

R6

VSS

R22

VSS

R25

VSS

T3

VSS

T5

VSS

T21

VSS

T23

VSS

T26

VSS

U2

VSS

U6

VSS

U22

VSS

U24

VSS

V1

VSS

V4

VSS

V5

VSS

V21

VSS

V25

VSS

W3

VSS

W6

VSS

W22

VSS

Banias-Processor

Dothan

3 OF 3

POWER, GR OUND AND NC

VID

1

W23

VSS

W26

VSS

Y2

VSS

Y5

VSS

Y21

VSS

Y24

VSS

AA1

VSS

AA4

VSS

AA6

VSS

AA8

VSS

AA10

VSS

AA12

VSS

AA14

VSS

AA16

VSS

AA18

VSS

AA20

VSS

AA22

VSS

AA25

VSS

AB3

VSS

AB5

VSS

AB7

VSS

AB9

VSS

AB11

VSS

AB13

VSS

AB15

VSS

AB17

VSS

AB19

VSS

AB21

VSS

AB23

VSS

AB26

VSS

AC2

VSS

AC5

VSS

AC8

VSS

AC10

VSS

AC12

VSS

AC14

VSS

AC16

VSS

AC18

VSS

AC21

VSS

AC24

VSS

AD1

VSS

AD4

VSS

AD7

VSS

AD9

VSS

AD11

VSS

AD13

VSS

AD15

VSS

AD17

VSS

AD19

VSS

AD22

VSS

AD25

VSS

AE3

VSS

AE6

VSS

AE8

VSS

AE10

VSS

AE12

VSS

AE14

VSS

AE16

VSS

AE18

VSS

AE20

VSS

AE23

VSS

AE26

VSS

AF2

VSS

AF5

VSS

AF9

VSS

AF11

VSS

AF13

VSS

AF15

VSS

AF17

VSS

AF19

VSS

AF21

VSS

AF24

VSS

TECHNOLOGY COPR.

Title

Dothan CPU-2

Document Number Re v

2

Date: Sheet

S04 MAINBOARD

1

640Monday, June 14, 2004

A

of

Page 7

5

hocnghetructuyen.vn

HDJ[0..63]5 HAJ[3..31] 5

HDJ0

HDJ1

HDJ2

HDJ3

HDJ4

HDJ5

HDJ6

HDJ7

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

R102 54.9

R105 54.9

R110 24.9

R111 24.9

HDJ8

HDJ9

HDJ10

HDJ11

HDJ12

HDJ13

HDJ14

HDJ15

HDJ16

HDJ17

HDJ18

HDJ19

HDJ20

HDJ21

HDJ22

HDJ23

HDJ24

HDJ25

HDJ26

HDJ27

HDJ28

HDJ29

HDJ30

HDJ31

HDJ32

HDJ33

HDJ34

HDJ35

HDJ36

HDJ37

HDJ38

HDJ39

HDJ40

HDJ41

HDJ42

HDJ43

HDJ44

HDJ45

HDJ46

HDJ47

HDJ48

HDJ49

HDJ50

HDJ51

HDJ52

HDJ53

HDJ54

HDJ55

HDJ56

HDJ57

HDJ58

HDJ59

HDJ60

HDJ61

HDJ62

HDJ63

5

D D

C C

B B

H_XSCOMP

H_YSCOMP

A A

H_XRCOMP

H_YRCOMP

U4A

E4

HD0#

E1

HD1#

F4

HD2#

H7

HD3#

E2

HD4#

F1

HD5#

E3

HD6#

D3

HD7#

K7

HD8#

F2

HD9#

J7

HD10#

J8

HD11#

H6

HD12#

F3

HD13#

K8

HD14#

H5

HD15#

H1

HD16#

H2

HD17#

K5

HD18#

K6

HD19#

J4

HD20#

G3

HD21#

H3

HD22#

J1

HD23#

L5

HD24#

K4

HD25#

J5

HD26#

P7

HD27#

L7

HD28#

J3

HD29#

P5

HD30#

L3

HD31#

U7

HD32#

V6

HD33#

R6

HD34#

R5

HD35#

P3

HD36#

T8

HD37#

R7

HD38#

R8

HD39#

U8

HD40#

R4

HD41#

T4

HD42#

T5

HD43#

R1

HD44#

T3

HD45#

V8

HD46#

U6

HD47#

W6

HD48#

U3

HD49#

V5

HD50#

W8

HD51#

W7

HD52#

U2

HD53#

U1

HD54#

Y5

HD55#

Y2

HD56#

V4

HD57#

Y7

HD58#

W1

HD59#

W3

HD60#

Y3

HD61#

Y6

HD62#

W2

HD63#

C1

HXRCOMP

C2

HXSCOMP

D1

HXSWING

T1

HYRCOMP

L1

HYSCOMP

P1

HYSWING

ALVISO_90

+VCCP

R0603+/-1%

R0603+/-1%

R0402+/-1%

R0402+/-1%

+VCCP +VCCP +VCCP

R106

221

+/-1%

R0603

R112

100

+/-1%

R0603

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HADSTB#0

HOST

HADSTB#1

HVREF

HBNR#

HBPRI#

HBREQ0#

HCPURST#

HCLKINN

HCLKINP

HDBSY#

HDEFER#

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HDPWR#

HDRDY#

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HEDRDY#

HHIT#

HHITM#

HLOCK#

HPCREQ#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS0#

HRS1#

HRS2#

HCPUSLP#

HTRDY#

H_XSWING H_YSWING H_VREF M_RCOMPN

BC75

*

0.1uF

C0603

NEAR NB NEAR NB NEAR NB

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

4

HAJ3

G9

HAJ4

C9

HAJ5

E9

HAJ6

B7

HAJ7

A10

HAJ8

F9

HAJ9

D8

HAJ10

B10

HAJ11

E10

HAJ12

G10

HAJ13

D9

HAJ14

E11

HAJ15

F10

HAJ16

G11

HAJ17

G13

HAJ18

C10

HAJ19

C11

HAJ20

D11

HAJ21

C12

HAJ22

B13

HAJ23

A12

HAJ24

F12

HAJ25

G12

HAJ26

E12

HAJ27

C13

HAJ28

B11

HAJ29

D13

HAJ30

A13

HAJ31

F13

F8

B9

E13

H_VREF

J11

A5

D5

E7

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

H_CPUSLPJ_GMCH

G8

B5

R107

221

+/-1%

R0603

R113

100

+/-1%

R0603

4

BNRJ 5

BPRIJ 5

HBREQJ0 5

H_CPURSTJ 5

CLK_MCH_BCLKJ 4

CLK_MCH_BCLK 4

BC76

*

0.1uF

C0603

ADSJ 5

HADSTBJ0 5

HADSTBJ1 5

DBSYJ 5

DEFERJ 5

HDBIJ0 5

HDBIJ1 5

HDBIJ2 5

HDBIJ3 5

DPWRJ 5

DRDYJ 5

HDSTBNJ0 5

HDSTBNJ1 5

HDSTBNJ2 5

HDSTBNJ3 5

HDSTBPJ0 5

HDSTBPJ1 5

HDSTBPJ2 5

HDSTBPJ3 5

HITJ 5

HITMJ 5

HLOCKJ 5

HREQJ0 5

HREQJ1 5

HREQJ2 5

HREQJ3 5

HREQJ4 5

RSJ0 5

RSJ1 5

RSJ2 5

R99 0

HTRDYJ 5

R0402+/-5%

Dummy

*

R108

100

+/-1%

R0603

R114

200

+/-1%

R0603

BC70

0.1uF

C0603

H_CPUSLPJ 5,14

BC77

*

0.1uF

C0603

3

M_CLK_DDR012

M_CLK_DDR112

M_CLK_DDR313

M_CLK_DDR413

M_CLK_DDRJ012

M_CLK_DDRJ112

M_CLK_DDRJ313

M_CLK_DDRJ413

M_CKE012

M_CKE112

M_CKE213

M_CKE312,13

M_CSJ012

M_CSJ112

M_CSJ212,13

M_CSJ313

R95 40.2 R0402+/-1%

R97 40.2 R0402+/-1%

M_VREF

VDIMM

R109

80.6

+/-1%

R0402

M_RCOMPP

R115

80.6

+/-1%

R0402

3

DMI_TXN015

DMI_TXN115

DMI_TXN215

DMI_TXN315

DMI_TXP015

DMI_TXP115

DMI_TXP215

DMI_TXP315

DMI_RXN015

DMI_RXN115

DMI_RXN215

DMI_RXN315

DMI_RXP015

DMI_RXP115

DMI_RXP215

DMI_RXP315

SMOCDCOMP0

SMOCDCOMP1

M_RCOMPN

M_RCOMPP

SMXSLEW

SMYSLEW

+2.5V

R103

10K

R0402

+/-5%

AA31

AB35

AC31

AD35

Y31

AA35

AB31

AC35

AA33

AB37

AC33

AD37

Y33

AA37

AB33

AC37

AM33

AL1

AE11

AJ34

AF6

AC10

AN33

AK1

AE10

AJ33

AF5

AD10

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AD1

AE27

AE28

AF9

AF10

R104

10K

R0402

+/-5%

2

U4B

DMIRXN0

DMIRXN1

DMIRXN2

DMIRXN3

DMIRXP0

DMIRXP1

DMIRXP2

DMIRXP3

DMITXN0

DMITXN1

DMITXN2

DMITXN3

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

SM_CK1

SM_CK2

SM_CK3

SM_CK4

SM_CK5

SM_CK0#

SM_CK1#

SM_CK2#

SM_CK3#

SM_CK4#

SM_CK5#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

ALVISO_90

PM_EXTTSJ0

PM_EXTTSJ1

2

1

GMCH_CFG0

G16

CFG0

H13

CFG1

G14

CFG2

F16

CFG3

F15

CFG4

G15

CFG5

E16

CFG6

D17

CFG7

DMI

CFG/RSVD

DDR MUXING

THRMTRIP#

PMCLK

DREF_CLKN

DREF_CLKP

DREF_SSCLKN

DREF_SSCLKP

NC

VDIMM

R100

4.7K

+/-5%

R0603

Dummy

R101

4.7K

+/-5%

R0603

Dummy

Title

Document Number Re v

Date: Sheet

J16

CFG8

D15

CFG9

E15

CFG10

D14

CFG11

E14

CFG12

H12

CFG13

C14

CFG14

H15

CFG15

J15

CFG16

H14

CFG17

G22

CFG18

G23

CFG19

D23

CFG20

G25

RSVD21

G24

RSVD22

J17

RSVD23

A31

RSVD24

A30

RSVD25

D26

RSVD26

D25

RSVD27

J23

BM_BUSY#

EXT_TS0#

EXT_TS1#

PWROK

RSTIN#

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

PM_EXTTSJ0

J21

PM_EXTTSJ1

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

BC71

*

*

0.1uF

C0402

Alviso MCH-1

S04 MAINBOARD

*

PM_THRMTRIPJ 5,14

IMVP_PWG 15,31

PLT_RSTJ 15, 17,21,38

R934 0 R0402+/-5%

R935 0 R0402+/-5%

R96 0 R0402+/-5%

R98 0 R0402+/-5%

BC72

2.2uF

C0603

BC69

0.1uF

C0603

Dummy

*

R93 10K R0402+/-5%

MCH_BSEL1 4

MCH_BSEL0 4

CFG5 8

CFG6 8

CFG8 8

CFG9 8

CFG16 8

CFG18 8

CFG19 8

CFG20 8

R94

0

+/-5%

R0402

MCH_SYNCJ 15,16

PM_BMBUSYJ 15

M_VREF

BC73

*

2.2uF

C0603

1

BC74

0.1uF

C0402

+VCCP

DREFCLKJ 4

DREFCLK 4

DREFssCLKJ 4

DREFssCLK 4

TECHNOLOGY COPR.

of

740Monday, June 14, 2004

A

Page 8

5

hocnghetructuyen.vn

4

3

2

1

R_M_A_DQ[0..63]12

R_M_A_DQ0

R_M_A_DQ1

R_M_A_DQ2

R_M_A_DQ3

D D

C C

B B

R_M_A_DQ4

R_M_A_DQ5

R_M_A_DQ6

R_M_A_DQ7

R_M_A_DQ8

R_M_A_DQ9

R_M_A_DQ10

R_M_A_DQ11

R_M_A_DQ12

R_M_A_DQ13

R_M_A_DQ14

R_M_A_DQ15

R_M_A_DQ16

R_M_A_DQ17

R_M_A_DQ18

R_M_A_DQ19

R_M_A_DQ20

R_M_A_DQ21

R_M_A_DQ22

R_M_A_DQ23

R_M_A_DQ24

R_M_A_DQ25

R_M_A_DQ26

R_M_A_DQ27

R_M_A_DQ28

R_M_A_DQ29

R_M_A_DQ30

R_M_A_DQ31

R_M_A_DQ32

R_M_A_DQ33

R_M_A_DQ34

R_M_A_DQ35

R_M_A_DQ36

R_M_A_DQ37

R_M_A_DQ38

R_M_A_DQ39

R_M_A_DQ40

R_M_A_DQ41

R_M_A_DQ42

R_M_A_DQ43

R_M_A_DQ44

R_M_A_DQ45

R_M_A_DQ46

R_M_A_DQ47

R_M_A_DQ48

R_M_A_DQ49

R_M_A_DQ50

R_M_A_DQ51

R_M_A_DQ52

R_M_A_DQ53

R_M_A_DQ54

R_M_A_DQ55

R_M_A_DQ56

R_M_A_DQ57

R_M_A_DQ58

R_M_A_DQ59

R_M_A_DQ60

R_M_A_DQ61

R_M_A_DQ62

R_M_A_DQ63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

U4C

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

ALVISO_90

AK15

SA_BS0#

AK16

SA_BS1#

AL21

SA_BS2#

R_M_A_DM0

AJ37

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

DDR SYSTEM MEMORY A

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

RCVENIN#

RCVENOUT#

SA_WE#

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

R_M_A_DM1

R_M_A_DM2

R_M_A_DM3

R_M_A_DM4

R_M_A_DM5

R_M_A_DM6

R_M_A_DM7

R_M_A_DQS0

R_M_A_DQS1

R_M_A_DQS2

R_M_A_DQS3

R_M_A_DQS4

R_M_A_DQS5

R_M_A_DQS6

R_M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BSJ0 12

M_A_BSJ1 12

M_A_WEJ 12

R_M_A_DM[0..7] 12

R_M_A_DQS[0..7] 12

M_A_A[0..13] 12

M_A_CASJ 1 2,13

M_A_RASJ 1 2,13

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AK9

AK6

AH5

AK8

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

AJ9

AJ7

AJ4

AJ8

AJ5

U4D

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

ALVISO_90

AJ15

SB_BS0#

AG17

SB_BS1#

AG21

SB_BS2#

AF32

SB_DM0

AK34

SB_DM1

AK27

SB_DM2

AK24

SB_DM3

AJ10

SB_DM4

AK5

SB_DM5

AE7

SB_DM6

AB7

SB_DM7

AF34

SB_DQS0

AK32

SB_DQS1

AJ28

SB_DQS2

AK23

SB_DQS3

AM10

SB_DQS4

AH6

SB_DQS5

AF8

SB_DQS6

AB4

SB_DQS7

AF35

SB_DQS0#

AK33

SB_DQS1#

AK28

SB_DQS2#

AJ23

SB_DQS3#

AL10

SB_DQS4#

AH7

SB_DQS5#

AF7

SB_DQS6#

AB5

SB_DQS7#

M_B_A0

AH17

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

DDR SYSTEM MEMORY B

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_BSJ0 13

M_B_BSJ1 13

M_B_CASJ 13

M_B_RASJ 13

M_B_WEJ 13

M_B_A[0..13] 13

CFG[3..17] internal pullup

R118 2.2K

CFG57

CFG87

A A

CFG97 CFG167

R0402+/-5%

R120 2.2K

R0402+/-5%

R123 2.2K

R0402+/-5%

5

Dummy

Dummy

Dummy

1=DMI 8X

0=DMI 4X

R124 2.2K

4

Dummy

R0402+/-5%

CFG[18..20] internal pulldown

R116 1K

CFG187

R122 1K

CFG197

R125 1K

CFG207

3

R0603+/-1%

CPU_VTT=1.05V

R0603+/-1%

CPU_VTT=1.05V

R0603+/-1%

Dummy

Dummy

+2.5V

+2.5V

+2.5V

CFG67

R117 2.2K

Dummy

R0402+/-5%

DDR

TECHNOLOGY COPR.

Title

Alviso MCH-2

Document Number Re v

2

Date: Sheet

S04 MAINBOARD

1

840Monday, June 14, 2004

A

of

Page 9

5

hocnghetructuyen.vn

AA29

W29

V29

U29

P29

L29

H29

G29

F29

E29

D29

A29

AC28

AB28

AA28

W28

E28

AN27

AL27

AJ27

AG27

AF27

AB27

AA27

W27

G27

E27

AN24

B27

J26

G26

E26

A26

AL24

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS266

VSS261

VSS262

VSS263

VSS264

VSS265

VSS267

D D

AG29

AD29

VSS102

AJ29

VSS100

VSS101

AM29

VSS99

C30

VSS98

Y30

VSS97

AA30

4

AB30

VSS95

VSS96

AC30

VSS94

AE30

VSS93

AP30

VSS92

D31

VSS91

E31

VSS90

F31

VSS89

G31

VSS88

H31

VSS87

J31

VSS86

K31

VSS85

L31

VSS84

M31

VSS83

N31

VSS82

P31

VSS81

R31

VSS80

T31

VSS79

U31

VSS78

V31

VSS77

W31

VSS76

AD31

VSS75

AG31

VSS74

AL31

VSS73

A32

VSS72

C32

VSS71

Y32

VSS70

AA32

VSS69

AB32

VSS68

AC32

VSS67

3

AD32

VSS66

AJ32

VSS65

AN32

VSS64

D33

VSS63

E33

VSS62

F33

VSS61

G33

VSS60

H33

VSS59

J33

VSS58

K33

VSS57

L33

VSS56

M33

VSS55

N33

VSS54

P33

VSS53

R33

VSS52

T33

VSS51

U33

VSS50

V33

VSS49

W33

VSS48

AD33

VSS47

AF33

VSS46

AL33

VSS45

C34

VSS44

AA34

VSS43

AB34

VSS42

AC34

VSS41

AD34

VSS40

AH34

VSS39

AN34

VSS38

2

B35

VSS37

D35

VSS36

E35

VSS35

F35

VSS34

G35

VSS33

H35

VSS32

J35

VSS31

K35

L35

VSS29

VSS30

M35

N35

VSS27

VSS28

P35

VSS26

R35

VSS25

T35

VSS24

U35

VSS23

V35

VSS22

W35

VSS21

Y35

VSS20

AE35

VSS19

C36

VSS18

AA36

VSS17

AB36

VSS16

AC36

VSS15

AD36

VSS14

AE36

VSS13

AF36

VSS12

AJ36

VSS11

AL36

VSS10

AN36

VSS9

E37

VSS8

H37

1

VSS7

K37

VSS6

M37

VSS5

P37

VSS4

T37

VSS3

V37

VSS2

Y37

VSS1

AG37

VSS0

U4E

ALVISO_90

VSS

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208V9VSS209

VSS210K9VSS211H9VSS212A9VSS213

VSS214Y8VSS215P8VSS216L8VSS217E8VSS218

VSS219

VSS220

VSS221

VSS222

VSS223V7VSS224G7VSS225

VSS226

VSS227

VSS228

VSS229T6VSS230P6VSS231L6VSS232J6VSS233B6VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242P4VSS243L4VSS244H4VSS245C4VSS246

VSS247

VSS248

VSS249

VSS250

VSS251A3VSS252

VSS253

VSS254

VSS255

VSS256

VSS257V2VSS258T2VSS259P2VSS260

VSS268J2VSS269

VSS270D2VSS271

VSSALVDS

L2

Y1

G2

B36

C C

AD2

C3

AN2

AJ3

AB3

AA3

AC3

AL2

AE2

AH2

E5

Y4

U4

W5

AL5

AF4

AP5

AN4

AJ6

AE6

AA6

AC6

C8

AK7

AA7

AN7

AG7

T9

AL8

L10

F11

Y11

Y10

H11

D10

AE9

AA9

AN9

AH9

AC9

AA10

AA11

AF11

AG11

AJ11

AL11

AN11

J14

J12

F14

K14

B14

A14

B12

D12

AG14

AJ14

AL14

AN14

K16

A16

K15

C17

H16

D16

C15

AL16

G17

AJ17

AF17

AN17

J19

T19

B18

A18

H19

C19

U18

AL18

W19

AG19

AN19

A20

D20

VDIMM

F20

V20

E20

C21

G20

AK20

J22

F21

E22

A22

D22

AF21

AH22

AN21

AL22

J24

F24

B24

D24

H23

AF23

AG24

AJ24

Y14

B B

VSS_NCTF15

VSS_NCTF16

VSS_NCTF17

VSS_NCTF18

VSS_NCTF19

VSS_NCTF20

VSS_NCTF21

VSS_NCTF22

VSS_NCTF23

VSS_NCTF24

VSS_NCTF25

VSS_NCTF26

VSS_NCTF27

VSS_NCTF28

VSS_NCTF29

VSS_NCTF30

VSS_NCTF31

VSS_NCTF32

VSS_NCTF33

VSS_NCTF34

VSS_NCTF35

VSS_NCTF36

VSS_NCTF37

VSS_NCTF38

VSS_NCTF39

VSS_NCTF40

VSS_NCTF41

VSS_NCTF42

VSS_NCTF43

VSS_NCTF44

VSS_NCTF45

VSS_NCTF46

VSS_NCTF47

VSS_NCTF48

VSS_NCTF49

VSS_NCTF50

VSS_NCTF51

VSS_NCTF52

VSS_NCTF53

VSS_NCTF54

VSS_NCTF56

VSS_NCTF57

VSS_NCTF58

VSS_NCTF59

VSS_NCTF60

VSS_NCTF61

VSS_NCTF62

VSS_NCTF63

VSS_NCTF64

VSS_NCTF65

VSS_NCTF66

VSS_NCTF67

VSS_NCTF68

VSS_NCTF55

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VSS_NCTF13

VSS_NCTF14

AA24

Y24

AB23

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

AA25

Y25

AB24

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

AB26

AA26

Y26

AB25

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF0

AB12

VCCSM_NCTF31

AC14

AD13

AC13

AB13

AD12

AC12

VCCSM_NCTF26

VCCSM_NCTF27

VCCSM_NCTF28

VCCSM_NCTF29

VCCSM_NCTF30

AD14

VCCSM_NCTF24

VCCSM_NCTF25

AD17

AC17

AD16

AC16

AD15

AC15

VCCSM_NCTF19

VCCSM_NCTF20

VCCSM_NCTF21

VCCSM_NCTF22

VCCSM_NCTF23

AC18

VCCSM_NCTF17

VCCSM_NCTF18

AC21

AD20

AC20

AD19

AC19

AD18

VCCSM_NCTF12

VCCSM_NCTF13

VCCSM_NCTF14

VCCSM_NCTF15

VCCSM_NCTF16

AD21

AD23

AC23

AD22

AC22

VCCSM_NCTF6

VCCSM_NCTF7

VCCSM_NCTF8

VCCSM_NCTF9

VCCSM_NCTF10

VCCSM_NCTF11

AC26

AD25

AC25

AD24

AC24

VCCSM_NCTF1

VCCSM_NCTF2

VCCSM_NCTF3

VCCSM_NCTF4

VCCSM_NCTF5

AD26

U4F

ALVISO_90

VCCSM_NCTF0

AA23

Y23

AB22

AA22

Y22

AB21

AA21

Y21

R21

AB20

AA20

AB19

AA19

AB18

AA18

AB17

AA17

Y17

R17

AB16

AA16

Y16

W16

V16

U16

T16

R16

P16

N16

M16

L16

AB15

AA15

Y15

W15

V15

U15

T15

R15

P15

N15

M15

L15

AB14

AA14

W14

V14

U14

T14

R14

P14

N14

M14

L14

AA13

Y13

AA12

Y12

NCTF

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

VCC_NCTF68

VCC_NTTF69

VCC_NCTF70

VCC_NCTF71

VCC_NCTF72

VCC_NCTF73

VCC_NCTF74

VCC_NCTF75

VCC_NCTF76

VCC_NCTF77

VCC_NCTF78

VTT_NCTF0

VTT_NCTF1

VTT_NCTF2

VTT_NCTF3

VTT_NCTF4

VTT_NCTF5

VTT_NCTF6

VTT_NCTF7

VTT_NCTF8

VTT_NCTF9

VTT_NCTF10

VTT_NCTF11

VTT_NCTF12

VTT_NCTF13

VTT_NCTF14

VTT_NCTF15

VTT_NCTF16

VTT_NCTF17

L12

N12

M12

+VCCP

A A

5

L13

W12

T13

V13

P13

U13

R13

N13

M13

T12

V12

P12

U12

R12

W13

L17

M17

L18

T17

V17

P17

N17

4

N18

U17

M18

W17

P19

Y18

P18

R19

N19

R18

M19

Y20

P20

Y19

R20

N20

M21

M20

L21

L20

L19

L22

T21

V21

P21

N21

N22

U21

M22

W21

3

L23

T22

V22

P22

R22

N23

U22

M23

W22

L24

T23

V23

P23

R23

N24

U23

M24

W23

L25

T24

V24

P24

R24

N25

U24

M25

W24

2

L26

W25

T26

V26

P26

U26

R26

N26

M26

W26

VCORE_GMCH

T25

V25

P25

U25

R25

TECHNOLOGY COPR.

Title

Alviso MCH-3

Document Number Re v

Date: Sheet

S04 MAINBOARD

1

940Monday, June 14, 2004

A

of

Page 10

5

hocnghetructuyen.vn

BC85

BC84

0.22uF

0.22uF

C0603

C0603

D D

+VCCP

BC88

*

*

4.7uF

C1206

BC89

4.7uF

C1206

BC90

*

2.2uF

C0805

*

*

G1

BC86

0.47uF

*

C0603

BC87

0.47uF

*

C0603

4

VCORE_GMCH

R828 0 R0603+/-5% @M24

VTT23Y9VTT24W9VTT25U9VTT26R9VTT27P9VTT28N9VTT29M9VTT30L9VTT31J9VTT32N8VTT33M8VTT34N7VTT35M7VTT36N6VTT37M6VTT38A6VTT39N5VTT40M5VTT41N4VTT42M4VTT43N3VTT44M3VTT45N2VTT46M2VTT47B2VTT48V1VTT49N1VTT50M1VTT51

R127 0 R0603+/-5% @M24

U10

T10

R10

P10

N10

M10

K10

J10

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

V10

VTT14

W10

VTT13

K11

VTT12

L11

VTT11

GMCH_VCC_SYNC

M11

R11

P11

N11

VTT7

VTT8

VTT9

VTT10

T11

VTT6

U11

VTT5

VCCA_CRTDAC

J13

K12

W11

V11

VTT1

VTT2

VTT3

VTT4

K13

VTT0

VCCH_MPLL+VCCP

H20

G19

VCC_SYNC

VSSA_CRTDAC

3

VCCH_HPLL

VCCH_DPLLB

AA1

AA2

F19

E19

C35

VCCA_HPLL

VCCA_MPLL

VCCA_CRTDAC0

VCCA_CRTDAC1

VCCH_DPLLA

+1.5V

AC2

AC1

B23

VCCA_DPLLA

VCCA_DPLLB

VCCH_MPLL1

VCCH_MPLL0

K17

VCC48

K18

VCC47

T18

VCC46

V18

VCC45

W18

VCC44

K19

VCC43

U19

VCC42

V19

VCC41

K20

VCC40

T20

VCC39

U20

VCC38

W20

VCC37

K21

VCC36

K22

VCC35

K23

VCORE_GMCH

H26

K25

J25

K24

VCC30

VCC31

VCC32

VCC33

VCC34

K26

VCC29

2

H27

VCC28

J27

VCC27

K27

VCC26

L27

VCC25

M27

VCC24

N27

VCC23

R27

P27

VCC22

T27

VCC20

VCC21

U27

VCC19

V27

VCC18

VCORE_GMCH

BC78

*

0.1uF

C0402

K28

J28

H28

G28

VCC14

VCC15

VCC16

VCC17

R126 0 R1206+/-5%

*

R28

P28

N28

M28

L28

VCC9

VCC10

VCC11

VCC12

VCC13

BC79

0.1uF

C0402

U28

T28

VCC8

V28

VCC7

VCC6

*

J29

K29

VCC5

BC80

0.1uF

C0402

M29

VCC4

N29

VCC3

R29

VCC2

*

T29

VCC1

1

BC81

10uF

C0805

U4G

ALVISO_90

VCC0

+VCCP

BC82

10uF

C0805

BC83

*

10uF

C0805

*

POWER

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCA_TVBG

VSSA_TVBG

VCCD_TVDAC

VCCDQ_TVDAC

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCA_LVDS

VCCHV0

VCCHV1

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCCA_SM0

VCCA_SM1

VCCA_SM2

VCCA_SM3

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL0

VCCA_3GPLL1

VCCA_3GPLL2

VCCA_3GBG

VSSA_3GBG

C C

BC91

0.1uF

C0402

F37

G37

+2.5V

*

J37

L37

Y29

Y28

Y27

VCCA_3GPLL VC CA_3G VCCA_SM +2.5V

U37

R37

N37

W37

AE37

AF18

AF19

AP19

AF20

A28

A27

H17

D19

BC100

10nF

C0402

E18

H18

G18

VCCA_TVBG

VCCD_TVDAC

VCCDQ_TVDAC

+2.5V

BC101

*

0.1uF

C0402

D18

C18

TVDACB

TVDACC

R128

0 R0603+/-5% @M24

TVDACA

R129 0 R0603+/-5% @M24

R130 0 R0603+/-5% @M24

R131 0 R0603+/-5% @M24

R133 0 R0603+/-5% @M24

R134 0 R0603+/-5% @M24

BC102

*

10uF

C0805

+1.5V

BC103

*

0.1uF

C0402

B28

AB9

AP8

AE1

AM1

AB11

AB10

BC96

BC95

*

*

0.1uF

0.1uF

C0402

C0402

AC11

AD11

AE12

AF12

*

AG12

AH12

BC97

0.1uF

C0402

AJ12

AK12

AL12

AM12

AN12

AP12

VDIMM

AE13

AF13

AG13

AH13

AJ13

AK13

AL13

AM13

AN13

AP13

AE14

AE15

AE16

AE17

AE18

AE19

AE20

AE21

*

AE22

AE23

BC92

0.1uF

C0402

AE24

AE25

AF25

AG25

AH25

AJ25

*

AK25

AL25

AM25

BC93

0.1uF

C0402

AN25

AP25

AE26

AF26

AG26

*

AH26

AJ26

AK26

BC94

0.1uF

C0402

AL26

AM26

AN26

AP26

AC27

AD27

AD28

AP29

BC98

0.1uF

C0402

AH37

AM37

A21

+2.5V

BC99

*

*

10uF

C0805

*

B26

B25

A25

A35

B22

B21

F17

F18

E17

L1 L0805 1uH

EC5

220uF

2.5V, +/-20%

CTX

4

*

L3 L1211 82nH

*

1A

L5 L0805 1uH

*

L6 L0805 1uH

*

L7 L0805 1uH

*

FB45

FB L0805 180 Ohm

@GM

VDIMM

BC104 0.1uF C0402

B B

BC105 0.1uF C0402

BC108 0.1uF C0402

BC111 0.1uF C0402

BC112 0.1uF C0402

BC113 0.1uF C0402

BC117 10uF C0805

BC120 10uF C0805

A A

BC130

*

0.1uF

C0402

*

*

*

*

*

*

VCCA_3GPLL

*

*

VCCH_MPLL

+2.5V

BC132

BC131

*

*

4.7uF

C1206

0.1uF

C0402

5

BC106

*

0.1uF

C0402

BC114

*

10uF

C0805

BC123

*

10uF

C0805

BC129

*

0.1uF

C0402

BC133

*

0.1uF

C0402

BC732

*

0.1uF

C0402

@GM

EC3

220uF

*

2.5V, +/-20%

CTX

BC115

10uF

C0805

*

*

*

*

BC124

0.1uF

C0402

EC8

470uF

2.5V, +/-20%

CTX

EC9

470uF

2.5V, +/-20%

CTX

*

BC733

22pF

*

C0402

@GM

+1.5VVCCA_SM

+1.5VVC CA_3G

+1.5V

+1.5VVCCH_HPLL

+1.5V

21

+2.5VVCCA_CRTDAC

VCCH_DPLLB

TVDACA

TVDACB

TVDACC

BC107

*

0.1uF

C0402

BC116

*

0.1uF

C0402

BC122

22pF

BC121

*

*

C0402

0.1uF

@GM

C0402

@GM

BC128

22pF

BC127

*

*

*

3

0.1uF

C0402

@GM

BC134

0.1uF

C0402

@GM

C0402

@GM

BC135

22pF

*

C0402

@GM

*

*

EC4

470uF

2.5V, +/-20%

CTX

EC6

470uF

2.5V, +/-20%

CTX

L2 L0805 10uH

*

L4 L0805 10uH

*

21

FB4

FB L0805 180 Ohm

@GM

21

FB6

FB L0805 180 Ohm

@GM

21

FB7

FB L0805 180 Ohm

@GM

2

VCCA_TVBG

+1.5VVCCH_DPLLA

+1.5V

VCCD_TVDAC

+3V

+3V

+3V

VCCDQ_TVDAC

GMCH_VCC_SYNC

BC109

0.1uF

C0402

@GM

BC118

22pF

C0402

@GM

BC125

22pF

C0402

@GM

BC110

22pF

*

*

C0402

@GM

BC119

0.1uF

*

*

C0402

@GM

BC126

0.1uF

*

*

C0402

@GM

BC734

*

0.1uF

C0402

@GM

21

+3V

FB3

FB L0805 180 Ohm

@GM

21

+1.5V

FB46

FB L0805 180 Ohm

@GM

21

+1.5V

FB5

FB L0805 180 Ohm

@GM

21

+2.5V

FB47

FB L0805 180 Ohm

@GM

TECHNOLOGY COPR.

Title

Alviso MCH-4

Document Number Re v

Date: Sheet

S04 MAINBOARD

1

10 40Monday, June 14, 2004

A

of

Page 11

5

hocnghetructuyen.vn

4

3

2

1

PEG_RXN[0..15]

PEG_RXP[0..15]

PEG_TXN [0..15]

AB29

AC29

G21

H24

H25

A15

C16

A17

J18

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

PEG_TXP [0..15]

U4H

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CRTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

ALVISO_90

D D

+2.5V

TV_CHROMA21,24

TV_LUMA21,24

TV_COMP21,24

C C

B B

+2.5V

R162 2.2K R0 402+/-5% @GM

R164 2.2K R0 402+/-5% @GM

DDCCLK21,24

DDCDAT21,24

CRT_B21,24

CRT_G21,24

CRT_R21,24

CRTVS_VGA21,24

A A

CRTHS_VGA21,24

+2.5V

R165 0 R0402+/-5% @GM

R166 0 R0402+/-5% @GM

R167 0 R0402+/-5% @GM

R168 0 R0402+/-5% @GM

R170 0 R0402+/-5% @GM

R172 0 R0402+/-5% @GM

R173 0 R0402+/-5% @GM

R174 0 R0402+/-5% @GM

R176 0 R0402+/-5% @GM

R178 0 R0402+/-5% @GM

R179 255 R0402+/-1% @GM

R181 100K R0402+/-5% @GM

R183 100K R0402+/-5% @GM

R184 2.2K R 0402+/-5% @GM

R185 2.2K R 0402+/-5% @GM

R186 2.2K R 0402+/-5% @GM

R188 2.2K R 0402+/-5% @GM

R191 1.5K R 0402+/-5% @GM

5

DDCCLK

DDCDAT

R144 0 R0402+/-5% @GM

R145 0 R0402+/-5% @GM

R146 0 R0402+/-5% @GM

R147 5.6K R 0402+/-5% @GM

5K+/-0.5%

VCORE_GMCH

GMCH_VGA_DDCCLK

GMCH_VGA_DDCDATA

GMCH_VG A_BLUE

GMCH_VGA_BLUEJ

GMCH_VGA_GREEN

GMCH_VGA_GREENJ

GMCH_VGA_RED

GMCH_VGA_RED J

GMCH_VGA_VSYNC

GMCH_VGA_HSYNC

GMCH_VG A_REFSET

VGA_BLON

DISP_ON

GMCH_LC TLA_CLK

GMCH_LCTLB_DATA

EDIDCLK

EDIDDATA

GMCH_LIBG

4

R148

0

+/-5%

R0402

@M24

R152 0 R0402+/-5% @M24

R153 0 R0402+/-5% @M24

R154 0 R0402+/-5% @M24

R155 0 R0402+/-5% @M24

R156 0 R0402+/-5% @M24

R157 0 R0402+/-5% @M24

R158 0 R0402+/-5% @M24

R159 0 R0402+/-5% @M24

R160 1K R0402+/-1% @M24

R161 1K R0402+/-1% @M24

R163 0 R0402+/-5% @M24

VGA_BLON21,25

DISP_ON21,25

EDIDCLK21,25

EDIDDATA21,25

TXLCLKOUT-21,25

TXLCLKOUT+21,25

TXLOUT0-21,25

TXLOUT1-21,25

TXLOUT2-21,25

TXLOUT0+21,25

TXLOUT1+21,25

TXLOUT2+21,25

R169 0 R0402+/-5% @GM

R171 0 R0402+/-5% @GM

R175 0 R0402+/-5% @GM

R177 0 R0402+/-5% @GM

R180 0 R0402+/-5% @GM

R182 0 R0402+/-5% @GM

R187 0 R0402+/-5% @GM

R189 0 R0402+/-5% @GM

R190 0 R0402+/-5% @GM

R192 0 R0402+/-5% @GM

R193 0 R0402+/-5% @GM

R194 0 R0402+/-5% @GM

HW strap, 0= No SDVO device

R956 3.6K R0402+/-5%

CLK_PCIE_MCHJ4

CLK_PCIE_MCH4

R149

0

+/-5%

R0402

@M24

Dummy

R150

0

+/-5%

R0402

@M24

GMCH_VGA_DDCCLK

GMCH_VGA_DDCDATA

GMCH_VG A_BLUE

GMCH_VGA_BLUEJ

GMCH_VGA_GREEN

GMCH_VGA_GREENJ

GMCH_VGA_RED

GMCH_VGA_RED J

GMCH_VGA_VSYNC

GMCH_VGA_HSYNC

GMCH_VG A_REFSET

GMCH_VG A_BLON

GMCH_DISP_ON

GMCH_LC TLA_CLK

GMCH_LCTLB_DATA

GMCH_EDIDCLK

GMCH_EDIDDATA

GMCH_LIBG

GMCH_TXLCLKOUTGMCH_TXLCLKOUT+

GMCH_TXLOUT0GMCH_TXLOUT1GMCH_TXLOUT2-

GMCH_TXLOUT0+

GMCH_TXLOUT1+

GMCH_TXLOUT2+

GMCH_T V_CHROMA

GMCH_TV_COMP

GMCH_TV_REFSET

R151

0

+/-5%

R0402

@M24

3

MISCVGALVDS TV

PEG_RXN[0..15] 21

PEG_RXP[0..15] 21

PEG_TXN [0..15] 21

PEG_TXP[0..15] 21

EXP_COMPI

EXP_ICOMPO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6