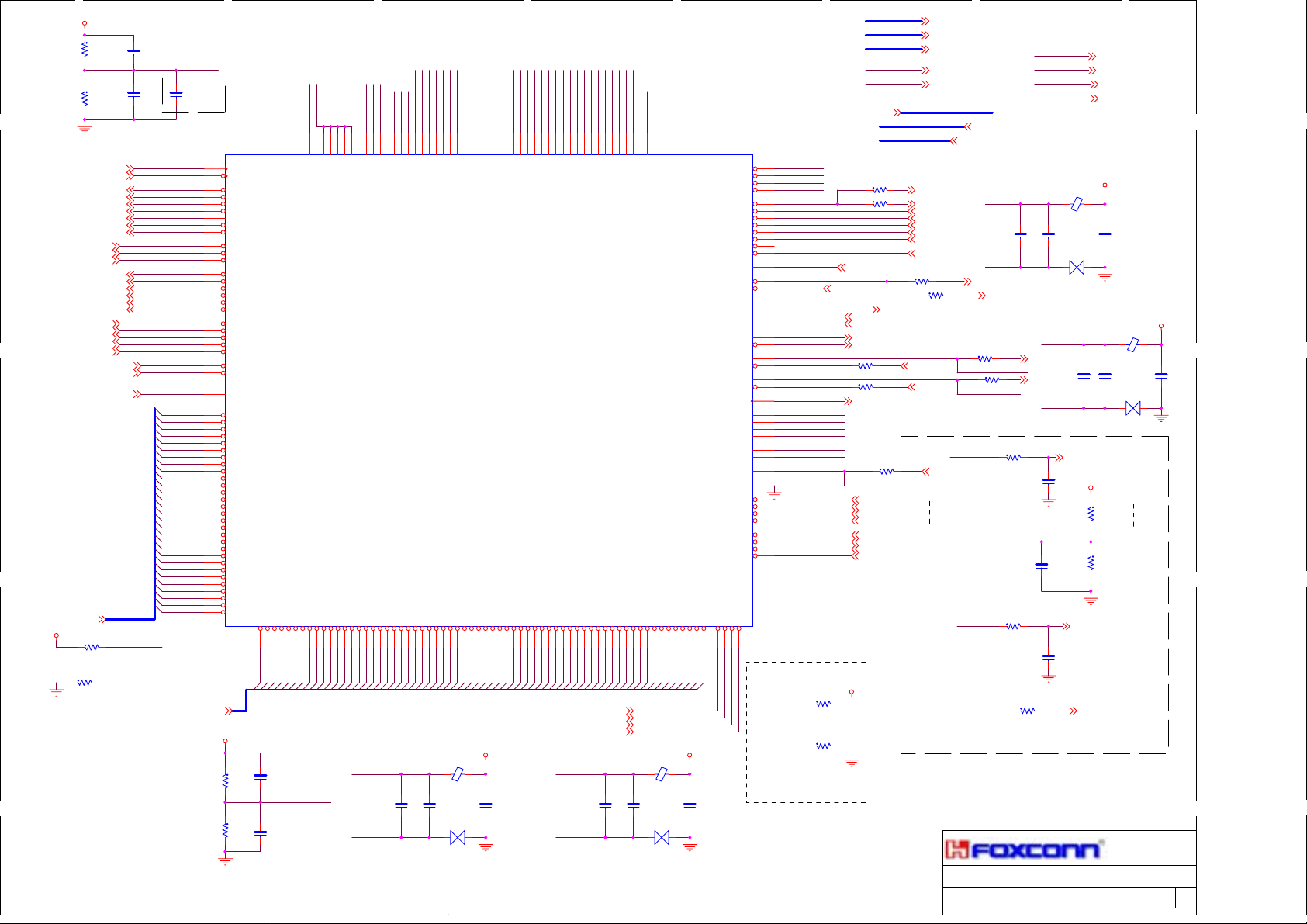

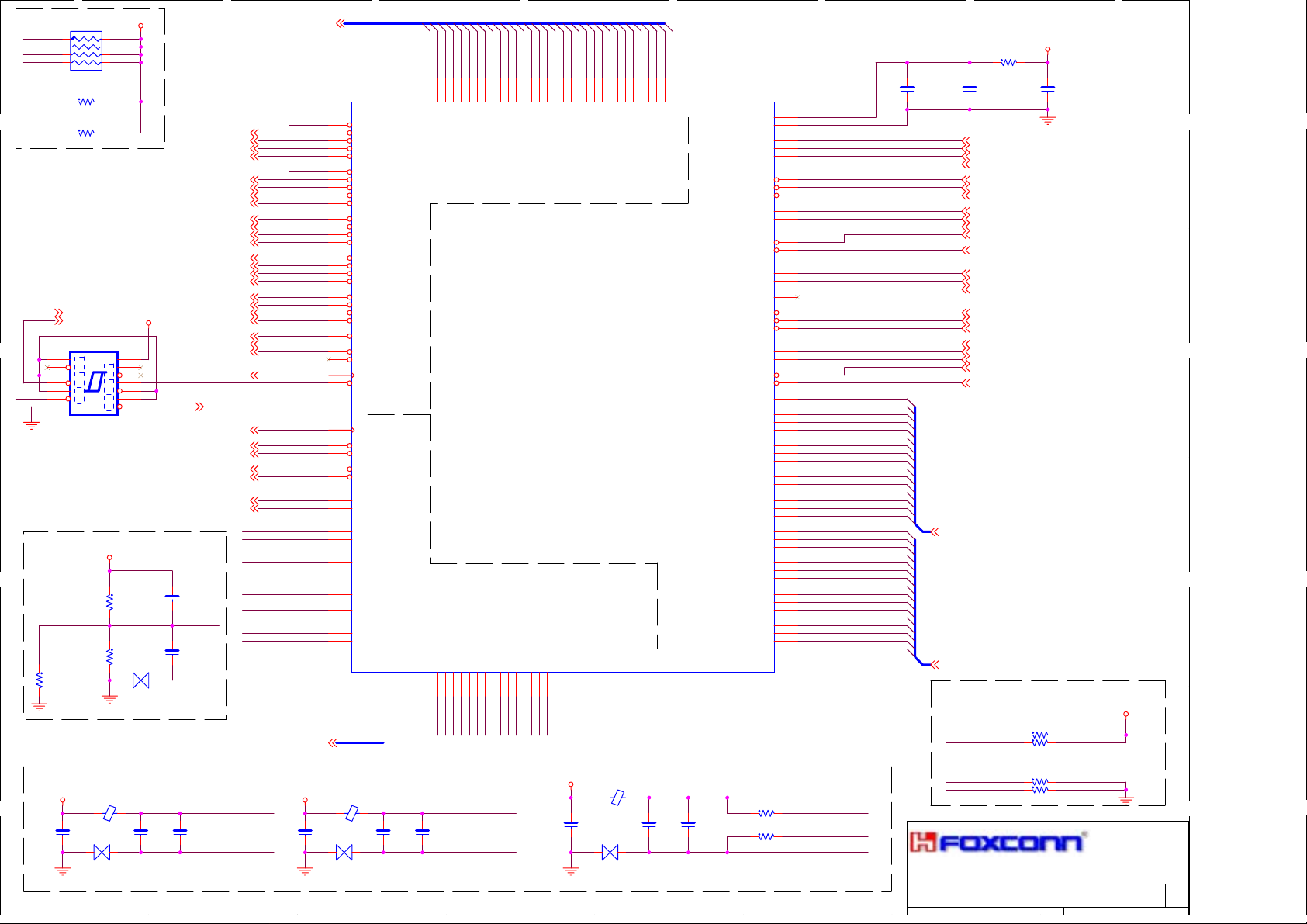

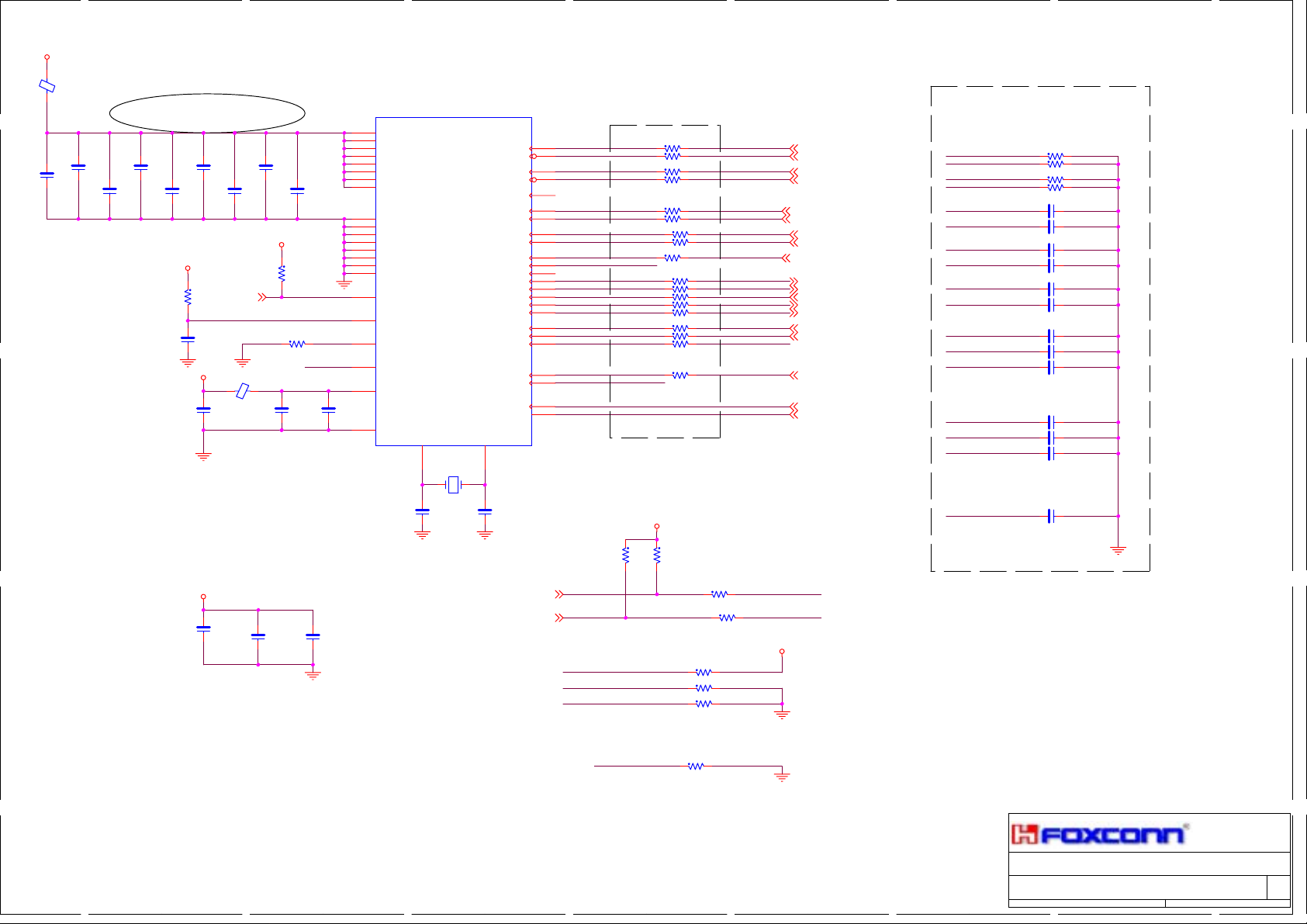

Page 1

8 7 6 5 4 3 2 1

A

www.hocnghetructuyen.vn

+3V

D D

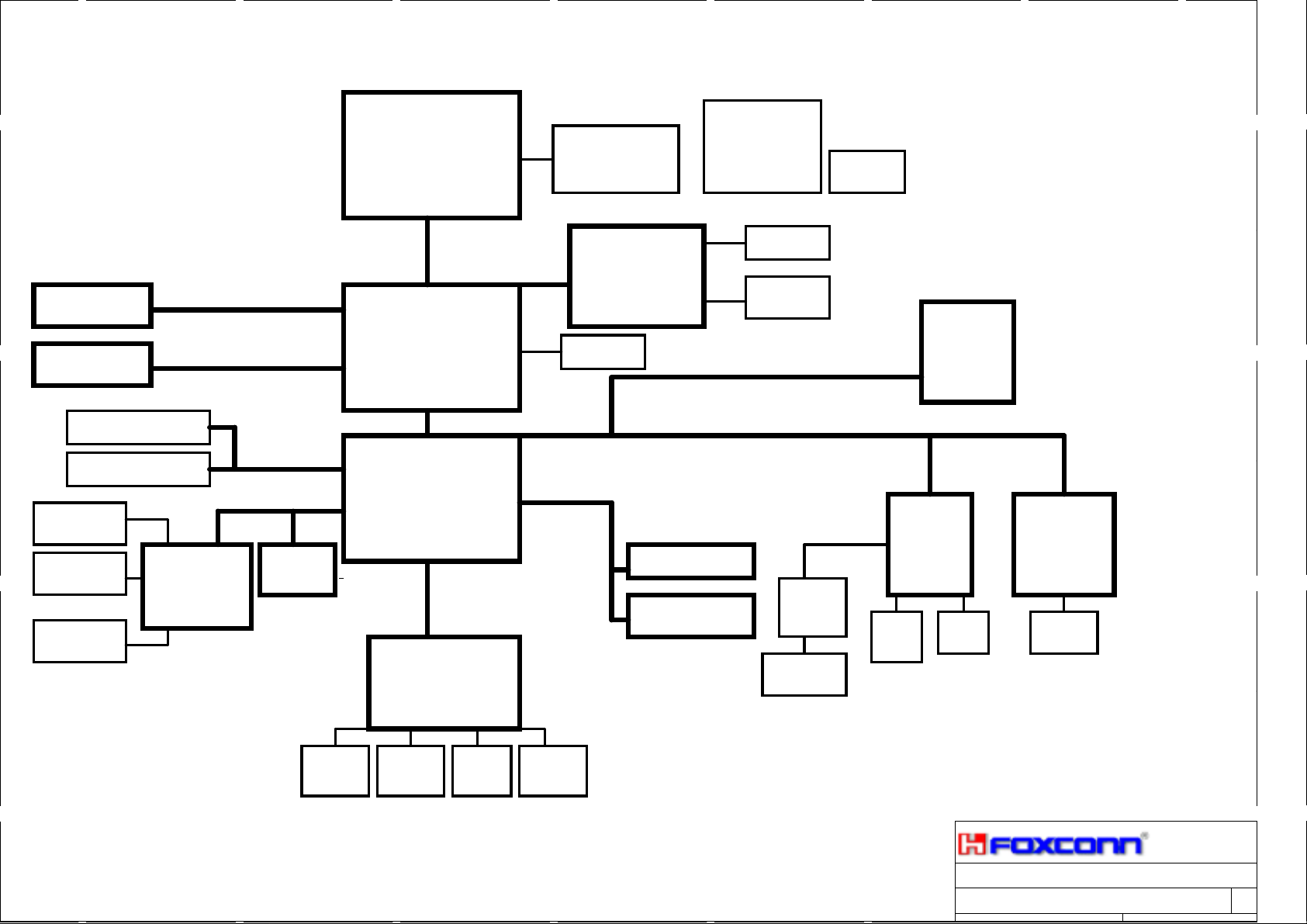

Dothan

478 Pins

(Micro-FCPGA)

CPU Thermal

Sensor

Clocks

ICS952005

Buffer

ICS93705

Host Bus

400MHZ

VTT_MEM

VDIMM

DDR-SODIMM1

DDR SDRAM 2.5V, 333/400MHz

533MHZ

SiSM661FX

C C

DDR-SODIMM2

Primary IDE - HDD

Master

DVD/CDRW/CD/COMBO

Slave

DDR SDRAM 2.5V, 333/400MHz

ATA 133/100

SiS963

AC-LINK

AGP

R.G,B

33MHZ, 3.3V PCI

USB 2.0

VCORE_VGA

Video Controller

SIS302LV

CRT port

33MHZ, 3.3V PCIMuTIOL.1G

Headphone

USB PORT -->2,6

External

B B

MIC

AUDIO

ALC202A(Codec)

TPA0312(Amp)

MDC

USB --> 1,3

Internal

MIC

+5V

+3V

+3VALW

VCCRTC

PC87591

176 Pins LQFP

LVDS

S-VIDEO

LCD Panel

CardReader

SD&MMC&MS

Slot

CardBus

CB810

CARD

BUS

SLOT

MINI-PCI

1394

CONN

LAN

10/100 Mbps

RTL8100C

RJ45

FLASH FAN 1Touchpad Keyboard

A

Title

Document Number Re v

Date: Sheet

661S03

TECHNOLOGY COPR.

of

150Friday, August 13, 2004

A

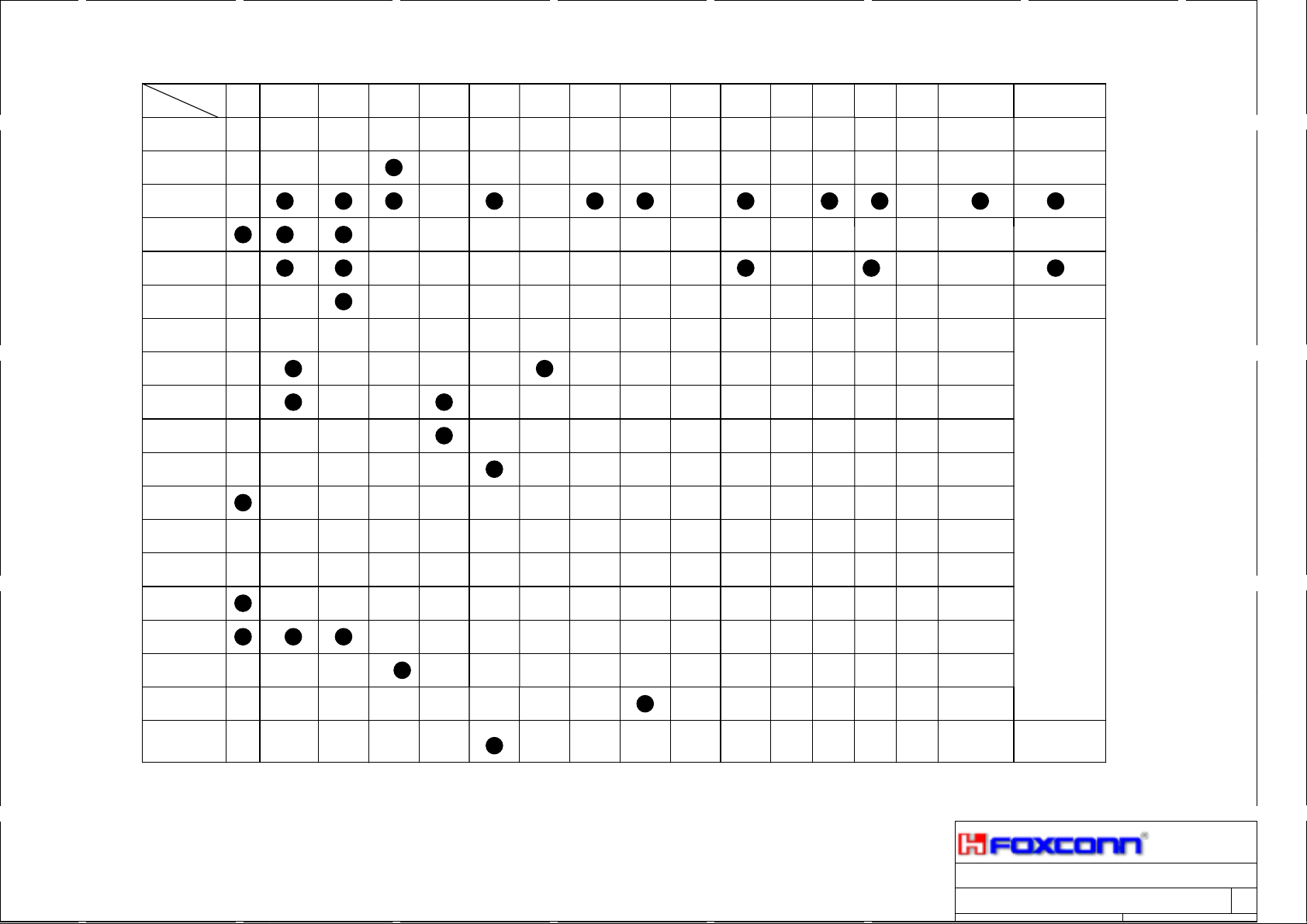

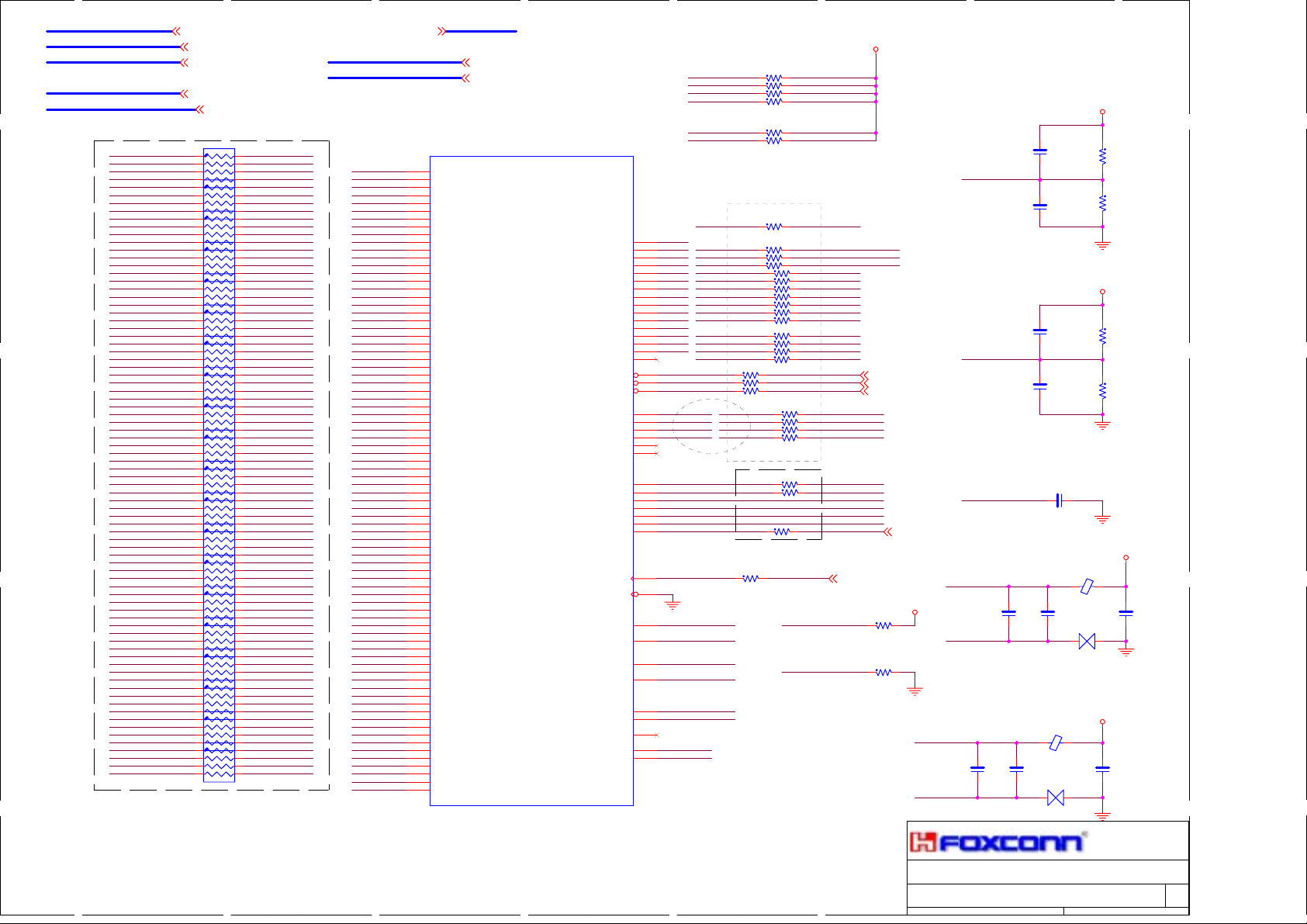

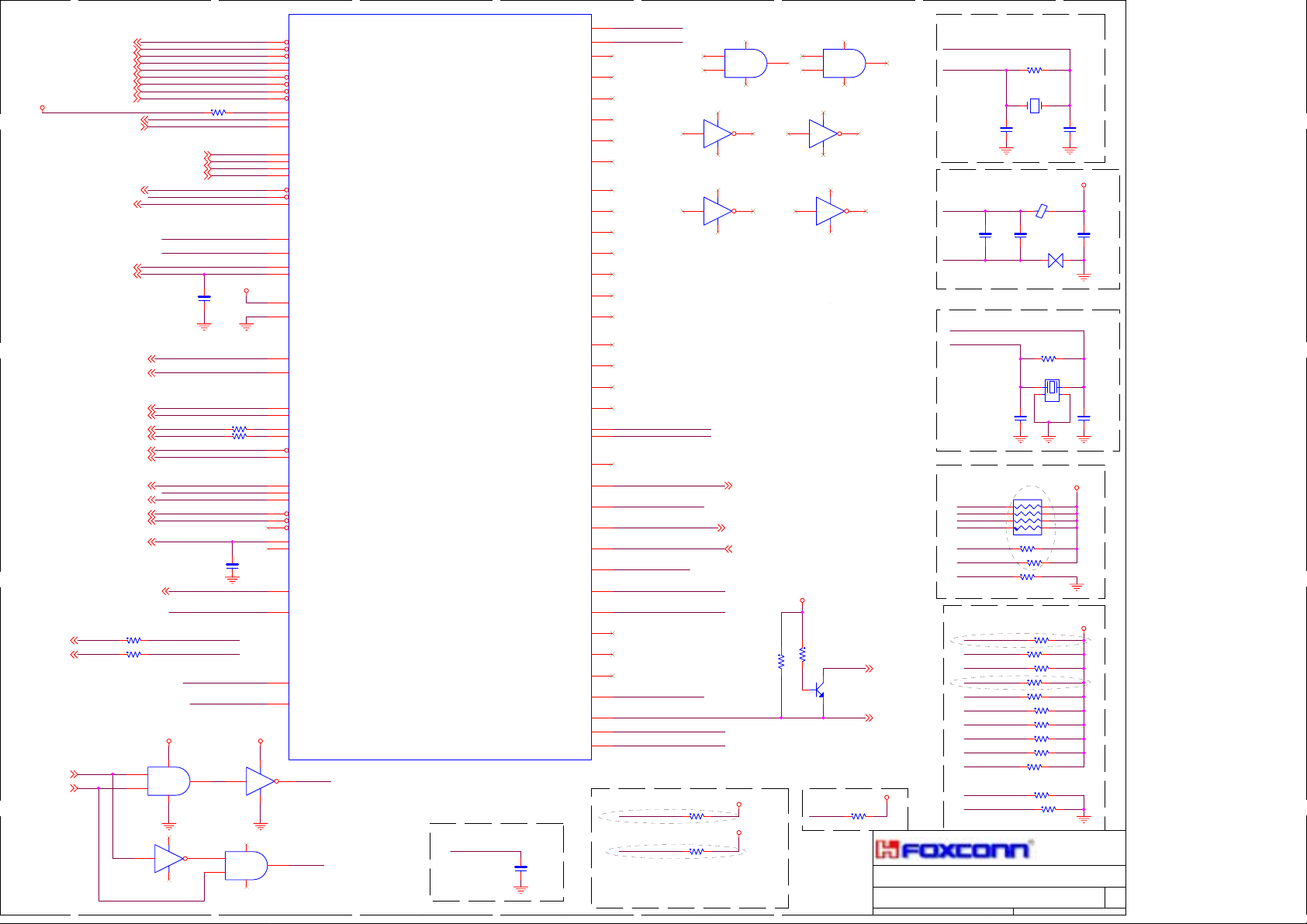

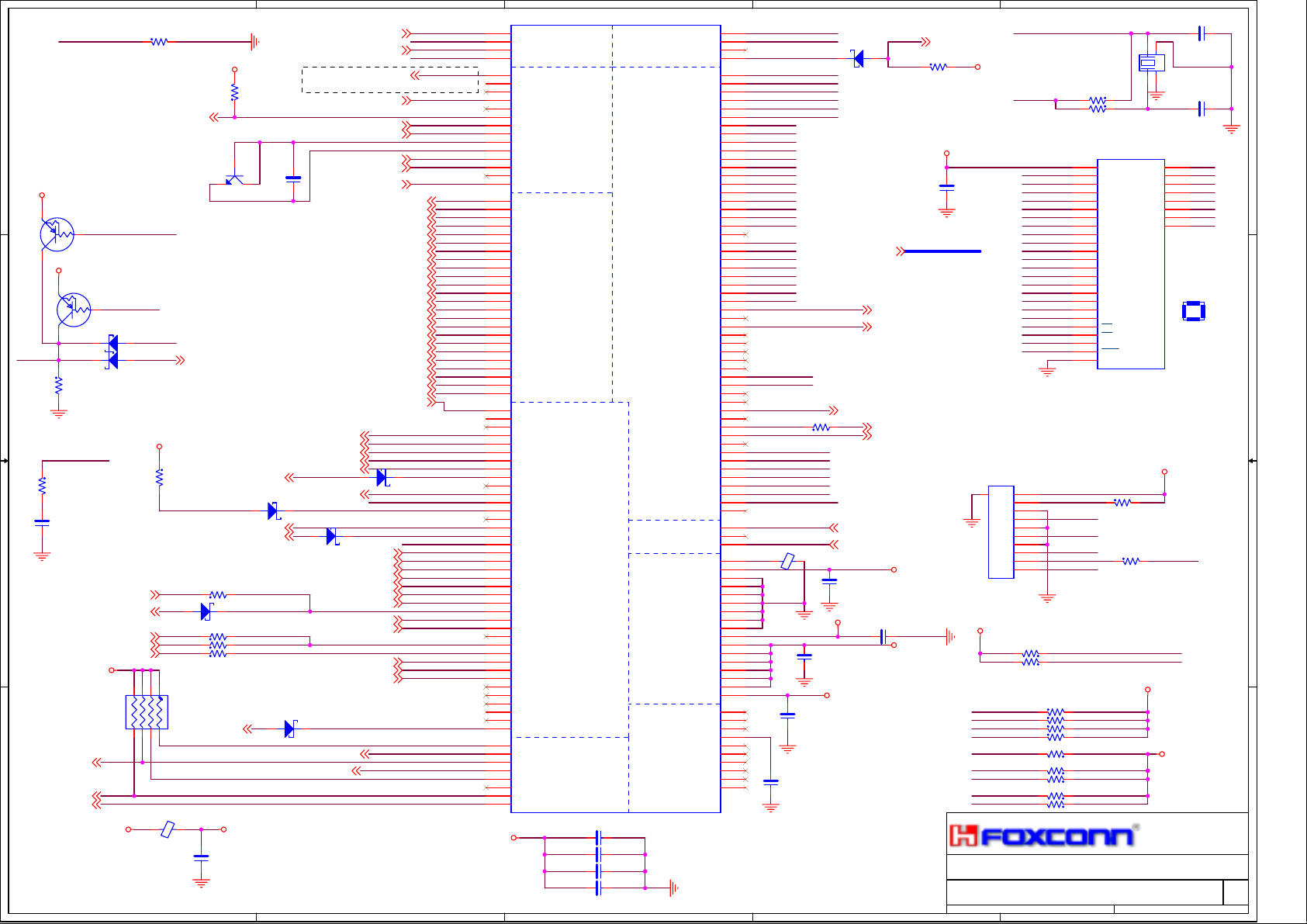

Page 2

8 7 6 5 4 3 2 1

A

www.hocnghetructuyen.vn

Device

M661FX

Rails MDC

CPU

963L

PC87591

DDR

M10

LCD302LV

MiniPCI

LAN

AUDIO cardbus

HDD

Buffer

CLK GEN.

D D

+1.5VSUS

+3VALW

+3v

+1.8V

3VAUX

+1.8VAUX

5VAUX

C C

VDDQ

VDIMM

DDR_VTT

+1.2V

+1.5V

+5VALW

+12V

B B

VCORE_CPU

VCCP

+5V

3VSUS

VCORE_VGA

TECHNOLOGY COPR.

of

250Friday, August 13, 2004

A

Title

Document Number Re v

Date: Sheet

Power Diagram

661S03

A

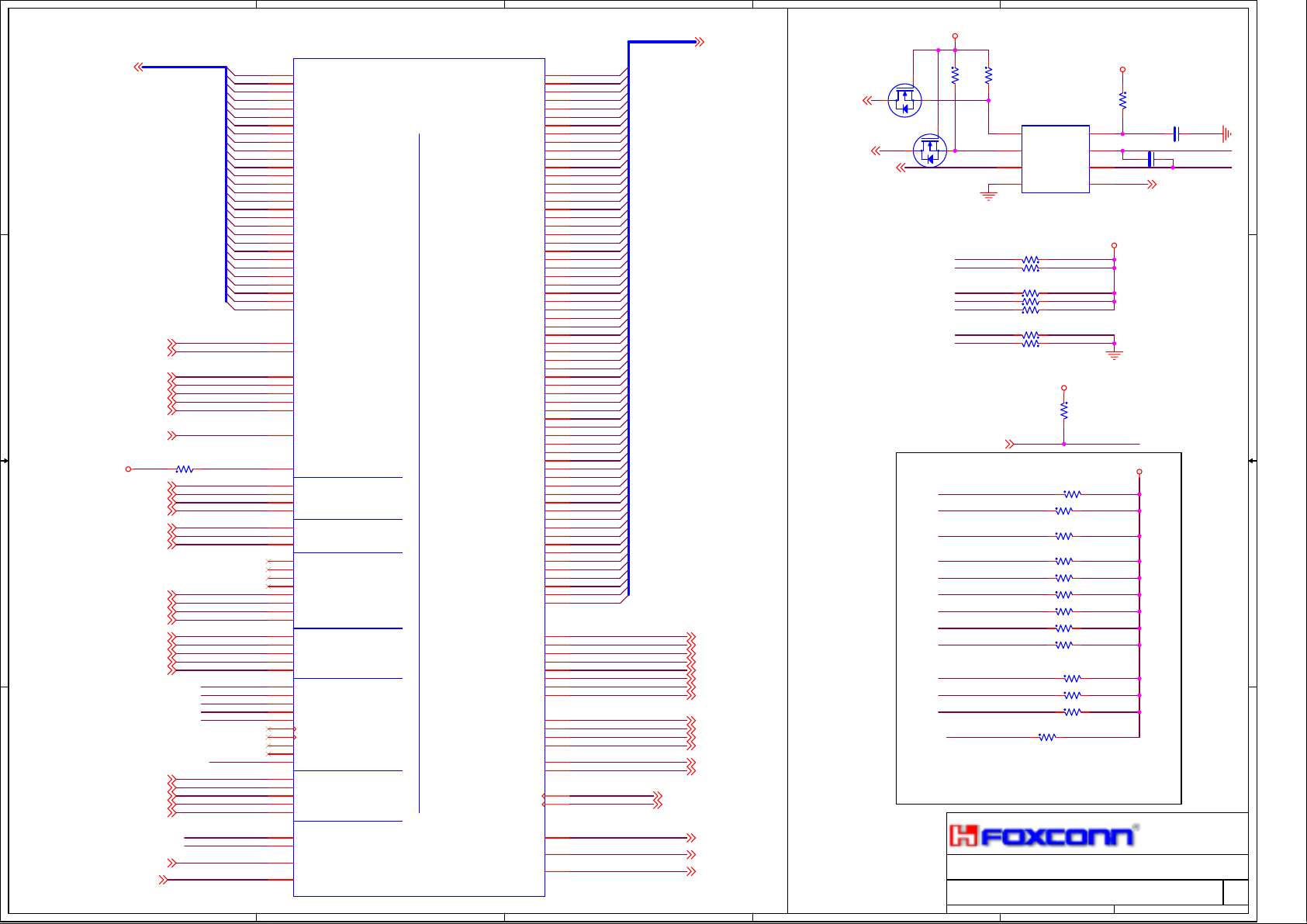

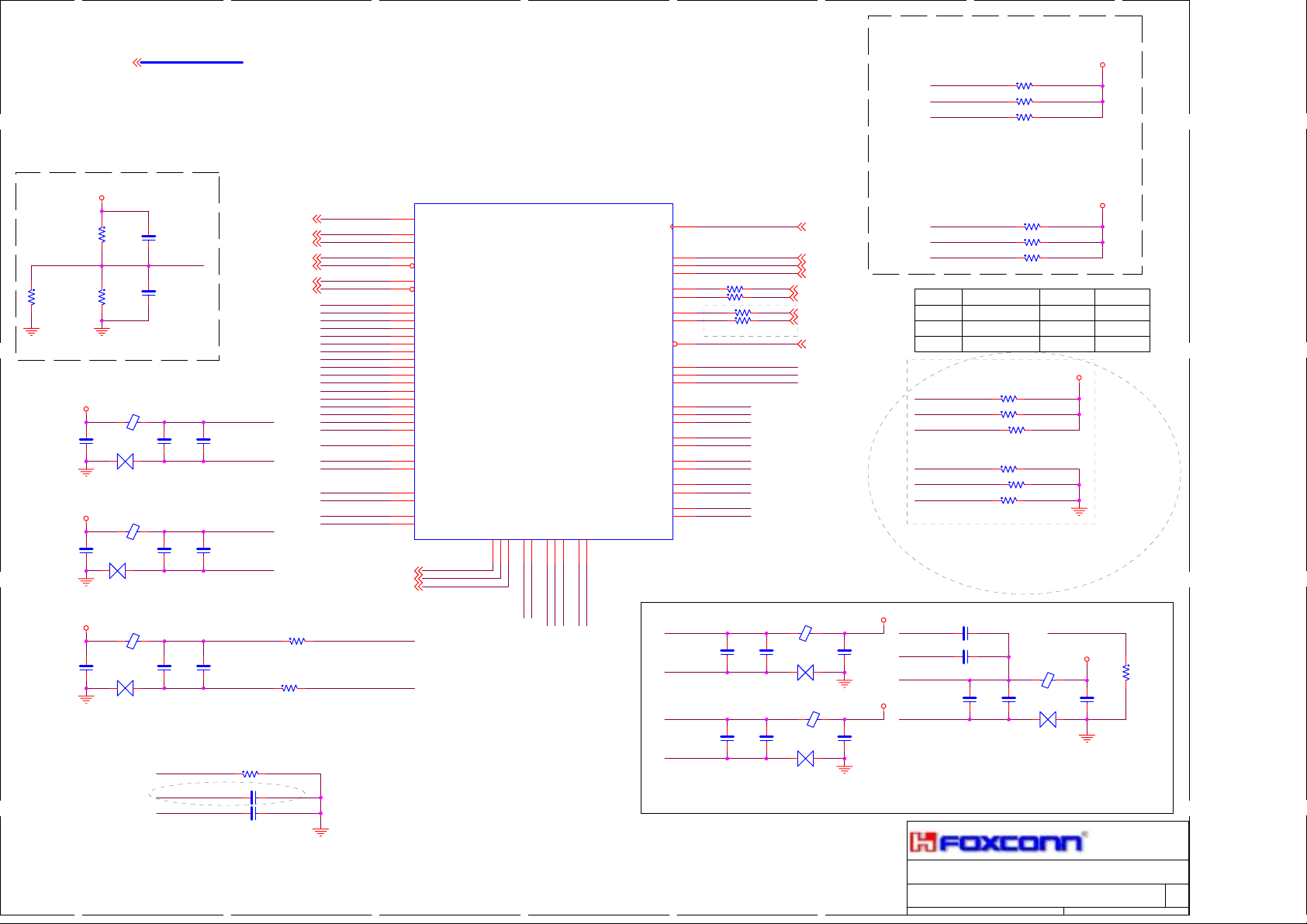

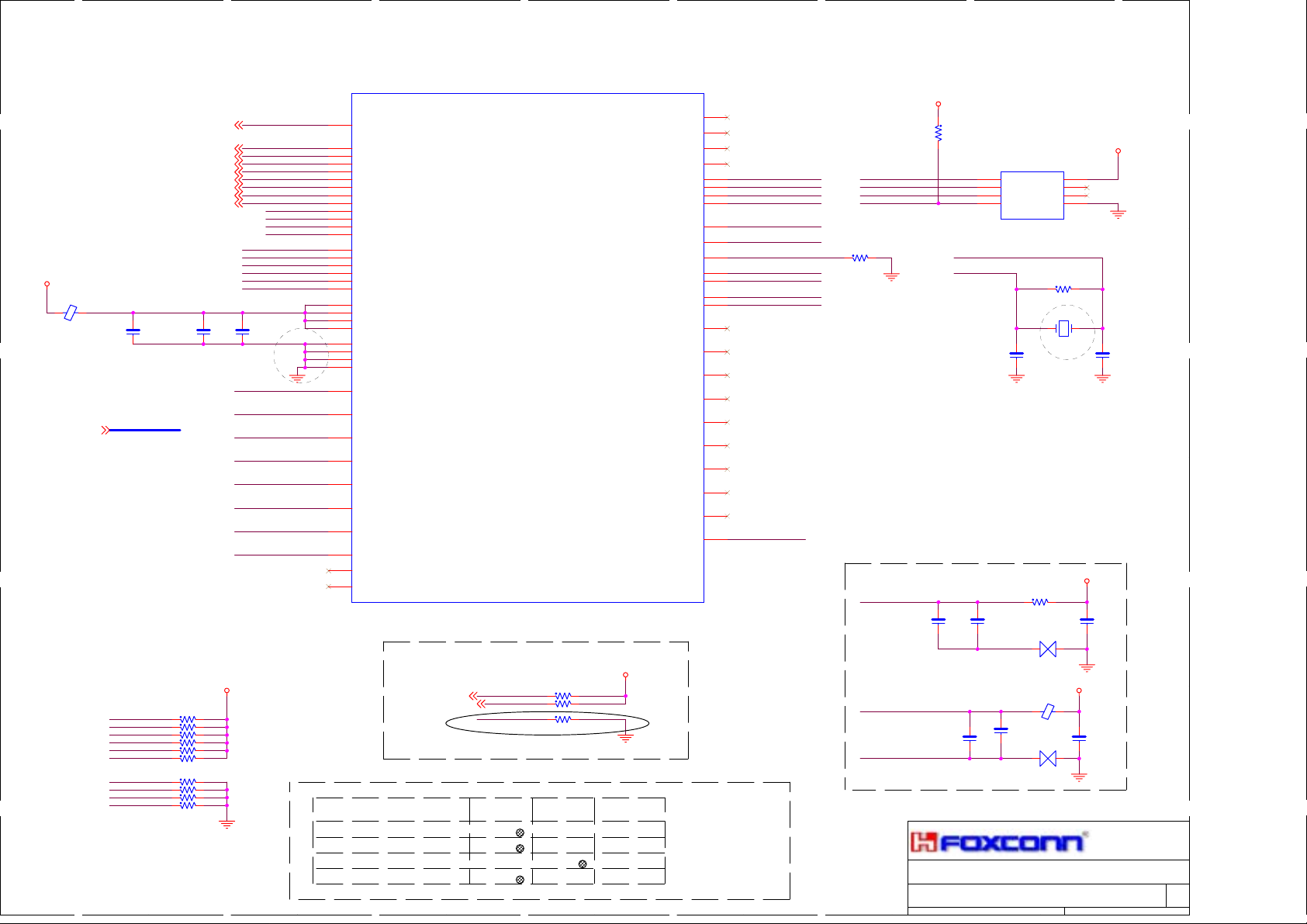

Page 3

5

www.hocnghetructuyen.vn

AA3

AA2

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

A13

A12

C12

C11

B13

A16

A15

B10

A10

B18

A18

C17

B17

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

Y3

U3

R2

P3

T2

P1

T1

N2

A4

N4

J3

L1

J2

K3

K4

L4

C8

B8

A9

C9

M3

H1

K1

L2

C2

D3

A3

E4

B4

A7

D1

D4

C6

A6

B7

U33A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB0#

ADSTB1#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADS#

IERR#

BR0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

BPM0#

BPM1#

BPM2#

BPM3#

TRDY#

RS0#

RS1#

RS2#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

TCK

TDO

TDI

TMS

TRST#

ITP_CLK0

ITP_CLK1

PREQ#

PRDY#

DBR#

LINT0

LINT1

STPCLK#

SLP#

DPSLP#

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

Banias-Processor

H_A20MJ10

H_FERRJ10

H_IGNNEJ10

CPUPWRGD5

H_SMIJ10

H_INTR10

H_NMI10

H_STPCLKJ10

H_CPUSLPJ10

H_DPSLPJ10,31

PM_THRMTRIPJ10

HAJ[3..31]

HADSTBJ05

HADSTBJ15

HREQJ05

HREQJ15

HREQJ25

HREQJ35

HREQJ45

ADSJ5

R508 56

+/-5% R0603

HBREQJ05

BPRIJ5

BNRJ5

HLOCKJ5

HITJ5

HITMJ5

DEFERJ5

HTRDYJ5

RSJ05

RSJ15

RSJ25

5

TCK_H

TDO_H

TDI_H

TMS_H

TRSTJ

THERMDA

THERMDC

PM_THRMTRIPJ

CPU_PROCHOTJ

HAJ3

HAJ4

HAJ5

HAJ6

HAJ7

HAJ8

HAJ9

HAJ10

HAJ11

HAJ12

HAJ13

HAJ14

HAJ15

HAJ16

HAJ17

HAJ18

HAJ19

HAJ20

HAJ21

HAJ22

HAJ23

HAJ24

HAJ25

HAJ26

HAJ27

HAJ28

HAJ29

HAJ30

HAJ31

DBRJ

HAJ[3..31]5

D D

C C

+VCCP

B B

A A

CPU_PROCHOTJ10

4

Dothan

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

4

1 OF 3

DATA

PHASE

SIGNALS

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN0#

DSTBP0#

DSTBN1#

DSTBP1#

DSTBN2#

DSTBP2#

DSTBN3#

DSTBP3#

DINV0#

DINV1#

DINV2#

DINV3#

DBSY#

DRDY#

BCLK1

BCLK0

INIT#

RESET#

DPWR#

A19

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

C23

C22

K24

L24

W25

W24

AE24

AE25

D25

J26

T24

AD20

M2

H2

B14

B15

B5

B11

C19

HDJ0

HDJ1

HDJ2

HDJ3

HDJ4

HDJ5

HDJ6

HDJ7

HDJ8

HDJ9

HDJ10

HDJ11

HDJ12

HDJ13

HDJ14

HDJ15

HDJ16

HDJ17

HDJ18

HDJ19

HDJ20

HDJ21

HDJ22

HDJ23

HDJ24

HDJ25

HDJ26

HDJ27

HDJ28

HDJ29

HDJ30

HDJ31

HDJ32

HDJ33

HDJ34

HDJ35

HDJ36

HDJ37

HDJ38

HDJ39

HDJ40

HDJ41

HDJ42

HDJ43

HDJ44

HDJ45

HDJ46

HDJ47H_IERRJ

HDJ48

HDJ49

HDJ50

HDJ51

HDJ52

HDJ53

HDJ54

HDJ55

HDJ56

HDJ57

HDJ58

HDJ59

HDJ60

HDJ61

HDJ62

HDJ63

3

HDJ[0..63]

H_CPURSTJ

3

HDJ[0..63] 5

HDSTBNJ0 5

HDSTBPJ0 5

HDSTBNJ1 5

HDSTBPJ1 5

HDSTBNJ2 5

HDSTBPJ2 5

HDSTBNJ3 5

HDSTBPJ3 5

HDBIJ0 5

HDBIJ1 5

HDBIJ2 5

HDBIJ3 5

DBSYJ 5

DRDYJ 5

CLK_CPU_BCLKJ 13

CLK_CPU_BCLK 13

H_INITJ 10

H_CPURSTJ 5

DPWRJ 5

2

+3V

R539

R540

8.2K

Q50

G

2N7002

D S

MBCLK15,39

Q51

2N7002

MBDATA15,39

TEMP_ALERTJ15

D S

8.2K

+/-5%

R0402

G

H_CPURSTJ

TDO_H

TMS_H

TDI_H

DBRJ

TCK_H

TRSTJ

H_PWRGD5

H_FERRJ

HBREQJ0

CPU_PROCHOTJ

PM_THRMTRIPJ

H_A20MJ

H_STPCLKJ

H_CPUSLPJ

H_SMIJ

H_INITJ

H_IGNNEJ

H_INTR

H_NMI

H_DPSLPJ

+/-5%

R0402

U34 MAX6648

8

7

6

5

R521 54.9+/-1% R0603

R524 54.9+/-1% R0603

R522 39.2+/-1% R0603

R523 150 +/-5% R0603

R517 150 +/-5% R0603

R527 27.4 +/-1% R0603

R525 680 +/-5% R0603

R532 56

R0603 +/-1%

R493 56

R0603 +/-1%

R507 56

R0603 +/-1%

R510 56

R0603 +/-1%

R516 62

R0603 +/-1%

VCC

SMCLK

DXP

SMDATA

DXN

-ALT

-OVT

GND

+VCCP

R498

200

+/-1%

R0402

R499 62

R0603 +/-1%

R526 62

R0603 +/-1%

R531 62

R0603 +/-1%

R514 56

R0603 +/-1%

R512 56

R0603 +/-1%

R505 56

R0603 +/-1%

R492 56

R0603 +/-1%

R506 56

R0603 +/-1%

+3V

1

2

3

4

+VCCP

CPUPWRGD

1

R534

100

+/-1%

R0603

BC565 2.2nF C0603

+VCCP

BC559

0.1uF

C0603

*

THERMDA

THERMDC

*

TEMP_OVTJ 32

Sis FAE Suggestion

Lonny update July 1st

Title

Dothan CPU-1

Document Numbe r R e v

2

Date: Sheet

661S03

TECHNOLOGY COPR.

350Friday, August 13, 2004

1

of

A

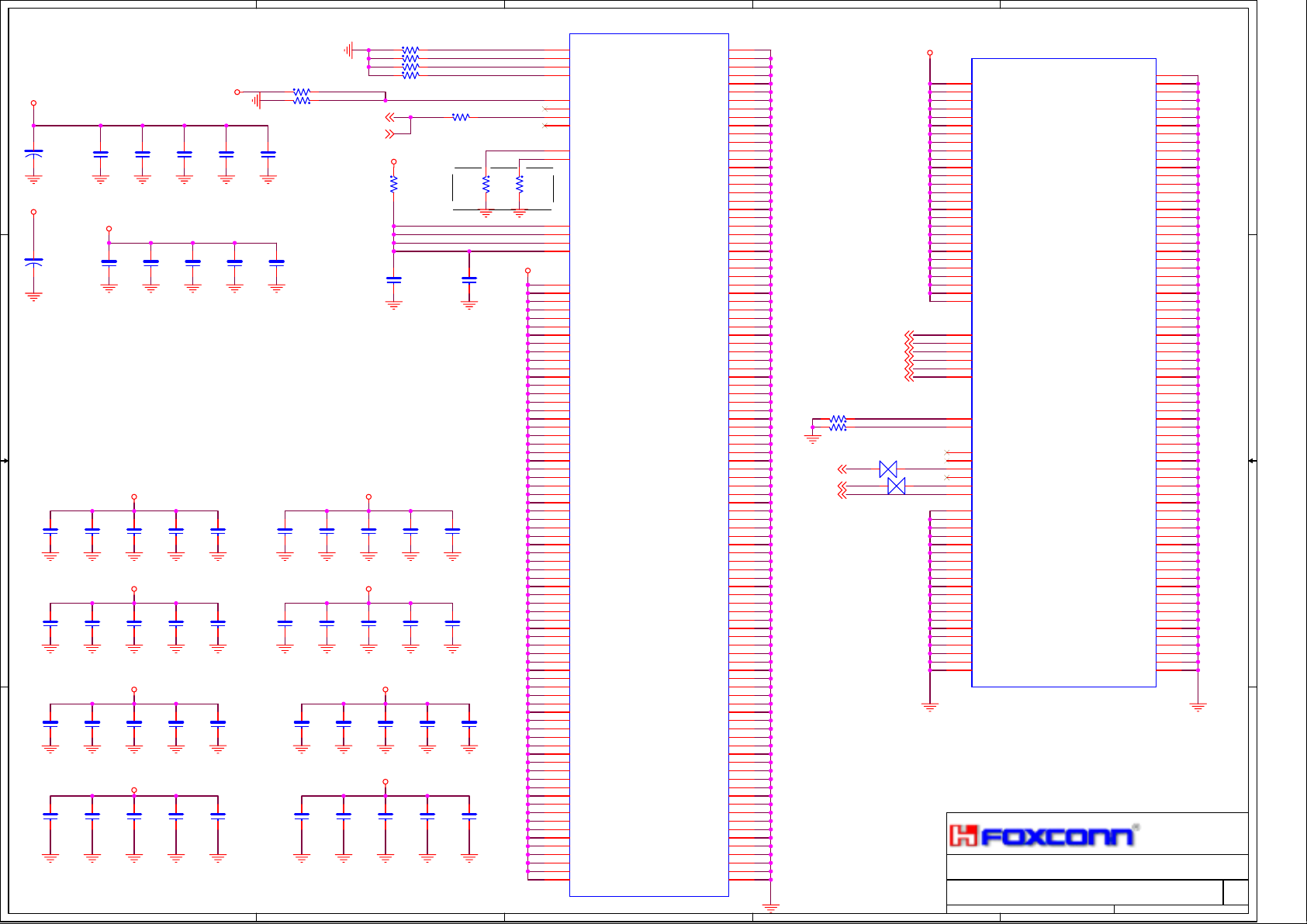

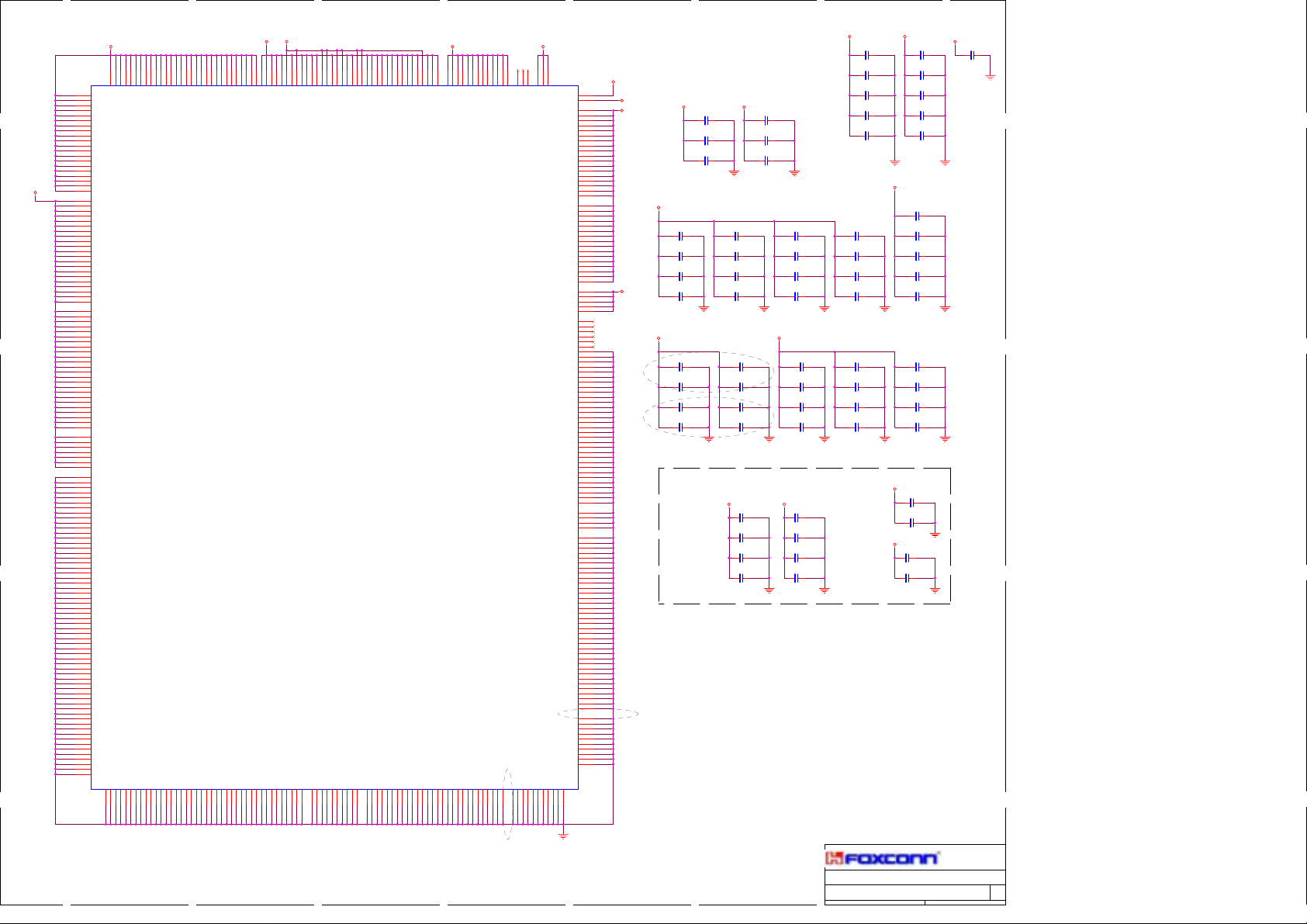

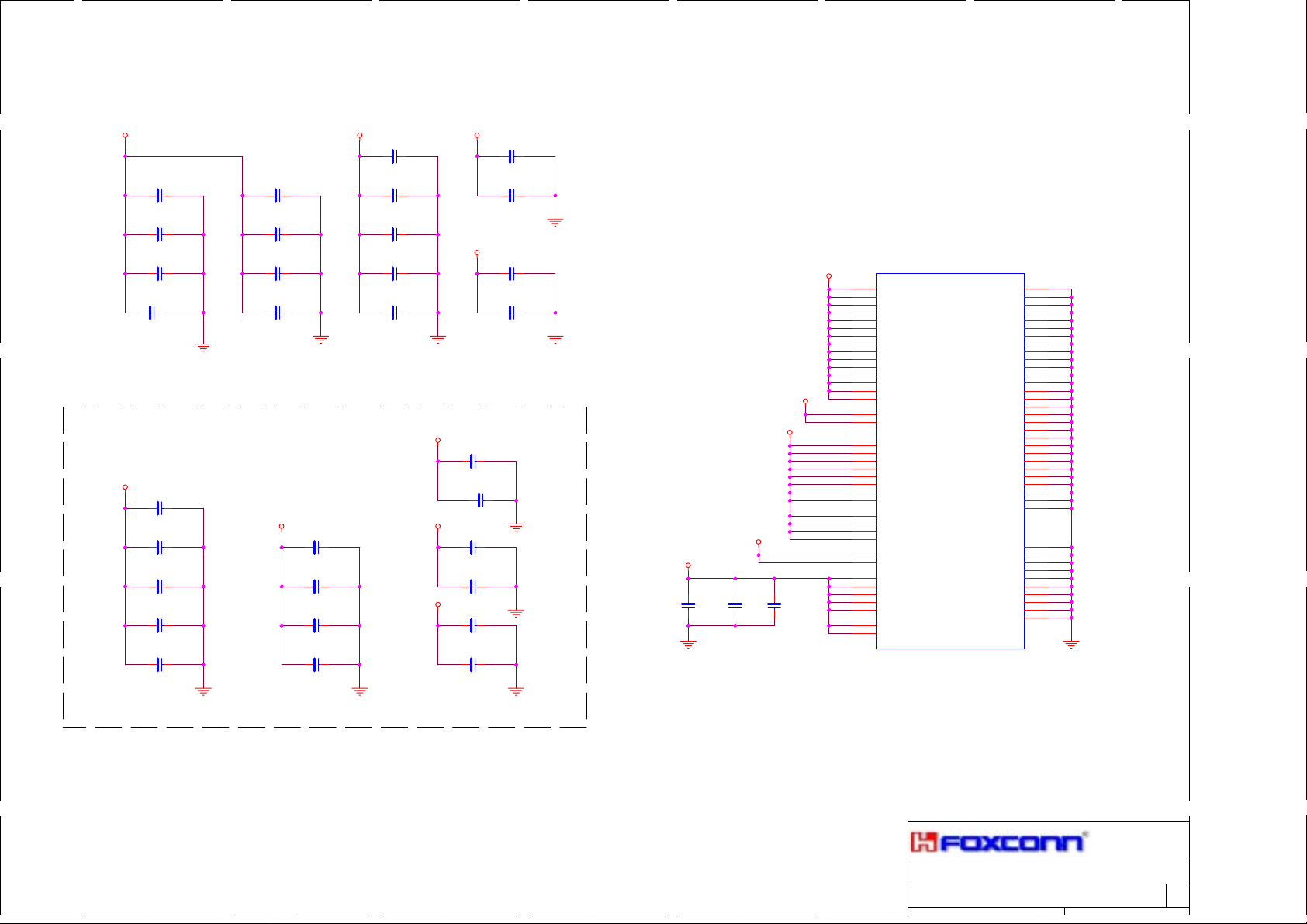

Page 4

5

www.hocnghetructuyen.vn

+VCCP

D D

EC1

150uF

*

2.5V, +/-20%

CTB

+VCCP

EC2

150uF

*

2.5V, +/-20%

CTB

C C

*

B B

*

*

A A

*

BC556

10uF

C0805

BC557

10uF

C0805

BC552

10uF

C0805

BC15

0.1uF

C0603

*

*

*

*

*

+VCCP

*

BC558

10uF

C0805

BC32

10uF

C0805

BC555

10uF

C0805

BC28

0.1uF

C0603

BC50

BC49

0.1uF

0.1uF

*

C0603

C0603

BC25

BC16

0.1uF

0.1uF

*

C0603

C0603

VCORE_CPU

BC571

10uF

*

C0805

BC581

10uF

*

C0805

VCORE_CPU VCORE_CPU

BC40

10uF

*

C0805

VCORE_CPU

BC41

0.1uF

*

C0603

5

+VCCP

BC27

0.1uF

*

C0603

BC33

0.1uF

*

C0603

10U/6.3V/X5R(CC0805)

5 mOhm*35

BC577

10uF

*

*

C0805

BC584

10uF

*

*

C0805

BC52

10uF

*

*

C0805

BC42

0.1uF

*

*

C0603

R5441K +/-5% R0603

R5482K +/-5% R0603

BC19

0.1uF

*

*

C0603

BC17

0.1uF

*

C0603

BC567

10uF

C0805

BC578

10uF

C0805

BC38

10uF

C0805

BC18

0.1uF

C0603

*

BC51

0.1uF

C0603

BC20

0.1uF

C0603

*

*

BC572

10uF

C0805

BC26

10uF

C0805

*

*

*

*

BC55

10uF

C0805

BC553

10uF

C0805

4

R545 27.4 +/-1% R0603

R543 54.9 +/-1% R0603

R497 27.4 +/-1% R0603

R495 54.9 +/-1% R0603

DPRSLPVR10,31

H_DPRSLPJ10,31

+1.8V

*

VCORE_CPU

BC564

BC569

10uF

10uF

*

C0805

C0805

VCORE_CPUVCORE_CPU

BC575

BC579

10uF

10uF

*

C0805

C0805

BC23

10uF

*

*

C0805

VCORE_CPU

BC549

10uF

*

*

C0805

4

0.5'' max length

R486 0 R0402+/-5%

R0805

+/-5%

Dummy

0

R549

BC586

10nF

25V, X7R, +/-10%

C0402

*

*

BC22

10uF

C0805

BC547

10uF

C0805

BC566

10uF

C0805

BC551

10uF

C0805

*

*

*

*

BC29

10uF

C0805

BC550

10uF

C0805

R511

1K

+/-5%

R0603

*

BC561

10uF

C0805

BC548

10uF

C0805

*

*

BC588

10uF

C0805

BC24

10uF

C0805

BC21

10uF

C0805

COMP0

COMP1

COMP2

COMP3

GTLREF0

TEST1

TEST2

Dummy

R546

1K

+/-5%

R0603

VCORE_CPU

P25

P26

AB2

AB1

AD26

E26

AC1

F23

AC26

F26

D18

D20

D22

E17

E19

E21

F18

F20

F22

G21

H22

K22

V22

W21

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

G1

C5

N1

B1

D6

D8

E5

E7

E9

F6

F8

G5

H6

J5

J21

U5

V6

W5

Y6

U33B

COMP0

COMP1

COMP2

COMP3

GTLREF0

RSVD

DPRSLP#

RSVD

TEST1

TEST2

VCCA3

VCCA2

VCCA1

VCCA0

VCC00

VCC01

VCC02

VCC03

VCC04

VCC05

VCC06

VCC07

VCC08

VCC09

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

Banias-Processor

3

Dothan

2 OF 3

POWER,

GROUND,

RESERVED

SIGNALS

3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A2

A5

A8

A11

A14

A17

A20

A23

A26

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

Dummy

R518 54.9+/-1% R0603

R513 54.9+/-1% R0603

Dummy

CPU_BSEL113

CPU_BSEL013

PSIJ31

2

CPU_VID031

CPU_VID131

CPU_VID231

CPU_VID331

CPU_VID431

CPU_VID531

JP11 SHORT

1 2

JP10

1 2

2

1

+VCCP

Z0501

Z0502

SHORT

D10

VCCP0

D12

VCCP1

D14

VCCP2

D16

VCCP3

E11

VCCP4

E13

VCCP5

E15

VCCP6

F10

VCCP7

F12

VCCP8

F14

VCCP9

F16

VCCP10

K6

VCCP11

L5

VCCP12

L21

VCCP13

M6

VCCP14

M22

VCCP15

N5

VCCP16

N21

VCCP17

P6

VCCP18

P22

VCCP19

R5

VCCP20

R21

VCCP21

T6

VCCP22

T22

VCCP23

U21

VCCP24

P23

VCCP25

W4

VCCP26

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AE7

VCCSENSE

AF6

VSSSENSE

B2

RSVD

AF7

RSVD

C14

BSE[1]

C3

RSVD

C16

BSE[0]

E1

PSI#

R6

VSS

R22

VSS

R25

VSS

T3

VSS

T5

VSS

T21

VSS

T23

VSS

T26

VSS

U2

VSS

U6

VSS

U22

VSS

U24

VSS

V1

VSS

V4

VSS

V5

VSS

V21

VSS

V25

VSS

W3

VSS

W6

VSS

W22

VSS

Banias-Processor

U33C

Dothan

3 OF 3

POWE R, GROUND AND NC

VID

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

TECHNOLOGY COPR.

Title

Dothan CPU-2

Document Numbe r R e v

Date: Sheet

661S03

450Friday, August 13, 2004

1

W23

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

of

A

Page 5

8

A

www.hocnghetructuyen.vn

+VCCP

R117

75

+/-1%

R0603

R118

150

+/-1%

R0603

D D

CLK_MCH_BCLK13

CLK_MCH_BCLKJ13

H_CPURSTJ3

CPUPWRGD3

HBREQJ03

HREQJ43

HREQJ33

HREQJ23

HREQJ13

C C

HREQJ03

B B

HAJ[3..31]3

+VCCP

R596 20

R0603 +/-1%

R107 110

R0603 +/-1%

BC179

10nF

*

C0402

BC172

10nF

*

C0402

place this capacitor

under 660FX solder side

HLOCKJ3

DEFERJ3

HTRDYJ3

BPRIJ3

RSJ23

RSJ13

RSJ03

ADSJ3

HITMJ3

HITJ3

DRDYJ3

DBSYJ3

BNRJ3

HADSTBJ13

HADSTBJ03

DPWRJ3

HNCOMP

Rds-on(n) = 10 ohm

HNCVERF = 1/3 VCCP

HPCOMP

Rds-on(p) = 56 ohm

HPCVERF = 2/3 VCCP

*

CLK_MCH_BCLK

CLK_MCH_BCLKJ

HLOCKJ

DEFERJ

HTRDYJ

H_CPURSTJ

CPUPWRGD

BPRIJ

HBREQJ0

H_RSJ2

H_RSJ1

H_RSJ0

ADSJ

HITMJ

HITJ

DRDYJ

DBSYJ

BNRJ

H_REQJ4

H_REQJ3

H_REQJ2

H_REQJ1

H_REQJ0

HADSTBJ1

HADSTBJ0

DPWRJ

HAJ31

HAJ30

HAJ29

HAJ28

HAJ27

HAJ26

HAJ25

HAJ24

HAJ23

HAJ22

HAJ21

HAJ20

HAJ19

HAJ18

HAJ17

HAJ16

HAJ15

HAJ14

HAJ13

HAJ12

HAJ11

HAJ10

HAJ9

HAJ8

HAJ7

HAJ6

HAJ5

HAJ4

HAJ3

HVREF

BC166

0.1uF

C0402

HDJ[0..63]3

AJ31

AJ33

T33

T35

V32

B23

F22

R34

U31

R33

T32

U35

V35

R35

U34

W34

U33

V33

W35

Y33

W31

W33

Y35

AG31

AA33

R36

AH33

AG33

AJ35

AF32

AJ34

AH32

AG35

AE31

AH35

AF35

AE35

AE33

AE34

AF33

AG34

AC33

AD32

AD33

AC35

AD35

AC31

AC34

AB35

AB32

AB33

AA35

AA31

Y32

AA34

SiSM661FX

+VCCP

7

U37A

CPUCLK

CPUCLK#

HLOCK#

DEFER#

HTRDY#

CPURST#

CPUPWRGD

BPRI#

BREQ0#

RS#2

RS#1

RS#0

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ4#

HREQ3#

HREQ2#

HREQ1#

HREQ0#

HASTB1#

HASTB0#

DPWR#

HA31#

HA30#

HA29#

HA28#

HA27#

HA26#

HA25#

HA24#

HA23#

HA22#

HA21#

HA20#

HA19#

HA18#

HA17#

HA16#

HA15#

HA14#

HA13#

HA12#

HA11#

HA10#

HA9#

HA8#

HA7#

HA6#

HA5#

HA4#

HA3#

R595

150

+/-1%

R0603

R593

75

+/-1%

R0603

*

*

C4XAVDD

C1XAVDD

C4XAVSS

C1XAVSS

HVREF

AL36

AJ36

AK34

AK35

AA26

HVREF0

C1XAVSS

C4XAVSS

C1XAVDD

C4XAVDD

HOST

HD63#

HD62#

HD61#

HD60#

HD59#

HD58#

HD57#

HD56#

HD55#

HD54#

F24

E23

B24

B25

C24

HDJ62

HDJ63

BC620

10nF

C0402

HNCVREF

BC621

10nF

C0402

B26

D23

D25

C26

D27

HDJ54

HDJ55

HDJ56

HDJ57

HDJ58

HDJ59

HDJ60

HDJ61

6

VBD6

VBD1

VBD3

VBD0

VBD4

VBD2

VBD7

VBD5

ST0

HNCVREF

HPCOMP

HNCOMP

ST1

ST2

B22

C22

D22

W26

U26

R26

L20

HVREF1

HVREF2

HVREF3

HVREF4

B5

ST0B6ST1F7ST2

HCOMP_P

AAD0Y5AAD1W4AAD2V2AAD3W6AAD4V4AAD5U2AAD6V5AAD7U4AAD8R2AAD9

HCOMP_N

HCOMPVREF_N

VAD4

VAD6

VAD5

T4

AAD10R3AAD11T5AAD12P2AAD13R4AAD14N2AAD15R6AAD16L3AAD17L4AAD18K2AAD19L6AAD20J2AAD21J3AAD22K4AAD23J4AAD24J6AAD25H4AAD26G3AAD27H5AAD28F2AAD29G4AAD30E2AAD31

M661FX-1

HD53#

HD52#

HD51#

HD50#

HD49#

HD48#

HD47#

HD46#

HD45#

HD44#

HD43#

HD42#

HD41#

HD40#

HD39#

HD38#

HD37#

HD36#

HD35#

HD34#

HD33#

HD32#

HD31#

F28

E27

B27

B28

E29

B29

B30

B31

B33

B35

B34

D26

D28

C28

C30

C32

HDJ41

HDJ42

HDJ43

HDJ44

HDJ45

HDJ46

HDJ47

HDJ48

HDJ49

HDJ50

HDJ51

HDJ52

HDJ53

C1XAVDD C4XAVDD

BC103

0.1uF

*

C0402

C1XAVSS

D29

C33

HDJ39

HDJ40

*

D32

HDJ35

HDJ36

HDJ37

HDJ38

FB7

FB L0805 60 Ohm

BC99

10nF

C0402

JP1

SHORT

E31

D31

D33

D35

HDJ31

HDJ32

HDJ33

HDJ34

21

*

12

5

AVSYNC

AHSYNC

VAD10

VAD11

VADE

VAD9

VAD7

VAD8

LVDS/AGP

HD30#

HD29#

HD28#

HD27#

HD26#

HD25#

HD24#

HD23#

J34

F33

F32

E33

E35

C35

D34

G31

HDJ30

BC100

10uF

10V, Y5V, +80%/-20%

C1206

HDJ23

HDJ24

HDJ25

HDJ26

HDJ27

HDJ28

HDJ29

VBD11

G34

HDJ22

HD22#

VBD10

VBD8

HD21#

HD20#

J33

F35

H35

HDJ20

HDJ21

C4XAVSS

VBD9

HD19#

HDJ19

VAD1

HD18#

J31

HDJ18

BC600

0.1uF

C0402

VAD0

HD17#

G35

HDJ17

VAD2

HD16#

H33

HDJ16

VAD3

HD15#

J35

HDJ15

*

K32

HDBIJ33

HDBIJ23

HDBIJ13

HDBIJ03

VBDE

HD14#

N33

HDJ14

VBCTL0

HD13#

HDJ13

VBCTL1

HD12#

K33

HDJ12

L31

*

BVSYNC

BHSYNC

G6

HD11#

HD10#

L33

K35

HDJ10

HDJ11

HDJ9

BC607

10nF

C0402

4

SBA7

SBA6

SBA5

SBA4

SBA3

SBA2

SBA7E3SBA6F4SBA5D2SBA4F5SBA3E4SBA2B2SBA1E6SBA0

HD9#

HD8#

HD7#

HD6#

HD5#

HD4#

HD3#

L35

L34

P32

P33

M35

M33

HDJ3

HDJ4

HDJ5

HDJ6

HDJ7

HDJ8

H_DINVJ3

H_DINVJ2

H_DINVJ1

H_DINVJ0

+3V+3V

FB35

21

FB L0805 60 Ohm

*

JP12

12

SHORT

BCLK

SBA1

B3

AC/BE3#

AC/BE2#

AC/BE1#

AC/BE0#

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

RBF#

WBF#

GC_DET#

ADBIH/PIPE#

ADBIL

SB_STB

SB_STB#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

AGPCLK

AGPCOMP_P

AGPCOMP_N

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AGPVSSREF

HDSTBN3#

HDSTBN2#

HDSTBN1#

HDSTBN0#

HDSTBP3#

HDSTBP2#

HDSTBP1#

HDSTBP0#

HD2#

HD1#

HD0#

DBI3#

DBI2#

DBI1#

F26

P35

B32

E34

N34

N35

HDJ0

HDJ1

HDJ2

BC595

10uF

10V, Y5V, +80%/-20%

C1206

3

AC-BE3

K5

AC-BE2

M5

AC-BE1

P4

AC-BE0

U6

C6

E8

N6

M4

N4

L2

P5

ASTOP_

M2

N3

RBF#

D7

B4

C7

C4

D6

C2

D3

T2

U3

G2

H2

D8

W2

Y2

B8

C8

A7

B7

W3

Y4

D24

F30

G33

N31

E25

D30

H32

M32

DBI0#

R31

AGP3.0 = 50 ohm

AGPRCOMN

Demo is 50 Ohm 1%

lonny 2004-06-02

AGPRCOMP

Demo is 43.75 Ohm 1%

lonny 2004-06-02

AGP_WBF# 41

AGP8X_MB_DETJ

DBI_HI

DBI_LOW

AGP_SBSTBF

AGP_SBSTBS

AGPCLK0

AGPRCOMP

AGPRCOMN

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AVREFGC

H_DSTVNJ3

H_DSTVNJ2

H_DSTVNJ1

H_DSTVNJ0

H_DSTVPJ3

H_DSTVPJ2

H_DSTVPJ1

H_DSTVPJ0

R634 49.9

R0603 +/-1%

R639 43

R0603 +/-1%

ST[0..2]41

@648

R614 0

R0402 +/-5%

R613 0

R0402 +/-5%

AGP_PAR 41

DB_HI 41

DB_LO 41

AGP_SBSTBF 41

AGP_SBSTBS 41

R666 0

R0402 +/-5%

R658 0

R0402 +/-5%

AGPCLK0 13

R653 0

R0402 +/-5%

HDSTBNJ3 3

HDSTBNJ2 3

HDSTBNJ1 3

HDSTBNJ0 3

HDSTBPJ3 3

HDSTBPJ2 3

HDSTBPJ1 3

HDSTBPJ0 3

VDDQ

VAD[0..11]

VBD[0..11]

VBCTL[0..1]

AHSYNC

AVSYNC

SBA[1..7]

AC-BE[0..3]

AGP_REQ# 41

VBCAD 40

AGP_GNT# 41

AGP_FRAME# 41

AGP_IRDY# 41

AGP_TRDY# 41

AGP_DEVSEL# 41

AGP_STOP# 41

R147 0

R0402 +/-5%

R152 0

R0402 +/-5%

AGP8X_MB_DETJ 41

@648

AGP_ADSTBS_0 41

@648

AGP_ADSTBS_1 41

@648

AVREFGC

2

VAD[0..11] 40,41

VBD[0..11] 40,41

VBCTL[0..1] 40,41

VAHSYNC 40,41

VAVSYNC 40,41

ST[0..2]

SBA[1..7] 41

AC-BE[0..3] 41

A4XAVDD

BC641

0.1uF

*

C0402

A4XAVSS

VBHCLK 40

@648

AGP_RBF# 41

R670 0

R0402 +/-5%

AGCLK

AGPREF 41,46

Sis FAE release demo ver0.8

change Value 200 Ohm from 300 Ohm

lonny 070704

BGCLK

R163 0

R0402 +/-5%

BGCLK

R645 10

R0402 +/-5%

16V, X7R, +/-10%

AVREFGC

R633 10

R0402 +/-5%

16V, X7R, +/-10%

BCLK

R635 10

R0402 +/-5%

@648

AGCLK

@648

BC664

0.1uF

C0402

Dummy

BC658

0.1uF

C0402

Dummy

BHSYNC

BVSYNC

VADE

VBDE

*

A1XAVDD

AGP_ADSTBF_0 41

AGP_ADSTBF_1 41

A1XAVSS

*

BC653

0.1uF

*

C0402

*

This part only for 661FX, and 648FX dummy

Title

Document Number Rev

Date: Sheet

661S03

FB41

21

FB L0805 60 Ohm

BC640

10nF

C0402

JP17

12

SHORT

BC639

0.1uF

*

C0402

VAGCLK 40

VDDQ

VBGCLK 40

VBCLK 40,41

1

VBHSYNC 40,41

VBVSYNC 40,41

VADE 40,41

VBDE 40,41

+3V

BC636

10uF

*

C1206

FB40

FB L0805 60 Ohm

BC638

10nF

*

C0402

JP16

SHORT

R640

200

+/-1%

R0603

R646

200

+/-1%

R0603

TECHNOLOGY COPR.

of

550Friday, August 13, 2004

+3V

21

BC637

10uF

*

C1206

12

A

A

Page 6

8

A

www.hocnghetructuyen.vn

/RMD[0..63]

/RDQM[0..7]

/RDQS[0..7]

/RCS-[0..3]

CKE[0..5]

D D

/RMD7 MD7

RN24

/RDQM0 DQM0

10

+/-5%

/RMD0 MD0

8P4R0603

/RMD6

RN23

/RDQS0

10

/RMD5 MD5

+/-5%

/RMD4 MD4

8P4R0603

/RDQS1

RN25

/RMD12

10

/RMD8

+/-5%

/RMD3 MD3

8P4R0603

RN28

10

/RMD17

+/-5%

/RMD20

8P4R0603

/RDQM1 DQM1

RN26

/RMD13 MD13

10

/RMD9 MD9

+/-5%

/RMD2 MD2

8P4R0603

/RMD11

RN27

/RMD14

10

/RMD15

+/-5%

/RMD10

8P4R0603

/RMD29 /RMD24

update sch following layout

C C

0719

B B

/RMD29 MD29

RN30

/RMD24 MD24

10

+/-5%

8P4R0603

/RMD19

RN31

/RMD22

10

/RMD18

+/-5%

/RDQS2

8P4R0603

RN33

/RMD30 MD30

10

+/-5%

/RDQS3

8P4R0603

/RMD31 MD31

RN32

/RMD26

10

/RMD25

+/-5%

/RMD28 MD28

8P4R0603

/RMD39 MD39

RN35

10

+/-5%

8P4R0603

/RMD53

RN39

/RMD49 MD49

10

/RMD47

+/-5%

/RMD42 MD42

8P4R0603

/RDQM4

RN34

/RMD34 MD34

10

/RMD37

+/-5%

/RMD36 MD36

8P4R0603

/RDQM5

RN37

/RMD45

10

/RMD44

+/-5%

/RMD38

8P4R0603

RN38

/RMD48 MD48

10

/RMD46 MD46

+/-5%

/RMD43 MD43

8P4R0603

/RDQS5

RN36

/RMD41

10

/RMD40 MD40

+/-5%

/RMD35 MD35

8P4R0603

/RDQM6

RN41

/RMD54

10

/RMD51

+/-5%

/RDQS6

8P4R0603

/RMD57

RN40

/RMD60 MD60

10

/RMD55

+/-5%

/RMD50

8P4R0603

/RMD63

/RMD62

/RDQM7

/RMD56

/RMD59

/RMD58 MD58

/RDQS7 DQS7

/RMD61 MD61

RN42

10

+/-5%

8P4R0603

RN43

10

+/-5%

8P4R0603

7

/RMD[0..63] 19,20

/RDQM[0. .7] 19,20

/RDQS [ 0 ..7] 19,20

/RCS-[ 0..3] 19,20

CKE[0. . 5] 19,20

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

1

2

*

3

4

5

6

7 8

MD1/RMD1

MD6

DQS0

DQS1

MD12

MD8

MD21/RMD21

MD16/RMD16

MD17

MD20

MD11

MD14

MD15

MD10

MD23/RMD23

DQM2/RDQM2

MD19

MD22

MD18

DQS2

MD27/RMD27

DQM3/RDQM3

DQS3

MD26

MD25

DQS4/RDQS4

MD33/RMD33

MD32/RMD32

MD53

MD47

DQM4

MD37

DQM5

MD45

MD44

MD38

MD52/RMD52

DQS5

MD41

DQM6

MD54

MD51

DQS6

MD57

MD55

MD50

MD63

MD62

DQM7

MD56

MD59

6

/RMD[0..63]

/RMA[0..14]

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7

MD[0..63]

AN35

AP36

AK33

AM33

AN34

AK32

AR34

AN33

AR35

AP34

AM32

AL31

AR31

AL30

AN32

AR33

AN31

AM31

AR32

AP32

AP30

AR30

AM29

AL27

AN30

AN29

AL28

AN28

AL29

AR29

AP26

AN25

AR24

AL24

AL25

AR26

AM25

AN24

AP24

AR25

AN21

AP20

AN20

AL18

AM21

AR21

AL19

AM19

AL20

AR20

AL15

AL14

AN15

AR15

AN16

AM15

AN14

AL13

AP16

AR16

AM13

AL12

AL11

AR12

AP14

AR14

AN13

AP12

AN12

AR13

AL10

AR11

AM9

AR9

AM11

AN11

AP10

AN9

AN10

AR10

/RMD[0..63] 19,20

/RMA[0..14] 19,20

U37B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0/CSB0#

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1/CSB1#

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2/CSB2#

MD24

MD25

MD26

MD27

MD28

M661FX-2

MD29

MD30

MD31

DQM3

DQS3/CSB3#

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4/CSB4#

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5/CSB5#

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6/CSB6#

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7/CSB7#

SiSM661FX

5

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

TEST1

SRAS#

SCAS#

SWE#

CS0#

CS1#

CS2#

CS3#

CS4#

CS5#

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

FWDSDCLKO

SDRCLKI

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

DDRVREFB

DDRVREFA

DRAM_SEL

DDRCOMP_P

DDRCOMP_N

4

CKE4

R621 0 R0402dummy

CKE2

R622 0 R0402dummy

CKE3

R623 0 R0402dummy

CKE5

R624 0 R0402dummy

CKE0

R620 0 R0402dummy

CKE1

R619 0 R0402dummy

R627 0 R0402

MA0

AR23

MA1

MA3 /RMA3

AN23

MA2

AN22

MA3

AM23

MA4

AL23

MA5

AL26

MA6

AN26

MA7

AN27

MA8

AR27

MA9

AR28

MA10

AP22

MA11

AN18

MA12 MA8

AR22

MA13

AP28

MA14

AM27

AT14

SRAS-

AL17

SCAS-

AR19

SWE-

AN19

CS-0

AM17

CS-1

AL16

DEBUG4

AN17

DEBUG5

AR17

AP18

AR18

DEBUG8 CKE0

AP4

DEBUG9

AT3

AR3

AP3

AR2

AN4

DEBUG14

AP2

ADCLKO FWDSDCLKO

AL21

AL22

DLLAVDD

AL35

DLLAVSS

AL34

DDRAVDD

AM35

DDRAVSS

AN36

DDRVREFB

AF16

DDRVREFA

AF23

AP1

DDRCOMP

AR8

DDRCOMN

AP8

R644 0 R0402

MA4

R642 0 R0402

MA2

R651 0 R0402

MA1

MA10

MA12

MA6

DEBUG4

DEBUG5

MA7

MA9

MA13

R661 0 R0402

R660 0 R0402

R665 0 R0402

CS-0

MA11

MA5

For debug mode

R119 22

R0402 +/-5%

R652 0 R0402

R647 0 R0402

R656 0 R0402

R655 0 R0402

R641 0 R0402

R668 0 R0402

R667 0 R0402

R626 0 R0402

R636 0 R0402

R630 0 R0402

R631 0 R0402

R671 0

R672 0

R664 0

R637 0

R612 0

R618 0

R628 0

R0402 +/-5%

3

/RMA4

/RMA2

/RSRAS/RSCAS/RSWE-

S3AUXSW-

40 ohms

DDRCOMN

40 ohms

DDRCOMP

VDIMM

/RMA14MA14

/RMA1

/RMA0MA0

/RMA10

/RMA12

/RMA6

/RCS-2

/RCS-3

/RMA8

/RMA7

/RMA9

/RMA13

/RSRAS- 19,20

/RSCAS- 19,20

/RSWE- 19,20

/RCS-1CS-1

/RCS-0

/RMA11

/RMA5

CKE1

CKE2DEBUG10

CKE3DEBUG11

CKE4DEBUG12

CKE5DEBUG13

FWDSDCLKO 14

R609 40.2

R0402 +/-1%

R610 40.2

R0402 +/-1%

S3AUXSW- 10,38

VDIMM

DDRAVDD

DDRAVSS

2

DDRVREFB

DDRVREFA

FWDSDCLKO

DLLAVDD

DLLAVSS

*

*

*

*

*

BC185 10pF

C0603 50V, NPO, +/-5%

BC602

0.1uF

*

C0402

BC102

BC101

10nF

0.1uF

*

C0402

C0402

JP2

BC186

10nF

C0402

BC199

10nF

16V, X7R, +/-10%

C0402

VDIMM

BC163

10nF

16V, X7R, +/-10%

C0402

BC144

10nF

16V, X7R, +/-10%

C0402

*

FB36 FB L0805 60 Ohm

BC603

10nF

*

C0402

JP13 SHORT

FB8

21

FB L0805 60 Ohm

12

SHORT

1

VDIMM

R120

150

+/-1%

R0603

R123

150

+/-1%

R0603

R116

150

+/-1%

R0603

R102

150

+/-1%

R0603

+3V

21

BC598

10uF

*

C1206

12

+3V

BC104

10uF

*

10V, Y5V, +80%/-20%

C1206

A

Title

TECHNOLOGY C OPR.

Document Number Rev

Date: Sheet

661S03

of

650Friday, August 13, 2004

A

Page 7

8

A

www.hocnghetructuyen.vn

ZAD[0..16]9

ZAD[0..16]

D D

7

6

5

4

3

NB Hardware Trap

(for SiS internal test only)

DLLENTRAP0

TRAP1

2

R139 0

R0402 +/-5%

R141 0

R0402 +/-5%

R144 0

R0402 +/-5%

1

+3V

dummy

dummy

dummy

+1.8V

ZCLK013

ZUREQ9

ZDREQ9

ZSTB09

ZSTB-09

ZSTB19

ZSTB-19

R138

75

+/-1%

R0402

R153

150

+/-1%

R0603

R146

150

+/-1%

R0603

BC248

0.1uF

*

16V, X7R, +/-10%

C0402

ZVREF

BC231

0.1uF

*

16V, X7R, +/-10%

C0402

C C

+3V

FB43 FB L0805 60 Ohm

21

BC670

10uF

*

C1206

JP18

SHORT

+3V

FB42 FB L0805 60 Ohm

BC669

10uF

*

C1206

JP19

B B

SHORT

+1.8V

FB11 FB L0805 60 Ohm

BC229

10uF

*

C1206

JP4

SHORT

BC657

0.1uF

*

C0402

12

21

BC649

0.1uF

*

C0402

12

21

BC230

0.1uF

*

C0402

12

ENTEST

PWRGD

AUXOK

Z1XAVDD

BC650

10nF

*

16V, X7R, +/-10%

C0402

Z1XAVSS

Z4XAVDD

BC656

10nF

*

16V, X7R, +/-10%

C0402

Z4XAVSS

BC233

10nF

*

16V, X7R, +/-10%

C0402

R142 4.7K

R0402 +/-5%

BC648 0.1uF C0402

BC655 0.1uF C0402

R148 56

R0603 +/-1%

R149 56

R0603 +/-1%

*

*

ZCLK0

ZUREQ

ZDREQ

ZSTB0

ZSTB-0

ZSTB1

ZSTB-1

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

ZVREF

ZCMP_N

ZCMP_P

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

NBRSTJ9

AUXOK10,32

ZCMP_P

PWRGD10,15,31

ZCMP_N

AL6

AL4

AK5

AE3

AF2

AH5

AK2

AH2

AH4

AG3

AG6

AF4

AG2

AF5

AG4

AD2

AE6

AE2

AE4

AL3

AK4

AD5

AD4

AN1

AM2

AL2

AL1

AJ2

AJ3

AJ4

AJ6

U37C

ZCLK

ZUREQ

ZDREQ

ZSTB0

ZSTB0#

ZSTB1

ZSTB1#

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

ZVREF

ZCOMP_N

ZCOMP_P

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

SiSM661FX

PWRGD

AUXOK

HyperZip

M661FX-3

PCIRST#

PWROK

AUXOK

TRAP1F9TRAP0

TESTMODE2C9TESTMODE1B9TESTMODE0

D10

AN2

AN3

AM4

TRAP1

TMODE2

TRAP0

A15

VOSCI

B12

ROUT

B13

GOUT

A13

VGA

DLLEN#

ENTEST

D9

B10

E10

TMODE0

ENTEST

TMODE1

DLLEN-

BOUT

HSYNC

VSYNC

VGPIO0

VGPIO1

INT#A

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

A11

B11

E13

C11

C10

D12

E12

D11

E15

D15

E14

D13

C12

D14

C13

B15

C15

B14

C14

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

BC628

C0402

BC632

C0402

R606 33 R0402

R605 33 R0402

R132 100 R0402

R135 100 R0402

Update sch basis on demo ver0.8

lonny 2004/07/12

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD

DACAVSS

DACAVDD

DACAVSS

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

10nF

*

*

10nF

*

*

REFCLK0 13

302LV_CRT_R 18

302LV_CRT_G 18

302LV_CRT_B 18

302LV_CRTHS_VGA 18

302LV_CRTVS_VGA 18

302LV_DDCCLK 18

302LV_DDCDAT 18

INT-A 9,2 2,23,40

FB38 FB L0805 60 Ohm

21

BC627

0.1uF

C0402

JP14

SHORT

FB39 FB L0805 60 Ohm

BC633

0.1uF

C0402

JP15

SHORT

BC626

10uF

*

C1206

12

21

BC631

10uF

*

C1206

12

This part only for 661FX, and 648FX reserved.

+3V

+3V

TMODE0

TMODE1

TMODE2

RSYNC

LSYNC

CSYNC TBD

RSYNC

LSYNC

CSYNC

RSYNC

LSYNC

CSYNC

VVBWN

BC197 0.1uF C0402

VCOMP

BC187 0.1uF C0402

DACAVDD

DACAVSS

R137 0

R0402 +/-5%

R608 0

R0402 +/-5%

R607 0

R0402 +/-5%

VGA Interrupt

TBD

R130 4.7K

R0402 +/-5%

R140 4.7K

R0402 +/-5% Dummy

R133 4.7K

R0402 +/-5% Dummy

R131 4.7K

R0402 +/-5% Dummy

R136 4.7K

R0402 +/-5%

R134 4.7K

R0402 +/-5%

*

*

*

BC198

0.1uF

C0402

*

FB10 FB L0805 60 Ohm

BC201

1uF

C0603

JP3

SHORT

This part only for 661FX, and 648FX reserved.

+3V

dummy

dummy

dummy

Enable Disable

1

1

1

+3V

VRSET

+1.8V

21

12

0

0

0

BC194

10uF

*

C1206

R122

130

+/-1%

R0402

A

Title

TECHNOLOGY C OPR.

Document Number Rev

Date: Sheet

661S03

of

750Friday, August 13, 2004

A

Page 8

8

A

www.hocnghetructuyen.vn

+VCCP

A17

A18

A19

A20

A21

B17

L25

VTT

L26

VTT

M18

VTT

M19

VTT

M20

VTT

M21

D D

VDIMM

C C

B B

VTT

M22

VTT

M23

VTT

M24

VTT

M25

VTT

M26

VTT

N25

VTT

P25

VTT

R25

VTT

T25

VTT

U25

VTT

V25

VTT

W25

VTT

Y25

VTT

AA25

VTT

AL7

VDDM

AL8

VDDM

AL9

VDDM

AM6

VDDM

AM7

VDDM

AM8

VDDM

AN5

VDDM

AN6

VDDM

AN7

VDDM

AN8

VDDM

AP5

VDDM

AP6

VDDM

AP7

VDDM

AR4

VDDM

AR5

VDDM

AR6

VDDM

AR7

VDDM

AT4

VDDM

AT5

VDDM

AT6

VDDM

AT7

VDDM

AB25

VDDM

AC25

VDDM

AD12

VDDM

AD25

VDDM

AE11

VDDM

AE12

VDDM

AE13

VDDM

AE14

VDDM

AE15

VDDM

AE16

VDDM

AE17

VDDM

AE18

VDDM

AE19

VDDM

AE20

VDDM

AE21

VDDM

AE22

VDDM

AE23

VDDM

AE24

VDDM

AE25

VDDM

AE26

VDDM

AF11

VDDM

AF12

VDDM

AF25

VDDM

AF26

VDDM

AB24

PVDDM

AC13

PVDDM

AD14

PVDDM

AD16

PVDDM

AD18

PVDDM

AD20

PVDDM

AD22

PVDDM

P14

VSS

P15

VSS

P16

VSS

P17

VSS

P18

VSS

P19

VSS

P20

VSS

P21

VSS

P22

VSS

P23

VSS

R14

VSS

R15

VSS

R16

VSS

R17

VSS

R18

VSS

R19

VSS

R20

VSS

R21

VSS

R22

VSS

R23

VSS

T14

VSS

T15

VSS

T16

VSS

T17

VSS

T18

VSS

T19

VSS

T20

VSS

T21

VSS

T22

VSS

T23

VSS

U14

VSS

U15

VSS

U16

VSS

U17

VSS

U18

VSS

U19

VSS

U20

VSS

U21

VSS

U22

VSS

U23

VSS

V14

VSS

V15

VSS

V16

VSS

V17

VSS

V18

VSS

V19

VSS

V20

VSS

V21

VSS

V22

VSS

V23

VSS

W14

VSS

W15

VSS

W16

VSS

W17

VSS

W18

VSS

W19

VSS

W20

VSS

W21

VSS

W22

VSS

W23

VSS

B18

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

7

IVDD

N13

B19

B20

B21

C17

C18

C19

C20

C21

D17

D18

D19

D20

D21

E17

VTT

VTT

VTT

VTT

VTT

E18

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

N14

E19

E20

E21

F17

F18

F19

F20

F21

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

IVDD

M661FX-4

Power

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y22

Y23

AA14

AA15

AA16

AA17

AA18

AA19

AA20

AA21

AA22

AA23

AB14

AB15

AB16

VSS

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AC14

AC15

AC16

6

+1.8V

N16

N18

N19

N21

N23

N24

P13

P24

T24

V24

W13

Y24

AA24

AB13

AC24

AD13

N20

N22

R24

T13

U24

V13

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

PVDD

PVDD

PVDD

PVDD

PVDD

PVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AC17

AC18

AC19

AC20

AC21

AC22

VSS

VSS

VSS

AF34

AE32

AE36

AC32

AC36

AD34

AC23

AG32

AD15

W24

Y13

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

PVDD

PVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ32

AH34

AG36

AM10

AM12

AM14

AM16

AM18

AM20

5

+1.8V

AD17

AD19

AD21

AD23

AD24

R13

U13

AA13

N15

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

PVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AP9

AP11

AP13

AP15

AP17

AM22

AM24

AM26

AM28

AM30

AD3

AE1

AF3

AH3

AJ1

AK3

VDDZ

VDDZ

VDDZ

VSS

VSS

VSS

AP19

AP21

AP23

AG1

AM3

W11

W12

Y11

Y12

AA12

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AT8

AT10

AT12

AT16

AP25

AP27

AT18

AP29

AP31

AP33

AP35

NCD4NCD5NC

VSS

AT20

4

+3V

AUX_IVDD

AM5

VSS

VSS

VSS

AT22

AT24

U37D

L17

M17

N17

AB12

AUX_IVDD

AC12

AA1

AA2

AA3

AA4

AA5

AA6

AB1

AB2

AB3

AB4

AB5

AB6

AC1

AC2

AC3

AC4

AC5

AC6

L11

L12

L13

M11

M12

M13

M14

M15

M16

N11

N12

P12

R12

T12

U12

V12

B16

C16

D16

E16

F15

E11

F11

F13

AL33

AM34

A9

A3

A5

C1

C3

C5

E1

E5

E7

E9

F3

G1

G5

H3

J1

J5

K3

L1

L5

M3

N1

N5

P3

R1

R5

T3

U1

U5

V3

W1

W5

Y3

AE5

AG5

AJ5

AL5

A22

A24

A26

A28

A30

A32

A34

C23

C25

C27

C29

C31

C34

C36

E22

E24

E26

E28

E30

E32

E36

F34

G32

G36

H34

J32

J36

K34

L32

L36

M34

N32

N36

P34

R32

T34

U32

U36

V34

W32

W36

Y34

AA32

AA36

AB34

SiSM661FX

3VAUX

VDDQ

IVDD

change to DPWR#

AUX3.3

VDD3.3

VDD3.3

VDD3.3

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

IVDD

IVDD

IVDD

IVDD

IVDD

NC

NC

NC

NC

NC

NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL32

AT26

AT28

AT30

AT32

AT34

3

AUX_IVDD 3VAUX

BC659 10uF

BC257 0.1uF C0402

BC251 0.1uF

C0402 16V, X7R, +/-10%

+VCCP

BC189 10uF

C1206

*

BC129 0.1uF C0402

*

Dummy

BC156 10uF

C1206

*

BC124 0.1uF C0402

*

Dummy

VDDQ

648 solder side

BC216 0.1uF C0402

*

BC221 0.1uF C0402

*

BC196 0.1uF C0402*BC190 0.1uF C0402

*

BC212 0.1uF C0402

*

close to 648

and on VDDQ

plane

Place these capacitors under 661 solder side

C1206

*

*

Dummy

*

BC155 1uF

*

BC127 0.1uF C0402

*

Dummy

BC128 0.1uF C0402

*

Dummy

BC123 0.1uF C0402

*

Dummy

BC223 0.1uF C0402

BC224 0.1uF C0402

BC222 0.1uF C0402

+1.8V

BC151 0.1uF C0402

BC204 0.1uF C0402

BC147 0.1uF C0402

Dummy

BC171 0.1uF C0402

Dummy

BC237 10uF

C1206

*

BC228 1uF

C0603

*

BC226 0.1uF

C0402 16V, X7R, +/-10%

*

BC182 0.1uF

C0603

BC126 0.1uF C0402

BC174 0.1uF C0402

BC122 0.1uF C0402

VDIMM

BC225 10uF

*

BC238 10uF

*

BC120 10uF

BC209 10uF

*

VDIMM

BC193 0.1uF C0402

*

BC157 0.1uF C0402

Dummy

*

BC154 0.1uF C0402

*

BC121 0.1uF C0402

*

*

*

Dummy

*

Dummy

*

Dummy

*

*

*

*

*

*

*

*

2

C0402

C1206

C1206

C1206

C1206

661 bottom side

IVDD IVDD

BC205 0.1uF

C0402

*

BC195 0.1uF

C0402

*

BC177 0.1uF

C0402

*

BC200 10uF

C1206

*

BC150 0.1uF C0402

*

Dummy

BC139 0.1uF

C0402

*

BC125 0.1uF C0402

*

Dummy

BC153 0.1uF C0402

*

Dummy

BC158 0.1uF C0402

*

Dummy

BC173 1uF

C0603

*

BC235 1uF

C0603

*

BC236 0.1uF C0402

*

BC165 0.1uF C0402

*

BC203 0.1uF

C0402

*

BC176 0.1uF

C0402

*

BC146 0.1uF

C0402

*

BC145 0.1uF

C0402

*

BC148 0.1uF

C0402

*

+1.8V

BC254 0.1uF C0402

*

BC660 10uF

C1206

*

BC152 1uF

C0603

*

BC253 0.1uF C0402

*

BC255 0.1uF C0402

*

BC218 1uF

C0603

*

BC132 1uF

C0603

*

BC138 0.1uF C0402

*

BC202 0.1uF C0402

*

3VAUX

BC211 0.1uF C0402

*

BC219 0.1uF C0402

*

VDDQ

BC220 0.1uF C0402

*

Dummy

BC206 0.1uF C0402

*

1

+3V

BC183 0.1uF

C0402

*

A

8

7

change to MA15

Title

Document Number Rev

6

5

4

3

Date: Sheet of

2

661S03

TECHNOLOGY COPR.

850Friday, August 13, 2004

1

A

Page 9

8

A

www.hocnghetructuyen.vn

RN18

INT-D

1

*

INT-A

3

INT-B

5

INT-C

7 8

8.2K

+/-1%

8P4R0603

PREQ-4

R250 4.7K

R0402 +/-5%

D D

PGNT-4

R252 4.7K

R0402 +/-5%

PCIRSTJ 15,17,22,23,29,40,41

NBRSTJ 7

C C

U11

1

I1

2

O1

3

I2

4

O2

5

I3

6

O3

7

GND

74LVC14

B B

R261

75

+/-1%

R0402

+1.8V

+3V

2

4

6

+3V

14

Vcc

13

I6

12

O6

11

I5

10

O5

9

I4

8

O4

R262

*

150

+/-1%

R0603

R767

*

150

+/-1%

R0603

JP7

12

SHORT

7

REQ3J23

REQ2J23

REQ1J22

REQ0J29

GNT3J23

GNT2J23

GNT1J22

GNT0J29

C/BE3J2 2,23,29

C/BE2J22,23,29

C/BE1J22,23,29

C/BE0J22,23,29

INT-A7,22,23,40

INT-B41,46

INT-C22,23,29

INT-D22,23

FRAMEJ2 2,23,29

IRDYJ22,23,29

TRDYJ22,23,29

STOPJ2 2,23,29

SERRJ22,23,29

PAR22,23,29

DEVSELJ22,23,29

96XPCLK13

PCIRSTJ

PCIRSTJ 15,17,22,23,29,40,41

ZCLK113

ZSTB07

ZSTB-07

ZSTB17

ZSTB-17

ZUREQ7

ZDREQ7

SVDDZCMP

SZCMP_N

SZCMP_P

SVSSZCMP

BC348

0.1uF

C0402

SZVREF

BC355

0.1uF

C0402

SZ1XAVDD

SZ1XAVSS

SZ4XAVDD

SZ4XAVSS

SZVREF

ZAD16

REQ3J

REQ2J

REQ1J

REQ0J

GNT3J

GNT2J

GNT1J

GNT0J

C/BE3J

C/BE2J

C/BE1J

C/BE0J

INT-A

INT-B

INT-C

INT-D

ZCLK1

ZSTB0

ZSTB-0

ZSTB1

ZSTB-1

ZUREQ

ZDREQ

AD[0..31]22,23,29

PREQ-4

PGNT-4

FRAMEJ

IRDYJ

TRDYJ

STOPJ

SERRJ

PAR

DEVSELJ

ZAD[0..16]7

M19

V20

N20

K20

N16

N17

R19

N18

R18

P18

U20

U19

T20

T19

R20

P20

J20

F1

F2

E1

H5

F3

H3

G1

G2

G3

H4

K3

M4

P1

R4

E3

F4

E2

G4

M3

M1

M2

N4

M5

N3

N1

N2

Y2

C3

6

AD[0..31]

PREQ4#

PREQ3#

PREQ2#

PREQ1#

PREQ0#

PGNT4#

PGNT3#

PGNT2#

PGNT1#

PGNT0#

C/BE3#

C/BE2#

C/BE1#

C/BE0#

INTA#

INTB#

INTC#

INTD#

FRAME#

IRDY#

TRDY#

STOP#

SERR#

PAR

DEVSEL#

PLOCK#

PCICLK

PCIRST#

ZCLK

ZSTB0

ZSTB0#

ZSTB1

ZSTB1#

ZUREQ

ZDREQ

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

ZVREF

ZAD16

5

AD22

AD31

AD31J5AD30J4AD29H2AD28H1AD27J3AD26K4AD25J2AD24J1AD23K5AD22K2AD21L3AD20K1AD19L1AD18L4AD17L5AD16L2AD15N5AD14P2AD13P3AD12P4AD11R2AD10

AD24

AD28

AD29

AD27

AD30

AD20

AD18

AD25

AD26

AD19

AD21

AD23

PCI

963-1

HyperZip

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

M18

L16

L20

N19

M17

M16

M20

ZAD0

ZAD1

ZAD6

ZAD4

ZAD3

ZAD5

ZAD2

J18

L18

K18

K19

K17

K16

H20

ZAD12

ZAD7

ZAD11

ZAD13

ZAD9

ZAD8

ZAD10

4

AD17

AD16

ZAD13

ZAD14

H19

H18

ZAD14

ZAD15

AD10

AD9

AD13

AD11

AD12

R3

AD8

AD9R1AD8T1AD7P5AD6T2AD5U1AD4U2AD3T3AD2R5AD1U3AD0

AD15

AD14

IDE

ZAD15

AD1

AD7

AD6

AD0

AD2

AD3

AD4

AD5

V1

IDEAVDD

IDEAVSS

ICHRDYA

IDREQA

IIRQA

CBLIDA

IIORA#

IIOWA#

IDACKA#

IDSAA2

IDSAA1

IDSAA0

IDECSA1#

IDECSA0#

ICHRDYB

IDREQB

IIRQB

CBLIDB

IIORB#

IIOWB#

IDACKB#

IDSAB2

IDSAB1

IDSAB0

IDECSB1#

IDECSB0#

IDA0

IDA1

IDA2

IDA3

IDA4

IDA5

IDA6

IDA7

IDA8

IDA9

IDA10

IDA11

IDA12

IDA13

IDA14

IDA15

IDB0

IDB1

IDB2

IDB3

IDB4

IDB5

IDB6

IDB7

IDB8

IDB9

IDB10

IDB11

IDB12

IDB13

IDB14

IDB15

U18A

Y3

Y4

W10

V10

Y11

U12

V11

Y9

Y10

T11

U11

W11

T12

V12

W17

Y17

T16

U17

T14

W16

V16

Y18

T15

V17

U16

W18

U10

V9

W8

T9

Y7

V7

Y6

Y5

W6

U8

W7

V8

U9

Y8

T10

W9

Y16

V15

U14

W14

V13

T13

Y13

Y12

W12

W13

U13

Y14

V14

W15

Y15

U15

SiS963L

3

ICHRDYA

IDEREQA

IDEIRQA

CBLIDA

IDEIOR-A

IDEIOW-A

IDACK-A

IDESAA2

IDESAA1

IDESAA0

IDECS-A1

IDECS-A0

ICHRDYB

IDEREQB

IDEIRQB

IDEIOR-B

IDEIOW-B

IDACK-B

IDESAB2

IDESAB1

IDESAB0

IDECS-B196XPCLK

IDECS-B0

HDD0

HDD1

HDD2

HDD3

HDD4

HDD5

HDD6

HDD7

HDD8

HDD9

HDD10

HDD11

HDD12

HDD13

HDD14

HDD15

CDD0

CDD1

CDD2

CDD3

CDD4

CDD5

CDD6

CDD7

CDD8

CDD9

CDD10

CDD11

CDD12

CDD13

CDD14

CDD15

*

2

R296 0

R0603 +/-1%

BC399

10nF

C0402

BC406

0.1uF

*

C0402

ICHRDYA 17

IDEREQA 17

IDEIRQA 17

CBLIDA 17

IDEIOR-A 17

IDEIOW-A 17

IDACK-A 17

IDESAA2 17

IDESAA1 17

IDESAA0 17

IDECS-A1 17

IDECS-A0 17

ICHRDYB 17

IDEREQB 17

IDEIRQB 17

IDEIOR-B 17

IDEIOW-B 17

IDACK-B 17

IDESAB2 17

IDESAB1 17

IDESAB0 17

IDECS-B1 17

IDECS-B0 17

HDD[0..15] 17

CDD[0..15] 17

Put near 96X Chip.

only for MUTIOL 1.0 backup solution

ZSTB0

ZSTB1

+1.8V

BC405

0.1uF

*

C0402

R255 0 R0402 dummy

R251 0 R0402 dummy

1

+1.8V

Analog Power supplies of Transzip function for 96X Chip.

+3V +3V

*

BC409

10uF

C1206

FB57

FB L1806 60 Ohm

21

JP9

12

SHORT

BC384

BC385

0.1uF

C0402

10nF

*

C0402

*

SZ1XAVDD

SZ1XAVSS

+1.8V

FB55

FB L1806 60 Ohm

21

BC391

10uF

*

C1206

JP8

SHORT

BC376

0.1uF

*

*

C0402

12

BC377

10nF

C0402

SZ4XAVDD

*

SZ4XAVSS

BC731

10uF

C1206

FB54

FB L1806 60 Ohm

21

JP6

12

SHORT

SVDDZCMP

BC739

BC740

10nF

C0402

R754 56

R0603 +/-1%

R257 56

R0603 +/-1%

0.1uF

*

*

C0402

SZCMP_N

SZCMP_P

SVSSZCMP

ZSTB-0

ZSTB-1

R256 0 R0402 dummy

R254 0 R0402 dummy

TECHNOLOGY C OPR.

Title

Document Number Rev

Date: Sheet

661S03

of

950Friday, August 13, 2004

A

A

Page 10

A

Programable on-die pull-high strength for CPU_S:

www.hocnghetructuyen.vn

( Infinite, 150, 110, 56 Ohm)

D D

C C

B B

8

SMBDAT13,14,19,46

SMBCLK13,14,19,46

PCSPK11,27

DPRSLPVR4,31

PMEJ22,23

AUXOK7,32

H_INITJ

H_A20MJ

H_SMIJ

H_INTR

H_NMI

H_IGNNEJ

H_FERRJ

H_STPCLKJ

H_CPUSLPJ

1

2

3 4

H_INITJ3

H_A20MJ3

H_SMIJ3

H_INTR3

H_NMI3

H_IGNNEJ3

H_FERRJ3

H_STPCLKJ3

SUSBJ15,29

SUSCJ15

SUSON15,33,38

H_CPUSLPJ3

CPU_PROCHOTJ3

PM_THRMTRIPJ3

LFRAMEJ/FWH415

SERIRQ15,23

BATOK32

PWRGD7,15,31

AC_SDIN027

AC_SDIN122

AC_SDOUT11,22,27

AC_SYNC22,27

AC_RESETJ22,27

AC_BITCLK22,27

REFCLK113

PWRBTN15

R615 100 R0603 +/-1%

R616 100 R0603 +/-1%

+3V

S3AUXSW-6,38

R290 10K

R0402 +/-1%

LAD0/FWH015

LAD1/FWH115

LAD2/FWH215

LAD3/FWH315

LFRAMEJ/FWH4

LDRQJ

SERIRQ

OSC32KHI

OSC32KHO

BATOK

*

SMBDAT

SMBCLK

AC_SDIN0

AC_SDIN1

AC_SDOUT

AC_SYNC

AC_RESETJ

AC_BITCLK

REFCLK1

SENTEST

PCSPK

PWRBTN

PMEJ

AUXOK

GPIO14

SLP_S3#

SLP_S4#

GPIO17

GPIO18

U40A

3

74LV08

7 14

147

U39B

74HCT14

7

VCCRTC

BC311

0.1uF

16V, X7R, +/-10%

C0402

R0402

R294 0

R771 0

R0402

BC290

0.1uF

*

16V, X7R, +/-10%

C0402

1 2

4

5

7 14

5VAUX5VAUX

+/-5%

+/-5%

147

T18

P16

R17

R16

Y20

U18

T17

W20

V19

Y19

V18

W19

W5

W4

W2

W3

A14

B14

D14

A15

D13

B15

U39A

74HCT14

U40B

6

74LV08

U18B

INIT#

A20M#

SMI#

INTR

NMI

IGNNE#

FERR#

STPCLK#

CPUSLP#

APICCK/LDTREQ#

APICD0/THERM2#

APICD1/GPIOFF#

V5

LAD0

T7

LAD1

U6

LAD2

LAD3

LFRAME#

U7

LDRQ#

V6

SIRQ

C2

OSC32KHI

D2

OSC32KHO

D3

BATOK

D1

PWROK

C1

RTCVDD

E4

RTCVSS

B2

GPIO20

A1

GPIO19

A2

AC_SDIN0

D5

AC_SDIN1

AC_SDOUT

T5

AC_SYNC

D6

AC_RESET#

Y1

AC_BIT_CLK

OSCI

G5

ENTEST

V3

SPK

PWRBTN#

PME#

PSON#

A3

AUXOK

ACPILED

B1

GPIO13/DPRSLPVR

E5

GPIO14

GPIO17/PMDAT

GPIO18/PMCLK

SiS963L

SLP_S4#

SLP_S3#

6

CPU_S

APIC

LPC

RTC

963-2

GPIO

AC97

ACPI

/others

KBC

/geyserville

GPIO

Place near to 96X

AC_BITCLK

5

MII

GPIO1/LDRQ1#

GPIO2/THERM#

GPIO3/EXTSMI#

GPIO4/CLKRUN#

GPIO5/PREQ5#

GPIO6/PGNT5#

GPIO8/RING

GPIO9/AC_SDIN2

GPIO10/AC_SDIN3

GPIO11/OSC25M/STP_PCI#

GPIO12/CPUSTP#

GPIO15/VR_HILO#

GPIO16/LO_HI#

BC389

10pF

*

50V, NPO, +/-5%

C0402

OSC25MHI

OSC25MHO

TXCLK

TXEN

TXD0

TXD1

TXD2

TXD3

RXCLK

RXDV

RXER

RXD0

RXD1

RXD2

RXD3

COL

CRS

MDC

MDIO

MIIAVDD

MIIAVSS

GPIO0

GPIO7

4

MCLK25I

A8

MCLK25O

A9

A6

B6

E8

D7

C6

B4

A7

C7

C8

D8

A5

B5

A4

B7

E9

C5

E7

CLKRUNJ

SMBALTJ

RF_DIS

GPIO11

MIIAVDD

MIIAVSS

SCIJ

THERM-

KBSMIJ

CLKRUNJ

GPIO6

SMBALTJ

CPUSTPGPIO15

GPIO16

R0402 +/-5%

dummy

R0402 +/-5%

dummy

B9

B8

V2

T8

T4

T6

W1

U5

U4

C4

C14

E6

B3

F5

D4

E13

A16

5 6

11 10

R282

R208

9

10

147

147

KBSMIJ 15

4.7K

4.7K

3

U40C

8

74LV08

7 14

U39C

74HCT14_1

U39E

74HCT14_1

SCIJ 15

CLKRUNJ 15,22,29

R238

4.7K

+/-1%

R0603

+3V

3VAUX

12

13

147

9 8

147

13 12

+3V

R253

24.9K

+/-1%

R0603

Q17

B

MMBT3904

E C