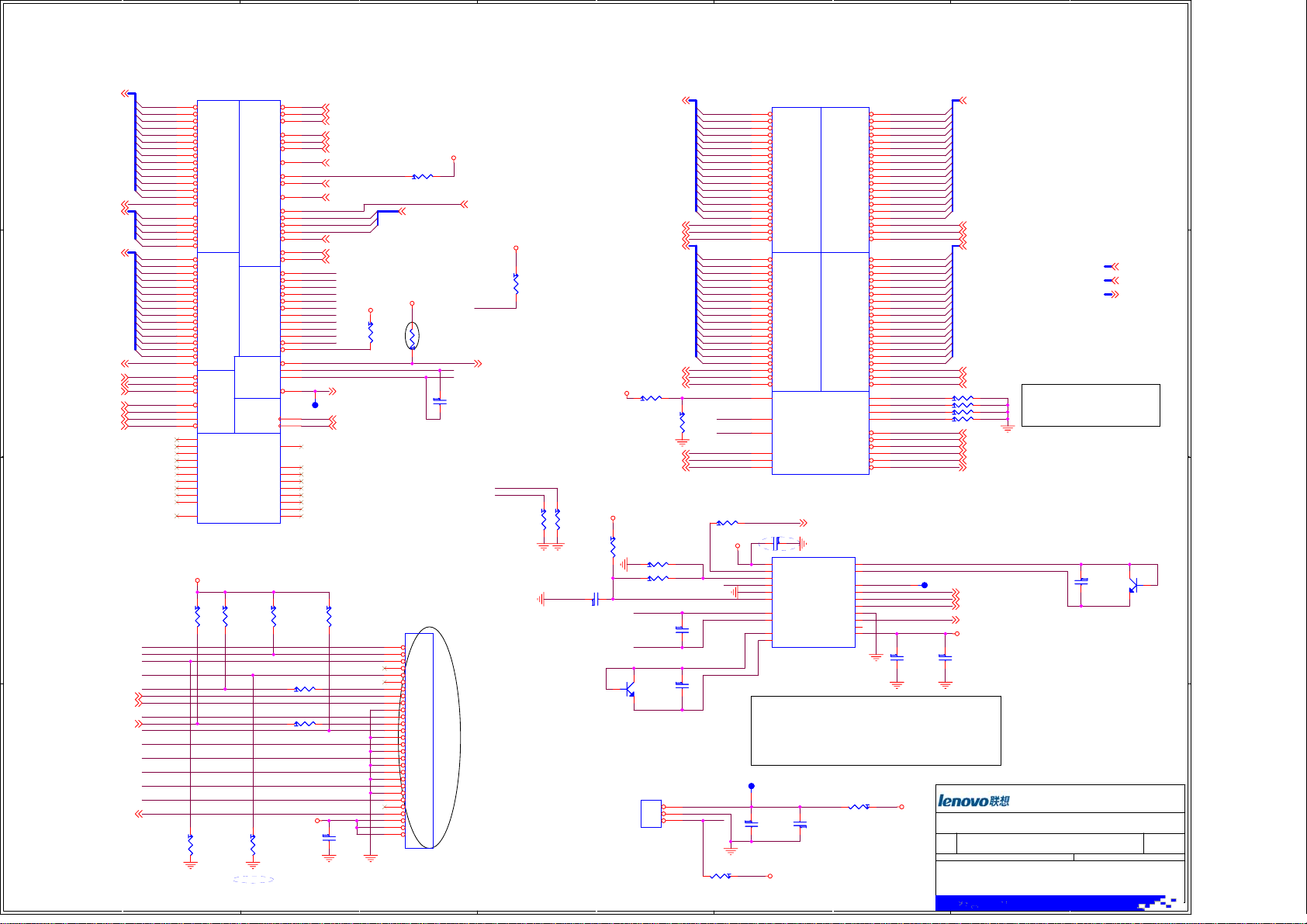

Lenovo F41 Schematics

5

4

3

2

1

DC/DC & Charger

< NAPA >

D D

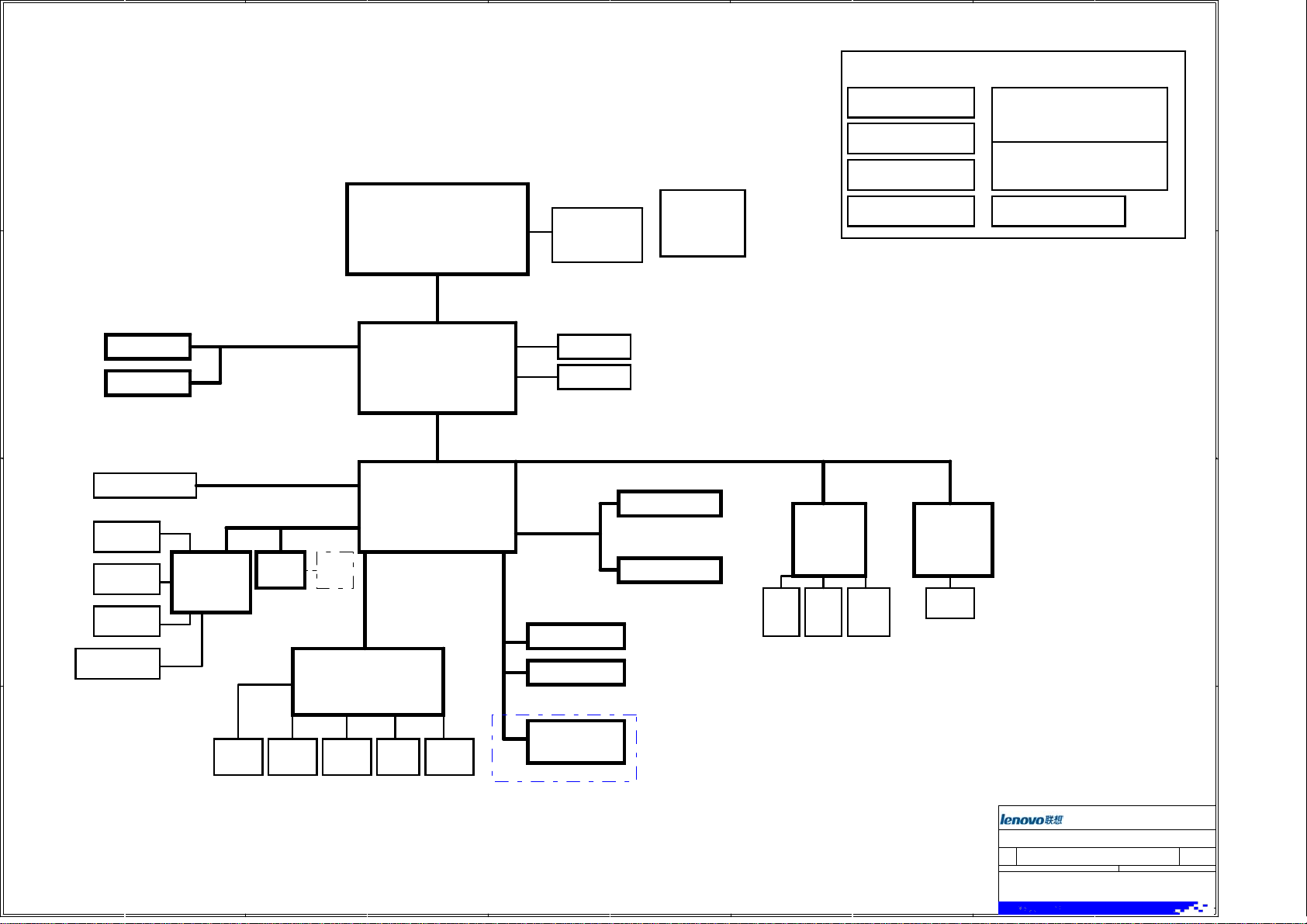

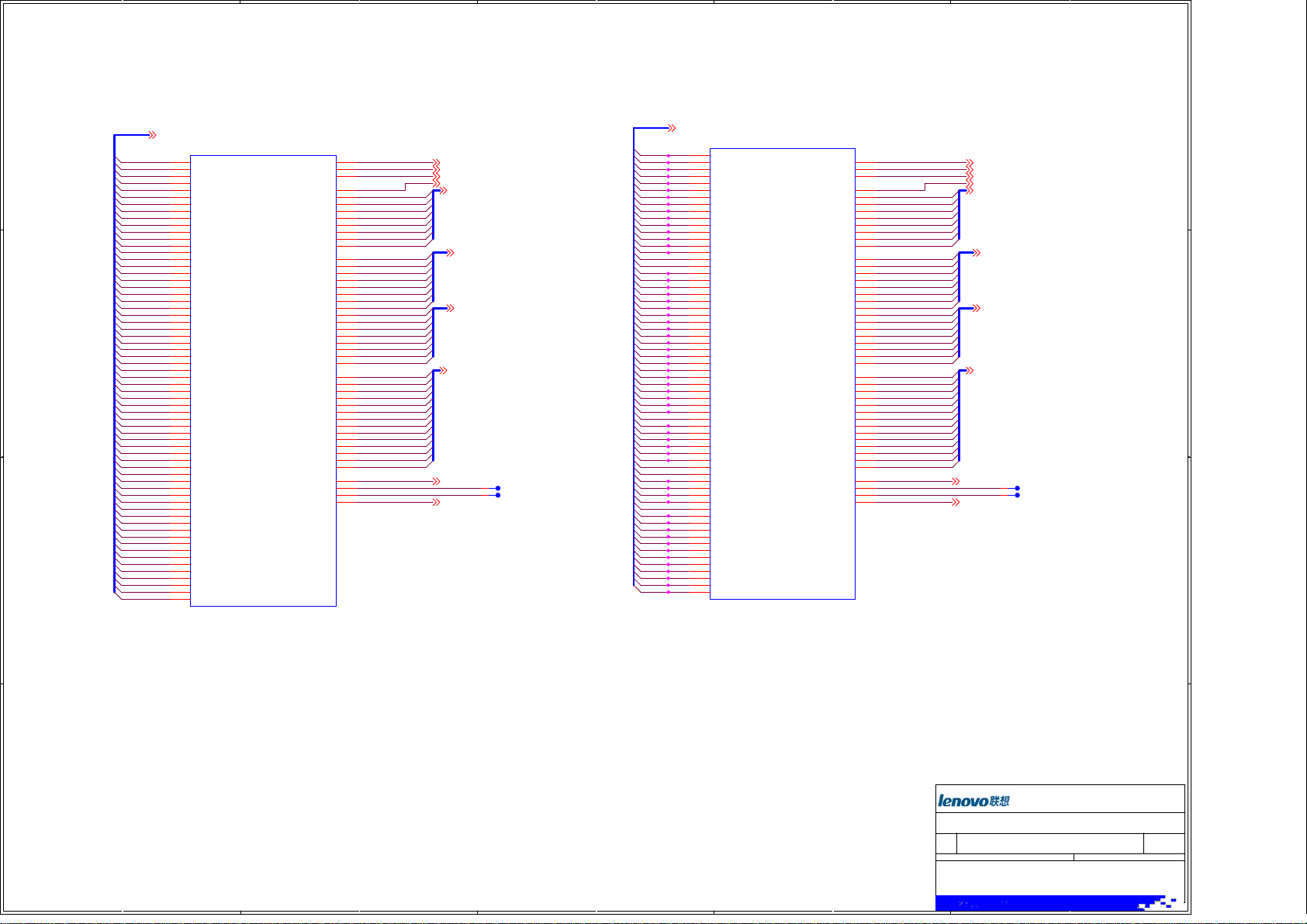

TAURUS2 BLOCK DIAGRAM

Yonah/Calistoga

VCORE_CPU

Yonah

479 Pins

(Micro-FCBGA)

+VCCP

FSB

4X133MHZ

P:6,7

+3V

CPU Thermal

Sensor

GMT

G792

P:6

Clocks

CK410

Silego:

+3V

SLG8LP453B

P:4

CPU VR

AC/BATT

Connector

BATT

Charger

ADI3207

P:36

P:37

OZ8602G_N

P:37

Switching

1.5V,+VCCP

3V,5V

LDO

2.5V

VTT_MEM(0.9V)

VDIMM(1.8V)

RTC Battery

OZ813

MAX8734

MAX8887EZK25

MAX8632

MAX8632

P:15

P:34

P:33

P:35

P:35

P:35

VTT_MEM

C C

P:14

P:14

VDIMM

DDR-SODIMM1

DDR-SODIMM2

DDRII SDRAM 1.8V, 667MHz

+VCCP(1.05V)

VDIMM(1.8V)

1.05V

+2.5V

945GM

Calistoga

1466 FCBGA

+1.5V

LVDS

R.G,B

LCD Panel

P:22

CRT port

P:21

P:8,9,10,11,12,13

DMI

AD23

REQ2

33MHZ, 3.3V PCI

CARD

READER

PIRQA#

+3VAUX

LAN

10/100/1G

BCM4401

RJ45

AD18

REQ0

P:25

P:24

+3VAUX

MDC

P:20

SATA 1.0

Azalia-LINK

+3V

SATA HDD

Headphone

B B

Azalia

External

MIC

Internal

MIC

InternalSpeaker

P:29

P:29

P:28

P:28

P:19

+5VA

AUDIO

ALC260(Codec)

TPA0312(Amp)

+3V

P:28

RJ11

P:25

+VCCP(1.05V)

+2.5V

+3VSUS

+3VALW

IT8511E

ICH7-M

+VCCP

652 BGA

P:15,16,17,18

+1.5VSUS

USB 2.0

+3V

PCI-Express x1

USB PORT -->0

+5VSUS

BlueTooth --> 4

3V

3G CARD -->0

3V,1.5V

MINI PCIe WLAN -->1

3V,1.5V

P:19

P:30

P:20

P:20

PIRQB#

CardBus

OZ711

P:26

1394

CARD

CONN

BUS

SLOT

P:26 P:27 P:27

176 Pins LQFP

P:31

+3VALW

+3VALW

APS

P:39

A A

+5V

Touchpad

P:30

+5V

Keyboard

P:30

FLASH

P:31

+5V

FAN 1

P:6

PVT Schematics Release

5

4

USB PORT -->1,2

+5VSUS

P:19

Dauther Board

LENOVO.NOD

LENOVO.NOD

LENOVO.NOD

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Document Number

Size Document Number

Size Document Number

C

C

C

Taurus2

Taurus2

Taurus2

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

3

2

HuZW LiXINP LiYJK LvXDA

140Thursday, June 29, 2006

140Thursday, June 29, 2006

140Thursday, June 29, 2006

1

Rev

Rev

Rev

s0.1

s0.1

s0.1

of

of

of

5

D D

C C

4

3

2

1

B B

A A

Title

Title

Title

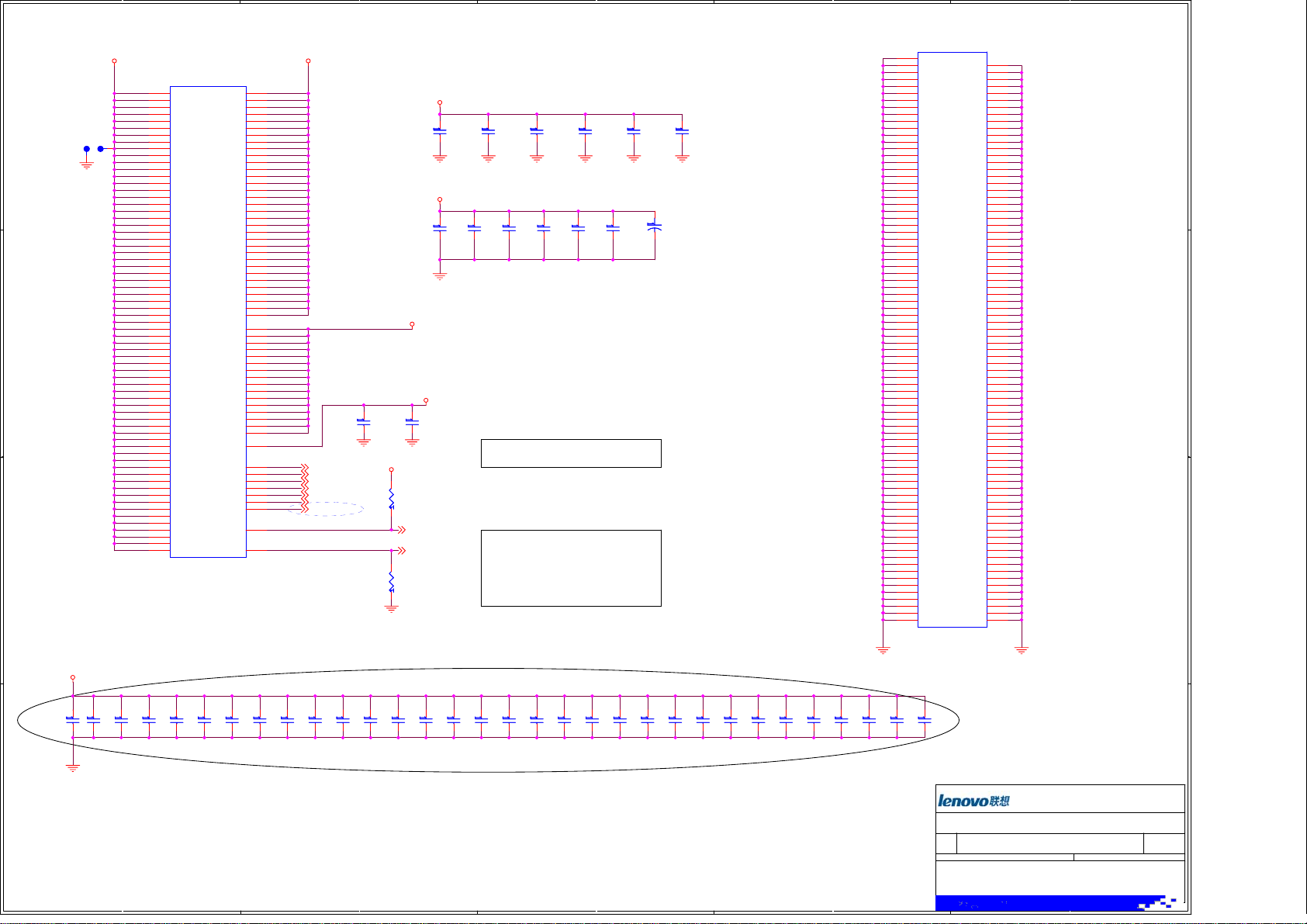

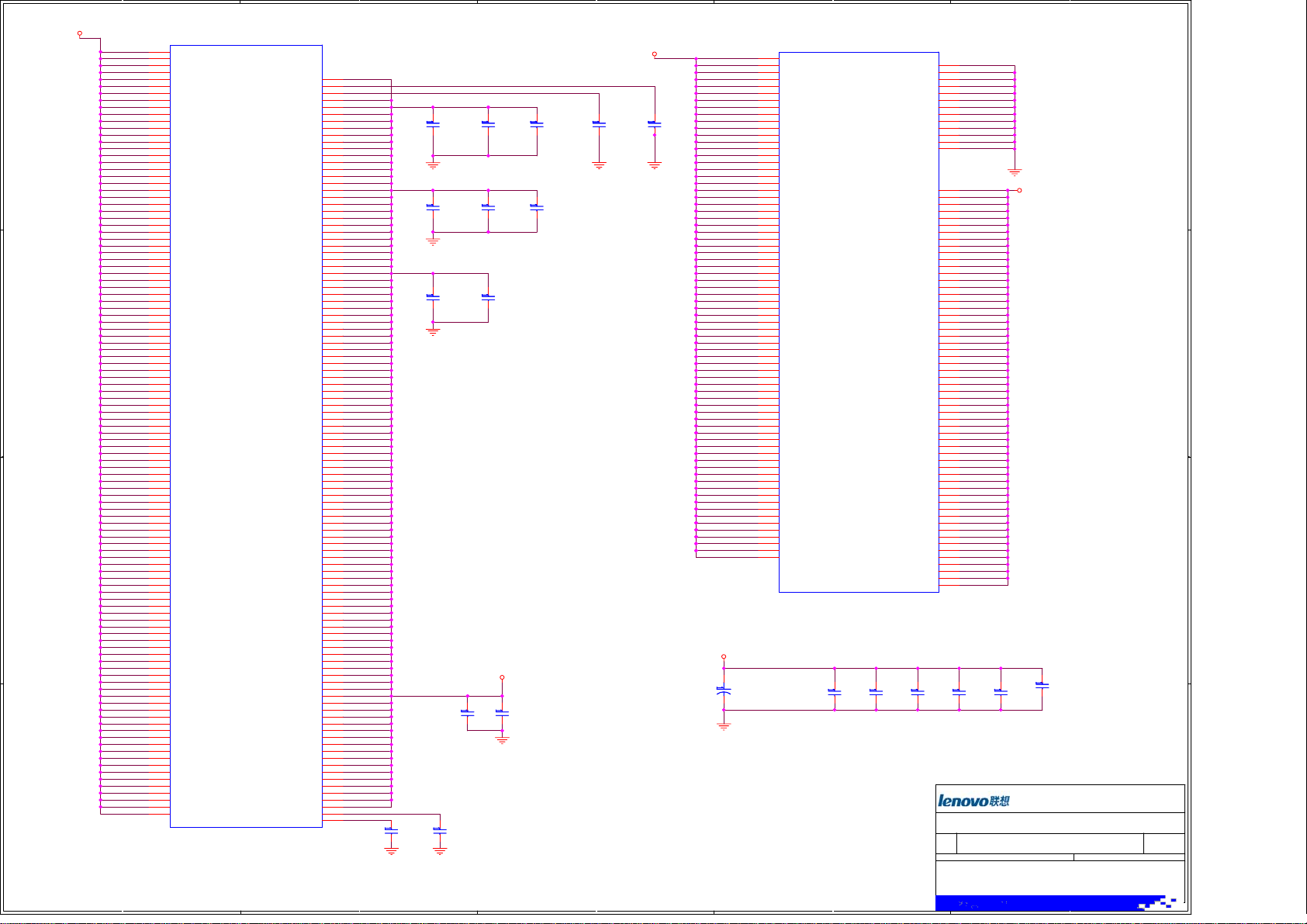

Power Sequence Block

Power Sequence Block

Power Sequence Block

Size Document Number

Size Document Number

Size Document Number

C

C

C

Taurus2

Taurus2

Taurus2

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

5

4

3

2

LENOVO.NOD

LENOVO.NOD

LENOVO.NOD

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

240Thursday, June 29, 2006

240Thursday, June 29, 2006

240Thursday, June 29, 2006

1

Rev

Rev

Rev

s0.1

s0.1

s0.1

of

of

of

ATI VGA PCIE

power

5

4

3

2

1

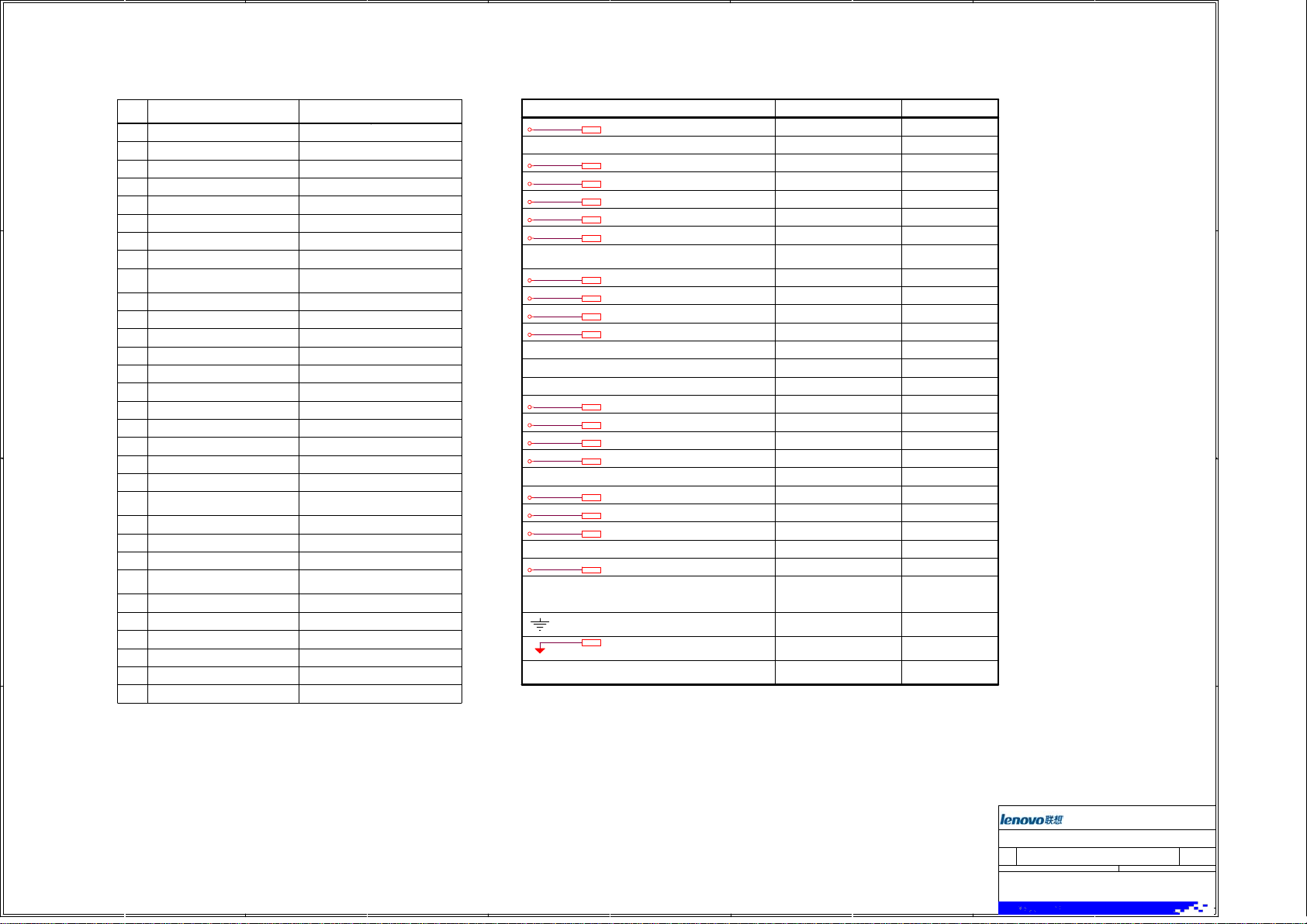

INDEX

ADIN

Label

ADIN

VIN

VCCRTC

+3VALW

+5VALW

3VAUX

VDIMM

+3VSUS

+5VSUS

+1.5V

+3V

+5V

+5VA

+5V_FAN

MOSVCC

VCORE_CPU

+VCCP

REF3V

ADIN 37

VIN 22,33,34,35,36,37

VCCRTC 15,18,31

+3VALW 15,17,22,23,30,31,33,37,39

+5VALW 32,33

3VAUX 20,24,25,33,34

VDIMM 8,10,14,32,35

+3VSUS 16,17,18,23,31,32,33,35

+5VSUS 18,19,32,33

+1.5V 10,11,12,17,18,20,32,34

+3V 4,6,8,11,12,14,15,16,17,18,19,20,21,22,23,24,26,27,28,30,31,32,33,36

+5V 6,18,19,21,26,28,30,31,32,33,36

+5VA 28

+5V_FAN 6

MOSVCC 22,26,27,30,32,33

VCORE_CPU 7,32,36

+VCCP 4,6,7,8,10,11,15,18,32,34

REF3V 37

GND

AUDGND 28,29

D D

C C

B B

DescriptionPg#

1

Block Diagram

2

Power Sequence Block

Frontpage

3

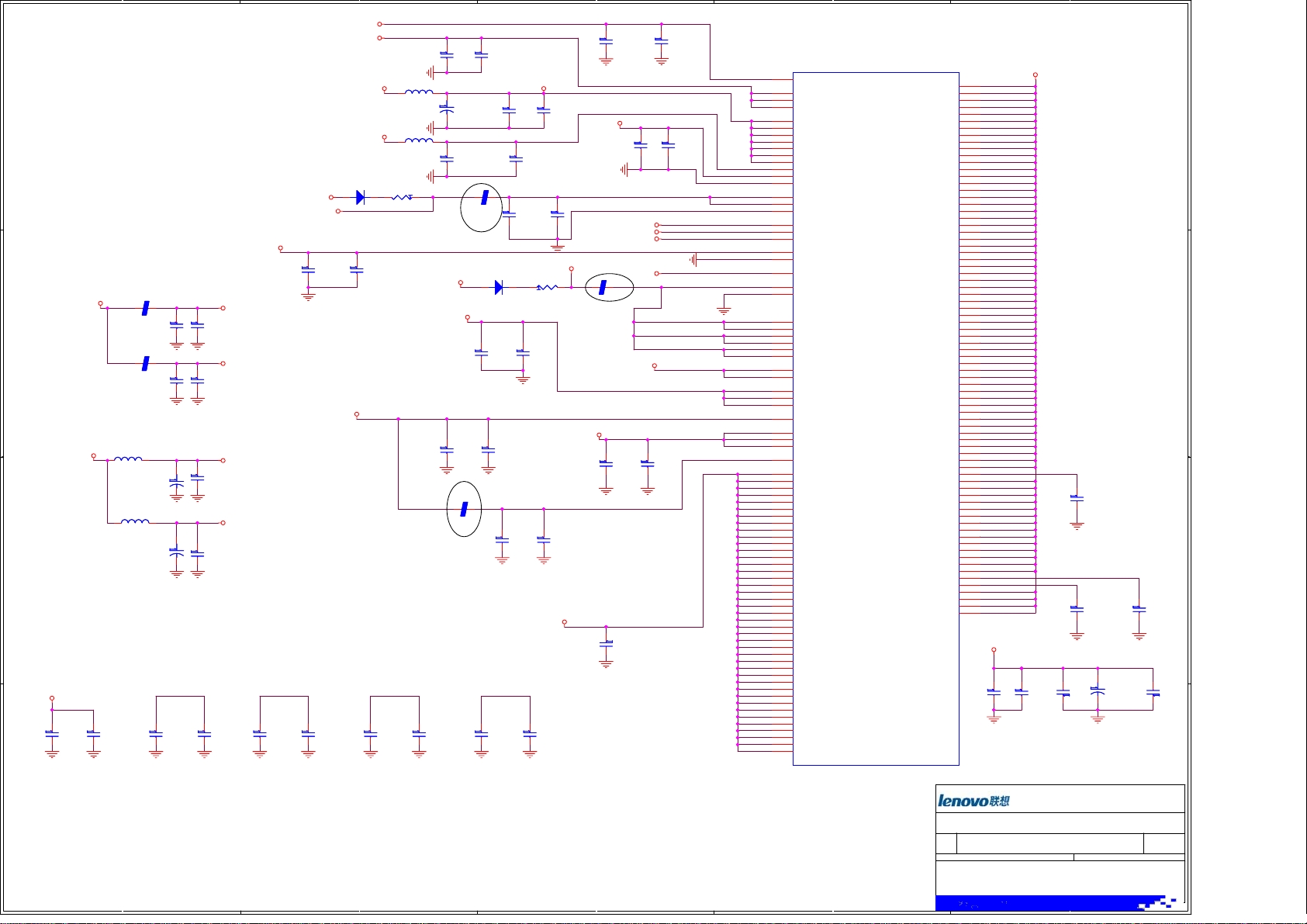

Clock Generator

4

6,7

Yonah CPU

8-13

Calistoga

14

DDR SO-DIMM

ICH7-M

15-18

19

USB & SATA

20

MINI PCIE, WWAN & MDC

21

CRT

22

LCD CONN

23

SWITCH & LED

24

BCM4401/5702 LAN

25

RJ11&RJ45

Cardbus OZ711

26

27

CARDREADER & 1394

28

AUDIO

29

AUDIO JACK

30

KB & TP & BT

31

IT8511E & FLASH

32

DISCHARGE

33

SYSTEM POWER

34

VCCP & GMCH CORE

35

DDR CORE

36

CPU CORE

37

BATTERY CHARGER

38

EMI PADs& Screws

39

APS

40

CHANGE LIST

DNI LIST

Power & Ground

Pg# Description

ALL PAGES

AC ADAPTER (19V)

MAIN BATTERY + (10~17V)

MAIN POWER (10~20V)

RTC & PCL POWER

(3_3V)

EC 3V always power

5V always power

LAN power

ICH7-M 1.5V SUS power

DDRII RAM 1.8V power

3V

5V

AGP I/O power

+3V

+5V

AUDIO analog 5V power

FAN 5V power

High Voltage to control MOS

CPU power

CPUIO powers(1.05V)

EC analog 3V power

DIGITAL GROUND

AUDIO GND

Control Signal

3VAUXEN

SUSON

SUSON

SUSON

SUSON

MAINON

MAINON

MAINON

MAINON

VFAN

RBAYON#

MAINON

VRON

MAINON

REFON

A A

Title

Title

Title

Frontpage

Frontpage

Frontpage

Size Document Number

Size Document Number

Size Document Number

C

C

C

Taurus2

Taurus2

Taurus2

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

5

4

3

2

LENOVO.NOD

LENOVO.NOD

LENOVO.NOD

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

340Thursday, June 29, 2006

340Thursday, June 29, 2006

340Thursday, June 29, 2006

1

Rev

Rev

Rev

s0.1

s0.1

s0.1

of

of

of

5

4

3

2

1

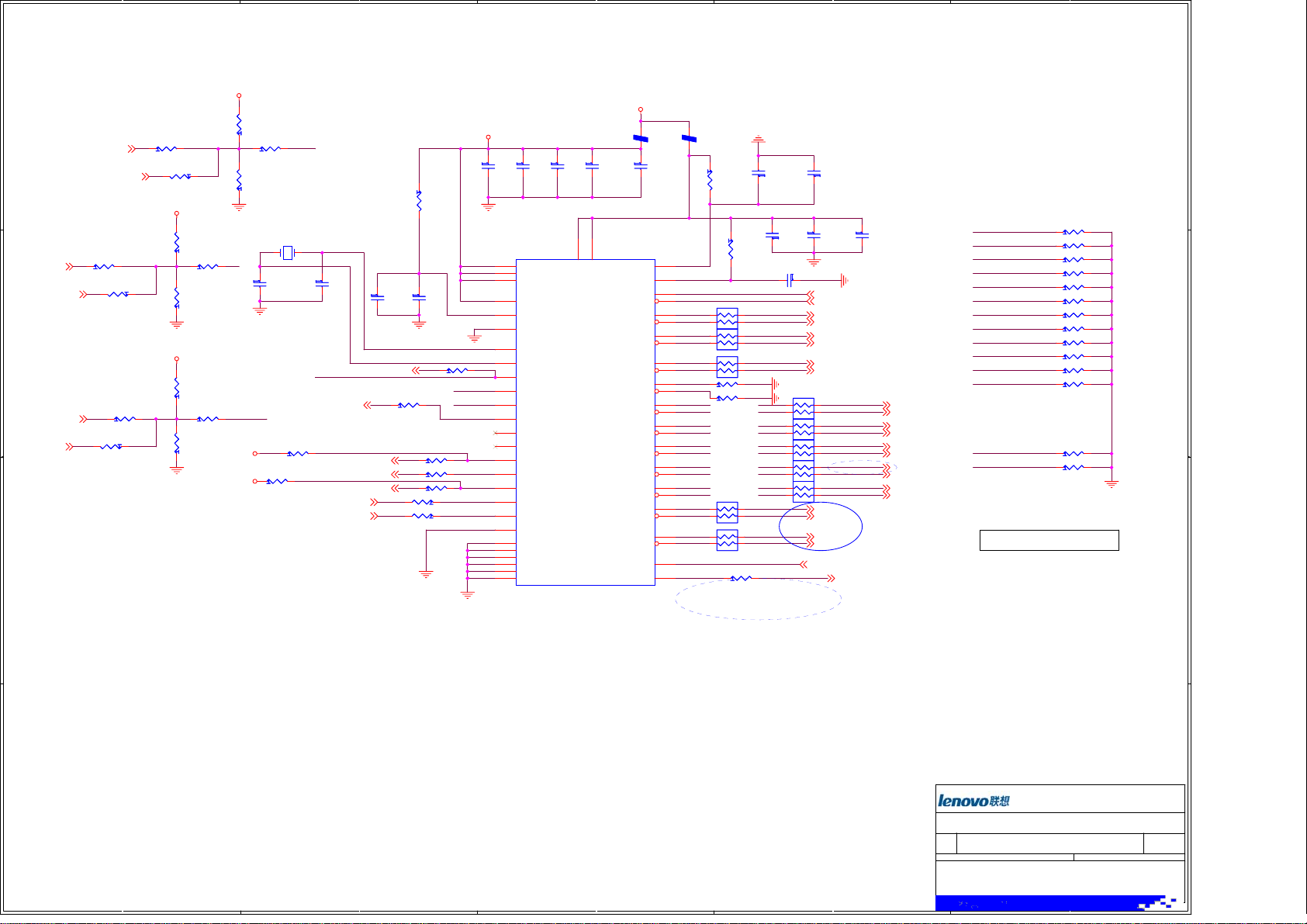

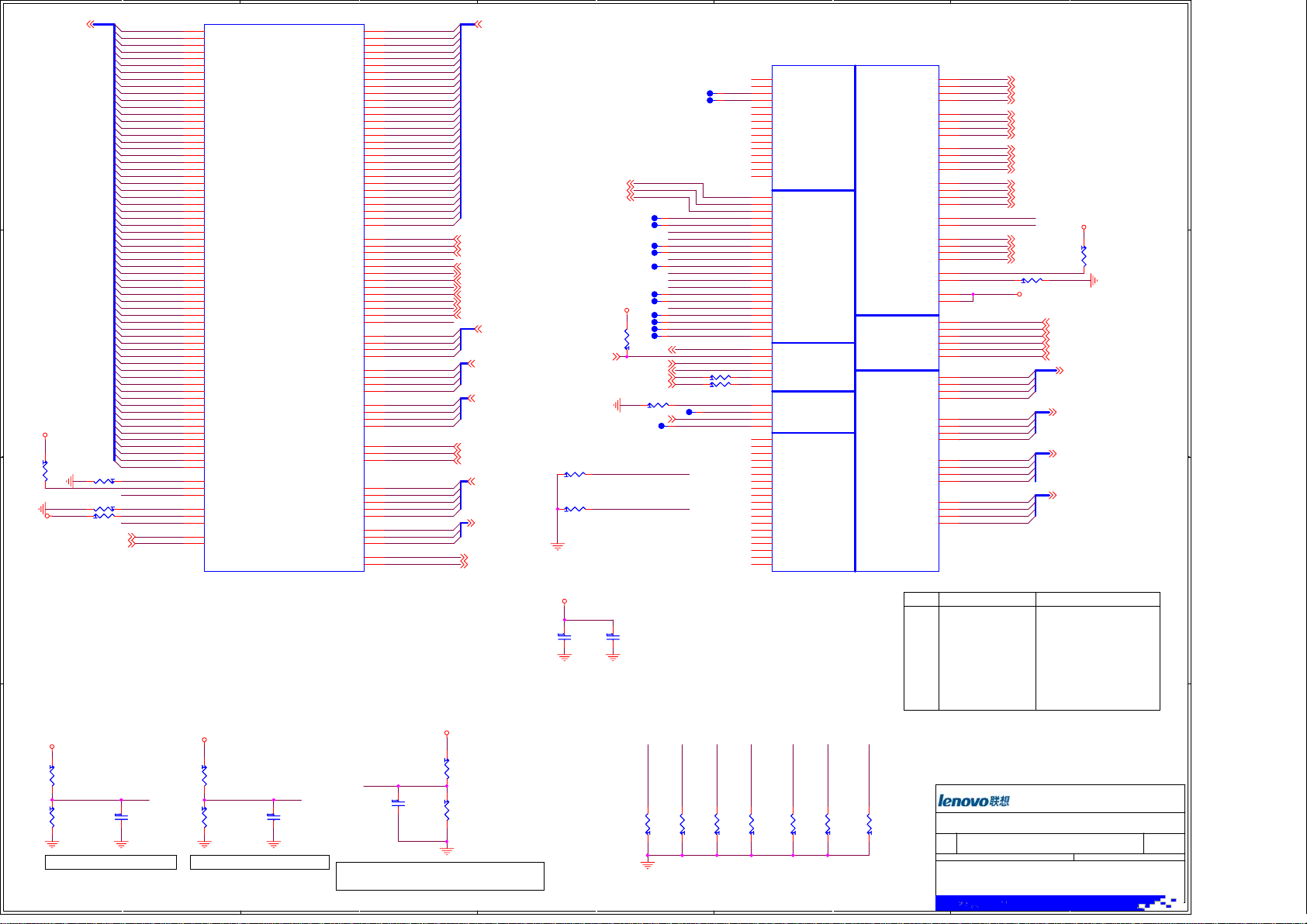

+VCCP

+3V

D D

R535 0 +-5%R_0402R535 0 +-5%R_0402

CPU_BSEL06

R532 1K +-1%R532 1K +-1%

MCH_BSEL08

+VCCP

R496

R496

1.2K +-1%

1.2K +-1%

NS

NS

R_0402

+VCCP

R_0402

0 +-5%

0 +-5%

R482

R482

1.2K +-1%

1.2K +-1%

R_0603

R_0603

NS

NS

R352

R352

1.2K +-1%

1.2K +-1%

R_0603

R_0603

NS

NS

R362

R362

1.2K +-1%

1.2K +-1%

R_0603

R_0603

NS

NS

R500 0 +-5%R_0402R500 0 +-5%R_0402

CPU_BSEL16

R463 1K +-1%R463 1K +-1%

MCH_BSEL18

C C

CPU_BSEL26

MCH_BSEL28

B B

R345 0 +-5%R_0402R345 0 +-5%R_0402

R363 1K +-1%R363 1K +-1%

R595

R595

R534

R534

1.2K +-1%

1.2K +-1%

NS

NS

R_0402

R_0402

8.2K +-5%

8.2K +-5%

R533

R533

1.2K +-1%

1.2K +-1%

R_0603

R_0603

NS

NS

BSEL1

R593

R593

BSEL2

8.2K +-5%

8.2K +-5%

R_0402

R_0402

+3V

R498 10K +-5% R_0603R498 10K +-5% R_0603

+3V

R594

R594

Y4

Y4

14.31818MHZ

14.31818MHZ

C311

C311

33PF/50V

33PF/50V

C_0603

C_0603

R353 10K +-5%

R353 10K +-5%

NS

NS

BSEL0

1

1

BSEL0

SMB_DATA_ICH714,16

PCLK_59131

SMB_CLK_ICH714,16

C310

C310

33PF/50V

33PF/50V

C_0603

C_0603

PCLK_OZ71126

PCLK_LAN24

PCLK_ICH716

VDD_A_CR

C314

C314

0.047UF/16V

0.047UF/16V

C_0402

C_0402

XTAL_OUT

CLK48_USB17

R378 33 +-5%R378 33 +-5%

For SLG8LP453.

R354

R354

2 +-5%

2 +-5%

R_0603

R_0603

C324

C324

10uF/6.3V

10uF/6.3V

C_0805

C_0805

XTAL_IN

R381 33 +-5%R381 33 +-5%

R346 33 +-5%R346 33 +-5%

R380 33 +-5%R380 33 +-5%

R379 33 +-5%R379 33 +-5%

R326 0 +-5%R326 0 +-5%

R325 0 +-5%R325 0 +-5%

CGCLK_SMB

CGDAT_SMB

IREF

1

1

C315

C315

0.1UF/10V

0.1UF/10V

C_0402

C_0402

VDD_48

VDD_REF

VDD_PCI0

PCI_STOP#

CPU_STOP#

CPU1

CPU1#

CPU0

CPU0#

CPU_2_ITP/SRC_7

CPU2_ITP/SRC7#

SRC6/CLKREQA#

SRC6#/CLKREQB#

SRC5

SRC5#

SRC4

SRC4#

SRC3

SRC3#

SRC2

SRC2#

SRC1

SRC1#

DREF_SSCLK

DREF_SSCLK#

DOT96

DOT96#

VTT_PWRGD#/PD

1

REF

VCC3_CLK

0.047UF/16V

0.047UF/16V

BSEL1

BSEL2

PCI2

PCIF0

C366

C366

C_0402

C_0402

21

28

34

42

37

38

50

49

12

16

53

56

46

47

39

13

29

45

51

C313

C313

0.047UF/16V

0.047UF/16V

C_0402

C_0402

U19

U19

VDD_SRC0

VDD_SRC1

VDD_SRC2

VDD_CPU

VDD_A

VSS_A

XTAL_IN

XTAL_OUT

FSA/USB_48

FSB/TEST_MODE

REF1/FSC/TEST_SEL

5

PCI5

4

PCI4

3

PCI3

PCI2/REQ_SEL

9

PCIF1/DREF_SEL

8

PCIF0/ITP_EN

SCLOCK

SDATA

IREF

VSS_48

VSS_SRC

VSS_CPU

2

VSS_PCI0

6

VSS_PCI1

VSS_REF

SLG8LP453B/SLG84420

SLG8LP453B/SLG84420

C363

C363

0.1UF/10V

0.1UF/10V

C_0402

C_0402

7

VDD_PCI1

1

SLG8LP453 buildin dumping and terminal res.

1

FB23

600 OHM/1.5A

600 OHM/1.5A

FB23

600 OHM/1.5A

600 OHM/1.5A

R473

R473

2 +-5%

2 +-5%

R_0603

R_0603

FB22

FB22

C345

C345

10uF/6.3V

10uF/6.3V

C_0805

C_0805

11

48

55

54

41

40

44

43

36

35

33

32

31

30

26

27

24

25

22

23

19

20

17

18

14

15

10

52

RN4

RN4

CPU1

1 2

CPU#1

3 4

RN3

RN3

CPU0

1 2

CPU#0

3 4

RN5

RN5

ITP

1 2

ITP#

3 4

R338 10K +-5%

R338 10K +-5%

NS

NS

R364 10K +-5%

R364 10K +-5%

PCIE5 PCIE5

PCIE#5

PCIE4

PCIE#4

PCIE3

PCIE#3

PCIE2

PCIE#2

PCIE1

PCIE1#

NS

NS

RN15 0X2

RN15 0X2

3 4

1 2

RN14 0X2

RN14 0X2

3 4

1 2

CKGEN_EN#

R334 12.1 +-1%R334 12.1 +-1%

Check the CLK14_ICH6 clock SI after bring up!!

If need changed to 33R

+V3.3S_CLKVDD1

R337

R337

1 +-5%

1 +-5%

R_0603

R_0603

VDD_REF_CR

0X2

0X2

0X2

0X2

R_SMT4_0402

R_SMT4_0402

R_SMT4_0402

R_SMT4_0402

0X2

0X2

NS

NS

R_SMT4_0402

R_SMT4_0402

PCIE#5

PCIE#4

PCIE4

PCIE#3

PCIE3

PCIE#2

PCIE2

PCIE1#

PCIE1

R_SMT4_0402

R_SMT4_0402

DREFSSCLK

DREFSSCLK#

R_SMT4_0402

R_SMT4_0402

DREFCLK

DREFCLK#

C365

C365

0.047UF/16V

0.047UF/16V

C_0402

C_0402

C413

C413

0.047UF/16V

0.047UF/16V

C_0402

C_0402

C312

C312

1 2

3 4

1 2

3 4

1 2

3 4

1 2

3 4

1 2

3 4

C414

C414

10uF/6.3V

10uF/6.3V

C_0805

C_0805

C350

C350

0.1UF/10V

0.1UF/10V

C_0402

C_0402

0.047UF/16V

0.047UF/16V

C_0402

C_0402

STP_PCI# 17

STP_CPU# 17

CLK_MCH_BCLK 8

CLK_MCH_BCLK# 8

CLK_CPU_BCLK 6

CLK_CPU_BCLK# 6

CLK_ITP 6

CLK_ITP# 6

0X2

0X2

RN19

RN19

0X2

0X2

R_SMT4_0402

R_SMT4_0402

RN30

RN30

0X2

0X2

R_SMT4_0402

R_SMT4_0402

RN18

RN18

0X2

0X2

R_SMT4_0402

R_SMT4_0402

RN17

RN17

CLK_PCIE_SATA#

CLK_PCIE_SATA

0X2

0X2

RN16

RN16

R_SMT4_0402

R_SMT4_0402

R_SMT4_0402

R_SMT4_0402

DREFSSCLK 8

DREFSSCLK# 8

DREFCLK 8

DREFCLK# 8

CKGEN_EN# 36

C513

C513

10uF/6.3V

10uF/6.3V

C_0805

C_0805

PCIECLK_3G 20

PCIECLK_3G# 20

PCIECLK_WLAN# 20

PCIECLK_WLAN 20

CLK_PCIE_MCH# 8

CLK_PCIE_MCH 8

CLK_PCIE_SATA# 15

CLK_PCIE_SATA 15

CLK_PCIE_ICH# 17

CLK_PCIE_ICH 17

Note:Pls confirm need BIOS modify?

CLK14_ICH7 17

For SLG8LP453 buildin Pulldown res.

R_0402NS

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK

CLK_MCH_BCLK#

DREFSSCLK

DREFSSCLK#

DREFCLK

DREFCLK#

CLK_PCIE_ICH#

CLK_PCIE_ICH

CLK_PCIE_SATA#

CLK_PCIE_SATA

CLK_PCIE_MCH

CLK_PCIE_MCH#

R_0402NS

R316 54.9 +-1%

R316 54.9 +-1%

R_0402NS

R_0402NS

R317 54.9 +-1%

R317 54.9 +-1%

R_0402NS

R_0402NS

R318 54.9 +-1%

R318 54.9 +-1%

R_0402NS

R_0402NS

R319 54.9 +-1%

R319 54.9 +-1%

R_0402NS

R_0402NS

R497 54.9 +-1%

R497 54.9 +-1%

R_0402NS

R_0402NS

R530 54.9 +-1%

R530 54.9 +-1%

R_0402NS

R_0402NS

R389 54.9 +-1%

R389 54.9 +-1%

R_0402NS

R_0402NS

R465 54.9 +-1%

R465 54.9 +-1%

R_0402NS

R_0402NS

R505 54.9 +-1%

R505 54.9 +-1%

R_0402NS

R_0402NS

R495 54.9 +-1%

R495 54.9 +-1%

R_0402NS

R_0402NS

R456 54.9 +-1%

R456 54.9 +-1%

R_0402NS

R_0402NS

R531 54.9 +-1%

R531 54.9 +-1%

R_0402NS

R_0402NS

R501 54.9 +-1%

R501 54.9 +-1%

R_0402NS

R_0402NS

R502 54.9 +-1%

R502 54.9 +-1%

change from 49.9 to 54.9

Place termination close to source IC

For SLG8LP453 differential clock remove the 33R.

FS_C FS_B FS_A CPU(MHz)

----------------------------------------------- 0 0 0 266.6

0 0 1 133.3

A A

5

0 1 0 200.0

0 1 1 166.6

1 0 0 333.3

1 0 1 100.0

1 1 0 400.0

1 1 1 Reserve

Title

Title

Title

CLOCK GENERATOR

CLOCK GENERATOR

CLOCK GENERATOR

Size Document Number

Size Document Number

Size Document Number

Custom

Custom

Custom

Taurus2

Taurus2

Taurus2

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

4

3

2

LENOVO.NOD

LENOVO.NOD

LENOVO.NOD

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

440Thursday, June 29, 2006

440Thursday, June 29, 2006

440Thursday, June 29, 2006

1

Rev

Rev

Rev

s0.1

s0.1

s0.1

of

of

of

5

D D

C C

4

3

2

1

B B

A A

Title

Title

Title

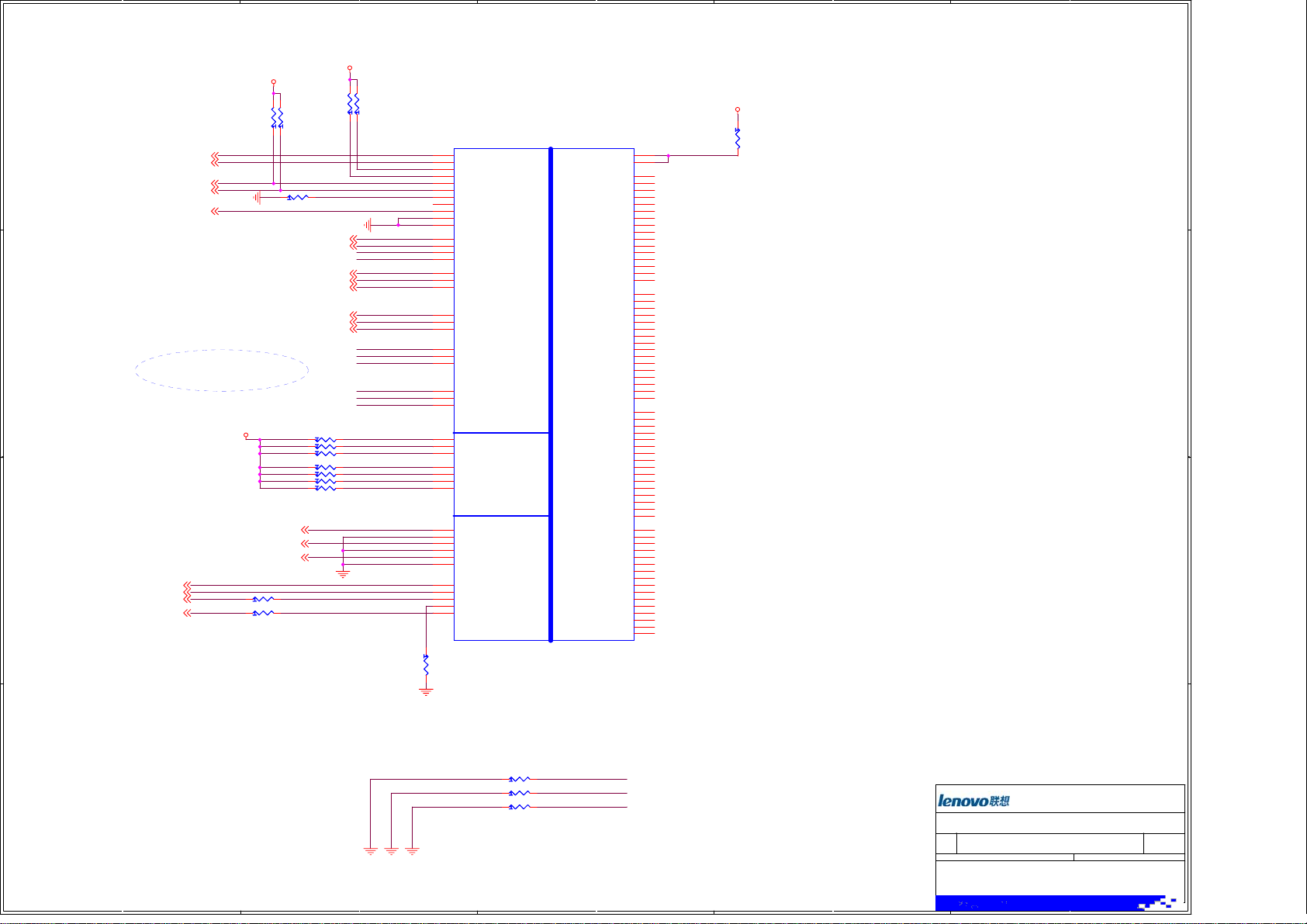

THERMAL MONITOR/ITP

THERMAL MONITOR/ITP

THERMAL MONITOR/ITP

Size Document Number

Size Document Number

Size Document Number

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

5

4

3

2

Taurus2

Taurus2

Taurus2

LENOVO.NOD

LENOVO.NOD

LENOVO.NOD

1

Rev

Rev

Rev

V0.1

V0.1

V0.1

540Thursday, June 29, 2006

540Thursday, June 29, 2006

540Thursday, June 29, 2006

of

of

of

5

4

3

2

1

H_A#[31:3]8

D D

H_ADSTB#08

H_REQ#[4:0]8

H_A#[31:3]8

C C

H_ADSTB#18

H_A20M#15

H_FERR#15

H_IGNNE#15

H_STPCLK#15

H_INTR15

B B

A A

PM_SYSRST#16,17

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11 H_D#39

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_NMI15

TDI

TMS

TRST#

TCK

TDO

CLK_ITP#4

CLK_ITP4

TCK

H_CPURST#

H_CPURST#8

PRDY#

BPM3#

BPM2#

BPM1#

BPM0#

5

54.9 +-1%

54.9 +-1%

NS

NS

PREQ#

R392

R392

54.9 +-1%

54.9 +-1%

U3A

U3A

J4

L4

M3

K5

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

Yonah ULV FCBGA

Yonah ULV FCBGA

+VCCP

R357

R357

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

RSVD[10]

RSVD[11]

54.9 +-1%

54.9 +-1%

ADDR GROUP

0

ADDR GROUP

0

ADDR GROUP

1

ADDR GROUP

1

PROCHOT#

THERM

THERM

THERMTRIP#

RESERVED

RESERVED

R491

R491

54.9 +-1%

54.9 +-1%

R_0603

R_0603

R366

R366

CRB 54.9R

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALSH CLK

XDP/ITP SIGNALSH CLK

THERMDA

THERMDC

BCLK[0]

BCLK[1]

RSVD[12]

RSVD[13]

RSVD[14]

RSVD[15]

RSVD[16]

RSVD[17]

RSVD[18]

RSVD[19]

RSVD[20]

R367 22.6 +-1%

R367 22.6 +-1%

R492 22.6 +-1%

R492 22.6 +-1%

+VCCP

+3V

Q13

Q13

1

1

H_D#[63:0]8

H_DSTBN#08

H_DSTBP#08

H_DINV#08

H_DSTBN#18

H_DSTBP#18

H_DINV#18

R200

R200

1K +-1%

1K +-1%

R_0603

R_0603

CPU_BSEL04

CPU_BSEL14

CPU_BSEL24

R358 20K +-1%

R358 20K +-1%

NS

NS

R320 10K +-1%R320 10K +-1%

GMT_VCC_W20

THERMDA_CPU

C588

C_0603 C588

C_0603

2200PF/50V

2200PF/50V

THERMDC_CPU

3

3

C591

C591

2200PF/50V

2200PF/50V

C_0603

C_0603

2

2

CON7

CON7

1

2

3

1ST_FAN

1ST_FAN

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26TDO

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

GTLREF0

R31

R31

2K +-1%

2K +-1%

ACLKPH

R_0603

R_0603

DCLKPH

R486 0 +-5% R_0603

R486 0 +-5% R_0603

NS

NS

THERMDA_VGA

THERMDC_VGA

+5V_FAN

FAN_FG1

R104 10K +-5% R_0603R104 10K +-5% R_0603

H1

H_ADS# 8

E2

H_BNR# 8

G5

H_BPRI# 8

H5

H_DEFER# 8

F21

H_DRDY# 8

E1

H_DBSY# 8

F1

H_BREQ#0 8

D20

B3

H4

B1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

A25

C7

A22

A21

H_IERR#

H_INIT# 15

H_LOCK# 8

H_CPURST#

H_RS#0

H_RS#1

H_RS#2

H_TRDY# 8

H_HIT# 8

H_HITM# 8

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TCK

TDI

TMS

TRST# H_D#60

TP_PROCHOT#

THERMDA_CPU

THERMDC_CPU

PM_THRMTRIP# 8,15

TP76TP76

CLK_CPU_BCLK 4

CLK_CPU_BCLK# 4H_SMI#15

+3V

R597

R597

1K +-5%

1K +-5%

NS

NS

R76

R76

56 +-5%

56 +-5%

H_RS#[2:0] 8

+VCCP

R312

R312

68 +-5%

68 +-5%

+VCCP

C63

C63

100PF/50V

100PF/50V

C_0402

C_0402

H_CPURST# 8

TDI

TP_PROCHOT# 36

+VCCP

R65

R65

54.9 +-1%

54.9 +-1%

R_0603

R_0603

T22

D2

F6

R490

R490

54.9 +-1%

54.9 +-1%

R_0603

R_0603

NS

NS

NS

NS

D3

C1

AF1

D22

C23

C24

+VCCP

0.1UF/10V

0.1UF/10V

C595

C595

NS

NS

R596

R596

54.9 +-1%

54.9 +-1%

R_0603

R_0603

CON71

CON71

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

MLX-CON28-U

MLX-CON28-U

NS

NS

4

ACLKPH

DCLKPH

51 +-5%

51 +-5%

R288

R288

R311

R311

1K +-5%

1K +-5%

NS

NS

100 +-5%

100 +-5%

R487

R487

C589

C589

0.1UF/10V

0.1UF/10V

MMBT3904

MMBT3904

For systeam ambient TEMP

3

U3B

U3B

E22

D[0]#

F24

D[1]#

E26

D[2]#

H22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H26

D[12]#

F26

D[13]#

K22

D[14]#

H25

D[15]#

H23

DSTBN[0]#

G22

DSTBP[0]#

J26

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L25

D[20]#

L22

D[21]#

L23

D[22]#

M23

D[23]#

P25

D[24]#

P22

D[25]#

P23

D[26]#

T24

D[27]#

R24

D[28]#

L26

D[29]#

T25

D[30]#

N24

D[31]#

M24

DSTBN[1]#

N25

DSTBP[1]#

M26

DINV[1]#

AD26

GTLREF

C26

TEST1

D25

TEST2

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

Yonah ULV FCBGA

Yonah ULV FCBGA

C392

C392

+5V_FAN

U15

U15

1

FAN1

2

RESET#

3

THERM_SET

FAN_FG1

4

FG1

5

DGND1

6

VCC

7

DXP1

8

SGND1

9

DXP2

10

SGND2

GMT-G792SFX

GMT-G792SFX

20P_QSOP_150

20P_QSOP_150

NOTE:

1.hardware shutdown for sensor2.

THERM_SET=[(Tset-72) x 0.02+0.34] x VCC

THERM_SET pin voltage from 0.35VCC to 0.95 VCC

and trigger point set from 72°C to 102°C,2°C a step.

2.software shutdown for sensor1,sensor3.

T8

*PADT8*PAD

C75

C75

4.7UF/10V

4.7UF/10V

C_0805

C_0805

+5V_FAN

D[32]#

D[33]#

D[34]#

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

DATA GRP 2

DATA GRP 2

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

DATA GRP 3

DATA GRP 3

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

MISC

MISC

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

HWPG 31,33

0.1UF/25VC_0603

0.1UF/25VC_0603

DXP3

SGND3

THERM#

CLK

ALERT#

SDA

DGND2

SCL

NC

DVCC

R85

R85

0 +-5%R_0603

0 +-5%R_0603

C76

C76

0.1UF/10V

0.1UF/10V

2

SLP#

PSI#

11

12

13

14

15

16

17

18

19

20

NS

NS

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

COMP0

R26

COMP1

U26

COMP2

U1

COMP3

V1

E5

B5

D24

D6

D7

AE6

THERMDA_DDR

THERMDC_DDR

ICH_SUSCLK

TEMP_ALERT#

MBDATA

MBCLK

10uF/6.3V

10uF/6.3V

H_D#[63:0] 8

H_DSTBN#2 8

H_DSTBP#2 8

H_DINV#2 8

H_D#[63:0] 8H_D#[63:0]8

H_DSTBN#3 8

H_DSTBP#3 8

H_DINV#3 8

R34 27.4 +-1%R_0603R34 27.4 +-1%R_0603

R69 54.9 +-1%R_0603R69 54.9 +-1%R_0603

R86 27.4 +-1%R_0603R86 27.4 +-1%R_0603

R56 54.9 +-1%R_0603R56 54.9 +-1%R_0603

H_DPRSTP# 15,36

H_DPSLP# 15

H_DPWR# 8

H_PWRGD 15

H_CPUSLP# 8

PSI# 36

T59 *PADT59 *PAD

ICH_SUSCLK 17

TEMP_ALERT# 31

MBDATA 31,37

MBCLK 31,37

+5V

C582

C582

1000PF/50V

1000PF/50V

Title

Title

Title

DOTHAN CPU (HOST BUS)-1

DOTHAN CPU (HOST BUS)-1

DOTHAN CPU (HOST BUS)-1

Size Document Number

Size Document Number

Size Document Number

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

Layout note:

Comp0,2 connect with Zo=27.4ohm, make

trace length shorter than 0.5".

Comp1,3 connect with Zo=55ohm, make

trace length shorter than 0.5".

For VGA ambient TEMP

LENOVO.NOD

LENOVO.NOD

LENOVO.NOD

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

Taurus2

Taurus2

Taurus2

1

C590

C590

2200PF/50V

2200PF/50V

C_0603

C_0603

+5V

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#40

H_D#41H_D#9

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#61

H_D#62

H_D#63

C586

C586

H_DINV#[3:0] 8

H_DSTBP#[3:0] 8

H_DSTBN#[3:0] 8

3

3

1

1

2

2

640Thursday, June 29, 2006

640Thursday, June 29, 2006

640Thursday, June 29, 2006

of

of

of

Q33

Q33

MMBT3904

MMBT3904

Rev

Rev

Rev

s0.1

s0.1

s0.1

5

VCORE_CPU VCORE_CPU

U3C

U3C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

D D

TP77TP77

TP78TP78

C C

B B

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

Yonah ULV FCBGA

Yonah ULV FCBGA

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

<NO-STUFF>

<NO-STUFF>

AF7

AE7

CPU_VID0 36

CPU_VID1 36

CPU_VID2 36

CPU_VID3 36

CPU_VID4 36

CPU_VID5 36

CPU_VID6 36

4

C233

C233

10uF/6.3V

10uF/6.3V

+VCCP

C203

C203

0.01UF/16V

0.01UF/16V

C_0402

C_0402

VCORE_CPU

R314

R314

100 +-1%

100 +-1%

R_0603

R_0603

VCCSENSE 36

VSSSENSE 36

R70

R70

100 +-1%

100 +-1%

R_0603

R_0603

+VCCP

+VCCP

+VCCP

C248

C249

C249

C248

0.1UF/10V

0.1UF/10V

C263

C263

0.1UF/10V

0.1UF/10V

C46

C46

0.1UF/10V

0.1UF/10V

C260

C260

0.1UF/10V

0.1UF/10V

C240

C240

0.1UF/10V

0.1UF/10V

C201

C201

0.1UF/10V

0.1UF/10V

Layout note:

Place c233 c203 near pin B26

Layout note:

Route VCCSENSE and VSSSENSE

traces at 27.4 OHM with 50

mil spacing ,place PU and PD

within 1 inch of CPU

3

C284

C289

C289

C284

0.1UF/10V

0.1UF/10V

0.1UF/10V

0.1UF/10V

C256

C256

0.1UF/10V

0.1UF/10V

C281

C281

0.1UF/10V

0.1UF/10V

0.1UF/10V

0.1UF/10V

+

+

CT3

CT3

220UF/2.5V

220UF/2.5V

TAJ_E

TAJ_E

C291

C291

0.1UF/10V

0.1UF/10V

2

U3D

U3D

A2

VSS[999]

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

A26

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Yonah ULV FCBGA

Yonah ULV FCBGA

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

<NO-STUFF>

<NO-STUFF>

1

VCORE_CPU

C299 22UF/6.3VC299 22UF/6.3V

A A

C254 22UF/6.3VC254 22UF/6.3V

C250 22UF/6.3VC250 22UF/6.3V

5

C270 22UF/6.3VC270 22UF/6.3V

C264 22UF/6.3VC264 22UF/6.3V

C282 22UF/6.3VC282 22UF/6.3V

C292 22UF/6.3VC292 22UF/6.3V

C288 22UF/6.3VC288 22UF/6.3V

C585 22UF/6.3VC585 22UF/6.3V

C294 22UF/6.3VC294 22UF/6.3V

C199 22UF/6.3VC199 22UF/6.3V

C53 22UF/6.3VC53 22UF/6.3V

C202 22UF/6.3VC202 22UF/6.3V

4

C242 22UF/6.3VC242 22UF/6.3V

C211 22UF/6.3VC211 22UF/6.3V

C247 22UF/6.3VC247 22UF/6.3V

C261 22UF/6.3VC261 22UF/6.3V

C253 22UF/6.3VC253 22UF/6.3V

C280 22UF/6.3VC280 22UF/6.3V

C269 22UF/6.3VC269 22UF/6.3V

3

C290 22UF/6.3VC290 22UF/6.3V

C285 22UF/6.3VC285 22UF/6.3V

C293 22UF/6.3VC293 22UF/6.3V

C67 22UF/6.3VC67 22UF/6.3V

C300 22UF/6.3VC300 22UF/6.3V

C198 22UF/6.3VC198 22UF/6.3V

C204 22UF/6.3VC204 22UF/6.3V

C200 22UF/6.3VC200 22UF/6.3V

C241 22UF/6.3VC241 22UF/6.3V

2

C251 22UF/6.3VC251 22UF/6.3V

C243 22UF/6.3VC243 22UF/6.3V

C255 22UF/6.3VC255 22UF/6.3V

LENOVO.NOD

LENOVO.NOD

LENOVO.NOD

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

Taurus2

Taurus2

Taurus2

HuZW LiXINP LiYJK LvXDA

740Thursday, June 29, 2006

740Thursday, June 29, 2006

740Thursday, June 29, 2006

1

of

of

of

Title

Title

Title

DOTHAN CPU (POWER/NC)-2

DOTHAN CPU (POWER/NC)-2

DOTHAN CPU (POWER/NC)-2

Size Document Number

Size Document Number

Size Document Number

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

Rev

Rev

Rev

s0.1

s0.1

s0.1

5

U5A

W11

AA10

AB11

AC11

AD10

AB7

AA9

AB8

AA4

AA7

AA2

AA6

AA1

AB4

AC9

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD4

AC8

AG2

AG1

F1

J1

H1

J6

H3

K2

G1

G2

K9

K1

K7

J8

H4

J3

K11

G4

T10

T3

U7

U9

U11

T11

W9

T1

T8

T4

W7

U5

T9

W6

T5

W4

W3

Y3

Y7

W5

Y10

W2

Y8

E1

E2

E4

Y1

U1

W1

+VCCP

U5A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_CLKIN

H_CLKIN#

CALISTOGA_1p0

CALISTOGA_1p0

R395

R395

221 +-1%

221 +-1%

R_0603

R_0603

R383

R383

100 +-1%

100 +-1%

R_0603

R_0603

H_YSWING

HOST

HOST

C438

C438

0.1UF/10V

0.1UF/10V

H_D#[63:0]6

D D

C C

+VCCP

R393

R393

54.9 +-1%

54.9 +-1%

R390 24.9 +-1%R390 24.9 +-1%

R_0603

R_0603

R382 24.9 +-1%R382 24.9 +-1%

+VCCP

R387 54.9 +-1%R387 54.9 +-1%

CLK_MCH_BCLK4

CLK_MCH_BCLK#4

R394

R394

221 +-1%

221 +-1%

R_0603

R_0603

H_XSWING

R386

R386

100 +-1%

100 +-1%

R_0603

R_0603

+VCCP

B B

A A

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12 H_A#15

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28 H_A#31

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

C398

C398

0.1UF/10V

0.1UF/10V

Layout Note:10mil width Layout Note:10mil width

5

4

+VCCP

H_A#[31:3] 6

H_ADS# 6

H_ADSTB#0 6

H_ADSTB#1 6

H_BNR# 6

H_BPRI# 6

H_BREQ#0 6

H_CPURST# 6

H_DBSY# 6

H_DEFER# 6

H_DPWR# 6

H_DRDY# 6

H_DINV#[3:0] 6

H_DSTBN#[3:0] 6

H_DSTBP#[3:0] 6

H_HIT# 6

H_HITM# 6

H_LOCK# 6

H_REQ#[4:0] 6

H_RS#[2:0] 6

H_CPUSLP# 6

H_TRDY# 6

R396

R396

100 +-1%

100 +-1%

R_0603

R_0603

R385

R385

200 +-1%

200 +-1%

R_0603

R_0603

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_VREF_0

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_VREF_1

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_SLPCPU#

H_TRDY#

Layout Note:close to GMCH less than

100 mils

4

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

E8

B9

C13

J13

C6

F6

C7

B7

A7

C3

J9

H8

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

H_VREF

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_CPUSLP#

C425

C425

0.1UF/10V

0.1UF/10V

H_VREF

H_VREF

H_A#3

H9

3

MCH_BSEL04

MCH_BSEL14

MCH_BSEL24

TP80TP80

TP81TP81

TP82TP82

TP84TP84 R406

TP83TP83

TP85TP85

TP86TP86

+3V

TP88TP88

TP89TP89

TP53TP53

R399

R399

TP79TP79

10K +-5%

10K +-5%

R_0402

R_0402

PM_BMBUSY#17

MEM_TS#14

R407 40.2 +-1%

R407 40.2 +-1%

R408 40.2 +-1%

R408 40.2 +-1%

M_VREF

C479

C479

0.1UF/10V

0.1UF/10V

placed close to VREF pins

of DDR2 SO-DIMM

R_0402

R_0402

NS

NS

R_0402

R_0402

NS

NS

3

DPRSLPVR17,36

PM_THRMTRIP#6,15

PWROK17,31

PLT_RST#16,17,20

R400 0 +-5%

NSR400 0 +-5%

NS

R_0402

R_0402

MCH_ICH_SYNC#16

TP93TP93

SM_OCDCOMP_0

SM_OCDCOMP_1

C480

C480

2.2UF/16V

2.2UF/16V

MCH_CFG5

R417

R417

R_0402

R_0402

2.2K +-5%

2.2K +-5%

2.2K +-5%

2.2K +-5%

NS

NS

R409

R409

R_0402

R_0402

NS

NS

TP87TP87

MCH_CFG6

TP39TP39

TP43TP43

MCH_CFG3

MCH_CFG4

MCH_CFG5

MCH_CFG6

MCH_CFG7

MCH_CFG8

MCH_CFG9

MCH_CFG10

MCH_CFG11

MCH_CFG12

MCH_CFG13

MCH_CFG14

MCH_CFG15

MCH_CFG16

MCH_CFG17

MCH_CFG18

MCH_CFG19

MCH_CFG20

R397 0 +-5%R397 0 +-5%

R405 100 +-1%R405 100 +-1%

MCH_CFG9

R410

R410

R413

R413

R_0402

R_0402

R_0402

R_0402

2.2K +-5%

2.2K +-5%

2.2K +-5%

2.2K +-5%

NS

NS

NS

NS

AG11

AF11

AH33

AH34

BA41

BA40

BA39

AY41

AW41

AW1

MCH_CFG11

T32

R32

J19

K30

J29

A41

A35

A34

D28

D27

K16

K18

J18

F18

E15

F15

E18

D19

D16

G16

E16

D15

G15

K15

C15

H16

G18

H15

J25

K27

J26

G28

F25

H26

H28

H27

K28

H32

C41

BA3

BA2

BA1

B41

AY1

A40

A39

U5B

U5B

F3

F7

H7

G6

D1

C1

B2

A4

A3

R_0402

R_0402

2.2K +-5%

2.2K +-5%

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BMBUSY#

PM_EXTTS#_0

PM_EXTTS#_1

PM_THRMTRIP#

PWROK

RSTIN#

SDVO_CTRLCLK

SDVO_CTRLDATA

ICH_SYNC#

CLK_REQ#

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

MCH_CFG12

R415

R415

R414

R414

R_0402

R_0402

2.2K +-5%

2.2K +-5%

NS

NS

NS

NS

2

CFGRSVD

CFGRSVD

PM

PM

MISC

MISC

NC

NC

CALISTOGA_1p0

CALISTOGA_1p0

MCH_CFG13

R416

R416

R_0402

R_0402

2.2K +-5%

2.2K +-5%

NS

NS

2

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP#

SM_RCOMP

SM_VREF_0

DDR MUXINGCLKDMI

DDR MUXINGCLKDMI

SM_VREF_1

G_CLKIN#

G_CLKIN

D_REFCLKIN#

D_REFCLKIN

D_REFSSCLKIN#

D_REFSSCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

LEVEL

CFG5 DMI x2

CFG6

CFG9 Reverse Lanes

CFG12

CFG16

CFG[17:3] INTERNAL PULLUP

CFG[20:18] INTERNAL

PULLDOWN

MCH_CFG16

1

AY35

AR1

AW7

AW40

AW35

AT1

AY7

AY40

AU20

AT20

BA29

AY29

AW13

AW12

AY21

AW21

AL20

AF10

BA13

BA12

AY20

AU21

AV9

AT9

AK1

AK41

AF33

AG33

A27

A26

C40

D41

AE35

AF39

AG35

AH39

AC35

AE39

AF35

AG39

AE37

AF41

AG37

AH41

AC37

AE41

AF37

AG41

SM_OCDCOMP_0

SM_OCDCOMP_1

M_RCOMPN

M_RCOMPP

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

0

M_CLK_DDR0 14

M_CLK_DDR1 14

M_CLK_DDR3 14

M_CLK_DDR4 14

M_CLK_DDR#0 14

M_CLK_DDR#1 14

M_CLK_DDR#3 14

M_CLK_DDR#4 14

M_CKE0 14

M_CKE1 14

M_CKE2 14

M_CKE3 14

M_CS#0 14

M_CS#1 14

M_CS#2 14

M_CS#3 14

M_ODT0 14

M_ODT1 14

M_ODT2 14

M_ODT3 14

R398 80.6 +-1%

R398 80.6 +-1%

R_0603

R_0603

M_VREF

CLK_PCIE_MCH# 4

CLK_PCIE_MCH 4

DREFCLK# 4

DREFCLK 4

DREFSSCLK# 4

DREFSSCLK 4

VDIMM

R406

80.6 +-1%

80.6 +-1%

R_0603

R_0603

DMI_RXN[3:0] 17

DMI_RXP[3:0] 17

DMI_TXN[3:0] 17

DMI_TXP[3:0] 17

1

DMI x4 (default)

Moby Dick

Calistoga

Normal Operation (default)

Calistoga

Reserved

ReservedCFG13

Dynamic ODT Disabled

Title

Title

Title

MCH-M_A (HOST,HUB,VCC)

MCH-M_A (HOST,HUB,VCC)

MCH-M_A (HOST,HUB,VCC)

Size Document Number

Size Document Number

Size Document Number

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

Taurus2

Taurus2

Taurus2

Moby DickCFG11

Reserved

Reserved

Dynamic ODT Enabled (default)

LENOVO.NOD

LENOVO.NOD

LENOVO.NOD

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

840Thursday, June 29, 2006

840Thursday, June 29, 2006

840Thursday, June 29, 2006

1

Rev

Rev

Rev

s0.1

s0.1

s0.1

of

of

of

5

4

3

2

1

D D

M_A_DQ[63:0] 14

U5D

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

C C

B B

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

AL5

AL2

U5D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

CALISTOGA_1p0

CALISTOGA_1p0

AU12

SA_BS_0

AV14

SA_BS_1

BA20

SA_BS_2

AY13

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_WE#

M_A_DM0

AJ33

M_A_DM1

AM35

M_A_DM2

AL26

M_A_DM3

AN22

M_A_DM4

AM14

M_A_DM5

AL9

M_A_DM6

AR3

M_A_DM7

AH4

M_A_DQS0

AK33

M_A_DQS1

AT33

M_A_DQS2

AN28

M_A_DQS3

AM22

M_A_DQS4

AN12

M_A_DQS5

AN8

M_A_DQS6

AP3

M_A_DQS7 M_B_DQS7

AG5

M_A_DQS#0

AK32

M_A_DQS#1

AU33

M_A_DQS#2

AN27

M_A_DQS#3

AM21

M_A_DQS#4

AM12

M_A_DQS#5

AL8

M_A_DQS#6

AN3

M_A_DQS#7

AH5

M_A_A0

AY16

M_A_A1

AU14

M_A_A2

AW16

M_A_A3

BA16

M_A_A4

BA17

M_A_A5

AU16

M_A_A6

AV17

M_A_A7

AU17

M_A_A8

AW17

M_A_A9

AT16

M_A_A10

AU13

M_A_A11

AT17

M_A_A12

AV20

M_A_A13

AV12

AW14

TP_MA_RCVENIN#

AK23

TP_MA_RCVENOUT#

AK24

AY14

M_A_BS#0 14 M_B_BS#0 14

M_A_BS#1 14

M_A_BS#2 14

M_A_CAS# 14

M_A_DM[7:0] 14

M_A_DQS[7:0] 14

M_A_DQS#[7:0] 14

M_A_A[13:0] 14

M_A_RAS# 14

1

1

1

M_A_WE# 14

1

TP1TP1

TP47TP47

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_DQ[63:0] 14

U5E

U5E

AK39

SB_DQ0

AJ37

SB_DQ1

AP39

SB_DQ2

AR41

SB_DQ3

AJ38

SB_DQ4

AK38

SB_DQ5

AN41

SB_DQ6

AP41

SB_DQ7

AT40

SB_DQ8

AV41

SB_DQ9

AU38

SB_DQ10

AV38

SB_DQ11

AP38

SB_DQ12

AR40

SB_DQ13

AW38

SB_DQ14

AY38

SB_DQ15

BA38

SB_DQ16

AV36

SB_DQ17

AR36

SB_DQ18

AP36

SB_DQ19

BA36

SB_DQ20

AU36

SB_DQ21

AP35

SB_DQ22

AP34

SB_DQ23

AY33

SB_DQ24

BA33

SB_DQ25

AT31

SB_DQ26

AU29

SB_DQ27

AU31

SB_DQ28

AW31

SB_DQ29

AV29

SB_DQ30

AW29

SB_DQ31

AM19

SB_DQ32

AL19

SB_DQ33

AP14

SB_DQ34

AN14

SB_DQ35

AN17

SB_DQ36

AM16

SB_DQ37

AP15

SB_DQ38

AL15

SB_DQ39

AJ11

SB_DQ40

AH10

SB_DQ41

AJ9

SB_DQ42

AN10

SB_DQ43

AK13

SB_DQ44

AH11

SB_DQ45

AK10

SB_DQ46

AJ8

SB_DQ47

BA10

SB_DQ48

AW10

SB_DQ49

BA4

SB_DQ50

AW4

SB_DQ51

AY10

SB_DQ52

AY9

SB_DQ53

AW5

SB_DQ54

AY5

SB_DQ55

AV4

SB_DQ56

AR5

SB_DQ57

AK4

SB_DQ58

AK3

SB_DQ59

AT4

SB_DQ60

AK5

SB_DQ61

AJ5

SB_DQ62

AJ3

SB_DQ63

CALISTOGA_1p0

CALISTOGA_1p0

AT24

SB_BS_0

AV23

SB_BS_1

AY28

SB_BS_2

AR24

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_WE#

M_B_DM0

AK36

M_B_DM1

AR38

M_B_DM2

AT36

M_B_DM3

BA31

M_B_DM4

AL17

M_B_DM5

AH8

M_B_DM6

BA5

M_B_DM7

AN4

M_B_DQS0

AM39

M_B_DQS1

AT39

M_B_DQS2

AU35

M_B_DQS3

AR29

M_B_DQS4

AR16

M_B_DQS5

AR10

M_B_DQS6

AR7

AN5

M_B_DQS#0

AM40

M_B_DQS#1

AU39

M_B_DQS#2

AT35

M_B_DQS#3

AP29

M_B_DQS#4

AP16

M_B_DQS#5

AT10

M_B_DQS#6

AT7

M_B_DQS#7

AP5

M_B_A0

AY23

M_B_A1

AW24

M_B_A2

AY24

M_B_A3

AR28

M_B_A4

AT27

M_B_A5

AT28

M_B_A6

AU27

M_B_A7

AV28

M_B_A8

AV27

M_B_A9

AW27

M_B_A10

AV24

M_B_A11

BA27

M_B_A12

AY27

M_B_A13

AR23

AU23

TP_MB_RCVENIN#

AK16

TP_MB_RCVENOUT#

AK18

AR27

M_B_BS#1 14

M_B_BS#2 14

M_B_CAS# 14

M_B_DM[7:0] 14

M_B_DQS[7:0] 14

M_B_DQS#[7:0] 14

M_B_A[13:0] 14

M_B_RAS# 14

1

1

M_B_WE# 14

1

1

TP2TP2

TP49TP49

LENOVO.NOD

LENOVO.NOD

Taurus2

Taurus2

Taurus2

LENOVO.NOD

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

HuZW LiXINP LiYJK LvXDA

940Thursday, June 29, 2006

940Thursday, June 29, 2006

940Thursday, June 29, 2006

1

Rev

Rev

Rev

s0.1

s0.1

s0.1

of

of

of

A A

Title

Title

Title

MCH-M_B (AGP, GND)

MCH-M_B (AGP, GND)

MCH-M_B (AGP, GND)

Size Document Number

Size Document Number

Size Document Number

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

"PROPERTY NOTE: this document contains information confidential and

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

property to LENOVO PND and shall not be reproduced or transferred to other documents

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

or disclosed to others or used for any purpose other than that for which it was

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

obtained without the expressed written consent of LENOVO PND."

5

4

3

2

5

4

3

2

1

+VCCP

D D

C C

B B

A A

5

AA33

W33

AA32

W32

M32

AA31

W31

M31

AA30

W30

M30

AA29

W29

M29

AB28

AA28

M28

M27

M25

M24

AB23

AA23

M23

AC22

AB22

W22

M22

AC21

AA21

W21

M21

AC20

AB20

W20

M20

AB19

AA19

M19

M18

M17

M16

U5G

U5G

VCC_0

VCC_1

P33

VCC_2

N33

VCC_3

L33

VCC_4

J33

VCC_5

VCC_6

Y32

VCC_7

VCC_8

V32

VCC_9

P32

VCC_10

N32

VCC_11

VCC_12

L32

VCC_13

J32

VCC_14

VCC_15

VCC_16

V31

VCC_17

T31

VCC_18

R31

VCC_19

P31

VCC_20

N31

VCC_21

VCC_22

VCC_23

Y30

VCC_24

VCC_25

V30

VCC_26

U30

VCC_27

T30

VCC_28

R30

VCC_29

P30

VCC_30

N30

VCC_31

VCC_32

L30

VCC_33

VCC_34

Y29

VCC_35

VCC_36

V29

VCC_37

U29

VCC_38

R29

VCC_39

P29

VCC_40

VCC_41

L29

VCC_42

VCC_43

VCC_44

Y28

VCC_45

V28

VCC_46

U28

VCC_47

T28

VCC_48

R28

VCC_49

P28

VCC_50

N28

VCC_51

VCC_52

L28

VCC_53

P27

VCC_54

N27

VCC_55

VCC_56

L27

VCC_57

P26

VCC_58

N26

VCC_59

L26

VCC_60

N25

VCC_61

VCC_62

L25

VCC_63

P24

VCC_64

N24

VCC_65

VCC_66

VCC_67

VCC_68

Y23

VCC_69

P23

VCC_70

N23

VCC_71

VCC_72

L23

VCC_73

VCC_74

VCC_75

Y22

VCC_76

VCC_77

P22

VCC_78

N22

VCC_79

VCC_80

L22

VCC_81

VCC_82

VCC_83

VCC_84

N21

VCC_85

VCC_86

L21

VCC_87

VCC_88

VCC_89

Y20

VCC_90

VCC_91

P20

VCC_92

N20

VCC_93

VCC_94

L20

VCC_95

VCC_96

VCC_97

Y19

VCC_98

N19