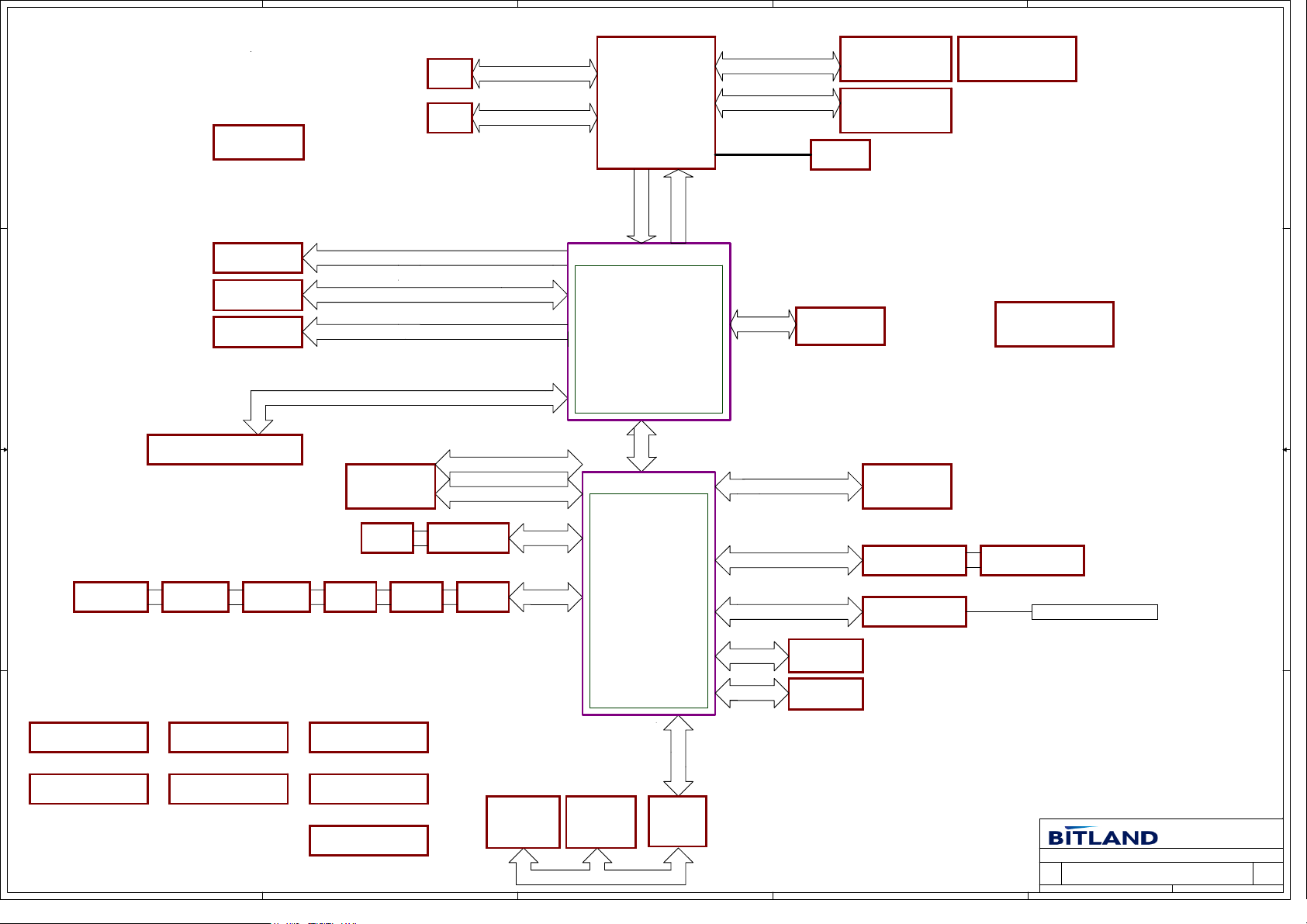

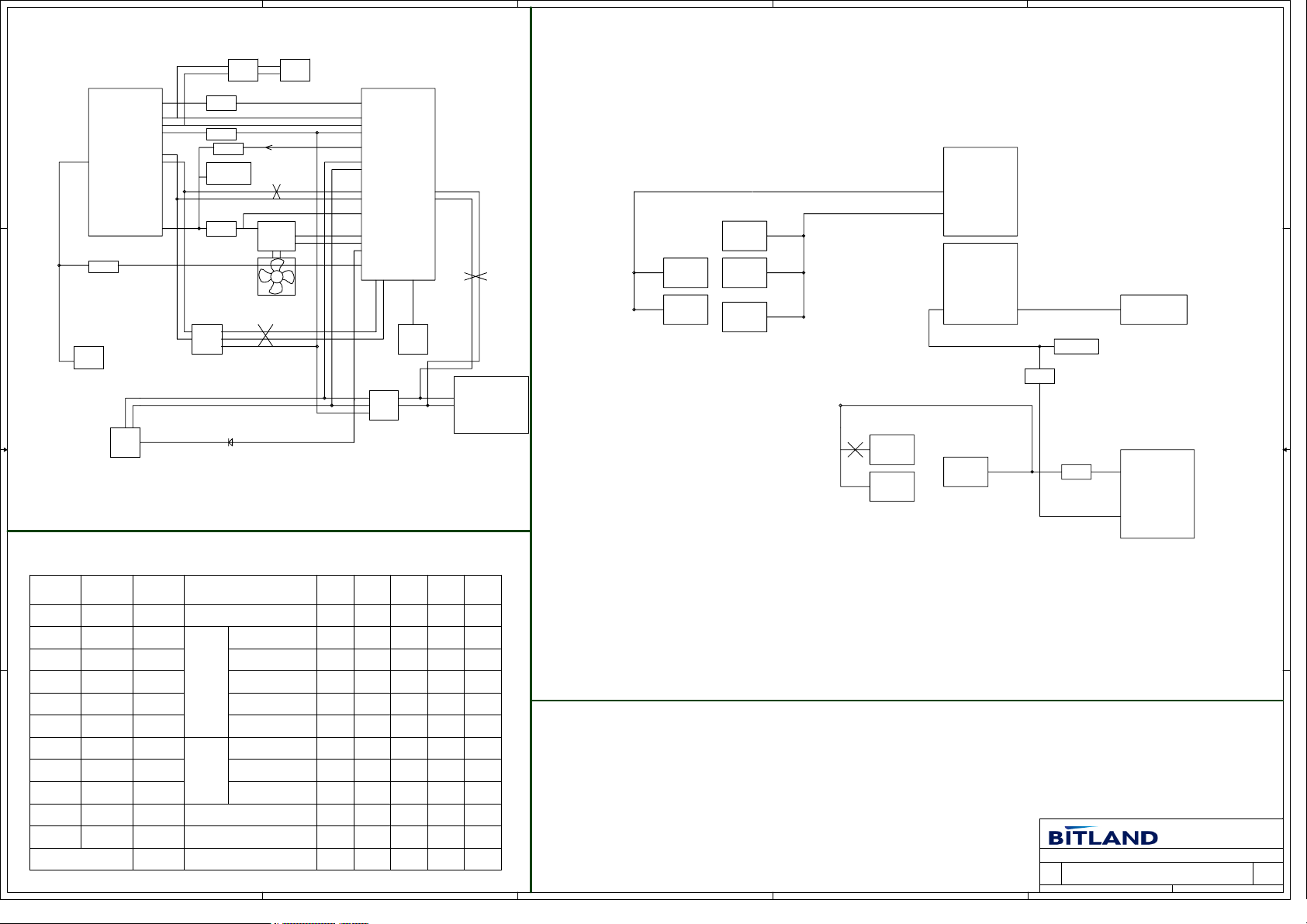

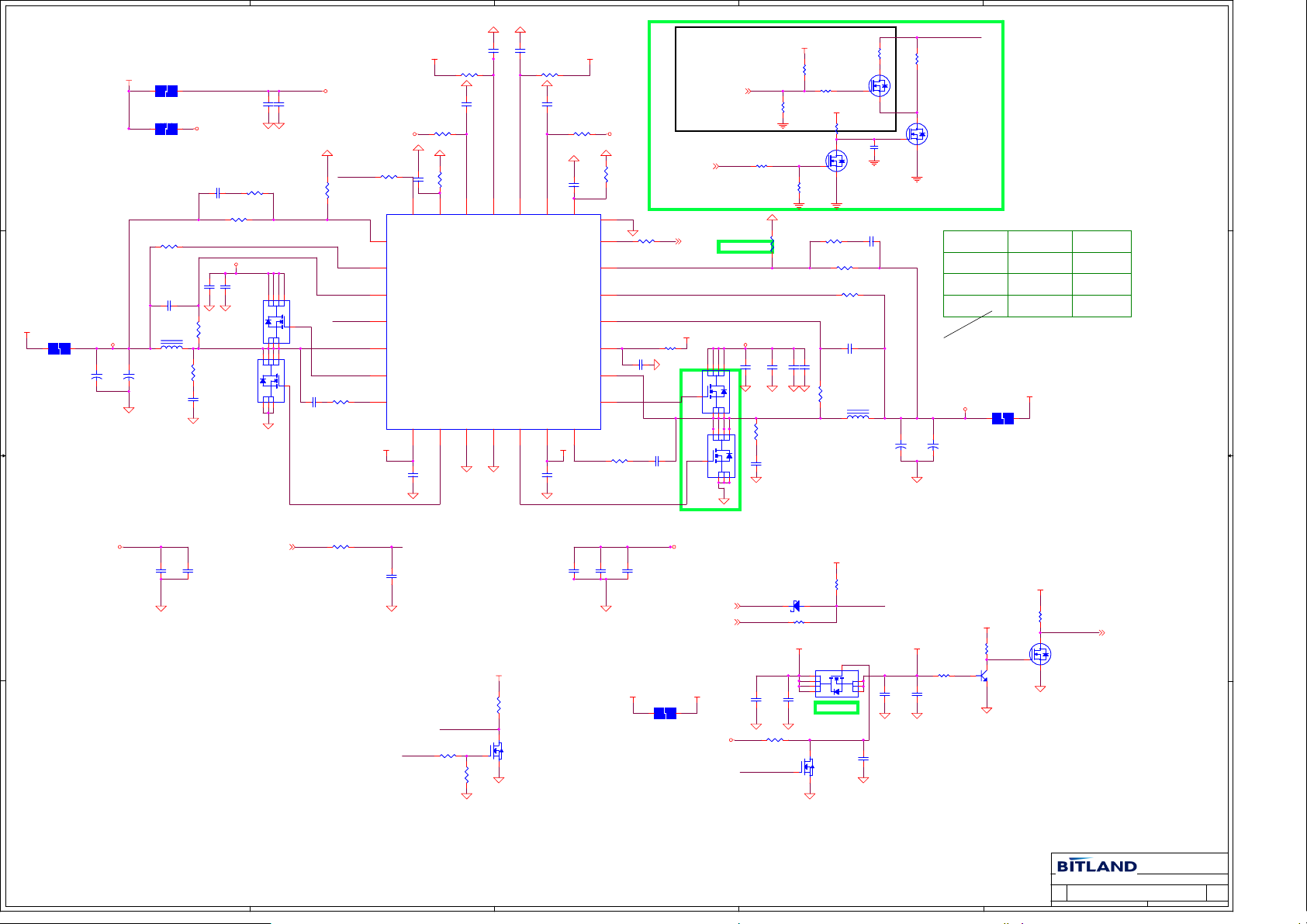

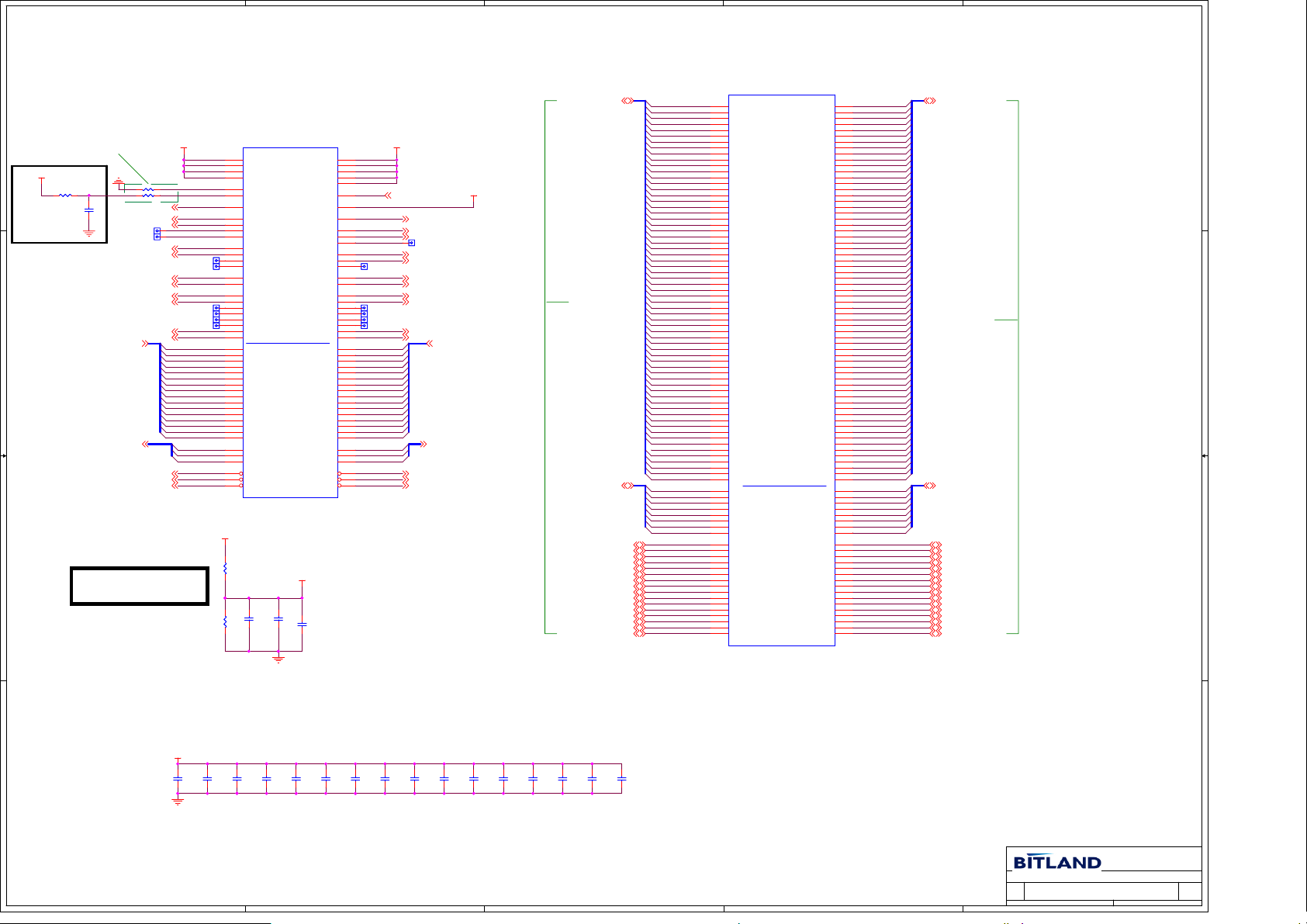

Lenovo B465 Schematics

5

PRELIMINARY

D D

EXTERNAL CLOCK GENERATOR

4

3

GUAM S1G4 SCHEMATIC DESIGN

DDR III, 1333MT/S

HDT

SCAN

16

16

AMD S1G4 CPU

Channel A

Channel B

2

UNBUFFERED DDR3

NEAR SODIMM

18,19

UNBUFFERED DDR3

FAR SODIMM

18,19

Optional CPU

Temperature sensor

16

1

SLG8LP625

20

14,15,16,17

OUT

HyperTransport

IN

LINK0

SB-TSI

16

16x16

LVDS CON

PARK_XT_S3

C C

VGA CON

43

31--40

44

LVDS MUX

CRT MUX

X16 PCIE MUX

RS880M

HyperTransport LINK0 CPU I/F

DX10 IGP

LVDS/TVOUT/TMDS

DISPLAY PORT X2

Side Port Memory

I2C I/F

BOOTSTRAPS

ROM(NB)

Ambient Light Sensor

24

52

1 X16 PCIE I/F

1 X4 PCIE I/F WITH SB

GPP PCIE INTERFACE

LAN&CARDREADER JMC261

B B

45

Finger Print

Reader

USB#6

45

Bluetooth

USB#7

CAM

USB#5

48

MINIPCIE WIFI

47

USB#4

SIM

card

socket

USB#1USB#3

45

46

46

MINIPCIE

USB#8

USB#0

USB 2.0

GPP INTERFACE

USB 2.0

49

USB 2.0

46

6 X1 PCIE I/F

SB820M

USB2.0 (14)+1.1(2)

SATA III (6 PORTS)

4 X1 PCIE GEN2 I/F

INT. CLK GEN.

GB MAC

HW MONITOR

PCI/PCI BDGE

INT. RTC

EC

HD AUDIO

LPC I/F

21,22,23,24,25

PCIE

X4

26,27,28,29

HD AUDIO I/F

SATA III I/F

HW MONITOR I/F

SPI I/F

SPI ROM

AZALIA CODEC

CX20671

HW MONITOR

42

Mobile 2.5" HDD Mobile ODD

41

28

28

41

CPU Tempreture Sensor

SPI I/F

ACPI 1.1

I2C I/F

BOOTSTRAPS

ROM (SB)

30

BATTERY CHAGER

A A

SYSTEM MAIN POWER

7

13

5

CPU CORE

1V1DUAL/VLDT/

VCC_NB/+1.1V

CPU MEMORY POWER

8

DISCHARGE CIRCUIT

10

1.5V/1.5VDUAL/

1.8V/3.3V/5V

RESET,FAN

& ENABLES

9

11

SCANNED

MATRIX

KEYBOARD

PS2

TOUCH PAD

55

4

IT8502E

EC

4949

3

49

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size

Document Number

Size

Document Number

Size

Document Number

Custom

Custom

Custom

Date:

Date:

Date:

Thursday, August 05, 2010 54

Thursday, August 05, 2010 54

2

Thursday, August 05, 2010 54

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Notebook R&D Division

BM5016

BM5016

BM5016

Sheet of

Sheet of

Sheet of

1

1

1

1

Rev

Rev

Rev

1.0

1.0

1.0

5

4

3

2

1

D D

C C

B B

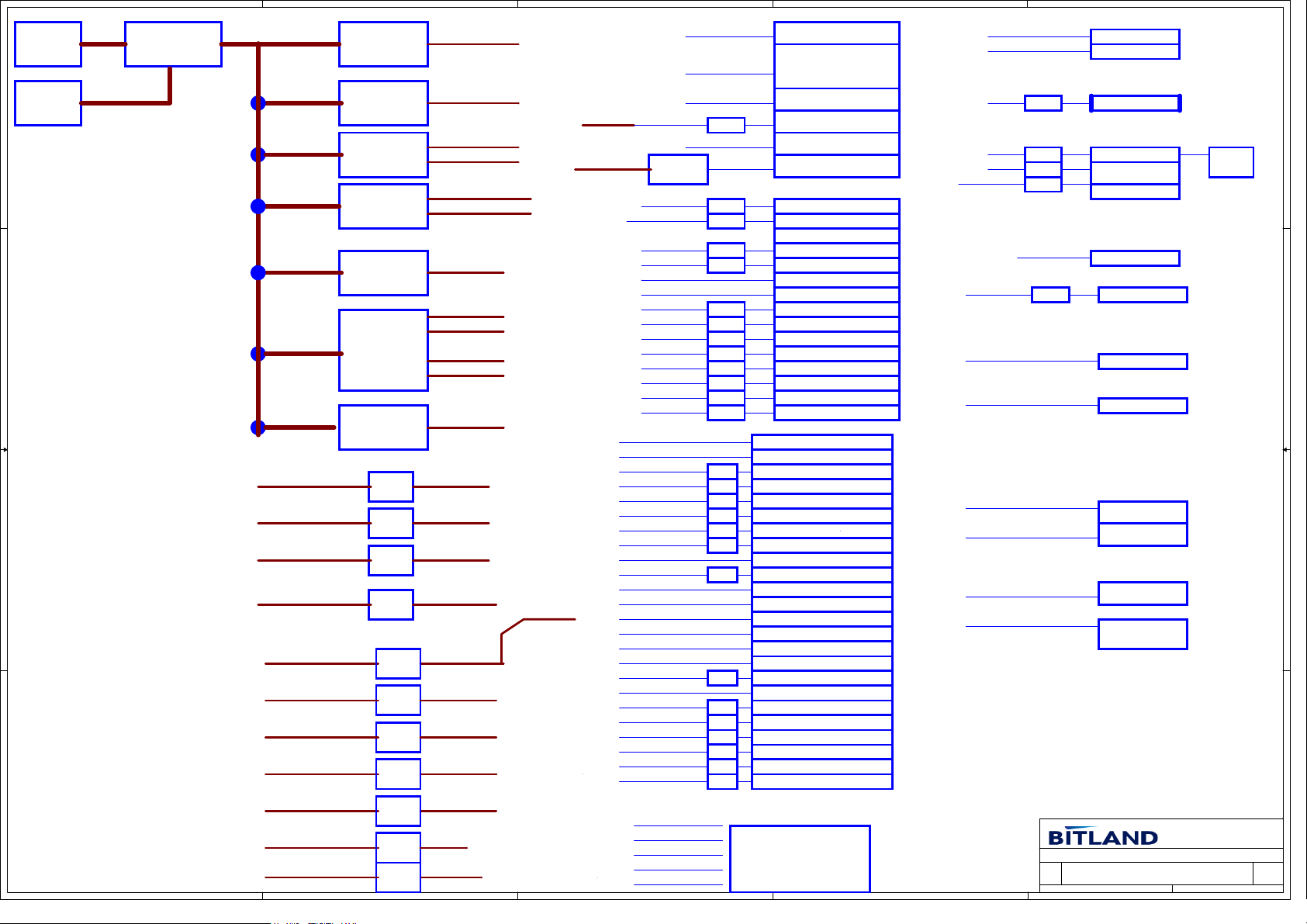

TABLE OF CONTENTS

A A

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

TABLE OF CONTENTS

TABLE OF CONTENTS

TABLE OF CONTENTS

Size

Document Number

Size

Document Number

Size

Document Number

Custom

Custom

Custom

Date:

Date:

Date:

Thursday, August 05, 2010 54

Thursday, August 05, 2010 54

5

4

3

2

Thursday, August 05, 2010 54

Notebook R&D Division

BM5016

BM5016

BM5016

Sheet of

Sheet of

Sheet of

1

Rev

Rev

Rev

1.0

1.0

2

2

2

1.0

5

BATTERY

11.1V 62WHr

AC ADAPTOR

15-16V 90W

D D

C C

BATTERY

CHARGER

ISL6251

+VIN

DDR3 PWM

LDO VTT

TPS51128&RT9199GSP

CPU_VDDIO_SUS +1.5V 4A

CPU_VDDIO_SUS 1.1V_1.0V_PWR

B B

+3.3VDUAL

+3.3VDUAL

CPU_VDDIO_SUS

+5VDUAL

+3.3VDUAL

A A

+1.1V DUAL

+3.3VDUAL

+3.3VDUAL

5

4

CPU core

PWM

ISL6265A

CPU core

PWM

ISL6265A

+1V~1.2V SW

+1.1V SW

ISL6228

+1.8V SW

MAX8716-2/2

+5V SW

+3V SW

+5V LDO

+3V LDO

tps51125

VDDC PWM

TPS51128

SWITCH

SWITCH

SWITCH

SWITCH

SWITCH

SWITCH

SWITCH

2.5V LDO

SWITCH

1.5V LDO

SWITCH

4

CPU_VDD_RUN@38A

CPU_VDDNB_RUN@4A

CPU_VDDIO_SUS@9A

MEM_VTT@1.5A

+1.1VDUAL@10A

+VCC_NB_RUN

+1.8V@1.3A

+3.3VALW

+5VALW

+3.3VDUAL@8A

+5VDUAL@8A

VDDC@15A

MVDDQ

+3VRUN

1.8V_REG 1.5A

+1.5V@1A

+5V

+3.3V

CPU_VDDA_RUN +3.3V

+1.1V

S3,S4,S5

+1.5VDUAL

2.6A

+1.5V

3

+5V

VLDT

+1.1V

+1.1V

+1.8V

+1.1V

+3.3V

+1.8V

+1.1V

+3.3V

+1.1V

+3.3V

+3.3VDUAL

+1.1VDUAL

+1.1V

+1.1V

VDDIO_GBE_S/2

+3.3VDUAL

+1.1VDUAL

PHY_VDDIO_DUAL

+3.3VDUAL

+1.1VDUAL

+1.1VDUAL

AZ_VDDIO_DUAL

+1.1VDUAL

+3.3V

+1.1V

+3.3VDUAL

+3.3VDUAL

+3.3VDUAL

VDDC

MVDDQ

1.1V_1.0V_PWR

1.8V_REG

+3VRUN

3

VLDT

AOZ1024

PWM

+VCC_NB

+3.3V

+1.8V

+1.5V

+1.5V

+3.3V

+1.8V

+3.3V

+1.8V

CPU_VDDA_RUN

CPU_VDD_RUN

CPU_VDDNB_RUN

BEAD

CPU_VDDIO_SUS

VDDR

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

AMD SB800

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

AMD S1G4

VCCA 2.5V

VDD CORE

1.375-1.500V 36A

VDDNB CORE

0.9V 4A

VLDT 1.2V TPDA

VDD MEM TPDA

VDDR 1.5A

RS880M

VDDHTTX 1.2V 0.68A

VDDHTRX+HT 1.1V 0.68A

VDDPCIE 1.1V 1.1A

VDDA18 1.8V 0.64A

VDDC 1.0V-1.1V 7.6A

VDDG33 3.3V 0.06A

VDDG18 1.8V 0.005A

VDD18_MEM 1.8V 0.005A

VDD_MEM 1.8V 0.23A

AVDD 3.3V 0.125A

VDDLT18 0.22A

VDDLT33 0A

PLLs 1.8V 0.1A

PLLs 1.1/1.2V 0.23A

VDDIO_33_PCIGP 3.3V 0.020A

VDDIO_18_FC 1.8V 0.050A

VDDAN_11_PCIE 1.1V 1A

VDDPL_33_PCIE 3.3V 0.030A

VDDAN_11_SATA 1.1V 0.8A

VDDPL_33_SATA 3.3V 0.020A

VDDAN_33_USB_S 3.3V 0.2A

VDDAN_11_USB_S 1.2V 0.2A

VDDCR_11 1.1V 0.5A

VDDAN_11_CLK 1.1V 0.4A

VDDRF_GBE_S

VDDIO_33_GBE_S 3.3V

VDDCR_11_GBE_S 1.1V

VDDIO_GBE_S 3.3V

VDDIO_33_S 3.3V

VDDCR_11_S 1.1V

VDDCD_11_USB 1.1V

VDDIO_AZ_S 3.3V OR 1.5V

VDDCR_11_USB_S 1.1V

VDDPL_33_SYS 3.3V SYS PLL

VDDPL_11_SYS 1.1 V SYS PLL

VDDPL_33_USB_S 3.3 V USB PLL

VDDAN_33_S 3.3V HWM

VDDXL_33_S 3.3V

AMD SB800

PARK_XT_S3

2

CPU_VDDIO_SUS

MEM_VTT

DDRiII SODIMMX2--SYSTEM

VDD MEM 4A

VTT_MEM 0.5A

1

CLOCK GEN

+3.3V

+5V

+3.3V

+3.3VDUAL

+3.3V

BEAD

BEAD

BEAD

BEAD

+3.3VDUAL

SW

3.3V

HD CODEC

5V

3V

SMSC1100--EC

3.3V 0.5A

LCD PANEL

3.3V 1.5A

AUDIO

OP

BACK LIGHT

+VIN

+5VDUAL

+1.5V

+3.3VDUAL

+5V

+5V

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

2

Date:

LED_BL

+VDD_MAIN

USB X2 FR

5VDual

MINI PCIE SLOT0,1,2

1.5V (S0, S1) 0.5A

each

3.3V (S3, S5) 2.75A

each

SATA HD0,1

5V (S3, S5) TBD

SATA ODD

5V (S0, S1) TBD

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

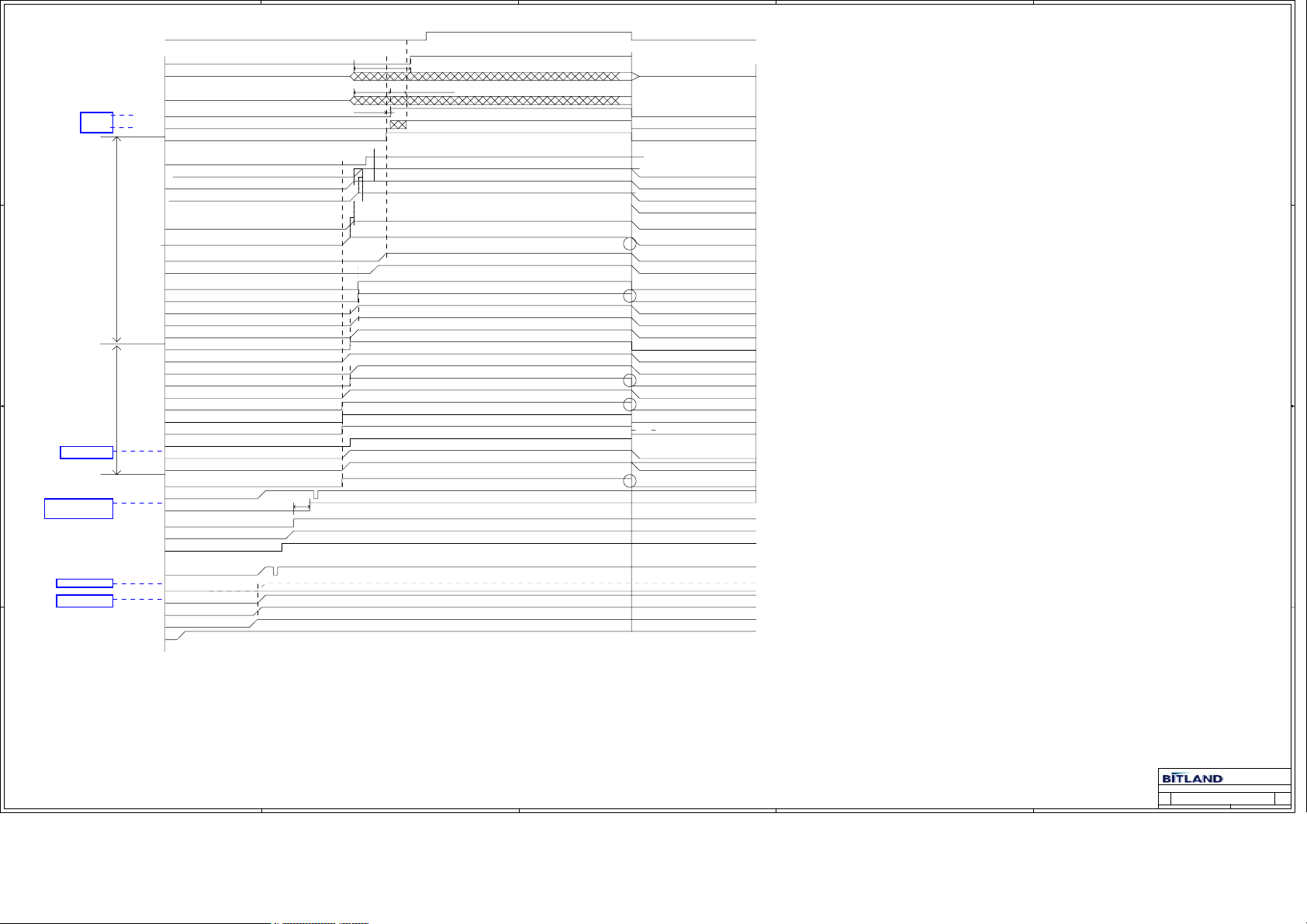

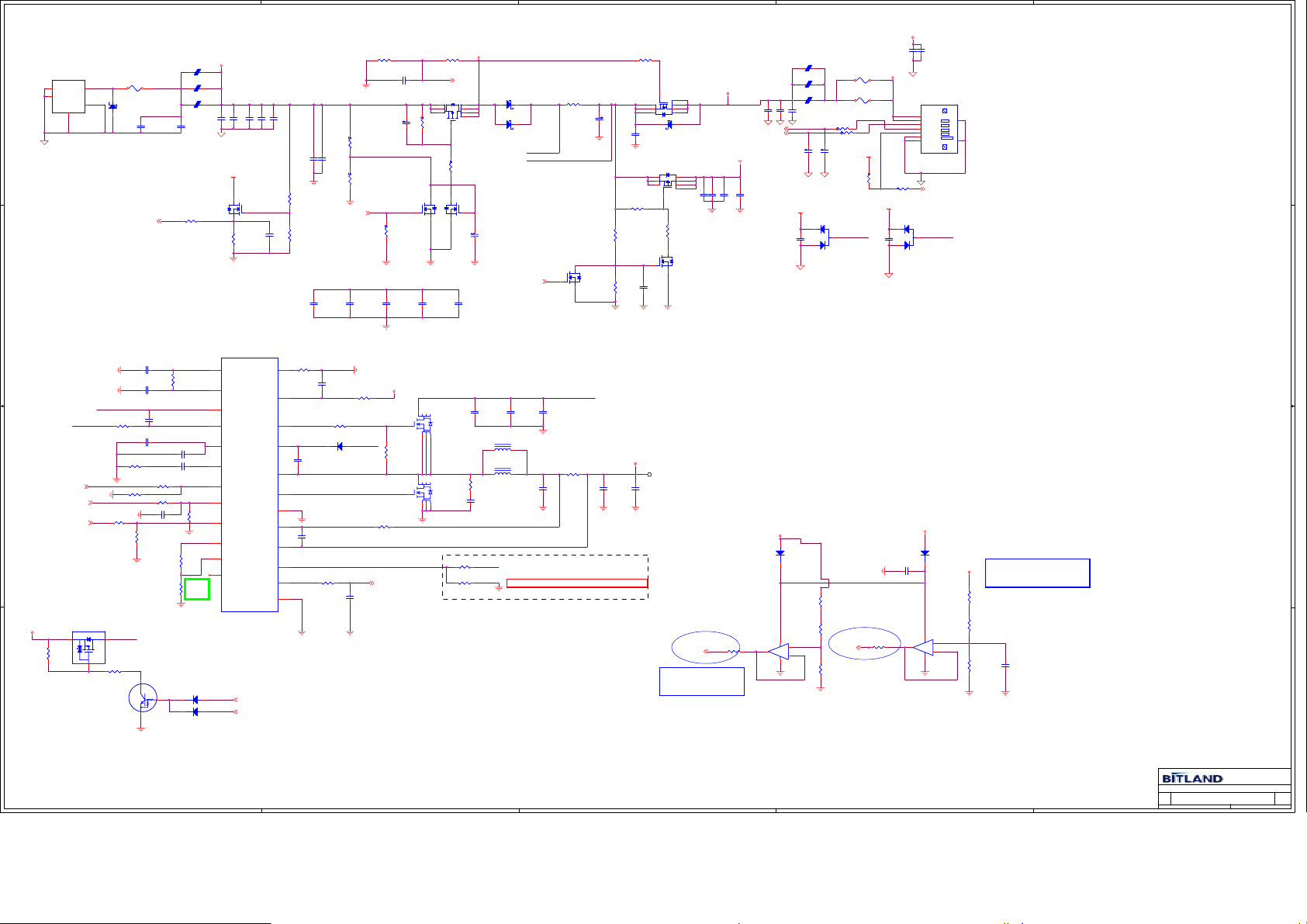

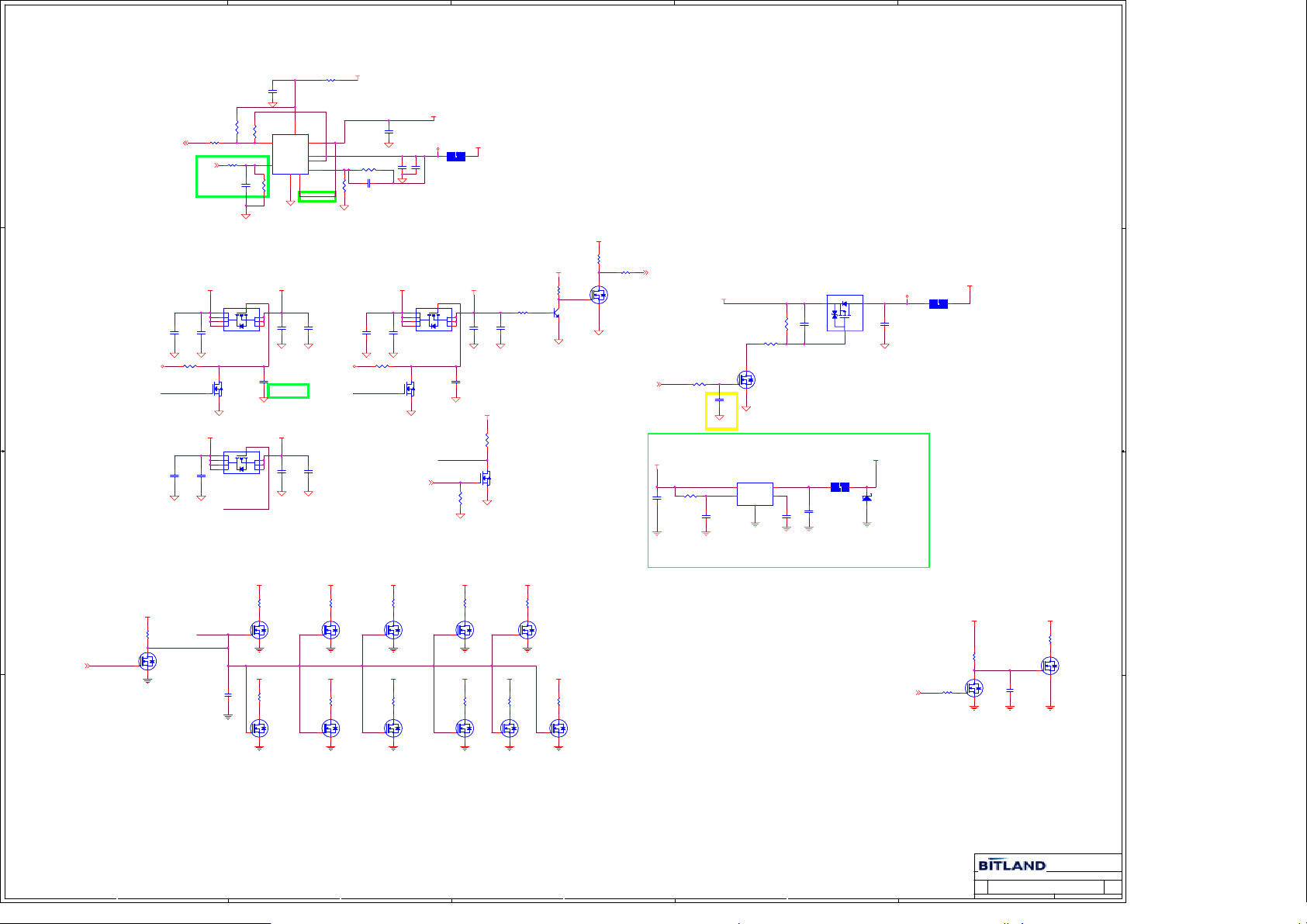

POWER DELIVERY CHART

POWER DELIVERY CHART

POWER DELIVERY CHART

Document Number

Document Number

Document Number

Thursday, August 05, 2010 54

Thursday, August 05, 2010 54

Thursday, August 05, 2010 54

Notebook R&D Division

BM5016

BM5016

BM5016

Sheet of

Sheet of

Sheet of

1

3

3

3

Rev

Rev

Rev

1.0

1.0

1.0

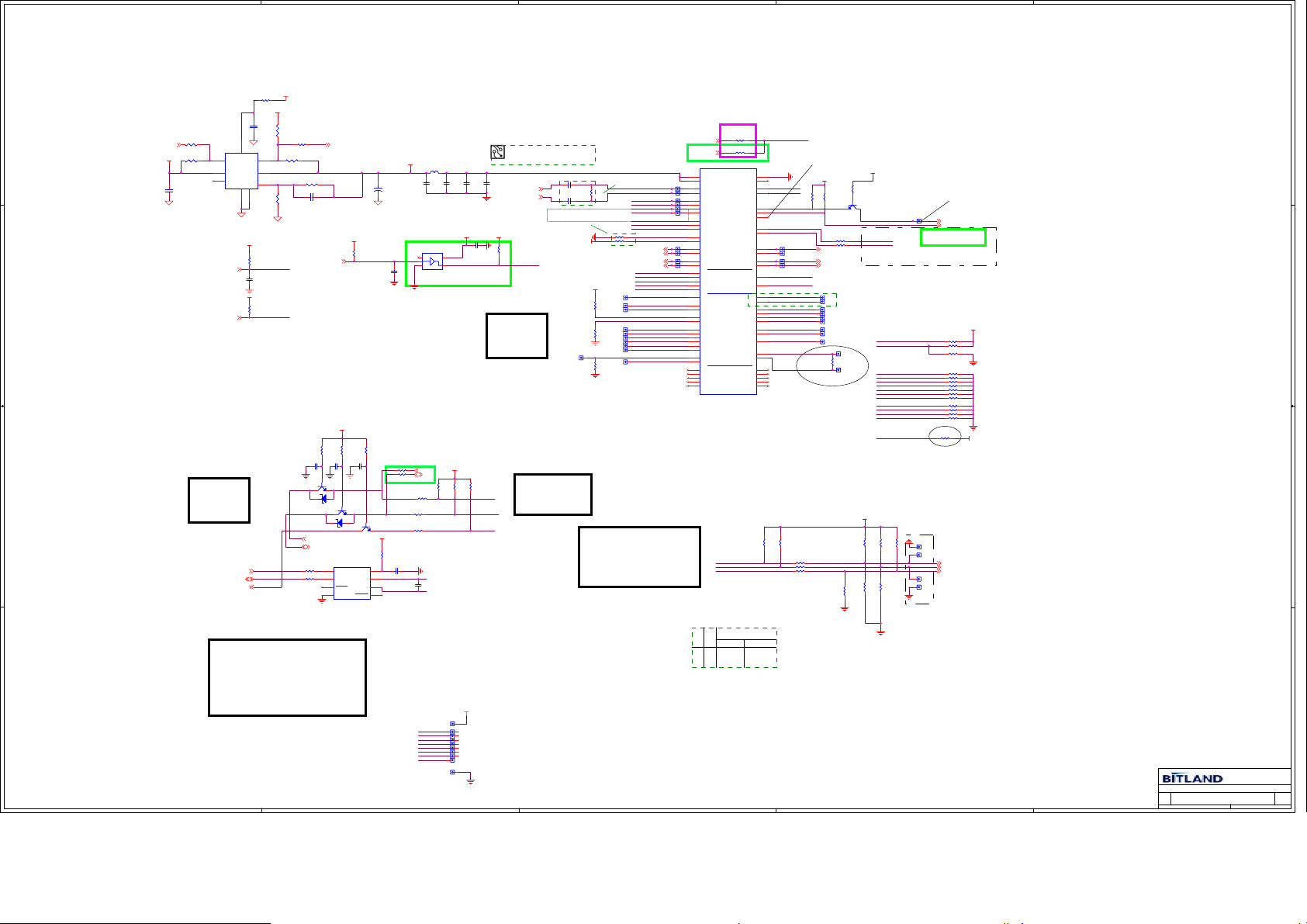

Power on Sequence required:

SB800:

1, +3.3VDUAL ramp before +1.1VDUAL

2, +3.3V ramp before +1.8v

3, +1.8V ramp before +1.1v

4, +3.3v ramp before +1.1v

5, +3.3VALW_R ramping down time > 300us

6, 50uS <= All power rails except +3.3VALW_R <= 40mS

7, 100uS <= +3.3VALW_R <= 40mS

RS880:

1, 0 <(+3.3V) - (+1.8v) < 2.1

2, +1.8V ramp before +1.1v

3. +1.1V ramp before VCC_NB

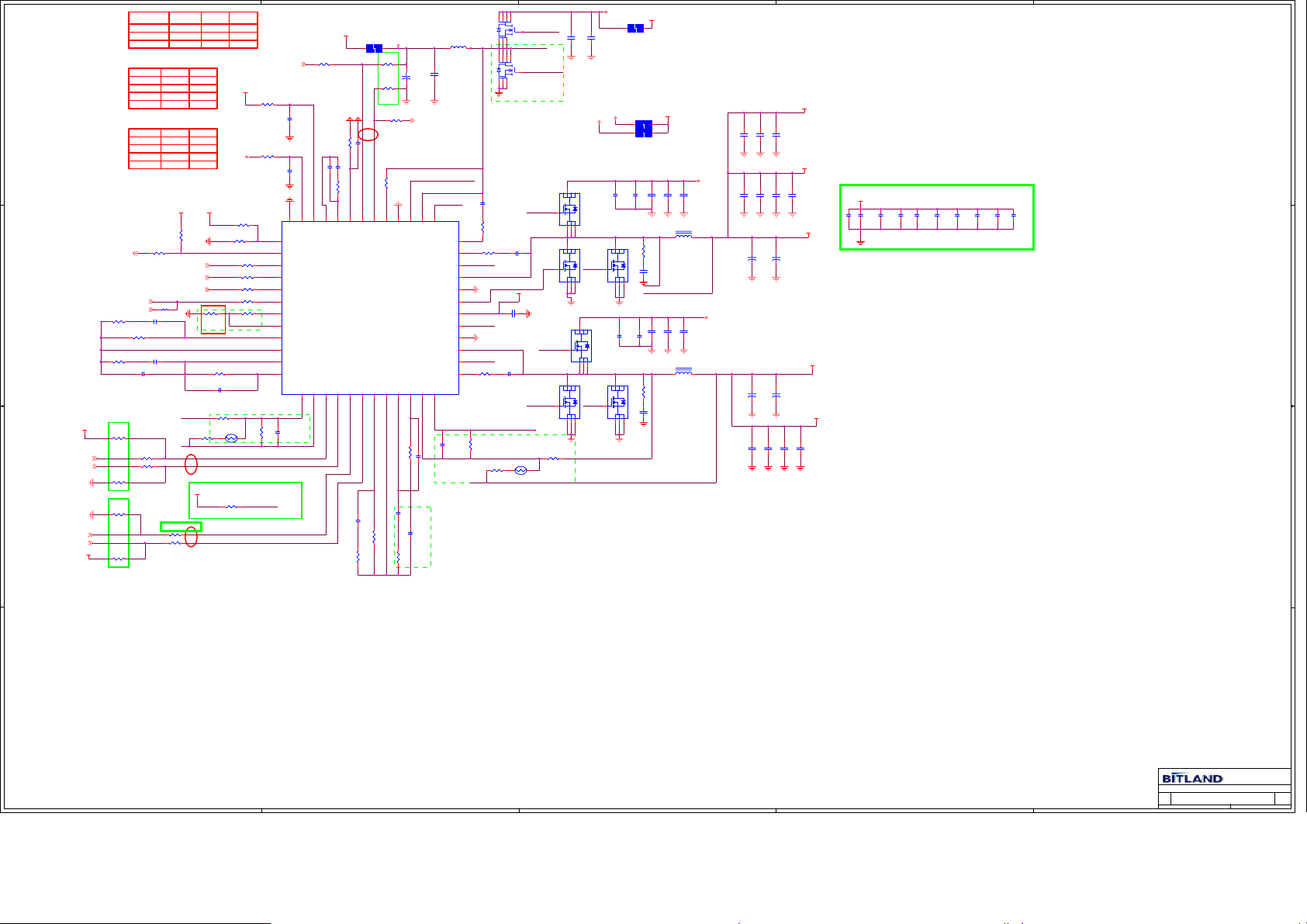

D D

C C

B B

SB OUTPUT

SB INPUT

CPU MEM CTL &

DDR3 SODIMM PWRS

CPU_THM/SB/SB_SCL1/2

SB_KB/SPI/LPC ROM PWRS

KBC is ready

KBC is powered by

A_VBAT & +3.3VALW

5

CPU_LDT_RST#

(SB TO CPU)

CPU_PWROK

(SB TO CPU)

CPU_CLKP/N running

NB_PWRGD

NB_PWRGD_IN

1)+1.5V SWITCH TO +1.5VDUAL 2)LASSO_PWRON 3)LPCPD# for TPM 4) TO SB&KBCSB_PWRGD

+1.2V_PWRGD

PARK-XT_PGOOD

1.8V_REG

1.1V_1.0V_PWR

PCIE_REFCLKP/N

VDD_CT

VDDC

MVDDQ

VCC_NB

VLDT

+1.1V

VRM_PWRGD

CPU_VDDR

CPU_VDD_RUN

CPU_VDDNB_RUN

VDDA_PWRGD

+2.5V_LDO

(CPU_VDDA_2.5_RUN)

+1.5V

1V8_PWRGD

GROUP A GROUP B

+1.8V

+5V/+3.3V

5V/3.3V_GATE

SLP_S3#

VDRAM_PWRGD

MEM_VTT

MEM_VREF

CPU_VDDIO_SUS

SLP_S5#

PWR_BTN#_EC

RSMRST#

V3V5DUAL_PWRGD

1V1DUAL_PWRGD

SYSTEM_DUAL_PG_DELAY

DUAL RAILS

VDD_DUAL_EN

Power button pressed

AC_OK

(ACIN detect)

+5VALW/+3.3VALW

LDO:5.4V

(from DCIN)

+VIN/+12V_HD

A_VBAT

VTT only will be shut down in S3 mode, and VTT for DDR3 SODIMM only.

RC=~ms

RC=~ms

RC=~ms

RC=~ms

RC=0

Power button from EC to SB

20mS

delay

+5VDUAL/+3.3VDUAL/+1.5VDUAL/+1.1VDUAL

When IMC, always on at all time( always PWR)

Power button pressed

AC not present scenario = LOW AC present= high

Battery inserted/AC IN

4

Req.

>1 mS

>1 mS Req.

running

>1 mS Req.

T3>0

T2>0

T1>=0

RC=~22ms

VCC_NB should not ramp before 1.1v

RC=~4.7ms

VRM_PWRGD AND 1V8_PWRGD

RC=0

RC=0

RC=0

VCC_NB(all NB power) valid before NB_PWRGD.

SLP_S3#

1V1DUAL_PWRGD

1V5_PWRGD/DNI

SYS_RST#

+1.2V_PWRGD

KBC_GPIO77/DNI

3

to S3

2

1

A A

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

Date:

Date:

Date:

Thursday, August 05, 2010 54D4

Thursday, August 05, 2010 54D4

5

4

3

2

Thursday, August 05, 2010 54D4

1

Notebook R&D Division

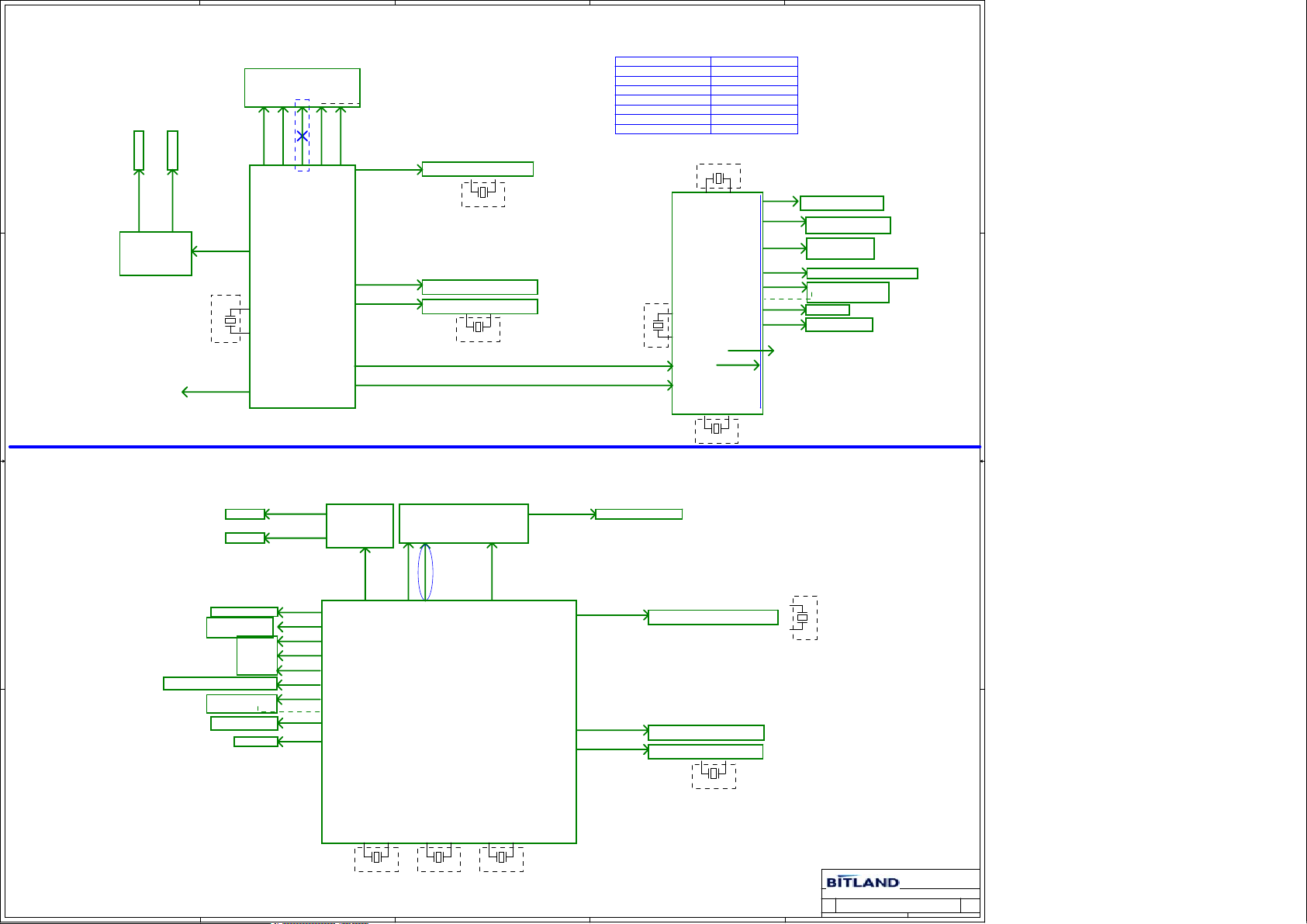

POWER SEQUENCE CHART

POWER SEQUENCE CHART

POWER SEQUENCE CHART

BM5016

BM5016

BM5016

Sheet of

Sheet of

Sheet of

Rev

Rev

Rev

1.0

1.0

1.0

5

4

3

2

1

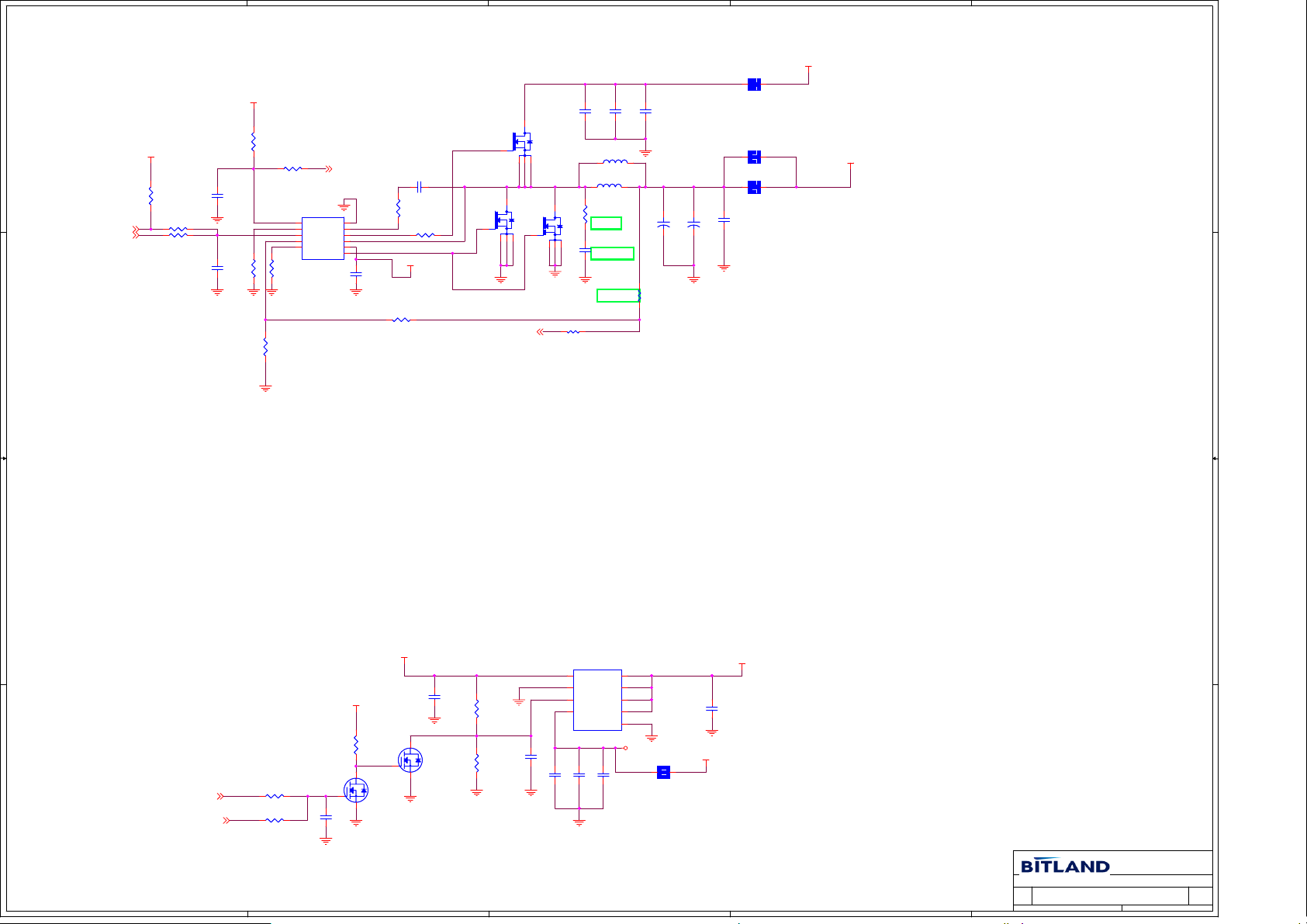

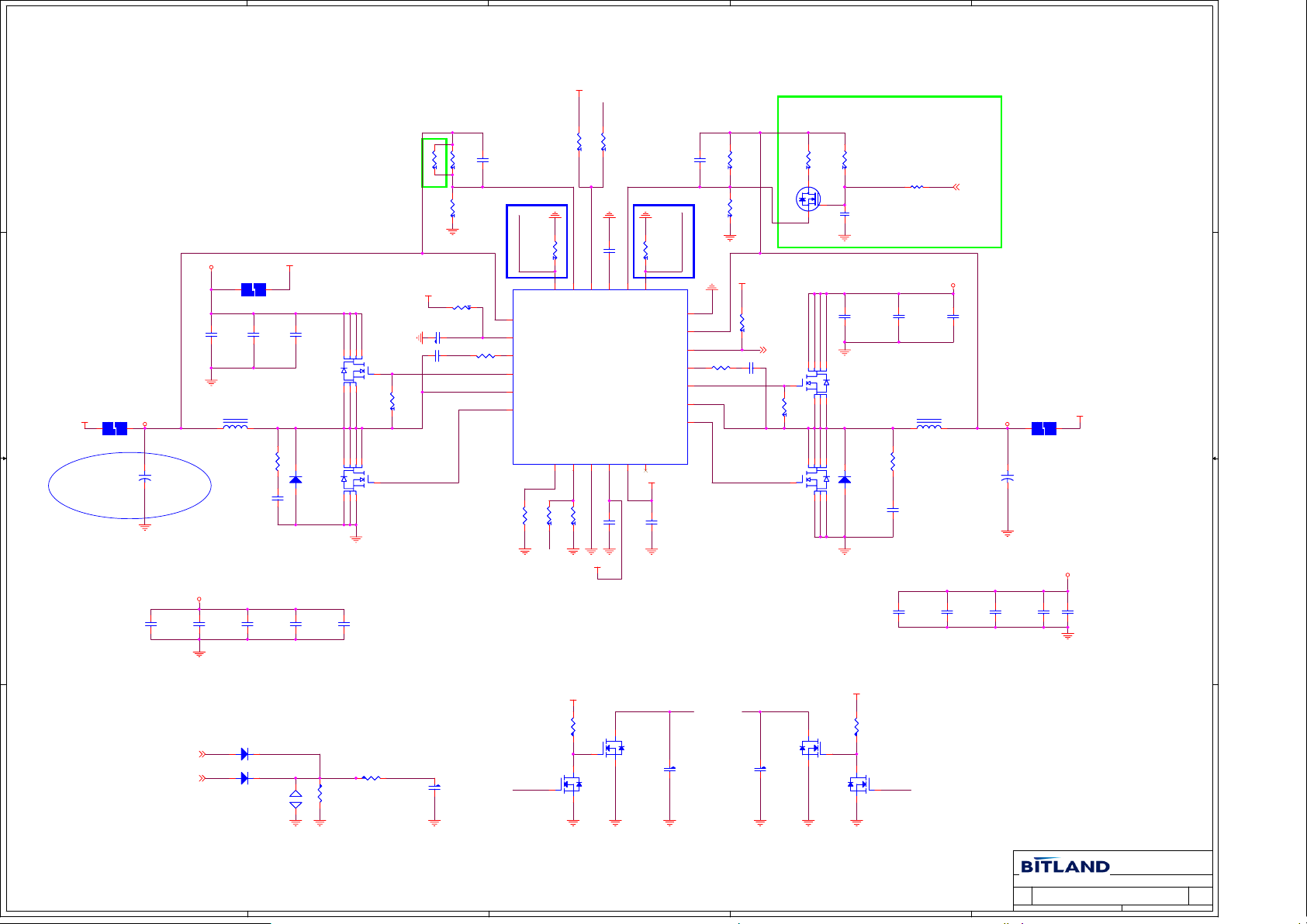

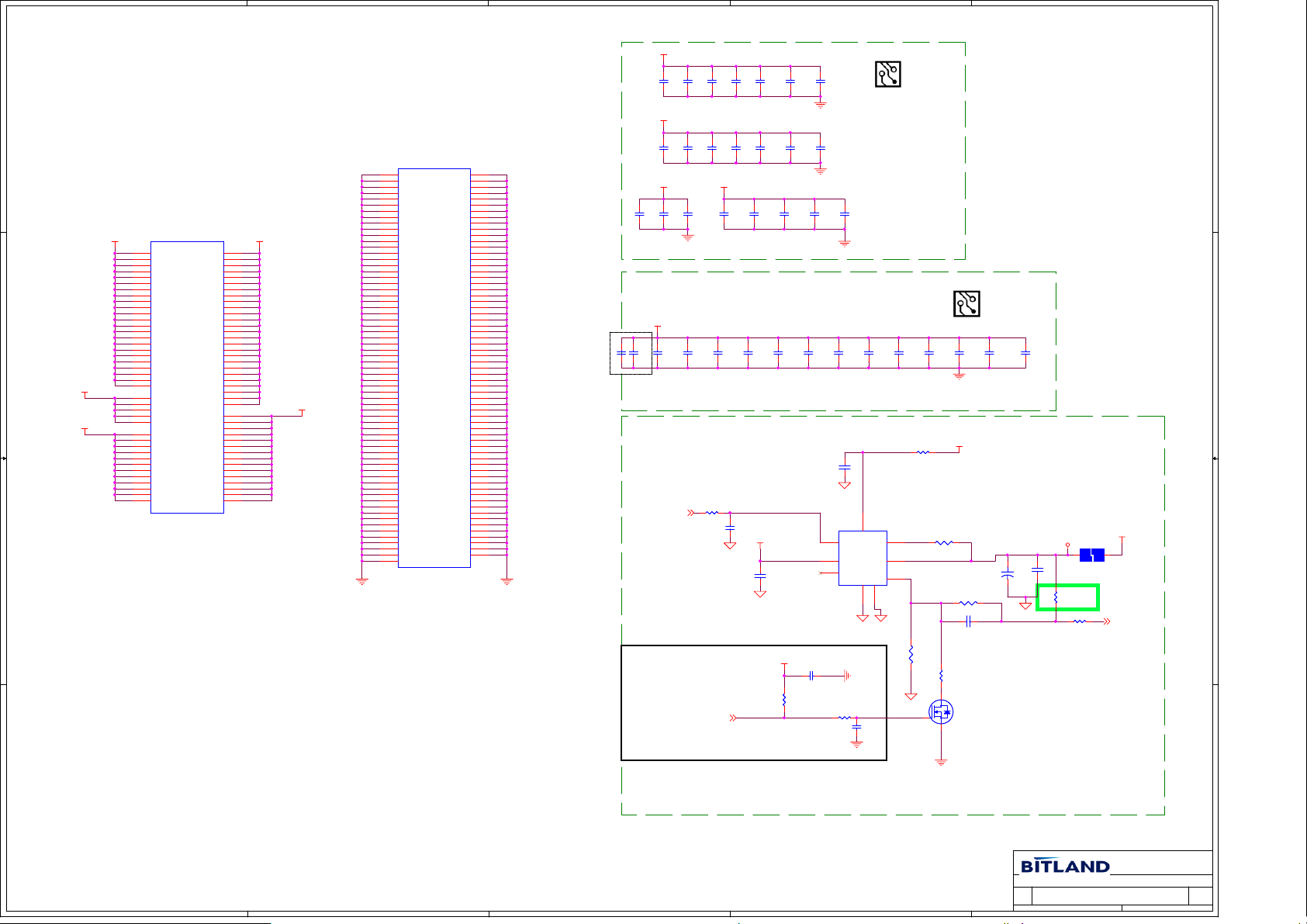

EXTERNAL CLOCK MODE

AMD NORTHBRIDGE

RS880M

A-LINK

GPP_REFCLK

D D

100MHZ

100MHZ

NBLINK_RCLKP/N

A_SODIMM

MEM_MB_CLK1_P/N

MEM_MB_CLK2_P/N

MEM_MA_CLK1_P/N

MEM_MA_CLK2_P/N

AMD

SIG4 CPU

B_SODIMM

CPU_CLKP/N

200MHZ

NB_GFX_REFCLKP/N

EXTERNAL

CLOCK GENERATOR

14.31818MHz

C C

SB_OSC

DNI

NB_OSC

100MHZ

100MHZ

14.318MHZ

GPP REF_CLK

HT_REFCLKP/N

PCIE_REFCLKP/N

100MHZ

CLK_REQ in CLK GEN

PCIE GFX PARK_XT(RS880M, 16 LANES)

EXT_PCIE_PE2_CLKREQ#

PARK_XT

27M Hz

PCIE_PE2_CLKP/N

100MHZ

PCIE_LAN_CLKP/N

100MHZ

MINIPCIE SLOT (SB800, 1 LANE)

EXT_PCIE_PE2_CLKREQ#

PCIE GPP I/F (RS880M, 1 LANE)

EXT_PCIE_LAN_CLKREQ#

PORT2:WLAN

JMC261

25M Hz

NB CLOCK INPUT TABLE

NB CLOCKS

HT_REFCLKP

HT_REFCLKN

REFCLK_P

REFCLK_N

GFX_REFCLK

GPP_REFCLK

GPPSB_REFCLK 100M DIFF

* RS880M can be used as clock buffer to output two PCIE referecence clocks

By deault, chip will configured as input mode, BIOS can program it to output mode.

RS880M

100M DIFF

100M DIFF

14M SE (1.1V)

vref

100M DIFF(IN/OUT)*

NC or 100M DIFF OUTPUT

25M Hz

PCICLK0

25M_X1

25M_X2

PCICLK1

PCICLK2

PCICLK3

PCICLK4

LPCCLK0

LPCCLK1

RTCCLK

AZ_BITCLK

SPI_CLK

GBE_RXCLK

GBE_TXCLK

FOR SATA

25M Hz

DNI

SBSRC_CLKP/N

100MHZ

CLK_48M_USB

48MHZ

AMD SB800

EXT CLK MODE

SATA_X1

SATA_X2

PCIE_RCLKP/N

USBCLK

PCI_CLK0

33MHZ

SMSC_CLK

33MHZ

PCI_CLK2

PCI_CLK3

PCI_CLK4

33MHZ

LPC_CLK0

33MHZ

LPC_CLK1

33MHZ

AZ_BIT_CLK

24MHZ

SPI_CLK

xxHZ

NC

FOR DEBUG PORT

STRAPS SETTING,

PCIE GEN1/PCIE GEN2

STRAPS SETTING,

UNUSED CLOCKS

EC/STRAPS SETTING :EC ENABLE

STRAPS SETTING,

CLOCKS ENABLE

HD AUDIO

SPI ROM & HEADER

32.768K Hz

INTERNAL CLOCK MODE

MEM_MA_CLK1_P/N

MEM_MA_CLK2_P/N

A_SODIMM

MEM_MB_CLK1_P/N

MEM_MB_CLK2_P/N

B_SODIMM

B B

STRAPS

SETTING,

UNUSED

CLOCKS

PCI_CLK0

SMSC_CLK

33MHZ

PCI_CLK2

33MHZ

PCI_CLK3

33MHZ

PCI_CLK4

33MHZ

LPC_CLK0

33MHZ

LPC_CLK1

33MHZ

SPI_CLK

xxHZ

AZ_BIT_CLK

24MHZ

FOR DEBUG PORT

STRAPS SETTING,

PCIE GEN1/PCIE GEN2

EC/STRAPS SETTING :EC ENABLE

STRAPS SETTING,

CLOCKS ENABLE

SPI ROM & HEADER

HD AUDIO

AMD

SIG4 CPU

CPU_CLKP/N

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

LPCCLK0

LPCCLK1

RTCCLK

SPI_CLK

AZ_BITCLK

200MHZ

CPU_HT_CLKP/N

AMD NORTHBRIDGE

RS880M

REFCLKP/N

A-LINK

100MHZ

100MHZ

NB_REFCLK_P/N

SB_NBLINK_RCLKP/N

PCIE_RCLKP/N

NB_DISP_CLKP/N

AMD SB820M

CLOCK GENERATOR

GPP_REFCLK

HT_REFCLKP/N

NB_HT_CLKP/N

100MHZ

SPM_CLK

xxxMHZ

SLT_GFX_CLKP/N

GPP_CLK2P/N

GPP_CLK3P/N

SIDE PORT MEMORY CHIP

PCIE_REFCLKP/N

100MHZ

SB_PCIE_PE2_CLKREQ#

100MHZ

PCIE_LAN_CLKP/N

100MHZ

PCIE GFX PARK_XT(RS880M, 16 LANES)

SB_MXM_CLKREQ#

MINIPCIE SLOT (SB800, 1 LANE)

CLK_REQ2 in SB

PCIE GPP I/F (RS880M, 1 LANE)

CLK_REQ3 in SB

PARK_XT

27M Hz

PORT2:WIFI

JMC261

25M Hz

A A

FOR MASTER FOR RTC FOR SATA

25M Hz

5

4

32.768K Hz

25M Hz

3

DNI

2

Title

Title

Title

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

Size

Document Number

Size

Document Number

Size

Document Number

Custom

Custom

Custom

Thursday, August 05, 2010 54

Thursday, August 05, 2010 54

Thursday, August 05, 2010 54

Date:

Date:

Date:

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Notebook R&D Division

BM5016

BM5016

BM5016

Sheet of

Sheet of

Sheet of

1

Rev

Rev

Rev

1.0

1.0

1.0

5

5

5

5

Thermal Systems

(Emergency Shutdown, Throttling, Fan Control)

4

3

2

1

NON-POP

OVERRIDE#translate

PWM

TACH

4-PIN CPU FAN

NON-POP

KBC

SMSC

W18

F24

M8

P5

J4

G7

T7

Y9

B6

C6

THERMTRIP#

SDA3

SCL3

TALERT#

FANOUT2

SDA0AA18

SCL0

TEMPIN0

TEMP_COMM

PROCHOT#

FANOUT0

FANIN0

TEMPIN3

GEVENT4#

SDA2

ADM

1032

(S5-S0)

(S0)

AMD

SB800

TEMP_COMM

SCL2

Place under DDR

TEMP

SENSOR

(Q600)

TEMPIN1

TEMPIN2

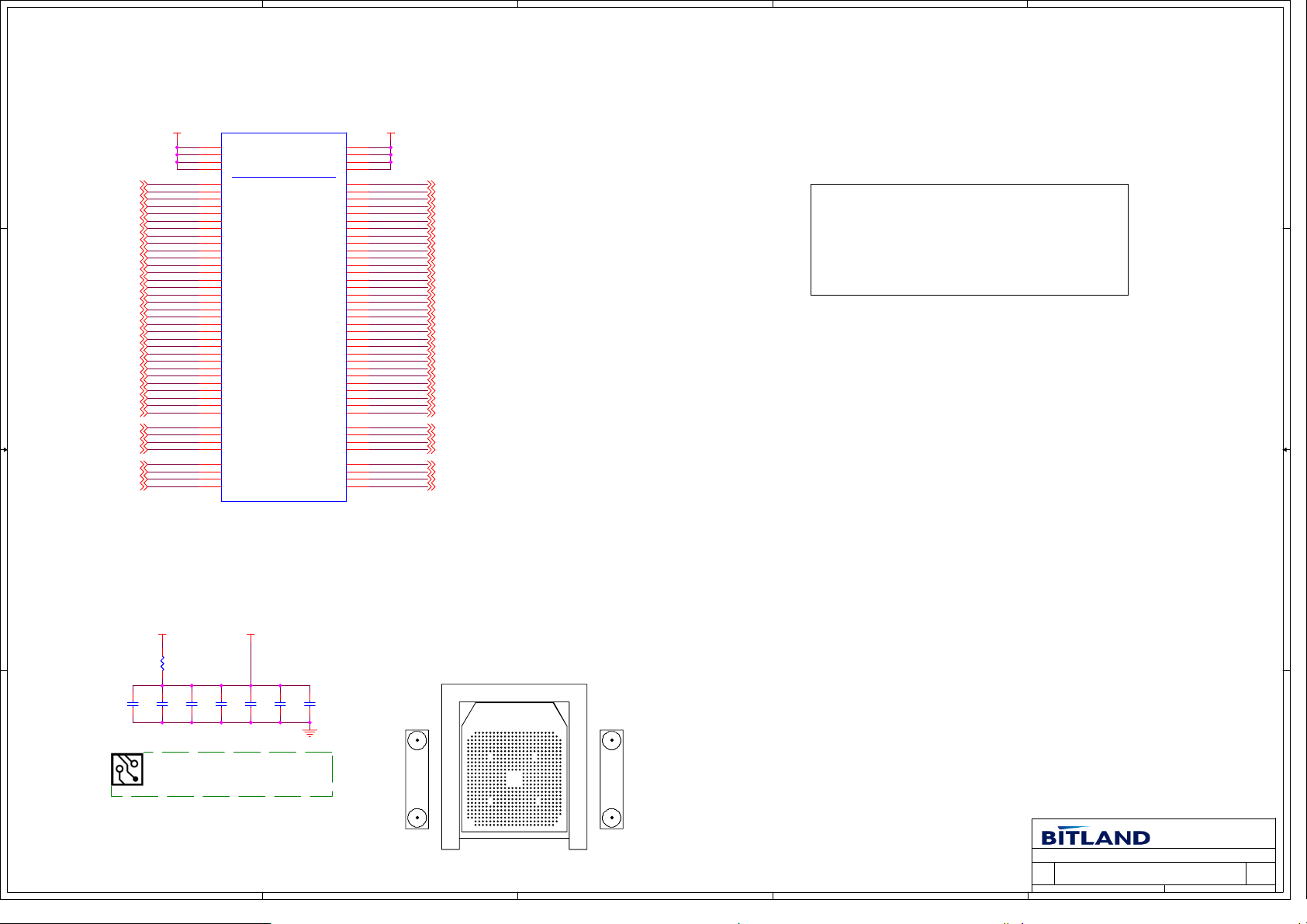

SMBus Block Diagram

(S5-S0)

A6

C6

DDR 2

SO-DIMM

J401

THERMDC

THERMDA

NON-POP

AMD

RS880

mini

PCI Exp x1

MPCIE1

PCI Exp x1

MPCIE2

mini

DDR 2

SO-DIMM

CLK. Gen.

9LRS4880

U800

J402

DUAL_SMB1

NOPOP

POP

SDATA1

SCLK1

SDATA0

SCLK0

CPU Thermal

Sensor

ADM1032

GPU Thermal

Sensor

U8

SB800

SDA1

(S5-S0)

SCL1

ASF Only

SDA0

(S0)

SCL0

SDA2

(S5-S0)

SCL2

S1G4

SIC

SID

MAX1535

battery charger

U2700

AMD

(master)

(S5-S0)

1.8V

AMD

SDA3

SCL3

BAT_DAT

BAT_CLK

(S5-S0)

MAX17009

SVC

CPU Core PWR PWM

SVD

U2800

EC

SMCLK0

SMDAT0

SMCLK1

SMDAT1

U103

(master)

(S5-S0)

(S5-S0)

(S3-S0)

SVC

SVD

J106

translate

POP

3.3V SB-TSI

translate1.5V TSI 3.3V TSI

THERMTRIP_L

D D

MEMHOT_L

ALERT_L

THERMDC

THERMDA

SID

SIC

AMD

translate

translate

translate

VRM Power

VRM_HOT#

S1G4

PROCHOT_L

translate

ADM

C C

SO-DIMM

EVENT

MXM

THERM#

SDA

SCL

1032

Thermal disaster prevention is implemented by PROCHOT_L and THERMTRIP_L with hardware

non-system dependant functions. Fan speed control will only be implemented

by SB TSI software based implementation

KBC1100L

B B

Global

System

State

A A

G2

G2/G3

Power State / Voltage Rail Activity Summary

Processor

Sleep

State

G0

G0

G0

G0

G0

G0

G1

G1

G2

S5 LOW

G3

Power

State

S0

S0

S0

S0

S0

S0

S1

S3

S4

S5

C0

C0

C1

C2

C3

c4

OFF

OFF

OFF

OFF

OFF

OFF

5

Running

Running

Sleeping

Description

P-state transitions

under OS control

Stop grant,

caches snoopable

TBD

TBD

Powered on suspend

Suspend to RAM

Suspend to diskON

Soft-off

Battery IN

Mechanical off

Halt

RTC ALW DUAL

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

SUS RUN

ON

ON

ON

OFF

OFF

OFF

OFF

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

Group Name Description

INT: Stuff when use internal clock generator

EXT: Stuff when use external clock generator

DNI/NC: DO NOT INSTALL

KBC: Stuff when use external KBC

IMC: Stuff when use internal EC

A11:Resistors marked with "A11" is only for SB800A11 ONLY.

OFF

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

OFF

OFF

Title

Title

Title

MISCELLANEOUS TABLES

MISCELLANEOUS TABLES

MISCELLANEOUS TABLES

Size

Document Number

Size

Document Number

Size

Document Number

Custom

Custom

Custom

Date:

Date:

Date:

Thursday, August 05, 2010 54

Thursday, August 05, 2010 54

3

2

Thursday, August 05, 2010 54

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Notebook R&D Division

BM5016

BM5016

BM5016

Sheet of

Sheet of

Sheet of

6

6

1

6

Rev

Rev

Rev

1.0

1.0

1.0

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

4

5

VPJ1

VPJ1

DC JACK 5P

DC JACK 5P

PCN1

PCN1

as BM5910

VPF1

VPF1

7A

7A

1 2

1 2

PR175

PR175

10

10

R0402

R0402

1 2

PR180

PR180

6.98K,1%

6.98K,1%

R0402

R0402

13

6251_DCIN

R0402

R0402

1 2

1206

1206

SSM34PT

SSM34PT

PC127

PC108

PC130

1 2

1 2

PD13

PD13

SMA

SMA

1uF/10V,X7R

1uF/10V,X7R

1uF/10V,X7R

1uF/10V,X7R

1000pF/50V,X7R

1000pF/50V,X7R

PR186

PR186

10K

10K

R0402

R0402

PR40

PR40

NC_31.6K,1%

NC_31.6K,1%

R0402

R0402

5A

12

PC22

PC22

1000P_0402_50V7K

1000P_0402_50V7K

ACIN49

1 2

C0603PC127

C0603

1 2

C0603PC108

C0603

5V_internal_LDO

12

PC143

PC143

0.1uF/25V,Y5V

0.1uF/25V,Y5V

C0402

C0402

1 2

C0402PC130

C0402

PC146

PC131

PR37

PR37

NC_15.4K,1%

NC_15.4K,1%

1 2

R0402

R0402

PR32

PR32

10K

10K

1 2

R0402

R0402

1 2

PC132

PC132

NC_0.01uF/25V,X7R

NC_0.01uF/25V,X7R

12

C0402

C0402

R0402

R0402

15.4K,1%

15.4K,1%

PR182

PR182

13

2

1

5

AD+

SHLD2

4

SHLD1

3

12

R0402

R0402

NC_100K,1%

NC_100K,1%

PR215

PR215

AD-1

AD-2

2

Isense_SYSN

CHGVADJ49

CHG_ON49

SET_I49

PQ6

PQ6

NC_TP0610K-T1-E3_SOT23-3

NC_TP0610K-T1-E3_SOT23-3

2

PR266 NC_100K,1%

PR266 NC_100K,1%

PQ5

PQ5

NC_DTC115EUA_SC70-3

NC_DTC115EUA_SC70-3

Isense_SYSP

1 2

D D

C C

B B

AD_6251+

A A

VPFB1

VPFB1

100ohm@100MHz,3A

100ohm@100MHz,3A

fb0805

fb0805

1 2

VPFB2

VPFB2

100ohm@100MHz,3A

100ohm@100MHz,3A

fb0805

fb0805

VPFB3

VPFB3

100ohm@100MHz,3A

100ohm@100MHz,3A

fb0805

fb0805

12

100P_0402_50V8J

100P_0402_50V8J

PR47

PR47

R0402

R0402

1 2

12

R0402

R0402

4.7

4.7

PR173

PR173

5600pF/50V,Y5V

5600pF/50V,Y5V

1 2

0.01uF/25V,X7R

0.01uF/25V,X7R

1 2

2.39V_Vref

12

R0402

R0402

20K_F

20K_F

PR183

PR183

0.1 Vref

12

R0402

R0402

10.5K_F

10.5K_F

PR185

PR185

SOD323

SOD323

NC_1N4148WS

NC_1N4148WS

PD36

PD36

PD34

PD34

NC_1N4148WS

NC_1N4148WS

SOD323

SOD323

1 2

1 2

PC24

PC24

100P_0402_50V8J

100P_0402_50V8J

PC21

PC21

1K

1K

VDDP

C0603PC146

C0603

C0402PC131

C0402

PR39

PR39

100K

100K

R0402

R0402

1 2

12

12

AD+

12

PQ49

PQ49

2N7002

2N7002

SOT23

SOT23

PR41

PR41

20K

20K

R0402

R0402

PU11

PU11

15

1

19

20

5

6

11

3

9

8

10

23

ISL6251HAZ

ISL6251HAZ

SSOP24_25_150

SSOP24_25_150

EC_V3.3AL49

VDDP

VDD

CSIP

CSIN

ICOMP

VCOMP

VADJ

EN

CHLIM

VREF

ACLIM

ACPRN

12

12

12

PC23

PC23

PC253

PC253

PC255

PC255

1000P_0402_50V7K

1000P_0402_50V7K

NC_10U_1206_25V6M

NC_10U_1206_25V6M

NC_10U_1206_25V6M

NC_10U_1206_25V6M

3

1

2

PC9

PC9

1000pF/50V,X7R

1000pF/50V,X7R

C0402

C0402

1 2

ACSET

UGATE

PHASE

LGATE

CELLS

CHG_ON 49

SLP_S3# 9,11,27,40,49,51

12

PC256

PC256

NC_10U_1206_25V6M

NC_10U_1206_25V6M

R0402

R0402

12

R0402

R0402

DCIN

BOOT

PGND

CSOP

CSON

ICM

GND

PC192

PC192

1000pF/50V,NPO

1000pF/50V,NPO

C0402

C0402

PR15

PR15

51K

51K

PR48

PR48

51K

51K

2

24

17

16

18

14

13

21

22

4

7

12

1 2

1 2

1 2

PR172

PR172

0R

0R

R0402

R0402

12

PC126

PC126

0.1uF/25V,Y5V

0.1uF/25V,Y5V

C0402

C0402

12

12

12

PC129

PC129

1uF/10V,X7R

1uF/10V,X7R

C0603

C0603

12

PC191

PC191

NC_100pF/50V,NPO

NC_100pF/50V,NPO

C0402

C0402

PC134

PC134

0.01uF/25V,X7R

0.01uF/25V,X7R

C0402

C0402

12

PC128

PC128

0.1uF/25V,Y5V

0.1uF/25V,Y5V

C0402

C0402

6251_DCIN

1 2

PD32

PD32

1N4148WS

1N4148WS

SOD323

SOD323

1 2

PR184

PR184

100

100

R0402

R0402

PR176

PR176

0R

0R

R0402

R0402

4

1 2

PR11 8.2K R0402PR11 8.2K R0402

PR142

PR142

51K

51K

R0402

R0402

PR132

PR132

51K

51K

R0402

R0402

ACOFF#49

Isense_SYSP

12

PC137

PC137

0.01uF/25V,X7R

0.01uF/25V,X7R

C0402

C0402

1 2

PR212

PR212

0R

0R

R0402

R0402

12

VDDP

phase

12

PC133

PC133

3300pF/50V,X7R

3300pF/50V,X7R

C0402

C0402

1 2

0.01UF/25V,X7R

0.01UF/25V,X7R

AD_6251+

PR181

PR181

2.2

2.2

R0402

R0402

设置适配器限流值为

100mV/25m ohm=4.0A.

PR9 20K R0402PR9 20K R0402

PC2

PC2

1 2

ALW_EN

0.1uF/25V,X7R

0.1uF/25V,X7R

PQ48

PQ48

C0603

C0603

AO4419

AO4419

SO8_50_150

SO8_50_150

1

2

3

PR131

PR131

PC116

PC116

100K

100K

R0402

R0402

C0402

C0402

3

PQ47

PQ47

2N7002

2N7002

SOT23

SOT23

1

2

PR140

PR140

4.7K

4.7K

R0402

R0402

12

12

PC10

PC10

PC117

PC117

0.01uF/25V,X7R

0.01uF/25V,X7R

100pF/50V,NPO

100pF/50V,NPO

C0402

C0402

C0402

C0402

5

D

D

PQ57

PQ57

4

AO4468

AO4468

G

G

PAK1212-8

PAK1212-8

S

S

123

12

R0402

R0402

10K

10K

PR177

PR177

phase

5

D

D

PQ58

PQ58

4

AO4468

AO4468

G

G

PAK1212-8

PAK1212-8

S

S

123

ADC1 49

Layout note:

Far away from critical signal trace

Iaclim=1/PR8*(0.05*Vaclim/Vref+0.05)

充电电流

SET_I

0V 0A

0.66V 400mA

3.3V 2A

ICHG=165mV/PR179*(VCHLIM/3.3V)

AD_6251+

1 2

ALW_EN 13

PD7

PD7

5A

1 2

8

7

6

SBM54PT

SBM54PT

SMA

SMA

5

S

S

D

D

PD8

G

G

4

3

2

1 2

1 2

PD8

1 2

SBM54PT

SBM54PT

SMA

SMA

Isense_SYSP

PR133

PR133

51K

51K

R0402

R0402

PQ42

PQ42

2N7002

2N7002

SOT23

SOT23

1

1000pF/50V,X7R

1000pF/50V,X7R

12

PC136

PC136

1000pF/50V,NPO

1000pF/50V,NPO

C0402

C0402

12

PC148

PC148

1000pF/50V,X7R

1000pF/50V,X7R

C0402

C0402

2A 2A 2A

PR49

PR49

4.7F

4.7F

0603

0603

1 2

PC41

PC41

680P_50V_M_B

680P_50V_M_B

0402

0402

1 2

PR36

PR36

NC_0

NC_0

R0402

R0402

PR35

PR35

0R

0R

R0402

R0402

Isense_SYSN

del BAT_OV#

PC135

PC135

C0402

C0402

1

SHDN49

1.5A

12

12

PC144

PC144

PC142

PC142

10uF/25V,X7R

10uF/25V,X7R

0.1uF/25V,X7R

0.1uF/25V,X7R

C1206

C1206

C0603

C0603

PL3

PL3

10uH/4A/68mOHM

10uH/4A/68mOHM

1 2

MHCI06030

MHCI06030

PL11

PL11

nc_10uH/4A/68m

nc_10uH/4A/68m

LS2_1040

LS2_1040

1 2

VDDP

12

PC147

PC147

4.7uF/25V,X7R

4.7uF/25V,X7R

C1206

C1206

CELLS CELLNUMBER

CELL PIN 4 VDD

CELL PIN 3 GND

CELL PIN 2 FLOAT

1 2

PR65

PR65

0.015_1W_F

0.015_1W_F

1608

1608

470pF/50V,NPO

470pF/50V,NPO

Isense_SYSN

1 2

PR179

PR179

50mOHM,1%

50mOHM,1%

R1206

R1206

3

1 2

PR10 10 R0402PR10 10 R0402

PQ34

PQ34

AO4419

AO4419

SO8_50_150

SO8_50_150

4

8A 8A

3 6

2

1

PD4

1 2

PR16

PR16

510K

510K

R0402

R0402

BATT+

12

12

PD4

SSM34PT

SSM34PT

PC3

PC3

SMA

SMA

0.1uF/25V,Y5V

0.1uF/25V,Y5V

C0402

C0402

1

2

3 6

4

1 2

3

1

2

12

PC8

PC8

1000pF/50V,X7R

1000pF/50V,X7R

C0402

C0402

12.6V

VBATS1

VBATS1

1

TPC60

TPC60

NC_TestP

NC_TestP

PC145

PC145

10uF/25V,X7R

10uF/25V,X7R

C1206

C1206

ADAPT_OUVP=1/9*AD+

Input OVP : 22.3V

Input UVP : 17.26V

PC193

PC193

C0603

C0603

PR14 510K R0402PR14 510K R0402

1 2

3

PQ53

PQ53

2N7002

2N7002

SOT23

SOT23

PR21

PR21

510K

510K

2

R0402

R0402

1 2

12

PC138

PC138

10uF/25V,X7R

10uF/25V,X7R

C1206

C1206

5

7

8

12

8

7

5

PQ41

PQ41

AO4419

AO4419

SO8_50_150

SO8_50_150

PR12

PR12

0R

0R

R0402

R0402

PQ33

PQ33

2N7002

2N7002

SOT23

SOT23

需接到EC之

ADAPT_OUVP49

BATT+

8A

12

12

12

PC44

PC44

PC18

PC18

NC_0.1uF/25V,X7R

NC_0.1uF/25V,X7R

NC_2200pF/50V,X7R

NC_2200pF/50V,X7R

C0402

C0402

C0402

C0402

1N4148WS/LMDL914T1G_SOD323-2~D

1N4148WS/LMDL914T1G_SOD323-2~D

ADC

1 2

+VIN

12

PC7

PC7

PC43

PC43

0.01uF/25V,X7R

0.01uF/25V,X7R

NC_0.1uF/25V,X7R

NC_0.1uF/25V,X7R

C0402

C0402

C0402

C0402

PR56

PR56

10K,1%

10K,1%

R0402

R0402

LM358DT_SO8

LM358DT_SO8

PFB1

PFB1

100ohm@100MHz,3A

100ohm@100MHz,3A

1 2

FB0805

FB0805

PFB3 100ohm@100MHz,3A

PFB3 100ohm@100MHz,3A

1 2

FB0805

FB0805

PFB2 100ohm@100MHz,3A

PFB2 100ohm@100MHz,3A

8A 8A

1 2

FB0805

12

PC140

@PC140

@

PC141

@PC141

@

PC25

PC25

nc_0.1u_0402_50V7K

nc_0.1u_0402_50V7K

nc_2200P_0402_50V7K

nc_2200P_0402_50V7K

1000P_0402_50V7K

1000P_0402_50V7K

1 2

EC_V3.3AL49

PC26

PC26

@

@

nc_0.1U_0402_16V7K

nc_0.1U_0402_16V7K

AD+

1

2

8

3

ADPT_OUVP_DET

P

+

2

-

G

4

12

FB0805

PC184

PC184

5.6pF/50V,NPO

5.6pF/50V,NPO

C0402

C0402

PZD2

PZD2

2

1

BAT54S

BAT54S

sot_23

sot_23

12

12

12

PR206 R0402

PR206 R0402

PC185

PC185

5.6pF/50V,NPO

5.6pF/50V,NPO

C0402

C0402

3

PR54

PR54

133K,1%

133K,1%

R0402

R0402

PR55

PR55

931K,1%

931K,1%

需接到EC之

R0402

R0402

BATT_OVP49

PR57

PR57

133K,1%

133K,1%

R0402

R0402

100PR205

100PR205

R0402

R0402

SM_BAT_SCL

12

BAT_DAT49

BAT_CLK49

SOD323

SOD323

D88

D88

PU27A

PU27A

1

0

ADAPT_OUVP_R

PF2

PF2

7A

7A

FUSE1206

FUSE1206

1 2

PF1

PF1

7A

7A

FUSE1206

FUSE1206

1 2

100

100

EC_V3.3AL49

1N4148WS/LMDL914T1G_SOD323-2~D

1N4148WS/LMDL914T1G_SOD323-2~D

VCC_358

ADC

PR207

PR207

300K

300K

R0402

R0402

EC_V3.3AL49

PR53

PR53

1 2

10K,1%

10K,1%

R0402

R0402

VMB

SM_BAT_SCL

12

PC27

PC27

@

@

nc_0.1U_0402_16V7K

nc_0.1U_0402_16V7K

SM_BAT_SDA

PR208

PR208

R0402 1K

R0402

PZD1

PZD1

2

1

BAT54S

BAT54S

sot_23

sot_23

1 2

2

VMB

12

@PC149

@

nc_2200P_0402_50V7K

nc_2200P_0402_50V7K

1

3

4

5

6

7

1K

SOD323

SOD323

D94

D94

PC31

PC31

0.01UF/25V,X5R

0.01UF/25V,X5R

C0402

C0402

7

0

BATT_OVP_R

12

PC150

@PC150

@

PC149

nc_0.1u_0402_50V7K

nc_0.1u_0402_50V7K

bat_bp02071-p5651-7f

bat_bp02071-p5651-7f

C10376-10701-B

C10376-10701-B

BATCON2

BATCON2

1

22GND

3

4

5

6

7

BAT_INT# 49

3

SM_BAT_SDA

+VIN

1

2

PU27B

PU27B

LM358DT_SO8

LM358DT_SO8

8

5

P

+

6

-

G

4

GND1

PBATT_OVP

8

9

BATT+

12

PR50

PR50

133K,1%

133K,1%

R0402

R0402

12

PR51

PR51

931K,1%

931K,1%

R0402

R0402

12

PR52

PR52

133K,1%

133K,1%

R0402

R0402

BATT-OVP=1/9*BATT+

LI-3CELLS:13.5V----BATT-OVP=1.5012V

LI-4CELLS :18.0V----BATT-OVP=2.001V

12

PC30

PC30

0.01UF/16V,X5R

0.01UF/16V,X5R

C0402

C0402

1

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

Date:

Date:

Date:

Thursday, August 05, 2010 54D7

Thursday, August 05, 2010 54D7

5

4

3

2

Thursday, August 05, 2010 54D7

1

Notebook R&D Division

ADP IN/BATTERY CHARGER

ADP IN/BATTERY CHARGER

ADP IN/BATTERY CHARGER

BM5016

BM5016

BM5016

Sheet of

Sheet of

Sheet of

Rev

Rev

Rev

1.0

1.0

1.0

5

Offset &

OFS/VFIXEN

Droop

GND

OX

+3.3V

X

+5VOX

Metal VID Codes

SVC

SVD

0

1

0

0

1

VRM_PWRGD10,51

R98

R98

1 2

R99

R99

1 2

R104

R104

1 2

R109

R109

1 2

VDDA_PWRGD16,17

VRM_RUN_EC49

R87255 R87255

R8954.9K_1%R8954.9K_1%

100

100

100

100

100

100

100

100

1 1 0.8

VFIXEN VID Codes

SVC

0

0

1

1

R2500RR250

0R

CPU_PWRGD_SVID_REG16

R2890 0RDNIR2890 0RDNI

C180 4700P

C180 4700P

12

1 2

X7R

X7R

16V

16V

12

R881K_1%R881K_1%

C189 1200P

C189 1200P

12

1 2

C233

C233

X7R

X7R

1 2

16V

16V

180P

180P

X7R

X7R

16V

16V

Close to

CPU socket

R1110RR111

0R

12

R112 0RR112 0R

12

Updata on rev:1.1

Close to

CPU socket

R113 NC_0RR113 NC_0R

R120 0RR120 0R

SVD

0

0

1

+3.3V

12

R251

R251

10K

10K

12

CPU_SVD16

CPU_SVC16

ISP_0

ISN_0

ISN_0

12

12

D D

C C

CPU_VDD_RUN

CPU_VDD0_RUN_FB_H16

CPU_VDD0_RUN_FB_L16

B B

CPU_VDD1_RUN_FB_L16

CPU_VDD1_RUN_FB_H16

CPU_VDD_RUN

SVI

O

X

O

Output

1.10

1.0

0.9

Output

1.4

1.21

1.0

0.8

+5V

12

R47

R47

34.8K_1%

34.8K_1%

R906.81K_1%R906.81K_1%

C275 1000P

C275 1000P

1 2

X7R

X7R

16V

16V

change from 16.2k to 16.5k

R139 NC_10K_1%R139 NC_10K_1%

1 2

12

NC_100K_0402_1%_TH11-4H104FT

NC_100K_0402_1%_TH11-4H104FT

Parallel

+1.8V

R170 10K_1%R170 10K_1%

Parallel

VFIX

X

CPU_VDDNB_RUN_FB_H16

+5V

R26710R267

10

1 2

R18610R186

10

1 2

+VIN

R1990RR199

0R

12

R142

R142

100K

100K

1

12

OFS/VFIXEN

2

PGOOD

R2230RR223

0R

12

3

PWROK

R2460RR246

0R

4

12

SVD

R2470RR247

0R

12

5

SVC

R2480RR248

0R

12

6

ENABLE

12

7

RBIAS

R86

R86

8

82.5K_1%

82.5K_1%

OCSET

9

VDIFF_0

10

FB_0

11

12

R93

R93

4.02K_1%

4.02K_1%

12

RTN_1

Update on rev:1.1

COMP_0

12

VW_0

2

C276

C276

0.1U

0.1U

1

X7R

X7R

16V

16V

12

12

R9116.2K_1%R9116.2K_1%

PH2

PH2

R2490RR249

1

C372

C372

1U

1U

2

X7R

X7R

10V

10V

1

C377

C377

0.1U

0.1U

2

X7R

X7R

25V

25V

49

48

47

VIN

VCC

GND

ISN_0

ISP_013VSEN_0

14

CPU_VDDNB_RUN

0R

12

R144

R144

22K_1%

22K_1%

1

1

C376

C376

33P

33P

2

2

X7R

X7R

12

25V

25V

46

45

FB_NB

COMP_NB

Pin 49 is GND Pin

ISL6265_QFN_48 6x6

ISL6265_QFN_48 6x6

RTN_0

15

16

4A

C375

C375

1200P

1200P

X7R

X7R

25V

25V

R145

R145

44.2K_1%

44.2K_1%

4

VDD_NB

PJ2

PJ2

2

112

JUMP_43X118

JUMP_43X118

R25247R252

47

12

R25347R253

47

PC215

PC215

12

330U_2.5V_R9mOHM

330U_2.5V_R9mOHM

Updata on rev:1.1

R2700RR270

0R

12

Parallel

1

C374

C374

1000P

1000P

2

X7R

X7R

25V

25V

12

R137

R137

11.5K_1%

11.5K_1%

42

40

43

44

41

RTN_NB

FSET_NB

VSEN_NB

PGND_NB

OCSET_NB

RTN_1

VSEN_1

VDIFF_119FB_120COMP_1

17

18

21

RTN_1

2

2

1

C277

C277

4700P

4700P

1

X7R

X7R

R128

R128

16V

16V

1K_1%

1K_1%

1 2

R127

R127

255

255

1 2

1 2

1

12

+

+

2

12

CPU_VDDNB_RUN_FB_L 16

38

37

39

LGATE_NB

PHASE_NB

UGATE_NB

VW_122ISP_123ISN_1

24

R266

R266

2

6.81K_1%

6.81K_1%

C356

C356

1000P

1000P

1 2

1

X7R

X7R

16V

16V

C344

C344

1200P

1200P

X7R

X7R

2

16V

16V

C345

C345

180P

180P

1

X7R

X7R

16V

16V

R129

R129

54.9K_1%

54.9K_1%

PL8

PL8

1 2

2.2UH +-20% 8A 20mo

2.2UH +-20% 8A 20mo

C73

C73

10U_0805_10V

10U_0805_10V

LGATE_NB

PHASE_NB

UGATE_NB

U2

U2

36

BOOT_NB

35

BOOT_0

34

UGATE_0

33

PHASE_0

32

PGND_0

31

LGATE_0

30

PVCC

29

LGATE_1

28

PGND_1

27

PHASE_1

26

UGATE_1

25

BOOT_1

2

C360

C360

0.1U

0.1U

1

X7R

X7R

16V

16V

567

8

D

D

PQ59

PQ59

AO4468

AO4468

SO8_50_150

SO8_50_150

S

S

123

PHASE_NB

567

8

D

D

S

S

123

1

C371

C371

0.22U

0.22U

2

X7R

X7R

12

25V

25V

R256

R256

2.2

2.2

C362

C362

R257

R257

1 2

2.2

2.2

0.22U

0.22U

UGATE_0

X7R

X7R

25V

25V

PHASE_0

+5V

LGATE_0

C61

C61

LGATE_1

2.2uF_X7R

2.2uF_X7R

PHASE_1

UGATE_1

C361

C361

R136 2.2R136 2.2

12

12

0.22U

0.22U

X7R

X7R

25V

25V

ISN_1

12

R131

R131

4.02K_1%

4.02K_1%

NC_PH3

NC_PH3

R134 NC_10K_5%R134 NC_10K_5%

1 2

12

100K_0402_1%_TH11-4H104FT

100K_0402_1%_TH11-4H104FT

ISN_1ISN_1

Fou Uni-plane:

G16,G17,R39:Assembly

R38:Not Assembly

4

UGATE_NB

G

G

PQ55

PQ55

AO4468

AO4468

SO8_50_150

SO8_50_150

4

LGATE_NB

G

G

UGATE_0

3 5

12

3 5

12

UGATE_1

LGATE_1 LGATE_1

3 5

12

R130 16.2K_1%R130 16.2K_1%

12

C62

C62

PQ31

PQ31

SIR462DP-T1-GE3

SIR462DP-T1-GE3

241

PQ35

PQ35

SIR466DP-T1-GE3

SIR466DP-T1-GE3

241

3 5

PQ39

PQ39

SIR466DP-T1-GE3

SIR466DP-T1-GE3

241

ISP_1

10U_1210_25V

10U_1210_25V

241

12

C64

C64

VIN1

Panasonic

ETQP4LR36WFC

LGATE_0

PQ32

PQ32

SIR462DP-T1-GE3

SIR462DP-T1-GE3

Panasonic

ETQP4LR36WFC

10U_1210_25V

10U_1210_25V

VIN3

VIN2

3 5

3 5

1 2

PAD-OPEN 4x4m

PAD-OPEN 4x4m

PAD-OPEN 4x4m

PAD-OPEN 4x4m

PAD-OPEN 4x4m

PAD-OPEN 4x4m

1

C378

C378

2200P

2200P

2

X7R

X7R

25V

25V

PQ37

PQ37

SIR466DP-T1-GE3

SIR466DP-T1-GE3

241

1

C380

C380

2200P

2200P

2

X7R

X7R

25V

25V

PQ40

PQ40

SIR466DP-T1-GE3

SIR466DP-T1-GE3

241

PJP36

PJP36

PJP34

PJP34

1 2

PJP35

PJP35

1 2

1

C379

C379

0.01u

0.01u

2

X7R

X7R

25V

25V

12

PR2272.2_5%PR2272.2_5%

1

C1931

C1931

2

1

2

12

PR228

PR228

2.2_5%

2.2_5%

1

C1932

C1932

2

3

+VIN

+VIN

12

12

12

C68

C68

C69

C69

C66

C66

10U_1210_25V

10U_1210_25V

10U_1210_25V

10U_1210_25V

10U_1210_25V

10U_1210_25V

0.36UH_PCMC104T-R36MN1R17_30A_20%

0.36UH_PCMC104T-R36MN1R17_30A_20%

1 2

PL15

PL15

680P_50V8J

680P_50V8J

ISP_0

ISN_0

12

12

12

C77

C77

C74

C74

C75

C381

C381

0.01u

0.01u

X7R

X7R

25V

25V

C75

10U_1210_25V

10U_1210_25V

10U_1210_25V

10U_1210_25V

10U_1210_25V

0.36UH_PCMC104T-R36MN1R17_30A_20%

0.36UH_PCMC104T-R36MN1R17_30A_20%

10U_1210_25V

1 2

PL16

PL16

680P_50V8J

680P_50V8J

2

CPU_VDD_RUN

1 2

1 2

1 2

C63

C63

C71

C71

C26

C26

10nF

10nF

180P

180P

0.22uF_6.3V

0.22uF_6.3V

CPU_VDD_RUN

VIN1

CPU_VDD_RUN

C44

C44

22uF_0805_6.3V

22uF_0805_6.3V

2

2

2

C338

C338

C389

C389

C340

C340

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

1

1

1

X7R

X7R

X7R

X7R

X7R

X7R

16V

16V

16V

16V

16V

16V

2

2

2

C383

C383

C382

C382

0.1U

0.1U

0.1U

0.1U

1

1

1

X7R

X7R

X7R

X7R

16V

16V

16V

16V

Updata on rev:1.1 for esd

C384

C384

0.1U

0.1U

X7R

X7R

16V

16V

2

2

2

C385

C385

0.1U

0.1U

1

X7R

X7R

16V

16V

2

C387

C387

C386

C386

C388

C388

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

1

1

1

X7R

X7R

X7R

X7R

X7R

X7R

16V

16V

16V

16V

16V

16V

LS2_1040

LS2_1040

1 2

1 2

PC217

PC217

1 2

1 2

C43

C43

C31

C31

C49

C49

22uF_0805_6.3V

22uF_0805_6.3V

22uF_0805_6.3V

22uF_0805_6.3V

22uF_0805_6.3V

22uF_0805_6.3V

CPU_VDD_RUN

1

1

+

+

+

+

PC218

PC218

2

2

330U_2.5V_R9mOHM

330U_2.5V_R9mOHM

330U_2.5V_R9mOHM

330U_2.5V_R9mOHM

1

0.7 - 1.3 V 36A

VIN2

LS2_1040

LS2_1040

1

+

+

PC220

PC220

2

330U_2.5V_R9mOHM

330U_2.5V_R9mOHM

1 2

CPU_VDD_RUN

1

+

+

PC221

PC221

2

330U_2.5V_R9mOHM

330U_2.5V_R9mOHM

CPU_VDD_RUN

1 2

1 2

1 2

C50

C50

C52

C52

C45

C45

C48

C48

22uF_0805_6.3V

22uF_0805_6.3V

22uF_0805_6.3V

22uF_0805_6.3V

22uF_0805_6.3V

22uF_0805_6.3V

22uF_0805_6.3V

22uF_0805_6.3V

A A

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

CPU CORE PWR

CPU CORE PWR

CPU CORE PWR

BM5016

BM5016

BM5016

Notebook R&D Division

Sheet of

Sheet of

Sheet of

Rev

Rev

Rev

1.0

1.0

1.0

Title

Title

Title

Size

Document Number

Size

Document Number

Size

Document Number

Date:

Date:

Date:

Thursday, August 05, 2010 54D8

Thursday, August 05, 2010 54D8

5

4

3

2

Thursday, August 05, 2010 54D8

1

5

+3.3VDual

D D

+3.3VDual

PR143

PR143

NC_10K_J

NC_10K_J

0402

0402

PR97

PR97

1 2

NC_1K_F

NC_1K_F

0402

0402

VDDIO_SUS_EN_EC49

SLP_S5#11,27,46,49

C C

1 2

1 2

PR92

PR92

1K_F

1K_F

0402

0402

PC83

PC83

0603_X5R

0603_X5R

NC_1U_10V_K

NC_1U_10V_K

12

12

PC78

PC78

0402_NPO

0402_NPO

NC_100P_50V_K

NC_100P_50V_K

PR93

PR93

1 2

12

0402

0402

120K_F

120K_F

PR89

PR89

10K_J

10K_J

0402

0402

1 2

1 2

DDR_TRIP

DDR_S5

DDR_VFB

DDR_RF

12

PR94

PR94

PR96

PR96

10K

10K

0402

0402

PR103

PR103

NC_0_F

NC_0_F

0402

0402

1

2

3

4

5

TPS51218DSCR

TPS51218DSCR

null

null

0402

0402

100K_F

100K_F

PU3

PU3

PGOOD

TRIP

EN

VFB

RF

VDRAM_PWRGD 49

11

GND

10

VBST

9

DRVH

8

SW

7

V5IN

6

DRVL

12

PC84

PC84

4.7U_10V_K

4.7U_10V_K

0805_X5R

0805_X5R

4

DDR_BST

DDR_DH

DDR_LX

DDR_DL

PC77

PC77

0.1U_25V_M

0.1U_25V_M

0603_X5R

0603_X5R

12

PR98

PR98

11.5K_F

11.5K_F

0402

0402

1 2

PR90

PR90

0R

0R

0603

0603

1 2

+5VDual

12

PR112

PR112

0R0603

0R0603

3

PJ7

PJ7

+

+

PC81

PC81

330U_2V_7.3x4.3

330U_2V_7.3x4.3

1 2

jump_gap_open_161x54

jump_gap_open_161x54

PJ8

PJ8

1 2

jump_gap_open_161x54

jump_gap_open_161x54

PJ9

PJ9

1 2

jump_gap_open_161x54

jump_gap_open_161x54

12

0402_X5R

0402_X5R

PC80

PC80

0.1U_6.3V_K

0.1U_6.3V_K

DDR_DCBATOUT

12

12

12

PC75

PC75

PC74

PC74

1206_X5R

1206_X5R

0603_X5R

D

D

PQ29

PQ29

S

S

SIR462DP-T1-GE3

SIR462DP-T1-GE3

5

D

D

4

G

G

S

S

231

SIR466DP-T1-GE3

SIR466DP-T1-GE3

R2860 200RR2860 200R

0.1U_25V_M

0.1U_25V_M

0603_X5R

10U_25V_M

10U_25V_M

NC_1UH +-20% FDV0630-1R0M=P3 12A

NC_1UH +-20% FDV0630-1R0M=P3 12A

PL9

PL9

1 2

PL12

PL12

1.0UH_11.5x10.4

1.0UH_11.5x10.4

1 2

12

PR91

PR91

3.3_J

3.3_J

0603

0603

PQ36

PQ36

12

PC82

PC82

1000P_50V_M

1000P_50V_M

SIR466DP-T1-GE3

SIR466DP-T1-GE3

0603_X7R

0603_X7R

update on rev:1.1

5

4

G

G

231

5

D

D

4

G

G

PQ30

PQ30

S

S

231

CPU_VDDIO_SUS_FB_H16

R2853

R2853

200R

200R

1206_X5R

1206_X5R

Place these CAPS

PC76

PC76

close to FETs

10U_25V_M

10U_25V_M

12

+

+

DDR_OUT1

PC79

PC79

330U_2V_7.3x4.3

330U_2V_7.3x4.3

12

+VIN

Iocp=19.6A

12A

3A

CPU_VDDIO_SUS

2

1

B B

CPU_VDDIO_SUS

+3.3VDual

PR82

PR82

100K_J

100K_J

0402

0402

1 2

0603_X5R

0603_X5R

NC_1U_10V_K

NC_1U_10V_K

61

D

D

Q50B

Q50B

2N7002DW-7-F

2N7002DW-7-F

G

G

2

S

S

12

4

PR267

PR267

0R

0R

0402

0402

A A

5

SLP_S3#7,11,27,40,49,51

MEM_VTT_EN49

1 2

PR268

PR268

1 2

NC_0 0402

NC_0 0402

PC197

PC197

2A

PC199

PC199

12

4.7U_6.3V_K

4.7U_6.3V_K

R576

0603_X5R

0603_X5R

R576

100K_F

100K_F

0402

0402

12

R577

R577

PC194

PC194

0603_X5R

0603_X5R

1U_10V_K

1U_10V_K

100K_F

100K_F

0402

0402

1 2

34

D

D

Q50A

Q50A

2N7002DW-7-F

2N7002DW-7-F

G

G

5

S

S

PU4

PU4

1

VIN

2

GND2

3

REFEN

4

VOUT

RT9199GSP_SO8

RT9199GSP_SO8

12

12

12

0402_X5R

0402_X5R

PC86

PC86

0.1U_6.3V_K

0.1U_6.3V_K

PC87

PC87

10U_6.3V_Y

0805_Y5V

10U_6.3V_Y

0805_Y5V

VCNTL

GND1

12

NC1

NC2

NC3

PC88

PC88

3

10U_6.3V_Y

0805_Y5V

10U_6.3V_Y

0805_Y5V

6

5

7

8

9

+0_75VRUN

2A

PJ10

PJ10

1 2

jump_gap_open_161x54

jump_gap_open_161x54

1U_10V_K

1U_10V_K

PC98

PC98

MEM_VTT

12

0603_X5R

0603_X5R

+3.3VDual

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

1

BM5016

BM5016

BM5016

Notebook R&D Division

Sheet of

Sheet of

Sheet of

9

9

9

Rev

Rev

Rev

1.0

1.0

1.0

Title

Title

Title

CPU MEM PWR

CPU MEM PWR

CPU MEM PWR

Size

Document Number

Size

Document Number

Size

Document Number

C

C

C

Date:

Date:

Date:

Thursday, August 05, 2010 54

Thursday, August 05, 2010 54

2

Thursday, August 05, 2010 54

5

4

3

2

1

32

C2946

C2946

100nF

100nF

DNI

DNI

Q2912

Q2912

NC_2N7002E

NC_2N7002E

CAP_7343

CAP_7343

1

2

FB_VCC_NB-1

R2965

R2965

133K

133K

32

Q2908

Q2908

1

2N7002E

2N7002E

参数待定

RS880M VCC_NB

When JU2903 is installed with a jumper

+1.1VP

12

12

+

+

+

+

PC172

PC172

PC170

PC170

CAP_7343

CAP_7343

220UF/6.3V/18M 6R3ME221M

220UF/6.3V/18M 6R3ME221M

+1.1V

R2981 1kR2981 1k

1

C2144

C2144

2

1U_0603_10V4Z

1U_0603_10V4Z

1

+5VDUAL

PJ13

PJ13

2

JUMP_43X118

JUMP_43X118

R2982

R2982

10k

10k

Q2941

Q2941

MMBT3904

MMBT3904

2 3

112

GPIO Mode Power Shift

PWM

01STRP_DATA

0.95V

N/A

1.1VRS880M VCC_NB

0.95V 1.25V

+1.1VDUAL

+5VDUAL

R2987

R2987

10k

10k

32

Q2909

Q2909

1

2N7002E

2N7002E

+1.2V_PWRGD 51

PC68

PC68

12

12

1U_0402_6.3V6K

12

4

VCC1

+5VDUAL

R1794

R1794

100K_0402_5%

100K_0402_5%

1 2

61

Q3638A

Q3638A

2

2N7002DW-T/R7_SOT363-6

2N7002DW-T/R7_SOT363-6

1U_0402_6.3V6K

2.2_0603_1%

2.2_0603_1%

1 2

3

VCC2

0.1U_0402_16V7K

0.1U_0402_16V7K

PR88

PR88

12

2

VIN2

1 2

+5VDUAL+5VDUAL

PC69

PC69

0.1U_0603_25V7K

0.1U_0603_25V7K

PR110

PR110

10_0603_1%

10_0603_1%

12

PC73

PC73

1000P_0402_50V7K

1000P_0402_50V7K

1

GND_T

FSET2

PGOOD2

OCSET2

PHASE2

UGATE2

21

BST_+1.1V

PC93

PC93

1U_0402_6.3V6K

1U_0402_6.3V6K

12

@PC110

@

PC110

FB2

VO2

EN2

12

<DEVICE>

<DEVICE>

1 2

29

28

27

26

25

24

23

22

0_0603_5%

0_0603_5%

1 2

LG_+1.1V

12

@

@

NC_10U_0805_16V7K

NC_10U_0805_16V7K

ISL6228_B+

PR115

PR115

18.2K_0402_1%

18.2K_0402_1%

1 2

+1.1VDUAL_EN

PC89

@PC89

@

nc_0.01U_0402_25V7K

nc_0.01U_0402_25V7K

1 2

UG_+1.1V

PR117

PR117

12

@

@

PC112

PC112

NC_10U_0805_16V7K

NC_10U_0805_16V7K

<DEVICE>

<DEVICE>

VLDT +1.1V

PC67

PC67

1U_0402_6.3V6K

1U_0402_6.3V6K

PR87

PR87

2.2_0603_1%

+VIN

PJ15

PJ15

JUMP_43X118

JUMP_43X118

2

112

PJ12

D D

PJ12

JUMP_43X118

JUMP_43X118

2

8.2K_0402_1%

8.2K_0402_1%

1 2

PR111

PR111

112

ISL6228_B+

PC72

PC72

1000P_0402_50V7K

1000P_0402_50V7K

35K_0402_1%

35K_0402_1%

12

PR95

PR95

PR104

PR104

3.3K_0402_5%

3.3K_0402_5%

1 2

12

12

12

PC124

@PC124

@

nc_2200P_0402_50V7K

nc_2200P_0402_50V7K

ISL6228_B++

12

12

PC104

PC104

PC105

1 2

12

12

4.7U_1206_25V6K

4.7U_1206_25V6K

PR102

PR102

9.1K_0402_1%

9.1K_0402_1%

PC105

4.7U_1206_25V6K

4.7U_1206_25V6K

8

D36D45D27D1

S3

S2

S1

3

2

1

8

D36D45D27D1

G

S3

S2

S1

3

2

1

PC85

PC85

0.033U_0603_50V7K

0.033U_0603_50V7K

1 2

VCC_NB

0.95V--1.1V 12A

PJ11

PJ11

C C

2

JUMP_43X118

JUMP_43X118

112

220U_6.3V_3528

220U_6.3V_3528

6TPC47MB

6TPC47MB

VCC_NBP

12

PC34

PC34

+

+

12

+

+

220U_6.3V_3528

220U_6.3V_3528

6TPC47MB

6TPC47MB

PC33

PC33

1UH_18A_20%

1UH_18A_20%

1 2

680P_0402_50V7K@

680P_0402_50V7K@

PL17

PL17

LS2_1040

LS2_1040

4.7_1206_5%@

4.7_1206_5%@

PR113

PR113

PC97

PC97

DCR 3.3m ohm(max) Cout ESR=15m ohm

+1.05VSP

Vo=Vref*((PR80+PR82)/PR80)

Ipeak=14.02A, Imax=9.81A

Iocp=19A

Csen=L/(Rocset*DCR)

0.015U=1U/(Rocset*6m) Rocset=11.111K~11.8K

Iocp=(Rocset*10uA)/DCR

Iocp=(11K*10uA)/(3.3m ohm*1.3) =15.1A

VCC_NBP

12

B B

A A

NC_0.1U_0402_16V7K

NC_0.1U_0402_16V7K

12

@PC95

@

PC95

PC109

@

PC109

@

NC_10U_0805_16V7K

NC_10U_0805_16V7K

<DEVICE>

<DEVICE>

VRM_PWRGD8,51

PC139

@PC139

@

nc_0.1u_0402_50V7K

nc_0.1u_0402_50V7K

PR107

PR107

60.4K_0402_1%

60.4K_0402_1%

<BOM Structure>

<BOM Structure>

6228_VCC_NBO1

PQ23

PQ23

SI4172DY-T1-GE3

SI4172DY-T1-GE3

4

G

PQ22

PQ22

SI4168DY-T1-GE3

SI4168DY-T1-GE3

4

PC101

PC101

0.1U_0402_16V7K

0.1U_0402_16V7K

ISL6228_B++

ISL6228_B++

PR188

PR188

0_0402_5%

0_0402_5%

1 2

+1.2V_PWRGD

1 2

FB_VCC_NB-1FB_VCC_NB

OCSET_VCC_NB

VCC_NB_EN OCSET_+1.1V

LX_VCC_NB

UG_VCC_NB

PR116

PR116

0_0603_5%

0_0603_5%

12

PR178

@PR178

@

10K_0402_5%

10K_0402_5%

1 2

PC71

PC71

1000P_0402_50V7K

1000P_0402_50V7K

8

FB1

9

VO1

10

OCSET1

11

EN1

12

PHASE1

13

UGATE1

12

14

BST_VCC_NB

BOOT1

+5VDUAL +5VDUAL

PC100

PC100

1U_0402_6.3V6K

1U_0402_6.3V6K

LG_VCC_NB

VCC_NB_EN

12

PC103

@PC103

@

0.1U_0402_16V7K

0.1U_0402_16V7K

+1.1V_EN

2.2_0603_1%

12

PC70

PC70

0.1U_0603_25V7K

0.1U_0603_25V7K

PR106

PR106

10_0603_1%

10_0603_1%

12

12

PR108

PR108

22K_0402_1%

22K_0402_1%

1 2

7

PGOOD1

6

FSET1

5

VIN1

Vref=0.6V

PU6

PU6

ISL6228HRTZ-T_QFN28_4X4

ISL6228HRTZ-T_QFN28_4X4

PVCC115LGATE116PGND117PGND218LGATE219PVCC220BOOT2

1 2

During Power Up

0 < 3.3v - 1.8v < 2.1v

VLDT_PWRGD#

PR189

@PR189

@

1K_0402_5%

1K_0402_5%

1 2

12

R1801

R1801

100K_0402_5%

100K_0402_5%

Updated on Rev2.0

NB_VOL_DET:

0: 0.95V / 1.1V

1:0.95V / 1.25V

NB_VOL_DET49

STRP_DATA23

R1822

R1822

0_0402_5%

0_0402_5%

1V1DUAL_PWRGD 49,51

FB_+1.1V-1 FB_+1.1V

6228_+1.1VO2

+5VDUAL

R2954 0RR2954 0R

PQ25

PQ25

SI4172DY-T1-GE3

SI4172DY-T1-GE3

S_LX_+1.1V

PQ24

PQ24

SI4168DY-T1-GE3

SI4168DY-T1-GE3

PC96

PC96

0.1U_0402_16V7K

0.1U_0402_16V7K

1 2

+1.1VP

PC113

PC113

PJ20

PJ20

2

112

JUMP_43X118

JUMP_43X118

update on rev:1.1

8

D36D45D27D1

4

G

S3

S2

S1

3

2

1

8

D36D45D27D1

4

G

S3

S2

3

2

1

update on rev:1.1

VRM_PWRGD8,51

1V1_EN_EC49

+VSB

R2953 0R2953 0

PR101

PR101

56K_0402_1%

56K_0402_1%

ISL6228_B+

12

S1

DCR 6m ohm(max) Cout ESR=15m ohm

Vo=0.6*((PR87+PR83)/PR83)=1.8V

1.8VP Ipeak=11.93A, Imax=8.351A

Csen=L/(Rocset*DCR)=1uF/(Rocset*6m ohm)=0.022uF

=>Rocset=7.575K, Choose 10K because of thermal factor

Iocp=(Rocset*10uA)/DCR=(10K*10uA)/(0.006*1.3)=12.82A

C2147

C2147

10U_0805_10V4Z

10U_0805_10V4Z

1 2

12

PC99

PC99

4.7U_1206_25V6K

4.7U_1206_25V6K

12

PR109

@PR109

@

4.7_1206_5%

4.7_1206_5%

12

PC94

@PC94

@

680P_0402_50V7K

680P_0402_50V7K

1

C2177

C2177

2

10U_0805_10V4Z

10U_0805_10V4Z

R1802

R1802

200K_0402_5%

200K_0402_5%

VLDT_PWRGD#

+5V

R3028 NC_33KR3028 NC_33K

R2972

R2972

NC_56K

NC_56K

12

12

@PC92

@

PC90

PC90

nc_2200P_0402_50V7K

nc_2200P_0402_50V7K

4.7U_1206_25V6K

4.7U_1206_25V6K

D2910RB751V-40 D2910RB751V-40

1 2

+1.1VDUAL

1

2

12

5

R3020

R3020

NC_4.7K

NC_4.7K

+5V

32

1

R29582KR2958

2K

PR99

PR99

3.3K_0402_5%

3.3K_0402_5%

PR114

PR114

51K_0402_1%

51K_0402_1%

1 2

20K_0402_1%

20K_0402_1%

1 2

68nf_0603_50V7K

68nf_0603_50V7K

1 2

PC92

PC123

@PC123

@

nc_0.1u_0402_50V7K

nc_0.1u_0402_50V7K

PR105

PR105

15K_0402_1%

15K_0402_1%

PL4

PL4

1uH/12A10mOHM

1uH/12A10mOHM

1 2

1 2

MHCI06030

MHCI06030

+3.3V

R2996

R2996

47K

47K

R29240R DNI R29240R DNI

4

U64

U64

5

7

8

SI4168_SO8

SI4168_SO8

VLDT_GATE

3

Q3638B

Q3638B

2N7002DW-T/R7_SOT363-6

2N7002DW-T/R7_SOT363-6

4

R3027

R3027

NC_56.2K

NC_56.2K

1

R2966

R2966

47K

47K

Q2917

Q2917

2N7002E

2N7002E

PC91

PC91

1000P_0402_50V7K

1000P_0402_50V7K

12

1 2

PR100

PR100

PC102

PC102

220UF/6.3V/18M 6R3ME221M

220UF/6.3V/18M 6R3ME221M

+1.1V_EN

VLDT 1.1V 2A

36

2

1

C2146

C2146

10U_0805_10V4Z

10U_0805_10V4Z

1

C2145

C2145

0.1U_0603_25V7K

0.1U_0603_25V7K

2

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Notebook R&D Division

1

Notebook R&D Division

BM5016

BM5016

BM5016

Sheet of

Sheet of

Sheet of

Rev

Rev

Rev

1.0

1.0

1.0

10

10

10

Title

Title

Title

1V1DUAL/VLDT/VCC_NB/+1.1V

1V1DUAL/VLDT/VCC_NB/+1.1V

1V1DUAL/VLDT/VCC_NB/+1.1V

Size

Document Number

Size

Document Number

Size

Document Number

Custom

Custom

Custom

Thursday, August 05, 2010 54

Thursday, August 05, 2010 54

Thursday, August 05, 2010 54

Date:

Date:

5

4

3

2

Date:

5

12

PC164

@PC164

@

1U_0402_16V7K

1U_0402_16V7K

D D

1V8_PWRGD51

1

C2130

C2130

C2131

C2131

10U_0805_10V4Z

10U_0805_10V4Z

1

+3.3VDUAL

32

+VSB

C2141

C2141

10U_0805_10V4Z

10U_0805_10V4Z

R3055

R3055

100K

100K

Q3041

Q3041

2N7002E

2N7002E

2

10U_0805_10V4Z

10U_0805_10V4Z

R1795

R1795

200K_0402_5%

200K_0402_5%

SUSP

1

C2142

C2142

2

10U_0805_10V4Z

10U_0805_10V4Z

C C

B B

SLP_S3#7,9,27,40,49,51

12

12

R1819

R1819

R1811

R1811

10K_0402_5%

10K_0402_5%

NC_1K_0402_5%

NC_1K_0402_5%

R2974 0RR2974 0R

R2983 1KR2983 1K

SLP_S3#7,9,27,40,49,51

1U_0402_16V7K

1U_0402_16V7K

update rev:1.1

+5DUAL TO +5V

+5VDUAL +5V

U61

U61

5

7

8

1

SI4800BDY-T1-E3_SO8

SI4800BDY-T1-E3_SO8

2

12

61

Q31A

Q31A

2

2N7002DW-T/R7_SOT363-6

2N7002DW-T/R7_SOT363-6

+3VDUALTO +3.3V

+3.3VDUAL +3.3V

U63

U63

5

7

8

1

SI4800BDY-T1-E3_SO8

SI4800BDY-T1-E3_SO8

2

SUSP

U2904

U2904

7

POK

VOUT1

APL5912

APL5912

8

EN

GND

12

1

12

R1827

R1827

PC189

PC189

10K_0402_5%

10K_0402_5%

@

@

4

36

2

1

1

C2132

C2132

10U_0805_10V4Z

10U_0805_10V4Z

2

5V/3.3V_GATE

1

C2137

C2137

NC_0.1U_0603_25V7K

NC_0.1U_0603_25V7K

2

update on rev:1.1

4

36

2

1

1

C2139

C2139

10U_0805_10V4Z

10U_0805_10V4Z

2

5V/3.3V_GATE

CPU_VDD_RUN +5V

R3058

R3058

100R

100R

32

Q3040

Q3040

1

2N7002E

2N7002E

C3013

C3013

R3053

R3053

100nF

100nF

100R

100R

32

Q3030

Q3030

1

2N7002E

2N7002E

6

VIN

VCNTL

VOUT

FB

vin1

9

update rev:1.1

1

C2133

C2133

2

1U_0603_10V4Z

1U_0603_10V4Z

1

C2140

C2140

2

1U_0603_10V4Z

1U_0603_10V4Z

R2975 10R2975 10

5

3

4

2

12K_0402_5%

12K_0402_5%

CPU_VDDNB_RUN

1

1

4

+5VDUAL

+3.3VDUAL

12

PC188

@ <DEVICE>PC188

@ <DEVICE>

22U_1206_6.3V

22U_1206_6.3V

12

R1810

R1810

PC190

PC190

1 2

15K_0402_5%

15K_0402_5%

12

R1809

R1809

C2135

C2135

10U_0805_10V4Z

10U_0805_10V4Z

+VSB

R3040

R3040

100R

100R

32

Q3033

Q3033

2N7002E

2N7002E

R3059

R3059

100R

100R

32

Q3039

Q3039

2N7002E

2N7002E

@ <DEVICE>

@ <DEVICE>

NC_0.1U_0402_16V7K

NC_0.1U_0402_16V7K

22U_1206_6.3V

22U_1206_6.3V

PC162

PC162

1 2

68P_0402_16V7K

68P_0402_16V7K

@

@

CPU_VDDIO_SUS

1

1

C2143

C2143

2

2

10U_0805_10V4Z

10U_0805_10V4Z

12

R1796

R1796

200K_0402_5%

200K_0402_5%

5

1V8_PWRGD#

1V8_PWRGD51

+3.3V MEM_VTT

R3064

R3064

100R

100R

32

Q3032

Q3032

1

2N7002E

2N7002E

+1.5V

R3060

R3060

100R

100R

32

Q3038

Q3038

1

2N7002E

2N7002E

+1.8VP

2

12

PC187

@PC187

@

4

U62

U62

5

7

8

SI4800BDY-T1-E3_SO8

SI4800BDY-T1-E3_SO8

+1.5V_GATE

3

Q30B

Q30B

2N7002DW-T/R7_SOT363-6

2N7002DW-T/R7_SOT363-6

4

100K_0402_5%

100K_0402_5%

1A

+1.8V

PJ25

PJ25

112

JUMP_43X118

JUMP_43X118

+1.5V

R3061

R3061

100R

100R

R3065

R3065

100R

100R

2

Q3034

Q3034

2N7002E

2N7002E

Q3031

Q3031

2N7002E

2N7002E

1

2

C2134

C2134

1U_0603_10V4Z

1U_0603_10V4Z

+5VDUAL

1 2

61

R2976 1kR29761k

1

2

R1792

R1792

100K_0402_5%

100K_0402_5%

Q30A

Q30A

2N7002DW-T/R7_SOT363-6

2N7002DW-T/R7_SOT363-6

1

CPU_VDDRVCC_NB VLDT

R3050

R3050

100R

100R

32

1

36

2

1

C2136

C2136

10U_0805_10V4Z

10U_0805_10V4Z

1

C2138

C2138

0.1U_0603_25V7K

0.1U_0603_25V7K

2

1V8_PWRGD#

12

R1797

R1797

32

1

+1.8V +1.1V

32

1

Q3029

Q3029

2N7002E

2N7002E

3

+5VDUAL

R2988

R2988

10k

10k

R2989 0R2989 0

Q3048

Q3048

2N7002E

2N7002E

1V5_PWRGD 51

+VIN

PR34

PR34

0_0402_5%

0_0402_5%

1

+3.3VDUAL

12

PC121

PC121

NC_10uF/6.3V,X5R_+1.5V

NC_10uF/6.3V,X5R_+1.5V

C0805

C0805

1 2

1 2

PR151

PR151

NC_10K,5%_+1.5V

NC_10K,5%_+1.5V

R0402

R0402

12

PC19

PC19

@

@

0.22U_0402_16V7K

0.22U_0402_16V7K

3

C525

C525

NC_0.01uF/10V,X7R_+1.5V

NC_0.01uF/10V,X7R_+1.5V

1 2

C0603

C0603

PU10 APL5312-15B_+1.5VPU10 APL5312-15B_+1.5V

VIN1VOUT

SHDN#

V3V5DUAL_PWRGD13,49

1

+5VDUAL

Q2940

Q2940

MMBT3904

MMBT3904

2 3

32

R2977

R2977

10k

10k

1

FOR SB820M 15MA

R3062

R3062

100R

100R

32

Q3037

Q3037

2N7002E

2N7002E

R3066

R3066

100R

100R

32

Q3042

Q3042

1

2N7002E

2N7002E

PR29

PR29

100K_0402_1%

100K_0402_1%

PR31

PR31

22K_0402_1%

22K_0402_1%

1 2

32

Q3049

Q3049

2N7002E

2N7002E

Updata on rev:1.3

BP

GND

2

DEL +1.5V

2

12

5

4

C518

C518

NC_0.01uF/10V,X7R+1.5V