123456

REVISION RECORD

LTR ECO NO: APPROVED:

DATE:

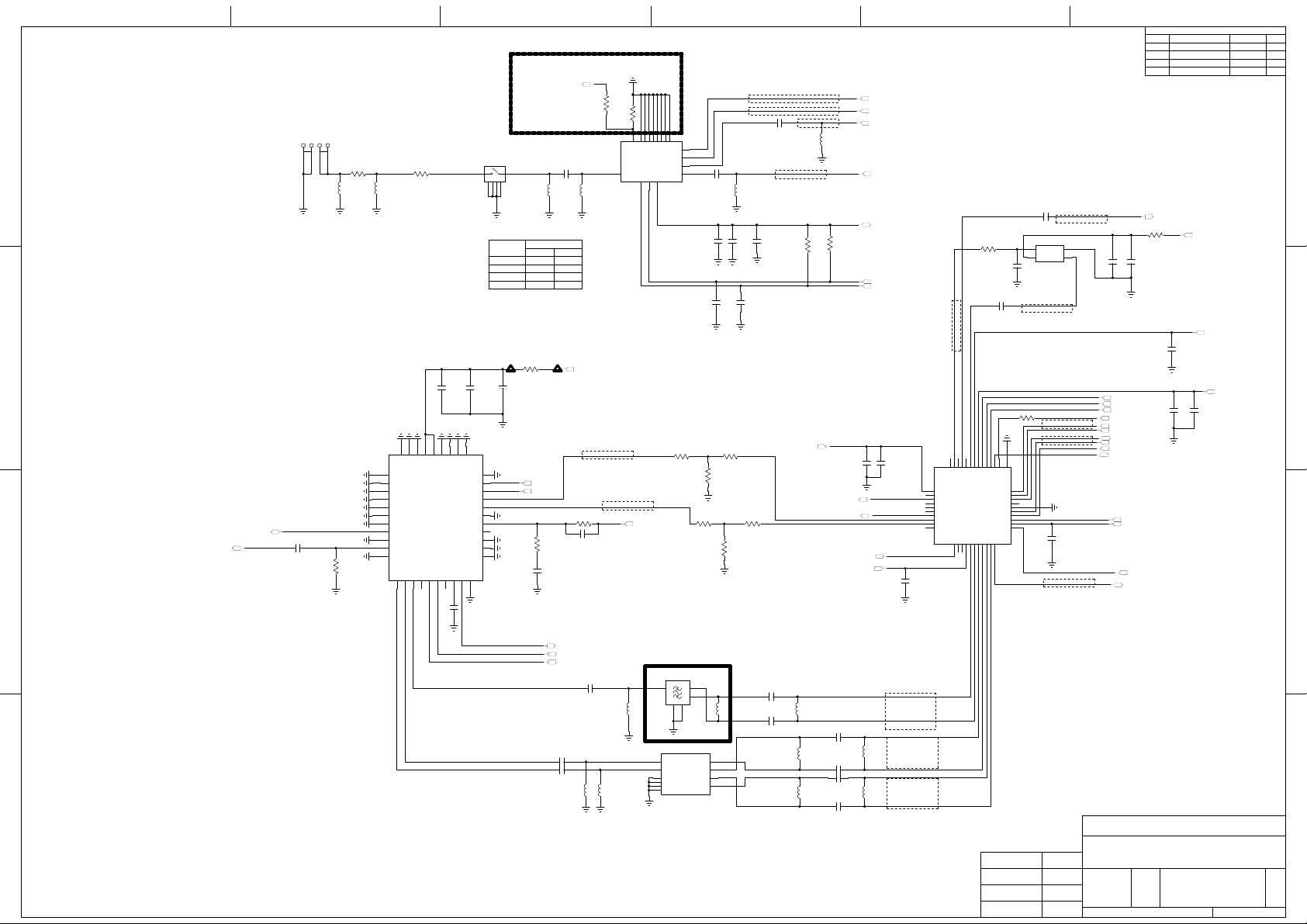

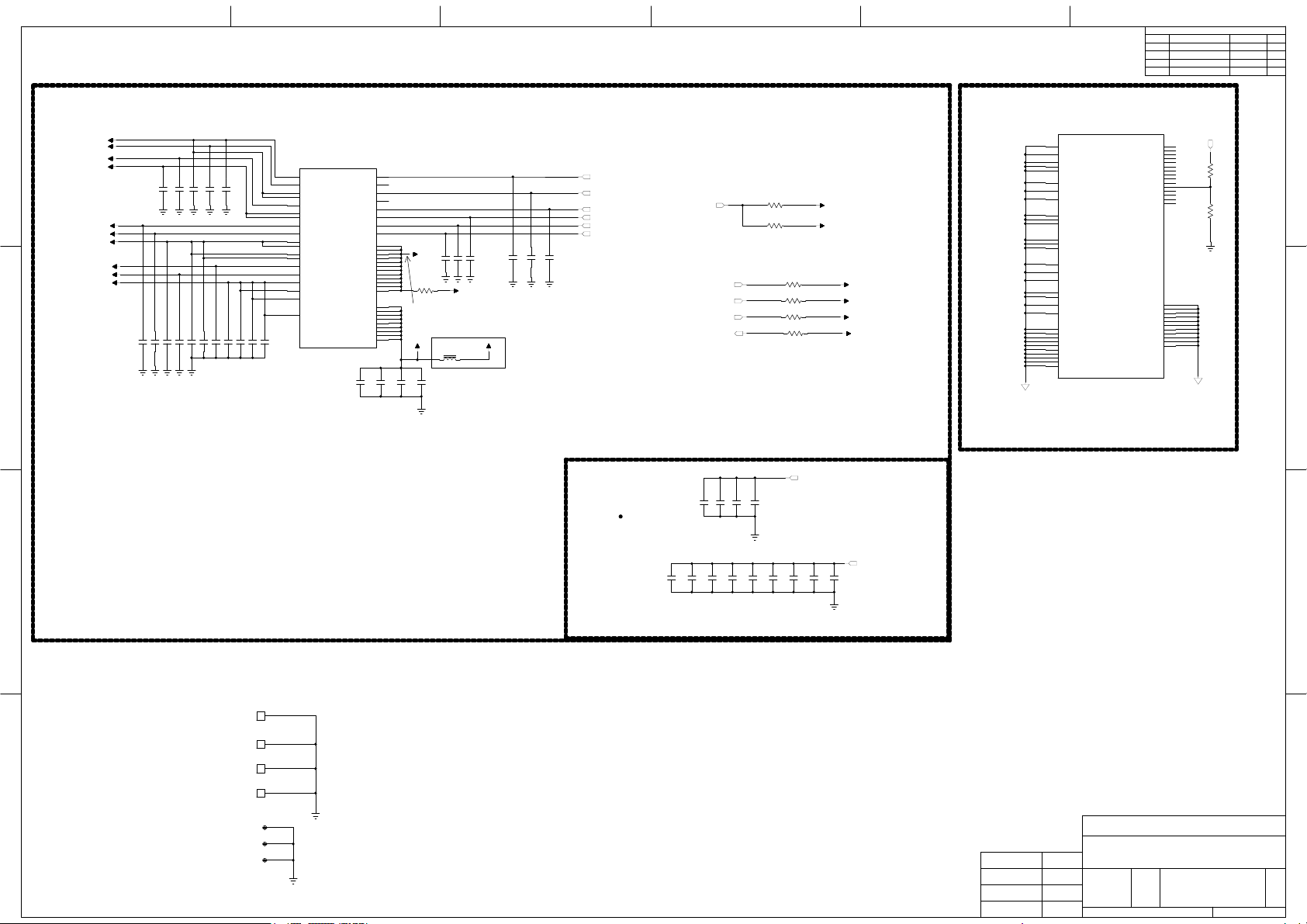

R119 for RF1450

D

C

[1]

TX_FEEDBACK

B

[1]

GSM

(50 Ohm line)

1857724-4

ANT2

ANT1

1857724-4

1

2

1

2

R141

0

L118

5.1n

GND

R111

2

1

0

L119

DNP

50 ohm

J101

SPC0200A1-001-SPA5G-50

OUT IN

6

12

345

ASM Algorithm

Band

GSM

TDTX

TD1900RX

TD2000RX

2mm

+

12

GND1213GND1314GND1415GND15

PAC_EN

GSM_IN

DCS_IN

LDO_XO_EN

LDO_XO

LDO_DIG_EN

LDO_DIG

41

C113

C112

47uF

1nF

11

GND11

10

9

TR_EN

8

7

6

5

VPC

4

3

2

1

GND1

GND4140SAT_DET39INTVB38LDO_RF37BS136BS035RX_GSM34RX_EGSM33RX_DCS32RX_PCS

U104

C111

100nF

16

18

GND1819GND1920GND20

GND21

GND22

GND23

GND24

GND25

GND26

GND27

ANT

GND29

COUP_OUT

GND31

SKY77524

VBATT117VBATT2

C115

1uF

21

22

23

24

25

26

COUPOUT

R101

56

+/-1%

27

28

29

30

31

(50 Ohm line)

(50 Ohm line)

C114

3.3pF

L102

DNP

Control Logic

ANT_SW2 ANT_SW1

R115

0

PAC_EN

TR_EN

R107

+/-1%

VCC_FE

[1,2,6]

DNP

R119

R120

0

1

5

7

9

12

14

16

17

(50 Ohm line)

[2,6,11,12,14]

N/C

PE42641MLIBB-Z

11

ANT

U102

C133

22pF

L101

DNP

L

L

H

L

L

H

H

H

V_BATT

2mm

(50 Ohm line)

[1]

[1]

(50 Ohm line)

R108

3.3k

C120

47

3.9pF

close to PA syk77524

C119

560pF

Debug Ramp

VPC_OUT

6

GND

GND

GND

GND10GND

GND

GND

GND

RF4

8

RF3

15

RF2

RF1

VDD3V24V1

2

[1]

R103

30

+/-1%

22pF

C105

13

L103

DNP

C108

C109

100pF

100nF

C107

C106

100pF

100pF

R104

0

L116

DNP

R105

R106

30

+/-1%

0

30

L117

+/-1%

(50 Ohm line)

(50 Ohm line)

22pF

C139

(50 Ohm line)

L104

DNP

(50 Ohm line)

C110

220n

(50 Ohm line)

(50 Ohm line)

R110

R109

1M

1M

[1,6]

VCC_RX_TX

[1]

[2]

TD2000RX

[2]

TD1900RX

[2]

TDTX

[1]

GSM

[1,2,6]

VCC_FE

[3]

ANT_SW2

[3]

ANT_SW1

C116

C117

100pF

2.2uF

BS0

SKY74218 GPIO5 -----PXA920 GPIO60

[1]

BS1

[1]

PAC_EN

[1,6]

VCC_RX_TX

D

C130

68nF

Shielding

R102

0

Shielding

U103

42

25

24

23

18

19

20

22

VCC521VCC4

GPIO841GPIO7

GPIO9

XTAL_IN

UHF_LDO

CTRLDATA

XTAL_OUT

26

VCC3

27

SKY74218

GPIO5

43

GPIO1

28

GPIO6

29

RSVD

30

RSVD

44

GPIO2

31

TXLB_OUT

32

TXHB_OUT

33

GPIO4

C118

10nF

Y101

1XTV26000AAA

1

2

VCONT

GND

4

3

C132

VCC

C125

33nF

C103

68nF

40

39

17

45

GND

GPIO0

CTRLEN

CTRLCLK

RESET_N

RXTXDATA

RXTXEN

SYSCLK

N/C

N/C

SYSCLKEN

STROBE

TX_FDBK

VCC2

SAT_DET

VPC34VCC11GPIO32LNA850+3LNA850-4LNA900+5LNA900-6LNA1800+7LNA1800-8LNA1900+9LNA1900-

35

OUT

Shielding

R112

Shielding_yang

0

Shielding

16

15

14

38

37

13

12

11

10

36

(50 Ohm line)

C121

2.2uF

Shielding

C131

1uF

68nF

GSM_CDATA

GSM_CCLK

GSM_CEN

SLAVE_RESET_OUT

RXTXDATA

RXTXEN

SYSCLK

SYSCLKEN

GSM_STROBE

TR_EN

TX_FEEDBACK

VCC_RX_TX

VPC_OUT

[2]

26MHZ_TD_CLK

[6]

V_LDO7

R114

10

[6]

C122

68nF

[3]

[3]

C123

68nF

[3]

[3]

[3]

[3]

[3]

[3]

[3]

[1]

[1]

[1,6]

[1]

SAT_DET

[1]

GSM_VCC_ANALOG

C

[6]

GSM_VCC_DIG

C124

22pF

B

[1]

SAT_DET

[1]

BS1

[1]

BS0

C101

(50 Ohm line)

(50 Ohm line)

(50 Ohm line)

22pF

C104

22pF

C126

22pF

L115

L100

6.8n

6.8n

A

U101

3

1

OUT

IN

4

OUT

GND

L105

15n

GND

2

5

U105

1

GSM1800_IN

GSM1800_OUT

4

GSM1900_IN

GSM1800_OUT

2

GND

GSM1900_OUT

3

GND

5

GND

GSM1900_OUT

10

GND

SFWG42PY002

C129

L108

DNP

8

9

6

7

2.2pF

L112

22n

C134

2.2pF

C135

6.8pF

L110

DNP

C136

6.8pF

C137

L109

DNP

8.2pF

C138

8.2pF

(75 Ohm lines)

(75 Ohm lines)

L113

4.7n

L114

(75 Ohm lines)

4.7n

DRAWN: DATED:

QUALITY CONTROL: DATED:

COMPANY:

TITLE:

DATED:CHECKED:

DATED:RELEASED:

CODE: SIZE: DRAWING NO: REV:

SCALE: SHEET: OF

BYD

T801T GSM part

A

123456

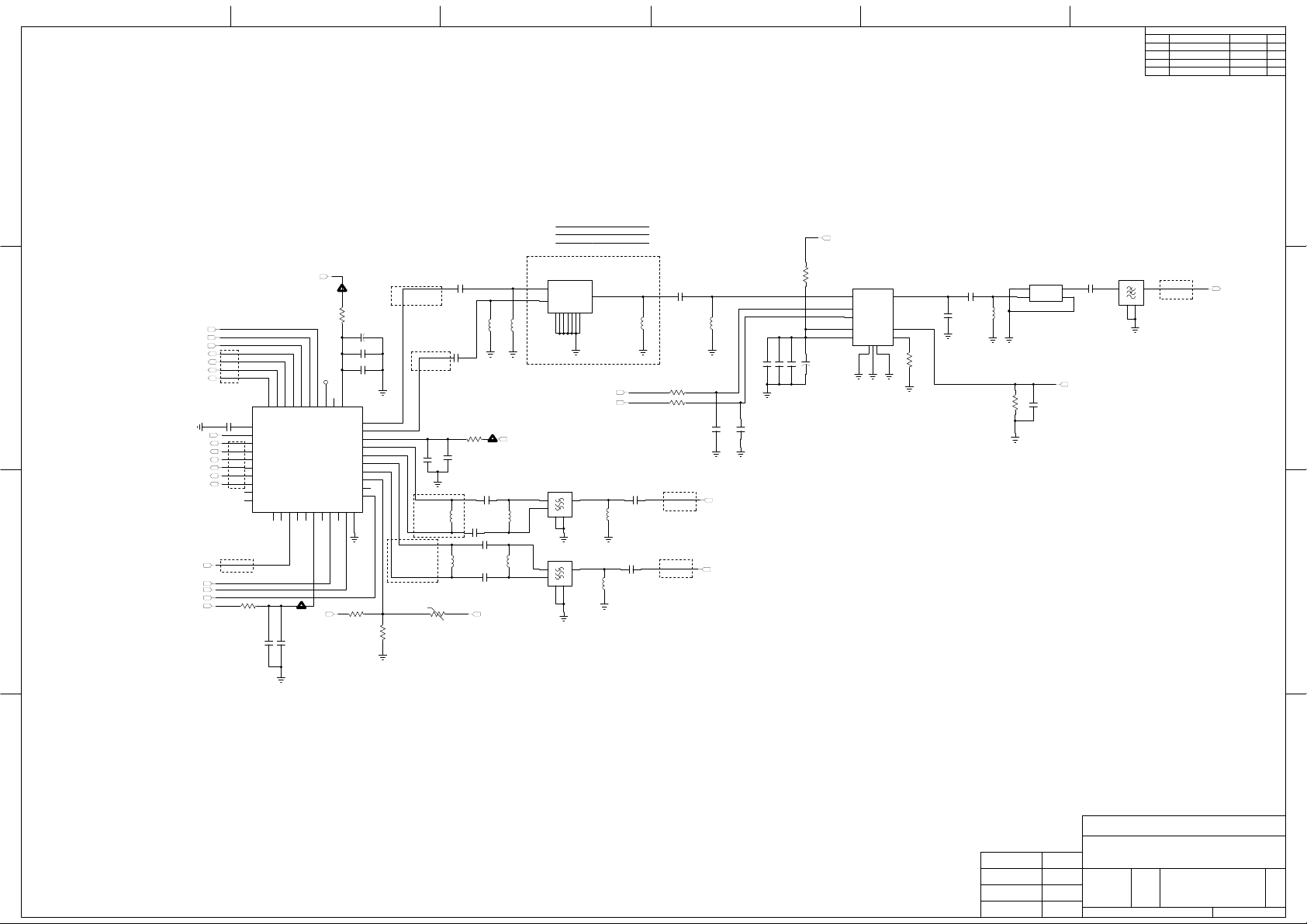

REVISION RECORD

LTR ECO NO: APPROVED:

DATE:

D

Control Logic

CTL1 CTL2

U301

1900/2017.5_IN

4

1

IN

2

1

IN

2

[3]

[3]

L307

DNP

H

L

L305 close to U201

1

TD_PA_MODE1

TD_PACTRL

L308

DNP

L

H

C318 22pF

L305

4.3n

R330

R305

C331

22pF

(50 Ohm lines)

C332

22pF

(50 Ohm lines)

L382

DNP

C323

C324

22pF

330P

0

0

C335

C336

22pF

22pF

[1]

TD2000RX

[1]

TD1900RX

R310

0

+

C321

47uF

C322

100nF

V_BATT

[1,2,6,11,12,14]

Update to sky77198-12

U307

SKY77198-11

2

3

4

1

10

RF_IN

VMODE_1

VMODE_0

VCC1

VCC2

9

RF_OUT

5

VEN

6

CPL

GND

GND8GND

7

11

R318

+/-1%

U309

C326

3.3pF

L306

C325

DNP

51

CEG231G95ECB100

1

4

GND1

OUTPUT

2

INPUT3GND2

4.7n

R304

C319

DNP

22pF

U310

C328

2017.50 MHz

22pF

4

2

IN

OUT

(50 Ohm lines)

1

3

[3]

TD_PAON

[1]

TDTX

Port1-Port2

Port2-Port3

V_BATT

[1,2,6,11,12,14]

[3]

TD_CEN

[3]

TD_CCLK

[3]

TD_CDATA

[3]

[1]

[3]

[3]

[1,2,6,11,12,14]

[3]

[3]

[3]

[3]

[3]

[3]

[3]

[3]

[3]

[3]

26MHZ_TD_CLK

[3]

TD_PDALL

TD_RXON

TD_TXON

TD_IQ_CLK

TD_IQ9

TD_IQ8

TD_IQ7

TD_IQ6

37

39

U308

DIGIO940DIGIO8

1

DVDD

2

CLK5M

3

DIGIO7

4

DIGIO6

5

DIGIO5

6

DIGIO4

7

DIGIO3

8

DIGIO2

9

DIGIO1

DIGIO0

XOUT212XTAL13REFCLK14XOUT15XAFC16VDD117SDO18PDN19XOUT2_EN20RXON

11

DIGIO1138DIGIO10

1uF

C330

TD_IQ5

TD_IQ4

TD_IQ3

TD_IQ2

TD_IQ1

TD_IQ0

10

Shielding

V_BATT

0.3mm

R309

0

C303

C304

100nF

22pF

C

B

0.3mm

R307

0

C333

+

C301

C302

TP301

31

32

33

34

35

36

SEN

SCLK

VAFC

SDIO

VDD3

PA_BIAS

RFOUT_2G

RFOUT_1G9

VDD2

RFIP_2G

RFIN_2G

RFIP_1G9

RFIN_1G9

VAUX

AVDD_OUT

TXON

GND

41

(50 Ohm lines)

47uF

22pF

100nF

30

29

28

27

26

25

24

23

22

21

(100 Ohm lines)

(100 Ohm lines)

DNP

[8]

RF_TMP

R399

R301

39k

Use SDNT1005X104F4150FTF sunlord

+/-1%

(50 Ohm lines)

C310

100nF

R302

t

100k

Close to TD PA

C305

C306

22pF

C309

22pF

L301

10n

L303

8.2n

NTC Thermistor,100K

22pF

L380

L381

DNP

DNP

R306

0

V_BATT

[1,2,6,11,12,14]

0.3mm

C312

22pF

L302

DNP

C311

22pF

C313

22pF

L304

DNP

C314

22pF

[1,6]

VCC_FE

SAWFD1G90KA0F00

6

2017.5_OUT

9

1900_OUT

GND3GND5GND7GND8GND10GND

2

U306

SAFEA2G01FL0F00R14

3

OUT

4

OUT

G

5

U305

SAFEB1G90FA0F05R14

3

OUT

4

OUT

G

5

GND

G

G

D

C

B

A

DRAWN: DATED:

QUALITY CONTROL: DATED:

COMPANY:

TITLE:

DATED:CHECKED:

DATED:RELEASED:

SCALE: SHEET: OF

BYD

T801T TD-SCDMA part

CODE: SIZE: DRAWING NO: REV:

A

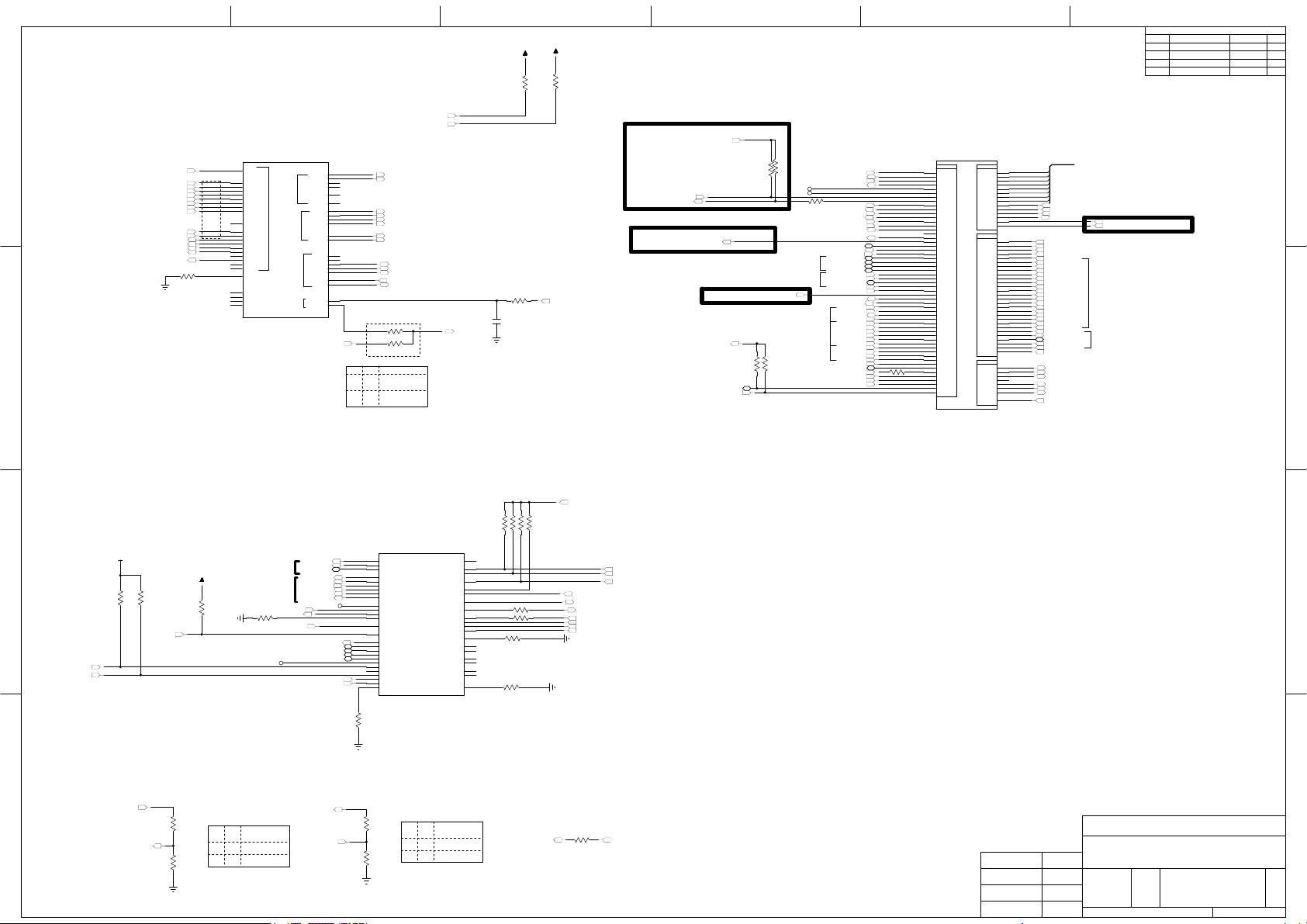

123456

REVISION RECORD

VCC_IO_WB

VCC_IO_WB

R485DNP

R484DNP

[3] T_TD_TXH/L_L

[1]

ANT_SW1

ANT_SW2

GSM_STROBE

GSM_CCLK

GSM_CEN

GSM_CDATA

RXTXEN

RXTXDATA

AGPS_PON

AGPS_RESET_N

8787_LDO_EN

TP_INT

TP_REST

R403

0

R404

DNP

SYSCLKEN SELECTION

USE TD SYSCLKEN

USE TD VCXO_EN

[3] T_TD_TXL/H_L

[1]

[1]

[1]

[1]

[1]

[1]

[1]

[12]

[12]

[12]

[9]

[9]

SYSCLKEN

R402

C401

DNP

[1]

[1]

SYSCLK

0

D

[2]

TD_IQ_CLK

[2]

TD_IQ0

[2]

TD_IQ1

[2]

TD_IQ2

[2]

TD_IQ3

[2]

TD_IQ4

[2]

TD_IQ5

[2]

TD_IQ6

[2]

TD_IQ7

[2]

TD_IQ8

[2]

TD_IQ9

[2]

TD_PAON

[2]

TD_PACTRL

[2] TD_RXON

[2]

TD_TXON

[2]

TD_PA_MODE1

R401

C

*** 920H***

C18

F15

B17

C17

H12

G13

A18

A17

B18

Shielding

B16

H13

C19

B19

A20

A19

C20

B20

B21

C21

C22

60.4k

+/-1%

A11

A12

A10

TDS_CLK

TDS_DIO0

TDS_DIO1

TDS_DIO2

TDS_DIO3

TDS_DIO4

TDS_DIO5

TDS_DIO6

TDS_DIO7

TDS_TXREV

TDS_DIO8

TDS_DIO9

TDS_PAON

TDS_PACTRL

TDS_RXON

TDS_TXON

TDS_LNACTRL

TDS_MIXCTRL

TDS_TRXSW

TDS_RXREV

B9

DIGRF_IREF

DIGRF_RX_DATA_N

DIGRF_RX_DATA_P

DIGRF_TX_DATA_N

A9

DIGRF_TX_DATA_P

PXA920H

U401-C

D9

ANT_SW1

C10

ANT_SW2

F11

ANT_SW3

C9

ANT_SW4

A8

PA_MODE

ANT_1.8v

B8

RF_CONT4

B14

GSM_STROBE

D15

GSM_CCLK

D14

GSM_CEN

B13

GSM_CDATA

G11

IO_GSM_1.8V

IO_FAE_1.8V

RXTXEN

D13

RXTXDATA

A16

GPIO_60

A15

GPIO_61

C15

GPIO_62

B15

GPIO_63

G12

GPIO_64

A14

IO_FAE_1.8V

GPIO_65

D16

GPIO_66

C14

SYSCLK

A13

SYSCLKEN

IO_GSM_1.8V

[3,7]

VCXO_EN

R403 R404

0R NC

NC 0R

change on 0714

TP firmware download port

FAST_BOOT

[14]

[4]

ND_RST

change on 0714

V_BUCK3_1V8

[3,4,5,6,7,8,9,10,11,12,14]

CAM_FRONT_PWDN

[11]

change on 0714

V_BUCK3_1V8

[3,4,5,6,7,8,9,10,11,12,14]

[6,7,9,11,12]

I2C_SCL

[6,7,9,11,12]

I2C_SDA

*** 920H***

100k

DNP

R491

R490

IIS

PCM

[9]

KEY_LED_EN

R4281kR427

1k

TP451

TP452

DNP

CMMB

WLAN

GPS

R406

[12]

BT/WALN/FM_HOST_WAKEUP

[12]

[12]

[12]

[10,14]

[10]

[9]

[9]

PSEN_INT

[11]

[10] OVP_EN

[12]

BT_WAKEUP_HOST

[11]

MAIN_CAM_CORE_EN

[12]

BT&FM&WIFI_PD

[12]

HOST_WAKEUP_BT

WLAN_BT_FM_RESET

[12]

[8]

HIFI_BITCLK

[8]

HIFI_SYNC

[8]

HIFI_SDATA_OUT

[8]

HIFI_SDATA_IN

[8,12]

[8,12]

[8,12]

[8,12]

WLAN_WAKEUP_HOST

AGPS_POWER_EN

[12]

CSEN_DRDY

[13]

[13]

SSP1_SFRM

[13]

[13]

[12]

[12]

[12]

[12]

[12]

[12]

[12]

GPS_UART_RXD

[12]

GPS_UART_TXD

[12]

GPS_UART_CTS

[12]

GPS_UART_RTS

[14]

[14]

[12]

[10]

[10]

[10,14]

LCD_RESET

VT_CAM_EN

GSEN_INT

PCM_CLK

PCM_SYNC

PCM_TXD

PCM_RXD

SSP1_CLK

SSP1_RXD

SSP1_TXD

WLAN_DAT3

WLAN_DAT2

WLAN_DAT1

WLAN_DAT0

WLAN_CMD

WLAN_CLK

GPS_I2C_REQ

FLAG_OVP

[14]

[14]

MKIN0

MKOUT0

MKIN1

MKOUT1

FFRXD

FFTXD

R483

CP_RXD

CP_TXD

U401-D

1.8V/2.8V1.8V

1.8V/2.8V

GPIO_67

GPIO_68

GPIO_69

GPIO_70

GPIO_71

GPIO_72

GPIO_73

GPIO_74

GPIO_75

GPIO_76

GPIO_77

GPIO_78

GPIO_79

GPIO_80

GPIO_81

GPIO_82

GPIO_83

GPIO_84

GPIO_85

GPIO_86

GPIO_87

GPIO_88

GPIO_89

GPIO_90

GPIO_91

GPIO_92

GPIO_93

GPIO_94

GPIO_95

GPIO_96

GPIO_97

GPIO_98

GPIO_100

GPIO_101

GPIO_102

GPIO_103

GPIO_104

GPIO_105

GPIO_106

GPIO_107

GPIO_108

GPIO_109

GPIO_110

GPIO_111

GPIO_112

GPIO_113

GPIO_114

GPIO_115

GPIO_116

GPIO_124

G9

C8

A7

B7

C7

C6

A6

B6

A5

B5

G6

C5

F7

G7

M20

L21

L17

K21

J15

K22

J16

J21

K17

K20

H15

J22

J19

H16

G21

K19

G20

H14

G22

G15

F22

H17

E22

J17

G19

G17

G16

F17

1.8V

E20

F21

F20

F19

E21

D22

D20

AA17

N15

GPIO_00

AB18

GPIO_01

U17

GPIO_02

W18

GPIO_03

AA18

GPIO_04

AB19

GPIO_05

N16

GPIO_06

Y18

GPIO_07

AA19

GPIO_08

AB20

GPIO_09

P17

GPIO_10

AA21

GPIO_11

Y21

GPIO_12

Y20

GPIO_13

V20

GPIO_14

W21

GPIO_15

AA20

GPIO_16

Y22

GPIO_17

V21

GPIO_18

W22

GPIO_19

Y19

GPIO_20

W19

GPIO_21

R17

GPIO_22

W20

GPIO_23

T17

GPIO_24

V19

GPIO_25

V22

GPIO_26

U22

GPIO_27

U19

GPIO_28

U21

GPIO_29

U20

GPIO_30

T22

GPIO_31

M16

GPIO_32

T21

GPIO_33

T20

GPIO_34

T19

GPIO_35

R22

GPIO_36

R21

GPIO_37

M15

GPIO_38

R20

GPIO_39

L15

GPIO_40

P19

GPIO_41

P22

GPIO_42

P21

GPIO_43

L16

GPIO_44

P20

GPIO_45

N22

GPIO_46

N19

GPIO_47

M19

GPIO_48

0

N21

GPIO_49

M17

GPIO_50

N20

GPIO_51

M22

GPIO_52

M21

GPIO_53

L19

GPIO_54

PXA920H

CAM_DATA7

CAM_DATA6

CAM_DATA5

CAM_DATA4

CAM_DATA3

CAM_DATA2

CAM_DATA1

CAM_DATA0

CAM_HSYNC

CAM_VSYNC

CAM_MCLK

CAM_PCLK

LCD_FCLK_RD_N

LCD_LCLK_A0

LCD_PCLK_WR_N

LCD_DATA_ENABLE

LCD_DATA0

LCD_DATA1

LCD_DATA2

LCD_DATA3

LCD_DATA4

LCD_DATA5

LCD_DATA6

LCD_DATA7

LCD_DATA8

LCD_DATA9

LCD_DATA10

LCD_DATA11

LCD_DATA12

LCD_DATA13

LCD_DATA14

LCD_DATA15

LCD_DATA16

LCD_DATA17

LCD_DATA18

LCD_DATA19

LCD_DATA20

LCD_DATA21

LCD_DATA22

LCD_DATA23

T_TD_TXL/H_L

TD_PDALL

TD_CDATA

TD_CCLK

TD_CEN

CAM_PWR_EN

CAM_DATA[0:7]

[11]

[11]

[11]

[11]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[9]

[3]T_TD_TXH/L_L

[3]

[2]

[2]

[2]

[2]

[11]

CAM_REAR_RESET

CAM_REAR_STBY

18Bits LCD DATA

GPIO[104] ---920 SPI_IN / LCD SPI_OUT

GPIO[105] ---920 SPI_OUT / LCD SPI_IN

LCD init Port

LTR ECO NO: APPROVED:

[11]

[11]

change on 0714

DATE:

D

C

V_BUCK3_1V8

R423

R422

R421

10k

2.2k

*** 920H***

U401-E

VCC_MMC

B

R410

R411

100k

100k

RESET_IN_N

[7,14]

[14] DOWNLOAD_CTRL

[14] RFMODE_CTRL

V_BUCK3_1V8

R414

USIM interface

JTAG Port

100k

R415

100k

T-FLASH

[12,14]

USIM_RST_N

[12,14]

USIM_CLK

[12,14]

USIM_DATA

[14]

PRI_TCK

[14]

PRI_TDI

[14]

PRI_TDO

[14]

PRI_TMS

[14]

PRI_TRST_N

[3]

JTAG_SEL

[3]

VCXO_REQ

[3,7]

VCXO_EN

[7,12]

CLK_32KHZ

[12]

[12]

MMC1_DAT<0>

[12]

MMC1_DAT<1>

[12]

MMC1_DAT<2>

[12]

MMC1_DAT<3>

TP8

[12]

[12]

change on 0714

A

V_BUCK3_1V8

[3,4,5,6,7,8,9,10,11,12,14]

V_BUCK3_1V8

R419

4.7K

R419 R418

Clock Source

[3]

CLK_SRC_SEL

R418

DNP

4.7k NC

NC 10k

Selection

Clock source is

SYSCLK pin(Digital)

Clock source is

VCXO_IN Pin(Analog)

[3,4,5,6,7,8,9,10,11,12,14]

[3]

JTAG_SEL

TP410

MMC1_CLK

MMC1_CMD

W3

USIM_NURST

W2

USIM_UCLK

Y3

USIM_UIO

R14

PRI_TCK

U15

PRI_TDI

Y16

PRI_TDO

AA16

PRI_TMS

AB17

PRI_TRST_N

Y13

JTAG_SEL

AA15

SLEEP_IND

T16

VCXO_REQ

T13

VCXO_EN

C13

SIN_0P4V

Y14

EXT_32K_IN

AB15

RESET_IN_N

W7

MMC1_CLK

Y5

MMC1_DAT0

U6

MMC1_DAT1

W6

MMC1_DAT2

AA2

MMC1_DAT3

W5

MMC1_DAT4

DOWNLOAD_CTRL

Y2

MMC1_DAT5

W4

MMC1_DAT6

RFMODE_CTRL

AA3

MMC1_DAT7

AA4

MMC1_CD

MMC1_CD

R7

MMC1_CMD

T7

MMC1_WP

PXA920H

2

100k

R499

1

R416

DNP

10k

R417

GPIO_21

R416 R417

NC

NC 10k

TEST_PIN_PLLM

PMIC_INT

CLK_SRC_SEL

SLAVE_RESET_OUT

VCXO_OUT

USB2_REXT

MIPI_CLKP

MIPI_CLKN

MIPI_DATA0_N

MIPI_DATA0_P

MIPI_DATA1_N

MIPI_DATA1_P

MIPI_RCOMP

***920H****

multi-function use on

the primary JTAG pins

Disable

NC

Enables

PWR_SCL

PWR_SDA

CLK_REQ

USBVBUS

USBID

USB_N

USB_P

2.2k

D11

AB16

W13

Y15

Y17

R15

W15

R405

1

W16

R424

U8

Y7

W9

W8

R425

+/-1%

+/-1%

R426

49.9

6.04k

AA6

C4

B4

B3

B2

A3

A4

C3

[3,4,5,6,7,8,9,10,11,12,14]

R434

4.7K

[7,9,11]

PWR_SCL

[7,9,11]

PWR_SDA

[7]

PMIC_INT_N

[3]

CLK_SRC_SEL

[1]

SLAVE_RESET_OUT

33

2

5.1K

VCXO_OUT

VBUS_SW

APPS_USBC_N

APPS_USBC_P

[7]

[6]

[10]USB_ID

[10]

[10]

B

A

COMPANY:

VCXO_REQ

10k

V_BUCK3_1V8

[3,4,5,6,7,8,9,10,11,12,14]

R420

DRAWN: DATED:

DATED:CHECKED:

QUALITY CONTROL: DATED:

DATED:RELEASED:

[3]

BYD

TITLE:

T801T Baseband part

CODE: SIZE: DRAWING NO: REV:

SCALE: SHEET: OF

123456

REVISION RECORD

LTR ECO NO: APPROVED:

V_DDR_1V8

[4]

[4]

[4]

[4]

[4]

[4]

[4]

[4]

[4]

[4]

DDR_DQS0

DDR_DQS0_N

DDR_DQS1

DDR_DQS1_N

DDR_DQS2

DDR_DQS2_N

DDR_DQS3

DDR_DQS3_N

DDR_A[0:9]

DQM[0:3]

[4]

[4] DDR_CKE1

[4]

[4]

[4]

[4]

DDR_CKE0

DDR_CLK

DDR_CLKN

DDR_CS0_N

DDR_CS1_N

DQM0

DQM1

DQM2

DQM3

D

C

[4]

ND_IO[0:15]

ND_IO0

ND_IO1

ND_IO2

ND_IO3

ND_IO4

ND_IO5

ND_IO6

ND_IO7

ND_IO8

ND_IO9

ND_IO10

ND_IO11

ND_IO12

ND_IO13

ND_IO14

ND_IO15

R599

300

+/-1%

U401-A

DDR_A0

L2

SDARM_ADDR0

DDR_A1

M3

SDARM_ADDR1

DDR_A2

M2

SDRAM_ADDR2

L8

DDR_A3

SDRAM_ADDR3

P2

DDR_A4

SDRAM_ADDR4

M7

DDR_A5

SDRAM_ADDR5

N3

DDR_A6

SDRAM_ADDR6

L4

DDR_A7

SDRAM_ADDR7

N2

DDR_A8

SDRAM_ADDR8

M8

DDR_A9

SDRAM_ADDR9

D3

SDRAM_DQM0

H8

SDRAM_DQM1

N4

SDRAM_DQM2

R4

SDRAM_DQM3

H1

SDRAM_DQS0

G1

SDRAM_DQSB0

J1

SDRAM_DQS1

K1

SDRAM_DQSB1

P1

SDRAM_DQS2

N1

SDRAM_DQSB2

T1

SDRAM_DQS3

R1

SDRAM_DQSB3

K3

SDRAM_CKE0

K4

SDRAM_CKE1

L1

SDRAM_CLK

M1

SDRAM_CLKN

L7

SDRAM_CSN0

J2

SDRAM_CSN1

PXA920H

U401-B

ND_NCS0_SM_NCS2

GPIO_85

GPIO_86

PXA920H

ND_IO0

ND_IO1

ND_IO2

ND_IO3

ND_IO4

ND_IO5

ND_IO6

ND_IO7

ND_IO8

ND_IO9

ND_IO10

ND_IO11

ND_IO12

ND_IO13

ND_IO14

ND_IO15

CAL_PAD

ND_NCS1_SM-NCS3

GPIO_89

GPIO_90

GPIO_1

GPIO_87

GPIO_88

GPIO_126

GPIO_127

GPIO_0

GPIO_2

GPIO_3

ND_CLE_SM_NOE

ND_ALE_SM_NWE

SM_ADVMUX

ND_RDY0

ND_RDY1

SM_SCLK

SM_NCS0

SM_NCS1

SM_NBE0

SM_NBE1

ND_NWE

ND_NRE

SM_ADV

SM_RDY

AB5

U9

AB6

AB7

AA7

U10

AA8

Y8

AB8

T11

AA9

AB9

Y9

U11

AB10

Y10

C1

D1

DDR_D0

SDRAM_DQ0

E4

DDR_D1

SDRAM_DQ1

D2

DDR_D2

SDRAM_DQ2

E3

DDR_D3

SDRAM_DQ3

E2

DDR_D4

SDRAM_DQ4

G4

DDR_D5

SDRAM_DQ5

J6

DDR_D6

SDRAM_DQ6

F2

DDR_D7

SDRAM_DQ7

G2

DDR_D8

SDRAM_DQ8

H7

DDR_D9

SDRAM_DQ9

J7

DDR_D10

SDRAM_DQ10

K6

DDR_D11

SDRAM_DQ11

G3

DDR_D12

SDRAM_DQ12

J4

DDR_D13

SDRAM_DQ13

H2

DDR_D14

SDRAM_DQ14

J3

DDR_D15

SDRAM_DQ15

P3

DDR_D16

SDRAM_DQ16

N6

DDR_D17

SDRAM_DQ17

P6

DDR_D18

SDRAM_DQ18

P4

DDR_D19

SDRAM_DQ19

R2

DDR_D20

SDRAM_DQ20

R3

DDR_D21

SDRAM_DQ21

T3

SDRAM_DQ22

N7

SDRAM_DQ23

T2

SDRAM_DQ24

R6

SDRAM_DQ25

U1

DDR_D26

SDRAM_DQ26

T4

DDR_D27

SDRAM_DQ27

V2

DDR_D28

SDRAM_DQ28

P7

DDR_D29

SDRAM_DQ29

V3

DDR_D30

SDRAM_DQ30

T6

DDR_D31

SDRAM_DQ31

AA10

AB11

AA11

R10

W11

AA12

AB13

Y12

U13

W10

AB12

U14

AA13

AB14

W12

AA14

0

R199

0

R204

0

R200

0

R503

DDR_D22

DDR_D23

DDR_D24

DDR_D25

SPI_DCLK

SM_SCLK

CMMB_IRQ

LCD_SDI

CMMB_PWR_EN

PG8211_SDI

GSEN_INT_01

LCD_CS

DDR_D[0:31]

[4]

[9]SPI_DOUT

TP2

[4]NAND_CLE_NOE

[9]

[4]

[13]CMMB_RST_N

[13]

[9]

[13]

[4]

[12]

[9]

[4]

DDR_D[0:31]

DDR_D0

DDR_D1

DDR_D2

DDR_D3

DDR_D4

DDR_D5

DDR_D6

DDR_D7

DDR_D8

DDR_D9

DDR_D10

DDR_D11

DDR_D12

DDR_D13

DDR_D14

DDR_D15

DDR_D16

DDR_D17

DDR_D18

DDR_D19

DDR_D20

DDR_D21

DDR_D22

DDR_D23

DDR_D24

DDR_D25

DDR_D26

DDR_D27

DDR_D28

DDR_D29

DDR_D30

V_DDR_1V8

DDR_D31

V_DDR_1V2

[4]

VREFCA

[4]

VREFDQ

DDR2 (4Gb)

U507

N8

DQ0

M8

DQ1

M7

DQ2

M9

DQ3

M6

DQ4

L7

DQ5

L8

DQ6

L9

DQ7

G9

DQ8

G8

DQ9

G7

DQ10

F6

DQ11

F9

DQ12

F7

DQ13

F8

DQ14

E8

DQ15

T7

DQ16

P6

DQ17

T8

DQ18

N5

DQ19

P7

DQ20

T9

DQ21

R8

DQ22

N6

DQ23

E6

DQ24

C8

DQ25

B9

DQ26

D7

DQ27

E5

DQ28

B8

DQ29

D6

DQ30

B7

DQ31

C1

VDD1_1

B6

VDD1_2

R1

VDD1_3

T6

VDD1_4

B5

VDD2_1

D2

VDD2_2

G1

VDD2_3

J7

VDD2_4

P2

VDD2_5

T5

VDD2_6

C7

VDDQ_1

C10

VDDQ_2

D5

VDDQ_3

E9

VDDQ_4

F10

VDDQ_5

H6

VDDQ_6

J6

VDDQ_7

K6

VDDQ_8

M10

VDDQ_9

N9

VDDQ_10

P5

VDDQ_11

R7

VDDQ_12

R10

VDDQ_13

F1

VDDCA_1

H1

VDDCA_2

N2

VDDCA_3

G3

VREFCA

J9

VREFDQ

H9TCNNN4JDMMPR-NYM

A1

A10

B10

T10

U2

U10

B2

DNU_1A2DNU_2A9DNU_3

NC_1B3NC_2J2NC_3K3NC_4L3NC_5R3NC_6T2NC_7T3NC_8

DNU_4B1DNU_5

DNU_6T1DNU_7

DNU_8U1DNU_9

DNU_10U9DNU_11

DNU_12

VSSQ_10

VSSQ_11

VSSQ_12

VSSQ_13

VSSCA_1

VSSCA_2

VSSCA_3

P3

CA0

N3

CA1

M3

CA2

M2

CA3

M1

CA4

G2

CA5

F2

CA6

F3

CA7

E3

CA8

E2

CA9

L6

DQS0

L5

DQS0#

G6

DQS1

G5

DQS1#

P8

DQS2

P9

DQS2#

D8

DQS3

D9

DQS3#

K5

DM0

H5

DM1

N7

DM2

E7

DM3

K1

CKE0

K2

CKE1

J3

CLK

H3

CLK#

L1

CS0#

L2

CS1#

C2

VSS_1

C5

VSS_2

D1

VSS_3

J8

VSS_4

P1

VSS_5

R2

VSS_6

R5

VSS_7

H2

VSS_8

C6

VSSQ_1

C9

VSSQ_2

D10

VSSQ_3

E10

VSSQ_4

F5

VSSQ_5

G10

VSSQ_6

J5

VSSQ_7

L10

VSSQ_8

M5

VSSQ_9

N10

P10

R6

R9

E1

J1

N1

D3

ZQ0

C3

ZQ1

[4]

DDR_A[0:9]

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

[4]

DDR_DQS0

[4]

DDR_DQS0_N

[4]

DDR_DQS1

[4]

DDR_DQS1_N

[4]

DDR_DQS2

[4]

DDR_DQS2_N

[4]

DDR_DQS3

[4]

DDR_DQS3_N

DQM0

DQM1

DQM2

DQM3

DDR_CS0_N

DDR_CS1_N

1

1

240

R809

+/-1%

240

R810

+/-1%

2

2

[4]

1

1

DQM[0:3]

[4]

[4]

1

DNP

R593

2

R589

R598

4.7K +/-5%

4.7K +/-5%

2

2

DDR_CLK

DDR_CLKN

1

DNP

R508

2

C528

DNP

[4]

[4]

DDR_CKE0

DDR_CKE1

The V_DDR_1V2

and GND of

divider must be

as close as

possible

respectively to

VDDCA and VSSCA

[4]

[4]

47pF

V_DDR_1V2

V_DDR_1V2

V_DDR_1V2

C535

C536

47pF

C541

C542

100nF

C545

100nF

C556

2.2uF

C543

100nF

100nF

C546

C547

100nF

100nF

C557

C558

1uF

100nF

10k

R515

+/-1%

[4]

VREFCA

10k

R516

+/-1%

C544

100nF

C548

C549

100nF

100nF

Place these caps as

C559

10pF

close as possible to

U5205 VDD2 pins

V_DDR_1V2

C537

47pF

C538

47pF

Place these caps as

close as possible to

U5205 VDD1 pins

C550

C551

100nF

100nF

10k

R517

+/-1%

VREFDQ

10k

R518

+/-1%

[4]

C552

100nF

The V_DDR_1V2

and GND of

divider must be

as close as

possible

respectively to

VDDDQ and VSSDQ

V_DDR_1V8 V_BUCK2

R538

0

Place these caps as

close as possible to

C553

U5205 VDDQ pins

100nF

V_DDR_1V2

Place these caps as

C554

C555

close as possible to

100nF

100nF

U5205 VDDCA pins

DATE:

D

C

920H

[3]

TP3

TP11

TP12

TP13

TP14

TP15

TP16

TP17

U505-A

SDIN4C2-4G-T

[4]

B

V_BUCK3_1V8

[4]

ND_IO[0:15]

ND_IO8

ND_IO9

ND_IO10

ND_IO11

ND_IO12

ND_IO13

ND_IO14

ND_IO15

R525

R541~R548=10K,R525~R532=DNP R541~R548=DNP,R525~R532=10K

Z2B

R536 R544

Strap Configuration

NC 10K

A

10K NC

R539 R547

NC 10K

10K NC

Boot from AP

Boot from CP

Strap Configuration

Enable sec JTAG

Only PRI JTAG

available

R521

DNP

10k

DNP

R526

DNP

DNP

DNP

R529

R527

R530

R528

R520 R528

NC 10K

10K NC

R523 R531

NC 10K

10K NC

[3,4,5,6,7,8,9,10,11,12,14]

DNP

R523

R531

DNP

DNP

DNP

R532

Y0

Strap Configuration

Boot from AP

Boot from CP

Strap Configuration

Enable sec JTAG

Only PRI JTAG

available

ND_IO0

[4]

ND_IO1

[4]

ND_IO2

[4]

ND_IO3

[4]

ND_IO4

[4]

ND_IO5

[4]

ND_IO6

[4]

ND_IO7

[4]

NAND_CLE_NOE

[4]

SM_SCLK

TP18

V_BUCK3_1V8

[3,4,5,6,7,8,9,10,11,12,14]

iNAND (4GB)

H3

DAT0

H4

DAT1

H5

DAT2

J2

DAT3

J3

DAT4

J4

DAT5

J5

DAT6

J6

DAT7

W5

CMD

W6

CLK

TP19

VSYS

R535

100k

C591

2.2uF

T10

VCC

U9

VCC

M6

VCC

N5

VCC

M7

VSS

P5

VSS

R10

VSS

U8

VSS

K6

VCCQ

W4

VCCQ

Y4

VCCQ

AA5

VCCQ

AA3

VCCQ

AA4

VSSQ

K4

VSSQ

Y2

VSSQ

Y5

VSSQ

AA6

VSSQ

K2

VDDI

C531

100nF

Vout=2.8V

S-1135B28-A6T1S

U503

S-1135B28-A6T1S

6

VIN

5

NC

20 mil

C590

100nF

C532

100nF

1

VOUT

2

VSS

3

NC4ON/OFF

7

R590

ND_VCC

0

C561

2.2uF

R522

2

1

V_BUCK3_1V8

0

C533

2.2uF

20 mil

C599

2.2uF

[3,4,5,6,7,8,9,10,11,12,14]

[4]ND_VCC

ND_RST

SDIN4C2-4G-T

U505-B

L4

A4

NC_INDEX

NC

M5

A6

NC

NC

M8

A9

NC

NC

M9

A11

NC

NC

M10

B2

[4]

NC

NC

J7

B13

NC

NC

H7

D1

NC

NC

U5

D14

NC

NC

U6

H1

NC

NC

U7

H2

NC

NC

U10

H13

NC

NC

N10

H14

NC

NC

T5

J1

NC

NC

R5

J14

NC

NC

P10

Y1

NC

NC

Y14

NC

AA1

NC

AA2

NC

W10

AA13

NC

NC

W11

AA14

NC

NC

W12

AE1

NC

NC

AE14

W13

NC

NC

AG2

W14

NC

NC

AG13

V1

NC

NC

AH4

V2

NC

NC

AH6

V3

NC

NC

AH9

V12

NC

NC

AH11

V13

NC

NC

V14

NC

H6

L1

NC

NC

H8

L2

NC

NC

H9

L3

NC

NC

H10

L12

NC

NC

H11

L13

NC

NC

H12

L14

NC

NC

J8

M1

NC

NC

J9

M2

NC

NC

J10

M3

NC

NC

J11

M12

NC

NC

J12

M13

NC

NC

J13

M14

NC

NC

K7

N2

NC

NC

K8

N1

NC

NC

K9

N3

NC

NC

K10

N12

NC

NC

K11

N13

NC

NC

K12

N14

NC

NC

K13

U1

NC

NC

K14

U2

NC

NC

U3

P1

NC

NC

U12

P2

NC

NC

U13

P12

NC

NC

U14

P3

NC

NC

T1

P13

NC

NC

T2

P14

NC

NC

AA7

T3

NC

NC

AA8

T12

NC

NC

AA9

T13

NC

NC

AA10

T14

NC

NC

AA11

R1

NC

NC

AA12

R2

NC

NC

Y6

R3

NC

NC

Y7

R12

NC

NC

Y8

R13

NC

NC

Y9

R14

NC

NC

Y10

K1

NC

NC

Y11

K3

NC

NC

Y12

K5

NC

NC

Y13

W1

NC

NC

W7

W2

NC

NC

W8

W3

NC

NC

W9

Y3

NC

NC

V_BUCK2

C595

DNP

100k

R591

DDR2 Power Supply

C592

AGND

V_BUCK3_1V8

R597

0

+/-1%

V_DDR_1.2_POWER

R512

0

R504

TP502

L501

12

1uH

C594

0

R511

10uF

DRAWN: DATED:

QUALITY CONTROL: DATED:

[4]

[4]

V_DDR_1.2_POWER

V_DDR_1V2

PG8211_SDI

100nF

U506

88PG8211A2-NXS2C000

1

2

14

100k

15

13

3

12

11

18

4

9

6

8

7

C593

4.7uF

DATED:CHECKED:

DATED:RELEASED:

19

SVIN

VLDO

SGND

20

VINLDO

SS_DONE

SDI16ENLDO

FB1

17

FB2

SLEEPN

EN1

EN2

MODE1

MODE2

SW1

10

SW2

PGND1

5

PGND2

PVIN1

21

PVIN2

PGND

COMPANY:

TITLE:

T801T Memory part

CODE: SIZE: DRAWING NO: REV:

SCALE: SHEET: OF

BYD

VSYS

2

R595

0

1

V_BUCK3_1V8

R592

10k

100k

R596

B

A

123456

REVISION RECORD

LTR ECO NO: APPROVED:

DATE:

920H

D

C

V_BUCK3_1V8

VCC_IO_ANT

VCC_IO_GPIO2

V_BUCK3_1V8

VCC_IO_GSM

VCC_IO_MMC1

V_BUCK3_1V8

V_BUCK3_1V8

V_LDO4

VCC_IO_WB

U401-F

D19

VCC_IO_TDS

C667

100nF

C690

C692

C691

100nF

100nF

100nF

100nF

100nF

100nF

100nF

C693

C668

C669

C670

C671

100nF

100nF

C672

100nF

100nF

100nF

100nF

C696

C697

C665

C666

F9

VCC_IO_ANT

K15

VCC_IO_GPIO1_1

R16

VCC_IO_GPIO1_2

D7

VCC_IO_GPIO2

H19

VCC_IO_GPIO3_1

L22

VCC_IO_GPIO3_2

F12

VCC_IO_GSM

Y4

VCC_IO_MMC1

T10

VCC_IO_NAND_1

T14

VCC_IO_NAND_2

R11

VCC_IO_PMIC1

W14

VCC_IO_PMIC2

V4

VCC_IO_USIM

E19

VCC_IO_WB

G10

VCC18_IO_ANT

F6

VCC18_IO_GPIO2

H21

VCC18_IO_GPIO3

T12

VCC18_IO_NAND

C673

C674

PXA920H

100nF

100nF

AVDD18_ANA_GRP

AVDD18_PLLM

AVDD5_USB

AVDD_USB

DIGRF_AVDD18

MIPI_AVDD1P2V

VCC_MAIN_1

VCC_MAIN_2

VCC_MAIN_3

VCC_MAIN_4

VCC_MAIN_5

VCC_MAIN_6

VCC_MAIN_7

VCC_MAIN_8

VCC_MAIN_9

VCC_MAIN_10

VCC_MAIN_11

VCC_MAIN_12

AB3

C16

NC_25

C12

D17

NC_26

AA5

T9

B11

D5

C2

D10

F14

VCC_MAIN

C661

H3

G8

J20

P16

W1

R9

U16

Y6

C11

F3

VDDQ_1

L6

VDDQ_2

V1

VDDQ_3

P8

VDDQ_4

U3

VDDQ_5

E1

VDDQ_6

H4

VDDQ_7

K2

VDDQ_8

K7

VDDQ_9

C631

C632

100nF

100nF

C695

100nF

R693

0

VCC_MAIN_BACKUP

in reference design

VDDQ

B690

BLM18PG121SN1

C629

C630

2.2uF

100nF

100nF

V_BUCK1

C618

C619

C662100nF

V_DDR_1V2

C616

100nF

100nF

100nF

AVDD18_ANA_GRP

AVDD18_PLLM

AVDD5_USB

AVDD_USB

DIGRF_AVDD18

MIPI_AVDD1P2V

[6]

[6]

[6]

[5]

[5]

[5]

[5]

VCC_IO_GPIO2

[5]

DIGRF_AVDD18

[5]

MIPI_AVDD1P2V

[5] AVDD_USB

[5]

VCC_IO_MMC1

C653

100nF

R610

2

1

DNP

R639

0

C689

C651

C652

100nF

100nF

100nF

V_LDO3_2V8

V_BUCK3_1V8

R603

0

R604

0

R606

0

R607

0

VDDQ

V_BUCK3_1V8

V_LDO12

V_LDO5

V_LDO14

[5]

920H

F16

B12

T8

Y11

B10

D4

D18

D8

K16

N17

W17

F8

H20

L20

F13

AB4

R12

R13

P15

Y1

D21

F4

K8

M4

N8

U4

F1

J8

U2

L3

M6

U401-G

VSS_20

AVSS_PLLM

AVSS_USB

VSS_IO_NAND_2

DIGRF_AVSS

MIPI_AVSS

VSS_IO_TDS

VSS_IO_ANT

VSS_IO_GPIO1_1

VSS_IO_GPIO1_2

VSS_IO_GPIO1_3

VSS_IO_GPIO2

VSS_IO_GPIO3_1

VSS_IO_GPIO3_2

VSS_IO_GSM

VSS_IO_MMC1

VSS_IO_NAND_1

VSS_IO_PMIC1

VSS_IO_PMIC2

VSS_IO_USIM

VSS_IO_WB

VSSQ_1

VSSQ_2

VSSQ_3

VSSQ_4

VSSQ_5

VSSQ_6

VSSQ_7

VSSQ_8

VSSQ_9

VSSQ_10

PXA920H

[5]

VDDQ

A1

NC_1

A2

NC_2

A21

NC_3

A22

NC_4

AA1

NC_5

AA22

NC_6

AB1

NC_7

AB2

VHV

AB21

NC_9

AB22

NC_10

B1

VREFS

B22

NC_12

H10

NC_13

H11

NC_14

H9

NC_29

D6

VSS_1

F10

VSS_2

G14

VSS_3

H22

VSS_4

H6

VSS_5

R19

VSS_6

R8

VSS_7

T15

VSS_8

U12

VSS_9

U7

VSS_10

D12

VSS_11

DNP

R618

DNP

R1609

GND

D

C

[5]

C640

C638

C639

C641

100nF

100nF

B

SH_PA

1

T801T_SH_PA

SH_TD

1

T801T_SH_TD

SH_CPU

1

T801T_SH_CPU

SH_CMMB1

1

A

T801T_SH_CMMB

DRIL5

DRILL_2.6_UP

DRIL6

DRILL_2.6_UP

DRIL7

DRILL_2.6_UP

100nF

C636

C635

C637

100nF

100nF

100nF

100nF

VCC_MAIN

C633

C634

2.2uF

100nF

B

A

DRAWN: DATED:

QUALITY CONTROL: DATED:

COMPANY:

TITLE:

T801T CPU Power part

DATED:CHECKED:

DATED:RELEASED:

CODE: SIZE: DRAWING NO: REV:

SCALE: SHEET: OF

BYD

Loading...

Loading...