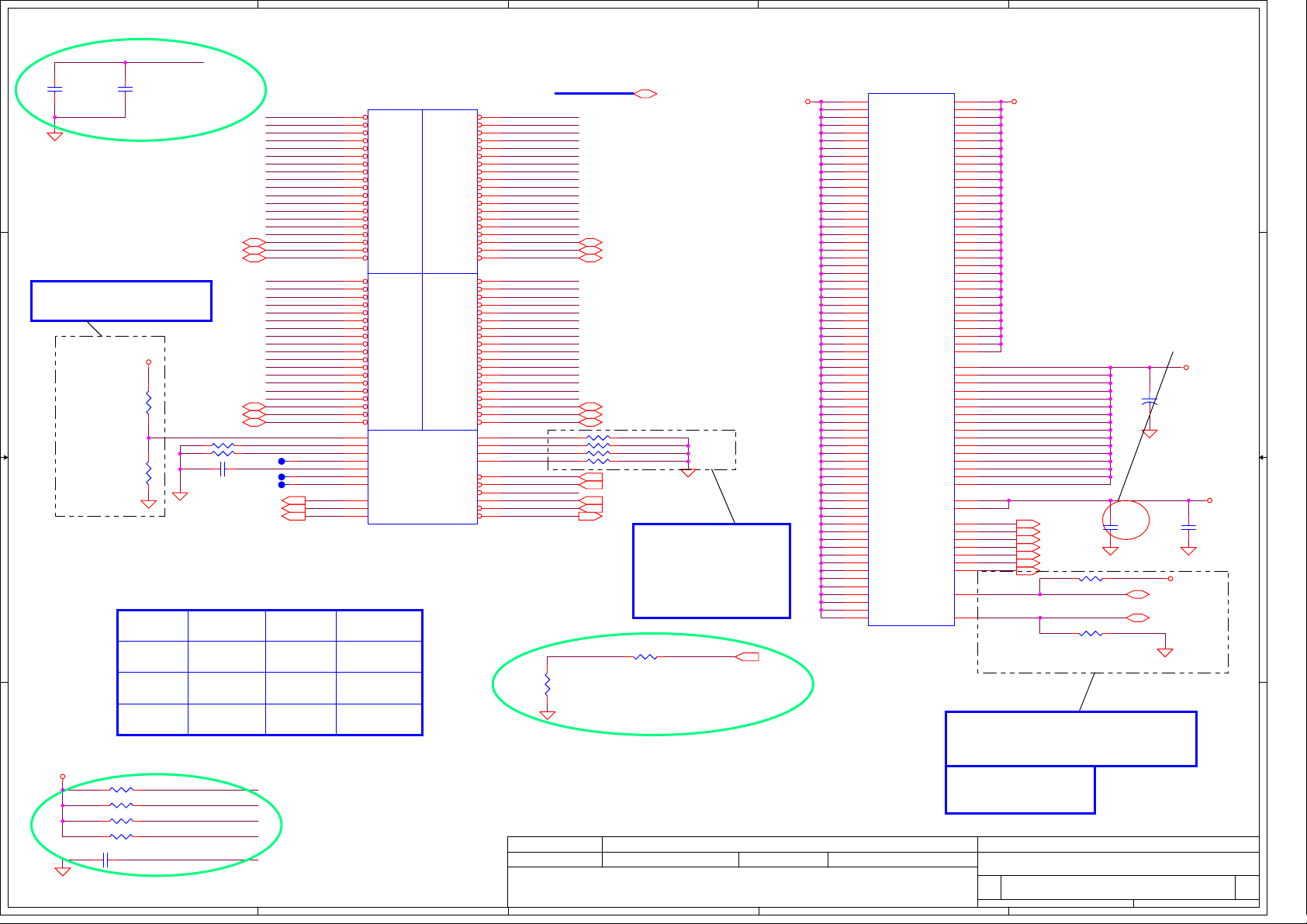

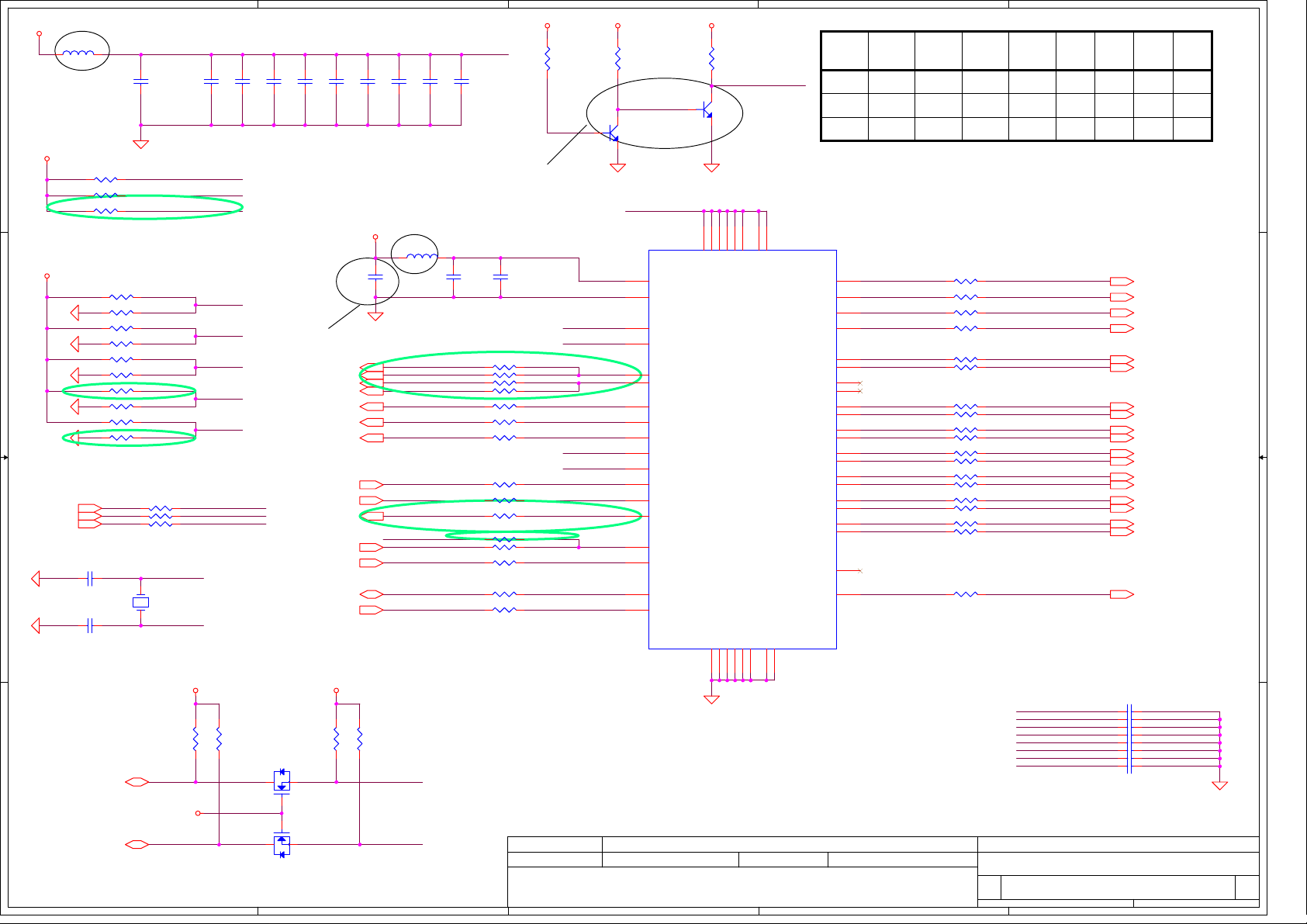

Lenovo 3000 Y400 Schematics

A

B

C

D

E

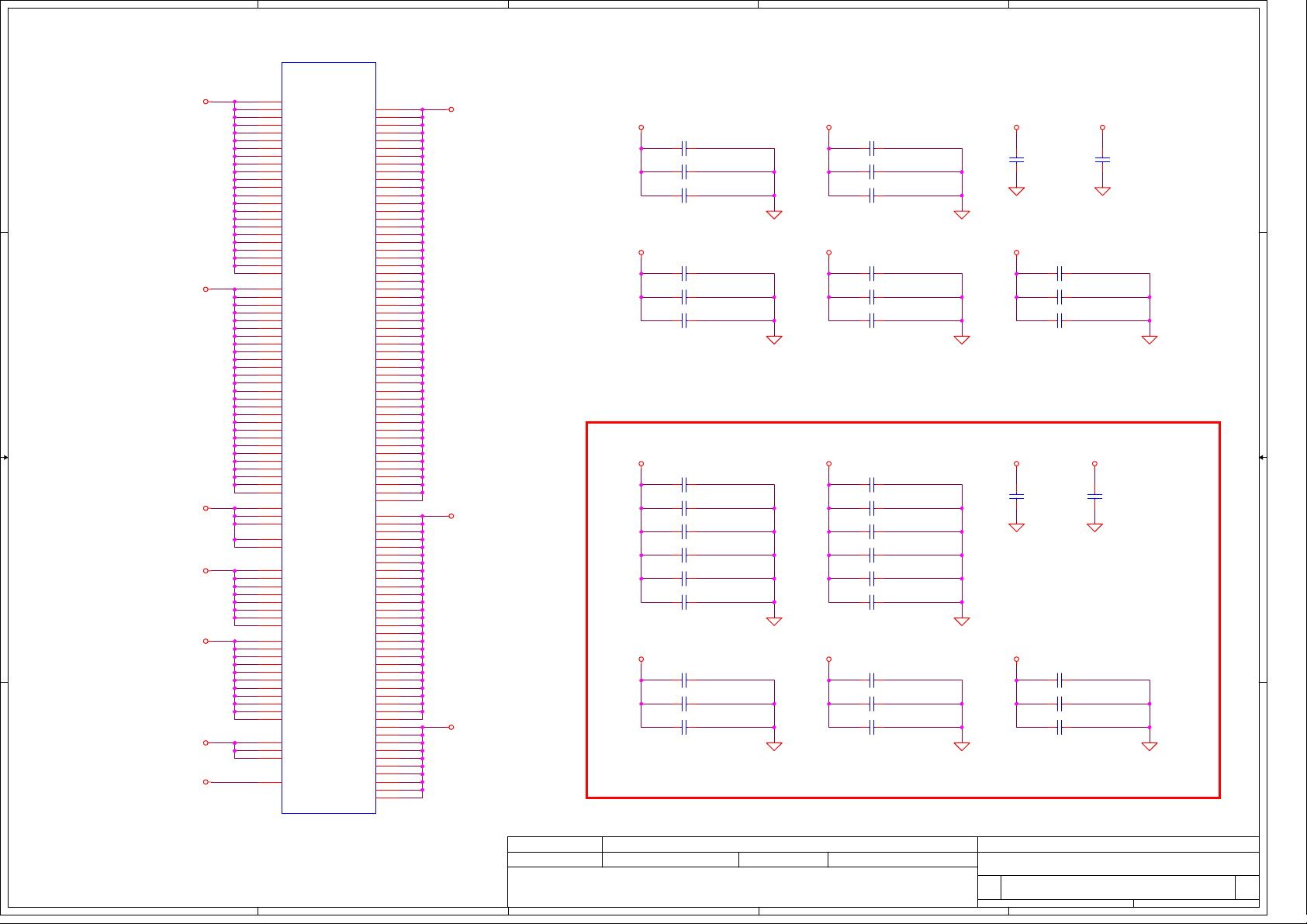

PJP1

14W_DCIN

14W_45@

1 1

ZZZ1

PCB

<BOM Structure>

PJP1

15W_DCIN

15W_45@

Compal Confidential

2 2

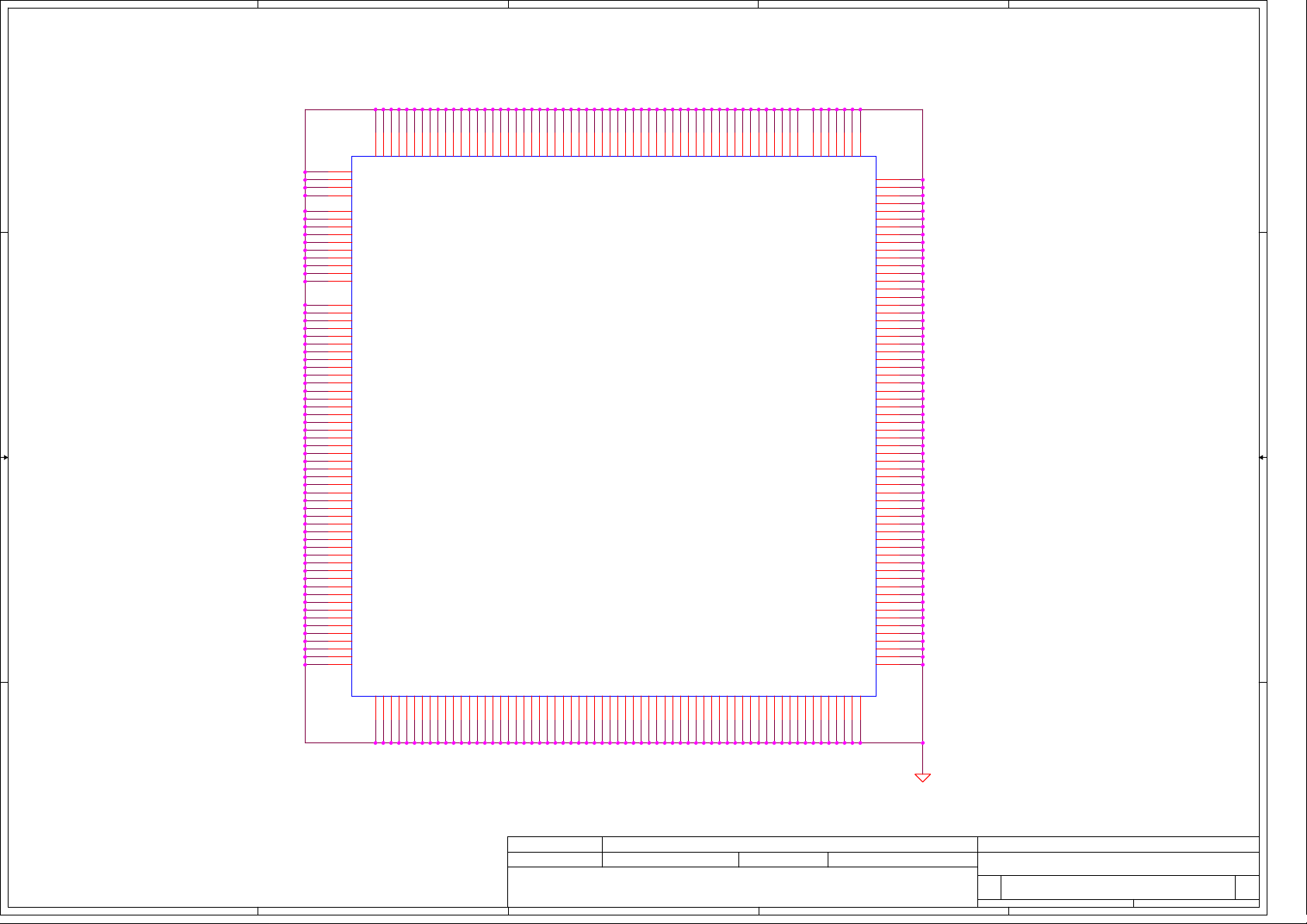

Intel Merom Processor with SiSM672MX + DDRII + SiS968 + SiS307LV

JFWXX Schematics Document

2007-09-06

REV: 0.3

3 3

4 4

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2006/08/18 2007/8/18

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

B

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

JFWXX M/B LA-3961P Schematic

149Thursday, September 06, 2007

E

0.2

of

A

B

C

D

E

Compal Confidential

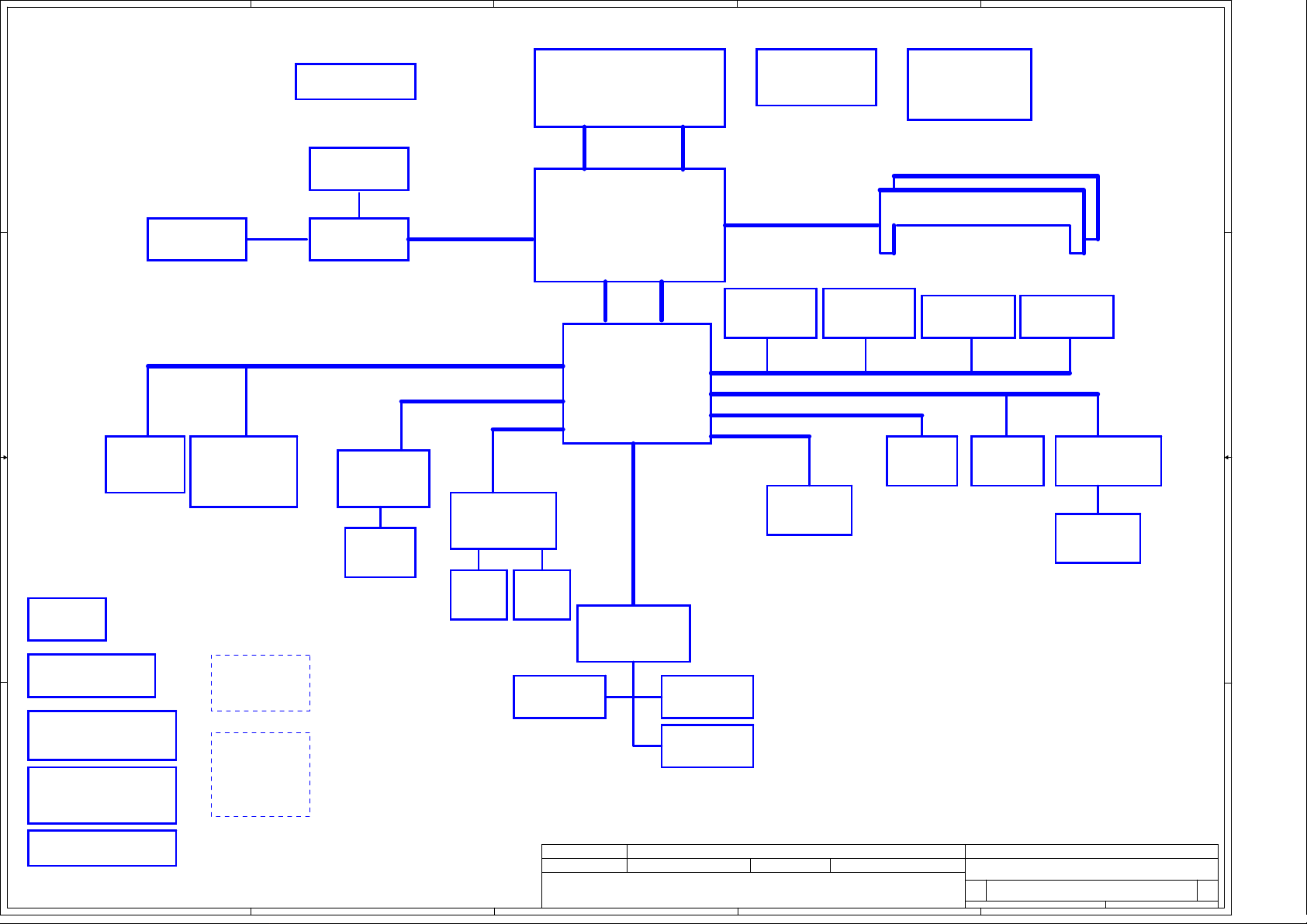

Model Name : JFWXX

Fan Control

page 4

File Name : LA-3961P

1 1

CRT & TV-out

page 17

Intel Merom Processor

uPGA-478 Package

H_A#(3..35)

FSB

667/800MHz

page 4,5,6

H_D#(0..63)

SiS M672MX

LCD Conn.

page 17

SiS 307LV

page 18

PCI-Express

TEBGA-847

page 7,8,9,10,11

Thermal Sensor

ADM1032

page 4

Memory BUS(DDRII)

Single Channel

1.8V DDRII 533/667

Clock Generator

ICS9LPRS600C+

ICS9P935

page 14,15

200pin DDRII-SO-DIMM X2

BANK 0, 1, 2, 3

page 12,13

1GB/s MuTIOL IO Link

2 2

PCI-Express

SiS968

MII

TEBGA-570

page 19,20,21,22,23

New Card

Socket

page 30

MINI Card x1

WLAN

page 29

LAN

page 28

PCI BUS

3.3V 33 MHz

IDSEL:AD22

(PIRQG#,PIRQH#,

GNT#0, REQ#0)

Card Reader

R5C833

page 26

USB conn x2

TO M/B

page 33

3.3V 48MHz

3.3V 24.576MHz/48Mhz

3.3V ATA-100

S-ATA

port 0

S-ATA HDD

Conn.

RJ45

3 3

RTC CKT.

page 20

Power On/Off CKT.

page 34

Switch/B Conn.

page 32

page 28

1394

Conn.

page 26

3 in 1

socket

page 27

Touch Pad

page 33

ENE KB926

LPC BUS

page 31

Int.KBD

page 32

USB conn x2

TO I/O/B

USB

IDE

page 24

Bluetooth

page 37 page 33 page 37

Conn

Web Camera

HD Audio

CDROM

Conn.

page 24

MDC 1.5

Conn

page 37

HDA Codec

ALC268

Audio AMP

page 36

page 35

DC/DC Int erface CKT.

page 40

I/O Conn.

BIOS

page 33

FRONT LCD /B.

Power Circuit DC/DC

4 4

page 41,42,44,458

46,47,48

LID SW

page 34

CHARGER

page 43

A

Security Classification

Issued Date

THIS SHEET OF EN GINEE RING D RAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/08/18 2007/8/18

C

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

B

D

Date: Sheet

Compal Electronics, Inc.

Block Diagrams

JFWXX M/B LA-3961P Schematic

E

of

249Thursday, September 06, 2007

0.1

A

B

C

D

E

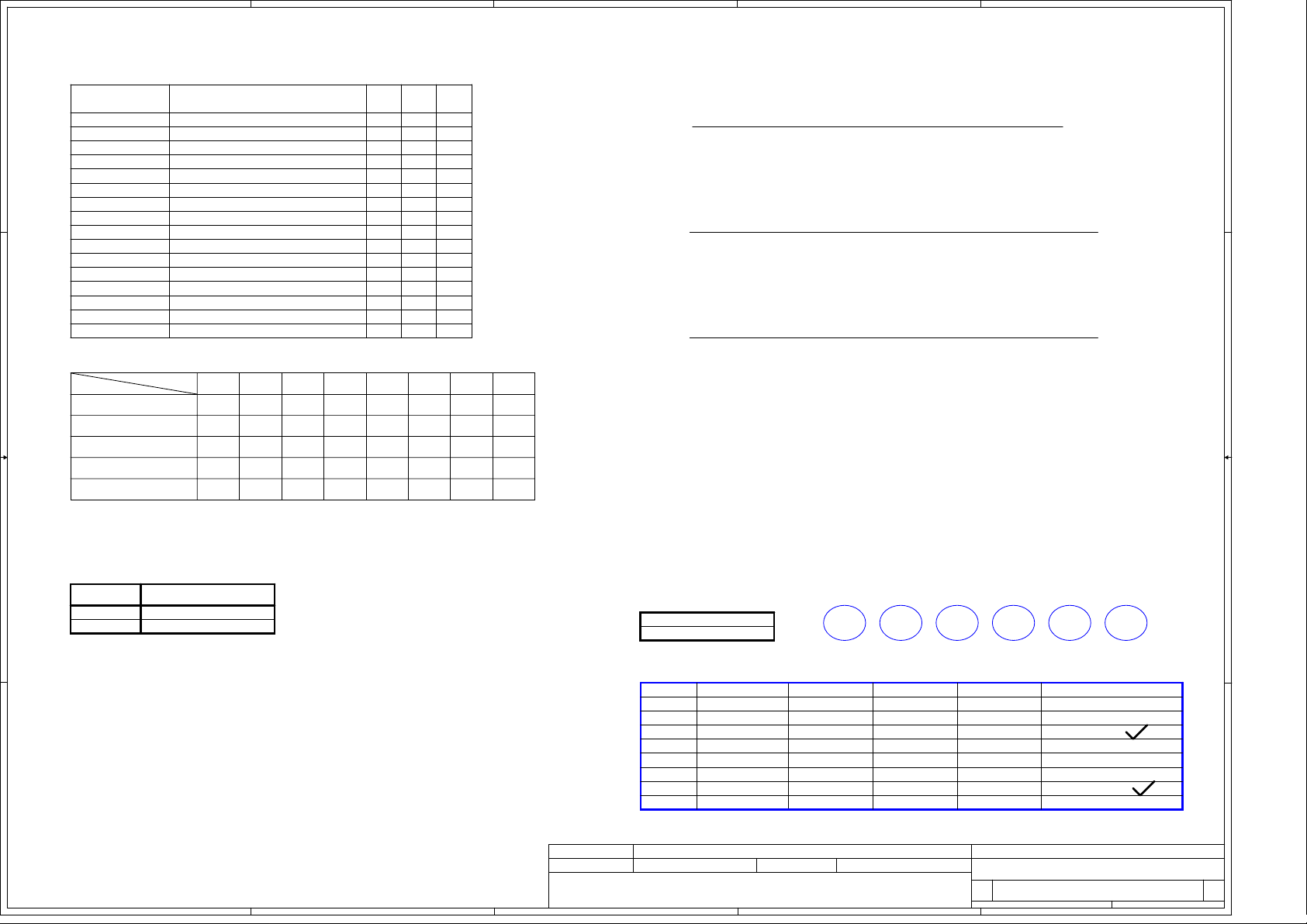

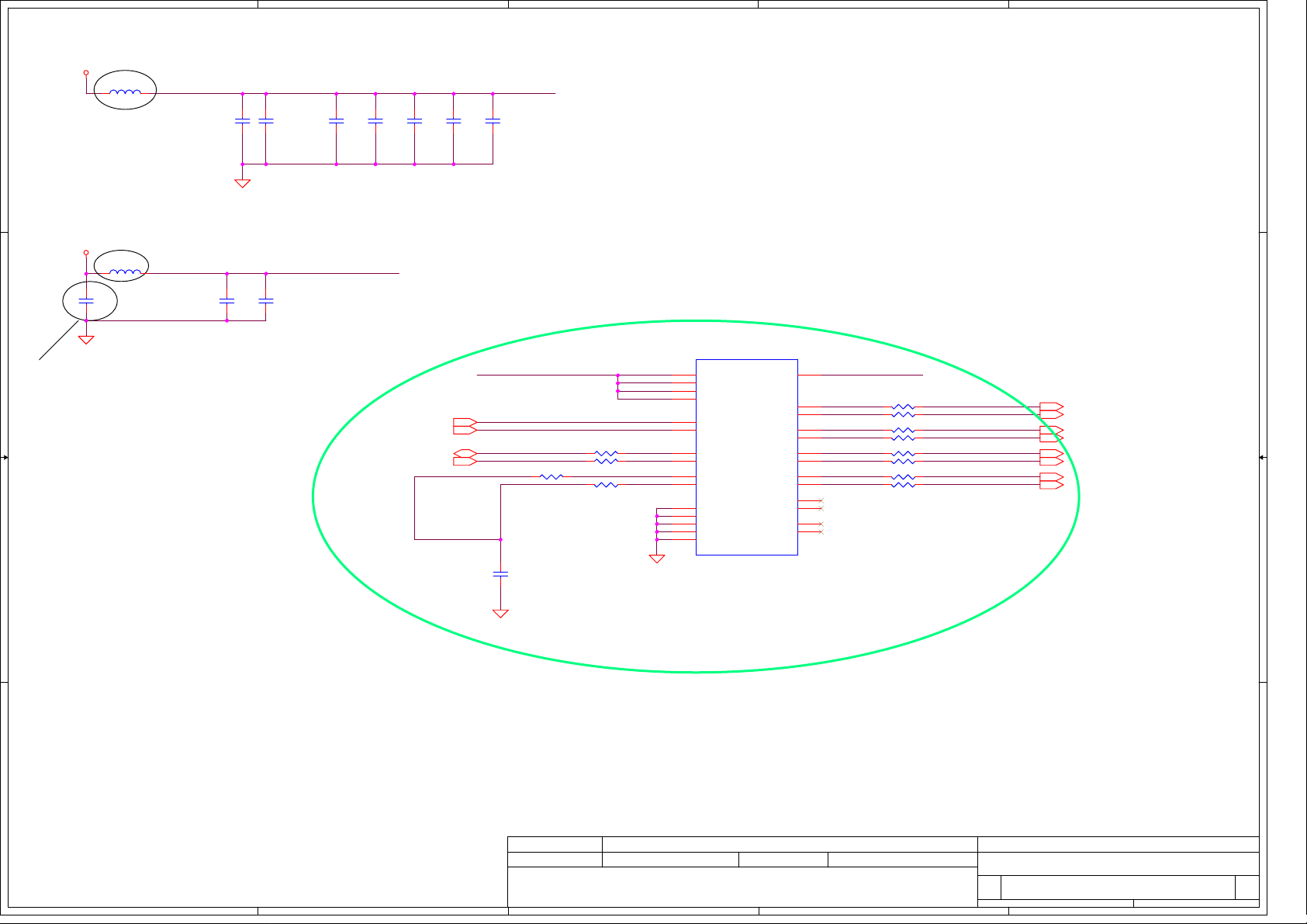

Voltage Rails

DescriptionPower Plane

1 1

2 2

VIN

B+

+CPU_CORE

+1.05VS

+1.5VS

+1.8V

+2.5VS

+3VALW

+3VS

+5VALW

+5VS

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

0.9V switched power rail for DDR terminator+0.9VS ( Actual +0.9V )

1.05V switched power rail

1.5V switched power rail

1.8V power rail for DDR

1.8V switched power rail+1.8VS

2.5V switched power rail

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

RTC power+RTCVCC

SIGNAL

SLP_S3#SLP_S1#

HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW

SLP_S4#

HIGH

LOWLOWLOW

SLP_S5#

HIGHHIGHHIGHHIGH

HIGH

HIGH

LOW

S3S1

N/A N/A N/A

OFFON

ON

ON

ON1.25V switched power rail+1.25VS

ON

ON

OFF

ON

ON

OFF

ON

ON

OFF

ON

ON

OFF

ON OFF

ONONON

+VALW

+V +VS Clock

ON

ON

ON

ON

ON

ON

ON

OFF

ON

OFF

S5

N/AN/AN/A

OFF

OFF

OFFOFFON

OFFOFF

OFFOFFON

OFF

OFF

OFF

ON*ON

OFF

ON*

ON*ONVSB always on power rail+VSB

ON

ON

OFF

OFF

OFF

ONON

LOW

OFF

OFF

OFF

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

External PCI Devices

DEVICE

1394+Cardreader G,H

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

IDSEL #

AD20

AD22

Address

1010 000X b

REQ/GNT #

2

PIRQ

C,DCARD BUS CB1410

0

EC SM Bus2 address

Device

ADI ADM1032

NVIDIA NB8X

Address

1001 100X b0001 011X b

ICH8M SM Bus address

Device

Clock Generator

(ICS9LPRS325AKLFT_MLF72)

DDR DIMM0

DDR DIMM1

Address

1101 001Xb

1010 000Xb

1010 010Xb

PROJECT ID Table

3 3

14W

15W

PROJECT_ID

R424 (Pull low)

NA (Internal Pull High)

SKU ID Table

Vcc 3.3V +/- 5%

100K +/- 5%Ra

Ra~ R312

R311

8.2K_0402_5%

14_B@

R311

18K_0402_5%

14_C@

R311

33K_0402_5%

14_MP@

R311

56K_0402_5%

15_A@

R311

100K_0402_5%

15_B@

Rb~ R311

Board ID

0

1

2

3

4

5

4 4

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

6

7

2006/08/18 2007/8/18

C

Rb

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

NC

Compal Secret Data

Vmin

AD_BID

0 V

Vtyp

AD_BID

0 V 0 V

0.217 V 0.250 V 0.288 V

0.439 V

0.721 V

1.054 V

0.503 V

0.819 V

1.185 V 1.325 V

1.489 V 1.650 V 1.819 V

2.019 V

3.135V

Deciphered Date

2.200 V

3.300 V

D

V

max

AD_BID

Rb BOM Structure

0.575 V

0.926 V

2.386 V

3.465 V

Title

Size Document Number Rev

B

Date: Sheet

Compal Electronics, Inc.

JFWXX M/B LA-3961P Schematic

14_A@

14_B@

14_C@

14_MP@

15_A@

15_B@

15_C@

15_MP@

Notes List

R311

200K_0402_5%

15_C@

E

0.1

of

349Thursday, September 06, 2007

5

4

3

2

1

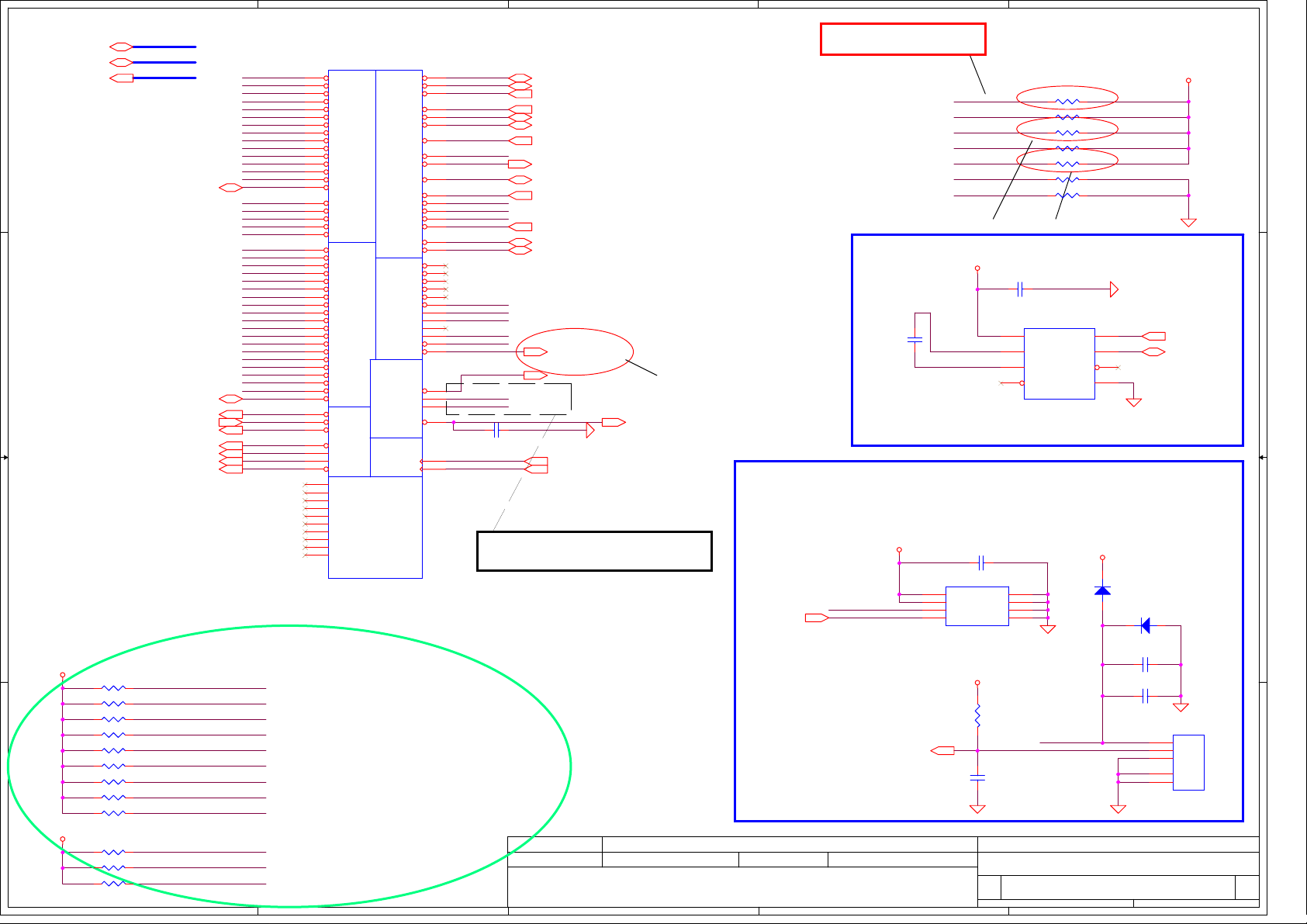

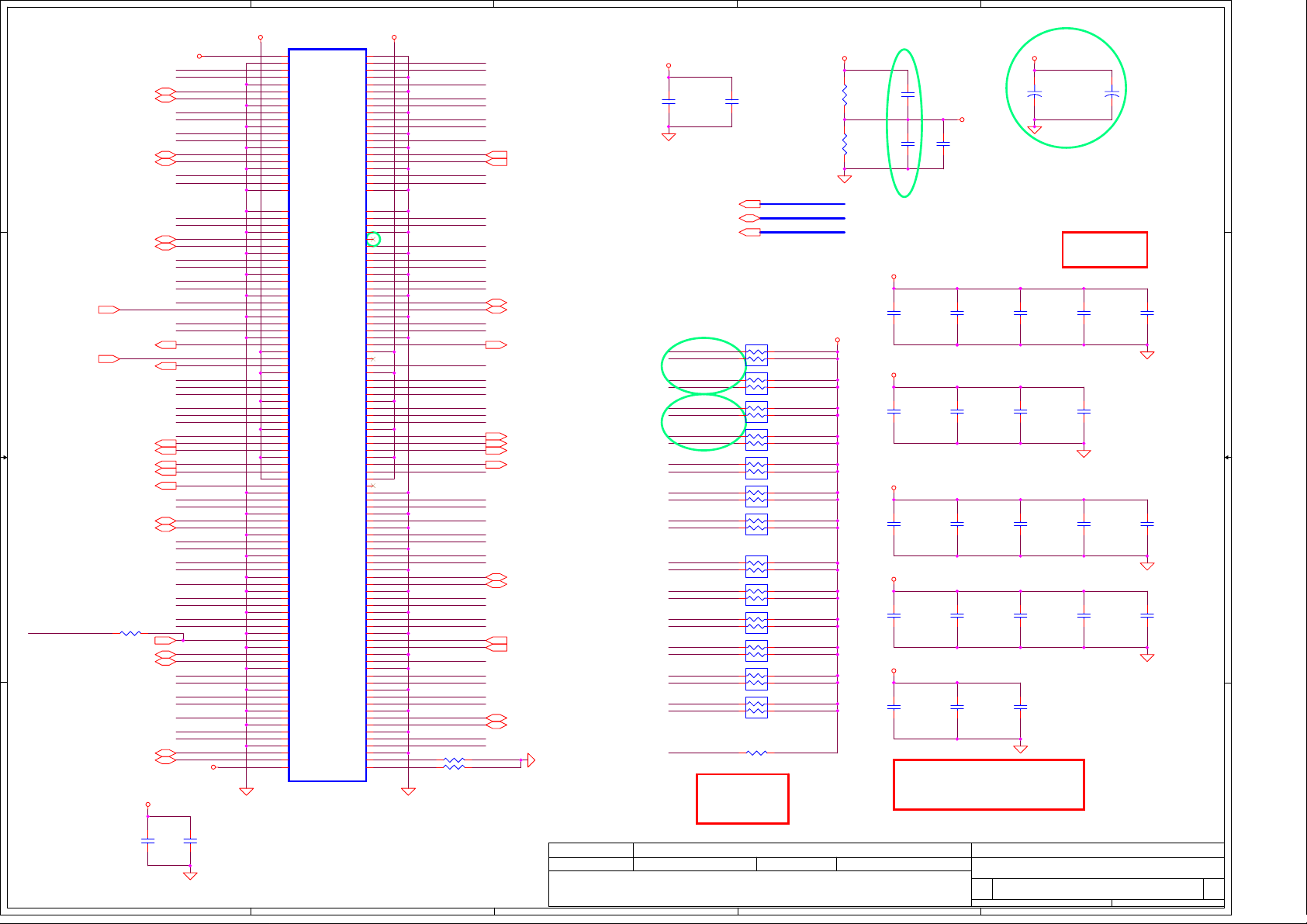

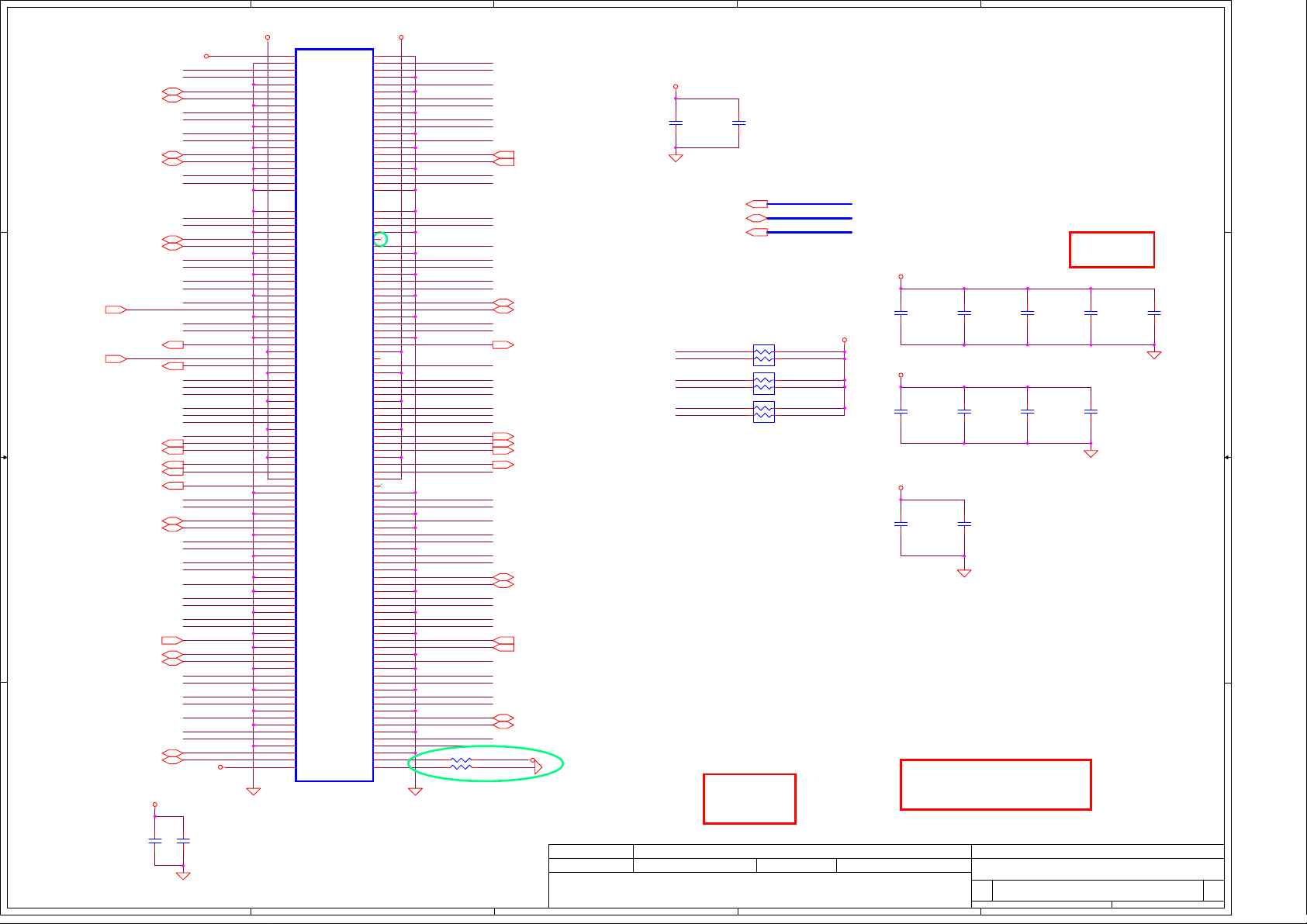

Trace length must short

H_PREQ#

H_IERR#

ITP_TMS

ITP_TDI

H_PROCHOT#

ITP_TCK

ITP_TRST#

Checklist recommend 39 Ohm

ADM1032

1

C111

2200P_0402_50V7K

+VCC_FAN1

EN_FAN1

+5VS

FAN_SPEED1<31>

2

THERMDA

2

THERMDC

C58 10U_0805_10V4Z

U3

1

VEN

2

VIN

3

VO

4

VSET

G993P1UF_SOP8

Place close to CPU within 500mil

+1.05VS

R85 56_0402_5%@

1 2

R115 56_0402_5%

1 2

R84 56_0402_5%

1 2

R83 150_0402_1%

1 2

R113 56_0402_5%

1 2

R69 27.4_0402_1%

1 2

R61 680_0402_5%

1 2

CRB pull 75 Ohm

+3VS

C112 0.1U_0402_16V4Z

1 2

U7

1

VDD

2

D+

3

DTHERM#4GND

ADM1032ARMZ_MSOP8

F75383M_MSOP8

1 2

8

GND

7

GND

6

GND

5

GND

+3VS

12

R31

10K_0402_5%

+VCC_FAN1

1

C54

1000P_0402_50V7K

2

Title

Size Document Number Rev

B

JFWXX M/B LA-3961P Schematic

Date: Sheet

SDATA

ALERT#

40mil

SCLK

8

7

6

5

+5VS

12

D12

1SS355_SOD323

1000P_0402_50V7K

C52 10U_0805_10V4Z

D11

1 2

BAS16_SOT23-3

1 2

C55

1 2

1

2

3

4

5

EC_SMB_CK2 <31>

EC_SMB_DA2 <31>

JP6

1

2

3

GND

GND

ACES_85205-03001

ME@

Compal Electronics, Inc.

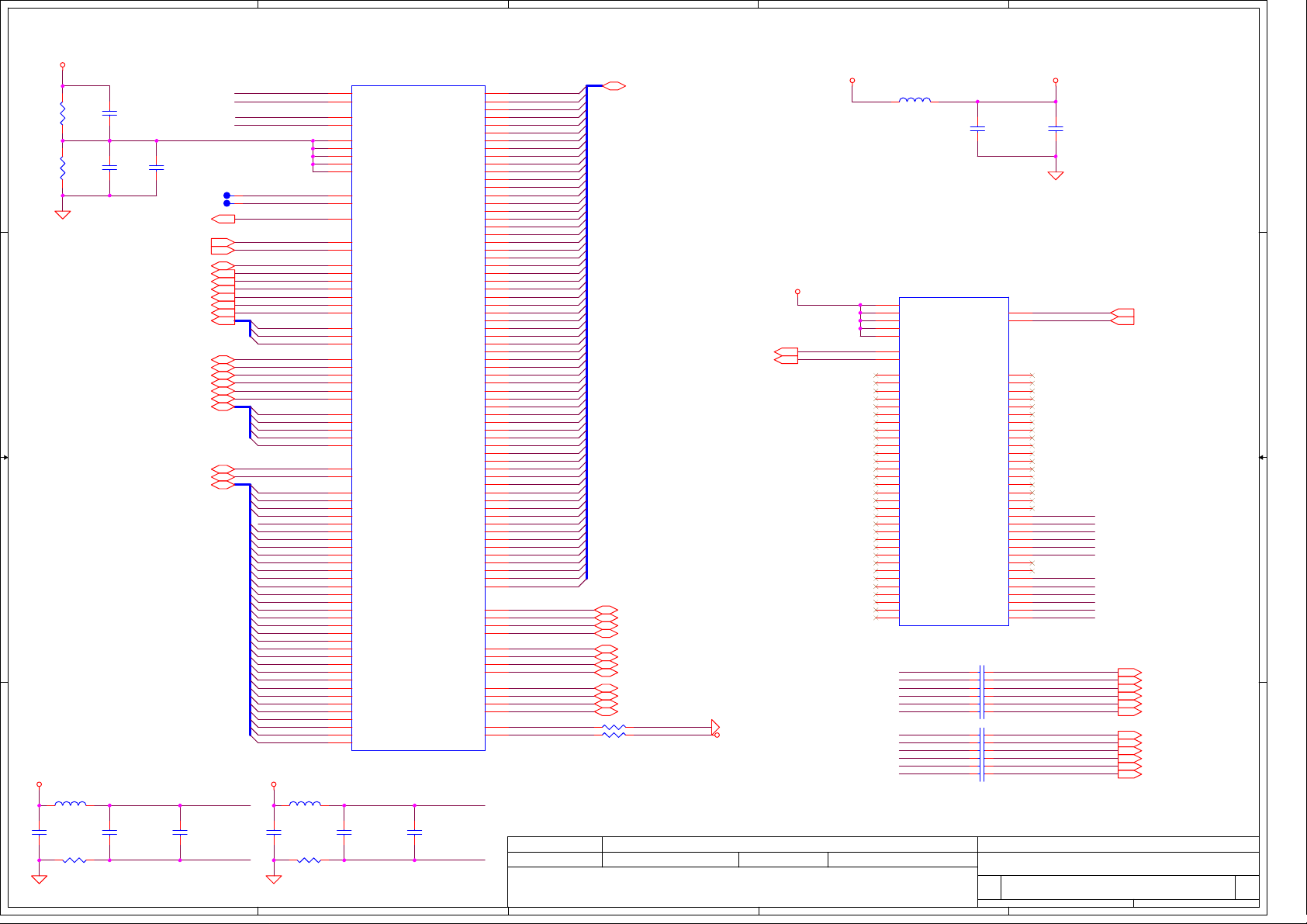

Merom (1/3)

449Thursday, Sept em be r 06, 2007

1

of

0.1

H_A#[3..35]

H_REQ#[0..4]

H_RS#[0..2]

5

H_ADSTB#0<7>

H_ADSTB#1<7>

H_A20M#<20>

H_FERR#<20>

H_IGNNE#<20>

H_STPCLK#<20>

H_INTR<20>

H_NMI<20>

H_SMI#<20>

H_STPCLK#

H_INIT#

H_IGNNE#

H_SMI#

H_A20M#

H_NMI

H_INTR

H_THERMTRIP#

H_FERR#

H_BR0#

H_RESET#

ITP_DBRESET#

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

JP36A

J4

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

AA4

A[33]#

AB2

A[34]#

AA3

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

C3

RSVD[06]

D2

RSVD[07]

D22

RSVD[08]

D3

RSVD[09]

F6

RSVD[10]

Merom Ball-out Rev 1a

conn@

ADDR GROUP 0 ADDR GROUP 1

ICH

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

XDP/ITP SIGNALS

DBR#

THERMAL

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

H CLK

BCLK[0]

BCLK[1]

RESERVED

H1

E2

G5

H5

F21

E1

F1

H_IERR#

D20

H_INIT#

B3

H4

H_RESET#

C1

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

H_PREQ#

AC1

ITP_TCK

AC5

ITP_TDI

AA6

TDI

AB3

ITP_TMS

AB5

ITP_TRST#

AB6

ITP_DBRESET#

C20

H_PROCHOT#

D21

THERMDA

A24

THERMDC

B25

H_THERMTRIP#

H_THERMTRIP#

C7

C114 0.1U_0402_16V4Z

1 2

A22

A21

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

Intel :Don't Pull-up SiS : Pull-up 56ohm (Mount)

Intel :Don't Pull-up SiS : Pull-up 56ohm (Mount)

Intel :Don't Pull-up SiS : Pull-up 56ohm (Mount)

Intel :Don't Pull-up SiS : Pull-up 56ohm (Mount)

Intel :Don't Pull-up SiS : Pull-up 56ohm (Mount)

Intel :Don't Pull-up SiS : Pull-up 56ohm (Mount)

Intel :Don't Pull-up SiS : Pull-up 56ohm (Mount)

Intel : Pull-up 56ohm (Mount) SiS : Pull-up 56ohm (Mount)

Intel : Pull-up 56ohm (Mount) SiS : Pull-up 56ohm (Mount)

Intel :Don't Pull-up SiS : Pull-up 56ohm (Mount)

Intel :Don't Pull-up SiS : Pull-up 56ohm (Un-Mount)

Intel :Don't Pull-up SiS : Pull-up 150ohm (Mount)

4

H_ADS# <7>

H_BNR# <7>

H_BPRI# <7>

H_DEFER# <7>

H_DRDY# <7>

H_DBSY# <7>

H_BR0# <7>

H_INIT# <20>

H_LOCK# <7>

H_RESET# <7>

H_TRDY# <7>

H_HIT# <7>

H_HITM# <7>

ITP_DBRESET#

H_PROCHOT# <20>

H_CLK_DP0 <14>

H_CLK_DN0 <14>

Connect SB SYS_RESET# or just left NC

Intel :Pull-up 56ohm (Un-Mount) SiS : Pull-up 56ohm (Mount)

Intel :Pull-up 56ohm (Mount) SiS : Pull-up 54.9ohm (Mount)

Intel :Pull-up 56ohm (Mount) SiS : Pull-up 75ohm (Mount)

H_THERMTRIP# <20>

FAN1 Conn

EN_FAN1<31>

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/08/18 2007/8/18

3

Compal Secret Data

Deciphered Date

H_A#[3..35]<7>

H_REQ#[0..4]<7>

H_RS#[0..2]<7>

D D

C C

B B

+1.05VS

CPU to SB interface

R120 56_0402_5%

1 2

R141 56_0402_5%

1 2

R128 56_0402_5%

1 2

R144 56_0402_5%

1 2

R148 56_0402_5%

1 2

R137 56_0402_5%

1 2

R140 56_0402_5%

1 2

R127 56_0402_5%

A A

1 2

R214 56_0402_5%

1 2

+1.05VS

R114 51_0402_1%

1 2

R136 56_0402_5%@

1 2

R112 150_0402_1%

1 2

5

GTL_REF

1

C368

1U_0603_10V4Z

2

D D

SiS Recommend

Close to CPU pin AD26

within 500mils.

C C

Width=20 mil

B B

layout note: Route TEST3 & TEST5 traces on ground referenced layer to the TPs

1

2

R321

1K_0402_1%

R319

2K_0402_1%

C369

220P_0402_50V7K

+1.05VS

1 2

R111 1K_0402_5%@

R98 1K_0402_5%@

1 2

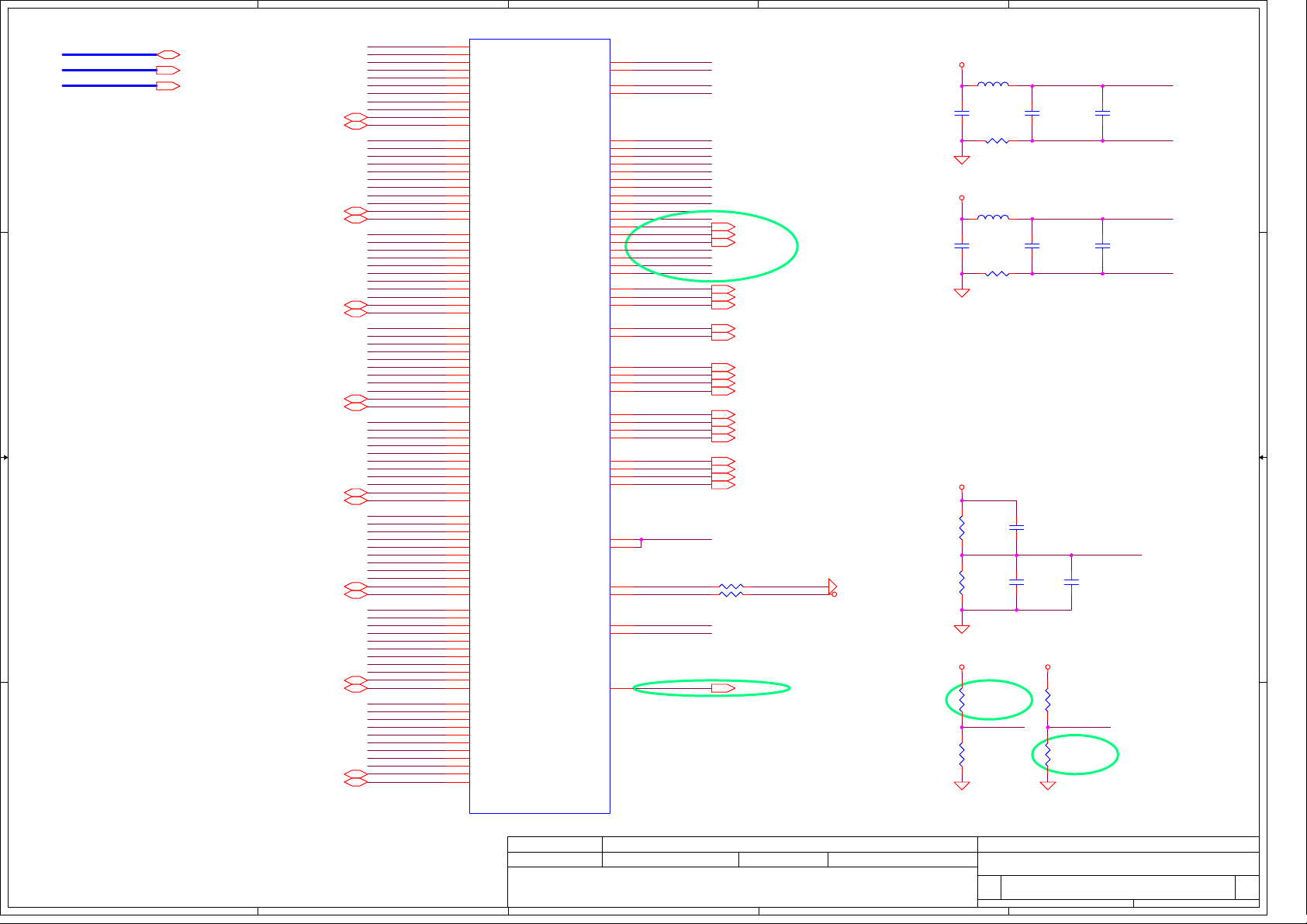

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

PAD

PAD

PAD

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

GTL_REF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

H_DSTBN#0<7> H_DSTBN#2 <7>

H_DSTBP#0<7> H_DSTBP#2 <7>

H_DINV#0<7>

H_DSTBN#1<7> H_DSTBN#3 <7>

H_DSTBP#1<7> H_DSTBP#3 <7>

H_DINV#1<7>

12

12

1 2

T3

T2

T23

H_BSEL0<14>

H_BSEL1<14>

H_BSEL2<14>

C364 0.1U_0402_16V4Z@

CPU_BSEL CPU_BSEL2 CPU_BSEL1

001133

166

200

01

0

1

4

JP36B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

Merom Ball-out Rev 1a

conn@

CPU_BSEL0

1

0

DATA GRP 0

DATA GRP 1

MISC

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

DATA GRP 2DATA GRP 3

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

H_DPSLP#

H_DPWR#_R

H_PWRGOOD

H_CPUSLP#

3

H_D#[0..63]

H_DINV#2 <7>

R324 27.4_0402_1%

R323 54.9_0402_1%

R42 27.4_0402_1%

R44 54.9_0402_1%

H_DPWR#_R H_DPWR#

R131

10_0402_5%

H_DINV#3 <7>

1 2

1 2

1 2

1 2

H_DPRSTP# <25,48>

H_DPSLP# <25>

H_PWRGOOD <7>

H_CPUSLP# <20>

H_PSI# <48>

H_D#[0..63] <7>

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

mils away from any other

toggling signal.

COMP[0,2] trace width is

18 mils. COMP[1,3] trace

width is 4 mils.

@

1 2

R126 0_0402_5%

+CPU_CORE

H_DPWR# <7>

2

JP36C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

Merom Ball-out Rev 1a

conn@

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

.

+CPU_CORE

VCCSENSE

VSSSENSE

CPU_VID0 <48>

CPU_VID1 <48>

CPU_VID2 <48>

CPU_VID3 <48>

CPU_VID4 <48>

CPU_VID5 <48>

CPU_VID6 <48>

R27

R24 100_0402_1%

Length match within 25 mils.

1

Place this cap more close to

B26/C26 rather than 10UF

1

+

C80

330U_D2E_2.5VM_R9

2

20mils

1

C438

0.01U_0402_16V7K

2

1 2

1 2

100_0402_1%

+CPU_CORE

VCCSENSE <48>

VSSSENSE <48>

+1.05VS

+1.5VS

1

C432

10U_0805_10V4Z

2

The trace width/space/other is

+1.05VS

R121 56_0402_5%

A A

1 2

R143 56_0402_5%

1 2

R133 56_0402_5%@

1 2

R119 56_0402_5%@

1 2

C650 0.1U_0402_16V4Z@

1 2

5

H_CPUSLP#

H_DPSLP#

H_PWRGOOD

H_DPWR#

H_PWRGOOD

Intel :Don't Pull-up SiS : Pull-up 56ohm (Mount)

SiS Recommend

Intel :Pull-up 56ohm (Un-Mount) SiS : Pull-up 56ohm (Mount)

Intel :Don't Pull-up (Connecte to ICH) SiS : Pull-up 56ohm (Un-Mount)

Intel :Don't Pull-up SiS : Pull-up 56ohm (Un-Mount)

Intel :Don't Pull-down SiS :Pull-down Cap (Un-Mount)

4

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/08/18 2007/8/18

3

Compal Secret Data

Deciphered Date

2

20/7/25.

Close to CPU pin

within 500mils.

Title

Size Document Number Rev

B

JFWXX M/B LA-3961P Schematic

Date: Sheet

Compal Electronics, Inc.

Merom (2/3)

549Thursday, Sept em be r 06, 2007

1

0.1

of

5

4

3

2

1

+CPU_CORE

JP36D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

D D

C C

B B

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Merom Ball-out Rev 1a

conn@

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

.

1

+

C47

330U_D2E_2.5VM_R9

2

+CPU_CORE

1

C394

2

10U_0805_6.3V6M

+CPU_CORE

1

C379

2

10U_0805_6.3V6M

+CPU_CORE

1

C107

2

10U_0805_6.3V6M

+CPU_CORE

1

C77

2

10U_0805_6.3V6M

+CPU-CORE

Decoupling

SPCAP,Polymer

MLCC 0805 X5R

3 x 330uF(9mOhm/3) 3 x 330uF(9mOhm/3)

1

+

C350

2

330U_D2E_2.5VM_R9

South Side Seco ndary North Side Sec ondary

1

C383

10U_0805_6.3V6M

2

10U_0805_6.3V6M

1

+

C390

@

330U_D2E_2.5VM_R9

2

1

C408

10U_0805_6.3V6M

2

(Place these capacitors on South side,Secondary Layer)

1

C378

10U_0805_6.3V6M

2

1

C377

2

10U_0805_6.3V6M

10U_0805_6.3V6M

(Place these capacitors on North side,Secondary Layer)

1

C106

10U_0805_6.3V6M

2

1

C105

2

10U_0805_6.3V6M

10U_0805_6.3V6M

(Place these capacitors on South side,Primary Layer)

1

C76

10U_0805_6.3V6M

2

1

C75

2

10U_0805_6.3V6M

10U_0805_6.3V6M

(Place these capacitors on North side,Primary Layer)

C,uF ESR, mohm ESL,nH

6X330uF 9m ohm/6 1.8nH/6

32X22uF 3m ohm/32 0.6nH/32

32X10uF 3m ohm/32 0.6nH/32

+1.05VS

1

2

0.1U_0402_16V4Z

1

C97

0.1U_0402_16V4Z

2

C87

0.1U_0402_16V4Z

1

2

1

2

1

2

1

2

1

C81

0.1U_0402_16V4Z

2

+CPU_CORE

1

+

C347

330U_D2E_2.5VM_R9

2

330U_D2E_2.5VM_R9

C409

C376

C104

C74

1

C410

2

10U_0805_6.3V6M

1

C375

2

10U_0805_6.3V6M

1

C103

2

10U_0805_6.3V6M

1

C84

2

10U_0805_6.3V6M

1

C96

2

0.1U_0402_16V4Z

1

+

C155

2

1

10U_0805_6.3V6M

2

1

10U_0805_6.3V6M

2

1

10U_0805_6.3V6M

2

1

10U_0805_6.3V6M

2

1

C83

0.1U_0402_16V4Z

2

C169

@

330U_D2E_2.5VM_R9

C411

10U_0805_6.3V6M

C385

10U_0805_6.3V6M

C89

10U_0805_6.3V6M

C78

10U_0805_6.3V6M

1

C73

2

1

+

2

1

C412

10U_0805_6.3V6M

2

1

C393

10U_0805_6.3V6M

2

1

C46

10U_0805_6.3V6M

2

1

C88

10U_0805_6.3V6M

2

1

CRB no stuff. Reserved!

C392

2

1

C384

2

1

C90

2

1

C85

2

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/08/18 2007/8/18

3

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

B

2

Date: Sheet

Compal Electronics, Inc.

Merom (3/3)

JFWXX M/B LA-3961P Schematic

649Thursday, Sept em be r 06, 2007

1

0.1

of

5

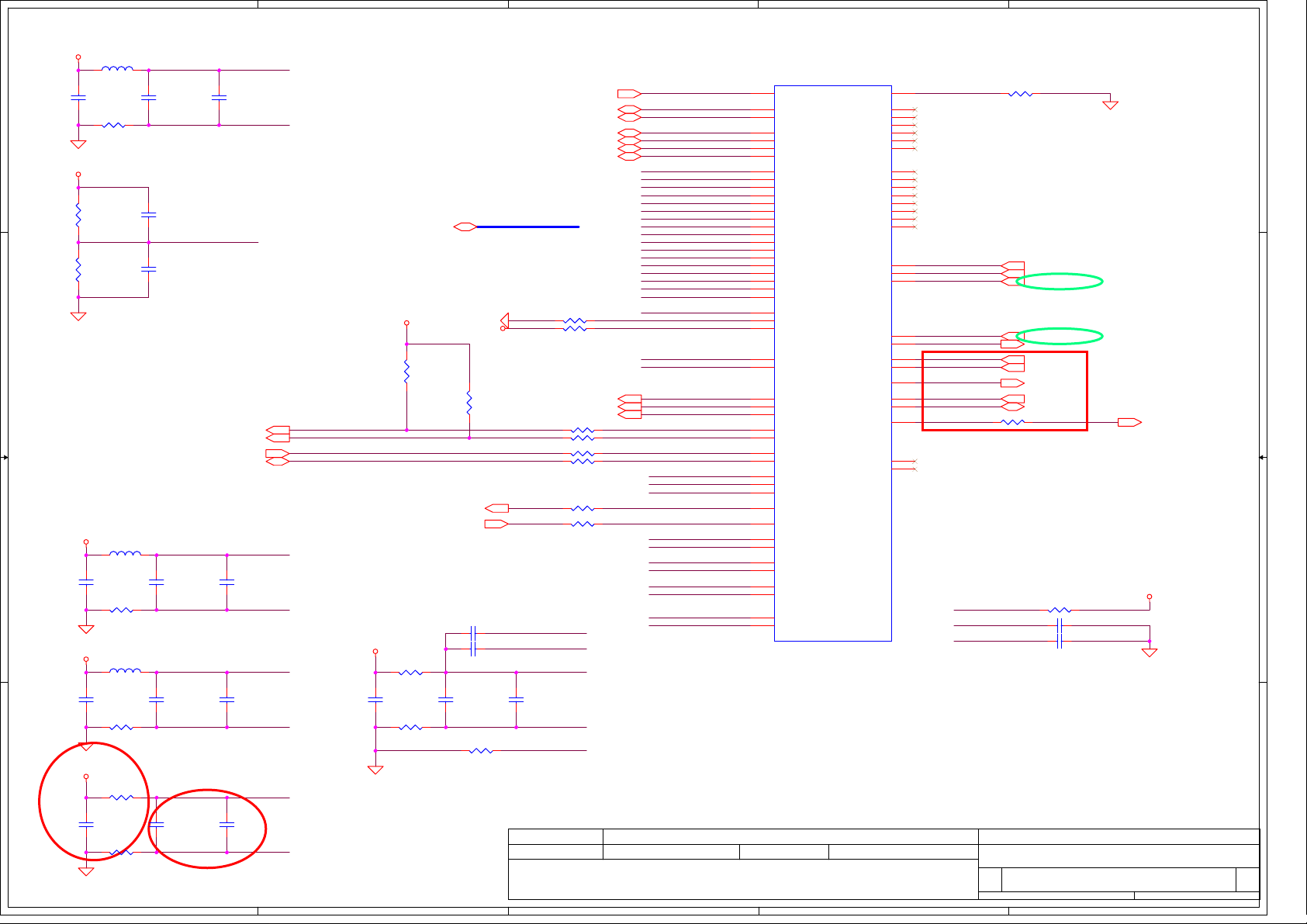

+1.05VS

12

R210

75_0402_1%

D D

12

R202

150_0402_1%

C C

B B

+1.8VS +1.8VS

A A

L40

1 2

MBK1608121YZF_0603

1

C454

10U_0805_10V4Z

2

1 2

R399 0_0402_5%

1

C191

0.01U_0402_16V7K

2

1

C212

2

0.01U_0402_16V7K

1

C472

0.1U_0402_16V4Z

2

5

1

C200

0.1U_0402_16V4Z

2

PAD

T30

PAD

T5

H_DPWR#<5>

H_CLK_DP1<14>

H_CLK_DN1<14>

H_LOCK#<4>

H_DEFER#<4>

H_TRDY#<4>

H_RESET#<4>

H_PWRGOOD<5>

H_BPRI#<4>

H_BR0#<4>

H_RS#[0..2]<4>

H_ADS#<4>

H_HITM#<4>

H_HIT#<4>

H_DRDY#<4>

H_DBSY#<4>

H_BNR#<4>

H_REQ#[0..4]<4>

H_ADSTB#0<4>

H_ADSTB#1<4>

H_A#[3..35]<4>

C1XAVDD:10mA C4XAVDD:12mA

C1XAVDD

1

C481

0.01U_0402_16V7K

2

C1XAVSS

C1XAVDD

C1XAVSS

C4XAVDD

C4XAVSS

NB_GTLREF

PCREQ#

EDRDY#

H_DPWR#

H_CLK_DP1

H_CLK_DN1

H_LOCK#

H_DEFER#

H_TRDY#

H_RESET#

H_PWRGOOD

H_BPRI#

H_BR0#

H_RS#0

H_RS#1

H_RS#2

H_ADS#

H_HITM#

H_HIT#

H_DRDY#

H_DBSY#

H_BNR#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

1 2

MBK1608121YZF_0603

1

C455

10U_0805_10V4Z

2

R400 0_0402_5%

L39

1 2

B16

C17

A17

B18

W24

U24

R24

N24

R34

P32

E21

F18

G18

P30

P31

F21

P28

N30

P33

K34

M31

K33

M34

N34

N32

M33

M32

T34

R30

R29

R32

P34

U34

AA34

T32

T28

T31

T33

T30

U32

U30

V34

U29

V33

V32

V28

V31

W34

Y33

W32

V30

W30

Y34

Y28

W29

Y32

Y30

Y31

AA32

AA30

AA29

AB33

AB34

AB32

AC34

AB30

AB31

L21

L32

L34

4

U30C

C1XAVDD

C1XAVSS

C4XAVDD

C4XAVSS

HVREF

HVREF

HVREF

HVREF

HVREF

PCREQ#

EDRDY#

DPWR#

CPUCLK

CPUCLK#

HLOCK#

DEFER#

HTRDY#

CPURST#

CPUPWRGD

BPRI#

BREQ0#

RS0#

RS1#

RS2#

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HASTB0#

HASTB1#

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HA32#

HA33#

HA34#

HA35#

SISM672MX-A1_TEBGA_847P

1

C470

0.1U_0402_16V4Z

2

Host

1

2

4

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DBI0#

DBI1#

DBI2#

DBI3#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HPCOMP

HNCOMP

C4XAVDD

C479

0.01U_0402_16V7K

C4XAVSS

3

H_D#0

N29

H_D#1

M30

H_D#2

M28

H_D#3

L30

H_D#4

L29

H_D#5

K28

H_D#6

K31

H_D#7

K30

H_D#8

H31

H_D#9

G34

H_D#10

H32

H_D#11

G32

H_D#12

K32

H_D#13

F34

H_D#14

F33

H_D#15

F32

H_D#16

H28

H_D#17

J30

H_D#18

H30

H_D#19

G29

H_D#20

J29

H_D#21

G30

H_D#22

F30

H_D#23

D33

H_D#24

D34

H_D#25

B32

H_D#26

B33

H_D#27

C34

H_D#28

D31

H_D#29

A32

H_D#30

A31

H_D#31

C31

H_D#32

B30

H_D#33

C30

H_D#34

A30

H_D#35

D28

H_D#36

G28

H_D#37

C29

H_D#38

C28

H_D#39

E28

H_D#40

E27

H_D#41

C27

H_D#42

G26

H_D#43

E26

H_D#44

D26

H_D#45

B26

H_D#46

A26

H_D#47

C26

H_D#48

G22

H_D#49

C24

H_D#50

A25

H_D#51

B24

H_D#52

C25

H_D#53

A24

H_D#54

E23

H_D#55

E25

H_D#56

G24

H_D#57

D22

H_D#58

C22

H_D#59

E22

H_D#60

C23

H_D#61

A23

H_D#62

A22

H_D#63

B22

H_DINV#0

J32

H_DINV#1

E32

H_DINV#2

F27

H_DINV#3

F23

H_DSTBN#0

H33

H_DSTBN#1

E31

H_DSTBN#2

B28

H_DSTBN#3

D24

H_DSTBP#0

H34

H_DSTBP#1

D32

H_DSTBP#2

A28

H_DSTBP#3

E24

H_PCOMP

A21

C21

R175 10_0402_5%

H_NCOMP

R188 110_0402_1%

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

H_D#[0..63] <5>

V_AVDD_PCIE_1.2V

SB_PCIE_WAKE#<21,29,30>

INT_N_A<9,19>

H_DINV#0 <5>

H_DINV#1 <5>

H_DINV#2 <5>

H_DINV#3 <5>

H_DSTBN#0 <5>

H_DSTBN#1 <5>

H_DSTBN#2 <5>

H_DSTBN#3 <5>

H_DSTBP#0 <5>

H_DSTBP#1 <5>

H_DSTBP#2 <5>

H_DSTBP#3 <5>

+1.05VS

2006/08/18 2007/8/18

3

Compal Secret Data

Deciphered Date

+1.2VS V_AVDD_PCIE_1.2V

SB_PCIE_WAKE#

INT_N_A

2

L22

1 2

MBK1608121YZF_0603

U30D

P7

PCIEAVDD

R7

PCIEAVDD

T7

PCIEAVDD

U7

PCIEAVDD

V7

PCIEAVDD

D7

PME#

G16

INTX#

E4

PERP0

E5

PERN0

F1

PERP1

G1

PERN1

H3

PERP2

H2

PERN2

H1

PERP3

J1

PERN3

K1

PERP4

PCIE

PERN4

PERP5

PERN5

PERP6

PERN6

PERP7

PERN7

PERP8

PERN8

PERP9

PERN9

PERP10

PERN10

PETN10(HDVBN1)

PERP11

PERN11

PETN11(HDVBN0)

PERP12

PERN12

PERP13

PERN13

PETN13(HDVAN2)

PERP14

PERN14

PETN14(HDVAN1)

PERP15

PERN15

PETN15(HDVAN0)

SISM672MX-A1_TEBGA_847P

HDVBP2

HDVBN2

HDVBP1

HDVBN1

HDVBP0

HDVBN0

HDVAP2

HDVAN2

HDVAP1

HDVAN1

HDVAP0

HDVAN0

AA1

AB1

AB2

AC1

AD1

AE1

AE2

AF1

AG1

K2

L1

M1

N1

N2

P1

R1

T1

T2

U1

V1

W1

W2

Y1

2

1

PCIEAVDD:77mA

1

C201

0.1U_0402_16V4Z

2

REFCLK+

REFCLK-

PETP0

PETN0

PETP1

PETN1

PETP2

PETN2

PETP3

PETN3

PETP4

PETN4

PETP5

PETN5

PETP6

PETN6

PETP7

PETN7

PETP8

PETN8

PETP9(HDVBP2)

PETN9(HDVBN2)

PETP10(HDVBP1)

PETP11(HDVBP0)

PETP12

PETN12

PETP13(HDVAP2)

PETP14(HDVAP1)

PETP15(HDVAP0)

C653 0.1U_0402_10V7K

12

C660 0.1U_0402_10V7K

12

C662 0.1U_0402_10V7K

12

C654 0.1U_0402_10V7K

12

C655 0.1U_0402_10V7K

12

C656 0.1U_0402_10V7K

12

C658 0.1U_0402_10V7K

12

C657 0.1U_0402_10V7K

12

C652 0.1U_0402_10V7K

12

C651 0.1U_0402_10V7K

12

C659 0.1U_0402_10V7K

12

C661 0.1U_0402_10V7K

12

Title

Size Document Number Rev

Custom

Date: Sheet

1

C218

0.01U_0402_16V7K

2

PCIE_CLK_NB

T5

T4

G6

H6

G4

G5

J6

K6

J4

J5

L6

M6

M4

M5

P6

R6

P4

P5

V6

W6

W4

W5

Y6

AA6

AA4

AA5

AB6

AC6

AC4

AC5

AD6

AE6

AE4

AE5

PCIE_CLK_NB#

HDVBP2

HDVBN2

HDVBP1

HDVBN1

HDVBP0

HDVBN0

HDVAP2

HDVAN2

HDVAP1

HDVAN1

HDVAP0

HDVAN0

HDVBP2_C

HDVBN2_C

HDVBP1_C

HDVBN1_C

HDVBP0_C

HDVBN0_C

HDVAP2_C

HDVAN2_C

HDVAP1_C

HDVAN1_C

HDVAP0_C

HDVAN0_C

PCIE_CLK_NB <14>

PCIE_CLK_NB# <14>

HDVBP2_C <18>

HDVBN2_C <18>

HDVBP1_C <18>

HDVBN1_C <18>

HDVBP0_C <18>

HDVBN0_C <18>

HDVAP2_C <18>

HDVAN2_C <18>

HDVAP1_C <18>

HDVAN1_C <18>

HDVAP0_C <18>

HDVAN0_C <18>

Compal Electronics, Inc.

M672MX (1/5)-HOST/PCIE

JFWXX M/B LA-3961P Schematic

1

0.1

749Thursday, Sept em be r 06, 2007

of

5

4

3

2

1

DDRA_SDQ[0..63]

DDRA_SDM[0..7]

DDRA_SMA[0..14]

D D

C C

B B

A A

DDRA_SDQ[0..63] <12,13>

DDRA_SDM[0..7] <12,13>

DDRA_SMA[0..14] <12,13>

DDRA_SDQS0<12,13>

DDRA_SDQS0#<12,13>

DDRA_SDQS1<12,13>

DDRA_SDQS1#<12,13>

DDRA_SDQS2<12,13>

DDRA_SDQS2#<12,13>

DDRA_SDQS3<12,13>

DDRA_SDQS3#<12,13>

DDRA_SDQS4<12,13>

DDRA_SDQS4#<12,13>

DDRA_SDQS5<12,13>

DDRA_SDQS5#<12,13>

DDRA_SDQS6<12,13>

DDRA_SDQS6#<12,13>

DDRA_SDQS7<12,13>

DDRA_SDQS7#<12,13>

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDM0

DDRA_SDQS0

DDRA_SDQS0#

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDM1

DDRA_SDQS1

DDRA_SDQS1#

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDM2

DDRA_SDQS2

DDRA_SDQS2#

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDM3

DDRA_SDQS3

DDRA_SDQS3#

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDM4

DDRA_SDQS4

DDRA_SDQS4#

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDM5

DDRA_SDQS5

DDRA_SDQS5#

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDM6

DDRA_SDQS6

DDRA_SDQS6#

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

DDRA_SDM7

DDRA_SDQS7

DDRA_SDQS7#

U30B

AD31

MD0A

AD30

MD1A

AG34

MD2A

AE29

MD3A

AE32

MD4A

AF34

MD5A

AF31

MD6A

AE30

MD7A

AD28

DQM0A

AF32

DQS0A

AF33

DQS0A#

AF28

MD8A

AJ34

MD9A

AH31

MD10A

AG30

MD11A

AF30

MD12A

AG32

MD13A

AJ32

MD14A

AJ31

MD15A

AH34

DQM1A

AH32

DQS1A

AH33

DQS1A#

AK34

MD16A

AH30

MD17A

AL32

MD18A

AM33

MD19A

AK32

MD20A

AG29

MD21A

AM34

MD22A

AL31

MD23A

AJ30

DQM2A

AK33

DQS2A

AL34

DQS2A#

AM32

MD24A

AP32

MD25A

AP31

MD26A

AM29

MD27A

AK30

MD28A

AK29

MD29A

AJ27

MD30A

AK28

MD31A

AN32

DQM3A

AM30

DQS3A

AM31

DQS3A#

AK20

MD32A

AM20

MD33A

AM19

MD34A

AJ19

MD35A

AN20

MD36A

AJ21

MD37A

AP19

MD38A

AH20

MD39A

AK21

DQM4A

AK19

DQS4A

AL19

DQS4A#

AK18

MD40A

AJ17

MD41A

AK17

MD42A

AP16

MD43A

AH18

MD44A

AP18

MD45A

AN18

MD46A

AP17

MD47A

AM18

DQM5A

AL17

DQS5A

AM17

DQS5A#

AN16

MD48A

AK16

MD49A

AN14

MD50A

AJ15

MD51A

AP15

MD52A

AM16

MD53A

AK15

MD54A

AP14

MD55A

AH16

DQM6A

AL15

DQS6A

AM15

DQS6A#

AL13

MD56A

AM13

MD57A

AM12

MD58A

AJ13

MD59A

AM14

MD60A

AK14

MD61A

AN12

MD62A

AH14

MD63A

AK13

DQM7A

AP12

DQS7A

AP13

DQS7A#

SISM672MX-A1_TEBGA_847P

DRAM

D1XAVDD

D1XAVSS

D4XAVDD

D4XAVSS

MA0A

MA1A

MA2A

MA3A

MA4A

MA5A

MA6A

MA7A

MA8A

MA9A

MA10A

MA11A

MA12A

MA13A

MA14A

MA15A

MA16A

MA17A

RASA#

CASA#

WEA#

FWDSDCLKOA

FWDSDCLKOA#

CS0A#

CS1A#

CS2A#

CS3A#

ODT0A

ODT1A

ODT2A

ODT3A

CKEA0

CKEA1

CKEA2

CKEA3

DDRVREF0

DDRVREF1

DDRCOMP

DDRCOMN

OCDVREFP

OCDVREFN

S3AUXSW#

A15

B15

AP11

AP10

AH24

AP25

AM25

AL25

AP26

AM26

AN26

AK25

AP27

AP28

AK24

AN24

AP24

AM28

AM27

AN28

AP21

AP29

AM23

AP22

AJ23

AK12

AH12

AP23

AH22

AM22

AM21

AK22

AP20

AN22

AL21

AN30

AP30

AH26

AK27

AD18

AD23

AJ25

AK26

AH28

AJ29

B6

D1XAVDD

D1XAVSS

D4XAVDD

D4XAVSS

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SBS0

DDRA_SBS1

DDRA_SBS2

DDRA_SMA11

DDRA_SMA12

DDRA_SMA13

DDRA_SRAS#

DDRA_SCAS#

DDRA_SWE#

CLK_INT

CLK_INC

DDRA_SCS0#

DDRA_SCS1#

DDRA_SCS2#

DDRA_SCS3#

DDRA_ODT0

DDRA_ODT1

DDRA_ODT2

DDRA_ODT3

DDRA_CKE0

DDRA_CKE1

DDRA_CKE2

DDRA_CKE3

DDRVREF

DDRCOMP

DDRCOMN

OCDVREFP

OCDVREFN

S3AUXSW#

DDRA_SBS0 <12,13>

DDRA_SBS1 <12,13>

DDRA_SBS2 <12,13>

DDRA_SRAS# <12,13>

DDRA_SCAS# <12,13>

DDRA_SWE# <12,13>

CLK_INT <15>

CLK_INC <15>

DDRA_SCS0# <12>

DDRA_SCS1# <12>

DDRA_SCS2# <13>

DDRA_SCS3# <13>

DDRA_ODT0 <12>

DDRA_ODT1 <12>

DDRA_ODT2 <13>

DDRA_ODT3 <13>

DDRA_CKE0 <12>

DDRA_CKE1 <12>

DDRA_CKE2 <13>

DDRA_CKE3 <13>

R225 36_0402_1%

R227 36_0402_1%

S3AUXSW# <31>

+1.8V

+1.8VS

1 2

MBK1608121YZF_0603

1

C456

10U_0805_10V4Z

2

R409 0_0402_5%

+1.8VS

1 2

MBK1608121YZF_0603

1

C583

10U_0805_10V4Z

2

R473 0_0402_5%

+1.8V

12

R276

1K_0402_1%

12

R501

1K_0402_1%

+1.8V +1.8V

12

R277

40.2_0402_1%

12

R224

36_0402_1%

L41

1

C480

0.1U_0402_16V4Z

1 2

L52

1 2

OCDVREFP OCDVREFN

2

1

C582

0.1U_0402_16V4Z

2

1

C251

0.1U_0402_16V4Z

2

1

C238

2

0.1U_0402_16V4Z

1

2

12

R511

36_0402_1%

12

R228

40.2_0402_1%

C233

1U_0603_10V4Z

D1XAVDD:7mA

D1XAVDD

1

C471

0.01U_0402_16V7K

2

D1XAVSS

D4XAVDD:10mA

D4XAVDD

1

C581

0.01U_0402_16V7K

2

D4XAVSSDDRA_SMA14

DDRVREF

Place C233

under M672MX

solder side.

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/08/18 2007/8/18

3

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

M672MX (2/5)-DDR

JFWXX M/B LA-3961P Schematic

849Thursday, Sept em be r 06, 2007

1

0.1

of

5

4

3

2

1

+1.8VS

L24

1 2

MBK1608121YZF_0603

1

C252

10U_0805_10V4Z

2

D D

C C

B B

A A

1 2

R231 0_0402_5%

+1.8VS

12

R232

150_0402_1%

12

R229

49.9_0402_1%

+1.8VS

1 2

MBK1608121YZF_0603

1

C467

10U_0805_10V4Z

2

1 2

R396 0_0402_5%

+1.8VS

1 2

MBK1608121YZF_0603

1

C491

10U_0805_10V4Z

2

1 2

R415 0_0402_5%

+1.8VS

1

C453

@

10U_0805_10V4Z

2

1 2

R383 0_0402_5%

L42

L45

R395

3.3_0402_5%

1

C250

0.1U_0402_16V4Z

2

1

C67

0.1U_0402_16V4Z

2

1

C249

0.1U_0402_16V4Z

2

1

2

1

2

1

2

7/24 modified

5

Z4XAVDD:10mA

1

C248

0.01U_0402_16V7K

2

Z_VREF

VGA_CRT_HSYNC<17>

VGA_CRT_VSYNC<17>

GMCH_CRT_CLK<17>

GMCH_CRT_DATA<17>

DCLKAVDD:5mA

C468

0.1U_0402_16V4Z

1

2

ECLKAVDD:5mA

C484

0.1U_0402_16V4Z

1

2

DACAVDD1:73mA

C461

@

1U_0603_10V4Z

1

2

7/30 modified to @

Z4XAVDD

Z4XAVSS

DCLKAVDD

C469

0.01U_0402_16V7K

DCLKAVSS

ECLKAVDD

C485

0.01U_0402_16V7K

ECLKAVSS

DACAVDD1

C463

@

0.1U_0402_16V4Z

DACAVSS1

VGA_CRT_HSYNC

VGA_CRT_VSYNC

GMCH_CRT_CLK

GMCH_CRT_DATA

+1.8VS

1 2

1

C174

10U_0805_10V4Z

2

1 2

R406 0_0402_5%

DACAVDD1 Spec.

Voltage : 1.5V +/- 5%

Current : 100mA

4

ZAD[0..16]<19>

+3VS

12

R178

390_0402_5%

R177

0_0402_5%

ZAD[0..16]

+1.8VS

12

R179

390_0402_5%

INT_N_A<7,19>

REF_CLK0<14>

1 2

C178 0.1U_0402_16V4Z

1 2

C177 0.1U_0402_16V4Z

DACAVDD2:73mA

1

C490

1U_0603_10V4Z

2

1 2

R174 130_0402_5%

Z_CLK0<14>

ZDREQ<19>

ZUREQ<19>

ZSTB_DP0<19>

ZSTB_DN0<19>

ZSTB_DP1<19>

ZSTB_DN1<19>

R472 56_0402_5%

1 2

R230 56_0402_5%

1 2

VGA_CRT_R<17>

VGA_CRT_G< 17>

VGA_CRT_B<17>

R184 0_0402_5%

1 2

R185 0_0402_5%

1 2

R183 0_0402_5%

1 2

R182 0_0402_5%

1 2

R196 0_0402_5%

1 2

R195 0_0402_5%

1 2

VCOMP

VVBWN

DACAVDD2

1

C483

0.1U_0402_16V4Z

2

DACAVSS2

VRSET

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Z_CLK0

ZDREQ

ZUREQ

ZSTB_DP0

ZSTB_DN0

ZSTB_DP1

ZSTB_DN1

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

Z_VREF

Z_COMP_P

Z_COMP_N

Z4XAVDD

Z4XAVSS

VGA_CRT_R

VGA_CRT_G

VGA_CRT_B

A_HSYNC

A_VSYNC

A_DDC1CLK

A_DDC1DAT

VCOMP

VVBWN

VRSET

INTA#

VOSCI

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

2006/08/18 2007/8/18

3

Compal Secret Data

U30A

AH10

ZCLK

AP8

ZDREQ

AN8

ZUREQ

AM7

ZSTB0

AL7

ZSTB0#

AP4

ZSTB1

AP5

ZSTB1#

AK10

ZAD0

AM6

ZAD1

AK11

ZAD2

AJ11

ZAD3

AP7

ZAD4

AJ9

ZAD5

AP6

ZAD6

AN6

ZAD7

AK9

ZAD8

AM4

ZAD9

AK6

ZAD10

AK8

ZAD11

AN4

ZAD12

AK7

ZAD13

AL5

ZAD14

AM5

ZAD15

AM8

ZAD16

AL9

ZVREF

AP9

ZCMP_P

AM9

ZCMP_N

AM10

Z4XAVDD

AN10

Z4XAVSS

D13

ROUT

C12

GOUT

C13

BOUT

F12

HSYNC

G12

VSYNC

D11

VGPIO0

E12

VGPIO1

D15

VCOMP

C15

VVBWN

C14

VRSET

F13

INTA#

F11

VOSCI

A12

DACAVDD1

B12

DACAVSS1

A13

DACAVDD2

B13

DACAVSS2

B10

DCLKAVDD

A11

DCLKAVSS

A9

ECLKAVDD

B8

ECLKAVSS

SISM672MX-A1_TEBGA_847P

Deciphered Date

ASL

ENTEST

TESTMODE0

TESTMODE1

TESTMODE2

TRAP0

TRAP1

TRAP2

TRAP3

TRAP4

TRAP5

TRAP6

TRAP7

TRAP8

TRAP9

TRAP10

AUXOK

PWROK

PCIRST#

AGPSTOP#

AGPBUSY#

VBVSYNC

VBHSYNC

VBHCLK

VBCLK

VBCAD

VACLK

NC0

NC1

F15

D16

E16

F16

D17

E17

F17

AC32

AD34

AB28

AD32

AD33

AE34

AC30

AC29

A5

C6

A7

G14

A6

D8

F7

E7

C8

E9

D9

AH2

AG3

2

NB_ENTEST

AUX_PWRGD

SB_PWRGD

NB_RST#

AGPSTOP#

AGPBUSY#

VBVSYNC

VBHSYNC

VBHCLK

VBCLK

VBCAD

R193 4.7K_0402_5%

1 2

AUX_PWRGD <20,31>

SB_PWRGD <20,31>

NB_RST# <18,19>

AGPSTOP# <20>

AGPBUSY# <20>

VBVSYNC <18>

VBHSYNC <18>

VBHCLK <18>

VBCLK <18>

R559 33_0402_5%

VBCAD <18>

1 2

VACLKH_VACLK

For SiS VB 307 use only

AGPBUSY#

AUX_PWRGD

SB_PWRGD

R216 4.7K_0402_5%

1 2

C180 0.1U_0402_16V4Z

1 2

C181 0.1U_0402_16V4Z

1 2

Title

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

M672MX (3/5)-ASL

JFWXX M/B LA-3961P Schematic

VACLK <18>

+3VS

1

0.1

of

949Thursday, September 06, 2007

5

U30E

4

3

2

1

+1.8V

D D

+1.8VS

C C

+1.8VS

B B

A A

+1.8VS

+1.2VS

+1.2VALW

+1.8VALW

W23

VCCM

Y23

VCCM

AA23

VCCM

AB23

VCCM

AC23

VCCM

AC18

VCCM

AC20

VCCM

AC16

VCCM

AD16

VCCM

AD17

VCCM

AD19

VCCM

AD20

VCCM

AD21

VCCM

AD22

VCCM

AJ22

VCCM

AJ24

VCCM

AL23

VCCM

AL26

VCCM

AN21

VCCM

AN23

VCCM

AN25

VCCM

AN27

VCCM

AN29

VCCM

AP3

VCC1.8

AB12

VCC1.8

AB13

VCC1.8

AC12

VCC1.8

AC13

VCC1.8

AC14

VCC1.8

AC15

VCC1.8

AH6

VCC1.8

AH7

VCC1.8

AJ4

VCC1.8

AJ5

VCC1.8

AJ6

VCC1.8

AJ7

VCC1.8

AN2

VCC1.8

AK4

VCC1.8

AK5

VCC1.8

AL1

VCC1.8

AL2

VCC1.8

AL3

VCC1.8

AL4

VCC1.8

AM1

VCC1.8

AM2

VCC1.8

AM3

VCC1.8

AN3

VCC1.8

AN5

VCC1.8

AN7

VCC1.8

AN9

VCC1.8

E8

VDDVB1.8

F9

VDDVB1.8

F8

VDDVB1.8

E10

VDD1.8

F10

VDD1.8

N19

PVDDH

N21

PVDDH

P20

PVDDH

P22

PVDDH

R21

PVDDH

T22

PVDDH

U21

PVDDH

V22

PVDDH

M11

VDDPEX

N11

VDDPEX

P11

VDDPEX

R11

VDDPEX

T11

VDDPEX

U11

VDDPEX

V11

VDDPEX

W11

VDDPEX

Y11

VDDPEX

AA11

VDDPEX

AB11

VDDPEX

B5

AUX_IVDD

C5

AUX_IVDD

D6

AUX_IVDD

G8

AUX1.8

SISM672MX-A1_TEBGA_847P

M13

IVDD

M14

IVDD

M15

IVDD

M16

IVDD

M17

IVDD

M18

IVDD

M19

IVDD

N16

IVDD

N17

IVDD

N18

IVDD

N20

IVDD

R22

IVDD

N22

IVDD

N13

IVDD

P13

IVDD

Y13

IVDD

Y22

IVDD

T13

IVDD

U13

IVDD

U22

IVDD

V13

IVDD

W13

IVDD

PWR

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

W22

AA13

AA22

AB14

AB15

AB16

AB18

AB20

AB22

AF6

AF7

AK3

AG4

AG5

AG6

AG7

R13

AH3

AH4

AH5

AJ1

AJ2

AJ3

AK1

AK2

AC22

AC21

AC19

AC17

A19

A20

B19

B20

C19

C20

D19

D20

E19

E20

F19

F20

G19

G20

L18

L19

L20

M20

M21

M22

M23

N23

P23

R23

T23

U23

V23

M12

N12

P12

R12

T12

U12

V12

W12

Y12

AA12

+1.2VS

+1.05VS

+1.8VS

+1.8V +1.2VS +1.8VALW +1.2VALW

C244 1U_0603_10V4Z

C245 1U_0603_10V4Z

C246 10U_0805_10V4Z

PVDDH/VCC1.8/VTTP/VDD1.8

+1.8VS +1.2VS

/VDDVB1.8:392mA

C232 0.1U_0402_16V4Z

C239 1U_0603_10V4Z

C247 10U_0805_10V4Z

VCCM:644mA

1 2

1 2

1 2

1 2

1 2

1 2

IVDD:2024mA

C225 1U_0603_10V4Z

1 2

C227 1U_0603_10V4Z

1 2

C243 10U_0805_10V4Z

1 2

VDDPEX:876mA

C202 0.1U_0402_16V4Z

1 2

C195 1U_0603_10V4Z

1 2

C229 10U_0805_10V4Z

1 2

Place these Cap under M672MX solder side.

+1.8V +1.2VS

C230 0.1U_0402_16V4Z

1 2

C231 0.1U_0402_16V4Z

1 2

C235 1U_0603_10V4Z

1 2

C223 1U_0603_10V4Z

1 2

C237 4.7U_0805_10V4Z

1 2

C236 4.7U_0805_10V4Z

1 2

+1.8VS +1.2VS +1.05VS

C198 0.1U_0402_16V4Z

1 2

C221 1U_0603_10V4Z

1 2

C193 1U_0603_10V4Z

1 2

C226 0.1U_0402_16V4Z

1 2

C209 0.1U_0402_16V4Z

1 2

C213 1U_0603_10V4Z

1 2

C220 1U_0603_10V4Z

1 2

C196 4.7U_0805_10V4Z

1 2

C242 4.7U_0805_10V4Z

1 2

C197 0.1U_0402_16V4Z

1 2

C240 1U_0603_10V4Z

1 2

C234 1U_0603_10V4Z

1 2

AUX1.8:1mA AUX_IVDD:92mA

1

C187

1U_0603_10V4Z

2

+1.05VS

C204 0.1U_0402_16V4Z

1 2

C192 1U_0603_10V4Z

1 2

C176 10U_0805_10V4Z

1 2

+1.8VALW +1.2VALW

1

C190

1U_0603_10V4Z

2

C188 0.1U_0402_16V4Z

1 2

C179 1U_0603_10V4Z

1 2

C184 1U_0603_10V4Z

1 2

1

C183

1U_0603_10V4Z

2

VTT:80mA

1

C182

1U_0603_10V4Z

2

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/08/18 2007/8/18

3

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

M672MX (4/5)-POWER

JFWXX M/B LA-3961P Schematic

10 49Thursday, Sept em be r 06, 2007

1

0.1

of

5

D D

B21

B23

B25

B27

B29

B31

C10

C11

C16

C18

G10

C32

C33

D10

D12

D21

D23

D25

D27

D29

E11

E13

E14

E18

E29

E30

E33

F14

F22

F24

F26

F28

P21

T21

V21

C C

B B

4

AA16

AA17

AA18

AA19

AA20

AA21

AA31

AA33

AB3

AB4

AB5

AB7

AB29

AC2

AC3

AC31

AC33

AD2

AD3

AD4

AD5

AD7

AD29

AE3

AE31

AE33

AF2

VSS

VSS

VSS

VSSM2VSSM3VSS

M29

AF3

VSS

VSS

VSS

GND

VSSN3VSSN4VSSN5VSSN6VSSN7VSS

U30F

A3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B2

VSS

B3

VSS

B4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C1

VSS

C2

VSS

C3

VSS

C4

VSS

C9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D1

VSS

D2

VSS

D3

VSS

D4

VSS

D5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E1

VSS

E2

VSS

E3

VSS

E6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F2

VSS

F3

VSS

F4

VSS

F5

VSS

F6

VSS

VSS

VSS

VSS

VSS

VSS

G2

VSS

G3

VSS

G7

VSS

VSS

VSS

VSS

VSS

VSSH5VSS

VSSJ2VSSJ3VSSJ7VSS

VSS

VSSK3VSSK4VSSK5VSS

VSSL2VSSL3VSSL4VSSL5VSSL7VSS

J33

K29

G31

VSS

G33

VSS

VSS

H4

H29

J31

VSS

VSS

L31

L33

VSS

AF4

VSS

AF5

N14

VSS

AF29

N15

VSS

VSS

AG2

N31

VSS

VSS

AG31

VSS

VSS

N33

3

AG33

AH1

VSS

VSS

VSSP2VSSP3VSS

2

AH29

AJ8

AJ10

AJ12

AJ14

AJ16

AJ18

AJ20

AJ26

AJ28

AJ33

AK31

AL6

AL8

AL10

AL12

AL14

AL16

AL18

AL20

AL28

AL30

AL33

AN11

AN13

AN15

AN17

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T29

VSS

U2

VSS

U3

VSS

U4

VSS

U5

VSS

U6

VSS

U14

VSS

U15

VSS

U16

VSS

U17

VSS

U18

VSS

U19

VSS

U20

VSS

U31

VSS

U33

VSS

V2

VSS

V3

VSS

V4

VSS

V5

VSS

V14

VSS

V15

VSS

V16

VSS

V17

VSS

V18

VSS

V19

VSS

V20

VSS

V29

VSS

AN33

VSS

AN31

VSS

AN19

VSS

W3

VSS

W14

VSS

W15

VSS

W16

VSS

W17

VSS

W18

VSS

W19

VSS

W20

VSS

W21

VSS

W31

VSS

W33

VSS

Y2

VSS

Y3

VSS

Y4

VSS

Y5

VSS

Y7

VSS

Y14

VSS

Y15

VSS

Y16

VSS

Y17

VSS

Y18

VSS

Y19

VSS

Y20

VSS

Y21

VSS

Y29

VSS

AA2

VSS

AA3

VSS

AA14

VSS

AA15

VSS

AB17

VSS

AB19

VSS

AB21

VSS

P19

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSR3VSSR4VSSR5VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSST3VSST6VSS

VSS

VSS

VSS

VSS

VSS

VSS

T14

P14

P15

P16

P17

P18

P29

R14

R15

R16

R17

R18

R19

R20

R31

R33

T15

SISM672MX-A1_TEBGA_847P

T16

T17

T18

T19

T20

1

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/08/18 2007/8/18

3

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

M672MX (5/5)-GND

JFWXX M/B LA-3961P Schematic

11 49Thursday, Sept em be r 06, 2007

1

0.1

of

5

+1.8V +1.8V

JP35

+DIMM_VREF

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQS0#<8,13>

DDRA_SDQS0<8,13>

D D

DDRA_SDQS1#<8,13>

DDRA_SDQS1<8,13>

DDRA_SDQS2#<8,13>

DDRA_SDQS2<8,13>

EC_TX_P80_DATA<13,31>

C C

EC_RX_P80_CLK<13,31>

B B

EC_RX_P80_CLK

A A

DDRA_CKE0<8>

DDRA_SBS2<8,13>

DDRA_SBS0<8,13>

DDRA_SWE#<8,13>

DDRA_SCAS#<8,13>

DDRA_SCS1#<8>

DDRA_ODT1<8>

DDRA_SDQS4#<8,13>

DDRA_SDQS4<8,13>

R237 0_0402_5%

1 2

EC_RX_P80_CLK_R<13>

DDRA_SDQS6#<8,13>

DDRA_SDQS6<8,13>

SDATA<13,14,15,20>

SCLK<13,14,15,20>

+3VS

C285

2.2U_0603_6.3V6K

5

DDRA_SDQS0#

DDRA_SDQS0

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQS1#

DDRA_SDQS1

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQS2#

DDRA_SDQS2

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDM3

EC_TX_P80_DATA

DDRA_SDQ26

DDRA_SDQ27

DDRA_CKE0

EC_RX_P80_CLK

DDRA_SBS2

DDRA_SMA12

DDRA_SMA9

DDRA_SMA8

DDRA_SMA5

DDRA_SMA3

DDRA_SMA1

DDRA_SMA10

DDRA_SBS0

DDRA_SWE#

DDRA_SCAS#

DDRA_SCS1#

DDRA_ODT1

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQS4#

DDRA_SDQS4

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDM5

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ48

DDRA_SDQ49

EC_RX_P80_CLK_R

EC_RX_P80_CLK_R

DDRA_SDQS6#

DDRA_SDQS6

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDM7

DDRA_SDQ58

DDRA_SDQ59

SDATA

SCLK

+3VS

1

C284

0.1U_0402_16V4Z

2

DIMM0 STD H:5.2mm (BOT)

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VSS

11

DQS0#

13

DQS0

15

VSS

17

DQ2

19

DQ3

21

VSS

23

DQ8

25

DQ9

27

VSS

29

DQS1#

31

DQS1

33

VSS

35

DQ10

37

DQ11

39

VSS

41

VSS

43

DQ16

45

DQ17

47

VSS

49

DQS2#

51

DQS2

53

VSS

55

DQ18

57

DQ19

59

VSS

61

DQ24

63

DQ25

65

VSS

67

DM3

69

NC

71

VSS

73

DQ26

75

DQ27

77

VSS

79

CKE0

81

VDD

83

NC

85

BA2

87

VDD

89

A12

91

A9

93

A8

95

VDD

97

A5