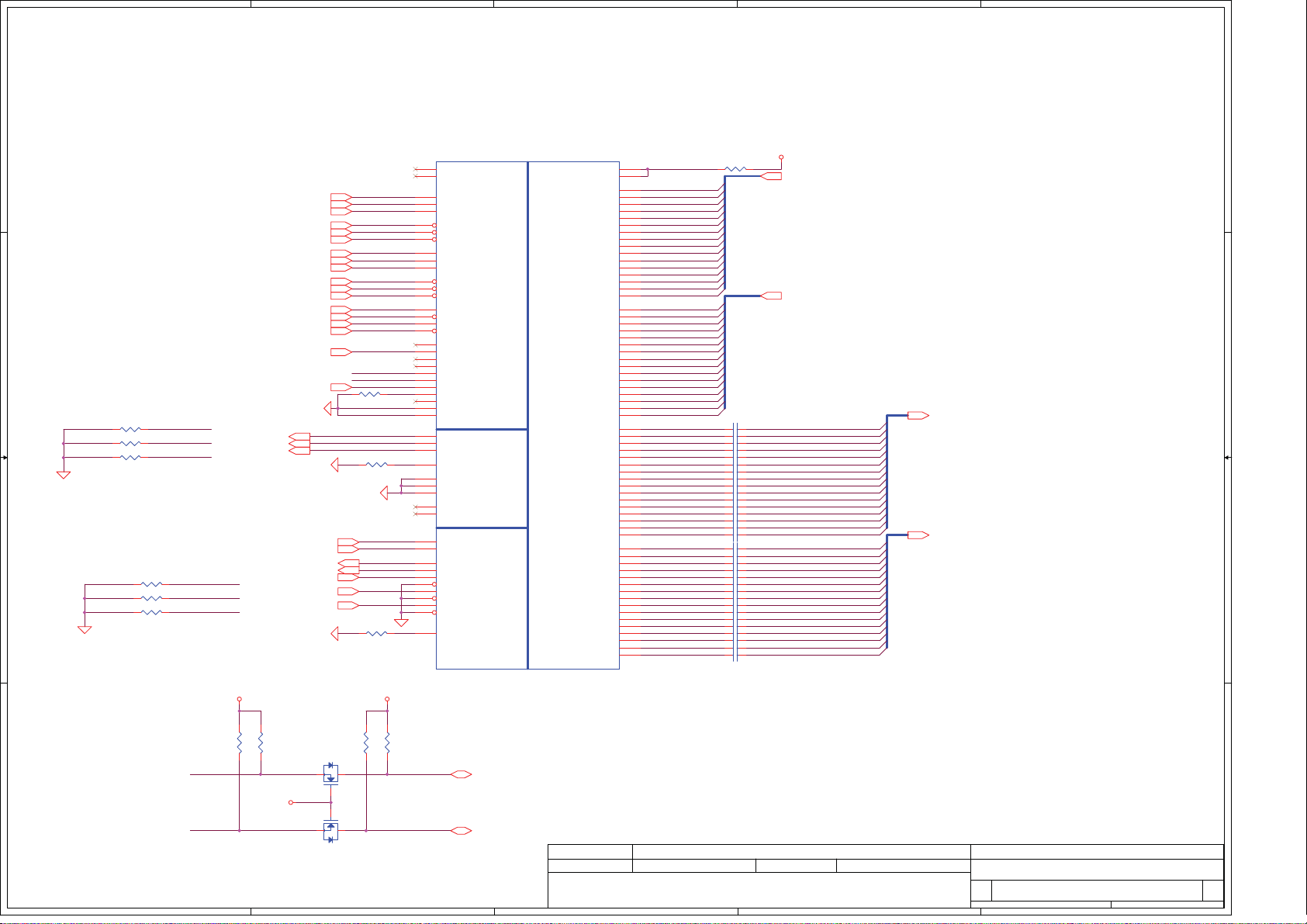

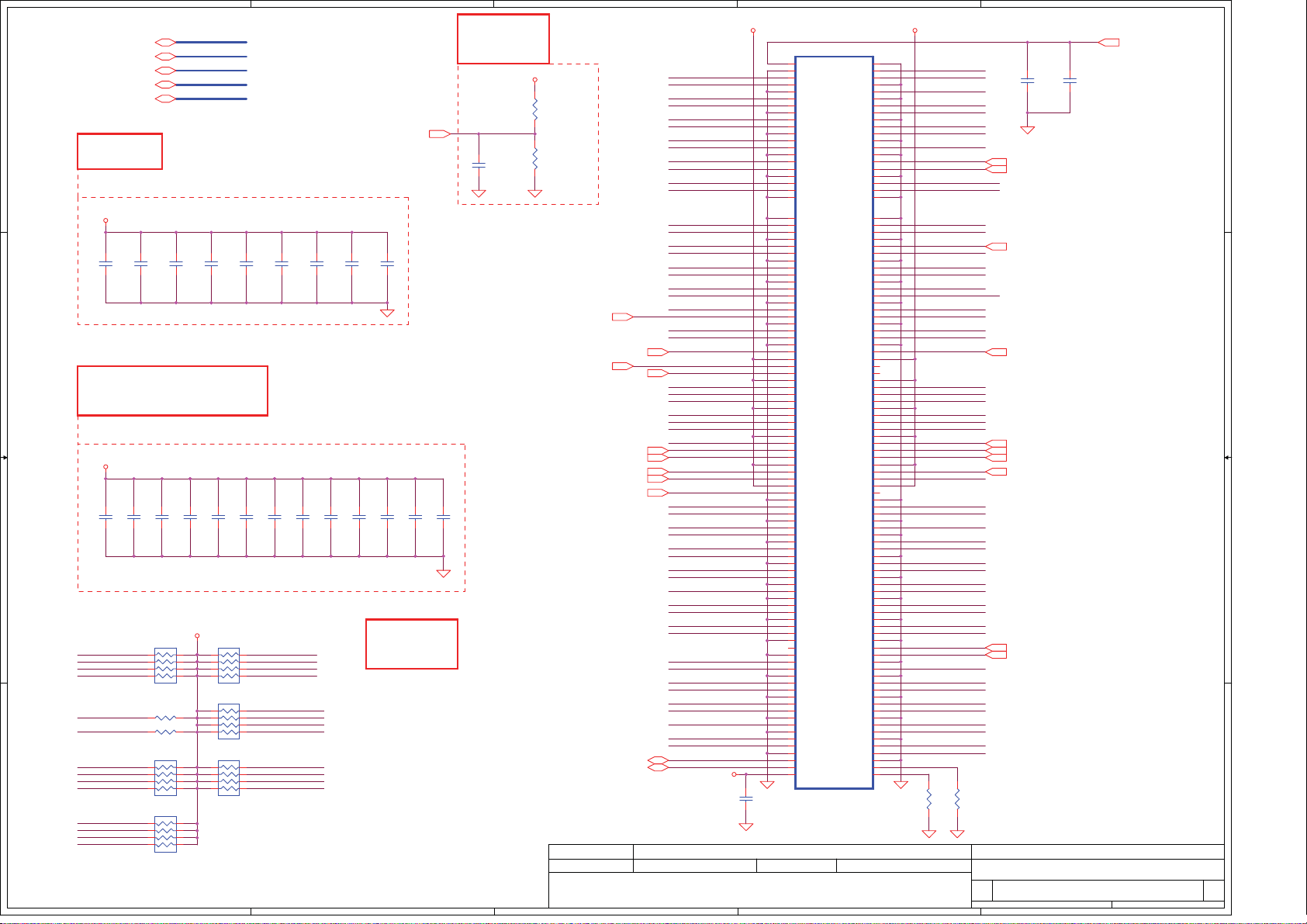

Lenovo 3000 C200 Schematics

A

星期三 七月

B

C

D

E

http://hobi-elektronika.net

1 1

2 2

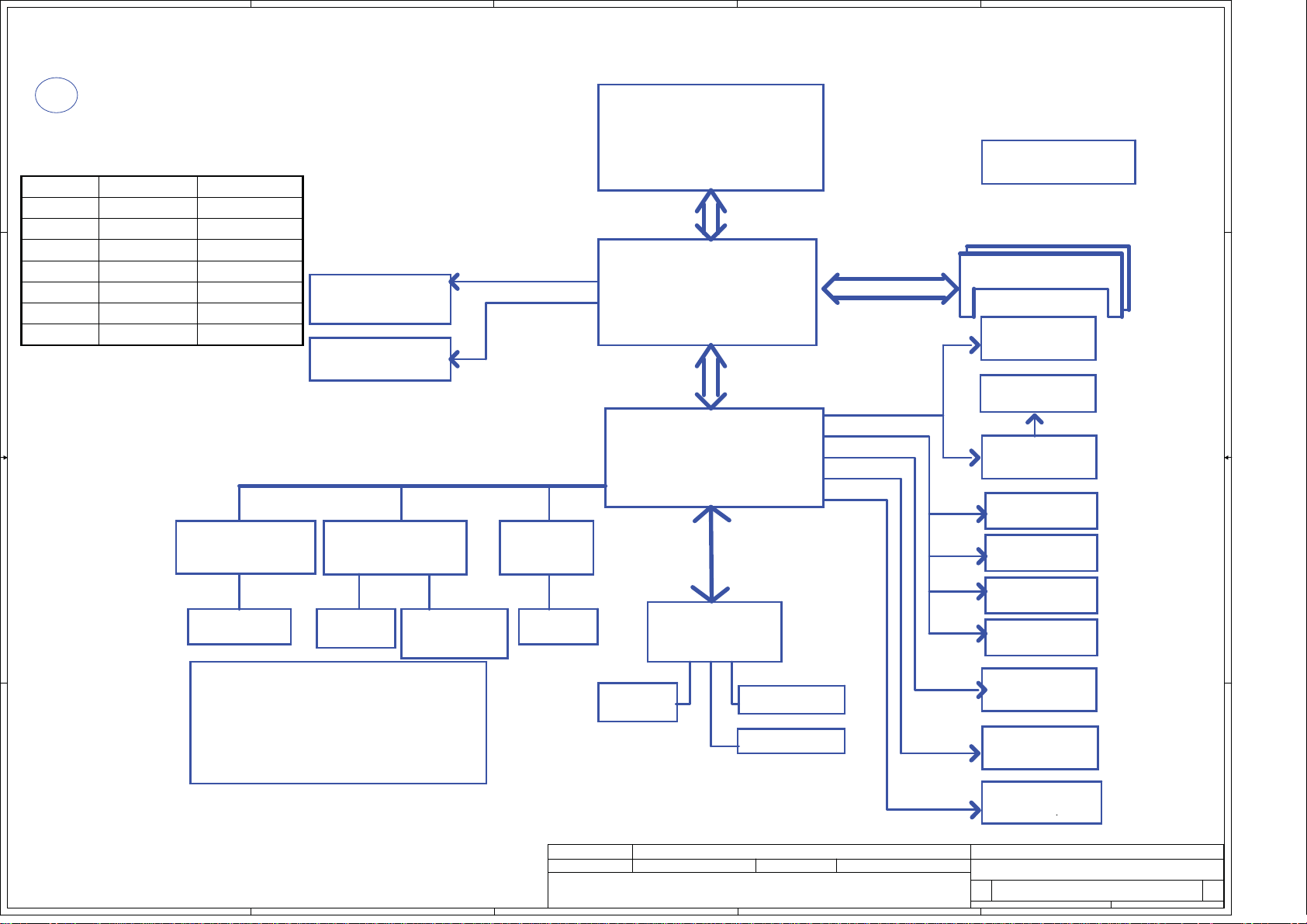

Triathlon

Schematics Document

Compal confidential

Mobile Yonah uFCPGA with Intel

3 3

Calistoga_GM/PM+ICH7-M core logic

, 12, 2

REV:0.3

006

4 4

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2005/10/06 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, M/B LA-3281

401429

E

B

of

147

A

B

C

D

E

Compal confidential

http://hobi-elektronika.net

File Name : LA-3281P

ZZZ1

14W_PCB

1 1

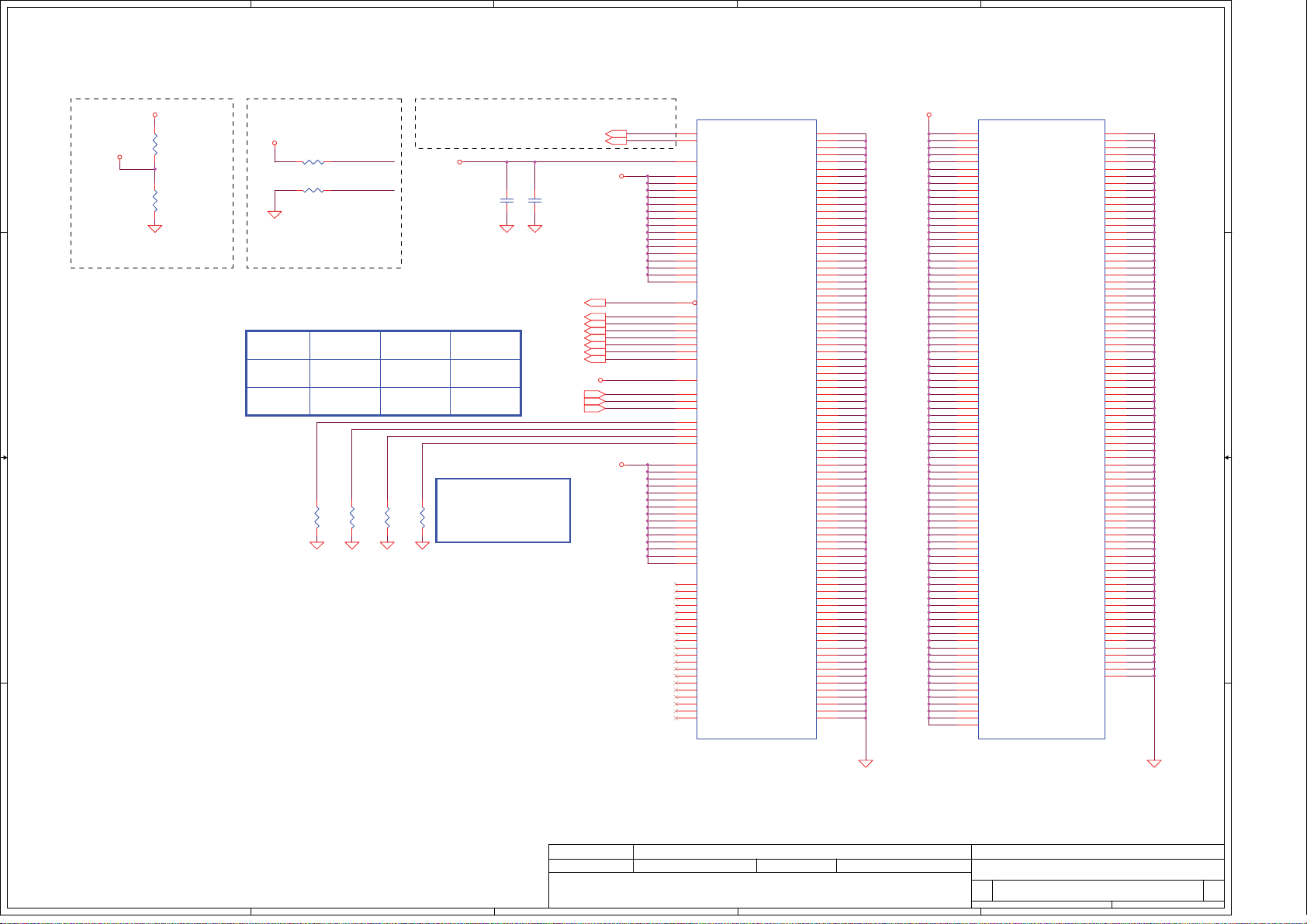

HDL20 PCB panelization Data for DVT

PCB Function

MB

Audio/USB

SW board

CRT board

TP board

FP Board

LED board

2 2

LA3281P

LS3251P

LS3102P

LS3253P

LS3104P

LS3255P

LS3256P

DVT build revisionPCB Number

0.2

0.2

1.0

0.1

1.0

0.1

CRT & TV OUT

page17

LVDS I/F

0.2

LVDS

Connector

page16

uFCBGA-479/uFCPGA-478 CPU

Intel Calistoga GMCH

Mobile Yonah

H_A#(3..31)

H_D#(0..63)

PCBGA 1466

page4,5,6

FSB

533/667MHz

page7,8,9,10,11,12

DMI

DDR2 -667

Dual Channel

Clock Gen.

ICS9LPR325AKLFT

DDR2-SO-DIMM X2

BANK 0, 1, 2, 3

page 13,14

MODEM

Ver 1.5

page 28

page15

AMP&Audio Jack

AZALIA

Intel ICH7-M

3.3V / 33 MHz

RTL8100CL

10/100M LAN

3 3

page27

1394+Card Reader

RICOH R5C832

page26

PCI BUS

CardBus

ENE CB1410

page24

mBGA-652

page19,20,21,22

LPC BUS

USB2.0

PCI-E

SATA

ATA100

Audio Codec

ALC 861VD

Finger printer

CMOS Camera

page30

page29

page36

page36

BlueTooth Conn

page28

page31

page28

page23

RJ45 CONN

page27

SUB Board

*RJ45 CONN

*RJ11 CONN

*MIC IN JACK

*HP OUT JACK

*LED

*SWITCH

page32,36

1394 Conn

page26 page25

Card reader(XD

SD/MMC/MS)

page26

*1394 CONN

*DC JACK

*TVOUT CONN

*USB CONN

*SWITCH

Slot 0

Touch Pad

page32

EC

ENE KB910L

page33

Int.KBD

BIOS

page32

page34

USB conn X4

PCI Express

Mini card Slot

SATA HDD

Connector

4 4

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2005/10/06 2006/10/06

Compal Secret Data

Deciphered Date

D

PATA CDROM

Connector

Title

Size Document Number Rev

Custom

401429

星期三 七月

Date: Sheet

page23

Compal Electronics, Inc.

SCHEMATIC, M/B LA-3281

06

247, 12, 20

E

of

B

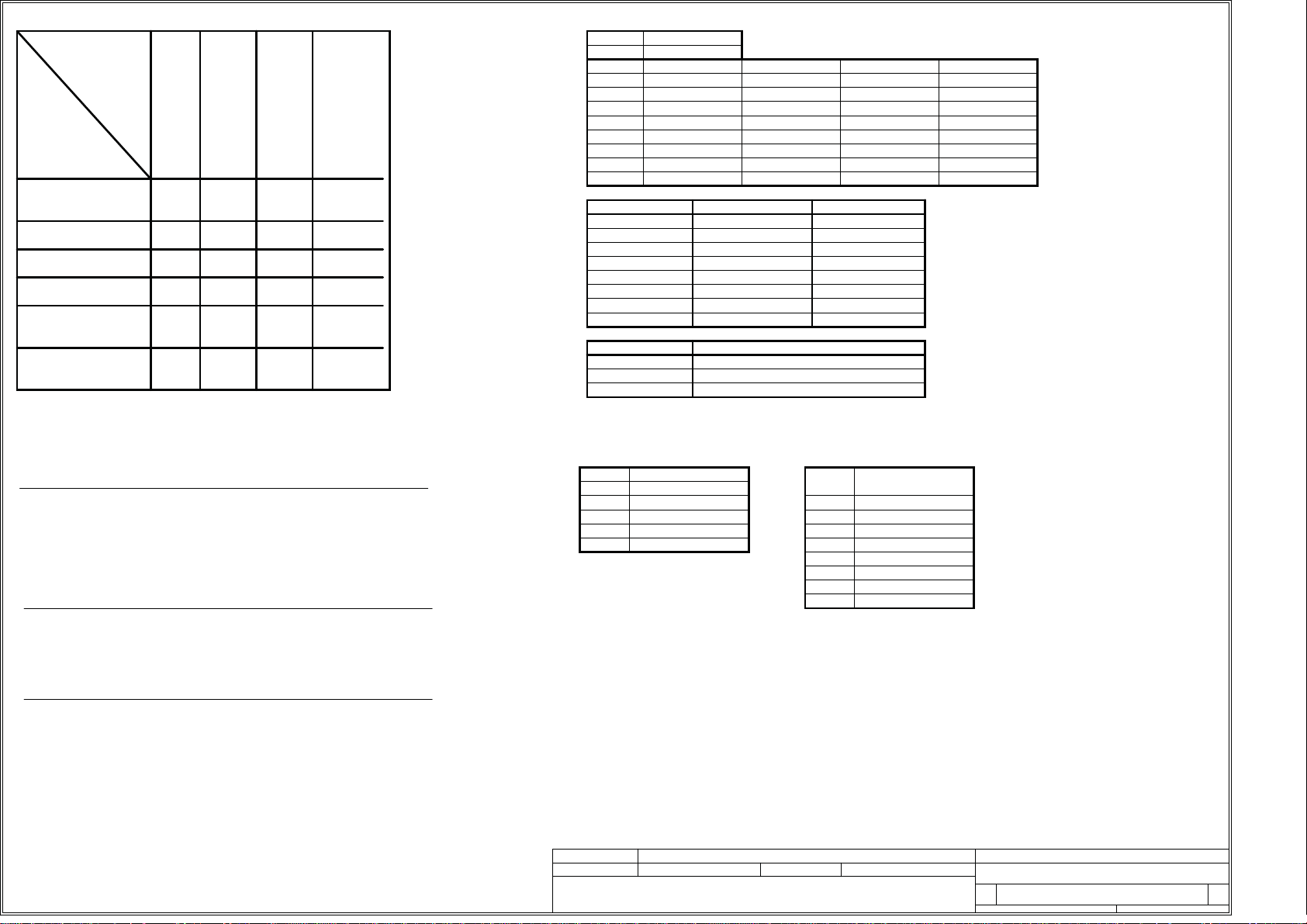

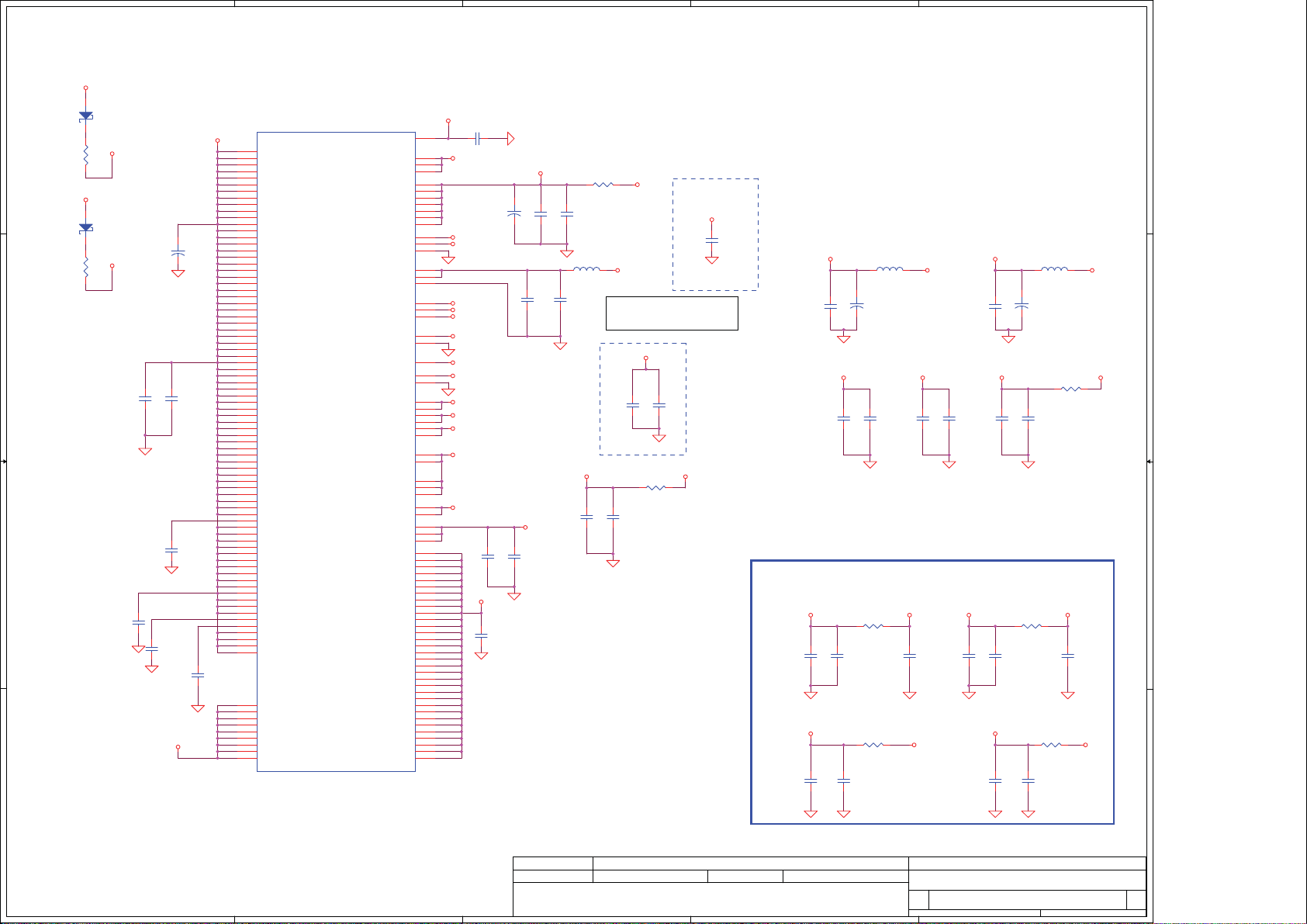

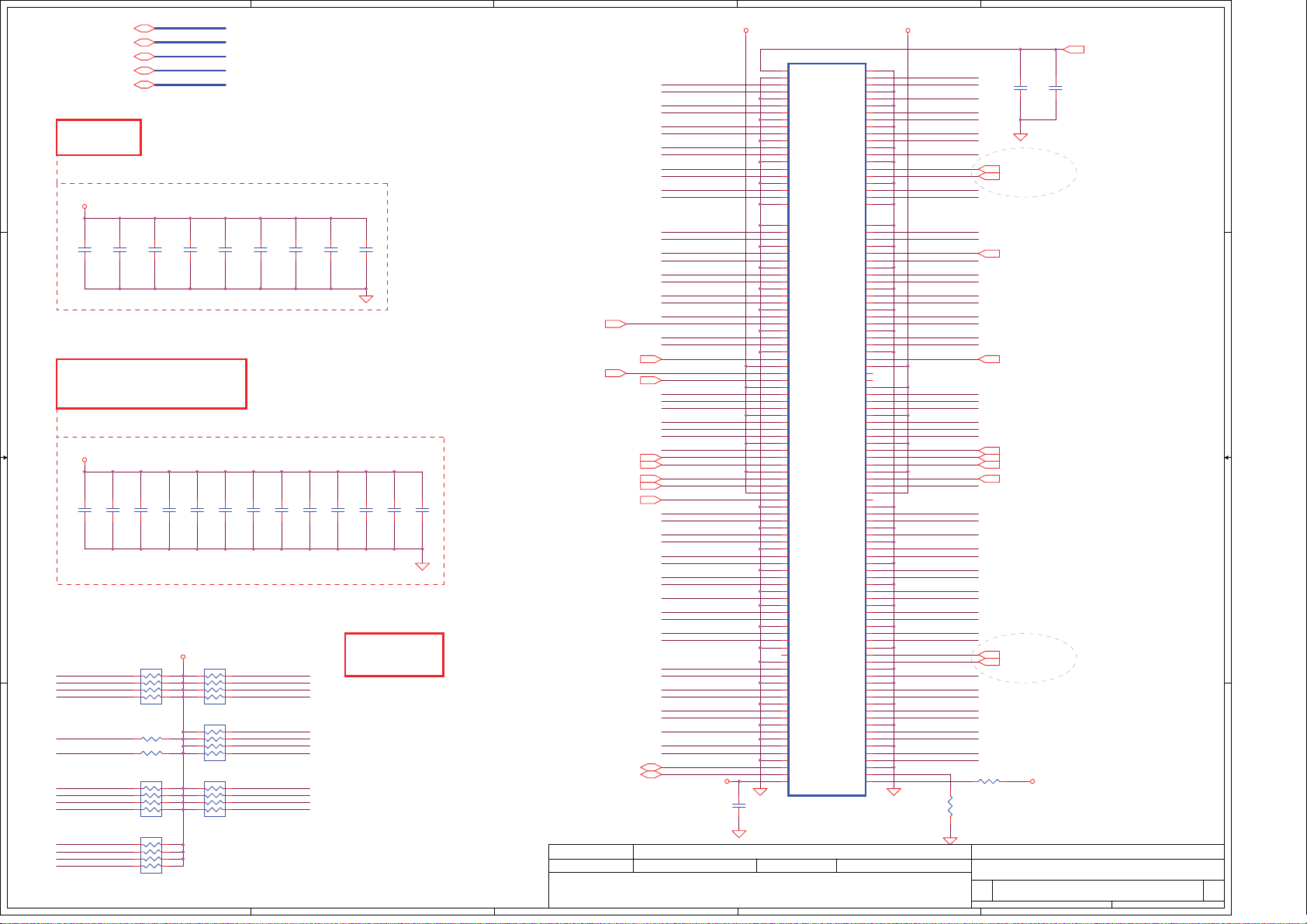

Voltage Rails

power

plane

State

S0

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

+B

LDO3

LDO5

+5VALW

+3VALW

O

O

O

O

O

O

O

O

O

X

X

XX X

+5V

O

XX

X

+5VS

+3VS

+2.5VS

+1.8VS

+1.5VS+1.8V

+1.2VS

+VGA_CORE

+0.9VS

+CPU_CORE

+VCCP

OO

OO

X

X

A

http://hobi-elektronika.net

SKU ID Table

Vcc 3.3V +/- 5%

Board ID

0

*

1

2

3

4

5

6

7 NC

SKU ID

100K +/- 5%Ra

Rb V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

MB ID(H)

0

1

2

3

4

*

5

HDL10

6

7

MB ID

H

L

15"

14"

Vtyp

AD_BID

0 V 0 V

0.503 V

0.819 V

1.185 V 1.264 V

2.200 V

3.300 V

MB ID(L)

HDL00

HDL20

HDL30IDL12

V

AD_BID

0.538 V

0.875 V

2.341 V

3.300 V

max

O MEANS ON

X MEANS OFF

S3 : STR

S4 : STD

S5 : SOFT OFF

1 1

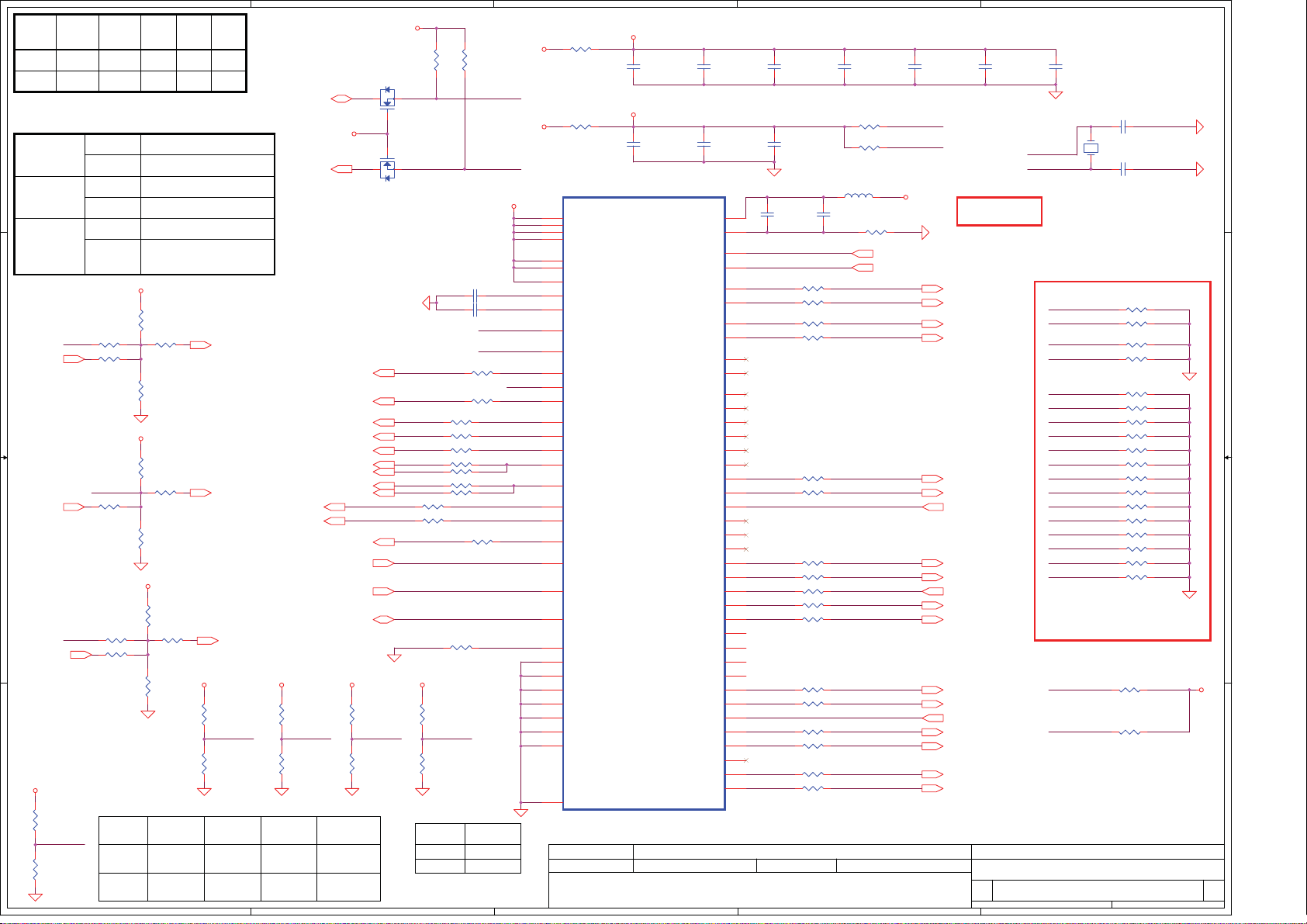

External PCI Devices

Device IDSEL # REQ # / GN T # Interrupts

1394 PIRQG/H

LAN

CardBus

AD22

AD17

AD20

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

Address

0001 011X b

1010 000X b

0

3PIRQF

2

PIRQA

EC SM Bus2 address

Device

ADM1032

Address

1001 100X b

BOM Structure USB PORT LIST

MARK FUNCTION

GIGA@

10/100@

NC FOR ALL@

8110SBL(SCL)Giga LAN

8100CL 10/100Mb LAN

UMA@

Internal 945GM

VGA@

External G7xM

PORT

0

1

2

3

4

5

6

7

DEVICE

LEFT SIDE

BT(HDL00/10)

RIGHT SIDE

CMOS

RIGHT SIDE

FINGER PRINTER

RIGHT SIDE

BT(HDL20)

ICH6 SM Bus address

Device

Clock Generator

( ICS954226)

DDRII DIMM0

DDRII DIMM1

Address

1101 001Xb

1010 000Xb

1010 010Xb

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

2005/10/06 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Re v

Custom

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, M/B LA-3281

401429

星期三 七月

of

347, 12, 2006

B

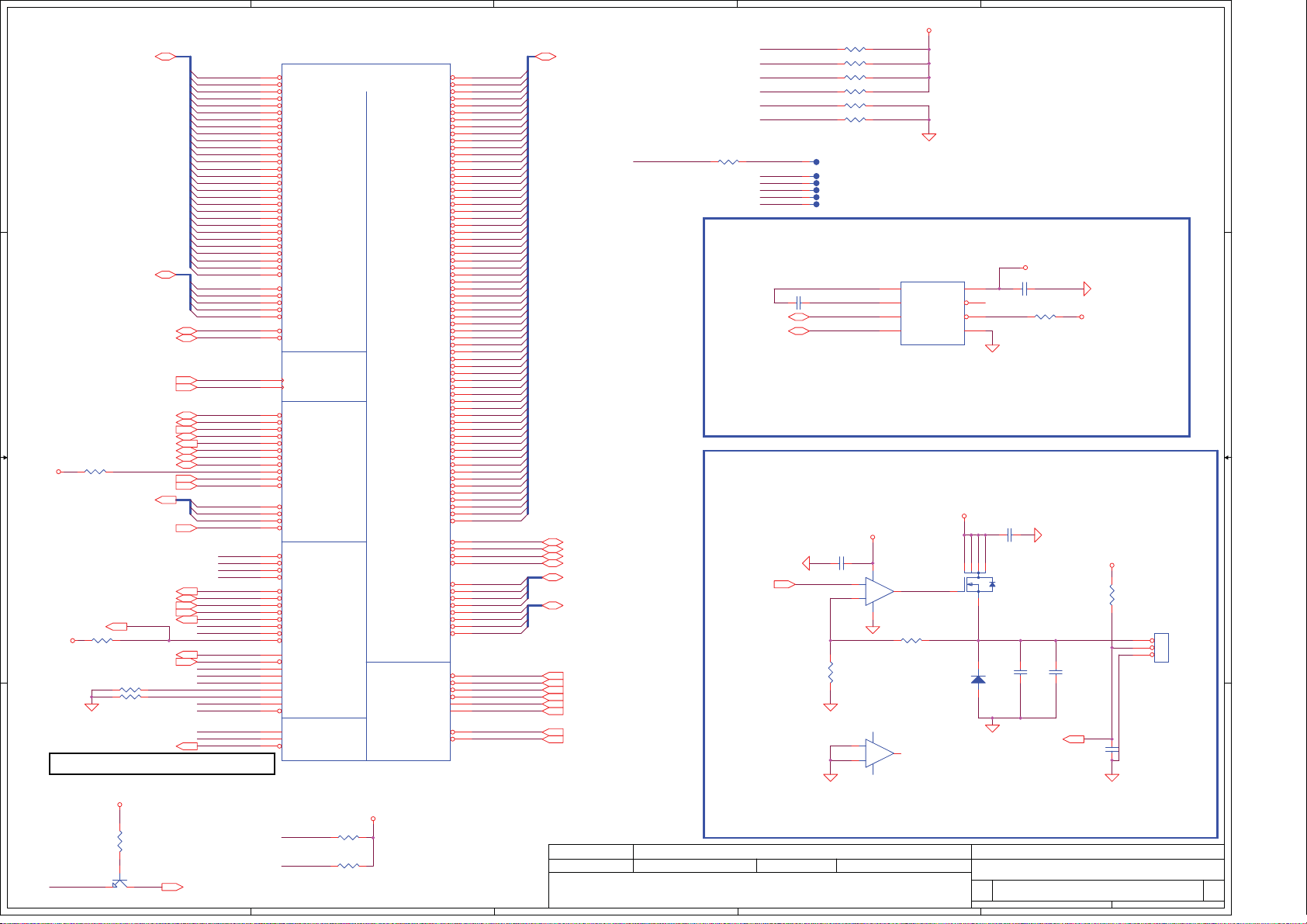

5

H_A#[3..31]<7>

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

D D

H_REQ#[0..4]<7>

H_ADSTB#0<7>

C C

R84

56_0402_5%

1 2

+VCCP

B B

H_PROCHOT#<45>

1 2

+VCCP

68_0402_5%

H_THERMDA, H_THERMDC routing together.

Trace width / Spacing = 10 / 10 mil

A A

H_PROCHOT# OCP#

H_ADSTB#1<7>

CLK_CPU_BCLK<15>

CLK_CPU_BCLK#<15>

H_ADS#<7>

H_BNR#<7>

H_BPRI#<7>

H_BR0#<7>

H_DEFER#<7>

H_DRDY#<7>

H_HIT#<7>

H_HITM#<7>

H_LOCK#<7>

H_RESET#<7>

H_RS#[0..2]<7>

H_TRDY#<7>

ITP_DBRESET#<21>

H_DBSY#<7>

H_DPSLP#<20>

H_DPRSTP#<20,45>

H_DPWR#<7>

R83

H_PWRGOOD<20>

H_CPUSLP#<7,20>

R71 1K_0402_5%@

1 2

R74 51_0402_5%

1 2

H_THERMTRIP#<7,20>

+VCCP

12

R73

56_0402_5%@

CBE

123

Q4

PMBT3904_SOT23@

5

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_DBRESET#

H_DBSY#

H_DPSLP#

H_DPRSTP#

H_DPWR#

ITP_BPM#4

ITP_BPM#5

H_PROCHOT#

H_PWRGOOD

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

H_THERMTRIP#

OCP# <21>

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

JP1A

J4

A3#

L4

A4#

M3

A5#

K5

A6#

M1

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L1

A13#

P4

A14#

P1

A15#

R1

A16#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U2

A23#

R4

A24#

T5

ADDR GROUP

A25#

T3

A26#

W3

A27#

W5

A28#

Y4

A29#

W2

A30#

Y1

A31#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L5

REQ4#

L2

ADSTB0#

V4

ADSTB1#

A22

BCLK0

A21

H1

E2

G5

F1

H5

F21

G6

E4

D20

H4

B1

F3

F4

G3

G2

AD4

AD3

AD1

AC4

C20

E1

B5

E5

D24

AC2

AC1

D21

D6

D7

AC5

AA6

AB3

C26

D25

AB5

AB6

A24

A25

C7

HOST CLK

BCLK1

ADS#

BNR#

BPRI#

BR0#

DEFER#

DRDY#

HIT#

CONTROL

HITM#

IERR#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

BPM0#

BPM1#

BPM2#

BPM3#

DBR#

DBSY#

DPSLP#

DPRSTP#

DPWR#

PRDY#

PREQ#

PROCHOT#

PWRGOOD

SLP#

TCK

TDI

TDO

TEST1

TEST2

TMS

TRST#

THERMAL

THERMDA

DIODE

THERMDC

THERMTRIP#

TYCO_1-1674770-2_Yonah~D

ME@

H_DPSLP#

H_DPRSTP#

YONAH

MISC

R100

1 2

56_0402_5%@

R99

1 2

56_0402_5%@

4

DATA GROUP

LEGACY CPU

+VCCP

4

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

3

http://hobi-elektronika.net

H_D#[0..63] <7>

H_D#0

E22

D0#

H_D#1

F24

D1#

H_D#2

E26

D2#

H_D#3

H22

D3#

H_D#4

F23

D4#

H_D#5

G25

D5#

H_D#6

E25

D6#

H_D#7

E23

D7#

H_D#8

K24

D8#

H_D#9

G24

D9#

H_D#10

J24

H_D#11

J23

H26

F26

K22

H25

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

J26

M26

V23

AC20

H23

M24

W24

AD23

G22

N25

Y25

AE24

A6

A5

C4

B3

C6

B4

D5

A3

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

H_DINV#0 <7>

H_DINV#1 <7>

H_DINV#2 <7>

H_DINV#3 <7>

H_DSTBN#[0..3] <7>

H_DSTBP#[0..3] <7>

H_A20M# <20>

H_FERR# <20>

H_IGNNE# <20>

H_INIT# <20>

H_INTR <20>

H_NMI <20>

H_STPCLK# <20>

H_SMI# <20>

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

ITP_DBRESET#

R85 200_0402_5%@

1 2

EC_SMB_CK2<33>

EC_SMB_DA2<33>

2005/10/06 2006/10/06

Compal Secret Data

ITP_TDI

ITP_TMS

ITP_TDO

ITP_BPM#5

ITP_TRST#

ITP_TCK

EN_FAN1<33>

This shall place near CPU

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

C311

1 2

Deciphered Date

2

R98 56_0402_5%

1 2

R97 56_0402_1%

1 2

R101 56_0402_5%

1 2

R103 56_0402_5%

1 2

R95 56_0402_5%

1 2

R96 56_0402_5%

1 2

T13

PAD

T17

PAD

T18

PAD

T20

PAD

T16

PAD

T19

PAD

+VSB

+IN

-IN

+IN

-IN

2

8

P

OUT

U15A

G

LM358A_SO8

4

OUT

U15B

LM358A_SO8

U16

2

D+

3

D-

8

SCLK

7

SDATA

G781F_SOP8

Address:100_1100

FAN1_ON

1

1 2

R218

100K_0402_5%

7

H_THERMDA

H_THERMDC

2200P_0402_50V7K

EC_SMB_CK2

EC_SMB_DA2

C309

12

0.1U_0603_25V7K

3

2

12

R219

150K_0402_5%

5

6

+VCCP

VDD1

ALERT#

THERM#

1N4148_SOD80

1

+3VS

1

6

4

5

GND

+5VS

6

2

1

G

3

S

4 5

12

D11

Title

Size Document Number Rev

Custom

Date: Sheet

12

C310 0.1U_0402_16V4Z

THERM#

1 2

C303

10U_1206_16V4Z

D

Q19

SI3456BDV-T1-E3_TSOP6

FAN1

1

2

FAN_SPEED1<33>

@

1000P_0402_50V7K

C307

1000P_0402_50V7K

12

+3VS

R22610K_0402_5%

+3VS

R222

10K_0402_5%

1 2

1

2

C305 10U_0805_10V4Z

C308

ACES_85205-0300

1

2

Compal Electronics, Inc.

SCHEMATIC, M/B LA-3281

401429

星期三 七月

1

447, 12, 2006

JP2

1

2

3

B

of

5

4

3

2

1

http://hobi-elektronika.net

D D

+CPU_GTLREF

Close to CPU pin AD26

within 500mils.

C C

B B

+VCCP

12

R69

1K_0402_1%

12

R62

2K_0402_1%

+CPU_CORE

R93

100_0402_1%

1 2

R94

100_0402_1%

1 2

VCCSENSE

VSSENSE

Close to CPU pin

within 500mils.

CPU_BSEL CPU_BSEL2 CPU_BSEL1

133

166

00

0

12

12

R72

R70

27.4_0402_1%

54.9_0402_1%

R102

Length match within 25 mils

The trace width 18 mils space

7 mils

+1.5VS

1

C122

C132

2

0.01U_0402_16V7K

CPU_BSEL0

1

1

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

mils away from any

other toggling signal.

12

27.4_0402_1%

1

R104

54.9_0402_1%

12

1

2

10U_0805_10V4Z

VCCSENSE<45>

VSSENSE<45>

H_PSI#<45>

CPU_VID0<45>

CPU_VID1<45>

CPU_VID2<45>

CPU_VID3<45>

CPU_VID4<45>

CPU_VID5<45>

CPU_VID6<45>

+CPU_GTLREF

CPU_BSEL0<15>

CPU_BSEL1<15>

CPU_BSEL2<15>

+CPU_CORE

+VCCP

VCCSENSE

VSSENSE

H_PSI#

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

COMP0

COMP1

COMP2

COMP3

JP1B

AF7

VCCSENSE

AE7

VSSSENSE

B26

VCCA

K6

VCCP

J6

VCCP

M6

VCCP

N6

VCCP

T6

VCCP

R6

VCCP

K21

VCCP

J21

VCCP

M21

VCCP

N21

VCCP

T21

VCCP

R21

VCCP

V21

VCCP

W21

VCCP

V6

VCCP

G21

VCCP

AE6

PSI#

AD6

VID0

AF5

VID1

AE5

VID2

AF4

VID3

AE3

VID4

AF2

VID5

AE2

VID6

AD26

GTLREF

B22

BSEL0

B23

BSEL1

C21

BSEL2

R26

COMP0

U26

COMP1

U1

COMP2

V1

COMP3

E7

VCC

AB20

VCC

AA20

VCC

AF20

VCC

AE20

VCC

AB18

VCC

AB17

VCC

AA18

VCC

AA17

VCC

AD18

VCC

AD17

VCC

AC18

VCC

AC17

VCC

AF18

VCC

AF17

VCC

D2

RSVD

F6

RSVD

D3

RSVD

C1

RSVD

AF1

RSVD

D22

RSVD

C23

RSVD

C24

RSVD

AA1

RSVD

AA4

RSVD

AB2

RSVD

AA3

RSVD

M4

RSVD

N5

RSVD

T2

RSVD

V3

RSVD

B2

RSVD

C3

RSVD

T22

RSVD

B25

RSVD

TYCO_1-1674770-2_Yonah~D

ME@

YONAH

POWER, GROUNG, RESERVED SIGNALS AND NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB26

AA25

AD25

AE26

AB23

AC24

AF24

AE23

AA22

AD22

AC21

AF21

AB19

AA19

AD19

AC19

AF19

AE19

AB16

AA16

AD16

AC16

AF16

AE16

AB13

AA14

AD13

AC14

AF13

AE14

AB11

AA11

AD11

AC11

AF11

AE11

AB8

AA8

AD8

AC8

AF8

AE8

AA5

AD5

AC6

AF6

AB4

AC3

AF3

AE4

AB1

AA2

AD2

AE1

B6

C5

F5

E6

H6

J5

M5

L6

P6

R5

V5

U6

Y6

A4

D4

E3

H3

G4

K4

L3

P3

N4

T4

U3

Y3

W4

D1

C2

F2

G1

+CPU_CORE

JP1C

AE18

VCC

AE17

VCC

AB15

VCC

AA15

VCC

AD15

VCC

AC15

VCC

AF15

VCC

AE15

VCC

AB14

VCC

AA13

VCC

AD14

VCC

AC13

VCC

AF14

VCC

AE13

VCC

AB12

VCC

AA12

VCC

AD12

VCC

AC12

VCC

AF12

VCC

AE12

VCC

AB10

VCC

AB9

VCC

AA10

VCC

AA9

VCC

AD10

VCC

AD9

VCC

AC10

VCC

AC9

VCC

AF10

VCC

AF9

VCC

AE10

VCC

AE9

VCC

AB7

VCC

AA7

VCC

AD7

VCC

AC7

VCC

B20

VCC

A20

VCC

F20

VCC

E20

VCC

B18

VCC

B17

VCC

A18

VCC

A17

VCC

D18

VCC

D17

VCC

C18

VCC

C17

VCC

F18

VCC

F17

VCC

E18

VCC

E17

VCC

B15

VCC

A15

VCC

D15

VCC

C15

VCC

F15

VCC

E15

VCC

B14

VCC

A13

VCC

D14

VCC

C13

VCC

F14

VCC

E13

VCC

B12

VCC

A12

VCC

D12

VCC

C12

VCC

F12

VCC

E12

VCC

B10

VCC

B9

VCC

A10

VCC

A9

VCC

D10

VCC

D9

VCC

C10

VCC

C9

VCC

F10

VCC

F9

VCC

E10

VCC

E9

VCC

B7

VCC

A7

VCC

F7

VCC

TYCO_1-1674770-2_Yonah~D

ME@

YONAH

POWER, GROUND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K1

J2

M2

N1

T1

R2

V2

W1

A26

D26

C25

F25

B24

A23

D23

E24

B21

C22

F22

E21

B19

A19

D19

C19

F19

E19

B16

A16

D16

C16

F16

E16

B13

A14

D13

C14

F13

E14

B11

A11

D11

C11

F11

E11

B8

A8

D8

C8

F8

E8

G26

K26

J25

M25

N26

T26

R25

V25

W26

H24

G23

K23

L24

P24

N23

T23

U24

Y24

W23

H21

J22

M22

L21

P21

R22

V22

U21

Y21

A A

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2005/10/06 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, M/B LA-3281

401429

星期三 七月

547, 12, 2006

1

B

of

5

4

3

2

1

http://hobi-elektronika.net

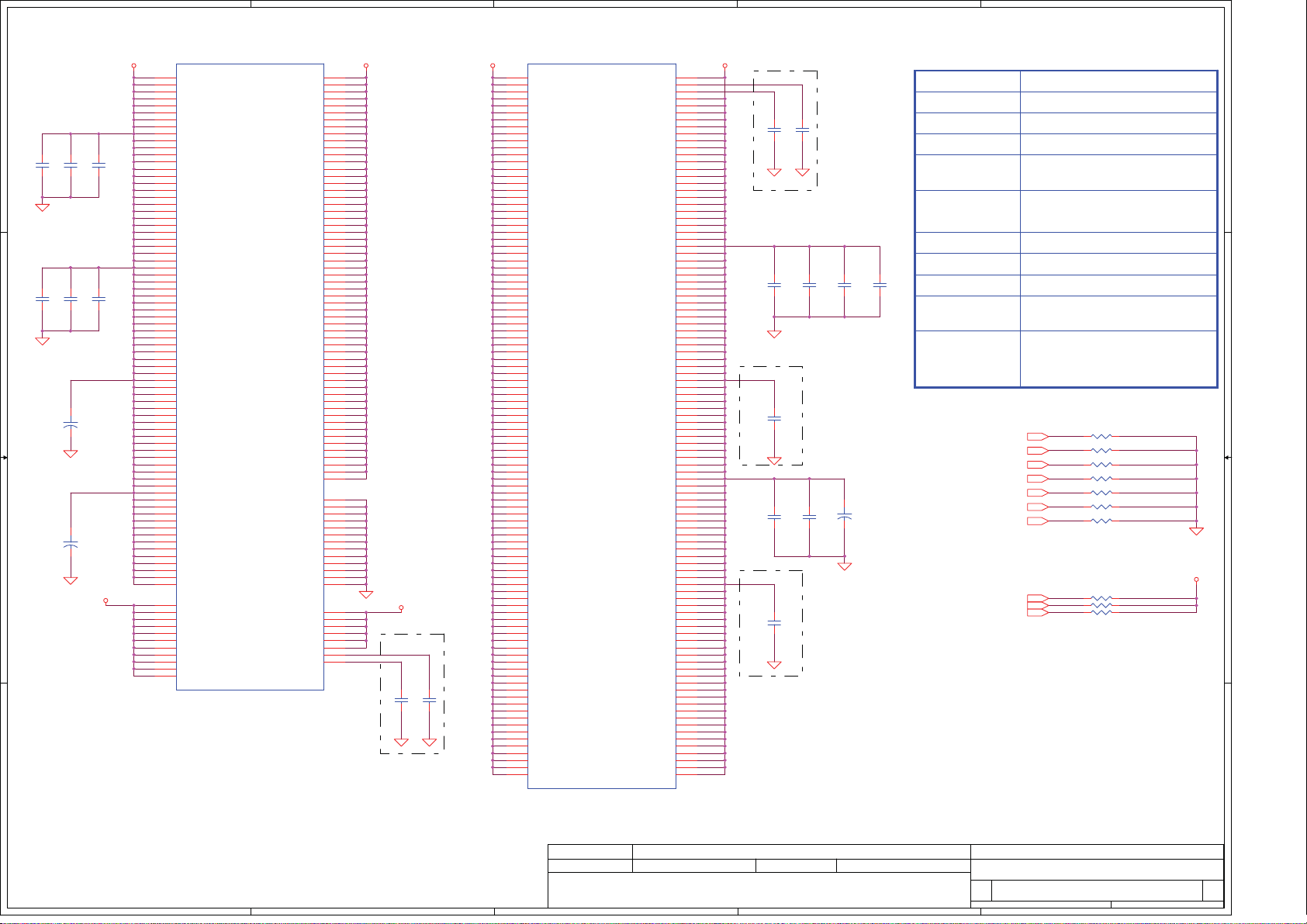

D D

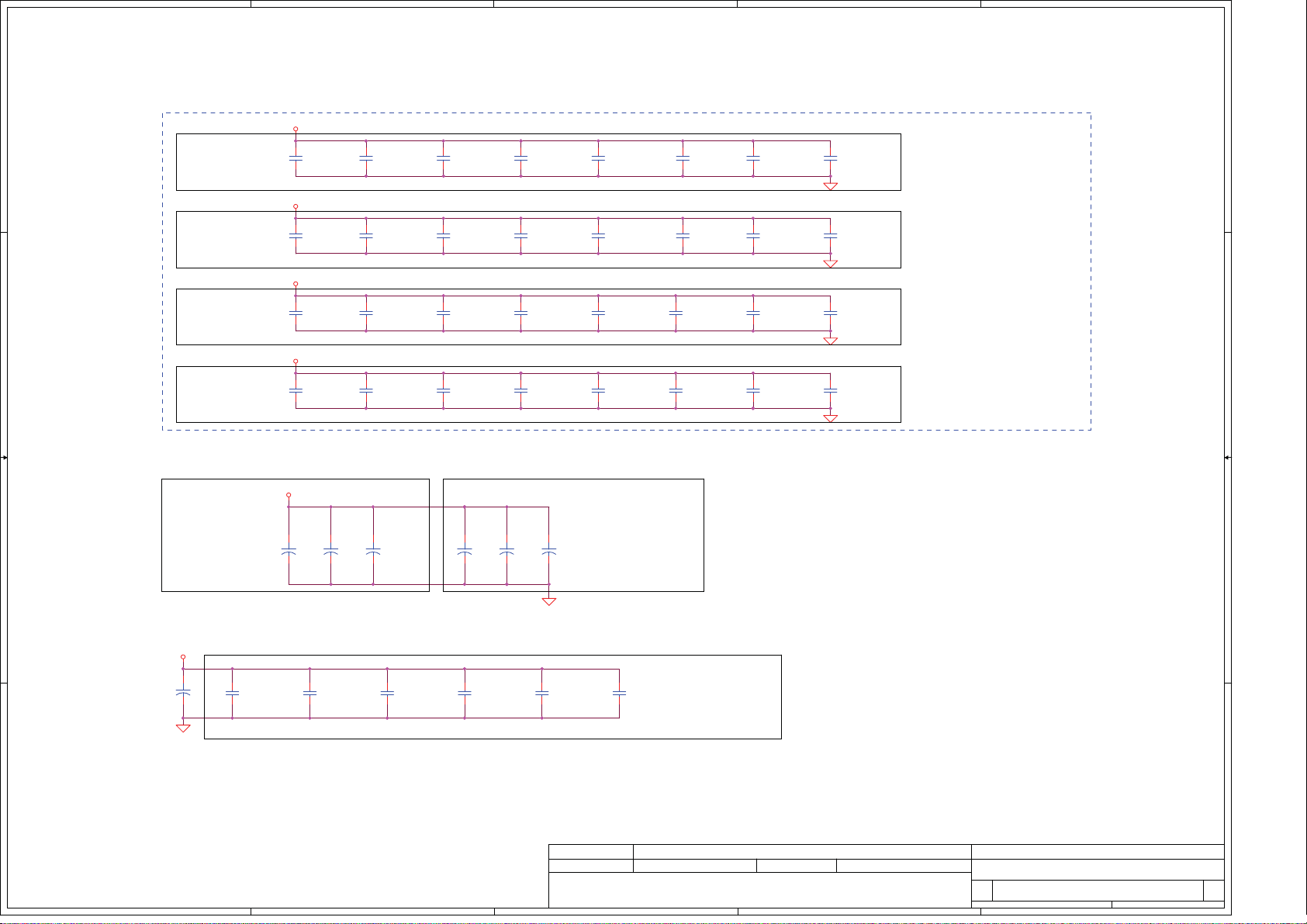

Place these capacitors on L8

(North side,Secondary Layer)

Place these capacitors on L8

(North side,Secondary Layer)

Place these capacitors on L8

(Sorth side,Secondary Layer)

C C

Place these capacitors on L8

(Sorth side,Secondary Layer)

+CPU_CORE

1

2

+CPU_CORE

1

2

+CPU_CORE

1

2

+CPU_CORE

1

2

C318

10U_0805_6.3V6M

C325

10U_0805_6.3V6M

C183

10U_0805_6.3V6M

C150

10U_0805_6.3V6M

1

C326

10U_0805_6.3V6M

2

1

C186

10U_0805_6.3V6M

2

1

C170

10U_0805_6.3V6M

2

1

C165

10U_0805_6.3V6M

2

1

C151

10U_0805_6.3V6M

2

1

C341

10U_0805_6.3V6M

2

1

C334

10U_0805_6.3V6M

2

1

C345

10U_0805_6.3V6M

2

1

C171

10U_0805_6.3V6M

2

1

C178

10U_0805_6.3V6M

2

1

C319

10U_0805_6.3V6M

2

1

C173

10U_0805_6.3V6M

2

1

C346

10U_0805_6.3V6M

2

1

C316

10U_0805_6.3V6M

2

1

C172

10U_0805_6.3V6M

2

1

C179

10U_0805_6.3V6M

2

1

C169

10U_0805_6.3V6M

2

1

C185

10U_0805_6.3V6M

2

1

C333

10U_0805_6.3V6M

2

1

C177

10U_0805_6.3V6M

2

1

C187

10U_0805_6.3V6M

2

1

C166

10U_0805_6.3V6M

2

1

C181

10U_0805_6.3V6M

2

1

C317

10U_0805_6.3V6M

2

1

C184

10U_0805_6.3V6M

2

1

C342

10U_0805_6.3V6M

2

1

C176

10U_0805_6.3V6M

2

1

C182

10U_0805_6.3V6M

2

Mid Frequence Decoupling

+CPU_CORE

ESR <= 1.5m ohm

Capacitor > 1980uF

C339

1

+

C320

2

330U_V_2.5VK_R9

330U_V_2.5VK_R9

1

1

+

+

C343

2

2

330U_V_2.5VK_R9

North Side Secondary

1

1

South Side Secondary

B B

C324

+

C180

2

330U_V_2.5VK_R9

330U_V_2.5VK_R9

1

+

+

C175

@

2

@

2

330U_V_2.5VK_R9

+VCCP

1

+

C109

220U_D2_4VM

A A

5

2

1

C190

0.1U_0402_16V4Z

2

1

C136

0.1U_0402_16V4Z

2

4

1

C138

0.1U_0402_16V4Z

2

1

C137

0.1U_0402_16V4Z

2

1

C189

0.1U_0402_16V4Z

2

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSE D TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

C188

0.1U_0402_16V4Z

2

3

Place these inside

socket cavity on L8

(North side

Secondary)

2005/10/06 2006/10/06

Compal Secret Data

Deciphered Date

2

Title

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, M/B LA-3281

401429

星期三 七月

647, 12, 2006

1

of

B

5

4

http://hobi-elektronika.net

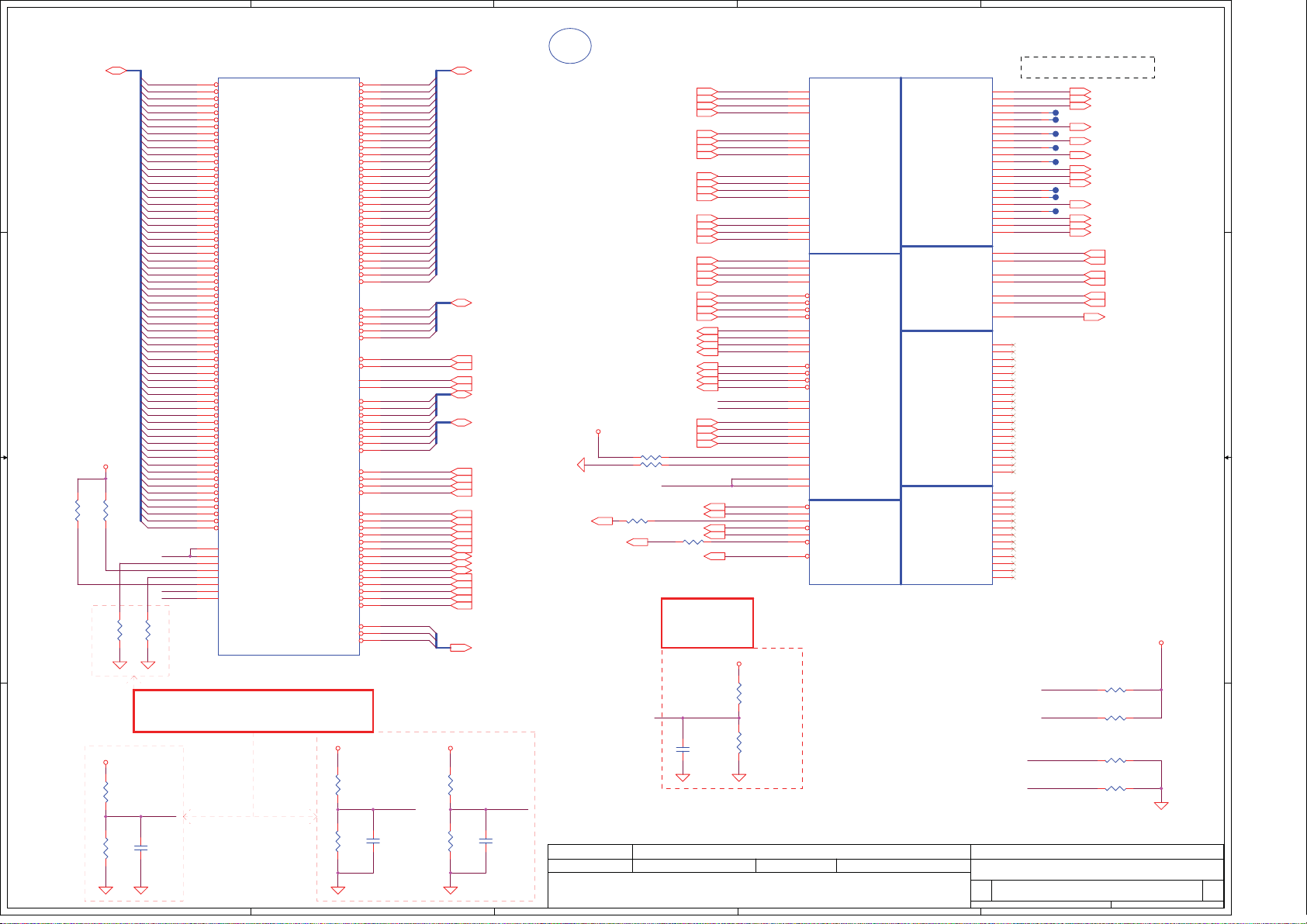

U14

3

2

1

H_D#[0..63]<4>

D D

C C

+VCCP

12

12

R26

R27

54.9_0402_1%

54.9_0402_1%

B B

12

R23

24.9_0402_1%

+VCCP

12

A A

R30

100_0402_1%

12

R36

200_0402_1%

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

+H_VREF

H_XRCOMP

H_XSCOMP

H_YRCOMP

H_YSCOMP

+H_SWNG0

+H_SWNG1

12

R20

24.9_0402_1%

Layout Note:

H_XRCOMP / H_YRCOMP / H_VREF / H_SWNG0 /

H_SWNG1 trace width and spacing is 10/20.

+H_VREF

1

C26

2

0.1U_0402_16V4Z

5

U14A

F1

HD0#

J1

HD1#

H1

HD2#

J6

HD3#

H3

HD4#

K2

HD5#

G1

HD6#

G2

HD7#

K9

HD8#

K1

HD9#

K7

HD10#

J8

HD11#

H4

HD12#

J3

HD13#

K11

HD14#

G4

HD15#

T10

HD16#

W11

HD17#

T3

HD18#

U7

HD19#

U9

HD20#

U11

HD21#

T11

HD22#

W9

HD23#

T1

HD24#

T8

HD25#

T4

HD26#

W7

HD27#

U5

HD28#

T9

HD29#

W6

HD30#

T5

HD31#

AB7

HD32#

AA9

HD33#

W4

HD34#

W3

HD35#

Y3

HD36#

Y7

HD37#

W5

HD38#

Y10

HD39#

AB8

HD40#

W2

HD41#

AA4

HD42#

AA7

HD43#

AA2

HD44#

AA6

HD45#

AA10

HD46#

Y8

HD47#

AA1

HD48#

AB4

HD49#

AC9

HD50#

AB11

HD51#

AC11

HD52#

AB3

HD53#

AC2

HD54#

AD1

HD55#

AD9

HD56#

AC1

HD57#

AD7

HD58#

AC6

HD59#

AB5

HD60#

AD10

HD61#

AD4

HD62#

AC8

HD63#

J13

HVREF0

K13

HVREF1

E1

HXRCOMP

E2

HXSCOMP

Y1

HYRCOMP

U1

HYSCOMP

E4

HXSWING

W1

HYSWING

CALISTOGA_FCBGA1466~D

UMA@

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HADSTB#0

HADSTB#1

HOST

HCLKN

HCLKP

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HCPURST#

HADS#

HTRDY#

HDPWR#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HCPUSLP#

HRS0#

HRS1#

HRS2#

12

R22

221_0603_1%

12

R24

100_0402_1%

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

D8

G8

B8

F8

A8

B9

C13

AG1

AG2

K4

T7

Y5

AC4

K3

T6

AA5

AC5

J7

W8

U3

AB10

B7

E8

E7

J9

H8

C3

D4

D3

B3

C7

C6

F6

A7

E3

B4

E6

D6

+H_SWNG0

1

2

4

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_MCH_BCLK#

CLK_MCH_BCLK

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_RESET#

H_ADS#

H_TRDY#

H_DPWR#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_CPUSLP#

H_RS#0

H_RS#1

H_RS#2

C19

0.1U_0402_16V4Z

+VCCP+VCCP

12

R18

221_0603_1%

12

R19

100_0402_1%

H_A#[3..31] <4>

H_REQ#[0..4] <4>

H_ADSTB#0 <4>

H_ADSTB#1 <4>

CLK_MCH_BCLK# <15>

CLK_MCH_BCLK <15>

H_DSTBN#[0..3] <4>

H_DSTBP#[0..3] <4>

H_DINV#0 <4>

H_DINV#1 <4>

H_DINV#2 <4>

H_DINV#3 <4>

H_RESET# <4>

H_ADS# <4>

H_TRDY# <4>

H_DPWR# <4>

H_DRDY# <4>

H_DEFER# <4>

H_HITM# <4>

H_HIT# <4>

H_LOCK# <4>

H_BR0# <4>

H_BNR# <4>

H_BPRI# <4>

H_DBSY# <4>

H_CPUSLP# <4,20>

H_RS#[0..2] <4>

+H_SWNG1

1

2

0.1U_0402_16V4Z

PM

VGA@

DMI_TXN0<21>

DMI_TXN1<21>

DMI_TXN2<21>

DMI_TXN3<21>

DMI_TXP0<21>

DMI_TXP1<21>

DMI_TXP2<21>

DMI_TXP3<21>

DMI_RXN0<21>

DMI_RXN1<21>

DMI_RXN2<21>

DMI_RXN3<21>

DMI_RXP0<21>

DMI_RXP1<21>

DMI_RXP2<21>

DMI_RXP3<21>

M_CLK_DDR0<13>

M_CLK_DDR1<13>

M_CLK_DDR2<14>

M_CLK_DDR3<14>

M_CLK_DDR#0<13>

M_CLK_DDR#1<13>

M_CLK_DDR#2<14>

M_CLK_DDR#3<14>

DDR_CKE0_DIMMA<13>

DDR_CKE1_DIMMA<13>

DDR_CKE2_DIMMB<14>

DDR_CKE3_DIMMB<14>

DDR_CS0_DIMMA#<13>

DDR_CS1_DIMMA#<13>

DDR_CS2_DIMMB#<14>

DDR_CS3_DIMMB#<14>

+1.8V

R29 80.6_0402_1%

R28 80.6_0402_1%

R88

DPRSLPVR<21,45>

C11

0_0402_5%

PLT_RST#<19,23,28>

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

M_ODT0<13>

M_ODT1<13>

M_ODT2<14>

M_ODT3<14>

1 2

1 2

+DDR_MCH_REF

PM_BMBUSY#<21>

PM_EXTTS#0<13,14>

12

H_THERMTRIP#<4,20>

ICH_POK<21,33>

R55 100_0402_1%

MCH_ICH_SYNC#<19>

Layout Note:

+DDR_MCH_REF

trace width and

spacing is 20/20.

+DDR_MCH_REF PM_EXTTS#1

C16

0.1U_0402_16V4Z

2005/10/06 2006/10/06

1

2

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR2

M_CLK_DDR3

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_OCDOCMP0

M_OCDOCMP1

M_ODT0

M_ODT1

M_ODT2

M_ODT3

SMRCOMPN

SMRCOMPP

PM_BMBUSY#

PM_E XTTS#0

PM_E XTTS#1

H_THERMTRIP#

ICH_POK

PLTRST_R#

12

+1.8V

12

R25

12

R21

Compal Secret Data

100_0402_1%

100_0402_1%

U14B

AE35

DMIRXN0

AF39

DMIRXN1

AG35

DMIRXN2

AH39

DMIRXN3

AC35

DMIRXP0

AE39

DMIRXP1

AF35

DMIRXP2

AG39

DMIRXP3

AE37

DMITXN0

AF41

DMITXN1

AG37

DMITXN2

AH41

DMITXN3

AC37

DMITXP0

AE41

DMITXP1

AF37

DMITXP2

AG41

DMITXP3

AY35

SM_CK0

AR1

SM_CK1

AW7

SM_CK2

AW40

SM_CK3

AW35

SM_CK0#

AT1

SM_CK1#

AY7

SM_CK2#

AY40

SM_CK3#

AU20

SM_CKE0

AT20

SM_CKE1

BA29

SM_CKE2

AY29

SM_CKE3

AW13

SM_CS0#

AW12

SM_CS1#

AY21

SM_CS2#

AW21

SM_CS3#

AL20

SM_OCDCOMP0

AF10

SM_OCDCOMP1

BA13

SM_ODT0

BA12

SM_ODT1

AY20

SM_ODT2

AU21

SM_ODT3

AV9

SM_RCOMPN

AT9

SM_RCOMPP

AK1

SM_VREF0

AK41

SM_VREF1

G28

PM_BMBUSY#

F25

PM_EXTTS0#

H26

PM_EXTTS1#

G6

PM_THERMTRIP#

AH33

PWROK

AH34

RSTIN#

K28

ICH_SYNC#

CALISTOGA_FCBGA1466~D

UMA@

Deciphered Date

DMI

2

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG

CFG17

CFG18

CFG19

CFG20

G_CLKP

G_CLKN

D_REF_CLKN

D_REF_CLKP

CLKNC

D_REF_SSCLKN

D_REF_SSCLKP

DDR MUXING

PM

CLK_REQ#

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

RESERVED7

RESERVED8

RESERVED9

RESERVED10

RESERVED11

RESERVED12

RESERVED13

RESERVED

Title

Size Document Number Rev

Custom

Date: Sheet

Description at page15.

MCH_CLKSEL0

K16

MCH_CLKSEL1

K18

MCH_CLKSEL2

J18

CFG3

F18

CFG4

E15

CFG5

F15

CFG6

E18

CFG7

D19

CFG8

D16

CFG9

G16

CFG10

E16

CFG11

D15

CFG12

G15

CFG13

K15

CFG14

C15

CFG15

H16

CFG16

G18

CFG17

H15

CFG18

J25

CFG19

K27

CFG20

J26

CLK_MCH_3GPLL

AG33

CLK_MCH_3GPLL#

AF33

CLK_MCH_DREFCLK#

A27

CLK_MCH_DREFCLK

A26

MCH_SSCDREFCLK#

C40

MCH_SSCDREFCLK

D41

MCH_CLKREQ#

H32

A3

A39

A4

A40

AW1

AW41

AY1

BA1

BA2

BA3

BA39

BA40

BA41

C1

AY41

B2

B41

C41

D1

T32

R32

F3

F7

AG11

AF11

H7

J19

A41

A34

D28

D27

A35

M_OCDOCMP0

M_OCDOCMP1

PM_EXTTS#0

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

MCH_CLKSEL0 <15>

MCH_CLKSEL1 <15>

MCH_CLKSEL2 <15>

T9

T3

CFG5 <11>

T10

CFG7 <11>

T7

CFG9 <11>

T5

CFG11 <11>

CFG12 <11>

CFG13 <11>

T2

T8

CFG16 <11>

T1

CFG18 <11>

CFG19 <11>

CFG20 <11>

MCH_CLKREQ# <15>

R46

10K_0402_5%

R49

10K_0402_5%@

R45

40.2_0402_1%@

R31

40.2_0402_1%@

Compal Electronics, Inc.

SCHEMATIC, M/B LA-3281

401429

星期三 七月

06

1

CLK_MCH_3GPLL <15>

CLK_MCH_3GPLL# <15>

CLK_MCH_DREFCLK# <15>

CLK_MCH_DREFCLK <15>

CLK_MCH_SSCDREFCLK# <15>

CLK_MCH_SSCDREFCLK <15>

+3VS

12

12

12

12

of

747, 12, 20

B

5

4

3

2

1

http://hobi-elektronika.net

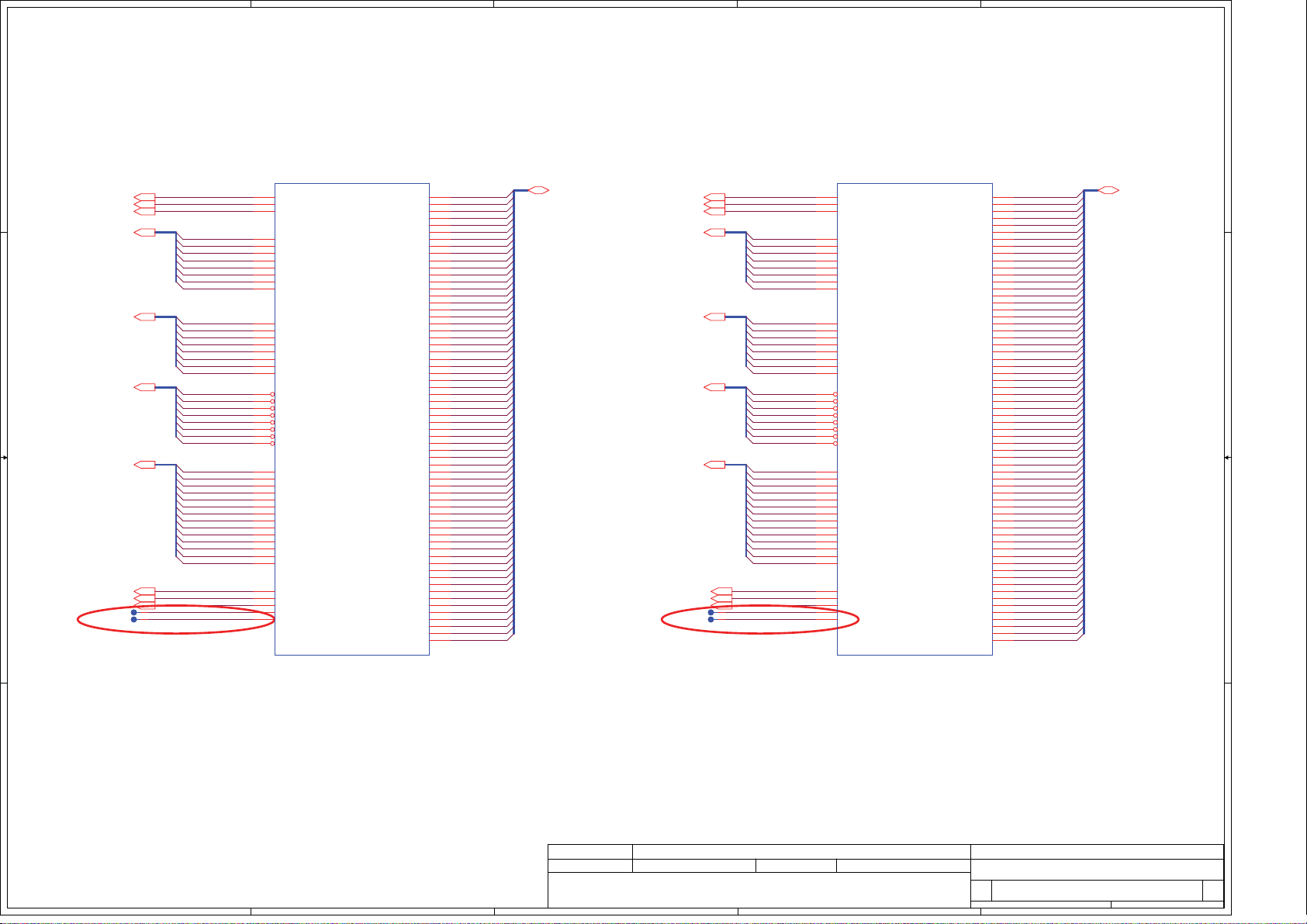

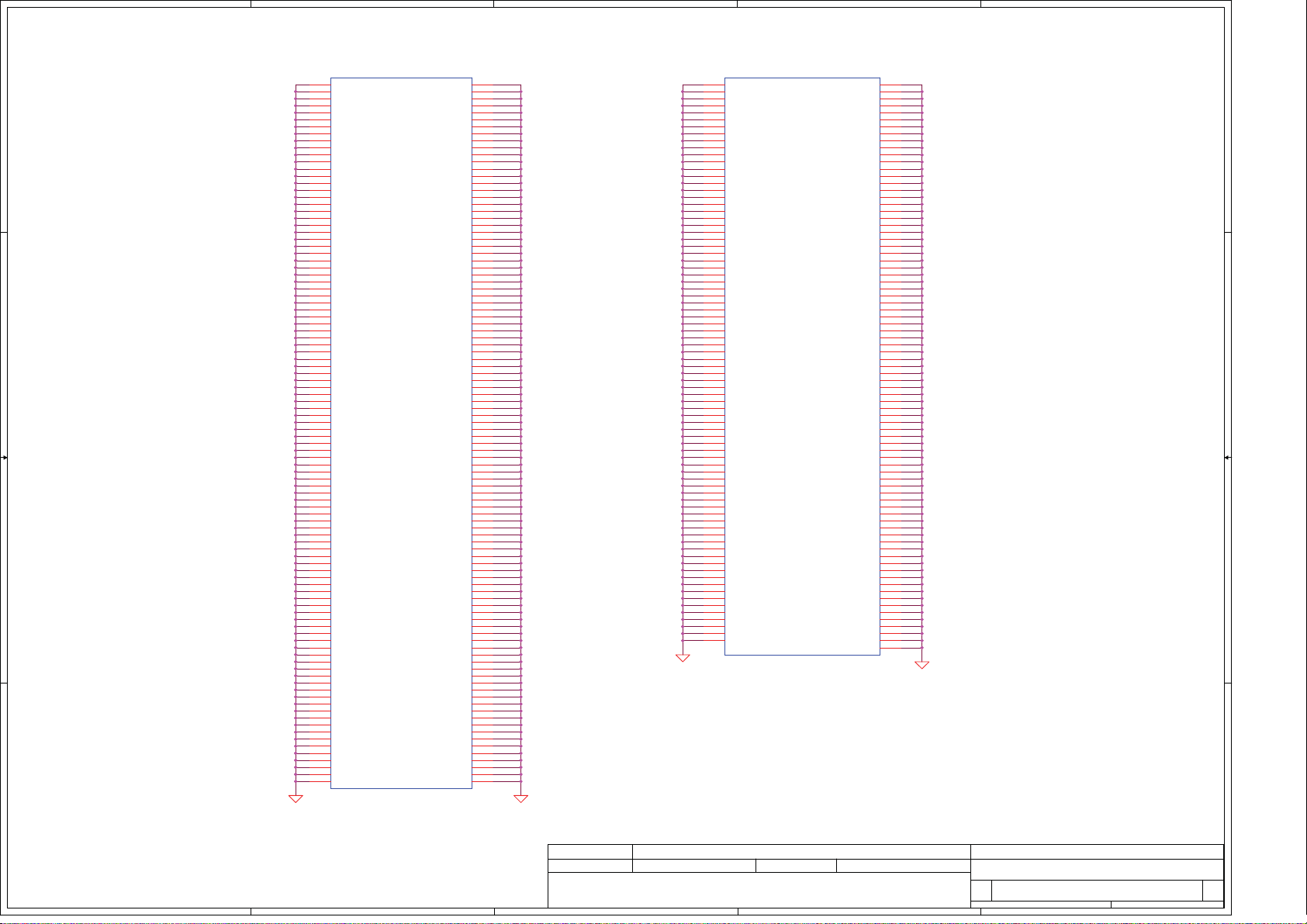

D D

DDR_A_BS#0<13>

DDR_A_BS#1<13>

DDR_A_BS#2<13>

DDR_A_DM[0..7]<13>

DDR_A_DQS[0..7]<13>

C C

DDR_A_DQS#[0..7]<13>

DDR_A_MA[0..13]<13>

B B

DDR_A_CAS#<13>

DDR_A_RAS#<13>

DDR_A_WE#<13>

T6 P AD

T12 PAD

DDR_A_BS#0

DDR_A_BS#1

DDR_A_BS#2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11 DDR_B_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

SA_RCVENIN#

SA_RCVENOUT#

check layout check layout

U14D

AU12

SA_BS0

AV14

SA_BS1

BA20

SA_BS2

AJ33

SA_DM0

AM35

SA_DM1

AL26

SA_DM2

AN22

SA_DM3

AM14

SA_DM4

AL9

SA_DM5

AR3

SA_DM6

AH4

SA_DM7

AK33

SA_DQS0

AT33

SA_DQS1

AN28

SA_DQS2

AM22

SA_DQS3

AN12

SA_DQS4

AN8

SA_DQS5

AP3

SA_DQS6

AG5

SA_DQS7

AK32

SA_DQS0#

AU33

SA_DQS1#

AN27

SA_DQS2#

AM21

SA_DQS3#

AM12

SA_DQS4#

AL8

SA_DQS5#

AN3

SA_DQS6#

AH5

SA_DQS7#

AY16

SA_MA0

AU14

SA_MA1

AW16

SA_MA2

BA16

SA_MA3

BA17

SA_MA4

AU16

SA_MA5

AV17

SA_MA6

AU17

SA_MA7

AW17

SA_MA8

AT16

SA_MA9

AU13

SA_MA10

AT17

SA_MA11

AV20

SA_MA12

AV12

SA_MA13

AY13

SA_CAS#

AW14

SA_RAS#

AY14

SA_WE#

AK23

SA_RCVENIN#

AK24

SA_RCVENOUT#

CALISTOGA_FCBGA1466~D

UMA@

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

DDR SYS MEMORY A

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_D[0..63] <13> DDR_B_D[0..63] <14>

DDR_B_BS#0<14>

DDR_B_BS#1<14>

DDR_B_BS#2<14>

DDR_B_DM[0..7]<14>

DDR_B_DQS[0..7]<14>

DDR_B_DQS#[0..7]<14>

DDR_B_MA[0..13]<14>

DDR_B_CAS#<14>

DDR_B_RAS#<14>

DDR_B_WE#<14>

T4 PAD

T11 PAD

DDR_B_BS#0

DDR_B_BS#1

DDR_B_BS#2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6DDR_A_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA12

DDR_B_MA13

DDR_B_CAS#

DDR_B_RAS#

DDR_B_WE#

SB_RCVENIN#

SB_RCVENOUT#

U14E

AT24

SB_BS0

AV23

SB_BS1

AY28

SB_BS2

AK36

SB_DM0

AR38

SB_DM1

AT36

SB_DM2

BA31

SB_DM3

AL17

SB_DM4

AH8

SB_DM5

BA5

SB_DM6

AN4

SB_DM7

AM39

SB_DQS0

AT39

SB_DQS1

AU35

SB_DQS2

AR29

SB_DQS3

AR16

SB_DQS4

AR10

SB_DQS5

AR7

SB_DQS6

AN5

SB_DQS7

AM40

SB_DQS0#

AU39

SB_DQS1#

AT35

SB_DQS2#

AP29

SB_DQS3#

AP16

SB_DQS4#

AT10

SB_DQS5#

AT7

SB_DQS6#

AP5

SB_DQS7#

AY23

SB_MA0

AW24

SB_MA1

AY24

SB_MA2

AR28

SB_MA3

AT27

SB_MA4

AT28

SB_MA5

AU27

SB_MA6

AV28

SB_MA7

AV27

SB_MA8

AW27

SB_MA9

AV24

SB_MA10

BA27

SB_MA11

AY27

SB_MA12

AR23

SB_MA13

AR24

SB_CAS#

AU23

SB_RAS#

AR27

SB_WE#

AK16

SB_RCVENIN#

AK18

SB_RCVENOUT#

CALISTOGA_FCBGA1466~D

UMA@

AK39

SB_DQ0

AJ37

SB_DQ1

AP39

SB_DQ2

AR41

SB_DQ3

AJ38

SB_DQ4

AK38

SB_DQ5

AN41

SB_DQ6

AP41

SB_DQ7

AT40

SB_DQ8

AV41

SB_DQ9

AU38

SB_DQ10

AV38

SB_DQ11

AP38

SB_DQ12

AR40

SB_DQ13

AW38

SB_DQ14

AY38

SB_DQ15

BA38

SB_DQ16

AV36

SB_DQ17

AR36

SB_DQ18

AP36

SB_DQ19

BA36

SB_DQ20

AU36

SB_DQ21

AP35

SB_DQ22

AP34

SB_DQ23

AY33

SB_DQ24

BA33

SB_DQ25

AT31

SB_DQ26

AU29

SB_DQ27

AU31

SB_DQ28

AW31

SB_DQ29

AV29

SB_DQ30

AW29

SB_DQ31

AM19

SB_DQ32

AL19

SB_DQ33

AP14

SB_DQ34

AN14

SB_DQ35

AN17

SB_DQ36

AM16

SB_DQ37

AP15

SB_DQ38

AL15

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

AJ11

AH10

AJ9

AN10

AK13

AH11

AK10

AJ8

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ5

AJ3

DDR SYS MEMORY B

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

A A

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2005/10/06 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, M/B LA-3281

401429

星期三 七月

06

1

B

of

847, 12, 20

5

4

3

2

1

http://hobi-elektronika.net

D D

+1.5VS_PCIE

U14C

H27

SDVOCTRL_DATA

H28

SDVOCTRL_CLK

R53 1.5K_0402_1%

TV_COMPS

TV_LUMA

TV_CRMA

LVDSA0+

LVDSA1+

LVDSA2+

LVDSA0LVDSA1LVDSA2-

LVDSB0+

LVDSB1+

LVDSB2+

LVDSB0LVDSB1LVDSB2-

LVDSAC+

LVDSACLVDSBC+

LVDSBC-

GMCH_ENBKL

LDDC_CLK

LDDC_DATA

GMCH_LVDDEN

R42

4.99K_0402_1%

3VDDCCL

3VDDCDA

CRT_VSYNC

CRT_HSYNC

CRT_B

CRT_G

CRT_R

R47

255_0402_1%

LVDSA0+<37>

LVDSA1+<37>

LVDSA2+<37>

LVDSA0-<37>

LVDSA1-<37>

LVDSA2-<37>

LVDSB0+<37>

LVDSB1+<37>

LVDSB2+<37>

LVDSB0-<37>

LVDSB1-<37>

LVDSB2-<37>

LVDSAC+<37>

LVDSAC-<37>

LVDSBC+<37>

LVDSBC-<37>

C C

TV_COMPS

12

R207 150_0603_1%UMA@

R208 150_0603_1%UMA@

R209 150_0603_1%UMA@

B B

12

12

R210 150_0603_1%UMA@

R211 150_0603_1%UMA@

R212 150_0603_1%UMA@

TV_LUMA

TV_CRMA

12

12

12

CRT_R

CRT_G

CRT_B

+2.5VS +3VS

GMCH_ENBKL<16>

GMCH_LVDDEN<16>

TV_COMPS<17>

TV_LUMA<17>

TV_CRMA<17>

3VDDCCL<17>

3VDDCDA<17>

CRT_VSYNC<17>

CRT_HSYNC<17>

CRT_B<17>

CRT_G<17>

CRT_R<17>

B37

LA_DATA0

B34

LA_DATA1

A36

LA_DATA2

C37

LA_DATA#0

B35

LA_DATA#1

A37

LA_DATA#2

F30

LB_DATA0

D29

LB_DATA1

F28

LB_DATA2

G30

LB_DATA#0

D30

LB_DATA#1

F29

LB_DATA#2

A32

LA_CLK

A33

LA_CLK#

E26

LB_CLK

E27

LB_CLK#

D32

LBKLT_CTL

J30

LBKLT_EN

H30

LCTLA_CLK

H29

LCTLB_DATA

G26

LDDC_CLK

G25

LDDC_DATA

F32

LVDD_EN

B38

12

12

12

LIBG

C35

LVBG

C33

LVREFH

C32

LVREFL

A16

TVDAC_A

C18

TVDAC_B

A19

TVDAC_C

J20

TV_IREF

B16

TV_IRTNA

B18

TV_IRTNB

B19

TV_IRTNC

J29

TV_DCONSEL1

K30

TV_DCONSEL0

C26

DDCCLK

C25

DDCDATA

H23

VSYNC

G23

HSYNC

E23

BLUE

D23

BLUE#

C22

GREEN

B22

GREEN#

A21

RED

B21

RED#

J22

CRT_IREF

CALISTOGA_FCBGA1466~D

UMA@

LVDS

TV CRT

EXP_COMPI

EXP_COMPO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

PCI-EXPRESS GRAPHICS

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

D40

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

PEGCOMP

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

R54

24.9_0402_1%

1 2

C153 0.1U_0402_16V4ZVGA@

C124 0.1U_0402_16V4ZVGA@

C142 0.1U_0402_16V4ZVGA@

C115 0.1U_0402_16V4ZVGA@

C155 0.1U_0402_16V4ZVGA@

C126 0.1U_0402_16V4ZVGA@

C148 0.1U_0402_16V4ZVGA@

C117 0.1U_0402_16V4ZVGA@

C157 0.1U_0402_16V4ZVGA@

C128 0.1U_0402_16V4ZVGA@

C140 0.1U_0402_16V4ZVGA@

C119 0.1U_0402_16V4ZVGA@

C159 0.1U_0402_16V4ZVGA@

C130 0.1U_0402_16V4ZVGA@

C144 0.1U_0402_16V4ZVGA@

C121 0.1U_0402_16V4ZVGA@

C152 0.1U_0402_16V4ZVGA@

C123 0.1U_0402_16V4ZVGA@

C141 0.1U_0402_16V4ZVGA@

C114 0.1U_0402_16V4ZVGA@

C154 0.1U_0402_16V4ZVGA@

C125 0.1U_0402_16V4ZVGA@

C147 0.1U_0402_16V4ZVGA@

C116 0.1U_0402_16V4ZVGA@

C156 0.1U_0402_16V4ZVGA@

C127 0.1U_0402_16V4ZVGA@

C139 0.1U_0402_16V4ZVGA@

C118 0.1U_0402_16V4ZVGA@

C158 0.1U_0402_16V4ZVGA@

C129 0.1U_0402_16V4ZVGA@

C143 0.1U_0402_16V4ZVGA@

C120 0.1U_0402_16V4ZVGA@

PEG_RXN[0..15] <18>

PEG_RXP[0..15] <18>

PEG_M_TXN0

PEG_M_TXN1

PEG_M_TXN2

PEG_M_TXN3

PEG_M_TXN4

PEG_M_TXN5

PEG_M_TXN6

PEG_M_TXN7

PEG_M_TXN8

PEG_M_TXN9

PEG_M_TXN10

PEG_M_TXN11

PEG_M_TXN12

PEG_M_TXN13

PEG_M_TXN14

PEG_M_TXN15

PEG_M_TXP0

PEG_M_TXP1

PEG_M_TXP2

PEG_M_TXP3

PEG_M_TXP4

PEG_M_TXP5

PEG_M_TXP6

PEG_M_TXP7

PEG_M_TXP8

PEG_M_TXP9

PEG_M_TXP10

PEG_M_TXP11

PEG_M_TXP12

PEG_M_TXP13

PEG_M_TXP14

PEG_M_TXP15

PEG_M_TXN[0..15] <18>

PEG_M_TXP[0..15] <18>

12

12

R215

UMA@

UMA@

2.2K_0402_5%

LDDC_CLK

A A

LDDC_DATA EDI D _ D A T _LCD

5

+2.5VS

R216

2.2K_0402_5%

Q18

BSS138_SOT23

UMA@

Q17

BSS138_SOT23

UMA@

2.2K_0402_5%

S

S

12

D

13

13

D

UMA@

12

EDID_CLK_LCD

4

R217

2.2K_0402_5%

UMA@

EDID_CLK_LCD <37>

EDID_DAT_LCD <37>

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2005/10/06 2006/10/06

Compal Secret Data

Deciphered Date

2

Title

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, M/B LA-3281

401429

星期三 七月

06

1

of

947, 12, 20

B

R214

G

2

G

2

5

4

3

2

1

http://hobi-elektronika.net

+VCCP

21

D D

C C

B B

A A

D13

CH751H-40_SC76@

CH751H-40_SC76@

12

+2.5VS

R221

10_0402_5%@

+1.5VS

21

D12

12

+3VS

R220

10_0402_5%@

1

C50

C24

2

4.7U_0805_10V4Z

1

C94

2

1

0.22U_0603_10V7K

2

1

+

C91

220U_D2_4VM

2

1

2

2.2U_0805_16V4Z

MCH_A6

1

C296

2

MCH_D2

C12

C10

0.22U_0603_10V7K

+1.5VS

+VCCP

0.47U_0603_10V7K

MCH_AB1

1

2

0.47U_0603_10V7K

U14H

AC14

VTT0

AB14

VTT1

W14

VTT2

V14

VTT3

T14

VTT4

R14

VTT5

P14

VTT6

N14

VTT7

M14

VTT8

L14

VTT9

AD13

VTT10

AC13

VTT11

AB13

VTT12

AA13

VTT13

Y13

VTT14

W13

VTT15

V13

VTT16

U13

VTT17

T13

VTT18

R13

VTT19

N13

VTT20

M13

VTT21

L13

VTT22

AB12

VTT23

AA12

VTT24

Y12

VTT25

W12

VTT26

V12

VTT27

U12

VTT28

T12

VTT29

R12

VTT30

P12

VTT31

N12

VTT32

M12

VTT33

L12

VTT34

R11

VTT35

P11

VTT36

N11

VTT37

M11

VTT38

R10

VTT39

P10

VTT40

N10

VTT41

M10

VTT42

P9

VTT43

N9

VTT44

M9

VTT45

R8

VTT46

P8

VTT47

N8

VTT48

M8

VTT49

P7

VTT50

N7

VTT51

M7

VTT52

R6

VTT53

P6

VTT54

M6

VTT55

A6

VTT56

R5

VTT57

P5

VTT58

N5

VTT59

M5

VTT60

P4

VTT61

N4

VTT62

M4

VTT63

R3

VTT64

P3

VTT65

N3

VTT66

M3

VTT67

R2

VTT68

P2

VTT69

M2

VTT70

D2

VTT71

AB1

VTT72

R1

VTT73

P1

VTT74

N1

VTT75

M1

VTT76

AG14

VCCAUX32

AF14

VCCAUX33

AE14

VCCAUX34

Y14

VCCAUX35

AF13

VCCAUX36

AE13

VCCAUX37

AF12

VCCAUX38

AE12

VCCAUX39

AD12

VCCAUX40

CALISTOGA_FCBGA1466~D

UMA@

P O W E R

VCC_SYNC

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL

VCCA_3GBG

VSSA_3GBG

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC2

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_LVDS

VSSA_LVDS

VCCA_MPLL

VCCA_TVBG

VSSA_TVBG

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCD_HMPLL0

VCCD_HMPLL1

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCD_TVDAC

VCCDQ_TVDAC

VCCHV0

VCCHV1

VCCHV2

VCCAUX0

VCCAUX1

VCCAUX2

VCCAUX3

VCCAUX4

VCCAUX5

VCCAUX6

VCCAUX7

VCCAUX8

VCCAUX9

VCCAUX10

VCCAUX11

VCCAUX12

VCCAUX13

VCCAUX14

VCCAUX15

VCCAUX16

VCCAUX17

VCCAUX18

VCCAUX19

VCCAUX20

VCCAUX21

VCCAUX22

VCCAUX23

VCCAUX24

VCCAUX25

VCCAUX26

VCCAUX27

VCCAUX28

VCCAUX29

VCCAUX30

VCCAUX31

H22

B30

C30

A30

AB41

AJ41

L41

N41

R41

V41

Y41

AC33

G41

H41

E21

F21

G21

B26

C39

AF1

A38

B39

AF2

H20

G20

E19

F19

C20

D20

E20

F20

AH1

AH2

A28

B28

C28

D21

H19

A23

B23

B25

AK31

AF31

AE31

AC31

AL30

AK30

AJ30

AH30

AG30

AF30

AE30

AD30

AC30

AG29

AF29

AE29

AD29

AC29

AG28

AF28

AE28

AH22

AJ21

AH21

AJ20

AH20

AH19

P19

P16

AH15

P15

AH14

+2.5VS

1 2

C306

0.1U_0402_16V4Z

+2.5VS

W=40 mils

+1.5VS_3GPLL

+2.5VS

+2.5VS_CRTDAC

+1.5VS_DPLLA

+1.5VS_DPLLB

+1.5VS_HPLL

+2.5VS

+1.5VS_MPLL

+3VS_TVBG

+3VS_TVDACA

+3VS_TVDACA

+3VS_TVDACA

+1.5VS

+1.5VS_TVDAC

1

2

C302

0.1U_0402_16V4Z

+1.5VS

1

C299

2

+1.5VS_PCIE

1

+

C108

2

1

2

C298

10U_1206_6.3V6M

0.1U_0402_16V4Z

220U_D2_4VM

1

2

+3VS

C107

1

2

C72

2200P_0402_50V7K

C105

10U_1206_6.3V6M

1

2

R57

0_0805_5%

12

+1.5VS

1

2

10U_1206_6.3V6M

L4 FBM-11-160808-601-T_0603

1 2

C71

+2.5VS

CRTDAC: Route caps within

250mil of Alviso. Route FB

within 3" of Calistoga

0.1U_0402_16V4Z

+2.5VS

1

C304

2

0.01U_0402_16V7K

close pin A38

0_0805_5%

1

1

C49

2

2

C63

0.1U_0402_16V4Z

2200P_0402_50V7K

1

C102

2

0.1U_0402_16V4Z

R205

+2.5VS

1

2

close pin G41

+3VS+3VS_TVBG

12

C99

0.1U_0402_16V4Z

+1.5VS_DPLLA +1.5VS_DPLLB

0.1U_0402_16V4Z

L16

1 2

FBM-L10-160808-301-T_0603

330U_D2E_2.5VM

UMA@

1

C82

C300

1

+

2

2

1

1

C55

2

2

2200P_0402_50V7K

C54

0.1U_0402_16V4Z

PCI-E/MEM/PSB PLL decoupling

+1.5VS+1.5VS_3GPLL

R56

0_0603_5%

12

1

1

C98

C97

2

2

0.1U_0402_16V4Z

10U_1206_6.3V6M

+1.5VS_MPLL

45mA Max. 45mA Max.

1

1

C8

C13

2

2

0.1U_0402_16V4Z

R16

0_0603_5%

10U_1206_6.3V6M

C104

0.1U_0402_16V4Z

@

12

0.1U_0402_16V4Z

1

1

C58

C297

2

2

2200P_0402_50V7K

0.1U_0402_16V4Z

+1.5VS_TVDAC +1.5VS

1

2

1

C67

2

0.1U_0402_16V4Z

C37

2200P_0402_50V7K

+1.5VS_HPLL

C14

1 2

FBM-L10-160808-301-T_0603

330U_D2E_2.5VM

UMA@

1

C101

C100

1

+

2

2

1

1

C45

2

2

2200P_0402_50V7K

R213

0_0603_5%

1

2

R17

0_0603_5%

1

1

C9

2

2

0.1U_0402_16V4Z

L5

0_0603_5%

C46

0.1U_0402_16V4Z

12

C301

0.1U_0402_16V4Z

@

10U_1206_6.3V6M

R206

+1.5VS+1.5VS

+3VS+3VS_TVDACA+3VS_TVDACA+3VS_TVDACA

12

1

2

12

+1.5VS+1.5VS

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMAT ION IT CON TAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2005/10/06 2006/10/06

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, M / B LA-3281

401429

期三 七月

1

B

of

10 47¬P , 12, 2006

5

+VCCP

D D

1

1

C69

2

0.22U_0603_10V7K

1

C48

2

10U_1206_6.3V6M

C C

B B

A A

1

C61

C25

2

2

0.22U_0603_10V7K

0.22U_0603_10V7K

1

1

C95

C31

2

2

1U_0603_10V4Z

10U_1206_6.3V6M

1

+

220U_D2_4VM

C18

2

1

+

C79

220U_D2_4VM@

2

+VCCP

U14F

AD27

VCC_NCTF0

AC27

VCC_NCTF1

AB27

VCC_NCTF2

AA27

VCC_NCTF3

Y27

VCC_NCTF4

W27

VCC_NCTF5

V27

VCC_NCTF6

U27

VCC_NCTF7

T27

VCC_NCTF8

R27

VCC_NCTF9

AD26

VCC_NCTF10

AC26

VCC_NCTF11

AB26

VCC_NCTF12

AA26

VCC_NCTF13

Y26

VCC_NCTF14

W26

VCC_NCTF15

V26

VCC_NCTF16

U26

VCC_NCTF17

T26

VCC_NCTF18

R26

VCC_NCTF19

AD25

VCC_NCTF20

AC25

VCC_NCTF21

AB25

VCC_NCTF22

AA25

VCC_NCTF23

Y25

VCC_NCTF24

W25

VCC_NCTF25

V25

VCC_NCTF26

U25

VCC_NCTF27

T25

VCC_NCTF28

R25

VCC_NCTF29

AD24

VCC_NCTF30

AC24

VCC_NCTF31

AB24

VCC_NCTF32

AA24

VCC_NCTF33

Y24

VCC_NCTF34

W24

VCC_NCTF35

V24

VCC_NCTF36

U24

VCC_NCTF37

T24

VCC_NCTF38

R24

VCC_NCTF39

AD23

VCC_NCTF40

V23

VCC_NCTF41

U23

VCC_NCTF42

T23

VCC_NCTF43

R23

VCC_NCTF44

AD22

VCC_NCTF45

V22

VCC_NCTF46

U22

VCC_NCTF47

T22

VCC_NCTF48

R22

VCC_NCTF49

AD21

VCC_NCTF50

V21

VCC_NCTF51

U21

VCC_NCTF52

T21

VCC_NCTF53

R21

VCC_NCTF54

AD20

VCC_NCTF55

V20

VCC_NCTF56

U20

VCC_NCTF57

T20

VCC_NCTF58

R20

VCC_NCTF59

AD19

VCC_NCTF60

V19

VCC_NCTF61

U19

VCC_NCTF62

T19

VCC_NCTF63

AD18

VCC_NCTF64

AC18

VCC_NCTF65

AB18

VCC_NCTF66

AA18

VCC_NCTF67

Y18

VCC_NCTF68

W18

VCC_NCTF69

V18

VCC_NCTF70

U18

VCC_NCTF71

T18

VCC_NCTF72

M19

VCC100

L19

VCC101

N18

VCC102

M18

VCC103

L18

VCC104

P17

VCC105

N17

VCC106

M17

VCC107

N16

VCC108

M16

VCC109

L16

VCC110

CALISTOGA_FCBGA1466~D

UMA@

VCCAUX_NCTF0

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

P O W E R

VCCAUX_NCTF37

VCCAUX_NCTF38

VCCAUX_NCTF39

VCCAUX_NCTF40

VCCAUX_NCTF41

VCCAUX_NCTF42

VCCAUX_NCTF43

VCCAUX_NCTF44

VCCAUX_NCTF45

VCCAUX_NCTF46

VCCAUX_NCTF47

VCCAUX_NCTF48

VCCAUX_NCTF49

VCCAUX_NCTF50

VCCAUX_NCTF51

VCCAUX_NCTF52

VCCAUX_NCTF53

VCCAUX_NCTF54

VCCAUX_NCTF55

VCCAUX_NCTF56

VCCAUX_NCTF57

VSS_NCTF0

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VCC_SM100

VCC_SM101

VCC_SM102

VCC_SM103

VCC_SM104

VCC_SM105

VCC_SM106

VCC_SM107

4

+1.5VS

AG27

AF27

AG26

AF26

AG25

AF25

AG24

AF24

AG23

AF23

AG22

AF22

AG21

AF21

AG20

AF20

AG19

AF19

R19

AG18

AF18

R18

AG17

AF17

AE17

AD17

AB17

AA17

W17

V17

T17

R17

AG16

AF16

AE16

AD16

AC16

AB16

AA16

Y16

W16

V16

U16