LENEAD LTC2290 User Manual

查询LTC2290供应商

FEATURES

■

Integrated Dual 12-Bit ADCs

■

Sample Rate: 10Msps

■

Single 3V Supply (2.7V to 3.4V)

■

Low Power: 120mW

■

71.3dB SNR

■

90dB SFDR

■

110dB Channel Isolation

■

Multiplexed or Separate Data Bus

■

Flexible Input: 1V

■

575MHz Full Power Bandwidth S/H

■

Clock Duty Cycle Stabilizer

■

Shutdown and Nap Modes

■

Pin Compatible Family

P-P

to 2V

P-P

Range

80Msps: LTC2294 (12-Bit), LTC2299 (14-Bit)

65Msps: LTC2293 (12-Bit), LTC2298 (14-Bit)

40Msps: LTC2292 (12-Bit), LTC2297 (14-Bit)

25Msps: LTC2291 (12-Bit), LTC2296 (14-Bit)

10Msps: LTC2290 (12-Bit), LTC2295 (14-Bit)

■

64-Pin (9mm × 9mm) QFN Package

U

APPLICATIO S

LTC2290

Dual 12-Bit, 10Msps

Low Power 3V ADC

U

DESCRIPTIO

The LTC®2290 is a 12-bit 10Msps, low power dual 3V

A/D converter designed for digitizing high frequency, wide

dynamic range signals. The LTC2290 is perfect for

demanding imaging and communications applications

with AC performance that includes 71.3dB SNR and 90dB

SFDR for signals well beyond the Nyquist frequency.

DC specs include ±0.3LSB INL (typ), ±0.15LSB DNL (typ)

and no missing codes over temperature. The transition

noise is a low 0.25LSB

A single 3V supply allows low power operation. A separate

output supply allows the outputs to drive 0.5V to 3.3V

logic. An optional multiplexer allows both channels to

share a digital output bus.

A single-ended CLK input controls converter operation.

An optional clock duty cycle stabilizer allows high performance at full speed for a wide range of clock duty cycles.

, LTC and LT are registered trademarks of Linear Technology Corporation.

All other trademarks are the property of their respective owners.

RMS

.

■

Wireless and Wired Broadband Communication

■

Imaging Systems

■

Spectral Analysis

■

Portable Instrumentation

U

TYPICAL APPLICATIO

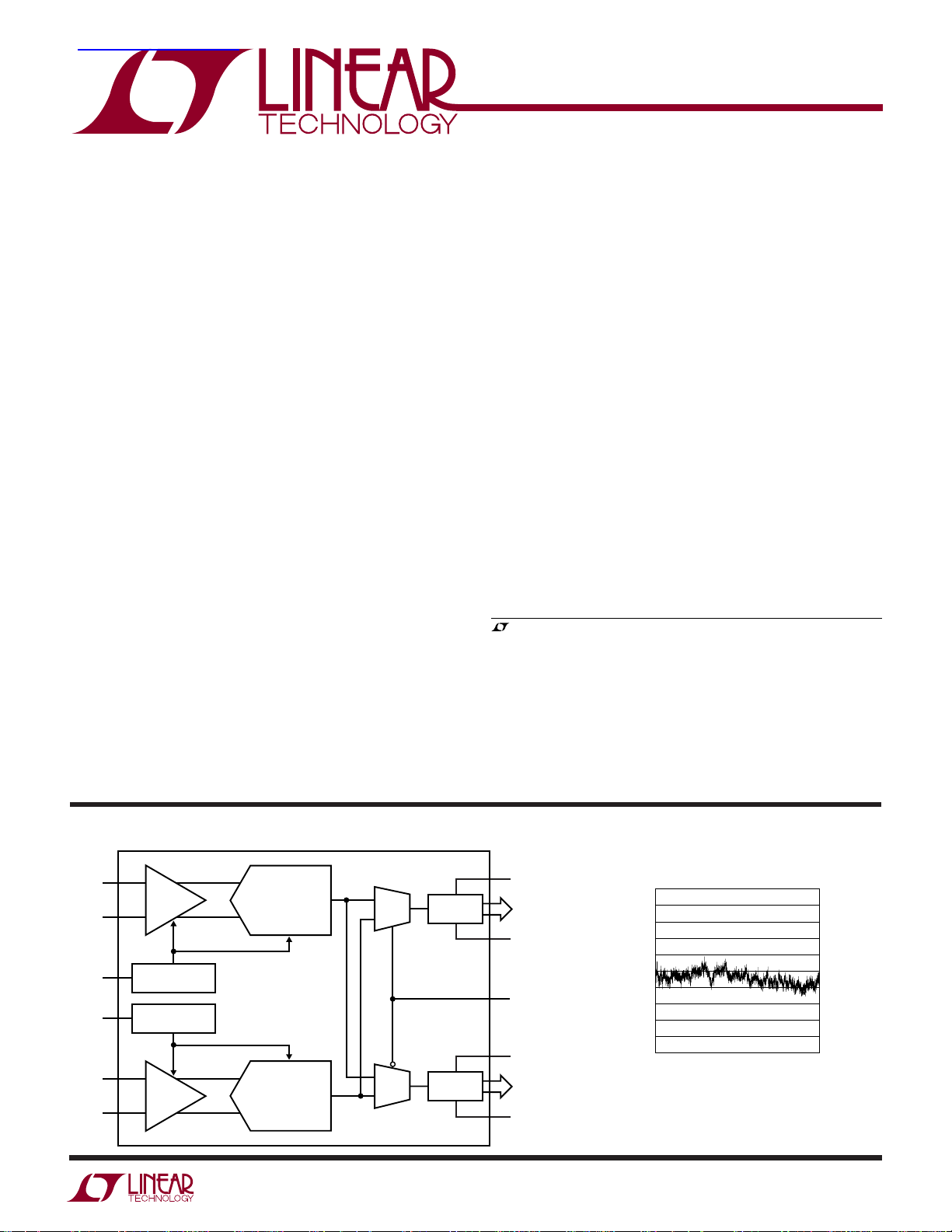

ANALOG

INPUT A

CLK A

CLK B

ANALOG

INPUT B

+

INPUT

S/H

–

CLOCK/DUTY CYCLE

CONTROL

CLOCK/DUTY CYCLE

CONTROL

+

INPUT

S/H

–

12-BIT

PIPELINED

ADC CORE

12-BIT

PIPELINED

ADC CORE

OUTPUT

DRIVERS

OUTPUT

DRIVERS

2290 TA01

OV

D11A

•

•

•

D0A

OGND

MUX

OV

D11B

•

•

•

D0B

OGND

DD

DD

Typical INL, 2V Range

1.0

0.8

0.6

0.4

0.2

0

–0.2

INL ERROR (LSB)

–0.4

–0.6

–0.8

–1.0

1024

0

2048

CODE

3072

4096

2290 TA01

2290f

1

LTC2290

WW

W

U

ABSOLUTE AXI U RATI GS

OVDD = VDD (Notes 1, 2)

Supply Voltage (VDD) ................................................. 4V

Digital Output Ground Voltage (OGND) ....... –0.3V to 1V

Analog Input Voltage (Note 3) ..... –0.3V to (V

Digital Input Voltage .................... –0.3V to (V

Digital Output Voltage ................– 0.3V to (OV

Power Dissipation............................................ 1500mW

Operating Temperature Range

LTC2290C ............................................... 0°C to 70°C

LTC2290I............................................. –40°C to 85°C

Storage Temperature Range ..................–65°C to 125°C

Lead Temperature (Soldering, 10 sec).................. 300°C

+ 0.3V)

DD

+ 0.3V)

DD

+ 0.3V)

DD

UUW

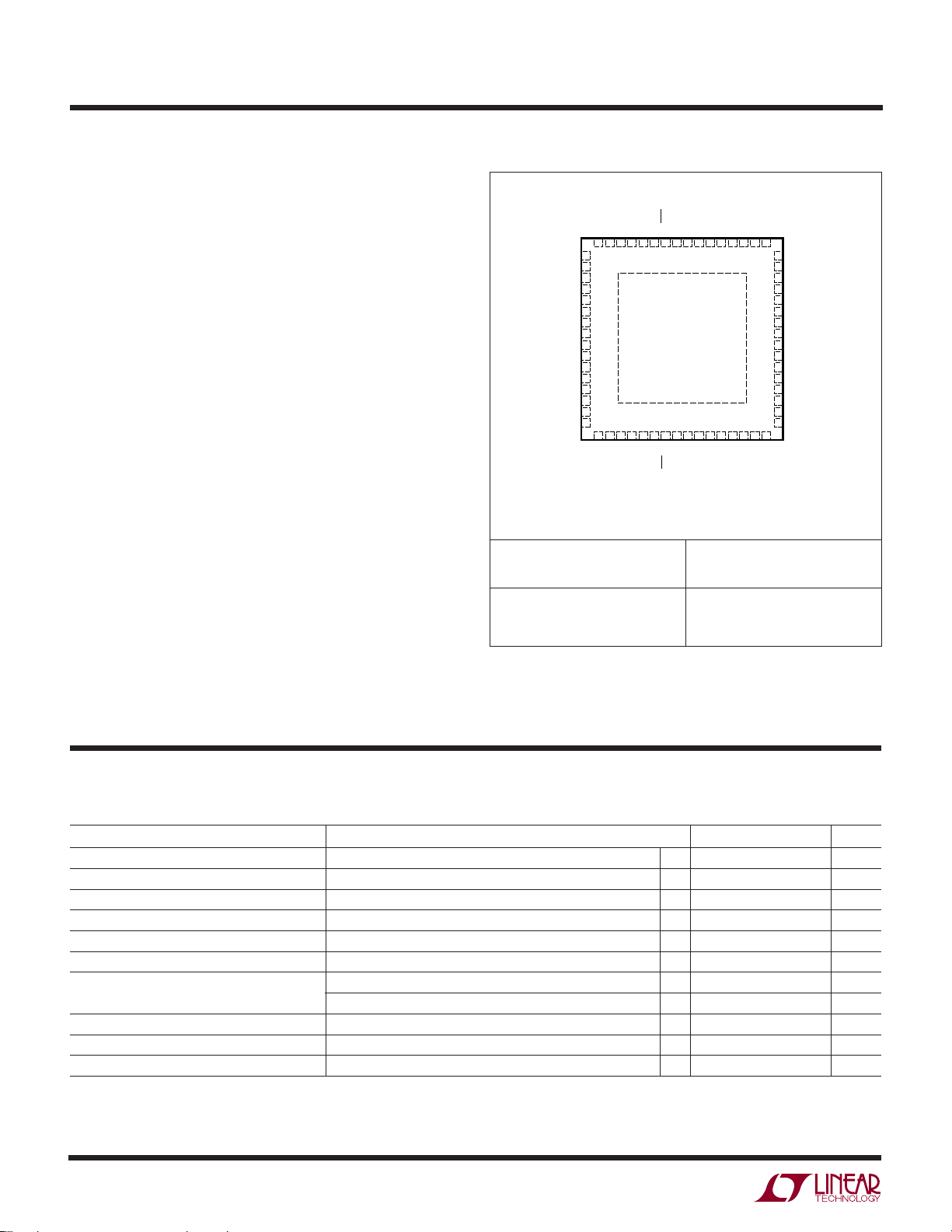

PACKAGE/ORDER I FOR ATIO

TOP VIEW

DD

64 GND

63 VDD62 SENSEA

61 VCMA

60 MODE

59 SHDNA

58 OEA

57 OFA

56 DA11

55 DA10

54 DA9

53 DA8

52 DA7

51 DA6

50 OGND

49 OV

1

A

INA+

–

A

2

INA

REFHA 3

REFHA 4

REFLA 5

REFLA 6

V

7

DD

CLKA

8

CLKB 9

V

10

DD

REFLB 11

REFLB 12

REFHB 13

REFHB 14

–

A

15

INB

+

A

16

INB

19

17

18

DD

V

GND

SENSEB

64-LEAD (9mm × 9mm) PLASTIC QFN

EXPOSED PAD (PIN 65) IS GND AND MUST BE SOLDERED TO PCB

T

65

20

NC 24

OEB 23

MUX 21

VCMB

SHDNB 22

UP PACKAGE

= 125°C, θJA = 20°C/W

JMAX

NC 25

DB0 26

DB1 27

DB2 28

ORDER PART

NUMBER

DB3 29

48 DA5

47 DA4

46 DA3

45 DA2

44 DA1

43 DA0

42 NC

41 NC

40 OFB

39 DB11

38 DB10

37 DB9

36 DB8

35 DB7

34 DB6

33 DB5

32

DD

DB4 30

OV

OGND 31

QFN PART*

MARKING

LTC2290CUP

LTC2290UP

LTC2290IUP

Consult LTC Marketing for parts specified with wider operating temperature ranges.

*The temperature grade is identified by a label on the shipping container.

U

CO VERTER CHARACTERISTICS

temperature range, otherwise specifications are at TA = 25°C. (Note 4)

PARAMETER CONDITIONS MIN TYP MAX UNITS

Resolution (No Missing Codes) ● 12 Bits

Integral Linearity Error Differential Analog Input (Note 5) ● –1.3 ±0.3 1.3 LSB

Differential Linearity Error Differential Analog Input ● –0.7 ±0.15 0.7 LSB

Offset Error (Note 6) ● –12 ±212 mV

Gain Error External Reference ● –2.5 ±0.5 2.5 %FS

Offset Drift ±10 µV/°C

Full-Scale Drift Internal Reference ±30 ppm/°C

External Reference ±15 ppm/°C

Gain Matching External Reference ±0.3 %FS

Offset Matching ±2mV

Transition Noise SENSE = 1V 0.25 LSB

The ● denotes the specifications which apply over the full operating

RMS

2

2290f

LTC2290

UU

A ALOG I PUT

specifications are at TA = 25°C. (Note 4)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

IN

V

IN,CM

I

IN

I

SENSE

I

MODE

t

AP

t

JITTER

CMRR Analog Input Common Mode Rejection Ratio 80 dB

U

Analog Input Range (A

Analog Input Common Mode Differential Input (Note 7) ● 1 1.5 1.9 V

Analog Input Leakage Current 0V < A

SENSEA, SENSEB Input Leakage 0V < SENSEA, SENSEB < 1V ● –3 3 µA

MODE Input Leakage Current 0V < MODE < V

Sample-and-Hold Acquisition Delay Time 0 ns

Sample-and-Hold Acquisition Delay Time Jitter 0.2 ps

Full Power Bandwidth Figure 8 Test Circuit 575 MHz

W

DY A IC ACCURACY

otherwise specifications are at TA = 25°C. AIN = –1dBFS. (Note 4)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

SNR Signal-to-Noise Ratio 5MHz Input ● 69.6 71.3 dB

SFDR Spurious Free Dynamic Range 5MHz Input ● 74 90 dB

2nd or 3rd Harmonic

SFDR Spurious Free Dynamic Range 5MHz Input ● 80 90 dB

4th Harmonic or Higher

S/(N+D) Signal-to-Noise Plus Distortion Ratio 5MHz Input ● 69 71.3 dB

I

MD

Intermodulation Distortion fIN = 4.3MHz, 4.6MHz 90 dB

Crosstalk fIN = 5MHz –110 dB

The ● denotes the specifications which apply over the full operating temperature range, otherwise

+

–

–A

IN

) 2.7V < V

IN

< 3.4V (Note 7) ● 1V to 2V V

DD

+

–

, A

< V

IN

IN

DD

DD

● –1 1 µA

● –3 3 µA

RMS

The ● denotes the specifications which apply over the full operating temperature range,

70MHz Input 70.7 dB

70MHz Input 85 dB

70MHz Input 90 dB

70MHz Input 70.4 dB

2290f

3

LTC2290

UU U

I TER AL REFERE CE CHARACTERISTICS

PARAMETER CONDITIONS MIN TYP MAX UNITS

VCM Output Voltage I

VCM Output Tempco ±30 ppm/°C

VCM Line Regulation 2.7V < VDD < 3.3V 3 mV/V

VCM Output Resistance –1mA < I

= 0 1.475 1.500 1.525 V

OUT

(Note 4)

< 1mA 4 Ω

OUT

UU

DIGITAL I PUTS A D DIGITAL OUTPUTS

full operating temperature range, otherwise specifications are at TA = 25°C. (Note 4)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

LOGIC INPUTS (CLK, OE, SHDN, MUX)

V

IH

V

IL

I

IN

C

IN

LOGIC OUTPUTS

OVDD = 3V

C

OZ

I

SOURCE

I

SINK

V

OH

V

OL

OV

= 2.5V

DD

V

OH

V

OL

OVDD = 1.8V

V

OH

V

OL

High Level Input Voltage VDD = 3V ● 2V

Low Level Input Voltage VDD = 3V ● 0.8 V

Input Current VIN = 0V to V

Input Capacitance (Note 7) 3 pF

Hi-Z Output Capacitance OE = High (Note 7) 3 pF

Output Source Current V

Output Sink Current V

High Level Output Voltage IO = –10µA 2.995 V

Low Level Output Voltage IO = 10µA 0.005 V

High Level Output Voltage IO = –200µA 2.49 V

Low Level Output Voltage IO = 1.6mA 0.09 V

High Level Output Voltage IO = –200µA 1.79 V

Low Level Output Voltage IO = 1.6mA 0.09 V

= 0V 50 mA

OUT

= 3V 50 mA

OUT

= –200µA ● 2.7 2.99 V

I

O

= 1.6mA ● 0.09 0.4 V

I

O

The ● denotes the specifications which apply over the

DD

● –10 10 µA

4

2290f

LTC2290

WU

POWER REQUIRE E TS

range, otherwise specifications are at T

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

DD

OV

IV

P

DISS

P

SHDN

P

NAP

DD

DD

Analog Supply Voltage (Note 9) ● 2.7 3 3.4 V

Output Supply Voltage (Note 9) ● 0.5 3 3.6 V

Supply Current Both ADCs at f

Power Dissipation Both ADCs at f

Shutdown Power (Each Channel) SHDN = H, OE = H, No CLK 2 mW

Nap Mode Power (Each Channel) SHDN = H, OE = L, No CLK 15 mW

= 25°C. (Note 8)

A

The ● denotes the specifications which apply over the full operating temperature

S(MAX)

S(MAX)

● 40 46 mA

● 120 138 mW

UW

TI I G CHARACTERISTICS

range, otherwise specifications are at TA = 25°C. (Note 4)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

f

s

t

L

t

H

t

AP

t

D

t

MD

Pipeline Latency 6 Cycles

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: All voltage values are with respect to ground with GND and OGND

wired together (unless otherwise noted).

Note 3: When these pin voltages are taken below GND or above V

will be clamped by internal diodes. This product can handle input currents

of greater than 100mA below GND or above VDD without latchup.

Note 4: VDD = 3V, f

drive, unless otherwise noted.

Sampling Frequency (Note 9) ● 1 10 MHz

CLK Low Time Duty Cycle Stabilizer Off ● 40 50 500 ns

CLK High Time Duty Cycle Stabilizer Off ● 40 50 500 ns

Sample-and-Hold Aperture Delay 0 nS

CLK to DATA Delay CL = 5pF (Note 7) ● 1.4 2.7 5.4 ns

MUX to DATA Delay CL = 5pF (Note 7) ● 1.4 2.7 5.4 ns

Data Access Time After OE↓ CL = 5pF (Note 7) ● 4.3 10 ns

BUS Relinquish Time (Note 7) ● 3.3 8.5 ns

= 10MHz, input range = 2V

SAMPLE

The ● denotes the specifications which apply over the full operating temperature

● 5 50 500 ns

● 5 50 500 ns

= 10MHz, input range = 1V

P-P

with differential

with differential

P-P

Duty Cycle Stabilizer On (Note 7)

Duty Cycle Stabilizer On (Note 7)

Note 5: Integral nonlinearity is defined as the deviation of a code from a

straight line passing through the actual endpoints of the transfer curve.

The deviation is measured from the center of the quantization band.

Note 6: Offset error is the offset voltage measured from –0.5 LSB when

DD

, they

the output code flickers between 0000 0000 0000 and 1111 1111 1111.

Note 7: Guaranteed by design, not subject to test.

Note 8: V

drive. The supply current and power dissipation are the sum total for both

channels with both channels active.

Note 9: Recommended operating conditions.

DD

= 3V, f

SAMPLE

2290f

5

LTC2290

INPUT FREQUENCY (MHz)

0

85

90

100

30 50

2290 G09

80

75

10 20

40 60 70

70

65

95

SFDR (dBFS)

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Crosstalk vs Input Frequency

–100

–105

–110

–115

CROSSTALK (dB)

–120

–125

–130

0

20 40 60 80

INPUT FREQUENCY (MHz)

8192 Point FFT, f

IN

–1dB, 2V Range

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dB)

–80

–90

–100

–110

–120

1

0

2

FREQUENCY (MHz)

= 5.1MHz,

3

4

2290 G01

2290 G04

100

5

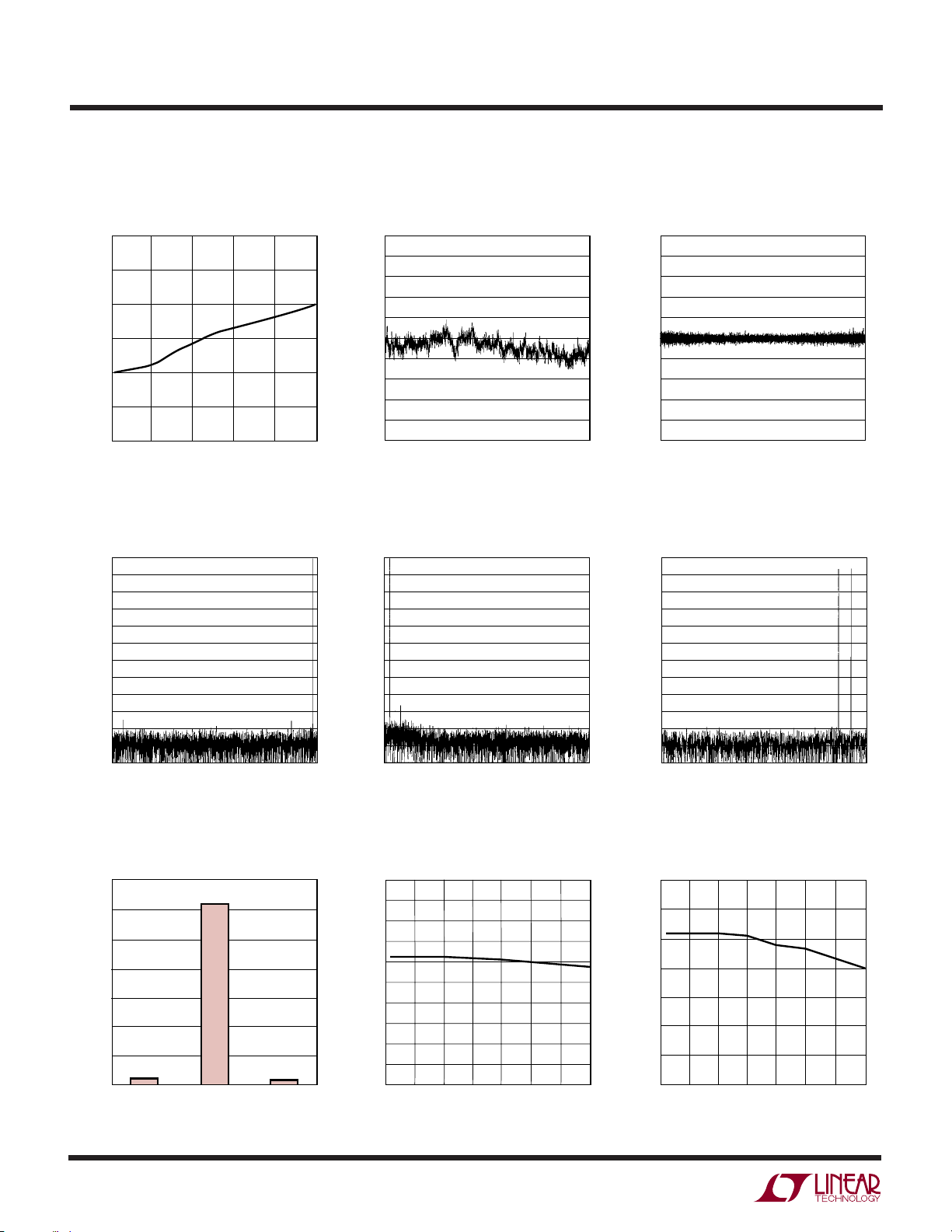

Typical INL, 2V Range Typical DNL, 2V Range

1.0

0.8

0.6

0.4

0.2

0

–0.2

INL ERROR (LSB)

–0.4

–0.6

–0.8

–1.0

1024

0

2048

CODE

8192 Point FFT, fIN = 70.1MHz,

–1dB, 2V Range

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dB)

–80

–90

–100

–110

–120

1

0

2

FREQUENCY (MHz)

3072

3

4096

2290 G02

4

5

2290 G05

1.0

0.8

0.6

0.4

0.2

0

–0.2

DNL ERROR (LSB)

–0.4

–0.6

–0.8

–1.0

1024

0

8192 Point 2-Tone FFT, fIN = 4.3MHz

and 4.6MHz, –1dB, 2V Range

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dB)

–80

–90

–100

–110

–120

1

0

FREQUENCY (MHz)

2

2048

CODE

3072

3

4096

2290 G03

4

5

2290 G06

Grounded Input Histogram

70000

60000

50000

40000

COUNT

30000

20000

10000

6

2155

0

2048

61758

2049

CODE

1607

2050

2290 G07

SNR vs Input Frequency, –1dB,

2V Range

75

74

73

72

71

70

69

SNR (dBFS)

68

67

66

65

0

20

10

INPUT FREQUENCY (MHz)

40

30

SFDR vs Input Frequency, –1dB,

2V Range

60

70

2290 G08

2290f

50

UW

TYPICAL PERFOR A CE CHARACTERISTICS

LTC2290

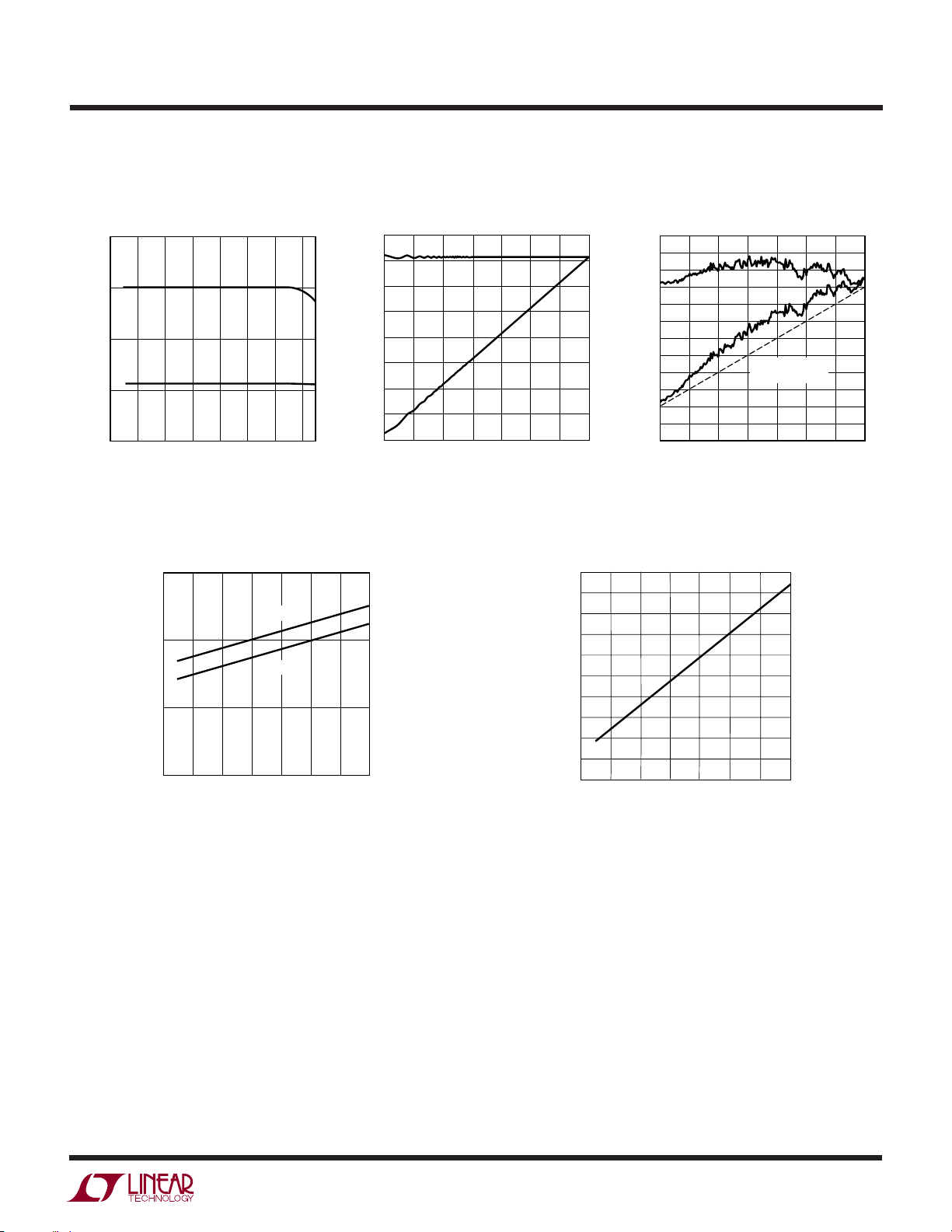

SNR and SFDR vs Sample Rate,

2V Range, f

100

90

80

SNR AND SFDR (dBFS)

70

60

0

2468

= 5MHz, –1dB

IN

SAMPLE RATE (Msps)

I

vs Sample Rate,

VDD

10 12 14

5MHz Sine Wave Input, –1dB

50

40

(mA)

VDD

I

30

20

02468

SAMPLE RATE (Msps)

2V RANGE

1V RANGE

2290 G10

10 12 14

SNR vs Input Level, fIN = 5MHz,

2V Range

80

70

60

50

40

30

SNR (dBc AND dBFS)

20

10

–0

–60 –50 –30

–70

2290 G13

dBFS

dBc

–40

INPUT LEVEL (dBFS)

–20 –10 0

2290 G11

2.0

1.8

1.6

1.4

1.2

(mA)

1.0

OVDD

0.8

I

0.6

0.4

0.2

0

SFDR vs Input Level,

fIN = 5MHz, 2V Range

120

110

100

90

80

70

60

50

40

SFDR (dBc AND dBFS)

30

20

10

0

–70

I

vs Sample Rate, 5MHz Sine

OVDD

Wave Input, –1dB, O

0

4

2

SAMPLE RATE (Msps)

–50

–60

VDD

8

6

dBFS

dBc

90dBc SFDR

REFERENCE LINE

–30

–40

INPUT LEVEL (dBFS)

= 1.8V

12

14

2290 G14

10

–20

–10

0

2290 G12

2290f

7

LTC2290

U

UU

PI FU CTIO S

+

A

(Pin 1): Channel A Positive Differential Analog

INA

Input.

–

A

(Pin 2): Channel A Negative Differential Analog

INA

Input.

REFHA (Pins 3, 4): Channel A High Reference. Short

together and bypass to Pins 5, 6 with a 0.1µF ceramic chip

capacitor as close to the pin as possible. Also bypass to

Pins 5, 6 with an additional 2.2µF ceramic chip capacitor

and to ground with a 1µF ceramic chip capacitor.

REFLA (Pins 5, 6): Channel A Low Reference. Short

together and bypass to Pins 3, 4 with a 0.1µF ceramic chip

capacitor as close to the pin as possible. Also bypass to

Pins 3, 4 with an additional 2.2µF ceramic chip capacitor

and to ground with a 1µF ceramic chip capacitor.

VDD (Pins 7, 10, 18, 63): Analog 3V Supply. Bypass to

GND with 0.1µF ceramic chip capacitors.

CLKA (Pin 8): Channel A Clock Input. The input sample

starts on the positive edge.

CLKB (Pin 9): Channel B Clock Input. The input sample

starts on the positive edge.

REFLB (Pins 11, 12): Channel B Low Reference. Short

together and bypass to Pins 13, 14 with a 0.1µF ceramic

chip capacitor as close to the pin as possible. Also bypass

to Pins 13, 14 with an additional 2.2µF ceramic chip ca-

pacitor and to ground with a 1µF ceramic chip capacitor.

REFHB (Pins 13, 14): Channel B High Reference. Short

together and bypass to Pins 11, 12 with a 0.1µF ceramic

chip capacitor as close to the pin as possible. Also bypass

to Pins 11, 12 with an additional 2.2µF ceramic chip ca-

pacitor and to ground with a 1µF ceramic chip capacitor.

–

A

(Pin 15): Channel B Negative Differential Analog

INB

Input.

+

A

(Pin 16): Channel B Positive Differential Analog

INB

Input.

and a ±1V input range. An external reference greater than

0.5V and less than 1V applied to SENSEB selects an input

range of ±V

V

(Pin 20): Channel B 1.5V Output and Input Common

CMB

Mode Bias. Bypass to ground with 2.2µF ceramic chip

capacitor. Do not connect to V

MUX (Pin 21): Digital Output Multiplexer Control. If MUX

is High, Channel A comes out on DA0-DA13, OFA; Channel B

comes out on DB0-DB13, OFB. If MUX is Low, the output

busses are swapped and Channel A comes out on DB0DB13, OFB; Channel B comes out on DA0-DA13, OFA. To

multiplex both channels onto a single output bus, connect

MUX, CLKA and CLKB together.

SHDNB (Pin 22): Channel B Shutdown Mode Selection

Pin. Connecting SHDNB to GND and OEB to GND results

in normal operation with the outputs enabled. Connecting

SHDNB to GND and OEB to V

tion with the outputs at high impedance. Connecting

SHDNB to VDD and OEB to GND results in nap mode with

the outputs at high impedance. Connecting SHDNB to V

and OEB to VDD results in sleep mode with the outputs at

high impedance.

OEB (Pin 23): Channel B Output Enable Pin. Refer to

SHDNB pin function.

NC (Pins 24, 25, 41, 42): Do Not Connect These Pins.

DB0 – DB11 (Pins 26 to 30, 33 to 39): Channel B Digital

Outputs. DB11 is the MSB.

OGND (Pins 31, 50): Output Driver Ground.

OVDD (Pins 32, 49): Positive Supply for the Output Driv-

ers. Bypass to ground with 0.1µF ceramic chip capacitor.

OFB (Pin 40): Channel B Overflow/Underflow Output.

High when an overflow or underflow has occurred.

DA0 – DA11 (Pins 43 to 48, 51 to 56): Channel A Digital

Outputs. DA11 is the MSB.

. ±1V is the largest valid input range.

SENSEB

.

CMA

results in normal opera-

DD

DD

GND (Pins 17, 64): ADC Power Ground.

SENSEB (Pin 19): Channel B Reference Programming Pin.

Connecting SENSEB to V

and a ±0.5V input range. VDD selects the internal reference

selects the internal reference

CMB

8

OFA (Pin 57): Channel A Overflow/Underflow Output.

High when an overflow or underflow has occurred.

OEA (Pin 58): Channel A Output Enable Pin. Refer to

SHDNA Pin Function.

2290f

Loading...

Loading...