ADM-3A

Maintenance Manual

TABLE

OF

CONTENTS

Section

1

2

3

GENERAL

1.1

1.2 ADM-3A

1.3

1.4

INSTALLATION

2.1

2.2

2.3

2.4

2.5

2.6

2.7

OPERATION

3.1

3.2

3.3

3.4

DESCRIPTION

INTRODUCTION.

PHYSICAL

SPECIFICATIONS.

GENERAL.

VISUAL

INSTALLATION.

SETTING

SETTING

SETTING

CONNECTING

GENERAL.

DISPLAYING

SPECIAL

PROGRAMMING&WORD

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CAPABILITIES

DESCRIPTION.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

INSPECTION

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

INTERNAL

FRONT

DISPLAY

FUNCTION

PANEL

CONTROL.

CABLES&TURNING

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

CHARACTERS

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SWITCHES.

SWITCHES.

KEYS.

STRUCTURE.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . .... . . . . .... . . .... . . . . . . . . . . .

ON

POWER.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

. . . . . . . . . . . . . . . . . . . . 2-4

Page

1-1

1-1

1-1

2-1

2-1

2-1

..

2-3

..

2-4

. . 3-1

4

5

6

THEORY

4.1

4.2

4.3

MAINTENANCE

5.1

5.2

5.3

5.4

5.5

5.6

DRAWINGS

6.1 SCHEMATIC

6.2

6.3

OF

OPERATION

GENERAL.

GENERAL

LOGIC

GENERAL.

INSTALLATION.

ROUTINE

OPENING

ADJUSTMENTS

CORRECTIVE

SYSTEMS

SCHEMATIC

INTERFACE

SCHEMATIC

CLEAR/ERASE

OFFSET

ROW

BEEPER

DESCRIPTION

MAINTENANCE.

ADM-3A

COUNTERS.

COUNTER

COUNTER.

CIRCUIT.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FUNCTIONAL

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

COVER.

MAINTENANCE

SHEET

SHEET#12

CONTROL.

SHEET#3

LOGIC

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

DESCRIPTION.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

#2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .... .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

. . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

~

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

..

. . 6-3

4-1

5-1

5-3

6-1

6-1

TABLE

OF

CONTENTS (Continued)

Section

6.4 SCHEMATIC

COLUMN

WRITE-PULSE

6.5 SCHEMATIC SHEET# 5

MEMORY ADDRESS GENERATION 6-6

6.6 SCHEMATIC

DATA RECEIVER . . 6-7

CHARACTER DECODERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LOAD CURSOR SEQUENCE

6.7 SCHEMATIC

CLEAR CIRCUIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

READ BACK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

MONITOR DRIVE

CURSOR

6.8 SCHEMATIC

REFRESH

CHARACTER

VIDEO SERIALIZER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

TRANSMIT DATA MULTIPLEXERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

6.9 SCHEMATIC SHEET

KEYBOARD

6.10 SCHEMATIC

DATA TRANSMITTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

CONTROL SECTION

CURRENT LOOP XMTR/RCVR. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

KEYBOARD LOCK CIRCUIT " 6-14

6.11 SCHEMATIC SHEET #

BAUD RATE

SHEET#4

COUNTER.

LOGIC.

SHEET#6

SHEET#7

SIGNALS.

GENERATION.

SHEET#8

MEMORY.

GENERATORS.

#9

CIRCUIT.

SHEET#10

OF

GENERATION.

Page

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

DETECTOR.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

UART.

11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

. . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6-5

..

6-8

7 PARTS

8 RETURNING EQUIPMENT

9

APPENDICES

A

B SCHEMATICS. . . . . .

C OPTIONS C-l

PAINT.

TIMING.

MONITOR A-2

POWER SUPPLY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

P.C. BOARD ASSEMBLY " A-4

WIRING

LIST.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FOR

REPAIR. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

..

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DIAGRAMS.

. . . . . . . . . . . . . . . . . . . . .... . .... . . . .... . . . . . . . . . . . . .

7-1

8-1

..

9-1

..

A-I

A-3

..

B-1

C-9

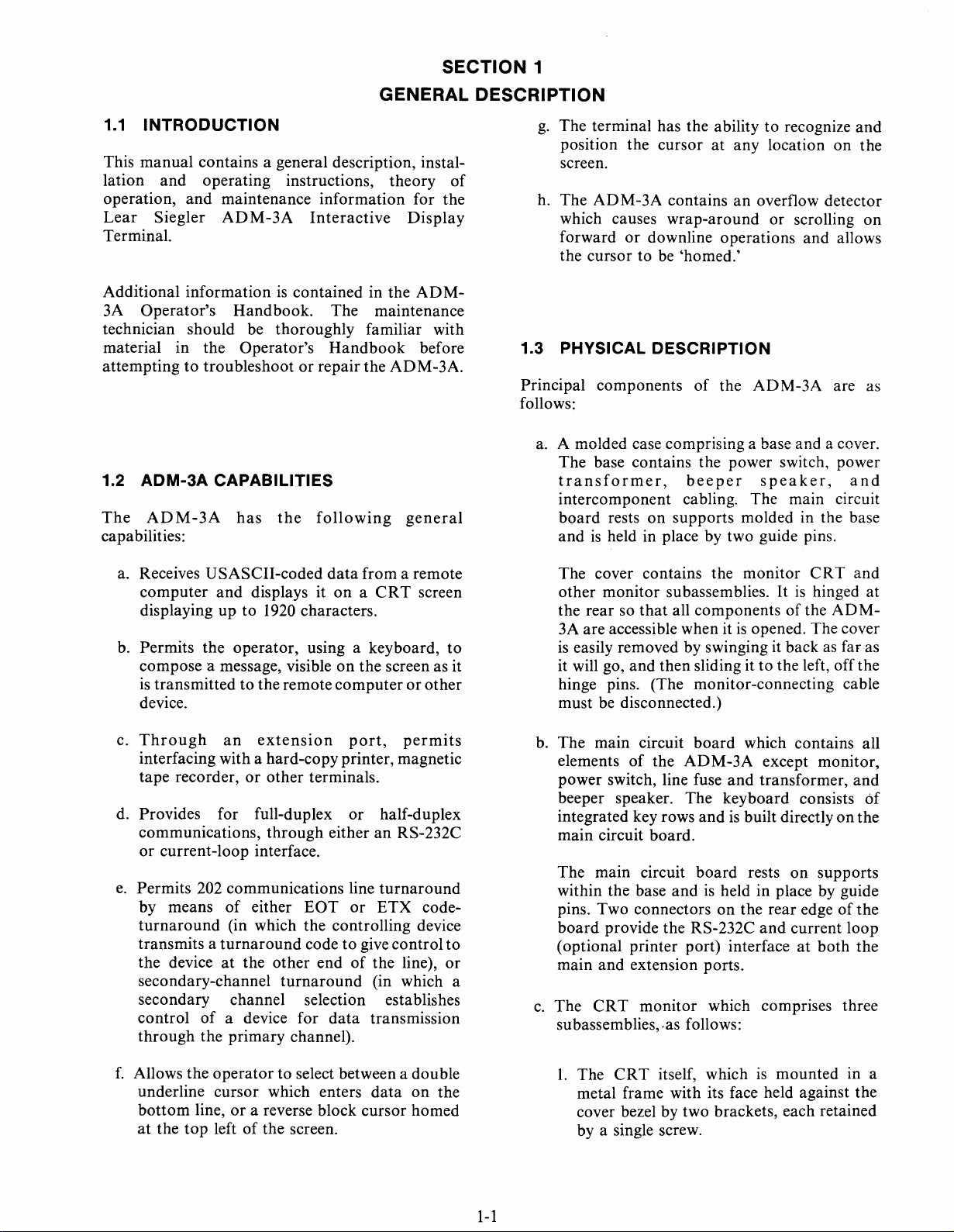

SECTION 1

GENERAL DESCRIPTION

1.1

INTRODUCTION

This manual contains a general description, instal-

and

lation

operation,

Lear

Terminal.

Siegler

operating instructions, theory

and

maintenance information for the

ADM-3A

Interactive

Display

of

g.

The terminal has the ability to recognize and

at

position the cursor

screen.

h. The ADM-3A contains

which causes wrap-around

or

forward

the cursor to be 'homed.'

downline operations and allows

any location on the

an

overflow detector

or

scrolling on

Additional information

3A Operator's Handbook. The maintenance

technician should be thoroughly familiar with

material in the Operator's

to

attempting

1.2 ADM-3A CAPABILITIES

The

ADM-3A

capabilities:

a.

Receives USASCII-coded

computer

displaying up to 1920 characters.

b. Permits the operator, using a keyboard,

compose a message, visibleonthe screen as it

is

transmitted to the remotecomputerorother

device.

Through

c.

interfacing with a hard-copy printer, magnetic

tape recorder,

d. Provides for full-duplex

communications,

or

e.

Permits 202 communications line

by means

turnaround

transmits a

the deviceatthe other endofthe line),

secondary-channel

secondary channel selection establishes

control

through

troubleshootorrepair the ADM-3A.

and

an

current-loop interface.

of

(in which the controlling device

turnaround

of

a device for

the primary channel).

is

contained in the

has

the

displays it

extension

or

other terminals.

through

either

EOT

codetogive control

turnaround

AD

Handbook

following

data

from a remote

onaCRT

port,

or

eitheranRS-232C

or

(in which a

data

transmission

before

general

screen

permits

half-duplex

turnaround

ETX code-

M-

to

to

or

1.3 PHYSICAL DESCRIPTION

Principal components

follows:

a. A molded case comprising a base and a cover.

The base contains the power switch, power

transformer,

intercomponent cabling. The main circuit

board

and

The cover contains the monitor

other monitor subassemblies.

the rear so

3A are accessible when itisopened. The cover

is

it will go, and then sliding it to the left, off the

hinge pins. (The monitor-connecting cable

must be disconnected.)

b. The main circuit

elements

power switch, line fuse

beeper speaker. The keyboard consists

integrated key rows andisbuilt directlyonthe

main circuit board.

The main circuit board rests

within the base

pins. Two connectors

board

(optional printer port) interface

main and extension ports.

c.

The

subassemblies,

rests

is

held in place by two guide pins.

that

easily removed by swinging it backasfar as

of

provide the RS-232C

CRT

monitor which compnses three

of

the

ADM-3A

beeper

on

supports molded in the base

all componentsofthe

board

the

ADM-3A

andisheld in place by guide

-as

follows:

speaker,

CRT

It

is

hinged at

which contains all

except monitor,

and

transformer, and

on

on

the rear edgeofthe

and

current loop

at

are as

ADM-

supports

both

and

and

of

the

f.

Allows the

underline cursor which enters

bottom

at

the

operator

line,ora reverse block cursor homed

top

leftofthe screen.

to select between a double

data

on

the

1-1

1.

The

CRT

itself, whichismounted in a

metal frame with its face held against the

cover bezel by two brackets, each retained

by a single screw.

2.

A printed circuit

containing most circuits

The video

cover molding

of

the flyback assemblyonthe other.

boardisheld in place by the

board

on

one side, and by pressure

(video board),

of

the monitor.

KEYBOARD

59-key solid-state keyboard designed similar to a

and

teletypewriter layout

keys:

containing the following

3.

The flyback assembly, whichisheld in

place by a single screw. Bosses in the cover

molding assembly surface retain the edge

the video board.

1.4 SPECIFICATIONS

DISPLAY

Screen

12-inch (diagonally measured) rectangular

with

P4

white

surface.

Display Format

Standard:

Optional:

Character Set

Generated:

Displayed:

phosphor

960 characters,

characters

1920 characters, 24 lines

characters

lL~

ASCII

lower case, numeric,

control)

Standard

Optional -

and

etched non-glare

12

lines

characters (upper

punctuation

- 64

ASCII

(upper case, numeric,

punctuation)

95

ASCII

(upper and lower case,

numeric, punctuation)

characters

characters

of

of

of

CRT

80

80

and

and

47 alphanumeric keys

RETURN

LINE

RUB

HERE

SHIFT

COMMUNICATIONS

Modem interiace

EIA

(switch selectable)

Extension Interface

Extension RS-232C

asynchronous auxiliary device (e.g., hard copy

printer, magnetic

terminals).

Optionally, the extension

RS-232C

Communication Rates

75, 110,

19200

Send/Receive Modes

Full duplex

FEED

IS

standard

and

150,

baud

RS-232C

tape

20mA current loop interfaces.

300,600, 1200, 1800, 2400, 4800, 9600,

(switch selectable)

and

half duplex (switch selectable)

and

port

recorderoradditional

portisavailable with

CTRL

BREAK

CLEAR

REPT

ESC (Escape)

Space Bar

20mA current loop

for interfacing serial

(Control)

(Repeat)

data

both

Character Generation

5 x 7

dot

matrix, 0.18 in. high x 0.075 in. wide

Cursor (2 modes) -

(I)

Underline, homes to lower leftofscreen

(2) Reverse block image, homes

screen

Data Entry

New

data

entersonprogressive lines,

oronbottom

scrolling

overflow,

Refresh Rate

60Hzor50Hz, dependentonan

to match power line frequency.

lineofscreen. Line feed causes upward

of

entire display page with top-of-page

if

cursorison

bottom

to

line.

internal switch set

upper

toptobottom

left

of

Word Structure

Total

word lengthisswitch selectable to9,10

bits consistingofthe following:

7-bit

data

word

or

8th bit - parity, odd

OR

forced

OR

8th bit suppressed

PHYSICAL AND ELECTRICAL

Dimensions

13.5 in. high x 15.5 in. wide x19in. deep

1-2

toIor

even

°

or

II

I start bit J

I

or

2 stop bits

Weight

25

pounds

50Hzor60Hz, switch selectable

Optional

230 Vac

Power Consumption

60 watts @115 Vac

MONITOR

Input (Necessary Accessory - Available)

Connector Printed circuit board card edge connector - Viking No. 2VK10S/1-2

Pulse Rate or Width Pulse Width:

Amplitude

ELECTRICAL SPECIFICATI,ONS

10%

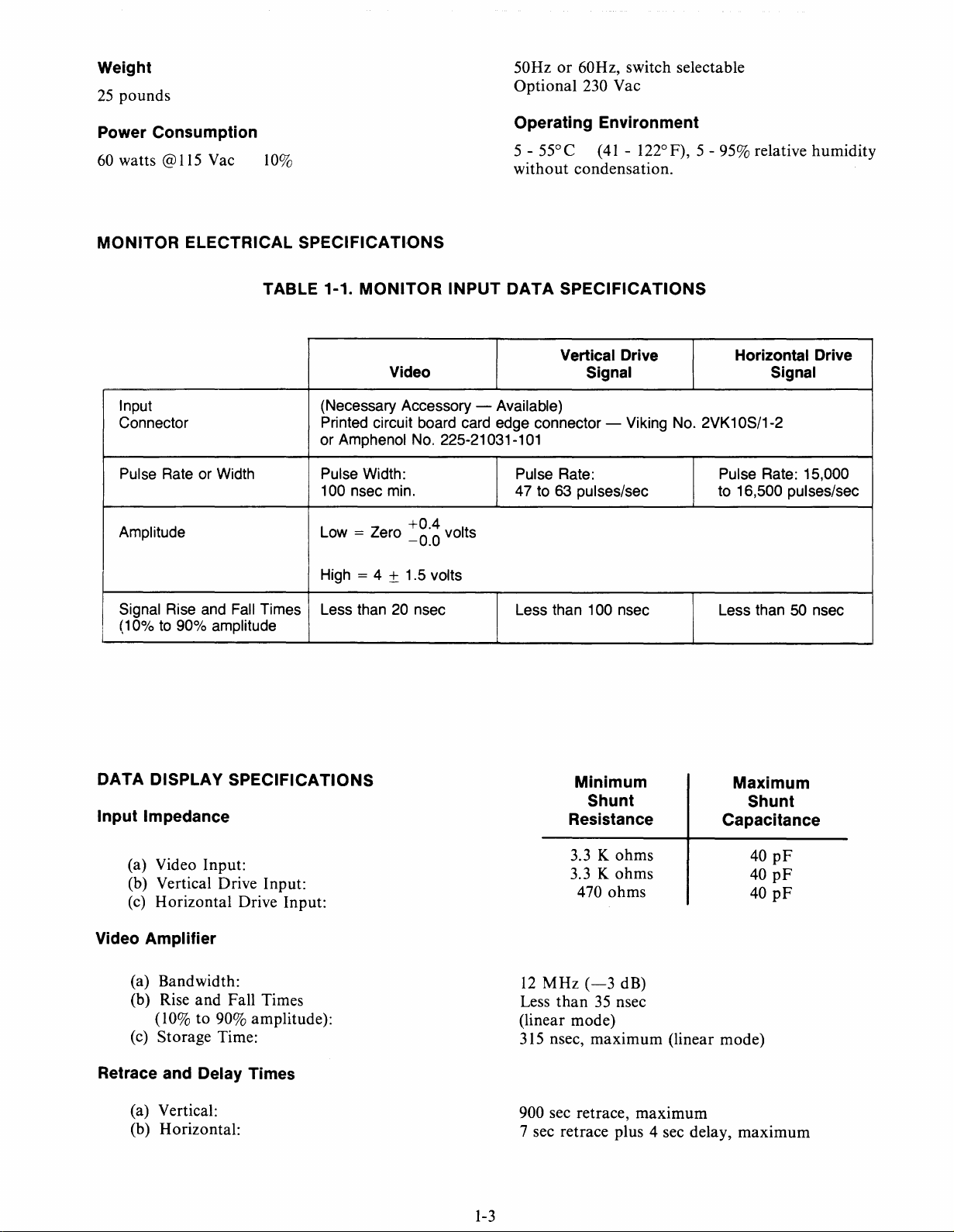

TABLE 1-1.

or Amphenol No, 225-21031-101

100 nsec min.

Low

MONITOR

Video

= Zero

~g:6

INPUT

volts

Operating Environment

5 - 55°C

without

DATA

Pulse Rate:

47 to 63 pulses/sec

(41

- 122°F), 5 - 95% relative humidity

condensation.

SPECIFICATIONS

Vertical

Drive

Signal Signal

Pulse Rate: 15,000

to 16,500 pulses/sec

Horizontal

Drive

Signal Rise and Fall Times

(10%

to

90% amplitude

DATA DISPLAY

Input Impedance

SPECIFICATIONS

(a) Video Input:

(b) Vertical Drive Input:

(c) Horizontal Drive Input:

Video Amplifier

(a) Bandwidth:

(b) Rise

and

Fall Times

(10% to 90% amplitude):

(c) Storage Time:

High

= 4 ± 1.5 volts

Less than 20 nsec

Less than 100 nsec

Minimum

Shunt

Resistance

3.3 K

ohms

3.3 K

ohms

470

ohms

12

MHz

(-3

dB)

than35nsec

Less

(linear mode)

315 nsec,

maximum

Less than

Maximum

Shunt

Capacitance

40

40

40

(linear mode)

pF

pF

pF

50

nsec

Retrace and Delay Times

(a) Vertical:

(b) Horizontal:

900 sec retrace,

7 sec retrace plus 4 sec delay,

1-3

maximum

maximum

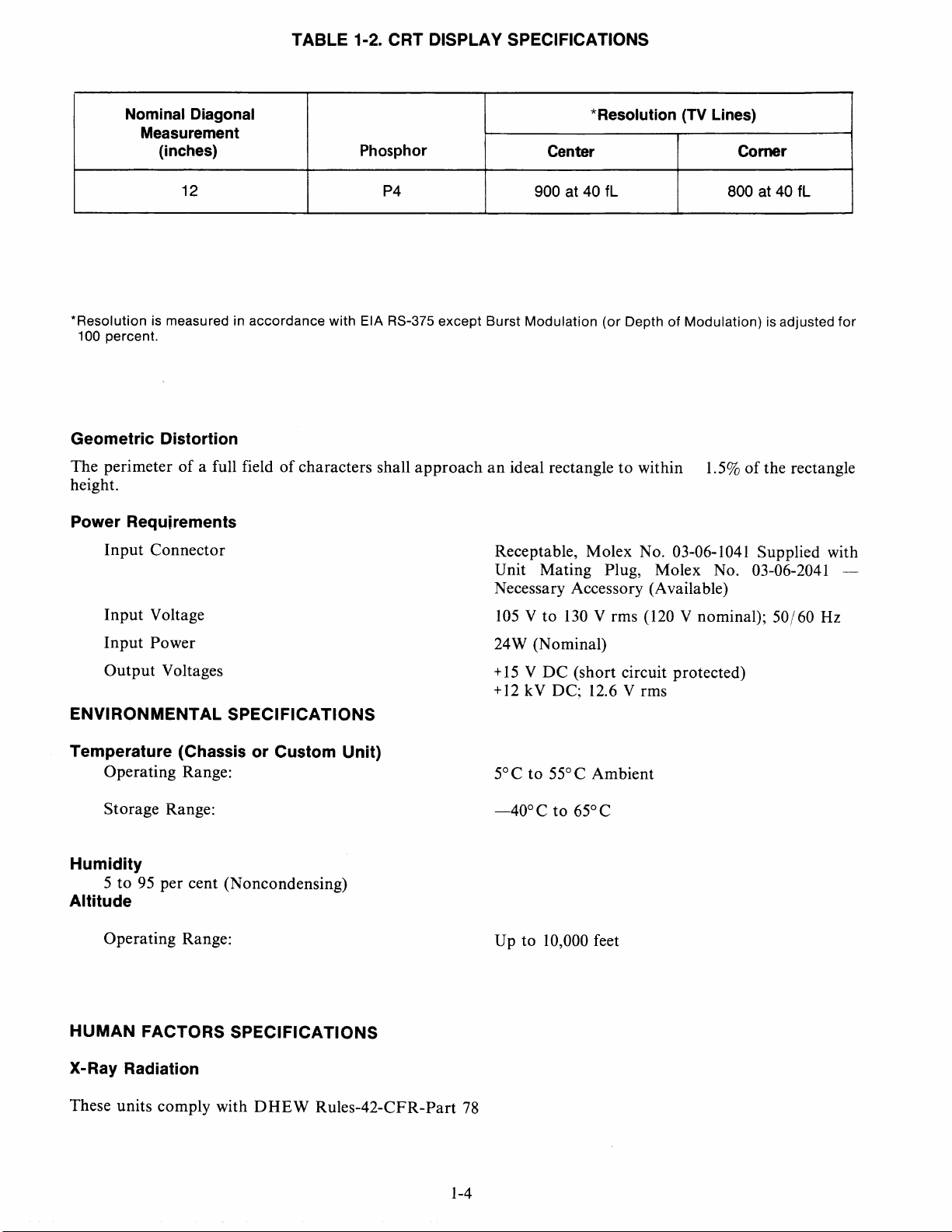

TABLE

1-2. CRT DISPLAY SPECIFICATIONS

Nominal Diagonal

Measurement

(inches) Phosphor

12

*Resolution is measured in accordance with EIA RS-375 except Burst

100 percent.

Geometric

Distortion

The perimeterofa full fieldofcharacters shall

P4

approachanideal rectangletowithin 1.5%ofthe rectangle

height.

Power

Requirements

Input

Connector

Receptable, Molex No. 03-06-1041 Supplied with

Unit Mating Plug, Molex No. 03-06-2041 Necessary Accessory (Available)

Input

Voltage

Input

Power

Output

Voltages

ENVIRONMENTAL

SPECIFICATIONS

105Vto

24W (Nominal)

+

15VDC

+

12

*Resolution (TV Lines)

Center Corner

900 at 40 fL 800 at 40 fL

Modulation

(or

DepthofModulation) is adjusted

130

V rms (120 V nominal);

50/60

(short circuit protected)

kV DC; 12.6 V rms

for

Hz

Temperature

(ChassisorCustom

Operating Range:

Storage Range:

Humidity

5to95

per cent (Noncondensing)

Altitude

Operating Range:

HUMAN

FACTORS

SPECIFICATIONS

X-Ray Radiation

These units comply with

DHEW

Unit)

Rules-42-CFR-Part

5°Cto55°C Ambient

-40°Cto

Up to 10,000 feet

78

1-4

65° C

2.1

GENERAL

SECTION 2

INSTALLATION

This section contains

the

ADM-3A

instructions

ADM-3A,

setting internal switches, connecting cables,

turning-on power.

2.2 VISUAL INSPECTION

It

is

recommeded

carton

should

Carefully inspect

damage

undergone stringent quality inspections

operational

in perfect operating condition.

If

immediately. Save the damaged shipping

as evidence for inspection by the carrier.

Only the consignee may register a claim with the

carrier for damage during shipment. However, Lear

Siegler

customer

2.3 INSTALLATION

The

of

and

you

the unit is damaged, notify the carrier

Data

ADM-3Aisdesignedtooperate in a wide range

environmental conditions:

5-55°C (41-122°F), 5-95% relative humidity

without condensation.

and

and

installing it in a suitable environment,

all packing materialstoprevent

wishtotransportorship the terminal.

during shipping. The terminal has

tests

Products

should such action be necessary.

informationtoaid in installing

preparing

information

that

yousave the originalshipping

your

priortoshipping; it left the factory

it for use. Included

for inspecting the

ADM-3A

will

cooperate

are

and

damage

for signs

container

fully with the

of

and

to

The unit is designed

any

other

suitable hard, flat surface.

In cold climates, care should be exercised

to

allow the

to

equalize with

removing the unit from the shipping

carton; this will prevent moisture from

condensing

warm

soft surface, such as carpeting, which

would obstruct the flow

through

could result in overheating

to

the unit.

2.4 SETTING INTERNAL SWITCHES

Twelve slide switches located inside the

caseonthe printed circuit logic boar-d are used to

select various terminal operating characteristics.

These switches are set

shipping

parameters specified by the

the terminal. Only the parameters listed

Ordering

have been selected

switch setting changes should be made before

attemptingtooperate the terminal. Locationsofthe

internal switches

Form

on

air. Avoid operating the unit on a

the

checkout

packed inside the shipping

sitona tableordesk top,

CAUTION

temperatureofthe terminal

room

temperature

a cold terminalexposed

of

cooling

bottomofthe chassis. This

at

the factory

according

customer

at

the factory. Any required

are

shown in Figure 2-1.

before

air

and

damage

ADM-3A

during

to

operating

when ordering

to

up

pre-

on

carton

or

the

,----------------------

I

I

I

I

I

I I

I I

I

-

--

-- --

---------

INTERNAL

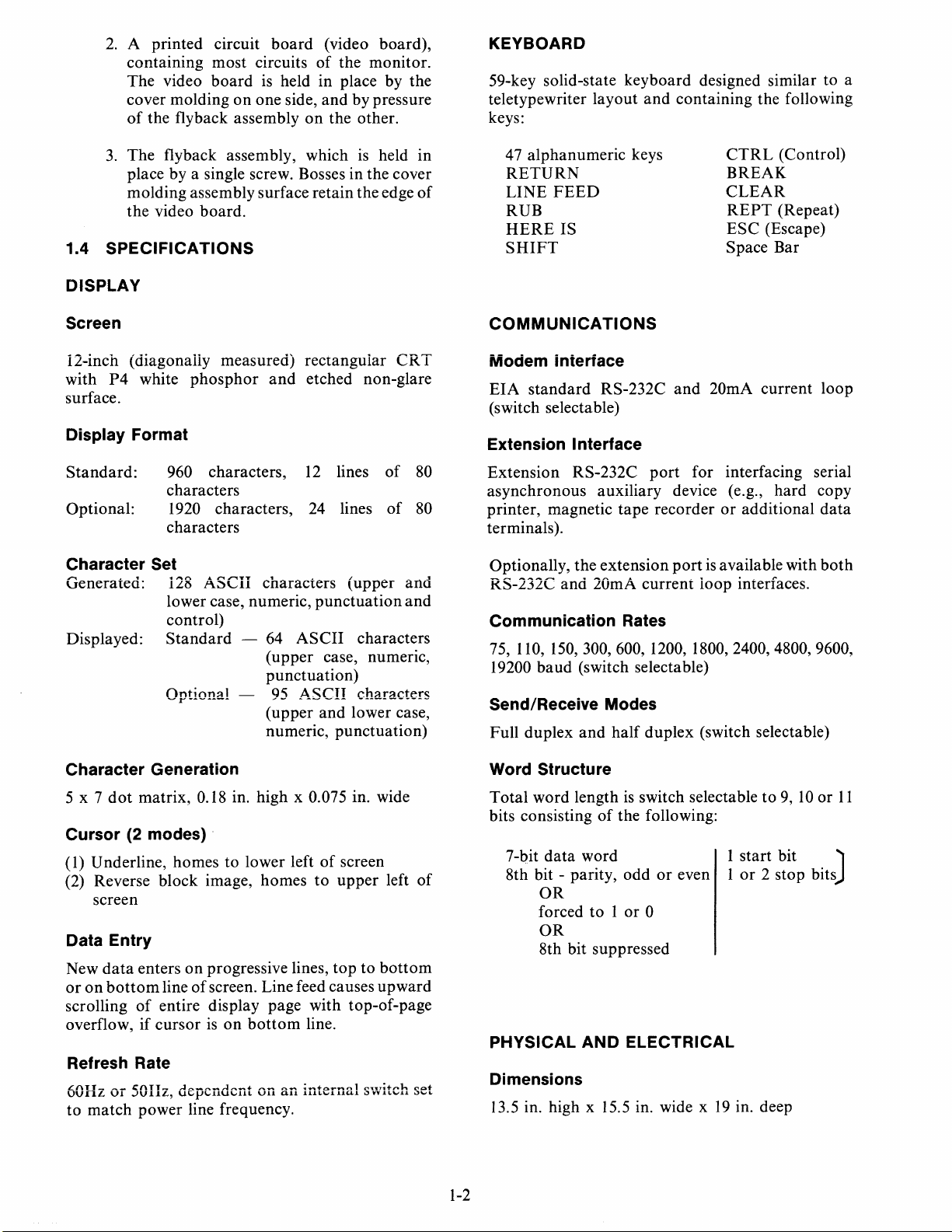

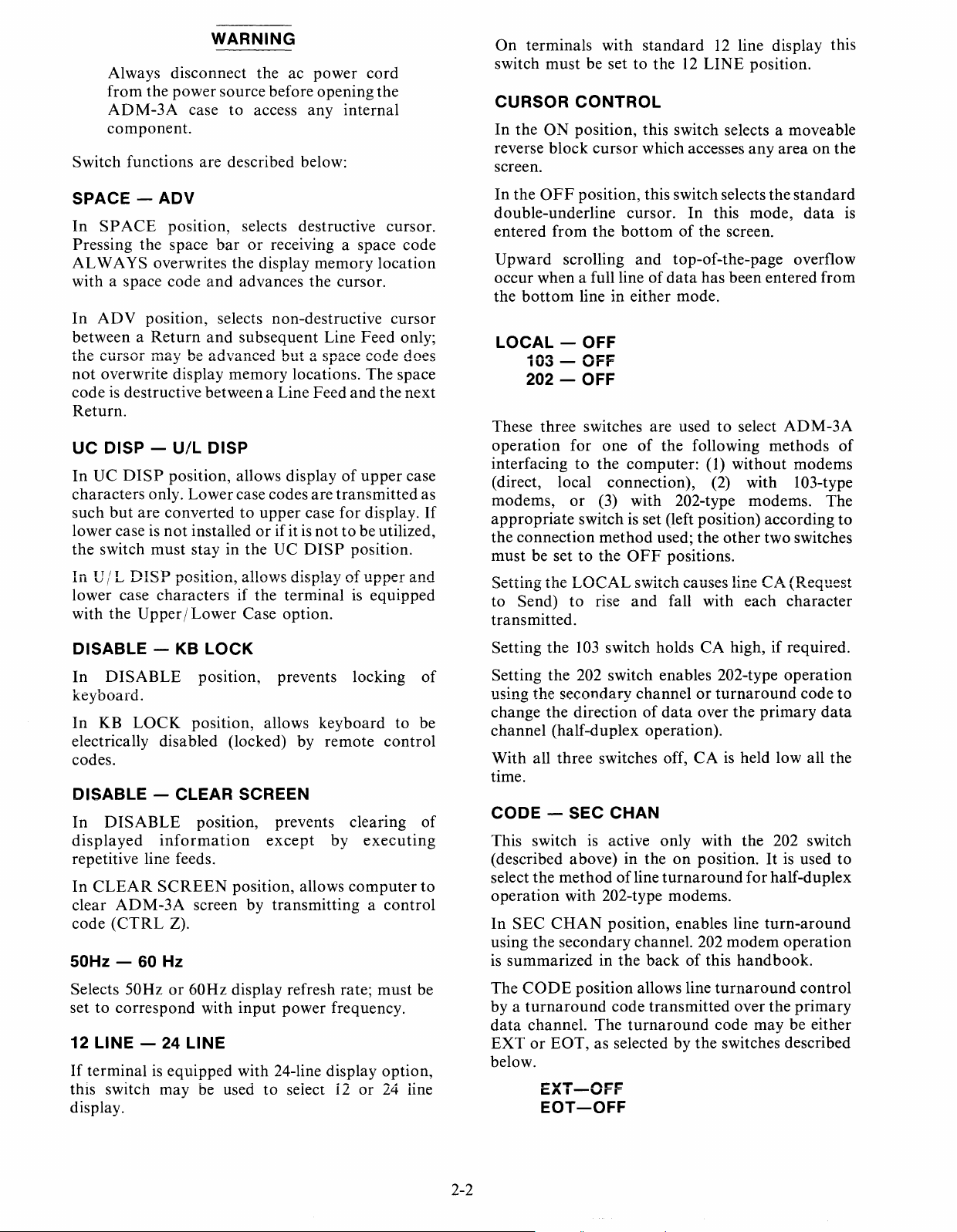

Figure 2-1.

SWITCHES

ADM-3A

-------,

FRONT

Internal

2-1

PANEL

Switches

SWITCHES

and

Controls

WARNING

Always

from

ADM-3A

disconnect

the

power

source before

case

to

the

access

ac

power

opening

any

component.

Switch functions

are

described below:

SPACE - ADV

In

SPACE

Pressing

AL

WAYS

with a space code

In

ADV

between a

the cursor ma

not

overwrite display

position, selects destructive cursor.

the

space

bar

or

receiving a space

overwrites

the

display

and

advances the cursor.

memory

position, selects non-destructive

Return

and

subsequent

1 be advanced but a space code does

y

memory

Line

locations.

codeisdestructive between a Line Feed

Return.

UC

DISP -

In

UC

DISP

characters

such

but

lower caseisnot

the

switch

In

UIL

lower case

with the

U/L

DISP

position, allows displayofupper

only.

Lower

are

convertedtoupper

case codes

case

installedorifitisnottobe utilized,

must

stay in

DrSp

position, allov/s displayofupper

characters

UpperILower

the

UC

DISP

if the

terminalisequipped

Case option.

are

cord

the

internal

code

location

cursor

Feed

only;

The

space

and

the

transmitted

for

display.

position.

next

case

as

and

On

terminals with

switch

must

CURSOR

In

the

ON

reverse

block

be settothe12LINE

CONTROL

position, this switch selects a moveable

cursor

standard

12

which accesses

line display this

position.

any

areaonthe

screen.

In

the

OFF

position, this switchselects the

double-underline

entered

Upward

occur

the

from

the

scrolling

when a full lineofdata

bottom

line in either mode.

cursor.

In

this mode,

bottomofthe screen.

and

top-of-the-page overflow

has

been entered

standard

data

from

is

LOCAL - OFF

103 - OFF

202 - OFF

These three switches

operation

for

one

interfacingtothe

are

usedtoselect

of

the following

computer:

(1)

methods

without

ADM-3A

of

modems

(direct, local connection), (2) with 103-type

If

modems,

appropriate

the

connection

must

Setting

to Send)

or

(3) with 202-type modems. The

switch is set (left position)

method

be settothe

the

LOCAL

to

rise

OFF

used; the

positions.

other

switch causes line

and

fall with each

according

two switches

C.A

ll

(Request

character

to

transmitted.

DISABLE -

In

DISABLE

KB

LOCK

position, prevents locking

keyboard.

In

KB

LOCK

position, allows

electrically disabled (locked) by

codes.

DISABLE - CLEAR SCREEN

In

DISABLE

displayed

position, prevents clearing

information

except

repetitive line feeds.

In

CLEAR

clear

code

(CTRL

SCREEN

ADM-3A

screen by

Z).

position, allows

transmittingacontrol

50Hz - 60 Hz

Selects

set

50Hzor60Hz

to

correspond

display refresh rate;

with

input

power

12 LINE - 24 LINE

If

terminalisequipped

this switch

may

with 24-line display

be used

to

seiect i2

display.

keyboard

remote

by

executing

computer

frequency.

or

to

control

must

option,

24

iine

be

to

be

of

of

Setting the

Setting the 202 switch enables 202-type

using the

change

channel

With all three switches off,

103

switch holds

secondary

the

directionofdata

channelorturnaround

over the

(half-duplex operation).

CAisheld low all the

CA

high,ifrequired.

primary

operation

code

to

data

time.

CODE

- SEC CHAN

This switch is active only with the 202 switch

(described above) in the

select the

operation

In

SEC

using

is

summarizedinthe

The

by a

data

EXTorEaT,

methodofline

with 202-type modems.

CHAN

the

secondary

CODE

turnaround

channel.

position, enables line

position

code

The

as selected by the switches described

on

turnaround

channel. 202

backofthis

allows line

transmitted

turnaround

position.Itis

for

half-duplex

turn-around

modem

handbook.

turnaround

over

the

code

may

used

operation

control

primary

be either

to

below.

I""v-r

I:.J\

I-vrr

,...~~

EOT-OFF

2-2

One

of

these two switchesissettothe

position

to

select the line

primary channel

(See

CODE-SEC

202

and

CODE

beonand

selected, oneofthese switches

the

other

selected,or202 off,

must be set to the

operation

CHAN

off; with 202

both

the

OFF

positions.

turnaround

with 202-type modems.

switch description.) With

and

ETX

and

SEC

EOT

on

(left)

code for

must

CHAN

switches

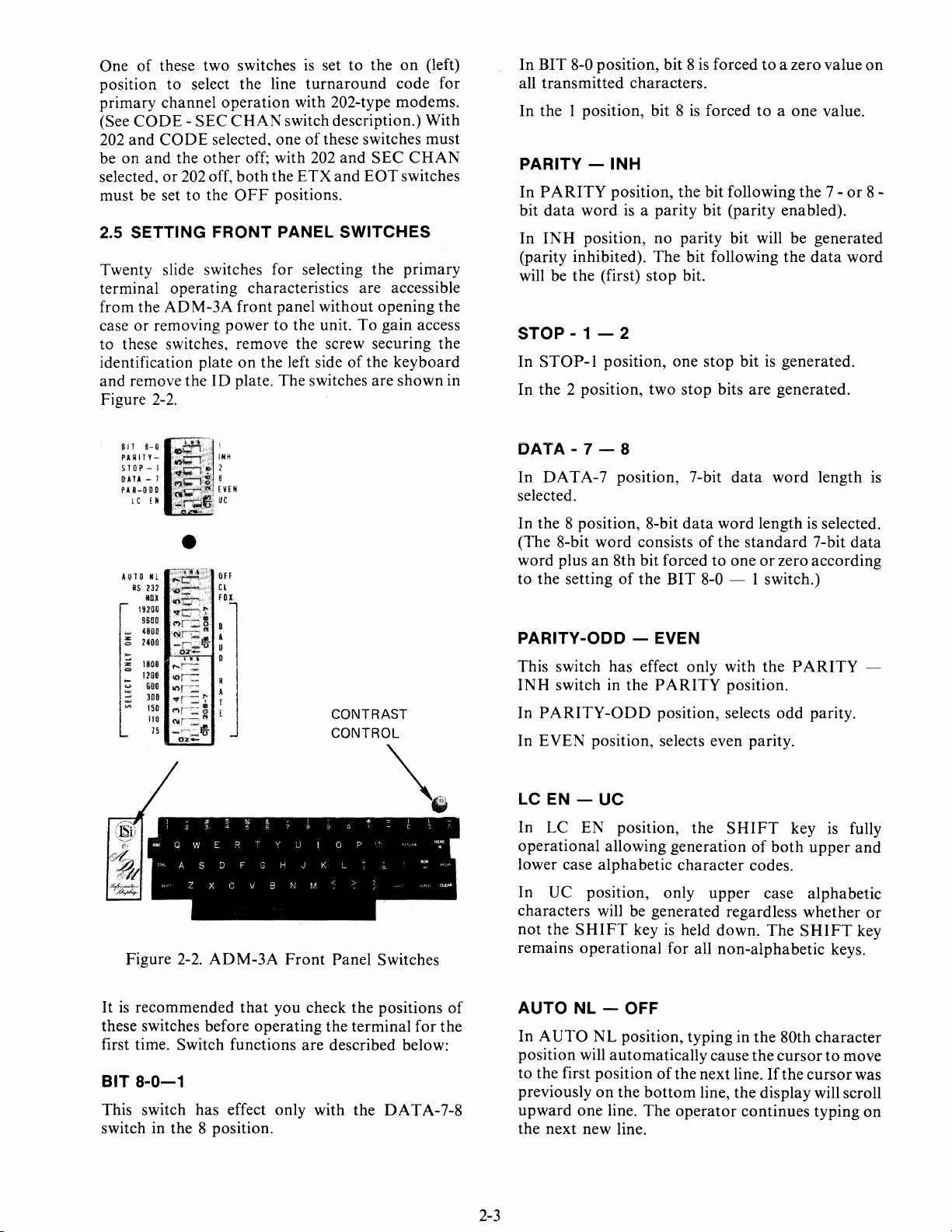

2.5 SETTING FRONT PANEL SWITCHES

Twenty slide switches for selecting the

primary

terminal operating characteristics are accessible

from the

case

ADM-3A

or

removing power to the unit.Togain access

front

panel without opening the

to these switches, remove the screw securing the

identification plate

and remove the10plate. The switches are

on

the left sideofthe

keyboard

shown

in

Figure 2-2.

In

BIT

8-0 position, bit 8isforcedtoa zero value

all

transmitted

In

the I position, bit 8isforcedtoa

PARITY

In

PARITY

bit

data

wordisa

In

INH

(parity inhibited).

will be

the

characters.

-INH

position,

position,

(first)

the

bit following

parity

no

The

stop

bit (parity enabled).

parity bit will be generated

bit following

bit.

STOP - 1 - 2

In

STOP-I

In the 2 position,

position, one

two

stop

stop

bits

one

value.

the

7 -or8 -

the

data

bitisgenerated.

are

generated.

on

word

BIT 8-0

PARITVSTOP

I'lATA

- J

PAR-ODD

l C £

AUTO

RS

1I0X

19200

9600

4BOO

:;

2400

...

:;

18011

1200

..,

....

I

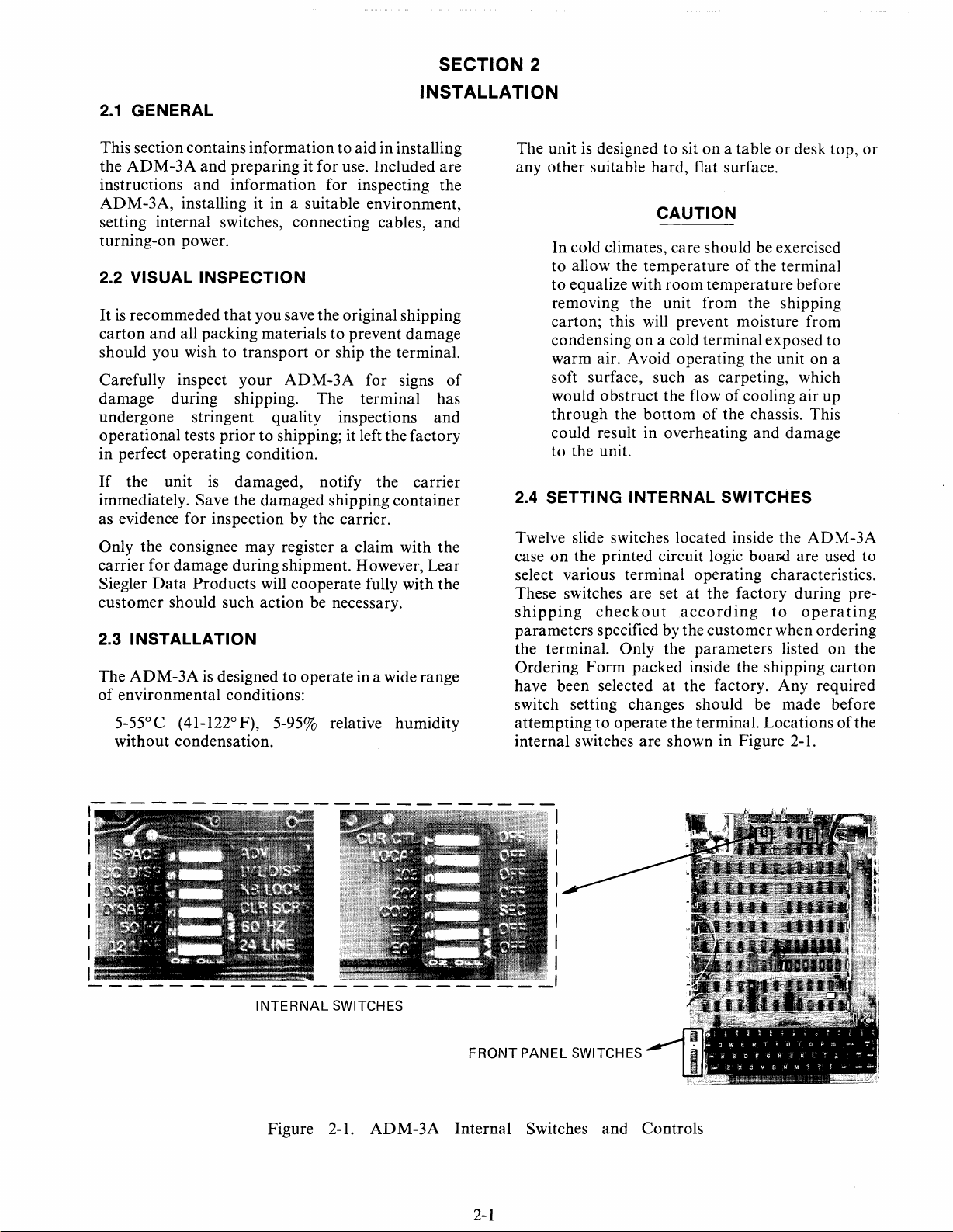

Figure 2-2.

- I

II

•

III Off

232

600

300

ISO

ilO

15

It

3

Q

W

A

S

Z

X

ADM-3A

I

IHH

2

e

[

VEil

UC

Cl

fOX

E R

D

C

DATA - 7 - 8

In

OAT

A-7 position, 7-bit

data

word

length

is

selected.

data

word

In the 8 position, 8-bit

(The 8-bit

word

consistsofthe

lengthisselected.

standard

7-bit

data

word plusan8th bit forcedtooneorzero according

to the setting

of

the

BIT

8-0 - I switch.)

PARITY-ODD - EVEN

This switch has effect only with

INH

switch in the

PARITY-ODD

CONTRAST

CONTROL

~

!,

y

F

G

V

N

M

8

p

0

K

"

In

In

EVEN

LC EN -

position, selects even parity.

UC

In LC EN position, the

operational

lower case

allowing

alphabetic

In UC position, only

PARITY

position, selects

generationofboth

character

upper

characters will be generated regardless

not

the

Front

Panel Switches

remains

SHIFT

operational

keyisheld down.

for all

the

PARITY

position.

odd

parity.

SHIFT

key

upper

codes.

case alphabetic

whether

The

SHIFT

non-alphabetic

is

keys.

-

fully

and

or

key

It

is

recommended

these switches before

first time. Switch functions

BIT

8-0-1

that

you check the positions

operating

the terminal

are

described below:

This switch has effect only with the

switch in the 8 position.

OAT

for

A-7-8

of

the

AUTO

In

AUTO

position will

to the first position

previously

upward

the

next

2-3

NL - OFF

NL

position, typing in

automatically

on

the

bottom

one line.

The

new line.

the

80th

cause the

of

the next line.Ifthe

cursortomove

line, the display will scroll

operator

continues typing

character

cursor

was

on

In

OFF

position, the

is

disabled. Continued typingatthe 80th character

position transmits each new character

the 80th character

RS232 - CL

In

RS-232 position, selects RS-232C communi-

at

cations

connector

In

CL

the

on

the rear panel.

position, selects 20m A current loop

communications

automatic

on

the display.

MODEM

at

the

New Line function

and

changes

(computer) interface

MODEM

interface

connector.

HDX-FOX

In

HDX

Characters typed are transmitted and automatically

echoed back from the

display.

position, selects half duplex operation.

ADM-3A

110 Channel for

top

of

the case. (See Figure 2-1.) Background

intensity

terminal

is

is

readjustment

adjusted

at

the factory before the

shipped and should

priortousing the terminal.

not

require

In

FDX

position, selects full duplex operation.

Characters typed are displayed only if echoed back

by the

computerormodem.

Communication Rate Switches

19200

9600

B These switches are used to select

4800

A the

U

2400

1800

O puter and auxiliary device.

send/receive

communications

rate for

with the com-

data

1200

600

R Setting one switch to

A hand (BAUD RATE)

300

150

T selects the associated rate.

the left-

position

110

EI

75

NOTE

Only one

selected (left position)

2.6 SETTING DISPLAY

BAUD

RATE

switch may be

at

a time.

CONTROLS

Figure 2-3. Background Intensity

Because

(located in

the

topofcase)

WARNING

Background

control must be adjusted with the

3A case open with power on, it should be

adjusted only by qualified service

personnel.

ON/OFF

The power

Switch

ONIOFF

switchislocatedonthe

3A rear panel.

2.7

CONNECTING

ON POWER

a.

With the

position, plug the

proper

the

CABLES AND

ONIOFF

ADM-3A

AC

power outlet.

switch in the

Control

Intensity

ADM-

ADM-

TURNING

OFF

power cord into

Contrast

The

Contrast

keyboard

operatortoadjust brightnessofthe characters

the

optimum

for

turned

clockwisetoincrease character brightness,

counterclockwise

Background intensity

controlislocatedtothe rightofthe

on

the

ADM-3A

readability. The

to

front panel.Itis

Contrast

decrease brightness.

used by

knob

A Background Intensity potentiometerislocated

inside the

ADM-3A

caseonthe circuit

board

in the

b. Connect the interface cable from the

or

modem

connector

c.

Connect the interface cable from the auxiliary

is

device (if present in your system)

EXTENSION

ADM-3A

d. Check the settings

verify

that

operation in

to

the

on

the

ADM-3A

interface connector

rear panel.

of

all front panel switches

the

terminalisset

your

system. Ivlakt; switl;h setting

MODEM

rear panel.

up

for

computer

interface

to

the

on

the

to

proper

changes if necessary.

2-4

e.

Set the ON /

position.

f.

Allow approximately20seconds for the unit

warm up.

OFF

power switch to the

• If the cursor control mode has been

selected, a reverse block cursor should

appear

• If the cursoe control mode

underline cursor should

bottom

• If the cursor does

contrast control

proper

in the

upper

left cornerofthe screen.

leftofthe screen.

not

on

intensity.

is

appear

appear, adjust the

the front panel for

OFF

near

ON

to

an

the

NOTE

If the Full-Duplex mode

at

typing

characters unless echo-back

by the

duplex

only if clear-to-send

disconnected.

the keyboard will not display

computer

is

selected,

or

modem. If half-

data

will be displayed

is

presentorcable

is

selected,

is

provided

is

2-5

3.1

GENERAL

SECTION 3

OPERATION

This section contains information

for using the

ADM-3A

keyboard facilities, and for

programming control functions

The keyboard allows the

transmit to the

128

all

3.2 DISPLAYING CHARACTERS

In the

USASCII character codes.

standard

computer

operator

(and/orauxiliary device)

ADM-3A,

and

instructions

at

the computer.

to generate and

64

characters are

displayed on the screen (upper case alphabet,

numbers

most symbols

and

punctuation).

and

When a non-displayable lower case character

typed, the

proper

lower case codeistransmitted

but

the characterisdisplayed as upper case.

If

your terminal contains the

95

Display feature,

characters will be displayed

(upper and lower case alphabet, numbers

and

punctuation

symbols).

NOTE

Upper/Lower

and

Case

all

Typingatthe keyboard always generates

codes which are transmitted; however, in

to

order for characters

be displayed

control codes to affect the

display the codes must be echoed back

the

ADM-3A

display memory

control logic, either by the

(FDX)

or

the

ADM-3A

I/O

and

ADM-3A

to

and

computer

Channel

(HDX).

All display actions described in the key

that

descriptions

follow assume the

generated codes are echoed.

If

the front panel

AD

V position, the space codeisnon-destructive

after typing the

or

computer

can space over

SPACE-ADV

RETURN

switchisin the

key;

that

is, the

operator

dataonthe line without

overwriting each character with a space. The space

bar

remains non-destructive following a

function until a LINE

LINE FEED Key

FEED

codeisgenerated.

RETURN

A codeisgenerated by this key which causes the

to

cursor

on

upward one line.

is

cursor to the first character position

SHIFT Keys

Eitherofthe two

typing

alphabetic characters

shown in the upper portion

move downward one line.Ifthecursorwas

the

bottom

line, the entire display will scroll

LINE

FEED

does

not

of

SHIFT

another

Setting the

key to generate

"LC

the front panel

keysisheld down while

or

to generate the character

of

a typed key.

NOTE

EN - UC" switch

ID

plate

to

return the

the new line.

upper

case

under

the UC

position causes upper case alphabetic

characters

without the

SHIFT

key remains operational for all

be generated with

SHIFT

key depressed. The

or

to

non-alphabetic keys.

RUB (Rubout) Key

When typed while holding down the

transmits a non-displayable

Rubout

SHIFT

key

code (ASCII

DEL)tothe computer. The cursorisnot advanced

and

the character code stored in the

ADM-3A

display memoryisnot overwritten.

3.3 SPECIAL

FUNCTION

KEYS

In additiontothe displayable character keys, the

ADM-3A

keys for various terminal

functions. Use

RETURN Key

keyboard contains a

and

of

these keysisdescribed below;

number

of

system control

other

A codeisgenerated by this key which moves the

of

cursor to the first character position

the line.

The

Rubout

computer

functionisnormally usedtotell the

that

a previous character should be

deleted.

The lower case RUB key transmits/displays

underline.

REPT (Repeat) Key

When held down while pressing a character key,

at

repeats the character

the terminalisoperatingata

a rateof12.5 per second.

baud

rate

permit 12.5 cps transmission, the repeat rate

reducedtothe transmission rate.)

3-1

that

will

an

(If

not

is

Space Bar

The

Space

key.

Causes

and

blank

exceptions

Bar

is'

consideredadisplayable

the

ASCII

storedinthe

spacetoappearonthe

see

code

ADM-3A

RETURN

CTRL (Control) Key

When

held

down

while

the

code

patternofthe

to

oneofthe

Code

chart.

The

ADM-3A

possible

haveafunction

in

Table

two

ASCII

3-1.

control

is

capable

codes,

within

foraspacetobe

display

screen.

Key).

typing

typed

the

another

key.

code

columnsinthe

of

although

machine.

The

generating

only

character

transmitted

memory

(For

key,

codeisforced

These

the

modifies

14

of

are

and

ASCII

all 32

only

them

listed

column-code

sequence.Inany

codetobe

CLEAR

a

Typing

SHIFT

function

SCREEN

(SPACE

mde,

transmittedtothe

Key

the

CLEAR

key clears

may

-

the

be

disabledbythe

DISABLE

through0)to

causes

key while

entire

the

computer.

screentospaces. (This

Switch.)

complete

ASClI

holding

internal

ESCape

down

CLEAR

the

the

HERE IS Key

If

your

terminalisequipped

Answer

identification

special

the

In

capability,

Back

memory)toidentify

computer

terminals \\lithout

this key

feature,

message

that

typing

(storedinthe

a message istofollow.

hasnofunction.

with

this key

your

terminal

iA,-utomatic

the

Automatic

transmits

ADM-3A

and

alert

i~ns,ver

Back

an

in a

Backspace (CTRL/H).

typed

while

holding

moves

the

transmittedtothe

in

Bell

ADM-3A

non-destructively

left.

The

conjunction

(CTRL/G)

and

CTRL/

computer.

with

Sounds

transmits

down

the

Each

time

theHkey

the

CTRL

one

character

H

backspace

CTRL/Hmaybeused

Repeat

the

the

CTRL/

key.

audible

key,

position

beepinthe

G bell

the

UPLINE (CTRL/K)

When

reverse-block

Return (CTRL/M).

RETURN

Line Feed (CTRL/J).

the

in

LINE

the

Cursor

cursortomove

key.

FEED

key.

Control

Duplicates

Duplicates

Mode,

upward

the

functionofthe

the

causes

one

function

Lock Keyboard (CTRL/O). Electrically

(disables)

further

unlocked

clearing

power

FORWARD SPACE

When

reverse

HOME

When

reverse

cornerofthe

the

ADM-3A

keyboard

byacontrol

the

off,

thenonagain.

in

the

block

activities.

screen

with

Cursor

cursortoadvance.

CURSOR (RS)

in

the

Cursor

block

cursor

screen.

keyboard,

The

code

from

the

CLR

(CTRL/M)

Control

Control

to

return

preventing

keyboard

the

keyorby

Mode,

Mode,

to

the

computer,

causes

causes

upper

ESCAPE KEY (ESC)

When

cursor

character,arow

in

Cursor

sequence.

Control

ESC

code

(SPACE

must

Mode,

be

followed

through7)and

initiatesaload-

cursor

code

code.

line.

locks

can

turning

by

an

to

the

of

any

be

the

the

left

is

is

BREAK

This key

function,

message.

Key

activates

normally

the

standard

usedtointerrupt

teletypewriter

an

incoming

Break

NOTE

The

Break

the

the

cause

your

BREAK

key

down

the

terminal.

functionissustainedaslong

keyisheld

foranextended

computer

down.

to

disconnect

period

as

Holding

may

from

3.4 PROGRAMMING & WORD STRUCTURE

The

=

a

computertowhich

has

full

control

functions

keyboard,

be

executed

The

ting

character

codes

3.4.1

The

control

Backspace

non-destructively

left.

which

plus a few

computer

the

appropriate

codes

will be

are

from

controls

will be

recognized

Remote Control Functions

remote

computer

functions:

BS

Bell BEL (CTRL/G).

the

ADM-3A.

Return CR (CTRL/M)

destruciively

present

to

line.

the

over

the

possible

additional

the

computer.

the

ASCII

displayed,

and

can

(CTRL/H).

one

character

Sounds

the

first

ADr-.1-3,A.isinterfaced

terminal.

from

functions,

ADM-3A

codes.

acted

perform

Moves

the

Moves

character

All

control

the

ADM-3A

can

by

transmit-

Displayable

and

valid

control

upon.

the

following

the

cursor

positiontothe

audible

the

positionofthe

beep

cursor

also

in

non-

3-2

Line Feed

IF

(CTRl/J).

Causes the entire

display to move upward one line, leaving the

cursor positioned in the same

character

position

on the next new line.

Upline (VT) - Moves cursor up vertically when

Cursor

in

Forward Space (FF) - Moves

when in

lock

locks the

Control Mode.

Cursor

Control

Keyboard

ADM-3A

cursor

Mode.

SI

(CTRl/O).

Electrically

keyboard, disabling all

forward

keyboard functions.

Unlock Keyboard SO

ADM-3A

keyboard, restoring all keyboard

(CTRl/N).

Unlocks the

functions.

Clear Screen SUB

character

memory

(This function

positions in the

and

clears the screentoblank

may

(DISABLE-CLEAR

Home Cursor (HOME) - Causes the

returntothe

in the

load

Cursor (ESC =YX) - This

Cursor

upper

Control

sequence causes the

row

and

and

X respectively.

column

defined bythe

The Reference Tables

(CTRl/Z).

ADM-3A

Clears all

display

spaces.

be disabled by

SCREEN

the

internal

switch.)

cursor

left

cornerofthe screen, when

Mode.

four-character

cursortobe positionedtothe

3-1

and

ASCII

3-2ofthis

values

manual

of

to

show the actual binary codes generated by the

ADM-3A

and

used for

computer

controlofthe

terminal.

Y

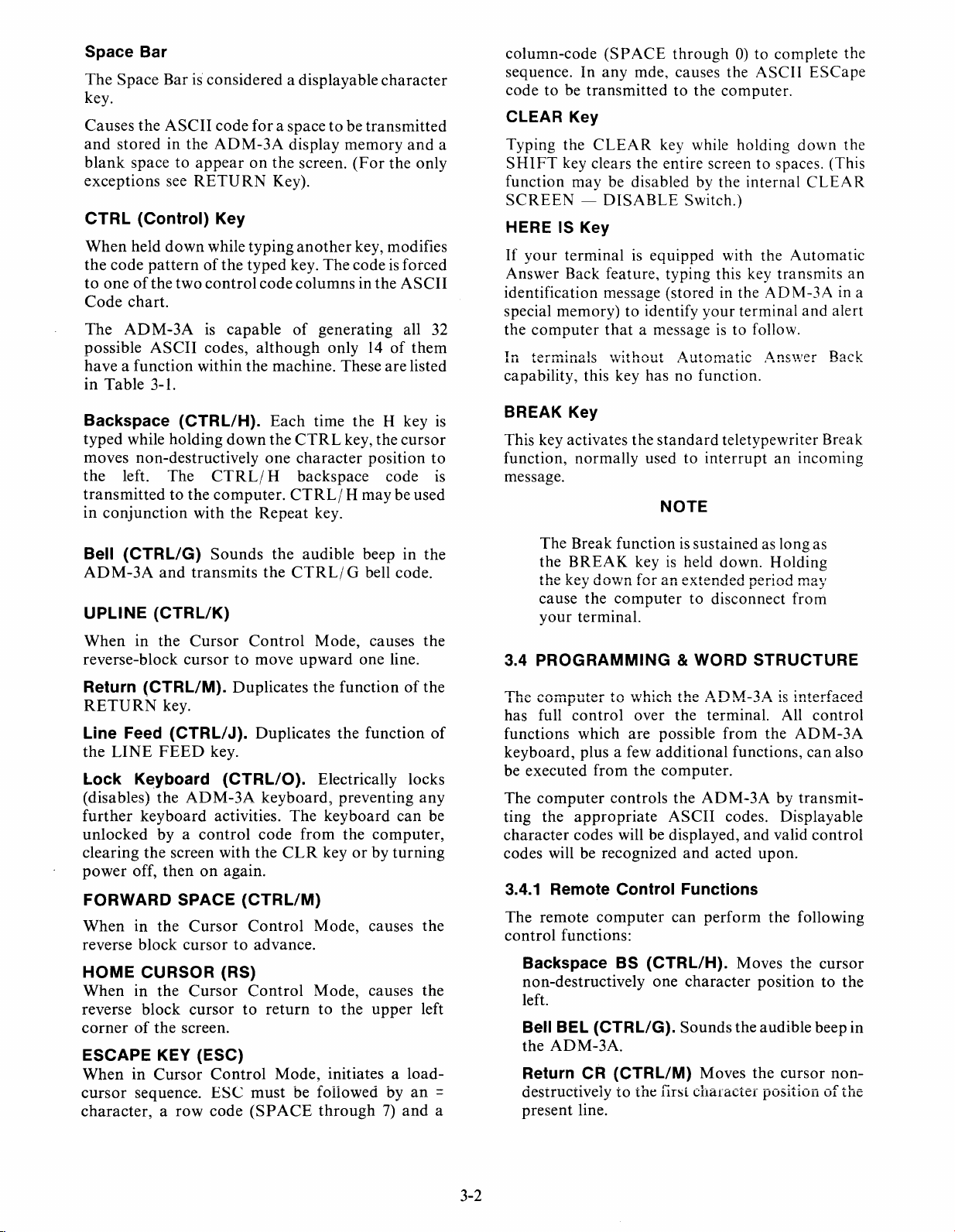

Table 3-1.

ASCII

Code Mnemonic Function ADM-3A

CTRL/@

CTRL/A

CTRL/B

CTRL/C

CTRL/D

CTRL/E ENQ

CTRL/F

CTRL/G BEL

CTRL/H BS

CTRL/I HT

CTRL/J

CTRL/K

CTRL/L

CTRL/M

CTRL/N

CTRL/O

CTRL/P

CTRL/Q

CTRL/R

CTRL/S

CTRL/T

CTRL/V

CTRL/V

CTRL/W

CTRL/X

CTRL/Y

CTRL/Z

CTRL/[

CTRL/x

CTRL/]

CTRL/A

NUL

SOH

STX

ETX

EaT

ACK

LF

VT

FF

CR

SO

SI

OLE

OC1

OC2

OC3

DC4

NAK

SYN

ETB

CAN

EM

SUB

ESC

FS

GS

RS

AD

M-3A Control Codes

as

Available

modem operation

Availableassecondary channel line

modem operation

Initiates

option*

Sounds audible beep in

Backspace

Line Feed

Upline

Forward Space

Return

Unlock

Lock

Keyboard*

Clear Screen

Initiate Load Cursor

Home

secondary channel line

10 message in

Keyboard*

Cursor

terminals

AOM-3A

with

turnaround

turnaround

automatic

code

for

code

for

"Answer

202

202

Back"

*Executable

only

from

computer.

3-3

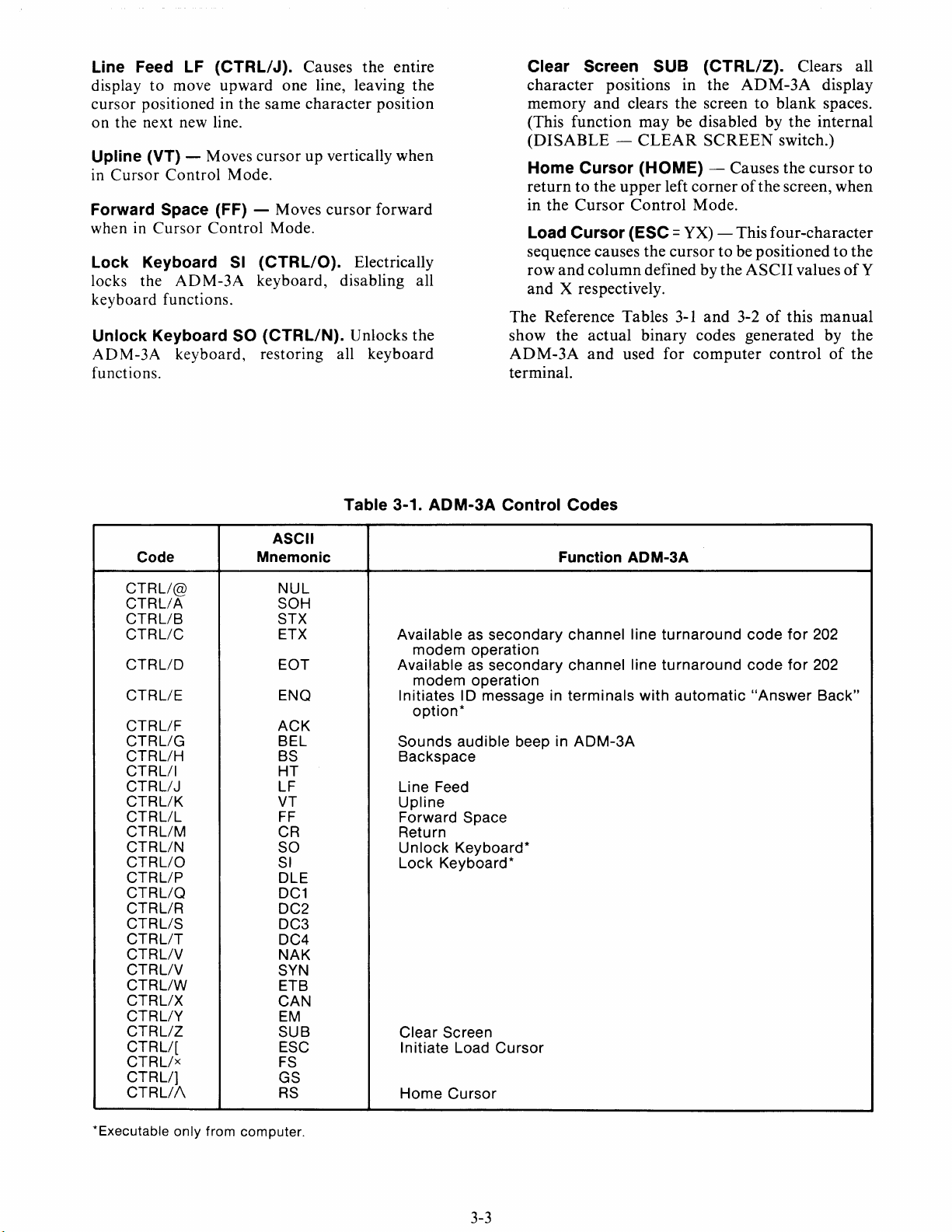

Table 3-2 USASCII Character Codes

GRAPHIC CHARACTER

CONTROL SET

BITS BITS

4321

765

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

......

f"\f"\

IIUU

0

000

NUL

SOH

STX

ETX

EOT

ENQ

ACK

BEEP

BS

HT

LF

VT

........

rr

1

001

OLE

DC1

DC2

DC3

DC4

NAK

SYN

ETB

CAN

EM

SUB

ESC

....

t'"'

rv

2

010

SP

!

"

# 3

$

0/0

&

( 8

) 9

*

+

,

3

011

1 A

2 B

4

100

@

5 6

101

P

Q

R

C S

4 0 T d

5 E

6

7 G W

F V

U

H X

Y i

Z j

[

\

,/

...........

I

J

K

I \ I

L

110

a

b

c s

e

f v

9

h x

k

I

7

111

P

q

r

t

u

w

Y

z

{

1101

1110

1111

""

CR

SO

SI

GS

RS

US

.........

Control

Codes

(Generated by

holding

key

the

key shown in

CTRL

while

typing

corresponding

col-

umns 4 and 5.)

3.4.2 Data Character Format

The

ADM-3A

America

change).

many

ADM-3A

the

f_l

..

n

_n_;"'u

\PiU",

peu

USASCIIisa 7-bit code. But because

of

the computers

iLy

uses

Standard

USASCII

Code for Information Inter-

and

(United States

other

devices to which

may be interfaced use 8-bit words

"'_

.,,;

...

\.."'

.....

Vi"'lLUVUL

_n_;"'u\

peu

"'\"0

iLyhLa,,-

i\

nl\.,f'2i\

rl.L'

",++0_"

U.L

-.)rl.

Vii"-i"

a wide choiceofword formats selectable by the user.

of

,,,

-

=

>

/

? 0

Displayable in

standard

~

M

N

ADM-3A

]

f\

+

m

}

,......

n

DEL

0

,

...

T

I

Displayable

with

ADM-3A

Upper/Lower

Case Display

feature.

3-4

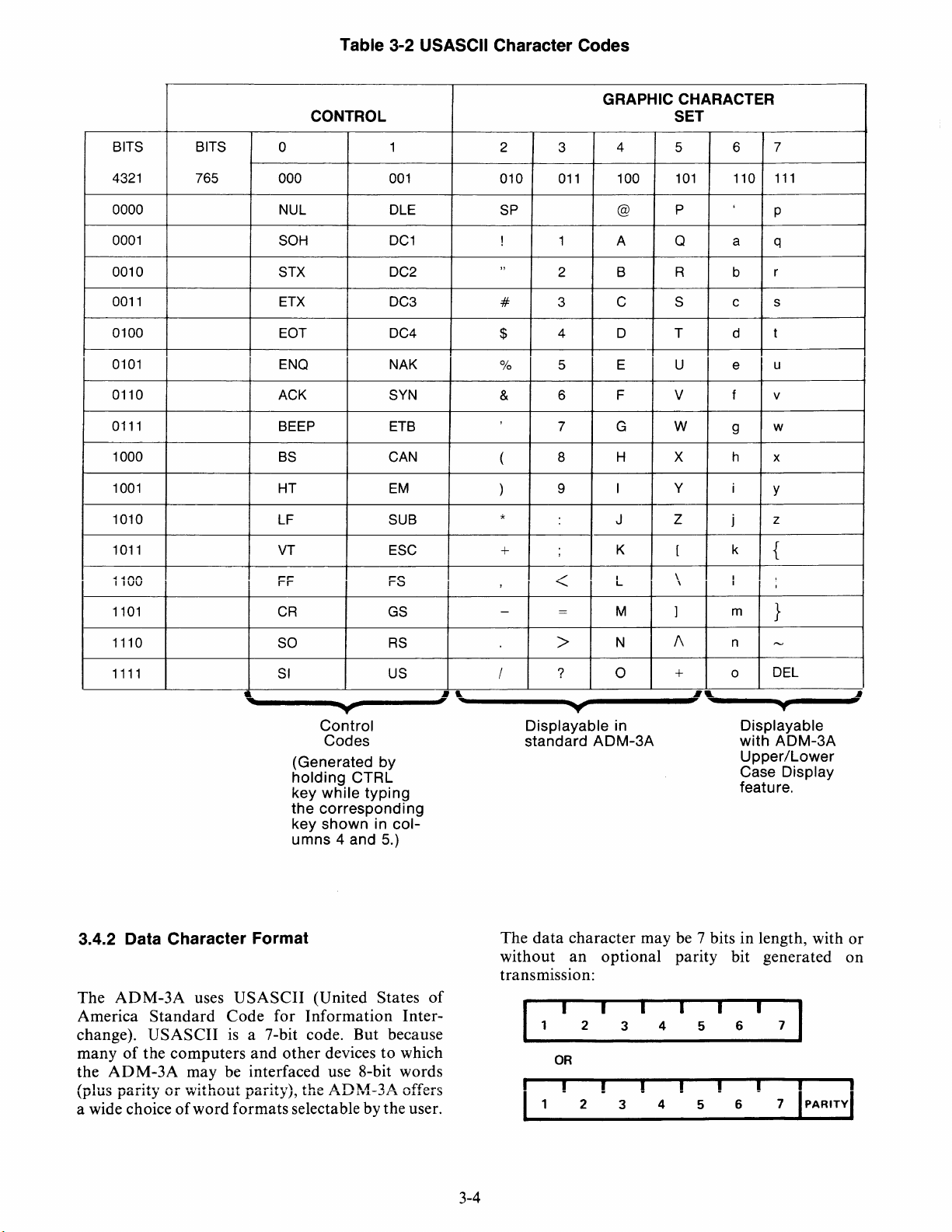

The

data

character may be 8 bits in length, plus

without

the optional parity bit.Inthe caseof8-bit

characters, bit 8

by the user.

is

always forcedto1or0as selected

or

DATA

(7 OR 8 BITS)

PLUS

OR

WIO

PARITY

OR

DATA(7OR8BITS)

PLUS OR

WIO

PARITY

3.4.3 Data Transmission Format

The

ADM-3A

This means each

uses

asynchronous

transmission.

characteristransmitted as a

complete, self-contained message consisting

data

character withorwithout

start

bit

and

followed by

parity, preceded by a

oneortwo stop bits.

of

the

When the

start

bitisreceived, a clock signal

initiatedtoclock in the remainderofthe word. The

one

or

two stop bits are usedtosignify the endofthe

word

and

terminate the receive clock.

Generally, transmission rates

use two stop bits,

stop

bit.

The

ADM-3A

and

control

ratesof150

codes

set are shown in tables

3-1

of

110

baud

and

higher use one

and

the USASCII code

and

3-2, respectively.

and

lower

is

3-5

4.1

GENERAL

SECTION

4

THEORY OF OPERATION

4.2.2 Display Refresh Operation

This section describes the

ADM-3A

first described with reference to

diagram, and then each element shown in the block

diagram

illustrations and to logic diagrams contained in

Section 6

4.2 GENERAL

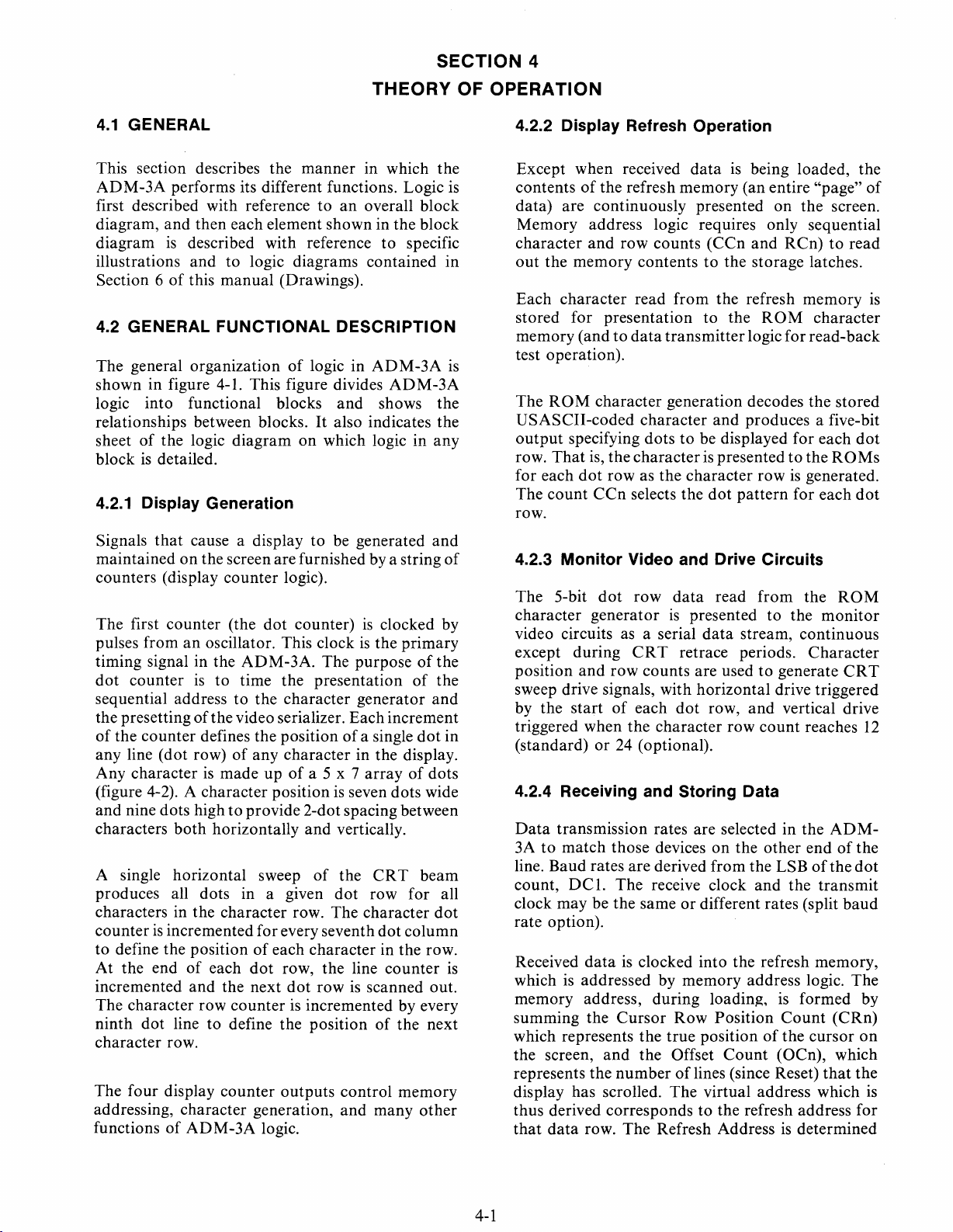

The general organizationoflogic in

shown in figure 4-1. This figure divides

logic into functional blocks and shows the

relationships between blocks.

sheet

block

4.2.1 Display Generation

Signals

maintained

counters (display counter logic).

The first counter (the

pulses from

timing signal in the ADM-3A. The purpose

dot

sequential address

the presettingofthe video serializer. Each increment

of

the counter defines the positionofa single

any line (dot row)

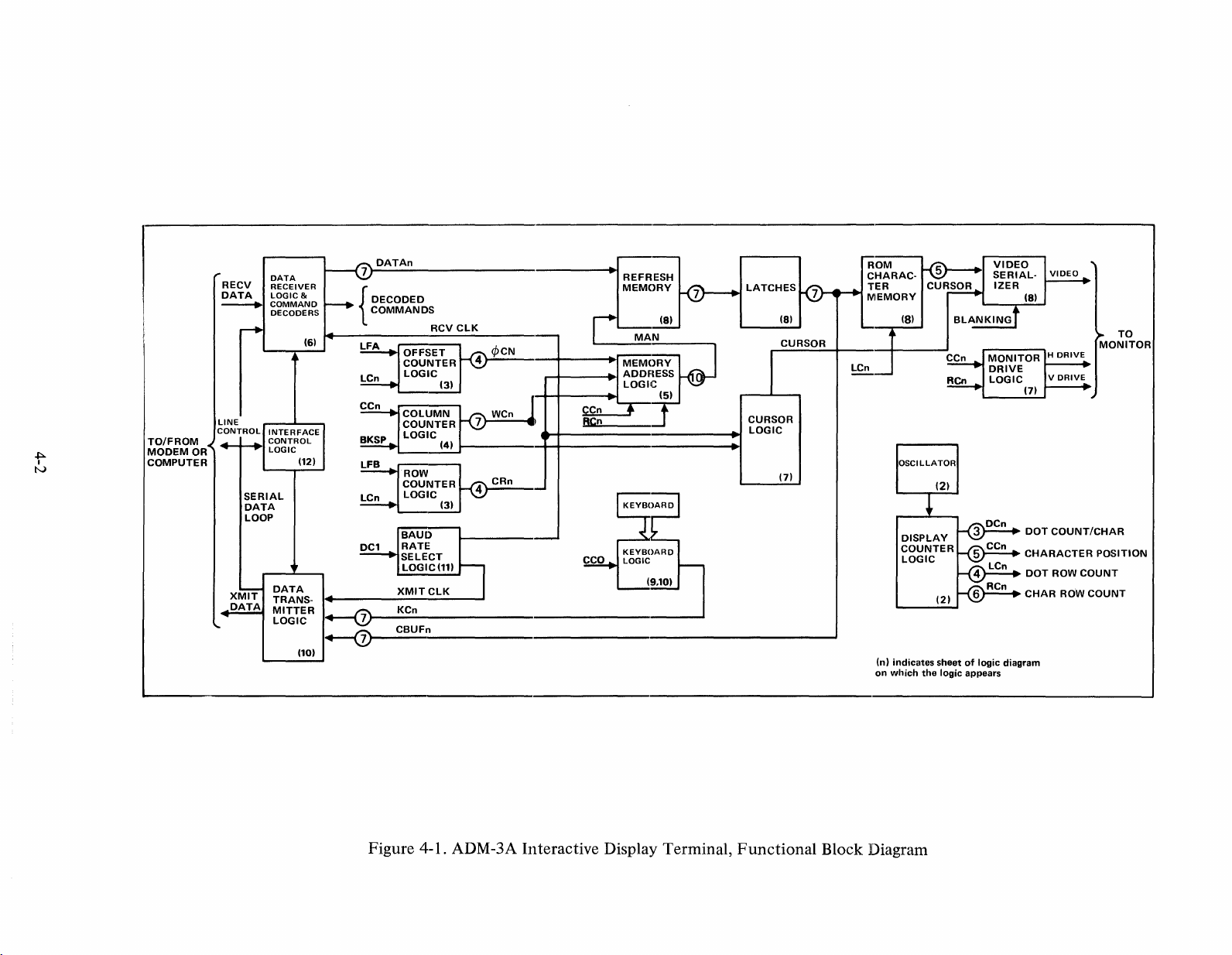

Any character

(figure 4-2). A character position

and nine dots high

characters

A single horizontal sweep

produces all dots in a given

characters in the character row. The character

counterisincrementedfor every seventh dot column

to define the position

At the end

incremented

The character row counter

ninth dot line to define the position

character row.

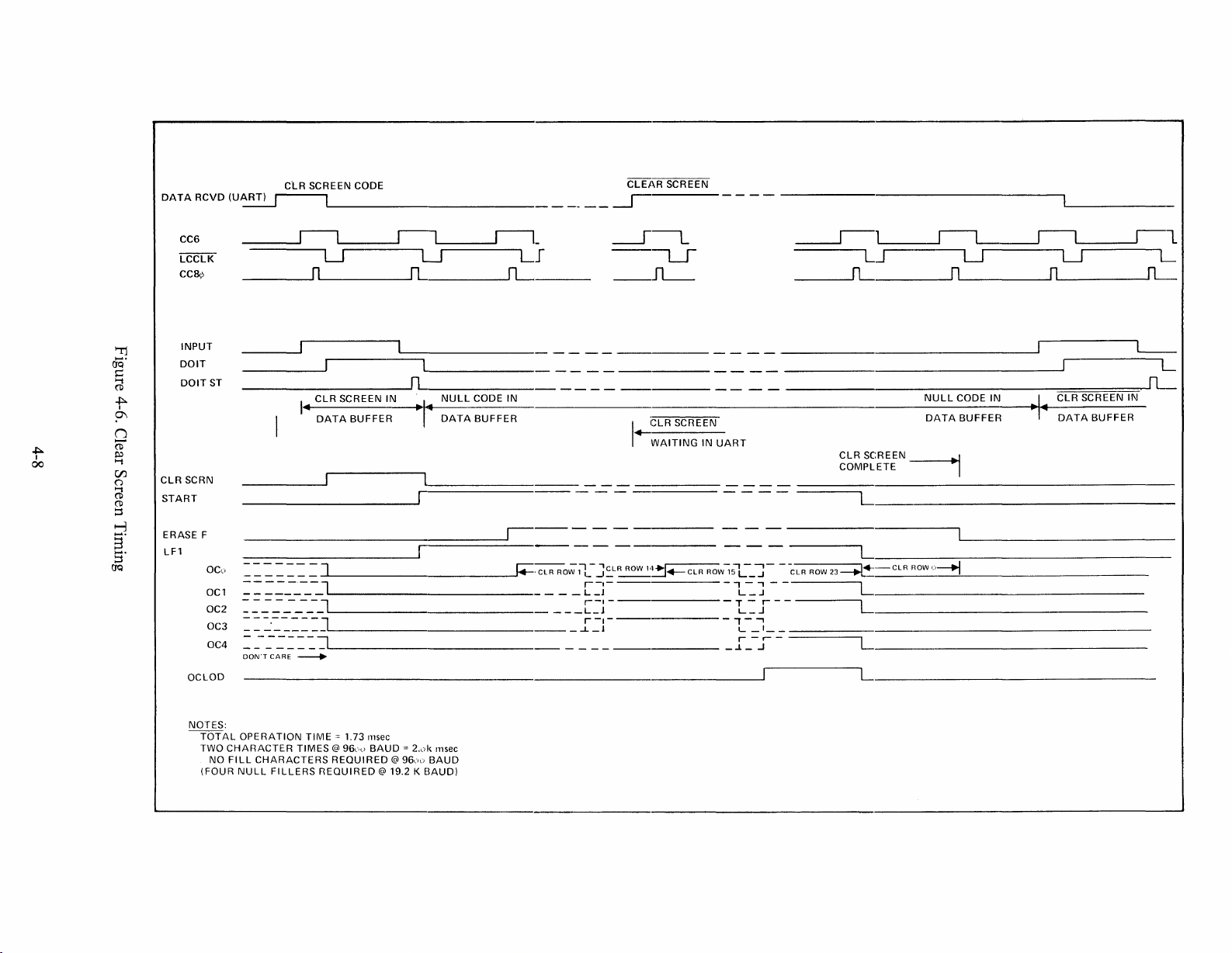

The four display counter outputs control memory

addressing, character generation, and many

functionsofADM-3A

performs its different functions. Logic

is

described with reference to specific

of

this manual (Drawings).

FUNCTIONAL

of

the logic diagram

is

detailed.

that

cause a display to be generated and

on

the screen arefurnished by a string

an

oscillator. This clockisthe primary

counteristo

both

of

and

time the presentation

to

of

any character in the display.

is

made upofa 5 x 7

to

provide 2-dot spacing between

horizontally and vertically.

of

each

dot

the next

manner

It

on

dot

counter)isclocked by

the character generator

of

each character in the row.

row, the line

dot

rowisscanned out.

is

incremented by every

logic.

in which the

an

overall block

DESCRIPTION

ADM-3A

AD

also indicates the

which logic in any

of

arrayofdots

is

seven dots wide

the

CRT

dot

row for all

counter

of

the next

M-3A

of

the

the

and

dot

beam

dot

other

of

in

is

Except when received

is

is

contents

data) are continuously presented

Memory address logic requires only sequential

character

out

Each character read from the refresh memory

stored for presentation to the

memory (and

test operation).

The

USASCII-coded character and produces a five-bit

output

row.

for each

The count

row.

4.2.3 Monitor Video and Drive Circuits

The 5-bit

character generatorispresented to the

video circuits as a serial

except during

position

sweep drive signals, with horizontal drive triggered

by the

triggered when the character row

(standard)or24 (optional).

4.2.4 Receiving and Storing Data

Data

3A

line. Baud rates are derived from the LSB

count,

clock may be the same

rate option).

Received

which

memory address, during loading,

summing the

which represents the true position

the screen,

represents the

display has scrolled. The virtual address which

thus derived corresponds to the refresh address for

that

of

the refresh memory (an entire "page"

and

row counts (CCn and RCn)toread

the memory contentstothe storage latches.

to

data

ROM

to

data

character generation decodes the stored

specifying dotstobe displayed for each

That

is, the characterispresentedtothe

dot

row as the character rowisgenerated.

CCn

selects the

dot

row

CRT

and

row counts are usedtogenerate

startofeach

transmission rates are selected in the

match those devices on the other endofthe

DC1.The receive clock and the transmit

dataisclocked into the refresh memory,

is

addressed by memory address logic. The

Cursor

and

the Offset

numberoflines (since Reset)

row. The Refresh Addressisdetermined

dataisbeing loaded, the

of

on

the screen.

ROM

transmitterlogicfor read-back

dot

pattern

data

read from the

data

stream, continuous

retrace periods.

dot

row,

and

count

or

different rates (split

Row Position

of

Count

character

dot

ROMs

for each

Character

vertical drive

reaches

is

formed by

Count

the cursor

(OCn), which

ROM

monitor

CRT

AD

of

the

baud

(CRn)

that

dot

M-

dot

on

the

12

is

is

4-1

+:>.

I

tv

TO/FROM

MODEM

OR

COMPUTER

RECV

DATA

LINE

CONTROL

SERIAL

DATA

lOOP

DATA

RECEIVER

LOGIC

&

COMMAND

DECODERS

INTERFACE

CONTROL

LOGIC

(12)

DATA

TRANSMITTER

lOGIC

(10)

DATAn

DECODED

COMMANDS

{

(6)

~

----0-~-----.-----.----'

+---0)--------------.--------1

KCn

CBUFn

RCV

ClK

....-.....-----+-1

REFRESH

MEMORY

MEMORY

ADDFIESS

lOGIC

(5)

(9.10)

lATCHES

(8)

CURSOR

lOGIC

(7)

(n)

on

indicates

which

OSCILLATOR

sheetoflogic

the

logic

appears

DOT

CHARACTER

DOT

CHAR

diagram

VIDEO

COUNT/CHAR

POSITION

ROW

COUNT

ROW

COUNT

Figure 4-1. ADM-3A Interactive Display Terminal,

Functional

Block Diagram

by

another

Row

Received commands are decoded and used

control

Feed, Backspace, Carriage Return,

functions.

4.2.5 Cursor Generation

The cursor marks the position

which the next character will appear. When the

Cursor

will be entered in the

cause the display to roll upward. The cursor

formed by displaying five dots in the eighth

ninth

rests.

logic alongwith character bits read from the ROMs.

When the

reverse block cursor

the reverse image

cursor currently resides.

The cursor position code WCn

refresh memory in read-back test operation.

circuit which sums the current Display

Count

dot

Cursor

(RCn) and the Offset

ADM-3A

Control

rowsofthe character position in which it

Cursor

logic.

Commands

switchisin the

bottom

informationisORed

Controlisin the

is

a 7 x 9

of

the character

Count

include Line

on

the display in

OFF

position,

row: Line Feed will

into video

0N

position, the

dot

figure containing

upon

is

used to address the

(OCn).

and

other

data

and

output

which the

to

4.2.6 Keyboard Logic

, The keyboard

compose

transmission. As a character

operator, it appears (as KCn)

logic, and (in half-duplex transmission)

into the refresh memory for display. In full-duplex,

communications characters originating

board

back from the

is

formatted

appearonthe display only if they are echoed

4.2.7 Data Transmitter Logic

Data

transmitter10gic receives characters generated

at

the keyboard

answerback logic

converts the seven-bit character into serial-bit form

along with start, parity,

In read-back test operation, the contents

memory buffer (CBUFn) may be accepted for

transmission in the same

lines.

and

associated logic are used

data

data

for

display

computerormodem.

(or

and

put

and

wordtothe modemorcomputer.

mannerasdata

and

simultaneous

is

typed by the

at

data

generated

on

KCn

stop bits, and sends the

transmitter

is

loaded

at

the key-

at

optional

lines) and

of

onthe KCn

to

the

DOT

COUNT

o 0

o 0

o 0

o 0

(DC)

0.0

0.00.

0.00.

0.00

COUNT

•

•

•

•

•

~7

00

o 0 0 0 0

0

•••••

O.

••••

•••••

000

•

••

•

•

•

•

•

•

o 0 0

r79

o 0

•

••

•

•

•

•

•

o 0

f

I-

Z

::J

0

U

:i:u

o...J

cr-

I-

0

0

!

8

f

I-

z

::J

0

U

:i:u

O...J

cr-

I-

0

0

~

0

-

~

.....

•

•

1-

•

.000.0

.000.00.

•••••

•

l-

z

::J

0

u

:i:

0

cr

crcr

w-

I-

U

«

cr

«

:I:

U

u

•

• •

•

•

•

•

•••••

•

•

•

• •

• •

•

_I

11

OR

23

I

-

-

CHARACTER

•

•

••••

•

•

•

•

•

••••

I

POSITION

(CC)

Figure 4-2. CRT Display Monitor

4.2.8 Interface Control Logic

This logic

Send

the

reverse-channel

control

the

other.

Switches

common

under

4.2.9

The

3A

is a

commercial

quality

The

construction

circuitsofthe

4.3

The

logic

diagram,

performing

Refertoblock

controls

exchanges

ADM-3A.

Clear-to-Send

between

Either

system

from

one

endofthe

internal

CRT

CRT

adapt

type

display

solid-state

the

logic

103

or

202

control.

Display Monitor

monitor

unit

installations

video

reproduction

monitor

LOGIC

following

features

for

reliability

TV

monitor

DESCRIPTION

paragraphs

representedbyeach

figure 4-1, as well as logic

functions

and

not

timing

modemorcomputer

a

code-turnaround

may

communication

to

modems,orto

employedinthe

for

useinindustrial

where

are

printed

and

are

describe

blockinthe

indicatedinFigure

diagrams

and

Request-to-

be

used

to

interface

reliability

and

desired.

circuit

uniformity.

transistorized.

the

operation

overall

and

that

accompany

or

transfer

line

with

operate

ADM-

high-

board

block

circuits

and

to

the

and

All

of

4- i.

the

text,

as well astothe

Section6in

this

manual.

logic

diagram

included

in

4.3.1 General Clear Circuit

a

Circuits

all

when

shownonsheet7of

control

logicinthe

applied

power

ADM-3A

causes

the

logic

tobeinitialized

the

+5Vdcsupply

diagram

cause

to

rise.

As

the

supply

retriggerable

signal

logic

the

CLEAR,

through

signal

actionofthe

voltage

one-shot,

the

whichisdistributed

six

inverters.Incircuit

TESTER

INITIALIZE

one-shot.

reaches

one-shot

trigger

creates

board

simulates

level

to

ADM-3A

of

the

reset

testing,

a

the

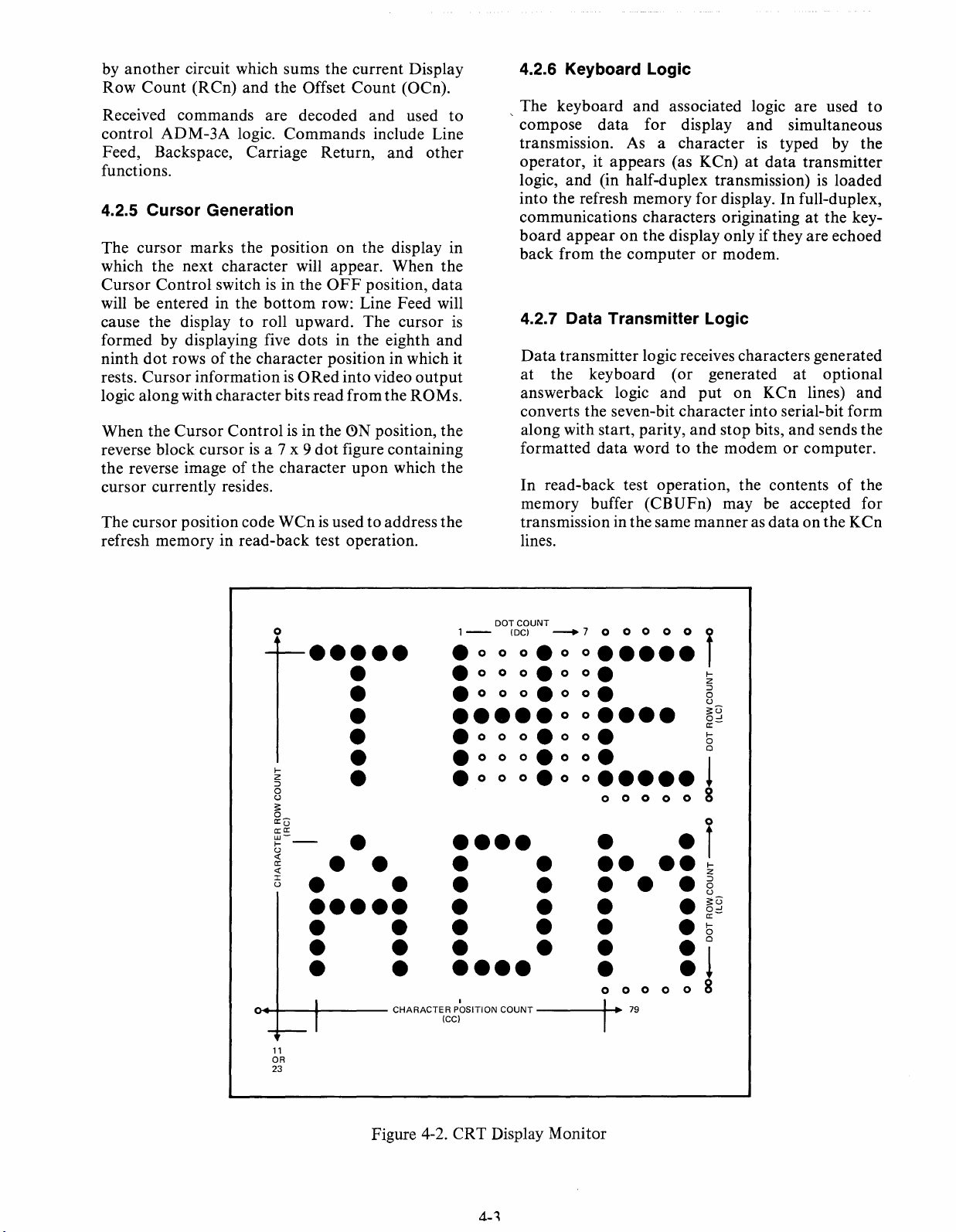

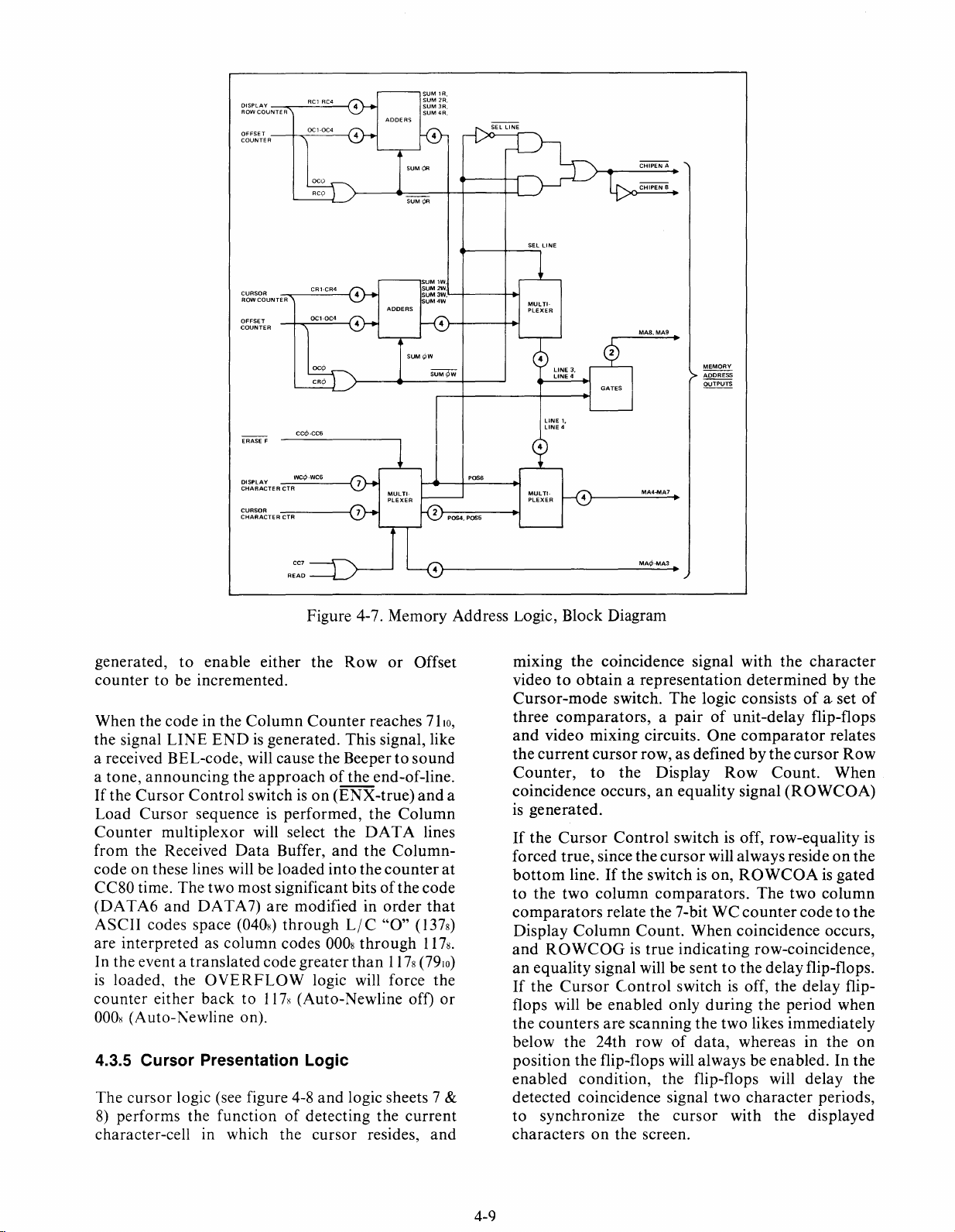

4.3.2 Display Counters

The

display

positions

character

define

and

the

the

display.

and

timingisshown

The

basic

byasimple oscillator

twice

the

the

dot

counters

and

dot

rows,

line,

and

character

positionofeach

position

Figure

clock

of

4-3 is a

is a

10.8864-MHz

video frequency.

counter.

provide

character

rows.

dotina

each

character

block

diagramofthis logic,

in figure 4-4.

circuit.

The

The

clock

a

count

position

These

character

in

signal

clock

frequency

(eLK)

of

dot

in a

counts

matrix,

the

total

generated

drives

is

SHEET 2

DC3

DCO -DC3

CCO-CC7

ICC80

LC3

LCO - LC3

RCO

- RC5

RC

RESET

Figure

4-3. Display

Counters,

4-4

Block

Diagram

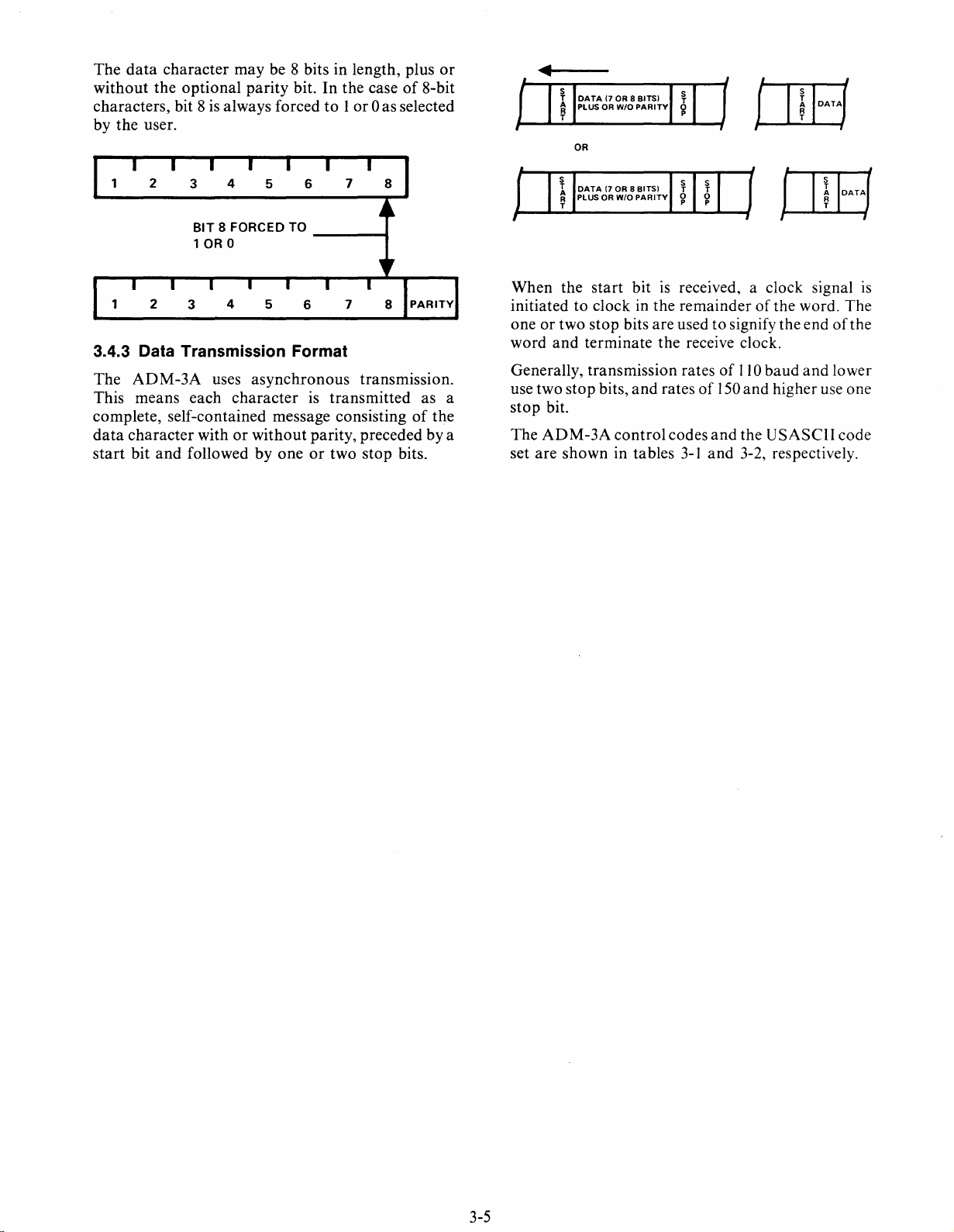

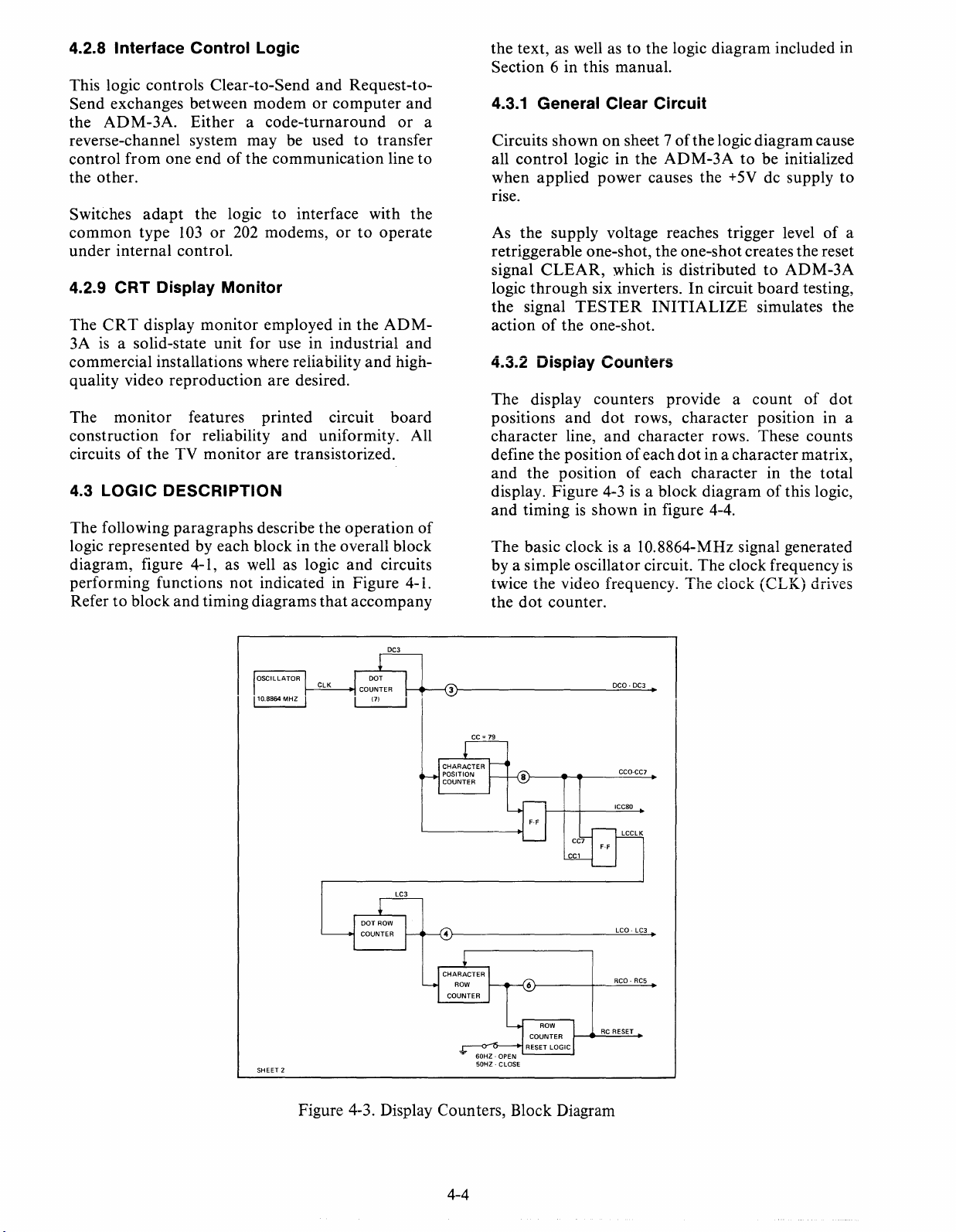

CLOCK

n..n..n.IlJlJ1I

PERIOD-643.¢¢39

nsee,

FREQUENCY

= 1.5552

MHA

DC¢~

DOT

DC1~

COUNTER

DC2~

PERIOD

DC3 U 1

CC¢

CC1

CC2

CC3

CC4

CC5

CC6

CC7

LCCLK

1---------------------::::=:;::::~::::=~;:;;.77'"'T7""".7"'7""::.._r"7_J

CHAR

VIDEOSRLOAD

U

= 555.555Msee,

COUNTER

FREQUENCY=1.8¢¢KHZ

RETRACE

POSITION

COUNTER

PERIOD

= 61.7284Msee

FREQ=16.2¢<iHDKHZ

H-

DRIVE

LC¢

LC1

LC2

LC3

CHARACTER

ROW

COUNTER.

51>

HZ

OPERATION

RC¢

RC1

RC2

RC3

I-----------------------J

RC4

RC5

t--------------------------------------.....J

6¢HZ

OPERATION

RC¢

RC1

RC2

RC3

RC4

RC5

(ALWAYS

LOW

DURING

6¢HZ

OPERATION)

6¢HZ

V-DRIVE

5I>HZ

J""L

LINE

COUNTER

(DOT

ROW

PERIOD-91.8577

V-DRIVE

COUNTER)

nsee,

--.n-

PERIOD

CLOCKED

PULSE

WIDTH

H-DRIVE

CHAR

LAST

CLOCKED

RISE

24.434Msee

TIME

VIDEO

PERIOD

FREQ=5¢HZ

RISE

FREQ=6¢HZ

NOTE:

ONE

AFTER

FREQUENCY=1¢.8854

~===~

EDGES

W/H-DRIVE

= 16.667msee,

W/H-DRIVE

STARTS

(643nsee)

=2¢ms

MHZ

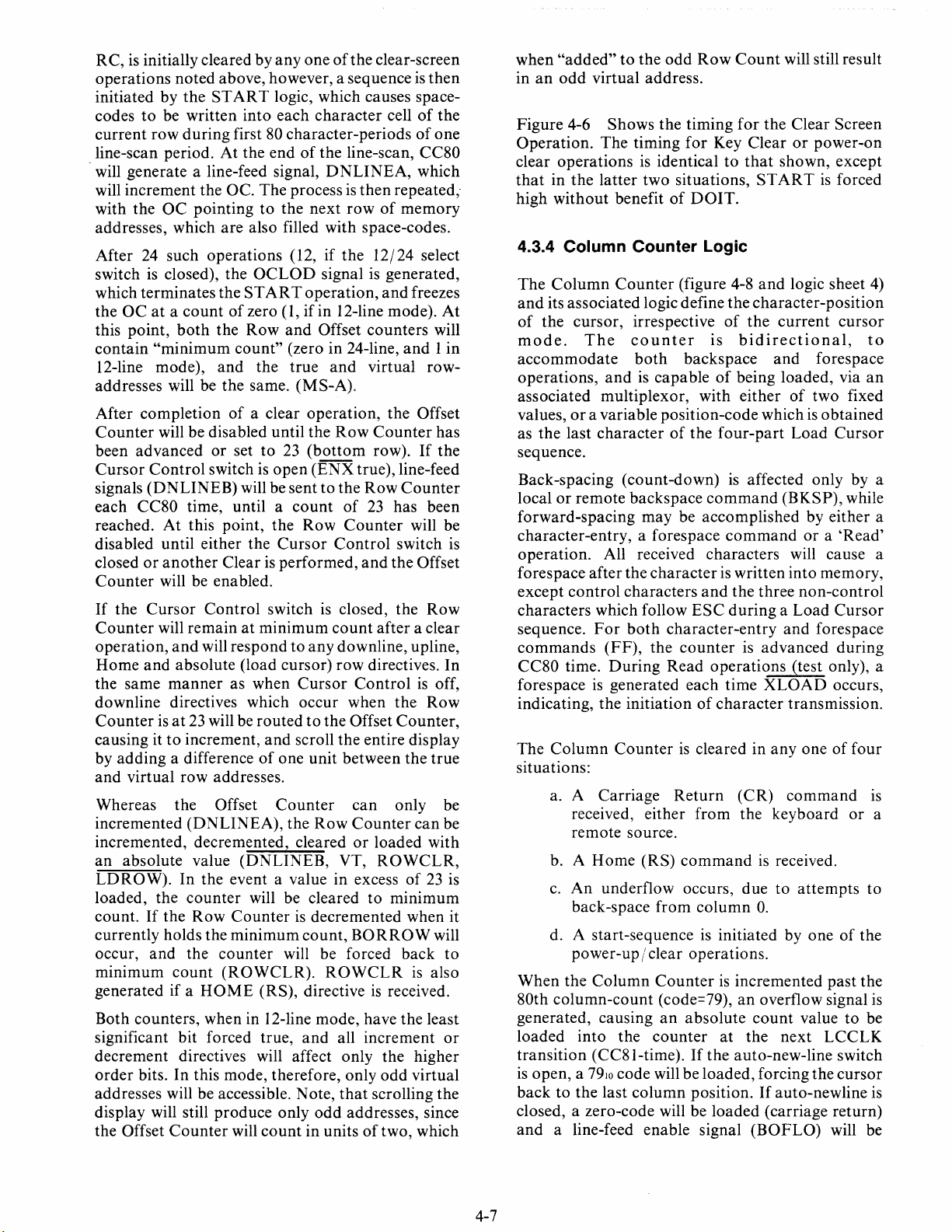

Figure 4-4. Display Counter Timing

4-5

The

dot

counter

comprising

to

10

overflowat15,

count,

character

position

The

eight-stage

the

positionofeach

raster

counter

character

The

character

each

at

the

count

andisagain

DC3,

clocks successive addresses

ROMs,

counter.

character

line,

and

controls

providesatotal

position,

position

79, presetsto240,

255,

and

then

wrapstozero,

CC6

are

binary

That

is,

ee7

is

low

counted,

A flip-flop

and

high

produces

countofretrace

which a

upon.

character

The

each

commandatthe

The

outputofthe

line

counter.

character

line

rowofcharacters.

counts

character.

of

the

The

zero,

presetatzero. Its final

and

triggers

position

characteronthe

horizontal

countof96 (80

and

16

count

counter

counts

counts,

through

but

CC7

while80character

during

time.

the

ICC80

retrace

signal

110 interface

LCCLK

counter

The

counts

counter

seven

dot

character

counts

through

the

counter

80-character

retrace

counts

for

the

counts

Outputs

from

the

CCO

overflow

has a valueof80.

positions

time.

ECC80

indicates

for

the

maybeacted

flip-flop clocks

the

lines

counts

columns

is preset

the

to

the

character

controls

time.

The

for

retrace).

zero

to

at

through

are

the

first

time

at

the

that

form

module

nine.

characters,

through7.The

row

The

rows

through

power

(60 EN) sets

proper

the

Counts

and

0

dot

last

and

rows

count,

8

form

are

formed

LC3, clocks

spaces between

counterata frequencyof1.8 KHz.

character

appearing

line,

time, resetting

next

row

counter

counts

verticallyonthe

vertical retrace time (six

and12counts

up

logictoproduce

character

row

for

a 50-Hz line). A switch

the

countertozerotobegin

count.

the24character

display,

counts

RCRESETatthe

by

the

character

and

for

counts

counts

a 60-Hz

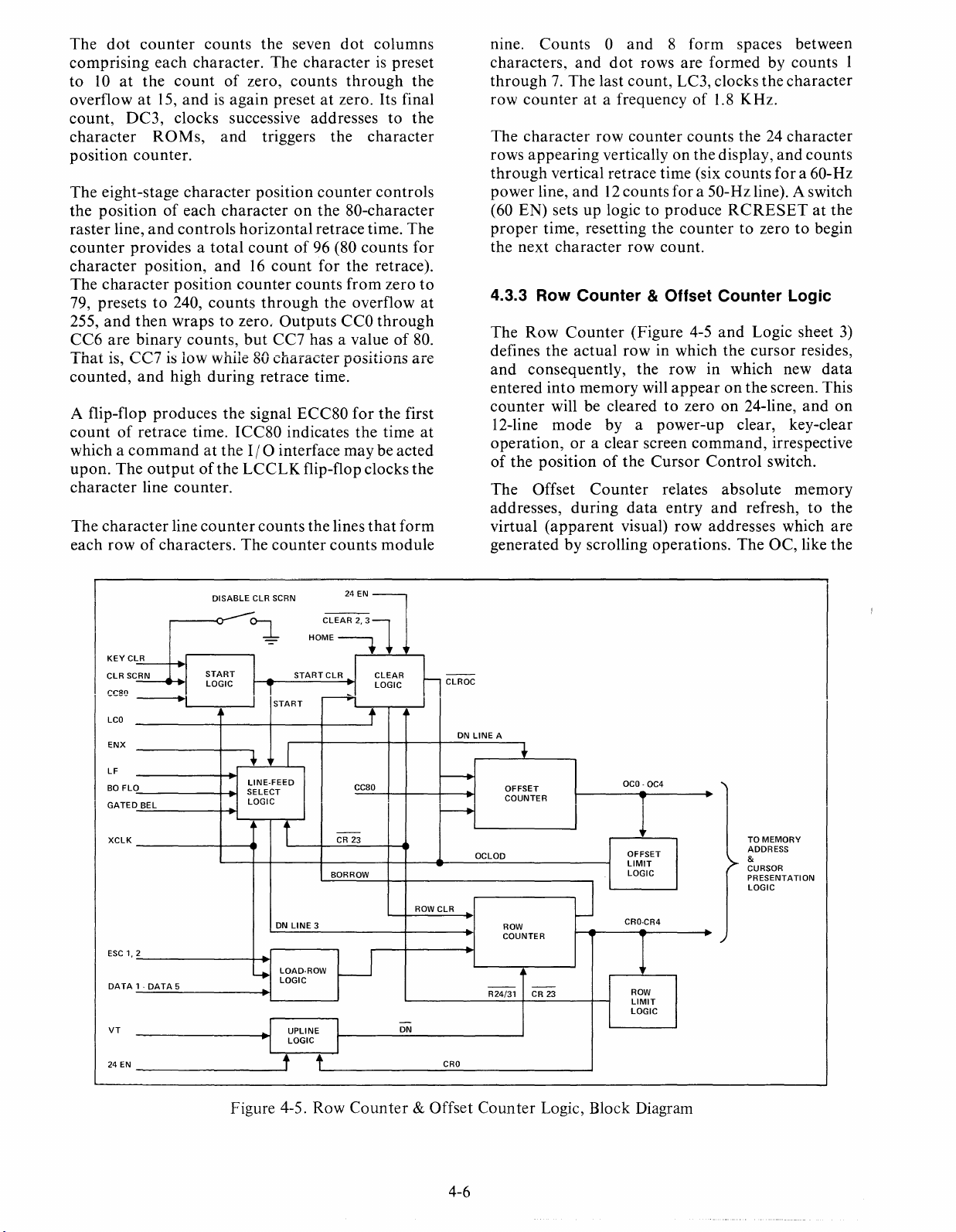

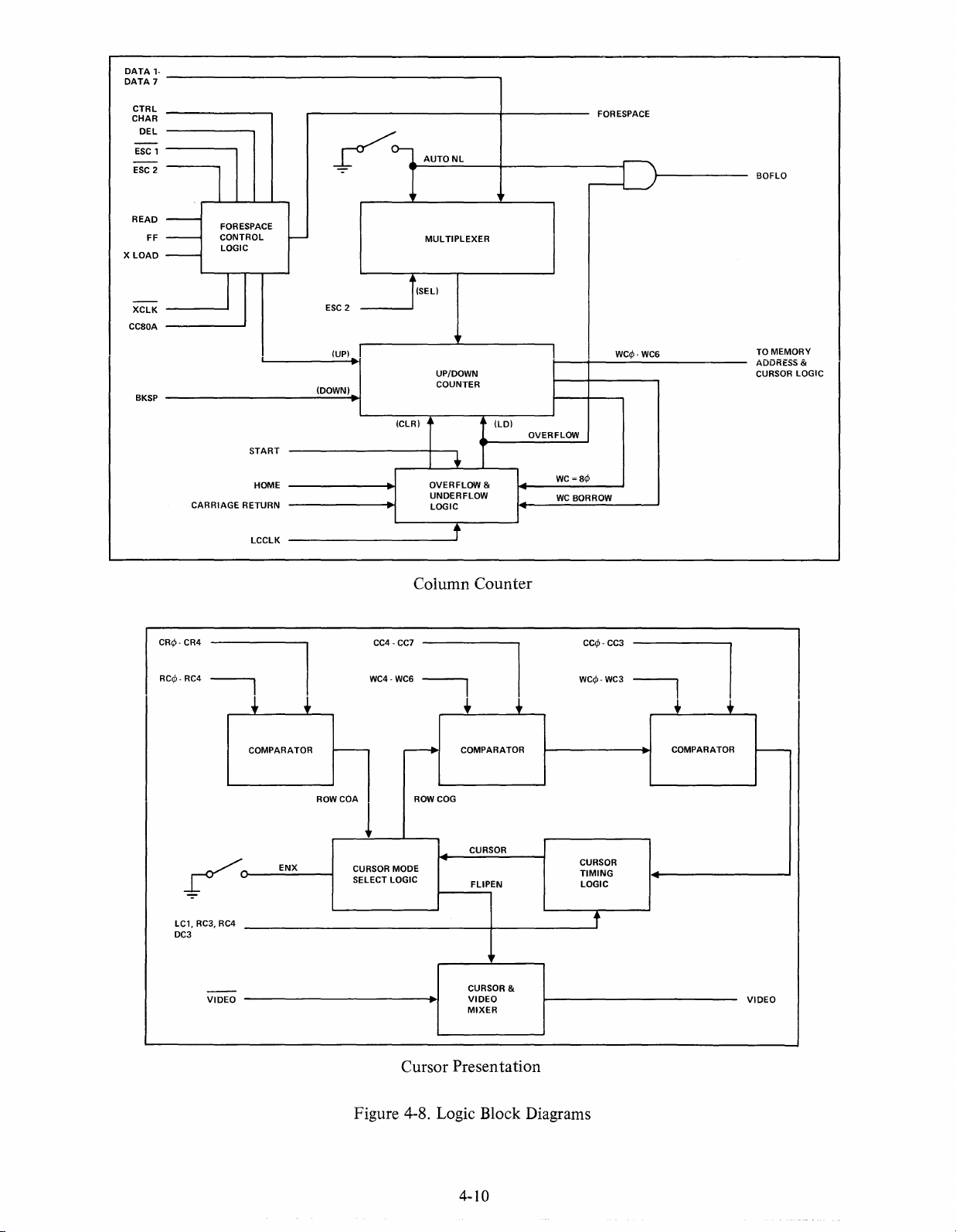

4.3.3 Row Counter & Offset Counter Logic

The

Row

Counter

defines

and

entered

counter

12-line

the

actual

consequently,

into

memory

will be clearedtozeroon24-line,

mode

operation,ora

of

the

positionofthe

The

Offset

addresses,

virtual

during

(apparent

generatedbyscrolling operations.

(Figure

row

by

clear

Counter

data

visual)

in which

the

row

will

appearonthe

a

power-up

screen

Cursor

relates

entry

row

4-5

and

Logic sheet

the

cursor

in which new

screen. This

clear, key-clear

command,

Control

irrespective

switch.

absolute

and

refresh,

addresses which

The

OC,

resides,

and

memory

to

like

1

3)

data

on

the

are

the

KEY

CLR

CC8G

LCO

ENX

LF

BO

FL

GATED

XCLK

ESC

DATA

VT

24

EN

24 EN

~

ccao

-

CR 23

BORROW

U

-

CLEAR

LOGIC

t

r

~

-

DN

f--

-+

-+

ROW CLR

CLROC

DN

CRO

LINE

OCLOD

--

R24/31

A

OFFSET

COUNTER

ROW

COUNTER

t

-

CR 23

J

OCO

- OC4

,

OFFSET

LIMIT

LOGIC

CRO-CR4

ROW

LIMIT

LOGIC

~

~

TO

MEMORY

ADDRESS

&

CURSOR

PRESENTATION

LOGIC

DISABLE

CLR SCRN

-

~

LR

C

RN

SC

0

BEL

I

-I

START

LOGIC

~I

I

START

t

LINE-FEED

SELECT

LOGIC

---

CLEAR2.3~

HOME-.

STARTCLR

~

I

i

LINE

3

DN

2

1,

1·

DATA

5

4

~

~

I

LOAD-ROW

LOGIC

UPLINE

LOGIC