A

Vinafix.com

1 1

B

C

D

E

LCFC Confidential

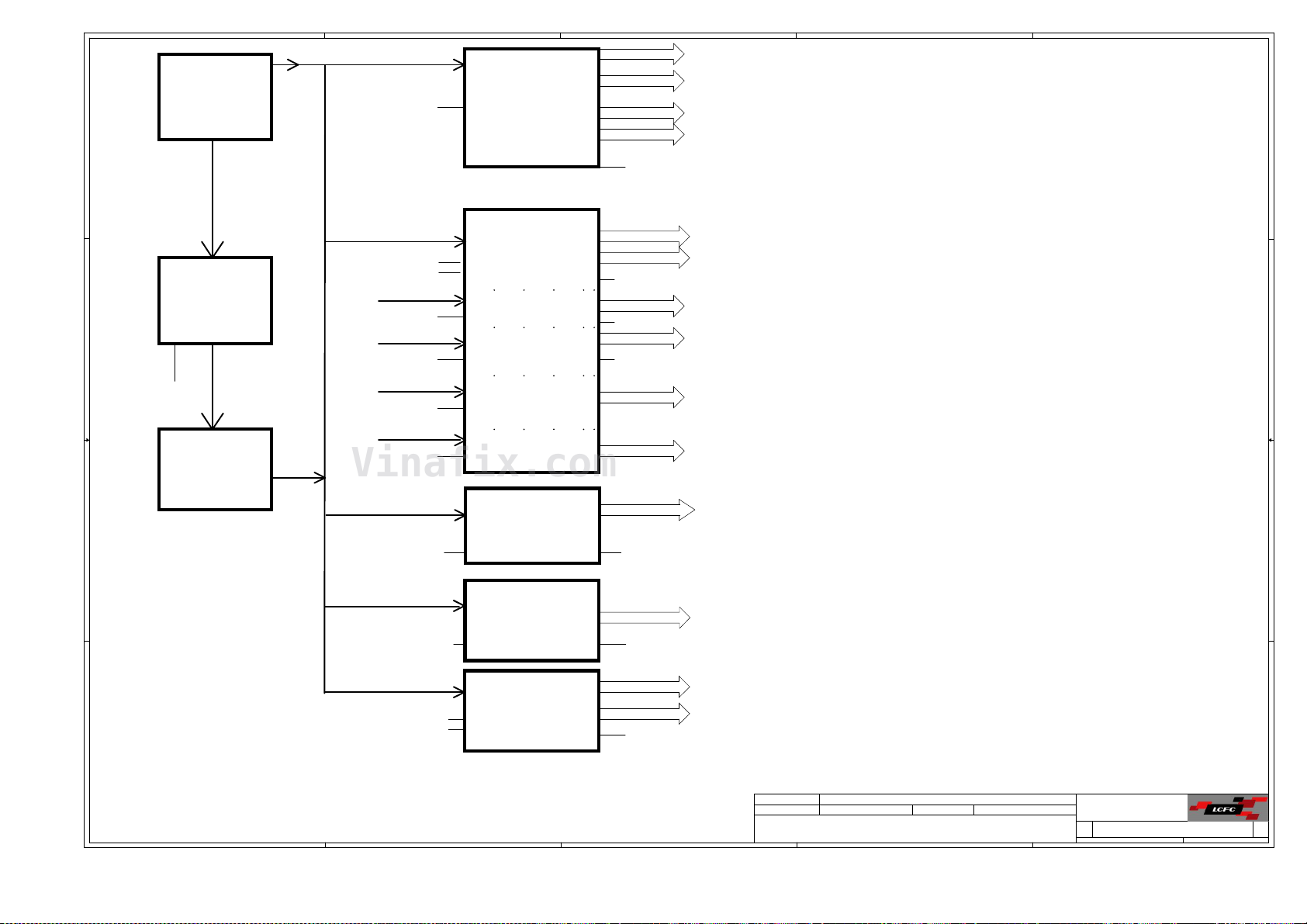

S145AST M/B Schematics Document

2 2

REV:0.2

AMD FT4 Stoney SOC with DDRIV

AMD R17M-M1-70

3 3

4 4

A

2018-10

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

C

2017/03/14

2017/03/14

2017/03/14

LC Future Center Secr et Data

LC Future Center Secr et Data

LC Future Center Secr et Data

Deciphered Date

Deciphered Date

Deciphered Date

2017/03/14

2017/03/14

2017/03/14

D

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, October 25, 2018

Thursday, October 25, 2018

Date: Sheet of

Date: Sheet of

Date: Sheet of

Thursday, October 25, 2018

S145AST

S145AST

S145AST

E

1 50

1 50

1 50

0.2

0.2

0.2

A

Vinafix.com

LCFC confidential

File Name : German

B

C

D

E

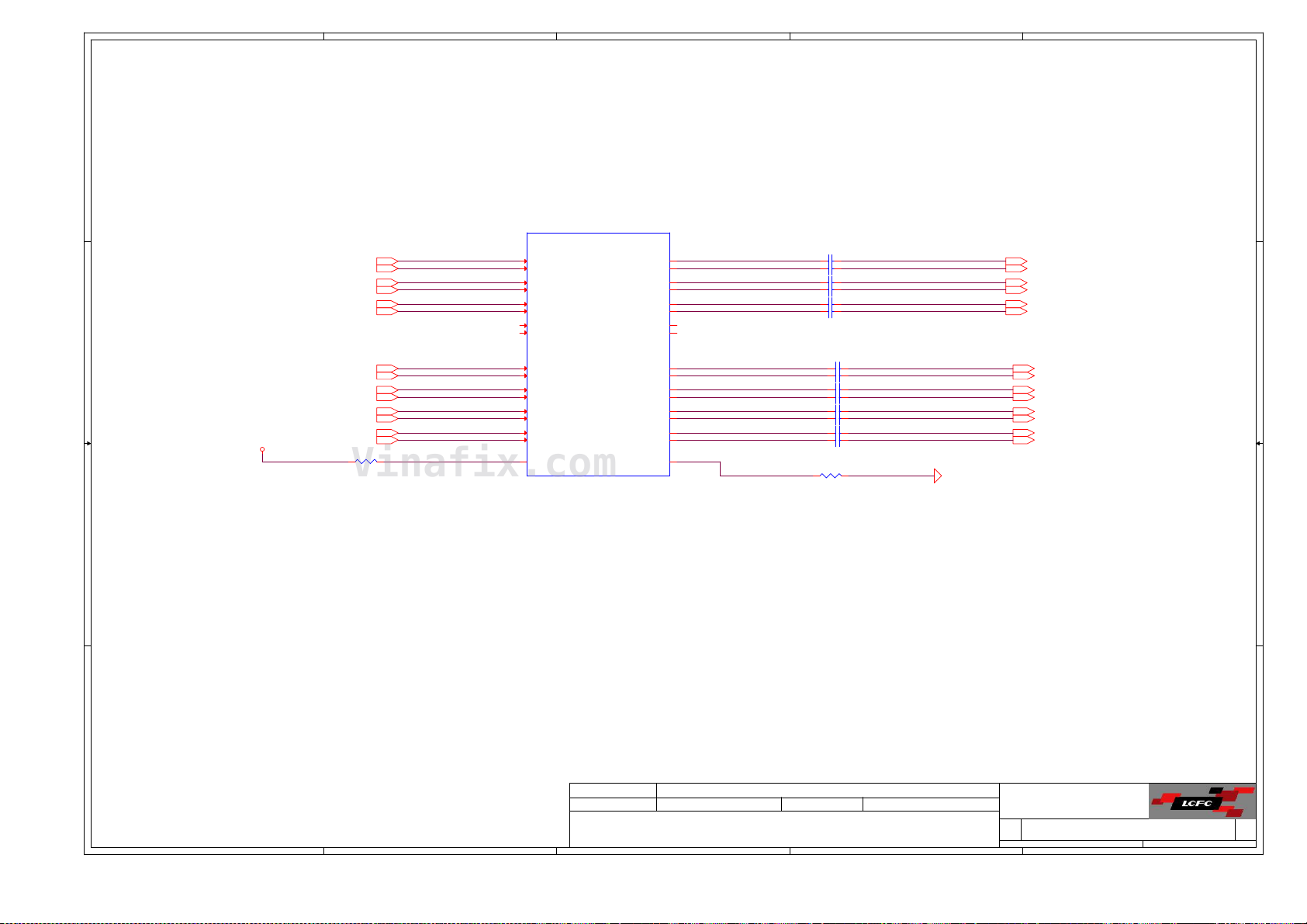

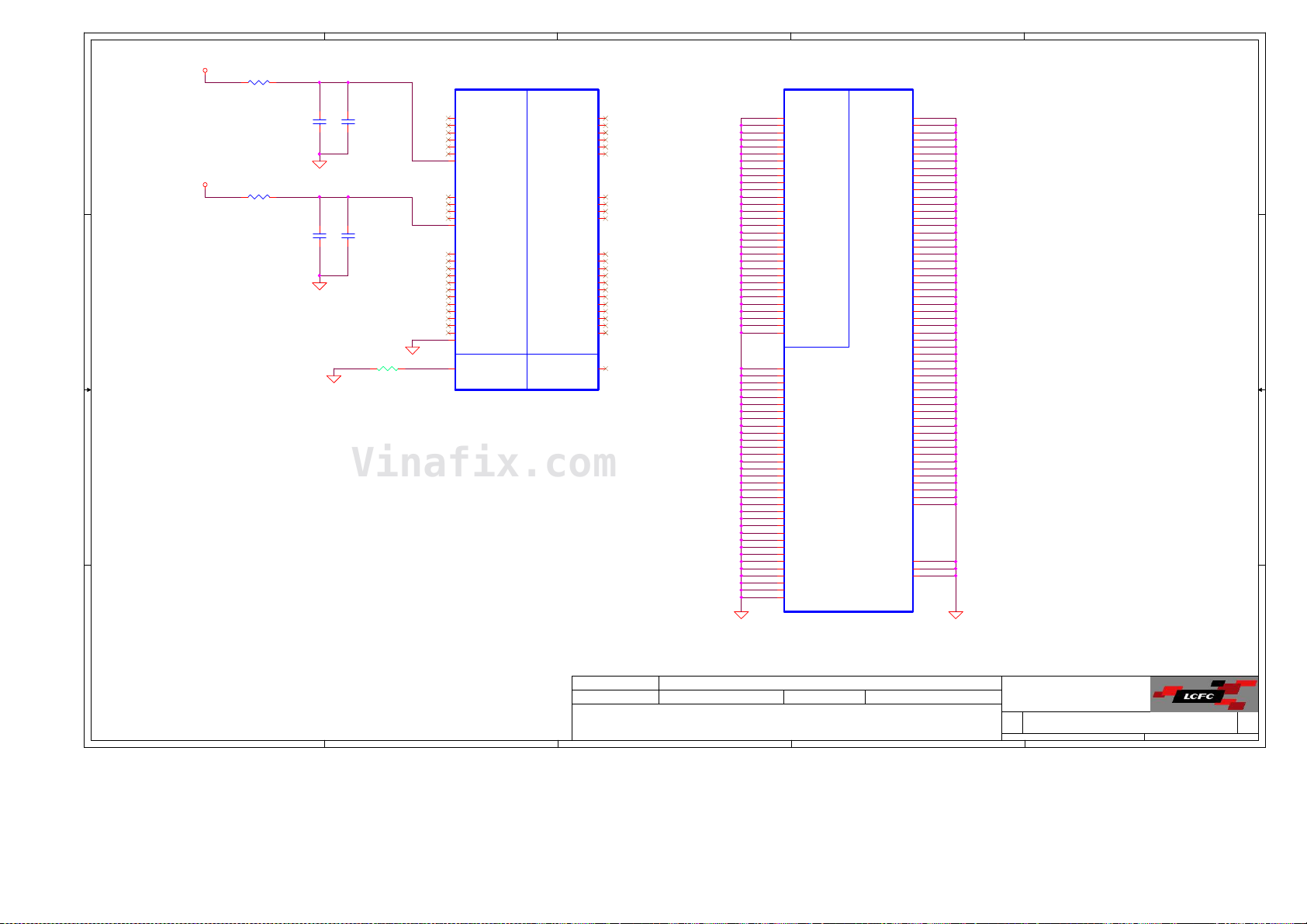

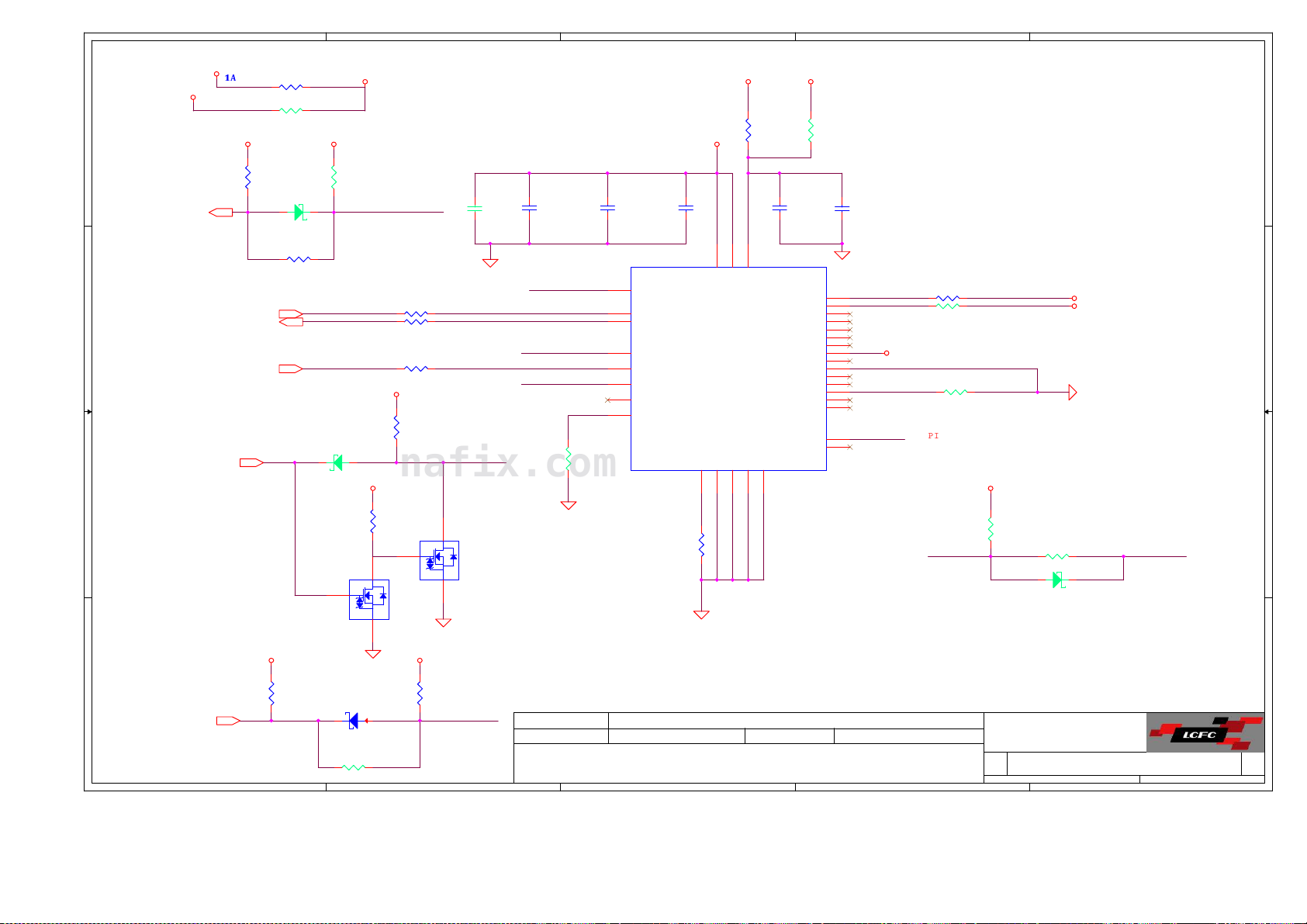

AMD: R17M-M1-70

Package: S3

WĂŐĞϭϱΕϭϵ

1 1

VRAM: 256*32

GDDR5*2: 2GB

WĂŐĞϮϬΕϮϭ

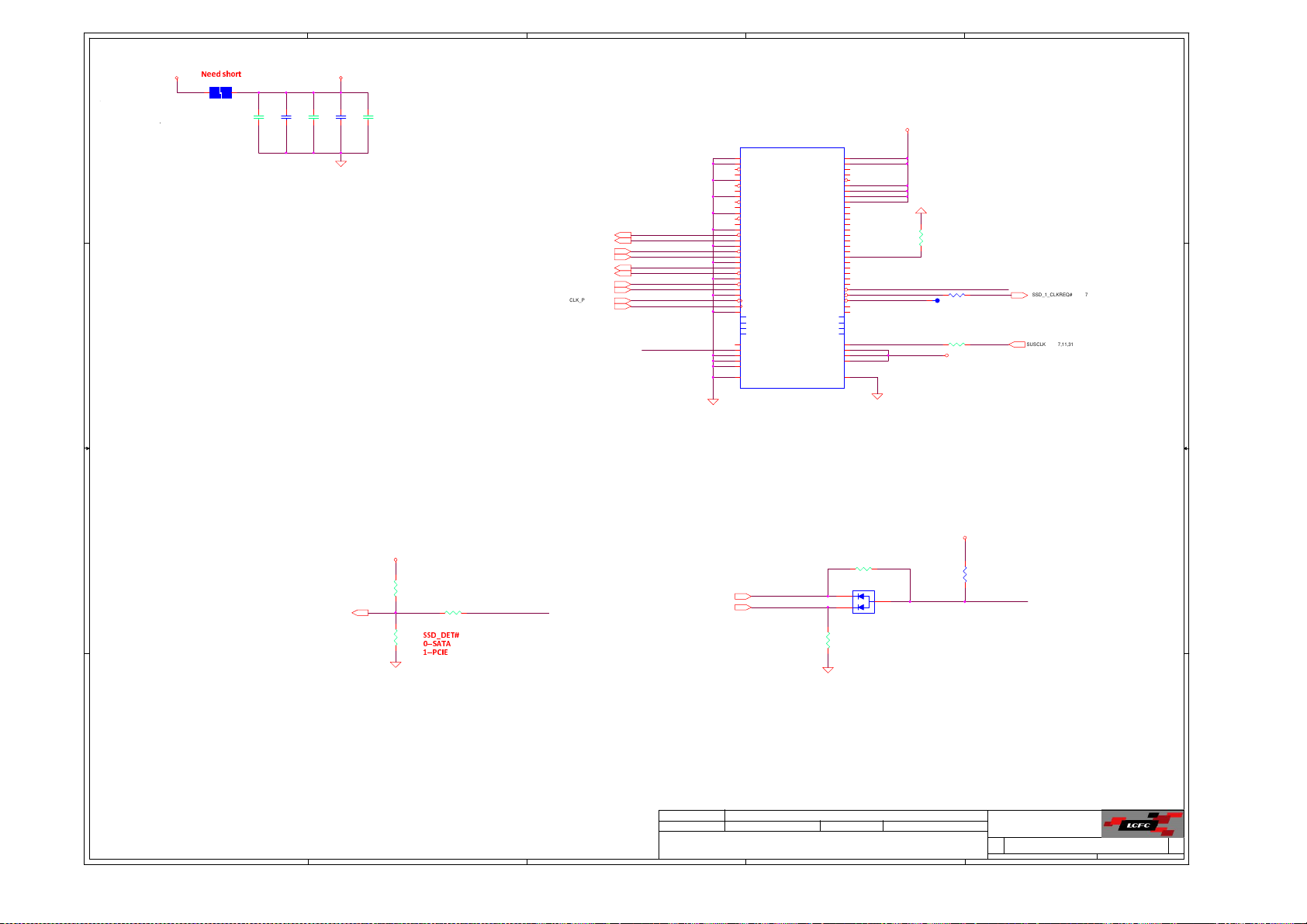

PCIe Port 1~4

HDMI Conn.

WĂŐĞϮϰ

Touch Screen

USB 2.0 Port

eDP Conn

Int. Camera

2 2

USB2.0 Port2

Int. MIC Conn.

WĂŐĞϮϯ

WĂŐĞϮϯ

SATA HDD

WĂŐĞϯϰ

NGFF SSD

WĂŐĞϮϵ

PCI-Express

4x Gen3

HDMI x4 Lane Port1

USB 2.0 1x

eDP x2 Lane

USB2.0 1x

SATA Gen3

SATA Port0

PCI-Express 2x Gen3

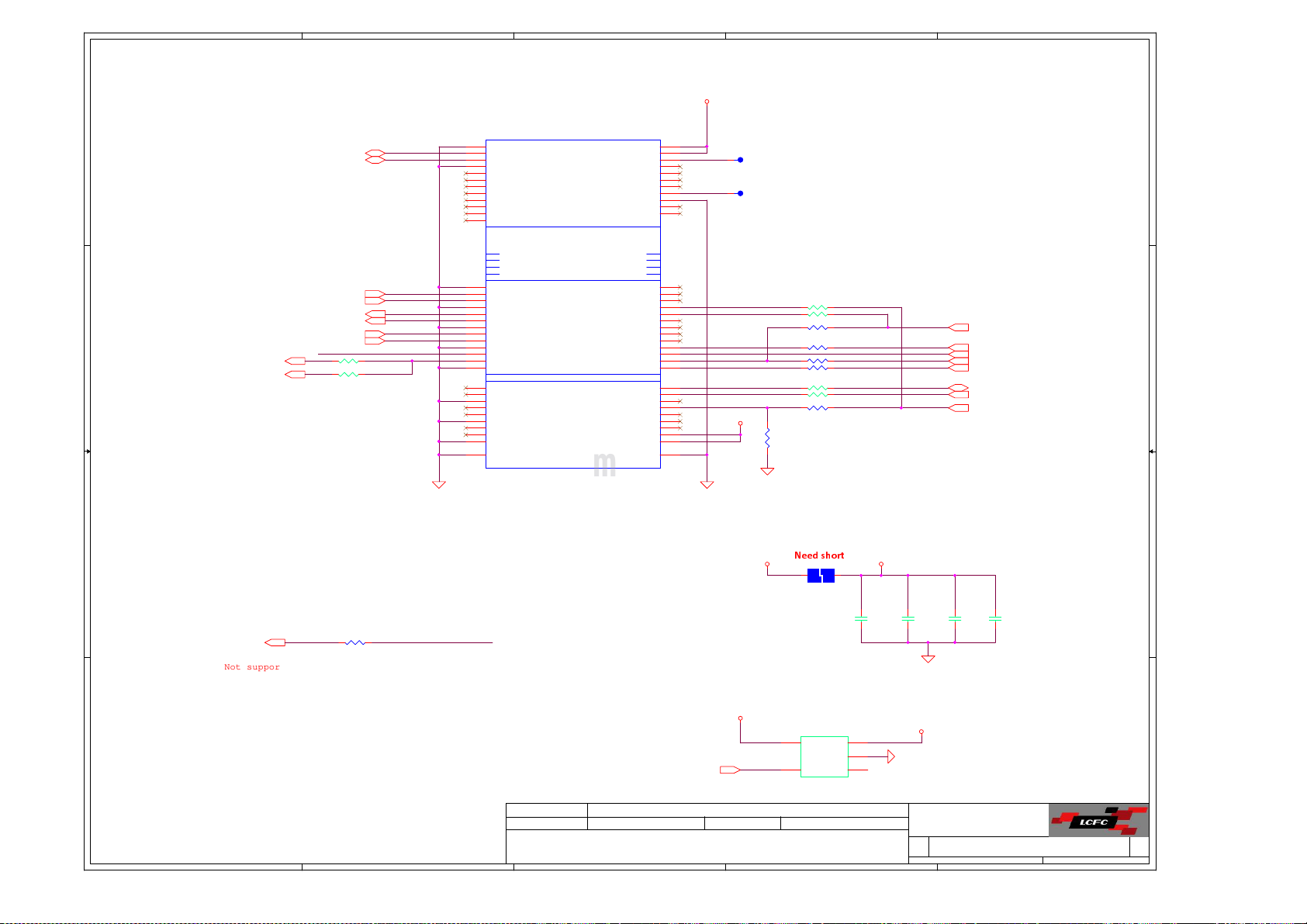

AMD FT4 APU

Stoney 15W

(Integrated FCH)

BGA-769

24mm*24mm

Memory BUS (DDR4)

Single Channel B

1.2V DDR4 2133 MT/s

1866 MT/s

USB3.0 x1

USB2.0 x1

USB3.0 Left Conn

USB3.0 Port0

USB2.0 Port4

USB2.0 Left Conn

USB2.0 x1

USB3.0 x1

USB2.0 x1

USB 2.0 1x

PCIe 1x

SPI BUS

USB2.0 Port3

USB3.0 Left Conn

USB3.0 Port1

USB2.0 Port5

NGFF Card

WLAN&BT

Key E

WĂŐĞϯϭ

SPI ROM

8MB

PCIe Por t2

USB2.0 Port1

WĂŐĞϬϴ

DDR4-SO-DIMM X1

Page 12

UP TO 8G

WĂŐĞϮϱ

WĂŐĞϮϱ

WĂŐĞϮϱ

TPM (Reserved)

SD/MMC Conn.

3 3

SPK Conn.

Codec & C/R

Realtek RTS5119

USB2.0 x1

HD Audio

WĂŐĞϰΕϭϭ

HP&Mic Combo Conn.

LPC BUS

SMBUS

SMBUS

IO Board

USB2.0 Port0

EC

ITE IT8586E-LQFP

WĂŐĞϯϱ

ST33HTPH2E32AHB4

WĂŐĞϮϲ

Touch Pad

WĂŐĞϯϲ

Bat tery

WĂŐĞϰϯ

4 4

A

B

Int.KBD

WĂŐĞϯϲ

Thermistor

WĂŐĞϯϬ

Charger

Hall sensor

AH9247

WĂŐĞϯϲ

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEI THER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEI THER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEI THER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

C

2017/03/14

2017/03/14

2017/03/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Decipher ed Date

Decipher ed Date

Decipher ed Date

Thermal Sensor

F75303M

WĂŐĞϯϬ

D

WĂŐĞϰϰ

reserve

2017/03/14

2017/03/14

2017/03/14

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Docu me nt Nu mb er Rev

Size Docu me nt Nu mb er Rev

Size Docu me nt Nu mb er Rev

Cus to m

Cus to m

Cus to m

Thursday, October 25, 2018

Thursday, October 25, 2018

Thursday, October 25, 2018

Dat e: Sheet of

Dat e: Sheet of

Dat e: Sheet of

S145AST

S145AST

S145AST

E

2 50

2 50

2 50

0.2

0.2

0.2

A

Vinafix.com

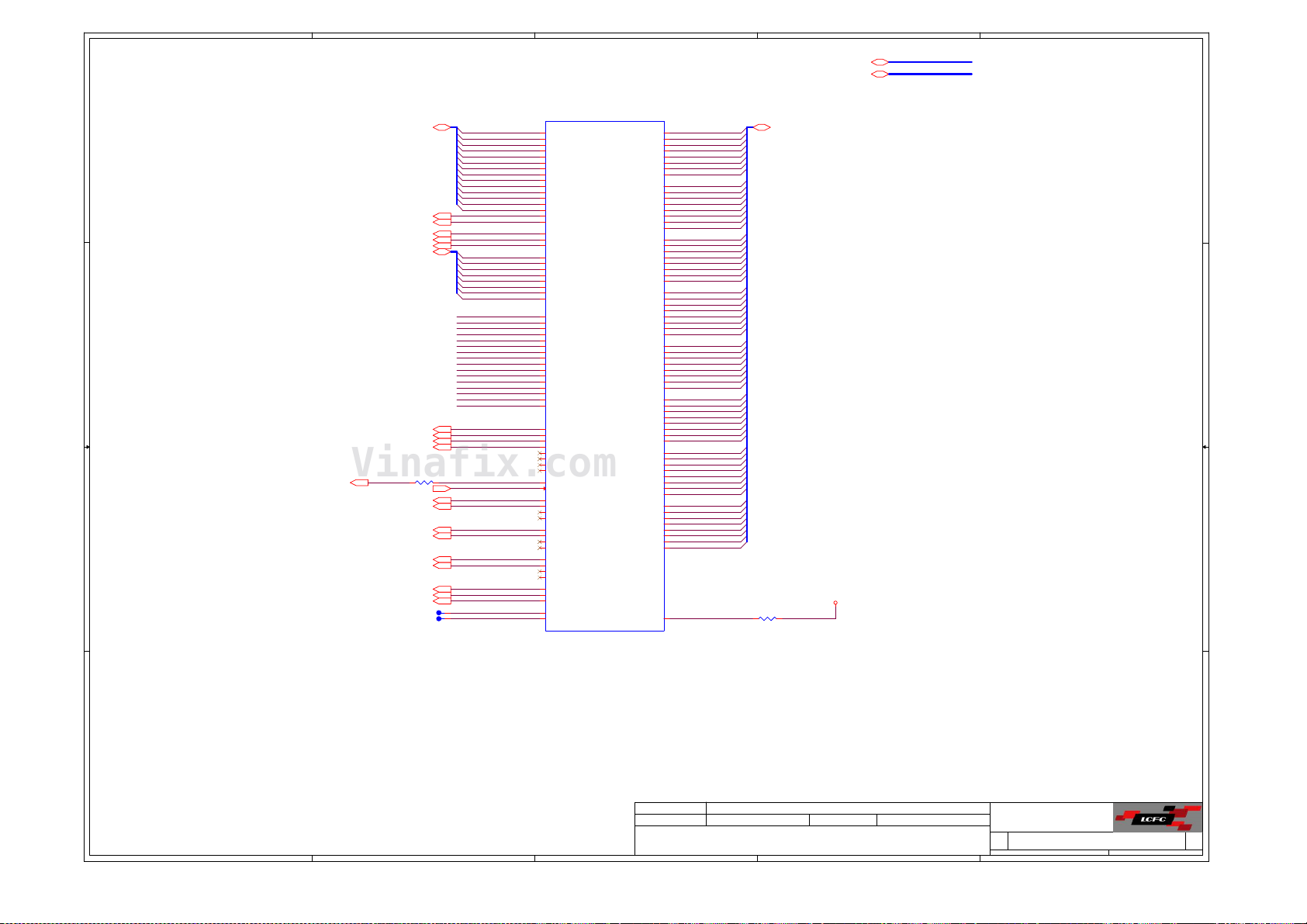

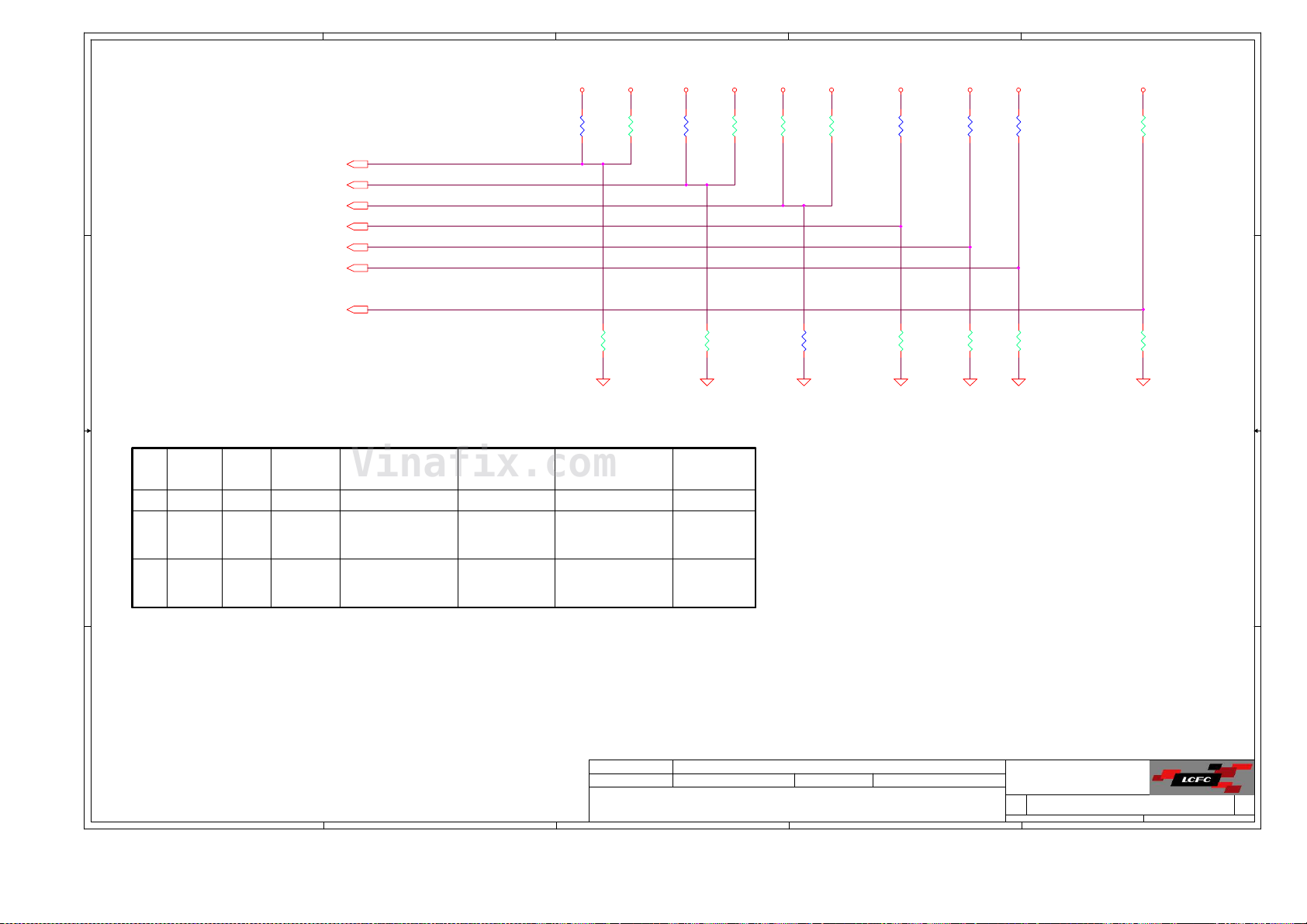

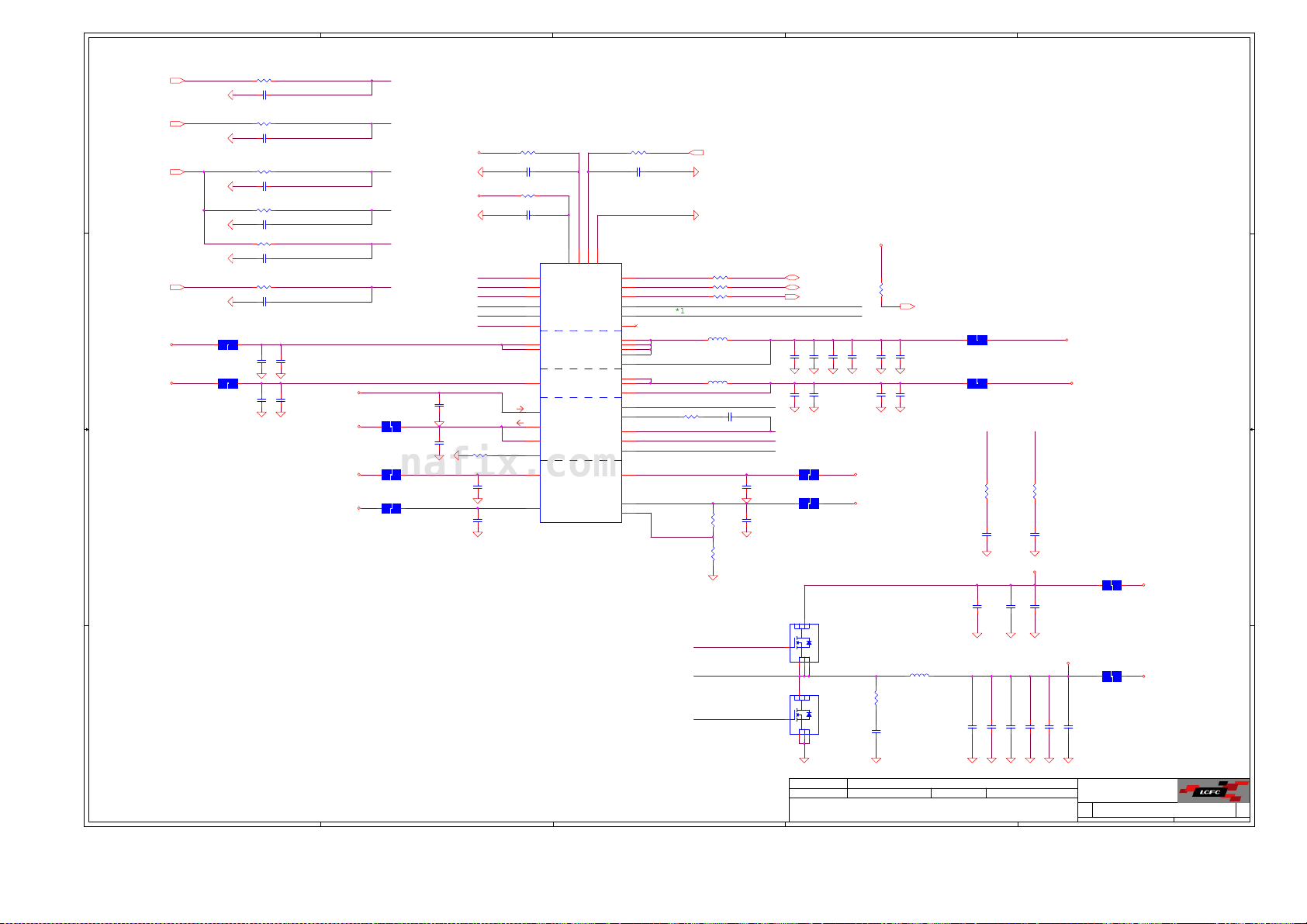

Voltage Rails

1 1

State

S0

S3

2 2

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

( O --> Means ON , X --> Means OFF )

power

plane

B+

(+20VSB)

+3VL

+5VLP

O

O

O

O

X

+5VALW

+3VALW

(+3VALW_APU)

+1.8VALW

+0.95VALW

+0.775VALW

O

O

O

X

X X X

+2.5V

+1.2V

(+VSYSMEM_APU)

SMBUS Control Table

SOURCE

EC_SMB_CK1

EC_SMB_DA1

3 3

EC_SMB_CK3

EC_SMB_DA3

APU_SMB_CLK

APU_SMB_DATA

EC_SMB_CK2

EC_SMB_DA2

TP_I2C0_SCL_R

TP_I2C0_SDA_R

IT8586E

+3VL_EC

IT8586E

+3VS

APU

+3VS

IT8586E

+3VL_EC

APU

+1.8VS

EC SM Bus1 address

Device

Battery

Ch ar ger

4 4

A d d r e s s

0X16 1001_100xb(reserve)

0001 0010 b

APU SM Bus1 address

Device A d d r e s s

Touch pad

GPU BATT SODIMM WLAN Thermal

X

X

V

+3VS_VGA

X X X X

X

X

V V

X X X X X X XXV

X X X X X X X X

EC SM Bus2 address

A

0x15

Device

PMI C

A P U S M B u s 2

No use

A d d r e s s

0X34

APU SM Bus3 address

Device A d d r e s s

DDR DIMM

WLAN

B

+5VS

+3VS

+1.8VS

+1.5VS

+0.95VS

+0.6VS

+APU_CORE

+APU_CORE_NB

+APU_GFX

+VGA_CORE

+3VGS

+1.8VGS

+1.35VGS

+0.95VGS

O

X X

X

Sensor

XV

X

V

X

Device

Therm al Sensor

GPU

APU SB-TSI

0xA0h

RSVD

B

STATE

S0 (Full ON)

S1 (Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

USB Port Table for Stoney FT4

OO

EHCI

X

xHCI 2

X

APUIT8586E

Charger

PMIC

V

X

V

APU_SIC

APU_SID

1.8VS for AST

X

X

X

X

EC SM Bus3 address

A d d r e s s

0x41(default)

releate to F3x1E4[SbiAddr] or

Address Select Pins setting

APU SM Bus4

No use

C

SIGNAL

SLP_S3# SLP_S5# +VALW +V +VS Clock

HIGH HIGH

LOW

LOW LOW

USB 3.0USB 2.0 Port

HIGHHIGH

HIGHLOW

LOW

Port device

0

Card Reader

1

Blue Tooth

2

Camera

3

LEFT USB (2.0)

4

LEFT USB (3.0) Lower

5

LEFT USB (3.0) upper

6

Touch screen

7

ON

ON

ON

ON

ON

ONONON ON

ON

OFF

OFF

ON

OFF

OFF

OFF

D

LOW

OFF

OFF

OFF

BOM Structure Table

@

ME@

Debug@

NODebug@

EMC@

EMC_NS@

EMC_PX@

EMC_PXNS@

RF_NS@

RF_PXNS@

UMA@

PX@

EXO@

TOPAZ@

TPM@

AOAC@

HDT@

TS@

NOTS@

S4GX4@

M4GX4@

Touch

Pad

X

PCIE PORT LIST

Port Device

0

SSD

1

GPP

2

WL AN

3

N/A

0

1

GFX

DIS GPU

2

3

H4GX4@

X

S2GX4@

M2GX4@

H2GX4@

X

VRAM

X

S2G@

M2G@

H2G@

S1G@

M1G@

H1G@

SIVCD@

2017/03/14

2017/03/14

2017/03/14

HDMI@

STN@

V

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEE RING DRAWING IS THE PROPRIETARY P ROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAWING IS THE PROPRIETARY P ROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAWING IS THE PROPRIETARY P ROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R& D

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R& D

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R& D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

C

2017/03/14

2017/03/14

2017/03/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

E

BOARD

BOARD_ID1

Config.

0: Dis

1: UMA

BOARD

BOARD_ID0 BOARD_ID3

Config.

14''

15''

17''

BOARD_ID2 reserve

0

0 1

1 0

0: No KBL

1: KBL

0

BTO ItemBOM Structure

Not stuff

Connector

For USB debug part

For USB no debug part

EMC Part

EMC reserve Part

EMC GPU part

EMC GPU reserve part

RF reserve Part

RF GPU reserve part

UMA SKU ID part

Discrete GPU SKU part

EXO GPU Part

TOPAZ GPU Part

TPM part

AOAC support part

HDT Debug part

Touch screen part

No Touch screen part

X76 SAMSUNG 2G

X76 MICRON 2G

X76 HYNIX 2G

X76 SAMSUNG 1G

X76 MICRON 1G

X76 HYNIX 1G

SAMSUNG 2G

MICRON 2G

HYNIX 2G

SAMSUNG 1G

MICRON 1G

HYNIX 1G

SIV COST down material

HDMI Logo

Stoney part

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Thursday, October 25, 2018

Thursday, October 25, 2018

Thursday, October 25, 2018

Date: Sheet of

Date: Sheet of

Date: Sheet of

S145AST

S145AST

S145AST

E

3 50

3 50

3 50

0.2

0.2

0.2

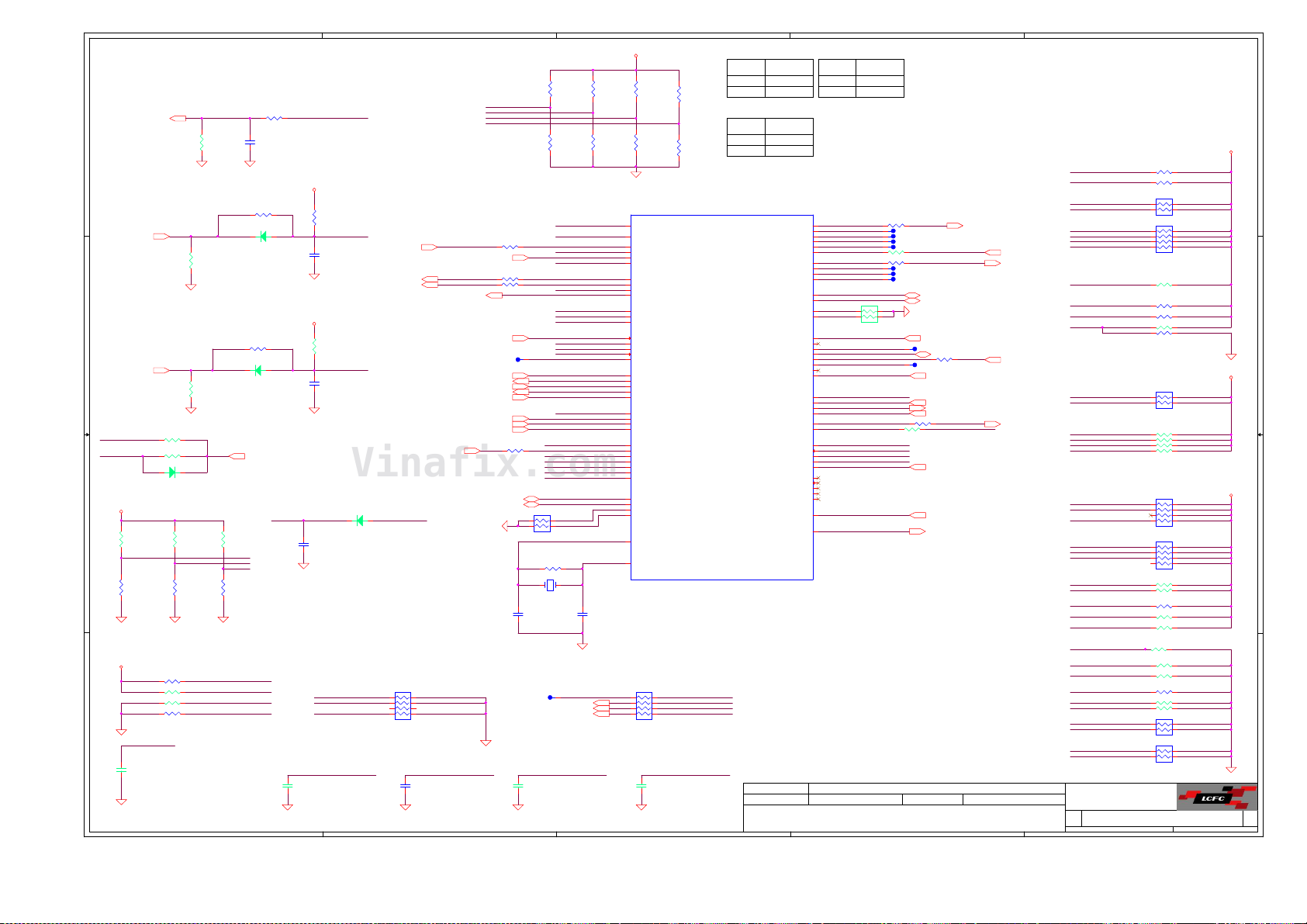

5

Vinafix.com

D D

PCIE_CRX_DTX_P029

M.2 SSD1

WLAN WLAN

C C

GPU

+0.95VS

PCIE_CRX_DTX_N029

PCIE_CRX_DTX_P129

PCIE_CRX_DTX_N129

PCIE_PRX_DTX_P131

PCIE_PRX_DTX_N131

PCIE_CRX_GTX_P015

PCIE_CRX_GTX_N015

PCIE_CRX_GTX_P115

PCIE_CRX_GTX_N115

PCIE_CRX_GTX_P215

PCIE_CRX_GTX_N215

PCIE_CRX_GTX_P315

PCIE_CRX_GTX_N315

1 2

with BOM strcture control, RC1 change to 196_0402_1% for Stoney and Carrizo

CarrizoL not support GFX4-GFX7

4

UC2B

PCIE

PCIE_CRX_DTX_P0

PCIE_CRX_DTX_N0

PCIE_CRX_DTX_P1 PCIE_CTX_DRX_P1

PCIE_CRX_DTX_N1

PCIE_PRX_DTX_P1

PCIE_PRX_DTX_N1

PCIE_CRX_GTX_P0

PCIE_CRX_GTX_N0

PCIE_CRX_GTX_P1

PCIE_CRX_GTX_N1

PCIE_CRX_GTX_P2

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P3

PCIE_CRX_GTX_N3

P_TX_ZVDD

RC1196_0402_1% STN@

U4

U5

R8

R10

R5

R4

N4

N5

L5

L4

J5

J4

G5

G4

D7

E7

U8

P_GPP_RXP0

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_GFX_RXP0

P_GFX_RXN0

P_GFX_RXP1

P_GFX_RXN1

P_GFX_RXP2

P_GFX_RXN2

P_GFX_RXP3

P_GFX_RXN3

P_ZVDDP

@

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

FT4 REV 0.93

AMD-STONEY-FT4_BGA769

P_ZVSS

3

D2

D1

C2

C1

B2

B1

A3

B3

A4

B4

A5

B5

A6

B6

A7

B7

W8

P_RX_ZVDD

PCIE_CTX_DRX_P0

PCIE_CTX_DRX_N0

PCIE_CTX_DRX_N1

PCIE_PTX_DRX_P1

PCIE_PTX_DRX_N1

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_N3

1 2

CC3 0.22U_0201_6.3V6-K

1 2

CC4 0.22U_0201_6.3V6-K

1 2

CC13 0.22U_6.3V_K_X5R_0201

1 2

CC14 0.22U_6.3V_K_X5R_0201

1 2

CC1 0.1U_0201_6.3V6-K

1 2

CC2 0.1U_0201_6.3V6-K

1

CC5 0.22U_0201_6.3V6-KPX@

CC6 0.22U_0201_6.3V6-KPX@

CC7 0.22U_0201_6.3V6-KPX@

CC8 0.22U_0201_6.3V6-KPX@

CC9 0.22U_0201_6.3V6-KPX@

CC10 0.22U_0201_6.3V6-KPX@

CC11 0.22U_0201_6.3V6-KPX@

CC12 0.22U_0201_6.3V6-KPX@

1

1

1

1

1

1

1

1 2

2

2

2

2

2

2

2

2

RC3196_0402_1% STN@

2

PCIE_CTX_C_DRX_P0

PCIE_CTX_C_DRX_N0

PCIE_CTX_C_DRX_P1

PCIE_CTX_C_DRX_N1

PCIE_PTX_C_DRX_P1

PCIE_PTX_C_DRX_N1

PCIE_CTX_C_GRX_P0

PCIE_CTX_C_GRX_N0

PCIE_CTX_C_GRX_P1

PCIE_CTX_C_GRX_N1

PCIE_CTX_C_GRX_P2

PCIE_CTX_C_GRX_N2

PCIE_CTX_C_GRX_P3

PCIE_CTX_C_GRX_N3

PCIE_CTX_C_DRX_P0 29

PCIE_CTX_C_DRX_N0 29

PCIE_CTX_C_DRX_P1 29

PCIE_CTX_C_DRX_N1 29

PCIE_PTX_C_DRX_P1 31

PCIE_PTX_C_DRX_N1 31

PCIE_CTX_C_GRX_P0 15

PCIE_CTX_C_GRX_N0 15

PCIE_CTX_C_GRX_P1 15

PCIE_CTX_C_GRX_N1 15

PCIE_CTX_C_GRX_P2 15

PCIE_CTX_C_GRX_N2 15

PCIE_CTX_C_GRX_P3 15

PCIE_CTX_C_GRX_N3 15

1

GPU

B B

A A

5

Title

Title

Security Cl assificat ion

Security Cl assificat ion

Security Cl assificat ion

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2017/03/14

2017/03/14

2017/03/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2017/03/14

2017/03/14

2017/03/14

2

Title

FT4 (PCIE I/F)

FT4 (PCIE I/F)

FT4 (PCIE I/F)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet o f

Date: Sheet of

Date: Sheet of

Thursday, October 25, 2018

Thursday, October 25, 2018

Thursday, October 25, 2018

S145AST

S145AST

S145AST

1

4 50

4 50

4 50

0.2

0.2

0.2

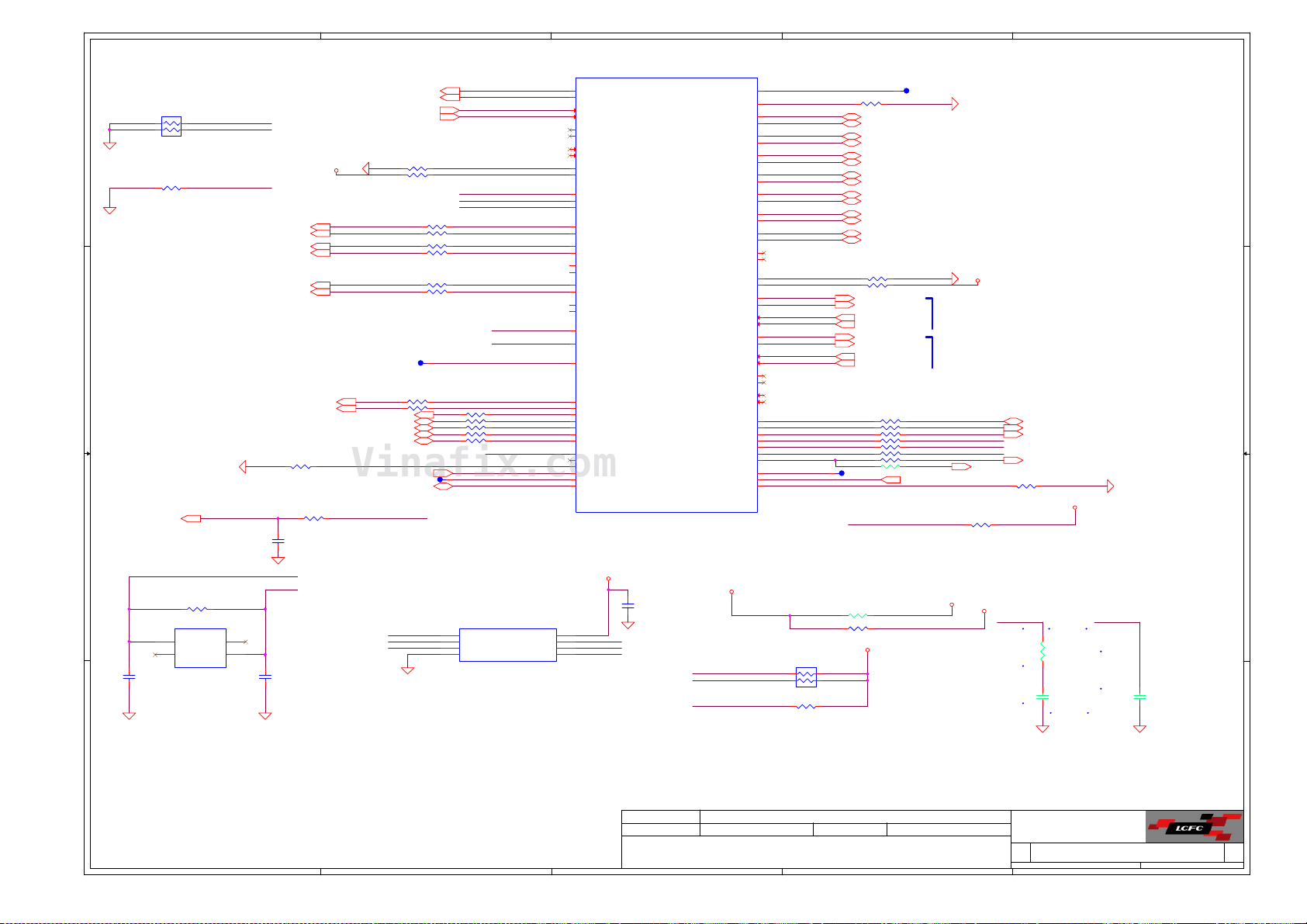

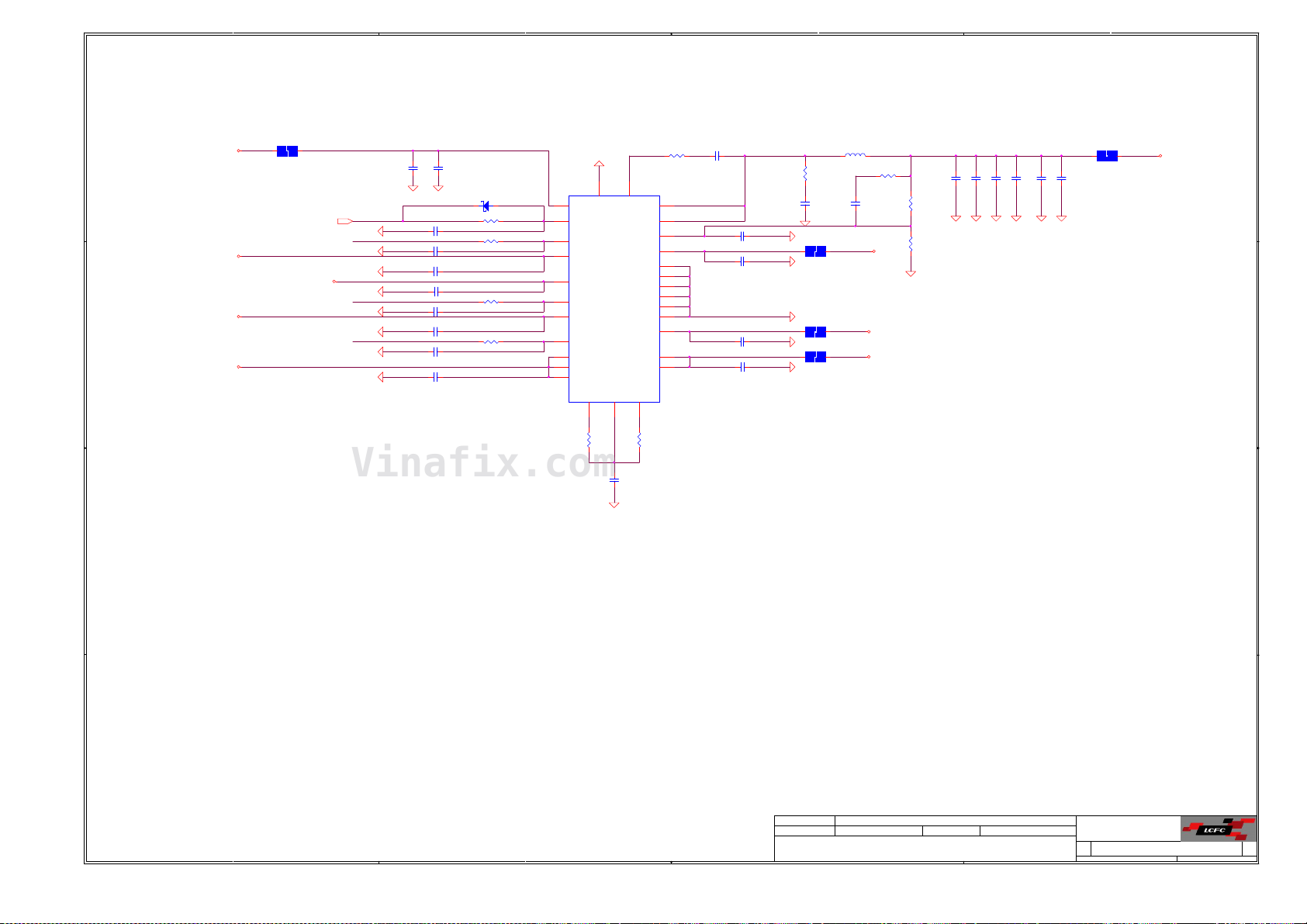

5

Vinafix.com

D D

C C

MEM_MB_RST#12

B B

4

DDRB_MA[13..0]12

DDRB_BG112

DDRB_ACT#12

DDRB_BA012

DDRB_BA112

DDRB_BG012

DDRB_DM[7..0]12

DDRB_CLK012

DDRB_CLK0#12

DDRB_CLK112

DDRB_CLK1#12

1 2

RC240 10_0402_5%

MEM_MB_EVENT#12

DDRB_CKE012

DDRB_CKE112

DDRB_ODT012

DDRB_ODT112

DDRB_CS0#12

DDRB_CS1#12

DDRB_MA16_RAS#12

DDRB_MA15_CAS#12

DDRB_MA14_WE#12

TC8 6 @

TC7 0 @

1

1

DDRB_MA0

DDRB_MA1

DDRB_MA2

DDRB_MA3

DDRB_MA4

DDRB_MA5

DDRB_MA6

DDRB_MA7

DDRB_MA8

DDRB_MA9

DDRB_MA10

DDRB_MA11

DDRB_MA12

DDRB_MA13

DDRB_BG1

DDRB_ACT#

DDRB_BA0

DDRB_BA1

DDRB_BG0

DDRB_DM0

DDRB_DM1

DDRB_DM2

DDRB_DM3

DDRB_DM4

DDRB_DM5

DDRB_DM6

DDRB_DM7

DDRB_DQS0

DDRB_DQS#0

DDRB_DQS1

DDRB_DQS#1

DDRB_DQS2

DDRB_DQS#2

DDRB_DQS3

DDRB_DQS#3

DDRB_DQS4

DDRB_DQS#4

DDRB_DQS5

DDRB_DQS#5

DDRB_DQS6

DDRB_DQS#6

DDRB_DQS7

DDRB_DQS#7

DDRB_CLK0

DDRB_CLK0#

DDRB_CLK1

DDRB_CLK1#

MEM_MB_RST#_R

MEM_MB_EVENT#

DDRB_CKE0

DDRB_CKE1

DDRB_ODT0

DDRB_ODT1

DDRB_CS0#

DDRB_CS1#

DDRB_MA16_RAS#

DDRB_MA15_CAS#

DDRB_MA14_WE#

+MEM_VREF

APU_M_VREFDQ

AG3 8

M_ A D D 0

W35

M_ A D D 1

W38

M_ A D D 2

W34

M_ A D D 3

U38

M_ A D D 4

U37

M_ A D D 5

U34

M_ A D D 6

R35

M_ A D D 7

R38

M_ A D D 8

N38

M_ A D D 9

AG3 4

M_ A D D 1 0

R34

M_ A D D 1 1

N37

M_ A D D 1 2

AN35

M_ A D D 1 3

L38

M_ADD14/M_BG1

L35

M_ADD15/M_ACT_L

AJ3 8

M_BANK0

AG3 5

M_ B A N K 1

N34

M_BANK2/M_BG0

B35

M_ D M 0

D40

M_ D M 1

K40

M_ D M 2

T41

M_ D M 3

AE41

M_ D M 4

AL40

M_ D M 5

AU40

M_ D M 6

BA37

M_ D M 7

B36

M_DQS_H0

A36

M_DQS_L0

E40

M_DQS_H1

D41

M_DQS_L1

L40

M_DQS_H2

K41

M_DQS_L2

U41

M_DQS_H3

U40

M_DQS_L3

AF4 1

M_DQS_H4

AE40

M_DQS_L4

AM40

M_DQS_H5

AM41

M_DQS_L5

AV40

M_DQS_H6

AV41

M_DQS_L6

BA36

M_DQS_H7

AY36

M_DQS_L7

AC35

M_CLK_H0

AC34

M_CLK_L0

AA34

M_CLK_H1

AA32

M_CLK_L1

AE38

M_CLK_H2

AE37

M_CLK_L2

AA37

M_CLK_H3

AA38

M_CLK_L3

G38

M_RESET_L

AA41

M_EVENT_L

J38

M0_CKE0

J34

M0_CKE1

L34

M1_CKE0

J37

M1_CKE1

AN37

M0_ODT0

AU38

M0_ODT1

AL34

M1_ODT0

AN34

M1_ODT1

AL35

M0_CS_L0

AR37

M0_CS_L1

AJ3 4

M1_CS_L0

AR38

M1_CS_L1

AJ3 7

M_RAS_L/M_RAS_L_ADD16

AN38

M_CAS_L/M_CAS_L_ADD15

AL38

M_WE_L/M_WE_L_ADD14

AA40

M_VREF

Y41

M_VREFDQ

@

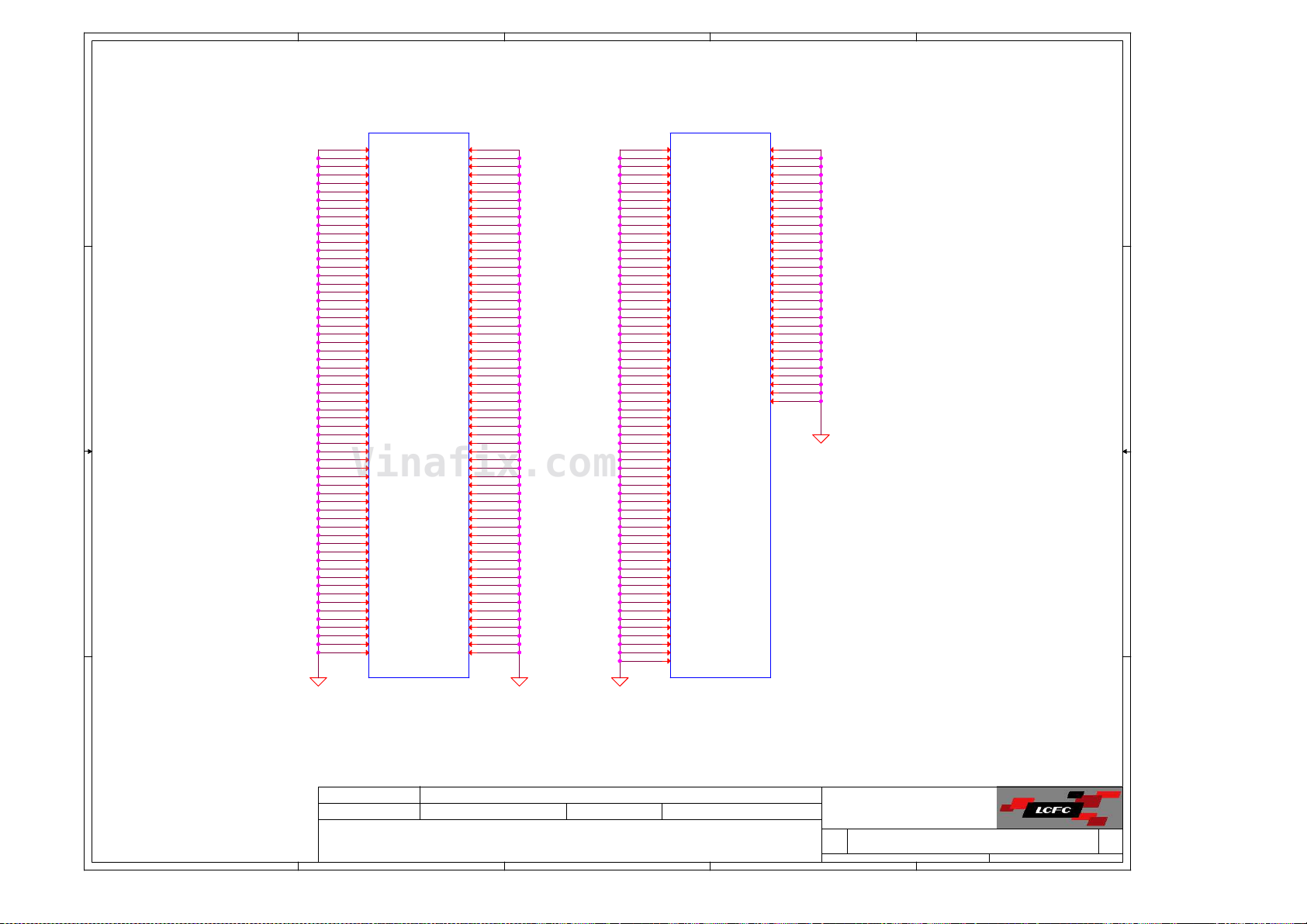

UC2A

MEMO RY

M_ZVDDIO_MEM_S3

FT4 REV 0.93

AMD-STONEY-FT4_BGA769

3

M_ D A T A 0

M_ D A T A 1

M_ D A T A 2

M_ D A T A 3

M_ D A T A 4

M_ D A T A 5

M_ D A T A 6

M_ D A T A 7

M_ D A T A 8

M_ D A T A 9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

A34

B34

A38

B38

A33

B33

A37

B37

B41

C40

F41

G40

A40

B40

E41

F40

J40

J41

N40

N41

H40

H41

M4 0

M4 1

R40

T40

W40

Y40

P40

P41

V40

V41

AD41

AD40

AH41

AH40

AB40

AC40

AF4 0

AG4 0

AK41

AK40

AP41

AP40

AJ4 1

AJ4 0

AN41

AN40

AT4 0

AU41

AY40

BA40

AR40

AT4 1

AW 40

AY41

BA38

AY37

BA34

BA33

AY39

AY38

AY35

AY34

AB41

DDRB_DQ0

DDRB_DQ1

DDRB_DQ2

DDRB_DQ3

DDRB_DQ4

DDRB_DQ5

DDRB_DQ6

DDRB_DQ7

DDRB_DQ8

DDRB_DQ9

DDRB_DQ10

DDRB_DQ11

DDRB_DQ12

DDRB_DQ13

DDRB_DQ14

DDRB_DQ15

DDRB_DQ16

DDRB_DQ17

DDRB_DQ22

DDRB_DQ23

DDRB_DQ20

DDRB_DQ21

DDRB_DQ19

DDRB_DQ18

DDRB_DQ24

DDRB_DQ25

DDRB_DQ26

DDRB_DQ27

DDRB_DQ29

DDRB_DQ28

DDRB_DQ30

DDRB_DQ31

DDRB_DQ36

DDRB_DQ32

DDRB_DQ39

DDRB_DQ35

DDRB_DQ33

DDRB_DQ37

DDRB_DQ34

DDRB_DQ38

DDRB_DQ41

DDRB_DQ44

DDRB_DQ43

DDRB_DQ47

DDRB_DQ45

DDRB_DQ40

DDRB_DQ46

DDRB_DQ42

DDRB_DQ54

DDRB_DQ53

DDRB_DQ50

DDRB_DQ52

DDRB_DQ49

DDRB_DQ48

DDRB_DQ51

DDRB_DQ55

DDRB_DQ60

DDRB_DQ57

DDRB_DQ58

DDRB_DQ59

DDRB_DQ61

DDRB_DQ56

DDRB_DQ63

DDRB_DQ62

MB_ZVDDIO

DDRB_DQ[63..0] 12

1 2

RC10 39.2_0402_1%

2

DDRB_DQS[0..7]12

DDRB_DQS#[0..7]12

DDRB_DQS[0..7]

DDRB_DQS#[0..7]

1

DATA16--DATA23 Byte internal swap

DATA24--DATA31 Byte internal swap

DATA32--DATA39 Byte internal swap

DATA40--DATA47 Byte internal swap

DATA48--DATA55 Byte internal swap

DATA56--DATA63 Byte internal swap

+1.2V

A A

5

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2017/03/14

2017/03/14

2017/03/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered D ate

Deciphered D ate

Deciphered D ate

2

2017/03/14

2017/03/14

2017/03/14

Title

FT4 (MEM)

FT4 (MEM)

FT4 (MEM)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

S145AST

S145AST

S145AST

Thursday, October 25, 2018

Thursday, October 25, 2018

Thursday, October 25, 2018

5 50

5 50

1

5 50

0.2

0.2

0.2

1 4

Vinafix.com

2 3

5

1

CC1286

2

@

0.01U_0201_25V6-K

APU_PWROK

RPC 10

1K_0404_4P2R_5%

STN@

1

1

CC1287

2

@

@

0.01U_0201_25V6-K

1

2

2

G1

D16S1

QC6A

PJT7838_SOT363-6

STN@

1

CC1288

2

0.01U_0201_25V6-K

CC1276

0.01U_0201_25V6-K

EMC_NS@

+1.8VS+1.8VS

5

G2

4

D23S2

QC6B

PJT7838_SOT363-6

STN@

APU_SVT49

AP U _ S VC49

AP U _ S VD49

H_P RO CH OT #35,46

1000P_0402_25V7-K

+3VALW_APU

EC_SMB_CK3

EC_SMB_DA3

RC249 0_0402_5%

RC213 22_0402_5%

RC215 22_0402_5%

RC31 0_0402_5%

AP U _ S VT _ L

12

CC21 0

@

1 2

1 2

1 2

1 2

APU_PWROK49

EC_SMB_CK3 16,30,35

EC_SMB_DA3 16,30,35

AP U _ S VT

AP U _ S VC

AP U _ S VD

+1.8VS

12

RC18

300_0402_5%

D D

C C

B B

AP U _ R S T #

PLACE CC16 CAPS CLOSE TO APU,CRB reserve 27pf

1

CC16

56P_0402_50V8-J

2

@

+1.8VS

12

RC19

300_0402_5%

AP U _ P W R O K

PLACE CC17 CAPS CLOSE TO APU,CRB reserve 27pf

1

CC17

56P_0402_50V8-J

2

@

AP U _ S I C

AP U _ S I D

With HDT+ Header

+1.8VS

RC7

1K_0402_5%

1 2

AP U _ T R S T #

A A

RC76 33_0402_5%HD T@

2

CC84

0.01U_6.3V_K_X7R_0201

1

1 2

5

1 8

2 7

3 6

4 5

APU_TRST#_R

RPC 17

10K_0804_8P4R_5%

HDT@

JHDT1

@

1

1

3

3

5

5

7

7

9

9

10

11

11

12

13

13

14

15

15

16

17

17

18

19

19

20

SAMTE_ASP-136446-07-B

2

4

6

8

2

4

6

8

10

12

14

16

RC27 3 33_0402_5%HD T@

18

20

AP U _ S VT _ L

APU_SVC_L

APU_SVD_L

12

RC23 9100K_0402_5% @

AP U _ T C K

AP U _ T M S

AP U _ T D I

AP U _ T D O

APU_PWROK_BUF

APU_RST#_BUF

APU_DBRDY

1 2

APU_TEST19_PLLTEST0

APU_TEST18_PLLTEST1

4

AP U _ S I C

AP U _ S I D

AL E R T #

APU_PROCHOT#_R

APU_PWROK

AP U _ R S T #

AP U _ T D I

AP U _ T D O

AP U _ T C K

AP U _ T M S

APU_TRST#

APU_DBRDY

APU_DBREQ#

Cor e_ ty p e

APU_DBREQ#

4

AE34

AM15

AM17

AM19

AP13

AP15

AP17

AR13

AR15

AR17

AU13

AU15

AU17

AV11

AV13

AV15

AV17

H27

E27

D27

B30

B29

A30

A31

G25

D29

B25

A27

B27

B26

A29

A26

A25

D9

D11

D13

E4

E31

H11

H13

L11

AN8

AU4

AV7

AV9

AY3

AY7

DISPLAY/SVI2/JTAG/TEST

SVT

SVC

SVD

SIC

SID

ALERT_L

PROCHOT_L

PWROK

RESET_L

TD I

TD O

TC K

TM S

TRST_L

DBRDY

DBREQ_L

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

RSVD_16

RSVD_17

RSVD_18

RSVD_19

RSVD_20

RSVD_21

RSVD_22

RSVD_23

RSVD_24

RSVD_25

RSVD_26

RSVD_27

RSVD_28

RSVD_29

RSVD_30

RSVD_31

@

RPC 5

1K_0804_8P4R_5%

2

CC21 3

HDT@

0.01U_6.3V_K_X7R_0201

1

UC2C

DP_VARY_BL

DP_AUX_ZVSS

DP_STEREOSYNC/TEST36

VDDCR_CPU_SENSE

VDDCR_NB_SENSE

VDDIO_MEM_S3_SENSE

VDDP_SENSE

VSS_SENSE_A

FT4 REV 0.93

VSS_SENSE_B

AMD-STONEY-FT4_BGA769

+1.8VS+1.8VS

18

27

36

45

AP U _ P W R O K

AP U _ R S T #

APU_TDIAP U _ D B R E Q #

DP_BLON

DP_DIGON

DP_ZVSS

DP0_AUXP

DP0_AUXN

DP0_HPD

DP1_AUXP

DP1_AUXN

DP1_HPD

DP2_AUXP

DP2_AUXN

DP2_HPD

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP2_TXP0

DP2_TXN0

DP2_TXP1

DP2_TXN1

DP2_TXP2

DP2_TXN2

DP2_TXP3

DP2_TXN3

TE S T 4

TE S T 5

TE S T 6

TE S T 9

TE S T 1 0

TE S T 1 4

TE S T 1 5

TE S T 1 6

TE S T 1 7

TE S T 1 8

TE S T 1 9

TEST28_H

TEST28_L

TE S T 3 1

TE S T 4 1

0.1U_0201_6.3V6-K

B23

B24

A24

D21

B18

G15

H15

D15

G17

H17

D17

G19

H19

D19

A9

B9

A10

B10

A11

B11

A12

B12

A14

B14

A15

B15

A16

B16

A17

B17

A19

B19

A20

B20

A21

B21

A22

B22

H29

G29

H25

R32

N32

G21

H21

D23

E23

A28

B28

N8

N10

H31

D25

B31

D31

E33

D35

AM21

D33

AM23

UC6

3

2A

2

GND

1

1A

2

1

HDT@

CC21 2

0.01U_0201_10V6K

@

DP_ENBKL

DP_ENVDD

DP_EDP_PWM

DP_150_ZVSS

DP_2K_ZVSS

APU_EDP_AUX

APU_EDP_AUX#

APU_EDP_HPD

APU_DDC_CLK

APU_DDC_DATA

APU_HDMI_HPD

APU_EDP_TX0+

APU_EDP_TX0APU_EDP_TX1+

APU_EDP_TX1-

APU_HDMI_TX2+

APU_HDMI_TX2APU_HDMI_TX1+

APU_HDMI_TX1APU_HDMI_TX0+

APU_HDMI_TX0APU_HDMI_CLK+

APU_HDMI_CLK-

TES T 5

TES T 9

TES T 1 0

APU_TEST14_BP0

APU_TEST15_BP1

APU_TEST16_BP2

APU_TEST17_BP3

APU_TEST18_PLLTEST1

APU_TEST19_PLLTEST0

APU_TEST28_H_PLLCHARZ

APU_TEST28_L_PLLCHARZ

APU_TEST31_MEM_TEST

APU_TEST36_STEREOSYNC

TES T 4 1

APU_VDDCORE_SEN_H

APU_VDDNB_SEN_H

VDDIO_MEM_S3_SENSE

VDD_095_FB_H

APU_VSS_SEN_L

VSS_SENSE_B

1

CC25

2

2Y

VCC

1Y

SN74LVC2G07YZPR_WCSP6HD T@

3

1 2

RC12 150_0402_1%

RC55 2K_0402_1%

1 2

APU_EDP_AUX 23

APU_EDP_AUX# 23

APU_EDP_HPD 23

APU_DDC_CLK 24

APU_DDC_DATA 24

APU_HDMI_HPD 24

AP U _ E D P _ T X 0 + 23

APU_EDP_TX0- 23

AP U _ E D P _ T X 1 + 23

APU_EDP_TX1- 23

APU_HDMI_TX2+ 24

APU_HDMI_TX2- 24

APU_HDMI_TX1+ 24

APU_HDMI_TX1- 24

APU_HDMI_TX0+ 24

APU_HDMI_TX0- 24

APU_HDMI_CLK+ 24

APU_HDMI_CLK- 24

TC1 4 @

1

TC8 0@

1

1

TC8 1@

RC21 1K_0402_5%@

1 2

TC1 8@

1

1 2

RC23 1K_0402_5%@

RC24 1K_0402_5%@

1 2

TC2 1@

1

1

TC2 3@

TC2 5@

1

TC7 8@

1

APU_VDDCORE_SEN_H 49

APU_VDDNB_SEN_H 49

1

@

@

1

TC7 6

TC2 6

1 2

RC23 6 0_0402_5%

TC7 7@

1

+1.8VS+1.8VS

12

RC32

300_0402_5%

HDT@

4

5

6

3

12

RC36

300_0402_5%

HDT@

APU_RST#_BUF

APU_PWROK_BUF

2

APU_DDC_CLK

APU_DDC_DATA

APU_EDP_HPD

eDP

AL E R T #

APU_PROCHOT#_R

HDMI

To EDP panel

eDP

+3VALW_APU

HDMI

DP_EDP_PWM

RPC 14 1K_0404_4P2R_5%

14

23

RC28 1K_0402_5%

1 2

1 2

RC27 1K_0402_5%

@

AP U _ V D D _ S E N _ L 49

APU_VDDNB_SEN_H

APU_VDDCORE_SEN_H

APU_VDD_SEN_L

APU_TEST31_MEM_TEST

1

1

1

+1.8VS

TC2 7@

TC2 8@

TC2 9@

@

@

1 2

1 2

RC27 4

39.2_0402_1%

RC27 5

39.2_0402_1%

+1.8VS

DP_ EN VDD

DP_ENBKL

Reserve follow CRB

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIV ISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIV ISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIV ISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

2017/03/14

2017/03/14

2017/03/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2

RC11

100K_0402_5%

RC13

100K_0402_5%

@

2

G1

+3VALW_APU

G1

12

12

LCD Power IC can change for PCH_ENVDD for cost down

+3VALW_APU

2

RC14

100K_0402_5%

@

G1

12

PCH_ENBKL con EC 1.8V level GPI pin cost down

2017/03/14

2017/03/14

2017/03/14

+3VS_APU

RC71

10K_0402_5%

1 2

5

G2

6

D1

QC8A

PJT7838_SOT363-6

S1

1

RC20 5 0_0402_5%@

1 2

+3VS_APU

RC73

10K_0402_5%

@

1 2

5

G2

6

D1

QC9A

PJT7838_SOT363-6

@

S1

1

1 2

RC20 6 0_0402_5%

+3VS_APU

1 2

RC75

10K_0402_5%

@

3

1 2

5

G2

6

4

D1

QC10A

PJT7838_SOT363-6

@

S1

1

RC20 7 0_0402_5%

1 2

1

RPC 18

1 4

2 3

2.2K_0404_4P2R_5%

RC35 100K_0402_5%

1 2

RPC 11

23

14

1K_0404_4P2R_5%

12

RC70

4.7K_0402_5%

3

D2

QC8B

PJT7838_SOT363- 6

S2

4

12

RC74

4.7K_0402_5%

@

3

D2

QC9B

PJT7838_SOT363- 6

@

S2

4

RC77

2.2K_0402_5%

@

D2

QC10B

PJT7838_SOT363-6

@

S2

Title

Title

Title

FT4 (DISPLAY/CLK/MISC)

FT4 (DISPLAY/CLK/MISC)

FT4 (DISPLAY/CLK/MISC)

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

Cus t om

Cus t om

Cus t om

Date: Sheet of

Date: Sheet of

Date: Sheet of

+3VS_APU

PCH_EDP_PWM 23

PCH_ENVDD 23

PCH_ENBKL 2 3

S145AST

S145AST

S145AST

Thursday, October 25, 2018

Thursday, October 25, 2018

Thursday, October 25, 2018

1

+1.8VS

6 50

6 50

6 50

0.2

0.2

0.2

5

Vinafix.com

PLT_RST#15,26,29,31,35

D D

EC_RSMRST#35

12

RC66

100K_0402_5%@

12

RC43

100K_0402_5%@

LRB751V-40T1G_SOD323-2

RC38 33_0402_5%

1

CC19

150P_25V_J_NPO_0402

2

1 2

RC247 0_0402_5%

DC1

1 2

@

1 2

with QC16,QC17, EC must set EC_RSMRST# and EC_SYS_PWRGD reversed compare to DC1 and DC2

C C

EC_SYS_PWRGD35

PCIE_WAKE#_RA

RC88 0_0402_5%@

AGPIO5

SDM10U45LP-7_DFN1006-2-2

+3VALW_APU

RC84

B B

2.2K_0402_5%

@

1 2

RC195

15K_0402_5%

1 2

1 2

2

@

0_0402_5%

2 1

@

1 2

1 2

12

RC82

100K_0402_5%@

1

RC92

DC3

RC85

1K_0402_5%

@

RC196

15K_0402_5%

1 2

RC95 0_0402_5%

DC2

1 2

LRB751V-40T1G_SOD323-2

PCIE_WAKE# 31,35

RC20

2.2K_0402_5%

@

1 2

TEST0

TEST1

TEST2

RC197

15K_0402_5%

1 2

@

PCIE_RST#_R

+1.8VALW

Connected to 10-ms RC-delay circuit on VDD_18_S5 power rail.

(CRB PWR Dealy: 22K/0.1uF)

12

RC53

10K_0402_5%

RSMRST#_R

+3VS_APU

12

1

CC21

0.1U_0201_6.3V6-K

2

RC72

10K_0402_5%

@

SYS_PWRGD_R

1

CC22

0.1U_0201_6.3V6-K

2

PBTN_OUT#35

PM_SLP_S3#35

PM_SLP_S5#35

Add USB_OC3# for USB2.0 port3

Connect TouchPad to I2C port0 following CRB 10/28

DC4

SYS_PWRGD_RSYS_RESET#

1 2

LRB751V-40T1G_SOD323-2

1

CC38

0.1U_0201_6.3V6-K

2

@

PXS_PWREN_R/PXS_RST#_R/VR_VGA_PWRGD internal pull up 40k

+3VS_APU

5

PXS_PWREN_R

VR_VGA_PWRGD

PXS_PWREN_R

VR_VGA_PWRGD

@

HDA_RST# HDA_RST_AUDIO#

HDA_SYNC

HDA_SDOUT

For EMI

1

CC4222

2P_25V_NPO_0201

2

Close to PCH

1 8

2 7

3 6

4 5

1 2

RC98 10K_0402_5%PX@

1 2

RC100 10K _0402_5%@

1 2

RC101 100K _0402_5%@

1 2

RC104 2K _0402_5%UMA @

A A

VR_VGA_PWRGD

1

CC4223

0.1U_0201_6.3V6-K

2

@

4

RC191 0_0402_5%

SYS_RESET#11

PM_SLP_S3#

RC193 0_0402_5%

PM_SLP_S5#

RC194 0_0402_5%

APU_S5_MUX_CTRL9

AC_PRESENT35

SSD_1_CLKREQ#29

PCH_WLAN_OFF#31

WLAN_CLKREQ#31

PCH_BT_OFF#31

GPU_CLKREQ#16

USB_OC1#25

USB_OC2#25

USB_OC3#25

HDA_SDIN036

RC201 0_0402_5%

TP_I2C0_SCL_R36

TP_I2C0_SDA_R36

Max ESR < 65K ohm !!

RPC21

1K_0804_8P4R_5%

For EMI For EMI

HDA_BITCLK HDA _SYNC HDA_SDOUTHDA_SDIN0_R

1

CC4220

56P_50V_J_NPO_0201

2

EMC@

Close to PCH

4

RC40

RC39

10K_0402_5%

10K_0402_5%

UMA@

TS @

1 2

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

1 2

1 2

1 2

TC 9 0 @

1 2

1 2

RC47

RC48

2K_0402_5%

2K_0402_5%

NOTS@

PCIE_RST#_R

RSMRST#_R

PWRBTN#_RPBTN_OUT#

SYS_PWRGD_R

SYS_RESET#

PCIE_WAKE#_RA

PM_SLP_S3#_R

PM_SLP_S5#_R

AGPIO10

TEST0

TEST1

TEST2

AC_PRESENT

BOARD_ID0

BOARD_ID1

BOARD_ID3

ODD_E N

SSD_1_CLKREQ#

PCH_WLAN_OFF#

WLAN_CLKREQ#

PCH_BT_OFF#

GPU_CLKREQ#

BOARD_ID2

USB_OC1#

USB_OC2#

USB_OC3#

HDA_BITCLK

HDA_SDIN0_R

HDA_SDIN1

HDA_SDIN2

HDA_RST#

HDA_SYNC

HDA_SDOUT

TP_I2C0_SCL_R

TP_I2C0_SDA_R

I2C1SCL

I2C1SDA

1

CC24

2

1

1 2

32K_X1

32K_X2

20P_0402_50V8

PX@

1 2

APU_S5_MUX_CTRL

1

RPC3

1 4

2 3

10K_0404_4P2R_5%

RC102

1 2

20M_0402_5%

YC1

1 2

32.768KHZ_12.5PF_202740-PG14

1

CC23

2

20P_0402_50V8

TC 8 7 @

HDA_SYNC_AUDIO36

HDA_SDOUT_AUDIO36

HDA_BITCLK_AUDIO36

1

CC4221

@

2P_25V_NPO_0201

2

Close to PCH Close to PCH

+3VALW_APU

AE4

AG1

AD2

AE2

AF1

AE7

AC2

AG4

AB1

AA7

AF2

AE1

AC8

AH2

AA4

AG8

AL5

AE8

AY32

AY31

AV29

AP31

AV35

AB2

AG2

AJ1

AH1

AY6

BA6

AY5

BA5

AY4

BA3

BA4

AY22

BA22

AU19

AV19

BA2

AY2

3

RC41

RC1660

10K_0402_5%

10K_0402_5%

BD15@

RC49

2K_0402_5%

BD14@

For EMI

1

CC4219

2P_25V_NPO_0201

2

3

1 2

1 2

@

RC1659

2K_0402_5%

@

ACPI/SD/AZ/GPIO/RTC/MISC

HDA_RST#

HDA_SYNC

HDA_SDOUT

HDA_BITCLK

1 2

1 2

PCIE_RST_L/EGPIO26

RSMRST_L

PWR_BTN_L/AGPIO0

PWR_GOOD

SYS_RESET_L/AGPIO1

WAKE_L/AGPIO2

SLP_S3_L

SLP_S5_L

S0A3_GPIO/AGPIO10

S5_MUX_CTRL/EGPIO42

TEST0

TEST1/TMS

TEST2

AC_PRES/USB_OC4_L/IR_RX0/AGPI O23

IR_TX0/USB_OC5_L/AGPIO13

IR_TX1/USB_OC6_L/AGPIO14

IR_RX1/AGPIO15

IR_LED_L/LLB_L/AGPIO12

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

CLK_REQ1_L/AGPIO115

CLK_REQ2_L/AGPIO116

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

CLK_REQG_L/OSCIN/EGPIO132

USB_OC0_L/TRST_L/AGPIO16

USB_OC1_L/TDI/AGPIO17

USB_OC2_L/TCK/AGPIO18

USB_OC3_L/TDO/AGPIO24

AZ_BITCLK/I2S_BCLK_MIC

AZ_SDIN0/I2S_DATA_MIC 0

AZ_SDIN1/I2S_LR_PLAYBACK

AZ_SDIN2/I2S_DATA_PLAYBACK

AZ_RST_L/I2S_LR_MIC

AZ_SYNC/I2S_BCLK_PLAYBACK

AZ_SDOUT/I2S_DATA_MIC 1

I2C0_SCL/EGPIO145

I2C0_SDA/EGPIO146

I2C1_SCL/EGPIO147

I2C1_SDA/EGPIO148

X32K_X1

X32K_X2

@

RPC4

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

@

2

1

0

1

AGPIO3

AGPIO4

AGPIO5

AGPIO8

AGPIO9

AGPIO40

HVBEN_L

RTCCLK

BOARD

BOARD_ID1

Config.

DIS

UMA 1

BA28

AY29

AY13

BA14

AY15

BA29

AY14

BA13

BA16

AY16

AY33

BA32

AC5

AC4

AJ7

AK2

AK1

AL4

AJ2

AJ4

AG5

AD1

AJ8

AR29

AP29

AU35

AV33

AU33

AP23

AP25

AR25

AV25

AU23

AP21

AV21

AP19

AV23

AR21

AP27

AN4

0

1 2

RC1667 0_0402_5%PX@

EGPIO101

SD_PWR_CNTL

1

ODD_DETECT#

1

1

1

SD_LED

1 2

RC1670 0_0402_5%@

SD_DATA0_R

1 2

RC1673 0_0402_5%

SD_DATA1_R

1

SD_DATA2_R

1

SD_DATA3_R

1

APU_SMB_CLK

APU_SMB_DATA

RPC2

1 4

SCL1

2 3

SDA1

@

10K_0404_4P2R_5%

AGPIO5

PCH_TP_INT#_L

AGPIO8

PCH_PWRBT#

BLINK

VR_VGA_PWRGD

PXS_PWREN_R

PCH_TP_INT#_R PCH_TP_INT#

APU_UART0_CTS#

APU_UART0_RXD

APU_UART0_RTS#

APU_UART0_TXD

RC109 1K _0402_5%PX@

RC1662

PXS_RST# change from AGPIO76 to EGPIO101

TC 4 4@

TC 8 9@

TC 4 5@

TC 5 9@

SSD_SATA_PCIE_DET1#

APU_SSD_RST#

TC 6 3@

TC 6 4@

add APU_SSD_RST#

TC 6 5@

APU_SMB_CLK 12,31

APU_SMB_DATA 12,31

AGPIO3 11

1

TC 8 3@

USBDEBUG 25

1 2

RC1663 0_0402_5%

1

TC 9 2@

PCH_PWRBT# 35

VR_VGA_PWRGD 15,48

PCH_BEEP 36

GATEA2 0 35

1 2

1

2

@

0_0402_5%

reserve UART0 for BIOS debug

PCH_SPI_PIRQ# 26

delete APU_SHUTDOWN# signal for Stoney FT4

HVB_EN

APU_S5_MUX_CTRL 100K pull high follow CRB

BLINK isn't strap pin, don't need pull high

HVB_EN 11,35

SUSCLK 11,29,31

PXS_RST# 8,15

add USBDEBUG

BOARD

BOARD_ID0

Config.

TS

NOTS 0

BOARD

BOARD_ID3

Config.

14'

15'

UC2D

SD_WP/EGPIO101

SD_PWR_CTRL/AGPIO102

SD_CD/AGPIO25

SD_CLK/EGPIO95

SD_CMD/EGPI O96

SD_LED/EGPIO93

SD_DATA0/EGPIO97

SD_DATA1/EGPIO98

SD_DATA2/EGPIO99

SD_DATA3/EGPIO100

SCL0/I2C2_SCL/EGPIO113

SDA0/I2C2_SDA/EGPIO114

SCL1/I2C3_SCL/AGPIO19

SDA1/I2C3_SDA/AGPIO20

AGPIO6/LDT_RST_L

AGPIO7/LDT_PWROK

BLINK/USB_OC7_L/AGPIO11

GENINT2_L/AGPIO90

SPKR/AGPIO91

GA20IN/AGPIO126

FANIN0/AGPIO84

FANOUT0/AGPIO85

UART0_CTS_L/EGPIO135

UART0_RXD/EGPIO136

UART0_RTS_L/EGPIO137

UART0_TXD/EGPIO138

UART0_INTR/AGPIO139

UART1_CTS_L/BT_I2S_BCLK/EGPIO140

UART1_RXD/BT_I2S_SDI/ EGPIO141

UART1_RTS_L/EGPIO142

UART1_TXD/BT_I2S_SDO/EGPIO143

UART1_INTR/BT_I2S_LRC LK/AGPIO144

FT4 REV 0.93

AMD-STONEY-FT4_BGA769

follow Checklist, HDA_BITCLK PD reserve

CRB: CARRIZO NEED 10K PD ON UNUSED SDIN

DG: 10K PD

Securi ty Cl assific ation

Securi ty Cl assific ation

Securi ty Cl assific ation

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2017/03/14

2017/03/14

2017/03/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciph ered Date

Deciph ered Date

Deciph ered Date

2

SSD_SATA_PCIE_DET1# 29

APU_SSD_RST# 29

PCH_TP_INT# 36

PXS_PWREN 47,48

2017/03/14

2017/03/14

2017/03/14

1

+3VS_APU

PCH_TP_INT#

APU_SSD_RST#

APU_SMB_CLK

APU_SMB_DATA

SSD_1_CLKREQ#

WLAN_CLKREQ#

PCH_BT_OFF#

PCH_WLAN_OFF#

PCH_PWRBT#

GPU_CLKREQ#

GATEA 20

PXS_RST#

TP_I2C0_SCL_R

TP_I2C0_SDA_R

APU_UART0_CTS#

APU_UART0_RXD

APU_UART0_RTS#

APU_UART0_TXD

PCIE_WAKE#_RA

AC_PRESENT

PBTN_ OUT#

USB_OC1#

USB_OC2#

USB_OC3#

PM_SLP_S3#

PM_SLP_S5#

APU_S5_MUX_CTRL

BLINK

APU_SSD_RST#

PCH_TP_INT#

SD_LED

AGPIO10

GPU_CLKREQ#

HDA_BITCLK

HDA_SDIN0_R

RSMRST#_R

SYS_PWRGD_R

HDA_SDIN2

HDA_SDIN1

Title

Title

Title

FT4 (GEVENT/GPIO/SD/AZ)

FT4 (GEVENT/GPIO/SD/AZ)

FT4 (GEVENT/GPIO/SD/AZ)

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

Thursday, October 25, 2018

Thursday, October 25, 2018

Thursday, October 25, 2018

Date: Sheet of

Date: Sheet of

Date: Sheet of

1 2

RC1655 10K_0402_5%

1 2

RC1671 10K_0402_5%

RPC9

23

14

2.2K_0404_4P2R_5%

RPC6

18

27

36

45

10K_0804_8P4R_5%

1 2

RC287 10K_0402_5%@

1 2

RC64 10K_0402_5%UMA@

1 2

RC276 10K_0402_5%

2

1

RC280 10K_0402_5%@

2

1

RC281 10K_0402_5%PX@

RPC19

1 4

2 3

2.2K_0404_4P2R_5%

2

2

2

2

RPC15

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

RPC22

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

1 2

1 2

1 2

STN@

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

RPC24

1 4

2 3

1/16W_100K_5%_4P2R_0404

RPC23

1 4

2 3

10K_0404_4P2R_5%

S145AST

S145AST

S145AST

1

1

1

1

1

7 50

7 50

7 50

RC3136 1K_0402_1%@

RC3137 1K_0402_1%@

RC3138 1K_0402_1%@

RC3139 1K_0402_1%@

RC203 2.2K_0402_5%@

RC208 2.2K_0402_5%@

RC248 100K_0402_5%

RC277 10K_0402_5%@

RC1672 10K_0402_5%@

RC1661 10K_0402_5%@

RC97 10K_0402_5%@

RC80 10K_0402_5%@

RC65 2K_0402_5%PX@

RC1675 10K_0402_5%@

RC91 10K_0402_5%@

+1.8VS

+3VALW_APU

0.2

0.2

0.2

5

Vinafix.com

SATA_PTX_DRX_P034

RPC13

23

14

D D

C C

B B

10K_0404_4P2R_5%

STN@

1 2

RC147 10K_0402_5%

Add 0ohm for LPC DAT, cause

LPC data signal overshoot/undershoot issue

APU_LPC_RST#35

1 2

RC140 1M_0402_5%

YC2

1

OSC 1

1

2

NC12OSC 2

48MHZ 10PF X1E000021083400

CC28

12P_0402_50V8-J

NC2

SATA0_DEVSLP_R

EGPIO70

APU_TS_ON#

CLK_PCIE_GPU15

CLK_PCIE_GPU#15

CLK_PCIE_SSD29

CLK_PCIE_SSD#2 9

CLK_PCIE_WLAN31

CLK_PCIE_WLAN#31

RC149 10K_0402_5%

48M_X1

48M_X2

4

3

1

2

HDD

+0.95VS

CLK_PCI_EC11,35

LPC_CLK111

1 2

1 2

RC46 33_0402_5%

1

CC20

150P_25V_J_NPO_0402

2

CC29

12P_0402_50V8-J

SATA_PTX_DRX_N034

SATA_PRX_DTX_N034

SATA_PRX_DTX_P034

RC113 1K_0402_1%

RC114 1K_0402_1%

CLK_PCIE_GPU#

CLK_PCIE_SSD# CLK_PCIE_SSD#_R

CLK_PCIE_WLAN#

RC126 0_0402_5%

RC127 0_0402_5%

LPC_FRAME#11, 35

LPC_AD035

LPC_AD135

LPC_AD235

LPC_AD335

LPC_RST#_R

8M ROM

with BOM strcture control, UC3 change to 1.8V SPI ROM for CZ

4

SATA_PTX_DRX_P0

SATA_PTX_DRX_N0

SATA_PRX_DTX_N0

SATA_PRX_DTX_P0

X14M_25M_48M_OSC

1 2

1 2

1 2

1 2

1 2

1

UC3

1

/CS

2

DO( I O1 )

3

/WP(IO2)

4

GND

W25Q64FWSSIQ_SO 8

SATA_CALRN

SATA_CALRP

APU_TS_ON#

SATA0_DEVSLP_R

EGPIO70

CLK_PCIE_GPU_RCLK_PCIE_GPU

CLK_PCIE_GPU#_R

CLK_PCIE_SSD_RCLK_PCIE_SSD

CLK_PCIE_WLAN_RCLK_PCIE_WLAN

CLK_PCIE_WLAN#_R

48M_X1

48M_X2

LPCCLK0

LPCCLK1

LPC_RST#_R

AGPIO21

ODD_DA#

/HOLDor/RESET(IO3)

1 2

1 2

1 2

RC117 0_0402_5%

1 2

RC118 0_0402_5%

1 2

RC1665 0_0402_5%

1 2

RC1664 0_0402_5%

1 2

RC119 0_0402_5%

1 2

RC120 0_0402_5%

1

TC53 @

1 2

1 2

RC3144 0_0402_5%

RC3140 0_0402_5%

RC3141 0_0402_5%

RC3142 0_0402_5%

RC3143 0_0402_5%

EC_SCI#35

TC91 @

SERIRQ35

SPI_CS0#

SPI_SO SPI_HOLD#

FRAME#

LAD0

LAD1

LAD2

LAD3

VCC

CLK

DI (I O0 )

BA10

SATA_TX0P

AY10

SATA_TX0N

AY12

SATA_RX0N

BA12

SATA_RX0P

AY9

SATA_TX1P

BA9

SATA_TX1N

BA8

SATA_RX1N

AY8

SATA_RX1P

AU11

SATA_ZVSS

AP11

SATA_ZVDDP

AY30

SATA_ACT_L/AGPIO130

AV31

DEVSLP0/EGPIO67

AU31

DEVSLP1/EGPIO70

H2

GFX _CLK P

H1

GFX _CLK N

M2

GPP _CLK 0P

M1

GPP _CLK 0N

L2

GPP _CLK 1P

L1

GPP _CLK 1N

K2

GPP _CLK 2P

K1

GPP _CLK 2N

J2

GPP _CLK 3P

J1

GPP _CLK 3N

F2

X48M_X1

F1

X48M_X2

AU27

X25M_48M_OSC

BA25

LPCCLK0/EGPIO74

BA24

LPCCLK1/EGPIO75

AY24

LFRAME_L

BA26

LAD0

AY28

LAD1

AY25

LAD2

AY23

LAD3

AY27

LPC_RST_L

AY26

LPC_CLKRUN_L/AGPIO88

AC1

LPC_PD_L/AGPIO21

AA8

LPC_PME_L/AGPIO22

BA27

LPC_SMI_L/AGPIO86

AV27

SERIRQ/AGPIO87

@

8

7

SPI_CLKSPI_WP#

6

SPI_SI

5

+VCC_SPI

3

UC2E

CLK/SATA/USB/SPI/LPC

USBCLK/25M_48M_OSC

SPI_CLK/ESPI_CLK/EGPIO117

SPI_DO/ESPI_DAT0/EGPIO121

SPI_DI/ESPI_DAT1/EGPIO120

SPI_HOLD_L/ESPI_DAT3/E GPIO133

SPI_WP_L/ESPI_DAT2/EGPIO122

SPI_TPM_CS_L/AGPIO76

ESPI_ALERT_L/LDRQ0_L

ESPI_RESET_L/KBRST_L/AGPIO129

SPI_CS2_L/ESPI_CS_L/EGPIO119

FT4 REV 0.93

AMD-STONEY-FT4_BGA769

1

CC27

0.1U_0201_6.3V6-K

2

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

USB_HSD6P

USB_HSD6N

USB_HSD7P

USB_HSD7N

USB_SS_ZVSS

USB_SS_ZVDDP

USB_SS_0TXP

USB_SS_0TXN

USB_SS_0RXP

USB_SS_0RXN

USB_SS_1TXP

USB_SS_1TXN

USB_SS_1RXP

USB_SS_1RXN

USB_SS_2TXP

USB_SS_2TXN

USB_SS_2RXP

USB_SS_2RXN

SPI_CS1_L/EGPIO118

+VCC_SPI

SPI_WP#

SPI_HOLD#

SPI_CS0#

CLK_USB48M

AL8

USB_RCOMP

AN7

AW1

AW2

AV1

AV2

AU1

AU2

AT1

AT2

AR1

AR2

AP1

AP2

AN1

AN2

AM1

AM2

W4

W5

T1

T2

V2

V1

R1

R2

W2

W1

P1

P2

Y2

Y1

AY17

AY20

BA17

BA18

BA20

AY21

BA21

AY18

BA30

AY19

+VCC_SPI

RC138 10K_0402_5%

RC112 11.8K_0402_1%

USB20_P0

USB20_N0

USB20_P1

USB20_N1

USB20_P2

USB20_N2

USB20_P3

USB20_N3

USB20_P4

USB20_N4

USB20_P5

USB20_N5

USB20_P6

USB20_N6

USBSS_CALRN

USBSS_CALRP

USB30_TX_P0

USB30_TX_N0

USB30_RX_P0

USB30_RX_N0

USB30_TX_P1

USB30_TX_N1

USB30_RX_P1

USB30_RX_N1

SPI_CLK_R

SPI_SI_R

SPI_SO_R

SPI_HOLD#_R

SPI_WP#_R

SPI_CS0#_R

SPI_TPM_CS_R

1

EGPIO119

RC135 0_0402_5%@

RC192 0_0402_5%

RPC8

1 4

2 3

10K_0404_4P2R_5%

1 2

2

1

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

KBRST#

TC69@

Card Reader

Blue Tooth

Camera

LEFT USB (2.0)

LEFT USB (3.0) lower

LEFT USB (3.0) upper

Touch Screen

@

KBRST# 35

1 2

USB20_P0 36

USB20_N0 36

USB20_P1 31

USB20_N1 31

USB20_P2 23

USB20_N2 23

USB20_P3 25

USB20_N3 25

USB20_P4 25

USB20_N4 25

USB20_P5 25

USB20_N5 25

USB20_P6 23

USB20_N6 23

1 2

RC123 1K_0402_1%

1 2

RC124 1K_0402_1%

USB30_TX_P0 25

USB30_TX_N0 25

USB30_RX_P0 25

USB30_RX_N0 25

USB30_TX_P1 25

USB30_TX_N1 25

USB30_RX_P1 25

USB30_RX_N1 25

RC209 0_0402_5%

RC198 0_0402_5%

RC199 0_0402_5%

RC133 0_0402_5%

RC132 0_0402_5%

RC202 0_0402_5%

RC243 0_0402_5%TPM@

RC1674 0_0402_5%

TC54@

KBRST#

1 2

1 2

+VCC_SPI

1

USB3.0 port0 must map to USB2.0 port4,

USB3.0 port1 must map to USB2.0 port5,

USB3.0 port2 must map to USB2.0 port6

+0.95VALW

Connect the four USB 3.0 ports to onboard devices first

starting from the lower ports and then the remaining

ports can be used for routing to USB 3.0 connectors.

Less than four USB 3.0 ports can be utilized provided

the unused ports are higher-numbered consecutive

LEFT USB (3.0) lower

ports.

None of the four USB 3.0 ports can be configured

as USB 2.0 external ports.

LEFT USB (3.0) upper

SPI_CLK

SPI_SI

SPI_SO

SPI_HOLD#

SPI_WP#

SPI_CS0#

SPI_CS#_TPM

PXS_RST# 7,15

1 2

RC279 10K_0402_5%

+3VALW_APU

+1.8VS

2

SPI_CLK

SPI_CLK 26

SPI_SI 26

SPI_SO 26

SPI_CS#_TPM 26

1

RC14410K_0402_5% STN@

+3VS_APU

RC139

10_0402_5%

EMC_NS@

1 2

2

CC26

10P_0402_50V8J

EMC_NS@

1

EMC

KBRST#

EMC_NS@

1 2

CC1274

1000P_0402_25V7-K

A A

5

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEE RING DRAWING IS THE PROPRIETARY P ROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAWING IS THE PROPRIETARY P ROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAWING IS THE PROPRIETARY P ROPERTY OF LC FUTURE CENTER. AND CONT AINS CONFIDENTIAL

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R& D

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R& D

AND TRADE SECRET INFORMA TION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R& D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2017/03/14

2017/03/14

2017/03/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2017/03/14

2017/03/14

2017/03/14

Title

FT4 (SATA/USB/LPC/SPI)

FT4 (SATA/USB/LPC/SPI)

FT4 (SATA/USB/LPC/SPI)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

S145AST

S145AST

S145AST

Thursday, October 25, 2018

Thursday, October 25, 2018

Thursday, October 25, 2018

8 5 0

8 5 0

8 5 0

1

0.2

0.2

0.2

5

Vinafix.com

4

3

2

1

+1.2V

1

1

+1.2V

1

1

D D

SIVCD@

+0.95VS

1

CC222

CC221

2

SIVCD@

22UC_6.3VC_MC_X5RC_0603

C C

VCCRTC

RC231 10K_0402_5%

B B

+1.2V

CC168

A A

1

CC42

CC55

CC54

2

22UC_6.3VC_MC_X5RC_0603

1

1

CC223

2

2

SIVCD@

22UC_6.3VC_MC_X5RC_0603

1 2

1

1

CC169

2

2

0.22U_0201_6.3V6-K

SIVCD@

DECOUPLING BETWEEN PROCESSOR AND DIMMs

ACROSS VDDIO AND VSS SPLIT

CC56

2

2

22UC_6.3VC_MC_X5RC_0603

22UC_6.3VC_MC_X5RC_0603

1

1

CC174

CC224

CC225

2

2

SIVCD@

22UC_6.3VC_MC_X5RC_0603

22UC_6.3VC_MC_X5RC_0603

22UC_6.3VC_MC_X5RC_0603

1

CC37

AP2138N-1.5TRG1_SOT23-3

2

1U_0402_6.3V6K

1

1

CC170

CC172

2

2

0.22U_0201_6.3V6-K

0.22U_0201_6.3V6-K

0.22U_0201_6.3V6-K

SIVCD@

5

1

1

1

CC58

CC57

CC59

2

2

2

SIVCD@

22UC_6.3VC_MC_X5RC_0603

22UC_6.3VC_MC_X5RC_0603

22UC_6.3VC_MC_X5RC_0603

1

1

CC227

CC226

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

SIVCD@

UC5

1

Vi n

3

Vo u t

2

GND

1

1

CC176

CC179

2

2

SIVCD@

180P_50V_J_NPO_0402

1

1

CC60

2

2

22UC_6.3VC_MC_X5RC_0603

22UC_6.3VC_MC_X5RC_0603

1

1

CC228

2

2

1000P_16V_K_X7R_0402

1000P_16V_K_X7R_0402

RC6

+1.8VS

RC212 0_0402_5%

+RTCBATT

1

CC194

2

1U_0402_6.3V6K

180P_0402_50V8-J

1

CC53

2

SIVCD@

1

CC229

2

1 2

1K_0402_5%

1 2

1000P_16V_K_X7R_0402

CC258

22UC_6.3VC_MC_X5RC_0603

1

1

CC230

CC203

2

2

1000P_16V_K_X7R_0402

180P_50V_J_NPO_0402

CD@

+RTCBATT_APU+RTCBATT

CC192

+VDDIO_AZ_APU

12

JCMOS1

SHORT PADS

@

L2N7002KWT1G_SOT323-3

1

CC185

2

2

1U_0402_6.3V6K

CD@

1

CC220

47P_0402_50V8J

RF_NS@

2

0.1A

1

2

1U_0402_6.3V6K

0.2A

12

RC8

470_0603_5%

13

D

S

@

+APU_CORE_NB

1

CC207

10U_0603_6.3V6M

2

SDVCD@

1U_0402_6.3V6K

CC236

QC7

CC214

2

1

2

1U_0402_6.3V6K

@

EC_RTCRST#_ON

2

G

+0.775VALW

1

2

SDVCD@

4

CC165

1U_0402_6.3V6K

+APU_CORE

+0.95VALW

CC182

1

CC235

CC234

2

SIVCD@

1000P_16V_K_X7R_0402

CC208

10U_0603_6.3V6M

1

2

180P_50V_J_NPO_0402

1

CC215

2

1U_0402_6.3V6K

1

2

10U_0603_6.3V6M

1 2

1000P_0402_25V7-K

12

RC15

100K_0402_5%

@

+5VALW

CC209

SDVCD@

22A

1

CC216

2

SIVCD@

0.79A

1

CC219

2

1U_0402_6.3V6K

EC_RTCRST#_ON 35

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

CC231

SIVCD@

1

CC137

2

180P_50V_J_NPO_0402

1 2

1000P_0402_25V7-K

UC7

1

2

3

G5018RD1U_TDFN8_3X3

STN@

+1.2V

+VDDCR_FCH_S5

+0.95VS

6.9A

VO U T _ 1

VI N 1 _ 1

VI N 1 _ 2

VO U T _ 2

VI N 2

VC C4EN

0.4A

GND

J35

3A

VDDIO_MEM_S3_1

L32

VDDIO_MEM_S3_2

L37

VDDIO_MEM_S3_3

N35

VDDIO_MEM_S3_4

R37

VDDIO_MEM_S3_5

U32

VDDIO_MEM_S3_6

U35

VDDIO_MEM_S3_7

W32

VDDIO_MEM_S3_8

W37

VDDIO_MEM_S3_9

AA 3 5

VDDIO_MEM_S3_10

AC 3 2

VDDIO_MEM_S3_11

AC 3 7

VDDIO_MEM_S3_12

AE 3 2

VDDIO_MEM_S3_13

AE 3 5

VDDIO_MEM_S3_14

AG 3 2

VDDIO_MEM_S3_15

AG 3 7

VDDIO_MEM_S3_16

AJ 3 2

VDDIO_MEM_S3_17

AJ 3 5

VDDIO_MEM_S3_18

AL 3 2

VDDIO_MEM_S3_19

AL 3 7

VDDIO_MEM_S3_20

A

R35

VDDIO_MEM_S3_21

K21

VD D C R _ C P U _ 1

K23

VD D C R _ C P U _ 2

K25

VD D C R _ C P U _ 3

K27

VD D C R _ C P U _ 4

K29

VD D C R _ C P U _ 5

K31

VD D C R _ C P U _ 6

N21

VD D C R _ C P U _ 7

N23

VD D C R _ C P U _ 8

N25

VD D C R _ C P U _ 9

N27

VDDCR_CPU_10

N29

VDDCR_CPU_11

N31

VDDCR_CPU_12

U23

VDDCR_CPU_13

U25

VDDCR_CPU_14

U27

VDDCR_CPU_15

U29

VDDCR_CPU_16

U31

VDDCR_CPU_17

AA 2 5

VDDCR_CPU_18

AA 2 7

VDDCR_CPU_19

AA 2 9

VDDCR_CPU_20

AA 3 1

VDDCR_CPU_21

AR 4

VD D C R _ F C H _ S 5 _ 1

AR 5

VD D C R _ F C H _ S 5 _ 2

AR 7

VD D C R _ F C H _ S 5 _ 3

AU 7

VD D C R _ F C H _ S 5 _ 4

AJ 1 1

VDDP_S5_1

AL 1 1

VDDP_S5_2

AL 1 3

VDDP_S5_3

AJ 2 1

VD D P _ 1

AJ 2 3

VD D P _ 2

AJ 2 5

VD D P _ 3

AJ 2 7

VD D P _ 4

AL 2 3

VD D P _ 5

AL 2 5

VD D P _ 6

AL 2 7

VD D P _ 7

AL 2 9

VD D P _ 8

AM 1 1

VDDBT_RTC_G

AM 1 3

VDDIO_AUDIO

@

8

7

APU_S5_MUX_CTRL

6

SEL

5

9

+0.95VALW

2.2U_0402_6.3V6M

+VDDCR_FCH_S5

UC2F

POWER

VDDCR_NB_1

VDDCR_NB_2

VDDCR_NB_3

VDDCR_NB_4

VDDCR_NB_5

VDDCR_NB_6

VDDCR_NB_7

VDDCR_NB_8

VDDCR_NB_9

VDDCR_NB_10

VDDCR_NB_11

VDDCR_NB_12

VDDCR_NB_13

VDDCR_NB_14

VDDCR_NB_15

VDDCR_NB_16

VDDCR_NB_17

VDDCR_NB_18

VDDCR_NB_19

VDDCR_NB_20

VDDCR_NB_21

VDDCR_NB_22

VDDCR_NB_23

VDDCR_NB_24

VDDCR_NB_25

VDDCR_NB_26

VDDCR_NB_27

VDDCR_NB_28

VDDCR_NB_29

VDDCR_NB_30

VDDCR_NB_31

VDDCR_NB_32

VDDCR_NB_33

VDDCR_NB_34

VDDCR_NB_35

VDDCR_NB_36

VDDCR_NB_37

VDDCR_NB_38

VDDCR_NB_39

VDDCR_NB_40

VDDCR_NB_41

VDDCR_NB_42

VDDCR_NB_43

VDDCR_NB_44

VDDCR_NB_45

VDDCR_NB_46

VDDCR_NB_47

VDDCR_NB_48

VDDCR_NB_49

VDDCR_NB_50

VDD_18_1

VDD_18_2

VDD_18_S5_1

VDD_18_S5_2

VDD_33_1

VDD_33_2

VDD_33_S5_1

VDD_33_S5_2

FT4 REV 0.93

AMD-STONEY-FT4_BGA769

2

2

CC1280

CC1281

1

1

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

EMC_NS@

EMC_NS@

EMC_NS@

APU_S5_MUX_CTRL 7

3

+APU_CORE_NB

18A

E9

E11

E13

E15

E17

E19

G7

J7

K11

K13

K15

K17

K19

ϮϯϳϮϯϴ^ƚƵĨĨĨŽƌ

L7

DƚĞƐƚĨĂŝůϭϬϭϲ

L10

L15

L17

N7

N11

N13

N15

N17

N19

R7

U7

U11

U13

U15

U17

U19

U21

W7

AA 1 1

AA 1 3

AA 1 5

AA 1 7

AA 1 9

AA 2 1

AA 2 3

AE 1 1

AE 1 3

AE 1 5

AE 1 7

AE 1 9

AE 2 1

AE 2 3

AE 2 5

AE 2 7

AE 2 9

AE 3 1

+1.8VS

AJ 1 5

1.5A

AL 1 7

AJ 1 3

0.5A

AL 1 5

AJ 1 9

0.2A

AL 2 1

+3VALW_A PU

AJ 1 7

0.2A

AL 1 9

2

2

CC1282

1

2.2U_0402_6.3V6M

EMC_NS@

2

2

CC1284

CC1283

1

1

1

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

EMC_NS@

EMC_NS@

1

1

CC162

CC217

2

2

10U_0603_6.3V6M

STN@

STN@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRA WING IS THE PROPRIETARY PROP ERTY OF LC FUTURE CENTER. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRA WING IS THE PROPRIETARY PROP ERTY OF LC FUTURE CENTER. A ND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRA WING IS THE PROPRIETARY PROP ERTY OF LC FUTURE CENTER. A ND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

+1.8VALW

CC1285

1U_0402_6.3V6K

CC218

SIVCD@

1

2

CC232

1U_0402_6.3V6K

SIVCD@

+APU_CORE_NB

EMC_PX@

1

CC252

2

CC233

1 2

1000P_0402_25V7-K

STN@

2017/03/14

2017/03/14

2017/03/14

1

1

CC237

CC238

2

2

EMC@

1000P_16V_K_X7R_0402

OK

+1.8VS

1

1

CC246

CC247

2

2

10U_0603_6.3V6M

1

CC253

2

1U_0402_6.3V6K

10U_0603_6.3V6M

1

2

1000P_16V_K_X7R_0402

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

1

1

CC240

CC241

CC239

2

2

CD@

1000P_16V_K_X7R_0402

22UC_6.3VC_MC_X5RC_0603

22UC_6.3VC_MC_X5RC_0603

CC245

1 2

1U_0402_6.3V6K

1000P_0402_25V7-K

SIVCD@

RC214 0_0402_5%

1 2

CC251

1 2

1000P_0402_25V7-K

SIVCD@

VDDCR_CPU

VDDCR_NB

VDDCR_GFX

VDDIO_MEM_S3

VDDCR_FCH_S5

VDDP

VDDP_GFX

VDDP_S5

VDD_18

VDD_18_S5

VDD_33

VDD_33_S5

VDDIO_AUDIO

VDDBT_RTC_G

Deciphered Date

Deciphered Date

Deciphered Date

2

1

CC242

2

SIVCD@

22UC_6.3VC_MC_X5RC_0603

+1.8VALW

1

CC249

2

10U_0603_6.3V6M

Design Guide CRBG FT4

7*22uf 0603

2*1uf 0402

1*180pf 0402

11*22uf 0603

1*1uf 0402

1*180pf 0402

9*22uf 0603