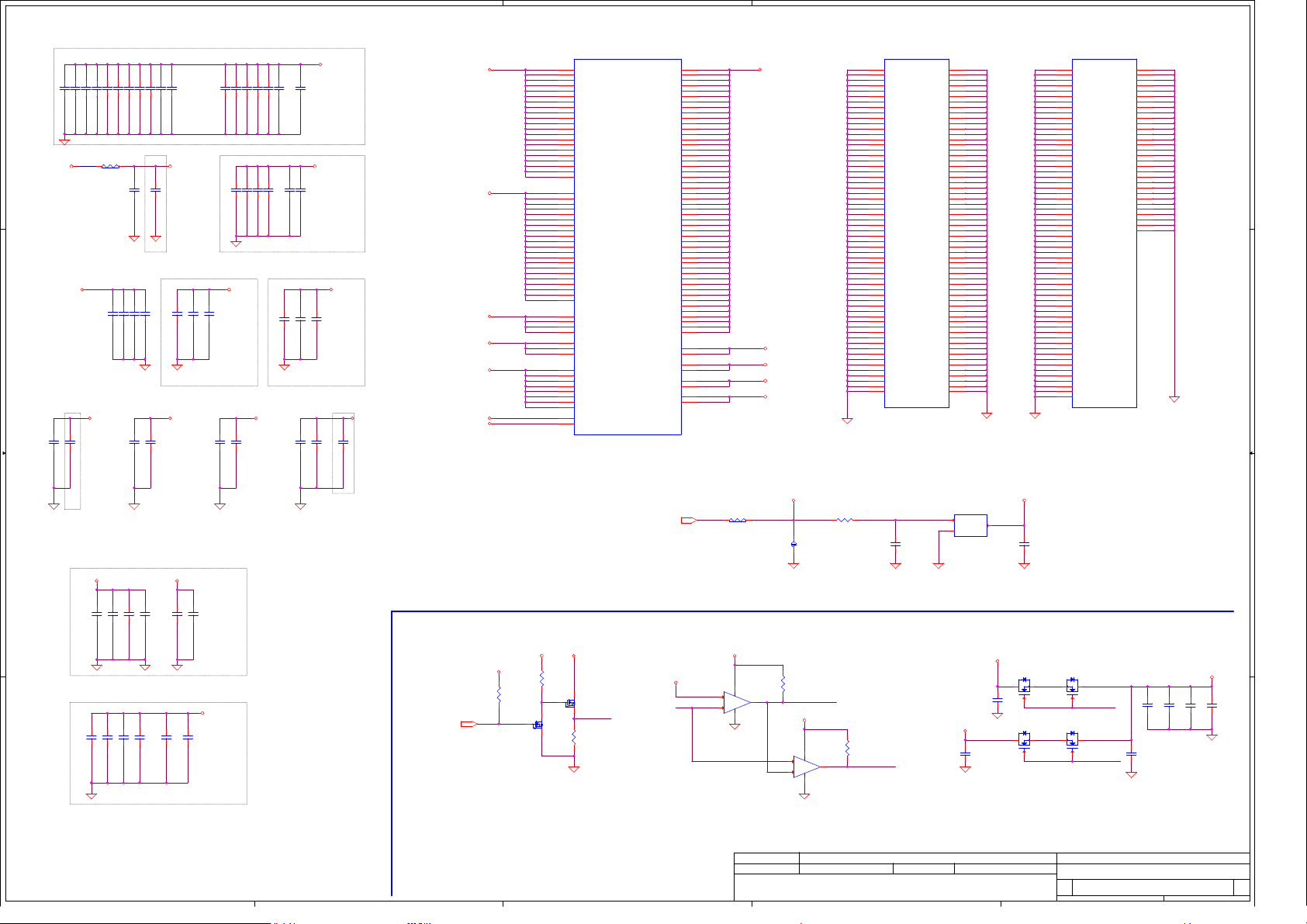

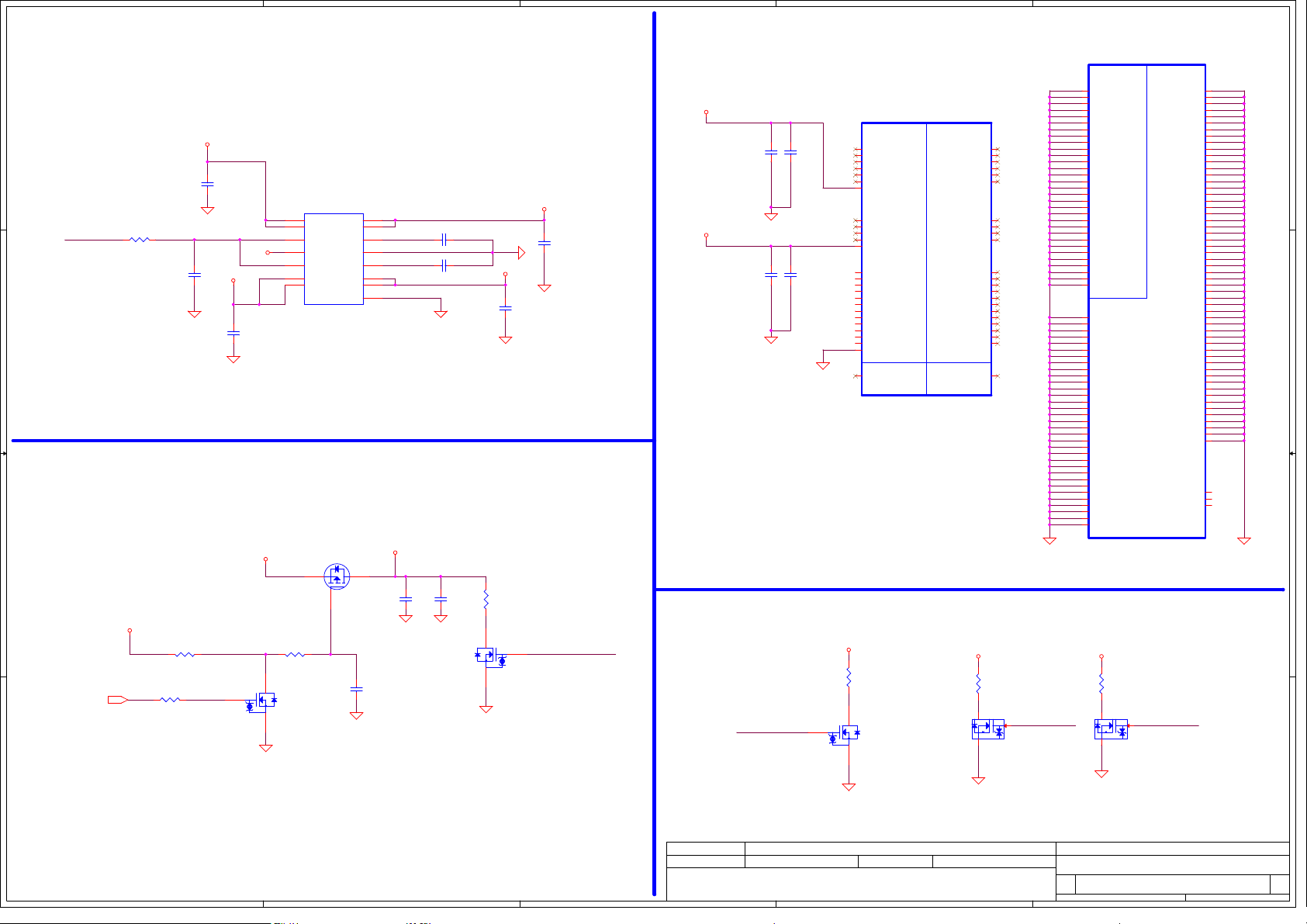

LCFC DIS M schematics

A

1 1

B

C

D

E

Compal C

2 2

DIS M

/B Schematics Document

AMD S

toney Ridge FT4

onfidential

LA-G241P

3 3

2018

R E V

-03-12

:

:

1 . 0

::

4 4

Secu

Secu

Secu

rity Classification

rity Classification

rity Classification

Issued Date

Issued Date

Issued Date

THIS

THIS

THIS

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

2018

2018

2018

/03/12 2019/03/ 12

/03/12 2019/03/ 12

/03/12 2019/03/ 12

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Comp

Comp

Comp

al Electronics, Inc.

al Electronics, Inc.

Titl

Titl

Titl

e

e

e

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Cust

Cust

Cust

om

om

om

Date : Sheet

Date : Sheet

D

Date : Sheet

al Electronics, Inc.

Cove

Cove

Cove

r Page

r Page

r Page

LA-G

LA-G

LA-G

241P

241P

241P

1 43Monday, March 12 , 2018

1 43Monday, March 12 , 2018

1 43Monday, March 12 , 2018

E

1.0

1.0

1.0

o f

o f

o f

A

www.schematic-x.blogspot.com

B

C

D

E

1 1

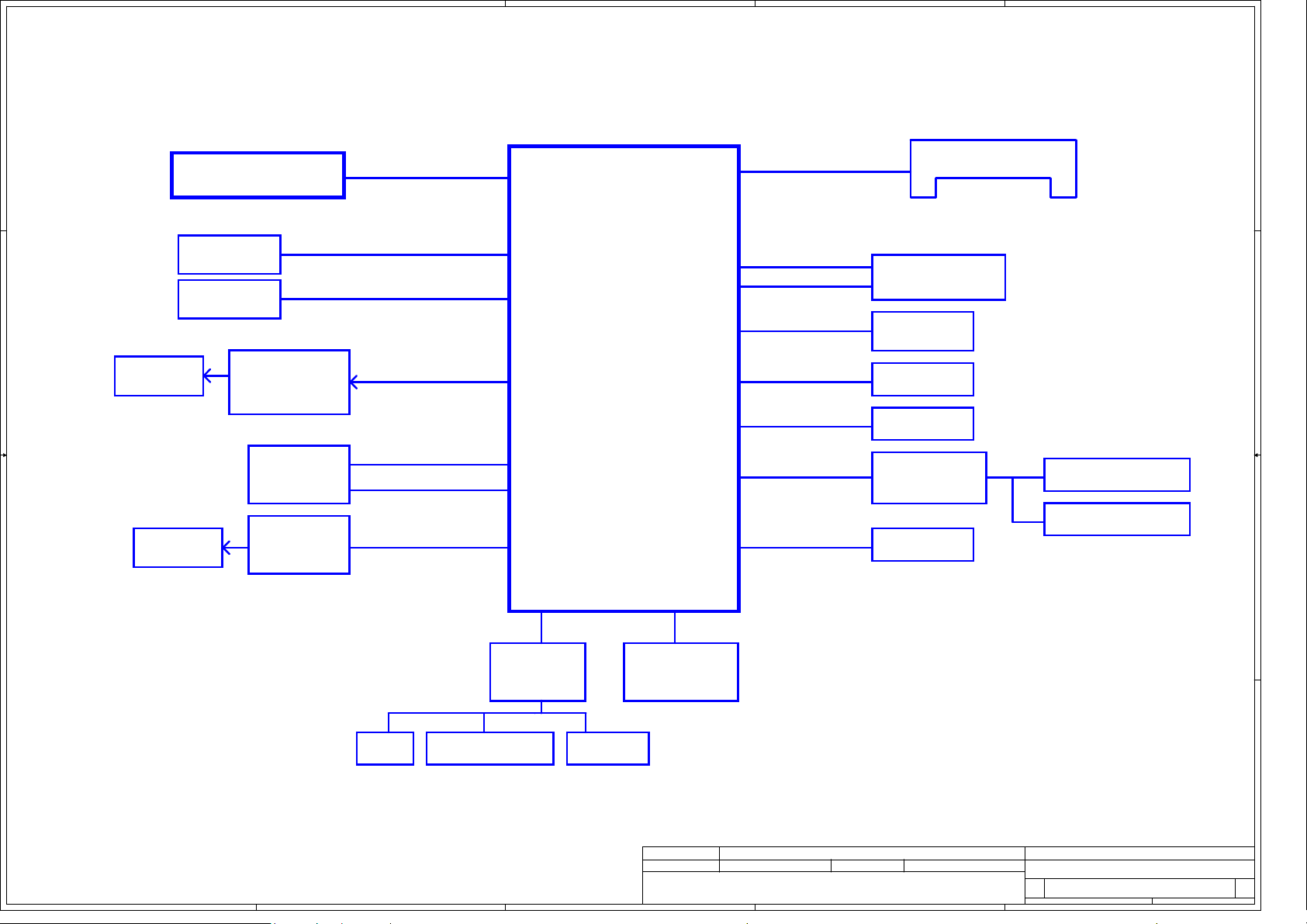

AMD R17M-M1-70

A

PCIe x4

D Stoney Ridge FT4

M

2133 MHz 1.2V

DDR4 SO-DIMM X1

VRAM(GDDR5)*2 2GB

eDP Conn.

HDMI Conn.

2 2

RJ45 Conn.

LAN

Realtek

RTL8106E-CG

10/100

eDP X1 (2 Lanes)

DP X1 (4 Lanes)

PCIe x1

AMD

Stoney Ridge FT4

Processor

BGA 769

USB3.0 x2

USB2.0 x2

USB2.0 x1

SATA X1

SATA X1

Left USB3.0 x2

Int. Camera

HDD Conn.

ODD Conn.

PCIe X1 for WLAN

WLAN / BT

(1 Lanes)

USB2.0 x1 for BT

HDA

Audio Codec

Realtek

ALC3240-VA3-CG

Int. Speaker

Stereo / Mono

Combo Jack

SD Conn.

3 3

Realtek

RTS5146-GR

Card Reader

USB2.0 x1

I2C

Touch Pad

Headphone / MIC

SPILPC

EC

ENE

KB9022QD

Th

LED

4 4

A

B

ermal Diode

Int. KBD

SPI ROM

8MB

XMC

XM25QU64ARIG

Se

Se

Se

curity Classification

curity Classification

curity Classification

Issued Date

Issued Date

Issued Date

TH

TH

TH

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

20

20

20

18/03/12 2019/03/12

18/03/12 2019/03/12

18/03/12 2019/03/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

De

De

De

ciphered Date

ciphered Date

ciphered Date

D

Com

Com

Com

pal Electronics, Inc.

pal Electronics, Inc.

Ti

Ti

Title

tle

tle

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Cu

Cu

Cu

stom

stom

stom

Date : Sheet

Date : Sheet

Date : Sheet

pal Electronics, Inc.

Bl

Bl

Bl

ock Diagram

ock Diagram

ock Diagram

LA

LA

LA

-G241P

-G241P

-G241P

E

2 43Monday, March 12, 2018

2 43Monday, March 12, 2018

2 43Monday, March 12, 2018

of

of

of

1.

1.

1.

0

0

0

A

B

C

D

E

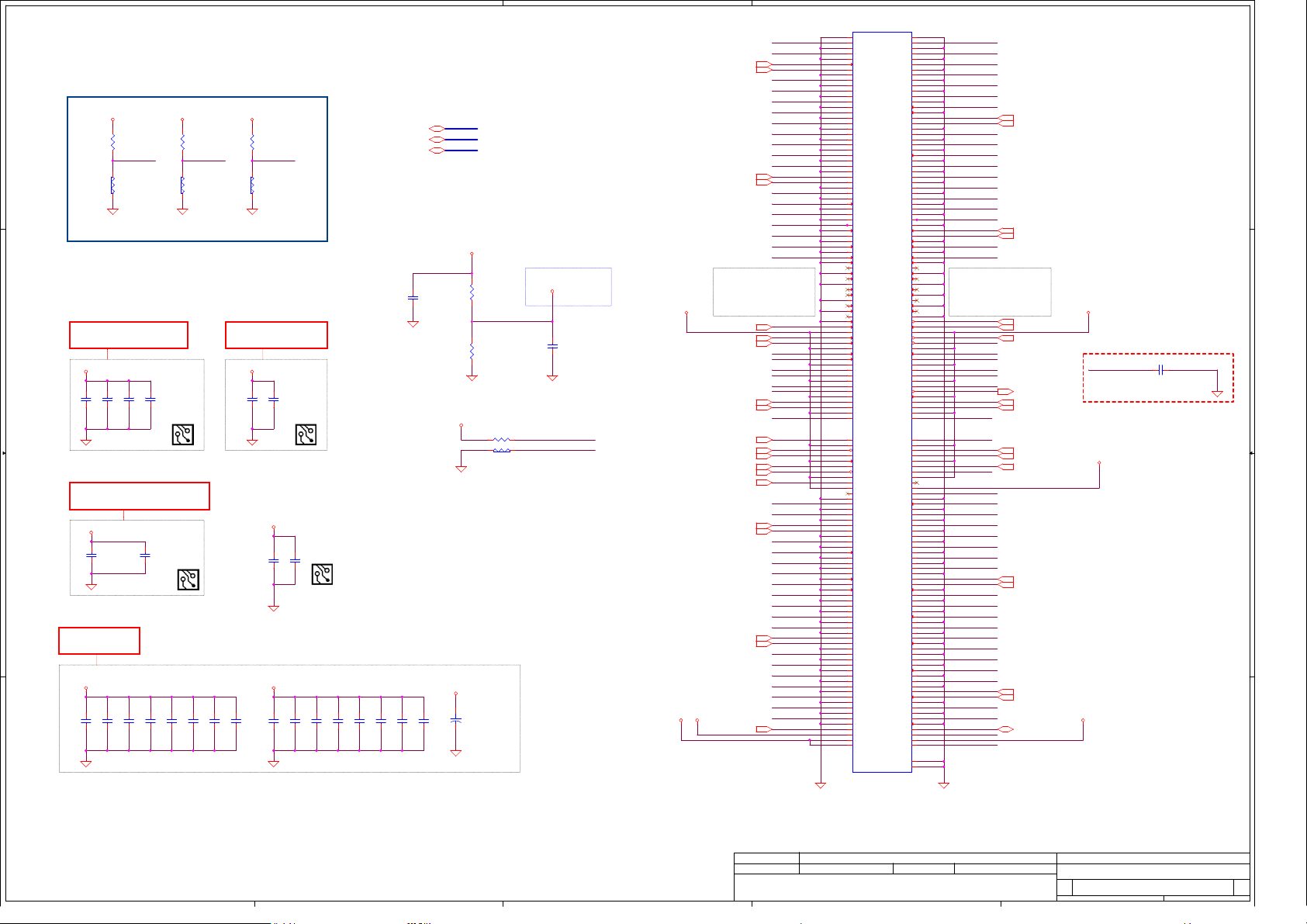

V

oltage Rails

D

P

ower Plane

V

IN

B

+

+

APU_CORE

+

AP

1 1

2 2

U_CORE_NB ON

+3VALW

+3VS

+1.8VALW

+1.8VS

+0.95VALW

+0.9

5VS

+1.2V

+2.5

V

+0.6V

+5VALW

+5VS

+RTCVBATT

+0.775 VALW

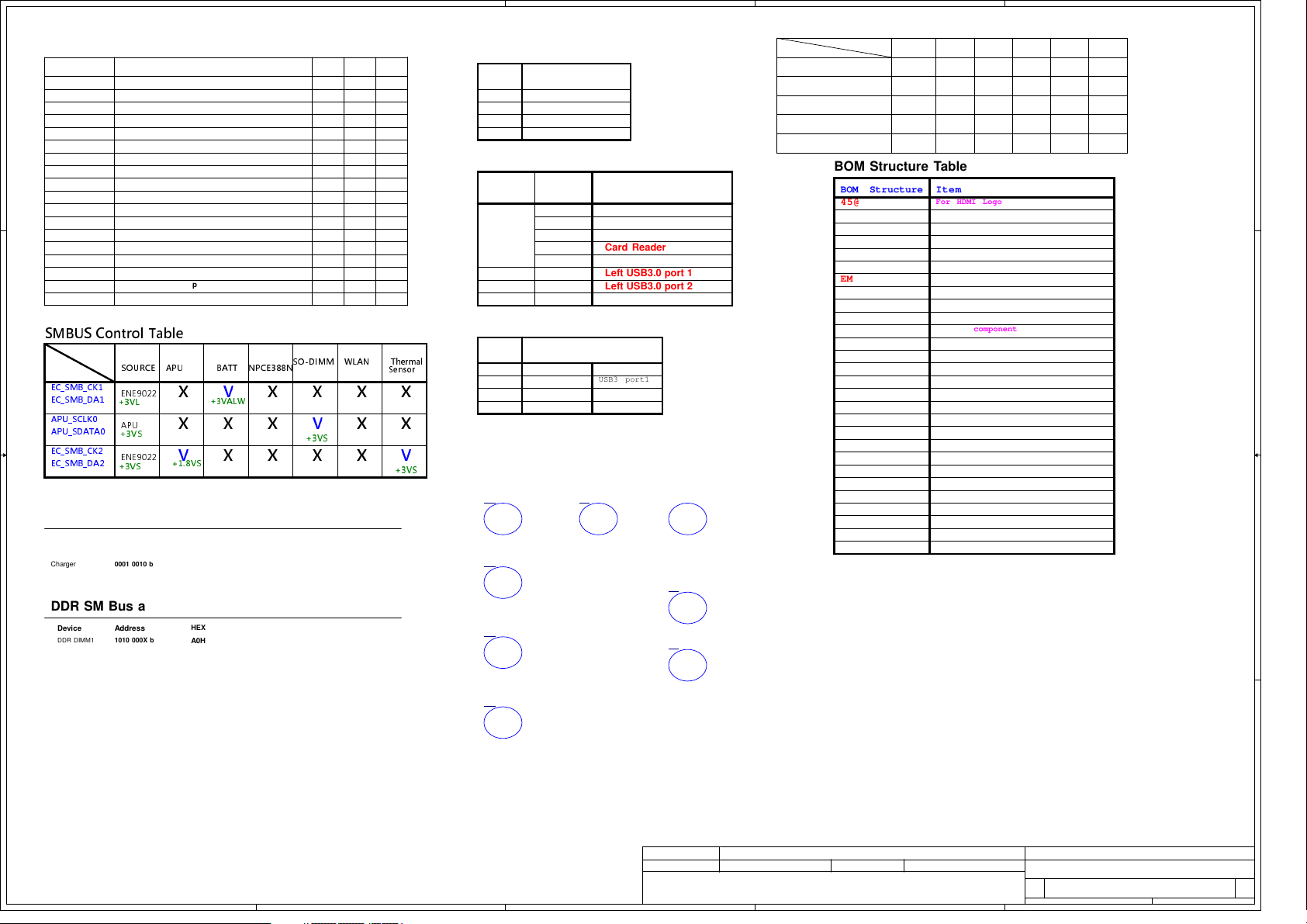

SMBUS Control Table

EC_SMB_CK1

EC_SMB_DA1

APU_SCLK0

APU_SDATA0

EC_SMB_CK2

EC_SMB_DA2

escription

Ada

ter power supply (19V)

p

AC or battery power rail for power circuit.

Core voltage for APU

Vol

age for On-die VGA of APU

t

3.3V always on power rail

.3V switched power rail

3

1.

8V always on power rail

1.8V switched power rail

0.95V always on power rail

0.95V switched power rail

1.2V power rail for APU and DDR

2.5V switched power rail for DDR

0.6V switched power r ail for DDR terminator

5V always on power r ail

5V switched power rail

RTC power

0.775V always on power rail

APU

SOURCE

ENE9022

+3VL

APU

+3VS

ENE9022

+3VS

BATT NPCE388N

X X

V

+3

VALW

X

X

X

V

+1.8VS

S

0 S3 S5

ONO

O

N

O

N

ON ON

ON

ON

ON

ON

ON

ON

ON

ON ONON

IMM

WLAN

SO-D

X

X

V

+3VS

X X

X

ON

N

ONONON

OFF

OFF

OFF

O

O

O

NON

O

OFF

ON

OFF OFF

ON ON

OFF O

OFF

ON

OFF

ONON

OFFOF

F

ON O

OFF O

ONONON

Thermal

Sensor

X

X

FF

N

FF

FF

N

FF

X

X

V

+3VS

A

PU PCIE PORT LIST

DevicePor t

0

L

AN

1

2

LAN

W

3

USB Port Table

USB 2.0USB 3.0

0

1

2

3

USB2 port5

425@

4

5

6

7

USB

X4E

ZZZ

1

2

USB

OC MAPPING

0

1

2

3

APU part

UC1

A9_9

3 External

USB Port

WLAN/BT Combo

Camera

Card Reader

Left US

Left USB3.0 port 2

PortOC#

USB3 port1

level BOM

X4E_15@

B3.0 port 1

HDMI

ZZZ

logo

45@

STA

E

T

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF) LOW

SIGNA L

SLP_S3 # S LP_S5# +VALW +V +VS Clock

HIGH HIGH

HIGHHIGH

HIGH

HIGH

LOW

HIGH

LOW

BOM Structure Table

BOM Structure I tem

45@

UMA @

DIS @

HDT @

X4E_ 15@

X76 @

EMI @

@EM I@

ESD @

@ES D@

RF@

@RF @

CON N@

2HD D@

8111 GLDO @

@

S2G @

H2G @

M2G @

For HDMI Logo

For UMA SKU

For DIS SKU

AMD Dubeg Header

X4E level BOM For 15"

X76 level BOM

EMI pop component

EMI Un pop component

ESD pop component

ESD Un pop component

RF pop component

RF Un pop component

ME part

2nd HDD component

LAN chip 8111LDO pop component

Unpop

Samsung VRAM SKU

Hynix VRAM SKU

Micron VRAM SKU

ON

ON

ON

ON

ON

ONONON ON

ON

ON

OFF

OFF

OFF

OFF

OFF

LOW

OFF

OFF

OFF

EC SM Bus1 address EC SM Bus2 address

X4EA

A9_9

Devi

ce

Smart Battery

Char

3 3

ger

Address

0001

011x b

0001

0010 b

DDR SM Bus address

Device

DDR

DIMM1

Address

1010

000X b

HEX

Device

APU

16H

12H

GPU SM Bus address

HEX

Device

GPU

A0H

Address

100

1 100X b

Address

0100

0001 b

HEX

98H

HEX

0

X41H

425_R3

SA0000BGS20

UC1

A6_9

A6-9

225_R3

SA0000BGT20

UC1

A4_9

225@

125@

BS38L51

HDMI

Logo

RO00

00003HM

PCB part

ZZZ

ODD@

PCB

DLADE LA-G241P LS-G201P/G202P 02

D

AZ29700101

ZZZ

DmyO

DD@

A4_9

125_R3

SA0000BM510

UC1

E2_9

000@

E2_9

000_R3

SA00009W8 10

4 4

A

B

PCB

DLADE LA-G241P LS-G201P 02

DAZ29700201

Secu

Secu

Secu

rity Classification

rity Classification

rity Classification

Issued Date

Issued Date

Issued Date

THIS

THIS

THIS

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2018

2018

2018

/03/12 2019/03/12

/03/12 2019/03/12

/03/12 2019/03/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Decip

Decip

Decip

hered Date

hered Date

hered Date

D

Compal E

Compal E

Titl

Titl

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Cust

Cust

Cust

Date : Sheet

Date : Sheet

Date : Sheet

Compal E

e

e

om

om

om

lectronics, Inc.

lectronics, Inc.

lectronics, Inc.

NOTE

NOTE

NOTE

S LIST

S LIST

S LIST

LA-G

LA-G

LA-G

241P

241P

241P

E

of

of

of

3 43Monday, March 12, 2018

3 43Monday, March 12, 2018

3 43Monday, March 12, 2018

1.0

1.0

1.0

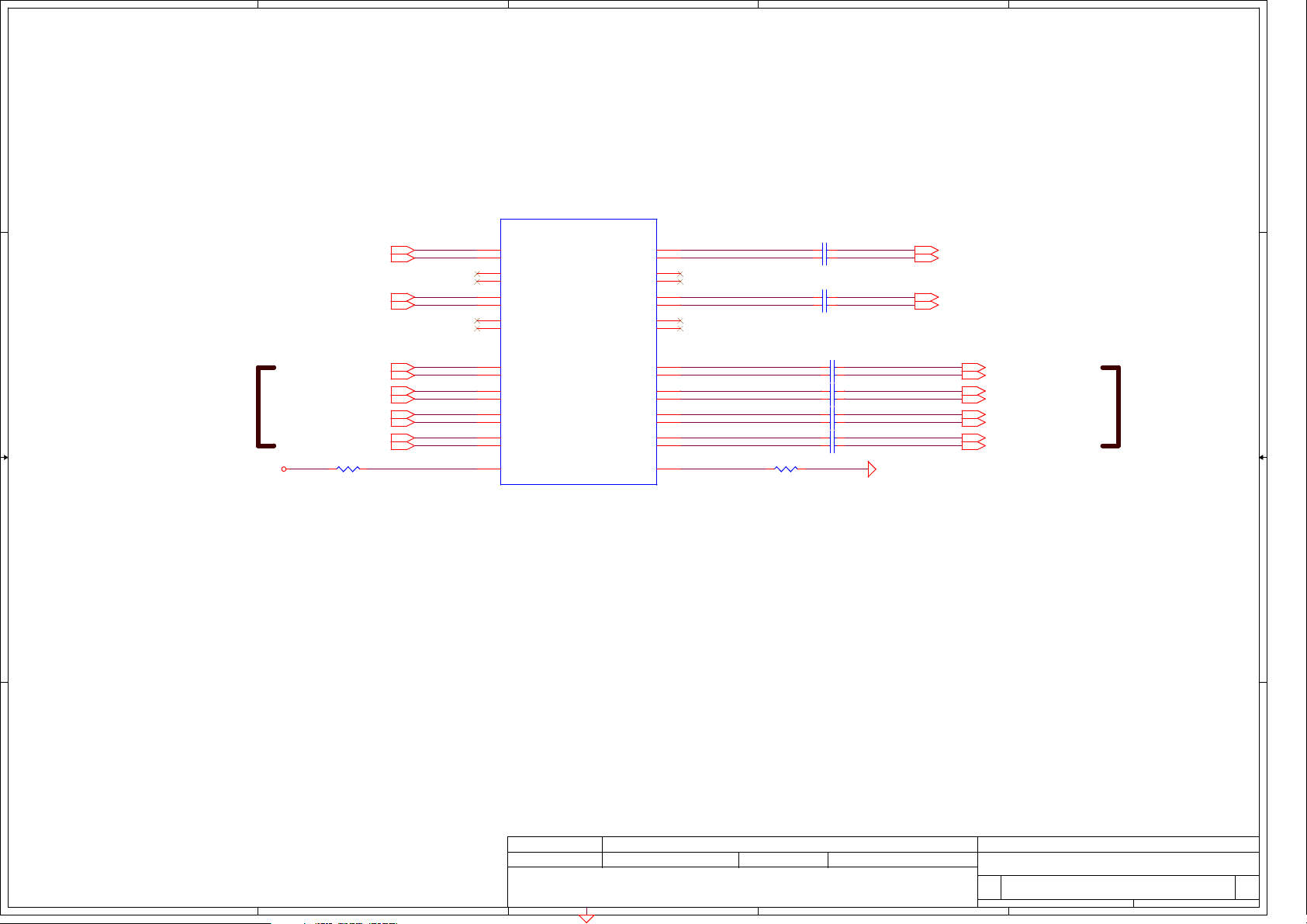

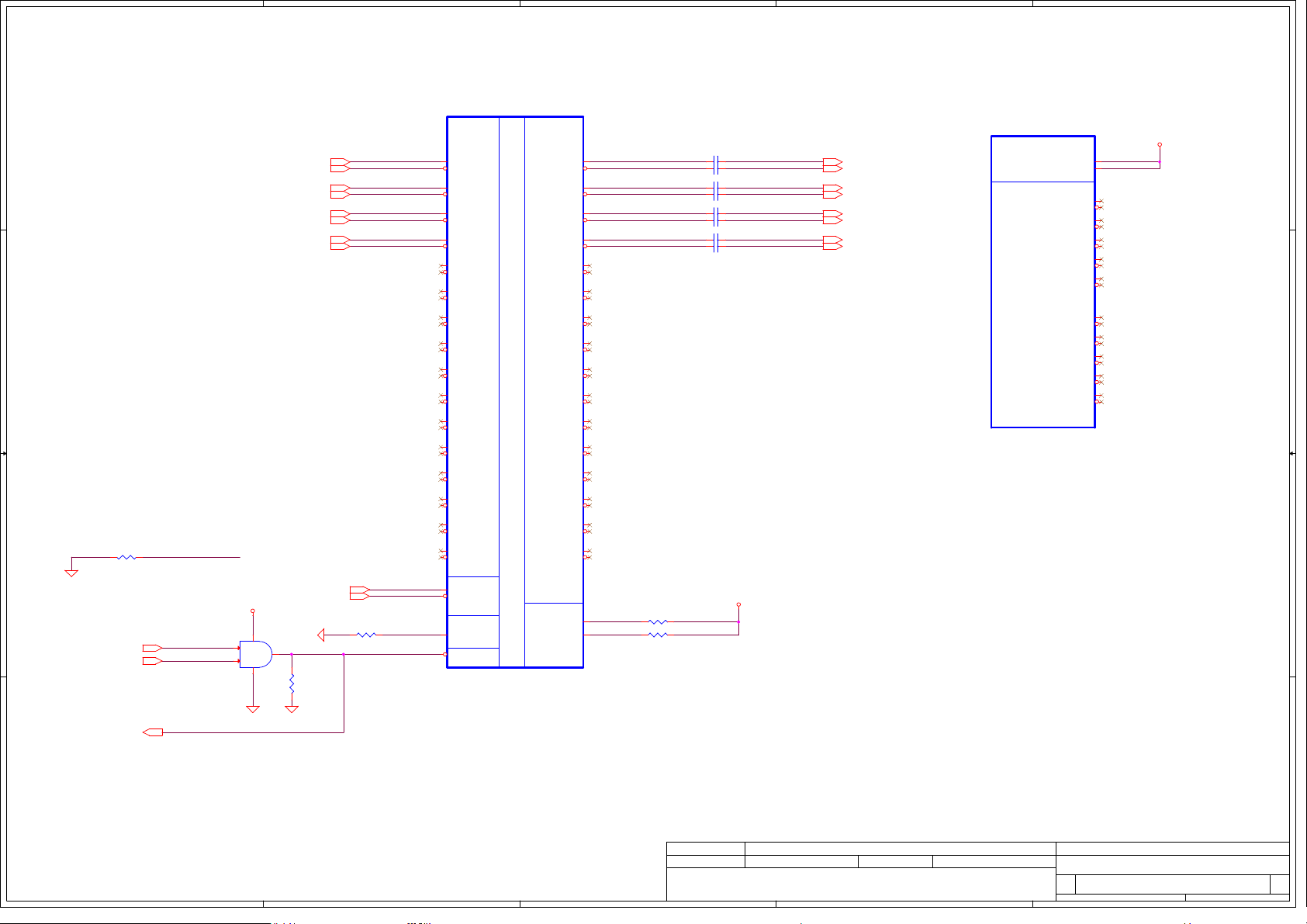

5

D D

4

3

2

1

UC1B

PCIE_

LAN

WLA

N WLAN

C C

GPU GPU

+0.95

VS

B B

ARX_DTX _P0<20>

PCIE_

ARX_DTX _N0<20>

PCIE_

ARX_DTX _P2<22>

PCIE_

ARX_DTX _N2<22>

PCIE_

ARX_GTX _P0<11>

PCIE_

ARX_GTX _N0<11>

PCIE_

ARX_GTX _P1<11>

PCIE_

ARX_GTX _N1<11>

PCIE_

ARX_GTX _P2<11>

PCIE_

ARX_GTX _N2<11>

PCIE_

ARX_GTX _P3<11>

PCIE_

ARX_GTX _N3<11>

1 2

RC1 196

_0402_1 %

P_ZVD

U4

P_GPP

U5

P_GPP

R8

P_GPP

R10

P_GPP

R5

P_GPP

R4

P_GPP

N4

P_GPP

N5

P_GPP

L5

P_GFX

L4

P_GFX

J5

P_GFX

J4

P_GFX

G5

P_GFX

G4

P_GFX

D7

P_GFX

E7

P_GFX

DP

U8

P_ZVD

DP

A6-92

00E_BGA 769

@

_RXP0

_RXN0

_RXP1

_RXN1

_RXP2

_RXN2

_RXP3

_RXN3

_RXP0

_RXN0

_RXP1

_RXN1

_RXP2

_RXN2

_RXP3

_RXN3

PCIE

PCIE_

P_GPP

P_GPP

P_GPP

P_GPP

P_GPP

P_GPP

P_GPP

P_GPP

P_GFX

P_GFX

P_GFX

P_GFX

P_GFX

P_GFX

P_GFX

P_GFX

_TXP0

_TXN0

_TXP1

_TXN1

_TXP2

_TXN2

_TXP3

_TXN3

_TXP0

_TXN0

_TXP1

_TXN1

_TXP2

_TXN2

_TXP3

_TXN3

P_ZVS

PCIE_

PCIE_

PCIE_

PCIE_

PCIE_

PCIE_

PCIE_

PCIE_

PCIE_

PCIE_

PCIE_

P_ZVS

S

ATX_DRX _P0

ATX_DRX _N0

ATX_DRX _P2

ATX_DRX _N2

ATX_GRX _P0

ATX_GRX _N0

ATX_GRX _P1

ATX_GRX _N1

ATX_GRX _P2

ATX_GRX _N2

ATX_GRX _P3

ATX_GRX _N3

1 2

RC2 196

D2

D1

C2

C1

B2

B1

A3

B3

A4

B4

A5

B5

A6

B6

A7

B7

W8

S

1 2

CC1 0.1

CC2 0.1

CC3 0.1

CC4 0.1

CC104 0

CC105 0

CC106 0

CC107 0

CC108 0

CC109 0

CC110 0

CC111 0

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

_0402_1 %

U_0201_ 10V6K

U_0201_ 10V6K

U_0201_ 10V6K

U_0201_ 10V6K

PCIE_

ATX_C_D RX_P0 <20>

PCIE_

ATX_C_D RX_N0 <20>

PCIE_

ATX_C_D RX_P2 <22>

PCIE_

ATX_C_D RX_N2 < 22>

.22U_040 2_6.3V6KDIS@

.22U_040 2_6.3V6KDIS@

.22U_040 2_6.3V6KDIS@

.22U_040 2_6.3V6KDIS@

.22U_040 2_6.3V6KDIS@

.22U_040 2_6.3V6KDIS@

.22U_040 2_6.3V6KDIS@

.22U_040 2_6.3V6KDIS@

PCIE_

PCIE_

PCIE_

PCIE_

PCIE_

PCIE_

PCIE_

PCIE_

LAN

ATX_C_G RX_P0 <11 >

ATX_C_G RX_N0 <11>

ATX_C_G RX_P1 <11 >

ATX_C_G RX_N1 <11>

ATX_C_G RX_P2 <11 >

ATX_C_G RX_N2 <11>

ATX_C_G RX_P3 <11 >

ATX_C_G RX_N3 <11>

A A

Securit

Securit

Securit

y Classification

y Classification

y Classification

2018/

2018/

2018/

03/12 2019/03/1 2

03/12 2019/03/1 2

Issued Date

Issued Date

Issued Date

THIS

THIS

THIS

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

03/12 2019/03/1 2

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compa

Compa

Compa

l Electronics, Inc.

l Electronics, Inc.

Title

Title

Title

S

S

S

ize Document Number Re v

ize Document Number Re v

ize Document Number Re v

Custo

Custo

Custo

m

m

m

Date : Sheet

Date : Sheet

2

Date : Sheet

l Electronics, Inc.

GPP &

GPP &

GPP &

PCIE

PCIE

PCIE

LA-G2

LA-G2

LA-G2

41P

41P

41P

4 43Monday, March 12 , 2018

4 43Monday, March 12 , 2018

4 43Monday, March 12 , 2018

1

1.0

1.0

1.0

o f

o f

o f

5

4

3

2

1

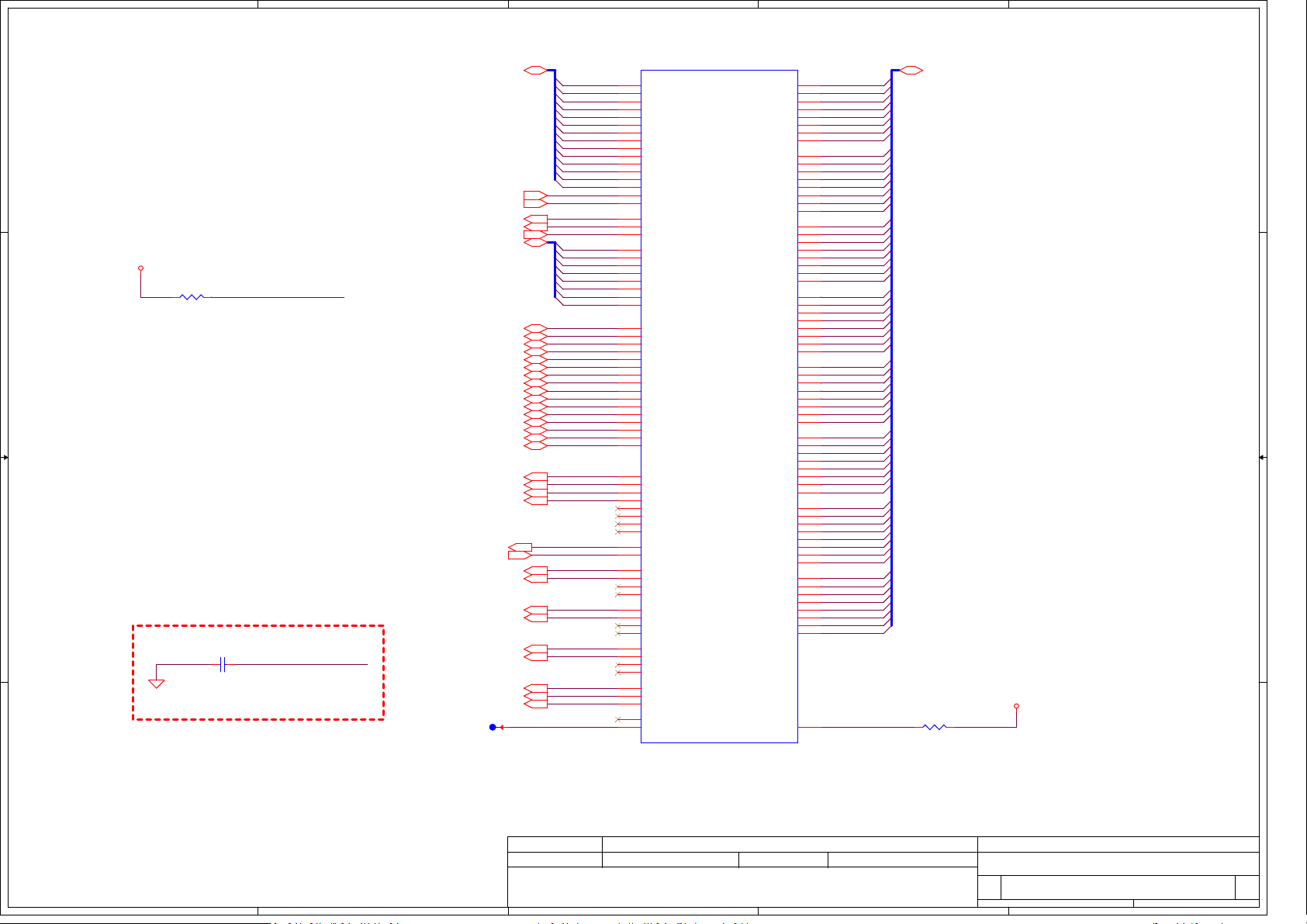

DDR

A_SMA[13 ..0]<10>

_

D D

DDR_

A_SBG1<10>

DDR_

A_SACT#<10>

DDR_

A_SBS0#<10>

DDR_

A_SBS1#<10>

DDR_

A_SBG0<10>

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

A_RST#<10>

A_EVENT #<10>

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

A_SDM[7..0 ]<10>

A_SDQS0<10>

A_SDQS0 #<10>

A_SDQS1<10>

A_SDQS1 #<10>

A_SDQS2<10>

A_SDQS2 #<10>

A_SDQS3<10>

A_SDQS3 #<10>

A_SDQS4<10>

A_SDQS4 #<10>

A_SDQS5<10>

A_SDQS5 #<10>

A_SDQS6<10>

A_SDQS6 #<10>

A_SDQS7<10>

A_SDQS7 #<10>

A_CLK0<10>

A_CLK0#<10>

A_CLK1<10>

A_CLK1#<10>

A_CKE0<10>

A_CKE1<10>

A_ODT0<10>

A_ODT1<10>

A_SCS0#<10>

A_SCS1#<10>

A_SRAS#<1 0>

A_SCAS#<1 0>

A_SW E#<10>

APU_

T1

+1.2

C C

B B

EVENT# pull high

V

1 2

RC4 1K

_0402_5 %

DDR_

A_EVENT #

ESD

ESD@

1 2

CC11

2 100P_0402 _50V8J

DDR_

A_RST#

DDR_

DDR_

MA_VREF DQ

DDR

A_SMA0

_

DDR

A_SMA1

_

_

A_SMA2

DDR

DDR

A_SMA3

_

_

A_SMA4

DDR

DDR

A_SMA5

_

_

A_SMA6

DDR

DDR

A_SMA7

_

DDR

A_SMA8

_

DDR

A_SMA9

_

DDR_A_S MA10

DDR_A_S MA11

DDR_A_S MA12

DDR_A_S MA13

DDR_

A_SDM0

DDR_

A_SDM1

DDR_

A_SDM2

DDR_

A_SDM3

DDR_

A_SDM4

DDR_

A_SDM5

DDR_

A_SDM6

DDR_

A_SDM7

A_RST#

A_EVENT #

AG3

W35

W38

W34

U38

U37

U34

R35

R38

N38

AG34

R34

N37

AN35

AJ38

AG35

N34

B35

D40

K40

AE41

AL40

AU40

BA37

B36

A36

E40

D41

K41

U41

U40

AF41

AE40

AM40

AM41

AV40

AV41

BA36

AY36

AC35

AC34

AA34

AA32

AE38

AE37

AA37

AA38

G38

AA41

AN37

AU38

AL34

AN34

AL35

AR37

AJ34

AR38

AJ37

AN38

AL38

AA40

L38

L35

T41

L40

J38

J34

L34

J37

Y41

UC1A

8

A6-9

@

M_A

D0

D

M_A

D1

D

M_A

D2

D

M_A

D3

D

M_A

D4

D

M_A

D5

D

D

D6

M_A

M_A

D7

D

D

D8

M_A

M_ADD9

M_ADD10

M_ADD11

M_ADD12

M_ADD13

M_AD

D14/M_BG1

M_AD

D15/M_ACT_L

M_BA

NK0

M_BA

NK1

M_BA

NK2/M_BG0

M_DM

0

M_DM

1

M_DM

2

M_DM

3

M_DM

4

M_DM

5

M_DM

6

M_DM

7

M_DQ

S_H0

M_DQ

S_L0

M_DQ

S_H1

M_DQ

S_L1

M_DQ

S_H2

M_DQ

S_L2

M_DQ

S_H3

M_DQ

S_L3

M_DQ

S_H4

M_DQ

S_L4

M_DQ

S_H5

M_DQ

S_L5

M_DQ

S_H6

M_DQ

S_L6

M_DQ

S_H7

M_DQ

S_L7

M_CL

K_H0

M_CL

K_L0

M_CL

K_H1

M_CL

K_L1

M_CL

K_H2

M_CL

K_L2

M_CL

K_H3

M_CL

K_L3

M_RE

SET_L

M_EV

ENT_L

M0_C

KE0

M0_C

KE1

M1_C

KE0

M1_C

KE1

M0_O

DT0

M0_O

DT1

M1_O

DT0

M1_O

DT1

M0_C

S_L0

M0_C

S_L1

M1_C

S_L0

M1_C

S_L1

M_RA

S_L/M_RAS_L_ADD16

M_CA

S_L/M_CAS_L_ADD15

M_WE

_L/M_WE_L_ADD14

M_VR

EF

M_VR

EFDQ

200E_BG A769

MEM

O

RY

M_ZV

M_D

A

M_D

A

M_D

A

M_D

A

M_D

A

M_D

A

A

M_D

M_D

A

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DA

TA13

M_DA

TA14

M_DA

TA15

M_DA

TA16

M_DA

TA17

M_DA

TA18

M_DA

TA19

M_DA

TA20

M_DA

TA21

M_DA

TA22

M_DA

TA23

M_DA

TA24

M_DA

TA25

M_DA

TA26

M_DA

TA27

M_DA

TA28

M_DA

TA29

M_DA

TA30

M_DA

TA31

M_DA

TA32

M_DA

TA33

M_DA

TA34

M_DA

TA35

M_DA

TA36

M_DA

TA37

M_DA

TA38

M_DA

TA39

M_DA

TA40

M_DA

TA41

M_DA

TA42

M_DA

TA43

M_DA

TA44

M_DA

TA45

M_DA

TA46

M_DA

TA47

M_DA

TA48

M_DA

TA49

M_DA

TA50

M_DA

TA51

M_DA

TA52

M_DA

TA53

M_DA

TA54

M_DA

TA55

M_DA

TA56

M_DA

TA57

M_DA

TA58

M_DA

TA59

M_DA

TA60

M_DA

TA61

M_DA

TA62

M_DA

TA63

DDIO_MEM_S3

TA0

TA1

TA2

TA3

TA4

TA5

TA6

TA7

A34

B34

A38

B38

A33

B33

A37

B37

B41

C40

F41

G40

A40

B40

E41

F40

J40

J41

N40

N41

H40

H41

M40

M41

R40

T40

W40

Y40

P40

P41

V40

V41

AD41

AD40

AH41

AH40

AB40

AC40

AF40

AG40

AK41

AK40

AP41

AP40

AJ41

AJ40

AN41

AN40

AT40

AU41

AY40

BA40

AR40

AT41

AW40

AY41

BA38

AY37

BA34

BA33

AY39

AY38

AY35

AY34

AB41

DDR

A_SDQ0

_

DDR

A_SDQ1

_

_

A_SDQ2

DDR

DDR

A_SDQ3

_

_

A_SDQ4

DDR

DDR

A_SDQ5

_

_

A_SDQ6

DDR

DDR

A_SDQ7

_

DDR

A_SDQ8

_

DDR_A_S DQ9

DDR_A_S DQ10

DDR_A_S DQ11

DDR_A_S DQ12

DDR_A_S DQ13

DDR_

A_SDQ14

DDR_

A_SDQ15

DDR_

A_SDQ16

DDR_

A_SDQ17

DDR_

A_SDQ18

DDR_

A_SDQ19

DDR_

A_SDQ20

DDR_

A_SDQ21

DDR_

A_SDQ22

DDR_

A_SDQ23

DDR_

A_SDQ24

DDR_

A_SDQ25

DDR_

A_SDQ26

DDR_

A_SDQ27

DDR_

A_SDQ28

DDR_

A_SDQ29

DDR_

A_SDQ30

DDR_

A_SDQ31

DDR_

A_SDQ32

DDR_

A_SDQ33

DDR_

A_SDQ34

DDR_

A_SDQ35

DDR_

A_SDQ36

DDR_

A_SDQ37

DDR_

A_SDQ38

DDR_

A_SDQ39

DDR_

A_SDQ40

DDR_

A_SDQ41

DDR_

A_SDQ42

DDR_

A_SDQ43

DDR_

A_SDQ44

DDR_

A_SDQ45

DDR_

A_SDQ46

DDR_

A_SDQ47

DDR_

A_SDQ48

DDR_

A_SDQ49

DDR_

A_SDQ50

DDR_

A_SDQ51

DDR_

A_SDQ52

DDR_

A_SDQ53

DDR_

A_SDQ54

DDR_

A_SDQ55

DDR_

A_SDQ56

DDR_

A_SDQ57

DDR_

A_SDQ58

DDR_

A_SDQ59

DDR_

A_SDQ60

DDR_

A_SDQ61

DDR_

A_SDQ62

DDR_

A_SDQ63

MEM_

MA_ZVDD IO

Plac

e them close to APU within 1"

DDR

A_SDQ[63 ..0] < 10>

_

1 2

RC3 39

.2_0402_ 1%

+1.2

V

A A

Secu

Secu

Secu

rity Classification

rity Classification

rity Classification

2018

2018

2018

/03/12 2019/03/ 12

/03/12 2019/03/ 12

Issued Date

Issued Date

Issued Date

THIS

THIS

THIS

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

/03/12 2019/03/ 12

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Comp

Comp

Comp

al Electronics, Inc.

al Electronics, Inc.

Titl

Titl

Titl

e

e

e

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Cust

Cust

Cust

om

om

om

Date : Sheet

Date : Sheet

2

Date : Sheet

al Electronics, Inc.

Memo

Memo

Memo

ry

ry

ry

LA-G

LA-G

LA-G

241P

241P

241P

5 43Monday, March 12 , 2018

5 43Monday, March 12 , 2018

5 43Monday, March 12 , 2018

1

1.0

1.0

1.0

o f

o f

o f

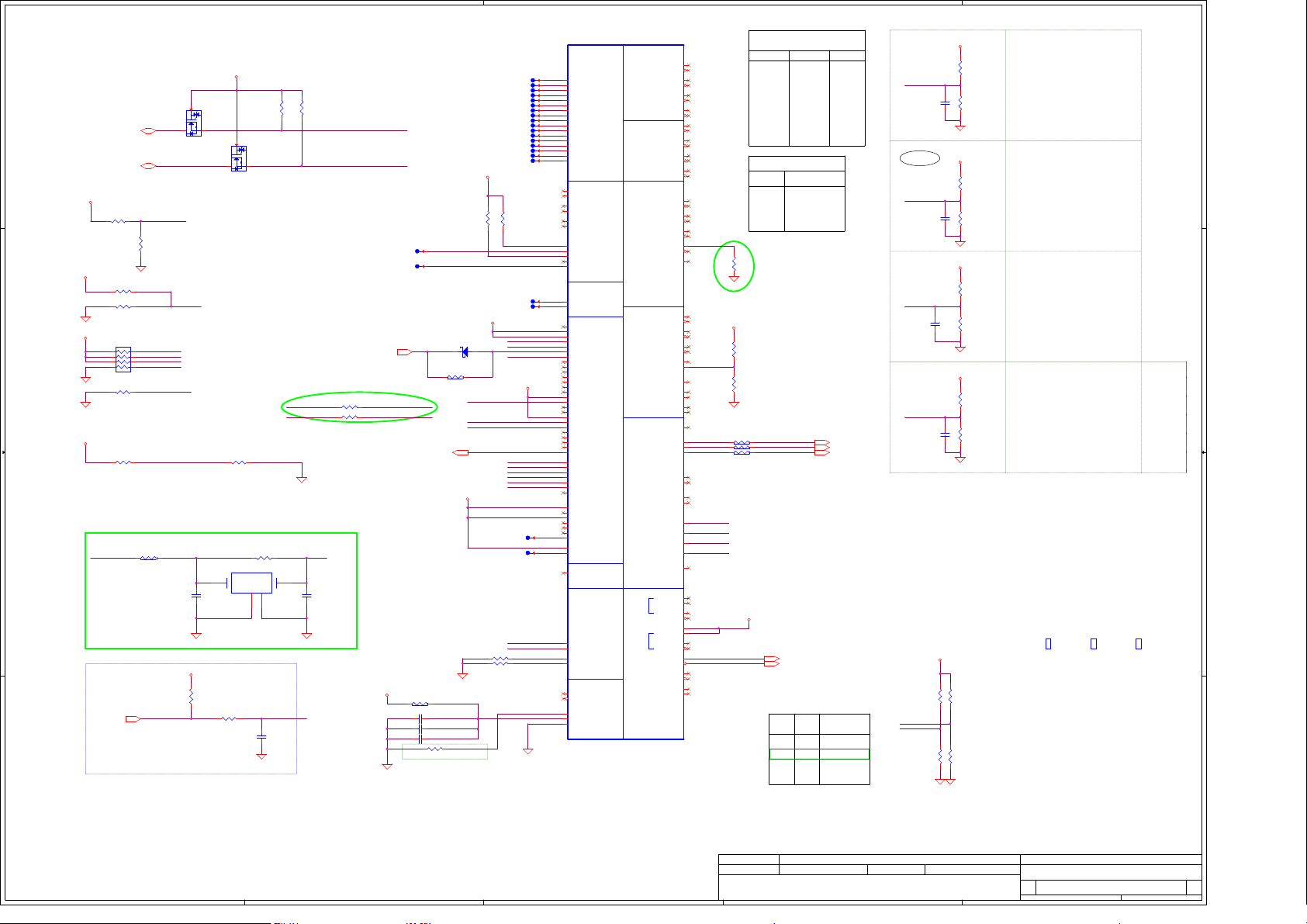

5

D D

+1.8V

S

RPC14

APU_SVT

18

APU_SVC

27

APU_SVD

36

45

1

K_0804_8P4 R_5%

@

+1.8V

S

RPC1

1K

+1.8V

S

1 2

RC13 30

1 2

RC14 30

C C

B B

ESD

1 2

CC113 10 0P_

1 2

CC114 10 0P_

1 2

CC115 10 0P_

PU

on EC side

EC_SM

B_CK2<12,25>

EC_SM

B_DA2<12,25>

18

27

36

45

_0804_8P4R _5%

0_0402_5%

0_0402_5%

0402_50V8JESD@

0402_50V8JESD@

0402_50V8JESD@

H_PRO

APU_S

APU_A

APU_S

CHOT#

ID

LERT#

IC

APU_P

APU_R

+1.8V

6 1

D

QC2B

PJ

2

G

WRGD

ST#

H_PRO

CHOT#

APU_P

WRGD

APU_R

ST#

S

5

3 4

SGD

QC2A

PJ

T138KA_SOT36 3-6

S

T138KA_SOT36 3-6

APU_S

APU_S

H_PRO

APU_P

APU_S

APU_S

APU_S

IC

ID

4

UC1C

AY/SVI2/ JTAG/ TEST

DISPL

IC

ID

LERT#

CHOT#

WRGD

ST#

DI

DO

AE34

AM15

AM17

AM19

AP13

AP15

AP17

AR13

AR15

AR17

AU13

AU15

AU17

AV11

AV13

AV15

AV17

H27

E27

D27

B30

B29

A30

A31

G

D29

B25

A27

B27

B26

A29

A26

A25

D11

D13

E31

H11

H13

L11

AN8

AU4

AV7

AV9

AY3

AY7

SVT

SVC

SVD

SIC

SID

ALERT

PROCH

25

PWROK

RESET

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

VDD_18 Domain

D9

RSVD_

RSVD_

RSVD_

E4

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

A6-92

@

_L

OT_L

_L

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

00E_BGA769

VT<38>

VC<38>

VD<38>

CHOT#<25>

WRGD<38>

APU_S

APU_S

APU_A

H_PRO

APU_P

APU_R

APU_T

APU_T

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

VDD_1

8 Domain

but 3.3V tolerant

VDD_18 Domain

DP_ST

EREOSYNC/TEST36

VDDCR

VDDCR

VDDIO

VDD_18 Domain

DP_VA

DP_AU

_CPU_SENSE

_MEM_S3_SENSE

VDDP_

VSS_S

VSS_S

DP_BL

DP_DI

GON

RY_BL

X_ZVSS

DP_ZV

DP0_A

UXP

DP0_A

UXN

DP0_H

DP1_A

UXP

DP1_A

UXN

DP1_H

DP2_AUXP

DP2_AUXN

DP2_HPD

DP0_TXP0

DP0_TXN0

DP0_T

DP0_T

DP0_T

DP0_T

DP0_T

DP0_T

DP1_T

DP1_T

DP1_T

DP1_T

DP1_T

DP1_T

DP1_T

DP1_T

DP2_T

DP2_T

DP2_T

DP2_T

DP2_T

DP2_T

DP2_T

DP2_T

TEST4

TEST5

TEST6

TEST9

TEST1

TEST1

TEST1

TEST1

TEST1

TEST1

TEST1

TEST2

TEST2

TEST3

TEST4

_NB_SENSE

SENSE

ENSE_A

ENSE_B

3

ENBKL

B23

ON

B24

A24

D21

B18

SS

G15

H15

D15

PD

G17

H17

D17

PD

G19

H19

D19

A9

B9

A10

XP1

B10

XN1

A11

XP2

B11

XN2

A12

XP3

B12

XN3

A14

XP0

B14

XN0

A15

XP1

B15

XN1

A16

XP2

B16

XN2

A17

XP3

B17

XN3

A19

XP0

B19

XN0

A20

XP1

B20

XN1

A21

XP2

B21

XN2

A22

XP3

B22

XN3

H

G

H

R

N32

0

G21

4

H21

5

D23

6

E23

7

A28

8

B28

9

N8

8_H

N10

8_L

H31

1

D25

B31

1

D31

E33

D35

AM21

D33

AM23

_R

ENVDD

_R

INVT_

PWM_R

DP_AU

X_ZVSS

DP_ZVS

S

APU_T

29

APU_T

29

APU_T

25

APU_T

32

APU_T

APU_T

APU_T

APU_T

APU_T

APU_T

APU_T

APU_T

APU_T

APU_T

APU_T

APU_T

EST4

EST5

EST6

EST9

EST10

EST14

EST15

EST16

EST17

EST18

EST19

EST28_H

EST28_L

EST31

EST36

EST41

1 2

RC1

6 1

1 2

RC1

7 2

EDP_A

EDP_A

EDP_H

APU_D

APU_D

APU_D

EDP_TXP0 <17>

EDP_TXN0 <17>

EDP_T

EDP_T

APU_D

APU_D

APU_D

APU_D

APU_D

APU_D

APU_D

APU_D

T2

T3

T4

T5

T6

T7

T8

T9

T10

T11

T12

T13

T14

T16

T18

T60

VSS_S

5

0_0402_1%

K

_0402_1%

UXP <17>

UXN <17>

PD <17>

P1_AUXP <18>

P1_AUXN <18 >

P1_HPD <18>

XP1 <17>

XN1 < 17>

P1_P0 <18>

P1_N0 <18>

P1_P1 <18>

P1_N1 <18>

P1_P2 <18>

P1_N2 <18>

P1_P3 <18>

<18>

P1_N3

APU_T

APU_T

APU_T

ENSE1

eDP

H

DMI

eDP

HDMI

EST17

EST16

EST14

T15

T19

T61

APU_V

DD_SEN <38>

APU_V

DDNB_SEN <38>

APU_V

DDP_RUN_FB _H <37>

APU_V

RPC2

18

27

36

45

1K

_0804_8P4R _5%

@

DD_RUN_FB_ L <38 >

2

+1.8V

S

QC1

2

Gat

e

1

ENBKL

_R

Drain

3

Sourc

S139WT1 G_SC70-3

LBS

e

+LCDVDD_CONN PWR switch enable pin VIH=1.2V

ENVDD

INVT_

_R

PWM_R

RC20 0_

1

2

ENBKL

_R

INVT_

PWM_R

1 2

+1.8V

S

5

UC21

P

NC

Y

A

G

74

AUP1G07GW_S C70-5

3

SA00005U600

RC22 100K_

RC24 4.7K_

APU_T

APU_T

APU_T

0402_5%@

+3VS

4

1 2

1 2

EST18

EST19

RST#

+3V

1 2

RC21

4.

1 2

RPC3

1 8

2 7

3 6

4 5

1K

S

8

RC1

2

2K_0402_5%

.

7K_0402_5%

0402_5%

0402_5%

+1.8V

_0804_8P4R _5%

S

ENBKL

APU_E

NVDD < 17>

APU_I

NVT_PWM <17>

1

<17,25>

HDT+

+3VS

5

UC22

1

P

NC

4

Y

APU_R

ST#_EC<25>

A A

5

2

A

G

74

AUP1G07GW_S C70-5

3

SA00007WE0 0

@

RC30 0_

12

0402_5%@

APU_R

ST#

Stoney Ridge FP4_FT4 Interlock July_2017 ver 2.1:

To enable HDMI, it must be pull ed up to 1.8V_S0 rail

by 1K ohm resistor

APU_T

EST36

4

1 2

RC25 1K

1 2

RC26 1K

_0402_5%

_0402_5%@

+1.8V

S

3

Debug conn - HDT@

+1.8V

S

JHDT1

APU_T

RST#

1 2

RC27 3

CC7 0.

1 8

2 7

3 6

4 5

Secur

Secur

Secur

ity Classification

ity Classification

ity Classification

Issued Date

Issued Date

Issued Date

THIS

THIS

THIS

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

HDT@

3_0402_5%

HDT@

1 2

01U_0402_ 16V7K

RPC5

10

K_0804_8P4 R_5%

HDT@

APU_T

RST#_R

APU_T

RST#_R

HDT_P

11

HDT_P

13

HDT_P

HDT_P

11

HDT_P

13

HDT_P

15

2018/

2018/

2018/

03/12 2019/03/12

03/12 2019/03/12

03/12 2019/03/12

15

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciph

Deciph

Deciph

ered Date

ered Date

ered Date

1

3

5

7

9

11

13

15

17

19

2

2

1

2

4

3

4

6

5

6

8

7

8

10

9

10

12

11

12

14

13

14

16

15

16

18

17

18

20

19

20

S

AMTE_ASP-136446 -07-B

CONN@

+1.8V

S

APU_T

APU_T

APU_T

APU_T

APU_P

APU_R

APU_D

APU_D

APU_T

APU_T

CK

MS

DI

DO

WRGD

ST#

BRDY

BREQ#

EST19

EST18

APU_T

APU_T

APU_T

APU_D

Title

Title

Title

S

S

S

ize Document Number Re v

ize Document Number Re v

ize Document Number Re v

Custo

Custo

Custo

m

m

m

Date : Sheet

Date : Sheet

Date : Sheet

RPC4

CK

1 8

MS

2 7

DI

3 6

BREQ#

4 5

1K

HDT@

Compal El

Compal El

Compal El

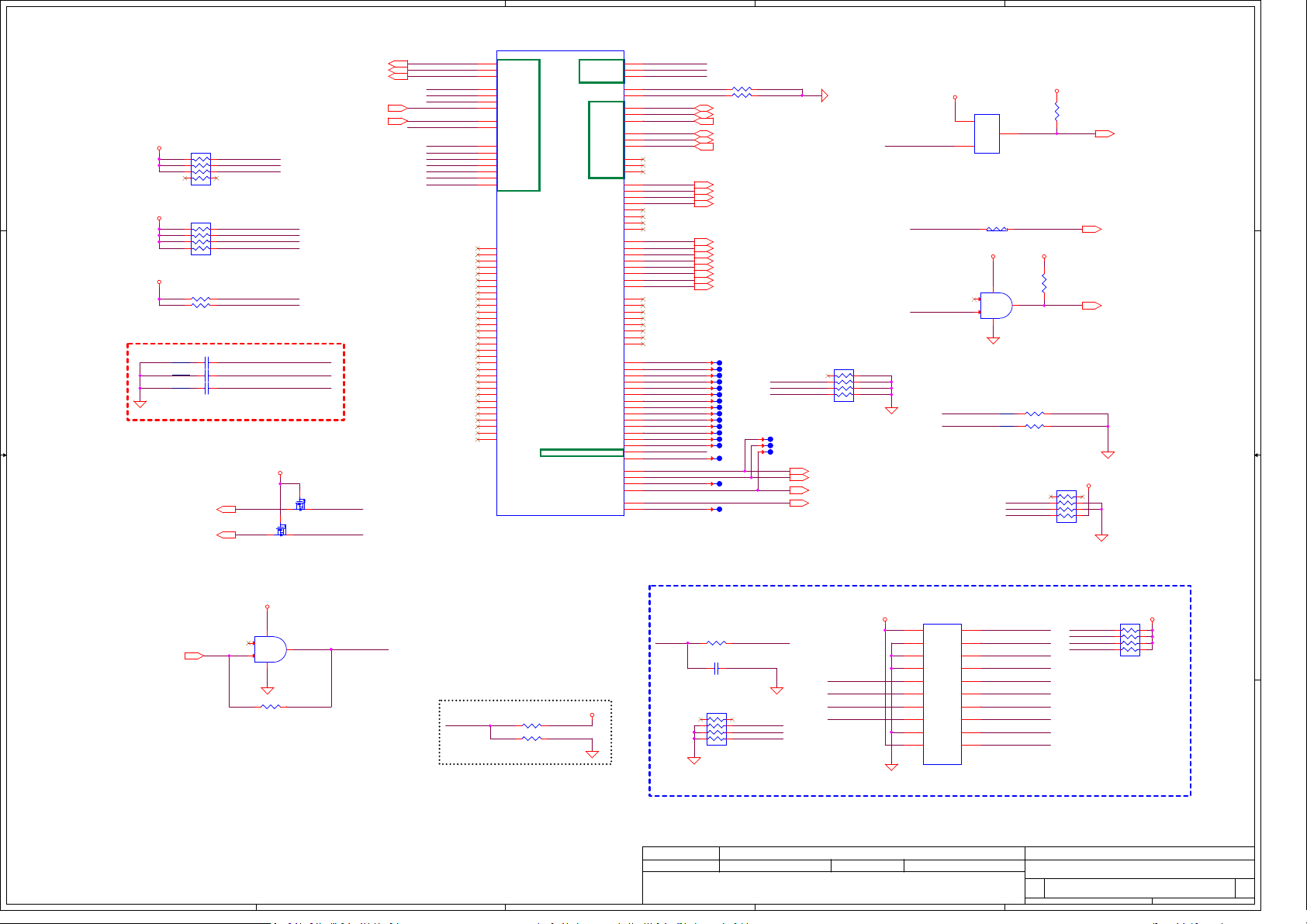

Display

Display

Display

LA-G241P

LA-G241P

LA-G241P

_0804_8P4R _5%

ectronics, Inc.

ectronics, Inc.

ectronics, Inc.

/ SVI2

/ SVI2

/ SVI2

1

1.0

1.0

1.0

of

of

of

6 43Monday, March 12, 2018

6 43Monday, March 12, 2018

6 43Monday, March 12, 2018

5

4

3

2

1

PWRGD_R

SCL

SDA

C215

UC1D

AE4

PCI

_RST_L/EGPIO26

E

AG1

RSM

ST_L

R

AD2

PWR

BTN_L/AGPIO0

_

AE2

PWR

GOOD

_

AF1

SYS

RESET_L/AGPIO1

_

AE7

E

_L/AGPIO2

WAK

AC2

SLP

S3_L

_

AG4

_

S5_L

SLP

AB1

S0A

_GPIO/AGPIO10

3

AA7

S5_

UX_CTRL/EGPIO42

M

AF2

T

0

TES

AE1

TES

1/TMS

T

AC8

TES

2

T

AH2

AC_PRES/USB_OC4_L/IR_RX0/AGPIO23

AA4

IR_TX0/USB_OC5_L/AGPIO13

AG8

IR_TX1/USB_OC6_L/AGPIO14

AL5

IR_RX1/AGPIO15

AE8

IR_LED_L/LLB_L/AGPIO12

AY32

CLK_

REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

AY31

CLK_

REQ1_L/AGPIO115

AV29

CLK_

REQ2_L/AGPIO116

AP31

CLK_

REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

AV35

CLK_

REQG_L/OSCIN/EGPIO132

AB2

USB_

OC0_L/TRST_L/AGPIO16

AG2

USB_

OC1_L/TDI/AGPIO17

AJ1

USB_

OC2_L/TCK/AGPIO18

AH1

USB_

OC3_L/TDO/AGPIO24

AY6

AZ_B

ITCLK/I2S_BCLK_MIC

BA6

AZ_S

DIN0/I2S_DATA_MIC0

AY5

AZ_S

DIN1/I2S_LR_PLAYBACK

BA5

AZ_S

DIN2/I2S_DATA_PLAYBACK

AY4

AZ_R

ST_L/I2S_LR_MIC

BA3

AZ_S

YNC/I2S_BCLK_PLAYBACK

BA4

AZ_S

DOUT/I2S_DATA_MIC1

AY22

I2C0

_SCL/EGPIO145

BA22

I2C0

_SDA/EGPIO146

AU19

I2C1

_SCL/EGPIO147

AV19

I2C1

_SDA/EGPIO148

VDD_18 Domain

and OD ty pe

BA2

X32K

_X1

AY2

X32K

_X2

A6-9

200E_BGA769

@

+1.8

VS

12

12

RC146

RC147

.2K_0402_5%

2

1

1

C215

0

1

100P_0402_50V8J

2

2

@

@

SYS_

PWRGD_EC

.2K_0402_5%

2

5

34

SGD

QC17A

P

JT138KA_SOT363-6

+3VA

1

NC

2

A

1 2

RC64 0_

I

/SD/AZ/GP IO/RTC/MI SC

ACP

VDD_18_S5 Domain

2

G

61

S

D

QC17B

P

JT138KA_SOT363-6

LW

5

UC24

P

4

Y

G

74

AUP1G07GW_SC70-5

3

SA00007WE00

@

SD_

SD_

WR_CTRL/AGPIO102

P

SD_

SD_

SD_

SD_

SD_

SD_

SD_

SCL

/I2C2_SCL/EGPIO113

0

SDA

/I2C2_SDA/EGPIO114

0

1

/I2C3_SCL/AGPIO19

SCL

SDA

/I2C3_SDA/AGPIO20

1

AGPIO6/LDT_RST_L

AGPIO7/LDT_PWROK

BLIN

K/USB_OC7_L/AGPIO11

GENI

GA20

FANO

VDD_18 Domain

UART

0_CTS_L/EGPIO135

UART

UART

0_RTS_L/EGPIO137

UART

UART

UART

UART

+3VS

0402_5%@

0_INTR/AGPIO139

1_CTS_L/BT_I2S_BCLK/EGPIO140

UART

1_RXD/BT_I2S_SDI/EGPIO141

UART

1_RTS_L/EGPIO142

UART

1_TXD/BT_I2S_SDO/EGPIO143

1_INTR/BT_I2S_LRCLK/AGPIO144

12

12

RC144

RC145

.2K_0402_5%

.2K_0402_5%

2

2

+3VA

LW

12

RC63

4.

7K_0402_5%

APU_F

P/EGPIO101

W

SD_

D/AGPIO25

C

LK/EGPIO95

C

MD/EGPIO96

C

ED/EGPIO93

L

D

ATA0/EGPIO97

ATA1/EGPIO98

D

ATA2/EGPIO99

D

ATA3/EGPIO100

D

AGPIO3

AGPIO4

AGPIO5

AGPI

AGPI

AGPI

NT2_L/AGPIO90

SPKR

/AGPIO91

IN/AGPIO126

FANI

N0/AGPIO84

UT0/AGPIO85

0_RXD/EGPIO136

0_TXD/EGPIO138

HVBE

RTCC

I2C0_

SCL_TP <27>

I2C0_

SDA_TP <27>

CH_PWRGD_R

BA28

AY29

AY13

H

DETECT

DD_ODD_

BA14

PXS

RST#

_

AY15

DGP

PWR_EN

U_

BA29

BT_

FF#

O

AY14

O

FF#

WL_

BA13

DG

PU_PWRGD

APU_

BA16

MODE

_ID#

L

AY16

APU_

CLK0

S

AY33

APU_

DATA0

S

BA32

AC5

AC4

AJ7

AGPIO3

AK2

AK1

AL4

AJ2

AJ4

O8

AG5

O9

AD1

O40

AJ8

AGPI

O11

AR29

AP29

AU35

GATE

A20

AV33

AU33

AP23

AP25

AR25

AV25

AU23

AP21

AV21

AP19

AV23

AR21

AP27

N_L

RTC_CL

K

AN4

LK

RC12

9 0

RC13

0 0

RC16

4 0

H

DD_ODD_

PXS

RST# <11>

_

DGP

PWR_EN <13,25,40,41>

U_

1 2

1 2

1 2

S

CLK0 <10>

APU_

APU_

DATA0 <10>

S

TP_I

NT# <27>

APU_S

GATE

A20 <25>

T28

T26

RTC_CL

H

L

DETECT <24 >

_0201_5%@

_0201_5%@

_0402_5%@

PKR <19>

K <22>

APU_P

CIE_RST#_R

LPC_F

LPC_CL

LPC_CL

APU_

T_OFF#

B

W

L_OFF#

APU_

U_

PWRGD

DGP

DDR4

11/16 confirm with BIOS member

RC71 33

BOOT FAIL

TIMER

ENABLED

BOOT FAIL

TIMER

DISABLED

(DEFAULT)

RAME#<8,25>

K0_EC<8,25>

K1<8>

APU_

T_OFF# <22>

B

APU_

L_OFF# <22>

W

1 2

_0402_5%

150

CC9

1

P_0402_50V8J

2

Use 48MHz crystal

CLK and generate

both internal and

external CLK

(DEFAULT)

Use 100MHz PCIE

CLK as reference

CLK and generate

internal CLK only

+3VS

12

RC75

10

K_0402_5%

AGPI

O3

RTC_CL

K

SYS_

RST#

12

@

RC76

2K

_0402_5%

MC7

4VHC1G08DFT2G SC70 5P

APU_

DATA0

S

RC16

APU_

AGP

HDD_ODD_DETECT

HDD/

MODEL

_ID#

2 2

CLK0

S

RC16

3 2

I

O11

RC69 1

ODD Detect

0K_0402_5% @

0K_0402_5% @

Model size (reserve strap pin)

+3VA

LW

CC10

1 2

0.

1U_0201_10V6K

5

2

12

@

RC77

10

12

RC78

2K

SA00000OH00

LPC_

SPI ROM

(DEFAULT)

LPC ROM

K_0402_5%

_0402_5%

1

@

1 2

RC73 0_

FRAME#LPC_CLK0 _EC LPC_C LK1

ENHANCED RESET

LOGIC

(for quicker S5

resume)

(DEFAULT)

TRADITION

RESET

+3VA

12

RC79

10

K_0402_5%

12

@

RC80

2K

_0402_5%

P

B

Y

A

G

3

AGPIO3

<INT PU>

LW

4

UC23

0402_5%@

12

RC81

10

12

@

RC82

2K

1 2

1 2

@

K_0402_5%

_0402_5%

12

12

.2K_0402_5%

.2K_0402_5%

12

0

K_0402_5%@

12

RC15810K_0402_5%

12

RC15910K_0402_5% @ODD@

RC1561

RC1571

RTC_

<INT PU>

COIN BATT

ON BOARD

(DEFAULT)

COIN BATT

NOT ON

BOARD

12

RC83

10

K_0402_5%

12

@

RC84

2K

_0402_5%

+3V

S

+3V

LW

A

+3VS

Functio n

+3VS

APU_P

CLK

12

RC85

10

K_0402_5%

12

@

RC86

2K

_0402_5%

ODD

2nd HDD

CIE_RST# <11,20,22>

SYS_RST #

<INT PU>

NORMAL

RESET MODE

(DEFAULT)

SHORT RST

MODE

Detect

0

1

A

LW

+3V

1 2

RC34 2

RC35 2

RC36 1

D D

+3VS

+3VS

+3VS

C C

+3VS

+3VA

LW

1 2

1 2

@ESD@

1 2

CC16

2 1

HDA_SYNC_AUDIO<19>

HDA_SDOUT_AUDIO<19>

HDA_BITCLK_AUDIO<19>

RPC12

1 8

2 7

3 6

4 5

1

0K_0804_8P4R_5%

RPC13

1 8

2 7

3 6

4 5

1

0K_0804_8P4R_5%

1 2

RC133 1

1 2

RC134 1

1 2

RC41 10

1 2

RC44 10

1 2

RC45 10

1 2

RC46 10

.

.

K

00P_0402_50V8J

GATE

LAN_CL

CLK_

WLAN_

2K_0402_5%@

2K_0402_5%@

_0402_5%@

A20

REQ3#

0K_0402_5%UMA@

0K_0402_5%DIS@

K_0402_5%@

K_0402_5%@

K_0402_5%

K_0402_5%

KREQ#

CLKREQ#

APU_

APU_

APU_

E

MI

RPC6

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

EMI@

VGA_

APU_B

PBTN_

USB_

USB_

EST0

T

EST2

T

EST1

T

SYS

E

SATA

DEVS

DEVS

CLKREQ#

T_OFF#

OUT#

OC0#

OC1#

_

RST#

SD

_ACT# <8>

LP1 <8>

LP0 <8>

HDA_SYNC

HDA_SDOUT

HDA_BITCLK

RPC9

1 8

2 7

3 6

4 5

1K

_0804_8P4R_5%

1 2

RC49 10

12

RC52 10

12

RC53 10

12

RC54 10

1 2

RC160 1

1 2

RC161 1

DGPU_

K_0402_5%@

K_0402_5%

K_0402_5%

K_0402_5%@

0K_0402_5%

0K_0402_5%

PBT

N_

PM_

S

PM_

S

M

UX_CTRL<9>

S5_

1 2

RC38 1

1 2

RC39 1

1 2

RC40 1

LAN_CL

WLAN_

CLKREQ#< 22>

VGA_

CLKREQ#<12>

USB_

HDA_S

HDA_S

HDA_RS

HDA_B

HDA_S

HDA_S

HDA_S

I2C1_

I2C1_

SCL

SDA

RC66 0_

HDA_S

DOUT

YNC

T#

ITCLK

DIN1

DIN2

DIN0

PWRGD<40>

OUT#<25>

LP_S3#<25>

LP_S5#<25,33,36>

KREQ#<20>

OC1#<26>

1 2

DIN0<19>

T31

5

5

5

K_0402_5%

K_0402_5%

K_0402_5%

0402_5%@

APU_

EC_RS

PBT

APU_

SYS

APU_

PM_

PM_

S5_

LAN_CL

WLAN_

CLK_

VGA_

USB_

USB_

HDA_B

HDA_S

HDA_S

HDA_S

HDA_RS

HDA_S

HDA_S

I2C0_

I2C0_

I2C1_

I2C1_

32K_

32K_

CIE_RST#_R

P

RST#_R

M

OUT#

N_

CH_PWRGD_R

F

RST#

_

CIE_WAKE#

P

LP_S3#

S

LP_S5#

S

UX_CTRL

M

APU_

APU_

APU_

KREQ#

CLKREQ#

REQ3#

CLKREQ#

OC0#

OC1#

DGPU_

ITCLK

DIN0

DIN1

DIN2

T#

YNC

DOUT

SCL

SDA

SCL

SDA

X1

X2

EST0

T

T

EST1

EST2

T

I2C Port 0: Touch Pad

+1.8

VALW

1 2

RC59 0_

EC_RSM

B B

RST#<25>

RB751 Ma x Vf=0.37V

1 2

DC3

RB75

1V-40 SOD-323

SCS00003500

0402_5%@

@

EC_RSM

47

K_0402_5%

RST#_R

12

RC60

2

CC8

0.1

U_0201_10V6K

1

I2C0_

I2C0_

100P_0402_50V8J

32.768KMHz CRYSTAL

32K_

X1

32K_

1

CC12

12

P_0402_50V8J

2

X2

EC

SYS_

PWRGD_EC<25>

12

RC87 20

M_0402_5%

YC32

1 2

32

.768KHZ_9PF_X1A000141000200

1

CC11

12

P_0402_50V8J

2

A A

Secu

Secu

Secu

rity Classification

rity Classification

rity Classification

Issu

Issu

Issued Date

ed Date

ed Date

THIS

THIS

THIS

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPER TY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPER TY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPER TY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUS TODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHE R THIS SHEET NOR THE INFORM ATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHE R THIS SHEET NOR THE INFORM ATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHE R THIS SHEET NOR THE INFORM ATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS , INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS , INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS , INC.

2018

2018

2018

Comp

Comp

Compal Secret Data

al Secret Data

2

al Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

/03/12 2019/03/12

/03/12 2019/03/12

/03/12 2019/03/12

Comp

Comp

Comp

al Electronics, Inc.

al Electronics, Inc.

Titl

Titl

Title

e

e

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Cust

Cust

Cust

om

om

om

Date : Sheet

Date : Sheet

Date : Sheet

al Electronics, Inc.

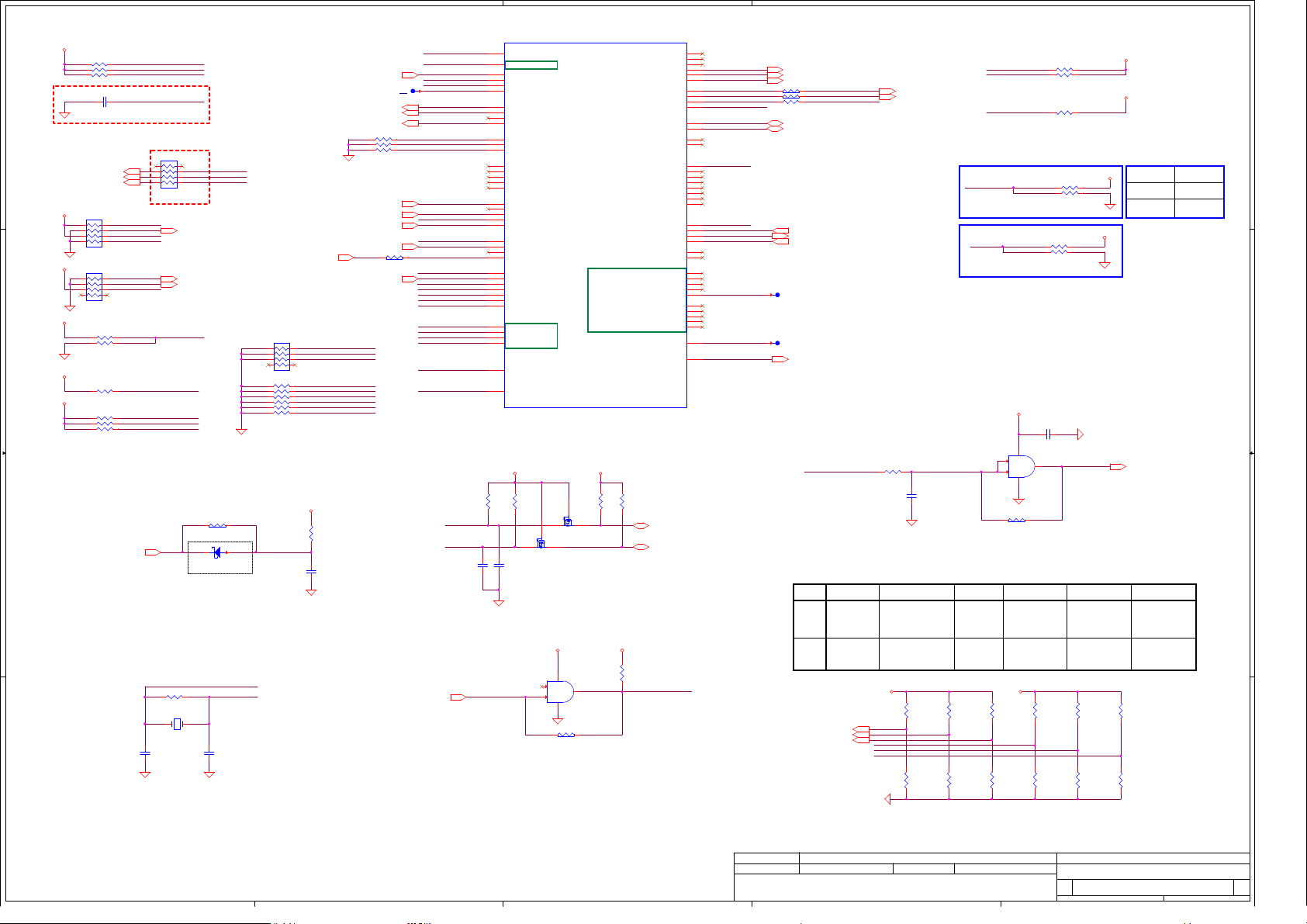

GPIO

GPIO

GPIO

/ AZ / I2C

/ AZ / I2C

/ AZ / I2C

LA-G

LA-G

LA-G

241P

241P

241P

1

7 43Monday, March 12, 2018

7 43Monday, March 12, 2018

7 43Monday, March 12, 2018

1.0

1.0

1.0

of

of

of

5

4

3

2

1

UC1E

SATA_

ATX_DRX _P0<23>

SATA_

HDD

D D

+0.95VS

O

DD

RC88 1K_0402 _1%

RC89 1K_0402 _1%

GPU

LAN

WLA

N

C C

B B

+3VS

RC90 10

RC112 1

LPC_R

ST#<25>

1 2

1 2

K_0402_ 5%@

0K_0402 _5%

10

RC94

0K_0402_5%

@

1 2

KBRST

LPC_P

D#

1 2

RC93 33_04

15

CC13

0P_0402_50V8J

1

2

ATX_DRX _N0<23>

ARX_DTX _N0<23>

SATA_

ARX_DTX _P0<23>

SATA_

ATX_DRX _P1<24>

SATA_

SATA_

ATX_DRX _N1<24>

SATA_

ARX_DTX _N1<24>

SATA_

ARX_DTX _P1<24>

12

12

SATA_

ACT#<7>

DEVSL

P0<7>

DEVSL

P1<7>

CLK_P

EG_VGA<11>

CLK_P

EG_VGA#<11>

CLK_P

CIE_LAN<20>

CLK_P

CIE_LAN#<20>

CLK_P

CIE_WL AN<22 >

CLK_P

CIE_WL AN#<22>

#

LPC_C

LK0_EC<7,25>

LPC_C

LK1<7>

LPC_F

RAME#<7,25>

LPC_A

D0<25>

LPC_A

D1<25>

LPC_A

D2<25>

LPC_A

D3<25>

02_5%

LPC_C

LKRUN#< 25>

EC_SC

I#<25>

SERIR

Q<25>

SATA_ZV SS

SATA_ZV DDP

48M_X

1

48M_X

2

LPC_R

ST#_R

LPC_P

D#

BA10

AY10

AY12

BA12

AY9

BA9

BA8

AY8

AU11

AP11

AY30

AV31

AU31

AU27

BA25

BA24

AY24

BA

AY

AY

AY

AY27

AY26

AC1

AA8

BA27

AV27

H2

H1

M2

M1

L2

L1

K2

K1

J2

J1

F2

F1

26

28

25

23

A6-92

@

SATA_

TX0P

SATA_

TX0N

SATA_

RX0N

SATA_

RX0P

SATA_

TX1P

SATA_

TX1N

SATA_

RX1N

RX1P

SATA_

SATA_ZVSS

SATA_ZVDDP

SATA_

ACT_L/AGPIO130

DEVSL

P0/EGPIO67

DEVSL

P1/EGPIO70

GFX_C

LKP

GFX_C

LKN

GPP_C

LK0P

GPP_C

LK0N

GPP_C

LK1P

GPP_C

LK1N

GPP_C

LK2P

GPP_C

LK2N

GPP_C

LK3P

GPP_C

LK3N

X48M_

X1

X48M_

X2

X25M_

48M_OSC

LPCCL

K0/EGPIO74

LPCCL

K1/EGPIO75

LFRAM

E_L

LAD0

LAD1

LAD2

LAD3

LPC_R

ST_L

LPC_C

LKRUN_L/AGPIO88

LPC_P

D_L/AGPIO21

LPC_P

ME_L/AGPIO22

LPC_S

MI_L/AGPIO86

SERIR

Q/AGPIO87

00E_BGA 769

48MHz CRYSTAL

48M_X

2_R

48M_X

1

1

4

4

1

2

1_R

YC48

48

MHZ_8PF _7V48000010

SJ10000 JP00

CC15

6.

8P_0402 _50V8C

RC103 1

2

2

A A

3

3

1

CC16

6.

8P_0402 _50V8C

2

12

M_0402_ 5%

5

1 2

RC105 3

1 2

RC104 3

3_0402_ 5%EMI@

3_0402_ 5%EMI@

EMI

48M_X

2

48M_X

1

APU_S

PI_CS1#

APU_S

PI_MISO

APU_S

PI_WP#

Securit

Securit

Securit

y Classification

y Classification

y Classification

Issued Date

Issued Date

Issued Date

THIS

THIS

THIS

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

CLK/S

VDD_18 Domain

but OD type

8MB S

UC2

1

CS#

2

DO(IO

1)

3

WP#(I

O2)

4

GND

XM2

5QU64AH IGT SOP 8P

SA0000B JU00

ATA/USB/SPI/LPC

USBCL

K/25M_48M_OSC

USB_S

VDD_18 Domain

SPI_C

LK/ESPI_CLK/EGPIO117

SPI_D

O/ESPI_DAT0/EGPIO121

SPI_D

I/ESPI_DAT1/EGPIO120

SPI_H

OLD_L/ESPI_DAT3/EGPIO133

SPI_W

P_L/ESPI_DAT2/EGPIO122

SPI_C

SPI_T

PM_CS_L/AGPIO76

ESPI_

ESPI_

SPI_C

ALERT_L/LDRQ0_L

RESET_L/KBRST_L/AGPIO129

S2_L/ESPI_CS_L/EGPIO119

PI ROM

8

VCC

HOLD#

7

(IO3)

6

CLK

5

DI(IO

0)

2018/

2018/

2018/

03/12 2019/03/1 2

03/12 2019/03/1 2

03/12 2019/03/1 2

3

USB_Z

VSS

USB_H

SD0P

USB_H

SD0N

USB_H

SD1P

SD1N

USB_H

SD2P

USB_H

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB_H

SD4P

USB_H

SD4N

USB_H

SD5P

USB_H

SD5N

USB_H

SD6P

USB_H

SD6N

USB_H

SD7P

USB_H

SD7N

USB_S

S_ZVSS

S_ZVDDP

USB_S

S_0TXP

USB_S

S_0TXN

USB_S

S_0RXP

USB_S

S_0RXN

USB_S

S_1TXP

USB_S

S_1TXN

USB_S

S_1RXP

USB_S

S_1RXN

USB_S

S_2TXP

USB_S

S_2TXN

USB_S

S_2RXP

USB_S

S_2RXN

S1_L/EGPIO118

APU_S

PI_HOLD#

APU_S

PI_CLK_R

APU_S

PI_MOSI

AL8

USB_Z

AN7

AW1

AW2

AV1

AV2

AU1

AU2

AT1

AT2

AR1

AR2

AP1

AP2

AN1

AN2

AM1

AM2

W4

W5

T1

T2

V2

V1

R1

R2

W2

W1

P1

P2

Y2

Y1

AY17

AY20

BA17

BA18

BA20

AY21

BA21

AY18

BA30

AY19

Compal Secret Data

Compal Secret Data

Compal Secret Data

VSS

USB20

USB20

USBSS

USBSS

APU_S

APU_S

APU_S

APU_S

APU_S

APU_S

KBRST

APU_S

+1.8V

S

1

CC14

0.

1U_0201 _10V6K

2

Deciphered Date

Deciphered Date

Deciphered Date

_ZVSS

_ZVDD

PI_CLK

PI_MOSI

PI_MISO

PI_HOLD#

PI_WP#

PI_CS1#

#

PI_CS2#

@

1 2

RC108 1

_P2

_N2

1 2

RC100 1

1 2

RC101 1

KBRST

1.8K_040 2_1%

USB20

_P1 <22>

USB20

_N1

USB20_P 3 <21>

USB20_N 3 <21>

USB20

_P5 < 26>

USB20

_N5

USB20

_P6 < 26>

USB20

_N6

K_0402_ 1%

K_0402_ 1%

USB3_

ATX_DRX _P1 <26>

USB3_

ATX_DRX _N1 <26>

USB3_

ARX_DTX _P1 <26>

USB3_

ARX_DTX _N1 < 26>

USB3_

ATX_DRX _P2 <26>

USB3_

ATX_DRX _N2 <26>

USB3_

ARX_DTX _P2 <26>

USB3_

ARX_DTX _N2 <26>

RC102 3

# <25>

USB20

_N2

USB20

_P2

+1.8V

2

T

<22>

B

Camera

Card Reader

<26>

<26>

USB 3.0 (MB)

USB 3.0 (MB)

+0.95

VALW

USB 3

.0 (MB)

USB 3.0 (MB)

APU_S

12

3_0402_ 5%EMI@

PI_CLK_R

EMI

1 2

R951 0_

1 2

R950 0_

S

0402_5%@

0402_5%@

RPC11

1 8

2 7

3 6

4 5

1

0K_0804 _8P4R_5%

Compa

Compa

Title

Title

Title

S

S

S

ize Document Number Re v

ize Document Number Re v

ize Document Number Re v

Custo

Custo

Custo

Date : Sheet

Date : Sheet

Date : Sheet

Compa

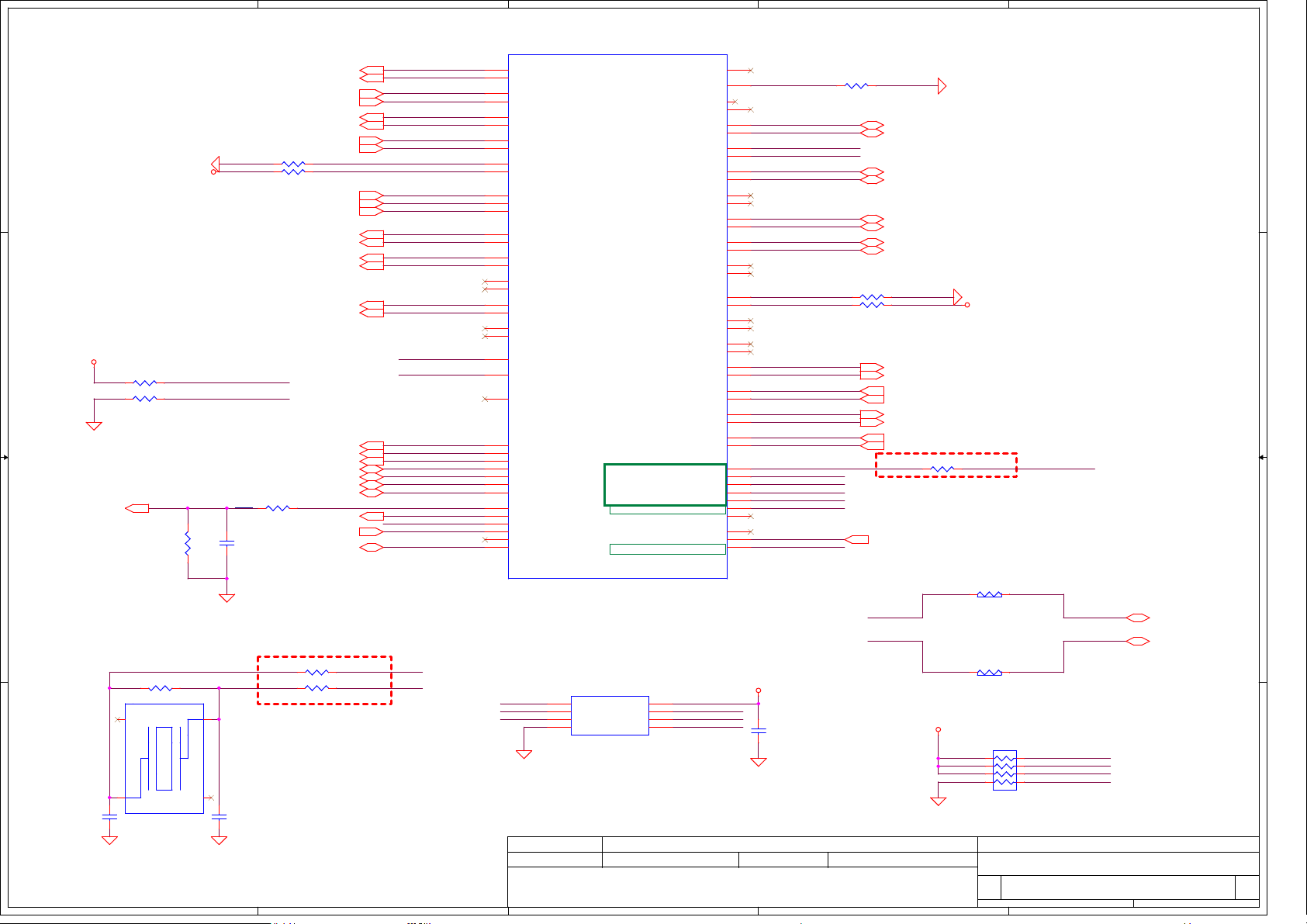

SATA

SATA

SATA

m

m

m

SPI R

USB20

_N2_R

USB20

_P2_R

APU_S

PI_HOLD#

APU_S

PI_WP#

APU_S

PI_CS1#

APU_S

PI_CS2#

l Electronics, Inc.

l Electronics, Inc.

l Electronics, Inc.

/ USB / LPC / SPI

/ USB / LPC / SPI

/ USB / LPC / SPI

LA-G2

LA-G2

LA-G2

41P

41P

41P

1

OM

USB20

USB20

_N2_R <17 >

_P2_R <17>

o f

o f

o f

8 43Monday, March 12 , 2018

8 43Monday, March 12 , 2018

8 43Monday, March 12 , 2018

1.0

1.0

1.0

5

4

3

2

1

AJ31

R19

H23

A2

A8

A13

A18

A23

A32

A35

A39

B8

B13

B32

B39

C3

C5

C7

C9

C11

C13

C15

C17

C19

C21

C23

C25

C27

C29

C31

C33

C35

C37

C39

C41

E1

E2

E3

E21

E25

E29

E35

E38

E39

G1

G2

G3

G11

G13

G23

G27

G31

G35

G37

G39

G41

J3

J8

J39

L3

L8

0K_0402_5%

UC1G

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

A6-9

@

215

_

214

_

213

_

1

_

_

2

3

_

4

_

5

_

_

6

7

_

8

_

9

_

10

_

_

11

12

_

13

_

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

200E_BGA769

1.5V

+RTCBA

1

CC18

0.

22U_0402_6.3V6K

2

GND

L13

VSS

59

_

L19

VSS

60

_

L21

VSS

61

_

L23

VSS

62

_

L25

_

63

VSS

L27

VSS

64

_

L29

VSS

65

_

L31

VSS

66

_

L39

_

67

VSS

L41

VSS

68

_

N1

VSS

69

_

N2

VSS

70

_

N3

VSS

71

_

N39

_

72

VSS

R3

VSS

73

_

R11

VSS

74

_

R13

VSS_75

R15

VSS_76

R17

VSS_77

R21

VSS_78

R23

VSS_79

R25

VSS_80

R27

VSS_81

R29

VSS_

82

R31

VSS_

83

R39

VSS_

84

R41

VSS_

85

U1

VSS_

86

U2

VSS_

87

U3

VSS_

88

U10

VSS_

89

U39

VSS_

90

W3

VSS_

91

W10

VSS_

92

W11

VSS_

93

W13

VSS_

94

W15

VSS_

95

W17

VSS_

96

W19

VSS_

97

W21

VSS_

98

W23

VSS_

99

W25

VSS_

100

W27

VSS_

101

W29

VSS_

102

W31

VSS_

103

W39

VSS_

104

W41

VSS_

105

AA1

VSS_

106

AA2

VSS_

107

AA3

VSS_

108

AA5

VSS_

109

AA10

VSS_

110

AA39

VSS_

111

AC3

VSS_

112

AC7

VSS_

113

AC10

VSS_

114

AC11

VSS_

115

AC13

VSS_

116

AC15

VSS_

117

AC17

VSS_

118

AC19

VSS_

119

W>=15mils

+RTCBA

UC25

TT_R

3

Vout

1

Vin

2

GND

AP

2138N-1.5TRG1_SOT23-3

SA000066U00

12

AA35

AC32

AC37

AE32

AE35

AG32

AG37

AR35

AA25

AA27

AA29

AA31

AM11

AM13

UC1F

J35

L32

L37

N35

R37

U32

U35

W32

W37

AJ32

AJ35

AL32

AL37

K21

K23

K25

K27

K29

K31

N21

N23

N25

N27

N29

N31

U23

U25

U27

U29

U31

AR4

AR5

AR7

AU7

AJ11

AL11

AL13

AJ21

AJ23

AJ25

AJ27

AL23

AL25

AL27

AL29

A6-9

@

+1.

V

CC42 1

80P_0402_50V8J

1

2

CC37 1

1

80P_0402_50V8J

2

CC43 1

1

80P_0402_50V8J

2

2

U

nder APU

+1.2V

+APU_

CORE

+1.

V

2

CC21 2

CC23 2

CC22 2

CC20 2

1

1

1

1

2U_0603_6.3V6M

2U_0603_6.3V6M

2U_0603_6.3V6M

2U_0603_6.3V6M

2

2

2

2

D D

1 2

RC120 0_0402_5%@

CC28 2

CC30 22U_0603_6.3V6M

CC26 2

CC24 2

1

2U_0603_6.3V6M

2

CC29 22U_0603_6.3V6M

CC27 2

CC25 2

1

1

1

1

1

1

@

@

@

2U_0603_6.3V6M

2U_0603_6.3V6M

2U_0603_6.3V6M

2U_0603_6.3V6M

2

2

2

2

2

2

+3VS_APU+3VS

CC76 0

CC44 1

1

1

.22U_0402_6.3V6K

0U_0603_6.3V6M

2

2

CC31 0

1

.22U_0402_6.3V6K

2

CC36 0

CC35 0

CC32 0

CC33 0

CC34 0

1

1

1

1

1

.22U_0402_6.3V6K

.22U_0402_6.3V6K

.22U_0402_6.3V6K

.22U_0402_6.3V6K

.22U_0402_6.3V6K

2

2

2

2

2

CC41 0

CC38 0

CC39 0

CC40 0

1

1

1

1

.22U_0402_6.3V6K

.22U_0402_6.3V6K

.22U_0402_6.3V6K

.22U_0402_6.3V6K

2

2

2

2

DIMMS /GND

Under APU ACROSS +1.2V_V DDQ AND VSS SPLIT

+APU_

CORE_NB

C C

CC72 0

CC74 0

CC73 0

CC75 0

1

1

.22U_0402_6.3V6K

.22U_0402_6.3V6K

2

2

CC45 22U_0603_6.3V6M

1

1

.22U_0402_6.3V6K

1

.22U_0402_6.3V6K

2

2

2

+1.8

VS

CC47 0

CC46 10U_0603_6.3V6M

1

1

.22U_0402_6.3V6K

2

2

CC48 1

12

U_0201_6.3V6M

Out s ide of APU

+3VA

CC51 1

1

0U_0603_6.3V6M

2

LW

CC52 0

1

.22U_0402_6.3V6K

2

+1.8

CC53 1

0U_0603_6.3V6M

VALW

CC54 0

1

1

.22U_0402_6.3V6K

2

2

+0.9

CC70 1

0U_0603_6.3V6M

5VALW

CC71 0

1

1

.22U_0402_6.3V6K

2

2

CC49 1

CC50 1

12

12

U_0201_6.3V6M

U_0201_6.3V6M

Under APU

CC56 1

CC55 1

1

1

0U_0603_6.3V6M

0U_0603_6.3V6M

2

2

+1.8

VS

+VDDCR_F

CH_ALW

+0.9

5VALW

0.8A

+0.9

5VS

7

A

+VDDCR_F

CH_ALW

CC57 0

1

.22U_0402_6.3V6K

2

+RTC_B

ATT

+1.8

VS

0.2A

W>=15mils

Under APUUnder APUUnder APUUnder APU

B B

+0.95VS OF APU

+0.9

5VS

CC61 1

CC60 1

CC59 1

CC58 1

1

1

1

12

U_0201_6.3V6M

0U_0603_6.3V6M

0U_0603_6.3V6M

0U_0603_6.3V6M

2

2

2

+0.9

5VS

CC62 10U_0603_6.3V6M

CC63 0.22U_0402_6.3V6K

1

1

2

2

VDD

O_MEM_S3_1

I

VDD

O_MEM_S3_2

I

VDD

O_MEM_S3_3

I

VDD

O_MEM_S3_4

I

I

O_MEM_S3_5

VDD

VDD

O_MEM_S3_6

I

VDD

O_MEM_S3_7

I

VDD

O_MEM_S3_8

I

I

O_MEM_S3_9

VDD

VDD

O_MEM_S3_10

I

VDD

O_MEM_S3_11

I

VDD

O_MEM_S3_12

I

VDD

O_MEM_S3_13

I

I

O_MEM_S3_14

VDD

VDD

O_MEM_S3_15

I