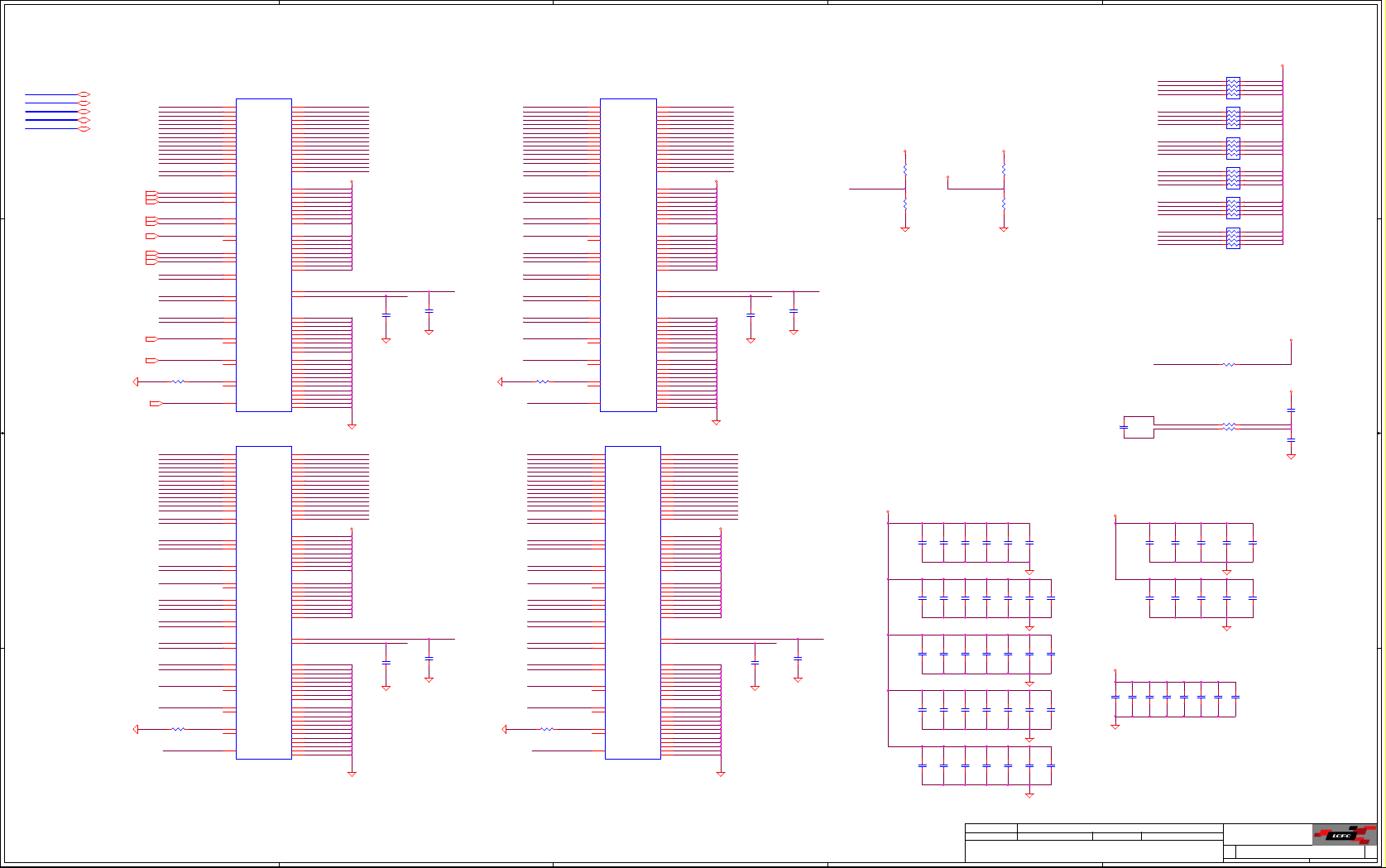

LCFC CG520 Schematic

A

1 1

B

C

D

E

LCFC Confidential

CG520

2 2

NM-A804

M/B Schematics Document

Intel Braswell M-Processor with DDRIIIL

2015-10-11

3 3

REV:1.0

4 4

Titl

Titl

Titl e

e

Security Class

Security Class

Security Class

THIS SHEE

THIS SHEE

THIS SHEE

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFE RED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFE RED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFE RED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT ASAU THORIZED BY LC FUTURE CENTER NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT ASAU THORIZED BY LC FUTURE CENTER NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT ASAU THORIZED BY LC FUTURE CENTER NEITHER THIS S HEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANYTHIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANYTHIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANYTHIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

A

B

ification

ification

ification

Issued Date

Issued Date

Issued Date

T OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

T OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

T OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

2015/10/

2015/10/

2015/10/08

C

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

08

08

Deciphered Date

2015/03/23

2015/03/23

2015/03/23

D

e

Cover Page

Cover Page

Cover Page

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Tuesday, Dec

Tuesday, Dec

Dat e: Sheet o f

Dat e: Sheet o f

Dat e: Sheet o f

Tuesday, December 08, 2015

CG520

ember 08, 2015

ember 08, 2015

E

1 57

1 57

1 57

1.01.0

5

4

3

2

1

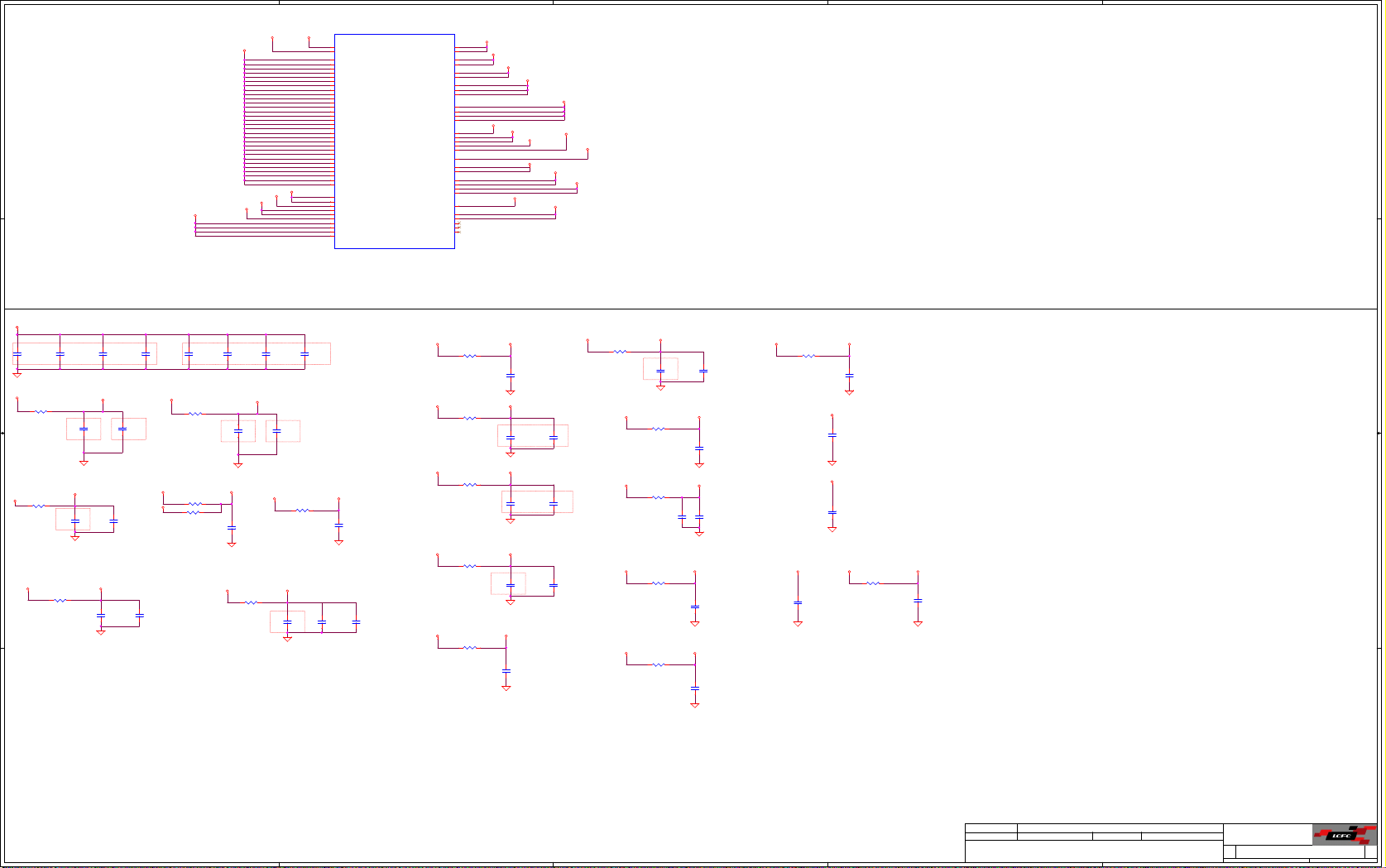

Memory BUS (DDR3L)

D D

HDMI Conn.

Page 34

HDMI

Dual Channel

1.35V DDR3L 1600 MT/s

MD 16x DDR3L 8Pcs

UP TO 8G

Page 14

eDP Conn.

Int. Camera

USB 2.0 Port3

Page 33

eDP x2 Lane

Braswell-M (4.5W)

BGA-1170

25mm*27mm

C C

SATA HDD

SATA Port0

Page 42

SATA ODD

SATA Port1

Page 42

LAN

RJ45 Conn.

Page 38

B B

Realtek ALC3240

Page 43

Realtec RTL8107E

(10M/100M)

Page 37

PCIe Port3

Codec

SPK Conn.

Page 43

SATA Gen3

SATA Gen1

PCIe 1x

HD Audio

Page 4˜12

FAB_AJ129

LPC BUS

USB3.0 1x

USB2.0 1x

USB2.0 1x

USB2.0 1x

USB2.0 1x

PCIe 1x

EC

ITE IT8886E-LQFP

Page 44

Mic

HP&Mic Combo Conn.

USB Left 3.0 Conn

Page 41

USB Left 2.0 Conn

Page 45

Cardreader Realtek

RTS5070

Page 30

NGFF Card WLAN&BT

Page 40

TPM

ST33ZP24AR28PVSP

USB 3.0 Port1

USB 2.0 Port1

USB 2.0 Port0

PUSB 2.0 Port3

USB 2.0 Port2

PCIe Port2

SD/MMC Conn.

Sub-board (for 15’’)

ODD Board (CG520 NS-A801)

Touch Pad

Page 45

A A

5

4

Int. KBD

Page 45

SecuSecuSecuririri

tytyty ClClClassassassiiifffiiicacacatititiononon

IIIsss

sssueduedued DaDaDatetete

S S S SHEET SHEET SHEET OFOFOF ENGIENGIENGINEERNEERNEERIIING NG NG DRDRDRAAAWWW IIING NG NG IIIS S S TTTHE HE HE PROPRIPROPRIPROPRIETETETAAARRRYYY PROPERPROPERPROPERTTTYYY OFOFOF LCLCLC FUTFUTFUTURURURE E E CENCENCENTTTER. AER. AER. ANDNDND CONTCONTCONTAAAIIINS NS NS CONFICONFICONFIDENDENDENTTTIIIAAALLL

TTTHIHIHI

AAANDNDND TTT RARARADE DE DE SECRSECRSECR ET ET ET IIINFORMANFORMANFORMATTTIIION. TON. TON. THIHIHIS S S SHEET SHEET SHEET MAMAMAYYY NOT NOT NOT BE BE BE TTT RARARANSFEREDNSFEREDNSFERED FROM FROM FROM TTTHE HE HE CUCUCUSTOSTOSTODYDYDY OFOFOF TTT HE HE HE COMPETCOMPETCOMPETENT ENT ENT DIDIDIVVVIIISISISION ON ON OFOFOF R&DR&DR&D

DEPDEPDEPAAARRRTTTMENT MENT MENT EXEXEXCEPT ACEPT ACEPT AS AS AS AUTUTUTHORIHORIHORIZED ZED ZED BYBYBY LCLCLC FUTFUTFUTURURURE E E CENCENCENTTTER ER ER NEINEINEITTTHERHERHER TTTHIHIHIS S S SHEET SHEET SHEET NOR NOR NOR TTTHE HE HE IIINFORMANFORMANFORMATTTIIION ON ON IIIT T T CONTCONTCONTAAAIIINSNSNS

MAMAMAYYYBE BE BE USEDUSEDUSED BYBYBY OR OR OR DIDIDISCLSCLSCLOSED TOSED TOSED TO O O AAANYNYNY TH TH THIIIRDRDRD PPPAAARRRTTTYYY WWWIIITTTHOUT HOUT HOUT PRIPRIPRIOR OR OR WWWRIRIRITTTTTTEN EN EN CONSENCONSENCONSENT T T OFOFOF LCLCLC FUTFUTFUTURURURE E E CENCENCENTTTER.ER.ER.

3

SPI ROM

8MB

222000111555/1/1/1000/0/0/0888

FutureFutureFuture CeCeCenter nter nter SecSecSecrereret t t DaDaDatatata

LCLCLC

DeciDeciDeciphphphererered ed ed DateDateDate

2

222000111555/0/0/0333/2/2/2333

TTT iiitttllleee

Block Diagram

eeent nt nt NuNuNummmbbbeeerrr RRReee vvv

SizeSizeSize DocumDocumDocum

CuCuCustostostommm

DDDaaattteee::: SSShhheeeeeettt

TuesdTuesdTuesday, ay, ay, DeDeDecember cember cember 08, 08, 08, 201520152015

CG520

1

2

1.01.0

ooofff

575757

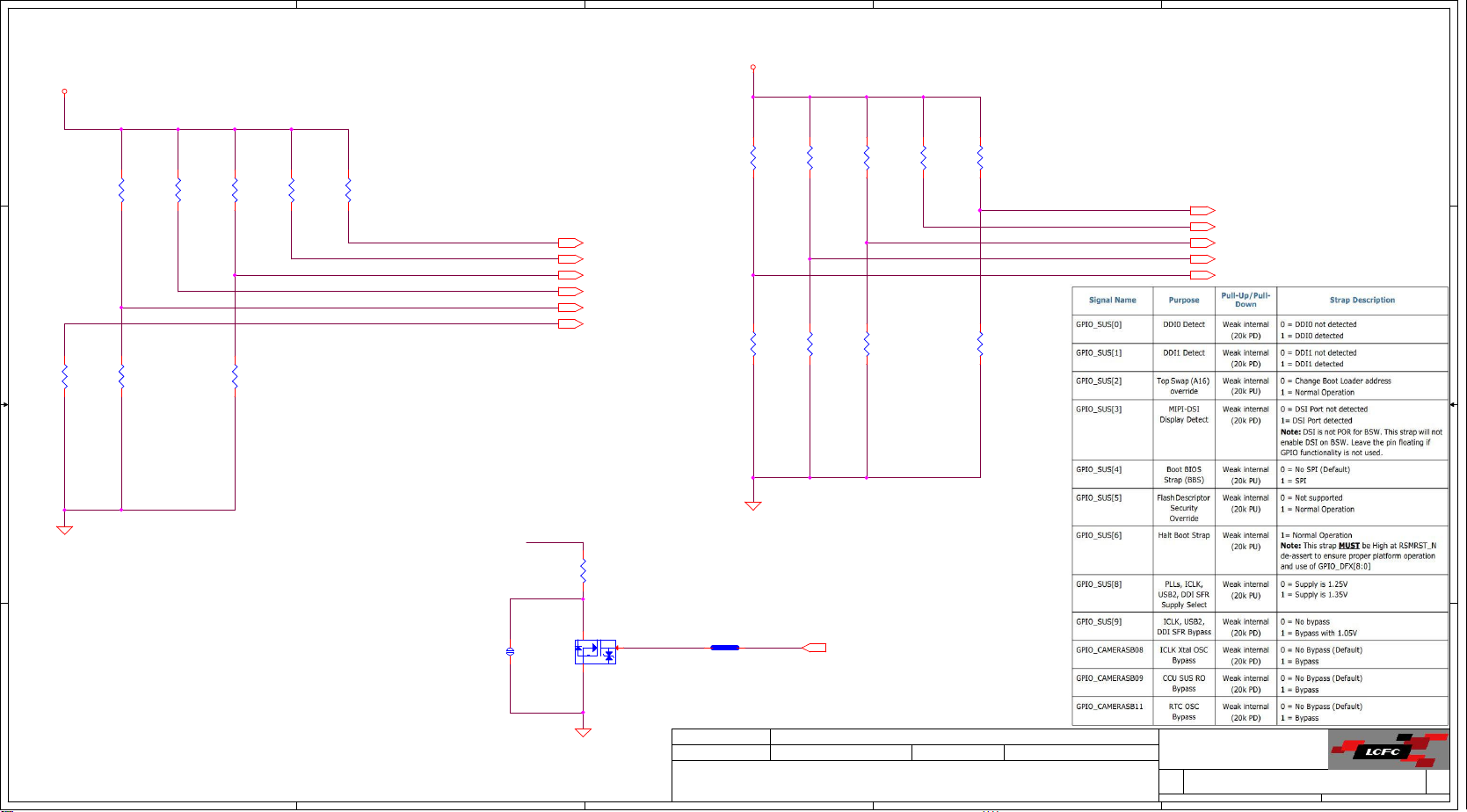

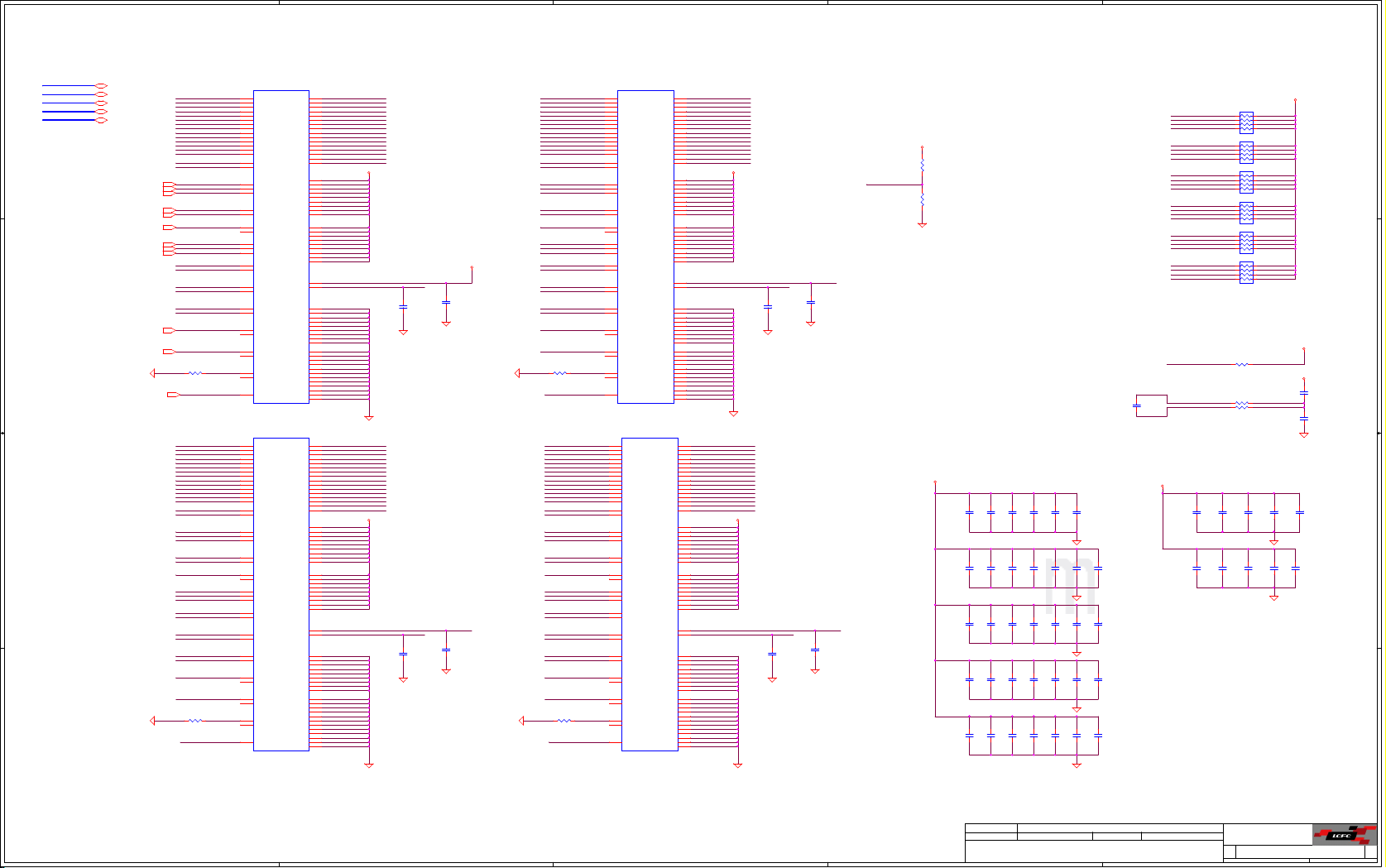

Voltage Rails

A

, X --> Means OFF

B

C

D

E

)( O --> Means ON

+5VS

Power Plane

+3VALW

B+

+3VL

1 1

State

S0

+5VAL

O

+3VALW_SOC

+1.0VALW

+1.8VALW

W

O O O

+1.35V

O

+3VS

+1.5VS

+0.68VS

CPU_COR E

GFX_C

ORE

STATE

Fu

ll ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

ON

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

ONONON ON

ON

ON

ON

ON

OFF

ON

OFF

ON

OFF

OFF

OFF

LOW

OFF

OFF

OFF

USB Port Table

S3

S5 S4/AC Only

S5 S4

Battery only

S5 S4

AC & Ba

2 2

don't exist

STATE SLP_S3#SLP_S1#

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk) ON

S5 (S

ttery

SIGNAL

oft OFF)

O

O X X

O

XX

SLP_S4# +VS+V Clock

LOW

HIGH HIGH

LOW

LOW HIGH

LOW

LOW LOW

LOW LOW

O

O

X

X

+VALW

HIGHHIGHHIGH

ON

ON

ON

ON

LOW OFF

ON

OO O X

XX

X

ONONON

ONONON

OFF

ON

X

X

ON

O

FF OFF

OFF

OFF

ONON

LOW

OFF

OFF

XHCI

USB 3.0

USB 2.0

USB HUB

Port

0

1

0

1

2

3

4

1

2

3

4

Port device

USB Port (Left Side)

USB3.0 Card Reader

USB Port (Left Side)

USB Port (Right Side)

BT

Camera

USB Port (Right Side)

BOM Structure Table

BTO ItemBOM Structure

AOAC@

OPT@

UMA@

14@

15@

100M@

N15SGT@

N15VGM@

GIGA@

GC6@

TS@

RANKA@

RANKB@

ME@

CD@

@

AOAC support part

GPU Part

UMA SKU ID part

For 14" part

For 15" part

100M LAN part

N15SGT Part

N15GSM Part

GIGA LAN Part

GPU GC6 Part

Touch Screen

GPU VRAM RANKA PART

GPU VRAM RANKB PART

Connect or

COST DOWN

Not stuff

part

PCIE PORT LIST

SMBUS Control Table

WLAN

VGA BATT SODI

X

V

+3VGS

X

ECEC_SMB_C K1

+3VALW

EC

K

+3VALW_P CH

SOURCE

+3VS

PCH

3 3

EC_SMB_D A1

EC_SMB_C K2

E

C_SMB_D A2

PCH_SMB_CL

PCH_SMB_D ATA

EC SM Bus1 address

4 4

Device

Smart Battery

Charger

0001 011X b

need to update

A

IT8986E

V

+3VALW

X

V

+3VS

X X X

EC SM Bus2 address

Device

Thermal Sensor EMC1403-2

MM

X

V V

+3VS +3VS

VGA

Thermal

WiMAX

Sensor

X

X XV

X

V

+3VS

V

Address

(rese rve)

1001_ 100xb

0x9E(base on NV defa

B

Module

XX

X

+3VALW_P CH

PCH SM Bus address

ult)

X

X

Device

DDR DIMMA

Wlan

TP

charger

V

X

X

Port Device

1

Discrete GPU

2

Discrete GPU

3

WLAN

4

LAN

5

H4T@

M4T@

S4T@@

6

7

8

Address

1010 000Xb

Rsvd

need to update

Security Cl assifica

Security Cl assifica

Security Cl assifica

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY

MAY BE USED BY

MAY BE USED BY

tion

tion

tion

OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF LC FUTURE CENT ER.

C

2015/10/08

2015/10/08

2015/10/08

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

2015/03/23

2015/03/23

2015/03/23

Hynix VRAM Part

VRAM Part

Micron

Samsung VRAM Part

DDI PORT LIST

Port Device

DDI0

DDI1

DDI2

DP TO VGA

eDP

HDMI

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number R

Size Document Number R

Size Document Number R

Custom

Custom

Custom

Tuesday, December 08, 2015

Tuesday, December 08, 2015

Date: Sheet

Date: Sheet

Date: Sheet

Tuesday, December 08, 2015

CGx20

CGx20

CGx20

E

of

3 57

of

3 57

of

3 57

ev

ev

ev

1.01.0

5

DDI0_RCOMP_P

12

RC1

402_0402_1%

DDI0_RCOMP_N

DDI1_RCOMP_P

12

RC2

D D

402_0402_1%

DDI1_RCOMP_N

DP TO VGA Co

nverter

CPU_EDP_TX0+33

CPU_EDP_TX0-33

CPU_EDP_TX1+33

CPU_EDP_TX1-33

DDI0_RCOMP_P

DDI0_RCOMP_N PCH_ENBKL

CPU_EDP_TX0+

CPU_EDP_TX0CPU_EDP_TX1+

CPU_EDP_TX1-

EDP

C C

HDMI D2

HDMI D1

HDMI D0

HDMI CLK

B B

CPU_EDP_AUX33

CPU_EDP_AUX#33

PCH_ENVDD33

HDMI_TX2+34

HDMI_TX2-34

HDMI_TX1+34

HDMI_TX1-34

HDMI_TX0+34

HDMI_TX0-34

HDMI_CLK+34

HDMI_CLK-34

HDMI_HPD34

DDPB_CLK34

DDPB_DATA34

CPU_EDP_AUX

CPU_EDP_AUX#

EDP_HPD#

PCH_ENBKL

PCH_BKLT_CTRL_Q

PCH_ENVDD

DDI1_RCOMP_P

DDI1_RCOMP_N

HDMI_TX2+

HDMI_TX2-

HDMI_TX1+

HDMI_TX1HDMI_TX0+

HDMI_TX0-

HDMI_CLK+

HDMI_CLK-

DDI PORT LIST

Port Device

DDI0

DDI1

DDI2

NA

eDP

HDMI

4

UC1C

D50

DDI0_TXP_0

C51

DDI0_TXN_0

H49

DDI0_TXP_1

H50

DDI0_TXN_1

F53

DDI0_TXP_2

F52

DDI0_TXN_2

G53

DDI0_TXP_3

G52

DDI0_TXN_3

H47

DDI0_AUXP

H46

DDI0_AUXN

W51

HV_DDI0_HPD

Y51

HV_DDI0_DDC_SCL

Y52

HV_DDI0_DDC_SDA

V52

PANEL0_BKLTEN

V51

PANEL0_BKLTCTL

W53

PANEL0_VDDEN

F38

DDI0_PLLOBS_P

G38

DDI0_PLLOBS_N

J51

DDI1_TXP_0

H51

DDI1_TXN_0

K51

DDI1_TXP_1

K52

DDI1_TXN_1

L53

DDI1_TXP_2

L51

DDI1_TXN_2

M52

DDI1_TXP_3

M51

DDI1_TXN_3

M42

DDI1_AUXP

K42

DDI1_AUXN

R51

HV_DDI1_HPD

P51

PANEL1_BKLTEN

P52

PANEL1_BKLTCTL

R53

PANEL1_VDDEN

F47

DDI1_PLLOBS_P

F49

DDI1_PLLOBS_N

F40

DDI2_TXP_0

G40

DDI2_TXN_0

J40

DDI2_TXP_1

K40

DDI2_TXN_1

F42

DDI2_TXP_2

G42

DDI2_TXN_2

D44

DDI2_TXP_3

F44

DDI2_TXN_3

D48

DDI2_AUXP

C49

DDI2_AUXN

U51

HV_DDI2_HPD

T51

HV_DDI2_DDC_SCL

T52

HV_DDI2_DDC_SDA

B53

RSVD_B53

A52

RSVD_A52

E52

RSVD_E52

D52

RSVD_D52

B50

RSVD_B50

B49

RSVD_B49

E53

RSVD_E53

C53

RSVD_C53

A51

RSVD_A51

A49

RSVD_A49

G44

RSVD_G44

BRASW

@

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

3 OF 13

NC's

ELL_FCBGA151170

?

DDI0

V1P8A

V1P8

V1P8

V1P8

V1P8

V1P8

DDI1

D

V1P8A

V1P8

V1P8

V1P8

DI2

V1P8A

V1P8

V1P8

CHV_MCP_EDS

DDR3_M0_DQ_63

REV = 1.2

SDMMC1

SDMM

?

SDMMC3

V1P24

rface

V1P24

V1P24

V1P24

V1P24

V1P24

V1P24

V1P24

V1P24

V1P24

MCSI and Camera inte

V1P24

V1P24

V1P24

V1P24

V1P24

V1P24

V1P24

GP_CAMERASB00

GP_CAMERASB01

GP_CAMERASB02

GP_CAMERASB03

GP_CAMERASB04

GP_CAMERASB05

GP_CAMERASB06

GP_CAMERASB07

GP_CAMERASB08

GP_CAMERASB09

GP_CAMERASB10

GP_CAMERASB11

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

SDMMC1_D3_CD_

V1P8

SMMC1_D4_SD_W

V1P8

V1P8

V1P8

V1P8

V1P8

SDMMC1_RCOMP

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

SDMMC2_D3_CD_

C2

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

SDMMC3_1P8_EN

V1P8

SDMMC3_PWR_ EN

V1P8

SDMMC3_RCOMP

RSVD_M44

RSVD_K44

RSVD_K48

RSVD_K47

MCSI_1_CLKP

MCSI_1_CLKN

MCSI_1_DP_0

MCSI_1_DN_0

MCSI_1_DP_1

MCSI_1_DN_1

MCSI_1_DP_2

MCSI_1_DN_2

MCSI_1_DP_3

MCSI_1_DN_3

MCSI_2_CLKP

MCSI_2_CLKN

MCSI_2_DP_0

MCSI_2_DN_0

MCSI_2_DP_1

MCSI_2_DN_1

MSCI_3_CLKP

MSCI_3_CLKN

MCSI_COMP

SDMMC1_CLK

SDMMC1_CMD

SDMMC1_D0

SDMMC1_D1

SDMMC1_D2

SMMC1_D5

SMMC1_D6

SMMC1_D7

SMMC1_RCLK

SDMMC2_CLK

SDMMC2_CMD

SDMMC2_D0

SDMMC2_D1

SDMMC2_D2

SDMMC3_CLK

SDMMC3_CMD

SDMMC3_CD_N

SDMMC3_D0

SDMMC3_D1

SDMMC3_D2

SDMMC3_D3

3

M44

K44

K48

K47

T44

T45

Y47

Y48

V45

V47

V50

V48

T41

T42

P50

P48

P47

P45

M48

M47

T50

T48

P44

AB41

AB45

AB44

AC53

AB51

AB52

AA51

AB40

Y44

Y42

Y41

V40

M7

P6

M6

M4

P9

P7

N

T6

E

T7

T10

T12

T13

P13

K10

K9

M12

M10

K7

K6

N

F2

D2

K3

J1

J3

H3

G2

K2

L3

_N

P12

RC24

1 2

150_0402_1%

GPIO_CAM_8

RC106

1 2

100_0402_1%

1 2

RC107 80.6_0402_1%

GPIO_CAM_8 12

GPIO_CAM_9 12

GPIO_CAM_11 12

2

1

+1.8VALW

EDP_HPD

EDP_HPD#

QC4A

61

D

S

G

2N7002KDWH_SOT363-6

12

RC9290

1K_0402_5%

2

12

RC4

0604

100K_0402_5%

0604

CPU_EDP_HPD 33

PCH_ENBKL 33

PCH_ENBKL can direct connect to EC for costdown

+3VS

RPC26

10K_0404_4P2R_5%

G25

QC2A

PJT138K_SOT363-6

QC2B

D2 3

PJT138K_SOT363-6

S2

4

PCH_EDP_PWM 33

PCH_BKLT_CTRL_Q

+3VALW

1 4

2 3

D1 6S11

2

G1

A A

Title

Title

Security Cl assification

Security Cl assification

Security Cl assification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USE

MAY BE USE

MAY BE USE

D BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

D BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

D BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/10/08

2015/10/08

2015/10/08

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2015/03/23

2015/03/23

2015/03/23

Title

SOC (DDI,EDP,HDMI)

SOC (DDI,EDP,HDMI)

SOC (DDI,EDP,HDMI)

Size Document Nu mber Re v

Size Document Nu mber Re v

Size Document Nu mber Re v

Custom

Custom

Custom

Tuesday, December 08, 2015

Tuesday, December 08, 2015

Tuesday, December 08, 2015

Date: Sheet

Date: Sheet

Date: Sheet

CGx20

CGx20

CGx20

4 57

4 57

4 57

of

of

1

of

1.01.0

5

DDRA_MA15

DDRA_MA14

DDRA_MA13

DDRA_MA12

12

M0_RCOMPPD

RC34

182_0402_1%

DDRA_MA11

DDRA_MA10

DDRA_MA9

DDRA_MA8

DDRA_MA7

DDRA_MA6

DDRA_MA5

DDRA_MA4

DDRA_MA3

DDRA_MA2

DDRA_MA1

DDRA_MA0

DDRA_DRAMRST#_R

DDR_PWROK

D D

DDRA_BS2#14

DDRA_BS1#14

DDRA_BS0#14

DDRA_CAS#14

DDRA_RAS#14

DDRA_WE#14

DDRA_CS0#14

DDRA_CLK014

DDRA_CLK0#14

DDRA_CKE014

DDRA_ODT014

C C

INTEL PDG 182 ohm

SD00001KG00

DDRA_DRAMRST#14

B

DDRA_DM6

DDRA_DM7

DDRA_DM5

DDRA_DM4

DDRA_DM3

DDRA_DM1

DDRA_DM2

DDRA_DM0

DDRA_DQS6

DDRA_DQS#6

DDRA_DQS7

DDRA_DQS#7

DDRA_DQS5

DDRA_DQS#5

DDRA_DQS4

DDRA_DQS#4

DDRA_DQS3

DDRA_DQS#3

DDRA_DQS1

DDRA_DQS#1

DDRA_DQS2

DDRA_DQS#2

DDRA_DQS0

DDRA_DQS#0

BD49

BD47

BF44

BF48

BB49

BJ45

BE52

BD44

BE46

BB46

BH48

BD42

BH47

BJ48

BC42

BB47

BF52

AY40

BH46

BG45

BA40

BH44

AU38

AY38

BD38

BF38

AY42

BD40

BF40

BB44

AT30

AU30

AV36

BA38

AT28

AU28

BA42

AV28

BA28

BH30

BD32

AY36

BG41

BA53

AP44

AT48

AP52

BH32

BG31

BC30

BC32

AT32

AT34

BH40

BG39

AY52

BA51

AT42

AT41

AV47

AV48

AM52

AM51

1

CC143

0.1u_0201_10V6K

2

@

DDR3_M0_MA _15

DDR3_M0_MA _14

DDR3_M0_MA _13

DDR3_M0_MA _12

DDR3_M0_MA _11

DDR3_M0_MA _10

DDR3_M0_MA _9

DDR3_M0_MA _8

DDR3_M0_MA _7

DDR3_M0_MA _6

DDR3_M0_MA _5

DDR3_M0_MA _4

DDR3_M0_MA _3

DDR3_M0_MA _2

DDR3_M0_MA _1

DDR3_M0_MA _0

DDR3_M0_B S_2

DDR3_M0_B S_1

DDR3_M0_B S_0

DDR3_M0_CA S_N

DDR3_M0_RA S_N

DDR3_M0_W E_N

DDR3_M0_CS B_1

DDR3_M0_CS B_0

DDR3_M0_CK _1

DDR3_M0_CK B_1

DDR3_M0_CK E_1

DDR3_M0_CK _0

DDR3_M0_CK B_0

DDR3_M0_CK E_0

RSVD_AT30

RSVD_AU3 0

DDR3_M0_O DT_0

DDR3_M0_O DT_1

DDR3_M0_O CAVREF

DDR3_M0_O DQVREF

DDR3_M0_DR AMRST_N

DDR3_DRAM_ PWROK

DDR3_M0_RC OMPPD

DDR3_M0_DM _7

DDR3_M0_DM _6

DDR3_M0_DM _5

DDR3_M0_DM _4

DDR3_M0_DM _3

DDR3_M0_DM _2

DDR3_M0_DM _1

DDR3_M0_DM _0

DDR3_M0_DQ S_7

DDR3_M0_DQ SB_7

DDR3_M0_DQ S_6

DDR3_M0_DQ SB_6

DDR3_M0_DQ S_5

DDR3_M0_DQ SB_5

DDR3_M0_DQ S_4

DDR3_M0_DQ SB_4

DDR3_M0_DQ S_3

DDR3_M0_DQ SB_3

DDR3_M0_DQ S_2

DDR3_M0_DQ SB_2

DDR3_M0_DQ S_1

DDR3_M0_DQ SB_1

DDR3_M0_DQ S_0

DDR3_M0_DQ SB_0

BRASWELL_FCBGA151170

REV = 1.2

@

1

RC9291

0_0402_5%

?

CHV_MCP_EDS

DDR0

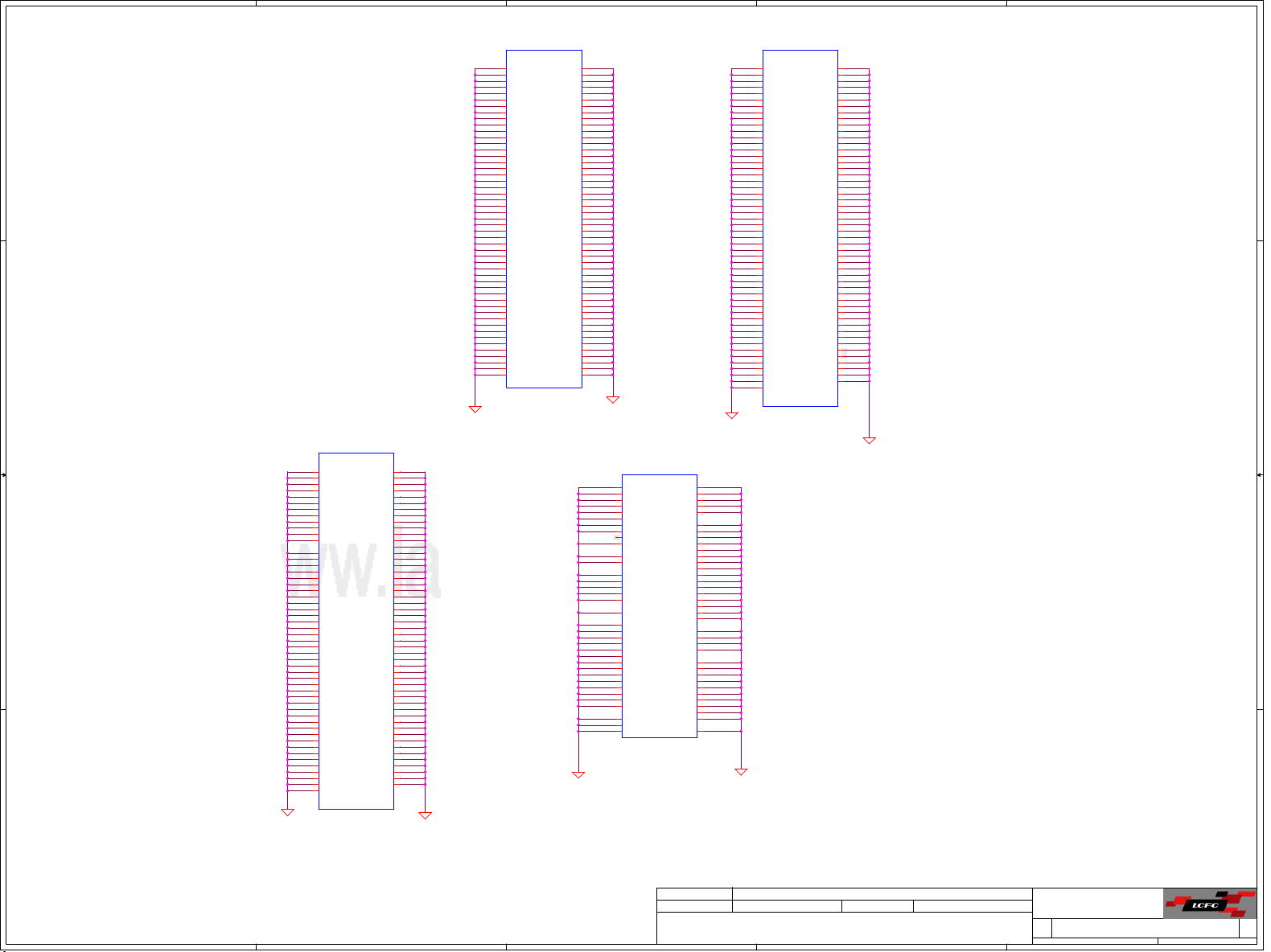

1 OF 13

2

4

DDRA_DQ[63:0] 14

DDRA_MA[15:0] 14

DDRA_DQS[7:0] 14

DDRA_DQS#[7:0] 14

DDRA_DM[7:0] 14

DDR3_M0_DQ_63UC1A

DDR3_M0_DQ _63

DDR3_M0_DQ _62

DDR3_M0_DQ _61

DDR3_M0_DQ _60

DDR3_M0_DQ _59

DDR3_M0_DQ _58

DDR3_M0_DQ _57

DDR3_M0_DQ _56

DDR3_M0_DQ _55

DDR3_M0_DQ _54

DDR3_M0_DQ _53

DDR3_M0_DQ _52

DDR3_M0_DQ _51

DDR3_M0_DQ _50

DDR3_M0_DQ _49

DDR3_M0_DQ _48

DDR3_M0_DQ _47

DDR3_M0_DQ _46

DDR3_M0_DQ _45

DDR3_M0_DQ _44

DDR3_M0_DQ _43

DDR3_M0_DQ _42

DDR3_M0_DQ _41

DDR3_M0_DQ _40

DDR3_M0_DQ _39

DDR3_M0_DQ _38

DDR3_M0_DQ _37

DDR3_M0_DQ _36

DDR3_M0_DQ _35

DDR3_M0_DQ _34

DDR3_M0_DQ _33

DDR3_M0_DQ _32

DDR3_M0_DQ _31

DDR3_M0_DQ _30

DDR3_M0_DQ _29

DDR3_M0_DQ _28

DDR3_M0_DQ _27

DDR3_M0_DQ _26

DDR3_M0_DQ _25

DDR3_M0_DQ _24

DDR3_M0_DQ _23

DDR3_M0_DQ _22

DDR3_M0_DQ _21

DDR3_M0_DQ _20

DDR3_M0_DQ _19

DDR3_M0_DQ _18

DDR3_M0_DQ _17

DDR3_M0_DQ _16

DDR3_M0_DQ _15

DDR3_M0_DQ _14

DDR3_M0_DQ _13

DDR3_M0_DQ _12

DDR3_M0_DQ _11

DDR3_M0_DQ _10

DDR3_M0_DQ _9

DDR3_M0_DQ _8

DDR3_M0_DQ _7

DDR3_M0_DQ _6

DDR3_M0_DQ _5

DDR3_M0_DQ _4

DDR3_M0_DQ _3

DDR3_M0_DQ _2

DDR3_M0_DQ _1

DDR3_M0_DQ _0

DDRA_DRAMRST#_R

3

DDRB_DQ[63:0] 15

DDRB_MA[15:0] 15

DDRB_DQS[7:0] 15

DDRB_DQS#[7:0] 15

DDRB_DM[7:0] 15

DDRA_DQ55

BG33

DDRA_DQ54

BH28

DDRA_DQ53

BJ29

DDRA_DQ52

BG28

DDRA_DQ51

BG32

DDRA_DQ50

BH34

DDRA_DQ49

BG29

DDRA_DQ48

BJ33

DDRA_DQ63

BD28

DDRA_DQ62

BF30

DDRA_DQ61

BA34

DDRA_DQ60

BD34

DDRA_DQ59

BD30

DDRA_DQ58

BA32

DDRA_DQ57

BC34

DDRA_DQ56

BF34

DDRA_DQ47

AV32

DDRA_DQ46

AV34

DDRA_DQ45

BD36

DDRA_DQ44

BF36

DDRA_DQ43

AU32

DDRA_DQ42

AU34

DDRA_DQ41

BA36

DDRA_DQ40

BC36

DDRA_DQ39

BH38

DDRA_DQ38

BH36

DDRA_DQ37

BJ41

DDRA_DQ36

BH42

DDRA_DQ35

BJ37

DDRA_DQ34

BG37

DDRA_DQ33

BG43

DDRA_DQ32

BG42

DDRA_DQ31

BB51

DDRA_DQ30

AW53

DDRA_DQ29

BC52

DDRA_DQ28

AW51

DDRA_DQ27

AV51

DDRA_DQ26

BC53

DDRA_DQ25

AV52

DDRA_DQ24

BD52

DDRA_DQ15

AV42

DDRA_DQ14

AP41

DDRA_DQ13

AV41

DDRA_DQ12

AT44

DDRA_DQ11

AP40

DDRA_DQ10

AT38

DDRA_DQ9

AP42

DDRA_DQ8

AT40

DDRA_DQ23

AV45

DDRA_DQ22

AY50

DDRA_DQ21

AT50

DDRA_DQ20

AP47

DDRA_DQ19

AV50

DDRA_DQ18

AY48

DDRA_DQ17

AT47

DDRA_DQ16

AP48

DDRA_DQ7

AP51

DDRA_DQ6

AR53

DDRA_DQ5

AK52

DDRA_DQ4

AL53

DDRA_DQ3

AR51

DDRA_DQ2

AT52

DDRA_DQ1

AL51

DDRA_DQ0

AK51

?

Group 6

Group 7

Group 5

Group 4

Group 3

Group 1

Group 2

Group 0

Del CS_2(chip select: 1 per Rank)

Del CKE_2(chip select: 1 per Rank)

DDR_CORE_PWROK55

12

RC35

182_0402_1%

INTEL PDG 182 ohm

For dual rank

DDRB_BS2#

15

DDRB_BS1#

15

DDRB_BS0#

15

DDRB_CAS#

15

DDRB_RAS#

15

DDRB_WE#

15

DDRB_CS0#

15

DDRB_CLK015

DDRB_CLK0#15

DDRB_CKE015

DDRB_ODT015

M1_RCOMPPD

DDRB_DRAMRST#15

DDRB_DRAMRST#_R

DDR_CORE_PWROK

DDRB_MA15

DDRB_MA14

DDRB_MA13

DDRB_MA12

DDRB_MA11

DDRB_MA10

DDRB_MA9

DDRB_MA8

DDRB_MA7

DDRB_MA6

DDRB_MA5

DDRB_MA4

DDRB_MA3

DDRB_MA2

DDRB_MA1

DDRB_MA0

DDRB_DM7

DDRB_DM6

DDRB_DM5

DDRB_DM4

DDRB_DM3

DDRB_DM2

DDRB_DM1

DDRB_DM0

DDRB_DQS7

DDRB_DQS#7

DDRB_DQS6

DDRB_DQS#6

DDRB_DQS5

DDRB_DQS#5

DDRB_DQS4

DDRB_DQS#4

DDRB_DQS3

DDRB_DQS#3

DDRB_DQS2

DDRB_DQS#2

DDRB_DQS1

DDRB_DQS#1

DDRB_DQS0

DDRB_DQS#0

2

BD5

BD7

BF10

BF6

BB5

BJ9

BE2

BD10

BE8

BB8

BH6

BD12

BH7

BJ6

BC12

BB7

BF2

AY14

BH8

BG9

BA14

BH10

AU16

AY16

BD16

BF16

AY12

BD14

BF14

BB10

AT24

AU24

AV18

BA16

AT26

AU26

BA12

AV26

BA26

BH24

BD22

AY18

BG13

BA1

AP10

AT6

AP2

BH22

BG23

BC24

BC22

AT22

AT20

BH14

BG15

AY2

BA3

AT12

AT13

AV7

AV6

AM2

AM3

BRASWELL_FCBGA151170

REV = 1.2

@

1

2

CHV_MCP_EDS

UC1B

DDR3_M1_MA _15

DDR3_M1_MA _14

DDR3_M1_MA _13

DDR3_M1_MA _12

DDR3_M1_MA _11

DDR3_M1_MA _10

DDR3_M1_MA _9

DDR3_M1_MA _8

DDR3_M1_MA _7

DDR3_M1_MA _6

DDR3_M1_MA _5

DDR3_M1_MA _4

DDR3_M1_MA _3

DDR3_M1_MA _2

DDR3_M1_MA _1

DDR3_M1_MA _0

DDR3_M1_B S_2

DDR3_M1_B S_1

DDR3_M1_B S_0

DDR3_M1_CA S_N

DDR3_M1_RA S_N

DDR3_M1_W E_N

DDR3_M1_CS B_1

DDR3_M1_CS B_0

DDR3_M1_CK _1

DDR3_M1_CK B_1

DDR3_M1_CK E_1

DDR3_M1_CK _0

DDR3_M1_CK B_0

DDR3_M1_CK E_0

RSVD_AT24

RSVD_AU2 4

DDR3_M1_O DT_0

DDR3_M1_O DT_1

DDR3_M1_O CAVREF

DDR3_M1_O DQVREF

DDR3_M1_DR AMRST_N

DDR3_VCCA_ PWROK

DDR3_M1_RC OMPPD

DDR3_M1_DM _7

DDR3_M1_DM _6

DDR3_M1_DM _5

DDR3_M1_DM _4

DDR3_M1_DM _3

DDR3_M1_DM _2

DDR3_M1_DM _1

DDR3_M1_DM _0

DDR3_M1_DQ S_7

DDR3_M1_DQ SB_7

DDR3_M1_DQ S_6

DDR3_M1_DQ SB_6

DDR3_M1_DQ S_5

DDR3_M1_DQ SB_5

DDR3_M1_DQ S_4

DDR3_M1_DQ SB_4

DDR3_M1_DQ S_3

DDR3_M1_DQ SB_3

DDR3_M1_DQ S_2

DDR3_M1_DQ SB_2

DDR3_M1_DQ S_1

DDR3_M1_DQ SB_1

DDR3_M1_DQ S_0

DDR3_M1_DQ SB_0

RC9292

CC144

0.1u_0201_10V6K

@

?

DDR1

2 OF 13

1

0_0402_5%

DDR3_M0_DQ_63

DDR3_M1_DQ _63

DDR3_M1_DQ _62

DDR3_M1_DQ _61

DDR3_M1_DQ _60

DDR3_M1_DQ _59

DDR3_M1_DQ _58

DDR3_M1_DQ _57

DDR3_M1_DQ _56

DDR3_M1_DQ _55

DDR3_M1_DQ _54

DDR3_M1_DQ _53

DDR3_M1_DQ _52

DDR3_M1_DQ _51

DDR3_M1_DQ _50

DDR3_M1_DQ _49

DDR3_M1_DQ _48

DDR3_M1_DQ _47

DDR3_M1_DQ _46

DDR3_M1_DQ _45

DDR3_M1_DQ _44

DDR3_M1_DQ _43

DDR3_M1_DQ _42

DDR3_M1_DQ _41

DDR3_M1_DQ _40

DDR3_M1_DQ _39

DDR3_M1_DQ _38

DDR3_M1_DQ _37

DDR3_M1_DQ _36

DDR3_M1_DQ _35

DDR3_M1_DQ _34

DDR3_M1_DQ _33

DDR3_M1_DQ _32

DDR3_M1_DQ _31

DDR3_M1_DQ _30

DDR3_M1_DQ _29

DDR3_M1_DQ _28

DDR3_M1_DQ _27

DDR3_M1_DQ _26

DDR3_M1_DQ _25

DDR3_M1_DQ _24

DDR3_M1_DQ _23

DDR3_M1_DQ _22

DDR3_M1_DQ _21

DDR3_M1_DQ _20

DDR3_M1_DQ _19

DDR3_M1_DQ _18

DDR3_M1_DQ _17

DDR3_M1_DQ _16

DDR3_M1_DQ _15

DDR3_M1_DQ _14

DDR3_M1_DQ _13

DDR3_M1_DQ _12

DDR3_M1_DQ _11

DDR3_M1_DQ _10

DDR3_M1_DQ _9

DDR3_M1_DQ _8

DDR3_M1_DQ _7

DDR3_M1_DQ _6

DDR3_M1_DQ _5

DDR3_M1_DQ _4

DDR3_M1_DQ _3

DDR3_M1_DQ _2

DDR3_M1_DQ _1

DDR3_M1_DQ _0

2

BG21

BH26

BJ25

BG26

BG22

BH20

BG25

BJ21

BD26

BF24

BA20

BD20

BD24

BA22

BC20

BF20

AV22

AV20

BD18

BF18

AU22

AU20

BA18

BC18

BH16

BH18

BJ13

BH12

BJ17

BG17

BG11

BG12

BB3

AW1

BC2

AW3

AV3

BC1

AV2

BD2

AV12

AP13

AV13

AT10

AP14

AT16

AP12

AT14

AV9

AY4

AT4

AP7

AV4

AY6

AT7

AP6

AP3

AR1

AK2

AL1

AR3

AT2

AL3

AK3

?

DDRB_DRAMRST#_R

1

DDRB_DQ63

DDRB_DQ62

DDRB_DQ61

DDRB_DQ60

DDRB_DQ59

DDRB_DQ58

DDRB_DQ57

DDRB_DQ56

DDRB_DQ55

DDRB_DQ54

DDRB_DQ53

DDRB_DQ52

DDRB_DQ51

DDRB_DQ50

DDRB_DQ49

DDRB_DQ48

DDRB_DQ47

DDRB_DQ46

DDRB_DQ45

DDRB_DQ44

DDRB_DQ43

DDRB_DQ42

DDRB_DQ41

DDRB_DQ40

DDRB_DQ39

DDRB_DQ38

DDRB_DQ37

DDRB_DQ36

DDRB_DQ35

DDRB_DQ34

DDRB_DQ33

DDRB_DQ32

DDRB_DQ31

DDRB_DQ30

DDRB_DQ29

DDRB_DQ28

DDRB_DQ27

DDRB_DQ26

DDRB_DQ25

DDRB_DQ24

DDRB_DQ23

DDRB_DQ22

DDRB_DQ21

DDRB_DQ20

DDRB_DQ19

DDRB_DQ18

DDRB_DQ17

DDRB_DQ16

DDRB_DQ14

DDRB_DQ13

DDRB_DQ12

DDRB_DQ11

DDRB_DQ10

DDRB_DQ9

DDRB_DQ8

DDRB_DQ7

DDRB_DQ6

DDRB_DQ5

DDRB_DQ4

DDRB_DQ3

DDRB_DQ2

DDRB_DQ1

DDRB_DQ0

+3VALW +1.35V

12

RC9296

10K_0402_5%

@

34

D

5

QC5B

G

2N7002KDWH_SOT363-6

@

S

61

D

2

VDDQ_PGOOD55

1

A A

2

@

5

G

CC3

0.1u_0201_10V6K

QC5A

2N7002KDWH_SOT363-6

@

S

RC9298

1 2

0_0402_5%

12

RC9297

10K_0402_5%

1

CC1

0.1u_0201_10V6K

2

@

4

DDR_PWROK

12

RC9293

10K_0402_5%

@

34

D

5

G

QC10B

2N7002KDWH_SOT363-6

S

61

D

SYS_PWROK7,44

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING

THIS SHEET OF ENGINEERING DRAWING

THIS SHEET OF ENGINEERING DRAWING

AND TRADE SECRETINFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRETINFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRETINFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENTEXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENTEXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

1

CC19

0.1u_0201_10V6K

2

CD@

2

G

QC10A

2N7002KDWH_SOT363-6

S

@

2015/10/08

2015/10/08

2015/10/08

IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

3

@

LC Future Center Sec ret Data

LC Future Center Sec ret Data

LC Future Center Sec ret Data

Deciphered Date

Deciphered Date

Deciphered Date

+1.35V+3VALW

12

RC9294

10K_0402_5%

DDR_CORE_PWROK

1

CC18

0.1u_0201_10V6K

2

2

2015/03/23

2015/03/23

2015/03/23

Title

Title

Title

SOC(DDR3L)

SOC(DDR3L)

SOC(DDR3L)

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

CGx20

CGx20

CGx20

Friday, December 11, 2015

Friday, December 11, 2015

Friday, December 11, 2015

of

5 57

of

5 57

of

5 57

1

1.01.0

5

D D

CC103 0.1u_0201_10V6K

PCIE_PTX_C_DRX_P440

WLAN

LAN

C C

PCIE_PTX_C_DRX_N440

PCIE_PRX_DTX_P440

PCIE_PRX_DTX_N440

PCIE_PTX_C_DRX_P337

PCIE_PTX_C_DRX_N337

PCIE_PRX_DTX_P337

PCIE_PRX_DTX_N337

1 2

CC104 0.1u_0201_10V6K

1 2

CC106 0.1u_0201_10V6K

1 2

0.1u_0201_10V6K

1 2

CC105

CLK_PCIE_WLAN40

CLK_PCIE_WLAN#40

CLK_PCIE_LAN37

CLK_PCIE_LAN#37

PCIE_PTX_DRX_P4

PCIE_PTX_DRX_N4

PCIE_PRX_DTX_P4

PCIE_PRX_DTX_N4

PCIE_PTX_DRX_P3

PCIE_PTX_DRX_N3

PCIE_PRX_DTX_P3

PCIE_PRX_DTX_N3

GPU_CLKREQ#_Q

PCIE_CLKREQ_2#

WLAN_CLKREQ#_Q

LAN_CLKREQ#_Q

CLK_PCIE_WLAN

CLK_PCIE_WLAN#

CLK_PCIE_LAN

CLK_PCIE_LAN#

PCIE_RCOMP_DP

PCIE_RCOMP_DN

4

C24

B24

G20

J20

A25

C25

D20

F20

B26

C26

D22

F22

A27

C27

G24

J24

AM10

AM12

AK14

AM14

A21

C21

C19

B20

C18

B18

C17

A17

C16

B16

D26

F26

V14

Y13

Y12

V13

V12

UC1D

PCIE_TXP0

PCIE_TXN0

PCIE_RXP0

PCIE_RXN0

PCIE_TXP1

PCIE_TXN1

PCIE_RXP1

PCIE_RXN1

PCIE_TXP2

PCIE_TXN2

PCIE_RXP2

PCIE_RXN2

PCIE_TXP3

PCIE_TXN3

PCIE_RXP3

PCIE_RXN3

PCIE_CLKREQ0_N

PCIE_CLKREQ1_N

PCIE_CLKREQ2_N

PCIE_CLKREQ3_N

CLK_DIFF_P_0

CLK_DIFF_N_0

CLK_DIFF_P_1

CLK_DIFF_N_1

CLK_DIFF_P_2

CLK_DIFF_N_2

CLK_DIFF_P_3

CLK_DIFF_N_3

RSVD_C16

RSVD_B16

PCIE_RCOMP_P

PCIE_RCOMP_N

SPI1_CLK

SPI1_CS0_N

SPI1_CS1_N

SPI1_MISO

SPI1_MOSI

ELL_FCBGA151170

BRASW

@

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P0

V1P8

V1P8

V1P8

V1P8

V1P8

PCIe

SPI

CHV_MCP_EDS

V1P8

V1P8

V1P8

V1P8

?

DDR3_M0_DQ_63

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

SATA

V1P8

V1P8

V1P8

V1P8

SATA_GP2/SATA_DEVSLP0

V1P8

SATA_GP3/SATA_DEVSLP1

SATA_RCOMP_P

SATA_RCOMP_N

V1P8

V1P8

FST_SPI_CS0_N

V1P8

FST_SPI_CS1_N

V1P8

FST_SPI_CS2_N

V1P8

V1P8

FAST SPI

V1P8

V1P8

V1P5

MF_HDA_RST_N

V1P5

V1P5

V1P5

V1P5

V1P5

V1P5

MF_HDA_DOCKEN_N

V1P5

MF_HDA_DOCKRST_N

AUDIO

GP_SSP_2_CLK

GP_SSP_2_TXD

GP_SSP_2_RXD

REV = 1.2

SATA_TXP0

SATA_TXN0

SATA_RXP0

SATA_RXN0

SATA_TXP1

SATA_TXN1

SATA_RXP1

SATA_RXN1

SATA_LED_N

SATA_GP0

SATA_GP1

FST_SPI_CLK

FST_SPI_D0

FST_SPI_D1

FST_SPI_D2

FST_SPI_D3

MF_HDA_SDI1

MF_HDA_CLK

MF_HDA_SDI0

MF_HDA_SYNC

MF_HDA_SDO

V1P8

SPKR

GP_SSP_2_FS

4 OF 13

3

SATA_PTX_DRX_P0

C31

SATA_PTX_DRX_N0

B30

SATA_PRX_DTX_P0

N28

SATA_PRX_DTX_N0

M28

SATA_PTX_DRX_P1

C29

SATA_PTX_DRX_N1

A29

SATA_PRX_DTX_P1

J28

SATA_PRX_DTX_N1

K28

AH3

AH2

AG3

AG1

3

AF

SATA_RCOMP_DP

N30

SATA_RCOMP_DN

M30

PCH_SPI_CLK_R

W3

PCH_SPI_CS0#_R

V4

V6

V7

PCH_SPI_D0_R

V2

PCH_SPI_D1_R

V3

PCH_SPI_D2_R

U1

PCH_SPI_D3_R

U3

HDA_RST_AUDIO#_R

AF13

AD6

HDA_BITCLK_AUDIO_R

AD9

AD7

HDA_SYNC_AUDIO_R

AF12

HDA_SDOUT_AUDIO_R

AF14

9

AB

AB7

H4

AK9

AK10

AK12

AK13

RC39

1 2

75_0402_1%

RC40

1 2

75_0402_1%

1 2

RC42 75_0402_1%

1 2

RC43 75_0402_1%

SATA_PTX_DRX_P0 42

SATA_PTX_DRX_N0

SATA_PRX_DTX_P0 42

SATA_PRX_DTX_N0

SATA_PTX_DRX_P1 42

SATA_PTX_DRX_N1

SATA_PRX_DTX_P1 42

SATA_PRX_DTX_N1

12

RC13410_0402_1%

12

RC13533_0402_5%

12

RC13010_0402_1%

12

RC13110_0402_1%

12

RC13210_0402_1%

12

RC13310_0402_1%

HDA_RST_AUDIO# 43

HDA_BITCLK_AUDIO 43

HDA_SDIN0 43

HDA_SYNC_AUDIO

HDA_SDOUT_AUDIO 43

PCH_BEEP 43

HDD

42

42

42

ODD

42

EC_SPI_CLK 44

EC_SPI_CS0# 44

EC_SPI_D0 44

EC_SPI_D1 44

EC_SPI_D2 44

EC_SPI_D3 44

2

+1.8VALW

RPC1

WLAN_CLKREQ#_Q

45

PCIE_CLKREQ_2#

36

GPU_CLKREQ#_Q

27

LAN_CLKREQ#_Q

18

10K_0804_8P4R_5%

LAN_CLKREQ#_Q

2N7002KDWH_SOT363-6

LAN_CLKREQ#_Q LAN_CLKREQ#

D

QC22B

2N7002KDWH_SOT363-6

RC19 0_0402_5%

@

34

S

QC22A

1 2

5

G

+3VS

RC11

10K_0402_5%

1 2

61

D

S

1

@

@

2

G

LAN_CLKREQ# 37

LAN_CLKREQ# is OD,Can pull high to 1.8V

+3VS

RC3

QC8A

5

G

10K_0402_5%

1 2

61

D

S

2

G

WLAN_CLKREQ# 40

43

WLAN_CLKREQ#_Q

34

2N7002KDWH_SOT363-6

D

QC8B

S

2N7002KDWH_SOT363-6

+1.8VALW

PCH_SPI_CS0#

PCH_SPI_D1

PCH_SPI_D2

PCIE_RCOMP_DP

PCIE_RCOMP_DN

@

1 2

RC84

0_0402_5%

UC2

1

CS#

2

DO

3

WP#

4

GND

W25Q64FVSSIQ_SO8

0605

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_D0

PCH_SPI_D1

PCH_SPI_D2

PCH_SPI_D3

1 2

PCH_SPI_CS0#_R

VCC

HOLD#

CLK

DI

RC38

402_0402_1%

8

PCH_SPI_D3

7

PCH_SPI_CLK

6

PCH_SPI_D0

5

50mA

PCH_SPI_CS0# 44

PCH_SPI_CLK 44

PCH_SPI_D0 44

PCH_SPI_D1 44

PCH_SPI_D2 44

PCH_SPI_D3 44

4

+VCC_SPI

2

1

CC8

0.1u_0201_10V6K

fication

fication

Security Cl assi

Security Cl assi

Security Cl assi

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USE

MAY BE USE

MAY BE USE

fication

Issued Date

Issued Date

Issued Date

D BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

D BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

D BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2015/10/08

2015/10/08

2015/10/08

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2015/03/23

2015/03/23

2015/03/23

Title

Title

Title

SOC (PCIE&HDA&SPI&SATA)

SOC (PCIE&HDA&SPI&SATA)

SOC (PCIE&HDA&SPI&SATA)

Size Document Nu m

Size Document Nu m

Size Document Nu m

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

ber Rev

ber Rev

ber Rev

CGx20

CGx20

Tuesday, December 08, 2015

Tuesday, December 08, 2015

Tuesday, December 08, 2015

CGx20

1

6 57

6 57

6 57

of

of

of

1.01.0

SATA_RCOMP_DP

RC30

402_0402_1%

1 2

+VCC_SPI

PCH_SPI_CS0#

@

+3VALW

+VCC_SPI

SATA_RCOMP_DN

1 2

RC94

0_0402_5%

1 2

RC20

100K_0402_5%

B B

A A

SPI ROM

5

5

32.768K need

SERIRQ 32,44

UC1G

TCK

V1P8

TDI

V1P8

TDO

V1P8

TMS

P8

V1

JTAG/ITP

TRST_N

V1P8

CX_PRDY_N

CX_PREQ_N

RSVD_M13

MF_LPC_CLKO

MF_LPC_CLKO

_N

LPC_CLKRUN

LPC_FRAME_N

MF_LPC_AD0

MF_LPC_AD1

MF_LPC_AD2

MF_LPC_AD3

LPC_HVT_RCOMP

ILB_SERIRQ

V1P8

RSVD_H5

RSVD_H7

RSVD_P28

RSVD_P30

RSVD_AF50

RSVD_AF48

RSVD_AF44

Reserved

RSVD_AF45

PROCHOT_N

BRASWELL_FCBGA151170

REV = 1.2

VCC_AXG_SENSE

UNCORE_VSS_SENSE

CHV_MCP_ED S

UT0

V3P3

UT1

V3P3

V3P3

V3P3

V1P8

V3P3

LPC

V3P3

V3P3

V3P3

V1P8

as in tel EDS New request

?

V3P3

V3P3

V1P8

V1P8

V1P8

V1P8

V1P8

PMU_RESETBUTTON_N

PMU

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

D

V1P8

V1P8

SVI

V1P8

CORE_VCC0_SENSE

CORE_VSS0_SENSE

CORE_VCC1_SE

CORE_VSS1_SE

UNCORE_VSS_

Voltage sense

UNCORE_VSS_

7 OF 13

+1.8VALW +1.8VALW+3VALW

RC96

0_0402_5%

1 2

UC3

1

VCCA

VCCB

D D

SOC_SERIRQ

0.1u_0201_10V6K

SERIRQ level

C C

2

GND

A43B4

1

CC15

TPM@

SOC_SERIRQ

G2129TL1U_SC70-6

TPM@

2

NTPM@

1 2

RC33

shift need IC, not MOS for freq uence

PCH_PCI_CLK

_R

1

C4932

0.1U_0201_6.3V6-K

2

EMC_NS@

CLK_PCI_EC44

CLK_PCI_TPM32

LPC_FRAME#32,44

LPC_AD032,44

LPC_AD132,44

LPC_AD232,44

LPC_AD332,44

SOC_SERIRQ

1

TP13 @

1

TP14 @

1

TP15 @

1

TP16 @

1

TP17 @

1

TP18 @

1

TP19 @

1 2

RC80 0_0402_5%

1 2

RC81 0_0402_5%

TPM@

100_0402_1%

RC104

+1.8VALW

RC48

20K_0402_5%

@

RC65

1 2

10K_0402_5%

1 2

CPU_VCC_SENSE

CPU_VSS_SENSE

H_PROCHOT#44,55

+CPU_CORE +GFX_CORE

12

RC12 100_0402_1%

12

RC13 100_0402_1%

RTC_INTRUDER

RC98

RC97

10K_0402_5%

0_0402_5%

TPM@

1 2

1 2

6

5

EO

4

1

CC16

0.1u_0201_10V6K

2

TPM@

SERIRQ

0_0402_5%

XDP_TCLK

AF42

XDP_TDI

AD47

XDP_TDO

AF40

XDP_TMS

AD48

XDP_TRST#

AB48

XDP_PRDY#

5

AD4

XDP_PREQ#

AF41

M13

PCH_PCI_CLK_R

P2

R3

T3

P3

M3

M2

3

N

1

N

RCOMP_LPC_HVT

1 2

H_PROCHOT# PCH_SMB_CLK

AF50

A

A

A

AD50

12

RC28 100_0402_1%

12

RC29 100_0402_1%

T4

T2

H5

H7

P28

P30

F48

F44

F45

@

change to SJ10000IM00,

1 2

RC92 10M_0402_5%

RTC_X1

YC1

1 2

32.768KHZ_9PF_X1A000141000200

2

CC11

7P_0402_50V8-B

1

CRYST AL

1,Space 15MIL

2,No trace under crystal

3,place on oppsosit side of MCP for temp influence

DDR3_M0_DQ_63

RTC

RSVD_VSS_G18

SUSPWRDNACK

PMU_SLP_S4_N

PMU_SLP_S3_N

PMU_PLTRST_N

PMU_BATLOW_N

PMU_AC_PRESENT

PMU_SLP_S0IX_N

PMU_SLP_LAN_

PMU_WAKE_N

PMU_PWRBTN_N

PMU_WAKE_LAN

SVID0_ALERT_N

DDI_VGG_SENSE

RTC_X1

RTC_X2

RTC_EXTPAD

RTC_RST_N

COREPWROK

RSMRST_N

RTC_TEST_N

SUS_STAT_N

PMU_SUSCLK

SVID0_CLK

SVID0_DATA

SENSE_2

SENSE_1

RTC_X1

M18

RTC_X2

K18

BVCCRTC_EXTPAD

F16

RTC_RST#

D18

SYS_PWROK

G16

EC_RSMRST#

F18

SRTC_RST#

J16

RTC_INTRUDER

G18

PMC_SUSWARN#

AE3

D14

PMC_SUSCLK

C15

PM_SLP_S4#

C12

PM_SLP_S3#

B14

PMC_RSTBTN#

AF2

PMC_PLTRST#

F14

PMC_BATLOW#

C14

PMC_ACIN

C13

PMC_SLP_S0IX#

13

A

PMU_SLP_LAN#

B12

PMC_PCIE_WAKE#

N

N16

PBTN_OUT#

M16

PMC_LAN_WAKE#

P18

_N

AD42

AD41

AD4

0

VCC0_SENSE

AG32

VSS0_SENSE

AJ32

VCC1_SENSE

AD29

VSS1_SENSE

NSE

AF27

VCC_AXG_SENSE

NSE

D24

A

UNCORE_VSS_SENSE

AD22

VNN_SENSE

AC27

?

RTC_X2

2

CC12

7P_0402_50V8-B

1

CC17

1

TP5@

1 2

RC72 20K_0402_1%

1 2

RC9284

0_0402_5%

VCC0_SENSE

VSS0_SENSE

VCC1_SENSE

VSS1_SENSE

CPU_SVID_ALERT#

4

1,Spec. request 19.2MHz, Cp=12pf, RC=200K

XTAL19_IN

1 2

RC93 200K_0402_5%

YC2

1

OSC1

1

NC12OSC2

CC13

27P_0402_50V8J

19.2MHZ_12PF_7V19200001

2

CC140

SYS_PWROK

1 2

0.1u_0201_10V6K

EMC@

0.1u_0201_10V6K

1 2

RTC_RST# 44

SYS_PWROK 5,44

EC_RSMRST# 44

PMC_PLTRST# 32,37,40,44

+1.8VALW

1

TP4@

1

TP20@

1

TP21@

CPU_SVID_CLK

CPU_SVID_DAT

CPU_SVID_ALERT#

VCC_AXG_SENSE 57

UNCORE_VSS_SENSE 57

VNN_SENSE 55

RPC5

1 4

2 3

RPC6

1 4

2 3

RC66

1 2

CPU_SVID_ALERT#

100_0404_4P2R_1%

100_0404_4P2R_1%

200_0402_1%

CPU_SVID_CLK

CPU_SVID_DAT

CPU_VCC_SENSE

CPU_VSS_SENSE

4

NC2

3

56,57

56,57

56,57

+1.05VA_SOC_G3

change from

XTAL19_OUT

1

CC14

27P_0402_50V8J

2

2.49K_0402_1%

EC_SCI#12,44

CPU_VCC_SENSE 56

CPU_VSS_SENSE 56

1.05VA for layo ut

RTC

RST#

XTAL19_IN

XTAL19_OUT

RC45

12

12

RC4449.9_0402_1%

1

TP23 @

1

TP22 @

GPIO_SUS_012

GPIO_SUS_112

GPIO_SUS_212

1

@

TP24

GPIO_SUS_412

GPIO_SUS_512

EC_SMI#

GPIO_SUS_912

GPIO_SUS_812

1

@

TP25

12

RC108 100_0402_1%

3

RESERVED

I2C

V1P8

V1P8

V1P8

V1P8

SMBUS

V1P8

RSVD_C11

RSVD_B10

RSVD_F12

RSVD_F10

RSVD_D12

RSVD_J12

RSVD_J14

RSVD_L13

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

V1P8

RSVD_AA3

MF_SMB_CLK

MF_SMB_DATA

MF_SMB_ALER

VCCRTC

RSVD_E8

RSVD_C7

RSVD_D6

RSVD_F7

I2C0_SCL

I2C0_SDA

I2C1_SCL

I2C1_SDA

I2C2_SCL

I2C2_SDA

I2C3_SCL

I2C3_SDA

I2C4_SCL

I2C4_SDA

I2C5_SCL

I2C5_SDA

I2C6_SCL

I2C6_SDA

RSVD_Y2

PCH_SMB_CLK_Q

C11

B10

2

F1

0

F1

D12

E8

C7

PCH_SMB_DATA_Q

D6

2

J1

F7

J14

L1

3

AK6

AH7

AF6

AH6

AF9

AF7

AE4

AD2

AC1

AD3

PCH_CMOS_ON#_Q

AB2

AC3

AA1

AB3

AA

3

Y2

AM6

PCH_SMB_DATA

AM7

PCH_SMB_ALERT#

AM9

T_N

?

SRTC_RST#

RTC_RST#

1U_0402_6.3V6K

1

CC9

2

UC1E

P24

OSCIN

M22

OSCOUT

6

J2

RSVD_J26

6

N2

ICLK_ICOMP

RSVD_N26

P20

ICLK_RCOMP

ICLKICOMP

N20

ICLKRCOMP

P26

RSVD_P26

K26

RSVD_K26

M26

RSVD_M26

A

H45

RSVD_AH45

A9

MF_PLT_CLK0

C9

MF_PLT_CLK1

B8

MF_PLT_CLK2

B7

MF_PLT_CLK3

B5

MF_PLT_CLK4

B4

MF_PLT_CLK5

AM40

GPIO_DFX0

AM41

PCB_ID0

GPIO_DFX1

AM44

PCB_ID1

GPIO_DFX2

AM45

PCB_ID2

GPIO_DFX3

AM47

PCB_ID3

GPIO_DFX4

AK48

PCB_ID4

GPIO_DFX5

AM48

PCB_ID5 PCB_ID4

GPIO_DFX6

AK41

XDP_GPIO_DFX8

KBRST#

GPIO_RCOMP18

AK42

AD51

AD52

AH50

AH48

AH51

AH52

AG51

AG53

2

AF5

1

AF5

1

AE5

1

AC5

0

AH4

Y3

@

GPIO_DFX7

GPIO_DFX8

GPIO_SUS0

GPIO_SUS1

GPIO_SUS2

GPIO_SUS3

GPIO_SUS4

GPIO_SUS5

GPIO_SUS6

GPIO_SUS7

SEC_GPIO_SUS9

SEC_GPIO_SUS8

SEC_GPIO_SUS10

SEC_GPIO_SUS11

GPIO0_RCOMP

GPIO_ALERT

RASWELL_FCBGA151170

B

REV = 1.2

RC89 20K_0402_1%

RC90 20K_0402_1%

1U_0402_6.3V6K

CC10

1

2

?

CHV_MCP_ED S

iCLK

V1P8

V1P8

V1P8

V1P8

V1P8

PLTFM CLK's

V1P8

GPIO_DFX

GPIO_SUS

5 OF 13

1 2

1 2

12

JCMOS1

SHORT PADS

@

JCMOS/ JCMOS1

Place under Bottom

RTCRST #

Space 15Mil

DDR3_M0_DQ_63

Internal 20K(H)

2

PCH_SMB_CLK

PCH_SMB_DATA

6 1

@

2N7002KDWH_SOT363-6

RPC22

2.2K_0404_4P2R_5%

1 4

2 3

QC20B

PJT138K_SOT363-6

@

3 4

@

2N7002KDWH_SOT363-6

2

G

QC6A

S

D

1 2

RC124 0_0402_5%

@

+1.8VALW

2

QC20A

PJT138K_SOT363-6

@

G2 5

D2 3S24

+3VS

5

G

QC6B

S

D

1 2

RC123 0_0402_5%

@

+3VALW+1.8VALW

RPC23

2.2K_0404_4P2R_5%

1 4

2 3

@

G1

PCH_SMB_CLK_Q

D1 6S11

PCH_SMB_DATA_Q

SMB_CLK_S3 40

SMB_DATA_S3 40

PCB ID

X X X X

0

X X X X

1

0

X

X

X

X

X

X

X

X

X

X

X

X

1

PMC_PLTRST#

PCH_SMB_ALERT#

PMC_RSTBTN#

PMC_SUSWARN#

PMC_SUSCLK

EC_RSMRST#

EC_RSMRST#

PMC_SUSWARN#

SMB_CLK_S3

SMB_DATA_S3

@

15@

RC58

RC59

1 2

1 2

2.2K_0402_5%

2.2K_0402_5%

PCB_ID0

PCB_ID1

PCB_ID2

PCB_ID3

PCB_ID5

@

14@

RC62

RC64

1 2

1 2

2.2K_0402_5%

2.2K_0402_5%

PCB_ID3PCB_ID2PCB_ID1PCB_ID0 Description

PCB_ID4 PCB_

X X X

X X X1

0 0 1

00 1

1 1

0

1 00

0 11

RC70

10K_0402_5%

RC120

10K_0402_5%

1 2

RC73 10K_0402_5%

RC71

1 2

1 2

RC83 10K_0402_5%@

RC930 100K_0402_5%

CC132

@

1 2

RC75

1 2

RPC29

@

2.2K_0404_4P2R_5%

+1.8VALW

@

RC949

RC948

1 2

2.2K_0402_5%

@

RC951

RC950

1 2

2.2K_0402_5%

ID5

Reserve

14''

Reserve

15'' SKU

Reserve

single channel DRAM CHA@

Reserve

dual chanel DRAM CHA@ and CHB@

Reserve

Samsung 4G(K4B4G1646E-BYK0)

Reserve

Hynix 4G(H5TC4G63CFR-PBA)

Reserve

Micron 4G(MT41K256M16TW-107:P)

Hynix 8G(H5TC8G63CMR-PBA)

Reserve

Micron 8G(MT41K512M16HA-125:A)

Reserve

12

@

12

@

100K_0402_5%@

12

0.01U_0201_25V6-K

100K_0402_5%

14

23

@

1 2

2.2K_0402_5%

@

1 2

2.2K_0402_5%

SKU

RC9286

RC9287

+1.8VALW

@

1 2

2.2K_0402_5%

@

1 2

2.2K_0402_5%

+3VS

@

RC9288

1 2

2.2K_0402_5%

@

RC9289

1 2

2.2K_0402_5%

B B

+3VS+3VALW

D2 3

S2

4

5

QC15B

PJT138K_SOT363-6

@

KBRST# 44

PBTN_OUT# 44

12

1 2

RC9300

10K_0402_5%

RC105

100K_0402_5%

PLT_RST# 32,37,40,44

PMC_PCIE_WAKE#

PM_SLP_S3#

PM_SLP_S4#

+1.8VALW

+1.8VALW

3

4

RPC28

10K_0404_4P2R_5%

1 4

2 3

PJA138K_SOT23-3

QC168

D

S

G

2

+1.8VALW

RPC2

10K_0404_4P2R_5%

@

1 4

2 3

EC_SMI#

3

+1.8VALW

RC14

10K_0402_5%

1 2

EC_SMI# 44

PMC_SUSWARN#

12

@

RC22

2.2K_0402_5%

PCH_CMOS_ON#_Q

+1.8VALW

2

G

3

S

QC12

PJA138K_SOT23-3

1

D

@

+3VALW

1

PCIE_WAKE# 40,44

PM_SLP_S3# 44

PM_SLP_S4# 44

12

RC9299

10K_0402_5%

@

G25

QC15A

1

C4937

0.1U_0201_6.3V6-K

2

@

KBRST#

PBTN_OUT#

D1 6S11

2

G1

PJT138K_SOT363-6

@

+1.8VALW

RPC4

10K_0404_4P2R_5%

1 4

2 3

PMC_PLTRST#

A A

+3VS

RC112

10K_0402_5%

@

1 2

CMOS_ON#

QC18

1

D

2

G

S

@

3

PJA138K_SOT23-3

+3VALW

RC23

10K_0402_5%

@

1 2

SUSWARN# 44

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI

THIS SHEET OF ENGINEERING DRAWI

THIS SHEET OF ENGINEERING DRAWI

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPTAS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPTAS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPTAS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USE

MAY BE USE

MAY BE USE

NG IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

NG IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

NG IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

D BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

D BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

D BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2

2015/10/08

2015/10/08

2015/10/08

PMC_SUSCLK

PMC_ACIN

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

12

@

1 2

RC932

2.2K_0402_5%

RC63

10K_0402_5%

@

+1.8VALW

2

G

3

S

QC203

PJA138K_SOT23-3

+1.8VALW

1 2

13

D

S

@

@

1

D

@

RC61

2.2K_0402_5%

QC9

2

G

2N7002KW_SOT323-3

2015/03/23

2015/03/23

2015/03/23

+3VALW

RC933

10K_0402_5%

1 2

SUSCLK 40

2

G

3

1

D

S

QC207

PJA138K_SOT23-3

0605

Title

Title

Title

SOC (RTCI&PM&SM&GPIO)

SOC (RTCI&PM&SM&GPIO)

SOC (RTCI&PM&SM&GPIO)

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Friday, December 11,

Friday, December 11,

Friday, December 11,

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

AC_PRESENT 44

ACIN# 44

CGx20

CGx20

CGx20

2015

2015

2015

7 57

7 57

7 57

1.01.0

5

4

3

2

1

?

CHV_MCP_EDS

C32

D28

C33

D30

C34

G32

C35

G34

D34

C37

D36

M34

M32

C38

G36

N34

B32

F28

A33

F30

B34

J32

A35

J34

F34

A37

F36

B38

J36

P34

BRAS

REV = 1.2

@

+1.8VALW

UC1F

USB3_TXP0

USB3_TXN0

USB3_RXP0

USB3_RXN0

USB3_TXP1

USB3_TXN1

USB3_RXP1

USB3_RXN1

USB3_TXP2

USB3_TXN2

USB3_RXP2

USB3_RXN2

USB3_TXP3

USB3_TXN3

USB3_RXP3

USB3_RXN3

USB3_RCOMP_P

USB3_RCOMP_N

RSVD_C37

RSVD_A37

RSVD_F36

RSVD_D36

RSVD_M34

RSVD_M32

RSVD_C38

RSVD_B38

RSVD_G36

RSVD_J36

RSVD_N34

RSVD_P34

WELL_FCBGA151170

V1P05A

V1P05A

V1P05A

V1P05A

V1P05A

V1P05A

V1P05A

V1P05A

V1P05A

V1P05A

V1P05A

V1P05A

V1P05A

USB3.0

V1P05A

V1P05A

V1P05A

V1P2

V1P2

V1P2

RESERVED

D D

USB30_TX_P041

LEFT USB (3.0)

C C

RC192

402_0402_1%

1 2

USB3_RCOMP_DP

USB3_RCOMP_DN

USB30_TX_N041

USB30_RX_P041

USB30_RX_N041

USB3_RCOMP_DP

USB3_RCOMP_DN

USB30_TX_P0

USB30_TX_N0

USB30_RX_P0

USB30_RX_N0

DDR3_M0_DQ_63

V1P8

USB_OTG_ID

V1P8

USB_DP0

V1P8

USB_DN0

V1P8

USB_DP1

V1P8

USB_DN1

V1P8

USB_DP2

V1P8

USB_DN2

V1P8

USB_DP3

V1P8

USB_DN3

V1P8

USB_DP4

V1P8

USB_DN4

V1P8

USB_OC1_N

USB2.0

V1P8

USB_OC0_N

RSVD_B46

USB_VBUSSNS

USB_RCOMP

USB_HSIC_0_STROBE

USB_HSIC_0_DATA

CUART

USB_HSIC_1_STROBE

V1P2

HSI

USB_HSIC_1_DATA

V1P2

USB_HSIC_RCOMP

V1P8

UART1_TXD

V1P8

UART1_RXD

V1P8

UART1_CTS_B

V1P8

UART1_RTS_B

V1P8

UART2_TXD

V1P8

UART2_RXD

V1P8

UART2_CTS_N

V1P8

UART2_RTS_N

6 OF 13

+1.8VALW

B48

C42

B42

C43

B44

C41

A41

C45

A45

B40

C40

P16

P14

B46

USB_VBUSSNS

B47

USB_RCOMP

A48

M36

N3

6

K38

38

M

USB_HSIC_RCOMP

N38

AD10

AD12

AD13

AD14

Y6

Y7

V9

V10

?

USB20_P0

USB20_N0

USB20_P1

USB20_N1

USB20_P2

USB20_N2

USB20_P3

USB20_N3

USB20_P4

USB20_N4

USB_OC1#

USB_OC0#

1 2

RC16 0_0402_5%

1 2

RC193 113_0402_1%

PDG 112.5 oh

Demo 113 ohm

SD00001KH00

RC9301 45.3_0402_1%@

UART0_TXD

UART0_RXD

only for Wi

+3VALW

USB20_P0 41

USB20_N0 41

USB20_P1 41

USB20_N1 41

USB20_P2 30

USB20_N2 30

USB20_P3 40

USB20_N3 40

USB20_P4 33

USB20_N4 33

USB_OC1# 41

m

1 2

n7 debug port

LEFT USB (3.0)

LEFT USB (2.0)

Card reader (2.0)

BT

Camera

USB_OC1#

USB_OC0#

RPC18

2 3

1 4

10K_0404_4P2R

+1.8VALW

_5%

RPC31

2R_5%

2.2K_0404_4P

B B

UART0_TXD

UART0_RXD

A A

5

@

1 4

2 3

2

G1

D1 6S11

QC11A

PJT138K_SOT363-6

4

4

S2

QC11B

PJT138K_SOT363-6

@

G2 5

D2 3

@

only for Win7 debug port

Security Cl ass

Security Cl ass

Security Cl ass

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAYNOT BE TRANSFERED FROM THE CU STODYOF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE

MAY BE

MAY BE

RPC32

2.2K_0404_4P2R_5%

@

1 4

2 3

UART_TX_DEBUG

UART_RX_DEBUG

ification

ification

ification

Issued Date

Issued Date

Issued Date

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF LC FUTURE CENTER.

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF LC FUTURE CENTER.

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF LC FUTURE CENTER.

3

2015/10/08

2015/10/08

2015/10/08

40

40

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2015/03/23

2015/03/23

2015/03/23

Title

Title

Title

SOC (USB)

SOC (USB)

SOC (USB)

Size Document Nu

Size Document Nu

Size Document Nu

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

mber Rev

mber Rev

mber Rev

CGx20

CGx20

Tuesday, December 08, 2015

Tuesday, December 08, 2015

Tuesday, December 08, 2015

CGx20

1

of

8 57

of

8 57

of

8 57

1.01.0

5

D D

+1.15VA_DDI_G3

C C

4

+CPU_CORE

+1.15VA_SOC_G3

+1.15VA_FUSE_G3

+GFX_CORE

7.7A EDS

UC1H

AF36

CORE_VCC1_3

AG33

CORE_VCC1_7

AG35

CORE_VCC1_8

AG36

CORE_VCC1_9

AG38

CORE_VCC1_10

AJ33

CORE_VCC1_14

AJ36

CORE_VCC1_15

AJ38

CORE_VCC1_16

AF30

CORE_VCC1_2

AG27

CORE_VCC1_4

AG29

CORE_VCC1_5

AG30

CORE_VCC1_6

AJ27

CORE_VCC1_11

AJ29

CORE_VCC1_12

AJ30

CORE_VCC1_13

AF29

CORE_VCC1_1

AD16

DDI_VGG_1

AD18

DDI_VGG_2

AD19

DDI_VGG_3

AF16

DDI_VGG_4

AF18

DDI_VGG_5

AF19

DDI_VGG_6

AF21

DDI_VGG_7

AF22

DDI_VGG_8

AJ19

DDI_VGG_15

AG16

DDI_VGG_9

AG18

DDI_VGG_10

AG19

DDI_VGG_11

AG21

DDI_VGG_12

AG22

DDI_VGG_13

AG24

DDI_VGG_14

AJ21

DDI_VGG_16

AJ22

DDI_VGG_17

AJ24

DDI_VGG_18

AK

24

DDI_VGG_19

30

AK

CORE_V1P15_1

AK

35

CORE_V1P15_2

36

AK

CORE_V1P15_3

29

AM

CORE_V1P15_4

AK33

FUSE_V1P15_2

A

J35

FUSE_V1P15_1

AM19

VCCSRAMGE

AK21

VCCSRAMGEN_1P151

BRASWELL_FCBGA151170

@

N_1P152

?

CHV_MCP_EDS

VCCSRAMS

VCCSRAMS

VCCSRAMS

VCCSRAMS

VCCSRAMS

VCCSRAMS

VCCSRAMS

VCCSRAMS

VCCSRAMS

VCCSRAMS

8 OF 13

3

DDR3_M0_DQ_63

UNCORE_VNN_S4_

UNCORE_VNN_S4_

UNCORE_VNN_S4_

UNCORE_VNN_S4_

UNCORE_VNN_S4_

UNCORE_VNN_S4_

UNCORE_VNN_S4_7

UNCORE_VNN_S4_

UNCORE_VNN_S4_

UNCORE_VNN_S4_10

UNCORE_VNN_S4_

UNCORE_VNN_S4_

UNCORE_VNN_S4_13

UNCORE_VNN_S4_

RSVD_AA30

OCIUN_1P056

OCIUN_1P051

OCIUN_1P052

OCIUN_1P053

OCIUN_1P054

OCIUN_1P055

OCIUN_1P057

OCIUN_1P058

OCIUN_1P059

OCIUN_1P0510

ICLK_GND_OFF_2

ICLK_GND_OFF_1

iCLK

DDR_V1P05A

_G3_1

_G3_4

DDR_V1P05A

DDR_V1P05A_G3_2

DDR_V1P05A

_G3_5

DDRPCIeSATAUSBFUSE

_G3_6

DDR_V1P05A

DDR_V1P05A

_G3_3

A_G3_1

PCIE_V1P05

PCIE_V1P05

A_G3_2

SATA_V1P

05A_G3_2

05A_G3_1

SATA_V1P

A_G3_2

USB3_V1P05

USB3_V1P05A_G3_1

USBSSIC_

V1P05A_G3

FUSE3_V1P05A_G5

FUSE_V1P05A

REV = 1.2

2

AA18

1

AA19

2

AA21

3

AA22

4

AA24

5

AA25

6

AC18

AC19

8

AC21

9

AC22

AC24

11

AC25

12

AD25

AD27

14

AA30

V33

AA32

AA33

AA35

AA36

AC32

Y30

Y32

Y33

Y35

V

19

18

V

AM21

AM33

AM22

AN22

AN32

AM32

V22

V24

U24

U22

V27

U27

V29

N18

U19

_G3

?

+VNN_1.05VA_S4

+1.05VA_SOC_G3

+1.05VA_ICLK_S4

+1.05VA_DDR_G3

+1.05VA_MPHY_G3

+1.05VA_SSIC_G3

1

+CPU_CORE

6.4 A

1

CC41

33P_0402_50V8J

RF_NS@

2

1

CC48

1U_0402_6.3V6K

2

CD@

1

CC54

1U_0402_6.3V6K

2

@

1

CC33

4.7U_0402_6.3V6M

2

CD@

1

CC39

22U_0603_6.3V6-M

2

@

+GFX_CORE

1

2

CD@

1

CC49

1U_0402_6.3V6K

2

1

CC34

4.7U_0402_6.3V6M

2

1

2

CC141

22U_0603_6.3V6-M

Note:Place CAP Back of CPUNote:Place CAP Back of CPU

10uF 0402 change

1

CC35

4.7U_0402_6.3V6M

2

CC139

33P_0402_50V8J

RF_NS@

1

CC44

22U_0603_6.3V6-M

2

to 4.7uF for cost down

1

CC50

1U_0402_6.3V6K

2

@

+1.15VA_SOC +1.15VA_FUSE_G3

RC9279

1 2

4

1

2

1

2

@

0_0603_5%

CC51

1U_0402_6.3V6K

CC45

22U_0603_6.3V6-M

1

CC30

4.7U_0402_6.3V6M

2

Note:Place CAP

+CPU_CORE

1

CC36

22U_0603_6.3V6-M

2

CD@

B B

Note:Place Close of CPU's Edge

+GFX_CORE

1

CC31

4.7U_0402_6.3V6M

2

Back of CPU Note:Place CAP Back of CPU

1

CC37

22U_0603_6.3V6-M

2

CD@

1

CC32

4.7U_0402_6.3V6M

2

1

CC38

22U_0603_6.3V6-M

2

@

11A

1

2

+1.15VA_SOC

A A

+1.15VA_SOC

CC40

22U_0603_6.3V6-M

RC9243

1 2

RC9244

1 2

1

CC138

4.7U_0402_6.3V6M

2

0_0603_5%

1

CC46

1U_0402_6.3V6K

2

CD@

0_0603_5%

1

2

Note:Place CAP Back of CPU

1

4.7U_0402_6.3V6M

2

+1.15VA_SOC_G3

Note:Place CAP

+1.15VA_DDI_G3

CC52

1U_0402_6.3V6K

CD@

5

CC42

1

CC47

1U_0402_6.3V6K

2

Back of CPU Note:Place Close of CPU's Edge

1

CC53

1U_0402_6.3V6K

2

Note:Place Close of CPU's Edge

+1.05VA +VNN_1.05VA_S4

Need short

@

PJ1

1

CC145

33P_0402_50V8J

RF_NS@

2

2

JUMP_43X79

112

1

CC55

1U_0402_6.3V6K

2

3.5A

1

CC56

1U_0402_6.3V6K

2

1

CC57

1U_0402_6.3V6K

2

Note:Place CAP Back of CPU Note:Place Close of CPU's Edge

+1.05VA +1.05VA_SOC_G3

RC9238

1 2

0_0603_5%

1

CC63

1U_0402_6.3V6K

2

1

CC64

1U_0402_6.3V6K

2

1

CC65

1U_0402_6.3V6K

2

Note:Place CAP Back of CPU Note:Place Close of CPU's Edge

+1.05VA

RC9281

1 2

0_0603_5%

1

CC69

1U_0402_6.3V6K

2

+1.05VA_DDR_G3

1

CC70

1U_0402_6.3V6K

2

1

CC71

22U_0603_6.3V6-M

2

CD@

1

CC72

22U_0603_6.3V6-M

2

Note:Place CAP Back of CPU Note:Place Close of CPU's Edge

+1.05VA +1.05VA_SSIC_G3

RC9242

0_0603_5%

1 2

1

CC76

1U_0402_6.3V6K

2

1