A family of universal modules of the ADC, DAC

Measuring voltage converters

E20-10

E20-10-1

E20-10-D

E20-10-D-1

E20-10-D-I

E20-10-D-1-I

User manual

Revision 2.01.00

October 2017

http://en.lcard.ru

en@lcard.ru

DAQ SYSTEMS DESIGN, MANUFACTURING & DISTRIBUTION

Author of the manual:

A.V. Garmanov

L-CARD LLC

117105, Mosc ow , Varsha vskoye shosse, 5, block 4, bld. 2

tel.: (495) 785-95-19

fax: (495) 785-95-14

Internet contacts:

http://en.lcard.ru

E-Mail:

Sales department: en@lcard.ru

Tec hn ica l sup port: en@lcard.ru

E20-10 module © Copyright 2005-2017, L-Card LLC. All rights reserved.

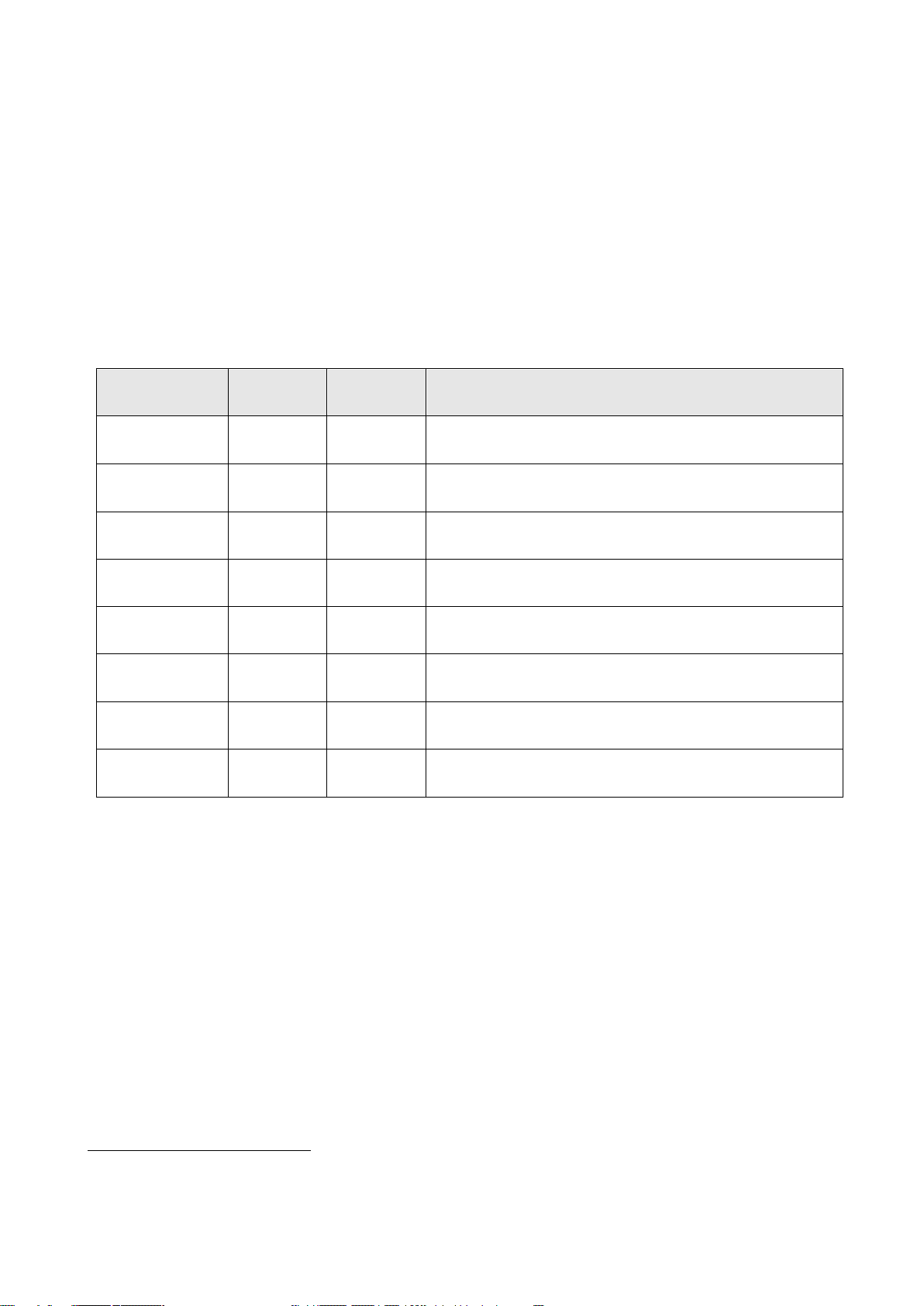

Manual

Date

Notes to the updates

1.00.02 –

1.00.07

05-2006 -

05-2007

Guidelines on E20-10 revision А release of which was

completed in late 2007.

2.00.01

04-2008

The m anua l is significantly amended, updated due to addition

2.00.02

04-2008

Table in p. 7.3 is updated, p. 3.3.4 is added, table 5-5 is

updated, er ror is corrected in table 6-3

2.00.03

09-2008

FPGA (p. 3.3.4) firmware upgrade details are updated.

2.00.04

10-2008

Explanatory figure is added in p. 4.4.

2.00.05

10-2008

FPGA (p. 3.3.4) firmware upgrade details are updated.

2.00.06

04-2009

E20-10 (p. 3.3.2)design versions designation system is

changed and amended

2.00.07

12-2009

Paragraph 6.5.4.3 ha s new ver si on

2.00.08

06-2010

Paragraph updated 7.1.3

2.00.09

07-2010

Paragraph 6.3 edited

2.00.10

06-2011

P.5.2.2 edite d. Paragraph 6.5.1 added

2.00.11

03-2012

Man or c hang e s in do cumen t a tion

2.00.12

09-2012

ADC frame is oversi zed up t o 8192 s amples!

inpu t is un c onnected

2.00.13

11-2012

Details are added to p. 3.3.4

2.00.14

02-2013

Details on revision B.01 are entered. (p. 2.1)

2.00.15

03-2013

Paragraph 2.1 edited

2.00.16

01-2014

Paragraph 6.5.1 edited

2.00.17

02-2014

table 6-7, p. 7.4, p. 6.5.1 are updated

2.00.18

12-2014

Details on new fi rmware 2.00.10, p. 3.3.4 are adde d

2.01.00

10-2017

Industrial design versions are added

Revision history of this document

revision

of num erou s de ta i l s o n E20-10 revision В.

Characteristic is added to Table 7.1 : Zero offs et when AD C

The characteristics according to the results

preparation of L-CARD Vol tage measu rin g converter series for

certification as Means of Measurement

The latest re vision of this document is always be ing reco rded on the CD-ROM incl uded in

the del ivery p ac ka ge (p. 3.3). B e si de s , you can find the latest revision in the library of files on our

website http://en.lcard.ru/download

.

Contents

1. What this document is about ................................................................................................................ 6

1.1. On revisions А, B and В.01 of moduleE20-10........................................................................... 6

1.2. Desi gna tion s ystem....................................................................................................................... 7

1.3. Design versi ons ............................................................................................................................. 7

1.4. How to read this manual?............................................................................................................. 8

2. Primary application properties ............................................................................................................. 9

2.1. Complete list of user differences of revisions А, В and B.01 for E20-10 module ................ 11

3. Gene ral description ............................................................................................................................. 14

3.1. Device applicat ion ...................................................................................................................... 14

3.2. Appearance ................................................................................................................................. 14

3.3. Module configuration ................................................................................................................. 16

3.3.1. Standard supply package ................................................................................................... 16

3.3.2. Design versi ons .................................................................................................................. 16

3.3.3. Software delivery ............................................................................................................... 17

3.3.3.1. Operational software ...................................................................................................... 17

3.3.3.2. Libra ry Lus ba p i .............................................................................................................. 17

3.3.3.3. LComp library ................................................................................................................ 17

3.3.3.4. Opti o nal so ft ware ........................................................................................................... 18

3.3.4. FPGA firmware versions ................................................................................................... 18

4. Install ation and customization ........................................................................................................... 20

4.1. Module connecting to computer ................................................................................................ 20

4.2. USB drivers installation ............................................................................................................. 20

4.2.1. USB drivers installation from Lusbapi ............................................................................. 20

4.2.2. USB drivers installation from LComp .............................................................................. 20

4.3. Recognition of the module ......................................................................................................... 21

4.4. Differences in USB driver of Lusbapi library .......................................................................... 22

5. Overview of the hardware components and operation principles ................................................... 25

5.1. Block diagram ............................................................................................................................. 25

5.2. E20-10 operating principle. ....................................................................................................... 28

5.2.1. Chan n el sampli ng principle ............................................................................................... 29

5.2.2. Synchronization in E20-10 ................................................................................................ 30

5.2.2.1. Synchronization modes.................................................................................................. 32

5.2.3. Data fo rm at of E20-10 ....................................................................................................... 37

5.2.3.1. Coding of word siz e ov er l oa ding si gn E20-10 or revision А ..................................... 37

5.2.3.2. Coding of data continuous area start in E20-10 of revision B .................................... 37

5.2.4. FIFO buffer and its overloading elim ina tion l o gic .......................................................... 38

5.2.5. Readings adjustment (calibration) .................................................................................... 38

5.2.6. ADC wor d s ize overflow w a rn ing .................................................................................... 38

5.2.7. DAC optional ..................................................................................................................... 39

6. Connection of signals ......................................................................................................................... 40

6.1. Gene ral Information ................................................................................................................... 40

6.2. External c on nect ors .................................................................................................................... 40

6.3. Analog sig na l conn e ct ors ............................................................................................................. 1

6.3.1. Digita l signa l an d e xterna l po w er conn e ct ors .................................................................. 43

6.4. Characte ristic s o f s ig na l line inpu ts and outputs ...................................................................... 45

6.4.1. Operating mode .................................................................................................................. 45

6.4.2. Power-off mode .................................................................................................................. 46

E20-10 User Manual

Limiting through currents .................................................................................................. 47

6.4.3.

6.4.4. External power supply input characteristic ...................................................................... 47

6.4.5. External p ower supply ou t pu ts char a c teristic ................................................................... 48

6.5. Spe cification and connection examples .................................................................................... 49

6.5.1. Connections to USB ........................................................................................................... 49

6.5.2. Multimodule connections .................................................................................................. 50

6.5.3. Circuits GND, GND* and AGND .................................................................................... 51

6.5.4. ADC input connecting ....................................................................................................... 52

6.5.4.1. Intrinsic input current of ADC analog input ................................................................ 52

6.5.4.2. Connecting to high-resistance output and alternate current output ............................ 52

6.5.4.3. On sta nda rd fe el er o s cillographic gauge connectivity ................................................ 53

6.5.4.4. On ef fe ct o f throug h cu r rent s on si gna l-to-noise ratio................................................. 53

6.5.4.5. How can you find out tha t t h e through-currents degrade the signal-to-noise ratio in

your c o nnecti on diagra m? ............................................................................................................. 54

6.5.4.6. How to solve the problem if the through currents are detected? ................................ 54

6.5.4.7. On disconnected ADC inputs ........................................................................................ 54

6.5.1. Dig it a l lines an d s ynch ron ization lines connecting.......................................................... 54

7. Specifications ...................................................................................................................................... 56

7.1. ADC............................................................................................................................................. 56

7.1.1. E20-10, E20-10-I, E20-10-D-I: limits of the pe rmissible relativ e basic error of

measuring the ac volt a ge .................................................................................................................... 58

7.1.2. E20-10-1, E20-10-1-I, E20 -10-D-1-I : limits of th e pe rmissible relativ e basic error of

measuring the ac volt a ge .................................................................................................................... 58

7.1.3. ADc synchr oniza ti o n s y st em ............................................................................................. 59

7.2. DAC............................................................................................................................................. 59

7.3. Digital lines ................................................................................................................................. 60

7.4. Power ........................................................................................................................................... 61

7.5. Physical properties ..................................................................................................................... 62

7.6. Oper ation conditions .................................................................................................................. 63

7.6.1. Nor ma l c onditi o n s .............................................................................................................. 63

7.6.2. Oper ating conditions .......................................................................................................... 63

8. Problems so lution under abnormal situations ................................................................................... 64

8.1. How to be consulted. .................................................................................................................. 65

9. Bibliography........................................................................................................................................ 66

List of tables. ............................................................................................................................................... 67

List of figure s. ............................................................................................................................................. 67

1. What this document is about

This documen t is a User Manual w ritten in a1 user-friendl y manner a s far a s po s s ible. It

describes the technical (hardware) properties of E20-10, explains the operation rules a nd princ iples

of functioning, contains specifications and contents of delivery.

This documen t does no t cover any programming or software issues . These iss ues are given

in progr amm er's ma nu a l [1].

So, You need two documents to operate with E20-10: user manual and programm er's

manual.

1.1. On revisions А, B and В.01 of module E20-10.

Rapidly de v elopin g pres en t element base a nd technol ogies and long-term experience in

ser ial production of E20-10, many user stories are causes of s ign ificant redesigning of project E20-

10: to add a significant number of additional useful functions and properties saving compatibility

with previous functions as m uch a s possib le keep ing the same va lue category for data acquisit ion

devices. Revision B is assigned to new E20-10 and its manufacturing has started with 2008.

Revision А executed before the end of 2007 of E20-10 module is taken out of production but, of

cour s e, i s b ei ng supported by L-Card, and its des cr ipt ion is given in th is manual. E20-10 of

revision В– it is a technologically new device, so, next observe that any changes in E20-10 revision

А into revision В are impossible.

In 2013 L-Card issued new revision B.01 di f f er e nt fr o m older ones in signi fi ca ntly exten de d

power voltage range, see p. 7.4, pag e 61.

Complete list of А, В and В.01 revision differences can be found in p. 2.1 of this manual.

Unless otherwise specified, throughout the text of this manual when it comes to

revision B the same informa t ion relates to revision B.01 as well.

In 2017 the certification of modules of L-CARD series including E20-10 modules as of

industrial versions was started.

Characteristics of revision B.01 gi ven in thi s manual comp ly with L -CARD-E20-10

characteristics.

1

but not according to GOST

E20-10 User Manual

E20-

10-

-

-

Модификация

преобразователя

1

Полоса частот

пропускания

5 МГц

D

ЦАП (2 канала)

присутствует

ЦАП

отсутствует

Преобразователи напряж ения

измерительные

I

+5

…

+

55

°

С

-40

…

+60

°

С

С лакировкой

Нет

индекса

Нет

индекса

D

Нет

индекса

1

Полоса частот

пропускания 1,2 МГц

Converter

modification

There is a DAC (2

channels)

With polish

DAC

no

No

index D

No

index

No

index 1

Measur ing volt a ge

converters

Bandwidth

of 5 MHz

Bandwidth

of 1.2 MHz

1.2. Designation system

1.3. Design versions

• E20-10 (ADC frequency bandwidth of 1.2 MHz, 2-channel DAC is not available).

• E20-10-D (ADC frequency bandwidth of 1.2 MHz, 2-channel DAC is available).

• E20-10-1 (ADC frequenc y bandwid th of 5 MHz, 2-channel DAC is not available).

• E20-10-D-1 (ADC frequency bandwidth of 5 MHz, 2-c hannel DAC is av ailab le) .

• E20-10-D-I (ADC frequency bandwidth of 1.2 MHz 2-channel DAC is available,

industria l design version ).

• E20-10-D-1-I (ADC frequency bandwidth of 5 MHz 2-channel DAC is available,

industria l design version ).

Industrial versio ns (with a lphabetic notation "I") designed to ope rate under

temperature from -40 to +60 °С have cards sealed with varnishing that improves the product

environmental res istance.

More detailed information on operational conditions see in Appendix 0.

1.4. How to read this manual?

Sket c hy infor ma tion o n pr imar y ap plicat i o n propertie s o f E20-10 is given in Chapter 2.

This chapter is targeted for wide range of stakeholders.

In Chapters 3, 0, 6 detail s relatin g to practi cal work it s elf wit h E20-10 are given. The

issues discussed herein will be of interest for specialists and operators.

Whe n ex ploratory r ea ding, Chapt er 5 can be missed because it describes internal

architect ure of mod ule E20-10 which is essential when closer looking.

In Chapter 0 the specifications for E20-10 are given. List if characteristics on E20-10 given

herein is intended for specialis ts.

In Chapter 8 practical information on problems sol ution under abnor mal situations is given.

E20-10 User Manual

2. Primary application properties

E20-10 — is a module o f hi g h-speed analog-digital conv er si on with USB 2.0 interface. The

product primar y ap plication proper t i es are su mm e d up belo w in s hort.

• Continuous 16-bit data acquisition with frequency up to 10 MHz is provided by USB2.0

2

interface

• 4-cha nn el arc hite ctur e w ith on e 14-bit ADC, switch, input buffer amplifiers, filters in each

channel.

impossible.

• Each o f ADC 4 cha nn el s ca n s et in softwar e th e f ollowi n g i npu t signa l sub-ranges

individ ually per cha nnel: ±3.0V, ±1.0V, ±0.3V.

• Each channel has LPF (l ow pass filter ) 3-ord er with fr eq uen c y cut-off of 1.25 MHz

(optimal bandwidt h f or 4 -channel ADC conversion mode and frequency is 10 MHz)

improvin g si gnal -noise-rate. Other LPF frequency cut-offs a re possible (p. 3.3.2).

.

Due to input buffer amplifiers the dynamic switching interference eff ect is

• ADC conversi on frequenc y F

can be s et wi t hin the range from 1. 00 to 10.0 MHz. ADC

ADC

conversion frequency can be both as set in software, frequency spectrum in megahertz is

determi n ed from the f ormu la F

= 30/к, where к = {3,4, 5, ..., 30}, and as external with

ADC

any frequency of from 1.00 to 10.0 MHz (lower data acquisition frequency can be

reached by interframe delay setting).

• Maximum data acquisition fr equenc y p er c ha n nel is F

,/п, where п = {1,2,3,4} —

ADC

number of sampled channels.

• In module control table the frame — ran dom s equen c e of channel sampling with length of

from 1 to 256 can be programmed. Size of sampled channels will be selected cyclically

from the set size table and order of output data samples E20-10 will comply with

cha n n e ls sequence.

3

• Inte r frame ADC sampl ing delay can be programmed from 0 to 65535

of ADC conve r s ion

frequency periods . Due to this the lower sampling frequencies can be implemented per

channel.

• Multi-mod e syste m has advance d s y nc hronizati on mode s f or da t a a cqu isition an d/or ADC

conversi on frequenc y. F or e xa m ple, by c onnecting modules E20-10 according to one

setting devi ce - many receivers diagram the synchronous multi-mo du le data a cqu isition

sy st em can b e achieve d!

• Architecture external ly completely downloaded: downloaded FPGA

, controller firmware

can be updated. Due to this the use r can update firmwares with latest versions by himself.

• FIFO data internal buffer with size of 8 MV bu f f ers da t a sav i ng their lo s s i n case when

4

computer operating system "thinks"

(to 400 ms at an acquisition frequency of 10 MHz to

4 s at an acquisition f requency of 1 MHz).

• Digital input-output i s prese nted in form of 16 input and 16 output dig ital TTL-compatible

lines. Digital outputs can be optional translated in the third state.

• Two-channel 12-bit DAC (option) allows to set constant voltage within ±5 V under

asynchronous mode operation.

• External device power supply outp ut ±12 V, 35 mA

2

Under full-speed (USB1.1) mode the maximum available frequency makes 500 kHz

3

In E20-10 revision B

4

for example, in Windows – in non-real-time (off-line) system

• Power supply of E20-10 from external unr e gulate d source is +8V...+40 V5 (po w er supply

circuit fro m USB i s n ot u sed). It can b e netw or k card o f -220/=12 V (in cluded in the

delivery.). Under off-line conditions E20-10 can be energiz ed fro m ex t er na l power sup pl y

sourc e of from +9 to +27 V. Power consumptio n — max. 4.5 W

E20-10 module has ex t ended supply voltage range f rom +8 to + 40 V .

In addition, revision В forE20-10 module in comparison with revision A has a number of

improved parameters and optional capabilities listed below (p. 2.1).

5

for module revision B.01

6

In E20-10 revision B

6

. Revision B.01 f or

E20-10 User Manual

Characteristic, parameter, function,

property

E20-10 revision А

E20-10 of revisions B and B.01,

L-CARD-E20-10

Interframe delay range

0-255 ADC c onversion

0-65535 ADC conversion frequency

Power c onsumption

to 5 W

to 4.5 W

Typical signal -to-noise rat io

70 dB

73 dB

Minimum data ac q u isition rate

2.1. Complete list of user differences of revisions А, В

and B.01 for E20-10 module

Since 2008 L-Card has decided to release E20-10 of revision В with advanced useful

quality.

All E20-10 modules of 2006 and 2007 production years should be related to revision А (see

labe l on the bod y bottom), since 2008 L-Card has star te d t o pr o du c e E20-10 of revision В.

In 2013 L-Card has started to release revision B.01 with extended power voltage range.

Revisions B an d B.01 are not diffe red in program. Revision B.01 spec if ied on label on body bottom

face , new power volt age range "+8.0...+40 V" is specified on body to p cover.

E20-10 module has signed in 2017 as modification in L-CARD Measuring voltage converter

series.

All consumer diff erenc es of E20-10 of revisions А and В are given in Table:

Data calibration procedure...

(p.

5.2.5)

(p. 5.2.1)

(p. 7.4)

Power supply voltage

ADC i nput offset current software

di sconnecting capability (p.

Intrinsic input curre nt of ADC analog

input ( p.

(p. 7.1)

maximum interframe delay and ADC

conversi on f requency of 1 MHz (p.

7.1)

6.5.4.1)

at

7.1)

is performed on computer

(by imple me nting of the

relevant library function)

frequency periods

is performed inside E20-10 by

FPGA hardware.

periods

+9.0...+27 V +9.0...+27 V (revision B)

+8.0...+40 V (revision B.01)

no yes

-15...0 µA (typical value 7 µA)

7.8 kb y t e/ s 30 byt e/s

10 nA (typical value ) , if input

current is not specially on

Input res istance of analog input min. 5 MOhm 10 MOhm ± 5%

Inter-channel i nterfere nce , not more

than (p.

- at constant volta ge

- at frequency of 1 kHz

- at frequency of 1 MHz

Operating current of output of +5V of

external devices power supply

7.1):

-50 dB

-70 dB

-60 dB

35 mA 35 mA (revision B)

-70 dB

-75 dB

-65 dB

100 mA (revision B.01)

Characteristic, parameter, function,

property

E20-10 revision А

E20-10 of revisions B and B.01,

L-CARD-E20-10

Synchroni zation start mode s for data

Marker mode of first fra me – logic

no

yes

restart is not required, because of the

Number of design versions

2 (fixed)

4

acquisition "ac cording to level" of

signal of selected physical channel

5.2.2)

(p.

ind icator of data continuous section

5.2.3.2)

(p.

no yes

Capability to set additional permit

conditions for ADC data recordi ng in

buffer memor y E20-10:

- "acc or ding to differ ential" signa l in

ADC selected channel,

- blockage of set number of frames

transmission from the beginning of data

acquisition ( p.

5.2.2)

Mode of hardware acquisition st opping

according set number of collect ed data

frames (p.

5.2.2)

On stop the data acquisition restart can

be started, for example, per external

sync-signal START. In practice this

capability allows to implement startstop opera tion for seve r al data

acquisition st art modes

In initiating of internal memory

overflow 8 MV E20-10event

recognizable in hardware (computercaused spooling by USB high dela y)

(p.

5.2.4)

no yes

no yes

data acquisition

mandatory compute r sourced restart is requi red

requir ed minimum number of data

frames will be automatically

(hard ware logic) deleted from buffer

memory of E20-10 to eliminate

overfl ow, and program-accessible

overfl ow indicator is activa ted.

ADC word size overflow indicator per

ADC channel (p.

5.2.6).

External minor constr uction features

15)

(page

Internal major construction feature s 2-storied construction

(p. 3.3.2)

Certificate of Means of Measurement No

7

In this case the references to product E20-10 of L-CARD LLC are required in Your system end user

documentation.

E20-10 User Manual

inserted in ADC data

flow (in relevant mod e

initiation)

BNC connectors (ADC

inputs) ha ve flanges with

4 screws

based on two boards

is not i nse r ted in ADC data flow and

raise s t he releva nt pr ogram event

BNC connectors (ADC i nputs)

without f langes have one nut

retaining

More reli ab l e 1-storied single-board

construc tion, in particul ar, easy-touse E20-10 without body as built-in

ADC module in Your system

7

.

6 (for L-CARD-E20-10)

E20-10

- Not available L-CARD-

E20-10 (under certification)

As shown in table above, revision В of E20-10 module has better useful quality in variety of

significant par ameters in comparison wit h r ev ision А!

3. General description

This ch apter describes E20-10 device application, informs about required and optional

equipment, content of software package for CD-ROM as well as contains the start operation

instructions.

3.1. Device application

E20-10 is s mall-bodie d mu l t ifunct i onal m easuring modu l e connecte d to PC throug h U S B

2.0-i nt erface . Th e m odu le is intend e d f or rapid fl ow capture with ADC c onversion frequency of to

10 MHz.

Bas ic functions of E20-10:

• 4-channel ADC of 10 MHz with c hannel multiplexing , with buffered input, with advanced

functions of internal, external, multi-module synchronization

• digital asynchronous input-output

• 2-channel asynchronous DAC (option)

Fast E20-10 modul e i s comple m e nted wit h s o m e sl ower ADC USB -modules: E-154, E14-

140, E14-440 and is intend e d for creati ng multi-channel measuring analog data acquisition systems

as well as for digital control and mo nitor ing of externa l de vi c es state.

3.2. Appearance

Revisions А and В of E20-10 mod u le have minor e xterna l dif f erences (fig . 3 -1, fig. 3-2). In

addition, on factory label ( on the body bottom) of E20-10 module of revision А the production

years 2006 or 2007 are specified, and on label of revision В – 2008 o r later. Moreover, on the la bel

the design version of E20-10 module is specified in compli ance with agreed not ation (p. 3.3.2).

E20-10 User Manual

Fig. 3-1. E20-10 revision А

appearance

Fig. 3-2. E20-10 revision В

appearance

Appearances of E20-10 of revision B and B.01 are simil ar.

Details on revision B.01 are s pe cifie d on label on b ody bottom wall .

Power supply v oltage range is specified on body top cover.

Design version

Description

E20-10

Bas ic design version — without DAC, bandwidth of 1.25 MHz per

ADC channel

E20-10-D

2-channel DAC bandwidth of 1.25 MHz of each ADC channel. This

version was named as "E20-10D" in ol d notati on

E20-10-1

With out DAC, bandwidt h of 5 MHz of e ach ADC channel (des ign

version is available for revision В only)

E20-10-D-1

With 2-channe l DAC, bandwidth of 5 MHz of e ac h ADC ch annel

(design version is available for revision В only)

3.3. Module configuration

3.3.1. St anda rd su pply packag e

• module E20-10 (1 pcs.)

• com munication cable on USB 2.0 (1 pcs.) — А-В type, length of 1.3...2.0 m

• network card for E20-10 power s upply from alternate current network of 220 V, 50 Hz

• ma gnetic sweep cable of conne ctor (1pcs.) — DB-37M with housing DP-37P — for

digit a l s ignal cable termina t ing pro ducti on

• ma gnetic sweep cable of conne ctor (1pcs.) — DJK-10A — for extern power supply

circuit cable terminating production, if required, to energize E20-10 not from circuit of

220V through attached network card but from different source of +9...+27 V

• ma gnetic sweep cable of conne ctor (1pcs.) — MDN-9P — for production of magnetic

swee p cable to externa l device power supply outputs of ± 12 V and to DAC outputs.

• CD-ROM with documents and software.

Attention! DAC is not included in standard supply package (p.3.3.2).

If required, use hub stations, power units for them and auxiliary USB-cables. When dealing

with E20-10 the user mu s t bu y t hi s equ ipm ent by him s el f in t hird-party manufacturers. The same is

related to not included in delivery package intercon ne cting w ires, auxiliar y cable s , connectors and

terminals to connect sign al sources a nd arran ge network interface communications.

3.3.2. Des ign v ersi ons

E20-10 is produced in the following design versions:

Attention! Specify the required design version in ordering E20-10.

Design version is specified on factory l abe l on the bod y bottom.

Anot her ADC channel bandwidths are available as agreed upon with L-Card.

E20-10 User Manual

library including all sources, import libraries,

Designs on module programming examples across different

3.3.3. So ftware del ivery

3.3.3.1. Operational software

For historical reasons, L-Card LLC firm pr ov i d e cu r rentl y t w o librar i es for th e u ser t o

opera te wit h m odu le E20-10, as follows: Lusbapi and LComp. Both libraries are intended to

operate under Windows’98/2000/XP/Vista environments. Both Lusbapi, and LCo mp provide

complete functional support for module E20-10. LComp library benefit is wider support the

product p er fo r m e d b y L-Card LLC. So, Lusbapi supports USB devices only, and LComp library

provide additionally operation with ISA and PCI products of L-Card LLC.

Attention! Both libraries Lusbapi and LCo mp have programming interfaces incompatible

com plet el y bu t t h ey use the same universal USB driver named Ldevusbu.sys.

3.3.3.2. Library Lusbapi

The w hol e Lusbapi library package is located in accompanied to module branded CD-

ROM in base direct or y \USB\Lusbapi. The same libr a ry ca n be do w nload e d fr o m ou r w eb s ite

en.lcard.ru from the section " Fil e Li brary ". There, in subsection "Software for Windows" you

shou ld select t h e self -extracting archive lusbapiXY.exe, w h ere X.Y denotes the software current

version nu mber . At the time o f this manua l wr iti ng, th e late st Lusbapi libr ary has versi o n 3.2, and

its archive is named

The stru cture o f arr ange m en t on brande d CD-ROM of all Lusbapi library components is

given in table below (paths are specified relatively to base directory \USB\Lusbapi):

lusbapi34.exe.

Directory Intended pur po s e

\DLL\ Lusbapi

declaration modules and, etc.

\DRV\

\E20-10\DOC\ Doc umentatio n Inc luding prog rammer 's ma nual on o perat ion

\E20-10\Examples\

To provide Your applications proper operation with module E20-10 it is recommended to

copy binary file of \DLL\Bin\Lusbapi.dll library to directory %SystemRoot%\system32, tha t can

be im pl ement e d by us ing fin i sh e d ba tch fil e \DLL\CopyLusbapi.bat. This operation is often

applied because Windows’98/2000/XP/Vista, if required, searches aut omatically the require d

libraries in specified directory. On the other hand, Lusbapi.dll library can be conceptually loc ated

in dir e ctory o f ultimat e applica t i on or in one of the di rector ies spe cifie d in e nviro n m en t variable

PATH.

All user required components of Lusbapi library (include files, programming examples

and, etc.) are moved to target computer by copying of required directories and files from delivered

branded CD-ROM.

USB driver of module and inf-file.

with Lusbapi library.

development environments: Borland C++ 5.02, Borland C++

Builder 5.0, Delphi 6.0 and MS Visual C++ 6.0.

3.3.3.3. LComp library

LComp library is presented in form of installation tool LComp.exe, whi ch is lo ca t e d on

branded CD-ROM in directory \DLL\LComp. The same library can be downloaded from our

website en.lcard.ru from the section "File Library". There, in subsection "Software for Windows"

you should select self-ext r acting archive lcomp.exe.

Installat io n tool LComp.exe is intended for proper arrangement of all components of

LComp library on user's computer. Moreover, such required LComp components as so urces,

import libraries, decla r a t io n m odule s , pr o gr ammi ng exam ples, el e ct roni c do cu m e nt a tion a nd , et c.

will be located in dire c tory assigned by the user in librar y instal lation .

3.3.3.4. Optional software

• Free program L-Graph II. It is intended for operation on Windows'XP only. L-Graph II

opera tes with modu l e E20-10 through LComp library. This program is higher-end version

of L-Graph I. For example, it offers the possibility to user to view and record data fr o m

ADC sim u l t ane o usly. L-Graph II can be installed using installation tool

\LGraph2\setup.exe from bra nde d CD-ROM attached to the module. L-Graph II

distribution can be also downloaded from our website en.lcard.ru from the section

Library". There, from subsection "LGraph2 software package" you mus t s elect

distribution lgraph2.zip.

• Commercial program of multi-channel recorder PowerGraph. The program is i ntended to

record, process and hold analog signals and allows to use personal computer as tape

recorder. Windows'98/2000/XP/Vista. Developing, delivering and technical support –

"Interoptica-S "LLC , www.powergraph.ru

module E20-10 includes demo version PowerGraph located in directory \P_graph on

our branded CD-ROM.

. Standard software package delivered with

"File

• Comme r cial automation complex ACTest for experimental and process plants. This

comple x is intended to rea l-time view, record, store and process data.

Windows'98/2000/XP. Developing, delivering and technical support – "Automated

systems laboratory" LLC, www.actech.ru

module E20-10 includes demo version ACTest located in directory ACTest on our

branded CD-ROM.

. Sta ndard s o ft wa re pa ck a ge del ivered wit h

3.3.4. FP GA f irmwar e ve rsions

In E20-10 FPGA firmware version and creation date are programm-accessible [ 1]. The

current delivered FPGA firmware is integrated into delivered program library functions.

Conceptually, you can update E20-10 firmware by two ways: download upgraded software in

"Files library" or order FPGA firmware new file in L-Card (en@lcard.ru

initialization function E20-10. The last way is technically appropriate only if exchanged FPGA

firmwares are compatible on program library functions – th is and res t user inform ation about

available firmwares of E20-10 is given in ta ble below.

You ca n f ind out about ac tual FPGA fir m ware of Your module E20-10 using utility

ModulesViewer which can be downloaded from website L-Card from section Files library

) and use it in calling

.

E20-10 User Manual

rev.В are recommended to update firmware

Firmware

version

1.00.06

dd. 15.01.07.

2.00.03

dd. 10.04.08.

2.00.05

dd. 24.07.08.

2.00.06

dd. 01.09.08г.

Firmware descripti on

Final firmware E20-10 rev.А.

First firmware of serial E20-10 rev.В.

Users applying internal calibration in E20-10

to elder version where the effect to damage individual data sampl es in code approximating

to ADC word si ze edge has been eliminated . Negative ef fects have not be en found when

internal calibr ation is off.

Updated firmware of serial E20-10 rev.В.

In FPGA 2.00.05 firmware the add itional prog r am start is not required unde r

addi tional sta rtup condition "on

and shut down condition "on number of M re corded fra mes", due completing of the next

shutdown condition fulfillment the addi tional data acquisition start will begin

automaticall y upon completing of new start condition fulfillment. For anot her start

conditions

FPGA 2.00.05 firmwa re is simi lar to 2.00.03 firmware. Als o refer to

signal passing t hrough given level in selected channel"

table 5-5 notes to it.

FPGA 2.00.0 3 an d 2.00.0 5 fir mwares are f ully compatible on program library func tions.

Updated firmware of serial E20-10 rev.В.

One-channel mode sensitive data acquisition fault has been eliminated.

1.00.07

dd. 29.10.08.

2.00.07

dd. 05.09.12.

2.00.08

dd. 20.11.12.

2.00.10

dd. 15.12.14.

Updated firmware of serial E20-10 rev.A.

Data corruption in repetiti ve interleaving of external start and program shutdown has been

eliminated (this relates to rev.A only). FP GA 1.00.07 firmware means simultaneous

upgrad ing of AVR contr oller firmware .

For E20 -10 rev.В the embedded software upgrading enabling to boost maximum possible

frame size up to 8192 samples of ADC has been d eveloped ! To upgr ade it is required to

alter AVR controller and upgrade library re mot ely (FPGA 2.00.07 firmware has been yet

added in which). Compatibility with old software of upper level is existed.

Firmware for E20-10 rev.В. In comparison with version 2.00.07, the fault on odd data

interference in ADC buffer in additional data acquisition starti ng on si gnal START under

data acquisiti on pr ogr am shutdown mod e has been el iminated.

Firmware for E20-10 rev.В. Data acquisition restart on signal START fault has been

eliminated.

4. Ins t allation an d c u stomizat ion

4.1. Module connecting to computer

Inspe ct packa ge and p rod uct comp onents for mech an ical damage s. Switch on the computer

if it was off and download operating system Windows’98/2000/XP/Vista. These particular operating

systems are enabled to support adequate operation of USB interface.

USB i nt erface spec ificat i on provides us ers wit h op er a tiona l capabiliti es to wor k with

peripheral devices under t rue mode Plug&Play. This means that USB standard provides

device"hot" connection to live computer, its automated recognition by operating system

immediately upon connecting and next downloading of drivers relevant to this device. Moreover,

USB device can be disconnected from comp uter at any time. In addition, the computer c an be

swit c hed on if USB device has been p reviousl y connec ted.

Hardwared connecting of m odule E20-10 to computer is as follows: apply external power to

E20-10 by connecting ne twork car d included in delivery p ac kage, conne ct USB m odu le co nn e ctor

to computer USP port using cable incl uded in delivery package . All specific aspects to conne ct

signals are described in Ch.6, in particular, on connectin g to USB, ref er to p. 6.5.1.

Note that when operating with drivers L Comp you should download f irst the dr ivers 4.2.2

and conne ct E20-10 once this is done.

4.2. USB drivers installat ion

Procedures on USB drivers in stallation from l ibr a ries Lusbapi and LComp are a bit

different for E20-10 module. These particular differen ce s are described in the following two

paragraphs.

4.2.1. US B dri vers inst allat ion fr om Lu sbapi

Whe n very first connecting of E20-10 module to computer using included standard USB

cable the operating system should request driver files for first-time connected USB device. In this

case, it is required to specify inf-file fr om Lusbapi l ibr a ry fro m ou r branded CD-ROM:

\USB\Lusbapi\DRV\Lusbapi.inf. Whi le doing so the oper ating system copies itself all fil e s

requir ed for it to necessary slots and performs all necessary entries in its regist ry . Windows system

should su bs e qu e ntly perfor m s o cal led enumeration procedure of USB device, see description

below in p. 4.3 "Recognition of the module".

4.2.2. US B dri vers inst allat ion fr om L Comp

Prior to use module E20-10 with application of LComp li brary it i s re quired to perf orm

installa tio n tool LComp.exe located on branded CD-ROM in directory \DLL\LComp. In addition,

this tool ins talls to user target computer all nece s sary files required f or operating system duri ng

reco g ni tion m odu le E20-10 when it is firstly connec ted to computer USB port. Upon successful

completion of pr og r a m LComp.exe only you may connect module to computer using included

standard USB cable. W h ile doing so, Windows sy stem s ha l l p erform numeratio n procedure for USB

device, see description in the following paragraph of this manual.

E20-10 User Manual

4.3. Recognition of the module

As w as mentione d above , the opera ting system Windows shall perform numeration

procedure for eac h co n necte d USB de vi ce . Su c h proce du r e for USB devices is performed on-the-fly

when they are co nnected to computer without any user inter a c ting or cl ient sof tware.

During the executio n of numeration the module USB indicator – LED, located near to USB

connector E20-10, sha ll fla sh continu ousl y, and upon completi o n it s ha ll be red or gr ee n. This wil l

mean that connected USB device is recogn ized properly by operating system an d is ready for

further operation. Indicator's color informs about E20-10 co n n ecti o n s peed to int erfa ce USB

• red – full speed,

• green – high speed.

You can further check connected module validity of recognition by operating system in

"Device Manager" . There, in app eared s e ct ion "L-Card USB devices" device E20-10 will be

dis pla yed, a s it, for exampl e, is show n in figur e below:

8

:

In further working with module E20-10 the oper a ting system will a lready know the location

of driver for this type of the device and will load it automatically during product connecting to the

computer.

8

In E20-10 revision В the indicator is flashing when data transmitting on USB–it is a natural occurance.

4.4. Differences in USB driver of Lusbapi library

From the version 3.2 in Lusbapi library the primar y fil e of USB driver, now it is call ed

Ldevusbu.sys inst ead of ol d Ldevusb.sys. So, those users who has already installed on

computers USB drivers fr o m Lusbapi library of version 3.1 or la ter shall be ve ry attentive during

moving to ne w er li br a ry, becau s e he mu st chan ge module E20-10 to opera te wit h ne w USB drivers.

To do this the user must perform several standard actions using "Device Manager" .

Firstly, you may verify that mo dule E20-10 connected to the computer operates with old

USB driver Ldevusb.sys. To do this you sh ou ld find in "Device Manager" th e device of

module E20-10 type and consecutive call of panel with its features. Then, on this panel you should

move to bookm a rk "Driver" on which click on button " Driver Details…" . In this case the panel

with li st of all dr iver s e na bled for s el e cted d evi ce will ap pea r. In ou r ca se, dri v er Ldevusb.sys

shall be in this list. Th is m ean s, tha t to operat e with module E20-10 the USB drivers from Lusbapi

libra ry of version 3.1 or older are used.

To move to new USB driver (from Lusbapi library of version 3.2 or newer) you should

perf orm the followin g a ctions. Selec t in “Device Manager” the same moduleE20-10 mentioned in

previous paragraph and call pop-up men u us ing right clicking. The fo llowing picture must be as a

result of these actions:

E20-10 User Manual

Then, you should acti vate the driver upgrade point usin g left clicking. It should be noted

that depending on Windows configuratio n the information pane ls of type to alert abo ut failure of

driver digi ta l signature and propose to find drivers in Internet may be displayed. Then, you should

move to standard information panels “Hardware Update Wi z ard” on which you s h ould sp e ci f y

selection varian ts given on f igures below and click button “Next” :

Then, the following panel will appear on which you should just click the button “Have

Disk…” ().

In this case, in appeared dialogue box “Install From Disk ” you should s p ec if y inf-file

\USB\Lusbapi\DRV\Lusbapi.inf from our branded CD-ROM and click button“OK”. Upo n

completion, on return to previous panel you should click button “Next” :

Now, the only you need is to drive the nail home, in other words, you have to be reassured

by Windows tha t driv er s insta llation f or m odu le E20-10 is completed successfully and the device is

ready for further operation.

I n g enera l, to op er a te wi th E20-10 USB drivers bot h a s o f ol d ( v ersion 3.1 or older) as new

(version3.2 or ne w er) Lusbapi libraries can be simultaneously installed on computer. The thing is

USB driver from exactly which library would be selected by operating system during module

connecting to computer. Yo u ma y c lear up this sit ua tion and make a decis ion on used ( active) USB

driver by viewin g in “Device Manager” as it was m e ntione d in the be gi nning of this paragraph.

Using operational tools of “Device Manager” you can s wi t c h back an d f orth with reas o na ble

facility among both USB drivers, i.e. as you want you can make active these particular drivers

whi ch are r equ i red for curr en t operat i n g w ith modu le E20-10.

E20-10 User Manual

5. Overview of the hardwa re components

and operation principles

Firstly, th e description of hardw a re components which provides insig ht into E20-10

oper a tion principles is given in this c hap ter a nd detailin g of oper ational ch aracter istics is given

belo w . D e s cripti o n do es not cover low-level definition of hardware but it is quite s ufficient for

und er standi n g of product i mp ort ant perfor ma nce charact eristics.

5.1. Block diagram

Module E20-10 contains process nodes shown on diagram (fig. 5-1). Consider next

functional unit E20-10 according to this diagram.

Four identic al analog paths consist of in put offset current control ci rcuit, inp ut static

commutator, controlled amplifier, active LPF of 3-order.

Input offset cur rent contr ol circuit is available in revision В of module E20-10 only. In

revision A typical input offset current makes -7 µA ( in particular, th is curre nt cause d oversw ing to

ADC scale negative values under quiescent ADC analog input). This current was amplifier

component property applied in revis ion A. Amplifier with incomparably lower inp ut current may be

applied in revision B. But, due to the fact of input current existence of revision A could be used in

different propositions (for example, as signal external source connecting sign), that in revision B the

negative offset cur rent can be live on command (therewith, offset curre nt is gener ated artificially) to

be compatib le with old revisi on, but input offset current is dead by de fault in revision B (p.6.5.4.1).

Input static com mutator is designe d to enga g e m o d e f or measuring module E20-10 own zero

independently per ADC channel. Measuring of own zero prior data acquisition session and

program record-keeping of measured value may compensate long-term temperature and time ADC

zero drift. It should be noted, that this commutator is unappropriated for such zero compensation

"on-fly" (i.e., during data acquisition).

Controlled ampl ifier has 3 transfer ratios programmed individually for each ADC channel.

These transfer ratios implement input ADC subranges: ±3 V, ±1 В, ±0.3 V.

Active LPF in basic version has boundary frequency of 1.25 MHz (optimal for 4-channel

9

mode at maximum acquisition frequency), and another versions

frequencies are tec hnically possible (p. 3.3.2).

Signal from active LPF outputs of each channel enters to dynamic commutator pe r forming

swit c hing o f signal s wi th AD C c on v ersion fr eque nc y from four analog paths to ADC input.

Chan n el numbers switchin g s e qu e nce is ar bi t r a ri l y given in control li st.

Pipelined ADC — 14-bit high-frequency A DC of LTC2245 type of Linear Technology. This

ADC has two major features which have a direct effect on E20-10 archi tectur e: deeply pi p el ined

architect ure of this ADC, ADC conversion frequency r ange of from 1.0 to 10 MHz.

Data enters to FPGA from ADC output. In revision А E20-10, beside the above mentioned

mixi ng of ADC word siz e ov erloading fea ture the data flow is not furt her converted bec a us e

cali br a tion pr o c e du r e is impl e m en t e d h ere by up pe r-level tools (in comp u ter). To cal ibr ate flow of

10 megasamp les per seco nd (20 MB/s) "on-the-fly", especially if more than one module E20-10is

connect ed t o the computer, – is a reso urc e-intensive procedure even for modern computer, so,in

revision B of m odule E20-10 the data cal ibration procedure is imple m ented by FPGA tools.

9

this issue are to be arranged with L-CARD

of E20-10 with other boundary

In module of revision А the series Aceх FPGA is used, in revision B the more resourceintensive FPGA of series Cyc lon is used. These downloade d FPGA of Altera corporation perform

full range of fast-acting logic operations in E20-10. FPGA firmware is downloaded from the

10

computer t hroug h U SB at each program init ia l isin g o f E20-10

. L-Card does not rule out FPGA

firmware upgrading (see p. 3.3.4) due to updat ing of E20-10.

Microcontrol ler AV R AtMega162 of Atme l corp or a t ion ( hereafter - AVR)— this contr oll er

performs asynchronous programmable control of module (on upper-level commands), supporting

information interchange through USB , F PGA do wnl oadi n g an d c on t rol pro c edu re, st or i ng

cali br a tion factors and pr oduct serial nu mber.

In revision А E20-10 USB-controlle r ISP1581 is used – this is low-level USB controller

controlled from AVR. More advanced USB-controller ISP1583 is used in re vision B . Both these

controllers of NXP corporation support protocols of full- an d hig h-speed USB interface.

SDRAM -based FIFO buffer of 8 MV is us e d t o buffer ADC data fl o w. Such de pt h of the

buffer is quite sufficient for operating under any operating system at ADC maximum conversion

11

freq ue ncy of 10 MHz

. Contr ol logic o f SDRAM is impl e m ented in F PGA (detailed information

about FIFO s e e in p.5.2.4).

Two-channel asy nchronous DAC (option) is contr olled f rom AVR a s ynchr onou sl y o nl y

using control pipe of USB interface and by relevant function of upper level.

Digital input r egister D I1...DI16 strobe s 16 TTL-lines of data exactly parallel from digital

inpu t s, A VR r ea d s re gister cont e nt. Note , that D I16 line has program mable alternative func tion of

bi-directional acquisition signal START .

10

it is enough to download firmware once upon E20-10 energizing

11

without interframe delays and other settings slowing down data acquisition

E20-10 User Manual

FPGA

Статический

коммутатор

Вход 1

Управляемый

усилитель

Активный

ФНЧ

Канал 1

Канал 2

Канал 3

Канал 4

Вход 2

Вход 3

Вход 4

конвейер-

ное

АЦП

Буфер

FIFO

8 MB

USB

контрол-

лер

Преобра-

зователь

напряжения

Вход

+9...+27 В

Контрол-

лер

AVR

Цифровой

ввод-

вывод

ЦАП

2

канала

USB

DI1...DI15

Выходы ЦАП:

Выход

±12 В

DO1...DO16

TTL-линии:

DAC1

DAC2

SYNC

Динами-

ческий

коммутатор

DI16 / START

START

DI16

16

15

Логика

калибровки

и доп. условий

разрешения

записи (рев.В)

данные

синхрони-

зация

Управление

входным

током

смещения

(рев. В)

Конвейерный АЦП

Размер

кадра

Логика

калибровки

данных

(рев. В)

Логика

разрешения

записи в

буфер FIFO

Счётчик

задержки

записи

заданного

количества

кадров от

начала сбора

Логика

устранения

переполнения

(рев. В)

Счётчик

количества

собранных

кадров

данных

Логика управления

процессом сбора

данных

конвейерным АЦП

(триггер START)

Внешний старт от

перепада сигнала START

Программный старт-стоп

Старт-стоп от уровня

сигнала START (рев. В)

Стоп по количеству собранных кадров (рев.B)

Логика

разрешения

записи по

аналоговому

уровню и

переходу

через уровень

FIFO

8 MB

вход

выход

Дополнительные условия

разрешения записи в буфер FIFO (рев.В)

вход

выход

USB-

интерфейс

Указатель

на строку

управляющей

таблицы

Логика

управляющей

таблицы

управляющая

таблица

Входы АЦП

Аналоговые

каналы АЦП

Динамичечкий

коммутатор

Счётчик

межкадровой

задержки

Сигнал START в режиме "ведущий"

Input 1

Input 2

Input 3

Input 4

synchroniz

data

Input

offset

current

control

(rev. В)

Channel 2

Channel 1

Channel 3

Channel 4

Static

commutat or

Controlled

Active

LPF

converter

DAC

2 channels

Control-

Digital

input

FIFO

controller

Input

+9...+27 V

Output

±12 V

DAC outputs:

TTL-lines:

Logic of

and additional

(rev.B)

ADC anal og

channels

Dynamic

commutator

ADC inputs

Data

(rev. В )

Interframe

counter

control table

Logic on write

on analog level

Pipeli ned ADC

Size

frame

Data frame

Set frame

USB-

interface

Overflow

logic (rev. В)

input

input

output

output

Logic on write

buffer

FIFO

8 MV

FPGA

Pipelined

ADC

write enable

ation

calibration

conditions

ampli fier

buffer

8 MV

ler

AVR

USB

Voltage

Dynamic

commutator

-output

delay

Fig. 5-1. Block diagram E20-10

calibration

logic

enable

and transition

though the

level

enable

in FIFO

amount w ri ting

delay

from

acquisition

start counter

collected

amount

counter

elimination

Fig. 5-2. Explanation of data acquisition equipment logic interaction in E20-10

Digital output register DO1...D O 16 sets exactly parall el 16 -bit data on TT L-ou t pu ts for

programmable controllability of the third outputs state as well as for controllability of the third state

on signal EN_OE (table 6-2).

START acquisition start synchronization i nput-output. If digital line DI16 for input

asynchronous function is not active, then this digital line may be set in software to functions

"mas t er " ( ou tput) or " sla v e" (input) o f ST A RT signa l . These fea t u res can be used, for exampl e, for

multi-module synchronization of data acquisition start for several E20-10 according to diagram

"on e mast er – some slaves" (p. 5.2.2).

Digital input-output of ADC sync hr onizati on freque nc y SYN C can be used fro multi-module

synchronization of ADC conversion frequency synchronization of several E20-10 according to

diagram "one master – some slaves" (p. 5.2.2).

Voltage convert er converts unstable input voltage of +9V...+ 27V into stable power supply

voltages for internal nodes of E20-10. Auxiliar y volta ge o f ±12V is output from transm itter output

to ana lo g outpu ts connector of modu le E20-10 for ex ternal de vice powe r supply.

LED indic a tor (not shown on di agra m , ou t pu t to front panel of module) is controlled

directly from AVR. Connection conditions on US B and other events are signalized by mo de a nd

color of emission, details see in Programmer's manual [1].

5.2. E20-10 operating principle.

USB-module E20-10 does not use power supply circuit of USB 2.0 interface. To switch on

module it is re quired to apply power voltage of +9.0V...+27V to it

6.3.1) from network ca r d in cl uding in delivery packa ge (p. 3.3.1) or from ex t er na l c on s t a nt -voltage

sou r c e. Pow er supply cir cuit par am et ers for E20-10 see in p. 7.4.

Upon switching on the program of USB-device upgraded in AVR completes proced ure on

connecting on USB as soo n as computer conne c tion wi ll be detected.

Upon successful detecting of E20-10 by your computer operating system the

ready to oper a te on level of software app li cations using delivered by L-Card lib rary functions, in

particula r , one of these func tions is FP GA E20-10 downloading – this download is required to be

performed once upon as E20-10 switching on (see Programmer's manual [1]).

At the close of FPGA download from software level all information about this module E20-

10, in particular, serial number, module revision, AVR firmware v er sion, FPGA firmware version

will be available.

Prior to start data acquisition it is required to configurate it in software, because you m ay not

change conf iguration settings during data acquisition. Main configuration parameters are:

• ADC conversi on frequenc y (within the range of f rom 1.0 to 10 MHz).

• Data acquisit ion frame s ize: f r am e s ize, interf r am e delay duration Number of sampled

inpu t channel s ca n b e f le xible c on f igurated fr o m 1 to 4. ADC convers ion fr equenc y is

divided am ong sam pled channel s in a cc ordan c e wi t h t he ir qu a nt i t y an d sampling order

(frequency). The required sampling order of channe l s f orming th e fra m e i s pr e vi ously

recorded in co ntrol l ist with size of from 1 to 256 ADC paths, m. Whe n data acquisit ion

the numbers of channels are repeatedly read with given ADC conversion frequency

(1.. .10MHz) and are sent to dynamic comm utator as control s ign al. To achieve dat a

acquisition lower frequencies the interframe delay is programmed which allows to achieve

lower data acquisit ion frequencies . Under given nonzero interfram e delay upon

completion of contro l list access cycle (in frame completion) the relevant number of

12

On trigging E20-10 power supply voltage should be min. +9.5 V.

13

device driver installation is performed under first-time connecting (p.4.2)

12

through power connector (p.

13

module is

E20-10 User Manual

nonoperating periods of ADC conversion frequency is inserted; data on these periods are

deleted on hardware level and, due to this, traffic on USB is not overloaded with garbage.

• ADC conversi on frequenc y s ynchronizat ion mode (p. 5.2.2). To implement external and

multimodule synchronization mechanism of ADC conversion frequency you should use

configure d bi-directional TTL-signal SYNC (p. 6.3.1).

• Acquisition start mode (p. 5.2.2). To implement ext er nal, mul timo du le synchron ous star t

of data a cquisi t i on you can use con f igure d bi-directional TTL-signal START (p. 6.3.1).

• ADC channel input param e ters. It is noteworthy, that each channel individual installations

on required voltage input subrange, on input offset current as well as on own zero

measurement mode are not controlled in real time (synchronously) but they are controlled

st a ti cally and asynch ronously from AVR.

Main functional nodes engaged in data acquisition are shown in fig. 5-2. Note, that fairly

large number of new functional nodes implemented in revision B have not been available in

revision A (see verbal instructions of "Rev. В" on this figure).

In E20-10 of revision А "data acqui sit io n contr ol lo gi c" is start in g of "ADC —FIFO—USB-

interfac e" pipeline fr o m progra m sta r t e ve nt or fr om external START signal edge. In fact,

"START Trigger" indicates ADC start state (in combination with control list logic). In revision А

pipe line st op ping (START tri gger cl ea r ing) i s p er f ormed according to progr am pipe line st op ping

event only (followed by FIF O da ta clearing) an d logic o f wr ite ena bl e i n FI F O buffer is ac ti vated

fro m interframe d ela y mecha nis m onl y (i nterframe de l a y k e y po i nt is des cr ibed in p. 5.2.1).

Specifically, that START outpu t signal s tate under "master" mode is fully complies with "START

trigger" stat e.

In E20-10 of revision В the additional logic of write enable in FIFO buffer ( acquisition

sto pping ) whic h is dire ctly relating to da ta analysis a t AD C output is interstitia l dow n stream of

ADC pipeline but upstream of FIFO buffer: write enable on analog level, given amount of frames

fro m a cqu i s i tion sta rt w ri te delay cou nt er , c ol l ecte d frame s a mount cou nter. Al l t h e se ne w

functional nodes are involved in new synchronization mechanism of revision В (see description of

all synchronization modes in p. 5.2.2.1) , bu t , i t is impor t a nt to note , tha t th e s e m e chani s m s ar e

completely rela t e d n ot to ac quisition pi peline starting bu t t o o pe r a tion of wr i t e e na b l e to FI FO

buff er me c hani s m onl y agai n st ADC pre viou sl y tr i g g ered in co njunc tio n with "control li st logi c".

It follows, that "START trigger" as well as START sync signal under "master" mode

behavior logic is unrelated to "added logic of write enable in buffer". This feature will be essential

to the understanding of synchronization modes described below (p.5.2.2) w her e S TART sig nal i s

involved.

5.2.1. Ch annel sampl ing princ iple

In E20-10 acquisi tion fr ame size can be se t of from 1 to 256 (to 8192 ADC paths in FPGA

new fi rmware, p. 3.3.4). The following can be set: random sequence of channel numbers inside the

fr ame, specified in co ntrol lis t as well as interframe delay of from 0 to 255 AD C conversi on

freq ue ncy pe riods (fo r E20-10 of revisio n A ) or from 0 to 65535 ADC periods (for E20-10 of

revision B). T h e given size of co ntrol li st is always equa l to a c quisition frame si z e. Und er any

synchronization mode the data acquisition start is always bound to channel number specified on top

of control list and nonzero interframe de lay is always inse rted upon c ompleti on of last channel

number sampling at the bottom of control list of a given size. In any case, if data acquisition is not

stopped the next channel number will be taken from top of control list (and following the period of

frame given size from 1 to 256) upon completion of channel number sampling given in last string of

control list. Each period of ADC channel number periodic reading from control list as well as each

period of interframe delay counting are bou nd to given A D C c onver si on fre qu e n cy period of E20-

10 (from 1.0 to 10 MHz).

5.2.2. Syn chron izat ion i n E20-10

If synchro nizati on is not r e qu ired, t ha t i nt ernal ADC conver si on frequenc y s ou rce is use d i n

E20-10 as well as simple program data acquisition start. But, E20-10 has also exter nal

synchronization tools both as on ADC conversion frequency as on acquisition start. These are two

independent mechanisms which can be used both as separately and as together.

Synchronizati on on ADC c onve r sion fre quency (within possible range 1.0 – 10 MHz) is

performed using SYNC line which can be configured in software to output or to input (table 5-1).

Due to this the f ollowin g problems can be so lved:

• ADC conversion fr equenc y -based synchronization of several E20-10. To do this

you should switch on several E20-10 according to diagram "master-slaves"

connecting similar circuits GND and SYNC of several E20-10.

• Conversion frequency synchronization signal E20-10 generati n g t o e xterna l de vice,

for example, to frequency meter to monitor conversion frequency.

• External sync hroniza tion on TTL-s ignal (w ith freq ue ncy of 1. 0 – 10 MHz and on-

off time 2) for external synchronization of one or more E20-10 on ADC co nver sion

frequency.

The following problems m ay be s olved using acquisit ion start synchroni z ati on via START

line configured in software to input or to output (table 5-2):

• Transmitting of acquisition program start internal signal through START line for

synchrono us s tarting data acquisition in other modules E20-10. To do this, you

should swi t ch on s e veral E20-10 according to diagram "master-slaves " connecting

similar circuits GND and START of several E20-10

• E20-10 data acquisition start synchronization from external source of TTL -signal.

• Transmitting of acquisition program start internal signal in E20-10through ST ART

TTL-line to external d e vice for s ynchro nization or indica tion of data acquisi t io n

process.

Module E20-10 of revision "В" supports addit ional permit condi tions f or ADC data

recording in buf fer memor y of E20-10 (on edg e i n select e d ADC cha nnel, disabl i ng trans m issio n o f

given amount of frames from acquisition start), as well as additional conditions for acquisition

stopping (on data collected frames amount). In addition, "on level" data acquisition mode series is

added in revision B. These additional synchronization conditions improve synchronization tools of

module E20-10 of revis io n "B" in compar ison wi t h re vision "A".

The following limitation should be noted: addi tional c onditions for ADC data recording

and acquisiti on stopping permi t conditions can be applied inside o ne E20-10 module only and they

have no effe ct on STA RT si gnal behavior in inte r m odule sync hr onization ac c or ding to masterslaves principle. At the same ti m e, i f de s i red, in differ ent modu les E20-10 the similar auxiliary

conditions for data recording and acquisition stopping permit conditions may be made , and as a

result, under connecting "master-slaves " m odule s E20-10 on START signals you may achieve

conditions for synchronous operation of additional conditions for data and acquisi tion st opping

recording permi t condit ions in diff er en t m odu les E20-10 .

It is natural, that in multimodule connections of E20-10 on "master-slave" principle the user

must judiciously configurate control lists, interframe delays (and in E20-10 of revisio n B the

additional conditions for buffer write enable as well) of these modules in order to be able to make

sense of relative time connections among the sample flows obtained from these modules. Master

E20-10 should be earlier started in software to collect data, because they should enter in start

waiting from master, and in this case, upon slave data acquisition starting completion the data

acquisition in masters will b e sta r ted in ha rdwar e an d s yn c hronousl y wit h s lave E20-10.

It shou ld be not ed, that when SY N C line co n fi gu r a ting to fu n ction " slave" (u nder externa l

synchronization of ADC conversion frequency from digital TTL- sy nc signa l externa l s ource) it will

E20-10 User Manual

be incorrectly to feed SYNC pulses outside more rapidly than in 100 ns (10 MHz) or less often than

in 1000 ns (1.0 MHz), bec ause under this mode SYNC pulse is fed di rectly to ADC LTC2245, and,

according to manufacturer's documents, this ADC operates within conversion frequency range of

from 1.0 to 10 MHz. Severe require m e nts are also pose d on SYNC signal on-off time (p.7.1.3). It is

natural, that SYNC signal from "master" E20-10 complies wit h th ese requirements.

Note, that TTL-line D I16/STAR T configurated "on input" , electrically ha s pull-up resistor

(providing specific one state of unconnected input), and TTL-line SYNC configurated "on i nput"

does n ot ha v e pul l -up resistor, i. e. certainty of SYNC unconnected input state is not provided, table

6-2.

Synchronization

frequency

n

30

n

30

Implemented

E20-10

"software":

table 5-3

Software asynchronous start. S topping possible

"software – master on

table 5-3

START signal of maste r E20-10 is fed by active

5.2.2.1. Synchronization modes

Possible synchronization modes for E20-10 are given in tables below. Take note of

information about what exactly revisions of E20-10 one mode is implem e nted.

Table5-1. Modes of synchronization on ADC conversion frequency

(on SYNC signal)

on ADC

conversion

"internal" A, V

"internal-master" A, V SYNC li ne is configura ted to output: signal with on-off

"external - slave" A, V SYNC line is used "on input" for sync hr onization from

Implemented

in revisions

of E20-10

Notes

ADC conversion frequency:

where, n=3,4,5,…,29,30.

SYNC li ne is not used (transfered to Z-state)

time 2 and ADC conversion frequency is generated:

MHz, where, n=3,4,5,…,29,30.

ADC data physical sampling moment corresponds to

SYNC output signal ed ge

TTL-output of external device: signal with frequenc y of

from 1.0 to 10 MHz, wit h on-off time 2 (meander) is

required

MHz,

Table5-2. Acquisition start synchronization modes (on START signal)

Data acquisition start

synchronization

- without additional start

conditions

- with additional start

conditions,

START signal":

- without additional start

conditions

- with additional start

conditions.

in version

A, V

V

A, V

V

Notes

conditions – table 5-5

START lin e is in Z-state

level "1" (connected slave E20-10 shall be in "on

START signal edge " condition). Stopping possible

conditions –

START li ne is in "on output" state

table 5-5

E20-10 User Manual

Implemented

E20-10

"external - slave on START

table 5-3.

Sta rt on S TART signal

"external – slave on S TART

table 5-3.

Sta rt on S TART signal

"on level" data acquisition

5-3.

V On signal analog le vel in selected channel

Additional conditions

Implemented in

version E20-10

Notes

Blockage of give n N number of f r ames record ing

from the a cquisition start

B

0 ≤ N ≤ 16777214,

where, N-integral

On bott omup t ransiti on through the given signal level

frames recording fr om a cquisition start

B

0 ≤ N ≤ 16777214,

On top-down transiti on through the given signal level

frames recording fr om a cquisition start

B

0 ≤ N ≤ 16777214,

"on level" acquisition modes

Impleme

E20-10

Notes

"on signa l level above threshold of si gnal in 1 ADC cha nnel"

B

Stoppi ng will occur at

"on signa l level above threshold of si gnal in 2 ADC cha nnel"

B

"on signa l level above threshold of si gnal in 3 ADC cha nnel"

B

"on signa l level above threshold of si gnal in 4 ADC cha nnel"

B

"on signa l level below threshold of signal in 1 ADC channel"

B

"on signa l level below threshold of signal in 2 ADC channel"

B

"on signa l level below threshold of signal in 3 ADC channel"

B

"on signa l level below threshold of signal in 4 ADC channel"

B

Data acquisition start

synchronization

signal edge":

- without additional

conditions

- with additional start

conditions.

signal fall":

- without additional

conditions

- with additional start

conditions.

synchronizat ion modes, table

in version

A, V

V

A, V

V

Notes

Stoppi ng possible conditions -

table 5-5.

Possibl e stopping conditions see in table5-5.

Table 5-3. Capability to set additional permit conditions for ADC data recording in

buffer memory E20-10:

in sel ected channel and blockage of N number of

in sel ected channel and blockage of N number of

(acquisition start and s top is performed on si gnal

Table 5-4. "On level" synchronization modes

nted in

level)

revision

fram e end e dg e

where, N-integral

where, N-integral

Acquisition stopping conditions

Implemented in

version E20-10

Notes

Software asynchronous stopping

A, B

based on frame edges

On number M of recorded frames

implement start-stop acquisition mod e

B

0 ≤ M ≤ 16777215,

10

1

Table 5-5. Acquisition stopping conditions

acquisition restartable (see notes 1, 2) under

sett led start conditions, for example, to

where, M-integral

Note1:

In FPGA firmware of version 2.00.03 (details on firmware versions see in p. 3.3.4)

for restarti n g und er an y start condit ion it is re quired to ac tiv ate software restart on