A family of universal modules of the ADC, DAC

Measuring voltage converters

E-502-P-EU-D-I

E-502-P-EU-D

E-502-X-EU-X

E-502-X-U-D

E-502-X-U-X

User manual

Revision 1.1.0

October 2017

http://en.lcard.ru

en@lcard.ru

DAQ SYSTEMS DESIGN, MANUFACTURING & DISTRIBUTION

L-Card LLC

117105, Mosc ow , Varsha vskoye shosse, 5, block 4, bld. 2

tel.: +7 (495) 785-95-19

fax: +7 (495) 785-95-14

Internet contacts:

http://en.lcard.ru/

E-Mail:

Sales department: en@lcard.ru

Customer care: en@lcard.ru

E-502 Module © Copy right 2014-2017, L-Card LLC. All rights reserved.

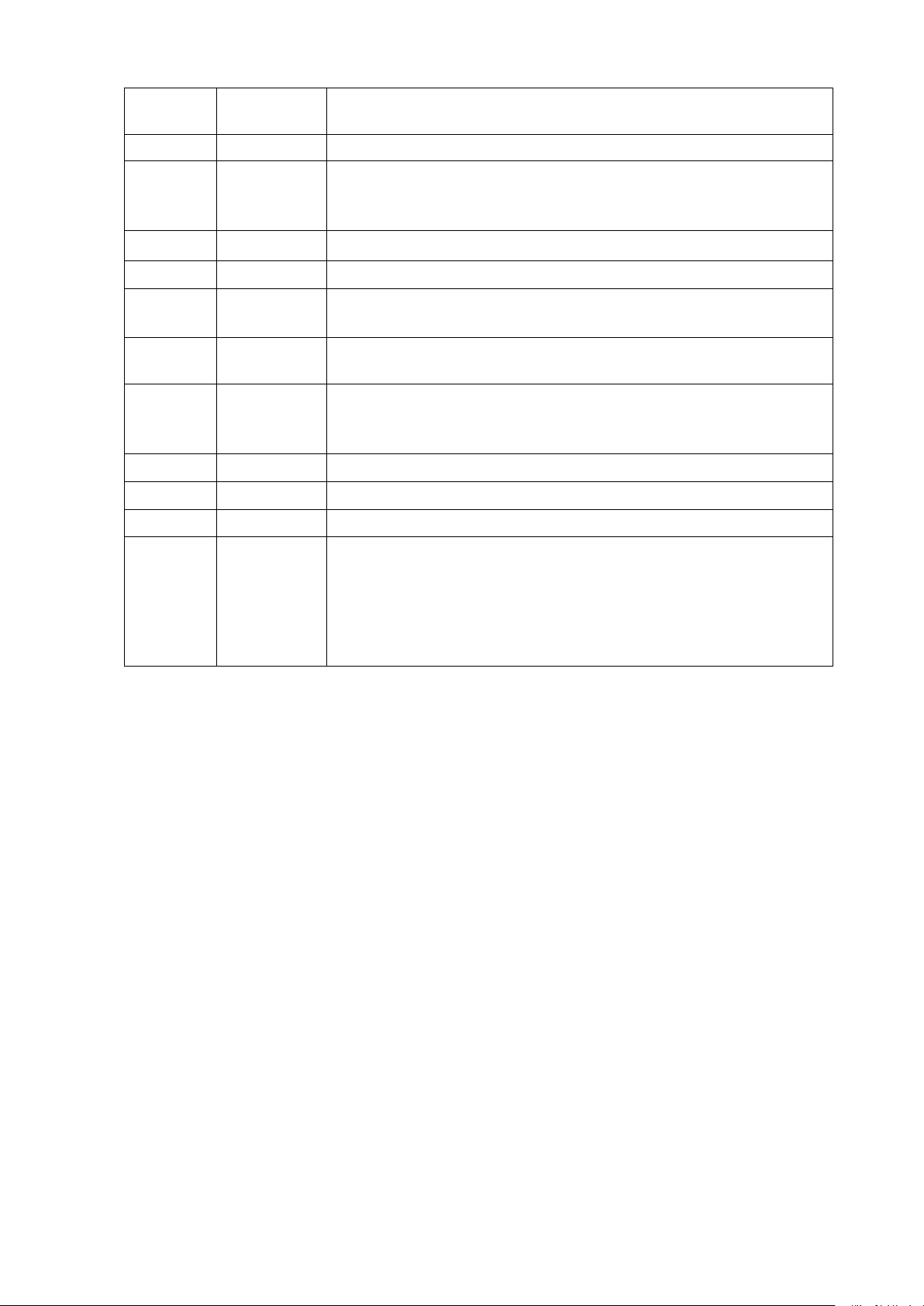

Revis ion hist or y of this document

Date

Document

Contents of the change

09.2014

1.0.0

Prelimin ar y data

05.2015

1.0.1

The ope r ating tempera ture range has been changed (

),

05.2016

1.0.2

10.2016

1.0.3

01.2017

1.0.4

1-1

5.3,6.3

01.2017

1.0.6

1.1.1

2.1

02.2017

1.0.7

Pa ragraph added 3.3.4.1

06.2017

1.0.8

Comments are added to sec. 2.3.3, section is added. 2.8

06.2017

1.0.9

3.3.5.2

10.2017

1.1.0

Added indu strial design versions.

3.3.8

4.7

revision

fig. 1-1

upgraded Chapter 2, Chapter 4. Added section 4.8, Chapter 7,

technical data corrected – Chapter 5.

Orde r option E-502-X-EU-X has been added to the sec tion 1.1.

Fixe d bugs i n the drawings 6.3

Information on the industrial design versi on is included. Amended fig.

.

01.2017 1.0.5 The e r r or about the presence of pull -up resistors on DI inputs is

corrected (s.

The ope r ating tempera ture range in the table of section 5.9 has been

brought into correspondence, amended the section 5.8, the tables in

subparagraphs

)

are amended,

A warning i s added to item.

The characteristics according to the results

of prepar ation of the family of L-CARD voltage measuring converters

for cer tificati on as Means of Measure ment are brought into

correspondence.

Added to item

. Paragraph added

W he n r eading this document elec tronical ly, t o faci litate navigat ion, use the electroni c tree

of the t able of content s (for exampl e, Acrobat Reader) , as well as hyperl inks wit hin the document.

Contents

CHAPTER 1. GE NER AL D E S C R IPT ION................................................................... 7

1.1. Order informa t ion............................................................................................................... 8

1.1.1. Distribution kit ................................................................................................................... 9

1.2. Appearance and main structural elements ................................................................... 10

CHAPTER 2. INSTALLATION AND CONFIGURATION. ....................................... 11

2.1. E-502 con figurati on "by default". .................................................................................. 11

2.2. Internal construction elements and E-502 configuration. .......................................... 12

2.2.1. Configuration of the DAC outputs of the connector Analog (DAC1/+15V/AGND/NC

and D AC 2 /-15V/DGND/NC) ....................................................................................................... 13

2.2.2. Configuration of the resol ution of the active s tate of the digital outp uts DO1 ... D O 16

on the Digital connector. ............................................................................................................... 13

2.3. Functions of the status LEDs on the front panel. ......................................................... 13

2.3.1. LED1. ................................................................................................................................ 13

2.3.2. LED2. ................................................................................................................................ 14

2.3.3. LEDS Link and Activity (on LAN connector ) in modif ications E-502-P-EU. ............ 14

2.4. RESET functions ............................................................................................................... 14

2.5. Serial number. E-502 version number. Module identification in a multi-module

configuration. ............................................................................................................................... 15

2.6. E-502 appli c ation as a par t of user p r o g rams............................................................... 15

2.7. Software installation ......................................................................................................... 15

2.8. Ethernet int erface configu ration .................................................................................... 15

CHAPTER 3. THE MECHANISM AND PRI NCIPLE OF O PERATI ON OF E-502.. 16

3.1. Conventions ........................................................................................................................ 16

3.1.1. Convention on numberi ng ............................................................................................... 16

3.1.2. The assumption on the concept of "frequency" ............................................................. 16

3.2. Introduction (general information) ................................................................................ 16

3.3. Operation prin ciple ........................................................................................................... 17

3.3.1. Reference frequency ........................................................................................................ 18

3.3.2. ADC channel. ................................................................................................................... 18

3.3.3. Digital input channel. ....................................................................................................... 19

3.3.4. Digital output and DAC channels ................................................................................... 19

3.3.5. E-502 sync hr o nizati on gen era l princi ple. ....................................................................... 20

3.3.6. Adjustme nt of the ratio between th e time of setting the signal and the resol u tion for

each ADC channel......................................................................................................................... 22

3.3.7. Rela tiv e s w i tching delays in AD C cha nnels . ................................................................. 23

3.3.8. Rel a ti ve delays of the ADC, DAC and I/ O channels. .................................................... 25

3.4. Operation principle and funct ion circuit....................................................................... 27

3.5. All functi ona l d iff erences of E-502 and L-502. ............................................................. 29

CHAPTER 4. CONNECTION OF SIGNALS. ........................................................... 30

4.1. DGND, AGND circuits ..................................................................................................... 30

4.2. GND, 0 V, GND_USB, CHASSIS circuits ..................................................................... 30

4.3. Location of DGND, AGND, GND, 0 V, GND_USB, CHASSIS circuits on the board

30

4.4. E-502 conn ect ors description .......................................................................................... 31

4.4.1. Connector Analog. ........................................................................................................... 31

4.4.2. Connec tor Digital. ............................................................................................................ 34

4.4.3. JTAG connectors of Blac kfin processor. ........................................................................ 39

4.4.4. Connectors JTAG and UART0 of the ARM controller LPC-4333 (LPC-4337). ........ 39

4.5. The maximum allowable conditions at the inputs and outputs of signal lines. ....... 40

4.6. ADC input operation voltage range ............................................................................... 41

4.7. Preconditions for correct connect ion and correct set t ings of the input of the AD C

E-502.............................................................................................................................................. 43

4.7.1. The ph ysical cau ses of possible pr o blems ...................................................................... 43

4.7.2. Conditi on s for cor rect E-502 connec tion and settings. .................................................. 43

4.8. Calculation of total load power of E-502 output circuits ............................................ 44

CHAPTER 5. SPECIFICATIONS. ............................................................................. 46

5.1. ADC ..................................................................................................................................... 46

5.1.1. Limits of the perm issible relativ e basic erro r of m easuring the A C voltage ................ 47

5.1.2. ADC own input noise. ..................................................................................................... 47

5.1.3. AD C inter-channel passing.............................................................................................. 48

5.2. DAC. .................................................................................................................................... 48

5.2.1. AC voltage playback error ............................................................................................... 48

5.3. Digital inputs. ..................................................................................................................... 49

5.4. Digital outputs.................................................................................................................... 50

5.5. Synchronization in E-502. ................................................................................................ 50

5.6. Ch aracteris t ics of standard interfaces. .......................................................................... 51

5.7. Power supply system and galvanic isolation. ................................................................ 52

5.8. Construction specification. .............................................................................................. 53

5.9. Environmental conditions. ............................................................................................... 53

5.9.1. Nor ma l c on di t i o n s ............................................................................................................ 53

5.9.2. Operating conditions ........................................................................................................ 53

CHAPTER 6. CONNEXION SAMPLES. ................................................................... 54

6.1. ADC entry point conn ect ion ............................................................................................ 54

6.1.1. Connecting to the ADC entry point of single-phase volta ge sour c e ............................. 54

6.1.2. Connection to ADC input with up to 16 differential voltage sources .......................... 57

6.1.3. Connection to the ADC input for the case where the common wire of t he signal

source s has a offset p ot ential Ucm of max. ± 1 V relative to the AGND cir c u it. .................... 58

6.1.4. Measuremen t of the vo lt a ge drop on the c ircuit section in the differe ntial mode (up to

16- channels).................................................................................................................................. 58

6.1.5. Differ ential connect ion of the transfor mer (thr ottle) wi nding with midpoint and offset

potential with respect to AGND ................................................................................................... 59

6.1.6. Example of mixed connection of voltage sour ces "with common ground" and

differential...................................................................................................................................... 59

6.1.7. Connecting a power supp ly to the A DC input ............................................................... 59

6.1.8. The c oordina ted co n ne ction o f re m ote sour c e s of current or v ol tage throug h a lo ng

line with a wave impedance Zw ................................................................................................... 61

6.1.9. The c oordina ted co n ne ction o f a rem ote voltage sou rce throug h a pai r o f lon g l in e

with a wave resistance Zw with matching on the signal source si de ......................................... 62

6.2. Connecting the DAC outputs........................................................................................... 63

6.2.1. Mode "with common ground" 2-channel output ±5 V .................................................. 63

6.2.2. Single-channel differen tial output ±10 V ....................................................................... 63

6.3. Connecting the digital inputs and outputs. ................................................................... 64

6.3.1. Connecting the LED or the optron input. Option 1........................................................ 64

6.3.2. Connecting the LED or the optron input. Option 2........................................................ 64

6.3.3. Connecting a contact to a digital input ........................................................................... 64

6.3.4. Connect the optron output to the synchronization input ................................................ 64

CHAPTER 7. DES I GN D ATA ................................................................................... 65

7.1. Circuit plate draft. ............................................................................................................ 65

7.2. Front panel draft. .............................................................................................................. 66

7.3. Back panel draft. ............................................................................................................... 66

Chapter 1. General description.

L-Card pr esents a data collection system E-502 on the basis of USB and Ethernet interfaces.

E-502 – is a system dev eloped by LLC "L-Card". I t is made on the basis of high q ua lity prod uc tion

of the company, it provides i ts ow n technical s upport and maintenance.

E-502 has the continuity of architecture with L-502

same functionality as the L-502 is subjected to processing, except for the small functional

differences that will be discussed in this manual (s. 3.5, p. 29). The E-502 and L-502 software has

also has continuity (common library functions of the upper software level of the PC, identical to

the sof

• ADC: 16 bits, conversion frequ ency u p to 2 MHz, wit h switching to 16 different ial cha nnels or 32

• Modification E-502-…-…-D has D AC su pport: 1 6 bi ts, 2 cha nnels, out put ± 5 V, asynchronou s or

• Digital input : up to 17 digita l inputs of general pur pose, asynchronou s or synchronous da ta output

• Digital output: up to 16 digital outputs of general purpose, with separate control of the output

tware at the Blackfin level).

e most important characteristics of E-502:

Th

channels with common ground. Subranges: ±10 V”, “±5 V”, “± 2 V ”, “± 1 V”, ±0.5 V, ±0.2 V.

synchronous mode with a conversion frequency of up to 1 MHz for each channel.

mode with a frequency of up to 2 million words per second.

resolution of the high and low byte, asynchronous or synchronous data output mode with a frequency

of up to 1 million words per second.

: only the i nter face with t he PC with t he

• Processor (modification E-502-P-…) Blackfin 530 MHz, SDRAM 32 MB, the JTAG connector

allows to activate ready "advanced" signal processing and control functions inside the E-502 or

independently to be engaged in low-level programming of these functions.

• Galvanic isolat ion provides isolation of di gital a nd analogous signa l inputs/output s to all computer

circuits.

• The system can consist of one or more E-502 modules, synchronized from each other, from an internal

or external synchronization source with an ADC conversion frequency of up to 1.5 MHz.

• Design version "I" (E-502-…-…-…- I) has an industrial temperature range and a lacquer seal.

The E-502 notation system is gi ven in fig. 1-1.

E-

502

-

- - -

Модификация

преобразователя

P

- Процессор Blackfin 500

МГц,

ОЗУ

32 МВ и порт JTAG

присутствуют

X

- Отсутствуют процессор Blackfin

,

ОЗУ и разъём JTAG

U

EU

D

X

ЦАП (2 канала)

присутствует

ЦАП

отсутствует

Преобразователи напряж ения

измерительные

I

+5…+55

°

С

-40

…+

60

°

С

С лакировкой

Нет

индекса

USB 2.0

Ethernet 100

Мбит/

с

USB 2.0

No DAC

DAC (2 channels)

yes

- There is no Blackfin RAM processor

and JTAG connector

- There is Blackfin processor 500 MHz,

RAM, 32 MB, and JTAG connector

Mbit/s

Measur ing volt a ge

converters

No

index

With polish

Converter

modification

1.1. Order information

The E-502 versions and design versions available for ordering:

E-502-P-EU-D-I,

E-502-P-EU-D,

E-502-X-EU-X,

E-502-X-U-D,

E-502-X-U-X.

When ch oosing the modific ation of the E-502 mod ule f o r the o rder , it should be noted that when

you conta ct the L -Card sales department, the previously purchased E-502 module can not be

modified to anothe r modification or design vers ion.

Information on other modifications and design versions you can find in the L-Card sales

department (en@lcard.ru

Fig. 1-1. The notation system of the E-502 module

).

Power adapter network

adapter ~ 220V/ = 12V,

1.1.1. Distribution kit

Except for the E-502 mod ule , the distr ibut ion ki t inc l udes the follow ing acces so ries , dep endin g

on the version:

Accessory Quantity

E-502P-EU-D-I,

E-502P-EU-D,

E-502X-EU-X

DB-37F connecto r 1 pc. 1 pc. 1 pc. Cable receptacle

DB-37M connecto r 1 pc. 1 pc. 1 pc. Cable plug

Cover DP-37C 2 pcs. 2 pcs. 2 pcs. For DB-37 connectors

E-502X-U-D

E-502X-U-X

Note

DJK-10A s t raigh t con nec to r 1 pc. 1 pc. 1 pc. To connect low-voltage power

from a non-standard power

source.

Cable Ethernet Pathcord 5e,

L=1.5 m

USB cable, type A-B, L=1.8 m 1 pc. 1 pc. 1 pc.

0.5A , unst a bilize d

Jumper 2 pcs. 2 pcs. 2 pcs. For all E-502 jumper

1 pc. − −

1 pc. 1 pc. 1 pc. Linear transformer power supply

for m ains supply ~ 220 V , 50 Hz

modif ication s, the enable

confi guration of the digital

outputs is included.

The remaining jumpers are preinstalle d insi de th e E-502 by

"defa u lt", s.

2.1, p. 11

1.2. Appearance and main structural elements

Fig.1-2. Fr ont view (front panel)

Fig.1-3. Back view (back pan el)

Setting the resolution of the

Programmed

Progr amme d c o nt r ol

Progr amme d c o nt r ol

Output setti n g

DAC1

DAC1

NC

Chapter 2. Installation and configuration.

2.1. E-502 configuration "by default".

E-502 comes with presets "by default" corresponding to the table below.

Configuration E-502-P-EU-D

E-502-P-EU-D-I

high and low byte of DO

digit a l ou tputs on the

Analog connector

DAC1 / +15V / AGND / NC

on Analog connector

Output setti n g

DAC2 / -15V / GNDD / NC

on Analog connector

control

(no jumper on

fig. 2-1 on the

left)

(See fig. 2-1)

DAC2

(See fig. 2-1)

E-502-X-U-D

(no jumper on fig.

2-1 on the left)

(See fig. 2-1)

DAC2

(See fig. 2-1)

E-502-X-U-X

E-502-X-EU-X

(no jumper on fig. 2-1

on the left)

(See fig. 2-1)

NC

(See fig. 2-1)

"L-Card" installs this configuration using j ump ers on the board (fig. 2-1) – inside the pack. See

configura tion ex planat ion in subsection

Note: How to programmatically resolve the Ethernet interface, explained in p.

2.2.1, 2.2.2.

2.8.

2.2. Internal construction elements and E-502

Настройка выхода

DAC1 / +15V / AGND

DAC1

(см.

примеч.)

+15V

AGND

Настройка выхода

DAC2 / -15V / GNDD

DAC2

(см.

примеч.)

-15V

AGND

1

JTAG

Blackfin

JTAG

ARM

1

1

UART

ADSPBF523

FPGA

Cyclone

IV

SDRAM

SDRAM

ARM

LPC4337

CPLD

RESET

LAN

USB

+8…+30 VD I G I T A L

Элементы

ЦАП

Настройка разрешения

цифровых выходов DO:

Программное

управление

(по умолчанию)

DO1...16

активны

DO1...8 активны

DO9...16 программно

управляются

DO9...16 активны

DO1...8 программно

управляются

A N A L O G

NC (не

подлючён)

Гальванический

барьер

NC (не

подлючён)

Техноло-

гический

разъём

Технологический

разъём

DO1...8 active DO9...16

Output sett ing

Output sett ing

Galvanic

barrier

Technological

connector

DAC

elements

Technological

Programmed

control

(by default)

DO1.. . 8 software

controlled

DO9...16 active

DO1...16

active

NC (not

connected)

NC (not

connected)

(see

note)

(see

note)

Setting t he resolution of DO

configuration.

ote to fig. 2-1: in modules E-502-X-U-X, E-502-X-EU-X (without DAC), state of DAC1 or DAC2

N

is equivalent to the unconnected state of this o utput.

bott om of th e cha s si s, un scr ew t he 4 s cr ew s and disass emb le t he ho u si ng co ve r s. Rea s sem bl e in the

reverse order.

connector

digital output s:

software controlled

g. 2-1. Internal configuration

Fi

Att e ntion! Technologic al connectors are not designed f or us e r c onnections.

To access the elements of the internal structure, car efully remove the rubber feet fr om the

2.2.1. Configuration of the DAC outputs of the connector Analog

(DAC1/+15V/AGND/NC and DAC2 /-15V/DGND/NC)

If your mo

be connected to contacts 18 and 19 of the connector Analog (fig. 4-3, p. 32).

I

f necessary, you can independently change the configuration of these outputs by rearranging

the jumpers, according to

Analog connector is descr

dification E-502 (fig. 1-1) has DAC, then "by default" the DAC within E-502 should

fig. 2-1.

ibed in section 4.4.1, p. 31.

2.2.2. Configuration of the resoluti on of the active state of the digital outputs

DO1 ... DO16 on the Digital connector.

Activation of the digital outputs on the Digital connector (fig. 4-4, p. 34) is done in a

programmatic way "by default", and, as practice shows, users are satisfied in the overwhelming

maj o ri ty of case s.

B

ut, if necessary, digital outputs can be activated at power-up (without the possibility of

programmed transfer to the third state) – in this c ase, yo u n eed to ins tal l one or two addi tio n al j umpe rs

according to

is not permissible for the connected load.

fig. 2-1. This setting is made when t he initial high-impedance state of the digital outputs

2.3. Functions of the status LEDs on the front p anel.

2.3.1. LED1.

Usually LED1 on the front panel indicates a status of the module data collection:

LED1 state Description

Red light E-502 is connected and in the s ynchronous I/O s tandby mode.

Gree n light E-502 is in the synchronous I/O mode.

No lights Power is off.

I

n case o f u si ng m ore than o ne E-502 module, the user faces the task of identifying the module

with w hic h the progr a m is cur re nt ly ru nning. To solve t his pro blem i n a vis u a l ma nner, you can use

the software function of controlling the red glow of LED1. Of course, the task of automatic module

identi fication can be solved with software, r eading t he module's available serial number.

Not e: b ehavi or of LED1 on E-502 is identical to the behavio r of LED on the L-502 panel.

2.3.2. LED2.

No USB connec tio n (no c able connec ted , no dri ve rs inst alled or the PC

Periodically changing

up, this co uld be eit he r a sign

502 gets into this state

The LED2 on the front panel indicates the state of USB interface

LED2 state Description

Constant red light There is a USB connection at the Full-Speed (up to 12 Mbit/s)

Non-periodic short red

light

Constant green light There is a U SB c onnection at the H igh-Speed (up to 480 Mbit/s)

Variable green light Data transf er vi a USB at the High-Spee d ( up to 480 Mbit/s)

Yell o w orang e light

red-gre e n glow

No lights Power is off

Slow periodic red light

after powe r is on

Data transfer via USB at the Full-Speed (up to 12 Mbit/s)

opera tiona l s ystem has not f ou n d a U SB-devi ce E-502)

E-502 is in the service "bootloader" mode, or after holdi ng RESET

button, or in the software update process.

SDRAM test error.

If the E-502 got in to th is st ate af ter power-

of E-502 failure or a sign of the heavy external electromagnetic

environment in which the E-502 is located, which led to a malfunction.

Contact t he "L-Card" technical support if the Eafter turning on the powe r.

2.3.3. LEDS Link and Activity (on LAN connector) in modifications E-502-P-EU.

Link LED status Description

Yellow glow Connected to Ethernet

No gl o w No Etherne t connection

Note: in the curr ent manu factur ed produ cts, the opp osite logi c of the LINK LED illu minatio n

is p o ssible (this feature is not a malfunction of the E-502). But, in any cas e , if E-502 is programm ed

to operate wit h U SB , Link and Activity LED s will n ot glo w.

Activity LED status Description

Gree n glow Data transmission via Ethernet

No gl o w No data transmission via Ethernet

How to programmatically resolve the Ethernet interface, explained in p.

2.8.

2.4. RESET functions

The secret reset button is used to reset the ARM controller, after which the E-502 wi ll no rma lly

rest art the ARM-controller. For a normal restart, briefly press the RESET button.

The "loader" service mode will be activated after holding the RESET button for at least 10

seconds. The periodically changing red-green glow of LED2 indicates that the E-502 is in the

bootloa der mode.

2.5. Serial number. E -502 version number. Module identification in a multi-modul e con fi gu r ation.

The unique eight-digit product se r ia l number ( on the label on the bottom of the case) serves to

identify the module instance within its life circle. E-502 seri a l number is program-available.

2.6. E-502 application as a part of user programs

LLC "L-Card" supports integration of its modules in the user systems. But when E-502 is

included in any system, the system developer must mention in the documentation for his system t he

E-502 module of t he "L-Card" production, as the component part (the comp leting unit).

2.7. Software inst allation

To install the necessary dr ivers and libraries fo r W indows OS, you must download and run the

installer "L-Card L502 / E502 SDK" http://www.lcard.ru/download/lpcie_setup.exe

For information on installing the driver and libraries under Linux OS, see

http://en.lcard.ru/download/x502api.pdf

.

.

2.8. Ethernet interface configuration

To w ork with E-502 mod ule v ia Ethe rnet , it is req uired to make settings and resol ution of this

inter fa ce i n th e pr ogr am "L -Car d M easu re ment Stu di o" (https://bitbucket.org/lcard/lqmeasstudio/

connecting the module via USB. If Ethernet interface is not permitted, the E-502 module will not

respond to the connection of Ethernet cable (both LEDs Link and Activity on the LAN connector

will be turned of f).

),

Chapter 3. The mechanism and principle of operation of E-502.

3.1. Conventions

3.1.1. Convention on numbering

In all produ cts of the L-Card, the numbering of all physical objects (for example, channel

numbers) in the descr iption of the principle of ac tion and design is always mad e from one !

This a gree ment is c omplet ely unre lated t o the e ncoding method in pr ogram ming , wher e the

numbers of these physical objects can be encoded from scratch or otherwi se, in the context of the

corresponding library function or programming language.

3.1.2. The assumption on the concept of "frequency"

In the documentation for E-502, the frequenc y of discrete signals (e.g., synchronization signals)

is expressed in Hertz, and not in periods per second, as it is common for frequency for a nonsinusoida l proc es s .

3.2. Introduction (general information)

All modifications of E-502 (fig. 1-1, section 1.1) are made on t h e basi s of the same mult il ayer

PCB. Modification is achieved by different variants of the factory assembly. Changing E-502

modif ication s after fac tory assembly is not provided for.

The pr esen ce of th e

considered justified for those users who want to get the maximum of on-board signal processing

capabilities on-board, as well as for advanced users to have their own low-level programming of the

processor, possibly with the use of the JTAG-emulator (s.4.4.3, p. 39).

All E -502 modifications have a galvani c isolation of th e signa l cir cuits (f or L -502 a galvanic

isolation is an option).

DAC with 2 channels (modification E-502-░-░-D) allows to display output analog voltage

levels or voltag e time fu ncti on s.

ADC 16 bits with a con

switching (up to 16 differential channels, up to 32 with a common ground) with voltage subbands

of ±10 V, ±5 V, ±2 V, ±1 V, ±0.5 V, ±0.2 V has an analog ADC path, identical to L-502,

with a maximum conversion frequency of 2 MHz.

Note the limitations up to± 1 V of the operating ra nge of the input signal on the Y and GND32

inputs (for d etail s, see

Instrumental DAC 16 bits 2 channe ls ±5 V provides the opportunity of synchronous (streaming

up to 1 MH z for a channel), asynchronous mode on the selected D AC channel, including mixed

synchronous asynchronous mode on different channels, as well as a cyclic synchronous self-oscillator

from the E-502 inte rnal buff er (2 pages of 1.5 Mco unts.)

Digital output, 16 lines. Similarly to a DAC, i t is possible t o have a synchr onous output of up

to 1 MHz, as well as an asynchronous output, as well as a synchronous output from an internal buffer.

With synchronous output, the frequency is matched to t he frequency of t he DAC output. The output

enable allo ca t e d f or t he lo w a nd high byt e increa ses the flexibili t y of u si ng digital lines, for e xa m ple,

ADSP-BF 523

version frequency of up to 2 MHz with 16/32-channel circuit

4.6).

signal proce ssor wi th SDRAM (mod ificati on E-502-P-░-░) is

confi guration is possible: 8-bit 2-directional data bus + up to 8 data bits per input + up to 8 data bits

!

igital output, operation only in the same

per output. This allows the implementation of controlling bus diagrams for complex digital

devices (sec. 4.4.2.2, p.38).

With synchronous output to the DAC to d

synchr onous mode is supported: in the mode of streaming output, or a self-oscillator from

the internal buffer. At the same time, you can work asynchronously with any output

channels.

No te the limitatio n s of the asynchronous output for external synchronization (n.3.3.4.1).

Digital input, up to 17 lines, synchronous mode of up to 2 MHz or asynchronous one. In

synchr onous mode, the stream fr om digital lines i s synchronous wi th th e A DC st r ea m, but sepa ra te

and independent of the settings of the ADC data collection frame (the frequency of d ata collection b y

digit a l l i ne s i s set separ a t ely and do e s no t de pend o n th e ADC fra m e s ett i ngs) .

It should be n oted that in the E-502, the three highest digits in the group of digital inputs (DI14,

DI15, D I 16) have alternative synchronization funct ions (

The ADC, DAC, digital i nput a nd output streams are synchronized with respect to the same f

reference frequency, wh ich can be assigned programma ti cally: 1.5 MHz or 2 MHz.

Hardware-wise, in E-502, the physical frequency of the ADC and the synchronous digital input

is always equal t o f

Getting all the fractional frequences of the data input f

(where m and n are natural number s) occurs at the hardware processing level in the FPGA and/or in

the Blackfi n proce s s or.

E-502 has a mechanism of the intermodule synchronization (s.3.3.5, p. 20) to fo

synchronous I/O system.

E-502

or output, there is also a physical channel number. This hardware bindi ng of the physical cha nnel

number ensures that the channel number is mistaken even if the top-level program for some reason

lost an arbitrary amount of data.

For advanced users: HOST DMA access mode to the inter nal memory of the signal processor

ADSP-BF5 2 3 a llo ws you t o ap pl y an i nde pen de nt a cc ess c ha nnel t o t he B la ckf in i nter na l m emor y.

This creat es a huge conven ience - "transparency" with low-level Blackfin programming - to see w hat

happens in Black fin memory on an independent channel. To some extent, HOST DMA can replace

JTAG (the convenience of the technology of independent access channel in the signal processor

memory ha s b ee n e va luate d by users even in products E-440/ E14-440 by L-CARD!).

Oper a tion mod e s wi th E-502 v ia USB or Ethernet are alternative . E-502 use s 32 bit data w ords

for a tra nsmis sion via interface s (in each w ord the data is counted wit h the ind e x pa r t) .

has a 32-bit da ta w ord f or mat, in the f orma t of which, besides the actual data for input

, and the physi cal refresh rate of each D AC channe l a n d digital out put is f

ref

table 4-2).

/n and f

ref

/2m output fractional frequencies

ref

rm a single

ref

ref

/2.

When using USB, the E-502 ha s a bandwidt h limita tion of 5 Mcou nts/ s High -Speed, which

must be taken into account while applying the E-502.

When operating via Ethernet, the E-502 has a 2.5 Mcounts/s bandwidth limit on the input.

The inter face function (USB, Ether net) in E-502 is performed by a separate 2 cores ARM

controller LPC4333/4337, which has a separate JTAG connector on the board and an i ndependent

additional UART0 port.

3.3. Operation principle

In section 3.2the general information about E-502 was summarized, in this section further

detai ls are presented. This section in many r es pects repeats a sim ilar section of the manual L-502 due

to the similarit y o f these pr oj e cts.

3.3.1. Reference frequency

f

– a signal reference frequency, from which the conversion proces s e s are s ynchronized to

ref

the ADC, DAC, digital input and digital output. The E-502 uses a common refe rence frequency that

sync hroni zes the star t-up of the ADC, DAC, digital input and digital output to an accuracy of an

integer division of this freq uenc y. In E-502, the refe re nce freq uency sourc e can be inte rn al (2. 0 o r 1.5

MHz) or external (with a frequ ency of max. 2.0 MHz). In particular, the reference frequency from

the neighboring E -502 module ca n be used to form a synchronous multi-module system.

3.3.2. ADC channel.

The a nalog da ta inpu t chann el is a cha nnel wit h dynami c swit ching up to 3 2 input physical

analog channels of the E-502 modul e to the input of a single internal ADC module. The process of

switching chan nels itself is hardw are, according to a pre-configured control table. The input process

itself is conditionally divided into periodically alternating fra me periods and interframe delay with

pre-conf ig ured d ura tions of thes e pe rio ds (in te rfr ame de l ay, in p art icul ar, c an b e se t to zero). Duration

of frame, interframe delay, ADC output sample timing - all these times can be configured, but they

are always a multiple of t

= nsw / f

t

sw

– the ADC channel co mmutation period within the frame, equal to the sampling

ref

ref

= 1/ f

period of the AD C readouts, whe r e n

The preset number of sa mples in the frame and the si ze of the control table n

1 to 256. In each cell of the control table, the physical number of the ADC polling channel is

prescribed. Within the frame, the control table will be read completely: from the 1st to the n

and the read sequence of physical channels will be used in the har dware control mechanism of t he

channel switch.

The cell number of the control table is called the logical channel number. Accordingly, logical

channels ca n be up to 256, and physical - up to 32. For exa mple, it gives the opportun ity to o bta in a

differ ent frequency of polling different physi cal cha nnels within the frame.

Fra m e t ime: t

= nк * t

k

If necessary, between intermittently following frames, a non-zero i nter fra me dela y t

duration n

of synchroni zation frequency periods can be inserted:

d

= nd* t

t

d

ref

= nd /f

, where n

ref

The frame period is equal to the sum of the frame length and the interframe delay:

t

= tk + td = nк* nsw / f

ch

In other words, the frame period t

logical cha n nel o f the contr ol ta bl e.

During interframe delay, the sample of control words does not advance, and the analog channel

switch is always set in accor dance with the first cell of the control table.

Frequency of collection from one logical channel of the control table

f

= 1/ tch= f

ch

where f

= {1,2, …, 256}, n

n

к

ref

/(nк* nsw+ nd),

ref

can be 2.0 or 1.5 MHz for an internal synchronization or ≤2.0 MHz for an external,

={1,2,…,2097152}, nd ={0,1,…,2097151}.

sw

The a bove-mentioned frame structure of the ADC data is shown in

a 3-ch an nel ADC mode ope ration (n

- the period of the synchronization reference frequency.

ref

can be specified by an integer from 1 to 2097152

sw

= nк* nsw / f

sw

d

+ nd/ f

ref

can be s et with an integer from 0 to 2097151

ref

ref

i s equal to the period of data collection from the same

ch

fig. 3-1. Her e, f or e xa m ple,

= 3) is taken with a non-zero interframe delay td.

к

can b e s et from

к

cell

th

wit h a

d

2

1

3

2

3

Канал 1

Канал 2

Канал 3

t

k

nk=3

t

d

t

k

t

ch

Кадр

Межкадровая

задержка

Кадр

Межкадровая

задержка

t

sw

1

Момент сэмплирования отсчётов данных АЦП

Номер

логического

канала АЦП

Sampling timing of ADC data

Logical

ADC

Channel 2

Channel 3

Channel 1

Interframe

Interframe

Frame

Frame

number

delay

delay

3.3.3. Digital input channel.

digital input.

3.3.4. Digital output and DAC channels

of 2* t

outputs.

ch annels assign ed as sy nch rono us, the same sync hr onous mode is suppo rted : eith e r a streami ng or an

self-oscillator from an internal buffer.

3.3.4.1. Restrictions on the current implementation of asynchronous output during external synchronization.

conf ig ured fo r inte rna l sync hron izat io n. B ut async hron o us output to dig ital lines a nd to the DAC wi ll

not function in the standby mode for external synchronization of the star t of data acquisition or

waiting for more than 1 μs of the external clock of the ADC conversion.

Fig. 3-1. Illustration of the personnel principle for acquirin g ADC data

Sync hronous digital in put occurs with a period of t

where n

={1,2,…,2097152} is a configurable frequency division factor for synchronous

din

ref

* n

din

,

Synchronous digital output, as well as updating both channels of the DAC, occurs with a period

. If th e data bu f fer for t he outpu t an d t he D AC i s e mpt y, t hen the l ast va lue i s h eld a t th e

ref

With any DAC channel and digital output, you can work asynchronously, with the other

Asynchronous output to digital lines and to DAC in the operating mode will always work when

3.3.5. E-502 synchronization general principle.

!

502 there is a frequency limitation at the input

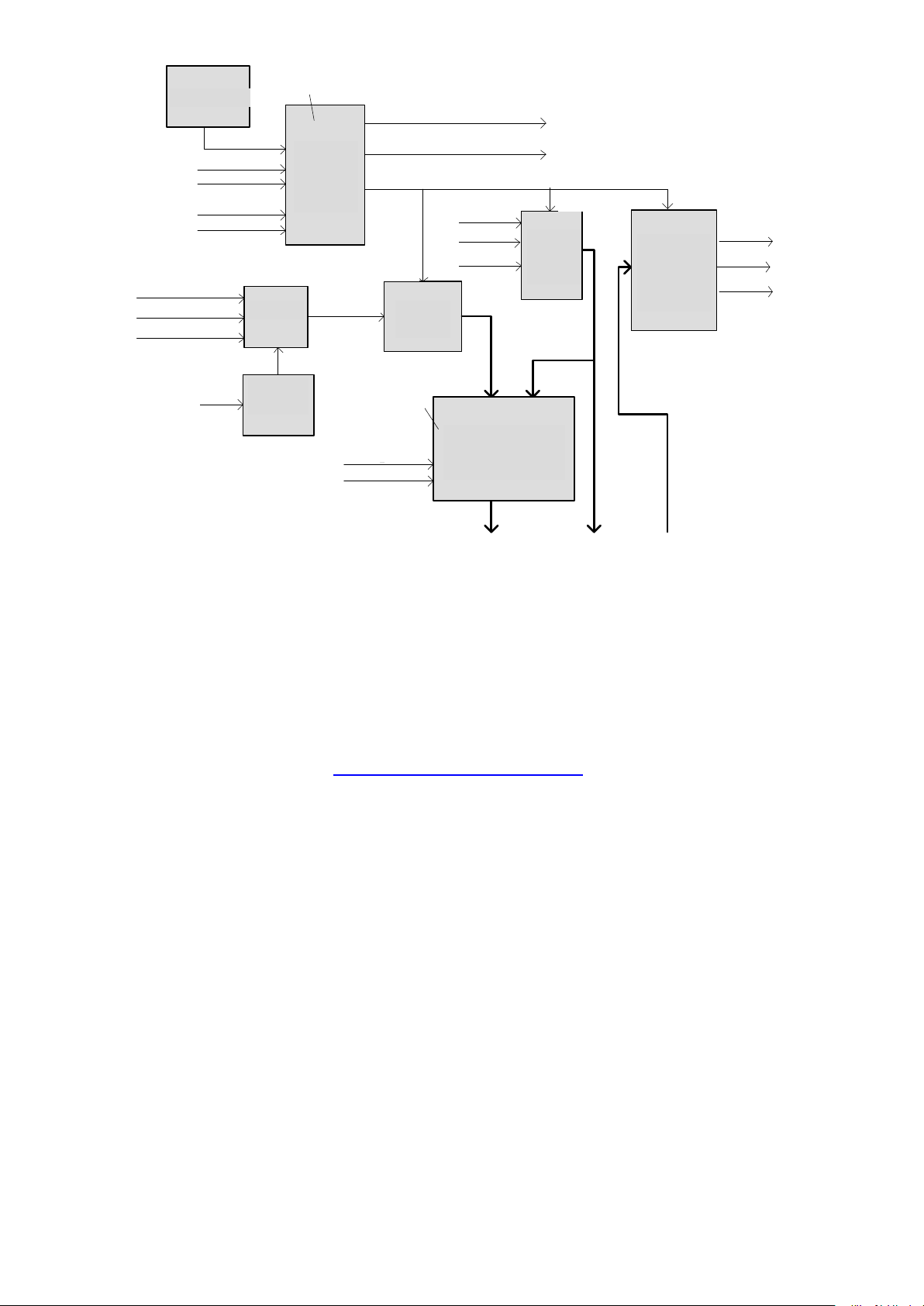

The fig. 3-2 shows a simplified block diagram explaining the general device of the

sync hroni zati on syst em in E-502. E-502 s ync hro ni zati on sy ste m co nsi sts of two part s: pri mary and

secondary synchron ization circui ts.

3.3.5.1. Primary sy nc hron iz ati on.

The pri m ary s ync hro nizat ion c irc uit (I) according to the setti ngs sel ect s the corr espon ding

external or internal source of the reference frequency, as well as the external or internal source of the

start signal. Using the selected signals, circuit I generates an internal reference signal f

sequence of synchronization pulses with a period t

strictly bound by this scheme to the external or internal start event, and all I/O equipment is

synchr onized (a nd simultaneousl y starts) from this sequence: nodes of the ADC (including the logic

of the control table), DAC a nd digital I/O. These nodes con tain the corresponding frequency divide rs

.

f

ref

We list all possible options for user settings related to the selection of sources of reference

frequency signals:

• Internal generator 2.0/ 1.5 MHz of this E-502 module (setting by default)

• The reference frequency from the DI_SYN1 input (on the front or on the drop)

. Moreover , the b egin ning of thi s sequ ence is

ref

as a

ref

• The reference frequency from the DI_SYN2 input (on the front or on the drop)

• The referenc e frequen cy from t he CONV_ IN input from the neighboring E-50 2, which act s as the

master.

We list all possible options for user settings for selecting s ources of t he start event of t he E-502

I/O system:

• Prog ram start from PC (default setting)

• On the signal from the input DI_SYN1 (on the front or on the drop)

• On the signal from the input DI_SYN2 (on the front or on the drop)

• By the signal from the input START_IN from the neighboring E-502, which acts as the master.

Each E-502 module always translates via its outputs CONV_OUT and START_OUT,

respect ively, its internal refer ence and start signals for one E-502 slave module.

02 module can be, at the same time, t he ma ster for one or two adjacent modules and t he

E-5

slave for the other adjacent E-502. Thus, synchronization of several E-502, connected by a chain, as

well as branching from one master to three slaves, is supported. The possible topology of

the synchronization circuits is discussed in detail in sec.4.4.2.1, p.37.

The pri mary sy nchroni zatio n circuit provi des sync hroniza tion of th e frequen cy and pha se of

the ADC , DAC and cycle cyc les of the digit al input and o utput sys tem. It is unde rstood th at in a multimodule synchronization system, the user will be a b le to in te l li ge n t ly set the contr ol t able s of dif f e ren t

modules, as wel l a s the divis ion of the r e f er ence frequen cy for th e required inpu t -outpu t proces s e s.

Note that for the slave ECONV_IN – no m ore than 1.5 MHz. Thus, two or more slave E-502 modules

can be s ynchronized only at a r e f erence fr eque nc y o f 1.5 MH z from the ma s t er .

Stopping the primary synchronization scheme is done only programmatically and

asynchronously.

!

The functionality of the secondary synchronization is embedded in the project,

Узел

АЦП

Узел

ЦАП и

цифрового

вывода

Узел

цифр.

ввода

Комму-

татор

Схема

первичной

синхрони-

зации

E-502

Генератор

f

ref

f

ref

Общие условия синхронизации всех процессов ввода-вывода

в E-502 (выбор опорной частоты и условий старта)

DI_SYN1

DI_SYN2

DI_SYN1

DI_SYN2

CONV_IN

START_IN

START_OUT

CONV_OUT

К ведомому

E-502

От ведущего

E-502

Внешняя

синхронизация

DI_SYN1

DI1...DI16

DI_SYN2

Управля

ющая

таблица

DAC2

DO1...DO16

DAC1

Cхема вторичной

синхронизации

данных АЦП

Поток данных “на ввод” Поток данных “на вывод”

Синхр.

Синхр.

Синхр.

Синхр.

X1...X16

Y1...Y16

GND32

2.0 / 1,5 МГц

Вход Выход

I

II

Схема селекции

данных АЦП в

зависимости

от вторичных

условий

синхронизации

Data flow "to input"

To E-502

Scheme of ADC

DAC and

output node

Generator

Primary

E-502

ADC secondary

data scheme

Digital

node

Control

table

Switch

ADC

node

MHz

External

synchronization

From the master

General synchronization conditions for all I/O processes

Data flow "to output"

Output

Input

Synch.

Synch.

Synch.

Synch.

E-502

in E-502 (selection of reference frequency and start conditions)

slave

synchroniz

ation

scheme

data selection in

dependence

from the

secondary

synchronization

conditions

Fig. 3-2. Synchronization system structure in E-502

3.3.5.2. Secondary synchronization.

input

synchronization

digital

but is not currently implemented. You can find out about the availability of this

in the sales department of L-Card.

functionality

The se co ndar y s ync hro nizat io n circ ui t (II) is t he ADC data s electi on cir cuit depen ding on

the secondary synchronization conditions, operating exclusively against the background of the

previ ously started clock signal from the out put of the primary synchronization circuit (I) , i.e. aga in st

the back gr ound of t he star t ed dat a stream of th e ADC.

The fol l owin g ADC data r esol u tion s y nchroniza tion modes are supported:

• No syn c hroniza tion ( tr a n s pa renc y m od e)

• Synchronization from an analog signal in the selected ADC channel

• Digital synchronization with the selected signal from the inputs DI1 ... DI16, or

DI_SYN1, or DI_SYN2

he following modes of sensitivity to the fluctuations of the synchronization signal are

T

supported:

• Enable of ADC data on the e dge (drop) of an anal o g or di gi ta l signa l

• Enable of A DC d ata at a l evel "above the threshold" or "below the threshold" (for analog

synchronizati o n) or at the logic level "1" (for digit a l s yn c hr o nization)

The fol l owin g ADC data i nhi bit mod e s are supp or ted:

• Software p rohib ition (stop ) with the possibility of re-a uth o riz a tio n (if the p rev io usly se

e

nable condition is repeated) without restarting the primary synchronization scheme

t

• Automatic prohibit ion (stop) after entering the specified number of frames (from 1 to

32

-1 frames) with the possibility of re-authorization (if the previously set resolution

2

ondition is repeated) without restarting the primary synchronization scheme

c

3.3.6. Adjustment of the ratio between the time of setting the signal and the resolution for each ADC channel.

Above was the principle of the frame-by-line input of AD C data, which was applied in all LCARD ADCs with the input channel switch, up to synchronization frequency, frame size and

interfra m e de l a y. B u t i n L-502 and E-502 this principle is developed for the better adapta tion to the

output physical properti es of the signal source. Further we will discuss it more pr ecisely.

If E -502 is used at the highest possible data acquisi tion frequency from each channel, then set

= 1, whic h means that the samp ling period of one measurement channel is tsw = t

n

sw

only one AD C sa mple i s con vert ed. For exa mple, for f

=2 MHz t imet

ref

sw

= t

ref

short switching period of the channel switch, which imposes restrictions on the output impeda nce of

the signal sour ce (and t he wires from it): the impedance should be suffi ciently smal l (not mor e than

50 Ohm) and not have a large reac ti ve component, so that the duration of the transient proce s s caused

by circuit switching does not exceed 0.5 μs. In other words, the signal sourse should be no more than

50 Ohm and have a short or coordinated cable. For those who used the L-783, the se req ui reme nts and

these application conditions roughly correspond to the conditions of application of the L-783 in the

mult ich anne l mode at the m axim um AD C conv e rsion frequency of the 3 M Hz, b ut w it h the diff e rence

that the ADC resolution of the E-502 is 16 bits rather than 12, and the electronic switch in the E-502

is much more "qu iet" (i.e., injects significan tly less p arasitic ch arge into the signal circuit at the time

of commutation, and the ref ore causes a significantly smaller shock excitation for a pos sible t ransient

proces s in the signal circui t) .

But if it is required to use the E-502 at a data acquisition rate for each channel less than the

maximum, and it is possible to reduce the switching frequency, then in E-502 with internal

synchronization there is no reduction in the frequency of ADC startup, and n

as it is sh ow n in th e e xam ple on

fig. 3-1. But, in the sense of n

– this is the number of cycl es of

sw

> 1 is set, for example,

sw

ADC co nv ersi on f or one switching period. In the E-502 it is set by default that for n

read outs are flipped, except for the la st one, during t he switching period. It creates th e maxi mum

settling time a fter commutation (due to "idle" ADC conver sion cycles) , therefore the least stringent

requirements are imposed to the impedance of the signal source. On

fig. 3-3, with n

conditions ar e set "by default" for the logica l channel 1: the first two counts are always discarded,

and t he thir d one i s used. But th e real ta sks of using multic hannel ADCs do not assu me that the

impedances of the signal sources are the same, and for channels with connected low-impedance

sources it would be good not to discard at least some of the ADC samples, but to use them for

avera ging the data, thereby increa sing the ena ble when measuring t his channel. Such option is

provided for in E-502 due to the f act that in every ce ll of the cont rol tab le, besid es the phys ical channel

number, the re is als o th e ave ra g ing f acto r n

, by def aul t, nav= 1. Averaging factor nav ={1,2,…,128}

av

means: "how many counts of the ADC from the end of the swit ching cycle of this channel will be

used to a vera ging t he data ". Acc ordi ngly, n

= nsw - n

su

means "how many ADC c ount s from t he

av

begi nni ng of the swit chi ng cy cl e of th e giv en cha nn el wil l be di sca rd ed ", or "how man y peri od s t

will be used to set the sig nal at th e ADC in put a fter sw it chin g ".

For e xamp le, on

whi ch m ea n s tha t for n

fig. 3-3 f or na viga tional cha nnel 2 , n

=3 the result of the last two conversion periods in one switching phase will

sw

= 2 i s install ed in th e control ta ble,

av

be used fo r averagi ng, and one fi rst period is added to the time of s igna l est abli shme nt afte r swit ch ing.

For log ical channel 3, al l three samples of the ADC are used for ave raging, and the refore the minim um

time is assigned here to establish a signal after switching.

, during which

ref

= 0,5 μs is a fairly

>1, all AD C

sw

=3, such

sw

ref

1 2 13 2

Канал 1

Канал 2

Канал 3

t

k

nk=3

nd=2

t

d

t

k

t

ch

nsw=3

Кадр

Межкадровая

задержка

Кадр

Межкадровая

задержка

nav=1

nav=2

nav=3

nsu=2

nsu=1

n

su

=0

Номер

логического

канала АЦП

Момент сэмплирования одиночного отсчёта данных АЦП

Моменты сэмплирования отсчётов данных АЦП и выдача усредненного отсчёта

Отброшенный отсчёт данных АЦП

t

ref

t

sw

3

1

ADC logical

channel

Sampling time of ADC data single sample

Sampling time of ADC data and output of averaged readout

Discarded ADC data sample

Interframe

Interframe

Frame

Frame

Channel 1

Channel 2

Channel 3

number

delay

delay

Fig. 3-3. The pr inciple of obtaining ADC data (in detail)

fig. 3-3 it also follows that the set non-zero interframe delay actually increases the settling

From

ti me fo r the firs t lo gic al ch anne l. This can be used, for example, by associating the first logical channel

with t he physical channel to which the signal source is connected by the largest impedance.

It can be argued that by setting optimal n

optimize the timing of the signal conditioning associated with the inter-channel passage and the

resolution of the ADC.

It is i m p ortan t to no te t ha t i n th e E -502, the ADC averaging algorithm described here ( by the

simple avera ge me thod) is considered as an inseparable part of the ana log-to-digital converter itself,

alth ough p hy sicall y the a vera ging pr oc edur e is pe rform ed by mean s of F PGA u sing 2 4-bit inte ger

arithmetic.

random components of the si gnal of different nature, improves th e s ignal/nois e by suppressing

the hig h-fre quenc y compo nents o f the s pectr um abov e the Ny quist f requenc y of 0 .5*f

giv en ph ysic al ch anne l as socia ted wit h one (or more) logi cal cha nnel. No t e in pa ssi ng t hat di git al

filtering by the Blackfin processor (or high-level software) has a fundamentally different active

filte r ing area, bec ause it is below the Nyquist freq uency.

Such an averaging operation increases the real resoluti on of the ADC by suppressing the

Once ag ain , we emphasize that "by default" in the E-502 settings n

does not occur by default.

3.3.7. Relative switching dela y s in ADC channels.

where the magnitude of the relative signal delay between the ADC channels is important for

measuring relative phase delays. For this class of problems, the theoretical calculated latency values

in the ADC channels are taken into account in the delay equalizati on algorithm based on one or

This i nfor mat io n will be im por tant o nl y for t hat cla s s o f multi -channel data acquisitio n tasks

anot h er m et hod of si gna l interpolation.

/ nav settings for each channel, we are tryin g to

su

=1 is set, and "averaging"

av

for a

ch

For ADC mode without averaging (nav=1), the relative switching delay between adjacent ADC

chan nel s wit hi n one fr am e (in th e ord er o f polli ng th e con tr ol ta bl e) is equ al to t

last channel of the previous frame and the first channel of the next one i s t

If the averaging mode is used (n

>1 ) , w her e nav are select ed equal for all ADC channels, t he

av

absolute delay for each channel will decrease by the same amount 0.5*n

delay will remai n equal to t

between neighboring channels of one f rame and equal t

sw

sw

av*tref

, and between the

sw

+ td.

. Theref o re, the rel ative

+ td between

sw

the nearest cha nnels of neighboring frames separated by inter frame delay.

If th e a v er aging mode is u sed (n

>1 ), wh er e nav ar e assi g ned in the co n trol t a ble different for

av

i- and j-th logical ADC channel, the absolute signal delay on the i- channel will decrease by

0.5n

+ 0, 5* t

t

sw

av

(i)*t

, and the relative delay j channel towards the previous i- ( within one frame) becomes

ref

(nav(i)- nav(j)), or becomes equal to tsw + td + 0,5* t

ref

(nav(i)- nav(j)) b e tween the nearest

ref

i-th and next j-th chann els of n ei gh bor ing fra me s s epa rat ed by int er fra me dela y ( if mor e pr e cis ely,

for the last channel in the fr ame always i = n

, and for first, always j = 1).

k

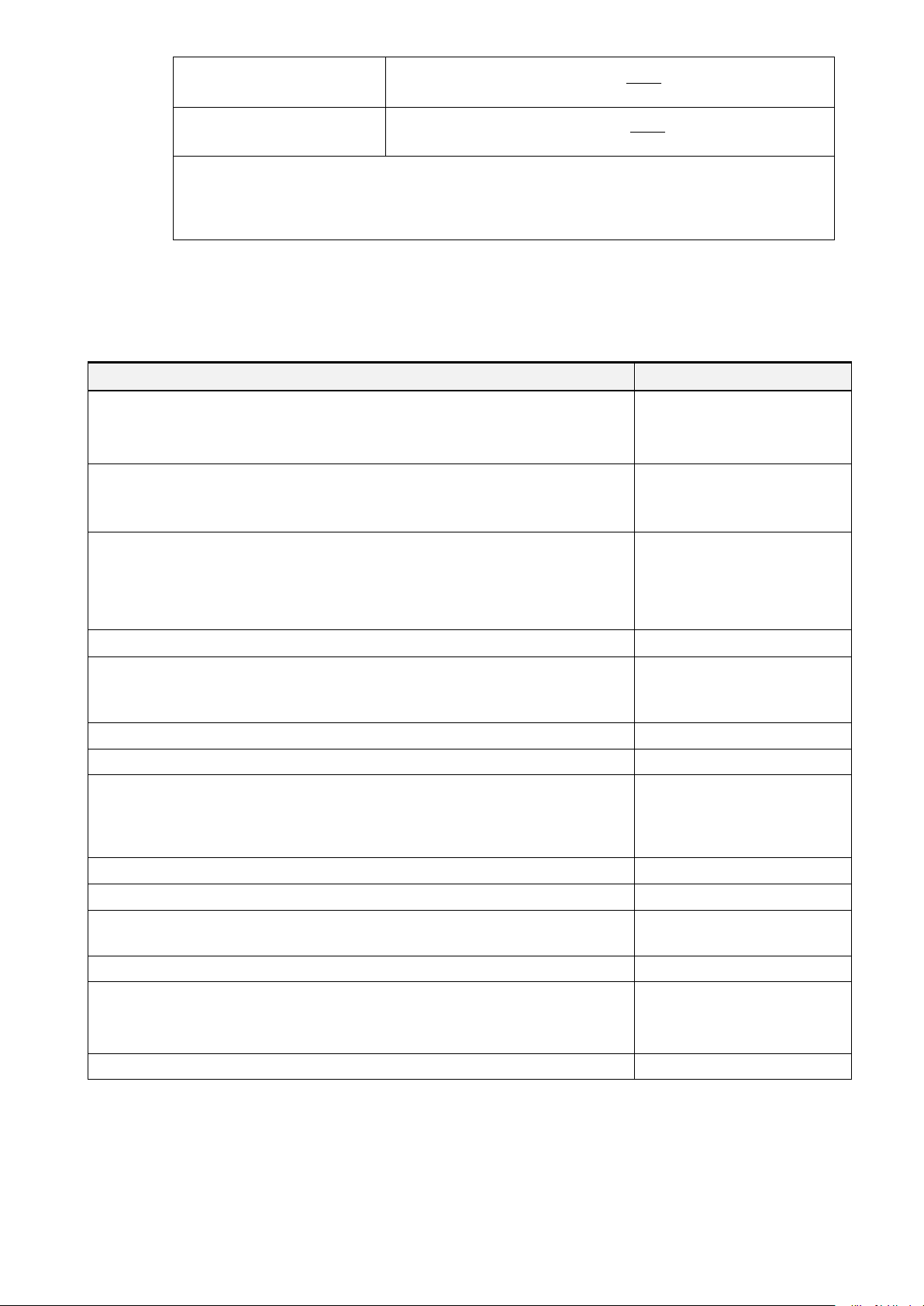

3.3.8. Relative delays of the ADC, DAC and I/O channels.

Description

Desig-

Timing sample

Minimum

Typical

Maximum

Reference frequency period

t

500 ns (2 MHz)

Durat ion of the signal pulse CONV_ OU T

tW

50 ns

The delay time from the front CONV_OUT

t

0 ns

The time to set the state "1" to

t

45 ns

DAC1,

DAC2

CONV_OUT

START_OUT

DO

DI

1-ый отсчёт DO 2-ый отсчёт DO

Выборка

1-го отсчёта АЦП

3-ий отсчёт DO

t

REF

2*t

REF

2*t

REF

Выборка

2-го отсчёта АЦП

t

ADC

t

DI_SU

t

DI_H

Выборка

1-го отсчёта DI

Внутренний

преобразо-

ватель (АЦП)

Выборка

2-го отсчёта DI

1-ый отсчёт DAC1, DAC2 2-ый отсчёт DAC1, DAC2

3-ий отсчёт

DAC1, DAC2

t

DO

t

DAC

Выборка

3-го отсчёта АЦП

Выборка

3-го отсчёта DI

t

W

t

ST_SU

t

ST_H

X,Y,

GND32

t

ADC_SU

Sample

3rd ADC count

Sample

2nd ADC count

Sample

1st ADC count

Sample

3rd DI count

Sample

2nd DI count

Sample

1st DI count

1st DO count

2nd DO count

3rd DO count

3rd DAC1,

DAC2 count

1st DAC1, DAC2 count

2nd DAC1, DAC2 count

Internal

converter

(ADC)

Fig.3-4. Synchronous I/O diagram

In the above-mentioned s ynchr on ous I/O di agram , t he out pu t si gnal CO NV_ O UT is used as a

reference clock signal, with respect to which all I/O delays are described . Temp or al paramete rs of the

diagram are describe d in the table below. The delays in the ADC channel are given for the operating

mode without averaging the data and without allocating additional cycles of the ADC for setting the

signal

Group de lay time of anal og channel of ADC

channel in E-502

to the sampling time of the ADC chip

START_O UT be f ore the fro nt

CONV_OUT

(start of data col l ectio n)

nation

REF

t

ADC_SU

ADC

ST_SU

667 ns (1.5 MHz)

15-70 ns

Description

Desig-

Timing sample

Minimum

Typical

Maximum

Time of holding st ate "1" to

START_OUT after the front

t

150 ns

The time to set the da ta at the D I input

t

5 ns

Data hold time at the DI input

t

-1 ns

CONV_OUT

(terminati o n o f data coll e ction )

nation

ST_H

DO delay time relative to the front

CONV_OUT

The group delay time of the sig nal at the

output of th e DAC rel ative to the front

CONV_OUT

(delay of the DAC chip plus the delay of

the analog filter- buffer at the output of

the DAC)

DI_SU

DI_H

tDO

t

DAC

6 ns

2 µs

ARM

LPC4333/

4337

HOST

DMA

ADSP-

BF523

Порты

в/в

Схема

первичной

синхронизаци

и E-502

Схема

вторичной

синхронизации

данных АЦП

FPGA

Cyclone IV

АЦП

Комму-

татор

ЦАП

Цифровой

в/в

JTAG

X1...X16, Y1...Y16, GND32

DI_

SYN1

,

DI_

SYN

2

DO1...DO16

DAC1

, DAC2

Подсистема

ввода

-вывода

DI1...DI16

гальваноразвязка всегда

присутствует в E-502

Узел гальвано-

развязки

Только для E-502-P- -

Только для E-502- - -D

CONV_IN, START_IN

CONV_OUT, START_OUT

Функционально

близкая к L-502

часть

сбора/

выдачи

данных и

обработки.

Ethernet

PHY

Ethernet

Гальвано-

развязка

Ethernet

RMII

SDRAM

32 МБ

Только в модификации с Ethernet

Flash-память

2 МБ

USB

Reset

LED

1

LED2

Link

Activity

SDRAM

32 МБ

Интерфейсная часть.

AGND, DGND

GND

Цепи

изолированы

Interface part.

Only in the modification with Ethernet

Flash memory

SDRAM

Ethernet

isolation

Channel 3

I/O sub-system

O/I

ADC secondary

32 MB

E-502 primar y

scheme

there is always a galvanic

Functionally

close to the L

502 part of the

data collection/

transmission and

pro

Circuits are

isolated Only for

Galvanic isolation

node

Switch

Digital O/I

ADC

DAC

Only for

Channel 3

3.4. Operation principle and function circuit

synchronization

isolation in E-502

cessing.

E-502 operational scheme is nominally divided in two parts:

1. The part related to the collection/output of ADC/DAC data is dig ita l I/O. This part

2. E-502 interface part on the basis on LPC4333 (LPC4337) ARM controller, with

All E-502 modif icat ions have a LPC4333 (L P C4337) A RM cont rol ler and a galvan ic isol atio n.

synchronization

-

32 MB

2 MB

repeats the architecture of L-502. DAC and signal processor ADSP-BF523 presents

data scheme

Fig. 3-5. B lock diagram

ports

galvanic

depends on the E-502 modification. The FP GA is focused on the logic of data collection

control, the A DC c a li b ra tio n lo g ic, th e secondar y synchr oni zat ion l ogic (

3.3.5), and the

interface with the LPC4333 (LPC4337) ARM contr oller and the ADSP -BF523 signal

processor.

USB and Ethernet support. Ethernet option depends on the E-502 modif ication.

Flash-memory with a capacity of 2 MB is desi gned for stor ing FPGA firmwar e, calibration

factors, factory serial number. Half the amount of Flash memory is provided for user tasks.

The E-502 I/O subsys tem (in par t 1.) contains nodes for the channel sw it c h, ADC, DAC, digital

I/O, as well as the primary synchroni zation circuit (

3.3.5).

A galvanic isola tion node isolated all cir cuits of the I/O sub system from circuits electri cally

connected with any other circuits.

Signal processor ADSP-BF 523 with S DRAM 32 MB is des igned fo r add itio nal d at a proce ss ing

and mana gement within user tasks. If the processor is enabled, the entire data stream and the I/O

subsystem are tran sferre d thr ough t he pr oce ssor' s I/O port s. For exa mple, it i s possi ble t o cr eate a

con trol loop th rough a sign al process or using al l the cap abilities of E-502 data coll ection and delive ry.

Independent processor a nd data transfer Interface is performed through the HOST DMA processor

port t o the ARM -controller. The processor has a JTAG connector on the board.

ARM controller LPC4333 (LPC4337) has it s

independent SDRAM 32 MB and hidden R eset

button, located on the E-502 front panel. The test of this SDRAM is always done after the power

is turned on (the error is indicated by LED2, s. 2.3.2, p. 14).

P

rocessors LPC4333, LPC4337 are identical, in terms of their resources involved, and the

option of bundling does not affect the consumer properties of the product

1

. ("L-Card"

The manufacturer reserves the right to optionally complete the E-502 module either with the

LPC 4333 or LPC 4337 p rocess o r without any dist inct ive pr od uct ma rking and without corr espond ing

differences in product passports.

A short press of the Reset but ton makes a normal reset of the AR M controller.

A long press (more than

10 s) of the Reset button (s. 2.4, p. 14) shifts the E-502 to a special

"loader" mode via USB. A special mode is needed to update the E-502 firmware and change the

Ethernet IP address.

A

fter power supply is applied to the E-502, the f irmware will be dow nloaded to the FPGA from

the Flash memory (

fig. 3-5), and the E-502 in ternal power s upply system will be fully turned on, after

which the E-502 will be ready for norma l operati on.

E-502 swit ches to work with USB or Ethernet after tur ning on t he po wer au t omat ica ll y on the

interface from which the first access to the E-502 will take place. Parallel operation from both

interfac e s is n ot supported.

1

distinctive product marking and without corresponding differences in product passports

"L-Card" reserves the right to optionally equip the E-502 module with either the LPC4333 or LPC4337 processor without any

3.5. All functional differences of E-502 and L-502.

PCI Express card (installed

The function of the inputs DI15,

DI16 is combined with the function

module synchronization

inputs CONV_IN, START_IN,

input of

external synchronization

up resistor of

resistor of DI digital

502 modifications

mode for output to the

Is supported by PC software

502, a data buffer 2 pages of 1.5

Functional difference L-502 E-502

Structure

ins ide the PC )

External module in relation to the

PC.

Int erfa ce wi th the P C PCI Express 1.0 USB 2.0

Ethernet (100BASE-TX)

Intermodule

synchronization interface

Uses a different connector.

CONV_IN, ST ART_ IN in puts

Has a singl e Digital c onnector wit h

digital I/O sig nals.

have constant pull-up r es istor s

to "zero ".

of the inter-

respectively.

DI15/CONV_IN, DI16/START_IN

inpu ts ha ve di ffe rent pr og ram ma bl e

pull-up resistors to "zero" (s.

34).

p.

The second 2

DI_SYN2

Is present separately on the

internal connector L-502.

Progr a mma ble pul l-u p r esi stor

Is combined w it h D 14 input.

Programmable pull-

DI14/ DI_SYN2 input

of DI_SYN2 input

4.4.2,

Programmable pull-up

Is present (separate for the high

and low byte)

inputs

Galvanic isolation Not all E-

hav e i t

Cyclic self-oscillator

driver.

DAC and digital output.

C

omparing to L-502, i n E-502 DAC meteorological characteristics have been improved (s. 5.2)

while reproducing direct and alternate current voltage.

No

All E-502 modifications have it

Is supported by the interface ARM

con tro ller L PC4333( 4337) within E-

Mcounts.

2

E-502

The first external clock input DI_SYN1 is available on the external connector in the L-502 and on the Analog connector in the

)

(f iguratively: G2). Thes e ci rcuits are connec ted to the common wi re of the ARM con troller and

AGND

DGND

GND

0V

CHASSIS

GND_USB

Фильтр

Гальванический

барьер

G2

G1

Galvanic barrier

Filter

Chapter 4. Connection of signals.

This section contains information on E-502 connectors, their contacts' purpose and main

characteristics of E-502 inp uts and out puts, related to the c urrent connection.

4.1. DGND, AGND circuits

AGND is a commo n wire circuit of isol ated analog circuits : ADC inputs and DAC outputs.

DGND is a common cable circuit of isolated digital circuits: digital inputs and outputs.

Inside the E-502, the AGND and DGND circuits have a common connection point

!

(figuratively: G1 ), but th ese cir cu it s are is ola t ed fr o m GND , USB m E t her ne t and E-502 power

input (

4.2. GND, 0 V, GND_USB, CHASSIS circuits

GND is a common w i re circuit of digital nodes of E-502 module in the non-isolated part.

0 V is a circuit of the zero potential of the low-voltage E-502 power input.

GND_USB is a common wire circuit of USB interface.

CHASSI S is a c ircui t f or chas sis connect ion ( onl y i f E-502 is us ed wi thout cover – for embedded

application) and signal cables display

!

Inside E-502, GND, 0 V, GND_USB, CH ASSIS circuits have a common connection point

fig. 4-1)

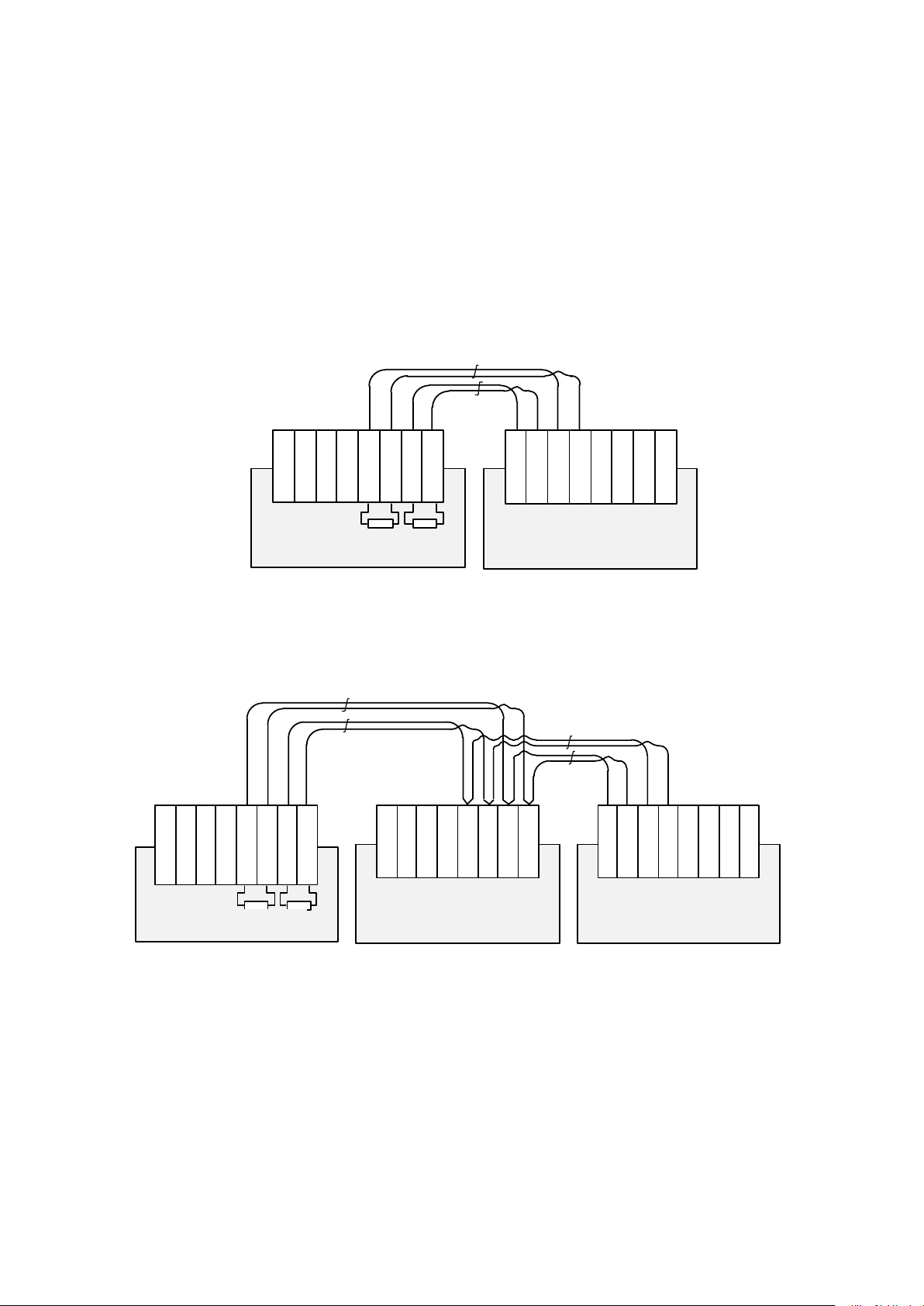

4.3. Location of DGND, AGND, GND, 0 V, GND_USB, CHASSIS circuits on the board

schematically their belonging to different functional parts of the E -502.

the non-is ol a ted USB interface (fig. 4-1).

Fig. 4-1: Internal connection of the "common wires" circuits in E-502.

In sub it ems 4.1 and 4.2the purpose of these circuit s is explained, and the figure below shows

1

JTAG Blackfin

(GND)

JTAG ARM

(GND)

1

1

UART

(GND)

ADSPBF523

FPGA

Cyclone

IV

SDRAM

SDRAM

ARM

LPC4337

CPLD

USB

(GND_USB)

D I G I T A L

Элементы

ЦАП

A N A L O G

Гальванический

барьер

Отв. 3,05 мм

GHASSIS

Корпус

разъёма

(CHASSIS)

Корпус

разъёма

(CHASSIS)

Цифровые

сигналы

(DGND)

DI_SYN1

(DGND)

Aналоговые

сигналы

(AGND)

Изололированные

входы Ethernet

GHASSIS

Отв. 3,05 мм

GHASSIS

0 V

DAC

elements

Digital signals

Port Ø3,05 mm

Port Ø3,05 mm

Connector

Isolated Ethernet

Galvanic barrier

Connector

chassis

Analog

signals

chassis

inputs

Fig. 4-2: The locat ion of the "common wires" circuits on the E-502 board

In particular, GND is a common wire for internal interfaces UART, JTAG Blackfin, JTAG

ARM.

If you use a sep arate E-502 board without a chassis

(CHASSIS), it is recommended to connect it to the solid metal surface of the chassis (case

cons truct ion). Two ri ght por ts of 3.05 mm on fig. 4-2 have a metal co at ing c onnec ted to a CHASSIS

3

in the emb edde d ch assis circuit applications

circu i t, and t w o left ports o f 3.05 mm are isolated from the other circuits. These 4 mounting ports

are used to secu re the E-502 board.

4.4. E-502 connectors description

4.4.1. Connector Analog.

Connector Analog is a 37-pin 2-row type DRB-37M plug on the front panel of the E-502. The

conductive connector contact piece (shield) is electrically connected to the GND signal ground

circuit. On the shield of the cable part of the conne ctor, the shield of the signal c able can be direc tly

sealed. The c onne ctor Analog shi el d doe s not ha ve a con tact wit h AGND , DG ND and oth er cir cui t s

of the Analog connector.

3

Here we do not consider the usage accuracy of the certified Measuring Device without a standard chassis.

Signal name

Commo

Direction

Description

X<1…16>

AGND

Input

recommended to be connected to

Y<1…16>

AGND

Input

recommended to be connected to

1

20

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

X16

X15

X14

X13

AGND

DAC1 / +15V / AGND / NC

Y2

Y1

GND32

DI_SYN1

X12

X11

X10

X9

X8

X7

X6

X5

X4

X3

X2

X1

Y4

Y3

Y6

Y5

Y8

Y7

Y10

Y9

Y12

Y11

Y14

Y13

Y16

Y15

DAC2 / -15V / DGND / NC

GND

Table 4-1: Connector Analog

4

The common wire circuit for the specified signal input or output

n point4

g. 4-3: Connector Analog

Fi

• Non-inverting channel voltage input 1 ... 16 for differential and

"common ground" mode:

•

Operation voltage range: ±10 V (see the details in section 4.6 p. 41).

• Unused inputs X <1 ... 16> are

AGND or the cor respond ing phy sic a l cha nnel not t o be inte rrogat ed

programmatically.

• Inverting channel voltage input 1 ... 16 for differe ntia l mode.

• Input channels 17 ... 32 for the mode "wit h common ground".

•

Operation voltage range: ±10 V (see the details in section 4.6 p. 41).

• Unused inputs X <1 ... 16> are

AGND or the cor respond ing phy sic a l cha nnel not t o be inte rrogat ed

programmatically.

Signal name

Commo

n point4

Direction

Description

DAC1

2.2.1

AGND

Output

For modif icati ons, E-502-░-░-D can be configured with a jumper as

DAC2

2.2.1

AGND

Output

For modifications, E-502-░-░-D can be confi gur ed with a jumper as

AGND

— — Analog gr ound

GND32

AGND

Input

DI_SYN1

DGND

Input

Synchroni zation input 1, which can also act as an additional input to

/ +15 V

/ AGND

/ NC

(see section

)

/ -15 V

/ DGND

/ NC

(see section

)

the output of the 1st channel of the D AC (voltage output in the

range -5 .. . + 5 V).

For any modificati ons, the E-502 can be configured with a jumper as +

15 V output of an externa l device, or as an additional A GN D contact, or

as an unconnected contact of the connector (NC).

(see section 2.2.1)

the output of the 2nd channel of the DAC (voltage output in the

range -5 ...+ 5 V).

For any modificati ons, the E-502 can be configured with a jumper as 15 V output of an externa l device, or as an additional A GN D contact, or

as an unconnected contact of the connector (NC).

(see section 2.2.1)

• In the "with common gr oun d" mode: common inverting channel input

1 ... 32.

• For a ll modes must be connected to AGND (in differential mode - to

increase noise immunit y). In the "with common ground" mode , t he

connection to AGND is recommended to do on the signal source side.

• Operation voltage range ±1 V (see the details in section 4.6 p.41).

the digital input.

Compatible with the output logic level of TTL/CMOS- cells with a

supply voltage of +2.5 V to +5 V. The input has an extended range of

maximum permissible voltage s (± 10 V r elative to GND ) .

The minimum rate of rise of the signal drop at the input DI_ S Y N1 is

not specified, since there is a Schmitt trigger on this input.

There is a software option to turn the 1k pull-up re si st or to a high logic