Page 1

Document Title

A7130 Data Sheet, 2.4GHz FSK/GFSK Transceiver with 4Mbps data rate

Revision History

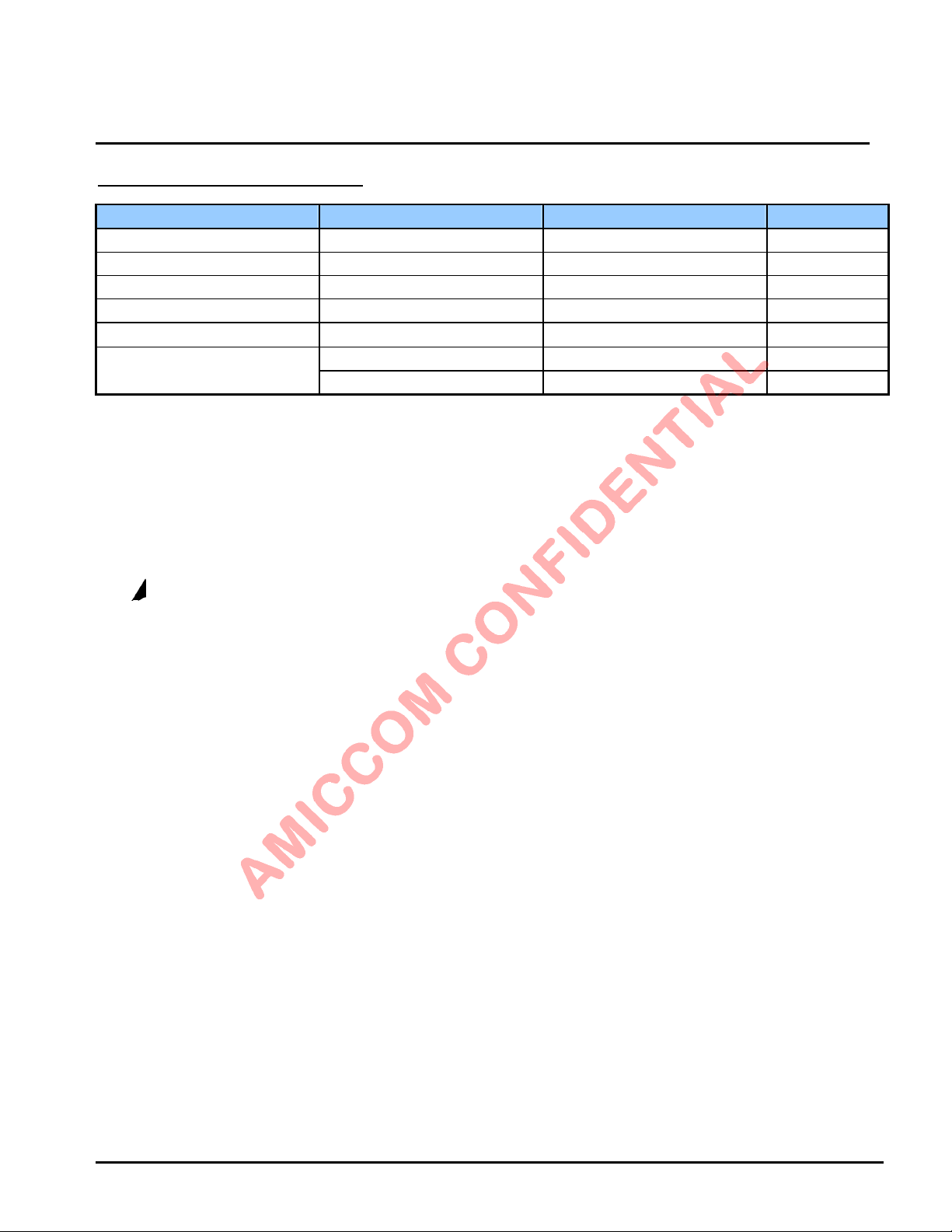

Rev. No. History Issue Date Remark

0.0 Initial issue. Dec, 2009 Objective

0.1 Update ch8 and the application circuit. July, 2011 Preliminary,

0.2 Modify the tape reel information and the add Shenzhen office

address.

0.3 Add Ch20 WOR and Ch21 AES128. Aug., 2011 Preliminary,

0.4 Add section 16.4.3 FIFO extension and Ch21 AES128.

Update sleep cur rent, Xtal start up time and PDL formula, TMOE

timing, WTR Timing, and Ch14.

0.5 Remove 3Mbps data rate

Add descriptions for HECF, FECF and CRCF clear method in 9.2.1

July, 2011 Preliminary,

Apr., 2012 Preliminary,,

Aug.,2012 Preliminary

LBA7130

0.6 Add suggestion in WOR function Oct. 2012 Preliminary

Important Notice:

AMICCOM reserves t he right t o make changes t o its produ cts or to discontinue any integrated circuit product or se rvice

without notice. AMICCOM integrated circuit products are not designed, intended, authorized, or warranted to be suitable for

use in life-support a pplications, de vices o r sys tems or ot her critical ap plications. Use of AM ICCOM products in such

applications is understood to be fully at the risk of the customer.

Oct., 2012, Version 0.6 (PRELIMINARY) 1 AMICCOM Electronics Corporation

Page 2

LBA7130

Table of Contents

1. General Description....................................................................................................................................................... 5

2. Typical Applications ....................................................................................................................................................... 5

3. Feature......................................................................................................................................................................... 5

4. Pin Configurations......................................................................................................................................................... 6

5. Pin Description (I: input; O: output, I/O: input or output)................................................................................................... 7

6. Chip Block Diagram....................................................................................................................................................... 8

7. Absolute Maximum Ratings............................................................................................................................................ 9

8. Electrical Specification..................................................................................................................................................10

9. Control Register ...........................................................................................................................................................12

9.1 Control register table............................................................................................................................................12

9.2 Control register description ..................................................................................................................................15

9.2.1 Mode Register (Address: 00h)....................................................................................................................15

9.2.2 Mode Control Register (Address: 01h)......................................................................................................15

9.2.3 Calibration Control Register (Address: 02h)..............................................................................................16

9.2.4 FIFO Register I (Address: 03h).................................................................................................................16

9.2.5 FIFO Register II (Address: 04h)................................................................................................................16

9.2.6 FIFO DATA Register (Address: 05h) .........................................................................................................16

9.2.7 ID DATA Register (Address: 06h)................................................................................................................16

9.2.8 RC OSC Register I (Address: 07h) .............................................................................................................17

9.2.9 RC OSC Register II (Address: 08h).............................................................................................................17

9.2.10 RC OSC Register III (Address: 09h)..........................................................................................................17

9.2.11 CKO Pin Control Register (Address: 0Ah) .................................................................................................17

9.2.12 GIO1 Pin Control Register I (Address: 0Bh)...............................................................................................18

9.2.13 GIO2 Pin Control Register II (Address: 0Ch) .............................................................................................20

9.2.14 Clock Register (Address: 0Dh)..................................................................................................................21

9.2.15 PLL Register I (Address: 0Eh)...................................................................................................................21

9.2.16 PLL Register II (Address: 0Fh)..................................................................................................................21

9.2.17 PLL Register III (Address: 10h).................................................................................................................22

9.2.18 PLL Register IV (Address: 11h).................................................................................................................22

9.2.19 PLL Register V (Address: 12h)...............................................................................................................22

9.2.20 Channel Group Register I (Address: 13h)..................................................................................................22

9.2.21 Channel Group Register II (Address: 14h).................................................................................................22

9.2.22 TX Register I (Address: 15h).....................................................................................................................23

9.2.23 TX Register II (Address: 16h)....................................................................................................................23

9.2.24 Delay Register I (Address: 17h)................................................................................................................23

9.2.25 Delay Register II (Address: 18h) ...............................................................................................................24

9.2.26 RX Register (Address: 19h)......................................................................................................................24

9.2.27 RX Gain Register I (Address: 1Ah)............................................................................................................25

9.2.28 RX Gain Register II (Address: 1Bh)...........................................................................................................25

9.2.29 RX Gain Register III (Address: 1Ch) .........................................................................................................25

9.2.30 RX Gain Register IV (Address: 1Dh).........................................................................................................26

9.2.31 RSSI Threshold Register (Address: 1Eh) ..................................................................................................26

9.2.32 ADC Control Register (Address: 1Fh)........................................................................................................26

9.2.33 Code Register I (Address: 20h).................................................................................................................26

9.2.34 Code Register II (Address: 21h)................................................................................................................27

9.2.35 Code Register III (Address: 22h)...............................................................................................................27

9.2.36 IF Calibration Register I (Address: 23h).....................................................................................................27

9.2.37 IF Calibration Register II (Address: 24h)....................................................................................................28

9.2.38 VCO current Calibration Register (Address: 25h).......................................................................................28

9.2.39 VCO band Calibration Register I (Address: 26h)........................................................................................28

9.2.40 VCO band Calibration Register II (Address: 27h).......................................................................................29

9.2.41 VCO Deviation Calibration Register I (Address: 28h).................................................................................29

9.2.42 VCO Deviation Calibration Register II (Address: 29h)................................................................................29

9.2.43 DASP0 (Address: 2Ah, Page 0 by AGT [3:0]=0) ........................................................................................30

9.2.43 DASP1 (Address: 2Ah, Page 1 by AGT[3:0]=1) .........................................................................................30

Oct., 2012, Version 0.6 (PRELIMINARY) 2 AMICCOM Electronics Corporation

Page 3

LBA7130

9.2.43 DASP2 (Address: 2Ah, Page 2 by AGT[3:0]=2) .........................................................................................30

9.2.43 DASP3 (Address: 2Ah, Page 3 by AGT[3:0]=3) .........................................................................................31

9.2.43 DASP4 (Address: 2Ah, Page 4 by AGT[3:0]=4) .........................................................................................31

9.2.43 DASP5 (Address: 2Ah, Page 5 by AGT[3:0]=5) .........................................................................................31

9.2.43 DASP6 (Address: 2Ah, Page 6 by AGT[3:0]=6) .........................................................................................31

9.2.43 DASP7 (Address: 2Ah, Page 7 by AGT[3:0]=7) .........................................................................................31

9.2.44 VCO Modulation Delay Register (Address: 2Bh)........................................................................................31

9.2.45 Battery detect Register (Address: 2Ch).....................................................................................................32

9.2.46 TX test Register (Address: 2Dh) ...............................................................................................................32

9.2.47 Rx DEM test Register I (Address: 2Eh) .....................................................................................................32

9.2.48 Rx DEM test Register II (Address: 2Fh).....................................................................................................33

9.2.49 Charge Pump Current Register I (Address: 30h) .......................................................................................33

9.2.50 Charge Pump Current Register II (Address: 31h).......................................................................................33

9.2.51 Crystal test Register (Address: 32h)..........................................................................................................33

9.2.52 PLL test Register (Address:33h) ...............................................................................................................34

9.2.53 VCO test Register I (Address:34h)............................................................................................................34

9.2.54 RF Analog Test Register (Address: 35h)....................................................................................................34

9.2.55 AES Key data Register (Address: 36h)......................................................................................................35

9.2.56 Channel Select Register (Address: 37h)....................................................................................................35

9.2.57 ROMP0 (Address: 38h, Page 0 by AGT[3:0]=0).........................................................................................35

9.2.57 ROMP1 (Address: 38h, Page 1 by AGT[3:0]=1).........................................................................................35

9.2.57 ROMP2 (Address: 38h, Page 2 by AGT[3:0]=2).........................................................................................36

9.2.57 ROMP3 (Address: 38h, Page 3 by AGT[3:0]=3).........................................................................................36

9.2.57 ROMP4 (Address: 38h, Page 4 by AGT[3:0]=4).........................................................................................36

9.2.58 Data Rate Clock Register (Address: 39h)..................................................................................................36

9.2.59 FCR Register (Address: 3Ah) ...................................................................................................................36

9.2.60 ARD Register (Address: 3Bh) ...................................................................................................................37

9.2.61 AFEP Register (Address: 3Ch)..................................................................................................................37

9.2.62 FCB Register (Address: 3Dh) ...................................................................................................................37

9.2.63 KEYC Register (Address: 3Eh).................................................................................................................38

9.2.64 USID Register (Address: 3Fh) ..................................................................................................................38

10. SPI.............................................................................................................................................................................39

10.1 SPI Format........................................................................................................................................................40

10.2 SPI Timing Characteristic...................................................................................................................................40

10.3 SPI Timing Chart................................................................................................................................................41

10.3.1 Timing Chart of 3-wire SPI........................................................................................................................41

10.3.2 Timing Chart of 4-wire SPI........................................................................................................................41

10.4 Strobe Commands .............................................................................................................................................42

10.4.1 Strobe Command - Sleep Mode................................................................................................................42

10.4.2 Strobe Command - ldle Mode ...................................................................................................................42

10.4.3 Strobe Command - Standby Mode ............................................................................................................43

10.4.4 Strobe Command - PLL Mode...................................................................................................................43

10.4.5 Strobe Command - RX Mode....................................................................................................................44

10.4.6 Strobe Command - TX Mode ....................................................................................................................44

10.4.7 Strobe Command – FIFO Write Pointer Reset...........................................................................................44

10.4.8 Strobe Command – FIFO Read Pointer Reset...........................................................................................45

10.4.9 Strobe Command – Deep Sleep Mode ......................................................................................................45

10.5 Reset Command................................................................................................................................................46

10.6 ID Accessing Command.....................................................................................................................................46

10.6.1 ID Write Command...................................................................................................................................46

10.6.2 ID Read Command ..................................................................................................................................47

10.7 FIFO Accessing Command.................................................................................................................................47

10.7.1 TX FIFO Write Command .........................................................................................................................47

10.7.2 Rx FIFO Read Command.........................................................................................................................48

11. State machine.............................................................................................................................................................49

11.1 Key states..........................................................................................................................................................49

11.2 FIFO mode ........................................................................................................................................................50

11.3 Direct mode .......................................................................................................................................................51

12. Crystal Oscillator ........................................................................................................................................................54

12.1 Use External Crystal ..........................................................................................................................................54

Oct., 2012, Version 0.6 (PRELIMINARY) 3 AMICCOM Electronics Corporation

Page 4

LBA7130

12.2 Use External Clock ............................................................................................................................................54

13. System Clock.............................................................................................................................................................55

13.2 Data Rate Setting ..............................................................................................................................................55

14. Transceiver LO Frequency..........................................................................................................................................56

14.1 LO Frequency Setting........................................................................................................................................56

14.2 IF Side Band Select ...........................................................................................................................................57

14.2.1 Auto IF Exchange.....................................................................................................................................58

14.2.2 Fast Exchange.........................................................................................................................................59

14.3 Auto Frequency Compensation...........................................................................................................................60

15. Calibration..................................................................................................................................................................60

15.1 Calibration Procedure ........................................................................................................................................60

16. FIFO (First In First Out)...............................................................................................................................................61

16.1 TX Packet Format in FIFO mode........................................................................................................................61

16.1.1 Basic FIFO mode.....................................................................................................................................61

16.1.2 Advanced FIFO mode...............................................................................................................................61

16.2 Bit Stream Process in FIFO mode.......................................................................................................................62

16.3 Transmission Time.............................................................................................................................................63

16.4 Usage of TX and RX FIFO .................................................................................................................................63

16.4.1 Easy FIFO ...............................................................................................................................................64

16.4.2 Segment FIFO .........................................................................................................................................65

16.4.3 FIFO Extension........................................................................................................................................67

17. ADC (Analog to Digital Converter)...............................................................................................................................71

17.1 RSSI Measurement............................................................................................................................................71

18. Battery Detect ............................................................................................................................................................73

19. Auto-ack and auto-resend...........................................................................................................................................74

19.1 Basic FIFO plus auto-ack auto-resend................................................................................................................74

19.2 Advanced FIFO plus auto-ack and auto-resend...................................................................................................74

19.3 WTR Behavior during auto-ack and auto-resend.................................................................................................76

19.6 Examples of auto-ack and auto-resend...............................................................................................................77

20. RC Oscillator..............................................................................................................................................................79

20.1 WOR Function...................................................................................................................................................79

20.2 TWOR Function.................................................................................................................................................80

21. AES128 Security Packet .............................................................................................................................................80

22. Application circuit........................................................................................................................................................81

22.1 MD7130-A01 .....................................................................................................................................................81

22.2 MD7130-F07 .....................................................................................................................................................82

23. Abbreviations..............................................................................................................................................................83

24. Ordering Information...................................................................................................................................................83

25. Package Information...................................................................................................................................................84

26. Top Marking Information..............................................................................................................................................85

27. Reflow Profile.............................................................................................................................................................86

28. Tape Reel Information.................................................................................................................................................87

29. Product Status............................................................................................................................................................89

Oct., 2012, Version 0.6 (PRELIMINARY) 4 AMICCOM Electronics Corporation

Page 5

LBA7130

1. General Description

A7130 is a high performance and low cost 2.4GHz ISM band wireless transceiver. This device integrates both high sensitivity

receiver (- 88dBm @4Mbps) and programmable power amplifier 5dBm. Based on Data Rate Register (39h), user can

configure on-air data rates to 4Mbps.

A7130 supports fast settling time (90 us) for frequency hopping system. For packet handling, A7130 has b uilt-in separated

64-bytes TX/ RX FIFO (could be logically extended t o 4K b ytes) for da ta buffering and bu rst trans mission, aut o-ack a nd

auto-resend, CRC for error packet filtering, FEC for 1-bit data correction per code word, RSSI for clear channel assessment,

therm al sensor for monitoring relative temperature, WOR (Wake on R X) function to support periodically wake up from sleep

mode to RX mode and listen for incoming packets without MCU interaction, data whitening for data encryption / decryption. In

addition, A7130 ha s bu ilt-in AES128 co -processor (Adva nced Encr yption St andard) for advan ced dat a e ncryption and

decryption which consists of the transformation of a 128-bit block into an encrypted 128-bit block. Those functions are very

easy to use while developing a wireless system. All features are integrated in a small QFN 4X4 20 pins package.

A7130’s control registers ar e a ccessed via 3- wire o r 4-wire S PI interface s uch as TX/RF FIFO, ID r egister, RSSI value,

frequency hopping to chip calibration procedures. Another one, via SPI as well, is the unique Strobe command, A7130 can

be cont rolled f rom power sav ing mode (deep s leep, sleep, idle , standby ), PLL mode, TX mode and R X mode. The o ther

connections between A7130 and MCU are GIO1 and GIO2 (multi-function GPIO) to output A7130’s status so that MCU could

use either polling or int errupt scheme for radio cont rol. Ove rall, this de vice is very easy-to-use for de veloping a w ireless

application with a MCU.

2. Typical Applications

n 2.4GHz video baby monitor

n 2.4GHz PC peripherals

n HiFi quality wireless audio streaming

n 2408 ~ 2468 MHz ISM system

n Wireless metering and building automation

n Wireless toys and game controllers

3. Feature

n Small size (QFN4 X4, 20 pins).

n Frequency band: 2408 ~ 2468MHz.

n FSK or GFSK modulation

n Low current consumption: RX 27mA (4Mbps), TX 29mA (at 5dBm output power).

n Deep sleep current (0.1 uA).

n Sleep current (2.5 uA).

n On chip regulator, support input voltage 2.0 ~ 3.6 V.

n Data rate 4Mbps.

n Programmable TX power level from 5 dBm.

n Ultra High sensitivity:

u -88dBm at 4Mbps on-air data rate.

n Fast settling time (90 us) synthesizer for frequency hopping system.

n On chip low power RC oscillator for WOR (Wake on RX) function.

n Built-in AES128 co-processor

n AGC (Auto Gain Control) for the wide RSSI dynamic range.

n AFC (Auto Frequency Compensation) for frequency drift due to temperature.

n Support low cost crystal (16 / 18 MHz).

n Low Battery Detector indication.

n Easy to use.

u Support 3-wire or 4-wire SPI.

u Unique Strobe command via SPI.

u ONE register setting for new channel frequency.

u CRC Error Packet Filtering.

u Auto-acknowledgement and auto-resend.

u Dynamic FIFO length.

u 8-bits RSSI measurement for clear channel indication.

u Auto Calibrations.

Oct., 2012, Version 0.6 (PRELIMINARY) 5 AMICCOM Electronics Corporation

Page 6

u Auto IF function.

u Auto FEC by (7, 4) Hamming code (1 bit error correction / code word).

u Separated 64 bytes RX and TX FIFO.

u Easy FIFO / Segment FIFO / FIFO Extension (up to 4K bytes).

u Support FIFO mode frame sync to MCU.

u Support direct mode with recovery clock output to MCU.

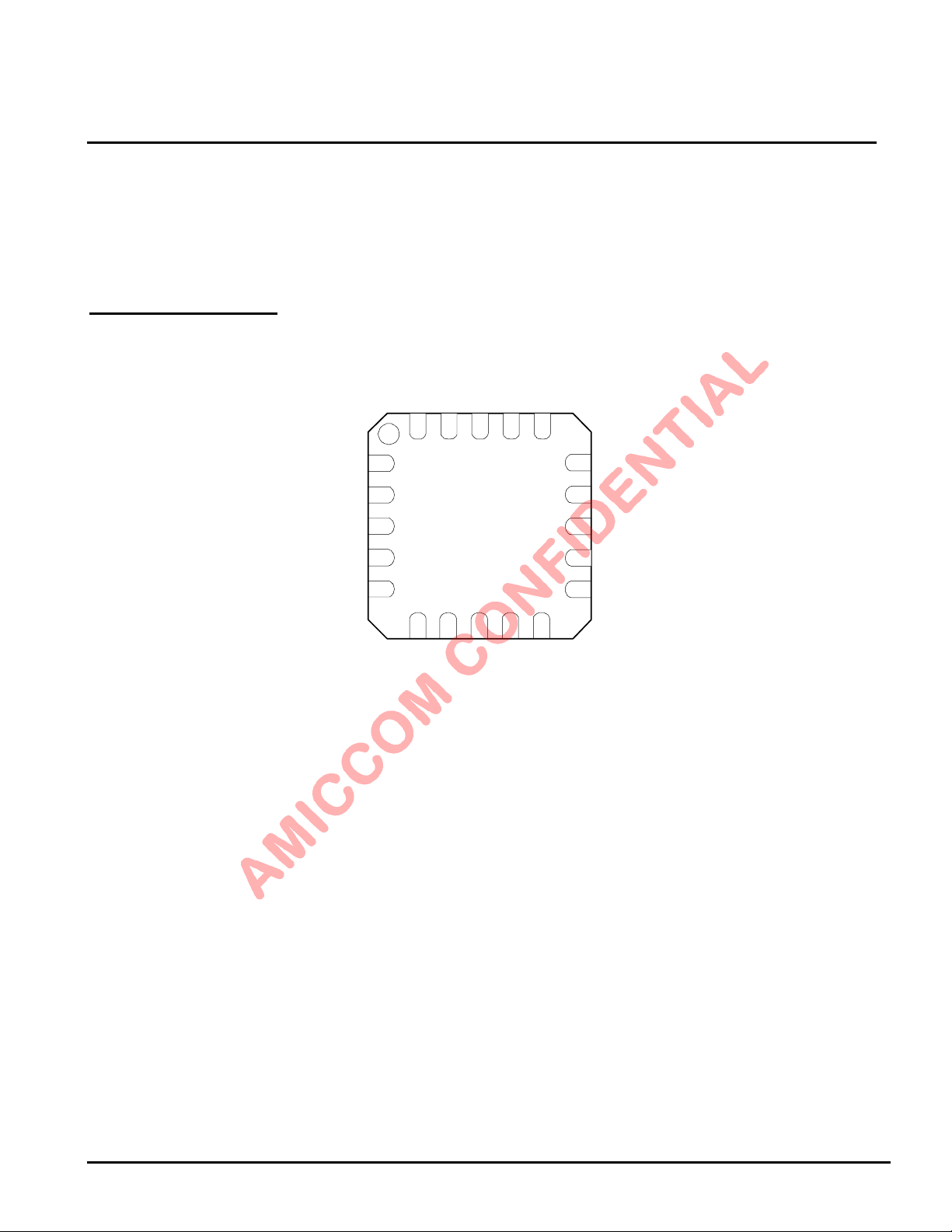

4. Pin Configurations

VDD_A

REGI

CKO

GIO2

LBA7130

GIO1

19

RSSI

BP_BG

RFI

RFO

RFC

20

1

2

3

4

5

6

7

CP

V_VCO

Fig 4-1. A7130 QFN 4x4 Package Top View

17

18

8

9

XI

V_PLL

16

15

14

13

12

11

10

XO

GND

SDIO

VDD_D

SCK

SCS

Oct., 2012, Version 0.6 (PRELIMINARY) 6 AMICCOM Electronics Corporation

Page 7

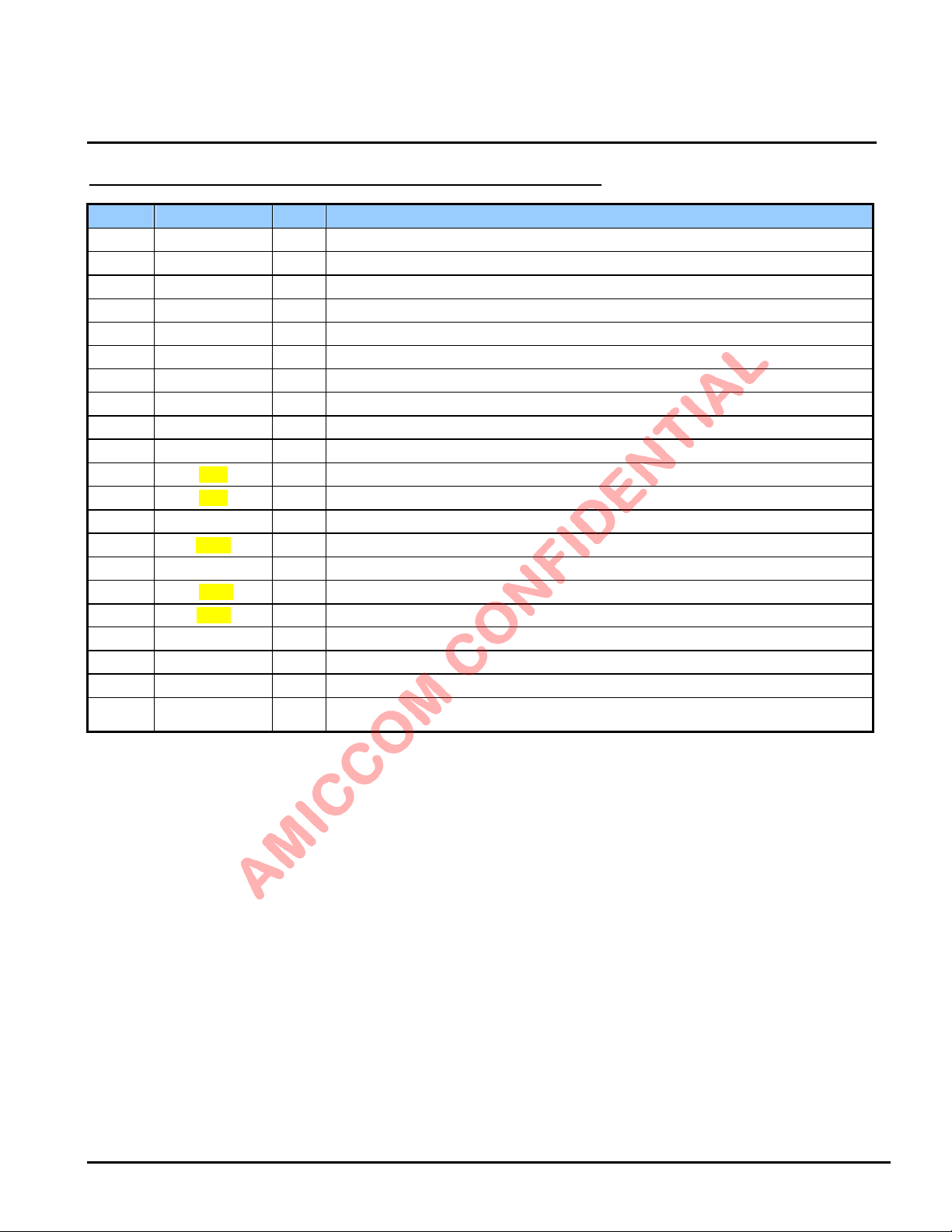

5. Pin Description (I: input; O: output, I/O: input or output)

Pin No. Symbol I/O Function Description

1 RSSI O Connected to a bypass capacitor for RSSI.

2 BP_BG O Connected to a bypass capacitor for internal Regulator bias point.

3 RFI I LNA input. Connected to matching circuit.

4 RFO O PA input. Connected to matching circuit.

5 RFC I RF Choke input. Connected to matching circuit.

6 V_VCO I VCO supply voltage input.

7 CP O Charge-pump. Connected to loop filter.

8 V_PLL I PLL supply voltage input.

9 XI I Crystal oscillator input.

10 XO O Crystal oscillator output.

11 SCS I SPI chip select.

12 SCK I SPI clock input pin.

13 VDD_D I Connected to a bypass capacitor to supply voltage for digital part.

14 SDIO I/O SPI read/write data.

15 GND G G round

16 GIO1 I/O Multi-function GIO1 / 4-wire SPI data output.

17 GIO2 I/O Multi-function GIO2 / 4-wire SPI data output.

18 CKO O

19 REGI I Regulator input (External Power Input)

20 VDD_A O

Back side plate G

Multi-function clock output.

Internal Regulator output to supply V_VCO (pin 6), V_PLL (pin 8) and RFC (pin 5).

Ground.

Back side plate shall be well-solder to ground; otherwise, it will impact RF performance.

LBA7130

Oct., 2012, Version 0.6 (PRELIMINARY) 7 AMICCOM Electronics Corporation

Page 8

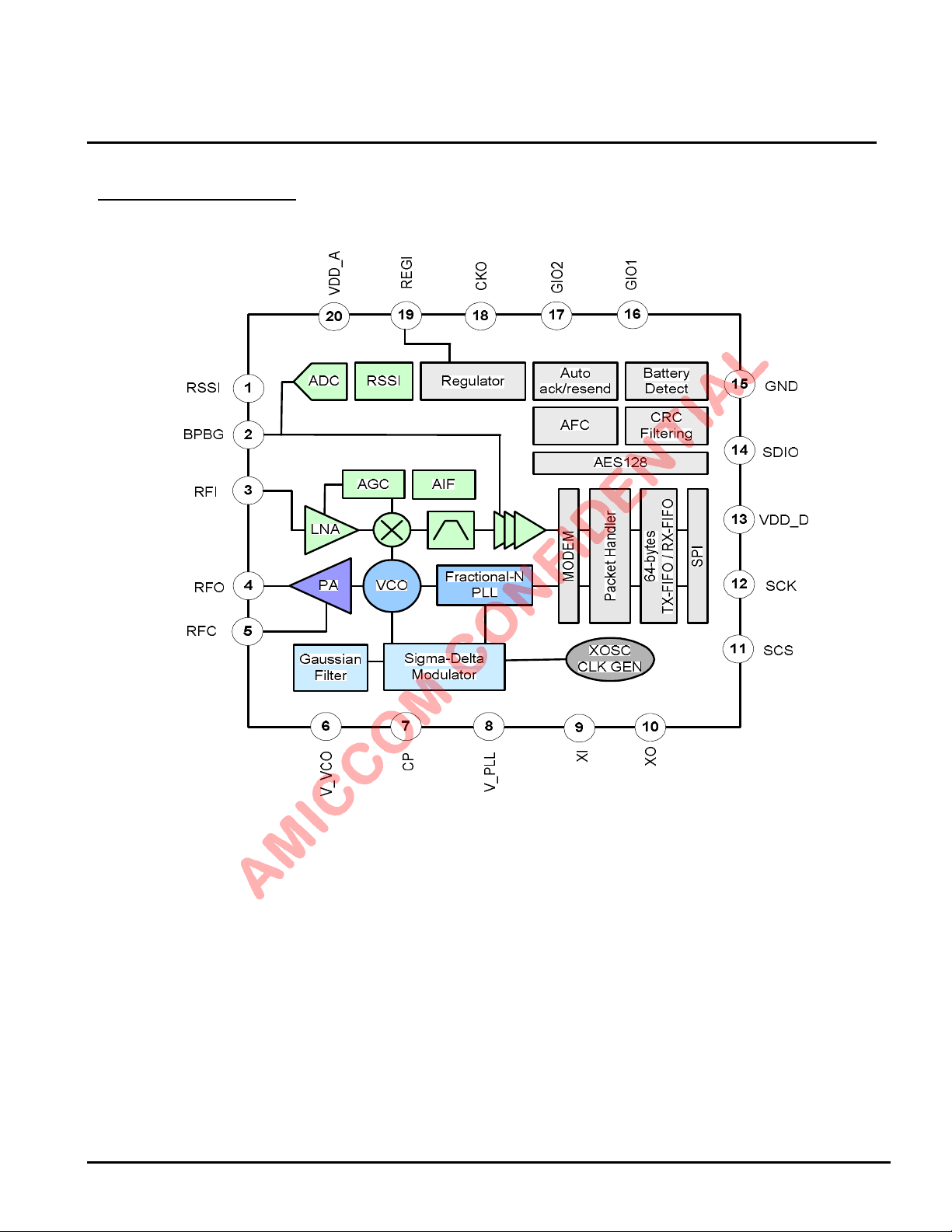

6. Chip Block Diagram

LBA7130

Fig 6-1. A7130 Block Diagram

Oct., 2012, Version 0.6 (PRELIMINARY) 8 AMICCOM Electronics Corporation

Page 9

LBA7130

7. Absolute Maximum Ratings

Parameter With respect to Rating Unit

Supply voltage range (VDD) GND -0.3 ~ 3.6 V

Digital IO pins range GND -0.3 ~ VDD+0.3 V

Voltage on the analog pins range GND -0.3 ~ 2.1 V

Input RF level 10 dBm

Storage Temperature range -55 ~ 125

HBM ± 2K VESD Rating

MM ± 100 V

*Stresses above those listed unde r “Absolute M aximum Rating” may cause permanent damage to the device. These are

stress ratings only; functional operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect

device reliability.

*Device is ESD sensitive. Use appropriate ESD precautions. HBM (Human Body Mode) is tested under MIL-STD-883F

Method 3015.7. MM (Machine Mode) is tested under JEDEC EIA/JESD22-A115-A.

*Device is Moisture Sensitivity Level III (MSL 3).

°C

Oct., 2012, Version 0.6 (PRELIMINARY) 9 AMICCOM Electronics Corporation

Page 10

8. Electrical Specification

LBA7130

(Ta=25℃, VDD=3.3V, F

=16MHz, with Match circuit and low pass filter, On Chip Regulator = 1.8V, unless otherwis e noted.)

XTAL

Parameter Description Min. Type Max. Unit

General

Operating Temperature -40 85

Supply Voltage (VDD) with internal regulator 2.0 3.3 3.6 V

Current Consumption

Deep Sleep mode*

1

0.1

(No registers retention)

Current Consumption

(DBL =0 at 0Fh, bit7)

Sleep mode (WOR off) *

Sleep mode (WOR on) *

1

1

Idle Mode (Regulator on) *

Standby Mode

1

2.5

3.5

0.3 mA

2.7 mA

(XOSC on, CLK Gen. on)

PLL mode 12.5 mA

RX Mode (4Mbps) 27 mA

TX Mode (5dBm) 29 mA

TX Mode (3dBm) 24 mA

TX Mode (0dBm) 20 mA

TX Mode ( -5dBm) 18 mA

TX Mode ( -17dBm) 16 mA

°C

mA

mA

mA

PLL block

Crystal start up time*

(3225 SMD type)

2

Crystal frequency Data rate: 4Mbps 16 MHz

Crystal tolerance Data rate: 4M/bps ±50 ppm

Crystal ESR 80 ohm

VCO Operation Frequency 2408 2468 MHz

PLL phase noise Offset 10k

PLL settling time*

3

Idle to standby

(Xtal osc. is stable at 20ppm)

Idle to standby

(Xtal osc. is stable at 10ppm)

Offset 500K

Offset 1M

Loop filter based on app. circuit.

(Standby to PLL)

1 ms

2 ms

75

90

100

30

dBc

mS

Transmitter

Output power range -17 0 5 dBm

Out Band Spurious Emission *

Frequency deviation*

Data rate 4M bps

TX ready time*

6

4

30MHz~1GHz -36

1GHz~12.75GHz -30

1.8GHz~ 1.9GHz -47

5.15GHz~ 5.3GHz -47

5

Data rate 4Mbps

Standby to TX

±1M

90

dBm

dBm

dBm

dBm

Hz

mS

Receiver

dBm

@ BER = 0.1%

Data rate 4Mbps -88Receiver sensitivity

Data rate 4Mbps (GFSK) -85

Oct., 2012, Version 0.6 (PRELIMINARY) 10 AMICCOM Electronics Corporation

Page 11

LBA7130

IF Filter bandwidth IFS = [11], 4Mbps 4.8M Hz

IF center frequency IFS = [11], 4Mbps 4M Hz

Interference *

(4Mbps , IF = 4MHz)

Maximum Operating Input Power @RF input (BER=0.1%) 5 dBm

RX Spurious Emission *

RX Ready Time 80

Regulator

Regulator settling time Pin 2 connected to 470pF.

Band-gap reference voltage 1.28 V

Regulator output voltage 1.79 1.8 2.3 V

Digital IO DC characteristics

High Level Input Voltage (VIH) 0.8*VDD VDD V

Low Level Input Voltage (VIL) 0 0.2*VDD V

High Level Output Voltage (VOH) @IOH= -0.5mA VDD-0.4 VDD V

Low Level Output Voltage (VOL) @IOL= 0.5mA 0 0.4 V

7

4

(Sleep to idle).

Co-Channel (C/I0) 11 dB

±4MHz Adjacent Channel

±8MHz Adjacent Channel

±12MHz Adjacent Channel

±16MHz Adjacent Channel

Image (C/IIM) - 10 dB

30MHz~1GHz -57 dBm

1GHz~12.75GHz -47

AGC = 0 -95 -50 dBmRSSI Range

AGC = 1 -95 -20 dBm

0 dB

- 10 dB

- 20 dB

- 30 dB

0.5 ms

ms

Note 1: When digital I/O pins are configured as input, those pins shall NOT be floating but pull either high or low (SCS shall

be pulled high only); otherwise, leakage current will be induced.

Note 2: Xtal settling time is depend on Xtal package type, Xtal ESR and Xtal Cm.

Note 3: Refer to Delay Register I (17h) to set PDL (PLL settling delay).

Note 4: With external RF filter that provides minimum 17dB of attenuation in the band: 30MHz ~ 2GHz and 3GHz ~12.75GHz.

Note 5: Refer to TX Register II (16h) to set FD [7:0].

Note 6: Refer to Delay Register I (17h) to set PDL and TDL.

Note 7: The wanted signal is set above sensitivity level +3dB. The modulation data of wanted signal and interferer

are PN9 and PN15, respectively.

Oct., 2012, Version 0.6 (PRELIMINARY) 11 AMICCOM Electronics Corporation

Page 12

LBA7130

9. Control Register

A7130 contains 69 control registers. MCU can access those control registers via 3-wire (SCS, SCK, SDIO) or 4-wire (SCS,

SCK, SDIO, GIO1/GIO2) SPI interface (max. 15 Mbps). Please refer to Chapter 10 for SPI timing. In general, most of control

registers are just need to configure the recommended values based on A7130 reference code.

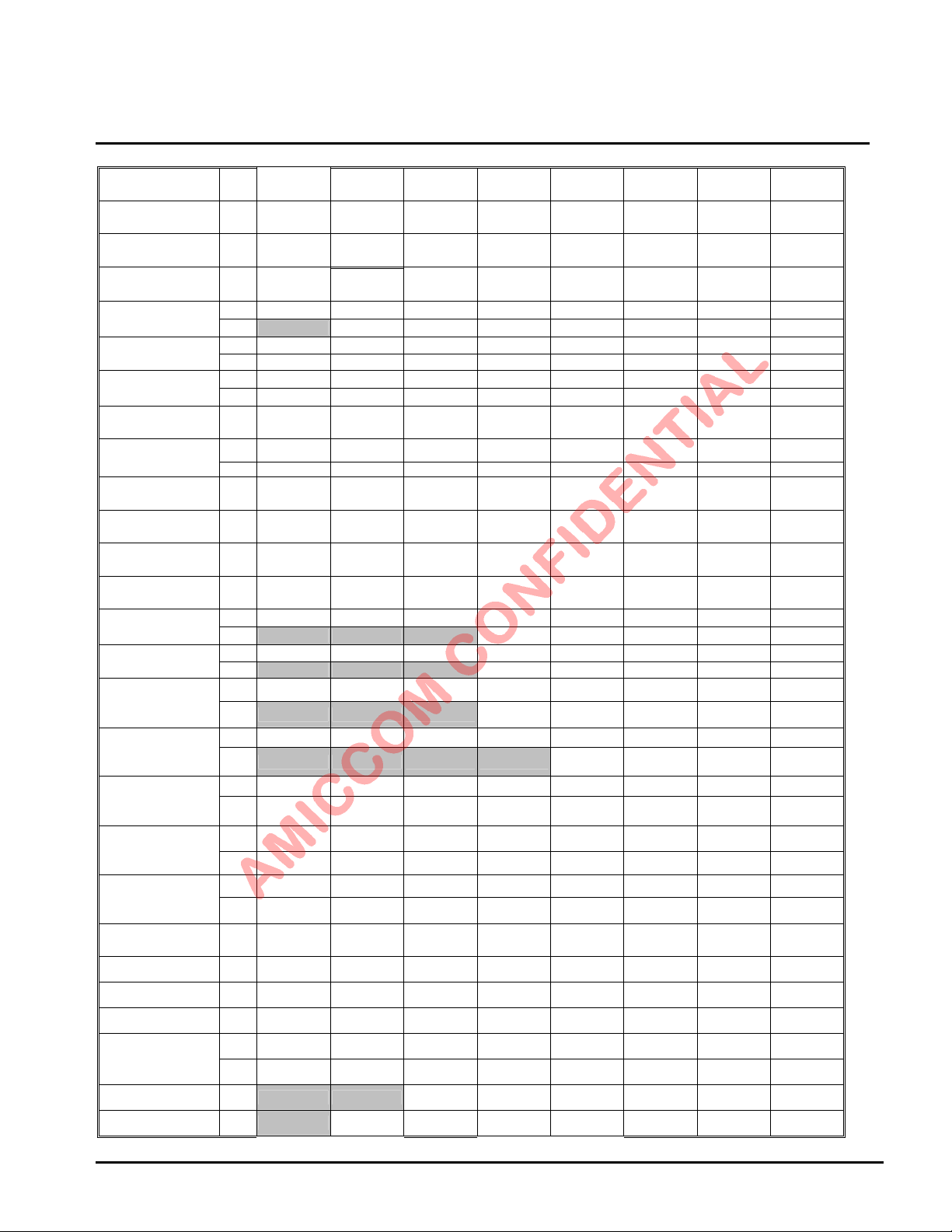

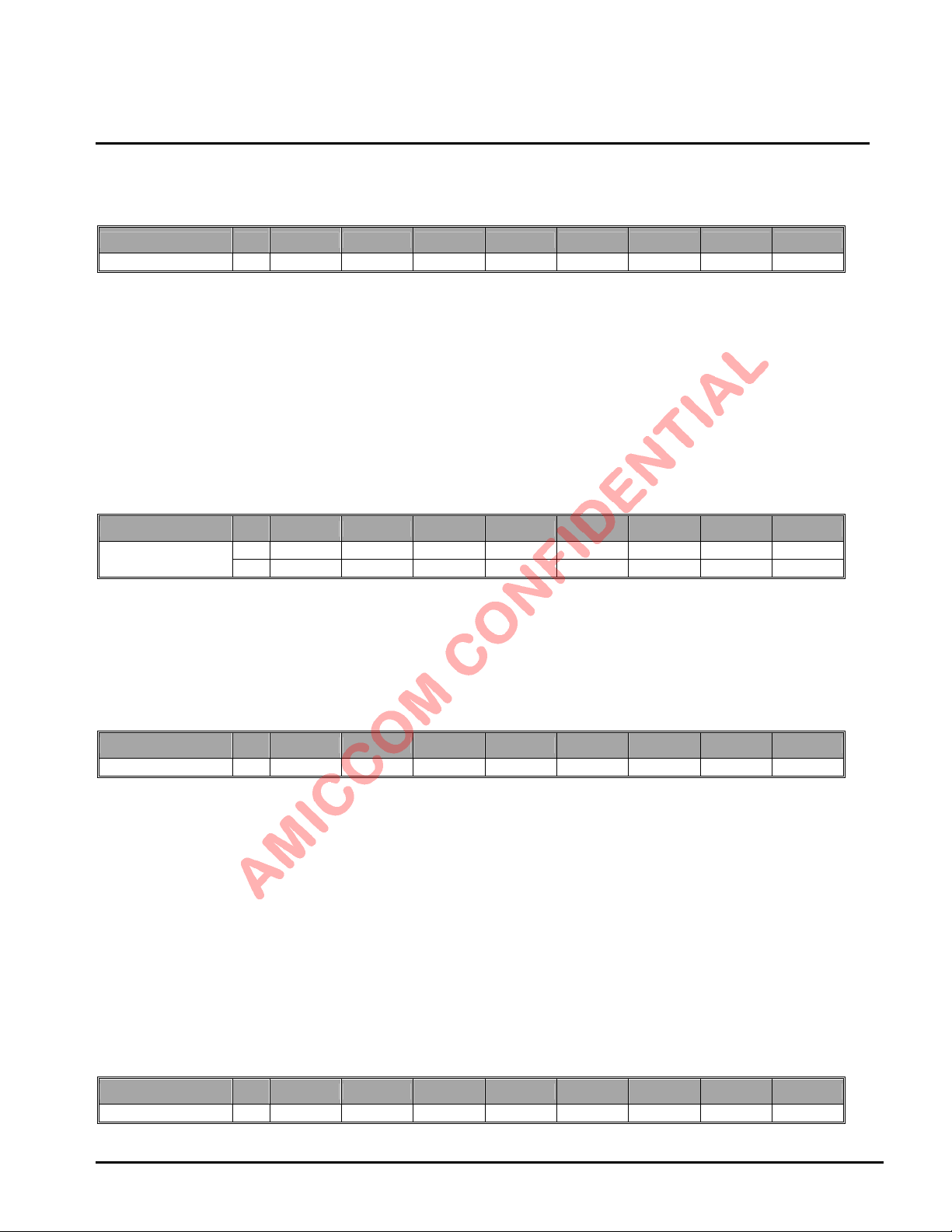

9.1 Control register table

Address /

Name

Mode

01h

Mode control

02h

Calc

03h

FIFO I

04h

FIFO II

05h

FIFO Data

06h

ID Data

07h

RC OSC I

08h

RC OSC II

09h

RC OSC III

0Ah

CKO Pin

0Bh

GPIO1 Pin I

0Ch

GPIO2 Pin II

0Dh

Clock

0Eh

PLL I

0Fh

PLL II

10h

PLL III

11h

PLL IV

12h

PLL V

13h

Channel Group I

14h

Channel Group II

15h

TX I

R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

W RESETN RESETN RESETN RESETN RESETN RESETN RESETN RESETN00h

R HECF FECF CRCF CER XER PLLER TRSR TRER

W DDPC ARSSI AIF DFCD WORE FMT FMS ADCM

R DDPC ARSSI AIF CD WORE FMT FMS ADCM

R/W

W -- -- -- -- FEP11 FEP10 FEP9 FEP8

R -- -- -- -- LENF11 LENF10 LENF9 LENF8

W FEP7 FEP6 FEP5 FEP4 FEP3 FEP2 FEP1 FEP0

R LENF7 LENF6 LENF5 LENF4 LENF3 LENF2 LENF1 LENF0

W

R/W FIFO7 FIFO6 FIFO5 FIFO4 FIFO3 FIFO2 FIFO1 FIFO0

R/W

W WOR_SL7 WOR_SL6 W OR_SL5 WOR_SL4 WOR_SL3 WOR_SL2 WOR_SL1 WOR_SL0

R RCOC7 RCOC6 RCOC5 RCOC4 RCOC3 RCOC2 RCOC1 RCOC0

W

W

R

W

W

W

W CGC1 CGC0 GRC3 GRC2 GRC1 GRC0 CGS XS

R IFS1 IFS0 GRC3 GRC2 GRC1 GRC0

R/W CHN7 CHN6 CHN5 CHN4 CHN3 CHN2 CHN1 CHN0

W DBL RRC1 RRC0 CHR3 CHR2 CHR1 CHR0 BIP8

R DBL RRC1 RRC0 CHR3 CHR2 CHR1 CHR0 IP8

W BIP7 BIP6 BIP5 BIP4 BIP3 BIP2 BIP1 BIP0

R IP7 IP6 IP5 IP4 IP3 IP2 IP1 IP0

W BFP15 BFP14 BFP13 BFP12 BFP11 BFP10 BFP9 BFP8

R FS YN-FP15 AC14-FP14 AC13-FP13 AC12-FP12 AC11-FP11 AC10-FP10 AC9-FP9 AC8-FP8

W BFP7 BFP6 BFP5 BFP4 BFP3 BFP2 BFP1 BFP0

R AC7-FP7

R/W CHGL7 CHGL6 CHGL5 CHGL4 CHGL3 CHGL2 CHGL1 CHGL0

R/W CHGH7 CHGH6 CHGH5 CHGH4 CHGH3 CHGH2 CHGH1 CHGH0

W

-- -- -- VCC VBC VDC FBC RSSC

FPM1 FPM0 PSA5 PSA4 PSA3 PSA2 PSA1 PSA0

ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0

WOR_SL9 WOR_SL8 W OR_AC5 WOR_AC4 WOR_AC3 WOR_AC2 WOR_AC1 WOR_AC0

RTCS RCOT2

RCOT1/

RTCC1

RCOT0/

RTCC0

CALWC

RCOSC_E TSEL TWORE

-- -- -- -- CALWR -- -- --

ECKOE CKOS3 CKOS2 CKOS1 CKOS0 CKOI CKOE SCKI

VKM VPM GIO1S3 GIO1S2 GIO1S1 GIO1S0 GIO1I GIO1OE

BBCKS1 BBCKS0 GIO2S3 GIO2S2 GIO2S1 GIO2S0 GIO2I GIO2OE

-- --

AC6-FP6 AC5-FP5 AC4-FP4 AC3-FP3 AC2-FP2 AC1-FP1 AC0-FP0

GDR GF TMDE TXDI TME FDP2 FDP1 FDP0

Oct., 2012, Version 0.6 (PRELIMINARY) 12 AMICCOM Electronics Corporation

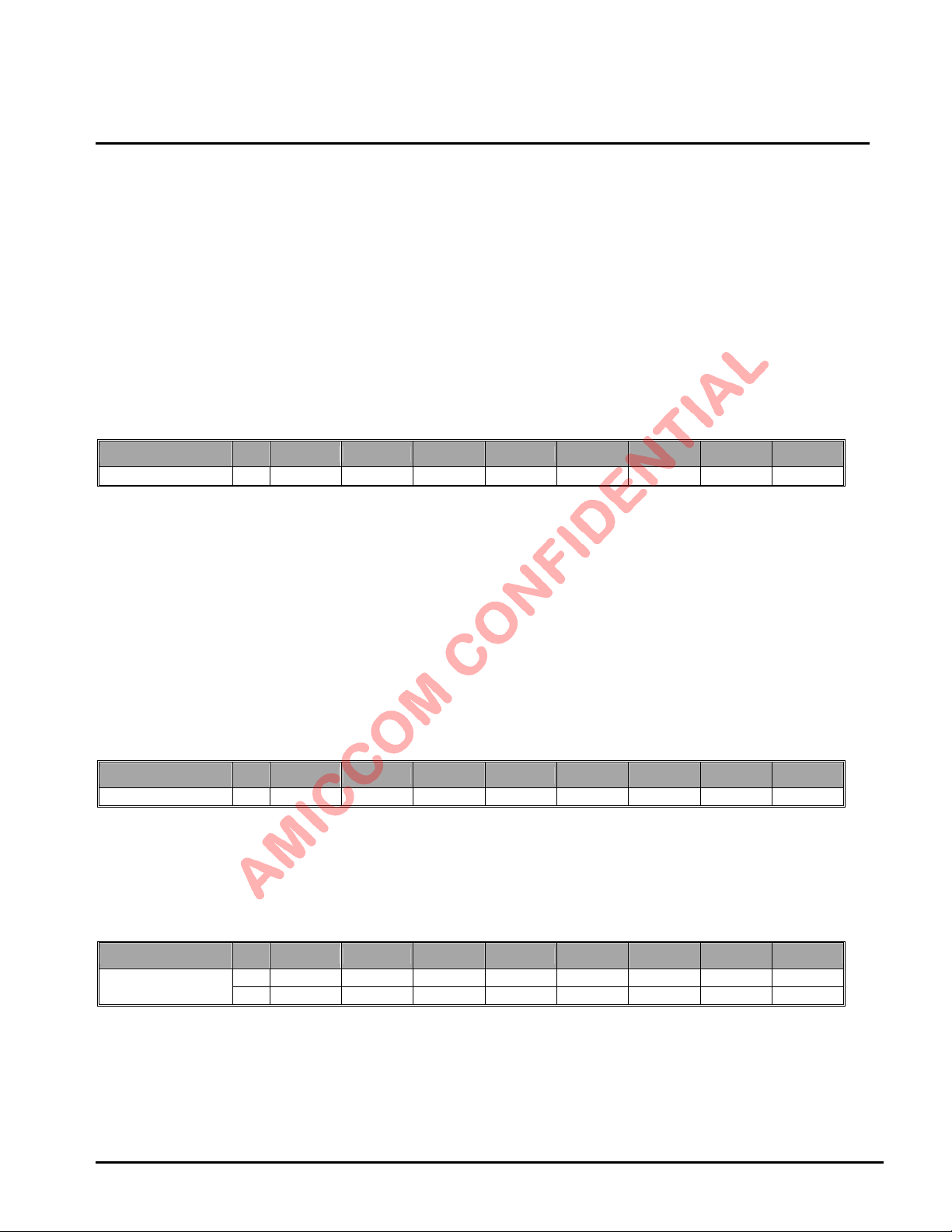

Page 13

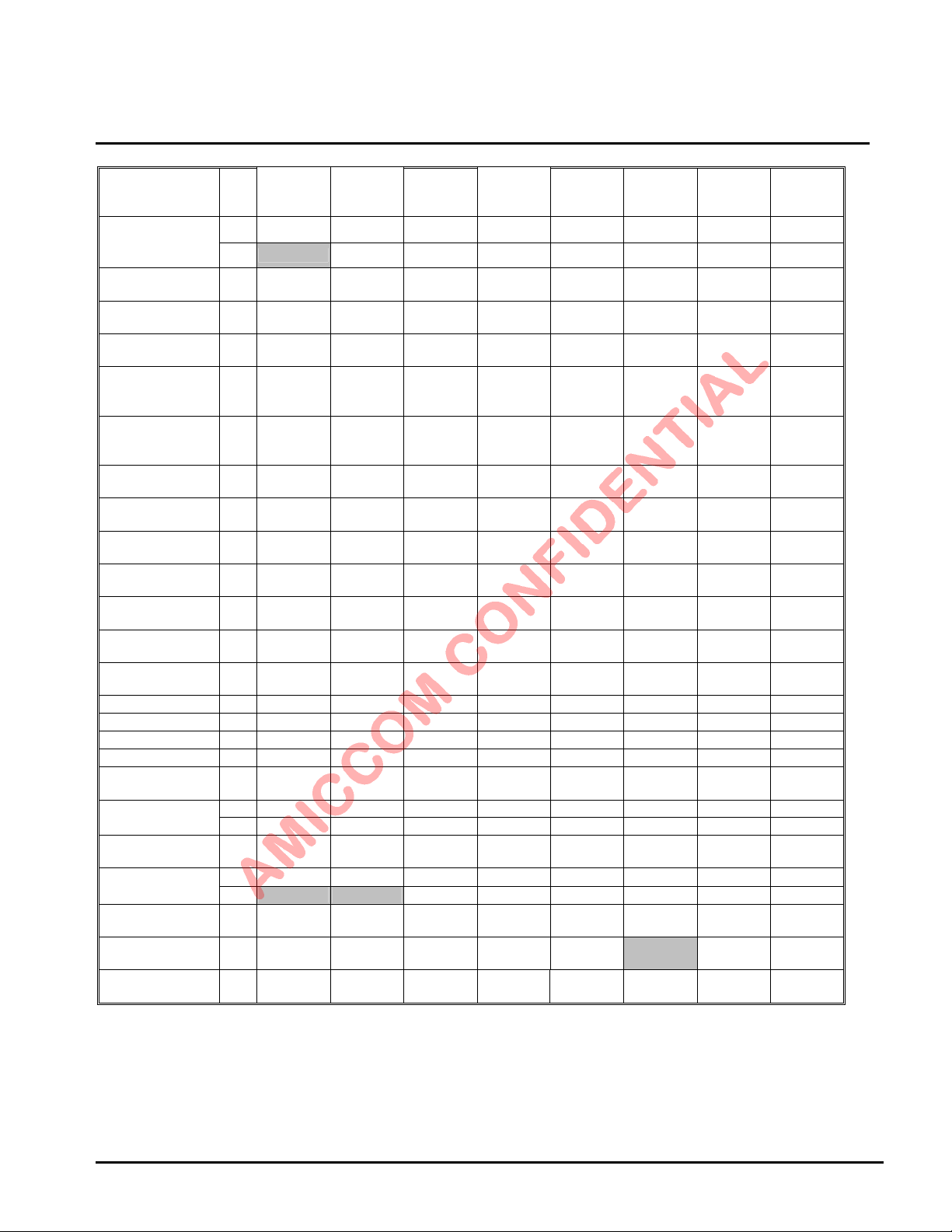

LBA7130

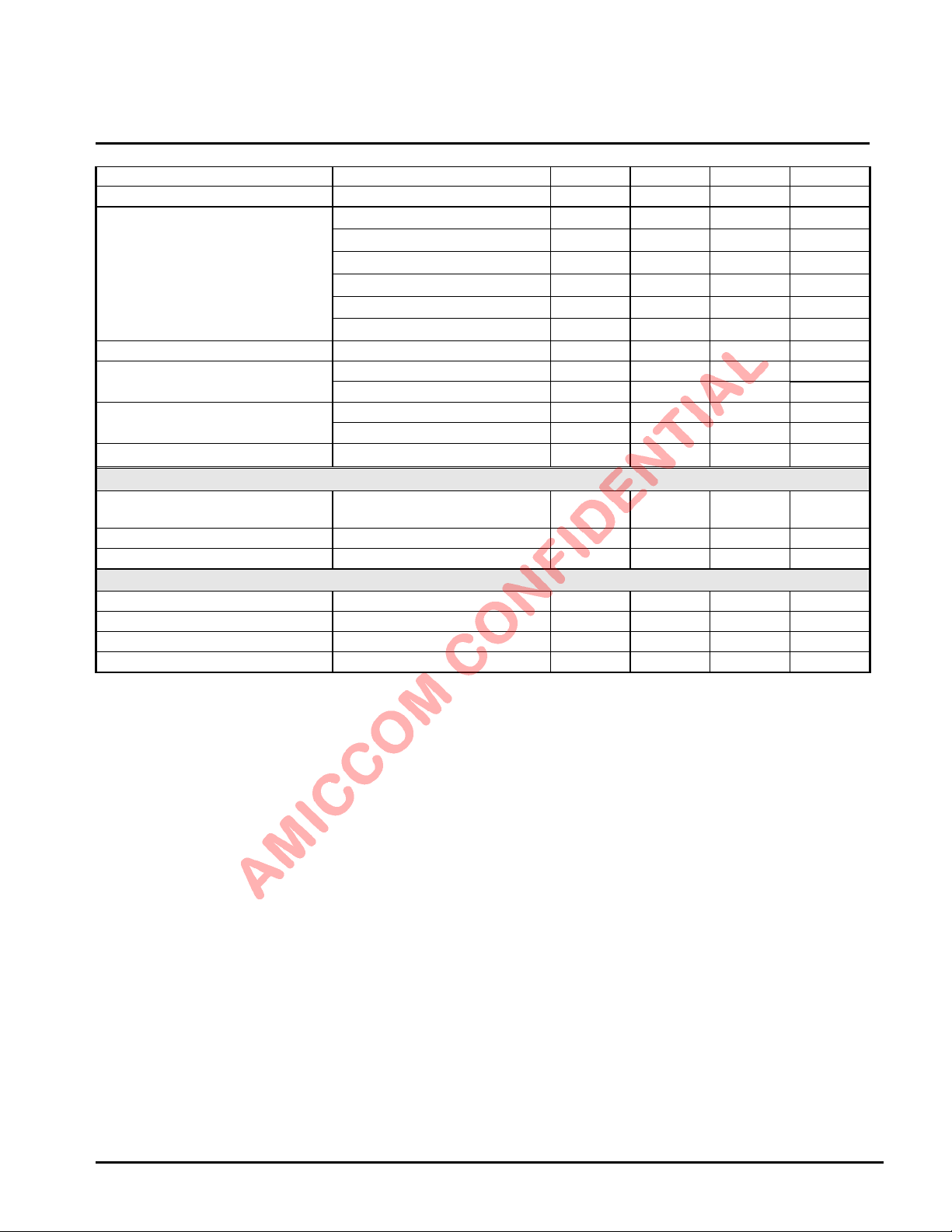

16h

TX II

17h

Delay I

18h

Delay II

19h

RX

1Ah

RX Gain I

1Bh

RX Gain II

1Ch

RX Gain III

1Dh

RX Gain IV

1Eh

RSSI Threshold

1Fh

ADC Control

20h

Code I

21h

Code II

22h

Code III

23h

IF Calibration I

IF Calibration II

25h

VCO current

Calibration

26h

VCO band

Calibration I

27h

VCO band

Calibration II

28h

VCO deviation

Calibration I

29h

VCO deviation

Calibration II

2Ah

DASP0

DASP1

DASP2

DASP3

DASP4

DASP5

DASP6

W

W DPR2 DPR1 DPR0 TDL1 TDL0 PDL2 PDL1 PDL0

W

W

W PRS MIC IGC1 IGC0 MGC1 MGC0 LGC1 LGC0

R

W RSAGC1 RSAGC0 VTL2 VTL1 VTL0 VTH2 VTH1 VTH0

R RH7 RH6 RH5 RH4 RH3 RH2 RH1 RH0

W -- RDU IFS1 IFS0 RSM1 RSM0 ERSSM RSS

R RL7 RL6 RL5 RL4 RL3 RL2 RL1 RL0

W LIMC IFBC1 IFBC0 IFAS MHC1 MHC0 LHC1 LHC0

W RTH7 RTH6 RTH5 RTH4 RTH3 RTH2 RTH1 RTH0

R ADC7 ADC6 ADC5 ADC4 ADC3 ADC2 ADC1 ADC0

W

W

W MSCRC EDRL HECS ETH2 ETH1 ETH0 PMD1 PMD0

W CRCINV WS6 WS5 WS4 WS3 W S2 WS1 WS0

W HFR CKGS1 CKGS0 MFBS MFB3 MFB2 MFB1 MFB0

R

W PWORS

R -- -- -- FCD4 FCD3 FCD2 FCD1 FCD0

W ROSCS RSIS VCRLS MVCS VCOC3 VCOC2 VCOC1 VCOC0

R -- -- -- VCCF VCB3 VCB2 VCB1 VCB0

W DCD1 DCD0 DAGS CWS MVBS MVB2 MVB1 MVB0

R - - - - VBCF VB2 VB1 VB0

W MDAG7 MDAG6 MDAG5 MDAG4 MDAG3 MDAG2 MDAG1 MDAG0

R ADAG7 ADAG6 ADAG5 ADAG4 ADAG3 ADAG2 ADAG1 ADAG0

W DEVS3 DEVS2 DEVS1 DEVS0 DAMR _M VMTE_M VMS_M MSEL

R DEVA7 DEVA6 DEVA5 DEVA4 DEVA3 DEVA2 DEVA1 DEVA0

W MVDS MDEV6 MDEV5 MDEV4 MDEV3 MDEV2 MDEV1 MDEV0

R ADEV7 ADEV6 ADEV5 ADEV4 ADEV3 ADEV2 ADEV1 ADEV0

W

W

W

W DCV7 DCV6 DCV5 DCV4 DCV3 DCV2 DCV1 DCV0

W VMG7 VMG6 VMG5 VMG4 VMG3 VMG2 VMG1 VMG0

R VMG7 VMG6 VMG5 VMG4 VMG3 VMG2 VMG1 VMG0

W -- -- PKT1 PKT0 PKS PKIS1 PKIS0 IFPK

W -- HPLS HRS PACTL IWS CNT MXD LXD

FD7 FD6 FD5 FD4 FD3 FD2 FD1 FD0

WSEL2 WSEL1 WSEL0 RSSC_D1 RSSC_D0 RS_DLY2 RS_DLY1 RS_DLY0

LNAGE AGCE RXSM1 RXSM0 AFCE RXDI DMG ULS

-- MICR IGCR1 IGCR0 MGCR1 MGCR0 LGCR1 LGCR0

AVSEL1 AVSEL0 MVSEL1 MVSEL0 RADC FSARS XADS CDM

MCS WHTS FECS CRCS IDL1 IDL0 PML1 PML0

-- -- -- FBCF FB3 FB2 FB1 FB0

TRT2 TRT1 TRT0 ASMV2

QLIM RFSP

STS CELS

VTRB3 VTRB2 VTRB1 VTRB0 VMRB3 VMRB2 VMRB1 VMRB0

INTRC

(CSXTL5)

CSXTL4 CSXTL3 CSXTL2 CSXTL1 CSXTL0

RGS RGC1 RGC0 VRPL1 VRPL0 INTPRC

ASMV1 ASMV0 AMVS24h

Oct., 2012, Version 0.6 (PRELIMINARY) 13 AMICCOM Electronics Corporation

Page 14

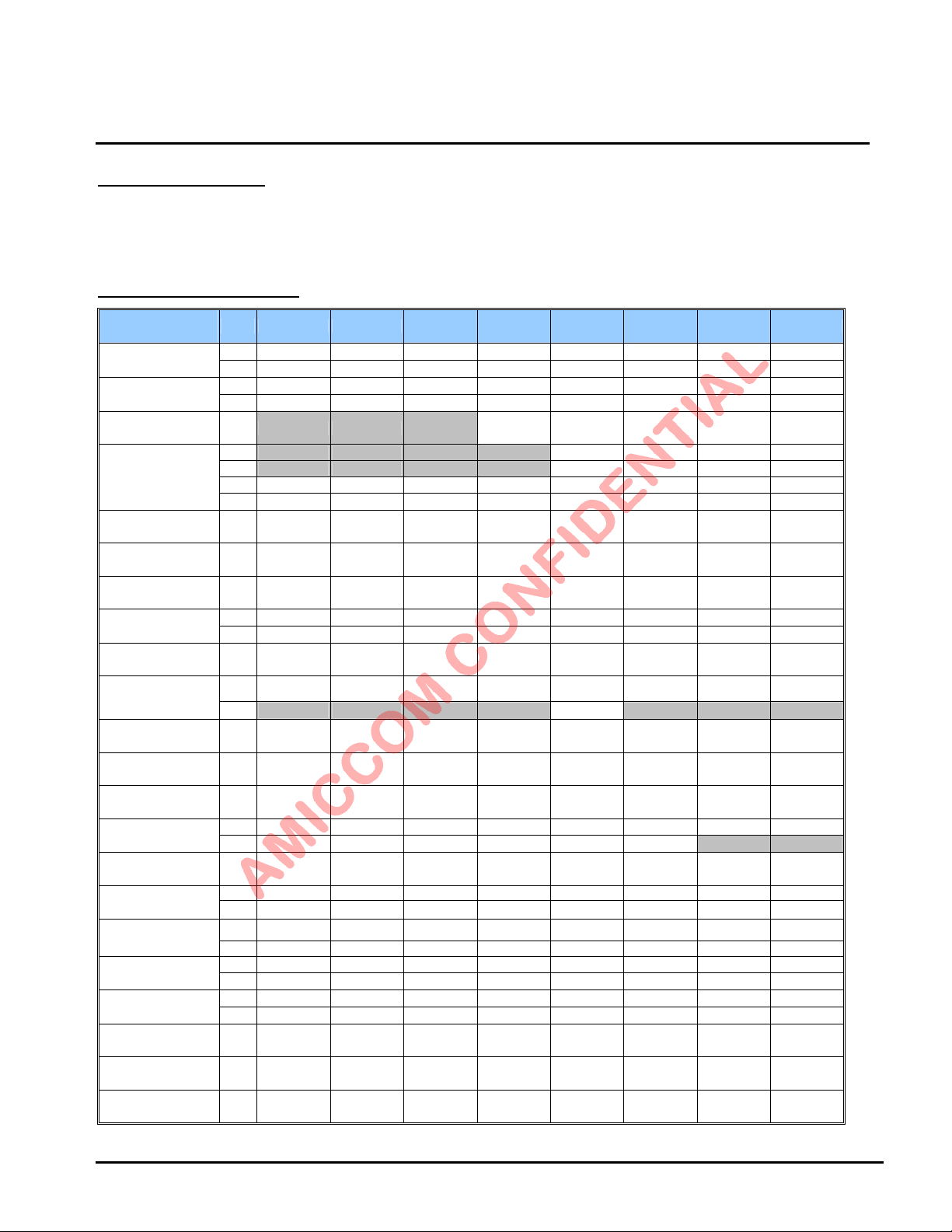

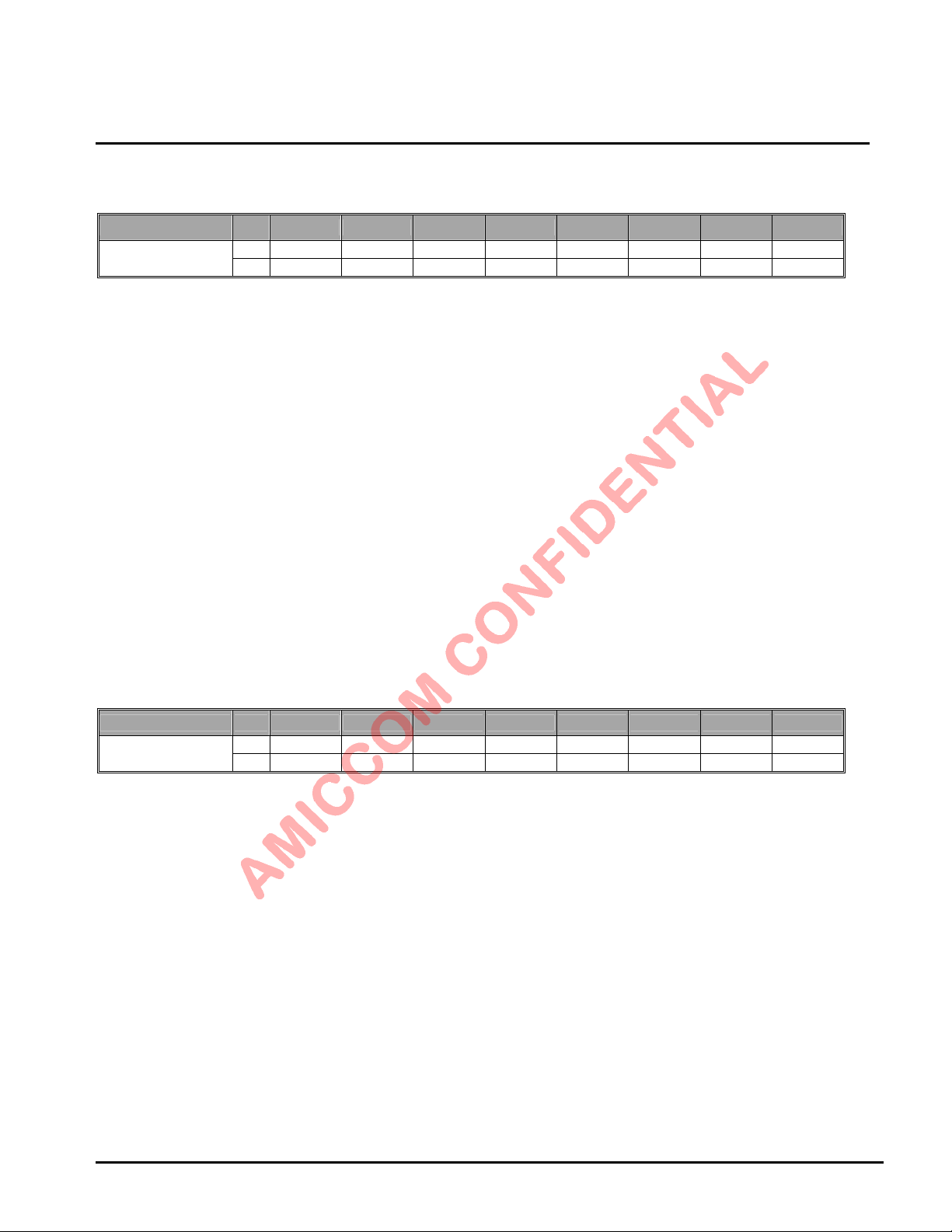

2Bh

VCO modulation

W

DMV1 DMV0 DEVFD2 DEVFD1 DEVFD0 DEVD2 DEVD1 DEVD0

Delay

2Ch

Battery detect

2Dh

TX test

2Eh

Rx DEM test I

2Fh

Rx DEM test II

W

W

W DMT DCM1 DCM0 MLP1 MLP0 SLF2 SLF1 SLF0

W DCH1 DCH0 DCL2 DCL1 DCL0 RAW CDTM1 CDTM0

LVR

R -- RGV1 RGV0 BDF BVT2 BVT1 BVT0 BD_E

RMP1 RMP0 TXCS PAC1 PAC0 TBG2 TBG1 TBG0

RGV1 RGV0 QDS BVT2 BVT1 BVT0 BD_E

30h

CPM3 CPM2 CPM1 CPM0 CPT3 CPT2 CPT1 CPT0

Charge Pump

W

Current I

31h

Charge Pump

W CPTX3 CPTX2 CPTX1 CPTX0 CPRX3 CPR X2 CPRX1 CPRX0

Current II

32h

Crystal test

33h

PLL test

34h

VCO test

35h

RF Analog test

36h

Key Data

37h

Channel Select

38h

ROM_P0

W

CDPM CPS CPH CPCS DBD XCC XCP1 XCP0

MDEN OLM PRIC1 PRIC0 PRRC1 PRRC0 SDPW NSDO

W

DEVGD2 DEVGD1 DEVGD0 TLB1 TLB0 RLB1 RLB0 VBS

W

AGT3 AGT2 AGT1 AGT0 RFT3 RFT2 RFT1 RFT0

W

W/R

KEY7 KEY6 KE Y5 KE Y4 KEY3 KEY2 KE Y1 KEY0

W CHI3 CHI2 CHI1 CHI0 CHD3 CHD2 CHD1 CHD0

W

MPOR EPRG MIGS MRGS MRSS MTMS MADS MBGS

ROMP1 W APG MPA1 MPA0 FBG4 FBG3 FBG2 FBG1 FBG0

ROMP2 W PTM1 PTM0 CTR5 CTR4 CTR3 CTR2 CTR1 CTR0

ROMP3 W -- -- CRS2 CRS1 CRS0 CTS2 CTS1 CTS0

ROMP4 W -- STMP STM5 STM4 STM3 STM2 ST M1 STM0

39h

Data Rate CLK

3Ah

FCR

3Bh

ARD

3Ch

AFEP

3Dh

FCB

3Eh

KEYC

3Fh

USID

W SDR7 SDR6 SDR5 SDR4 SDR3 SDR2 SDR1 SDR0

W FCL1 FCL0 ARC3 ARC2 ARC1 ARC0 EACKS EARTS

R ARTEF VPOAK

W

ARD7 ARD6 ARD5 ARD4 ARD3 ARD2 ARD1 ARD0

W EACKF SPSS ACKFEP5 ACKFEP4 ACKFEP3 ACKFEP2 ACKFEP1 ACKFEP0

R

W/R

W

W

-- -- EARTS EARTS EARTS TXSID2 TXSID1 TXSID0

F7 F6 F5 F4 F3 F2 F1 F0

MEDCS AFIDS ARTMS MIDS AESS -- AKFS EDCRS

RND7 RND6 RND5 RND4 RND3 RND2 RND1 RND0

RCR3 RCR2 RCR1 RCR0 EACKS EARTS

Legend: -- = unimplemented

LBA7130

Oct., 2012, Version 0.6 (PRELIMINARY) 14 AMICCOM Electronics Corporation

Page 15

9.2 Control register description

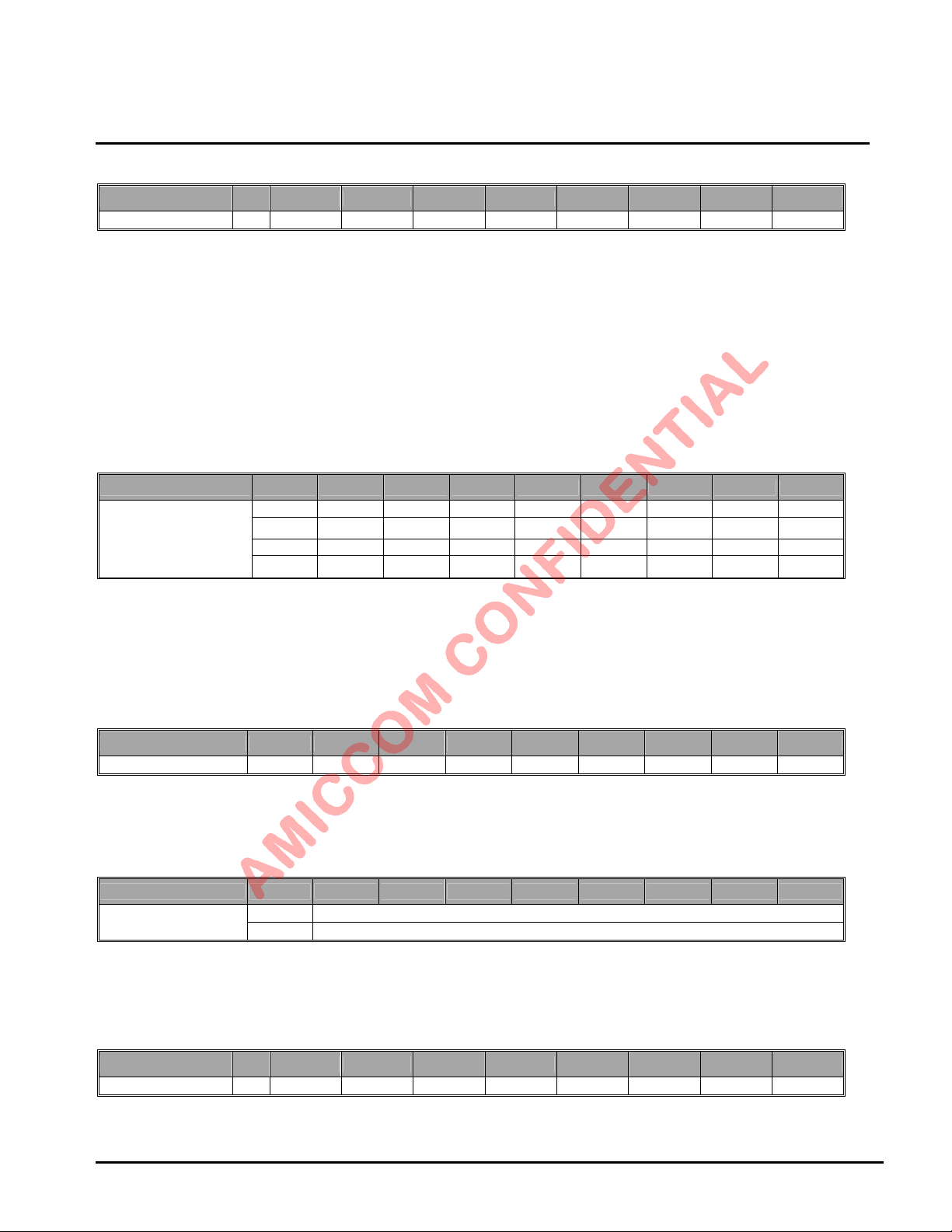

9.2.1 Mode Register (Address: 00h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Mode

RESETN: Write to this register by 0x00 to issue reset command, then it is auto clear

HECF: Head Control Flag. (HECF will be clear after issue a strobe command.)

HEC is CRC-8 result for the optional Packet Header (Please refer to chapter 16 for details)

[0]: HEC pass. [1]: HEC error.

FECF: FEC flag. (FECF will be clear after issue any strobe command.)

[0]: FEC pass. [1]: FEC error.

CRCF: CRC flag. (CRCF will be clear after issue any strobe command.)

[0]: CRC pass. [1]: CRC error.

CER: RF chip enable status.

[0]: RF chip is disabled. [1]: RF chip is enabled.

XER: Internal crystal oscillator enabled status.

[0]: Crystal oscillator is disabled. [1]: Crystal oscillator is enabled.

PLLE: PLL enabled status.

[0]: PLL is disabled. [1]: PLL is enabled.

TRER: TRX state enabled status.

[0]: TRX is disabled. [1]: TRX is enabled.

TRSR: TRX Status Register.

[0]: RX state. [1]: TX state.

Serviceable if TRER=1 (TRX is enable).

R HECF FECF CRCF CER XER PLLER TRSR TRER

W RESETN

RESETN RESETN RESETN RESETN RESETN RESETN RESETN

LBA7130

9.2.2 Mode Control Register (Address: 01h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Mode Control I

DDPC (Direct mode data pin control): Direct mode modem data can be accessed via SDIO pin.

[0]: Disable. [1]: Enable.

ARSSI: Auto RSSI measurement while entering RX mode.

[0]: Disable. [1]: Enable.

AIF (Auto IF Offset): RF LO frequency will auto offset one IF frequency while entering RX mode.

[0]: Disable. [1]: Enable.

CD: Carrier detector (Read only).

[0]: Input power below threshold. [1]: Input power above threshold.

DFCD: Data Filter by CD : The received packet would be filtered if the input power level is below RTH (1Eh).

[0]: Disable. [1]: Enable.

WORE: WOR (Wake On RX) Function Enable.

[0]: Disable. [1]: Enable.

FMT: Reserved for internal usage only. Shall be set to [0].

FMS: Direct/FIFO mode select.

[0]: Direct mode. [1]: FIFO mode.

ADCM: ADC measurement enable (Auto clear when done).

[0]: Disable measurement or measurement finished. [1]: Enable measurem ent.

Refer to chapter 17 for details.

R DDPC ARSSI AIF DFCD WORE FMT FMS ADCM

W DDPC ARSSI AIF CD WORE FMT FMS ADCM

Oct., 2012, Version 0.6 (PRELIMINARY) 15 AMICCOM Electronics Corporation

Page 16

9.2.3 Calibration Control Register (Address: 02h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Mode Control II R/W -- -- --

VCC: VCO Current calibration enable (Auto clear when done).

[0]: Disable. [1]: Enable.

VBC: VCO Bank calibration enable (Auto clear when done).

[0]: Disable. [1]: Enable.

VDC: VCO Deviation calibration enable (Auto clear when done).

[0]: Disable. [1]: Enable.

FBC: IF Filter Bank calibration enable (Auto clear when done).

[0]: Disable. [1]: Enable.

RSSC: RSSI calibration enable (Auto clear when done).

[0]: Disable. [1]: Enable.

VCC VBC VDC FBC RSSC

9.2.4 FIFO Register I (Address: 03h)

Name R/W Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8

W -- -- -- -- FEP11 FEP10 FEP9 FEP8

FIFO I

R -- -- -- -- LENF11 LENF10 LENF9 LENF8

W FEP7 FEP6 FEP5 FEP4 FEP3 FEP2 FEP1 FEP0

R LENF7 LENF6 LENF5 LENF4 LENF3 LENF2 LENF1 LENF0

LBA7130

FEP [11:0]: FIFO End Pointer for TX FIFO and Rx FIFO.

Data Sequence is FEP[7:0] and FEP[15:8].

Please refer to chapter 16 for details.

LENF [11:0]: Received FIFO Length for dynamic FIFO function. (Ready Only)

When EDRL =1, that means dynamic FIFO is enabled, MCU can read LENF [11:0] to know the RX FIFO length of the coming

packet. Please refer to chapter 16 for details.

9.2.5 FIFO Register II (Address: 04h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

FIFO II W FPM1 FPM0 PSA5 PSA4 PSA3 PSA2 PSA1 PSA0

FPM [1:0]: FIFO Pointer Margin

PSA [5:0]: Used for Segment FIFO.

Refer to chapter 16 for details.

9.2.6 FIFO DATA Register (Address: 05h)

Bit R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Name

FIFO [7:0]: TX FIFO / RX FIFO

TX FIFO and RX FIFO share the same address (05h).

TX FIFO and RX FIFO are separated physical 64 Bytes.

Refer to chapter 16 for details.

W TX-FIFO[7:0]

R/W RX-FIFO[7:0]

9.2.7 ID DATA Register (Address: 06h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

ID DATA R/W ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0

ID [7:0]: ID data.

When this address is accessed, ID Data is input or output sequential (ID Byte 0,1, 2 and 3) corresponding to Write or Read.

Oct., 2012, Version 0.6 (PRELIMINARY) 16 AMICCOM Electronics Corporation

Page 17

Recommend to set ID Byte 0 = 5xh or Axh.

Refer to section 10.6 for details.

9.2.8 RC OSC Register I (Address: 07h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RCOC7 RCOC6 RCOC5 RCOC4 RCOC3 RCOC2 RCOC1 RCOC0

RC OSC I

RCOC [7:0]: Reserved for internal usage (read only).

R

WOR_SL7 WOR_SL6 WOR_SL5 WOR_SL4 WOR_SL3 WOR_SL2 WOR_SL1 W OR_SL0

W

9.2.9 RC OSC Register II (Address: 08h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RC OSC II W

WOR_AC [5:0]: 6-bits WOR Active Timer for WOR and TWOR Function

WOR_SL [9:0]: 10-bits WOR Sleep Timer for WOR and TWOR Function.

WOR_SL [9:0] are from address (07h) and (08h),

Active period = (WOR_AC+1) x (1/4092).

Sleep period = (WOR_SL+1) x (1/32) x (1/4092).

WOR_SL9 WOR_SL8 WOR_AC5 WOR_AC4 WOR_AC3 WOR_AC2 WOR_AC1 WOR_AC0

LBA7130

9.2.10 RC OSC Register III (Address: 09h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RC OSC III

RTCS: internal Oscillator selection in sleep mode. Recommend RTCS= [0].

[0]: RC oscillator. [1]: RTC oscillator.

RCOT[2:0]: Reserved for internal used. Recommend RCOT= [000].

RCOT[1:0]: RCOSC current select for RC oscillator calibration.

[00]: 240nA [01]: 280nA [10]: 320nA [11]: 360nA

TSEL: Timer select for TWOR function.

[0]: Use WOR_AC. [1]: Use WOR_SL.

CALWC: RC Oscillator Calibration Enable.

[0]: Disable. [1]: Enable.

CALWR: RC Oscillator Calibration ending indication.

[0]: ending. [1]: Not ending.

RCOSC_E: RC-oscillator enable.

[0]: Disable. [1]: Enable.

TSEL: Timer Duty select for TWOR function.

[0]: Use WOR_AC. [1]: Use WOR_SL.

TWORE: Enable TWOR function.

[0]: WOR mode. [1]: TWOR mode.

W RTCS RCO T2

R -- -- -- -- CALWR

RCOT1/

RTCC1

RCOT0/

RTCC0

CALWC

RCOSC_E TSEL TW ORE

-- -- --

9.2.11 CKO Pin Control Register (Address: 0Ah)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

CKO Pin Control W ECKOE CKOS3 CKOS2 CKOS1 CKOS0 CKOI CKOE SCKI

ECKOE: CKO pin Output Enable.

[0]: Disable. [1]: Enable.

CKOS [3:0]: CKO pin output select.

Oct., 2012, Version 0.6 (PRELIMINARY) 17 AMICCOM Electronics Corporation

Page 18

[0000]: DCK (TX data clock) in TX mode, RCK (RX recovery clock) in RX mode.

[0001]: DCK (TX data clock) in TX mode, RCK (RX recovery clock) in RX mode.

[0010]: FPF (FIFO pointer flag).

[0011]: EOP, EOVBC, EOFBC, EOVCC, EOVDC, RSSC_OK. (Internal usage only).

[0100]: External clock output= F

[0101]: External clock output / 2= F

[0110]: RXD

[0111]: FSYNC.

[1000]: WCK.

[1001]: PF8M.(8Mhz, internal usage)

[1010]: ROSC.

[1011]: MXDEC(SLF[0]=1:~OKADCN, SLF[1]=0: DEC , internal usage)

[1100]: BDF (Battery Detect flag).

[1101]: F

[1110]: VPOAK.

[1111]: WRTC (internal usage)

CKOI: CKO pin output signal invert.

[0]: Non-inverted output. [1]: Inverted output.

CKOE: CKO pin Output Enable.

[0]: High Z. [1]: Enable.

SCKI: SPI clock input invert.

[0]: Non-inverted input. [1]: Inverted input.

SYCK

..

SYCK

/ 2.

SYCK

/ 4.

LBA7130

9.2.12 GIO1 Pin Control Register I (Address: 0Bh)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

GIO1 Pin Control I W VKM VPM GIO1S3 GIO1S2 GIO1S1 GIO1S0 GIO1I GI O1OE

VKM: Valid packet mode select.

[0]: by event. [1]: by pulse.

VPM: Valid Pulse width select.

[0]: 20u. [1]: 40u.

TX Mode (disable auto-resend, EAR=0).

Oct., 2012, Version 0.6 (PRELIMINARY) 18 AMICCOM Electronics Corporation

Page 19

RX Mode (disable Auto-ack, EAK =0).

LBA7130

Note1, If auto-resend is enabled (EAR = 1), WTR behavior is different while it is output to GIO1 and GIO2.

Note2, If auto-ack is enabled (EAK = 1), WTR behavior is different while it is output to GIO1 and GIO2.

Note3, VPOAK’s behavior is controlled by VPM (0Bh) and VPW (0Bh).

Refer to chapter 19 for details

GIO1S [3:0]: GIO1 pin function select.

GIO1S [3:0] TX state RX state

[0000] WTR (Wait until TX or RX finished)

[0001] EOAC (end of access code) FSYNC (frame sync)

[0010] TMEO (TX modulation enable) CD (carrier detect)

[0011] Preamble Detect Output (PMDO)

[0100] If RCOSC_E =1, output TWOR.

If RCOSC_E =0, output CWTR signal. (internal usage)

[0101] In phase demodulator input(DMII)or VT[0] (internal usage)

[0110] SDO ( 4 wires SPI data out)

[0111] TRXD In/Out (Direct mode)

[1000] RXD (Direct mode)

[1001] TXD (Direct mode)

[1010] PDN_RX

[1011]

[1100] MXINC(SLF[0]=1:EOADC.SLF[1]=0:INC.) (internal usage)

[1101] FPF

[1110] VPOAK (Valid Packet or Auto ACK OK Output)

[1111] FMTDO (internal usage)

If GIO1S = [0100] and RCOSC_E = 0, CWTR is an internal signal to monitor TX/RX cycles of auto-ack and auto-resend.If

GIO1S = [1011] and direct mode is selected, the internal frame sync function will be disabled. In such case, A7130 supports

to accept an external frame sync signal from MCU to feed to GIO1 pi n to determine the timing of fixing DC estimation voltage

of demodulator.

GIO1I: GIO1 pin output signal invert.

[0]: Non-inverted output. [1]: Inverted output.

GIO1OE: GIO1pin output enable.

[0]: High Z. [1]: Enable.

External FS YNC input in RX direct mode (internal usage)

Oct., 2012, Version 0.6 (PRELIMINARY) 19 AMICCOM Electronics Corporation

Page 20

LBA7130

9.2.13 GIO2 Pin Control Register II (Address: 0Ch)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

GIO2 Pin Control II W BBCKS1 BBCKS0 GIO2S3 GIO2S2 GIO2S1 GIO2S0 GIO2I GI O2OE

BBCKS [1:0]: Clock select for digital block. Recommend BBCKS = [00].

[00]: F

GIO2S [3:0]: GIO2 pin function select.

If GIO2S = [0100] and RCOSC_E = 0, CWTR is an internal signal to monitor TX/RX cycles of auto-ack and auto-resend.

GIO2I: GIO2 pin output signal invert.

[0]: Non-inverted output. [1]: Inverted output.

GIO2OE: GIO2 pin Output Enable.

[0]: High Z. [1]: Enable.

SYCK

. [01]: F

/ 2. [10]: F

SYCK

/ 4. [11]: F

SYCK

SYCK

/ 8.

GIO2S TX state RX state

[0000] WTR (Wait until TX or RX finished)

[0001] EOAC (end of access code) FSYNC (frame sync)

[0010] TMEO (TX modulation enable) CD (carrier detect)

[0011] Preamble Detect Output (PMDO)

[0100] If RCOSC_E =1, output TWOR.

If RCOSC_E =0, output CWTR signal. (internal usage)

[0101] Quadrature phase demodulator input (DMIQ) (internal usage)

[0110] SDO (4 wires SPI data out)

[0111] TRXD In/Out (Direct mode)

[1000] RXD (Direct mode)

[1001] TXD (Direct mode)

[1010] PDN_TX

[1011] ROMOK(ROM Program OK) (internal usage)

[1100] BDF (Battery Detect Flag)

[1101] FPF

[1110] VPOAK (Valid Packet or Auto ACK OK Output)

[1111] DCK (internal usage)

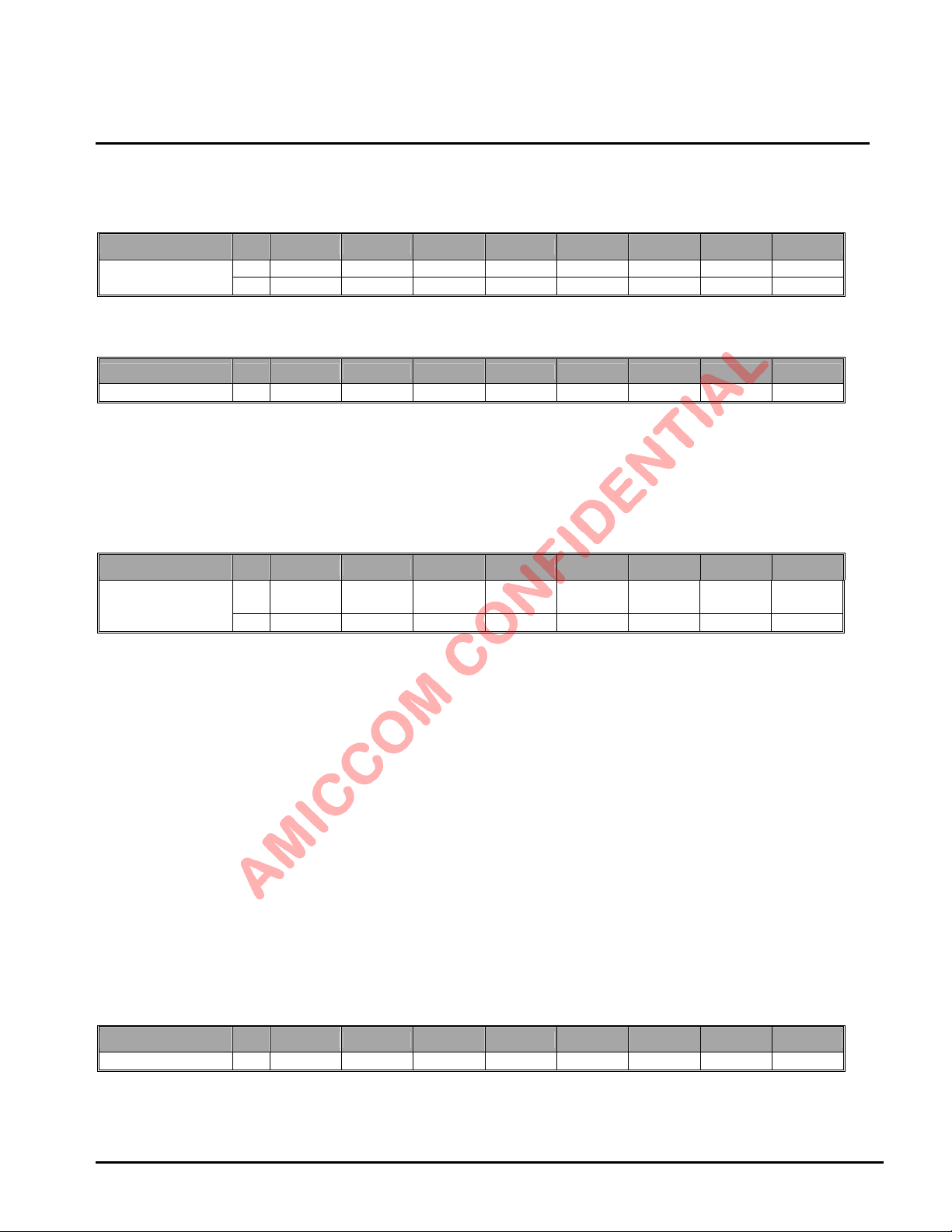

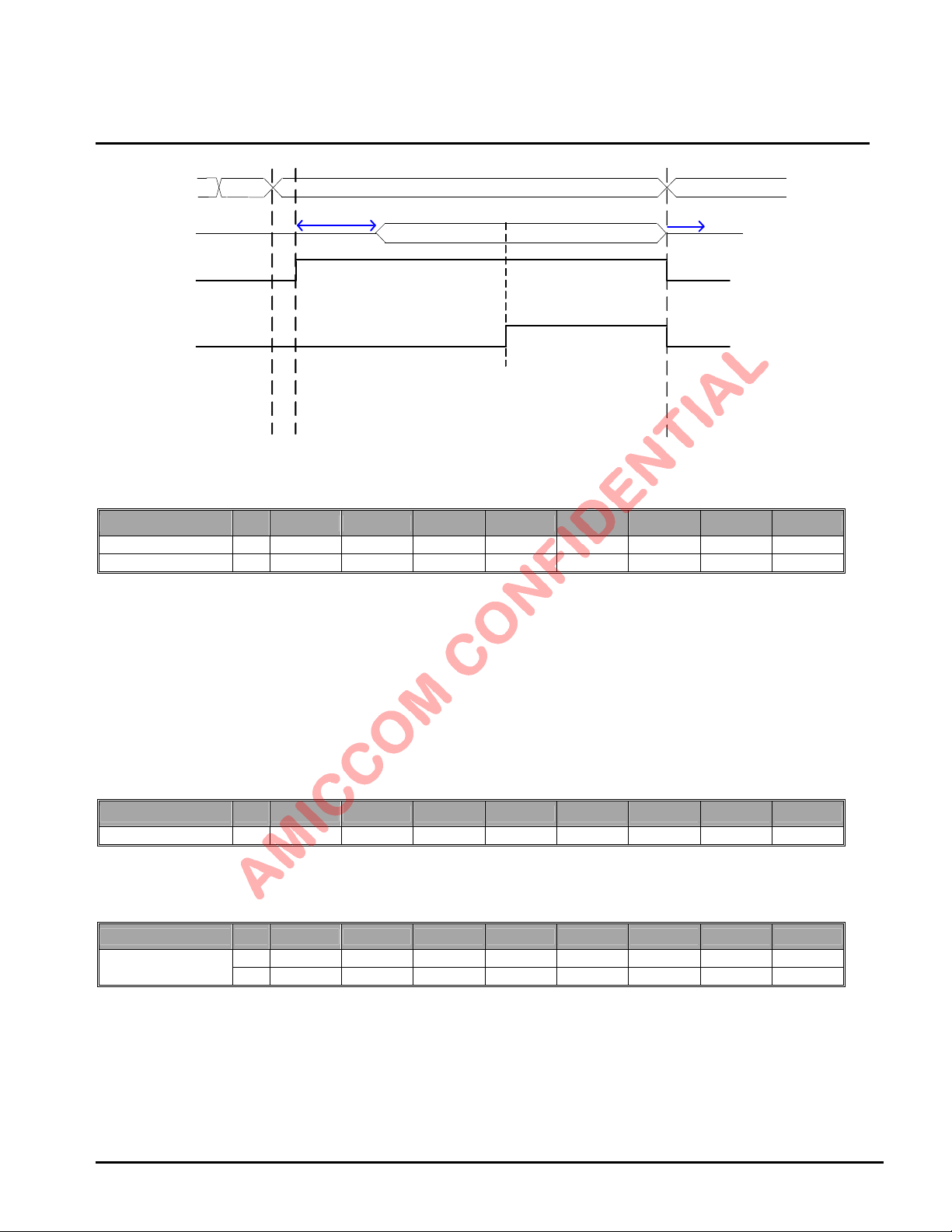

In TX mode

SPI

(SCS,SCK,SDIO)

RF Port

(Output)

GIO1 Pin - WTR

(GIO1S[3:0]=0000)

GIO2 Pin - TMEO

(GIO2S[3:0]=0010)

TX-Strobe

PLL Mode

10 us + (PDL+TDL)

T0

T1

< 1us

No Command Required

Preamble +

ID Code + Payload

+ CRC

16 us

PA Ramp Down

T2

Next Instruction

Auto Back

PLL Mode

T3

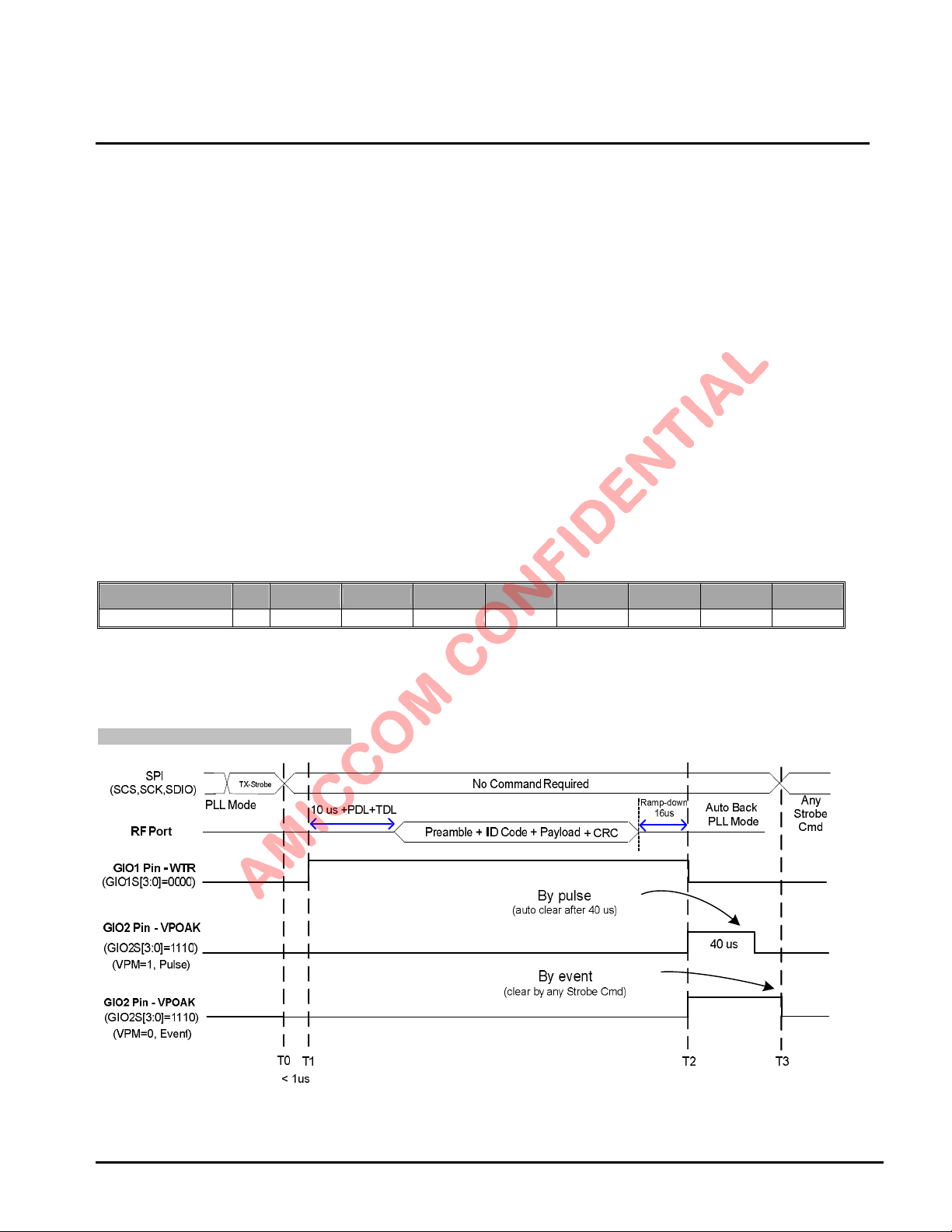

In RX mode

Oct., 2012, Version 0.6 (PRELIMINARY) 20 AMICCOM Electronics Corporation

Page 21

LBA7130

SPI

(SCS,SCK,SDIO)

RF Po rt

(Input)

GIO1 Pin - WTR

(GIO1S[3:0]=0000)

GIO2 Pin - FSYNC

(GIO2S[3:0]=0001)

RX-Strobe

PLL Mode

T0

< 1us

T1

10us+PDL+TDL

No Command Required

Preamble +

ID Code + Payload

ID-Matched

+ CRC

T2

9.2.14 Clock Register (Address: 0Dh)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Clock W

CGC [1:0]: Clock Gen. Current select. Shall be set to [10].

GRC [3:0]: Clock generation reference counter. Recommend GRC = [0111] for 16MHz Xtal.

GRC [3:0] is used to let below formula be true when CGS = 1.

F

x (DBL+1) / (GRC+1) = 2MHz.

XTAL

CGS: Clock generator enable. Recommend CGS = [1]

[0]: Disable. [1]: Enable.

XS: Crystal oscillator select. Recommend XS = [1]

[0]: External clock. [1]: Crystal.

IFS [1:0]: IF band selection. (Ready only)

CGC1 CGC0 GRC3 GRC2 GRC1 GRC0

IFS1 IFS0 GRC3 GRC2 GRC1 GRC0

R

Next Instruction

Auto Back

PLL Mode

CGS XS

-- --

9.2.15 PLL Register I (Address: 0Eh)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PLL I R/W CHN7 CHN6 CHN5 CHN4 CHN3 CHN2 CHN1 CHN0

CHN [7:0]: LO channel number select.

Refer to chapter 14 for details.

9.2.16 PLL Register II (Address: 0Fh)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PLL II

DBL: Crystal frequency doublers selection.

[0]: Disable. F

[1]: Enable. F

XREF

XREF

In FIFO mode, recommend to set DBL =0.

In Direct mode, recommend to set DBL =1.

Please refer to A7130 reference code for details.

RRC [1:0]: RF PLL reference counter setting. Recommend RRC = [00].

The PLL comparison frequency, F

Oct., 2012, Version 0.6 (PRELIMINARY) 21 AMICCOM Electronics Corporation

R DBL RRC1 RRC0 CHR3 CHR2 CHR1 CHR0 IP8

W DBL RRC1 RRC0 CHR3 CHR2 CHR1 CHR0 BIP8

= F

.

XTAL

=2 * F

XTAL

.

PFD

= F

*(DBL+1) / (RRC+1).

CRYSTAL

Page 22

CHR [3:0]: PLL channel step setting.

In FIFO mode, recommend to set CHR [3:0] = [0111].

In Direct mode, recommend to set CHR [3:0] = [1111].

Please refer to chapter 14 and A7130 reference code for details.

9.2.17 PLL Register III (Address: 10h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PLL III

BIP [8:0]: LO base frequency integer part setting. (0Fh and 10h)

In FIFO mode, recommend to set BIP [8:0] = [0x096].

In Direct mode, recommend to set BIP [8:0] = [0x04B].

Please refer to chapter 14 and A7130 reference code for details.

IP [8:0]: LO frequency integer part value.

IP [8:0] are from address (0Fh) and (10h),

Refer to chapter 14 for details.

R IP7 IP6 IP5 IP4 IP3 IP2 IP1 IP0

W BIP7 BIP6 BIP5 BIP4 BIP3 BIP2 BIP1 BIP0

9.2.18 PLL Register IV (Address: 11h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PLL IV

R RAC15 RAC14 RAC13 RAC12 RAC11 RAC10 RAC9 RAC8

W BFP15 BF P14 BFP13 BFP12 BF P11 BFP10 BFP9 BFP8

LBA7130

9.2.19 PLL Register V (Address: 12h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PLL V

BFP [15:0]: LO base frequency fractional part setting. (11h and 12h)

In FIFO mode, recommend to set BFP [15:0] = [0x0004].

In Direct mode, recommend to set BFP [15:0] = [0x0002].

Please refer to chapter 14 and A7130 reference code for details.

RAC [15:0]: Auto Frequency compensation value if AFC (19h) =1.

RAC [15:0] Note

AFC = 1 PLLFF [15:0] LO Freq. compensation value

AFC = 0 {SYNCF, AC [14:0]}

R RAC7 RAC6 RAC5 RAC4 RAC3 RAC2 RAC1 RAC0

W BFP7 BFP6 BFP5 BFP4 BFP3 BFP2 BFP1 BFP0

9.2.20 Channel Group Register I (Address: 13h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

CHGI R/W

CHGL [7:0]: PLL channel group low boundary setting for auto-calibration. Recommed CHGL[7:0] = 0x3C.

Refer to A7130 reference code for details.

CHGL7 CHGL6 CHGL5 CHGL4 CHGL3 CHGL2 CHGL1 CHGL0

9.2.21 Channel Group Register II (Address: 14h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

CHGII R/W

CHGH [7:0]: PLL channel group high boundary setting for auto-calibration. Recommed CHGH[7:0] = 0x78.

Refer to A7130 reference code for details.

CHGH7 CHGH6 CHGH5 CHGH4 CHGH3 CHGH2 CHGH1 CHGH0

PLL calibration frequency is divided into 3 groups by CHGL and CHGH:

Channel

Group1 0 ~ CHGL-1

Group2 CHGL ~ CHGH-1

Oct., 2012, Version 0.6 (PRELIMINARY) 22 AMICCOM Electronics Corporation

Page 23

Group3 CHGH ~ 255

9.2.22 TX Register I (Address: 15h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

TX I W GDR GF TMDE TXDI TME FDP2 FDP1 FDP0

GDR: Gaussian Filter Over Sampling Rate Select. Recommend GDR = [1].

[0]: BT= 0.7 [1]: BT= 0.5

GF: Gaussian Filter Select.

[0]: Disable. [1]: Enable.

TMDE: TX modulation enable for VCO modulation. Recommend TMDE = [1].

[0]: Disable. [1]: Enable.

TXDI: TX data invert. Recommend TXDI = [0].

[0]: Non-invert. [1]: Invert.

TME: TX modulation enable. Recommend TME = [1].

[0]: Disable. [1]: Enable.

FDP [2:0]: Frequency deviation power setting. Recommend FDP = [110].

In FIFO mode, recommend to set FDP [2:0] = [111].

In Direct mode, recommend to set FDP [2:0] = [110].

Please refer to chapter 14 and A7130 reference code for details.

LBA7130

9.2.23 TX Register II (Address: 16h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

TXI W

FD [7:0]: Frequency deviation setting.

F

= (F

DEV

Where F

/216) x FD[7:0] x 2

PFD

= F

PFD

* (DBL+1) / (RRC [1:0]+1), PLL comparison frequency.

XTAL

FD7 FD6 FD5 FD4 FD3 FD2 FD1 FD0

(FDP-1)

.

Data Rate FDP[2:0] FD[7:0] Fdev

4Mbps FIFO mode 111 0x40 1MHz

4Mbps Direct mode 110 0x40 1MHz

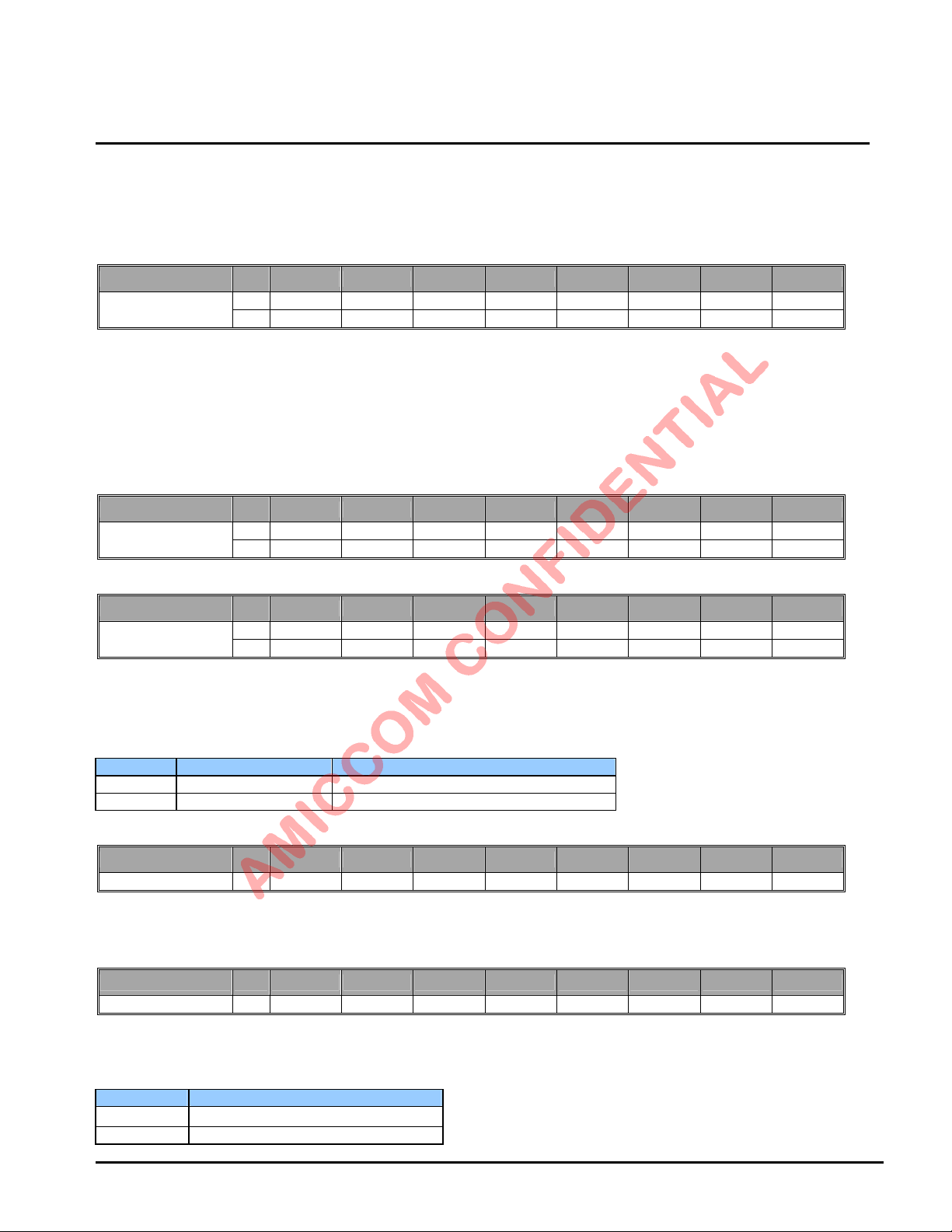

9.2.24 Delay Register I (Address: 17h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

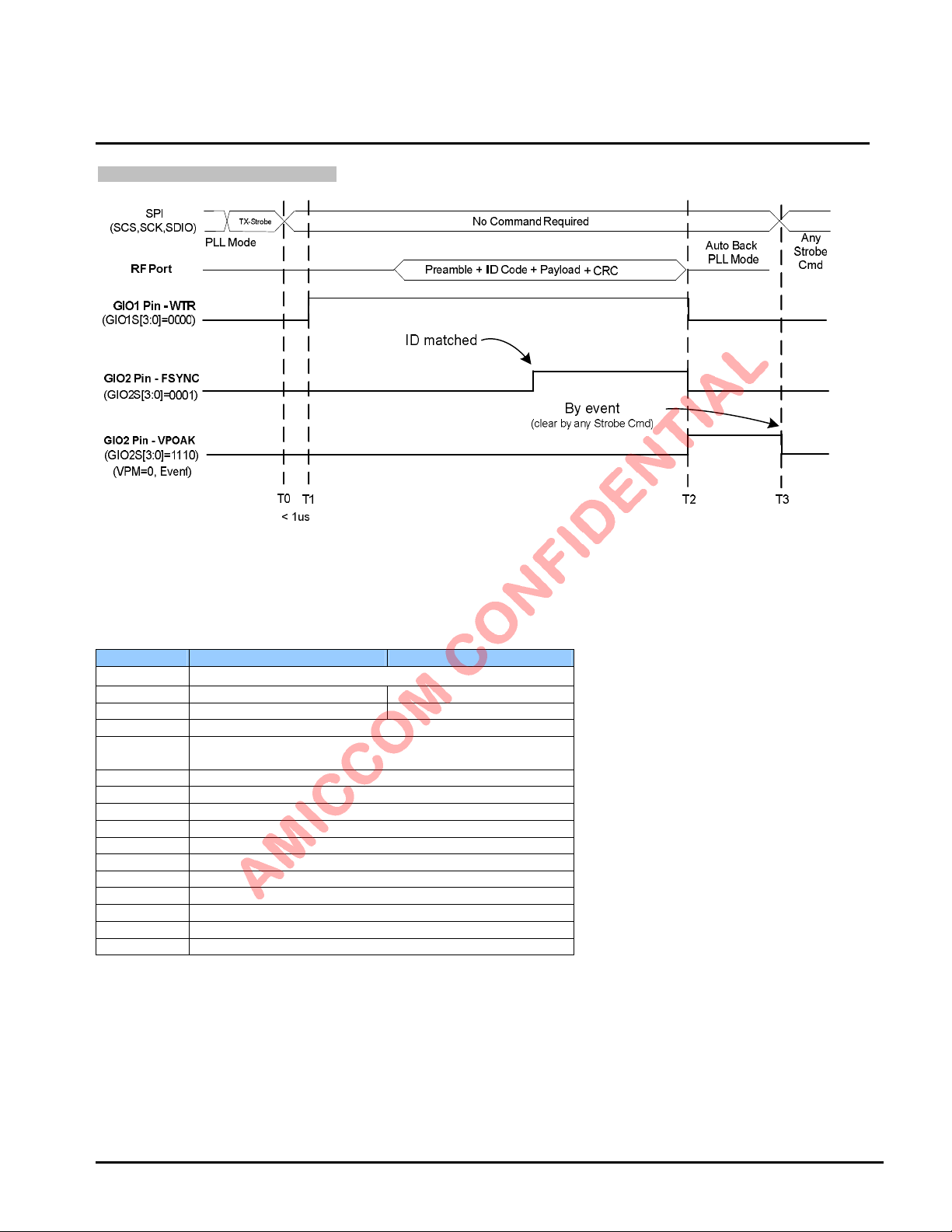

Delay W DPR2 DPR1 DPR0 TDL1 TDL0 PDL2 PDL1 PDL0

DPR [2:0]: Delay scale. Recommend DPR = [000].

TDL [1:0]: Delay for TX settling from WPLL to TX.

TDL Delay= 20 * (TDL [1:0]+1)*(DPR [2:0]+1) us.

DPR [2:0] TDL [1:0] WPLL to TX Note

000 00 20 us

000 01 40 us

000 10 60 us Recommend

000 11 80 us

PDL [2:0]: Delay for TX settling from PLL to WPLL.

PDL Delay= 10 + {20 * (PDL [2:0]+1)*(DPR [2:0]+1)} us.

DPR [2:0] PDL [2:0] PLL to WPLL

Note

(LO freq changed)

000 000 30 us Recommend

000 001 50 us

Oct., 2012, Version 0.6 (PRELIMINARY) 23 AMICCOM Electronics Corporation

Page 24

000 010 70 us

000 011 90 us

000 100 110 us

LBA7130

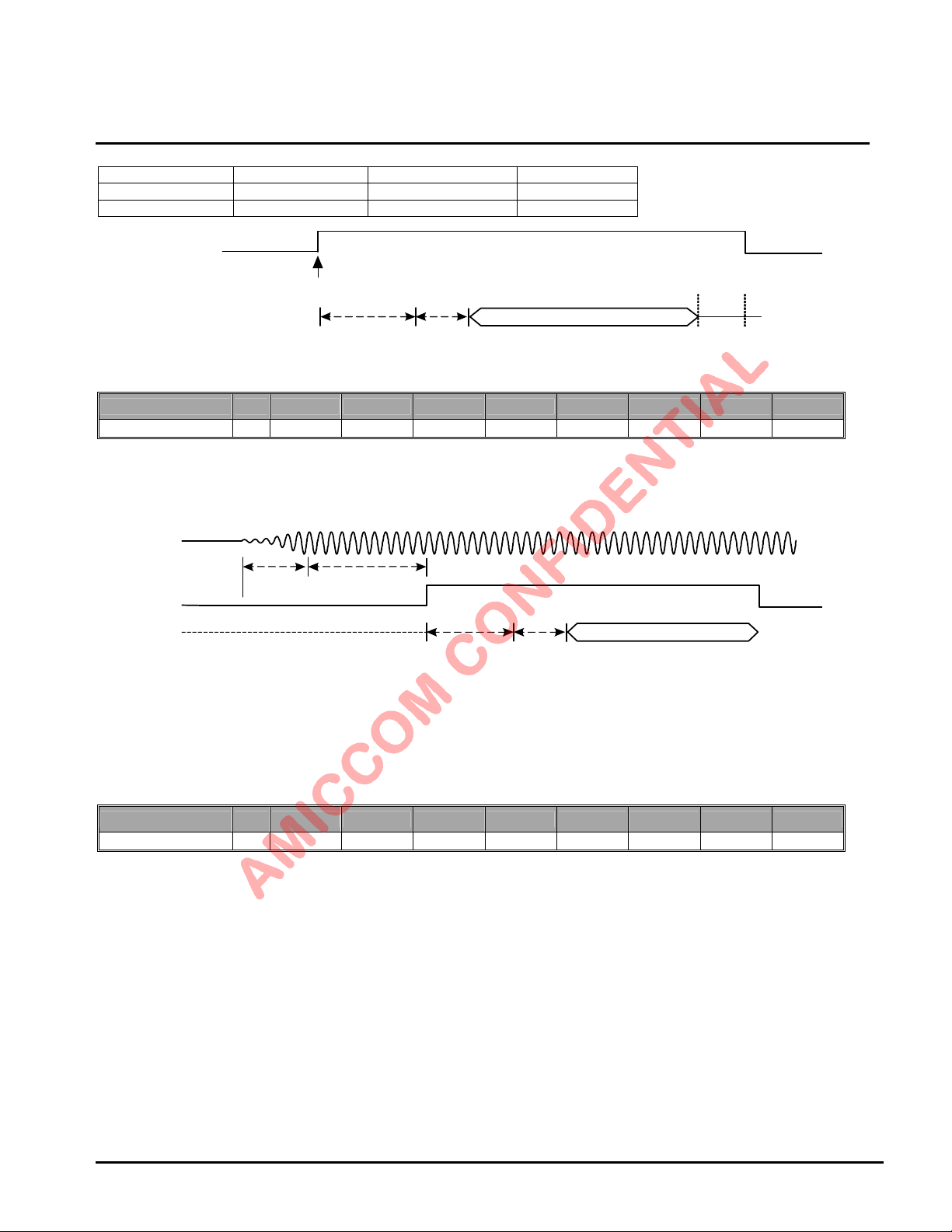

G IO 1 P in

(WTR)

R FO Pin

PLL Mode

TX Strobe

10 us + PDL

TDL

TX M ode

Packet

9.2.25 Delay Register II (Address: 18h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Delay W WSEL2 WSEL1 WSEL0 RSSC_D1 RSSC_D0 RS_DLY2 RS_DLY1 RS_DLY0

WSEL [2:0]: XTAL settling delay setting (200us ~ 2.5ms). Recommend WSEL = [011].

[000]: 200us. [001]: 400us. [010]: 600us. [011]: 800us.

[100]: 1ms. [101]: 1.5ms. [110]: 2ms. [111]: 2.5ms.

Crystal

O scilla tor

GIO1 Pin

(WTR)

R FO Pin

RSSC_D [1:0]: RSSI calibration switching time (10us ~ 40us). Recommend RSSC_D = [00].

[00]: 10us. [01]: 20us. [10]: 30us. [11]: 40us.

RS_DLY [2:0]: RSSI measurement delay (10us ~ 80us). Recommend RS_DLY = [000].

[000]: 10us. [001]: 20us. [010]: 30us. [011]: 40us.

[100]: 50us. [101]: 60us. [110]: 70us. [111]: 80us.

Id le

mode

300 us

WSEL

TX or R X S trob e Cm d

10 us + PDL

Packet (Preamble + ID + Payload)

TDL

PA

Ramp Down

16 us

9.2.26 RX Register (Address: 19h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RX W LNAGE AGCE RXSM1 RXSM0 AFCE RXDI DMG ULS

LNAGE: Auto LNA Gain Control Select.

[0]: Disable. [1]: Enable.

AGCE: Auto Front end Gain Control Select.

[0]: Disable. [1]: Enable.

RXSM1: RX clock recovery circuit moving average filter length. Recommend RXSM1 = [1].

[0]: 4 bits. [1]: 8 bits.

RXSM0: Demodulator LPF Bandwidth Select. Recommend RXSM0 = [1].

[0]: 2*IF. [1]: 1*IF.

AFCE: Frequency compensation select.

[0]: Disable. [ 1]: Enable.

RXDI: RX data output invert. Recommend RXDI = [0].

[0]: Non-inverted output. [1]: Inverted output.

DMG: Demodulator Gain Select. Recommend DMG = [1].

[0]: x 1. [1]: x 3.

Oct., 2012, Version 0.6 (PRELIMINARY) 24 AMICCOM Electronics Corporation

Page 25

ULS: RX Up/Low side band select. Recommend ULS = [0].

[0]: Up side band, [1]: Low side band.

Refer to section 14.2 for details.

9.2.27 RX Gain Register I (Address: 1Ah)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RX Gain I

PRS: Limiter amplifier discharge manual select. Recommend PRS =[0].

MIC: Mixer buffer gain setting. Recommend MIC =[1].

[0]: 0dB. [1]: 6dB.

IGC [1:0]: IFA Attenuation Select. Recommend IGC =[10].

[00]: 0dB. [01]: 6dB. [10]: 12dB. [11]: 18dB.

MGC [1:0]: Mixer Gain Attenuation select. Recommend MGC =[11].

[00]: 0dB. [01]: 6dB. [10]: 12dB. [11]: 18dB.

LGC [1:0]: LNA Gain Attenuation select. Recommend LGC =[11].

[00]: 0dB. [01]: 6dB. [10]: 12dB. [11]: 18dB.

W PRS MIC IGC1 IGC0 MGC1 MGC0 LGC1 LGC0

R -- MICR IGCR1 IGCR0 MGCR1 MGCR0 LGCR1 LGCR0

9.2.28 RX Gain Register II (Address: 1Bh)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RX Gain II

R RH7 RH6 RH5 RH4 RH3 RH2 RH1 RH0

W

RSAGC1 RSAGC0 VTL2 VTL1 VTL0 VTH2 VTH1 VTH0

LBA7130

RSAGC [1:0]: AGC clock select. Recommend RSAGC = [11].

[00]: IF / 8. [01]: IF / 4. [10]: IF/ 2. [11]: IF

VTL [2:0]: VCO tuning voltage lower threshold level setting. Recommend VTL = [000].

[000]: 0.1V. [001]: 0.2V. [010]: 0.3V. [011]: 0.4V.

[100]: 0.5V. [101]: 0.6V. [110]: 0.7V. [111]: 0.8V

VTH [2:0]: VCO tuning voltage upper threshold level setting. Recommend VTH = [010].

[000]: VDD_A – 0.6V. [001]: VDD_A – 0.7V. [010]: VDD_A – 0.8V. [011]: VDD_A – 0.9V

[100]: VDD_A – 1.0V. [101]: VDD_A – 1.1V. [110]: VDD_A – 1.2V. [111]: VDD_A – 1.3V

Remark: VDD_A is on chip analog regulator output voltage where is set to 1.8V.

RH [7:0]: RSSI Calibration High Threshold. (Read only)

.

9.2.29 RX Gain Register III (Address: 1Ch)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RX Gain III

RDU: Clock Generator Select. Recommend RDU = [0].

[0]: 128MHZ [1]: 96MHZ.

IFS [1:0]: IF Frequency Select.

[00]: reserved. [01]: reserved. [10]: reserved [11]: 4MHZ.

RSM [1:0]: RSSI Margin = RTH – RTL. Recommend RSM = [11].

[00]: 5. [01]: 10. [10]: 15. [11]: 20.

Refer to chapter 17 for details.

ERSSM: Ending Mode Select in RSSI Measurement. Recommend ERSSM = [0].

[0]: RSSI ending by RX. [1]: RSSI ending by SYNC_Ok.

RSS: RSSI measurement select. (XADS=0, RSS=0, default mode is thermal sensor.)

[0]: Disable. [1]: Enable (recomm end).

R RL7 RL6 RL5 RL4 RL3 RL2 RL1 RL0

W

-- RDU IFS1 IFS0 RSM1 RSM0 ERSSM RSS

Oct., 2012, Version 0.6 (PRELIMINARY) 25 AMICCOM Electronics Corporation

Page 26

RL [7:0]: RSSI Calibration Low Threshold. (Ready only)

9.2.30 RX Gain Register IV (Address: 1Dh)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RX Gain III W LIMC IFBC1 IFBC0 IFAS MHC1 MHC0 LHC1 LHC0

LIMC: IF limiter current select. Recommend LIMC = [1].

[0]: 0.3mA. [1]: 0.6mA.

IFBC [1:0]: IF BPF current Select. Recommend IFBC = [11].

[00]: 0.75 mA.. [01]: 1.4mA. [10]: 2.1mA. [11]: 3.5mA.

IFAS: IF Amp current select. Recommend IFAS = [0].

[0]: 0.3mA. [1]: 0.6mA.

MHC: Mixer Current Select. Recommend MHC = [01].

[00]: 0.6mA. [01]: 1.2mA. [10]: reserved. [11]: reserved.

LHC[1:0]: LNA Current Select. Recommend LHC = [11].

[00]: 0.5mA. [01]: 1mA. [10]: 1.5mA. [11]: 2m A.

9.2.31 RSSI Threshold Register (Address: 1Eh)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RSSI Threshold

R ADC7 ADC6 ADC5 ADC4 ADC3 ADC2 ADC1 ADC0

W

RTH7 RTH6 RTH5 RTH4 RTH3 RTH2 RTH1 RTH0

LBA7130

RTH [7:0]: Carrier detect threshold.

Refer to Chapter 17 for details.

CD (Carrier Detect)=1 when RSSI ≧ RT H.

CD (Carrier Detect)=0 when RSSI < RTL.

ADC [7:0]: ADC output value for RSSI measurement.

ADC input voltage= 1.2 * ADC [7:0] / 256 V.

9.2.32 ADC Control Register (Address: 1Fh)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

ADC Control W AVSEL1 AVSEL0 MVSEL1 MVSEL0 RADC FSARS XADS CDM

AVSEL [1:0]: ADC average times (for Carrier / temeperature sensor / external ADC). Recommend AVSEL = [11].

[00]: No average. [01]: Average 2 times. [10]: Average 4 times. [11]: Average 8 times.

MVSEL [1:0]: ADC average times (for VCO calibration and RSSI ). Recommend MVSEL = [11].

[00]: Average 8 times. [01]: Average 16 times. [10]: Average 32 times. [11]: Average 64 times.

RADC: ADC Read Out Average Mode. Recommend RADC = [0].

[0]: by AVSEL.

[1]: by MVSEL.

FSARS: ADC clock select. Recommend FSARS = [0].

[0]: 4MHz. [1]: 8MHz.

XADS: External ADC Input Signal Select.

[0]: Disable. [1]: Enable.

CDM: RSSI measurement mode. Recommend CDM = [1].

[0]: Single mode. [1]: Continuous mode.

9.2.33 Code Register I (Address: 20h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Code I W MCS WHTS FECS CRCS IDL1 IDL0 PML1 PML0

Oct., 2012, Version 0.6 (PRELIMINARY) 26 AMICCOM Electronics Corporation

Page 27

MSC: Manchester Enable.

[0]: Disable. [1]: Enable.

WHTS: Data Whitening (Data Encryption) Select.

[0]: Disable. [1]: Enable (The data is whitening by multiplying PN7).

FECS: FEC Select.

[0]: Disable. [1]: Enable (The FEC is (7, 4) Hamming code).

CRCS: CRC Select. Recommend CRCS = [1].

[0]: Disable. [1]: Enable.

IDL [1:0]: ID Code Length Select. Recommend IDL= [01].

[00]: 2 bytes. [01]: 4 bytes. [10]: 6 bytes. [11]: 8 bytes.

PML [1:0]: Preamble Length Select. Recommend PML= [11].

[00]: 1 byte. [01]: 2 bytes. [10]: 3 bytes. [11]: 4 bytes.

9.2.34 Code Register II (Address: 21h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Code II W MSCRC EDRL HECS ETH2 ETH1 ETH0 PMD1 PMD0

MSCRC: Mask CRC (CRC Data Filtering Enable). Recommend MSCRC = [1].

[0]: Disable. [1]: Enable.

EDRL: Enable FIFO Dynamic Length

[0]: Disable. [1]: Enable.

Please refer to chapter 16 for details.

HECS: HEC Header CRC-8 select.

[0]: Disable. [1]: Enable.

Please refer to chapter 16 for details.

ETH [2:0]: Received ID Code Error Tolerance. Recommend ETH = [001].

[000]: 0 bit, [001]: 1 bit. [010]: 2 bit. [011]: 3 bit. [100]: 4 bit, [101]: 5 bit. [110]: 6 bit. [111]: 7 bit.

PMD [1:0]: Preamble pattern detection length. Recommend PMD = [10].

[00]: 0bit. [01]: 4bits. [10]: 8bits. [11]: 16bits.

LBA7130

9.2.35 Code Register III (Address: 22h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Code III W CRCINV WS6 WS5 WS4 W S3 W S2 WS1 WS0

CRCINV: CRC Inverted Select.

[0]: Non-inverted. [1]: inverted.

WS [6:0]: Data Whitening seed setting (data encryption key).

The data is whitened by multiplying with PN7.

Please refer to chapter 16 for details.

9.2.36 IF Calibration Register I (Address: 23h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

IF Calibration I

HFR: Half Rate setting. Recommend HFR = [0].

[0]: Clk gen. by 32 x Data Rate. [1]: Clk gen. by 16 x Data Rate.

CKGS[1:0]: Clock gen. data rate manual setting. Recommend CKGS = [11].

[00]: reserved. [01]: reserved. [10]: reserved. [11]: 4MHZ.

When RDU=0, CKGS[1:0] = IFS[1:0]

When RDU=1, CKGS[1:0] = Manual setting.

MFBS: IF filter calibration value select. Recommend MFBS = [0].

Oct., 2012, Version 0.6 (PRELIMINARY) 27 AMICCOM Electronics Corporation

R -- -- -- FBCF FB3 FB2 FB1 FB0

W HFR CKGS1 CKGS0 MFBS MFB3 MFB2 MFB1 MFB0

Page 28

[0]: Auto calibration value. [1]: Manual calibrati on value.

MFB [3:0]: IF filter manual calibration value.

FBCF: IF filter auto calibration flag (read only).

[0]: Pass. [1]: Fail.

FB [3:0]: IF filter calibration value (read only).

MFBS= 0: Auto calibration value (AFB),

MFBS= 1: Manual calibration value (MFB).

9.2.37 IF Calibration Register II (Address: 24h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

IF Calibration II

PWORS: TX high power setting. Recommend PWORS = [1].

[0]: Disable. [1]: Enable.

TRT [2:0]: TX Ramp down discharge current select. Recommend TRT = [111].

AMSV [2:0]: TX Ramp up Timing Select. Recommend AMSV = [111].

[000]: 2us, [001]: 4us. [010]: 6us. [011]: 8us. [100]: 10us, [101]: 12us. [110]: 14us. [111]: 16us.

Real case of TX ramping up is AMSV [2:0] multiplied by 2^(RMP[1:0])

AMVS: TX Ramp Up Enable. Recommend AMVS = [1].

[0]: Disable. [1]: Enable.

FCD [4:0]: IF filter calibration deviation from goal (read only).

R -- -- FCD4 FCD3 FCD2 FCD1 FCD0

W PWORS TRT2 TRT1 TRT0 ASMV2 ASMV1 ASMV0 AMVS

LBA7130

9.2.38 VCO current Calibration Register (Address: 25h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

VCO current

Calibration

ROSCS: WOR RC select. Recommend ROSCS = [1]

RSIS: WOR current select. Recommend RSIS = [0]

VCRLS: VCO Current Resistor Select. Recommend VCRLS = [0]

[0]: low current select. [1]: high current select.

MVCS: VCO current calibration value select. Recommend MVCS = [0].

[0]: Auto calibration value. [1]: Manual calibrati on value.

VCOC [3:0]: VCO current manual calibration value.

VCCF: VCO Current Auto Calibration Flag (read only).

[0]: Pass. [1]: Fail.

VCB [3:0]: VCO current calibration value (read only).

MVCS= 0: Auto calibration value (VCB).

MVCS= 1: Manual calibration value (VCOC).

R -- -- -- VCCF VCB3 VCB2 VCB1 VCB0

ROSCS RSIS VCRLS MVCS VCO C3 VCOC2 VCOC1 VCOC0

W

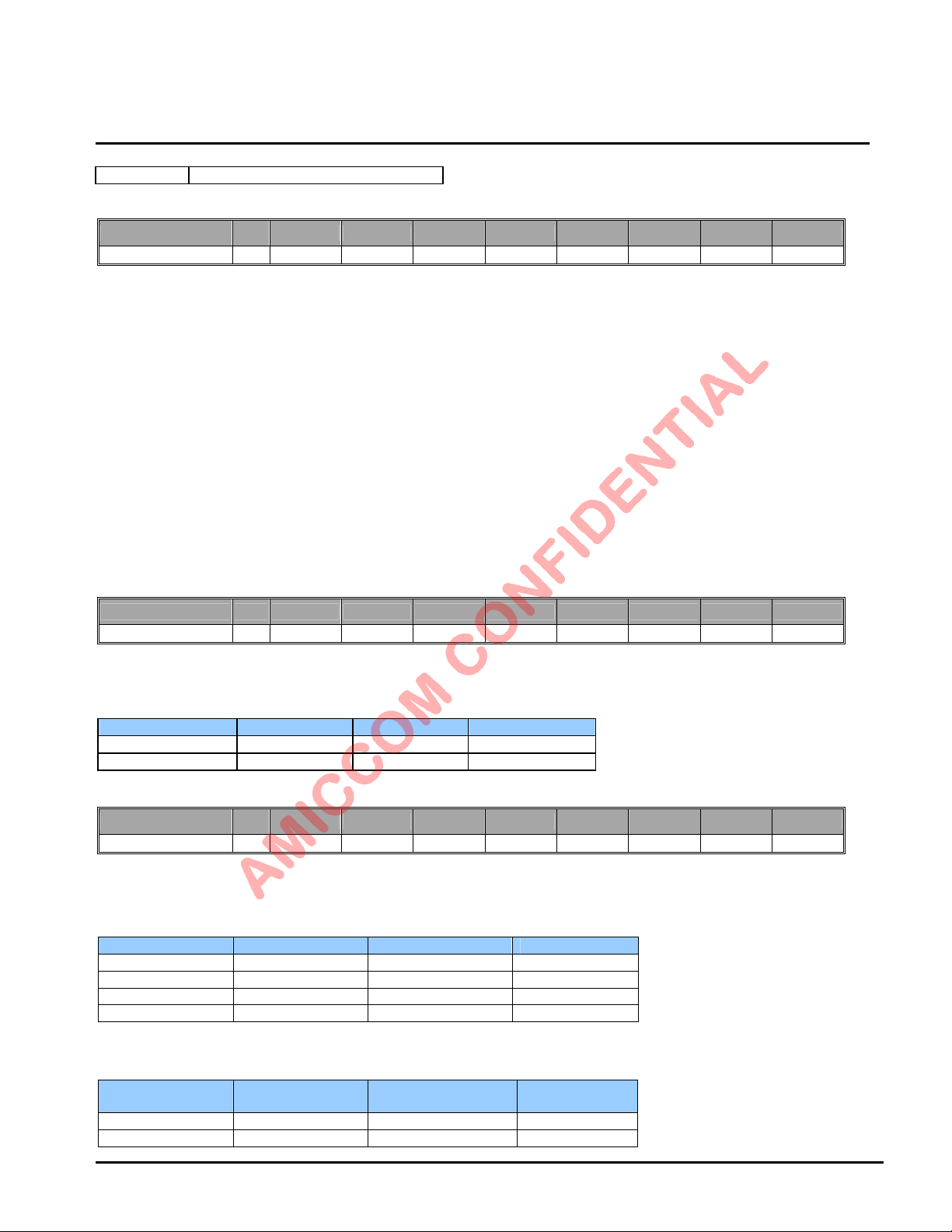

9.2.39 VCO band Calibration Register I (Address: 26h)

Name R/W Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

VCO Single band

Calibration I

DCD [1:0]: VCO Deviation Calibration Delay. Recommend DCD = [11].

Delay time = PDL (Delay Register I, 17h) × ( DDC + 1 ).

DAGS: DAG Calibration Value Select. Recommend DAGS = [0].