Lattice Semiconductor Corporation PALCE22V10H-15JI-4, PALCE22V10H-15PC-4, PALCE22V10H-15PI-4, PALCE22V10H-15SC-4, PALCE22V10H-20JI-4 Datasheet

...

PALCE22V10

PALCE22V10Z

COM'L: H-5/7/10/15/25,Q-10/15/25 IND: H-10/15/20/25

COM'L: -25 IND: -15/25

PALCE22V10 and PALCE22V10Z

Families

24-Pin EE CMOS (Zero P o wer) V er satile PAL Device

DISTINCTIVE CHARACTERISTICS

◆

As fast as 5-ns propagation delay and 142.8 MHz f

Low-power EE CMOS

◆

10 macrocells programmable as registered or combinatorial, and active high or active low to

◆

match application needs

◆

Varied product term distribution allows up to 16 product terms per output for complex

functions

Peripheral Component Interconnect (PCI) compliant (-5/-7/-10)

◆

Global asynchronous reset and synchronous preset for initialization

◆

◆

Power-up reset for initialization and register preload for testability

◆

Extensive third-party software and programmer support

24-pin SKINNY DIP, 24-pin SOIC, and 28-pin PLCC

◆

◆

5-ns and 7.5-ns versions utilize split leadframes for improved performance

(external)

MAX

GENERAL DESCRIPTION

The P ALCE22V10 provides user-programmable logic for replacing conventional SSI/MSI gates and

flip-flops at a reduced chip count.

®

The PALCE22V10Z is an advanced PAL

erasable CMOS technology. It provides user-programmable logic for replacing conventional zeropower CMOS SSI/MSI gates and flip-flops at a reduced chip count.

The PALCE22V10Z provides zero standby power and high speed. At 30 µA maximum standby

current, the PALCE22V10Z allows battery-powered operation for an extended period.

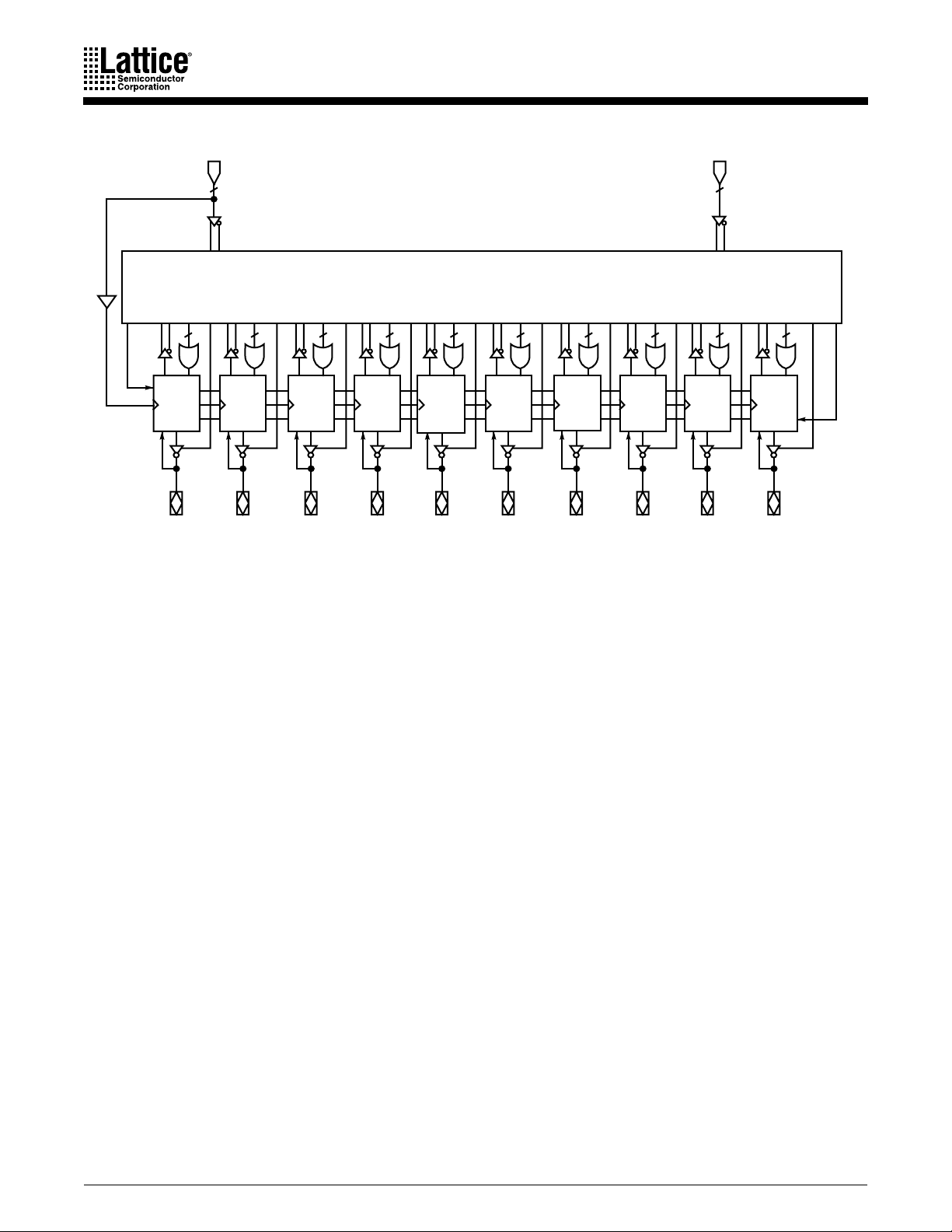

The P AL device implements the familiar Boolean logic transfer function, the sum of products. The

P AL device is a programmable AND array driving a fixed OR array. The AND array is programmed

to create custom product terms, while the OR array sums selected terms at the outputs.

The product terms are connected to the fixed OR array with a varied distribution from 8 to16 across

the outputs (see Block Diagram). The OR sum of the products feeds the output macrocell. Each

macrocell can be programmed as registered or combinatorial, and active-high or active low. The

output configuration is determined by two bits controlling two multiplexers in each macrocell.

device built with zero-power, high-speed, electrically-

Publication#

Amendment/

16564

0

Rev:

E

Issue Date:

November 1998

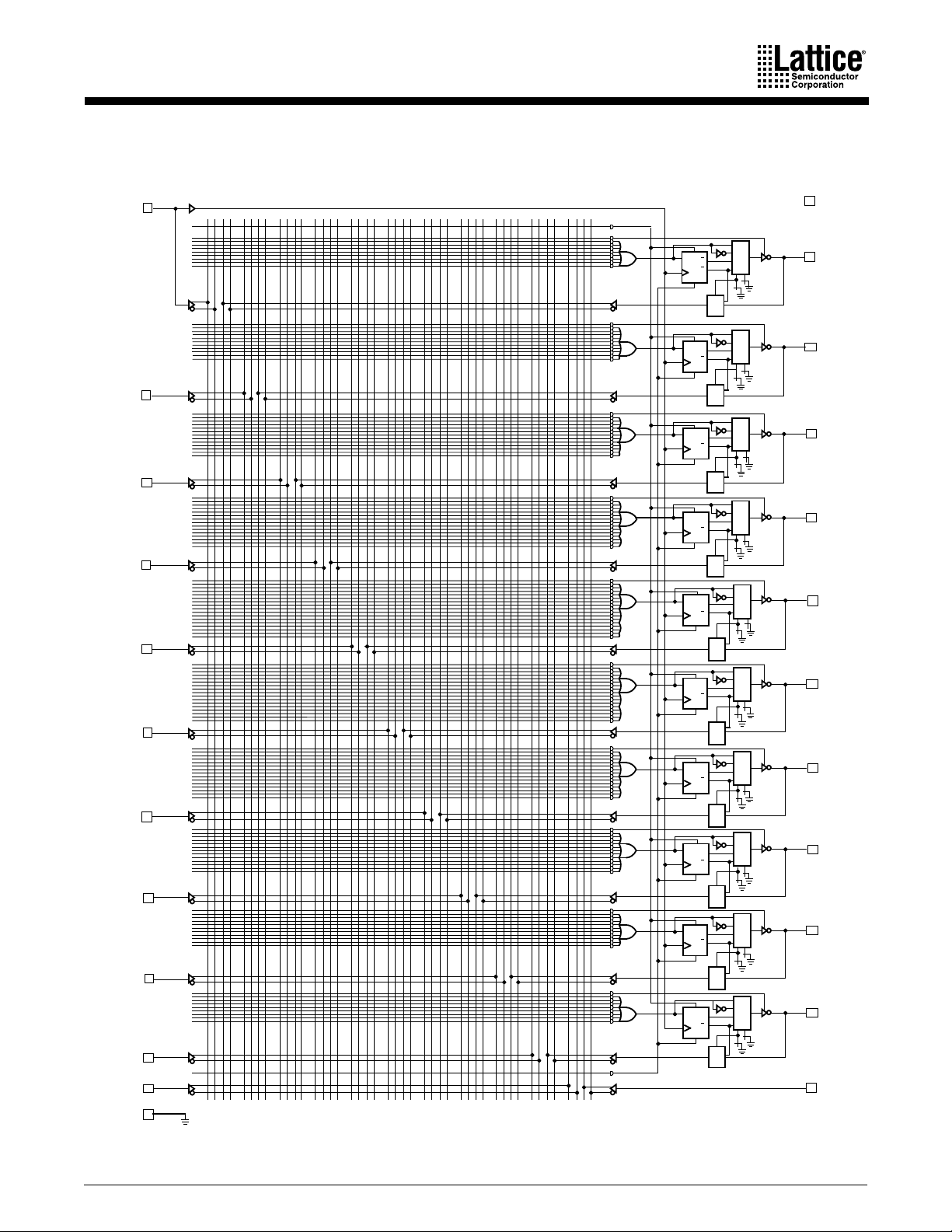

BLOCK DIAGRAM

I1 - I

11

11

OUTPUT

LOGIC

MACRO

CELL

PRESET

RESET

CLK/I

0

1

PROGRAMMABLE

AND ARRAY

(44 x 132)

81012141616141210 8

OUTPUT

LOGIC

MACRO

CELL

I/O0 I/O1 I/O2 I/O3 I/O4 I/O5 I/O6 I/O7 I/O8 I/O9

OUTPUT

LOGIC

MACRO

CELL

OUTPUT

LOGIC

MACRO

CELL

OUTPUT

LOGIC

MACRO

CELL

OUTPUT

LOGIC

MACRO

CELL

OUTPUT

LOGIC

MACRO

CELL

OUTPUT

LOGIC

MACRO

CELL

OUTPUT

LOGIC

MACRO

CELL

OUTPUT

LOGIC

MACRO

CELL

FUNCTIONAL DESCRIPTION

The PALCE22V10 allows the systems engineer to implement the design on-chip, by programming

EE cells to configure AND and OR gates within the device, according to the desired logic function.

Complex interconnections between gates, which previously required time-consuming layout, are

lifted from the PC board and placed on silicon, where they can be easily modified during

prototyping or production.

The P ALCE22V10Z is the zero-power version of the P ALCE22V10. It has all the architectural features

of the PALCE22V10. In addition, the PALCE22V10Z has zero standby power and unused product

term disable.

Product terms with all connections opened assume the logical HIGH state; product terms

connected to both true and complement of any single input assume the logical LOW state.

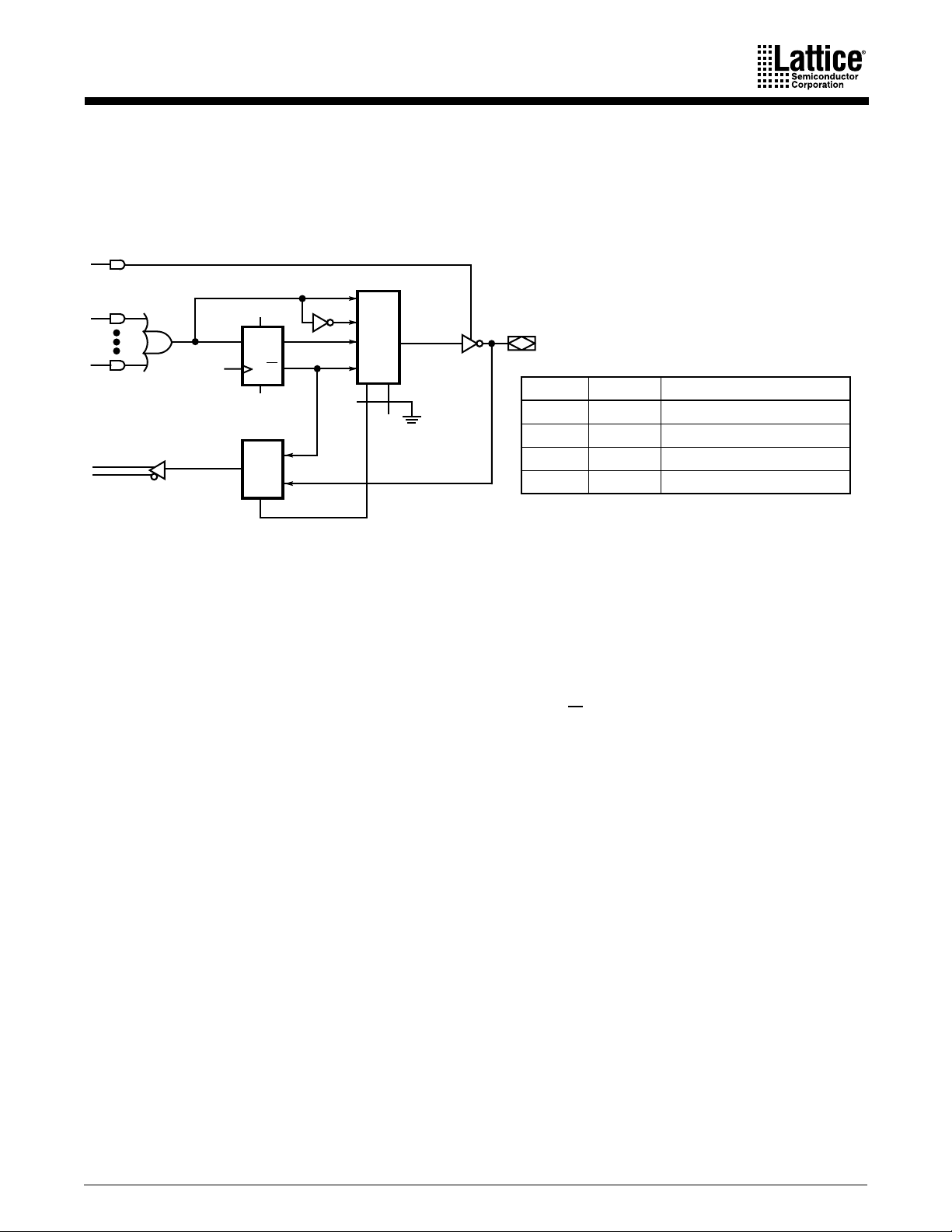

The P ALCE22V10 has 12 inputs and 10 I/O macrocells. The macrocell (Figure 1) allows one of four

potential output configurations registered output or combinatorial I/O, active high or active low

(see Figure 1). The configuration choice is made according to the user’s design specification and

- S

corresponding programming of the configuration bits S

. Multiplexer controls are connected

0

1

to ground (0) through a programmable bit, selecting the “0” path through the multiplexer. Erasing

the bit disconnects the control line from GND and it is driven to a high level, selecting the “1” path.

The device is produced with an EE cell link at each input to the AND gate array, and connections

may be selectively removed by applying appropriate voltages to the circuit. Utilizing an easilyimplemented programming algorithm, these products can be rapidly programmed to any

customized pattern.

2 PALCE22V10 and PALCE22V10Z Families

Variable Input/Output Pin Ratio

The PALCE22V10 has twelve dedicated input lines, and each macrocell output can be an I/O pin.

Buffers for device inputs have complementary outputs to provide user-programmable input signal

polarity. Unused input pins should be tied to V

or GND.

CC

10

11

00

01

S

1

S

0

Figure 1. Output Logic Macrocell Diagram

I/O

n

S

1

0 0 Registered/Active Low

0 1 Registered/Active High

1 0 Combinatorial/Active Low

1 1 Combinatorial/Active High

0 = Programmed EE bit

1 = Erased (charged) EE bit

S

0

Output Configuration

16564E-004

CLK

AR

D Q

Q

SP

0

1

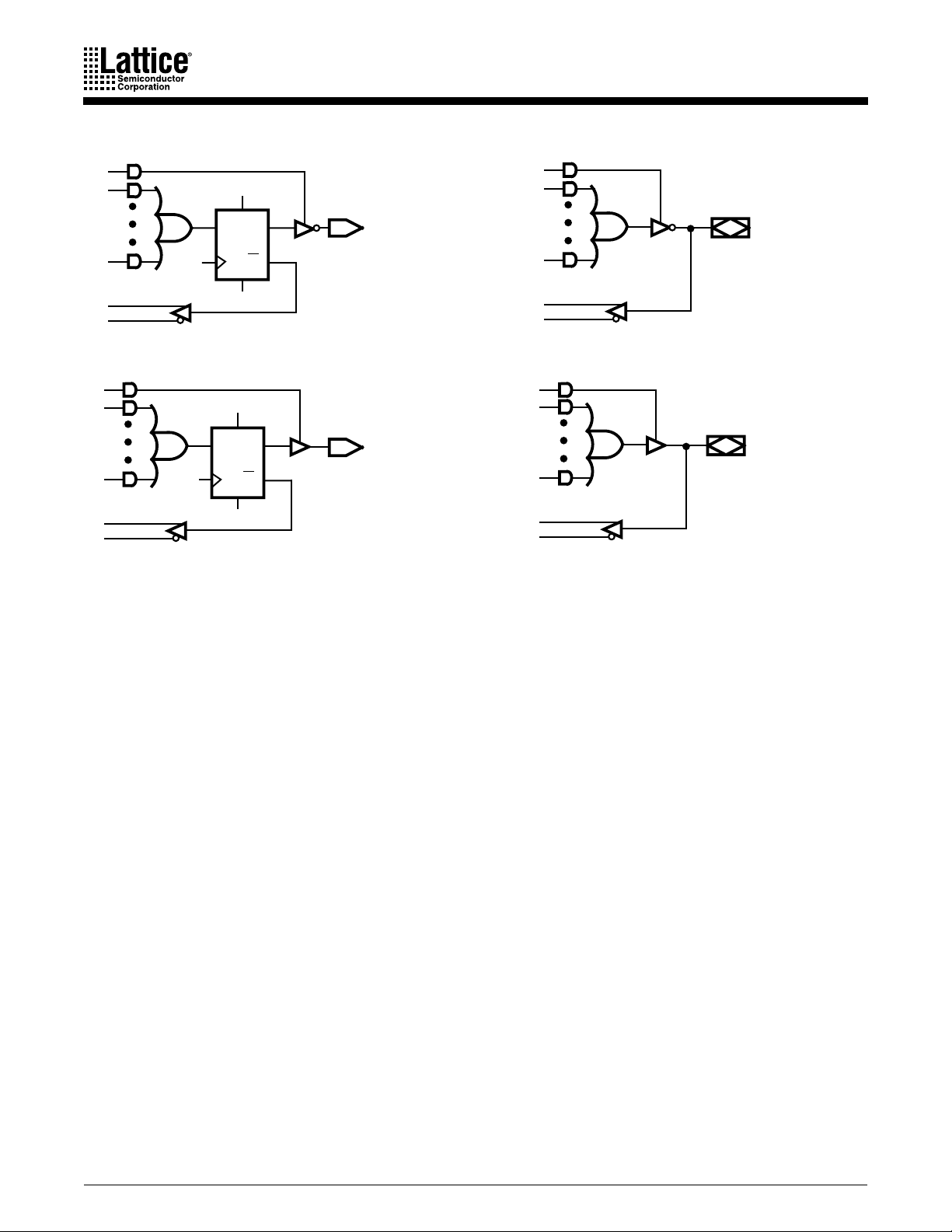

Registered Output Configuration

Each macrocell of the PALCE22V10 includes a D-type flip-flop for data storage and

synchronization. The flip-flop is loaded on the LOW-to-HIGH transition of the clock input. In the

registered configuration (S

Combinatorial I/O Configuration

= 0), the array feedback is from Q of the flip-flop.

1

Any macrocell can be configured as combinatorial by selecting the multiplexer path that bypasses

the flip-flop (S

= 1). In the combinatorial configuration, the feedback is from the pin.

1

PALCE22V10 and PALCE22V10Z Families 3

AR

DQ

CLK

a. Registered/active low

CLK

c. Registered/active high

Q

SP

AR

DQ

Q

SP

S0 = 0

S1 = 0

b. Combinatorial/active low

S0 = 1

S1 = 0

d. Combinatorial/active high

Figure 2. Macrocell Configuration Options

S0 = 0

S1 = 1

S

= 1

0

S1 = 1

16564E-005

Programmable Three-State Outputs

Each output has a three-state output buffer with three-state control. A product term controls the

buffer, allowing enable and disable to be a function of any product of device inputs or output

feedback. The combinatorial output provides a bi-directional I/O pin, and may be configured as

a dedicated input if the buffer is always disabled.

Programmable Output Polarity

The polarity of each macrocell output can be active high or active low, either to match output

signal needs or to reduce product terms. Programmable polarity allows Boolean expressions to be

written in their most compact form (true or inverted), and the output can still be of the desired

polarity. It can also save “DeMorganizing” efforts.

Selection is controlled by programmable bit S

in the output macrocell, and affects both registered

0

and combinatorial outputs. Selection is automatic, based on the design specification and pin

definitions. If the pin definition and output equation have the same polarity, the output is

programmed to be active high (S

= 1).

0

Preset/Reset

For initialization, the PALCE22V10 has preset and reset product terms. These terms are connected

to all registered outputs. When the synchronous preset (SP) product term is asserted high, the

output registers will be loaded with a HIGH on the next LOW-to-HIGH clock transition. When the

asynchronous reset (AR) product term is asserted high, the output registers will be immediately

loaded with a LOW independent of the clock.

4 PALCE22V10 and PALCE22V10Z Families

Note that preset and reset control the flip-flop, not the output pin. The output level is determined

by the output polarity selected.

Power-Up Reset

All flip-flops power up to a logic LOW for predictable system initialization. Outputs of the

PALCE22V10 will depend on the programmed output polarity. The V

rise must be monotonic,

CC

and the reset delay time is 1000ns maximum.

Register Preload

The register on the PALCE22V10 can be preloaded from the output pins to facilitate functional

testing of complex state machine designs. This feature allows direct loading of arbitrary states,

making it unnecessary to cycle through long test vector sequences to reach a desired state. In

addition, transitions from illegal states can be verified by loading illegal states and observing

proper recovery.

Security Bit

After programming and verification, a PALCE22V10 design can be secured by programming the

security EE bit. Once programmed, this bit defeats readback of the internal programmed pattern

by a device programmer, securing proprietary designs from competitors. When the security bit is

programmed, the array will read as if every bit is erased, and preload will be disabled.

The bit can only be erased in conjunction with erasure of the entire pattern.

Programming and Erasing

The PALCE22V10 can be programmed on standard logic programmers. It also may be erased to

reset a previously configured device back to its unprogrammed state. Erasure is automatically

performed by the programming hardware. No special erase operation is required.

Quality and Testability

The P ALCE22V10 offers a very high level of built-in quality. The erasability of the device provides

a direct means of verifying performance of all AC and DC parameters. In addition, this verifies

complete programmability and functionality of the device to provide the highest programming

yields and post-programming functional yields in the industry.

Technology

The high-speed PALCE22V10 is fabricated with Vantis’ advanced electrically erasable (EE) CMOS

process. The array connections are formed with proven EE cells. Inputs and outputs are designed

to be compatible with TTL devices. This technology provides strong input clamp diodes, output

slew-rate control, and a grounded substrate for clean switching.

PCI Compliance

The PALCE22V10H devices in the -5/-7/-10 speed grades are fully compliant with the PCI Local

Bus Specification

published by the PCI Special Interest Group. The PALCE22V10H’s predictable

timing ensures compliance with the PCI AC specifications independent of the design.

Zero-Standby Power Mode

The PALCE22V10Z features a zero-standby power mode. When none of the inputs switch for an

extended period (typically 50 ns), the PALCE22V10Z will go into standby mode, shutting down

PALCE22V10 and PALCE22V10Z Families 5

most of its internal circuitry. The current will go to almost zero (I

< 30 µA). The outputs will

CC

maintain the states held before the device went into the standby mode.

When any input switches, the internal circuitry is fully enabled, and power consumption returns

to normal. This feature results in considerable power savings for operation at low to medium

frequencies. This saving is illustrated in the I

vs. frequency graph.

CC

Product-Term Disable

On a programmed PALCE22V10Z, any product terms that are not used are disabled. Power is cut

off from these product terms so that they do not draw current. As shown in the I

vs. frequency

CC

graph, product-term disabling results in considerable power savings. This saving is greater at the

higher frequencies.

Further hints on minimizing power consumption can be found in a separate document entitled,

Minimizing Power Consumption with Zero-Power PLDs .

6 PALCE22V10 and PALCE22V10Z Families

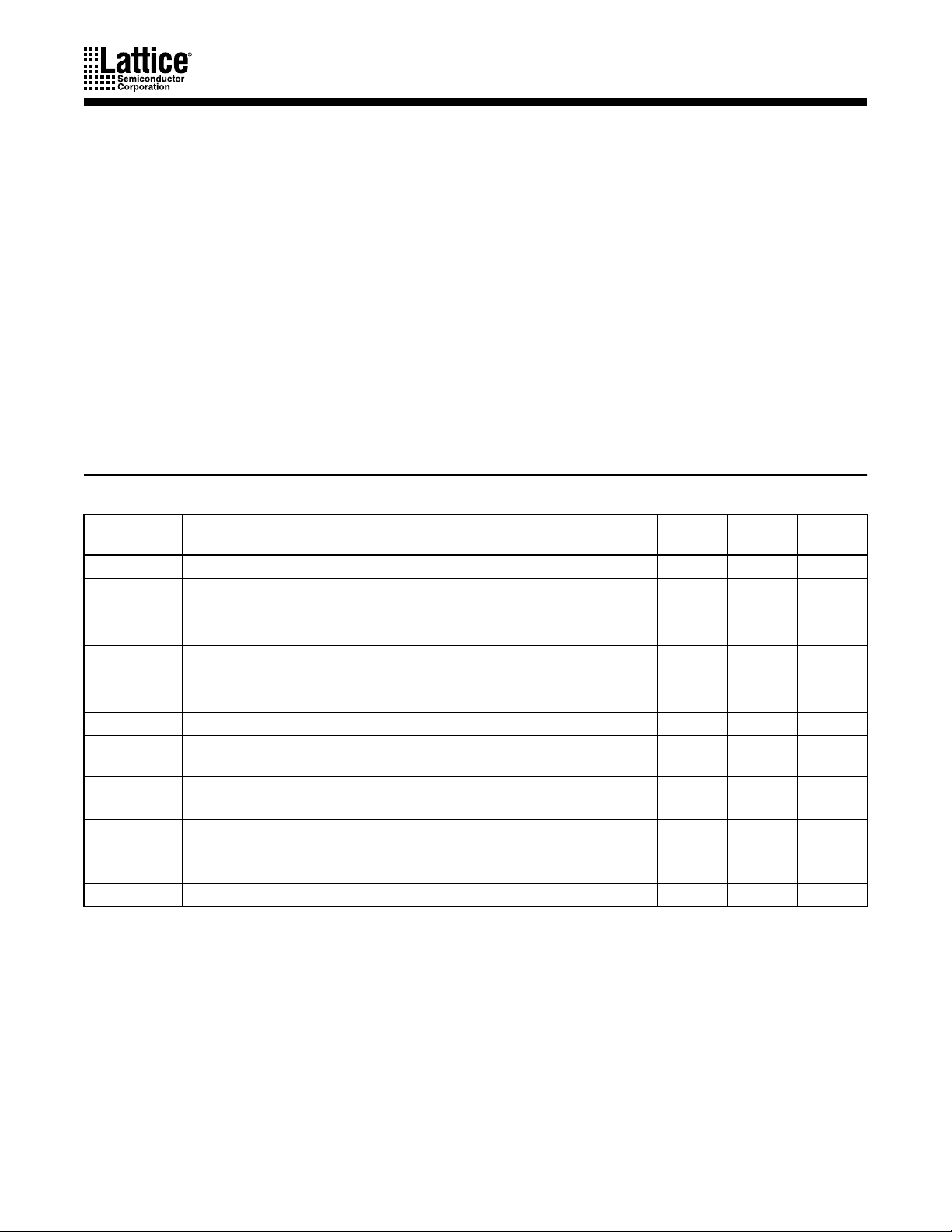

LOGIC DIAGRAM

CLK/I01

I

1

I

2

I

3

I

4

I

5

I

6

I

7

I

8

I

9

I

10

GND

(3)

(4)

(5)

(6)

(7)

(9)

(10)

(11)

10

(12)

(13)

12

(14)

24

(2)

2

3

4

5

6

7

8

9

0 34 78 1112151619202324272831323536394043

0

1

9

10

20

21

33

34

48

49

65

66

82

83

97

98

110

111

121

122

130

131

AR

10

1

1

AR

D

Q

00

1

Q

0

SP

0

1

10

1

1

AR

D

Q

00

1

Q

0

SP

0

1

10

1

1

AR

D

Q

00

1

Q

0

SP

0

1

10

1

1

AR

D

Q

00

1

Q

0

SP

0

1

10

1

1

AR

D

Q

00

1

0

Q

SP

0

1

10

1

1

AR

D

Q

00

1

0

Q

SP

0

1

10

1

1

AR

D

Q

00

1

0

Q

SP

0

1

10

1

1

AR

D

Q

00

1

0

Q

SP

0

1

10

1

1

AR

D

Q

00

1

Q

0

SP

0

1

10

1

1

AR

D

Q

00

1

0

Q

SP

0

SP

1

11

0 34 78 1112151619202324272831323536394043

(28)VCC

(27)

(26)

(25)

(24)

(23)

18

(21)

17

(20)

16

(19)

15

(18)

14

(17)

(16)

I/O923

I/O22

8

I/O21

7

I/O20

6

I/O19

5

I/O

4

I/O

3

I/O

2

I/O

1

I/O

0

I13

11

16564E-006

PALCE22V10 and PALCE22V10Z Families 7

µ

µ

µ

ABSOLUTE MAXIMUM RATINGS

Storage Temperature. . . . . . . . . . . . . .-65 ° C to +150 ° C

Ambient Temperature with

Power Applied . . . . . . . . . . . . . . . . . .-55 ° C to +125 ° C

Supply Voltage with

Respect to Ground . . . . . . . . . . . . . . .-0.5 V to +7.0 V

DC Input Voltage . . . . . . . . . . . .-0.5 V to V

DC Output or I/O Pin Voltage . . .-0.5 V to V

+ 1.0 V

CC

+ 1.0 V

CC

OPERATING RANGES

Commercial (C) Devices

Ambient Temperature (T

Operating in Free Air. . . . . . . . . . . . . . . 0 ° C to +75 ° C

Supply Voltage (V

CC

Respect to Ground. . . . . . . . . . . . . +4.75 V to +5.25 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

A

) with

)

Static Discharge Voltage . . . . . . . . . . . . . . . . . 2001 V

Latchup Current (T

Stresses above those listed under Absolute Maximum Ratings

may cause permanent device failure. Functionality at or above

these limits is not implied. Exposure to Absolute Maximum

Ratings for extended periods may affect device reliability.

Programming conditions may vary.

= 0 ° C to +75 ° C) . . . . . . . .100 mA

A

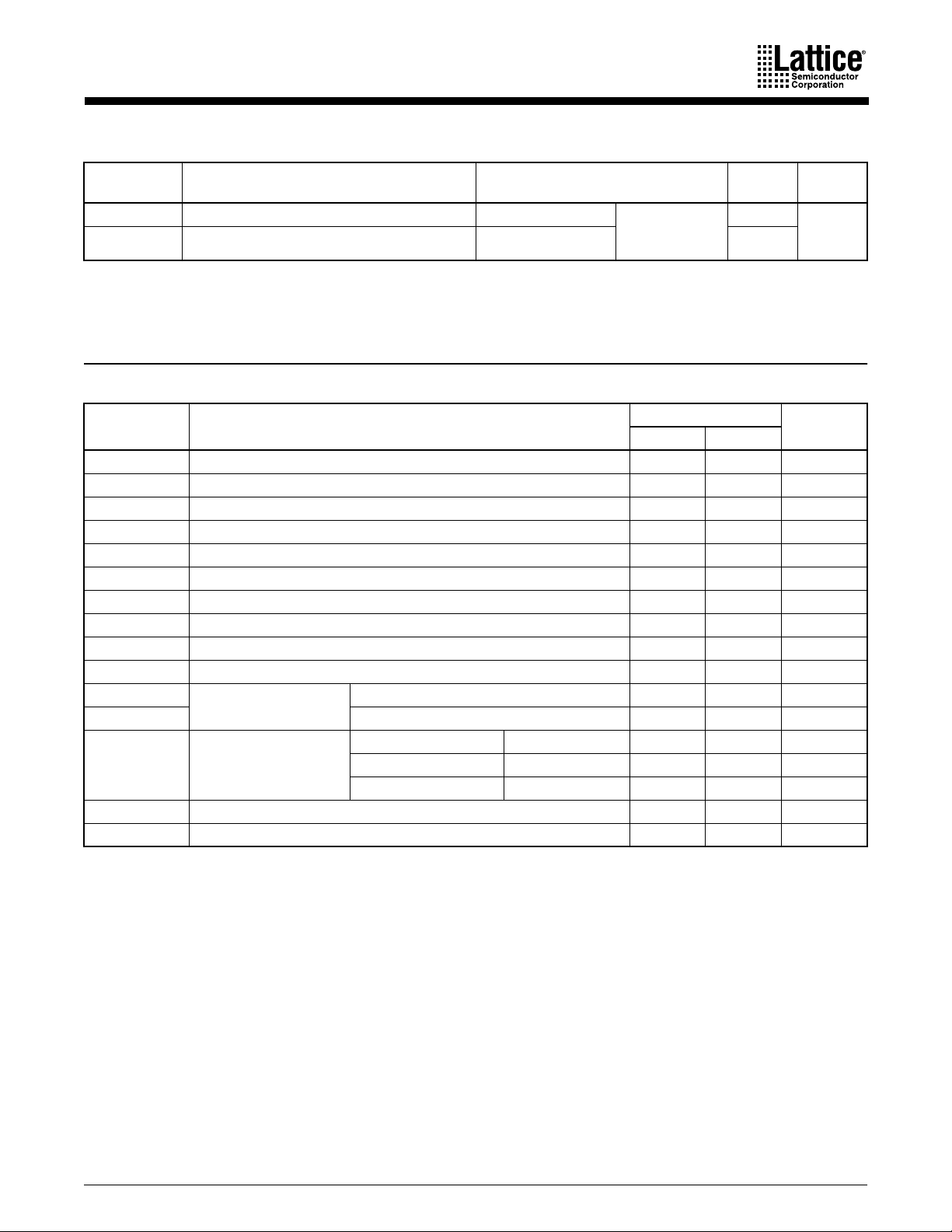

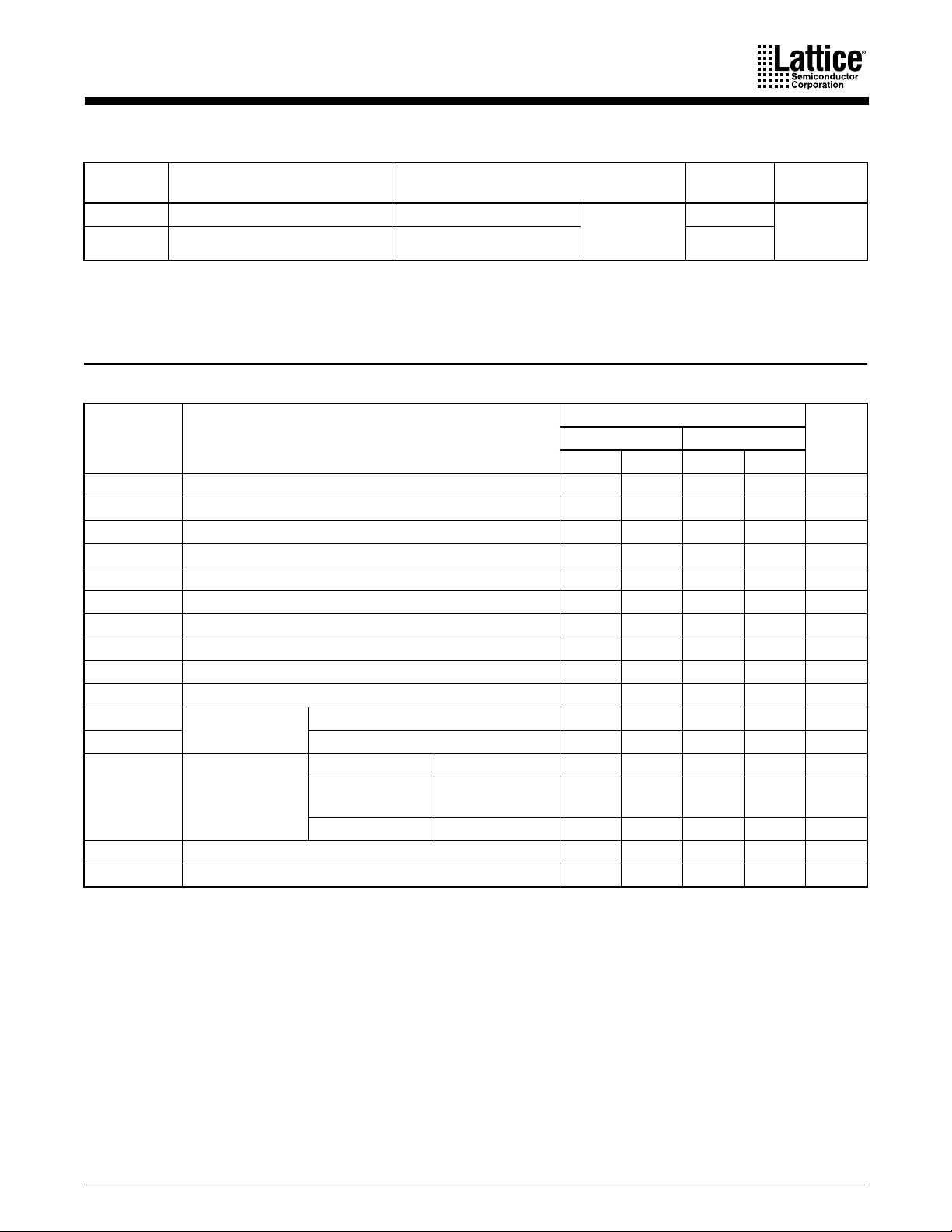

DC CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES

Parameter

Symbol Parameter Description Test Conditions Min Max Unit

V

OH

V

OL

V

IH

V

IL

I

IH

I

IL

I

OZH

I

OZL

I

SC

(Static) Supply Current Outputs Open, (I

I

CC

(Dynamic) Supply Current Outputs Open, (I

I

CC

Output HIGH Voltage I

Output LOW Voltage I

Input HIGH Voltage

Input LOW Voltage

Input HIGH Leakage Current V

Input LOW Leakage Current VIN = 0 V, VCC = Max (Note 2) -100

Off-State Output Leakage

Current HIGH

Off-State Output Leakage

Current LOW

Output Short-Circuit

Current

= -3.2 mA, VIN = V

OH

= 16 mA, V

OL

Guaranteed Input Logical HIGH

Voltage for all Inputs (Note 1)

Guaranteed Input Logical LOW

Voltage for all Inputs (Note 1)

= VCC, VCC = Max (Note 2) 10

IN

= VCC, VCC = Max,

V

OUT

V

= V

IN

IL

= 0 V, V

V

OUT

V

= VIL or VIH (Note 2)

IN

V

= 0.5 V, V

OUT

or V

IH

= V

or V

IN

IH

or VIH (Note 2)

= Max,

CC

= Max (Note 3) -30 -130 mA

CC

= 0 mA), VCC = Max 125 mA

OUT

= 0 mA), V

OUT

= Min 2.4 V

IL, VCC

= Min 0.4 V

IL, VCC

2.0 V

0.8 V

10

-100

= Max, f = 25 MHz 140 mA

CC

A

A

µ

A

A

Notes:

1. These are absolute values with respect to the device ground, and all overshoots due to system and tester noise are included.

2. I/O pin leakage is the worst case of I

3. Not more than one output should be tested at a time, and the duration of the short-circuit test should not exceed one second.

= 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

V

OUT

and I

IL

(or IIH and I

OZL

OZH

).

8 PALCE22V10H-5 (Com’l)

CAPACITANCE

1

Parameter

Symbol Parameter Description Test Conditions Typ Unit

C

IN

C

OUT

Input Capacitance V

Output Capacitance V

= 2.0 V VCC = 5.0 V

IN

= 2.0 V 8

OUT

T

= 25

A

f = 1 MHz

°C

5

pF

Note:

1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where

capacitance may be affected.

SWITCHING CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES

Parameter

Symbol Parameter Description

t

PD

t

S1

t

S2

t

H

t

CO

t

SKEWR

t

AR

t

ARW

t

ARR

t

SPR

t

WL

t

WH

Input or Feedback to Combinatorial Output 5 ns

Setup Time from Input or Feedback 3 ns

Setup Time from SP to Clock 4 ns

Hold Time 0 ns

Clock to Output 4ns

Skew Between Registered Outputs (Note 2) 0.5 ns

Asynchronous Reset to Registered Output 7.5 ns

Asynchronous Reset Width 4.5 ns

Asynchronous Reset Recovery Time 4.5 ns

Synchronous Preset Recovery Time 4.5 ns

Clock Width

LOW 2.5 ns

HIGH 2.5 ns

External Feedback 1/(t

f

MAX

Maximum Frequency (Note 3)

Internal Feedback (f

No Feedback 1/(t

t

EA

t

ER

Input to Output Enable Using Product Term Control 6 ns

Input to Output Disable Using Product Term Control 5.5 ns

+ tCO) 142.8 MHz

S

) 1/(tS + tCF) (Note 4) 150 MHz

CNT

+ tWL) 200 MHz

WH

-5

1

UnitMin Max

Notes:

1. See “Switching Test Circuit” for test conditions.

2. Skew is measured with all outputs switching in the same direction.

3. These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where

frequency may be affected.

is a calculated value and is not guaranteed. t

4. t

CF

t

CF

= 1/f

(internal feedback) - tS.

MAX

can be found using the following equation:

CF

PALCE22V10H-5 (Com’l) 9

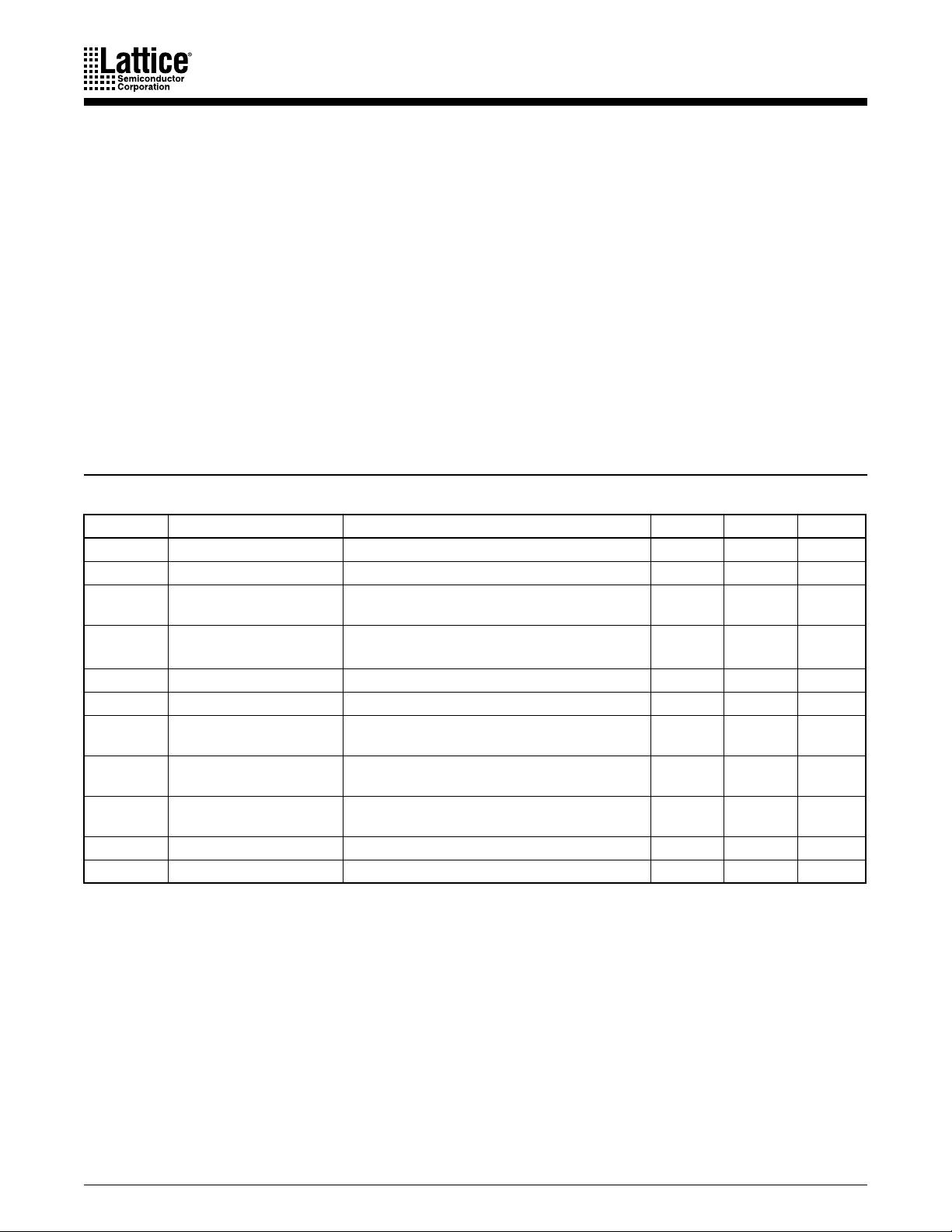

ABSOLUTE MAXIMUM RATINGS

OPERATING RANGES

Storage Temperature. . . . . . . . . . . . . .-65°C to +150°C

Ambient Temperature with

Power Applied . . . . . . . . . . . . . . . . . .-55°C to +125°C

Supply Voltage with Respect

to Ground . . . . . . . . . . . . . . . . . . . . .-0.5 V to +7.0 V

DC Input Voltage . . . . . . . . . . . .-0.5 V to VCC + 1.0 V

DC Output or I/O Pin Voltage . . .-0.5 V to VCC + 1.0 V

Commercial (C) Devices

Ambient Temperature (TA)

Operating in Free Air. . . . . . . . . . . . . . . 0°C to +75°C

Supply Voltage (VCC) with

Respect to Ground. . . . . . . . . . . . . +4.75 V to +5.25 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

Static Discharge Voltage . . . . . . . . . . . . . . . . . 2001 V

Latchup Current (TA = 0°C to +75°C) . . . . . . . .100 mA

Stresses above those listed under Absolute Maximum Ratings

may cause permanent device failure. Functionality at or above

these limits is not implied. Exposure to Absolute Maximum

Ratings for extended periods may affect device reliability.

Programming conditions may vary.

DC CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES

Symbol Parameter Description Test Conditions Min Max Unit

V

OH

V

OL

V

IH

V

IL

I

IH

I

IL

I

OZH

I

OZL

I

SC

(Static) Supply Current Outputs Open, (I

I

CC

(Dynamic) Supply Current Outputs Open, (I

I

CC

Output HIGH Voltage IOH = -3.2 mA, VIN = V

Output LOW Voltage I

Input HIGH Voltage

Input LOW Voltage

Input HIGH Leakage Current VIN = VCC, VCC = Max (Note 2) 10 µA

Input LOW Leakage Current VIN = 0 V, VCC = Max (Note 2) -100 µA

Off-State Output Leakage

Current HIGH

Off-State Output Leakage

Current LOW

Output Short-Circuit

Current

= 16 mA, VIN = V

OL

Guaranteed Input Logical HIGH

Voltage for all Inputs (Note 1)

Guaranteed Input Logical LOW

Voltage for all Inputs (Note 1)

V

= VCC, VCC = Max, V

OUT

V

= 0 V, V

OUT

V

= 0.5 V, VCC = Max

OUT

T

= 25°C (Note 3)

A

= Max, V

CC

OUT

OUT

or V

IH

or V

IH

IN

IN

= 0 mA), VCC = Max 115 mA

= 0 mA), VCC = Max, f = 25 MHz 140 mA

= Min 2.4 V

IL, VCC

= Min 0.4 V

IL, VCC

2.0 V

0.8 V

= V

or VIH (Note 2) 10 µA

IL

= VIL or VIH (Note 2) -100 µA

-30 -130 mA

Notes:

1. These are absolute values with respect to the device ground, and all overshoots due to system and tester noise are included.

2. I/O pin leakage is the worst case of I

3. Not more than one output should be tested at a time. Duration of the short-circuit test should not exceed one second.

= 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

V

OUT

and I

IL

(or IIH and I

OZL

OZH

).

10 PALCE22V10H-7 (Com’l)

CAPACITANCE

1

Parameter

Symbol Parameter Description Test Conditions Typ Unit

C

IN

C

OUT

Input Capacitance VIN = 2.0 V VCC = 5.0 V

T

= 25°C

Output Capacitance V

= 2.0 V 8

OUT

A

f = 1 MHz

5

pF

Note:

1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where

capacitance may be affected.

SWITCHING CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES

-7

Parameter

Symbol Parameter Description

t

PD

t

S1

t

S2

t

H

t

CO

t

SKEWR

t

AR

t

ARW

t

ARR

t

SPR

t

WL

t

WH

Input or Feedback to Combinatorial Output 3 7.5 3 7.5 ns

Setup Time from Input or Feedback 5 4.5 ns

Setup Time from SP to Clock 6 6 ns

Hold Time 0 0 ns

Clock to Output 2 5 2 4.5 ns

Skew Between Registered Outputs (Note 2) 1 1 ns

Asynchronous Reset to Registered Output 10 10 ns

Asynchronous Reset Width 7 7 ns

Asynchronous Reset Recovery Time 7 7 ns

Synchronous Preset Recovery Time 7 7 ns

Clock Width

LOW 3.5 3.0 ns

HIGH 3.5 3.0 ns

External Feedback 1/(t

f

MAX

Maximum Frequency

(Note 3)

Internal Feedback

(f

)

CNT

No Feedback 1/(t

t

EA

t

ER

Input to Output Enable Using Product Term Control 7.5 7.5 ns

Input to Output Disable Using Product Term Control 7.5 7.5 ns

+ tCO) 100 111 MHz

S

+ tCF) (Note 4) 125 133 MHz

1/(t

S

+ tWL) 142.8 166 MHz

WH

PDIP PLCC

Min Max Min Max

1

Unit

Notes:

1. See “Switching Test Circuit” for test conditions.

2. Skew is measured with all outputs switching in the same direction.

3. These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where

frequency may be affected.

is a calculated value and is not guaranteed. tCF can be found using the following equation:

4. t

CF

t

CF

= 1/f

(internal feedback) - tS.

MAX

PALCE22V10H-7 (Com’l) 11

Loading...

Loading...