Lattice Semiconductor Corporation MACH210AQ-20JC, MACH210AQ-15JC, MACH210AQ-12JC, MACH210A-7JC, MACH210A-14JI Datasheet

...

FINAL

MACH210A-7/10/12

COM’L: -7/10/12/15/20, Q-12/15/20 IND: -12/14/18/24

MACH210-12/15/20

MACH210AQ-12/15/20

High-Density EE CMOS Programmable Logic

DISTINCTIVE CHARACTERISTICS

44 Pins

64 Macrocells

7.5 ns tPD Commercial

12 ns t

133 MHz f

38 Inputs; 210A Inputs have built-in pull-up

resistors

Industrial

PD

CNT

GENERAL DESCRIPTION

The MACH210 is a member of the high-performance

EE CMOS MACH 2

approximately six times the logic macrocell capability of

the popular PAL22V10 without loss of speed.

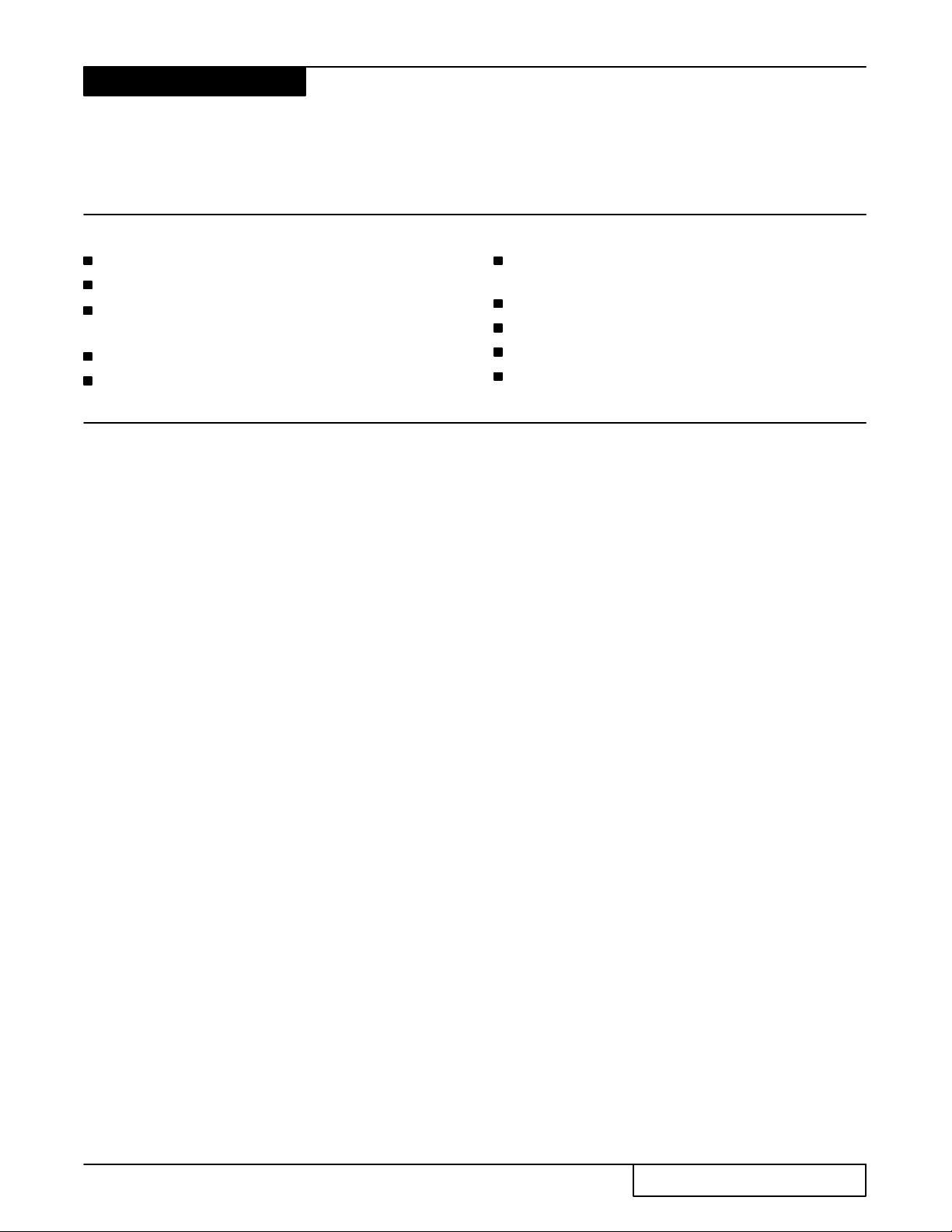

The MACH210 consists of four PAL blocks interconnected by a programmable switch matrix. The four PAL

blocks are essentially “PAL22V16” structures complete

with product-term arrays and programmable macrocells, including additional buried macrocells. The switch

matrix connects the PAL blocks to each other and to all

input pins, providing a high degree of connectivity

between the fully-connected PAL blocks. This allows

designs to be placed and routed efficiently.

The MACH210 has two kinds of macrocell: output and

buried. The MACH210 output macrocell provides regis-

device family. This device has

Peripheral Component Interconnect (PCI)

compliant

32 Outputs

64 Flip-flops; 2 clock choices

4 “PAL22V16” blocks with buried macrocells

Pin-compatible with MACH110, MACH111,

MACH211, and MACH215

tered, latched, or combinatorial outputs with programmable polarity. If a registered configuration is chosen,

the register can be configured as D-type or T-type to

help reduce the number of product terms. The register

type decision can be made by the designer or by the

software. All output macrocells can be connected to an

I/O cell. If a buried macrocell is desired, the internal

feedback path from the macrocell can be used, which

frees up the I/O pin for use as an input.

The MACH210 has dedicated buried macrocells which,

in addition to the capabilities of the output macrocell,

also provide input registers or latches for use in

synchronizing signals and reducing setup time requirements.

Lattice Semiconductor

Publication# 14128 Rev. I Amendment/0

Issue Date: May 1995

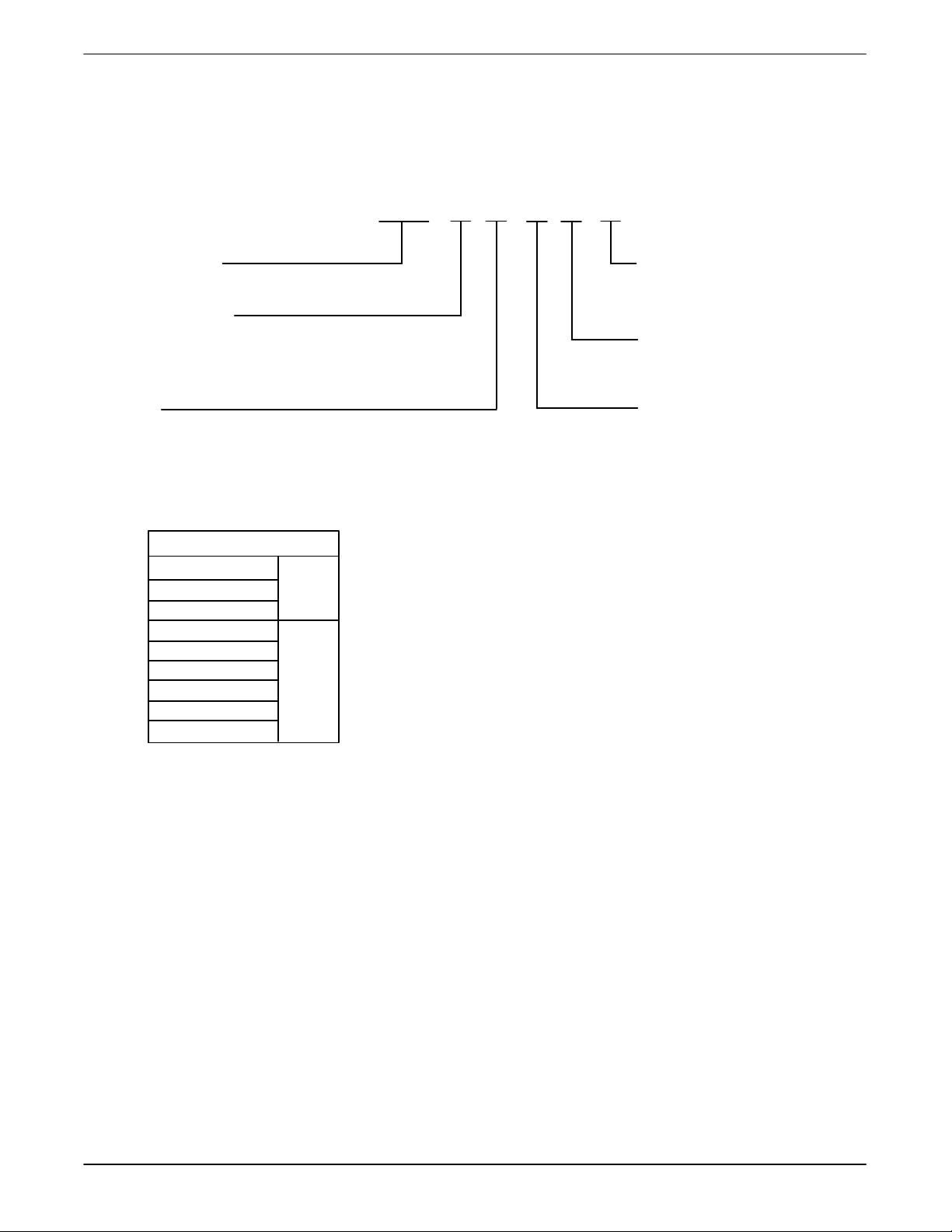

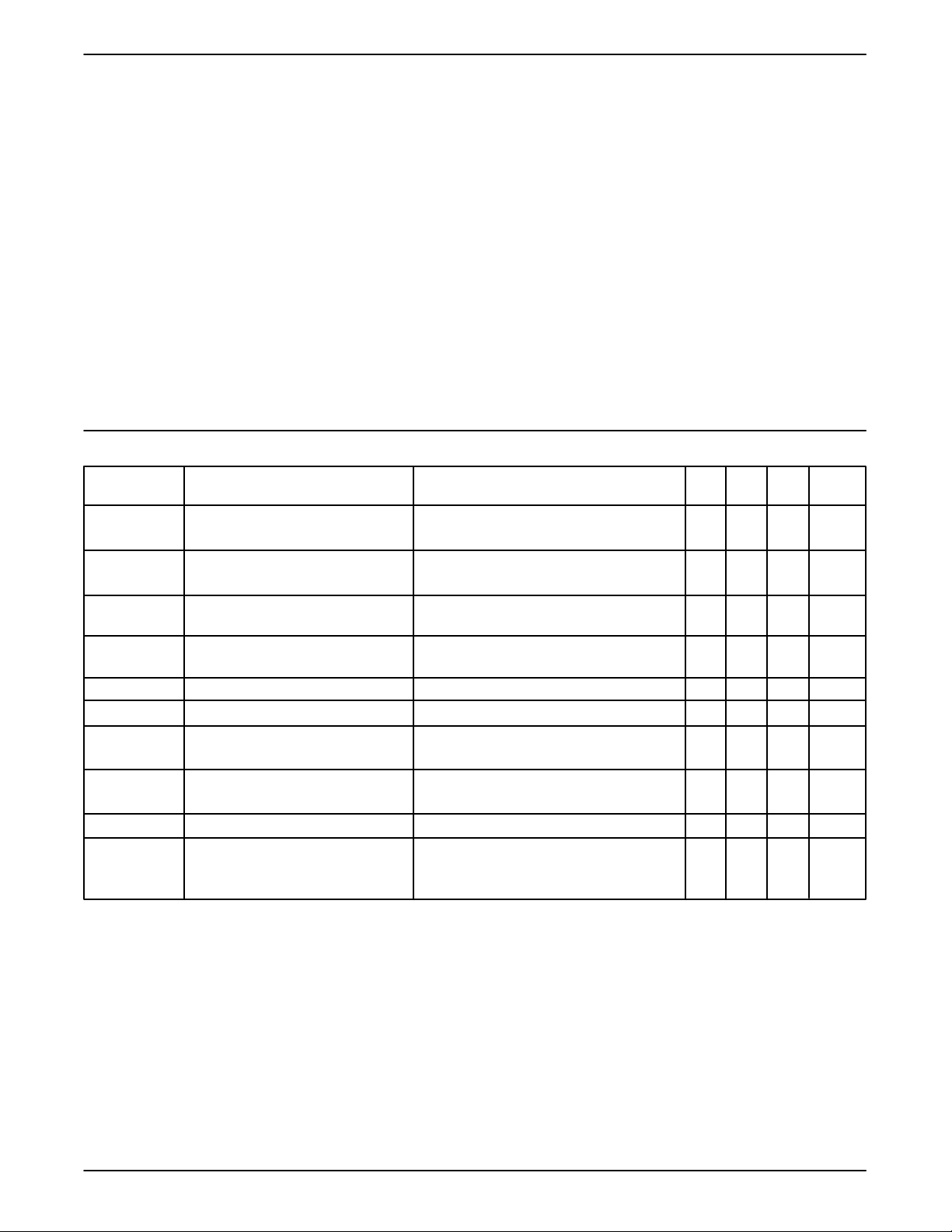

BLOCK DIAGRAM

–I/O

I/O

0

7

I/O8–I/O

I0–I

1,

I3–I

15

4

I/O Cells

8

Macrocells

8

8

I/O Cells

8

Macrocells

OE

Macrocells

44 x 68

AND Logic Array

and

Logic Allocator

22 22

Switch Matrix

22 22

44 x 68

AND Logic Array

and

Logic Allocator

OE

8

44 x 68

AND Logic Array

and

Logic Allocator

44 x 68

AND Logic Array

and

Logic Allocator

8

8

Macrocells

OE

OE

8

2

4

2

Macrocells

8

I/O Cells

I/O24–I/O

Macrocells

8

Macrocells

8

Macrocells

8

88

2

I/O Cells

16

–I/O

8

23

CLK0/I

CLK1/I

2,

5

14128I-1

8

31

I/O

MACH210-7/10/12/15/20, Q-12/15/202

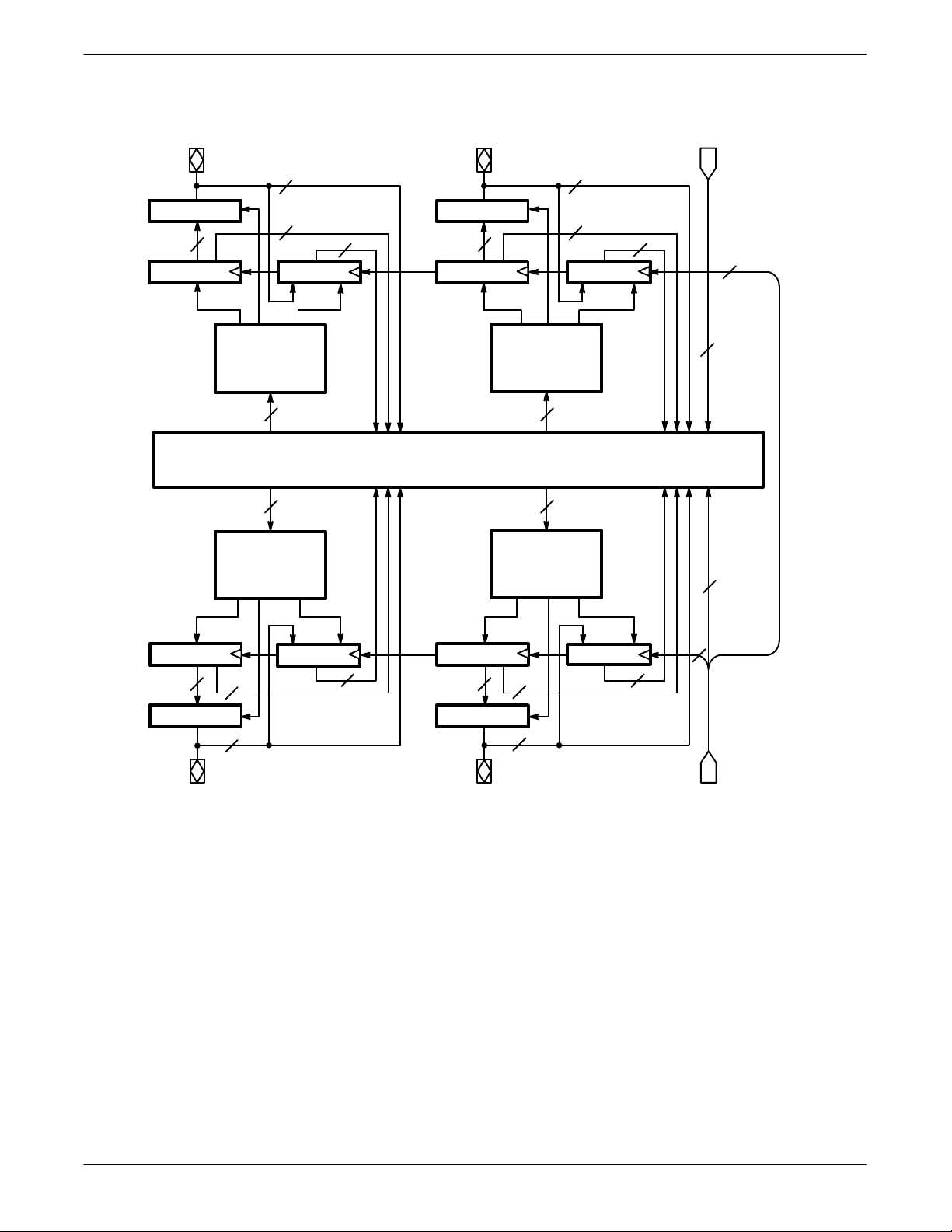

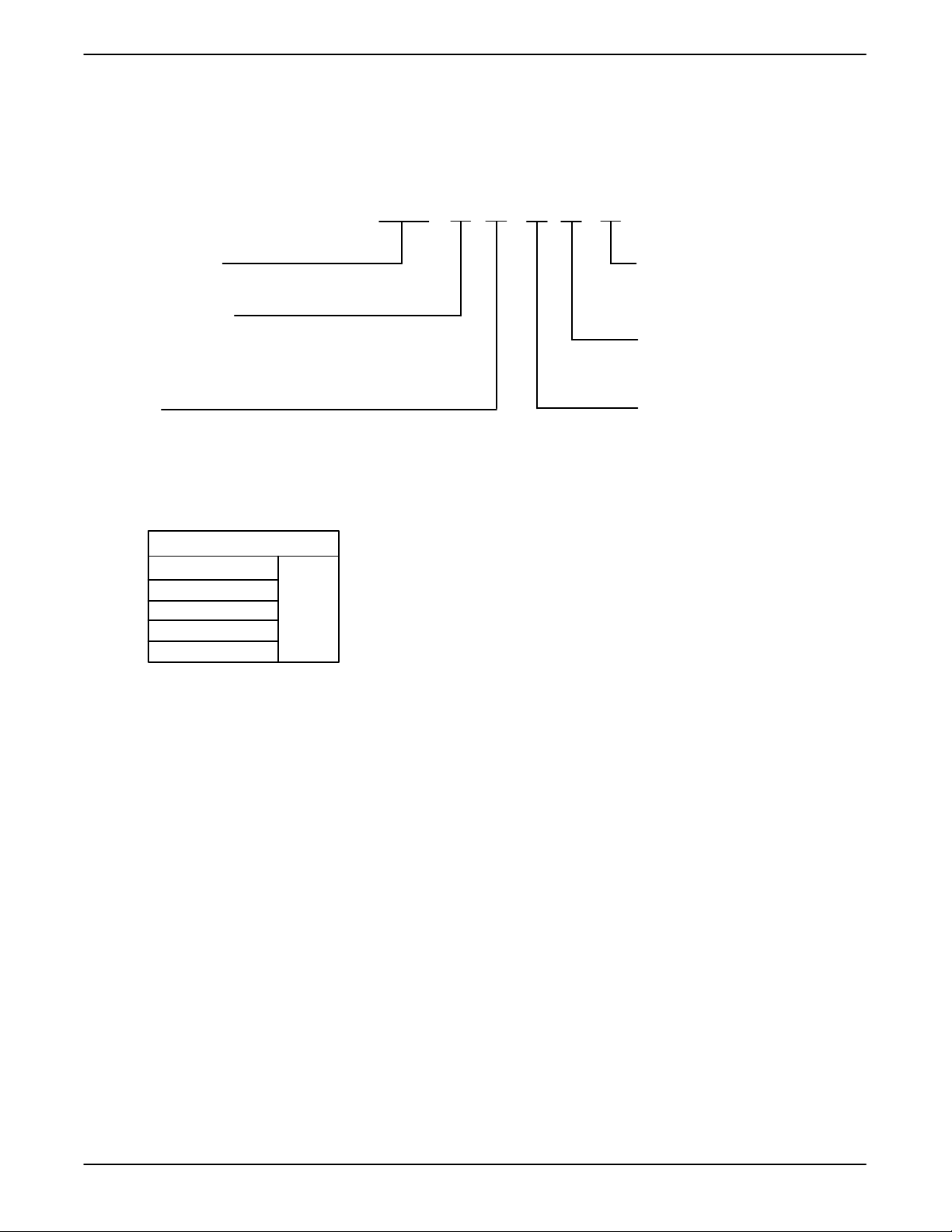

CONNECTION DIAGRAM

Top View

PLCC

I/O

I/O

I/O

GND

CLK0/I

I/O

I/O

I/O

I/O

10

I

I

11

3

I/O4I/O

561324 4443424140

7

5

8

6

9

7

10

0

11

1

12

13

2

14

8

15

9

16

17

18 282726252423222119 20

13

I/O12I/O

2

I/O

14

I/O

1

I/O

15

I/O

0

I/O

CC

V

GND

GND

CC

V

16

I/O

30

31

I/O

I/O

18

I/O17I/O

28

I/O29I/O

39

38

37

36

35

34

33

32

31

30

29

19

20

I/O

I/O

I/O

27

I/O

26

I/O

25

I/O

24

CLK1/I

GND

I

4

I

3

I/O

23

I/O

22

I/O

21

14128I-2

5

Note:

Pin-compatible with MACH110, MACH111, MACH211, and MACH215.

3MACH210-7/10/12/15/20, Q-12/15/20

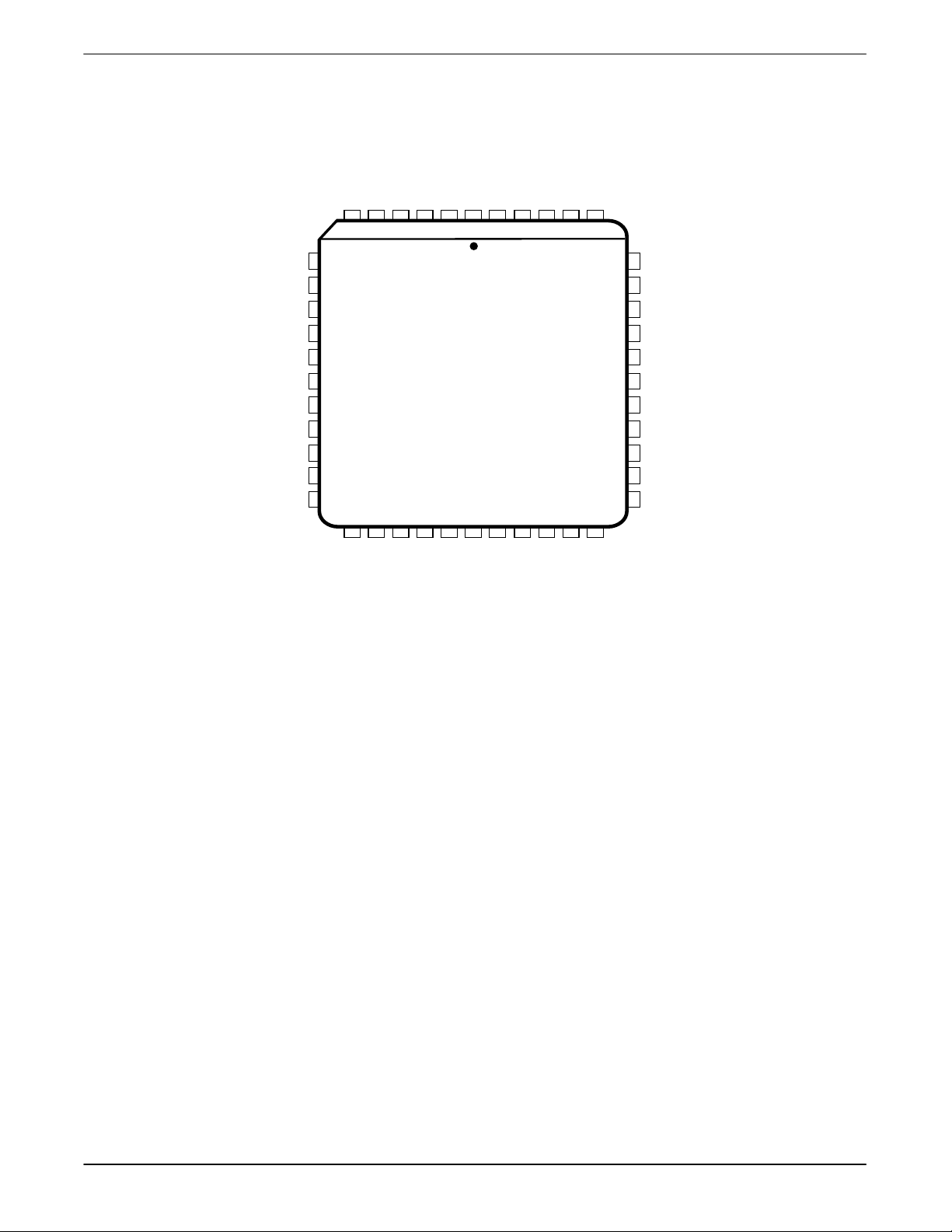

CONNECTION DIAGRAM

Top View

I/O4

I/O3

I/O2

TQFP

I/O0

I/O1

GND

V

CC

I/O30

I/O31

I/O28

I/O29

CLK0/I2

Note:

Pin-compatible with MACH111 and MACH211.

PIN DESIGNATIONS

I/O5

I/O6

I/O7

I0

I1

GND

I/O8

I/O9

I/O10

I/O11

4443424140

1

2

3

4

5

6

7

8

9

10

11

1213141516

I/O12

I/O13

I/O14

CC

V

I/O15

39

17

18

GND

I/O16

38

373635

192021

I/O17

I/O18

I/O19

34

33

32

31

30

29

28

27

26

25

24

23

22

I/O20

I/O27

I/O26

I/O25

I/O24

CLK1/I5

GND

I4

I3

I/O23

I/O22

I/O21

14128I-3

CLK/I = Clock or Input

GND = Ground

I = Input

I/O = Input/Output

V

= Supply Voltage

CC

MACH210-7/10/12/15/20, Q-12/15/204

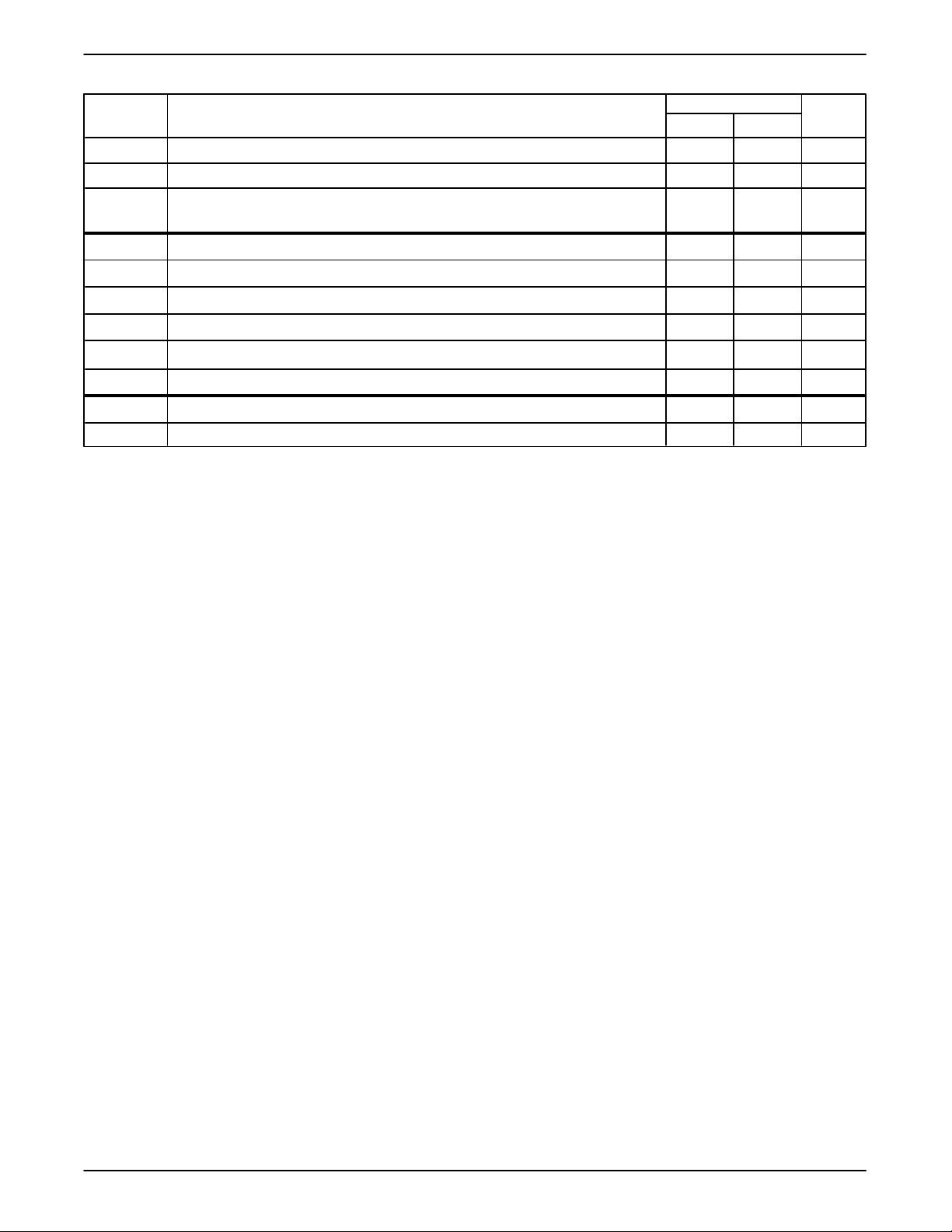

ORDERING INFORMATION

Commercial Products

Programmable logic products for commercial applications are available with several ordering options. The order number

(Valid Combination) is formed by a combination of:

MACH -7 J C

FAMILY TYPE

MACH = Macro Array CMOS High-Speed

DEVICE NUMBER

210 = 64 Macrocells, 44 Pins

210A = 64 Macrocells, 44 Pins, Input Pull-Up Resistors

210AQ = 64 Macrocells, 44 Pins, Input Pull-Up Resistors,

Quarter Power

SPEED

-7 = 7.5 ns t

-10 = 10 ns t

-12 = 12 ns t

-15 = 15 ns t

-20 = 20 ns t

PD

PD

PD

PD

PD

Valid Combinations

MACH210A-7

MACH210A-10

JC,

VC

MACH210A-12

MACH210-12

MACH210-15

MACH210-20

MACH210AQ-12

JC

MACH210AQ-15

MACH210AQ-20

210A

OPTIONAL PROCESSING

Blank = Standard Processing

OPERATING CONDITIONS

C = Commercial (0

°C to +70°C)

PACKAGE TYPE

J = 44-Pin Plastic Leaded Chip

Carrier (PL 044)

V = 44-Pin Thin Quad Flat Pack

(PQT044)

Valid Combinations

The Valid Combinations table lists configurations

planned to be supported in volume for this device. Consult your local sales office to confirm availability of

specific valid combinations or to check on newly released combinations.

MACH210-7/10/12/15/20, Q-12/15/20 (Com’l)

5

ORDERING INFORMATION

Industrial Products

Programmable logic products for industrial applications are available with several ordering options. The order number (Valid

Combination) is formed by a combination of:

MACH -12 J I

FAMILY TYPE

MACH = Macro Array CMOS High-Speed

DEVICE NUMBER

210 = 64 Macrocells, 44 Pins

210A = 64 Macrocells, 44 Pins, Input Pull-Up Resistors

SPEED

-12 = 12 ns t

-14 = 14.5 ns t

-18 = 18 ns t

-24 = 24 ns t

PD

PD

PD

PD

Valid Combinations

MACH210A-12

MACH210A-14

MACH210-14

MACH210-18

MACH210-24

JI

210A

OPTIONAL PROCESSING

Blank = Standard Processing

OPERATING CONDITIONS

I = Industrial (–40

PACKAGE TYPE

J = 44-Pin Plastic Leaded Chip

Carrier (PL 044)

Valid Combinations

The Valid Combinations table lists configurations

planned to be supported in volume for this device. Consult your local sales office to confirm availability of

specific valid combinations or to check on newly released combinations.

°C to +85°C)

6 MACH210-12/14/18/24 (Ind)

FUNCTIONAL DESCRIPTION

The MACH210 consists of four PAL blocks connected

by a switch matrix. There are 32 I/O pins and 4

dedicated input pins feeding the switch matrix. These

signals are distributed to the four PAL blocks for efficient

design implementation. There are two clock pins that

can also be used as dedicated inputs.

The MACH210A inputs and I/O pins have built-in pull-up

resistors. While it is always a good design practice to tie

unused pins high, the 210A pull-up resistors provide

design security and stability in the event that unused

pins are left disconnected.

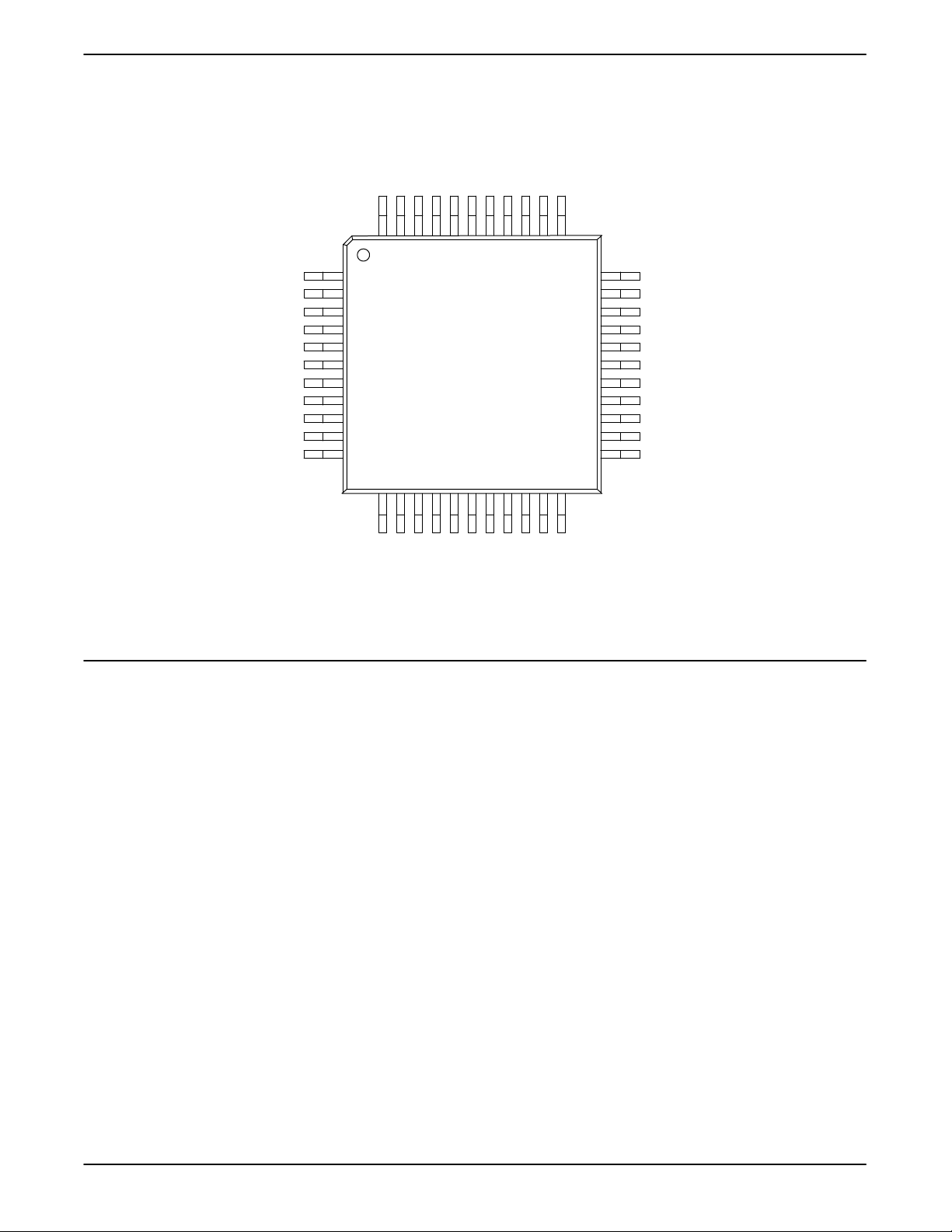

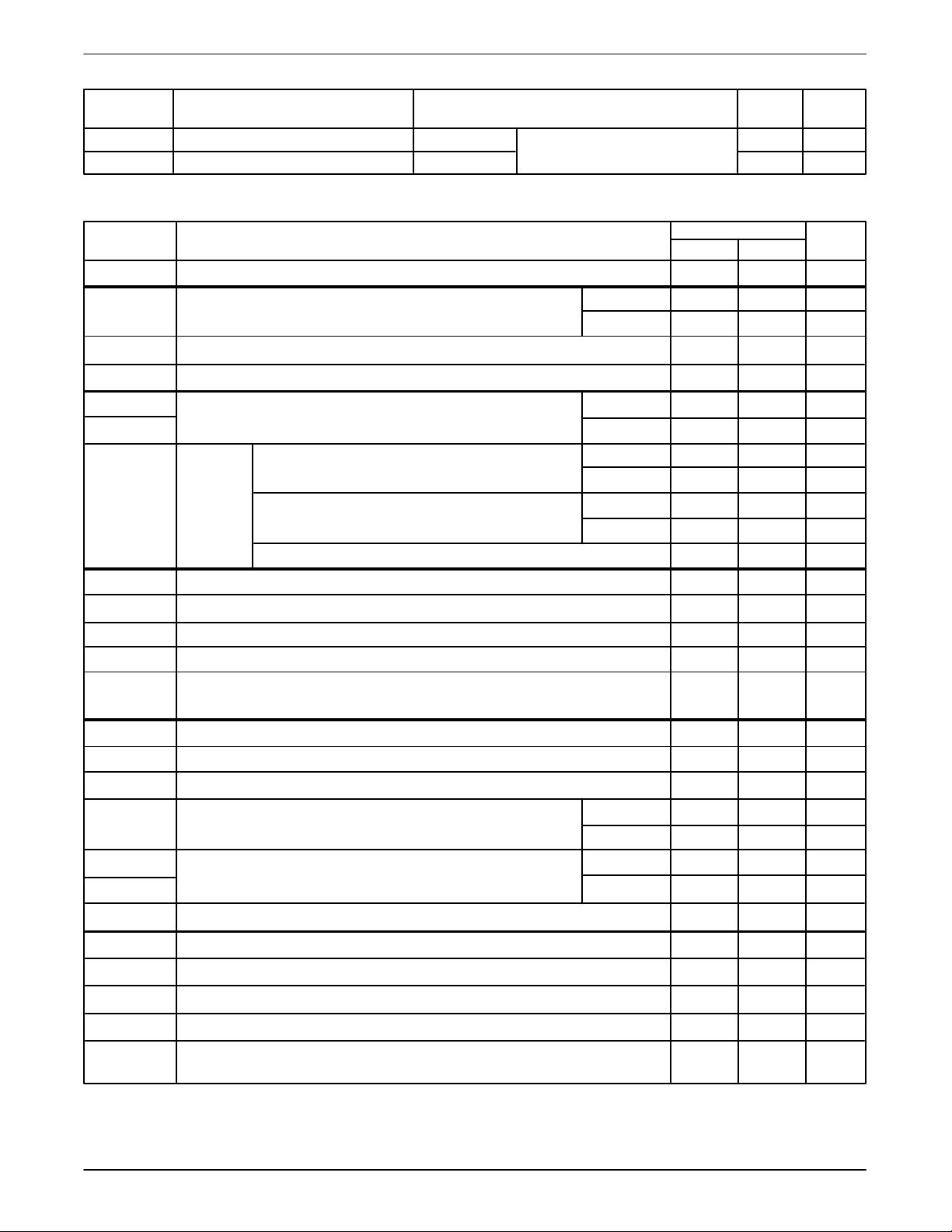

The PAL Blocks

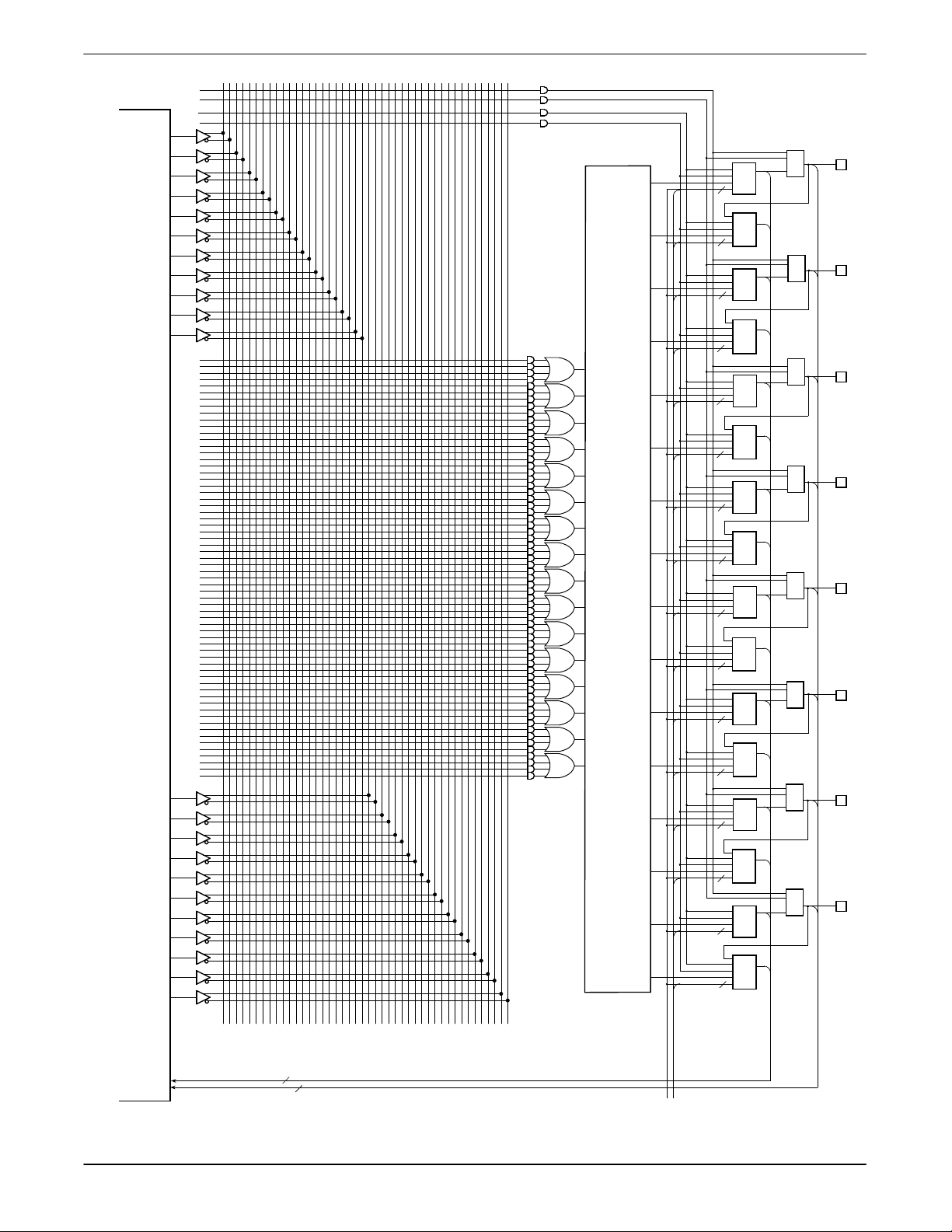

Each PAL block in the MACH210 (Figure 1) contains a

64-product-term logic array, a logic allocator, 8 output

macrocells, 8 buried macrocells, and 8 I/O cells. The

switch matrix feeds each PAL block with 22 inputs. This

makes the PAL block look effectively like an independent “PAL22V16” with 8 buried macrocells.

In addition to the logic product terms, two output enable

product terms, an asynchronous reset product term,

and an asynchronous preset product term are provided.

One of the two output enable product terms can be

chosen within each I/O cell in the PAL block. All flip-flops

within the PAL block are initialized together.

The Switch Matrix

The MACH210 switch matrix is fed by the inputs and

feedback signals from the PAL blocks. Each PAL block

provides 16 internal feedback signals and 8 I/O

feedback signals. The switch matrix distributes these

signals back to the PAL blocks in an efficient manner

that also provides for high performance. The design

software automatically configures the switch matrix

when fitting a design into the device.

The Product-term Array

The MACH210 product-term array consists of 64

product terms for logic use, and 4 special-purpose

product terms. Two of the special-purpose product

terms provide programmable output enable; one provides asynchronous reset, and one provides asynchronous preset.

The Logic Allocator

The logic allocator in the MACH210 takes the 64 logic

product terms and allocates them to the 16 macrocells

as needed. Each macrocell can be driven by up to 16

product terms. The design software automatically

configures the logic allocator when fitting the design into

the device.

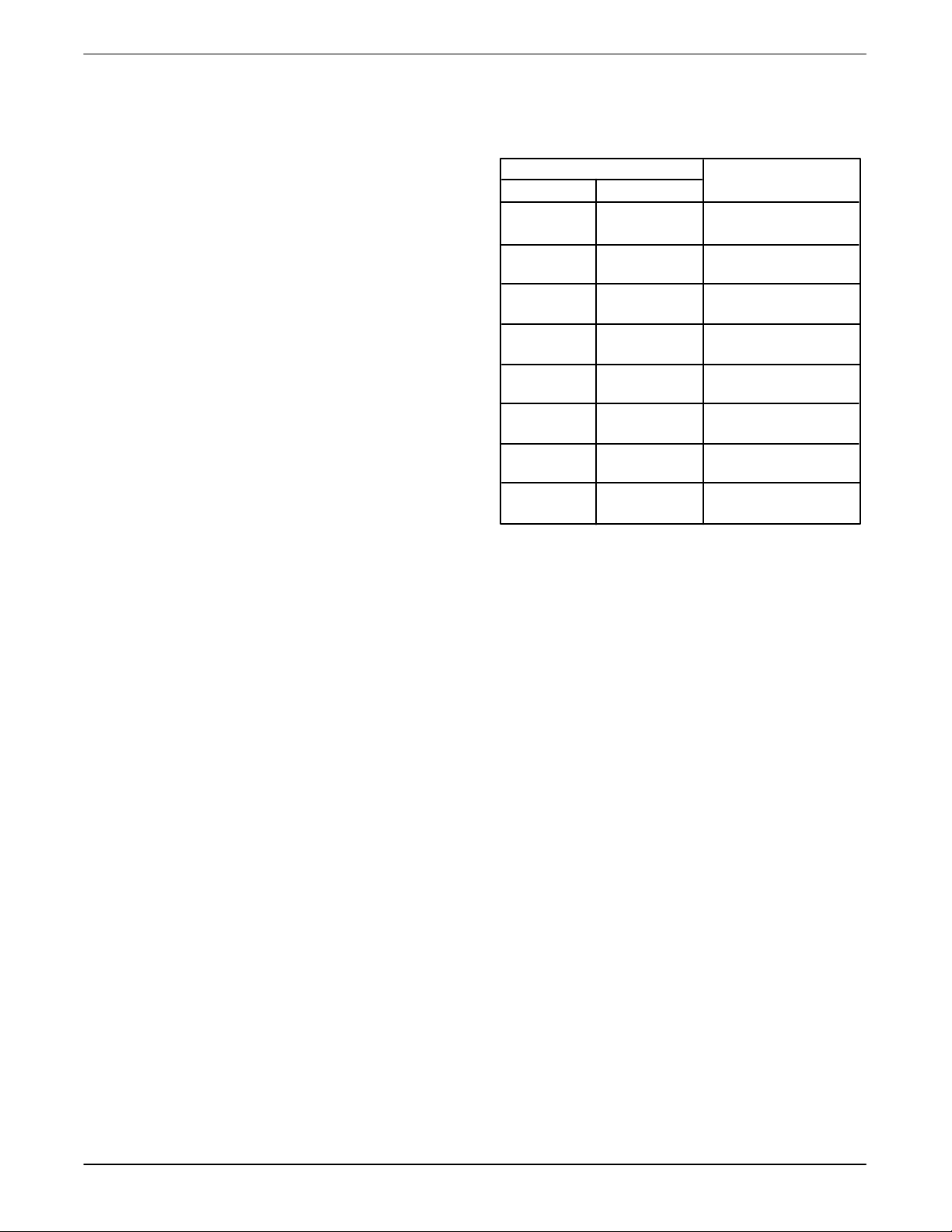

Table 1 illustrates which product term clusters are

available to each macrocell within a PAL block. Refer to

Figure 1 for cluster and macrocell numbers.

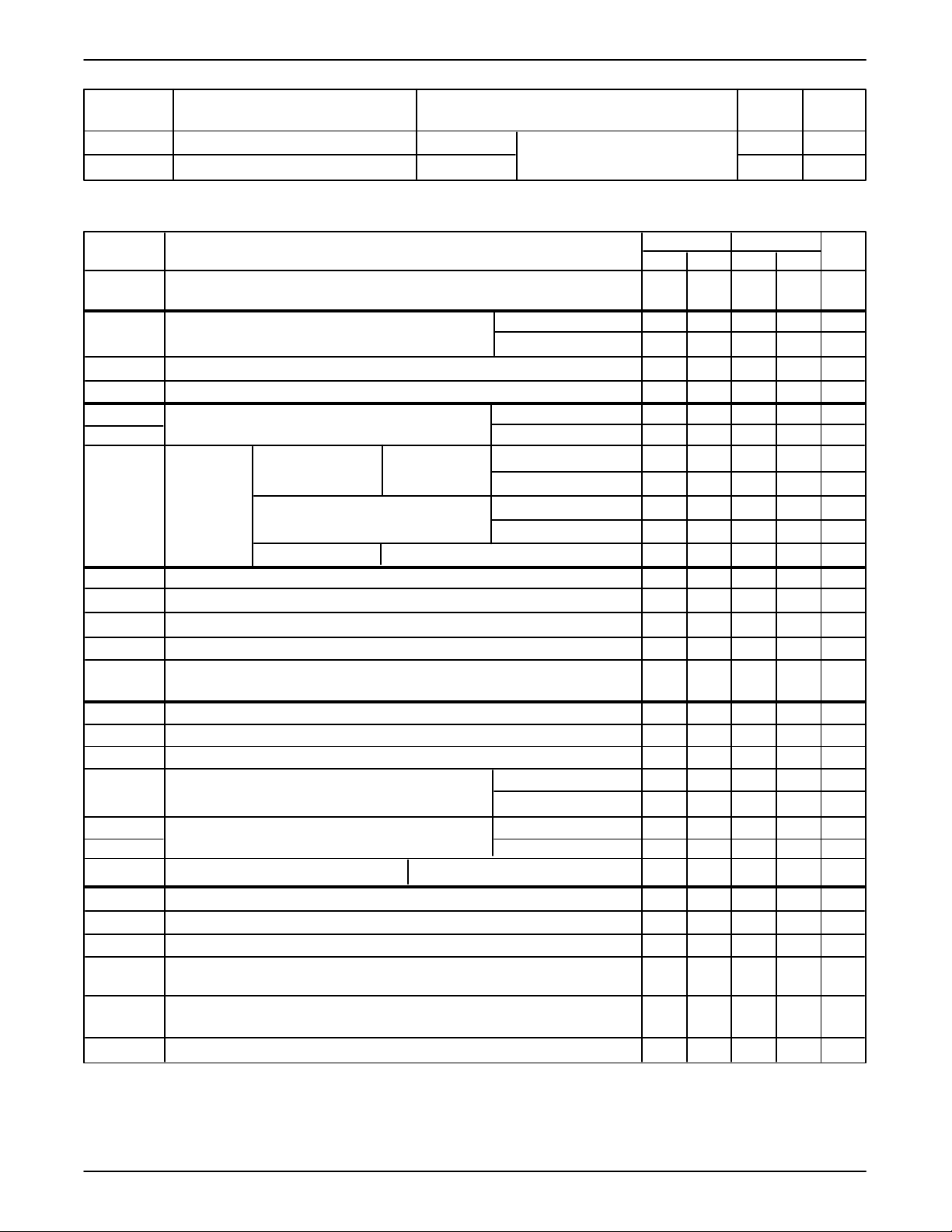

Table 1. Logic Allocation

Macrocell

Output Buried Clusters

M

0

M

1

M

2

M

3

M

4

M

5

M

6

M

7

M

8

M

9

M

10

M

11

M

12

M

13

M

14

M

15

Available

C0, C1, C

C0, C1, C2, C

C1, C2, C3, C

C2, C3, C4, C

C3, C4, C5, C

C4, C5, C6, C

C5, C6, C7, C

C6, C7, C8, C

C7, C8, C9, C

2

3

4

5

6

7

8

9

10

C8, C9, C10, C

C9, C10, C11, C

C10, C11, C12, C

C11, C12, C13, C

C12, C13, C14, C

C13, C14, C

C14, C

15

15

11

12

13

14

15

The Macrocell

The MACH210 has two types of macrocell: output and

buried. The output macrocells can be configured as

either registered, latched, or combinatorial, with programmable polarity. The macrocell provides internal

feedback whether configured with or without the flipflop. The registers can be configured as D-type or

T-type, allowing for product-term optimization.

The flip-flops can individually select one of two clock/

gate pins, which are also available as data inputs. The

registers are clocked on the LOW-to-HIGH transition of

the clock signal. The latch holds its data when the gate

input is HIGH, and is transparent when the gate input is

LOW. The flip-flops can also be asynchronously initialized with the common asynchronous reset and preset

product terms.

The buried macrocells are the same as the output

macrocells if they are used for generating logic. In that

case, the only thing that distinguishes them from the

output macrocells is the fact that there is no I/O cell

connection, and the signal is only used internally. The

buried macrocell can also be configured as an input

register or latch.

7MACH210-7/10/12/15/20, Q-12/15/20

The I/O Cell

The I/O cell in the MACH210 consists of a three-state

output buffer. The three-state buffer can be configured

in one of three ways: always enabled, always disabled,

or controlled by a product term. If product term control is

chosen, one of two product terms may be used to

provide the control. The two product terms that are

available are common to all I/O cells in a PAL block.

These choices make it possible to use the macrocell as

an output, an input, a bidirectional pin, or a three-state

output for use in driving a bus.

PCI Compliance

The MACH210A-7/10 is fully compliant with the

Local Bus Specification

Interest Group. The MACH210A-7/10’s predictable

timing ensures compliance with the PCI AC specifications independent of the design. On the other hand, in

CPLD and FPGA architectures without predictable

timing, PCI compliance is dependent upon routing and

product term distribution.

published by the PCI Special

PCI

MACH210-7/10/12/15/20, Q-12/15/208

0 4 8 12 16 20 24 28 40324336

Output Enable

Output Enable

Asynchronous Reset

Asynchronous Preset

Switch

Matrix

I/O

Output

M

0

M

1

M

2

M

0

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

63

3

0

M

1

4

2

M

3

5

4

M

5

6

6

M

7

7

Logic Allocator

8

M

9

8

10

M

11

9

12

M

13

10

14

M

15

11

M

12

Macro

cell

2

Buried

Macro

cell

2

Output

Macro

cell

2

Buried

Macro

cell

2

Output

Macro

cell

2

Buried

Macro

cell

2

Output

Macro

cell

2

Buried

Macro

cell

2

Output

Macro

cell

2

Buried

Macro

cell

2

Output

Macro

cell

2

Buried

Macro

cell

2

Output

Macro

cell

2

Cell

I/O

Cell

I/O

Cell

I/O

Cell

I/O

Cell

I/O

Cell

I/O

Cell

I/O

I/O

I/O

I/O

I/O

I/O

I/O

0 4 8 12 16 20 24 28 40324336

16

8

Figure 1. MACH210 PAL Block

Buried

M

13

M

14

M

15

CLK0

CLK1

Macro

cell

2

I/O

Output

Macro

cell

2

Buried

Macro

cell

2

Cell

I/O

14128I-4

9MACH210-7/10/12/15/20, Q-12/15/20

ABSOLUTE MAXIMUM RATINGS

Storage Temperature –65°C to +150°C. . . . . . . . . . .

Ambient Temperature

with Power Applied –55°C to +125°C. . . . . . . . . . . . .

Supply Voltage with

Respect to Ground –0.5 V to +7.0 V. . . . . . . . . . . . .

DC Input Voltage –0.5 V to VCC + 0.5 V. . . . . . . . . . .

DC Output or

I/O Pin Voltage –0.5 V to V

CC

+ 0.5 V. . . . . . . . . . . .

OPERATING RANGES

Commercial (C) Devices

Temperature (TA) Operating

in Free Air 0°C to +70°C. . . . . . . . . . . . . . . . . . . . . . .

Supply Voltage (V

Respect to Ground +4.75 V to +5.25 V. . . . . . . . . . . .

Operating ranges define those limits between which the functionality of the device is guaranteed.

CC

) with

Static Discharge Voltage 2001 V. . . . . . . . . . . . . . . . .

Latchup Current

(T

= 0°C to +70°C) 200 mA. . . . . . . . . . . . . . . . . . . .

A

Stresses above those listed under Absolute Maximum Ratings

may cause permanent device failure. Functionality at or above

these limits is not implied. Exposure to Absolute Maximum

Ratings for extended periods may affect device reliability. Programming conditions may differ.

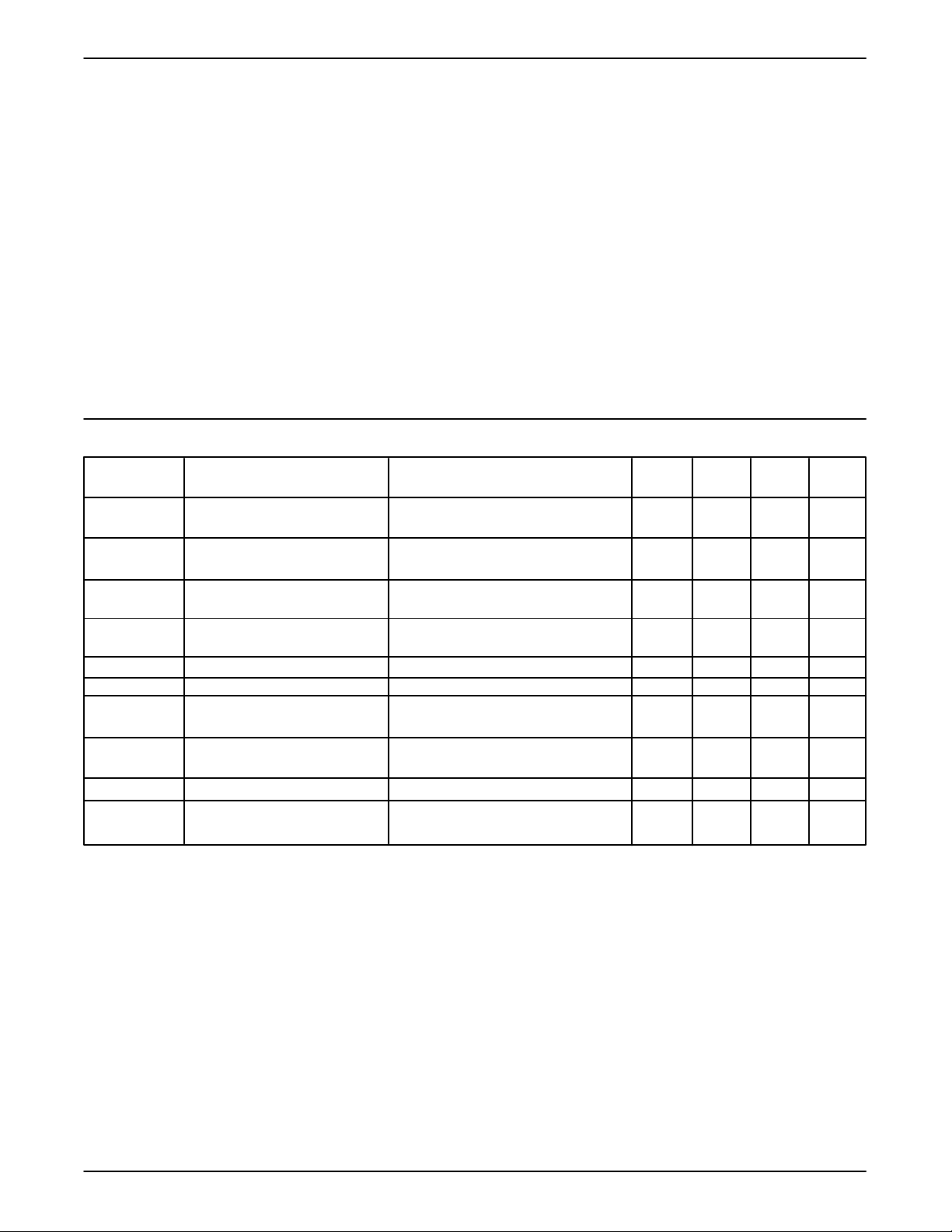

DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

Parameter

Symbol Parameter Description Test Conditions Min Typ Max Unit

V

OH

V

OL

V

IH

V

IL

I

IH

I

IL

IOZH Off-State Output Leakage V

IOZL Off-State Output Leakage V

I

SC

I

CC

(Note 4)

Notes:

1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

2. I/O pin leakage is the worst case of I

3. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

V

= 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

OUT

4. This parameter is measured with a 16-bit up/down counter pattern. This pattern is programmed in each PAL block and

capable of being loaded, enabled, and reset.

Output HIGH Voltage IOH = –3.2 mA, VCC = Min 2.4 V

= V

IH

or V

IL

V

IN

Output LOW Voltage IOL = 16 mA, VCC = Min 0.5 V

= V

IH

or V

IL

V

IN

Input HIGH Voltage Guaranteed Input Logical HIGH 2.0 V

Voltage for all Inputs (Note 1)

Input LOW Voltage Guaranteed Input Logical LOW 0.8 V

Voltage for all Inputs (Note 1)

Input HIGH Leakage Current VIN = 5.25 V, VCC = Max (Note 2) 10 µA

Input LOW Leakage Current V

Current HIGH V

Current LOW V

Output Short-Circuit Current V

Supply Current V

and I

IL

(or IIH and I

OZL

= 0 V, V

IN

= 5.25 V, VCC = Max 10 µA

OUT

= V

IN

IH

= 0 V, VCC = Max –100 µA

OUT

= V

IN

IH

= 0.5 V, VCC = Max (Note 3) –30 –160 mA

OUT

= 0 V, Outputs Open (I

IN

= 5.0 V, f = 25 MHz, TA = 25°C

V

CC

OZH

= Max (Note 2) –100 µA

CC

or VIL (Note 2)

or VIL (Note 2)

= 0 mA) 130 mA

OUT

).

10 MACH210A-7 (Com’l)

CAPACITANCE (Note 1)

Parameter

Symbol Parameter Description Test Conditions Typ Unit

C

C

OUT

IN

Input Capacitance V

Output Capacitance V

= 2.0 V VCC = 5.0 V, TA = 25°C, 6 pF

IN

= 2.0 V f = 1 MHz 8 pF

OUT

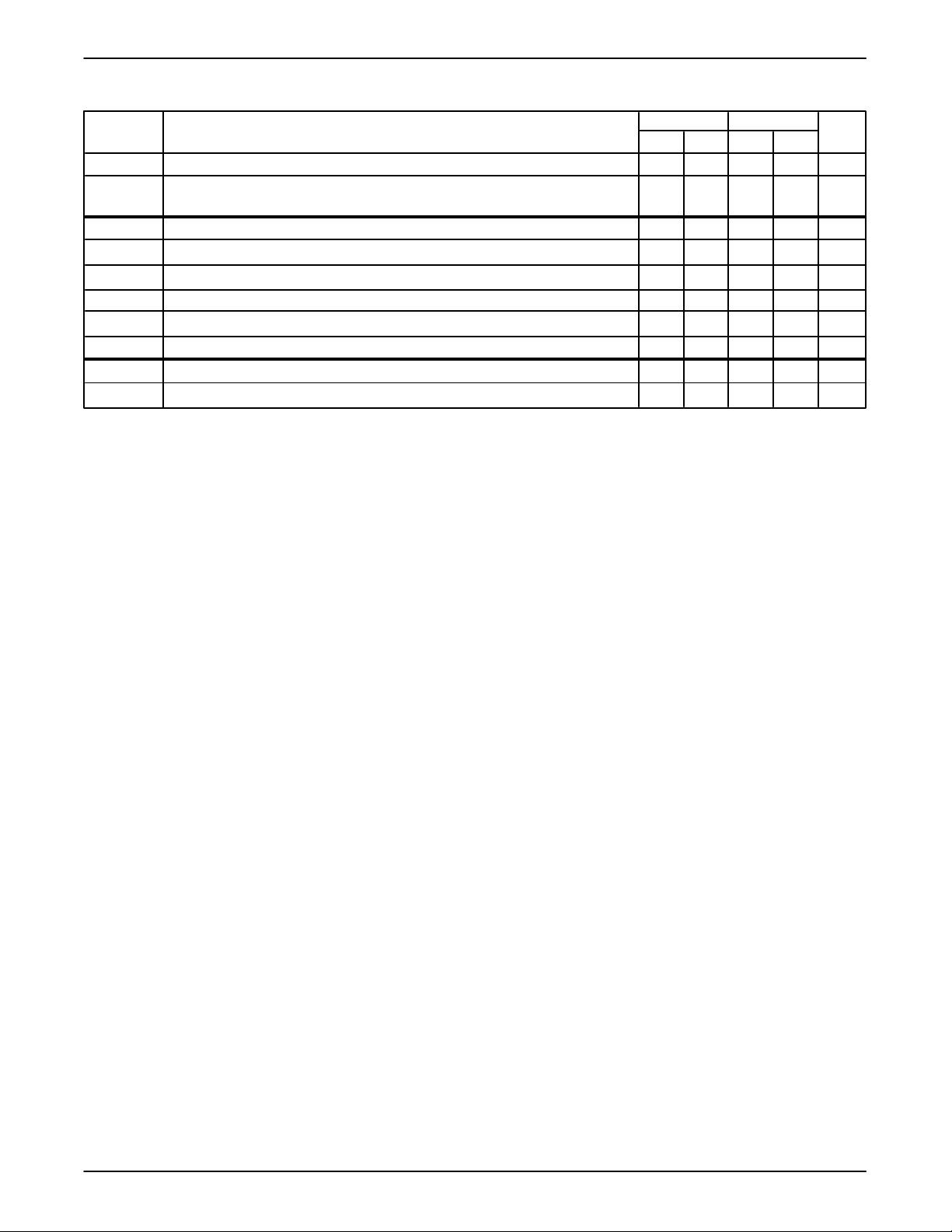

SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges

Parameter

Symbol Parameter Description Min Max Unit

t

PD

t

S

Input, I/O, or Feedback to Combinatorial Output 7.5 ns

Setup Time from Input, I/O or Feedback to Clock D-Type 5.5 ns

T-Type 6.5 ns

-7

t

H

t

CO

t

WL

t

WH

f

MAX

t

SL

t

HL

t

GO

t

GWL

t

PDL

t

SIR

t

HIR

t

ICO

t

ICS

Register Data Hold Time 0 ns

Clock to Output 5ns

Clock Width LOW 3 ns

HIGH 3 ns

D-Type 100 MHz

Maximum

D-Type 133 MHz

Frequency

External Feedback

Internal Feedback (f

No Feedback

CNT

T-Type 91 MHz

)

T-Type 125 MHz

166.7 MHz

Setup Time from Input, I/O, or Feedback to Gate 5.5 ns

Latch Data Hold Time 0 ns

Gate to Output 6ns

Gate Width LOW 3 ns

Input, I/O, or Feedback to Output Through 9.5 ns

Transparent Input or Output Latch

Input Register Setup Time 2 ns

Input Register Hold Time 2 ns

Input Register Clock to Combinatorial Output 11 ns

Input Register Clock to Output Register Setup D-Type 9 ns

T-Type 10 ns

t

WICL

t

WICH

f

MAXIR

t

SIL

t

HIL

t

IGO

t

IGOL

t

SLL

Input Register Clock Width LOW 3 ns

HIGH 3 ns

Maximum Input Register Frequency 166.7 MHz

Input Latch Setup Time 2 ns

Input Latch Hold Time 2 ns

Input Latch Gate to Combinatorial Output 12 ns

Input Latch Gate to Output Through Transparent Output Latch 14 ns

Setup Time from Input, I/O, or Feedback Through 7.5 ns

Transparent Input Latch to Output Latch Gate

11MACH210A-7 (Com’l)

SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (continued)

Parameter

-7

Symbol Parameter Description Min Max Unit

t

IGS

t

WIGL

t

PDLL

Input Latch Gate to Output Latch Setup 10 ns

Input Latch Gate Width LOW 3 ns

Input, I/O, or Feedback to Output Through Transparent 11.5 ns

Input and Output Latches

t

AR

t

ARW

t

ARR

t

AP

t

APW

t

APR

t

EA

t

ER

Asynchronous Reset to Registered or Latched Output 12 ns

Asynchronous Reset Width 8 ns

Asynchronous Reset Recovery Time 8 ns

Asynchronous Preset to Registered or Latched Output 12 ns

Asynchronous Preset Width 8 ns

Asynchronous Preset Recovery Time 8 ns

Input, I/O, or Feedback to Output Enable 7.5 ns

Input, I/O, or Feedback to Output Disable 7.5 ns

Note:

1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified

where capacitance may be affected.

12 MACH210A-7 (Com’l)

ABSOLUTE MAXIMUM RATINGS

Storage Temperature –65°C to +150°C. . . . . . . . . . .

Ambient Temperature

with Power Applied –55°C to +125°C. . . . . . . . . . . . .

Supply Voltage with

Respect to Ground –0.5 V to +7.0 V. . . . . . . . . . . . .

DC Input Voltage –0.5 V to V

DC Output or

I/O Pin Voltage –0.5 V to V

CC

CC

+ 0.5 V. . . . . . . . . . .

+ 0.5 V. . . . . . . . . . . .

OPERATING RANGES

Commercial (C) Devices

Temperature (T

in Free Air 0°C to +70°C. . . . . . . . . . . . . . . . . . . . . . .

Supply Voltage (V

Respect to Ground +4.75 V to +5.25 V. . . . . . . . . . . .

Operating ranges define those limits between which the functionality of the device is guaranteed.

) Operating

A

) with

CC

Static Discharge Voltage 2001 V. . . . . . . . . . . . . . . . .

Latchup Current (T

Stresses above those listed under Absolute Maximum Ratings

may cause permanent device failure. Functionality at or above

these limits is not implied. Exposure to Absolute Maximum

Ratings for extended periods may affect device reliability.

Programming conditions may differ.

= 0°C to +70°C) 200 mA. . . . . .

A

DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

Parameter

Symbol Parameter Description Test Conditions Min Typ Max Unit

V

OH

V

OL

V

IH

V

IL

I

IH

I

IL

I

OZH

I

OZL

I

SC

I

CC

Output HIGH Voltage IOH = –3.2 mA, VCC = Min 2.4 V

V

= VIH or V

IN

IL

Output LOW Voltage IOL = 16 mA, VCC = Min 0.5 V

= VIH or V

V

IN

IL

Input HIGH Voltage Guaranteed Input Logical HIGH 2.0 V

Voltage for all Inputs (Note 1)

Input LOW Voltage Guaranteed Input Logical LOW 0.8 V

Voltage for all Inputs (Note 1)

Input HIGH Leakage Current VIN = 5.25 V, VCC = Max (Note 2) 10 µA

Input LOW Leakage Current VIN = 0 V, V

Off-State Output Leakage V

Current HIGH V

Off-State Output Leakage V

Current LOW V

Output Short-Circuit Current V

Supply Current (Typical) V

= 5.25 V, VCC = Max 10 µA

OUT

= V

IN

= 0 V, VCC = Max –100 µA

OUT

= V

IN

= 0.5 V, VCC = Max (Note 3) –30 –160 mA

OUT

= 5V, TA = 25°C, f = 25 MHz 135 mA

CC

= Max (Note 2) –100 µA

CC

or VIL (Note 2)

IH

or VIL (Note 2)

IH

(Note 4)

Notes:

1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

2. I/O pin leakage is the worst case of I

and I

IL

(or IIH and I

OZL

OZH

).

3. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

= 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

V

OUT

4. Measured with a 16-bit up/down counter pattern. This pattern is programmed in each PAL block and is capable of being

loaded, enabled, and reset.

MACH210A-10/12 (Com’l)

13

CAPACITANCE (Note 1)

Parameter

Symbol Parameter Description Test Conditions Typ Unit

C

IN

C

OUT

Input Capacitance V

Output Capacitance V

= 2.0 V VCC = 5.0 V, TA = 25°C, 6 pF

IN

= 2.0 V f = 1 MHz 8 pF

OUT

SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)

Parameter

Symbol Parameter Description Min Max Min Max Unit

t

PD

Input, I/O, or Feedback to Combinatorial Output

(Note 3) 10 12 ns

t

S

t

H

t

CO

t

WL

t

WH

Setup Time from Input, I/O,

or Feedback to Clock

Register Data Hold Time 0 0 ns

Clock to Output (Note 3) 6 8 ns

Clock LOW 5 6 ns

Width HIGH 5 6 ns

D-Type 6.5 7 ns

T-Type 7.5 8 ns

D-Type 80 66.7 MHz

f

MAX

t

t

t

GO

t

GWL

t

PDL

Maximum

External Feedback 1/(tS + tCO)

Frequency

D-Type 100 83.3 MHz

(Note 1)

SL

HL

Setup Time from Input, I/O, or Feedback to Gate 6.5 7 ns

Latch Data Hold Time 0 0 ns

Internal Feedback (f

CNT

No Feedback 1/(t

)

S

+ t

)

H

Gate to Output (Note 3) 7 10 ns

Gate Width LOW 5 6 ns

Input, I/O, or Feedback to Output Through

T-Type 74 62.5 MHz

T-Type 91 76.9 MHz

Transparent Input or Output Latch 12 14 ns

t

SIR

t

HIR

t

ICO

t

ICS

Input Register Setup Time 2 2 ns

Input Register Hold Time 2 2 ns

Input Register Clock to Combinatorial Output 13 15 ns

Input Register Clock to Output Register Setup D-Type 10 12 ns

T-Type 11 13 ns

t

WICL

t

WICH

f

MAXIR

t

SIL

t

HIL

t

IGO

t

IGOL

Input Register LOW 5 6 ns

Clock Width HIGH 5 6 ns

Maximum Input Register Frequency 1/(t

WICL

+ t

) 100 83.3 MHz

WICH

Input Latch Setup Time 2 2 ns

Input Latch Hold Time 2 2 ns

Input Latch Gate to Combinatorial Output 14 17 ns

Input Latch Gate to Output Through Transparent

Output Latch 16 19 ns

t

SLL

Setup Time from Input, I/O, or Feedback Through

Transparent Input Latch to Output Latch Gate 8.5 9 ns

t

IGS

Input Latch Gate to Output Latch Setup 11 13 ns

-10 -12

100 83.3 MHz

14

MACH210A-10/12 (Com’l)

SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)

(continued)

Parameter

Symbol Parameter Description Min Max Min Max Unit

t

WIGL

t

PDLL

t

AR

t

ARW

t

ARR

t

AP

t

APW

t

APR

t

EA

t

ER

Notes:

1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified

where capacitance may be affected.

2. See Switching Test Circuit, for test conditions.

3. Parameters measured with 16 outputs switching.

Input Latch Gate Width LOW 5 6 ns

Input, I/O, or Feedback to Output Through Transparent

Input and Output Latches 14 16 ns

Asynchronous Reset to Registered or Latched Output 25 16 ns

Asynchronous Reset Width (Note 1) 10 12 ns

Asynchronous Reset Recovery Time (Note 1) 10 8 ns

Asynchronous Preset to Registered or Latched Output 15 16 ns

Asynchronous Preset Width (Note 1) 10 12 ns

Asynchronous Preset Recovery Time (Note 1) 10 8 ns

Input, I/O, or Feedback to Output Enable (Note 3) 10 12 ns

Input, I/O, or Feedback to Output Disable (Note 3) 10 12 ns

-10 -12

MACH210A-10/12 (Com’l)

15

Loading...

Loading...