Lattice Semiconductor Corporation ISPLSI3256A-90LQ, ISPLSI3256A-90LM, ISPLSI3256A-70LQI, ISPLSI3256A-70LQ, ISPLSI3256A-70LM Datasheet

...

®

ispLSI

3256A

In-System Programmable High Density PLD

Features

• HIGH-DENSITY PROGRAMMABLE LOGIC

— 128 I/O Pins

— 11000 PLD Gates

— 384 Registers

— High Speed Global Interconnect

— Wide Input Gating for Fast Counters, State

Machines, Address Decoders, etc.

— Small Logic Block Size for Random Logic

2

• HIGH-PERFORMANCE E

—

fmax = 90 MHz Maximum Operating Frequency

tpd = 12 ns Propagation Delay

—

— TTL Compatible Inputs and Outputs

— Electrically Erasable and Reprogrammable

— Non-Volatile

— 100% Tested at Time of Manufacture

— Unused Product Term Shutdown Saves Power

• IN-SYSTEM PROGRAMMABLE

— 5V In-System Programmable (ISP™) using Lattice

ISP or Boundary Scan Test (IEEE 1149.1) Protocol

— Increased Manufacturing Yields, Reduced Time-to-

Market, and Improved Product Quality

— Reprogram Soldered Devices for Faster Debugging

• 100% IEEE 1149.1 BOUNDARY SCAN COMPATIBLE

• OFFERS THE EASE OF USE AND FAST SYSTEM

SPEED OF PLDs WITH THE DENSITY AND FLEXIBILITY

OF FIELD PROGRAMMABLE GATE ARRAYS

— Complete Programmable Device Can Combine Glue

Logic and Structured Designs

— Enhanced Pin Locking Capability

— Five Dedicated Clock Input Pins

— Synchronous and Asynchronous Clocks

— Programmable Output Slew Rate Control to Mini-

mize Switching Noise

— Flexible Pin Placement

— Optimized Global Routing Pool Provides Global

Interconnectivity

• ispDesignEXPERT™ – LOGIC COMPILER AND COMPLETE ISP DEVICE DESIGN SYSTEMS FROM HDL

SYNTHESIS THROUGH IN-SYSTEM PROGRAMMING

— Superior Quality of Results

— Tightly Integrated with Leading CAE Vendor Tools

— Productivity Enhancing Timing Analyzer, Explore

Tools, Timing Simulator and ispANALYZER™

— PC and UNIX Platforms

CMOS® TECHNOLOGY

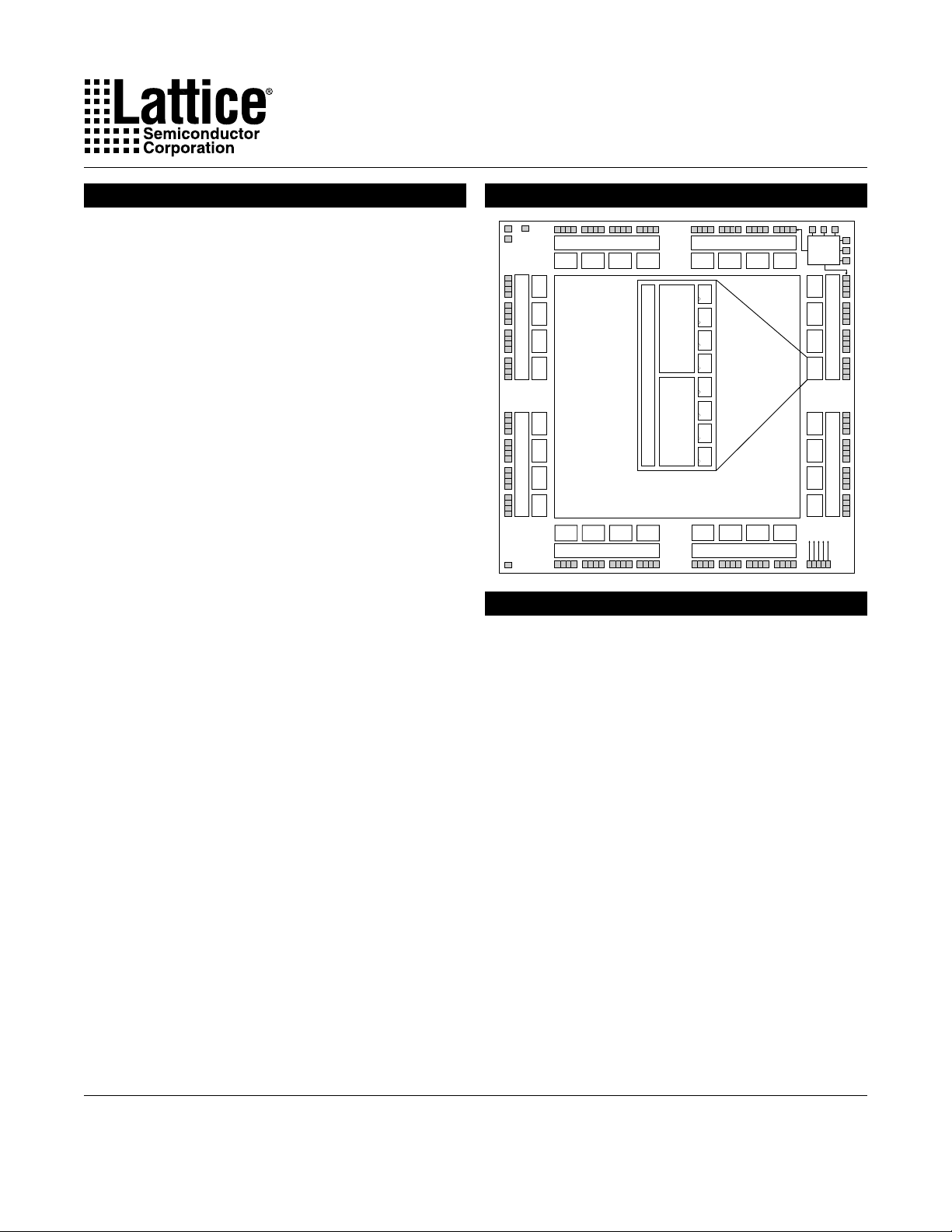

Functional Block Diagram

Output Routing Pool

H3 H2 H1 H0

A0

A1

A2

A3

Output Routing Pool

B0

B1

B2

B3

Output Routing Pool

C0 C1 C2 C3

Output Routing Pool

AND Array

Global Routing Pool

Output Routing Pool

G3

DQ

DQ

OR

Array

DQ

DQ

DQ

DQ

OR

Array

DQ

DQ

D0

Output Routing Pool

G2 G1 G0

Twin

GLB

D1 D2

D3

Boundary

Scan

F3

F2

F1

F0

Output Routing Pool

E3

E2

E1

E0

Output Routing Pool

0139A

Description

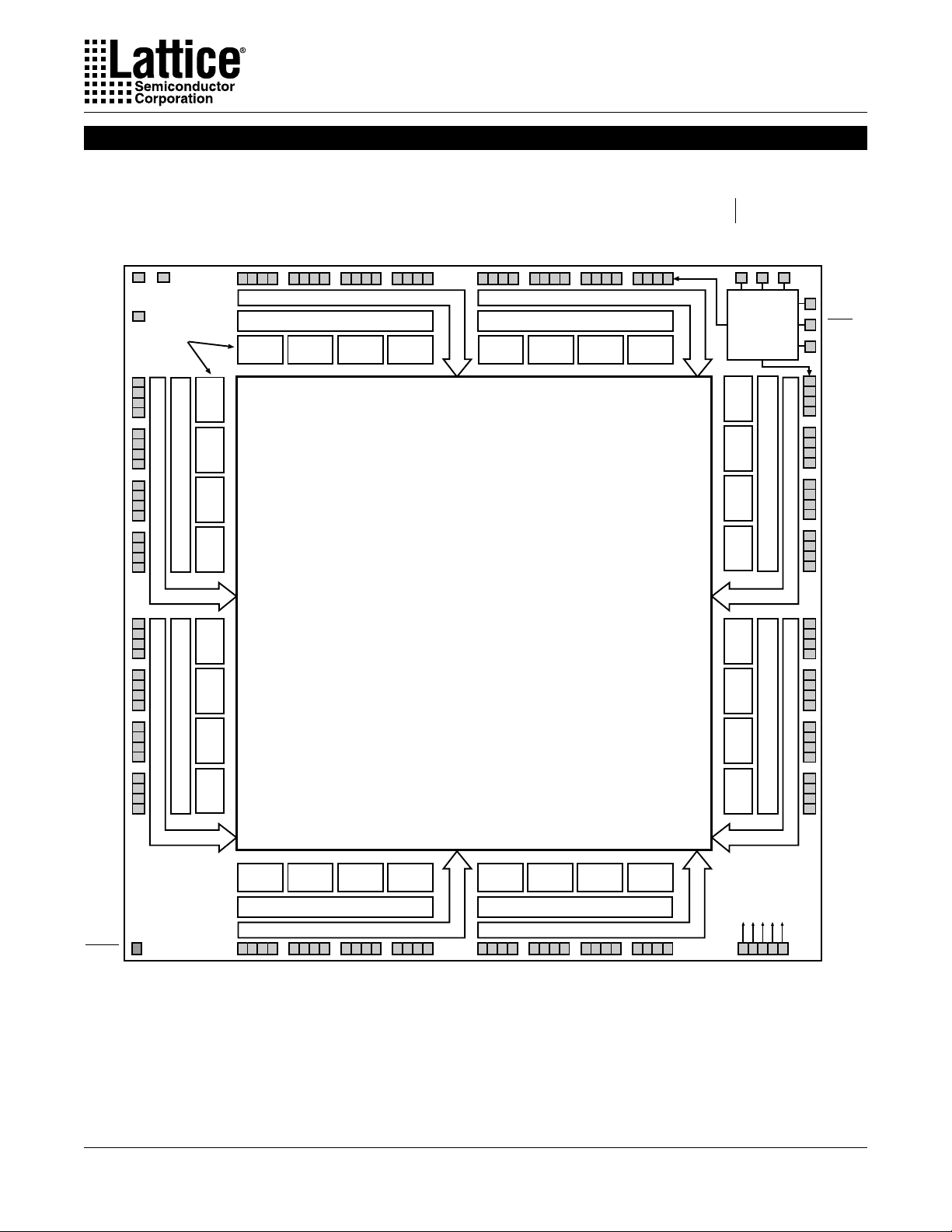

The ispLSI 3256A is a High-Density Programmable Logic

Device containing 384 Registers, 128 Universal I/O pins,

five Dedicated Clock Input Pins, eight Output Routing

Pools (ORP) and a Global Routing Pool (GRP) which

allows complete inter-connectivity between all of these

elements. The ispLSI 3256A features 5V in-system

programmability and in-system diagnostic capabilities.

The ispLSI 3256A offers non-volatile reprogrammability

of the logic, as well as the interconnect to provide truly

reconfigurable systems.

The basic unit of logic on the ispLSI 3256A device is the

Twin Generic Logic Block (Twin GLB) labelled A0, A1...H3.

There are a total of 32 Twin GLBs in the ispLSI 3256A

device. Each Twin GLB has 24 inputs, a programmable

AND array and two OR/Exclusive-OR Arrays, and eight

outputs which can be configured to be either combinatorial or registered. All Twin GLB inputs come from the

GRP.

Copyright © 1999 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A. May 1999

Tel. (503) 268-8000; 1-800-LATTICE; FAX (503) 268-8556; http://www.latticesemi.com

3256a_09 1

Functional Block Diagram

Figure 1. ispLSI 3256A Functional Block Diagram

GOE0

GOE1

I/O 127

I/O 126

I/O 125

I/O 124

I/O 123

I/O 122

I/O 121

I/O 120

I/O 119

I/O 118

I/O 117

I/O 116

I/O 115

I/O 114

I/O 113

I/O 112

Specifications ispLSI 3256A

BSCAN/ispEN

TCLK/SCLK

I/O 111

I/O 110

I/O 109

I/O 108

I/O 107

I/O 106

I/O 105

I/O 104

I/O 103

I/O 102

I/O 101

I/O 100

I/O 99

I/O 98

I/O 97

I/O 96

TMS/MODE

TOE

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

I/O 16

I/O 17

I/O 18

I/O 19

I/O 20

I/O 21

I/O 22

I/O 23

I/O 24

I/O 25

I/O 26

I/O 27

I/O 28

I/O 29

I/O 30

I/O 31

Generic

Logic

Output Routing Pool (ORP)

Blocks

H3

A0

A1

A2

Input Bus

A3

B0

B1

Input Bus

B2

B3

Output Routing Pool (ORP) Output Routing Pool (ORP)

H2 H1 H0

Input Bus Input Bus

Output Routing Pool (ORP)

G3

G2 G1 G0

Global Routing Pool

(GRP)

ISP and

Boundary

Scan TAP

F3

F2

F1

F0

E3

E2

E1

E0

Output Routing Pool (ORP) Output Routing Pool (ORP)

TDI/SDI

TRST

TDO/SDO

I/O 95

I/O 94

I/O 93

I/O 92

I/O 91

I/O 90

I/O 89

I/O 88

I/O 87

I/O 86

Input Bus

I/O 85

I/O 84

I/O 83

I/O 82

I/O 81

I/O 80

I/O 79

I/O 78

I/O 77

I/O 76

I/O 75

I/O 74

I/O 73

I/O 72

I/O 71

I/O 70

Input Bus

I/O 69

I/O 68

I/O 67

I/O 66

I/O 65

I/O 64

RESET

C0

C1 C2 C3

Output Routing Pool (ORP)

Input Bus Input Bus

I/O 32

I/O 33

I/O 34

I/O 35

I/O 36

I/O 37

I/O 38

I/O 39

I/O 40

I/O 41

I/O 42

I/O 43

I/O 44

I/O 45

I/O 46

I/O 47

D0

D1 D2 D3

Output Routing Pool (ORP)

I/O 48

I/O 49

I/O 50

I/O 51

I/O 52

I/O 53

I/O 54

I/O 55

I/O 56

I/O 57

I/O 58

2

I/O 59

I/O 60

I/O 61

I/O 62

I/O 63

CLK 1

CLK 0

Y0

Y1Y2Y3

IOCLK 0

IOCLK 1

CLK 2

Y4

0139isp/3256A

Description (continued)

Specifications ispLSI 3256A

All local logic block outputs are brought back into the

GRP so they can be connected to the inputs of any other

logic block on the device. The device also has 128 I/O

cells, each of which is directly connected to an I/O pin.

Each I/O cell can be individually programmed to be a

combinatorial input, a registered input, a latched input, an

output or a bidirectional I/O pin with 3-state control. The

signal levels are TTL compatible voltages and the output

drivers can source 4 mA or sink 8 mA. Each output can

be programmed independently for fast or slow output

slew rate to minimize overall output switching noise.

The 128 I/O cells are grouped into eight sets of 16 bits.

Each of these I/O groups is associated with a logic

Megablock through the use of the ORP. These groups of

16 I/O cells share one Product Term Output Enable which

is associated with a specific pair of Megablocks and two

Global Output Enables.

Four Twin GLBs, 16 I/O cells and one ORP are connected together to make a logic Megablock. The

Megablock is defined by the resources that it shares. The

outputs of the four Twin GLBs are connected to a set of

16 I/O cells by the ORP. The ispLSI 3256A device

contains eight of these Megablocks.

The GRP has as its inputs the outputs from all of the Twin

GLBs and all of the inputs from the bidirectional I/O cells.

All of these signals are made available to the inputs of the

Twin GLBs. Delays through the GRP have been equalized to minimize timing skew and logic glitching.

Clocks in the ispLSI 3256A device are provided through

five dedicated clock pins. The five pins provide three

clocks to the Twin GLBs and two clocks to the I/O cells.

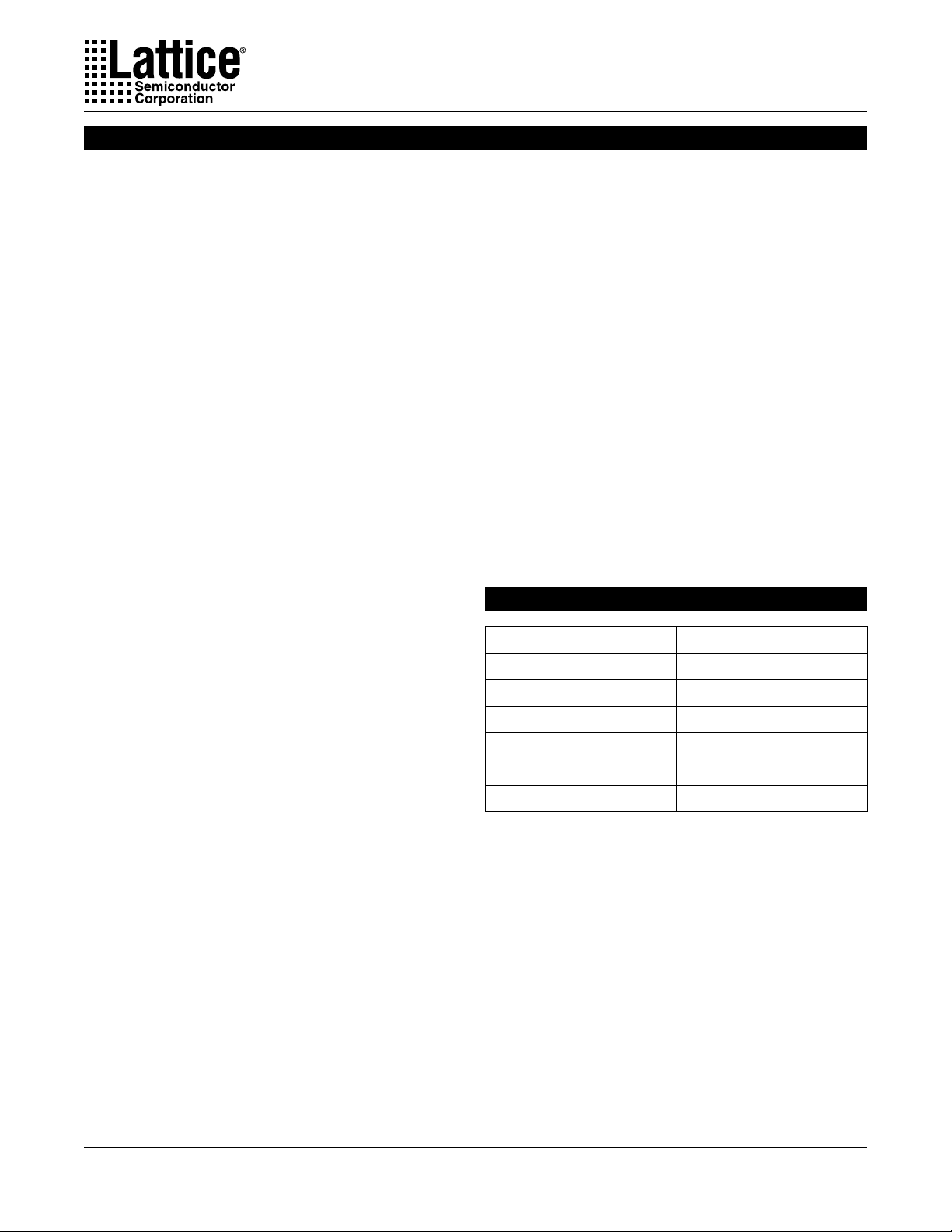

The table at right lists key attributes of the device along

with the number of resources available.

An additional feature of the ispLSI 3256A is its Boundary

Scan capability, which is composed of cells connected

between the on-chip system logic and the device’s input

and output pins. All I/O pins have associated boundary

scan registers, with 3-state I/O using three boundary

scan registers and inputs using one.

The ispLSI 3256A supports the full boundary scan IEEE

1149.1 specification for ISP programming and boardlevel tests via the TAP controller port. It is also fully

backward compatible to the Lattice ISP interface. While

fully JEDEC file and functionally compatible with the

earlier ispLSI 3256 devices, the 3256A requires a modified Boundary Scan Description Library (BSDL) model to

support boundary scan test and programming. As a

result, existing 3256 test programs that use the boundary

scan test feature must be updated to use the 3256A.

Please contact Lattice Applications for the new model.

The ispLSI 3256A supports all IEEE 1149.1 mandatory

instructions, which include BYPASS, EXTEST and

SAMPLE.

Key Attributes of the ispLSI 3256A

etubirttAytitnauQ

sBLGniwT23

sretsigeR483

sniPO/I821

skcolClabolG5

EOlabolG2

EOtseT1

6523/A3000-1elbaT

3

Specifications ispLSI 3256A

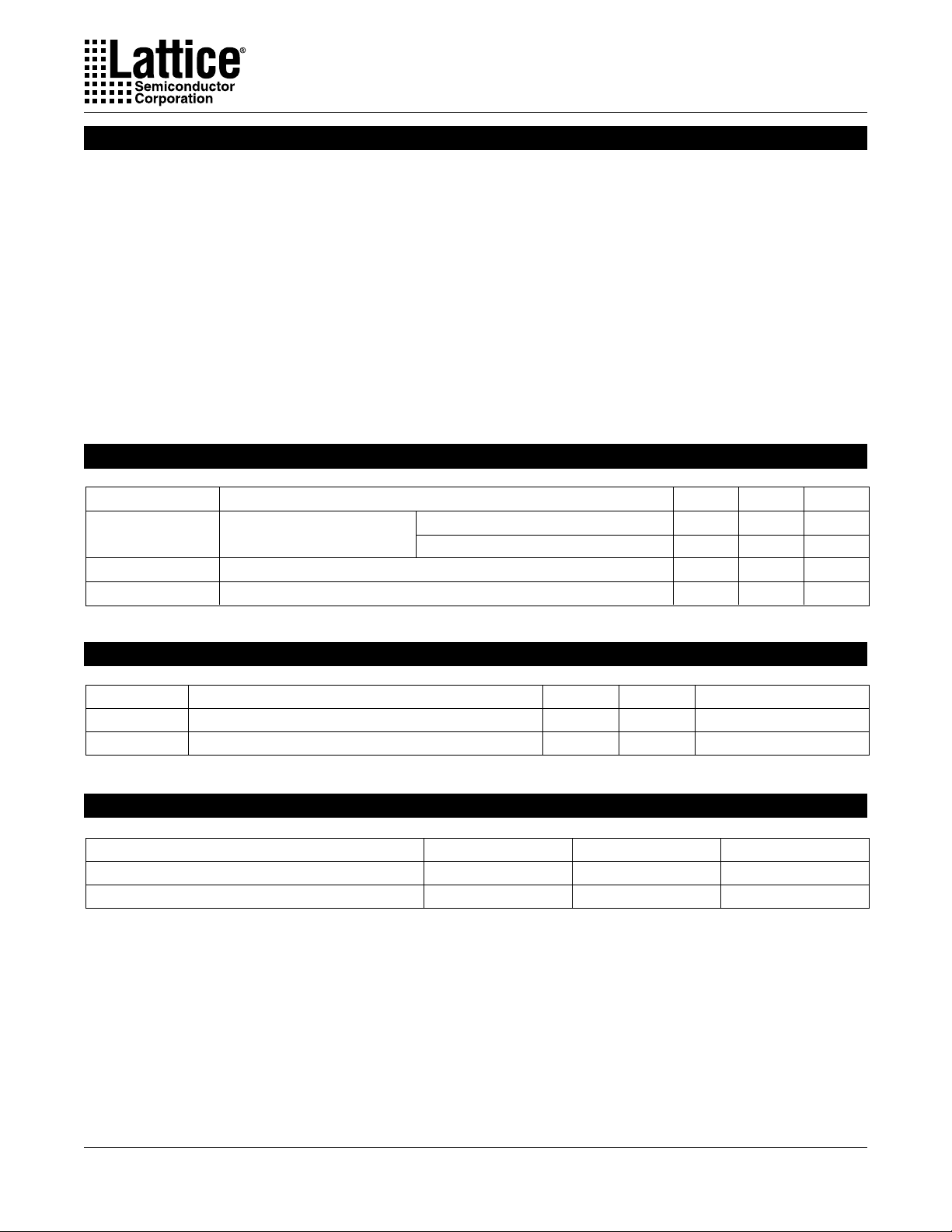

Absolute Maximum Ratings

1

Supply Voltage Vcc.................................. -0.5 to +7.0V

Input Voltage Applied........................ -2.5 to VCC +1.0V

Off-State Output Voltage Applied ..... -2.5 to VCC +1.0V

Storage Temperature................................ -65 to 150°C

Case Temp. with Power Applied .............. -55 to 125°C

Max. Junction Temp. (TJ) with Power Applied ... 150°C

1. Stresses above those listed under the “Absolute Maximum Ratings” may cause permanent damage to the device. Functional

operation of the device at these or at any other conditions above those indicated in the operational sections of this specification

is not implied (while programming, follow the programming specifications).

DC Recommended Operating Condition

V

V

V

CC

IL

IH

SYMBOL

Supply Voltage

Input Low Voltage

Input High Voltage

PARAMETER

Commercial

Industrial

TA = 0°C to + 70°C

= -40°C to + 85°C

T

A

MIN. MAX. UNITS

4.75

4.5

0

2.0

5.25

5.5

0.8

V

cc

+1

V

V

V

V

Table 2-0005/3256A

Capacitance (TA=25°C,f=1.0 MHz)

SYMBOL

C

1

C

2

I/O Capacitance (Commercial/Industrial)

Clock Capacitance

PARAMETER

Data Retention Specifications

PARAMETER

Data Retention

ispLSI Erase/Reprogram Cycles

UNITSTYPICAL TEST CONDITIONS

9

11

MINIMUM MAXIMUM UNITS

20

10000

pf V = 5.0V, V = 2.0V

pf V = 5.0V, V = 2.0V

–

–

CC I/O

CC Y

Table 2-0006/3256A

Years

Cycles

Table 2-0008/3256A

4

Loading...

Loading...