Lattice Semiconductor Corporation ISPLSI2128VE-250LT176, ISPLSI2128VE-250LQ160, ISPLSI2128VE-250LB208, ISPLSI2128VE-180LT176, ISPLSI2128VE-180LT100 Datasheet

...

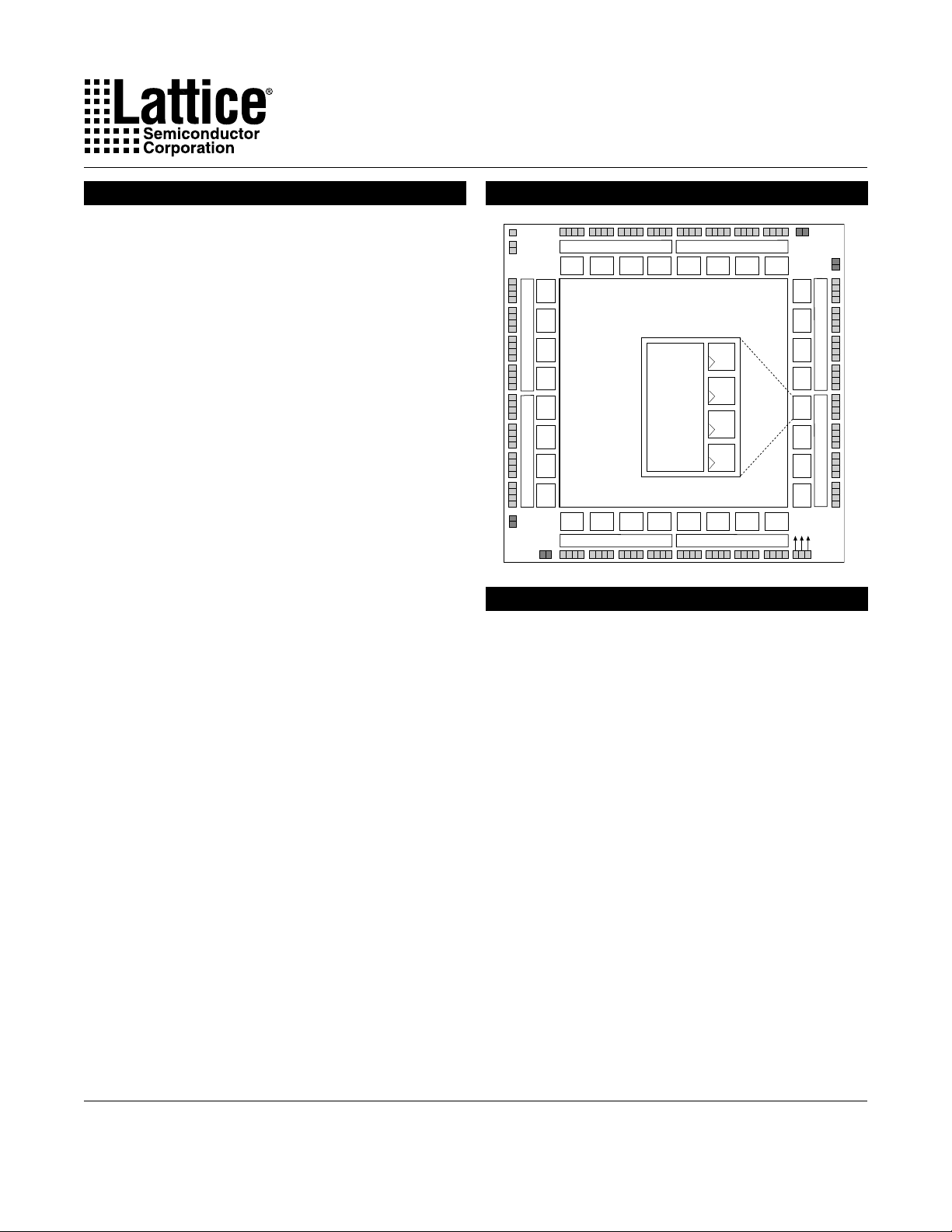

ispLSI® 2128VE

Global Routing Pool (GRP)

Output Routing Pool (ORP) Output Routing Pool (ORP)

Output Routing Pool (ORP) Output Routing Pool (ORP)

Output Routing Pool (ORP) Output Routing Pool (ORP)

CLK 0

Output Routing Pool (ORP) Output Routing Pool (ORP)

CLK 1

CLK 2

Logic

Array

GLB

DQ

DQ

DQ

DQ

0139A/2128VE

C7

C6

C5

C4

C3

C2

C1

C0

D3

D2

D1

D0

D7

D6

D5

D4

B4

B5

B6

B7

B0

B1

B2

B3

A0

A1

A2

A3

A4

A5

A6

A7

*128 I/O Version Shown

3.3V In-System Programmable

SuperFAST™ High Density PLD

• SuperFAST HIGH DENSITY IN-SYSTEM

• 3.3V LOW VOLTAGE 2128 ARCHITECTURE

• HIGH PERFORMANCE E

• IN-SYSTEM PROGRAMMABLE

• 100% IEEE 1149.1 BOUNDARY SCAN TESTABLE

• THE EASE OF USE AND FAST SYSTEM SPEED OF

• ispDesignEXPERT™ – LOGIC COMPILER AND COM-

Copyright © 2000 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A. September 2000

Tel. (503) 268-8000; 1-800-LATTICE; FAX (503) 268-8556; http://www.latticesemi.com

2128ve_08 1

Features

PROGRAMMABLE LOGIC

— 6000 PLD Gates

— 128 and 64 I/O Pin Versions, Eight Dedicated Inputs

— 128 Registers

— High Speed Global Interconnect

— Wide Input Gating for Fast Counters, State

Machines, Address Decoders, etc.

— Small Logic Block Size for Random Logic

— 100% Functional, JEDEC and Pinout Compatible

with ispLSI 2128V Devices

— Interfaces with Standard 5V TTL Devices

2

CMOS® TECHNOLOGY

—

fmax = 250MHz Maximum Operating Frequency

tpd = 4.0ns Propagation Delay

—

— Electrically Erasable and Reprogrammable

— Non-Volatile

— 100% Tested at Time of Manufacture

— Unused Product Term Shutdown Saves Power

— 3.3V In-System Programmability (ISP™) Using

Boundary Scan Test Access Port (TAP)

— Open-Drain Output Option for Flexible Bus Interface

Capability, Allowing Easy Implementation of Wired-

OR Bus Arbitration Logic

— Increased Manufacturing Yields, Reduced Time-to-

Market and Improved Product Quality

— Reprogram Soldered Devices for Faster Prototyping

PLDs WITH THE DENSITY AND FLEXIBILITY OF FPGAS

— Enhanced Pin Locking Capability

— Three Dedicated Clock Input Pins

— Synchronous and Asynchronous Clocks

— Programmable Output Slew Rate Control

— Flexible Pin Placement

— Optimized Global Routing Pool Provides Global

Interconnectivity

PLETE ISP DEVICE DESIGN SYSTEMS FROM HDL

SYNTHESIS THROUGH IN-SYSTEM PROGRAMMING

— Superior Quality of Results

— Tightly Integrated with Leading CAE Vendor Tools

— Productivity Enhancing Timing Analyzer, Explore

Tools, Timing Simulator and ispANALYZER™

— PC and UNIX Platforms

Functional Block Diagram*

Description

The ispLSI 2128VE is a High Density Programmable

Logic Device available in 128 and 64 I/O-pin versions.

The device contains 128 Registers, eight Dedicated

Input pins, three Dedicated Clock Input pins, two dedicated Global OE input pins and a Global Routing Pool

(GRP). The GRP provides complete interconnectivity

between all of these elements. The ispLSI 2128VE

features in-system programmability through the Boundary Scan Test Access Port (TAP) and is 100% IEEE

1149.1 Boundary Scan Testable. The ispLSI 2128VE

offers non-volatile reprogrammability of the logic, as well

as the interconnect to provide truly reconfigurable systems.

The basic unit of logic on the ispLSI 2128VE device is the

Generic Logic Block (GLB). The GLBs are labeled A0, A1

.. D7 (see Figure 1). There are a total of 32 GLBs in the

ispLSI 2128VE device. Each GLB is made up of four

macrocells. Each GLB has 18 inputs, a programmable

AND/OR/Exclusive OR array, and four outputs which can

be configured to be either combinatorial or registered.

Inputs to the GLB come from the GRP and dedicated

inputs. All of the GLB outputs are brought back into the

GRP so that they can be connected to the inputs of any

GLB on the device.

Specifications ispLSI 2128VE

Functional Block Diagram

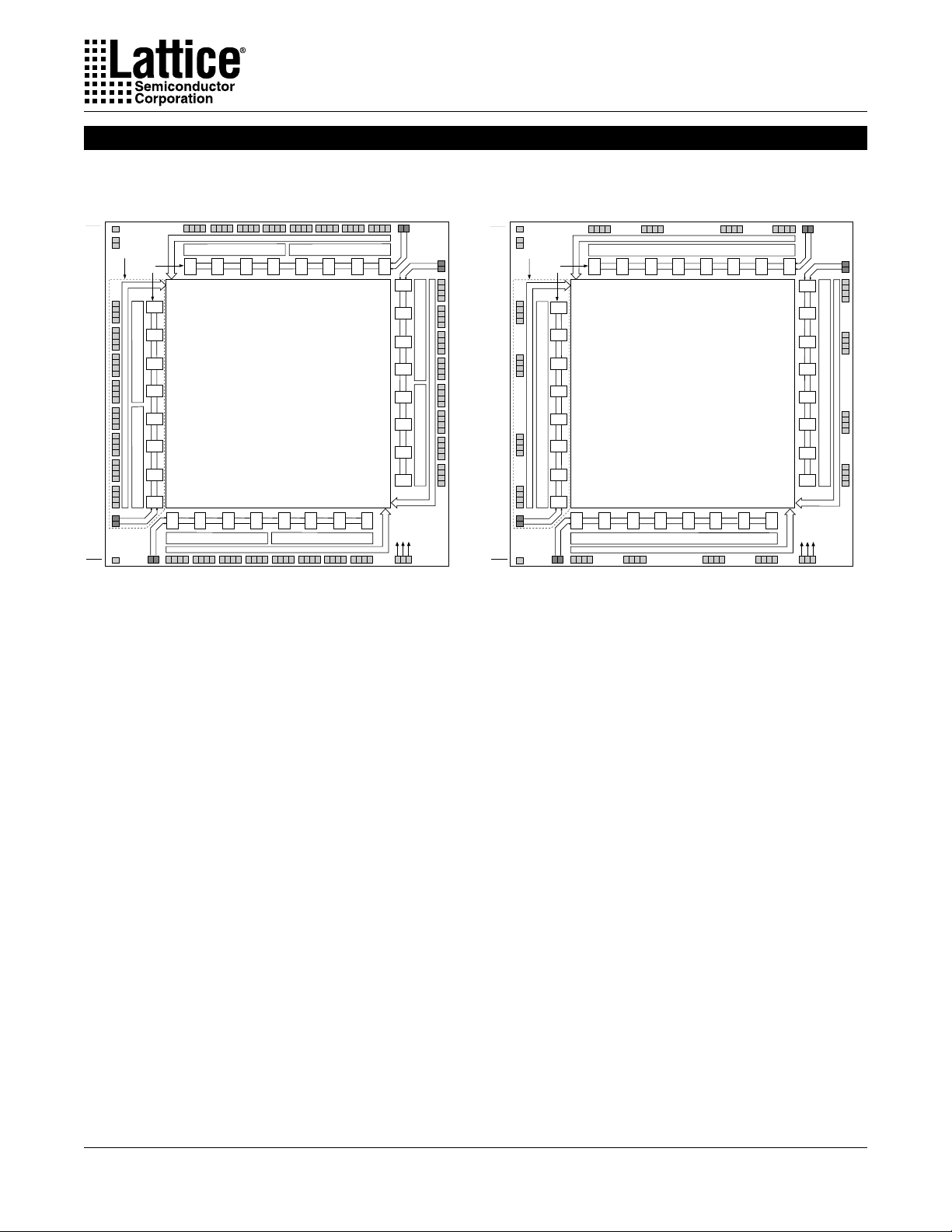

Figure 1. ispLSI 2128VE Functional Block Diagram (128-I/O and 64-I/O Versions)

I/O 127

I/O 126

I/O 125

I/O 124

I/O 123

I/O 122

I/O 121

I/O 120

I/O 119

I/O 118

I/O 117

I/O 116

I/O 115

I/O 114

I/O 113

I/O 112

I/O 111

I/O 110

I/O 109

I/O 108

I/O 107

I/O 106

I/O 105

I/O 104

I/O 103

I/O 102

I/O 101

I/O 100

I/O 99

I/O 98

I/O 97

I/O 96

IN 7

RESET

GOE 0

GOE 1

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

I/O 16

I/O 17

I/O 18

I/O 19

I/O 20

I/O 21

I/O 22

I/O 23

I/O 24

I/O 25

I/O 26

I/O 27

I/O 28

I/O 29

I/O 30

I/O 31

TDI/IN 0

TMS/IN 1

BSCAN

IN 6

I/O 42

I/O 43

Input Bus

D5

D4

Global

Routing

Pool

(GRP)

B3

Input Bus

I/O 44

I/O 45

I/O 46

I/O 47

I/O 48

D2

D3

B5

B4

I/O 49

I/O 50

I/O 51

I/O 52

I/O 53

I/O 54

I/O 55

I/O 56

I/O 57

D0

D1

C7

C6

C5

C4

Input Bus

C3

C2

C1

Output Routing Pool (ORP) Output Routing Pool (ORP)

C0

B7

B6

CLK 0

CLK 1

CLK 2

0139B/2128VE

I/O 60

I/O 61

I/O 62

I/O 63

Y0Y1Y2

I/O 58

I/O 59

Megablock

G

e

n

e

r

c

L

i

o

g

c

i

)

s

(

s

G

L

k

B

o

l

c

B

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

I/O 8

I/O 9

A0

A1

A2

A3

Input Bus

A4

A5

A6

Output Routing Pool (ORP) Output Routing Pool (ORP)

A7

TDO/IN 2

Output Routing Pool (ORP) Output Routing Pool (ORP)

D7

D6

B0

B1

B2

Output Routing Pool (ORP) Output Routing Pool (ORP)

I/O 32

I/O 33

I/O 34

I/O 35

I/O 36

I/O 37

I/O 38

I/O 39

I/O 40

TCK/IN 3

I/O 41

IN 5

IN 4

I/O 95

I/O 94

I/O 93

I/O 92

I/O 91

I/O 90

I/O 89

I/O 88

I/O 87

I/O 86

I/O 85

I/O 84

I/O 83

I/O 82

I/O 81

I/O 80

I/O 79

I/O 78

I/O 77

I/O 76

I/O 75

I/O 74

I/O 73

I/O 72

I/O 71

I/O 70

I/O 69

I/O 68

I/O 67

I/O 66

I/O 65

I/O 64

RESET

GOE 0

GOE 1

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

TDI/IN 0

TMS/IN 1

BSCAN

Megablock

G

e

n

e

r

i

k

o

s

l

c

B

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

Input Bus

I/O 8

I/O 9

Output Routing Pool (ORP)

I/O 63

I/O 62

I/O 61

I/O 60

I/O 59

I/O 58

c

L

o

g

c

i

D7

D6

B1

D5

B2

Output Routing Pool (ORP)

I/O 20

I/O 21

I/O 22

I/O 23

)

(

s

G

L

B

A0

A1

A2

A3

A4

A5

A6

A7

B0

I/O 16

I/O 17

I/O 18

I/O 19

TCK/IN 3

TDO/IN 2

I/O 57

I/O 56

Input Bus

Output Routing Pool (ORP)

D4

D3

Global

Routing

Pool

(GRP)

B3

B4

Input Bus

I/O 24

B5

I/O 25

I/O 26

I/O 55

I/O 27

I/O 54

D2

I/O 53

I/O 52

B6

I/O 51

I/O 50

I/O 49

I/O 48

IN 7*

IN 6*

D0

D1

C7

C6

C5

C4

C3

C2

C1

C0

B7

CLK 0

CLK 1

CLK 2

0139B/2128VE.64IO

Y0Y1Y2

I/O 28

I/O 29

I/O 30

I/O 31

*Not available on 84-PLCC Device

IN 5*

IN 4*

I/O 47

I/O 46

I/O 45

I/O 44

I/O 43

I/O 42

I/O 41

I/O 40

Input Bus

I/O 39

Output Routing Pool (ORP)

I/O 38

I/O 37

I/O 36

I/O 35

I/O 34

I/O 33

I/O 32

The 128-I/O 2128VE contains 128 I/O cells, while the 64I/O version contains 64 I/O cells. Each I/O cell is directly

connected to an I/O pin and can be individually programmed to be a combinatorial input, output or

bi-directional I/O pin with 3-state control. The signal

levels are TTL compatible voltages and the output drivers

can source 4mA or sink 8mA. Each output can be

programmed independently for fast or slow output slew

rate to minimize overall output switching noise. Device

pins can be safely driven to 5V signal levels to support

mixed-voltage systems.

Eight GLBs, 32 or 16 I/O cells, two dedicated inputs and

two or one ORPs are connected together to make a

Megablock (see Figure 1). The outputs of the eight GLBs

are connected to a set of 32 or 16 universal I/O cells by

the two or one ORPs. Each ispLSI 2128VE device

contains four Megablocks.

The GRP has as its inputs, the outputs from all of the

GLBs and all of the inputs from the bi-directional I/O cells.

All of these signals are made available to the inputs of the

GLBs. Delays through the GRP have been equalized to

minimize timing skew.

Y1, Y2) or an asynchronous clock can be selected on a

GLB basis. The asynchronous or Product Term clock

can be generated in any GLB for its own clock.

Programmable Open-Drain Outputs

In addition to the standard output configuration, the

outputs of the ispLSI 2128VE are individually programmable, either as a standard totem-pole output or an

open-drain output. The totem-pole output drives the

specified Voh and Vol levels, whereas the open-drain

output drives only the specified Vol. The Voh level on the

open-drain output depends on the external loading and

pull-up. This output configuration is controlled by a programmable fuse. The default configuration when the

device is in bulk erased state is totem-pole configuration.

The open-drain/totem-pole option is selectable through

the ispDesignEXPERT software tools.

Clocks in the ispLSI 2128VE device are selected using

the dedicated clock pins. Three dedicated clock pins (Y0,

2

Specifications ispLSI 2128VE

Absolute Maximum Ratings

1

Supply Voltage Vcc.................................. -0.5 to +5.4V

Input Voltage Applied............................... -0.5 to +5.6V

Off-State Output Voltage Applied ............ -0.5 to +5.6V

Storage Temperature................................ -65 to 150°C

Case Temp. with Power Applied .............. -55 to 125°C

Max. Junction Temp. (TJ) with Power Applied ... 150°C

1. Stresses above those listed under the “Absolute Maximum Ratings” may cause permanent damage to the device. Functional

operation of the device at these or at any other conditions above those indicated in the operational sections of this specification

is not implied (while programming, follow the programming specifications).

DC Recommended Operating Condition

V

V

V

CC

IL

IH

SYMBOL

Supply Voltage

Input Low Voltage

Input High Voltage

PARAMETER

Commercial

Industrial

TA = 0°C to + 70°C

= -40°C to + 85°C

T

A

MIN. MAX. UNITS

3.0

3.0

V – 0.5

SS

2.0

3.6

3.6

0.8

5.25

Table 2-0005/2128VE

V

V

V

V

Capacitance (TA=25°C, f=1.0 MHz)

SYMBOL

C

1

C

2

C

3

I/O Capacitance

Clock and Global Output Enable Capacitance

PARAMETER

Erase Reprogram Specifications

PARAMETER MINIMUM MAXIMUM UNITS

Erase/Reprogram Cycles

UNITSTYPICAL TEST CONDITIONS

8Dedicated Input Capacitance

6

10

10,000 – Cycles

pf

pf

pf V = 3.3V, V = 0.0V

V = 3.3V, V = 0.0V

CC

V = 3.3V, V = 0.0V

CC I/O

CC Y

IN

Table 2-0006/2128VE

Table 2-0008/2128VE

3

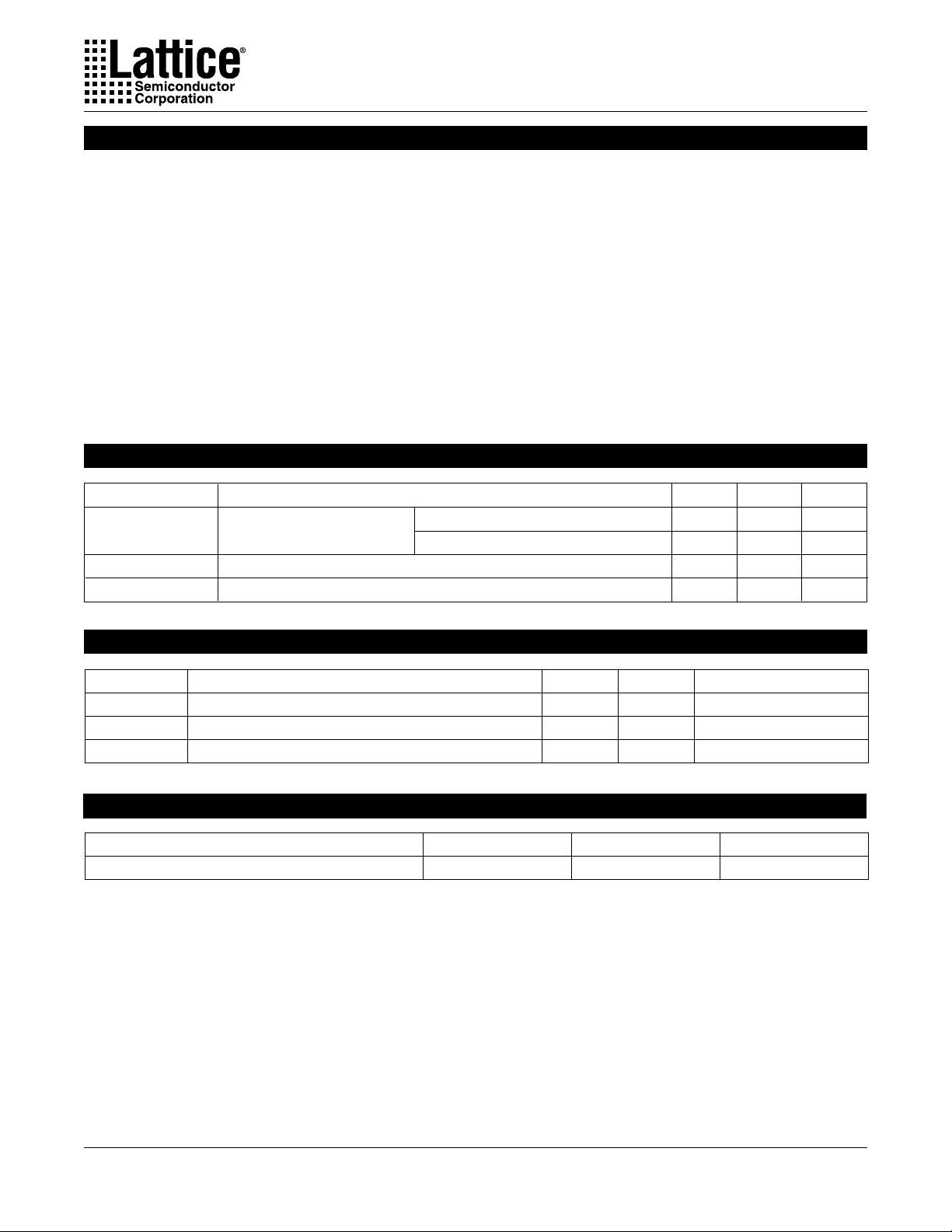

Switching Test Conditions

+ 3.3V

R

1

R

2

C

L

*

Device

Output

Test

Point

*

CL includes Test Fixture and Probe Capacitance.

0213A/2128VE

Specifications ispLSI 2128VE

Input Pulse Levels

Input Rise and Fall Time

Input Timing Reference Levels

Output Timing Reference Levels

Output Load

3-state levels are measured 0.5V from steady-state active level.

GND to 3.0V

≤ 1.5ns 10% to 90%

1.5V

1.5V

See Figure 2

Table 2 - 0003/2128VE

Figure 2. Test Load

Output Load Conditions (see Figure 2)

TEST CONDITION R1 R2 CL

A 316Ω 348Ω 35pF

∞

∞

348Ω 35pF

348Ω 5pF

Table 2-0004/2128VE

Active High

B

Active Low

Active High to Z

at V -0.5V

C

Active Low to Z

at V +0.5V

OH

OL

316Ω 348Ω 35pF

316Ω 348Ω 5pF

DC Electrical Characteristics

Over Recommended Operating Conditions

–

–

–

–

–

–

–

–

195

3

0.4

–

-10

10

10

-150

-150

-100

–

Table 2-0007/2128VE

µA

µA

µA

µA

µA

mA

mA

SYMBOL

V

OL

V

OH

I

IL

I

IH

I

IL-isp

I

IL-PU

I

OS

I

CC

Output Low Voltage

Output High Voltage

Input or I/O Low Leakage Current

Input or I/O High Leakage Current

BSCAN Input Low Leakage Current

I/O Active Pull-Up Current

1

Output Short Circuit Current

2, 4

Operating Power Supply Current

1. One output at a time for a maximum duration of one second. V = 0.5V was selected to avoid test

PARAMETER

CONDITION MIN. TYP. MAX. UNITS

I = 8 mA

OL

I = -4 mA

OH

0V ≤ V ≤ V (Max.)

IN IL

(V - 0.2)V ≤ V ≤ V

CC CC IN

V ≤ V ≤ 5.25V

IN

CC

0V ≤ V ≤ V

IN

IL

0V ≤ V ≤ V

IN IL

V = 3.3V, V = 0.5V

CC OUT

V = 0.0V, V = 3.0V

IL

f = 1 MHz

CLOCK

IH

OUT

–

2.4

–

–

–

–

–

–

–

problems by tester ground degradation. Characterized but not 100% tested.

2. Measured using eight 16-bit counters.

3. Typical values are at V = 3.3V and T = 25°C.

4. Maximum I varies widely with specific device configuration and operating frequency. Refer to the Power Consumption

CC

CC

A

section of this data sheet and Thermal Management section of the Lattice Semiconductor Data Book or CD-ROM to

estimate maximum I .

CC

V

V

4

Specifications ispLSI 2128VE

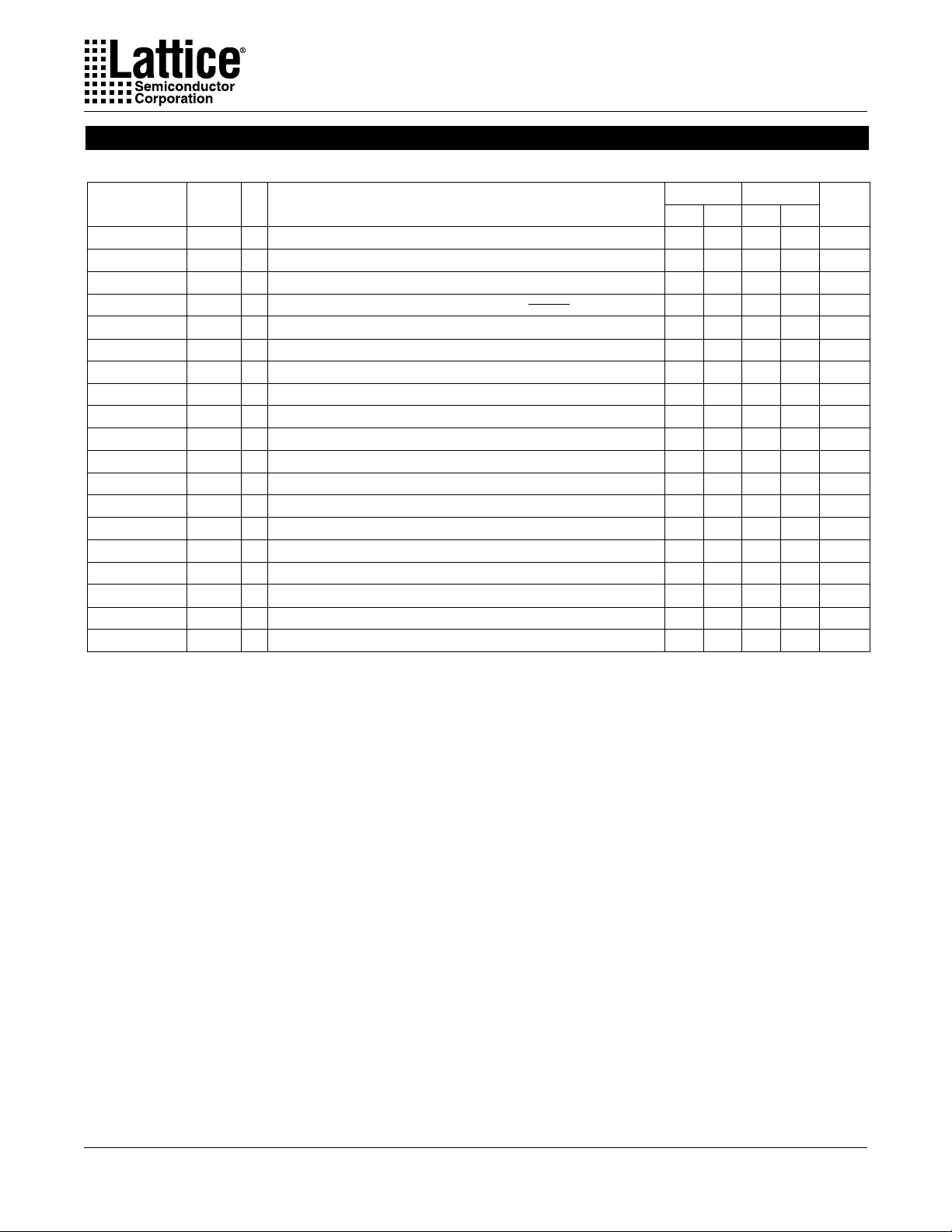

External Timing Parameters

Over Recommended Operating Conditions

3

TEST

COND.

t

pd1

t

pd2

f

max

f

max (Ext.)

f

max (Tog.)

t

su1

t

co1

t

h1

t

su2

t

co2

t

h2

t

r1

t

rw1

t

ptoeen

t

ptoedis

t

goeen

t

goedis

t

wh

t

wl

1. Unless noted otherwise, all parameters use a GRP load of four, 20 PTXOR path, ORP and Y0 clock.

2. Standard 16-bit counter using GRP feedback.

3. Reference Switching Test Conditions section.

A 1 Data Propagation Delay, 4PT Bypass, ORP Bypass ns

A 2 Data Propagation Delay ns

A 3 Clock Frequency with Internal Feedback MHz

— 4 Clock Frequency with External Feedback MHz

— 5 Clock Frequency, Max. Toggle MHz

— 6 GLB Reg. Setup Time before Clock, 4 PT Bypass ns

A 7 GLB Reg. Clock to Output Delay, ORP Bypass ns

— 8 GLB Reg. Hold Time after Clock, 4 PT Bypass ns

— 9 GLB Reg. Setup Time before Clock ns

A 10 GLB Reg. Clock to Output Delay ns

— 11 GLB Reg. Hold Time after Clock ns

A 12 Ext. Reset Pin to Output Delay, ORP Bypass ns

— 13 Ext. Reset Pulse Duration ns

B 14 Input to Output Enable ns

C 15 Input to Output Disable ns

B 16 Global OE Output Enable ns

C 17 Global OE Output Disable ns

— 18 External Synchronous Clock Pulse Duration, High ns

— 19 External Synchronous Clock Pulse Duration, Low ns

DESCRIPTION#PARAMETER

1

2

1

( )

tsu2 + tco1

MIN. MAX.

— 4.0

—

250 —

158.7

275

2.5

—

0.0

3.3

—

0.0

—

3.5

—

—

—

—

1.8 —

1.8 —

-250

6.0

—

—

—

3.0

—

—

3.7

—

6.0

—

6.0

6.0

4.0

4.0

-180

MIN. MAX.

— 5.0

7.5

—

180 —

125

—

200

—

3.5

—

3.5

—

—

0.0

—

4.5

4.5

—

—

0.0

7.0

—

—

4.0

10.0

—

10.0

—

5.0

—

5.0

—

2.5 —

2.5 —

Table 2-0030A/2128VE

UNITS

v.1.0

5

Specifications ispLSI 2128VE

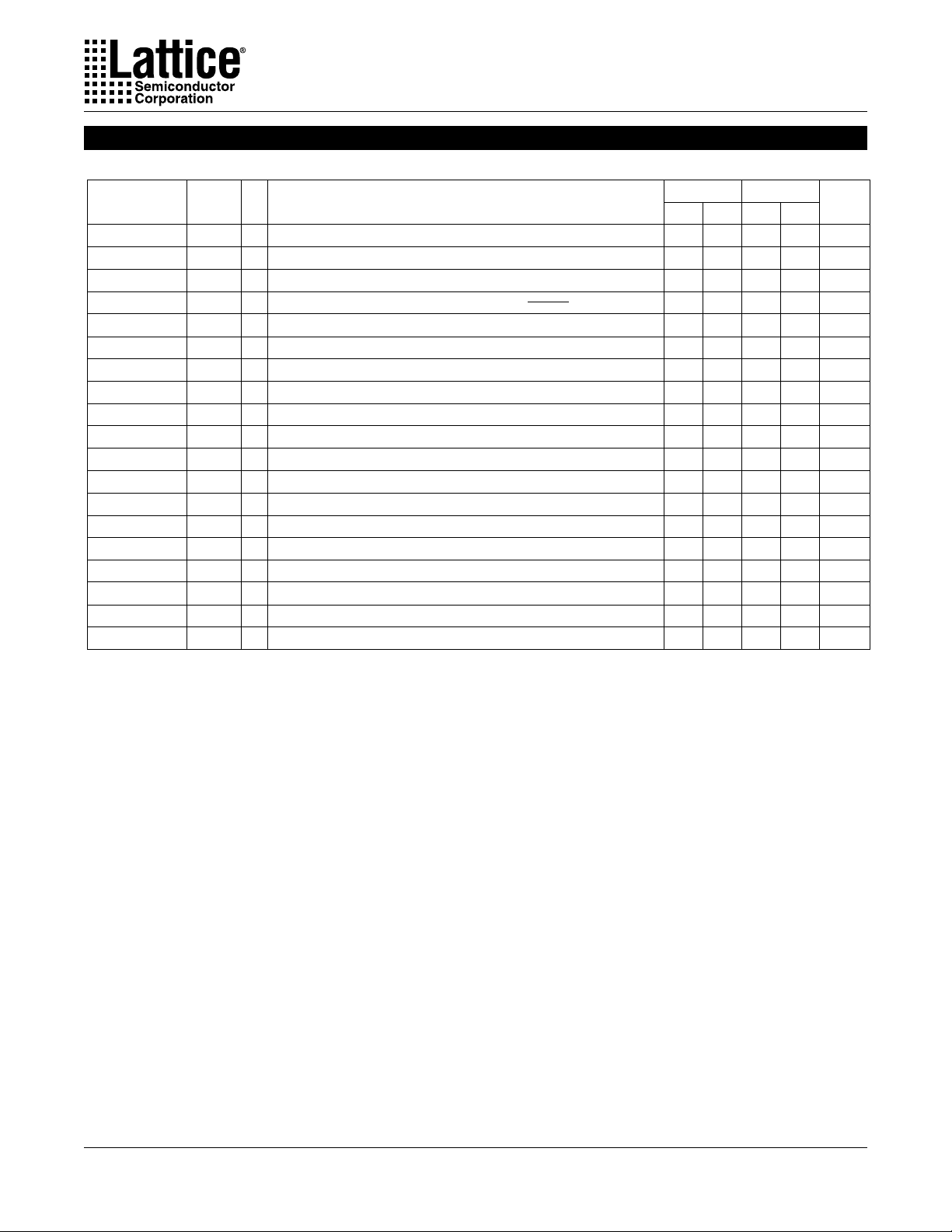

External Timing Parameters

Over Recommended Operating Conditions

3

TEST

COND.

t

pd1

t

pd2

f

max

f

max (Ext.)

f

max (Tog.)

t

su1

t

co1

t

h1

t

su2

t

co2

t

h2

t

r1

t

rw1

t

ptoeen

t

ptoedis

t

goeen

t

goedis

t

wh

t

wl

1. Unless noted otherwise, all parameters use a GRP load of four, 20 PTXOR path, ORP and Y0 clock.

2. Standard 16-bit counter using GRP feedback.

3. Reference Switching Test Conditions section.

A 1 Data Propagation Delay, 4PT Bypass, ORP Bypass ns

A 2 Data Propagation Delay ns

A 3 Clock Frequency with Internal Feedback MHz

— 4 Clock Frequency with External Feedback MHz

— 5 Clock Frequency, Max. Toggle MHz

— 6 GLB Reg. Setup Time before Clock, 4 PT Bypass ns

A 7 GLB Reg. Clock to Output Delay, ORP Bypass ns

— 8 GLB Reg. Hold Time after Clock, 4 PT Bypass ns

— 9 GLB Reg. Setup Time before Clock ns

A 10 GLB Reg. Clock to Output Delay ns

— 11 GLB Reg. Hold Time after Clock ns

A 12 Ext. Reset Pin to Output Delay, ORP Bypass ns

— 13 Ext. Reset Pulse Duration ns

B 14 Input to Output Enable ns

C 15 Input to Output Disable ns

B 16 Global OE Output Enable ns

C 17 Global OE Output Disable ns

— 18 External Synchronous Clock Pulse Duration, High ns

— 19 External Synchronous Clock Pulse Duration, Low ns

DESCRIPTION#PARAMETER

1

2

1

( )

tsu2 + tco1

MIN.

— 7.5 — 10.0

——

135 — 100 —

100

143

5.0

——

0.0 —

6.0 —

——

0.0 —

——

5.0 —

——

——

——

——

3.5 ——

3.5 ——

-135

10.0

4.0

5.0

9.0

12.0

12.0

7.0

7.0

-100

MIN.MAX. MAX.

13.0

77

——

100

——

6.5

——

5.0

0.0

—

8.0

—

6.0

—

0.0

12.5

—

6.5

15.0

15.0

9.0

9.0

5.0

5.0

Table 2-0030B/2128VE

UNITS

v.1.0

6

Loading...

Loading...