Lattice Semiconductor Corporation GAL6002B-20LP, GAL6002B-20LJ, GAL6002B-15LP, GAL6002B-15LJ Datasheet

GAL6002

High Performance E2CMOS FPLA

Generic Array Logic™

Features

• HIGH PERFORMANCE E2CMOS® TECHNOLOGY

— 15ns Maximum Propagation Delay

— 75MHz Maximum Frequency

— 6.5ns Maximum Clock to Output Delay

— TTL Compatible 16mA Outputs

— UltraMOS

®

Advanced CMOS Technology

• ACTIVE PULL-UPS ON ALL PINS

• LOW POWER CMOS

— 90mA Typical Icc

2

CELL TECHNOLOGY

• E

— Reconfigurable Logic

— Reprogrammable Cells

— 100% Tested/100% Y ields

— High Speed Electrical Erasure (<100ms)

— 20 Year Data Retention

• UNPRECEDENTED FUNCTIONAL DENSITY

— 78 x 64 x 36 FPLA Architecture

— 10 Output Logic Macrocells

— 8 Buried Logic Macrocells

— 20 Input and I/O Logic Macrocells

• HIGH-LEVEL DESIGN FLEXIBILITY

— Asynchronous or Synchronous Clocking

— Separate State Register and Input Clock Pins

— Functional Superset of Existing 24-pin PAL

®

and FPLA Devices

• APPLICATIONS INCLUDE:

— Sequencers

— State Machine Control

— Multiple PLD Device Integration

Description

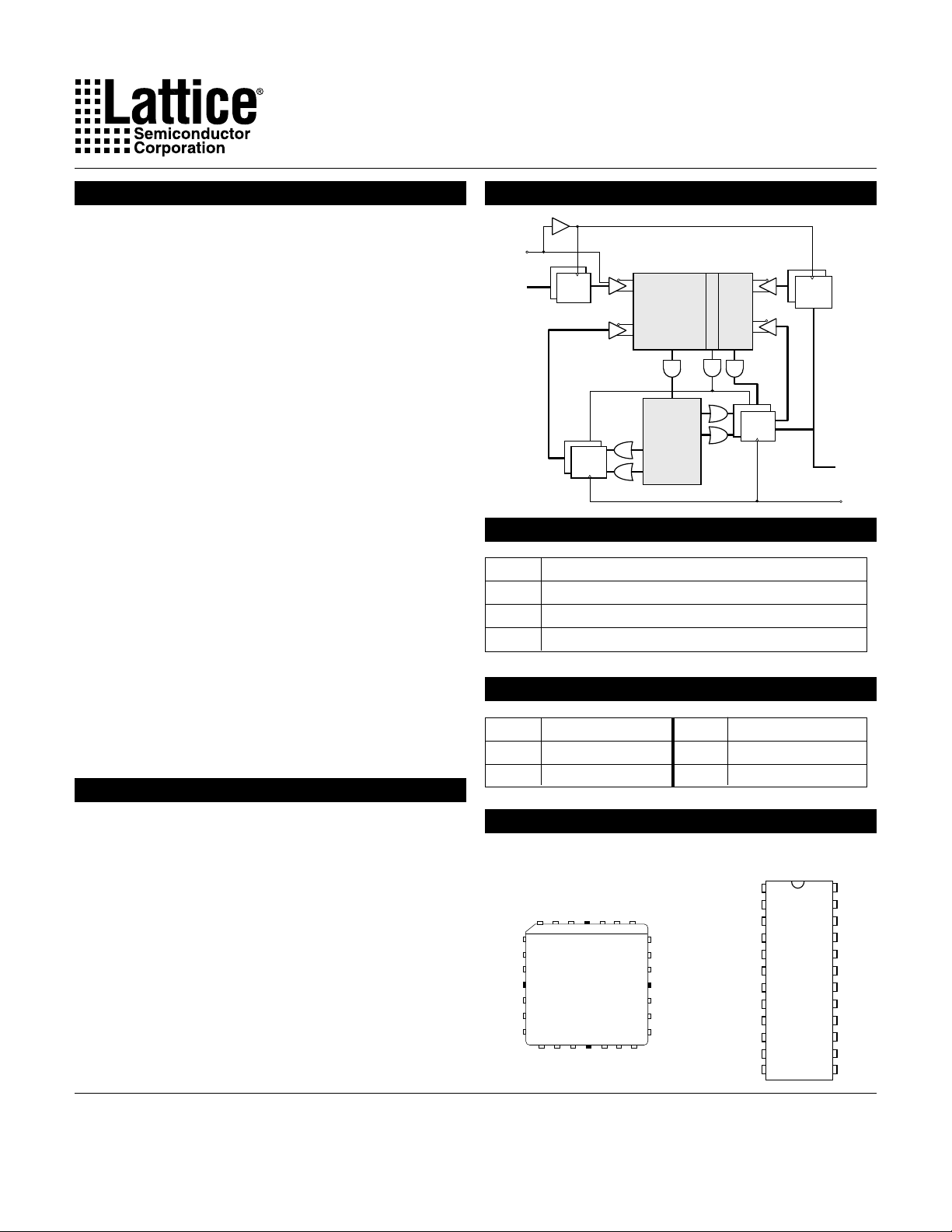

Functional Block Diagram

ICLK

INPUT

CLOCK

INPUTS

2-11

2

11

ILMC

{

OUTPUT

ENABLE

RESET

D

E

14

23

OLMC

OCLK

0

7

BLMC

AND

OR

D

E

Macrocell Names

ILMC INPUT LOGIC MACROCELL

IOLMC I/O LOGIC MACROCELL

BLMC BURIED LOGIC MACROCELL

OLMC OUTPUT LOGIC MACROCELL

PinNames

I0 - I

ICLK INPUT CLOCK V

OCLK OUTPUT CLOCK GND GROUND

INPUT I/O/Q BIDIRECTIONAL

10

POWER (+5V)

CC

14

23

IOLMC

OUTPUTS

{

OUTPUT

14 - 23

CLOCK

Having an FPLA architecture, the GAL6002 provides superior

Pin Configuration

flexibility in state-machine design. The GAL6002 offers the highest

GND

DIP

1

I

I

GAL

I

I

6002

6

I

I

I

I

I

I

12

Vcc

24

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

18

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

OCLK

13

degree of functional integration, flexibility, and speed currently

available in a 24-pin, 300-mil package. E

2

CMOS technology offers

high speed (<100ms) erase times, providing the ability to reprogram

or reconfigure the device quickly and efficiently.

The GAL6002 has 10 programmable Output Logic Macrocells

(OLMC) and 8 programmable Buried Logic Macrocells (BLMC). In

addition, there are 10 Input Logic Macrocells (ILMC) and 10

I/O Logic Macrocells (IOLMC). T wo clock inputs are provided for

independent control of the input and output macrocells.

Unique test circuitry and reprogrammable cells allow complete AC,

DC, and functional testing during manufacturing. As a result, Lattice

I

I

I

NC

I

I

I

Semiconductor delivers 100% field programmability and

functionality of all GAL products. In addition, 100 erase/write cycles

and data retention in excess of 20 years are specified.

Copyright © 1997 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

PLCC

NC

Vcc

I/ICLK

I

I

228

4

5

7

GAL6002

9

Top V iew

11

12 14 16 18

I

I

GND

NC

OCLK

I/O/Q

I/O/Q

I/ICLK

I/O/Q

26

25

I/O/Q

I/O/Q

23

I/O/Q

NC

21

I/O/Q

I/O/Q

19

I/O/Q

I/O/Q

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A. July 1997

Tel. (503) 268-8000; 1-800-LATTICE; FAX (503) 268-8556; http://www.latticesemi.com

6002_02

1

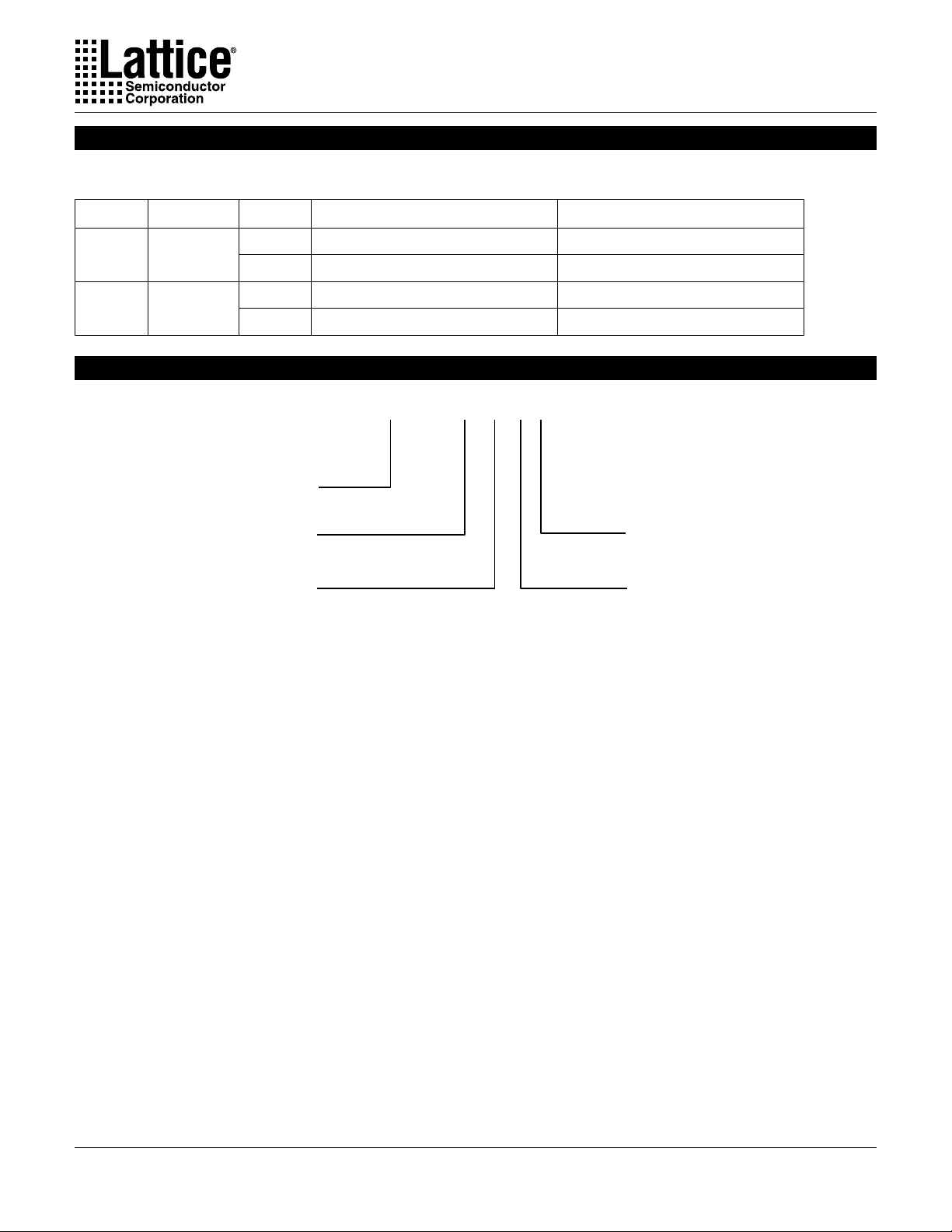

GAL6002 Commercial Device Ordering Information

Commercial Grade Specifications

)sn(dpT)zHM(xamF)Am(ccI#gniredrOegakcaP

5157531PL51-B2006LAGPIDcitsalPniP-42

531JL51-B2006LAGCCLPdaeL-82

0206531PL02-B2006LAGPIDcitsalPniP-42

531JL02-B2006LAGCCLPdaeL-82

Part Number Description

Specifications GAL6002

GAL6002B

Device Name

Speed (ns)

PowerL = Low Power

XXXXXXXX XX X X X

_

Grade

Package

Blank = Commercial

P = Plastic DIP

J = PLCC

2

Specifications GAL6002

Input Logic Macrocell (ILMC) and I/O Logic Macrocell (IOLMC)

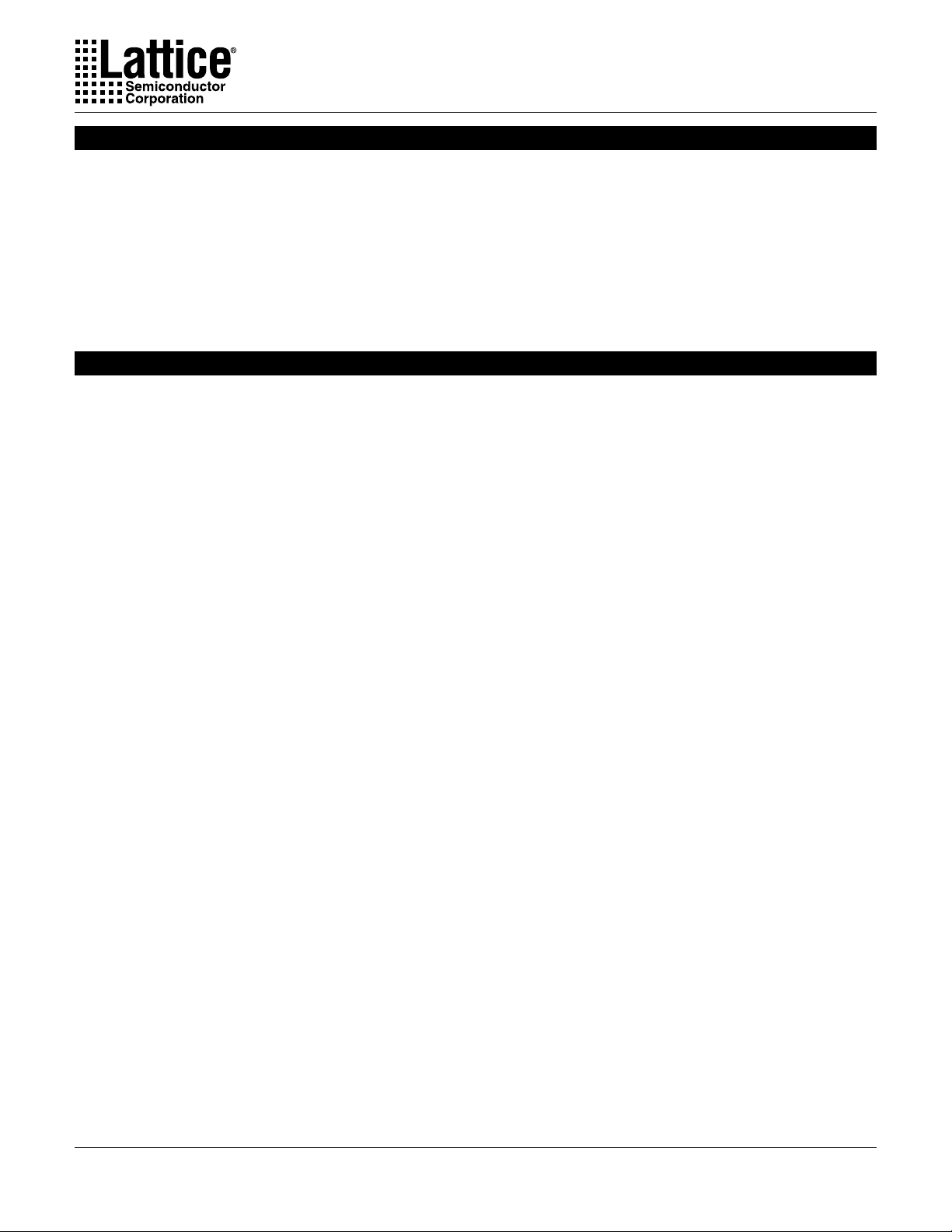

The GAL6002 features two configurable input sections. The ILMC

section corresponds to the dedicated input pins (2-11) and the

IOLMC to the I/O pins (14-23). Each input section is individually

configurable as asynchronous, latched, or registered inputs. Pin

1 (ICLK) is used as an enable input for latched macrocells or as a

clock input for registered macrocells. Individually configurable

inputs provide system designers with unparalleled design flexibility .

With the GAL6002, external input registers and latches are not

necessary.

Both the ILMC and the IOLMC are individually configurable and the

ILMC can be configured independently of the IOLMC. The three

valid macrocell configurations and its associated fuse numbers are

shown in the diagrams on the following pages. Note that these

programmable cells are configured by the logic compiler software.

The user does not need to manually manipulate these architecture

bits.

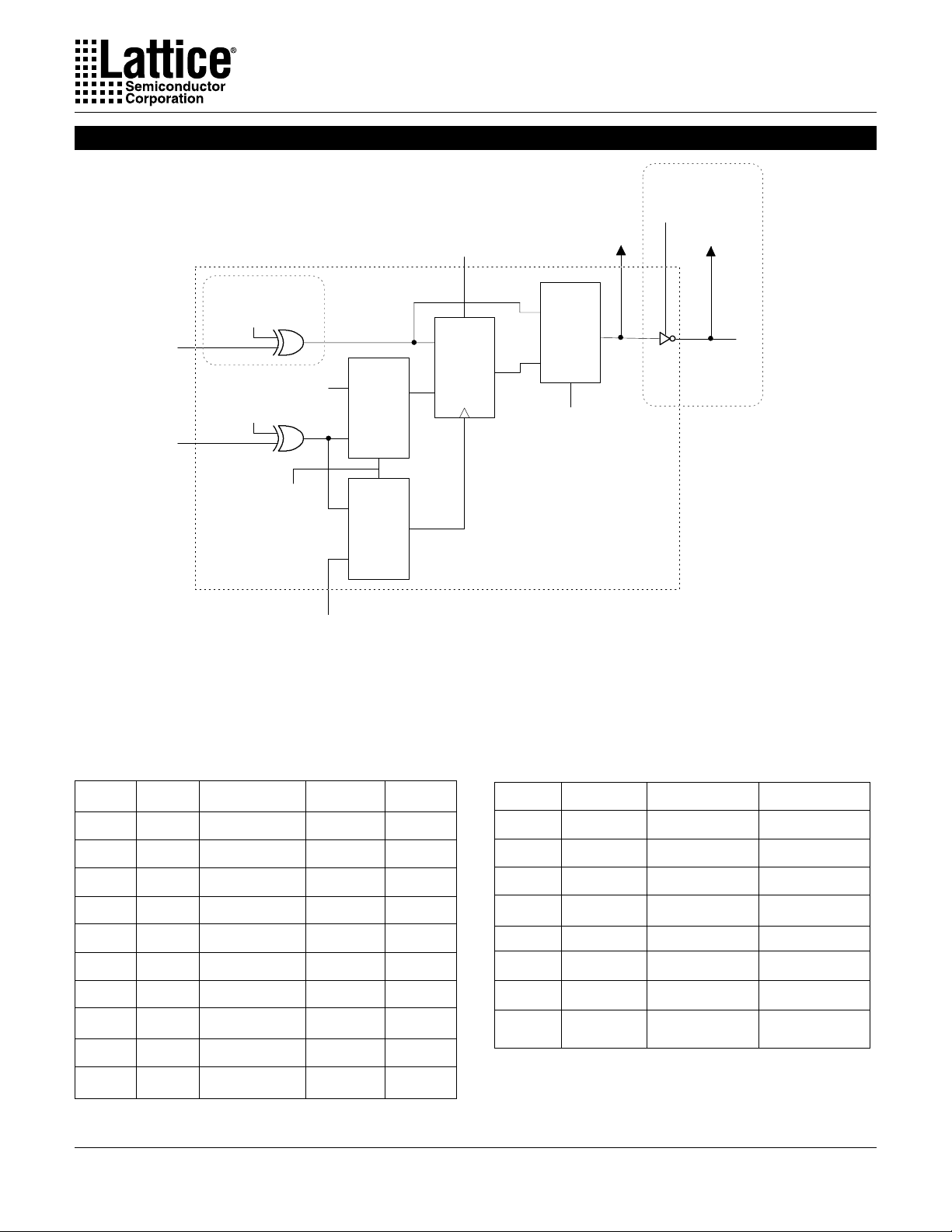

Output Logic Macrocell (OLMC) and Buried Logic Macrocell (BLMC)

The outputs of the OR array feed two groups of macrocells. One

group of eight macrocells is buried; its outputs feed back directly

into the AND array rather than to device pins. These cells are called

the Buried Logic Macrocells (BLMC), and are useful for building

state machines. The second group of macrocells consists of 10

cells whose outputs, in addition to feeding back into the AND array ,

are available at the device pins. Cells in this group are known as

Output Logic Macrocells (OLMC).

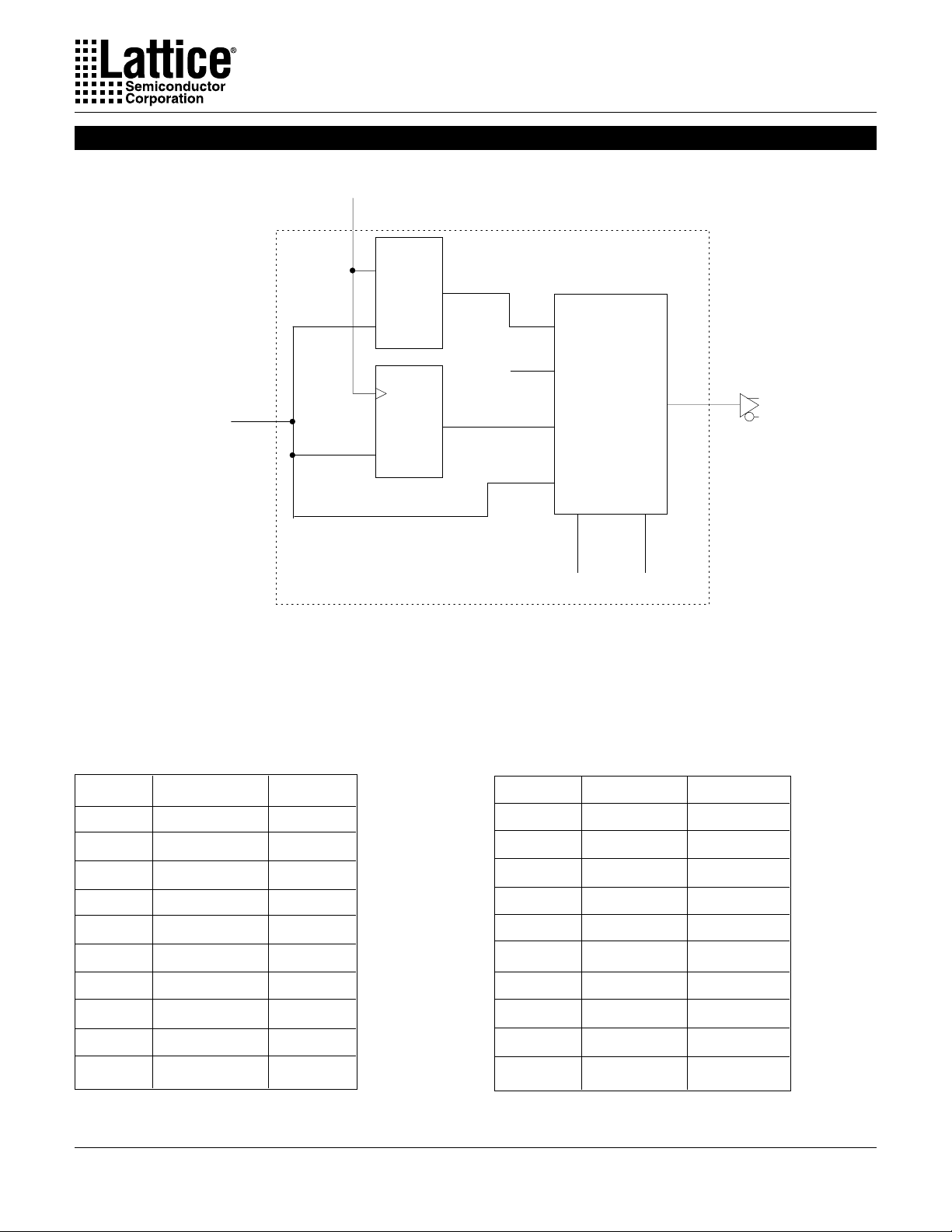

The Output and Buried Logic Macrocells are configurable on a

macrocell by macrocell basis. Buried and Output Logic Macrocells

may be set to one of three configurations: combinational, D-type

register with sum term (asynchronous) clock, or D/E-type register.

Output macrocells always have I/O capability, with directional control

provided by the 10 output enable (OE) product terms. Additionally,

the polarity of each OLMC output is selected through the

programmable polarity control cell called XORD. Polarity selection

for BLMCs is selected through the true and complement forms of

their feedbacks to the AND array. Polarity of all E (Enable) sum

terms is selected through the XORE programmable cells.

When the output or buried logic macrocell is configured as a

D/E type register, the register is clocked from the common OCLK

and the register clock enable input is controlled by the associated

"E" sum term. This configuration is useful for building counters and

state-machines with count hold and state hold functions.

When the macrocell is configured as a D type register with a sum

term clock, the register is always enabled and the associated “E”

sum term is routed directly to the clock input. This permits

asynchronous programmable clocking, selected on a register-byregister basis.

Registers in both the Output and Buried Logic Macrocells feature

a common RESET product term. This active high product term

allows the registers to be asynchronously reset. All registers reset

to logic zero. With the inverting output buffers, the output pins will

reset to logic one.

There are two possible feedback paths from each OLMC. The first

path is directly from the OLMC (this feedback is before the output

buffer). When the OLMC is used as an output, the second feedback

path is through the IOLMC. With this dual feedback arrangement,

the OLMC can be permanently buried without losing the use of the

associated OLMC pin as an input, or dynamically buried with the

use of the output enable product term.

The D/E registers used in this device offer the designer the ultimate

in flexibility and utility. The D/E register architecture can emulate

RS, JK, and T registers with the same efficiency as a dedicated RS,

JK, or T registers.

The three macrocell configurations are shown in the diagrams on

the following pages. These programmable cells are also configured

by the logic compiler software. The user does not need to manually

manipulate these architecture bits.

3

Y

ILMC and IOLMC Configurations

ICLK

LATCH

E

D

Specifications GAL6002

Q

MUX

0 0

REG.

INPUT

or I/O

D

Generic Logic Block Diagram

Input Macrocell JEDEC Fuse Numbers

INSYNC INLATCH ILMC

INVALID

Q

ILMC/IOLMC

I/O Macrocell JEDEC Fuse Numbers

IOSYNC IOLATCH IOLMC

0 1

1 0

1 1

LATCH(i)

AND

ARRA

ISYN(i)

8218 8219 0

8220 8221 1

8222 8223 2

8224 8225 3

8226 8227 4

8228 8229 5

8230 8231 6

8232 8233 7

8234 8235 8

8236 8237 9

8238 8239 9

8240 8241 8

8242 8243 7

8244 8245 6

8246 8247 5

8248 8249 4

8250 8251 3

8252 8253 2

8254 8255 1

8256 8257 0

4

OLMC and BLMC Configurations

RESET

Specifications GAL6002

OE

PRODUCT

TERM

AND

ARRAY

IOLMC

D

E

OLMC ONLY

XORD(i)

XORE(i)

CKS(i)

Vcc

OCLK

R

D

MUX

0

Q

E

1

MUX

0

1

OLMC/BLMC

Generic Logic Block Diagram

MUX

1

I/O

0

OLMC ONLY

OSYN(i)

OLMC JEDEC Fuse Numbers

OLMC CKS OUTSYNC XORE XORD

0 8178 8179 8180 8181

1 8182 8183 8184 8185

2 8186 8187 8188 8189

3 8190 8191 8192 8193

4 8194 8195 8196 8197

5 8198 8199 8200 8201

6 8202 8203 8204 8205

7 8206 8207 8208 8209

8 8210 8211 8212 8213

9 8214 8215 8216 8217

BLMC JEDEC Fuse Numbers

BLMC CKS OUTSYNC XORE

7 8175 8176 8177

6 8172 8173 8174

5 8169 8170 8171

4 8166 8167 8168

3 8163 8164 8165

2 8160 8161 8162

1 8157 8158 8159

0 8154 8155 8156

5

Loading...

Loading...