Lattice Semiconductor Corporation GAL18V10B-7LJ, GAL18V10B-20LP, GAL18V10B-20LJ, GAL18V10B-15LP, GAL18V10B-15LJ Datasheet

...

GAL18V10

High Performance E2CMOS PLD

Generic Array Logic™

Features

• HIGH PERFORMANCE E2CMOS® TECHNOLOGY

— 7.5 ns Maximum Propagation Delay

— Fmax = 11 1 MHz

— 5.5 ns Maximum from Clock Input to Data Output

— TTL Compatible 16 mA Outputs

— UltraMOS

®

Advanced CMOS Technology

• LOW POWER CMOS

— 75 mA T ypical Icc

• ACTIVE PULL-UPS ON ALL PINS

2

CELL TECHNOLOGY

• E

— Reconfigurable Logic

— Reprogrammable Cells

— 100% Tested/100% Yields

— High Speed Electrical Erasure (<100ms)

— 20 Year Data Retention

• TEN OUTPUT LOGIC MACROCELLS

— Uses Standard 22V10 Macrocell Architecture

— Maximum Flexibility for Complex Logic Designs

• PRELOAD AND POWER-ON RESET OF REGISTERS

— 100% Functional Testability

• APPLICATIONS INCLUDE:

— DMA Control

— State Machine Control

— High Speed Graphics Processing

— Standard Logic Speed Upgrade

• ELECTRONIC SIGNA TURE FOR IDENTIFICATION

Description

The GAL18V10, at 7.5 ns maximum propagation delay time, combines a high performance CMOS process with Electrically Erasable (E2) floating gate technology to provide a very flexible 20-pin

PLD. CMOS circuitry allows the GAL18V10 to consume much less

power when compared to its bipolar counterparts. The E2 technology offers high speed (<100ms) erase times, providing the ability

to reprogram or reconfigure the device quickly and efficiently .

By building on the popular 22V10 architecture, the GAL18V10

eliminates the learning curve usually associated with using a new

device architecture. The generic architecture provides maximum

design flexibility by allowing the Output Logic Macrocell (OLMC)

to be configured by the user. The GAL18V10 OLMC is fully compatible with the OLMC in standard bipolar and CMOS 22V10 devices.

Unique test circuitry and reprogrammable cells allow complete AC,

DC, and functional testing during manufacture. As a result, Lattice

Semiconductor delivers 100% field programmability and functionality of all GAL products. In addition, 100 erase/write cycles and

data retention in excess of 20 years are specified.

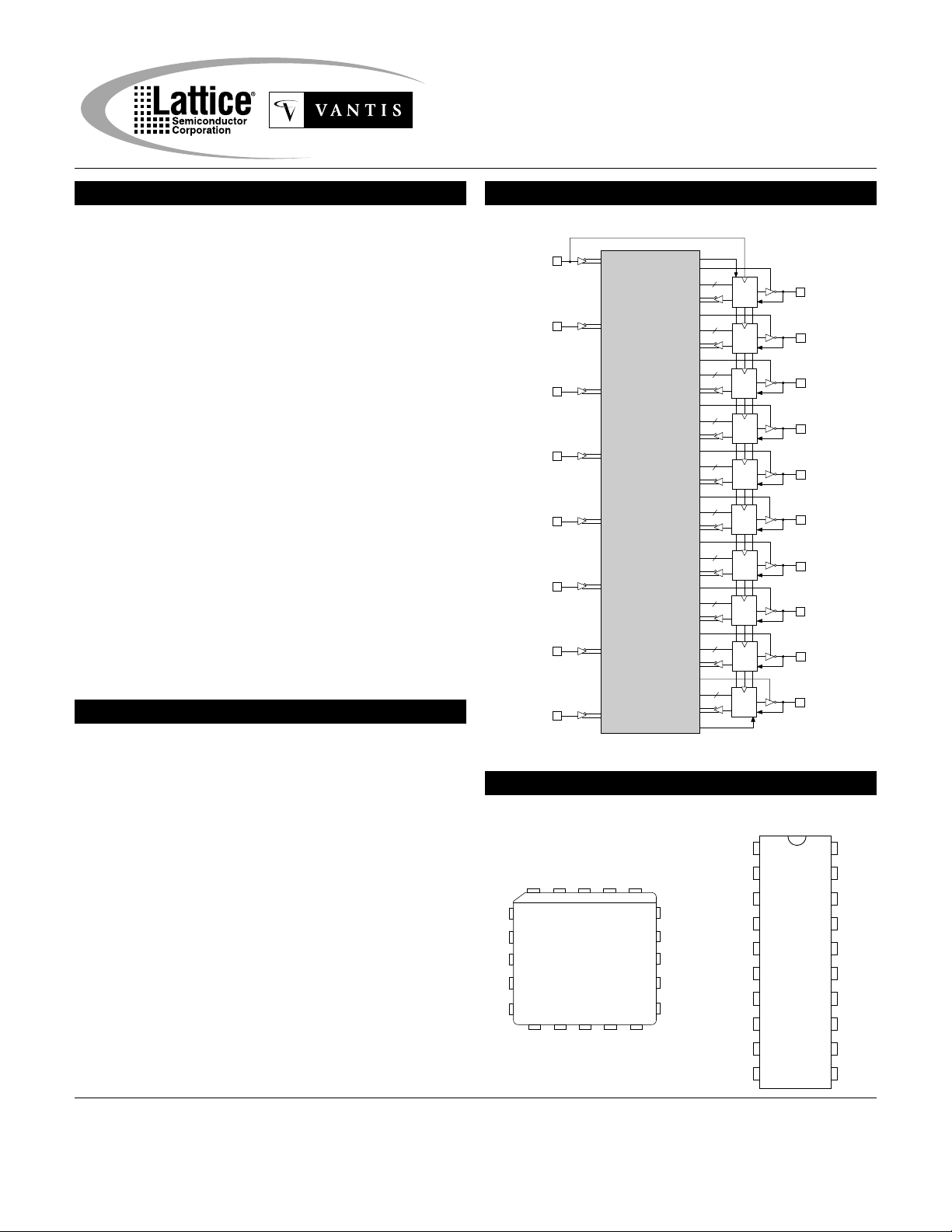

Functional Block Diagram

I/CLK

I

I

I

I

AND-ARRAY

RESET

8

8

8

10

10

(96X36)

8

PROGRAMMABLE

I

I

I

8

8

PRESET

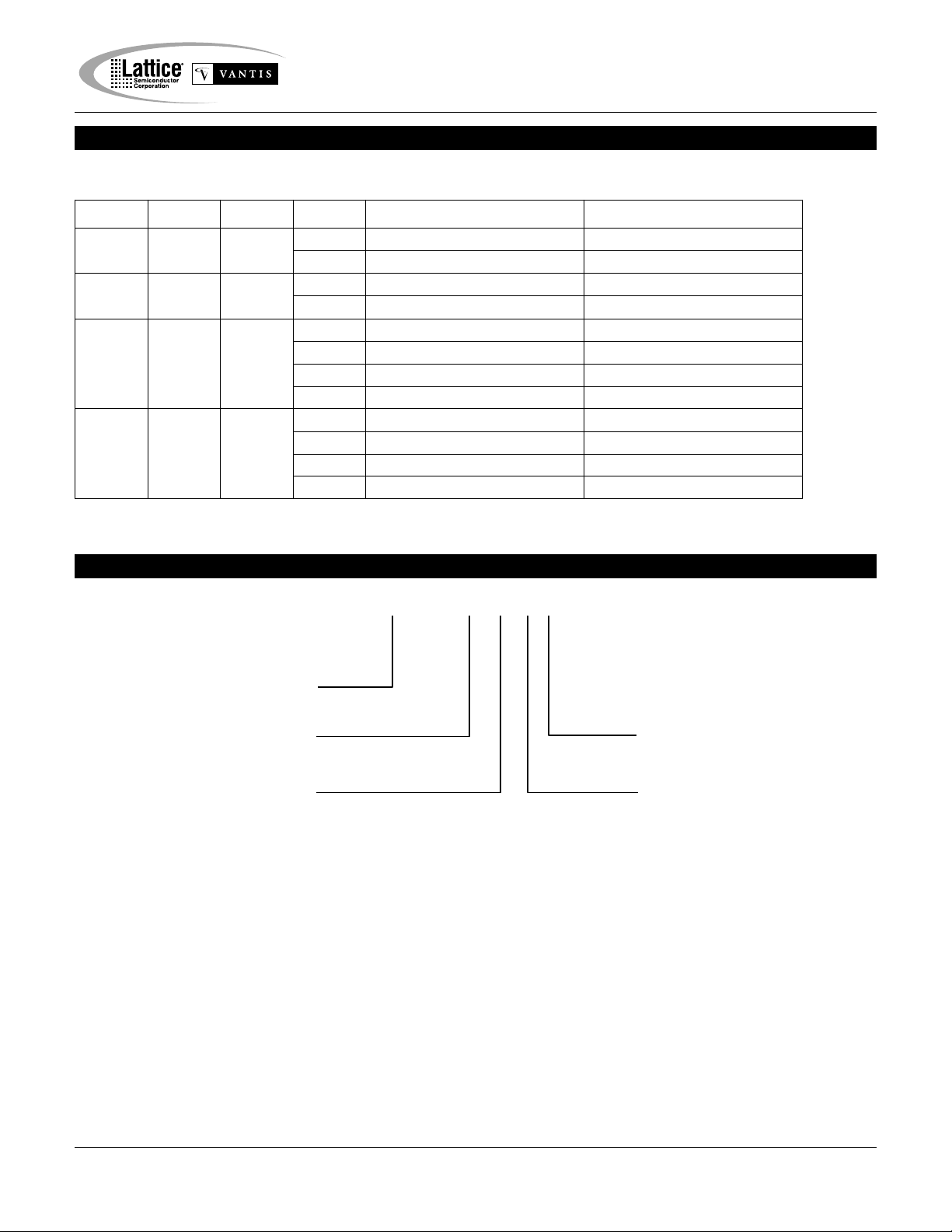

Pin Configuration

PLCC

I/CLKI

2

T op View

11

Vcc

I/O/Q

20

18

I/O/Q

I/O/Q

I/O/Q

16

I/O/Q

I/O/Q

14

13

I

4

I

I

I

I

I

GAL18V10

6

8

9

GND I/O/Q I/O/QI/O/Q I/O/Q

8

8

I/CLK

I/O/Q

GND

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

I

I

I

I

I

I

I

DIP

1

GAL

18V10

5

10

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

20

15

11

Vcc

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

Copyright © 1997 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A. July 1997

Tel. (503) 681-0118; 1-888-ISP-PLDS; FAX (503) 681-3037; http://www.latticesemi.com

18v10_03

1

GAL18V10 Ordering Information

Commercial Grade Specifications

)sn(dpT)sn(usT)sn(ocT)Am(ccI#gniredrOegakcaP

5.765.5511

511

0177 511

511

51801511

511

511PL51-01V81LAGPIDcitsalPniP-02

511JL51-01V81LAGCCLPdaeL-02

022121511

511

511PL02-01V81LAGPIDcitsalPniP-02

511JL02-01V81LAGCCLPdaeL-02

01V81LAG B-7 PL

01V81LAG B-7 JL

01V81LAGB1-0PL

01V81LAGB1-0JL

01V81LAGBPL5101V81LAGBJL51-

01V81LAGBPL0201V81LAGBJL02-

Specifications GAL18V10

PIDcitsalPniP-02

CCLPdaeL-02

PIDcitsalPniP-02

CCLPdaeL-02

PIDcitsalPniP-02

CCLPdaeL-02

PIDcitsalPniP-02

CCLPdaeL-02

Part Number Description

GAL18V10B

GAL18V10

Device Name

Speed (ns)

PowerL = Low Power

XXXXXXXX XX X X X

_

Grade

Package

Blank = Commercial

P = Plastic DIP

J = PLCC

2

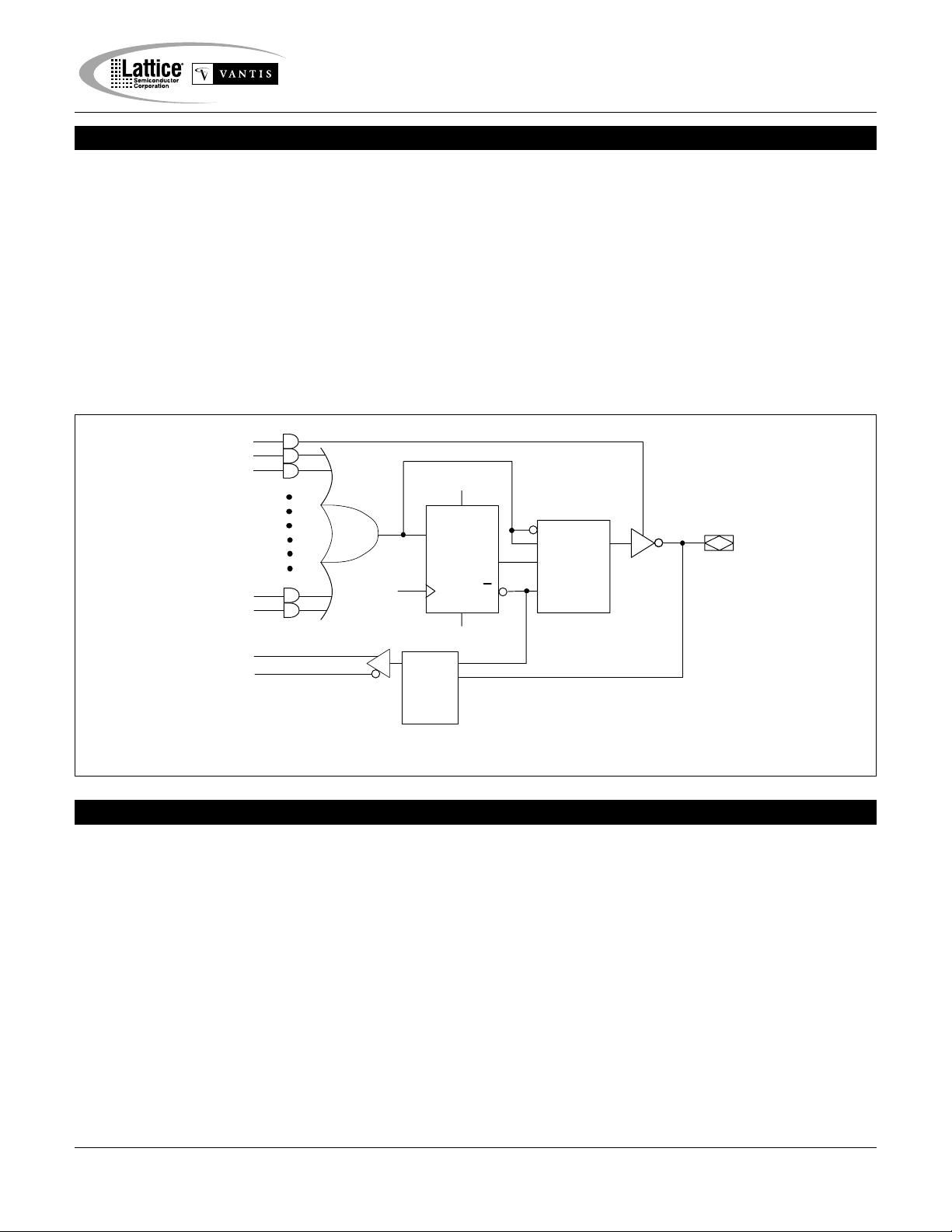

Output Logic Macrocell (OLMC)

Specifications GAL18V10

The GAL18V10 has a variable number of product terms per OLMC.

Of the ten available OLMCs, two OLMCs have access to ten product terms (pins 14 and 15), and the other eight OLMCs have eight

product terms each. In addition to the product terms available for

logic, each OLMC has an additional product-term dedicated to output enable control.

The output polarity of each OLMC can be individually programmed

to be true or inverting, in either combinatorial or registered mode.

This allows each output to be individually configured as either active

high or active low.

AR

D

The GAL18V10 has a product term for Asynchronous Reset (AR)

and a product term for Synchronous Preset (SP). These two product terms are common to all registered OLMCs. The Asynchronous

Reset sets all registered outputs to zero any time this dedicated

product term is asserted. The Synchronous Preset sets all registers

to a logic one on the rising edge of the next clock pulse after this

product term is asserted.

NOTE: The AR and SP product terms will force the Q output of the

flip-flop into the same state regardless of the polarity of the output.

Therefore, a reset operation, which sets the register output to a zero,

may result in either a high or low at the output pin, depending on

the pin polarity chosen.

Q

QCLK

4 TO 1

MUX

SP

2 TO 1

MUX

GAL18V10 OUTPUT LOGIC MACROCELL (OLMC)

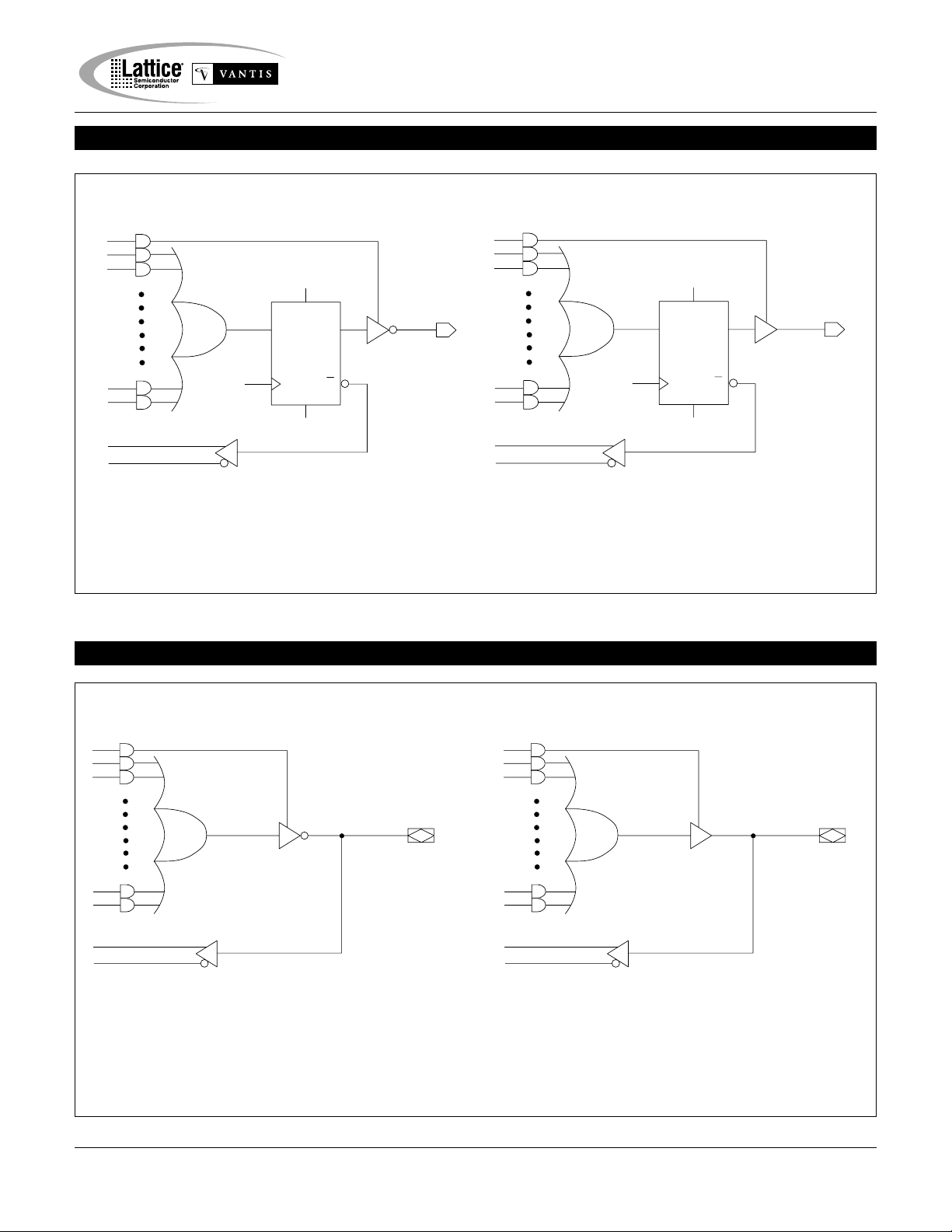

Output Logic Macrocell Configurations

Each of the Macrocells of the GAL18V10 has two primary functional

modes: registered, and combinatorial I/O. The modes and the

output polarity are set by two bits (SO and S1), which are normally

controlled by the logic compiler. Each of these two primary modes,

and the bit settings required to enable them, are described below

and on the the following page.

REGISTERED

In registered mode the output pin associated with an individual

OLMC is driven by the Q output of that OLMC’s D-type flip-flop.

Logic polarity of the output signal at the pin may be selected by

specifying that the output buffer drive either true (active high) or

inverted (active low). Output tri-state control is available as an individual product term for each OLMC, and can therefore be defined

by a logic equation. The D flip-flop’s /Q output is fed back into the

AND array, with both the true and complement of the feedback

available as inputs to the AND array.

NOTE: In registered mode, the feedback is from the /Q output of

the register, and not from the pin; therefore, a pin defined as registered is an output only , and cannot be used for dynamic

I/O, as can the combinatorial pins.

COMBINAT ORIAL I/O

In combinatorial mode the pin associated with an individual OLMC

is driven by the output of the sum term gate. Logic polarity of the

output signal at the pin may be selected by specifying that the output

buffer drive either true (active high) or inverted (active low). Output tri-state control is available as an individual product-term for

each output, and may be individually set by the compiler as either

“on” (dedicated output), “off” (dedicated input), or “product-term

driven” (dynamic I/O). Feedback into the AND array is from the pin

side of the output enable buffer . Both polarities (true and inverted)

of the pin are fed back into the AND array.

3

Registered Mode

Specifications GAL18V10

CLK

S0 = 0

S1 = 0

Combinatorial Mode

AR

D

SP

Q

Q

S0 = 1

S1 = 0

CLK

AR

D

ACTIVE HIGHACTIVE LOW

Q

Q

SP

S0 = 0

S1 = 1

ACTIVE HIGHACTIVE LOW

S0 = 1

S1 = 1

4

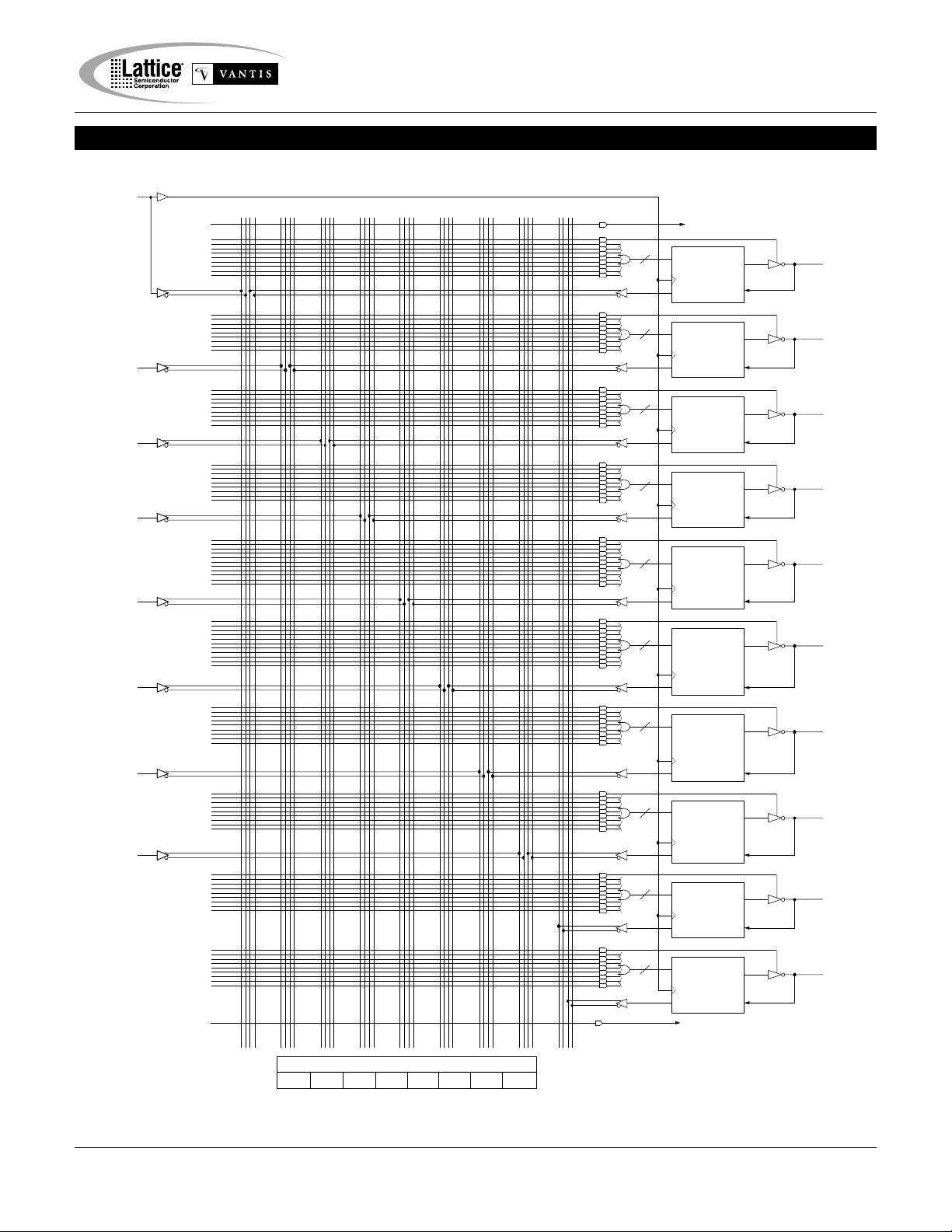

GAL18V10 Logic Diagram/JEDEC Fuse Map

DIP and PLCC Package Pinouts

1

0000

0036

0324

0360

0648

2

0684

0972

3

1008

1296

4

1332

1692

5

1728

2088

6

2124

2412

7

2448

2736

8

2772

3060

3096

3384

3420

0 4 8 12 16 20 24 28 32

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

L

S

B

Electronic Signature

3476, 3477 ...

Byte 7 Byte 6 Byte 5 Byte 4 Byte 3 Byte 2 Byte 1 Byte 0

M

S

B

... 3538, 3539

Specifications GAL18V10

ASYNCHRONOUS RESET

(TO ALL REGISTERS)

8

8

8

8

10

10

8

8

8

8

OLMC

S0

3456

S1

3457

OLMC

S0

3458

S1

3459

OLMC

SO

3460

S1

3461

OLMC

S0

3462

S1

3463

OLMC

S0

3464

S1

3465

OLMC

S0

3466

S1

3467

OLMC

S0

3468

S1

3469

OLMC

S0

3470

S1

3471

OLMC

S0

3472

S1

3473

OLMC

S0

3474

S1

3475

SYNCHRONOUS PRESET

(TO ALL REGISTERS)

19

18

17

16

15

14

13

12

11

9

5

Loading...

Loading...