Lattice Semiconductor Corporation GAL16V8ZD-15QJ, GAL16V8ZD-12QP, GAL16V8ZD-12QJ, GAL16V8Z-15QS, GAL16V8Z-15QP Datasheet

...

GAL16V8Z

GAL16V8ZD

Zero Power E2CMOS PLD

Features

• ZERO POWER E2CMOS TECHNOLOGY

• HIGH PERFORMANCE E

•E

• EIGHT OUTPUT LOGIC MACROCELLS

• PRELOAD AND POWER-ON RESET OF ALL REGISTERS

• APPLICATIONS INCLUDE:

• ELECTRONIC SIGNA TURE FOR IDENTIFICATION

µA Standby Current

— 100

— Input Transition Detection on GAL16V8Z

— Dedicated Power-down Pin on GAL16V8ZD

— Input and Output Latching During Power Down

2

CMOS TECHNOLOGY

— 12 ns Maximum Propagation Delay

— Fmax = 83.3 MHz

— 8 ns Maximum from Clock Input to Data Output

— TTL Compatible 16 mA Output Drive

— UltraMOS

2

CELL TECHNOLOGY

®

Advanced CMOS Technology

— Reconfigurable Logic

— Reprogrammable Cells

— 100% Tested/100% Y ields

— High Speed Electrical Erasure (<100ms)

— 20 Year Data Retention

— Maximum Flexibility for Complex Logic Designs

— Programmable Output Polarity

— Architecturally Similar to Standard GAL16V8

— 100% Functional Testability

— Battery Powered Systems

— DMA Control

— State Machine Control

— High Speed Graphics Processing

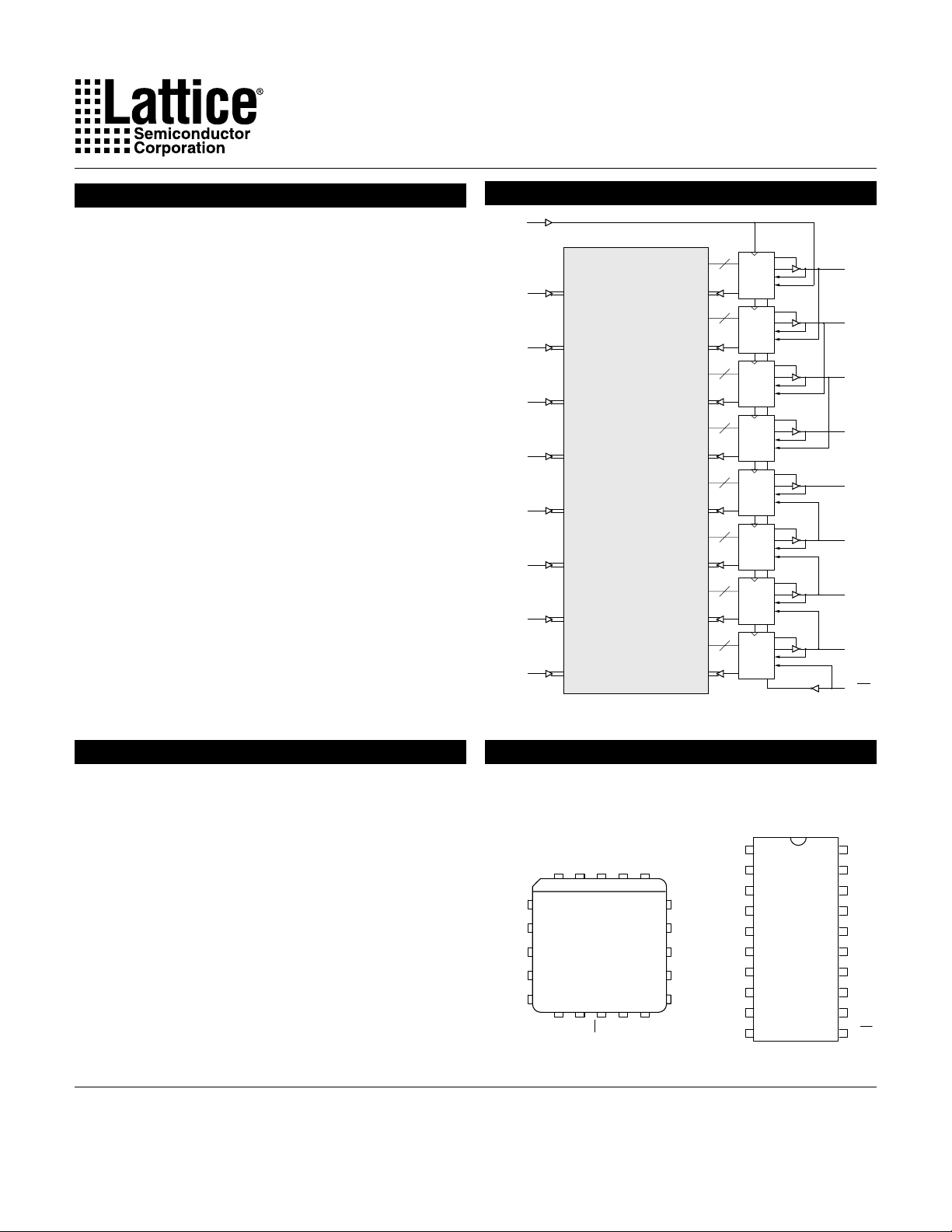

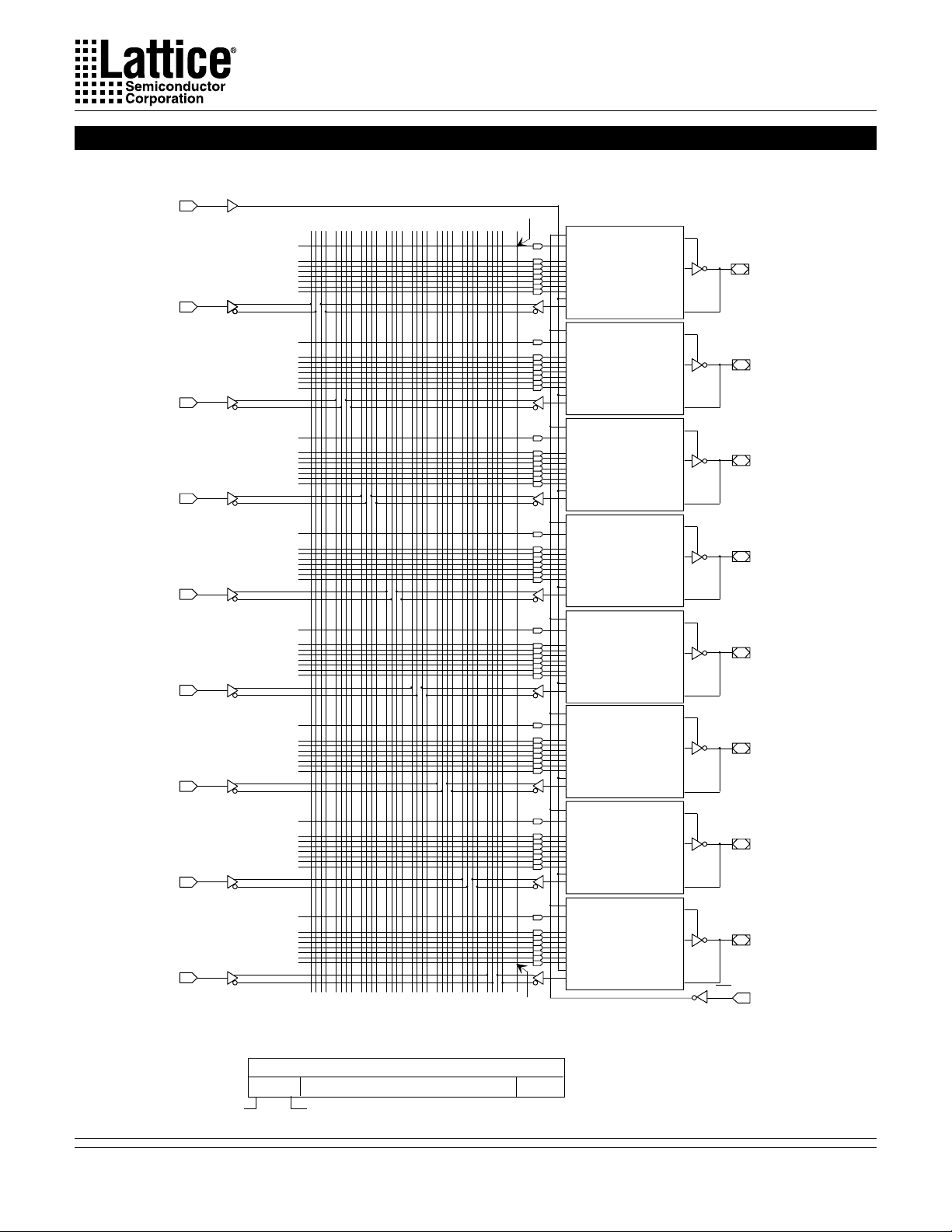

Functional Block Diagram

I/CLK

I

I

I/DPP

I

I

(64 X 32)

AND-ARRAY

I

I

I

PROGRAMMABLE

8

8

8

8

8

8

8

8

CLK

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

OE

I/OE

Description

The GAL16V8Z and GAL16V8ZD, at 100 µA standby current and

12ns propagation delay provides the highest speed and lowest

DESCRIPTION

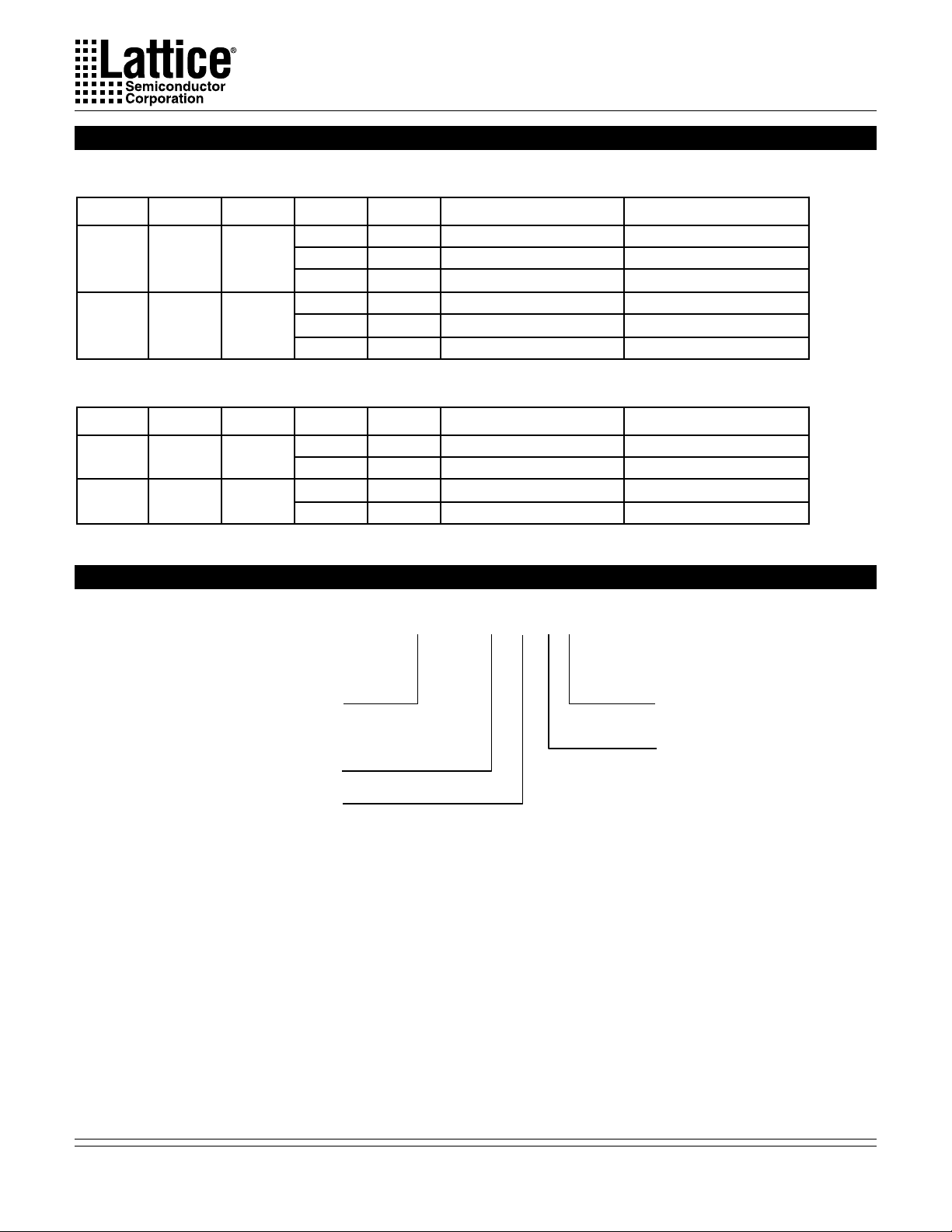

Pin Configuration

DIP/SOIC

power combination PLD available in the market. The GAL16V8Z/

ZD is manufactured using Lattice Semiconductor's advanced zero

power E

2

CMOS process, which combines CMOS with Electrically

Erasable (E2) floating gate technology .

The GAL16V8Z uses Input Transition Detection (ITD) to put the

device in standby mode and is capable of emulating the full functionality of the standard GAL16V8. The GAL16V8ZD utilizes a

dedicated power-down pin (DPP) to put the device in standby mode.

It has 15 inputs available to the AND array.

Unique test circuitry and reprogrammable cells allow complete AC,

DC, and functional testing during manufacture. As a result,

I/DPP

I

I

I

I

Lattice Semiconductor delivers 100% field programmability and

functionality of all GAL products. In addition, 100 erase/write cycles

and data retention in excess of 20 years are specified.

Copyright © 1997 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A. December 1997

Tel. (503) 268-8000; 1-800-LATTICE; FAX (503) 268-8556; http://www.latticesemi.com

16v8zzd_03

1

PLCC

I

3

4

GAL16V8Z

GAL16V8ZD

6

Top V iew

8

9

I

GND

11

I/CLK

120

I/CLKI

I/O/Q

Vcc

19

1

18

I/O/Q

I/O/Q

16

I/O/Q

I/O/Q

I/O/Q

14

13

I/OE

I/O/Q

I/O/Q

2

I

GAL

I

3

I/DPP

GND

16V8Z

4

16V8ZD

I

5

I

6

I

7

I

8

I

912

10 11

19

18

17

16

15

14

13

Vcc

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/OE

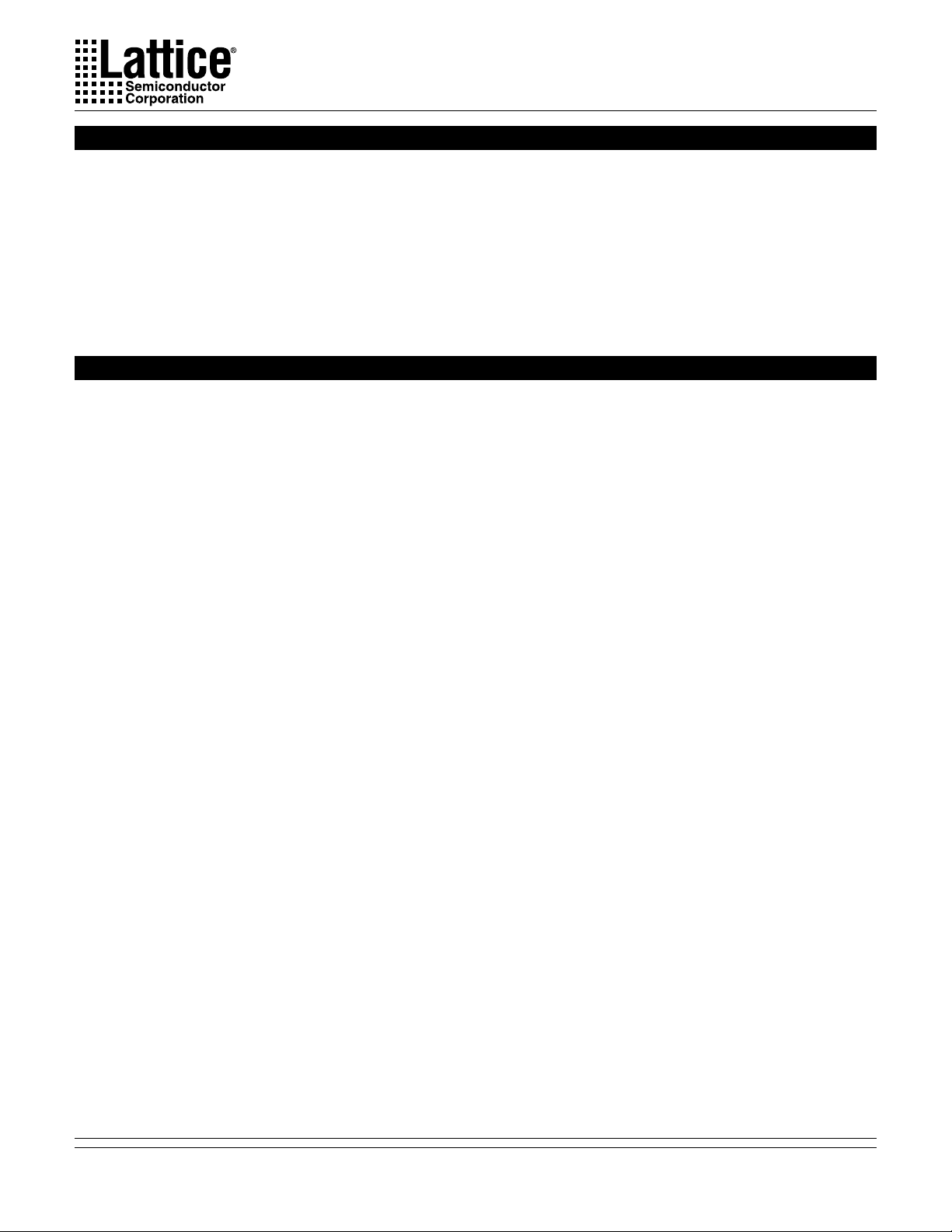

Specifications GAL16V8Z

GAL16V8ZD

GAL16V8Z/ZD Ordering Information

GAL16V8Z: Commercial Grade Specifications

Tpd (ns) Tsu (ns) Tco (ns) Icc (mA) Isb (µA) Ordering # Package

12 10 8 55 100 GAL16V8Z-12QP 20-Pin Plastic DIP

55 100 GAL16V8Z-12QJ 20-Lead PLCC

55 100 GAL16V8Z-12QS 20-Lead SOIC

15 15 10 55 100 GAL16V8Z-15QP 20-Pin Plastic DIP

55 100 GAL16V8Z-15QJ 20-Lead PLCC

55 100 GAL16V8Z-15QS 20-Lead SOIC

GAL16V8ZD: Commercial Grade Specifications

Tpd (ns) Tsu (ns) Tco (ns) Icc (mA) Isb (µA) Ordering # Package

12 10 8 55 100 GAL16V8ZD-12QP 20-Pin Plastic DIP

55 100 GAL16V8ZD-12QJ 20-Lead PLCC

15 15 10 55 100 GAL16V8ZD-15QP 20-Pin Plastic DIP

55 100 GAL16V8ZD-15QJ 20-Lead PLCC

Part Number Description

Device Name

GAL16V8Z (Zero Power ITD)

GAL16V8ZD (Zero Power DPP)

Speed (ns)

Active Power

Q = Quarter Power

XXXXXXXX XX X X X

_

Grade

Blank = Commercial

Package

P = Plastic DIP

J = PLCC

S = SOIC

2

Output Logic Macrocell (OLMC)

Specifications GAL16V8Z

GAL16V8ZD

The following discussion pertains to configuring the output logic

macrocell. It should be noted that actual implementation is accomplished by development software/hardware and is completely transparent to the user.

There are three global OLMC configuration modes possible:

simple, complex, and registered. Details of each of these modes

is illustrated in the following pages. T wo global bits, SYN and AC0,

control the mode configuration for all macrocells. The XOR bit of

Compiler Support for OLMC

Software compilers support the three different global OLMC modes

as different device types. Most compilers also have the ability to

automatically select the device type, generally based on the register

usage and output enable (OE) usage. Register usage on the device

forces the software to choose the registered mode. All combinatorial outputs with OE controlled by the product term will force the

software to choose the complex mode. The software will choose

the simple mode only when all outputs are dedicated combinatorial

without OE control. For further details, refer to the compiler software manuals.

When using compiler software to configure the device, the user

must pay special attention to the following restrictions in each mode.

In registered mode pin 1 and pin 1 1 are permanently configured

as clock and output enable, respectively . These pins cannot be configured as dedicated inputs in the registered mode.

each macrocell controls the polarity of the output in any of the three

modes, while the AC1 bit of each of the macrocells controls the input/output configuration. These two global and 16 individual architecture bits define all possible configurations in a GAL16V8Z/ZD.

The information given on these architecture bits is only to give a

better understanding of the device. Compiler software will transparently set these architecture bits from the pin definitions, so the

user should not need to directly manipulate these architecture bits.

In complex mode pin 1 and pin 1 1 become dedicated inputs and

use the feedback paths of pin 19 and pin 12 respectively . Because

of this feedback path usage, pin 19 and pin 12 do not have the

feedback option in this mode.

In simple mode all feedback paths of the output pins are routed

via the adjacent pins. In doing so, the two inner most pins ( pins

15 and 16) will not have the feedback option as these pins are

always configured as dedicated combinatorial output.

When using the standard GAL16V8 JEDEC fuse pattern generated

by the logic compilers for the GAL16V8ZD, special attention must

be given to pin 4 (DPP) to make sure that it is not used as one of

the functional inputs.

3

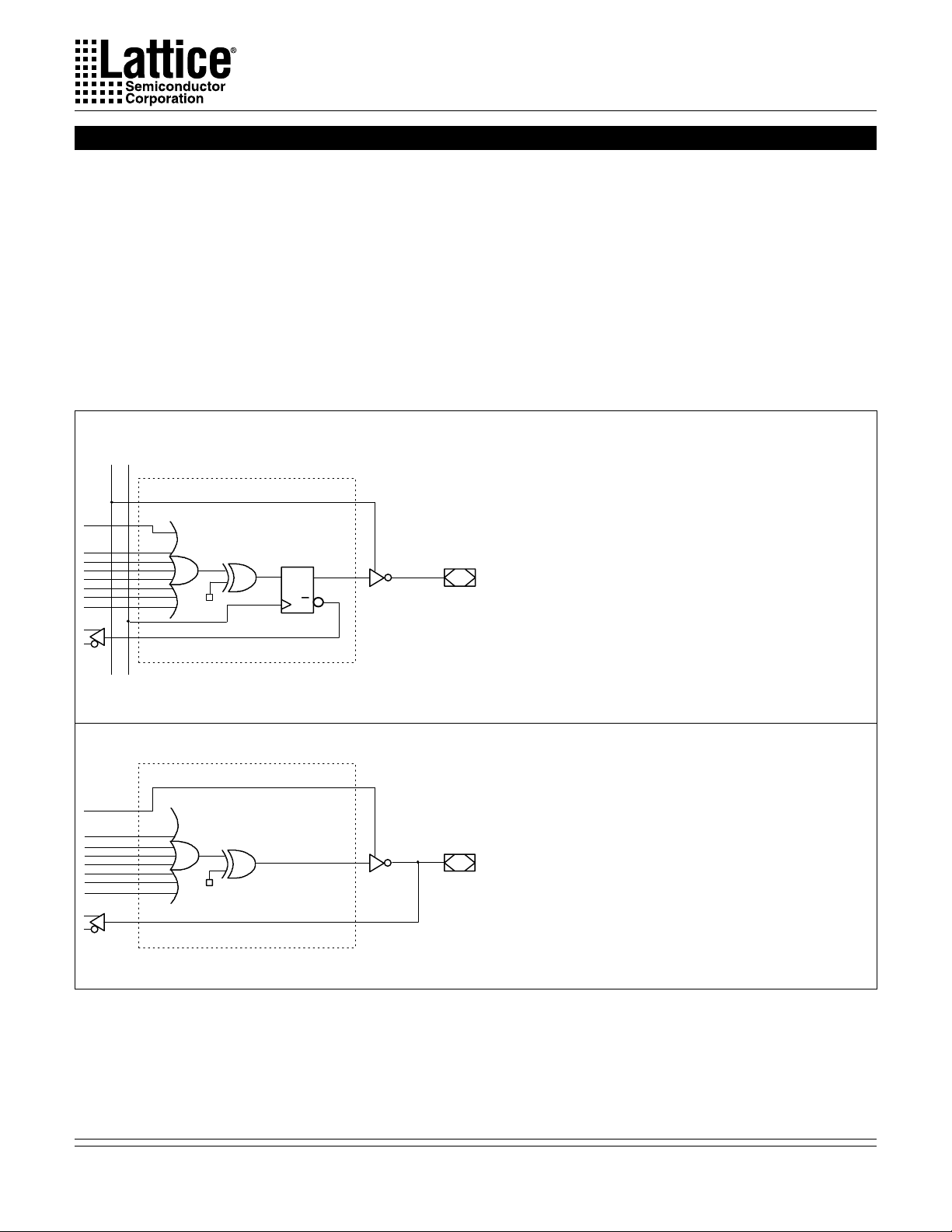

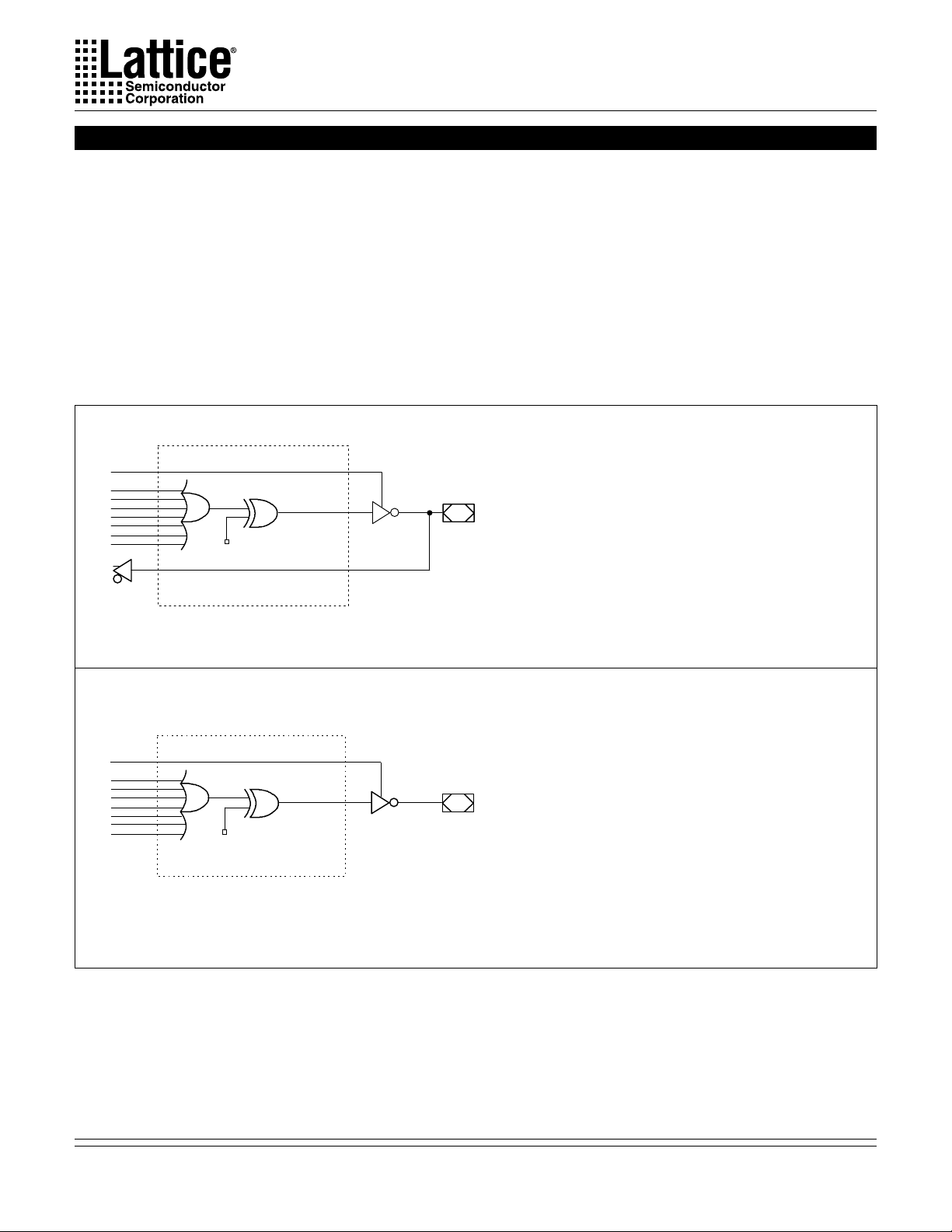

Registered Mode

Specifications GAL16V8Z

GAL16V8ZD

In the Registered mode, macrocells are configured as dedicated

registered outputs or as I/O functions.

Architecture configurations available in this mode are similar to

the common 16R8 and 16RP4 devices with various permutations

of polarity , I/O and register placement.

All registered macrocells share common clock and output enable

control pins. Any macrocell can be configured as registered or

I/O. Up to eight registers or up to eight I/Os are possible in this

mode. Dedicated input or output functions can be implemented

as subsets of the I/O function.

CLK

DQ

XOR

Q

Registered outputs have eight product terms per output. I/Os have

seven product terms per output.

Pin 4 is used as dedicated power-down pin on GAL16V8ZD. It

cannot be used as functional input.

The JEDEC fuse numbers, including the User Electronic Signature

(UES) fuses and the Product Term Disable (PTD) fuses, are

shown on the logic diagram on the following page.

Registered Configuration for Registered Mode

- SYN=0.

- AC0=1.

- XOR=0 defines Active Low Output.

- XOR=1 defines Active High Output.

- AC1=0 defines this output configuration.

- Pin 1 controls common CLK for the registered outputs.

- Pin 11 controls common OE for the registered outputs.

- Pin 1 & Pin 11 are permanently configured as CLK & OE

for registered output configuration.

OE

Combinatorial Configuration for Registered Mode

- SYN=0.

- AC0=1.

- XOR=0 defines Active Low Output.

- XOR=1 defines Active High Output.

XOR

Note: The development software configures all of the architecture control bits and checks for proper pin usage automatically.

- AC1=1 defines this output configuration.

- Pin 1 & Pin 11 are permanently configured as CLK & OE

for registered output configuration.

4

Registered Mode Logic Diagram

Specifications GAL16V8Z

GAL16V8ZD

DIP, SOIC & PLCC Package Pinouts

1

201612840

24

0000

0224

2

0256

0480

3

0512

0736

4

*

0768

0992

5

1024

1248

6

2128

28

PTD

OLMC

19

XOR-2048

AC1-2120

OLMC

18

XOR-2049

AC1-2121

OLMC

17

XOR-2050

AC1-2122

OLMC

16

XOR-2051

AC1-2123

OLMC

15

XOR-2052

AC1-2124

7

8

9

MSB LSB

1280

1504

1536

1760

1792

2016

2191

64-USER ELECTRONIC SIGNATURE FUSES

2056, 2057, .... .... 21 18, 2119

Byte7 Byte6 .... .... Byte1 Byte0

OLMC

14

XOR-2053

AC1-2125

OLMC

13

XOR-2054

AC1-2126

OLMC

12

XOR-2055

AC1-2127

OE

11

SYN-2192

AC0-2193

* Note: Input not available on GAL16V8ZD

5

Complex Mode

Specifications GAL16V8Z

GAL16V8ZD

In the Complex mode, macrocells are configured as output only or

I/O functions.

Architecture configurations available in this mode are similar to the

common 16L8 and 16P8 devices with programmable polarity in

each macrocell.

Up to six I/Os are possible in this mode. Dedicated inputs or outputs

can be implemented as subsets of the I/O function. The two outer

most macrocells (pins 12 & 19) do not have input capability . Designs requiring eight I/Os can be implemented in the Registered

mode.

XOR

All macrocells have seven product terms per output. One product

term is used for programmable output enable control. Pins 1 and

1 1 are always available as data inputs into the AND array.

Pin 4 is used as dedicated power-down pin on GAL16V8ZD. It cannot be used as functional input.

The JEDEC fuse numbers including the UES fuses and PTD fuses

are shown on the logic diagram on the following page.

Combinatorial I/O Configuration for Complex Mode

- SYN=1.

- AC0=1.

- XOR=0 defines Active Low Output.

- XOR=1 defines Active High Output.

- AC1 has no effect on this mode.

- Pin 13 through Pin 18 are configured to this function.

Combinatorial Output Configuration for Complex Mode

- SYN=1.

- AC0=1.

- XOR=0 defines Active Low Output.

XOR

Note: The development software configures all of the architecture control bits and checks for proper pin usage automatically.

- XOR=1 defines Active High Output.

- AC1 has no effect on this mode.

- Pin 12 and Pin 19 are configured to this

function.

6

Loading...

Loading...