Page 1

Evaluation Board User Guide

FPGA-EB-02018 Version 1.0

June 2018

CrossLink LIF-MD6000 Master Link Board Revision C

Page 2

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

Contents

Acronyms in This Document ................................................................................................................................................. 4

1. Introduction .................................................................................................................................................................. 5

2. Headers and Test Connections ..................................................................................................................................... 7

3. Programming Circuit ..................................................................................................................................................... 8

3.1. Bridging Circuit .................................................................................................................................................... 8

3.2. I2C Expander ........................................................................................................................................................ 9

4. Power Supply .............................................................................................................................................................. 10

5. Status Indicators ......................................................................................................................................................... 12

6. SMA IO Link Board ...................................................................................................................................................... 13

7. Breakout IO Link Board ............................................................................................................................................... 15

8. Ordering Information .................................................................................................................................................. 18

References .......................................................................................................................................................................... 19

Technical Support Assistance............................................................................................................................................... 19

Appendix A. LIF-MD6000-ML-EVN-BRD Schematics ........................................................................................................... 20

Appendix B. LIF-MD6000-ML-EVN-BRD Bill of Materials .................................................................................................... 28

Appendix C. SMA-IOL-EVN-BRD Schematics ....................................................................................................................... 34

Appendix D. SMA-IOL-EVN-BRD Bill of Materials................................................................................................................ 35

Appendix E. B-IOL-EVN-BRD Schematics............................................................................................................................. 36

Appendix F. B-IOL-EVN-BRD Bill of Materials ..................................................................................................................... 37

Revision History ................................................................................................................................................................... 38

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

2 FPGA-EB-02018-1.0

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 3

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

Figures

Figure 1.1. Top View of Master Link Board and its Key Components ................................................................................... 6

Figure 1.2. Bottom View of Master Link Board..................................................................................................................... 6

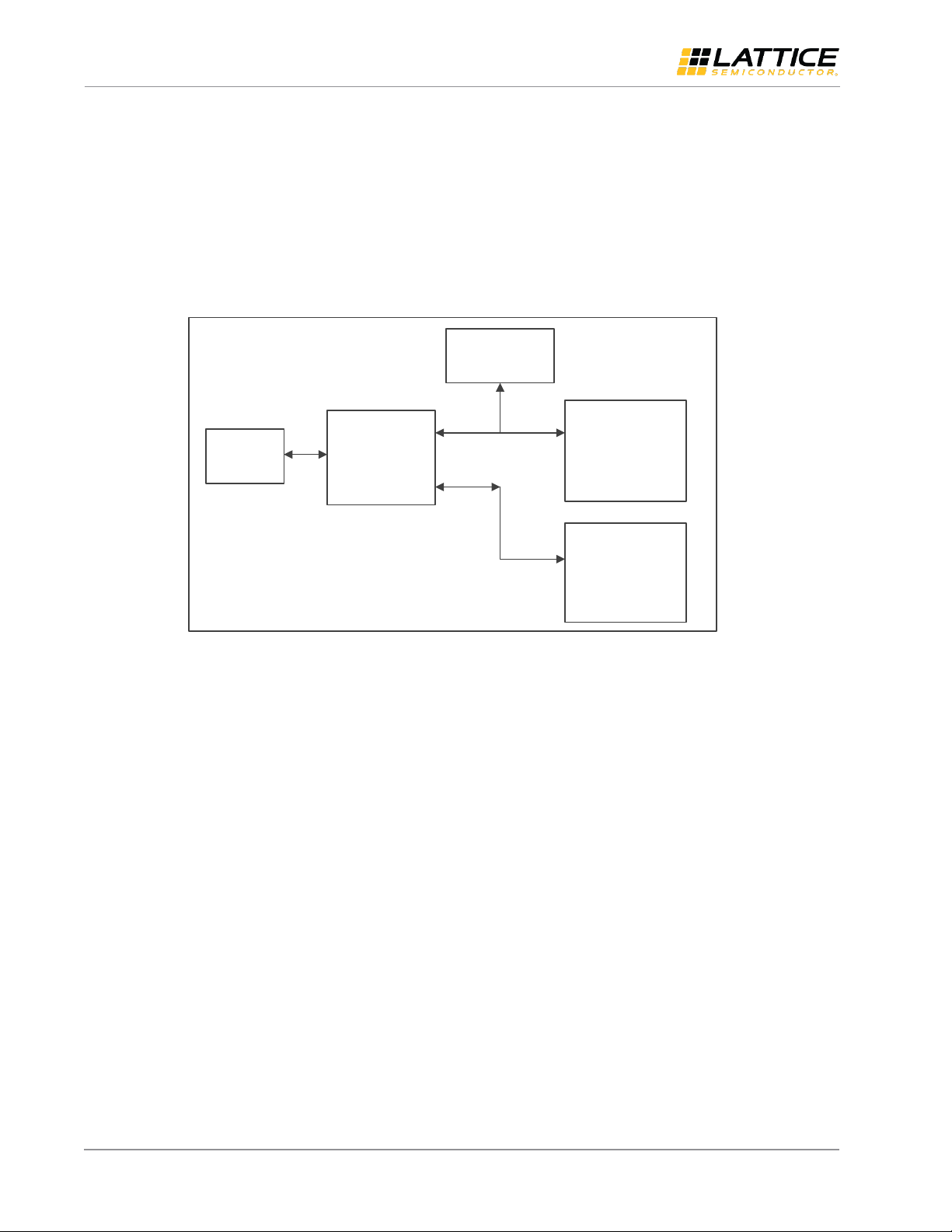

Figure 3.1. Programming Block ............................................................................................................................................. 8

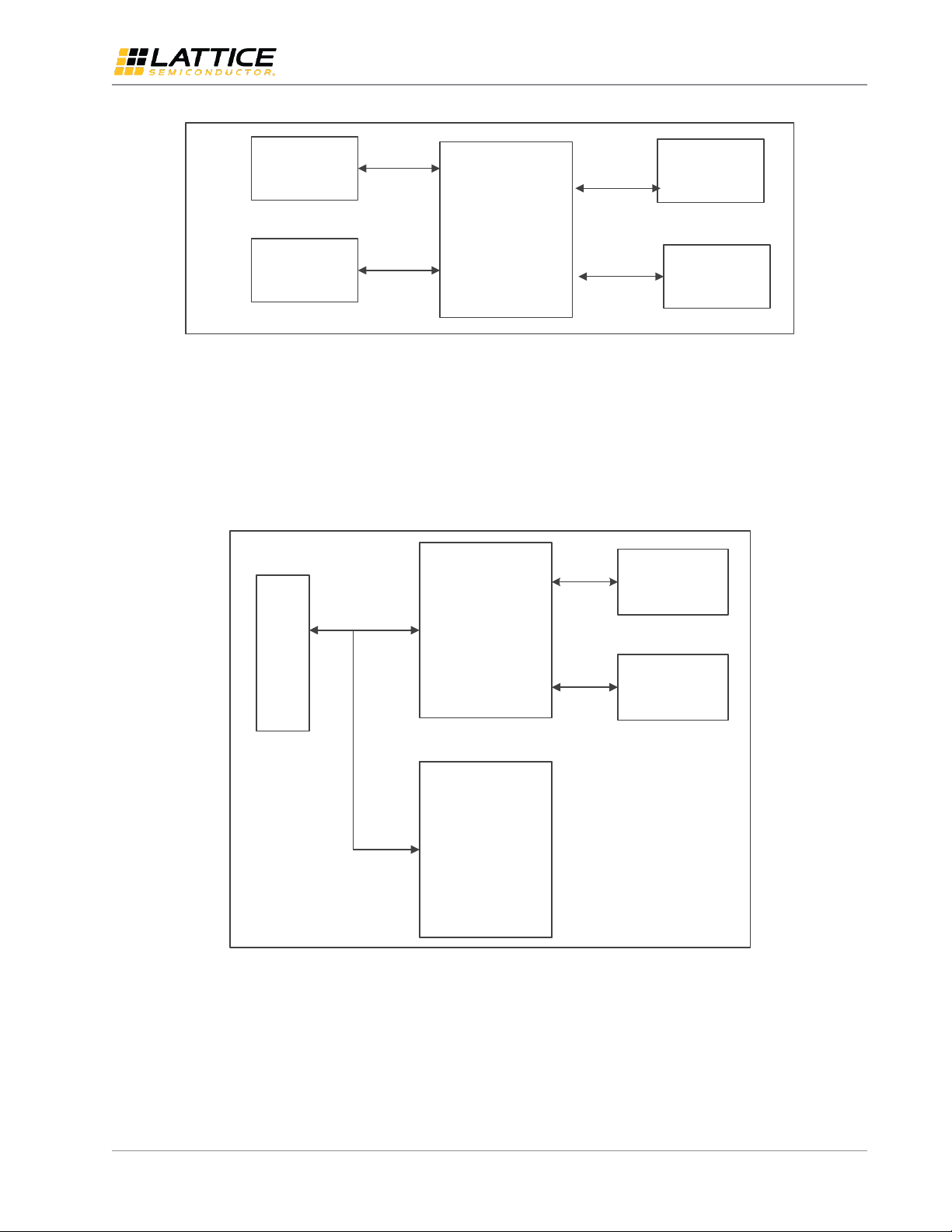

Figure 3.2. Bridging Block ..................................................................................................................................................... 9

Figure 3.3. I2C Expander Block .............................................................................................................................................. 9

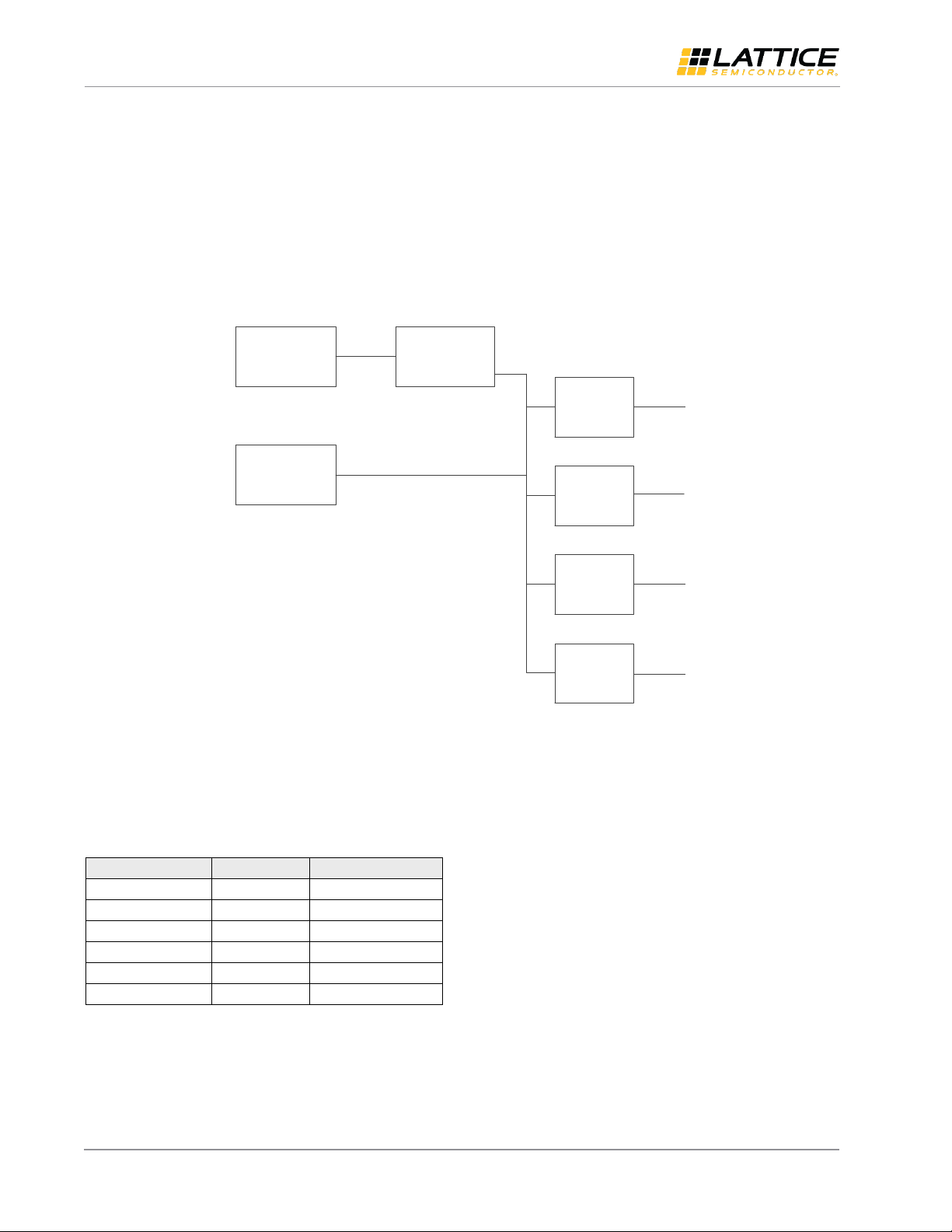

Figure 4.1. Power Supply Block........................................................................................................................................... 10

Figure 6.1. Top View of SMA IO Link Board ........................................................................................................................ 14

Figure 6.2. Bottom View of SMA IO Link Board .................................................................................................................. 14

Figure 7.1. Top View of Breakout IO Link Board ................................................................................................................. 17

Figure 7.2. Bottom View of Breakout IO Link Board ........................................................................................................... 17

Tables

Table 2.1. Headers and Test Connectors .............................................................................................................................. 7

Table 4.1. Power LEDs ........................................................................................................................................................ 10

Table 4.2. Device Power Rail Summary and Test Points ..................................................................................................... 11

Table 5.1. Status LED I/O Map ............................................................................................................................................ 12

Table 6.1. Headers and Test Connectors ............................................................................................................................ 13

Table 6.2. U1 Connector Description .................................................................................................................................. 13

Table 7.1. Headers and Test Connectors ............................................................................................................................ 15

Table 7.2. U1 Connector Description .................................................................................................................................. 15

Table 7.3. J2 Header Description ........................................................................................................................................ 16

Table 8.1. Ordering Information ......................................................................................................................................... 18

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02018-1.0 3

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 4

CrossLink LIF-MD6000 Master Link Board - Revision C

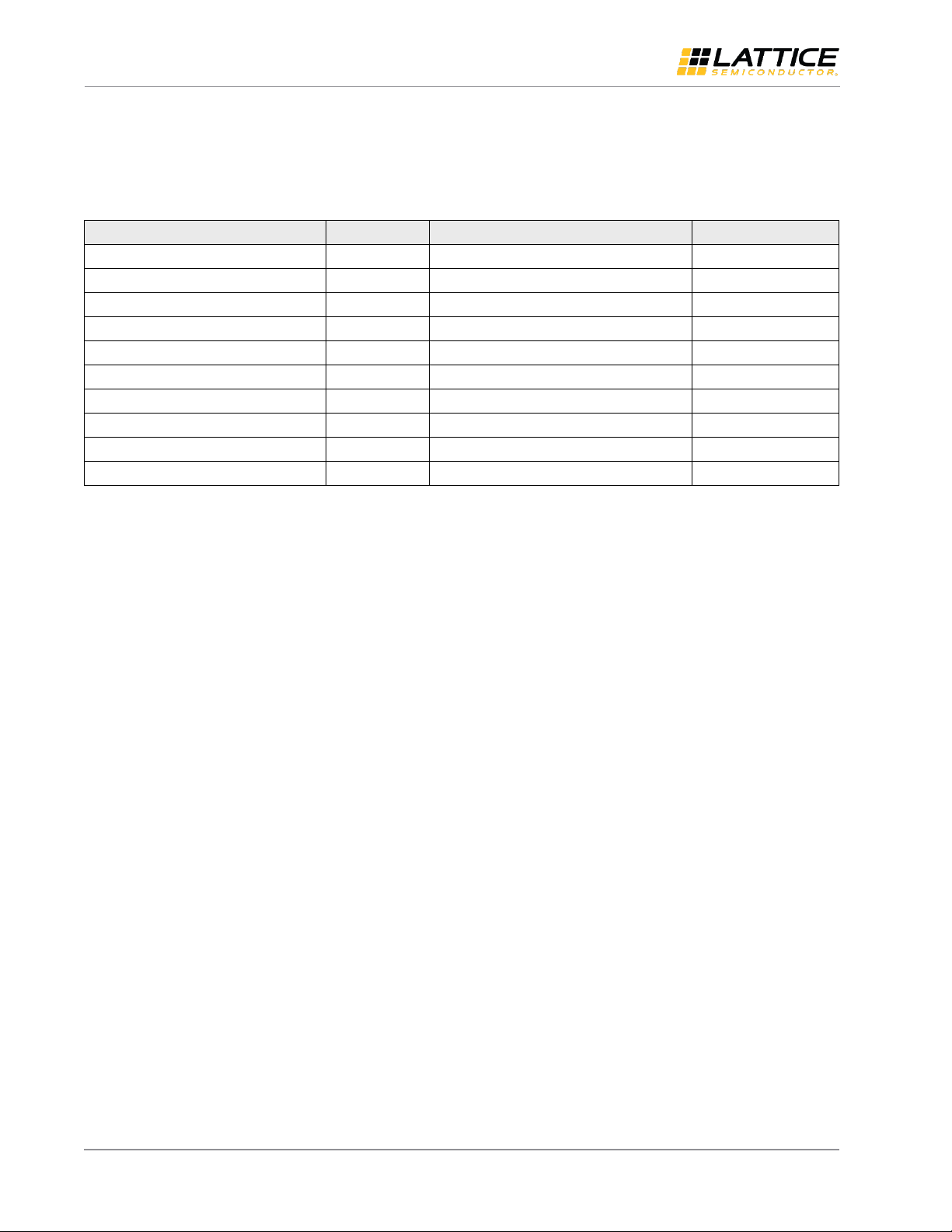

Acronym

Definition

CMOS

Complementary Metal-Oxide Semiconductor

CSI-2

Camera Serial Interface

DSI

Display Serial Interface

FTDI

Future Technology Devices International

I2C

Inter-Integrated Circuit

IO

Input/Output

LVDS

Low-Voltage Differential Signaling

MIPI

Mobile Industry Processor Interface

SPI

Serial Peripheral Interface

Evaluation Board User Guide

Acronyms in This Document

A list of acronyms used in this document.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

4 FPGA-EB-02018-1.0

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 5

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

1. Introduction

This document describes the Lattice Semiconductor CrossLink™ LIF-MD6000 Master Link Board –Revision C (Rev C) that

supports a variety of demos, encompassing different signaling logic standards bridging with MIPI® CSI-2/DSI interface.

The board‘s key component is the CrossLink Family device that features built in MIPI D-PHY hard blocks to support

different bridging solutions.

For the latest information about this board, including optional Tx/Rx Link boards, demo files, further documentation

and more, see the Lattice website at: www.latticesemi.com/masterlink.

For details about the CrossLink device, refer to CrossLink Family Data Sheet (FPGA-DS-02007).

The content of this user guide includes descriptions of on-board jumper settings, programming circuit, a complete set

of schematics, and bill of materials for LIF-MD6000 Master Link Rev C board.

Refer to Appendix A, B, C, D, E, F for the schematic and BOM of the CrossLink LIF-MD6000 Master Link Rev C board and

the schematics and BOMs of the Breakout IO Link and SMA IO Link boards that are included in the demo kit.

Circuits on the development kit board:

Programming Circuit

Mini USB Type-B connector to FTDI

FTDI to CrossLink using SPI

FTDI to CrossLink using I

FTDI to XO3LF device using JTAG

CrossLink

MIPI CSI-2/DSI hard block

Bridging of multiple signaling standards

SPI flash configuration

General Purpose Input/Output

LED display

LCMXO3LF-1300E

2

I

C muxing

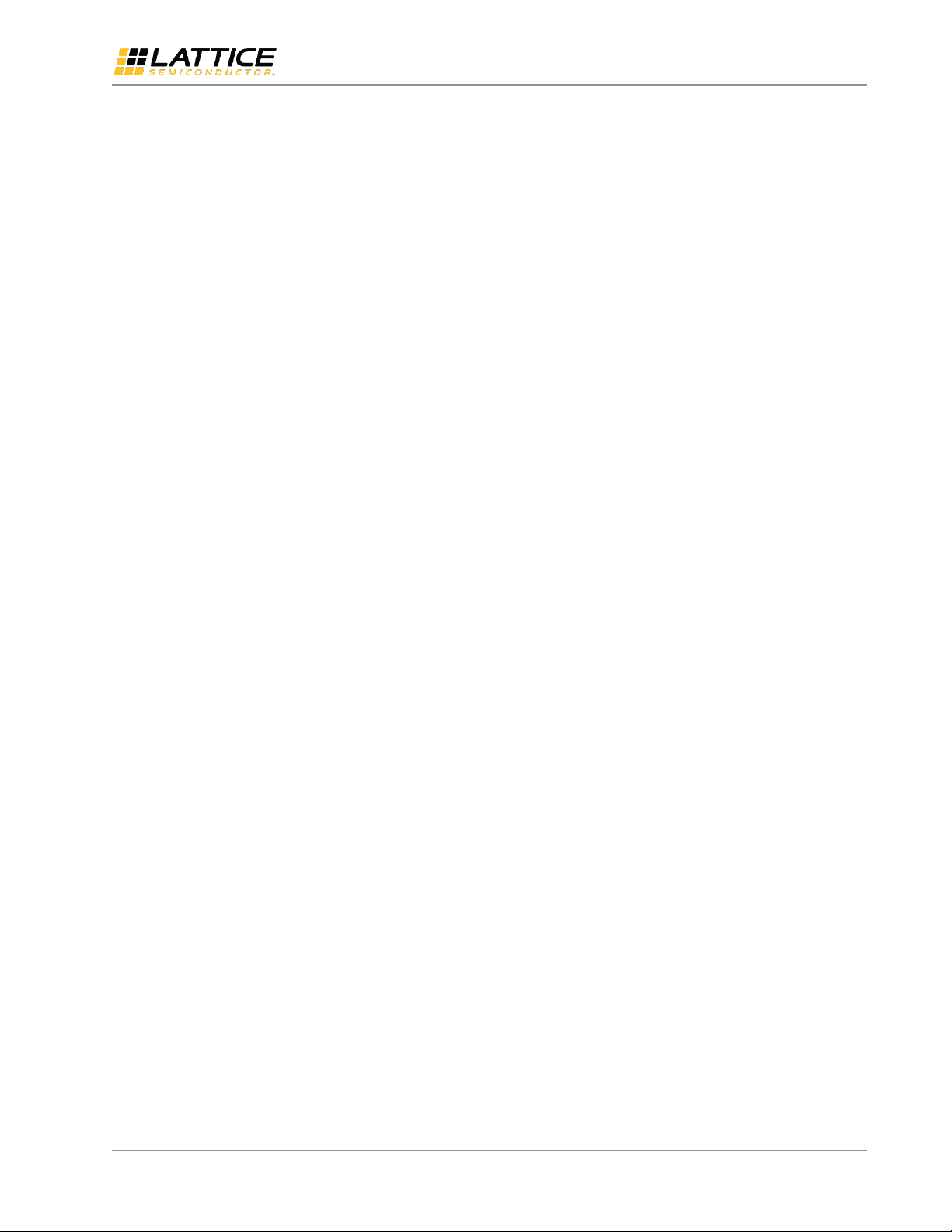

Figure 1.1 shows the top view of the LIF-MD6000 Master Link Rev C board and its key components. Figure 1.2 shows

the bottom view of the board.

2

C

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02018-1.0 5

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 6

CrossLink LIF-MD6000 Master Link Board - Revision C

Tx Connectors 1 and 2 (U9, U7)

Power Switch (SW1)

External Power Input

External Power Jack (J3)

LCMXO3L-1300E (U19)

USB 2.0 Mini-B (J2)

JTAG Header (J1)

FTDI Chip (U1)

SPI Flash Device (U14)

Rx Connectors (U11, U12)

Power LEDs

LIF-MD6000-CSFBGA81

Programming Header (J18)

Debug and

Configuration LEDs

Reset and wake-up buttons

Switch (SW2/SW4/SW5)

Clock Source Selection (J26, J27)

Bank 1, 2 Voltage Selection

Headers (J24, J25)

External Clock SMA Inputs

MachXO3 Reset (SW3)

Debug Header (J28)

Debug Header (J31)

Evaluation Board User Guide

Figure 1.1. Top View of Master Link Rev C Board and its Key Components

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

6 FPGA-EB-02018-1.0

Figure 1.2. Bottom View of Master Link Rev C Board

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 7

CrossLink LIF-MD6000 Master Link Board - Revision C

Part

Description

Setting

J1

External JTAG interface - For LCMX03 only

—

J2

mini-B USB connector

—

J3

External 12V power jack

—

J4

External clock input for MIPI D-PHY reference clock

—

J7

SW2 selector

OPEN-NOP, SHORT-CONFIGURATION RESET

J8

External 12 V terminal block

Open

J9

External 5 V terminal block

Open

J16

SPI/I2C programming selector for LIF-MD6000

1-2 (SPI), 2-3 (I2C)

J18

External SP/I2C access for LIF-MD6000

—

J19

SPI Flash chip select

OPEN-OFF, SHORT-ON

J22

External reference clock input for MIPI D-PHY reference clock

—

J23

LCMXO3L debug header

—

J24

VCCIO1 Bank voltage selector

1-2 (2.5 V), 2-3 (3.3 V), 2-4 (1.2 V)

J25

VCCIO2 Bank voltage selector

1-2 (2.5 V), 2-3 (3.3 V), 2-4 (1.2 V)

J26

Internal/External clock and I2C SDA Mux

1-2 (CLK_INT), 2-3 (CLK_EXT), 2-4 (SDA)

J27

Internal/External reference clock and I2C SCL Mux

1-2 (CLK_INT_REF), 2-3 (CLK_EXT_REF), 2-4 (SCL)

J28

Reveal analyzer signal connector

—

J29

Reset signal voltage selector

1-2 (VCCIO2), 2-3 (VCCIO0)

J31

External SPI/I2C access for LCMXO3L

—

J32

LCMXO3L configuration header

—

J35

SPI/I2C programming selector for LIF-MD6000

1-2 (SPI), 2-3 (I2C)

J36

SPI/I2C programming selector for LIF-MD6000

1-2 (SPI), 2-3 (I2C)

J37

FT2232H reset

OPEN-NORMAL OP, SHORT-RESET

SW1

External adaptor power ON/OFF

—

SW2

Configuration reset for LIF-MD6000

—

SW3

External reset for LCMXO3L

—

SW4*

External reset for LIF-MD6000

—

SW5

PMU WAKEUP Switch for LIF-MD6000

—

U7

Tx Connectors for external interface

—

U9

Tx Connectors for external interface

—

U11

Rx Connectors for external interface

—

U12

Rx Connectors for external interface

—

Evaluation Board User Guide

2. Headers and Test Connections

Figure 1.1 shows the top view of the Master Link Rev C board. The headers and test connections on the board provide

access to LIF-MD6000 Master Link Rev C board circuits. Table 2.1 lists the headers and test connectors.

Table 2.1. Headers and Test Connectors

*Note: Some CrossLink demos utilize this reset signal to ball G9 of Bank 2 while it is configured as a 1.2 V Bank. However, LVCMOS12

inputs are no longer supported across all 3 Banks. Lattice Diamond® Software 3.9 and later will not allow this signal to be placed on a

1.2 V Bank. If it is necessary to recompile one of these demo projects, the necessary modifications should be made to the project

and the board to move this reset signal to a non-1.2 V Bank on CrossLink.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02018-1.0 7

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 8

CrossLink LIF-MD6000 Master Link Board - Revision C

USB Mini-B

(J2)

FTDI Chip (U1)

SPI Flash (U14)

LIF-MD6000

CSFBGA81 (U8)

LCMXO3LF-1300E

MG121 (U19)

JTAG

SPI

SPI/I2C

Evaluation Board User Guide

3. Programming Circuit

The Mini-B USB connector is used for programming the board by using Lattice Diamond Programmer software.

Figure 3.1 shows the programming block of LIF-MD6000 Master Link Rev C board.

The Mini-B USB connector interfaces to the FTDI FT2232H IC. The FTDI IC works with Diamond Programmer software to

provide interfaces for:

JTAG – to program MachXO3 LCMXO3LF-1300E

SPI – to program CrossLink and/or SPI Flash Memory

2

I

C – to program CrossLink

Figure 3.1. Programming Block

3.1. Bridging Circuit

Figure 3.2 shows the block diagram of bridging of different standard interfaces. The CrossLink device is used as a

bridging device that supports a variety of I/O standards. This demo board supports development of the following

interface bridges:

1:1 MIPI DSI Display Interface Bridge

1:2 MIPI DSI Display Interface Bridge

2:1 MIPI CSI-2 Image Sensor Aggregator Bridge

CMOS to MIPI CSI-2 Image Sensor Interface Bridge

MIPI CSI-2 to CMOS Image Sensor Interface Bridge

MIPI DSI to CMOS Display Interface Bridge

OpenLDI LVDS to MIPI DSI Display Interface Bridge

CMOS to MIPI DSI Display Interface Bridge

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

8 FPGA-EB-02018-1.0

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 9

CrossLink LIF-MD6000 Master Link Board - Revision C

LIF-MD6000

CSFBGA81 (U8)

Rx Connector 1

Rx Connector 2

D-PHY I/F/

CMOS

D-PHY Rx/

LVDS/CMOS

D-PHY Rx/

LVDS/CMOS

Tx Connector 2

Tx Connector 1

D-PHY I/F/

CMOS

LCMXO3LF-1200E-

MG121 (U19)

Rx Connector 1

Rx Connector 2

LIF-MD6000

CSFBGA81 (U8)

Tx

H

e

a

d

e

r

I2C

2 X I2C

2 X I2C

Evaluation Board User Guide

Figure 3.2. Bridging Block

3.2. I

2

C Expander

Figure 3.3 shows the block diagram of the I2C expander. The LCMXO3LF-1200E device is used as an I2C expander and it

supports a single master and multiple slave devices connected to the board. The master I2C interface is connected to

the Tx header and the slave device I2C interface is connected to the Rx connectors supporting any slave device access

from the master based on the slave address.

Figure 3.3. I2C Expander Block

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02018-1.0 9

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 10

CrossLink LIF-MD6000 Master Link Board - Revision C

J3

J2

12 V to 5 V

converter

LDO

LDO

LDO

LDO

Power adaptor

Mini-B USB

5 V

5 V

U15

U5

U6

U17

12 V

U18

1.2 V

3.3 V

2.5 V

1.8 V

Voltage Rail

LEDs

Color

12

D26

Green

5

D3

Green

3.3

D25

Green

2.5

D29

Green

1.8

D28

Green

1.2

D27

Green

Evaluation Board User Guide

4. Power Supply

The power supply to the development kit is provided by the Mini-B USB connector or from an external adaptor.

Figure 4.1 shows the power supply block of the CrossLink LIF-MD6000 Master Link Rev C board. The external adaptor

provides 12 V power source through voltage regulators on the board to CrossLink and LCMXO3LF-1300E, as well as to

the external boards connected to Tx and Rx Headers. The Mini-B USB connector provides 5 V to the various voltage

regulators and is also used for device programming. Each I/O and core voltage rail on the board is accessible by a test

point on the board. The current flowing to each rail can be measured using a 1 Ω resistor placed in the path of each

voltage rail.

Table 4.1 lists the device power rails. There are five voltage regulators on the board used to supply the 5 V, 3.3 V, 2.5V

1.8 V, and 1.2 V rails. The input to these regulators is either from the Mini-B USB connector (J2), an external 12 V

adaptor (J3), or an external power supply to the terminal blocks of J8 or J9. Switch SW1 is used to connect or

disconnect power to the board.

Table 4.1. Power LEDs

Table 4.2 lists the board voltage rails, including the rail source voltage, test point number, and current sense resistor

number.

Figure 4.1. Power Supply Block

10 FPGA-EB-02018-1.0

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 11

CrossLink LIF-MD6000 Master Link Board - Revision C

Voltage Rail

Source Rail

Current Sense Resistor

Test Points

12 V — —

12V0

5 V

12 V — 5V0

+3.3 V

5 V — 3V3

+2.5 V

5 V — 2V5

+1.8 V

5 V — —

+1.2 V

5 V — 1V2

VCC_CORE

+1.2 V

R19

VCC_CORE1

VCCIO0

+2.5 V / +3.3 V

R20 / R24

VCCIO0

VCCIO1

+1.2 V / +2.5 V / +3.3 V

R21 / R25 / R434 / R448

VCCIO1

VCCIO2

+1.2 V / +2.5 V / +3.3 V

R28 / R33 / R435 / R449

VCCIO2

VCC_DPHY

+1.2 V

R417

VCC_DPHY

1K_VCC_CORE

+1.2 V

R190

1K_VCC_CORE1

1K_VCCIO0

+2.5 V / +3.3 V

R410 / R411

1K_VCCIO0

1K_VCCIO1

+2.5 V / +3.3 V

R184 / R185

1K_VCCIO1

1K_VCCIO2

+2.5 V / +3.3 V

R186 / R187

1K_VCCIO2

1K_VCCIO3

+2.5 V / +3.3 V

R188 / R189

1K_VCCIO3

Evaluation Board User Guide

Table 4.2. Device Power Rail Summary and Test Points

FPGA-EB-02018-1.0 11

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 12

CrossLink LIF-MD6000 Master Link Board - Revision C

Device

LED

Net Name

Color

CrossLink

D6

CMOS_IO_1

Blue

CrossLink

D7

CMOS_IO_2

Blue

CrossLink

D8

CMOS_IO_3

Blue

CrossLink

D9

CMOS_IO_4

Blue

CrossLink

D10

CDONE

Green

LCMX03LF-1300E

D23

DONE

Red

LCMX03LF-1300E

D30

LED1

Blue

LCMX03LF-1300E

D31

LED2

Blue

LCMX03LF-1300E

D32

LED3

Blue

LCMX03LF-1300E

D33

LED4

Blue

Evaluation Board User Guide

5. Status Indicators

The LED status indicators on the board show power, configuration, and application status. Table 5.1 lists the status LED

I/O map.

Table 5.1. Status LED I/O Map

12 FPGA-EB-02018-1.0

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 13

CrossLink LIF-MD6000 Master Link Board - Revision C

Part

Description

Mapping to U1

J1

SMA connector for DCK_TX_P

Pin 1

J2

SMA connector for DCK_TX_N

Pin 2

J3

SMA connector for DATA0_TX_P

Pin 4

J4

SMA connector for DATA0_TX_N

Pin 5

J5

SMA connector for DATA1_TX_P

Pin 7

J6

SMA connector for DATA1_TX_N

Pin 8

J7

SMA connector for DATA2_TX_P

Pin 13

J8

SMA connector for DATA2_TX_N

Pin 14

J9

SMA connector for DATA3_TX_P

Pin 16

J10

SMA connector for DATA3_TX_N

Pin 17

J11

SMA connector for DATA4_TX_P

Pin 24

J12

SMA connector for DATA4_TX_N

Pin 25

J13

SMA connector for DATA5_TX_P

Pin 27

J14

SMA connector for DATA5_TX_N

Pin 28

U1

Connector to interface to CrossLink Master Link Rev C board

N/A

Pin

Name

1

CH4_DCK_P

2

CH4_DCK_N

3

GND 4 CH4_DATA0_P

5

CH4_DATA0_N

6

GND

7

CH4_DATA1_P

8

CH4_DATA1_N

9

GND

10

SN

11

SCLK

12

GND

13

CH4_DATA2_P

14

CH4_DATA2_N

15

GND

16

CH4_DATA3_P

17

CH4_DATA3_N

18

GND

19

12V

20

12V Pin

Name

21

TBD

22

RESETN

23

PWR_5-0V

24

GND

25

GND

26

PWR_3-3V

27

GND

28

GND

29

PWR_1-8V

30

MOSI

31

MISO

32

PWR_1-8V

33

GND

34

GND

35

PWR_3-3V

36

GND

37

GND

38

PWR_5-0V

39

SDA

40

SCL

Evaluation Board User Guide

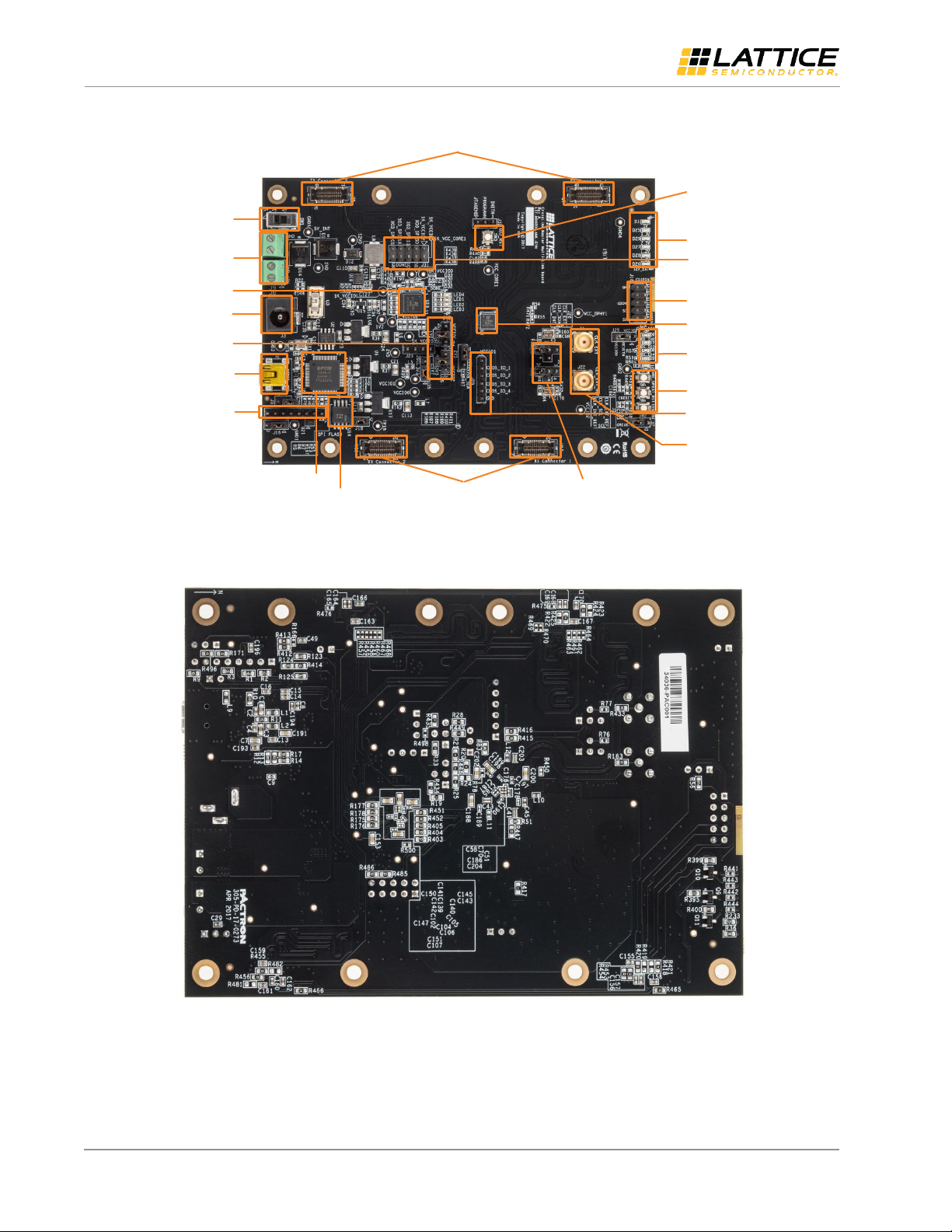

6. SMA IO Link Board

The SMA IO Link board connects to the CrossLink LIF-MD6000 Master Link Rev C board’s Tx or Rx connectors (U7, U9,

U11 or U12) and transfers signals to the respective SMA connectors.

Table 6.1. Headers and Test Connectors

Table 6.2. U1 Connector Description

Note: U1 connector pin names may be different than the actual signal depending on which CrossLink LIF-MD6000 Master Link Rev C

board connector this daughter board is connected to.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02018-1.0 13

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 14

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

Figure 6.1. Top View of SMA IO Link Board

Figure 6.2. Bottom View of SMA IO Link Board

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

14 FPGA-EB-02018-1.0

Page 15

CrossLink LIF-MD6000 Master Link Board - Revision C

Part

Description

Setting

J2

13x2 Header

—

U1

Connector to interface to CrossLink Master Link Rev C board

—

Pin

Name

1

CH4_DCK_P

2

CH4_DCK_N

3

GND

4

CH4_DATA0_P

5

CH4_DATA0_N

6

GND

7

CH4_DATA1_P

8

CH4_DATA1_N

9

GND

10

SN

11

SCLK

12

GND

13

CH4_DATA2_P

14

CH4_DATA2_N

15

GND

16

CH4_DATA3_P

17

CH4_DATA3_N

18

GND

19

12V

20

12V

Pin

Name

21

TBD

22

RESETN

23

PWR_5-0V

24

GND

25

GND

26

PWR_3-3V

27

GND

28

GND

29

PWR_1-8V

30

MOSI

31

MISO

32

PWR_1-8V

33

GND

34

GND

35

PWR_3-3V

36

GND

37

GND

38

PWR_5-0V

39

SDA

40

SCL

Evaluation Board User Guide

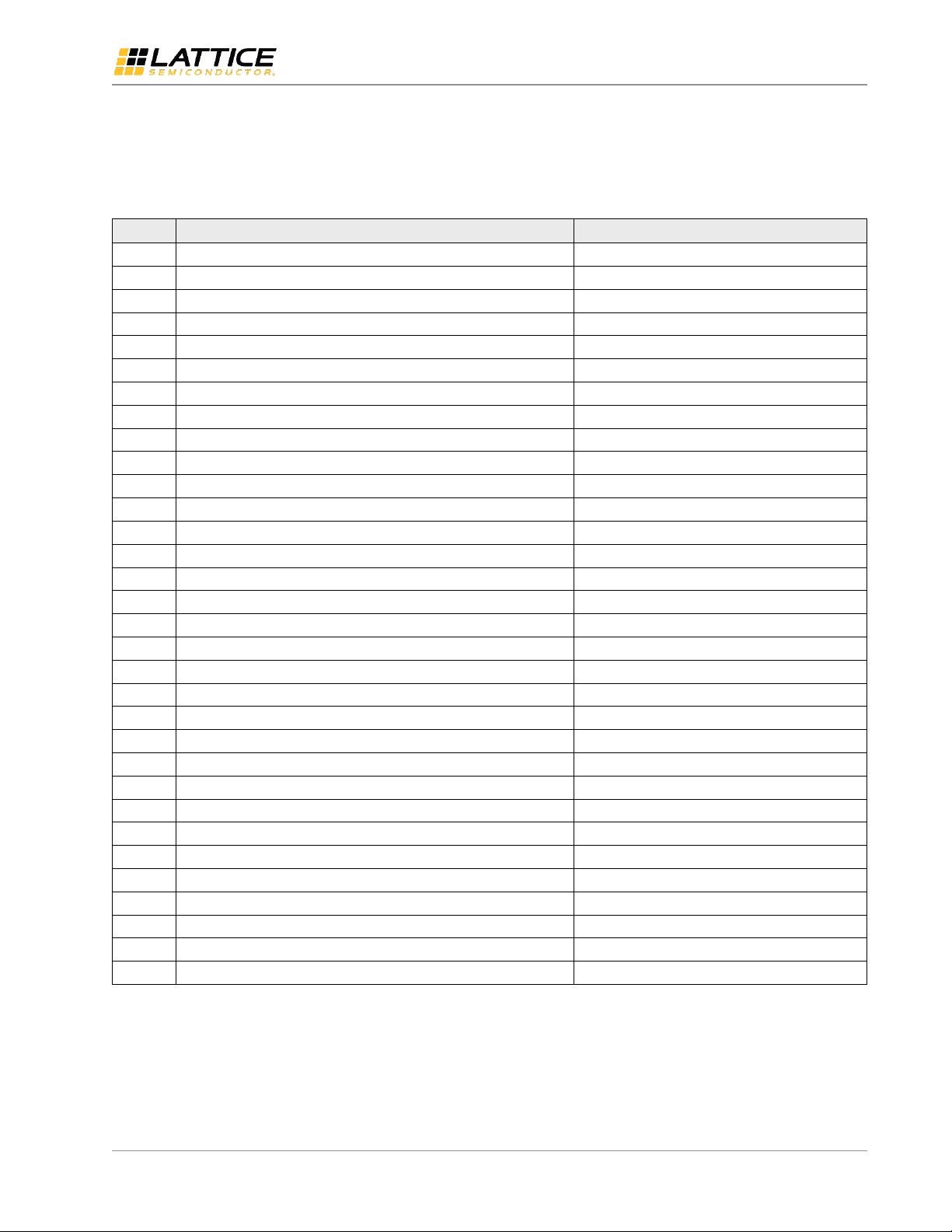

7. Breakout IO Link Board

The Breakout IO Link board connects to the CrossLink LIF-MD6000 Master Link Rev C board’s Tx or Rx connectors (U7,

U9, U11 or U12) and transfers signals to the 26-pin header (J2).

Table 7.1. Headers and Test Connectors

Table 7.2. U1 Connector Description

Note: U1 connector pin names may be different than the actual signal depending on which CrossLink LIF-MD6000 Master Link Rev C

board connector this daughter board is connected to.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02018-1.0 15

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 16

CrossLink LIF-MD6000 Master Link Board - Revision C

Pin

Name

Mapping to U1

1

+3.3V

N/A

2

+1.8V

N/A

3

RESETN

Pin 22

4

CH4_DCK_TX_P

Pin 1

5

SDA

Pin 39

6

CH4_DCK_TX_N

Pin 2

7

SCL

Pin 40

8

GND

N/A

9

GND

N/A

10

CH4_DATA0_TX_P

Pin 4

11

CH4_DATA3_TX_P

Pin 16

12

CH4_DATA0_TX_N

Pin 5

13

CH4_DATA3_TX_N

Pin 17

14

GND

N/A

15

GND

N/A

16

CH4_DATA1_TX_P

Pin 7

17

CH4_DATA4_TX_P

Pin 24

18

CH4_DATA1_TX_N

Pin 8

19

CH4_DATA4_TX_N

Pin 25

20

GND

N/A

21

GND

N/A

22

CH4_DATA2_TX_P

Pin 13

23

CH4_DATA5_TX_P

Pin 27

24

CH4_DATA2_TX_N

Pin 14

25

CH4_DATA5_TX_N

Pin 28

26

GND

N/A

Evaluation Board User Guide

Table 7.3. J2 Header Description

16 FPGA-EB-02018-1.0

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 17

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

Figure 7.1. Top View of Breakout IO Link Board

Figure 7.2. Bottom View of Breakout IO Link Board

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02018-1.0 17

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 18

CrossLink LIF-MD6000 Master Link Board - Revision C

Description

Ordering Part Number

China RoHS Environment-Friendly

Use Period (EFUP)

CrossLink: LIF-MD6000 Master Link Rev C Board

(Includes 1 SMA IO Link Board and 1 Breakout

IO Link Board)

LIF-MD6000-ML-EVN

CrossLink: LIF-MD6000 IO Link Boards

(Includes 1 SMA IO Link Board and 1 Breakout

IO Link Board)

LIFMD-IOL-EVN

Evaluation Board User Guide

8. Ordering Information

Table 8.1. Ordering Information

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

18 FPGA-EB-02018-1.0

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 19

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

References

For more information, refer to CrossLink Family Data Sheet FPGA-DS-02007 (previously DS1055).

Technical Support Assistance

Submit a technical support case through www.latticesemi.com/techsupport.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02018-1.0 19

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 20

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

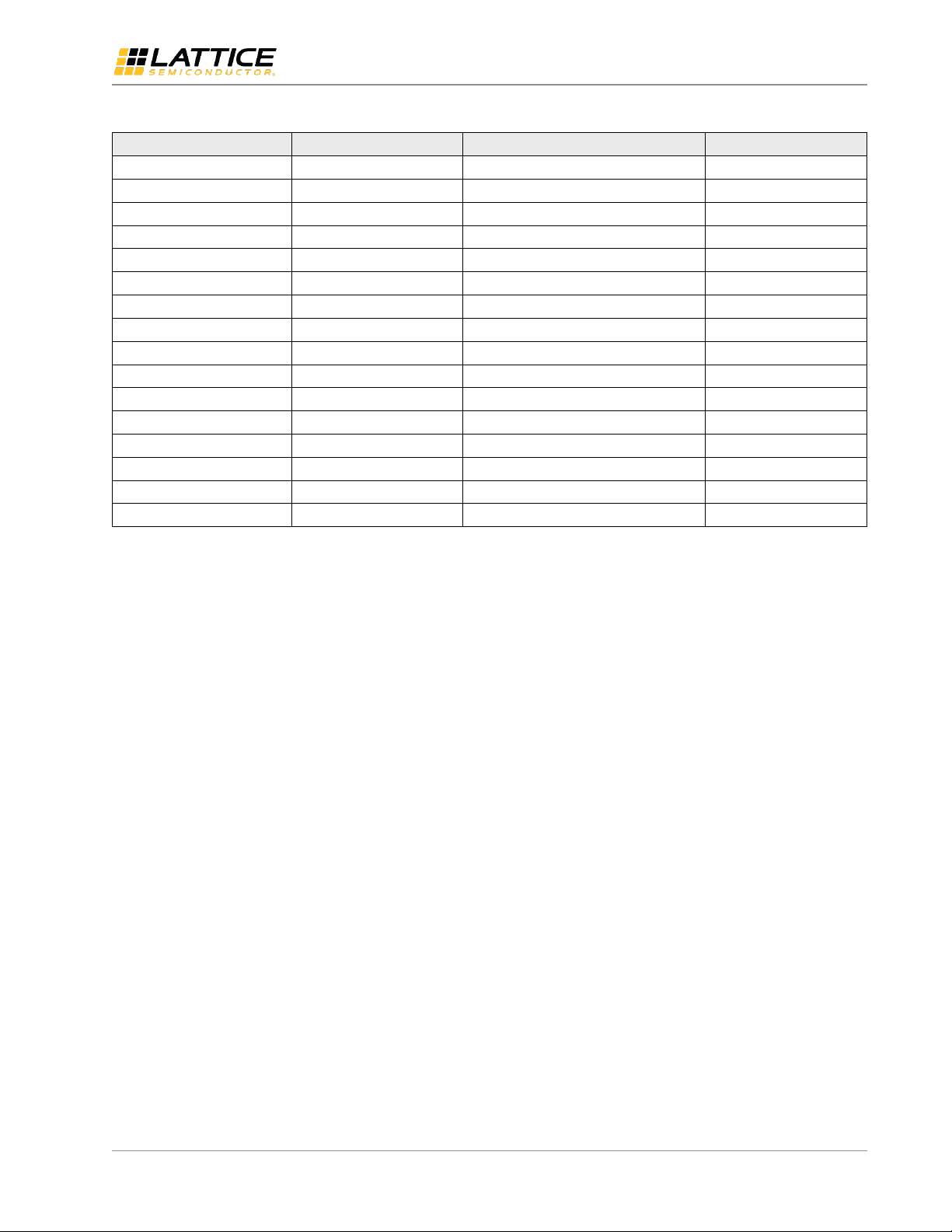

Appendix A. LIF-MD6000-ML-EVN-BRD Schematics

5

D D

Ext Power

Adaptor (12V)

C C

USB

CONNECTOR

OnBoard

LDO'S & Buck

USB to

JTAG / SPI/I2C

FTDI

USP Programming only

4

1V2,1V8,2V5,3V3,5V

MIPI TX I/O

MIPI TX HEADER1

JTAG_I/F/ SPI/I2C

SPI

SPI

3

LVDS RX HEADER1

SPI

I2C

DPHY BLOCK

2

LVDS RX HEADER2

SPI

I2C*2

LVDS RX In

SPI

LVDS RX In

BANK-1,2

LIFMD-6000-6MG81I

Targeted FPGA

1

SPI FLASH

I2C*1

I2C

BANK-0

SPI

MIPI TX I/O

MIPI TX HEADER2

B B

I2C

JTAG

I2C*3

BANK-2

LCMXO3LF-1300-MG121

I/O Expander - I2C Switch

A A

5

4

BANK-3,4

3

I2C

BANK-0

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

Title

Title

Title

BLOCK Diagram

BLOCK Diagram

BLOCK Diagram

Size

Size

Size

Project

Project

Project

B

B

B

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

Date:

28-Mar-17

Date:

28-Mar-17

Date:

2

28-Mar-17

Schematic Rev

Schematic Rev

Schematic Rev

Board Rev

Board Rev

Board Rev

1

1.0

1.0

1.0

1

1

1

ofSheet

81

ofSheet

81

ofSheet

81

LIF-MD6000 Master Link Rev C Board Block Diagram

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

20 FPGA-EB-02018-1.0

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 21

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

5

VBUS_5V

D D

J2

9

SHIELD4

8

SHIELD3

7

SHIELD2

6

SHIELD1

SKT_MINIUSB_B_RA

C C

+3.3V

C9

0.1uF

B B

+3.3V

A A

GND

C191

10uF

VCC

D-

D+

ID

8

7

6

5

1

2

3

4

R4 0

5

U2

VCC

NU

ORG

VSS

93LC56-SO8

5

12

L3

600ohm 500mA

C6 0.1uF

L9

600ohm 500mA

1

CS

2

CLK

3

DI

4

DO

C13

0.1uF

12

+3.3V

R12

10K

C14

0.1uF

C5

0.1uF

R13

10K

USB_DP

USB_DM

R14

10K

C15

0.1uF

1

GND

2

NC1

NC23D-

U20

VBUS

D+

ESDR0502N

R1712k

C16

0.1uF

VBUS_5V

6

5

4

4

4

+3.3V

+3.3V

VCC1_8FT

C10

18pF

L1

600ohm 500mA

L2

600ohm 500mA

USB_DM

USB_DP

C7

10uF

12MHZ{7}

C8

0.1uF

3

12

12

C2

C1

4u7

0.1uF

12

12

C3

C4

4u7

0.1uF

U1

FT2232HL

X1

113

G12G2

12MHZ

+3.3V

R10 2k2

J37

1

2

CON2

C201 1uF4V

R11 12k

FT_EECS

FT_EECLK

FT_EEDATA

3

4

C11

18pF

R180

DNI

50

49

14

63

62

61

13

7

8

6

2

3

VREGIN

VREGOUT

DM

DP

RESET#

REF

EECS

EECLK

EEDATA

OSCI

OSCO

TEST

PROGRAMMING INTERFACE

VCC1_8FT

4

9

64

VPLL

VPHY

VCORE12VCORE37VCORE

FTDI High-Speed USB

FT2232H

AGND10GND1GND5GND11GND15GND25GND35GND47GND

1-2 For SPI

3-2 For I2C

+3.3V

VCCIO20VCCIO31VCCIO42VCCIO

ADBUS0

ADBUS1

ADBUS2

ADBUS3

ADBUS4

ADBUS5

ADBUS6

ADBUS7

ACBUS0

ACBUS1

ACBUS2

ACBUS3

ACBUS4

ACBUS5

ACBUS6

ACBUS7

BDBUS0

BDBUS1

BDBUS2

BDBUS3

BDBUS4

BDBUS5

BDBUS6

BDBUS7

BCBUS0

BCBUS1

BCBUS2

BCBUS3

BCBUS4

BCBUS5

BCBUS6

BCBUS7

PWREN#

SUSPEND#

51

J16

56

HEADER 3

Manual selection for I2C/SPI

3

VCC1_8FT

16

17

18

19

21

22

23

24

26

27

28

29

30

32

33

34

38

39

40

41

43

44

45

46

48

52

53

54

55

57

58

59

60

36

1

2

3

C193

0.1uF

+3.3V

2

R171

4.7k

2

R230 DNI

R260

C194

0.1uF

R50

R60

R70

R1670

CDONE {6}

CRESETB {6}

+3.3V

J1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

header_1x8

R4960

R150

R160

R1800

R1810

Note : U21 Exposed pad must be soldered to a floating plane.

Do NOT connect to power or ground.

Title

Title

Title

FTDI INTERFACE

FTDI INTERFACE

FTDI INTERFACE

Size

Size

Size

Project

Project

Project

B

B

B

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

Date:

28-Mar-17

Date:

28-Mar-17

Date:

28-Mar-17

R2

4.7k

C196

0.1uF

1

TDO

TDI

TMS

TCK

1S1

1S2

2S1

2S2

3S1

3S2

4S1

4S2

1

+3.3V

R3

R1

4.7k

4.7k

R9

2k2

+3.3V

U21

2

VCC

16

D1

5

D2

8

D3

13

D4

3

123SEL

10

4SEL

11

GND

STG3693QTR

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

CSSPIN {4,5,6}

TCK {7}

TDI {7}

TDO {7}

TMS {7}

15

1

4

6

7

9

12

14

MCLK {6}

USB_SCL {6}

SISPI {4,5,6}

SPISO {4,5,6}

USB_SDA {6}

Schematic Rev

Schematic Rev

Schematic Rev

Board Rev

Board Rev

Board Rev

ofSheet

82

ofSheet

82

ofSheet

82

1.0

1.0

1.0

1

1

1

FTDI Interface

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02018-1.0 21

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 22

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

5

NOTE : INPUT VOLTAGE SHOULD BE 12V AT 3A Max

J3

1

3

D D

PJ-032A

5V

500mA traces

10uF

C94

C C

12

D3

Green

5V

B B

C23

10uF

5V

C114

A A

10uF

C130

2

10uF

GND3

NOTE : Place this gnd test point near J3

1

1

0.1uF

IN

C95

5V

R36

1K

U6

IN3OUT

TAB

GND

1

U17

IN3OUT

TAB

GND

1

C123

0.1uF

U15

OUT

GND

3

AP7313-12SAG-7

C20

10uF

500mA traces

R39 0

2

4

NCP1117ST25T3G

500mA traces

R192 0

2

4

NCP1117ST18T3G

U3

112

FUSE

2

U5

IN3OUT

GND

1

500mA traces

R165 0

TAB

12V

2

R144

R22

4.7k

4.7k

DNI

500mA traces

R37 0

2

4

NCP1117ST33T3G

VCC_2.5V

C24

22uF

C113

22uF

5V_INT

VBUS_5V

DNI

10uF

C96

600ohm 500mA

600ohm 500mA

ON BOARD POWER REGULATORS

5

SL44-E3/57T

SL44-E3/57T

VCC_1.2V

C21

22uF

L6

L7

D1

1 2

D14

1 2

0.1uF

C97

+2.5V

12

+1.8VVCC_1.8V

12

4

600ohm 500mA

600ohm 500mA

R499

1K

4

3

12V

J8

1

5V_SW

2 Position Terminal Block_0

+1.2V

L4

12

2 Position Terminal Block_0

+3.3VVCC_3.3V

L5

12

R233

470E

C115

10uF

1

2

2

5V_INT

J9

1

1

2

2

12

D25

Green

SW1

PWR

0.1uF

C29

12V

R229

15K

R230

34K

C127

680pF

+1.2V

R434 1

+1.2V

R435 1

+1.2V 1K_VCC_CORE

1K_VCC_CORE

5V5V_SW

12V

U18

LT3680

4

VIN

5

RUN_SS

9

VC

10

RT

7

PG

6

SYNC

LT3680

Manufacturer = Linear

PART_NUMBER = LT3680EDD#PBF

3

BD

FB

BOOST

SW

EPAD

R190 1

XO3-1K Voltage

Selection

12V0

1

8

2

3

11

J24

1V2

Snow Voltage

Selection

1V2

1

R231

536K

2V5

VCCIO1/2

3V3

Tri-Con

J25

2V5

VCCIO1/2

3V3

Tri-Con

+3.3V 1K_VCCIO0

+2.5V

GLOBAL POWER TEST POINTS

1V2

1

R232

100K

C128

0.47uF

4.7uH

D12

MBRA340T3G

0.3VF

2 1

4

4

1K_VCC_CORE1

+1.2V +2.5V

1

1

R25

2

R448

3

R21

1

R33

2

R449

3

R28

R410 1

R411 1

DNI

1K_VCCIO0

5V_INT

L8

2

1

1

1

1

1

1

1K_VCCIO0

1

2V5

2

+1.2V VCC_CORE

+2.5V

VCCIO1

+3.3V

VCC_CORE

+2.5V

VCCIO2

+3.3V

VCCIO0 VCCIO1

+3.3V 1K_VCCIO1

R184 1

+2.5V

R185 1

DNI

1K_VCCIO1 1K_VCCIO2

1

C129

47uF

Title

Title

Title

POWER REGULATOR I/F

POWER REGULATOR I/F

POWER REGULATOR I/F

Size

Size

Size

B

B

B

Date:

Date:

Date:

+3.3V VCCIO0

R19 1

+2.5V

VCC_CORE1

1

VCCIO0

1

+3.3V 1K_VCCIO2

R186 1

+2.5V

R187 1

DNI

1K_VCCIO1

1

3V3

+3.3V 5V

1

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

Project

Project

Project

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

28-Mar-17

28-Mar-17

28-Mar-17

R20 1

R24 1

DNI

1K_VCCIO2

1

1

+1.2V VCC_DPHY

VCC_DPHY

VCCIO1

1

+3.3V 1K_VCCIO3

R188 1

+2.5V

R189 1

1K_VCCIO3

5V0

GND2

1

1

1

R417 1

VCCIO2

DNI

GND1

1

Schematic Rev

Schematic Rev

Schematic Rev

Board Rev

Board Rev

Board Rev

VCC_DPHY1

1

1K_VCCIO3

1

GND4

1

ofSheet

83

ofSheet

83

ofSheet

83

VCCIO2

1

GND5

1

1.0

1.0

1.0

1

1

1

Power Regulator Interface

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

22 FPGA-EB-02018-1.0

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 23

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

5

D D

VCC_DPHY

100E

R51

VCC_DPHY

L11

120ohm 1.3A

VCC_DPHY

C C

120ohm 1.3A

B B

12

L10

12

C190

C41

0.1uF

2.2uF

16V

4V

C43

C189

2.2uF

0.1uF

4V

16V

C178

C45

0.1uF

2.2uF

16V

16V

Note :

1) Match length within pair as well as other pairs within 0.2mm

2)Differential impedance should be 100 Ohms and 50 Ohms as a single ended signals

3)All the power rails should be capable of carrying 1A current

4)Trace match P & N channels as well as individual pairs.

C4

VCCPLL_DPHY1

C6

VCCPLL_DPHY0

B5

GNDPLL_DPHYX

D3

VCCA_DPHY1

A5

VCCA_DPHY1

C3

GNDA_DPHY1

D7

VCCA_DPHY0

C7

GNDA_DPHY0

LIF-MD6000-6MG81I

U8D

4

DPHY1_CKP

DPHY1_CKN

DPHY1_DP0

DPHY1_DN0

DPHY1_DP1

DPHY1_DN1

DPHY1_DP2

DPHY1_DN2

DPHY1_DP3

DPHY1_DN3

DPHY0_CKP

DPHY0_CKN

DPHY0_DP0

DPHY0_DN0

DPHY0_DP1

DPHY0_DN1

DPHY0_DP2

DPHY0_DN2

DPHY0_DP3

DPHY0_DN3

A1

A2

B1

B2

A3

B3

C1

C2

A4

B4

A8

A9

B7

A7

B8

B9

B6

A6

C8

C9

CH5_DCK_TX_P

CH5_DCK_TX_N

CH5_DATA0_TX_P

CH5_DATA0_TX_N

CH5_DATA1_TX_P

CH5_DATA1_TX_N

CH5_DATA2_TX_P

CH5_DATA2_TX_N

CH5_DATA3_TX_P

CH5_DATA3_TX_N

CH4_DCK_TX_P

CH4_DCK_TX_N

CH4_DATA0_TX_P

CH4_DATA0_TX_N

CH4_DATA1_TX_P

CH4_DATA1_TX_N

CH4_DATA2_TX_P

CH4_DATA2_TX_N

CH4_DATA3_TX_P

CH4_DATA3_TX_N

3

CH4_DCK_TX_P

CH4_DCK_TX_N

CH4_DATA0_TX_P

CH4_DATA0_TX_N

CH4_DATA1_TX_P

CH4_DATA1_TX_N

CSSPIN

CSSPIN{2,5,6}

CH4_DATA2_TX_P

CH4_DATA2_TX_N

CH4_DATA3_TX_P

CH4_DATA3_TX_N

12V

CH5_DCK_TX_P

CH5_DCK_TX_N

CH5_DATA0_TX_P

CH5_DATA0_TX_N

CH5_DATA1_TX_P

CH5_DATA1_TX_N

CSSPIN

CH5_DATA2_TX_P

CH5_DATA2_TX_N

CH5_DATA3_TX_P

CH5_DATA3_TX_N

12V

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

43

44

41

U9

1

CH5_DCK_P

2

CH5_DCK_N

3

GND

4

CH5_DATA0_P

5

CH5_DATA0_N

6

GND

7

CH5_DATA1_P

8

CH5_DATA1_N

9

GND

10

SN

11

SCLK

12

GND

13

CH5_DATA2_P

14

CH5_DATA2_N

15

GND

16

CH5_DATA3_P

17

CH5_DATA3_N

18

GND

19

12V

20

12V

43

Shield3

44

Shield4

41

Shield1

U7

CH4_DCK_P

CH4_DCK_N

GND

CH4_DATA0_P

CH4_DATA0_N

GND

CH4_DATA1_P

CH4_DATA1_N

GND

SN

SCLK

GND

CH4_DATA2_P

CH4_DATA2_N

GND

CH4_DATA3_P

CH4_DATA3_N

GND

12V

12V

Shield3

Shield4

Shield1

RESETN

PWR_5-0V

PWR_3-3V

PWR_1-8V

PWR_1-8V

PWR_3-3V

TX Connector1

PWR_5-0V

Hirose - FX12 - 40 Pos

RESETN

PWR_5-0V

PWR_3-3V

PWR_1-8V

MOSI

MISO

PWR_1-8V

PWR_3-3V

TX Connector2

PWR_5-0V

Shield5

Shield6

Shield2

Hirose - FX12 - 40 Pos

GND

GND

GND

GND

MOSI

MISO

GND

GND

GND

GND

Shield5

Shield6

Shield2

TBD

GND

GND

GND

GND

GND

GND

GND

GND

SDA

SCL

TBD

SDA

SCL

2

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

45

46

42

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

45

46

42

5V +3.3V +1.8V

5V +3.3V +1.8V

GPIO1

GPIO2

GPIO1

GPIO2

DNI

1

RESETN

R4650

SDA

R4530

SCL

R4540

R4660

SDA

R4550

SCL

R4560

R4810 DNI

XO3_SCL {7}

R4820

XO3_SDA {7}

12V 5V +3.3V +1.8V

C155

0.1uF

R4180 DNI

R4190

DNI

R4200

R4210

SDA {6,7}

SCL {6,7}

RESETN

RESETN {5}

12V 5V +3.3V +1.8V

C159

0.1uF

C156

0.1uF

SISPI {2,5,6}

SPISO {2,5,6}

RPI1 {5}

RPI2 {5}

C161

0.1uF

C157

0.1uF

C160

0.1uF

C158

0.1uF

C162

0.1uF

A A

Title

Title

Title

MiPi Block - MIPI TX

MiPi Block - MIPI TX

MiPi Block - MIPI TX

Project

Project

Project

Size

Size

Size

B

B

B

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

Date:

28-Mar-17

Date:

28-Mar-17

Date:

5

4

3

2

28-Mar-17

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

1

Schematic Rev

Schematic Rev

Schematic Rev

Board Rev

Board Rev

Board Rev

ofSheet

84

ofSheet

84

ofSheet

84

1.0

1.0

1.0

1

1

1

MIPI Block – MIPI Tx

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02018-1.0 23

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 24

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

5

U8C

PB2A

PB2B

PB2C/MIPI_CLKT2_0

PB2D/MIPI_CLKC2_0

PB6A/GR_PCLK2_0

PB6B

PB6C

PB6D

D D

C C

LIF-MD6000-6MG81I

B B

SDA4{7}

SCL4{7}

A A

PB12A/GPLLT2_0

PB12B/GPLLC2_0

PB12C

PB12D

PB16A/PCLKT2_0

PB16B/PCLKC2_0

PB16C/PCLKT2_1

PB16D/PCLKC2_1

VCCIO2

VCCIO2

LIF-MD6000-6MG81I

U8B

PB29A/PCLKT1_0

PB29B/PCLKC1_0

PB29C/PCLKT1_1

PB29D/PCLKC1_1

PB34A/GR_PCLK1_0

PB34B

PB34C/MIPI_CLKT1_0

PB34D/MIPI_CLKC1_0

PB38A

PB38B

PB38C

PB38D

PB43C

PB43D

VCCIO1

VCCIO1

NOTE : PLACE ALL THE TERMINATION

RESISTORS ON TOP SIDE AND CLOSE

TO THE U8

CH0_DCK_P

CH0_DCK_N

CH0_DATA0_P

CH0_DATA0_N

CH0_DATA2_P

CH0_DATA2_N

CSSPIN

CSSPIN{2,4,6}

12V

R4610

R4620

CH2_DCK_P

CH2_DCK_N

CMOS_IO_1

CMOS_IO_2

R4710

R4720

5

F9

F8

G9

G8

E9

E8

H9

H8

F7

E7

J9

J8

D9

D8

J7

H7

E6

F6

G7

G6

J6

H6

D1

D2

J5

H5

E1

E2

J4

H4

J3

H3

F3

G4

CH0_DATA0_P

CH0_DATA0_N

EXT_RST

CMOS_IO_5

CH0_DATA2_P

CH0_DATA2_N

CH0_DATA1_P

CH0_DATA1_N

CMOS_IO_2

CMOS_IO_1

CH0_DATA3_P

CH0_DATA3_N

CH0_DCK_P

CH0_DCK_N

CH2_DCK_P

CH2_DCK_N

C51

100nF

16V

CH1_DCK_P

CH1_DCK_N

CH3_DCK_P

CH3_DCK_N

CH1_DATA1_P

CH1_DATA1_N

CMOS_IO_3

CMOS_IO_4

CH1_DATA0_P

CH1_DATA0_N

CH1_DATA3_P

CH1_DATA3_N

CH1_DATA2_P

CH1_DATA2_N

C58

100nF

16V

U12

1

CH0_DCK_P

2

CH0_DCK_N

3

GND

4

CH0_DATA0_P

5

CH0_DATA0_N

6

GND

7

CH0_DATA2_P

8

CH0_DATA2_N

9

GND

10

SN

11

SCLK

12

PWR_12V

13

SDA1

14

SCL1

15

GND

16

CH2_DCK_P

17

CH2_DCK_N

18

GND

19

CH2_DATA0_P

20

CH2_DATA0_N

43

Shield3

44

Shield4

41

Shield1

Hirose - FX12 - 40 Pos

C198

100nF

16V

C197

100nF

16V

C200

10uF

C199

10uF

RX Connector1

4

J29

CON3

Default short (J29.2,J29.3)

123

VCCIO2 VCCIO0

R56

DNI

RESETN

R4500

4.7k

VCCIO2

Note :

1) Match length within pair as well as other pairs within 0.2mm

2)Differential impedance should be 100 Ohms and 50 Ohms as a single ended signals

3)All the power rails should be capable of carrying 1A current

4)Trace match P & N channels as well as individual pairs.

VCCIO1

5V +3.3V +1.8V

12V

21

PWR_12-0V

22

RESETN

23

PWR_5-0V

PWR_3-3V

PWR_1-8V

MOSI

MISO

PWR_1-8V

GND

GND

PWR_3-3V

PWR_5-0V

SDA

SCL

Shield5

Shield6

Shield2

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

45

46

42

4

R4690

R4700

CH0_DATA1_P

CH0_DATA1_N

CH0_DATA3_P

CH0_DATA3_N

CH2_DATA1_P

CH2_DATA1_N

CMOS_IO_1

CMOS_IO_2

CMOS_IO_3

CMOS_IO_4

R4750

CH0_DATA1_P

CH0_DATA1_N

CH0_DATA3_P

CH0_DATA3_N

GPIO3

GPIO4

CMOS_IO_3

CMOS_IO_4

R4630

R4640

R54 470E

DNI

R55 470E

R57 470E

DNI

DNI

R59 470E

DNI

RESETN

SDA2 {7}

SCL2 {7}

3

D6

blue

1 2

D7

blue

1 2

D8

blue

1 2

D9

blue

1 2

EXTERNAL RESET

12V 5V +3.3V +1.8V

C167

0.1uF

C169

0.1uF

C168

0.1uF

3

SDA3{7}

SCL3{7}

CMOS_IO_5

EXT_RST

SW4

TL1015AF160QG

C170

0.1uF

R491

100E

CH1_DCK_P

CH1_DCK_N

CH1_DATA0_P

CH1_DATA0_N

CH1_DATA2_P

CH1_DATA2_N

CSSPIN

CH3_DCK_P

CH3_DCK_N

VCCIO2

R445

4.7k

C184

1uF

2

5V +3.3V +1.8V

U11

1

CH1_DCK_P

2

CH1_DCK_N

3

GND

4

CH1_DATA0_P

5

CH1_DATA0_N

6

GND

7

CH1_DATA2_P

8

CH1_DATA2_N

9

GND

10

SN

11

12V

R4570

R4580

R4670

R4680

R492

47K

SCLK

12

PWR_12_0V

13

SDA1

14

SCL1

15

GND

16

CH3_DCK_P

17

CH3_DCK_N

18

GND

19

CH3_DATA0_P

20

CH3_DATA0_N

43

Shield3

44

Shield4

41

Shield1

Hirose - FX12 - 40 Pos

EXT_RST

R4460

2

CH1_DATA1_P

CH1_DATA1_N

CH1_DATA3_P

CH1_DATA3_N

CH3_DATA1_P

RX Connector2

CH3_DATA1_N

Title

Title

Title

BANK1,2 - LVDS RX

BANK1,2 - LVDS RX

BANK1,2 - LVDS RX

Size

Size

Size

Project

Project

Project

B

B

B

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

Date:

28-Mar-17

Date:

28-Mar-17

Date:

28-Mar-17

12V

21

PWR_12V

22

RESETN

23

PWR_5-0V

24

25

26

PWR_3-3V

27

28

29

PWR_1-8V

30

MOSI

31

MISO

32

PWR_1-8V

33

GND

34

GND

35

PWR_3-3V

36

37

38

PWR_5-0V

39

SDA

40

SCL

45

Shield5

46

Shield6

42

Shield2

GPIO3

GPIO4

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

1

R4760

CH1_DATA1_P

CH1_DATA1_N

CH1_DATA3_P

CH1_DATA3_N

GPIO3

GPIO4

R4590

SDA1 {7}

R4600

SCL1 {7}

12V 5V +3.3V +1.8V

C163

C165

0.1uF

VCCIO1

CMOS_IO_1

CMOS_IO_2

CMOS_IO_3

CMOS_IO_4

C164

0.1uF

0.1uF

R4220 DNI

SISPI {2,4,6}

R4230

DNI

SPISO {2,4,6}

R4240

RPI1 {4}

R4250

RPI2 {4}

J28

1

2

3

4

5

6

CON6

Schematic Rev

Schematic Rev

Schematic Rev

Board Rev

Board Rev

Board Rev

1

RESETN

C166

0.1uF

ofSheet

ofSheet

ofSheet

RESETN {4}

1.0

1.0

1.0

1

1

1

85

85

85

Bank 1, 2 – LVDS Rx

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

24 FPGA-EB-02018-1.0

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 25

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

5

WAKE_UP

U8A

D D

C C

PB47/PCLKT0_0/USER_SDA

CDONE/PB49/PMU_WKUPN

PB48/PCLKT0_1/USER_SCL

LIF-MD6000-6MG81I

NOTE : PLACE SWITCH IN THE TOP SIDE

SW2

TL1015AF160QG

PB50/MOSI

PB51/MISO

PB52/SPI_SS/CSN/SCL

PB53/SPI_SCK/MCK/SDA

CRESET_B

VCCIO0

100E

R489

CRESETb

C183

1uF

J2

H2

F2

F1

J1

G1

H1

G2

G3

VCCIO0

R131

4.7k

R490

47K

CON3

J36

SW5

TL1015AF160QG

R4150

R4160

NOTE : PLACE R83 Close to U8 device

USB_SCLUSB_SDA

123

SYS_RST

CRESETB

CON3

J35

123

J7

1

2

CON2

CLK_SDA

CDONE

CLK_SCL

SISPI

SPISO

PLACE CLOSE TO U8

12V

B B

12

R441

3K

D26

Green

MMBT2222A

5V

R442

1K

12

D27

Green

32

1

Q9

R78

10K

R395 10K

CRESETB

+1.2V

5V

Q10

MMBT2222A

R443

1K

12

D28

Green

32

4

CDONE {2}

SISPI {2,4,5,6}

SPISO {2,4,5,6}

CSSPIN

CSSPIN {2,4,5,6}

R8330E

MCLK

CRESETB

C176

C202

100nF

10uF

16V

PLACE CLOSE TO U8

J4

12

3

4

50 Ohm Clock Route

5

73391-0060

J22

12

3

4

50 Ohm Clock Route

5

73391-0060

1

R399 10K

+1.8V

MCLK {2,6}

CRESETB {2}

VCCIO0

R1830

CLK_EXT_REF

R4330

Q11

MMBT2222A

CLK_EXT

5V

1K

12

32

R444

SDA{4,7}

SCL{4,7}

D29

Green

1

VCCIO0

R76

2K

SDA

SCL

VCCIO2

C98

100nF

10V

VCCIO2

C179

100nF

10V

R400 10K

R77

2K

4

4

OSCILLATOR

X3

VDD4STDBY#

2

GND

KC3225A27.0000C30E0A

X4

VDD4STDBY#

2

GND

KC3225A27.0000C30E0A

+2.5V

3

In3

In3

R160

100K

OSCILLATOR

R432

100K

MH1

ThruHole

J26

1

In1

2

Out

3

In2

Tri-Con

J27

1

In1

2

Out

3

In2

Tri-Con

NOTE : PLACE X3 NEAR U8

1

NOTE : R159 SHUOULD BE PLACED

NEAR X3

3

0

OUT

R159

NOTE : PLACE X4 NEAR U8

NOTE : R431 SHUOULD BE PLACED

1

NEAR X4

R431

3

0

OUT

VCCIO0

MCLK

SISPI

SPISO

CSSPIN

MH2

ThruHole

CLK_INT

CLK_SDA

CLK_EXT

CLK_INT_REF

CLK_SCL

CLK_EXT_REF

J18

1

3

5

7

9

HEADER 5X2

CLK_INT

CLK_INT_REF

2

4

6

8

10

MH3

ThruHole

2

VCCIO0

R498

R497

2K

2K

USB_SDA

USB_SDA{2}

USB_SCL

USB_SCL{2}

SISPI{2,4,5,6}

MCLK{2,6}

CSSPIN{2,4,5,6}

CON2

1

2

J19

TP18

VCCIO0

R80

680R

CDONE

12

Green

D10

SDA

SCL

CDONE

MH4

ThruHole

MH5

NOTE : PLACE SPI FLASH IN THE TOP SIDE

IT SUPPORTS 2.5/3.3 V

R166

1K

U14

8

5

VCC

SDI

6

SCK

3

WP

1

CS

GND

4

U8E

D6

GND

F4

GND

E5

GND

C5

GND

D4

GND

F5

GNDGPLL

LIF-MD6000-6MG81I

PLACE DECOUPLING CAPACITORS CLOSE TO THE U8 POWER PINS

C188

C185

10uF

0.1uF

0

0

1

ThruHole

R412

R413

VCC_CORE

SPI FLASH

2

SDO

SPI FLASH

7

HOLD

M25PX16-VMW6TG

VCC

VCC

VCCAUX25VPP

VCCGPLL

C187

C186

0.1uF

0.1uF

E3

E4

D5

G5

C204

100nF

1

VCCIO0

C49

100nF

R125

10K

R4470

C203

2.2uF

4V

10V

SPISO {2,4,5,6}

VCC_CORE

+2.5V

12

L12 120ohm 1.3A

R124

R123

10K

10K

R4140

C70

100nF

16V

16V

A A

5

4

MH6

ThruHole

3

MH7

ThruHole

MH8

ThruHole

MH9

ThruHole

MH10

2

ThruHole

Title

Title

Title

BANK0, Flash I/F

BANK0, Flash I/F

BANK0, Flash I/F

Project

Project

Project

Size

Size

Size

B

B

B

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

Date:

28-Mar-17

Date:

28-Mar-17

Date:

28-Mar-17

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

1

Schematic Rev

Schematic Rev

Schematic Rev

Board Rev

Board Rev

Board Rev

ofSheet

86

ofSheet

86

ofSheet

86

1.0

1.0

1.0

1

1

1

Bank0, Flash Interface

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-EB-02018-1.0 25

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 26

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

5

1K_VCCIO0

C143

C145

0.1uF

D D

C C

B B

A A

10uF

1K_VCCIO1

C151

C153

0.1uF

10uF

NOTE : PLACE SWITCH IN THE TOP SIDE

SW3

TL1015AF160QG

100E

R487

VCCIO0

R440

4.7k

C182

1uF

U19A

D6

VCCIO0

PT12C/SCL/PCLKTO_0

PT12D/SDA/PCLKC0_0

LCMXO3LF-1300E-5MG121C

U19B

H5

VCCIO1

BANK1

PR5D/PCLKC1_0

PR5C/PCLKT1_0

LCMXO3LF-1300E-5MG121C

XO3_RESET

R488

47K

BANK0

PT12B/PCLKC0_1

PT10D/TDI

PT12A/PCLKTO_1

PT17C/INITN

PT15D/PROGRAMN

PT15C/JTAGENB

PT11D/TMS

PT11C/TCK

PT17D/DONE

PT10C/TDO

PR2C

PR2D

PR2A

PR3B

PR3A

PR2B

PR4D

PR4C

PR4B

PR4A

PR5A

PR5B

PR8A

PR8B

PR8C

PR8D

PR9A

PR9B

PR9C

PR9D

PR10A

PR10C

PR10D

PR10B

XO3 RESET

5

PT9A

PT17A

PT16A

PT15A

PT11A

PT10A

PT17B

PT16B

PT15B

PT11B

PT10B

PT9B

PT9C

4

1K_VCCIO2

A10

A2

A3

A4

A5

A6

A7

A8

A9

B2

B3

B4

B5

B6

B7

B8

B9

C3

C4

C5

C6

C7

C8

D4

D7

R4520

XO3_RESET

R4510

INITN

PROGRAMN

JTAGENB

DONE

SCL

SCL {4,6}

12MHZ {2}

TDI {2}

SDA

SDA {4,6} SCL2 {5}

TMS {2}

TCK {2}

TDO {2}

R403

4.7k

C150

10uF

R404

4.7k

1K_VCCIO0

R405

4.7k

I/O Expander - I2C Muxing

1K_VCCIO3

B1

C1

C2

D1

D2

D3

E1

E2

E3

E4

F1

F2

F3

1K_VCC_CORE

F4

G1

G2

G3

G4

H1

H2

H3

H4

J1

J2

J3

K1

1K_VCC_CORE

C107

10uF

4

C141

10uF

U19E

D5

VCC

E5

VCC

F7

VCC

G7

VCC

LCMXO3LF-1300E-5MG121C

PLACE DECOUPLING CAPACITORS CLOSE TO THE U19 POWER PINS

C106

C104

0.1uF

0.1uF

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

0.1uF

C105

0.1uF

C142

C139

0.1uF

A1

A11

E6

E7

F5

F6

G5

G6

L1

L11

C102

0.1uF

C147

0.1uF

C140

0.1uF

3

2

1

CON3

3

J32

D8

F8

H8

3

VCCIO2H6PB6D/SO/SPISO

BANK2

LCMXO3LF-1300E-5MG121C

U19D

VCCIO3

PL2C/L_GPLLT_IN

VCCIO3

PL2D/L_GPLLC_IN

VCCIO3

PL3A/PCLKT3_2

PL3B/PCLKC3_2

PL2A/L_GPLLT_FB

BANK3

PL2B/L_GPLLC_FB

PL5B/PCLKC3_1

PL5A/PCLKT3_1

PL9B/PCLKC3_0

PL9A/PCLKT3_0

LCMXO3LF-1300E-5MG121C

U19C

PB6C/MCLK/CCLK

PB11B/PCLKC2_1

PB9B/PCLKC2_0

PB11A/PCLKT2_1

PB9A/PCLKT2_0

PL4A

PL4B

PL3C

PL4C

PL4D

PL3D

PL5C

PL8B

PL8A

PL8D

PL8C

PL10D

PL10A

PL10C

PB4A

PB18D

PB18C

PB15C

PB11D

PB4B

PB4C/CSSPIN

PB20D/SI/SISPI

PB20B

PB18B

PB15B

PB9C

PB6A

PB4D

PB20C/SN

PB20A

PB18A

PB15A

PB9D

PB6B

B10

B11

C10

C11

C9

D10

D11

D9

E10

E11

E8

E9

F10

F11

F9

G10

G11

G8

G9

H10

H11

J10

J11

K11

DEBUG1

DEBUG2

DEBUG3

DEBUG4

H7

H9

J4

J5

J6

J7

J8

J9

K10

K2

K3

K4

K5

K6

K7

K8

K9

L10

L2

L3

L4

L5

L6

L7

L8

L9

DEBUG1

DEBUG2

DEBUG3

DEBUG4

LED1

LED2

LED3

LED4

1K_VCCIO3

R483

4.7k

2

XO3_SPISO

XO3_SPICLK

XO3_SPISI

XO3_SPICS

1K_VCCIO2

R485

4.7k

R484

4.7k

1

2

3

4

4 HEADER

2

1K_VCCIO2 1K_VCCIO0

R480

R176

R175

4.7k

4.7k

R486

4.7k

XO3_SCL {4}

XO3_SDA {4}

J23

XO3_SPISO

XO3_SPISI

XO3_SPICLK

XO3_SPICS

R478

R177

R477

R178

4.7k

4.7k

4.7k

4.7k

HEADER 5X2

LED1

LED2

LED3

LED4

Title

Title

Title

I2C Expander

I2C Expander

I2C Expander

Size

Size

Size

Project

Project

Project

B

B

B

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

Date:

28-Mar-17

Date:

28-Mar-17

Date:

28-Mar-17

R479

4.7k

4.7k

J31

1

3

5

7

9

R436 470E

R437 470E

R438 470E

R439 470E

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

1

R500

680R

12

SDA1 {5}

Red

SCL1 {5}

D23

SDA2 {5}

SDA3 {5}

SCL3 {5}

SCL4 {5}

SDA4 {5}

1K_VCCIO01K_VCCIO2

2

4

SDA

6

SCL

8

DONE

10

D30

blue

1 2

D31

blue

1 2

D32

blue

1 2

D33

blue

1 2

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Lattice Semiconductor Applications

1

DONE

Schematic Rev

Schematic Rev

Schematic Rev

Board Rev

Board Rev

Board Rev

ofSheet

87

ofSheet

87

ofSheet

87

1.0

1.0

1.0

1

1

1

I2C Expander

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

26 FPGA-EB-02018-1.0

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Page 27

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

5

Routing guidlines for MIPI & LVDS

----------------------------------

D D

1)All differential routes are required to have the same length between the positive (true) and the negative (complimentary) routes.

Spacing between the positive (true) and the negative (complimentary) shall be 2 times trace width.

4

3

2

1

2)Target differential impedance shall be 100 Ohms

3)Trace length matching to be within 1.0 mm (40 mil) across the entire bus.

4)Use small humps for skew corrections

5)Place signal vias close together and remove copper in between vias.

Traces to be fully shielded with GND stitching terminating at both trace end points

6)Board trace impedance results must be within ±10 percent of target and

Power plane impedance to be within +/- 10 percent of target at operating frequency

C C

MIPI &LVDS Simulation Requirement

----------------------------------

1)MIPI Differential Mode insertion Loss shall be > -1.6dB at 750 MHz

2)MIPI Differential Mode Return Loss shall be < -15dB at 750 MHz

3)MIPI Common Mode Return Loss shall be < -15dB at 750 MHz

4)LVDS differential mode return loss shall be < -16.5db at 600 MHz

B B

5)LVDS common mode return loss shall be < -16.5db at 600 MHz

6)LVDS insertion loss shall be > -1.7db at 600 MHz

7)LVDS Cross coupling shall be < -22 dB for victim IO at 600MHz

8)Power plane impedance to be within +/- 10 percent of target at operating frequency

A A

Title

Title

Title

Layout Guidelines

Layout Guidelines

Layout Guidelines

Size

Size

Size

Project

Project

Project

B

B

B

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

CrossLink_Master_Multi-Link_Board

Date:

28-Mar-17

Date:

28-Mar-17

Date:

5

4

3

2

28-Mar-17

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Lattice Semiconductor Applications

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

Email: techsupport@Latticesemi.com

1

Schematic Rev

Schematic Rev

Schematic Rev

Board Rev

Board Rev

Board Rev

ofSheet

88

ofSheet

88

ofSheet

88

1.0

1.0