Publication TSM 20-319

TECHNICAL MANUAL

1KW UHF INTERNALLY D IPLEXED TV TRANSMITTER

MX1000U SERIES

LARCAN INC.

228 AMBASSADOR DRIVE

MISSISSAUGA, ONTARIO

CANADA L5T 2J2

PHONE: (905) 564 -9222

FAX: (905) 564 -9244

Rev 1: March 2003

1

INTRODUCTION

This manual describes the LARCAN model MX1000U, internally diplexed UHF television

transmitter.

LARCAN all -solid-state 1 kW UHF transmitters are designed to operate conservatively at 1 kW

peak sync visual/vision RF power and 100W average aural/sound single carrier RF power, with

superb performance, reliability and operating economy. The MX1000U transmitter accepts an

on-channel internally diplexed (in a 10:1 ratio vis to aur/snd) composite driving signal of 10 mW

peak visual RF, as input to its RF chain.

The 1 kW transmitter is self-contained within a single 19" cabinet with an integral cooling fan and

filtered rear door air intake. The simplicity of design, the employment of modular subassemblies,

and the use of standard readily available components, also enhances serviceability.

Important transmitter parameters are monitored, and can be displayed on the meters built into the

transmitter control panel. Additionally, telemetry readings are made available as DC signals for

monitoring by remote control systems. The MX1000U, like all other LARCAN transmitting

equipment, is suitable for unattended remote-control operation.

AMPLIFIER CHAIN (REFER TO FIGURE 1)

The Aural signal of the transmitter is diplexed (at IF) with the visual/vision signal within the exciter

(hence the term "internally diplexed), and is amplified in common with the visual signal in the

above amplifier chain (hence the term common amplification).

The internally diplexed composite RF output of the exciter/translator is fed to a 4-way active

splitter. The 4 outputs of the splitter are fed to conservatively designed broadband solid-state

amplifiers. The outputs from the four PA modules are combined for the tot al transmitter output

power. These amplifiers require no tuning or adjustment. Phasing for the four PA modules is

done at the splitter level. Internal cable lengths and precise production tolerances allow for a very

small adjustment range for phasing. Simplicity of operation, reduced maintenance costs and

increased reliability are a few of the major benefits derived from this modular amplifier design.

The modules are operated well below their maximum ratings.

Each RF power amplifier (PA module) is fully modular within itself and each module has a gain

equivalent to the entire gain of the transmitter (see Figure 2). Each PA module has it's own

preamplifier, Intermediate PA, Driver and PA section. The front end preamplifier on the PA

module monitors an d provides soft startup, overdrive and VSWR protection for the module itself

(independent of the transmitter protection). The output stage of the module consists of three

amplifier "pallets" each consisting of two push-pull LDMOS FET amplifiers that operate in class

AB, and are combined in quadrature. The outputs of these pallets are further combined in a 3way combiner. The amplifier module is rated for 350 watts, and in the present four PA module

system is operated at a total transmitter power of 1 kW sync peak + 100 watts aural/sound. The

module is provided with a test jack for monitoring.

The amplifier output is fed to the bandpass filter and a directional coupler, which provides a small

sample of forward and reflected output power for metering, AGC and VSWR supervisory

functions. An additional sample is available for monitoring and transmitter setup. The transmitter

output then passes to the antenna system.

TRANSMITTER CONTROL

The control circuitry in this solid state transmitter is straightforward and simple. The use of

latching type relays ensures that the transmitter state (on/off, or trip status) is “remembered”

under power failure conditions. Interlocking is provided for loss of airflow and for over

temperature conditions. An additional interlock connection point is provided for interlocking the

transmitter to an external patch panel.

2

Facilities are provided on the control board for telemetry, status, and control connections to and

from a remote control system. Thes e are available on 25 pin D-sub connector.

For remote control operation, simply press the REMOTE switch (LED illuminated). This places

+12V on Remote Enable line and allows the transmitter to be turned on and off via remote

control. In this mode the tra nsmitter cannot be turned on locally but for safety purposes, the

transmitter can always be turned off locally while in REMOTE.

The Remote Enable +12V appears as an arming signal at J5-5. A momentary connection of this

+12V to J5 -13 turns the transmitter ON, and momentary connection of the +12V to J5-8; turns the

transmitter OFF.

Control circuit power for the transmitter is supplied by two redundant power supplies wired in

parallel. The failure of either power supply will not affect the operation of the transmitter.

The transmitter's power supply consists of two ferro-resonant transformers each with dual

secondary windings. Each transformer secondary feeds a rectifier/filter and linear regulator

combination. The regulator modules are located inside the rear door of the transmitter and can be

removed for servicing by first disconnecting the two cables and then unplugging the module. This

can be done without turning off the transmitter.

A two pole fused disconnect or breaker is required for transmitter connection from line-to-line.

The transmitter is wired per Figure 5.

• Press the OFF button on the control panel. Pull out the regulators so they are no longer

mating with their respective AC power connectors. Turn on the power supply breakers. Press

the ON button. Looking into the back of the transmitter DS6 and DS7 on the AC distribution

board should be illuminated (refer to figure 3). If the blower comes on and DS6 and DS7do

not, then the AC Distribution board needs to be bench tested.

• Press the OFF button again. Install the regulators but disconnect the cables that mate at the

top of each regulator (connecting the regulators to the PAs). Turn on the transmitter.

Measure the voltage on the output connectors of the regulators. The voltage should be 28V

(±0.5V) for each regulator. Note: Since the regulators have no load, when the transmitter is

subsequently turned off it will take a while for the voltage to decay down to zero.

• Turn off the transmitter. Reconnect the cables to the regulators. Turn the RF drive level

down as far as it will go at the appropriate OUTPUT LEVEL/RF OUTPUT adjustment on the

exciter. Alternatively, disconnect the drive from the output of the exciter. Turn on the

transmitter. Using a clamp-on current meter, measure the current going from the regulators to

the PA's. Measure the current going through the +28V supply cables and not the return

cables (some of the ground current may return through the transmitter chassis as opposed to

the return wires, causing the current reading to be lower than it actually is). The 28V supply

cables are the two lower wires in the cable assembly (Figure 4). These are accessible by

pushing back the protective covering on the cable. The front panel current meter (the digital

LCD meter) can now be calibrated for each PA module. (Remember that the modules are

numbered 1-4 from left to right across the front of the transmitter. This will be reversed when

looking into the rear of the cabinet.) The corresponding adjustment pot on the control panel

(PC board 20C2065G1) is listed below.

PA1 Pot R221 PA2 Pot R225

PA3 Pot R229 PA4 Pot R223

These adjustments can be accessed by opening the hinged control panel on the front of the

transmitter.

• Disable the AGC using the front panel AGC Enable switch. Note: the AGC is disabled when

the LED on the enable switch is off. Increase the output power from the exciter until 100%

3

operating power in achieved. Use a thru-line type Wattmeter to measure the transmitter

power. Select FWD on the analog meter select switch and adjust R164 on the control board

until the forward power meter (analog meter) reads 100%.

• To calibrate the aural power, refer to the RF detector board description and setup procedure.

• Calibration of the reflected power metering and the VSWR cutback and trip is detailed next.

Note, this setup was done at the factory initially, and should not be adjusted unless absolutely

necessary. Conditions that would warrant this adjustment include the replacement of the RF

detector assembly or the control PC board.

• Turn R130 fully CW and R138, and R128 fully CCW

• The Reflected power meter reading corresponds to 10X the actual power reflected. That is,

when the reflected power meter reads 100%, this means 10% of the output power is being

reflected (ie: there is a VSWR of 1.9:1 at the transmitter output). (10dB match). To calibrate

the meter for this level, the forward sample port that feeds the RF detector circuitry for

metering is fed through a 10dB attenuator back to the reflected power input on the RF

detector board. To do this, disconnect the cable at the forward port of the output directional

couple and connect Reflected power sample cable through a 10dB pad to the forward power

port. This simulates having a 10dB mismatch on the output of the transmitter. Not e: AGC

must be disabled during this procedure. Adjust R117 until a 100% reading is achieved on the

RFL power setting of the analog meter.

• Change the attenuation from 10dB to 16db of the forward power into the reflected port on the

metering board. Adjust R138 so that the power just starts to cutback slightly

• Adjust R130 so that the VSWR CUTBACK LED just turns on.

• Change the attenuation to 13dB. The cutback circuit should cut the power way back. Adjust

R128 so that the transmitter trips and locks out with VSWR.

• Now change the attenuation to 14 dB of forward power into the reflected port on the metering

board. Adjust R128 so that the transmitter does not trip and lockout with VSWR. You may

have to press reset, adjust the pot, press reset, adjust the pot, et c. Then repeat the previous

step to verify that the transmitter still trips with 13 dB of reflected power.

• Reconnect the forward and reflected sample cables to the directional coupler as they were

before. Verify that the AGC buttons can raise and lower the power levels.

4

TABLE OF CONTENTS

1. INTRODUCTION .........................................................................................................................1

2. CIRCUIT DESCRIPTION..............................................................................................................2

Visual Forward And Combined Reflected Circuit Description..............................................................2

Aural Forward Metering ....................................................................................................................3

3. TEST AND CALIBRATION...........................................................................................................3

Test Equipment For Board Tests On The Bench: ...............................................................................3

Test Procedure ................................................................................................................................4

4. PARTS LIST...................................................................................Error! Bookmark not defined.

LIST OF FIGURES

Fig Title

1 RF Detector Board (Photo)

2 Test Equipment Setup for Bench Test

3 Assembly Drawing 41D1607

4 Schematic Diagram 41D1607S

1. INTRODUCTION

RF Power levels throughout the transmitter are sampled in directional couplers, and the resulting RF

samples are detected and appropriately processed to provide DC outputs corresponding to the amplitude

of the desired parameter of the input signal. These DC outputs contribute to the AGC/VSWR supervision

of the transmitter as well as the front panel metering.

The 41D1607G1 and 41D1607G3 dual RF detectors are designed for measuring forward visual/vision

signal, forward aural/sound signal and reflected combined visual and aural signal. Group 1 is for NTSC

and group 3 is for PAL. The circuitry provides DC outputs corresponding to the instantaneous

visual/vision forward and reflected RF levels at the back porch (blanking level) of the modulated signal, so

that the DC output remains proportionally constant regardless of the video signals to the transmitter. Two

virtually identical detector circuits reside on a single board for visual forward and reflected metering.

Detection sensitivity of the circuitry for reflected visual/vision power is approximately 10 dB greater than

for the visual/vision forward RF detector circuit. Group 1, (for NTSC) and group 3, (for PAL) differ only in

their colour subcarrier frequency, consequently in a few component values.

The aural/sound metering circuit takes a sample of detected video signal from forward port and provides

DC level proportional to the amplitude of the aural carrier. The sample of this DC level is used to

compensate visual forward reading affected by presence of the aural carrier at the forward po rt. The

reflected port does not have this compensation circuit so in reality reflected reading is combined visual

and aural power.

The 41D1607G2 and 41D1607G4 dual RF detectors are similar, but have identical detection sensitivities

for each circuit. They are designed for use in parallel amplifier systems. Group 2 is for NTSC and group

4 is for PAL; again, these differ only in colour subcarrier frequencies. The two ports J2 and J3 are not

identical. J2 has aural metering circuit and compensation circuit for the presence of aural carrier at J2

port. J3 will measure combined visual and aural power unless special trap is used to reject aural carrier

1

Figure 1: RF Detector Board

2. CIRCUIT DESCRIPTION

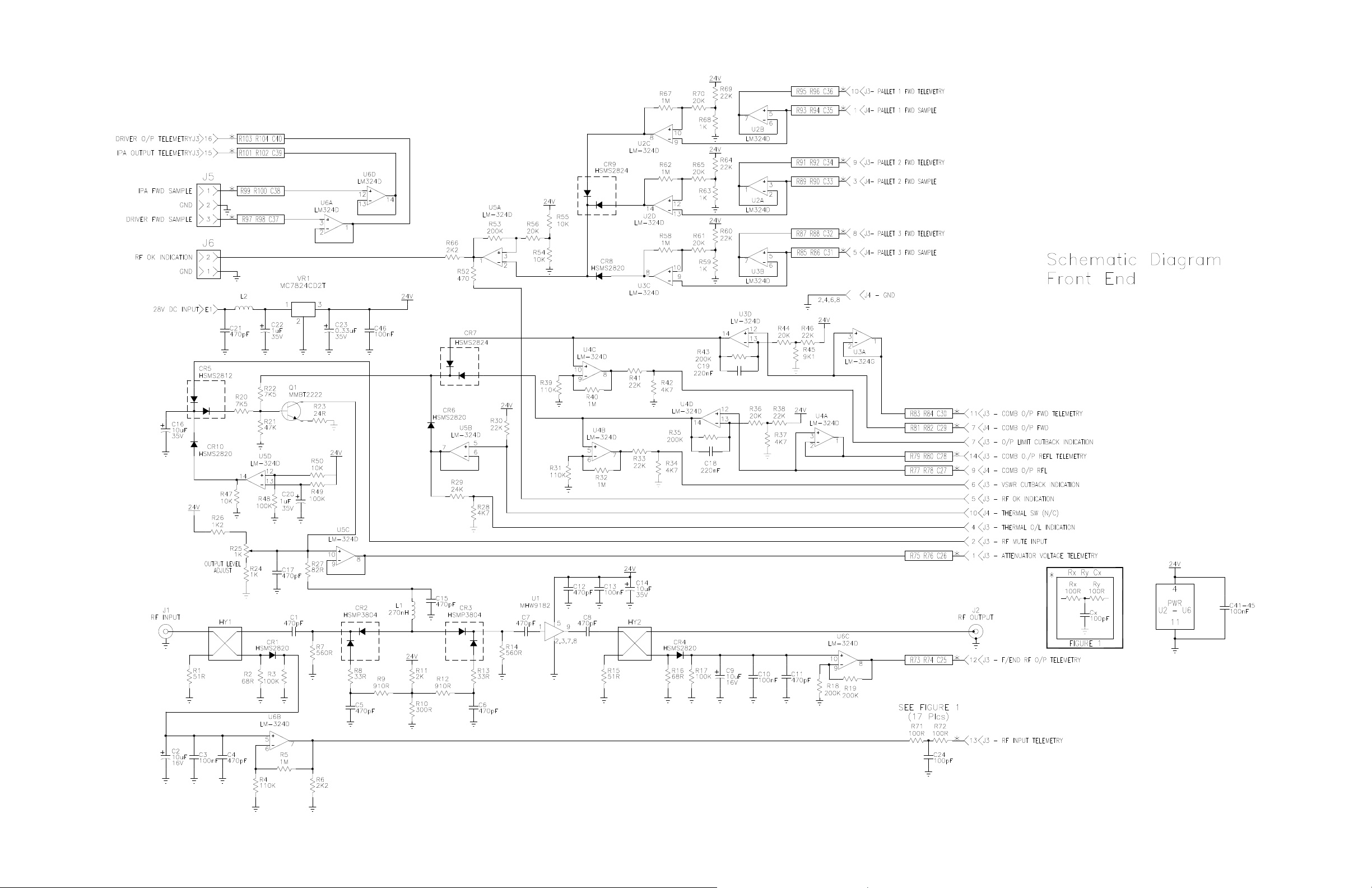

Drawing references: 41D1607 sheet 1 (Figure 3), and 41D1607S sheet 1 (Figure 4).

The visual/aural RF Detector board is fitted with two RF detectors, which respond to RF samples fed from

RF directional couplers mounted on transmission lines in the amplifier cabinets and/or on external probe

sections. The modulation envelope blanking level is measured because it remains constant, regardless

of the picture content of the transmission. Measurement sampling occurs during the back porch.

Both sections of the board are almost identically configured, except for the component numbering, system

gains and the function names given in schematic Figure 2. Because the same discussion applies to both

circuits, we will describe the first one only, but refer to the second one during the description by enclosing

the relevant component numbers in parentheses ( ).

VISUAL FORWARD AND COMBINED REFLECTED CIRCUIT DESCRIPTION

(REFER TO 41D1607S SHEET 1)

The RF sample is applied to input J2 (J3) and is terminated by R2 (R34). CR1 (CR3) and Q1 (Q6) form

an envelope detector. CR1 (CR3) is forward biased slightly by R1 (R33) and R3 (R35) to overcome CR1

(CR3) conduction threshold voltage, thereby improving detection linearity. Q1 (Q6) is forward biased by

R3 (R35) as well, and when RF is applied, Q1(Q6) is driven in the direction of turn off during each

positive-going half cycle, thus causing its emitter voltage to become more positive, and in effect forming a

linear envelope detector.

C50 (C51) utilizes the lead inductances of CR1 (CR3) and Q1(Q6) to form a Tee network, which provides

a matching section that improves the UHF signal transfer between the devices.

Q1(Q6) and CR1 (CR3) have similar temperature coefficients, and the opposing connection of the two in

this back-to-back configuration, provides temperature compensation.

Finally, Q1(Q6) serves as a low impedance video source to drive the colour traps FL2, FL4 and aural

traps FL1, FL3 which remove the colour subcarrier burst and aural carrier from the back porch.

Subsequent downstream sampling circuits monitor the blanking level, therefore require a clean back

2

porch. The detected video signal is phase split by Q2 (Q7) to produce two 180 ° out of phase signals. The

inverted video signal, after being buffered by Q11(Q13), is fed to input pin 11 of sync separator Ul (U8).

Ul (U8), pin 7 is an open collector "mute" output, which switches off when adequate horizontal sync

pulses matching the setting of R28 (R57) are present, lighting CR2 (CR4) the "sync ok" LED. If a TV sync

signal is not detected, pin 7 collector goes low, and CR2 (CR4) is turned off. When sync is detected, the

sync output at pin 9 delivers a positive-going composite sync pulse, which turns on Q5 (Q10) whose

collector then goes low. If no sync is detected by Ul (U8), its pin 9 remains LOW, and Q5 (Q10) remains

off.

After the pin 9 pulse has finished, Q5 (Q10) turns off and its collector output goes high. This low -to-high

transition activates blanking multivibrator U2 (U7), and an active low pulse is fed to Q3 (Q8), turning it on.

Q4, C5, and U4A (Q9, C22, and U6B) form a sample -and-hold circuit that samples the signal originating

from the emitter of Q2 (Q7) and which is buffered by Q12 (Q14). Sampling occurs during the back porch,

and holds during the subsequent horizontal line. This DC sample is amplified in U4A (U6B).

Because a "single supply" op-amp is used at U4 (U6), the output seen on TP9 (TP10) will contain a small

DC offset which must be minimized because low level signals are near ground/earth potential. With no

RF input, this offset voltage is adjusted by potentiometer R10 (R42) as near as possible to zero. A

residual voltage offset of 10 to 20 millivolts can be expected.

Outputs from unity gain op -amps U4A, U4B(U5A, U5B) drive the forward (reflected) power metering

circuits, and provide telemetry and AGC (VSWR) signals.

Bench test calibration consists of adjusting the level to U4A (U5A) on R13 (R43) with calibrated, properly

modulated input: The forward input at J2 should be 200 mW in 50Ω, (J3 Reflected input 20 mW for both

the 41Dl607G1 ,3 boards, or for 41D1607G2,4 boards the J3 Combined input 200 mW), and the voltage

observed at TP1 (TP2) should read 4.0 volts DC for full scale calibration.

AURAL FORWARD M ETERING

A sample of the signal detected by CR1 from J2 is buffered by Ql and high -pass filtered by R90, C55 and

the input impedance of Q15. R92 and R91 set the base bias for Q15 while R93 and R94 set the gain of

the stage to approximately 4.7 for the 4.5 MHz (5.5 MHz) aural intercarrier signal. The wideband

visual/aural signal drives FL1, an aural bandpass filter. This filter is chosen to match the broadcast

standard used. C59 couples the filtered aural signal to common emitter amplifier Q17 which is direct

coupled to common base amplifier Q16. The bias for these stages is set by resistors R95, R96, R97.

C57 and C58 provide bypassing. Q16 is a current amplifier with L7 as the collector load and C60 provides

frequency compensation.

The aural signal is then fed to a peak voltage detector consisting of CR6, C63 and R102. U9A provides

DC amplification of the detected signal. Amplifier gain is set by potentiometer R104 such that the DC

level at TP8 is in the range of 7VDC. This provides eno ugh "safety" range for the signal not to saturate

yet enough level to reliably give a 4VDC calibration at TP3.

3. TEST AND CALIBRATION

TEST EQUIPMENT FOR BOARD TESTS ON THE BENCH :

RF Detector test fixture, comprising a 12 volt DC power supply, suitable connectors for the board to be

tested, a signal generator, a modulator, and an amplifier good for 200 milliwatts output. An exciter will

suffice for the generator and modulator, but its output is good for a maximum +10 dBm (10 mW) therefore

3

TEST EQUIPMENT REQUIRED

requires an external amplifier, and the exciter aural output may be used as an unmodulated source if

required (A LARCAN exciter visual/vision section can not deliver unmodulated RF).

TEST PROCEDURE

For test setup, see Figure 2.

1. Connect board under test to power supply. Apply

ground on pin 7 & 8 of J2 and apply +12v (± 0.2 V) to

pins 3 & 4. Do not apply RF to J2 and J3 yet.

2. Adjust R111 max CW.

3. Adjust R10 to get a min voltage at Ul0-1 (TP9).

4. Check the voltage between U10 -2 and U10-3. It

should be no more than 10 mV.

• 12 V power supply

• UHF preamplifier (approx

200mWo/p).

• Video Generator.

• Modulator.

• UHFUpconverter.

• Oscilloscope.

• Spectrum Analyzer.

• VHF / UHF Two Way Splitter.

5. Adjust R42 to get a minimum voltage at U6-7 (TP10).

6. Check the voltage between U6-6 and U6 -5. It should

be no more than 10 mV.

7. Set R104 in mid position.

8. Apply staircase modulated RF signal from UHF upconverter to J2 and J3 through splitter

according to Table 1. The signal should include aural carrier 10 dB lower than visual sync peak.

Check this level on the spectrum analyzer. Note: Make sure to set spectrum analyzer resolution

RBW to 300 kHz to see sync peak level.

Assembly Group G1/G3 G2/G4

Connector J2 J3 J2 J3

Visual Peak

23 13 20 20

Signal

[dBm]

TABLE 1.

9 Adjust R104 for 7.5 ± 0.5 V at TP8.

10 Adjust R107 for 4V at TP3.

11 Adjust R28 so that CR2 lights up.

12 Adjust R57 so that CR4 lights up.

13 Using the oscilloscope, check that there are positive 12V pulses at TP4 and TP5.

14 Check DC voltage at TP9.

15 V

should be within 4.5V to 9.5V.

TP9

16 Check DC voltage at TP10.

17 V

should be within 4.5V to 9.5V.

TP1O

18 Turn off the aural carrier.

19 Adjust R13for4VatTP1.

20 Turn on the aural carrier.

21 Adjust R111 for4V at TPl.

22 Repeat steps 12 and 13 until voltage at TP1 stays the same with and without aural carrier.

23 Adjust R43 for 4 V at TP2 with aural carrier on.

4

Figure 2. Test Setup For Visual + Aural RF Detector Assembly.

5

TABLE OF CONTENTS

1. INTRODUCTION .........................................................................................................................1

2. CIRCUIT DESCRIPTION..............................................................................................................1

Front End Preamp. ........................................................................................................................1

IPA Module ....................................................................................................................................2

Pallet ..............................................................................................................................................3

Module Interface Board....................................................................................................................4

3-Way Splitter .................................................................................................................................4

3-Way Combiner .............................................................................................................................4

3. TESTING AND TROUBLESHOOTING ..........................................................................................4

Front-End Preamp ...........................................................................................................................5

Intermediate Amplifier (IPA) ............................................................................................................5

4. PARTS LIST...................................................................................Error! Bookmark not defined.

1. INTRODUCTION

The PA module for the MX1000 is a high gain linear amplifier.

Each PA module includes its own preamplifier, intermediate

amplifier, driver amplifier and power amplifiers. The gain of

the module is equal to the gain of the entire transmitter. Every

PA module has its own on -board protection against overdrive,

excessive VSWR and over temperature. A single LED on the

front panel indicates the status of the module. Any fault will

cause this LED to turn off.

2. CIRCUIT DESCRIPTION

FRONT END PREAMP.

The RF input to the module is via J1. U1 provides the amplification of the signal for this stage. This IC is

an 18dB gain broadband hybrid amplifier. The output of this stage to the following amplifier (IPA) stage is

through J2. A directional coupler HY1 provides a sample of the input power for a detector CR1, C2

through C4 and buffer amplifier U6B and associated components. A PIN attenuator circuit consisting of

CR2, CR3, R8 through R13 and C5 and C6 provides the means for controlling the signal gain through the

front-end stage. A higher voltage applied to this attenuator through L1 results in less attenuation through

the PIN attenuator and hence, more gain through the preamp unit. A further coupler HY2 provides an

output sample to a detector and buffer circuit (CR4 and U6C). The maximum gain of the front -end

preamplifier is approximately 8dB, however, in practice, the gain is adjusted to compensate for gain

differences in other stages such that the gain of each PA module is the same.

The three -way combiner circuit for the PA module incorporates a bi-directional coupler with detectors for

forward and reflected power on the module. These detected voltage samples for forward and reflected

power are fed into the front -end preamp through J4-7 and 14. Comparator circuitry is used to detect

either overdrive conditions or VSWR conditions. Since the circuitry is identical for both forward and

reflected, a circuit description will be given for the forward power circuit only.

U3D is configured as a comparator with the reference voltag e being provided by the voltage divider

consisting of R44, 45, 46. Note: this level is preset. Values for this voltage divider should not be

Figure 1: PA Module, MX1000

1

modified. Doing so without prior authorization from factory service personnel will void any warranty.

When the detected voltage rises above the preset level, the output of the comparator U3D goes high, and

forces transistor Q1 to the "on" state through diode CR7. Other inputs to Q1 include the reflected

(VSWR) signal, an external mute signal and a power-up delay circuit consisting of U5D configured as a

comparator along with R47 through R50 and C20. The action of turning on Q1 causes the voltage on the

PIN attenuator, preset by R25, to be shunted through the transistor, thus increasing the attenuation of the

PIN attenuator.

Additional circuitry on the front -end preamplifier also drives the logic for the Green LED on the front panel

of the PA module. Output samples from each of the power amplifier pallets are monitored and compared

with preset voltages through comparators U2C, U2D and U3C. A failure of the output of any one of these

pallets will cause the output of U5A to drop and the LED (connected to J6) to be extinguished. Note: this

applies if the input RF signal is removed and thus results in no output from the module (as well as in the

case of an overdrive situation or VSWR cutback situation).

There are buffered signals for the various stages on the PA module that are brought to the front-end

preamp and routed through to the interface board on the rear of the PA module. These signals are

present on the 25 pin connector (intended as an on-site troubleshooting port). In the MX 1000

application, these signals are present but most are not

monitored by the transmitter's control circuitry.

IPA MODULE

The intermediate amplifier consists of two FET

amplifiers, type MRF181 paralleled in RF phase

quadrature, and operated in class A. Amplifier static

bias control and over-current protection is provided by

an industry -standard type µA723 regulator IC, U1.

The overall gain of the Intermediate Amplifier is a

nominal 15 dB over the band.

The input signal is split evenly by quadrature hybrid

splitter HY1. Each FET gate is matched with the equivalent of an L network followed by a π network.

Capacitors C100 and C110 provide DC blocking of the gate voltage. A couple of low impedance

microstripline sections along with adjustable capacitor (C101 or C111) to ground and the gate

capacitance of the FET form the L-C-L-C matching network for the input circuit. This matching

arrangement is good for operation from 470 through 860 MHz, adjustable capacitors C101 and/or C111

provides for a flat frequency response over the range.

The output circuit is similar except it uses narrower (higher impedance) microstriplines because the drain

impedance of the FET is higher. The output matching network is adjustable with variable capacitor C103

or C113. Again, this capacitor is adjusted only to provide flat response over the 470 to 860 MHz range.

An output coupling capacitor C104 or C114 completes the match to 50 ohms; two amplifier outputs are

combined in a quadrature hybrid HY2.

Bias to the gates of the FETs passes through R100 or R110 from balance controls RV100 or RV110. The

bias regulator Ul uses an µA723 (MC1723CD) to provide approximately 6½ volts to the gate bias controls

RV100 & RV110. Voltage divider R5, R6 provides the inverting input of the regulator error amplifier with a

sample of the output voltage, and the wiper of RV3 provides the non inverting input with its reference

signal which is an adjustable fraction of the 7.15 V built -in reference of the µA723. The adjustment of

RV3 therefore should be able to give an output within the range from zero to approximately 9 volts. R4,

C2, C1, R3, and C4 provide frequency-compensation and maintain regulator stability.

Figure 2: IPA Module

2

Drain current of the two FETs is sampled by the voltage drop across R7. When this voltage exceeds

approximately 0.5V at normal operating temperature (about 1.5 amps total FET current), Q3 begins

conduction and feeds voltage to pin 2 of the regulator to start its current foldback/limiter circuit.

The regulator reduces its output voltage, which in turn reduces the bias on the FETs, they decrease their

drain currents, reducing the voltage drop across R7 and over-current protection is achieved. CR1

protects Q3 emitter -base junction from current inrush to C3 and C107 charging during start-up.

PALLET

The following description applies to the

driver amplifier as well as the circuitry

used in each of the three sub-modules

comprising the final PA stage of the PA

module. The difference being that the

driver consists of a single device

amplifier (called a “half-pallet”) while the

final stage are based on dual FET

amplifiers with an integral 3dB hybrid

combiner. Referring to the schematic

diagrams (figures 14 and 16) one will

notice that even the component

numbering is similar. The following

description is for the dual FET version of Figure 4: Driver

the amplifier (refer to fig 16).

The stripline balun developed at LARCAN is a practical implementation of the coaxial cable based

solution on a broadside-coupled horizontal stripline structure. It is made up of three printed circuit boards

of high dielectric material bolted together. Using this structure, very tight coupling can be achieved, thus

emulating the properties of a coaxial transmission line balun. With this arrangement, the characteristic

impedance and degree of coupling can be controlled through geometric dimensions. This circuit is the

subject of a patent application.

The amplifier pallet (full-pallet) couplers also include hybrid 3dB couplers as part of the multi-layer

stripline circuit. The resultant output of the coupler assembly is two pairs of equal and opposite phase

signals 90 degrees out of phase (that is, a set of signals at 0° and 180 °, and a set of signals at 90° and

270°).

Transistors Q1 and Q2 are Lateral N-Channel Broadband Push-Pull Power MOSFETs. One side of the

amplifier is described.

Components C6 through C11 and C52 along with the associated printed

circuit traces form the matching network to the gate of the push pull

transistor Q1. L2 and R2 along with L3 and R3 are low frequency parasitic

arrestors. Similarly, C14 through C15 and C53 along with associated

stripline traces provide output matching on the drain of the device. C6, C8,

C16 and C18 also provide DC blocking of the supply and bias voltage. C7

is factory adjusted for a flat frequency response from 470 to 860 MHz.

DC power enters the module through a screw terminal connection and is

fed to the main circuit board through a series of jumpers. 28V is fed to the

drains of the FETs via L5 and L6 with bypass capacitors C13, C25, C20,

C22 and C28. Bias for the devices is via L1/L4 with bypass capacitors C1,

C2, C5 and C12. The bias voltage is adjusted via R12 and R11, from a

regulated source provided by Ul. R12 sets the overall bias and R11

3

provides adjustment for balance between Q1 and Q2. Thermistors R21 and R22 provide therm al stability

for the bias.

MODULE I NTERFACE BOARD.

This PC board is located on the rear of each PA module. The RF input and DC input to the module

enters via this interface board. Four fuses are located on this board. Three fuses are in line with the 3

output PA pallets and one with the front end, IPA and driver modules. These fuses serve to protect the

circuitry from damage in the event of a device failing in the short circuit condition. This is part of the “soft

failure" mechanism of the PA modules. Because the normal failure mode of a transistor is a short circuit,

and we desire to keep the rest of the PA module functioning in the event of a failure, the fuse effectively

disconnects the failed circuit from the regulator, allowing it to supply the rest of the module.

The interface board performs a number of other signal routing functions. Various signals from the different

stages of the module are routed through this board to connectors. In the case of the MX1000, many of

these signals are not routed any further, but are present on the connector (J3).

3-WAY SPLITTER

The three -way splitter is a stripline implementations of a 1.76dB hybrid/3 dB hybrid combination. It is a

mechanical structure consisting of 3 PC boards sandwiched together to form the stripline structure. The

middle layer board thickness along with the trace locations determine to the largest extent the coupling.

J4 feeds a 1.76dB splitter. The input power to this splitter is divided 1/3 – 2/3 between the two outputs.

The 1/3 output is fed to J3 and the 2/3 output is fed to a further 3dB hybrid coupler. The two outputs of

this coupler are fed to J1 and J2. The termination load for the reject port of the 1.76dB splitter is at the far

end of the board from J4 and the termination load for the 3dB coupler is located at the edge of the board

between J2 and J3. J5 is connected to a directional coupler on the input to the splitter and is not used in

this configuration.

3-WAY COMBINER

The three -way combiner is essentially the mirror of the 3-way splitter. J1 and J2 are coupled to the inputs

of a 3 dB hybrid coupler. The output of this combiner is fed to the input of a 4.77dB hybrid coupler along

with the input from J3. The output of this coupler appears at J4. R6 serves as the balance load for the

3dB coupler while R7 serves as the balance load for the 4.77 dB coupler. Each of the inputs to this

combiner have a directional coupler and detector circuit that feeds a DC sample of the output of each

pallet to the sensing circuitry on the front -end module. As well, a directional coupler on the output of the

combiner has detectors for both the forward and reflected power samples of the output. All the

information fed back to the front -end appears at J11. Additionally, a second directional coupler provides

an RF sample that is fed to a front panel test point via J5.

3. TESTING AND TROUBLES HOOTING

Basic troubleshooting of a PA module is as follows. The front panel

LED is extinguished if one or more output amplifier pallet levels are

lower than nominal preset level. As mentioned earlier, if the drive is

removed from the module(s), the output of the amplifiers also satisfy

this condition and thus the LED will be off. In this case, there is

nothing wrong with the amplifier. Therefore, if all the LEDs are off,

the first place to look is at the output of the exciter.

If a fault condition exists (LED off) on a single module, the first place

to check is the PA module interconnect board where all the fuses are

installed. A blown fuse will most often indicate a defective amplifier

pallet. Most times, this will be the problem and replacing the

defective amplifier and fuse will rectify the problem. If, however,

there are no blown fuses, there are other areas to check. Figure 6: Fuses

4

The front panel current meter will give an indication of the current drawn by the modules in comparison to

one another both under drive conditions and under static bias conditions. Check the current under drive

conditions for overdrive situations and under static bias conditions (no drive) for amplifier stage failure.

Check for potential connector problems causing either no drive to a module (input connector) or VSWR

(output connector) problems. Also, if you suspect an over temperature condition, be extremely careful

when pulling out a module as the heatsink may be too hot to hold onto comfortably.

The following procedures are essentially the same procedures used during factory testing. Basically, if

there is no suspected problem with a particular stage, we would recommend not performing these

procedures.

FRONT-END P REAMP

• Short Pin J4-10 to ground (this can be accomplished by placing a small jumper across J4-10 and J4-

8). This simulates a good thermal switch.

• Connect a +28V power supply to E1 and ground.

• Apply a 0dBm (1mW) RF input to the amplifier.

• Turn R25 fully clockwise. The preamp should have minimum gain (approx. 7dB). Adjusting R25 from

one extreme to the other should vary the gain 4dB.

• Check RF output telemetry. There should be 1.5V ±0.5V at J3 -12.

• Check the RF input telemetry. There should be 1.0 ±0.2 V at J3-13.

• Check the RF attenuator voltage telemetry. There should be 5.4V ±0.2V at J3 -1

• Check Thermal switch status indication. J3-4 should be 0V.

• Remove the jumper from J4-10 to J4 -8. (This simulates the thermal switch opening). The voltage at

J3-4 should be high (4 Volts ±0.5V) and J3-1 should be 0V.

• Replace the jumper across J4 -10 and J4-8.

• RF Mute check: Connect a variable supply, to J3-2. Gradually increase the voltage until the gain

drops by 30dB or more. The applied voltage should be approximately 2.5 volts.

• Reflected Power Cutback check: Connect the variable supply to J4-9. Increase the voltage gradually

until the gain drops by 30dB or more. The voltage should be approximately 4.0Volts ±0.2V. This

same voltage should also be present at J3-14. J3 -6 should be 4.0 volts.

• Overdrive Cutback check: Connect the variable supply to J3-7. Increase the voltage until the gain

drops by 30dB or more. The voltage should be 7 volts ±0.5V. The voltage at J3 -11 should be the

same and the voltage at J3 -7 should be 4.0 volts.

• Set the adjustable supply to 2 volts. Connect this voltage to J4-1, J4 -3 and J4-5 simultaneously. J2-

6 and J3 -5 should be high. Disconnecting any one or more of J4-1,3 or 5 should cause both J2 -6 and

J3-5 to go low (0V).

INTERMEDIATE AMPLIFIER (IPA) BENCH TEST PROCEDURE :

This amplifier must be mounted on a properly sized heatsink for testing.

• Connect a suitable load to the output of the IPA.

• On the IPA under test, set RV200 fully clockwise and set RV110 fully counter-clockwise.

• Set variable power supply to 28.0 volts and set its current limit to 1 ampere.

• Apply the +28V to the feedthrough capacitor of the IPA shield box.

• Adjust RV3 to achieve 6.5 ±0.2 volts at the junction of R5 and RV100.

• Adjust RV200 to achieve total current draw of 500 ±20 mA.

• Check that the junction of R100 and CR100 measures between 3.5 and 5.5 volts.

• Adjust RV110 to raise total current draw to 1000 ±50 mA.

• Check that the junction of R110 and CR110 measures between 3.5 and 5.5 volts.

• Increase the power supply current limiting to 2.2 Amps.

5

• Increase RV3 clockwise slowly and check that the maximum current limits itself at 1.6 ±0.1 Amp but

do not allow current to go above 2 amps while performing this test.

• Reset RV3 to achieve 6.5 ±0.2 volts measured at the junction of R5 and RV100.

• Check balance of the two transistors with a voltmeter connected between the hot sides of C105 and

C115; difference voltage should be less than 3 mV.

• Apply RF drive (max. +18dBm to IPA) and adjust C101, C103, C111, and C113 for minimum

frequency response ri pple and flat response. Gain should be a minimum of 15 dB with maximum

variation less than 0.5 dB over the frequency range 470 MHz through 860 MHz (Note: IPA output will

then be about +33dBm or 2 Watts, so make sure you properly protect your test equipment).

• If roll off at the higher frequencies prevents meeting this gain-bandwidth specification, it may be necessary to

replace either C103 or C113 or both with a higher value; use variable capacitor made by Johanson, part #

16E2320-2, which is 2.5 to 10pF.

6

1

TABLE OF CONTENTS

1. INTRODUCTION .............................................................................................................1

2. BLOWER REPLACEMENT ..............................................................................................1

3. COMBINER AND REJECT LOAD.....................................................................................1

4. THERMAL SWITCH AND AIR SWITCH ............................................................................2

Thermal Switch ...................................................................................................................2

Air Switch............................................................................................................................2

5. PARTS LIST.......................................................................Error! Bookmark not defined.

LIST OF FIGURES

Fig. Description

1. Roof of Transmitter

2. Access to Blower

3. Thermal Switch/Air Switch Location

1. INTRODUCTION

The following description, while described as the module housing for the transmitter, in essence,

comprises the additional assemblies and circuits that are not included in the other assemblies

described in this manual. They include such assemblies as the Blower, the 4-way combiner and

reject load assemblies for the overall output, the various interface circuitry and the protection

circuitry. The “housing” is basically the assembly that brings all these items together.

2. BLOWER REPLACEMENT

The Blower is located on the top of the module housing. It is accessible through the top of the

transmitter. The blower is a backward curved motorized impeller. The motors have no

adjustments and need no maintenance. The bl ower motor bearing life should be on the order of

100,000 hours. Should the blower fail for any reason, the replacement is relatively simple. The

entire blower and motor assembly can be removed through the top of the cabinet.

Figure 1: Roof of Transmitter Figure 2: Access to Blower

3. COMBINER AND REJECT LOAD

The 4-way combiner used in the transmitter is basically a combination of three 3dB hybrid

couplers. Two couplers form the first level of combining and a third combines the outputs of the

first two for the final output. These combiners require balancing loads, or reject loads. The loads

2

are located in the module housing on an assembly similar to the module assembly. The Reject

load assembly is within the cooling air plenum and comprises all three reject loads for the

combiners. This reject load assembly is not removable when the transmitter is under power and

as such incorporates SMA connectors and is held in place additionally by screws through the rear

of the module housing. A sample of the input to each of the loads is provided on the front panel

of the reject load assembly. These samples can be used for setting up of the 4-way splitter.

Phase and gain of each power amplifier signal path can be adjusted to minimize the power in

these reject loads.

4. THERMAL SWITCH AND AIR SWITCH

THERMAL SWITCH

The thermal switch is located on the air duct

between the module housing and the blower. It

can be accessed by opening up the control panel.

The thermal switch, through its mounting on the air

duct essentially monitors the outgoing air

temperature of the module housing. The metal in

the duct itself serves to ‘average’ the temperature

in the duct. It is connected to the TEMP interlock

circuitry in the control electronics.

Figure 3: Thermal Switch/Air Switch Location

AIR SWITCH

The Airflow switch consists of a power resistor mounted back to back with a thermal switch. The

air that flows through the transmitter flows across this assembly, cooling the resistor. If the airflow

is compromised, the resistor is not cooled properly and thus heats up. At a certain temperature,

the thermal switch will open, shutting off the power supplies and thus protecting them from

damage. The thermal switch mounted on the resistor should not be confused with the

transmitter thermal protection.

The air switch is designed to detect the presence of air flow throughout the normal operating

temperature range of the transmitter and in fact operates, und er normal conditions at a much

higher temperature than the maximum operating temperature of the transmitter itself. The sole

purpose is to detect the presence of air flow, and in the case of reduced, or no air flow, the

resistor/thermal switch combination overheats and shuts off the supplies. WARNING: AC

VOLTAGE IS PRESENT ON THE AIR SWITCH RESISTOR. DO NOT REMOVE THIS

ASSEMBLY WITHOUT FIRST DISCONNECTING AC FROM THE TRANSMITTER.

TABLE OF CONTENTS

1. INTRODUCTION .............................................................................................................................1

2. CIRCUIT DESCRIPTION..................................................................................................................1

3 TEST AND TROUBLESHOOTING ....................................................................................................1

General...............................................................................................................................................1

Troubleshooting ..................................................................................................................................2

Splitter Setup ......................................................................................................................................2

4. PARTS LIST.......................................................................................Error! Bookmark not defined.

1. INTRODUCTION

The 4-way splitter provides four evenly balanced, equal amplitude, properly phased signals to each of the

PA modules in the transmitter. The intention is to provide the ability to fine match the phasing and gain of

the amplifiers such that they combine with the minimum of reject power. It has been found that normal

production tolerances do not cause wide variations in phasing between amplifiers and thus the control over

the output phase is limited to a relatively narrow range. At different channels, some touch-up of phasing

might be desireable in order to finely balance the PAs, although, it is not absolutely necessary.

2. CIRCUIT DESCRIPTION

The RF enters this splitter via J5 and is applied to a PIN attenuator circuit comprised of CR1 and CR2 and

associated circuitry. The attenuator voltage to this circuit is applied through L1 via buffer amplifier/ inverter

Q1. A higher voltage at E2 results in more attenuation through the PIN attenuator. E2 is fed from the

transmitters AGC/VSWR circuitry.

The signal at the output of the PIN attenuator is fed to a hybrid 3dB coupler HY1. The two outputs from HY1

are fed to two more hybrids HY2 and HY3. The result is four outputs, equal in amplitude but differing in

phase. Each of the four signals is then passed through a phasing network and a furt her PIN attenuator for

the purpose of balancing the transmitter phase and gain overall. All four balancing circuits are identical

therefore only the circuit that supplies PA1 will be described.

The phasing adjustment is accomplished by using two varactor diodes CR100 and CR101, connected to the

output ports of a 3dB hybrid coupler HY4. If the impedance of these pure reactances is kept equal, the

signal is reflected back through to the isolation port of the hybrid with a change in phase and minimal loss.

The reverse bias on the varactor diodes is controlled through R101 and R102/R103. Attenuation adjustment

is controlled by varying the bias across CR102 via R108 through R111. This has the effect of shunting

some signal to ground. R110 controls the coarse level adjustment and R109 controls the fine adjustment.

U1 is a signal buffer amplifier. The signal is then passed through a final coupler which provides a sample to

a detector circuit and to the output connector J1.

3 TEST AND TROUBLESHOOTING

GENERAL

Because the splitter, in its normal operation provides the phasing and balance for the modules in the

transmitter, often times, if the balance between modules is incorrect, the splitter is the first suspected

problem area. One must be very careful troubleshooting under these conditions. What may be suspected

as a gain or phase imbalance can simply be a problem with a PA module. In addition, in the field it may be

difficult to quantify phase relationships between signals without a network analyzer. As mentioned

elsewhere in this manual, the transmitter has been delivered to site in a fully functioning condition. As

designed, the phasing controls in the splitter circuitry will allow up to approximately 30 degrees of phase

1

shift. The bulk of the phase relationship between the signal is developed within the hybrid splitters

themselves. Additionally, the gain controls on the splitter is only for fine matching of the module outputs.

TROUBLESHOOTING

If trouble is suspected with the splitter unit itself, the following checks may be done to pinpoint the cause of

failure.

• Turn off the transmitter

• With +12V connected to E1, verify that there is +8V (±0.1V) at pin 3 of VR1.

• Disconnect the AGC signal to E2.

• With signal applied at the input use a spectrum analyzer, to verify that there is signal at each of the four

output ports. Note; if one of the output ports is significantly lower (10dB) than the rest, this may indicate

a problem in that particular circuitry.

• With a variable sup ply connected to E2, verify that the output levels of each port drop at least 30dB with

a voltage of 3.0 Volts.

SPLITTER SETUP

Fine balancing of the splitter outputs is accomplished with the transmitter operating at full power. Refer to

Figure 1 below. Firstly, the phasing and gain balance must be done between the inner level of combining,

that is between PA1 and PA2 and between PA3 and PA4. Then, carefully, the phasing must be done

between the PA1/PA2 combination and the PA3/PA4 combination.

The simplest way to balance the phase and gains is to monitor the reject

load power. On the front of the reject load assembly, there are various

sample ports for such purpose. The relative phasing and gain is adjusted

to minimize the signal level at these ports.

• Balance all four PA output levels. This is best done with a spectrum

analyzer connected to each sample port in turn and adjusting R110,

R210, R310 and R410 to adjust the level of its respective PA module

output.

• With the transmitter operating at full po wer, connect a spectrum

analyzer to reject load sample port for PA1/PA2. See figure 3.

• Adjust either R101 or R201 (one or the other, not both) to minimize the

measured signal at this sample port.

• Connect the spectrum analyzer to reject load sample port for PA3/PA4.

• Adjust either R301 or R401 (one or the other, not both) to minimize the

measured signal at this sample port.

• Connect the spectrum analyzer to the transmitter overall reject load

sample port.

• Carefully adjust phase adjustment pots R101 AND R201 together to

minimize the measured signal at this sample port (alternately

R301/R401 pair can be adjusted instead).

• Repeat the above steps to further reduce reject levels. Note: do not

use the gain adjustments to attempt to minimize reject load power.

2

*

*

R97 R98 C37

*

*

R85 R86 C31

R87 R88 C32

***

R73 R74 C25

*

*

R75 R76 C26

*

R77 R78 C27

R79 R80 C28

*

*

R81 R82 C29

R83 R84 C30

*

*

R89 R90 C33

R91 R92 C34

*

R95 R96 C36

R93 R94 C35

*

*

*

FIGURE 1

Rx Ry Cx

11

U2 - U6

PWR

4

1

TABLE OF CONTENTS

1. INTRODUCTION .............................................................................................................1

MX1000 Power supply.........................................................................................................1

Linear Regulator..................................................................................................................1

2. CIRCUIT DESCRIPTION..................................................................................................2

Rectification........................................................................................................................2

Regulation Circuitry .............................................................................................................2

Control Circuitry ..................................................................................................................2

3. TESTING AND TROUBLESHOOTING ..............................................................................5

4. PARTS LISTS.....................................................................Error! Bookmark not defined.

1. INTRODUCTION

MX1000 POWER SUPPLY

The MX1000 power supply consists of two transformers, each with dual (isol ated) secondary

windings. Each power amplifier module is fed from a 60A linear voltage regulator. The output

voltage of each regulator is 28 Vdc. The input of the regulator assembly fed from the secondary

of the ferro-resonant transformer secondary winding is 35 Vac. The AC power to the

transformers is supplied via a contactor on the AC distribution board. This contactor is controlled

through the transmitter’s control board, ensuring that all interlock and overload conditions are

observed.

LINEAR REGULATOR

The 60A linear voltage regulator is a ‘generic’ term for the entire plug-in assembly that performs

more than simply a regulation function. In essence, the Linear regulator assembly is an

independent power supply (less the transformer), performing rectification, regulation and self

protection. Assembly is accessible through the rear of the transmitter and can be removed from

service without turning off the transmitter. (For the purposes of description in this text, the ‘front’

of the linear regulator will be designated as the end with the handle, which is in actuality, located

at the rear of the transmitter). Obviously, removing a regulator will disable the associated power

amplifier and result in a lower output power. The AC input to the regulator is fed through the rear

of the regulator and the control, status and telemetry connections as well as the DC output fed to

the PA is located at the front of the module.

Figure 1: Linear Regulator Assy.

2

2. CIRCUIT DESCRIPTION

The linear regulator assembly incorporates the following circuitry:

• A semiconductor -controlled rectifier bridge, the input filter capacitor and power resistors (Q1,

C1 and R63, R64 respectively). This circuitry is shown in block A on the schematic diagram.

• The Voltage Regulator itself (block B).

• The control circuitry (block C,D,E,F,G )which provides a few different functions including

over-current protection, over-voltage protection and power -on and reset functions.

RECTIFICATION

Refer to block ‘A’ on the schematic diagram 40D1680S.

Rectification of the AC from the transformer secondary winding is performed by a semiconductor-

controlled bridge (SCR) rectifier, Q1. Capacitor C1 performs the filtering function. The

advantage of using a semi-controlled rectifier bridge instead of a conventional rectifier bridge is

significant. In normal operating conditions the bridge is constantly on because the opto-coupled

triacs, U33 and U34 ar e active. Thus Q1 behaves as a conventional rectifier bridge. In the case

of serious damage to the regulator unit the control can isolate the transformer secondary from the

rest of the transmitter by turning off the bridge (turning on U32). The power resistors R63, R64

are bleeder resistors, to safely discharge filter capacitor C1, when the unit is pulled out of the

transmitter.

REGULATION CIRCUITRY

Refer to block ‘B’ on Schematic Diagram 40D1680S.

The voltage regulator circuitry consists of a low current linear voltage regulator, U1 utilizing an

external high power pass transistor, giving the regulator the required current capability for this

application. The combination of pnp transistor Q3 and npn power transistor Q2, creates the

equivalent of a high power npn pass transistor.

OR gate U25d activates, as required by the various overload commands from the control circuitry,

The output of this gate is applied to the internal shut down circuitry of U1 -2. The command for

over-voltage shutdown is applied through U25d-12 and the command for over-current is applied

through U25d-13.

The output voltage setting for this regulator is provided by R18, R19 and R20. Additional

regulator output filtering is provided by C8 through C12

CONTROL CIRCUITRY

Control Circuit Operation

a. Over-current.

Whenever an over-current or short -circuit condition occurs the control

circuit will shut down the output of the regulator, wait for 3 seconds

and try to restart. A fault is indicated by two LEDs lighting up, a red

LED (previous trip) which latches on showing that a trip has been

recorded and counted and a yellow LED (over -current) which is on for

the 3 second shutdown duration only. After three trips a red LED

(lockout) will come on until a reset command is received, resetting all

counters and restarting the cycle.

b. Over-voltage

The operation of the overvoltage protection circuitry is much the same

Figure 2: Front

Panel Indicators

3

as that of the overcurrent circuitry with a couple of exceptions. One of the common

causes of failure in a series linear regulator is the short circuit of the series pass

transistor. Once the pass transistor has shorted, there is no way to shut down the

regulator output (to prevent over-voltage damage to the power amplifiers), hence the

SCR bridge that effectively disconnects the entire regulator from the transformer

secondary. When the over-voltage protection circuitry detects an over-voltage condition

the circuit shuts down the output of the regulator for 3 seconds and then tries to restart

the regulator. The fault is shown by two LEDs lighting up, the red LED (previous trip)

which latches on showing that a trip has been recorded and counted and a yellow LED

(over-voltage) which is on for the 3 second shutdown duration only. After three trips a

red LED (lockout) will come on until a reset command is received, resetting all counters

and restarting the cycle. In the event that the series pass transistor short circuits, turning

off the regulator IC will have no effect. In this case, additional control circuitry will shut

down the rectifier bridge isolating the regulator. A red LED (Q2 short -circuit) comes on.

A local reset switch for this circuitry is available for restarting the regulator (if the pass

transistor is indeed short circuited the circuitry will again shut down the regulator showing

the same fault condition). In this case the regulator must be serviced and Q2 replaced.

Until the necessary steps are taken to do this, the damaged regulator is safely isolated

from the rest of the transmitter.

c. Power ON Reset and Master Reset

The regulator assembly utilizes control voltages supplied by the transmitter control power

supplies. These are supplied via a connector on the front of the regulator module. In the

event that these ‘auxiliary’ voltages are removed from the circuit the regulator control

circuit shuts down the rectifier bridge, isolating the regulator. This situation could occur if

either the auxiliary power supply fails or if the 15 pin control connector is disconnected

leaving the unit without the auxiliary voltages. When the voltages are reapplied, the

circuitry sends a power -on reset pulse, setting all counters and protection circuits back to

original conditions. The same effect occurs when the master reset switch is pressed and

released.

Over-current protection (refer to block C on schematic diagram 41D1680S)

Along with current transducer S1, block C on the schematic contains the over -current protection.

The current information from S1 is amplified and compared to a threshold determined by the

setting of R51. When the current information reaches the threshold level, the output of

comparator U6 goes high (0 to 10V). U3 is

a buffer amplifier that is used to distribute

the over -current status to various other

circuits within the regulator (see table)

Whenever an over-current event happens,

the comparator output toggles (U6 -6) and

the positive level through U3 (pin 6) is

transferred through the closed contacts of

K1 to the gate of Q7. Q7 turns on and R35,

R41 and R43 form a voltage divider latching

Pin (U3) Output function

pin 10 front panel status LED (over -

current ) and via inverter U20d to

over-current event counter U14a.

pin 2 activates the OR gate U25d

shuting down the regulator.

pin 4 starts the timing circuitry (see

block E ).

pin 6 activates the locking circuitry.

U6 into the ‘tripped’ state. When a reset

command is issued relay K1 is activated, the gate of Q7 discharged and the circuit comes back to

its original state.

Over-Voltage Protection (refer to Block D on Schematic diagram 41D1680S)

Over-voltage condition is sensed by U4. This is a programmable voltage sensor. The threshold

over-voltage reference is set by the voltage divider consisting of R5, R21 and R22 (the threshold

is set by the following formula: V= 2.6 [1+ (R5+R21)/ R22] ). An over -voltage condition causes

4

the output of U8 (pin8) to go high. This triggers flip -flop U10a. Once set, the flip-flop output (pin

6) stays high until a reset pulse clears the flip -flop. The output of the flip-flop activates a yellow

LED (over-voltage indicator CR5), the over -voltage counter, U14b, the ‘trip recorded’ circuit of

U29b and the regulator shutdown circuitry of U25d.

The over-voltage circuitry is reset by U12 as follows: Once the over-voltage disappears, the

output of U4 returns to zero, pin 5 of AND gate U2b becomes logic 1. The signal at pin 4 of this

gate is connected to the output of U10a (already set to logic 1). After a delay determined by the

timing circuitry (see block E ), pin 3 of U2b goes high triggering U12 and resetting U10a. The

regulator will restart. If the fault is still present the over-voltage trip will re-occur and event

counters will allow three overloads before the lock out circuitry shuts the regulator down.

In the event that the regulat or is unable to shut down the output due to pass transistor short

circuit, the over -voltage shutdown circuitry will shut down the regulator but it will have no effect

on the output voltage. The output of U4 cannot return to zero in this case and pin 13 of U2a is

high (via inverter U20e) instead of pin 5 of U2b. After the timing circuitry delay, pin 1 of AND gate

U2a is set high, thus causing its output to go high. The output of flip -flop U10b is set and stays

high until reset via S2 ( Q2 FAIL RESET ). The output of U10b (pin 10) activates solid state relay

U32 . This removes drive from U33 and U34, turning OFF the bridge. The regulator circuitry is

now fully isolated from the secondary of the transformer and the rest of the transmitter.

Timing and Counting Circuitry (refer to Block E on Schematic diagram 41D1680S)

When overloads occur OR gate U25C triggers timer IC U26. This OR gate is triggered on pin 10

in the case of over-voltage trips and on pin 9 in the case of over -current trips. Once triggered the

timer releases a train of pulses to counter U28b. AND gates U30a, U30b and U31a monitor the

outputs of the counter and when all outputs are high U31a triggers the internal reset circuitry to

restart the regulator.

If the overload event was an over-current, U31d enables timer IC U16 (see block G). This IC

issues a pulse activating Q4, opto-coupler U15 and relay K1. The relay discharges the gate of

MOSFET Q7, releasing the over-current protection. Since relays are inherently slow devices,

opto-coupler U15 holds the shutdown pin of the regulator U1 high during the reset period. This

prevents serious over-current conditions on the output of the regulator from causing damage

during this transition period when the over-current protection circuit is resetting.

If the overload event was an over-voltage the output of U31a removes the shutdown condition

from AND gates U2a/U2b allowing the regulator to return to operation.

Each of the inputs to U25c are driven by an AND gate (U30d and U30c). These gates form part of

the three-shot lock-out circuitry. Binary counter U14a counts three over-current events and U14b

counts three over -voltage events. As long as the number of trips is less than three the outputs of

U31c and U31b are logic 0, the outputs of inverters U27e and U27d are logic 1 and over -current

or over-voltage trips are transmitted through the AND gates U30d/U30c. Once either of the event

counters reaches a count of three, the output of AND gate U31c or U31b goes high and the

internal reset circuitry is disabled . When the overload count reaches three LED CR8 (lockout )

turns on. A master reset is required to restart the regulator circuitry in this case.

Power-On and Master Reset Circuit (refer to Block F on Schematic diagram 41D1680S)

Whenever the control power supply from the transmitter (+ 12v) is disconnected and reconnected

to the circuitry, a power-up master reset is initiated. Q5 is activated after a delay given by

capacitors C36-C39 and divider R78, R74. K2 triggers the timer U18 which issues a mater reset

pulse. K2 can also be activated directly by pressing and releasing the master reset switch SW1

on the regulator.

5

Additionally, the main control board of transmitter can issues a reset command on pin 1 of

connector J1 (operator pressing tx front panel reset button). This external reset command will

only have an effect only if an overload trip has been recorded and is disregarded otherwise. In

this case U19 activates relay K2.

3. TESTING AND TROUBLES HOOTING

With the exception of replacing the pass transistor in this circuit, repair of the circuitry on these

units in the field is not recommended. Any adjustments provided on the module are for factory

settings only. Modification of these settings should not be attempted in the field as damage to

other sections of the transmitter may occur.

To remove a regulator module, first unplug the control cable (ribbon cable). This shuts off the

regulator. Then unplug the DC cable that feeds the PA module and pull the module out of the

housing. Support the bottom of the regulator as the slide mechanism is shorter than the regulator

itself and the regulator may drop suddenly, potentially damaging the AC input connector.

TABLE OF CONTENTS

1. INTRODUCTION .........................................................................................................................1

2. CIRCUIT DESCRIPTION..............................................................................................................1

3. TESTING AND TROUBLESHOOTING ..........................................................................................2

4. PARTS LIST...................................................................................Error! Bookmark not defined.

1. INTRODUCTION

In order to minimize the amount of wiring in the transmitter, a single circuit board was used to distribute

the AC power and various DC control voltages throughout the transmitter. The circuit board is mounted

on the AC circuit breakers behind the circuit breaker panel. On later models of the MX1000, the control

power supplies are also mounted on this panel.

2. CIRCUIT DESCRIPTION

The AC from the mains terminal block is distributed to the various power supplies and the blower via this

board and the breakers. The control power supplies receive their AC power via fuses Fl through F4 on J8

and J9. The three control voltages from these supplies come into the board on J8 and J9 as well. Each

of the voltages is monitored by voltage monitor ICs U3, U4, and U5. If one of the voltages fail, the PS1

FAIL or PS2 FAIL LED will illuminate. In addition, these control supply failure signals are routed to the

transmitter control board.

Each of the control voltages from the control power supplies is diode -ORed. Note that a single control

power supply can power the transmitter on it's own. Dual supplies are provided only for redundancy.

The AC to the transmitter blower and to the two power supplies is routed through circuit breakers CB1

through CB3. The BLOWER ON command is applied to this board on J8-39 from the tx control board.

An emergency interlock is provided for interlocking the transmitter to a building fire alarm system. This

interlock disables the transmitter blower as well as the power supplies (not the control power supplies).

The connections to this interlock are on J7. The interlock can be bypassed via JP1. K6 controls the AC

to the contactor relay K3 which provides AC to the blower at J2 -2 and J2 -3. The AC that supplies the

blower, also supplies power to the airflow switch.

The voltage applied to the blower also arms the power supply contactors K1 and K2.

The TX-ON command is applied through J8 -37 from the transmitter control board. This signal energizes

K4 and voltage is applied to the power supply contactor coils of K1 and K2 via the step start thermal

interlock circuits and the breaker auxiliary contacts.

The AC to the power supplies is applied through a step-start circuit to minimize the inrush currents

associated with the ferroresonant power supplies. This step start circuitry consists of a resistor in series

with the transformer that is shorted out after a predetermined delay period. A solid state relay is used to

short the resistors allowing full supply voltage to be applied to the power supplies. In the event of a

failure in this timing circuit there is a thermal cutout switch mounted on the step start resistors. These

thermals will remove the po wer to the power supply contactor coils, thus removing power from the supply.

The step start timing circuit for on e power supply will be described, the second circuit is identical. When

AC is applied to the surge The step start timing circuit for one power supplyresistors, AC is applied to

opto isolator U2 -3 (U2-4). This opto-isolator applies voltage to the timing circuit consisting of R5 and C5

1

(R16/C11). When the voltage across the capacitor reaches a predetermined level as set by the voltage

divider R10/R11 (R13/R14), the output of comparator UlA (UlB) goes high causing the solid state relay K7

(K5) to turn on, shorting out the surge limiting resistors.

3. TESTING AND TROUBLES HOOTING

This board is essentially an interconnec t circuit for the transmitter and, as such there are not many circuits

on the board to require service.

Much of the troubleshooting that can be done with this circuit is detailed in the installation section of this

manual. The troubleshooting can be done by simply observing which LEDs are illuminated and

determining where the problem lies. Refer to figure for the location of the LEDs and to the schematic

diagram (figure ) for their function.

DS 11 and DS12 indicate the presence of AC on the inputs to the circuit breakers CB1 through CB3.

DS5 indicates the presence of a blower command. DS8 indicates that the blower contactor K3 is closed.

DS6 and DS7 indicate that power supply contactors (K1 and K2 respectively) are closed. DS9 and DS10

are illuminated during the startup inrush limiting period, indicating essentially that the inrush resistors are

in circuit. Note that these resistors are provided to limit the inrush caused by the magnetizing current of

the ferroresonant transformers and protect the contactors from damage due to these high currents as well

as prevent inadvertent breaker trips. Should the inrush circuitry fail to function properly, leaving these

resistors in circuit and dissipating power, the thermal cutouts mounted on the surface of the resistors will

open, causing the contactors to open. DS1 and DS2 indicate this thermal cutout condition should it

occur.

2

R46

51K

R45

51K

DS11

J8-37

TX ON CMD

L1

L1

+12V

RES 1

THERMAL

RES 2

THERMAL

SCR 1 OPEN

DS9

TO RESISTOR 1

TO RESISTOR 2

DS10

SCR 2 OPEN

J16

E1

E2

E7

E8

9

R15

1K

L1

1uH

81311

6

4

K4

DS2E-S-DC12V

J8-39

BLOWER ON CMD

J7

1

EMERGENCY

2

INTERLOCK

DS12

AM2-A9A8AW

THERMAL 1 FAIL

DS1

1

2

3

4

DS2

THERMAL 2 FAIL

R41

20K

R42

20K

R1

51K

R2

51K

12

K7

CSD2425

4

DS6

3

4

R34

51K

CB2

2

C

NO

NC

869

1

K1

123

J1

R20

20K

+12V

J13

1

2

T92S11A12-240

123

4

J2

56

R49

1K

AM2-A9A8AW

4

21

K8

CSD2425

4

+12V +12V

1112

U2-3

ILQ1

C14

R48

22uF

43K

CB1

2

C

NO

NC

1N4001

CR10

R5

10M

C5

.1uF

T92S11A12-240

1

K2

DS7

R35

51K

869

3

4

R6

470R

R4

1K

+12V

U2-1

ILQ1

R10

1K

J14