FEUL610473-09

ML610471/ML610472/ML610473

ML610Q471/ML610Q472/ML610Q473

User’s Manual

Issue Date: Jan. 7, 2013

NOTES

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing LAPIS Semiconductor 's products (hereinafter "Products"). If you wish

to use any such Product, please be sure to refer to the specifications, which can be obtained from LAPIS Semiconductor upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and

operations of the Products. The peripheral condit ions must be taken into account when designing circuits for mass production.

Great care was taken in ensu ring the accuracy of the infor mation specified in this do cument. However, should you incur any damage

arising from any inaccuracy or mi sprint of such information, LAPIS Semiconductor shall bear no responsibility for such damage.

The technical informati on specified herein is intended only to show the typical functions of and examples of application circuits for

the Products. LAPIS Semiconductor does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or

other rights held by LAPIS Semiconductor and other parties. LAPIS Semiconductor shall bear no responsibility whatsoever for any

dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio

visual equipment, o ffice-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While LAPIS Semiconductor always makes efforts to enhance the quality and reliability of its Products, a Product may fail or

malfunction for a variety of reasons.

Please be sure to implement in your equ ipment using t he Products safety measures to gu ard against the po ssibility of ph ysical injury,

fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe

designs. LAPIS Semiconductor shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or

not in accordance with the i nstruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high

level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such

as a medical instrument, transportation equ ipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety

device). LAPIS Semiconductor shall bear no responsibility in any way for use of any of the Products for the above special purposes. If

a Product is intended to be used for any such special purpo se, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange

and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Copyright 2011 – 2013 LAPIS Semiconductor Co., Ltd.

Preface

This manual describes the operation of the hardware of the 8-bit microcontroller

ML610471/ML610472/ML610473/ML610Q471/ML610Q472/ML610Q473.

The following manuals are also available. Read them as necessary.

nX-U8/100 Core Instruction Manual

Description on the basic architecture and the each instruction of the nX-U8/100 Core.

MACU8 Assembler Package User’s Manual

Description on the method of operating the relocatable assembler, the linker, the

librarian, and the object converter and also on the specifications of the assembler

language.

CCU8 User’s Manual

Description on the method of operating the compiler.

CCU8 Programming Guide

Description on the method of programming.

CCU8 Langua ge Re fer ence

Description on the language specifications.

DTU8 Debugger User’s Manual

Description on the method of operating the debugger DTU8.

IDEU8 User’s Manual

Description on the integrated development environment IDEU8.

HTU8 User’s Manual

Description on the integrated development support software HTU8.

uEASE User’s Manual

Description on the on-chip debug tool uEASE.

FWuEASE Flash Writer Host Program User’s Manual

Description on the Flash Writer host program.

Notation

Classification Notation Description

♦ Numeric value xxh, xxH Indicates a hexadeci mal number. x: Any value in the range of 0 to F

xxb Indicates a binary number; “b” may be omitted. x: A value 0 or 1

♦ Unit word, W 1 word = 16 bits

byte, B 1 byte = 8 bits

nibble, N 1 nibble = 4 bits

maga-, M 10

kilo-, K 2

kilo-, k 10

milli-, m 10

micro-, µ 10

nano-, n 10

second, s (lower case) second

♦ Terminology “H” level, “1” level Indicates high voltage signal levels V

“L” level, “0” level Indicates low voltage signal levels V

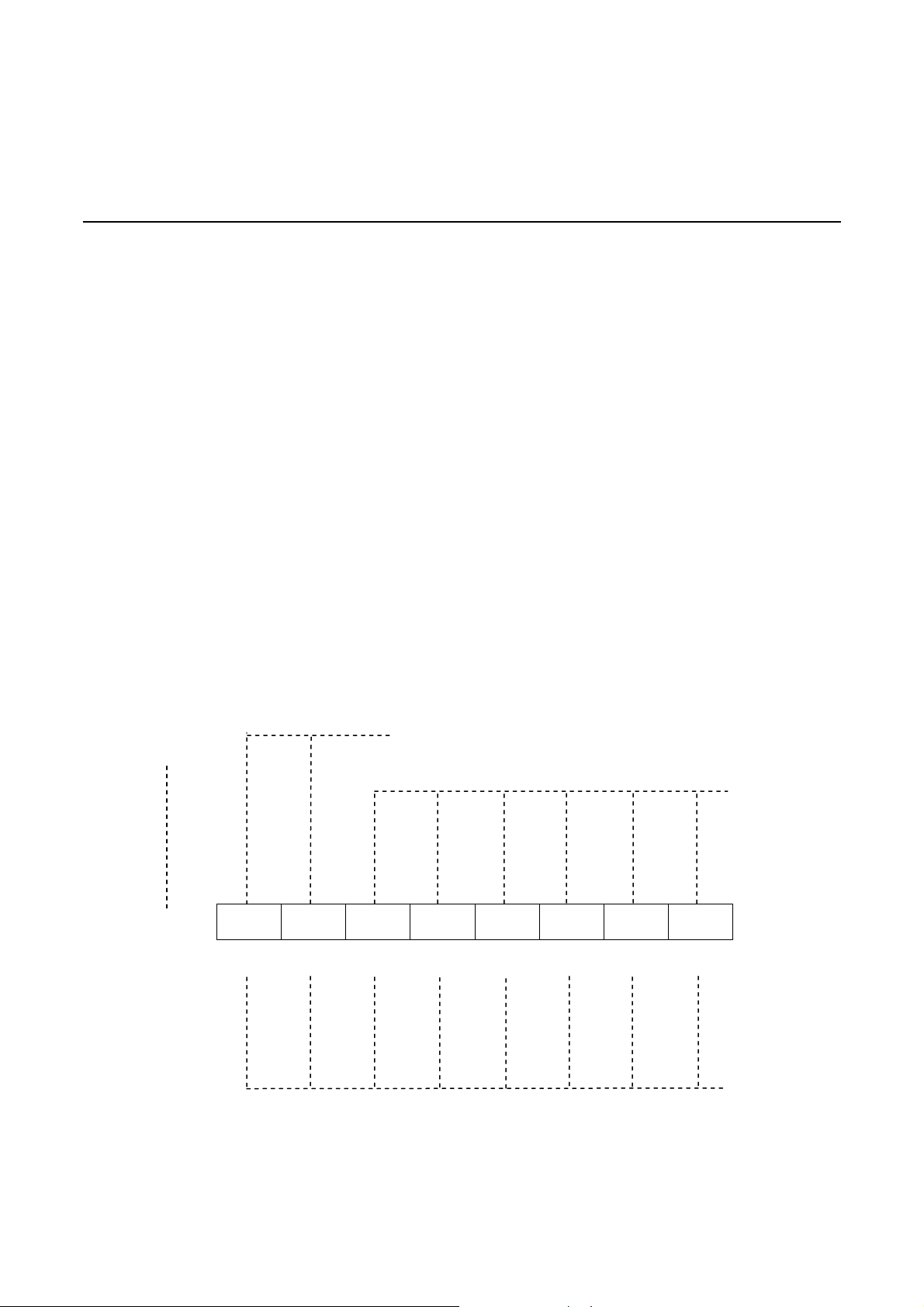

♦ Register description

R/W: Indicates that Read/Write attribute. “R” indicates that data can be read and “W” indicates that data can be written.

“R/W” indicates that data can be read or written.

Register name

MSB LSB

6

10

= 1024

3

= 1000

-3

-6

-9

and VOH as specified by the

IH

electrical characteristics.

and VOL as specified by the

IL

electrical characteristics.

Invalid bit: This bit reads “0” when read. Write to this bit is ignored.

Bit name

FCON0 ⎯ ⎯ OUTC1 OUTC0 OSCM1 OSCM0 SYSC1 SYSC0

R/W R/W R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 1 1 0 1 0 1

Initial value after reset

ML610471/472/473/Q471/Q472/Q473 User’s Manual

Table of Contents

Chapter 1

1. Overview .........................................................................................................................................................1-1

1.1 Features .......................................................................................................................................................1-1

1.2 Configuration of Functional Blocks............................................................................................................1-4

1.2.1 Block Diagram of ML610471/ML610472/ML610473.......................................................................... 1-4

1.2.2 Block Diagram of ML610Q471/ML610Q472/ML610Q473.................................................................1-5

1.3 Pins.............................................................................................................................................................. 1-6

1.3.1 Pin Layout.............................................................................................................................................. 1-6

1.3.1.1 Pin Layout of ML610471 / ML610Q471 48pin TQFP Package .....................................................1-6

1.3.1.2 Pin Layout of ML610471 / ML610Q471 64pin TQFP Package .....................................................1-7

1.3.1.3 Pin Layout of ML610472 / ML610Q472 48pin TQFP Package .....................................................1-8

1.3.1.4 Pin Layout of ML610472 / ML610Q472 64pin TQFP Package .....................................................1-9

1.3.1.5 Pin Layout of ML610473 / ML610Q473 48pin TQFP Package ...................................................1-10

1.3.1.6 Pin Layout of ML610473 / ML610Q473 64pin TQFP Package ...................................................1-11

1.3.1.7 Pin Layout of ML610471 Chip...................................................................................................... 1-12

1.3.1.8 Pin Layout of ML610472 Chip...................................................................................................... 1-13

1.3.1.9 Pin Layout of ML610473 Chip...................................................................................................... 1-14

1.3.1.10 Pin Layout of ML610Q471 Chip.................................................................................................1-15

1.3.1.11 Pin Layout of ML610Q472 Chip.................................................................................................1-16

1.3.1.12 Pin Layout of ML610Q473 Chip.................................................................................................1-17

1.3.1.13 Pad Coordinates of ML610471/ML610472/M610473 Chip .......................................................1-18

1.3.1.14 Pad Coordinates of ML610Q471/ML610Q472/M610Q473 Chip............................................... 1-19

1.3.2 List of Pins ...........................................................................................................................................1-20

1.3.3 Pin Descriptions...................................................................................................................................1-22

1.3.4 Handling of Unused Pins ..................................................................................................................... 1-25

Chapter 2

Contents

2. CPU and Memory Space...................................................................................................................................2-1

2.1 Overview....................................................................................................................................................... 2-1

2.2 Program Memory Space ............................................................................................................................... 2-1

2.3 Data Memory Space......................................................................................................................................2-2

2.4 Instruction Length......................................................................................................................................... 2-3

2.5 Data Type......................................................................................................................................................2-3

2.6 Description of Registers................................................................................................................................2-4

2.6.1 List of Registers .....................................................................................................................................2-4

2.6.2 Data Segment Register (DSR)................................................................................................................ 2-5

Chapter 3

3. Reset Function...................................................................................................................................................3-1

3.1 Overview....................................................................................................................................................... 3-1

3.1.1 Features..................................................................................................................................................3-1

3.1.2 Configuration .........................................................................................................................................3-1

3.1.3 List of Pins .............................................................................................................................................3-1

3.2 Description of Registers.............................................................................................................................. 3-2

3.2.1 List of Registers .....................................................................................................................................3-2

3.2.2 Reset Status Register (RSTAT)..............................................................................................................3-2

3.3 Description of Operation.............................................................................................................................3-3

3.3.1 Operation of System Reset Mode...........................................................................................................3-3

Chapter 4

4. MCU Control Function.................................................................................................................................... 4-1

4.1 Overview.....................................................................................................................................................4-1

Contents – 0

ML610Q471/ML610Q472/ML610Q473 User’s Manual

Contents

4.1.1 Features..................................................................................................................................................4-1

4.1.2 Configuration .........................................................................................................................................4-1

4.2 Description of Registers..............................................................................................................................4-2

4.2.1 List of Registers .....................................................................................................................................4-2

4.2.2 Stop Code Acceptor (STPACP).............................................................................................................4-3

4.2.3 Standby Control Register (SBYCON) ...................................................................................................4-4

4.2.4 Block Control Register 0 (BLKCON0).................................................................................................. 4-5

4.2.5 Block Control Register 1 (BLKCON1).................................................................................................. 4-6

4.2.6 Block Control Register 2 (BLKCON2).................................................................................................. 4-7

4.2.7 Block Control Register 4 (BLKCON4).................................................................................................. 4-8

4.3 Description of Operation.............................................................................................................................4-9

4.3.1 Program Run Mode................................................................................................................................ 4-9

4.3.2 HALT Mode........................................................................................................................................... 4-9

4.3.3 STOP mode.......................................................................................................................................... 4-10

4.3.3.1 STOP Mode When CPU Operates with Low-Speed Clock...........................................................4-10

4.3.3.2 STOP Mode When CPU Operates with High-Speed Clock..........................................................4-11

4.3.4 Note on Return Operation from STOP/HALT Mode...........................................................................4-12

4.3.5 Block Control Function........................................................................................................................4-13

Chapter 5

5. Interrupts..........................................................................................................................................................5-1

5.1 Overview.....................................................................................................................................................5-1

5.1.1 Features..................................................................................................................................................5-1

5.2 Description of Registers..............................................................................................................................5-2

5.2.1 List of Registers .....................................................................................................................................5-2

5.2.2 Interrupt Enable Register 1 (IE1)........................................................................................................... 5-3

5.2.3 Interrupt Enable Register 4 (IE4)........................................................................................................... 5-4

5.2.4 Interrupt Enable Register 5 (IE5)........................................................................................................... 5-5

5.2.5 Interrupt Enable Register 6 (IE6)........................................................................................................... 5-6

5.2.6 Interrupt Enable Register 7 (IE7)........................................................................................................... 5-7

5.2.7 Interrupt Request Register 0 (IRQ0)......................................................................................................5-8

5.2.8 Interrupt Request Register 1 (IRQ1)......................................................................................................5-9

5.2.9 Interrupt Request Register 4 (IRQ4)....................................................................................................5-10

5.2.10 Interrupt Request Register 5 (IRQ5)..................................................................................................5-11

5.2.11 Interrupt Request Register 6 (IRQ6)..................................................................................................5-12

5.2.12 Interrupt Request Register 7 (IRQ7)..................................................................................................5-13

5.3 Description of Operation...........................................................................................................................5-14

5.3.1 Maskable Interrupt Processing............................................................................................................. 5-15

5.3.2 Non-Maskable Interrupt Processing..................................................................................................... 5-15

5.3.3 Software Interrupt Processing.............................................................................................................. 5-15

5.3.4 Notes on Interrupt Routine...................................................................................................................5-16

5.3.5 Interrupt Disable State..........................................................................................................................5-19

Chapter 6

6. Clock Generation Circuit.................................................................................................................................6-1

6.1 Overview.....................................................................................................................................................6-1

6.1.1 Features..................................................................................................................................................6-1

6.1.2 Configuration .........................................................................................................................................6-1

6.1.3 List of Pins .............................................................................................................................................6-2

6.2 Description of Registers..............................................................................................................................6-2

6.2.1 List of Registers .....................................................................................................................................6-2

6.2.2 Frequency Control Register 0 (FCON0)................................................................................................6-3

6.2.3 Frequency Control Register 1 (FCON1)................................................................................................6-4

6.3 Description of Operation.............................................................................................................................6-5

6.3.1 Low-Speed Clock................................................................................................................................... 6-5

6.3.1.1 Low-Speed Clock Generation Circuit..............................................................................................6-5

Contents –1

ML610471/ML610472/ML610473 User’s Manual

6.3.1.2 Operation of Low-Speed Clock Generation Circuit ........................................................................ 6-6

6.3.2 High-speed clock.................................................................................................................................... 6-7

6.3.2.1 High-Speed Clock Circuit................................................................................................................ 6-7

6.3.2.2 Operation of High-Speed Clock Generation Circuit........................................................................ 6-8

6.3.3 Switching of System Clock.................................................................................................................... 6-9

6.4 Specifying Port Registers..........................................................................................................................6-10

6.4.1 Functioning P21 (OUTCLK) as the high-speed clock output..............................................................6-10

6.4.1 Functioning P20 (LSCLK) as the low-speed clock output...................................................................6-11

Chapter 7

7. Time Base Counter..........................................................................................................................................7-1

7.1 Overview.....................................................................................................................................................7-1

7.1.1 Features..................................................................................................................................................7-1

7.1.2 Configuration .........................................................................................................................................7-1

7.2 Description of Registers.............................................................................................................................. 7-3

7.2.1 List of Registers .....................................................................................................................................7-3

7.2.2 Low-Speed Time Base Counter Register (LTBR).................................................................................7-4

7.2.3 High-Speed Time Base Counter Divide Register (HTBDR) ................................................................. 7-5

7.2.4 Low-Speed Time Base Counter Frequency Adjustment Registers L and H (LTBADJL, LTBADJH)..7-6

7.3 Description of Operation.............................................................................................................................7-7

7.3.1 Low-speed Time Base Counter.............................................................................................................. 7-7

7.3.2 High-Speed Time Base Counter............................................................................................................. 7-8

7.3.3 Low-Speed Time Base Counter Frequency Adjustment Function......................................................... 7-9

7.3.4 A signal generation for 16-bit timer 2-3 frequency measurement mode..............................................7-10

Chapter 8

Contents

8. Capture .........................................................................................................................................................8-1

8.1 Overview.....................................................................................................................................................8-1

8.1.1 Features..................................................................................................................................................8-1

8.1.2 Configuration .........................................................................................................................................8-1

8.1.3 List of Pins .............................................................................................................................................8-1

8.2 Description of Registers..............................................................................................................................8-2

8.2.1 List of Registers .....................................................................................................................................8-2

8.2.2 Capture Control Register (CAPCON)....................................................................................................8-3

8.2.3 Capture Status Register (CAPSTAT)..................................................................................................... 8-4

8.2.4 Capture Data Register 0 (CAPR0) .........................................................................................................8-5

8.2.5 Capture Data Register 1 (CAPR1) .........................................................................................................8-6

8.2.6 Capture Time Base Data Register (CAPTB).......................................................................................... 8-7

8.3 Description of Operation.............................................................................................................................8-8

Chapter 9

9. Timer................................................................................................................................................................. 9-1

9.1 Overview....................................................................................................................................................... 9-1

9.1.1 Features..................................................................................................................................................9-1

9.1.2 Configuration .........................................................................................................................................9-1

9.1.3 List of Pins .............................................................................................................................................9-2

9.2 Description of Registers................................................................................................................................9-3

9.2.1 List of Registers .....................................................................................................................................9-3

9.2.2 Timer 2 Data Register (TM2D).............................................................................................................. 9-4

9.2.3 Timer 3 Data Register (TM3D).............................................................................................................. 9-5

9.2.4 Timer 2 Counter Register (TM2C).........................................................................................................9-6

9.2.5 Timer 3 Counter Register (TM3C).........................................................................................................9-7

9.2.6 Timer 2 Control Register 0 (TM2CON0)...............................................................................................9-8

9.2.7 Timer 3 Control Register 0 (TM3CON0)...............................................................................................9-9

9.2.8 Timer 2 Control Register 1 (TM2CON1).............................................................................................9-10

Contents –2

ML610Q471/ML610Q472/ML610Q473 User’s Manual

Contents

9.2.9 Timer 3 Control Register 1 (TM3CON1).............................................................................................9-11

9.3 Description of Operation ............................................................................................................................ 9-12

9.3.1 Timer mode operation.......................................................................................................................... 9-12

9.3.2 16-bit timer frequency measurement mode operation.......................................................................... 9-13

9.3.3 16-bit timer frequency measurement mode application for setting uart baud-rate............................... 9-15

9.4 Operating Timers by External Clock Inputs...............................................................................................9-16

9.4.1 Operating Timer 2 (8-Bit Timer Mode) by External Clock (P44/T2CK) ............................................9-16

9.4.2 Operating Timer 3 (8-Bit Timer Mode) by External Clock (P45/T3CK) ............................................9-17

9.4.3 Operating Timer 2 and Timer 3 (16-Bit Timer Mode) by External Clock (P44/T2CK)......................9-18

Chapter 10

10. Watchdog Timer.......................................................................................................................................... 10-1

10.1 Overview.................................................................................................................................................10-1

10.1.1 Features..............................................................................................................................................10-1

10.1.2 Configuration .....................................................................................................................................10-1

10.2 Description of Registers..........................................................................................................................10-2

10.2.1 List of Registers .................................................................................................................................10-2

10.2.2 Watchdog Timer Control Register (WDTCON)................................................................................ 10-3

10.2.3 Watchdog Timer Mode Register (WDTMOD).................................................................................. 10-4

10.3 Description of Operation.........................................................................................................................10-5

10.3.1 Handling example when you do not want to use the watch dog timer............................................... 10-7

Chapter 11

11. UART ..........................................................................................................................................................11-1

11.1 Overview...............................................................................................................................................11-1

11.1.1 Features..............................................................................................................................................11-1

11.1.2 Configuration .....................................................................................................................................11-1

11.1.3 List of Pins .........................................................................................................................................11-2

11.2 Description of Registers..........................................................................................................................11-2

11.2.1 List of Registers .................................................................................................................................11-2

11.2.2 UART0 Transmit/Receive Buffer (UA0BUF)...................................................................................11-3

11.2.3 UART0 Control Register (UA0CON)................................................................................................11-4

11.2.4 UART0 Mode Register 0 (UA0MOD0).............................................................................................11-5

11.2.5 UART0 Mode Register 1 (UA0MOD1).............................................................................................11-6

11.2.6 UART0 Baud Rate Registers L, H (UA0BRTL, UA0BRTH)...........................................................11-8

11.2.7 UART0 Status Register (UA0STAT) ................................................................................................ 11-9

11.3 Description of Operation.....................................................................................................................11-11

11.3.1 Transfer Data Format.......................................................................................................................11-11

11.3.2 Baud rate ..........................................................................................................................................11-12

11.3.3 Transmitted Data Direction..............................................................................................................11-13

11.3.4 Transmit Operation ..........................................................................................................................11-14

11.3.5 Receive Operation............................................................................................................................ 11-16

11.3.5.1 Detection of Start Bit.................................................................................................................11-18

11.3.5.2 Sampling Timing .......................................................................................................................11-18

11.3.5.3 Receive Margin.......................................................................................................................... 11-19

11.4 Specifying Port Registers....................................................................................................................11-20

11.4.1 Functioning P43(TXD0) and P42(RXD0) as the UART.................................................................11-20

11.4.1 Functioning P43(TXD0) and P02(RXD0) as the UART .................................................................11-21

Chapter 12

12. Port 0 ...........................................................................................................................................................12-1

12.1 Overview...............................................................................................................................................12-1

12.1.1 Features..............................................................................................................................................12-1

12.1.2 Configuration .....................................................................................................................................12-1

12.1.3 List of Pins .........................................................................................................................................12-1

Contents –3

ML610471/ML610472/ML610473 User’s Manual

12.2 Description of Registers..........................................................................................................................12-2

12.2.1 List of Registers .................................................................................................................................12-2

12.2.2 Port 0 Data Register (P0D) ................................................................................................................12-3

12.2.3 Port 0 Control Registers 0, 1 (P0CON0, P0CON1)...........................................................................12-4

12.2.4 External Interrupt Control Registers 0, 1 (EXICON0, EXICON1) ...................................................12-5

12.2.5 External Interrupt Control Register 2 (EXICON2)............................................................................12-6

12.3 Description of Operation.........................................................................................................................12-7

12.3.1 External Interrupt / Secondary Function............................................................................................12-7

12.3.2 Interrupt Request................................................................................................................................12-7

Chapter 13

13. Port 2 ...........................................................................................................................................................13-1

13.1 Overview...............................................................................................................................................13-1

13.1.1 Features..............................................................................................................................................13-1

13.1.2 Configuration .....................................................................................................................................13-1

13.1.3 List of Pins .........................................................................................................................................13-1

13.2 Description of Registers..........................................................................................................................13-2

13.2.1 List of Registers .................................................................................................................................13-2

13.2.2 Port 2 Data Register (P2D) ................................................................................................................13-3

13.2.3 Port 2 Control Registers 0, 1 (P2CON0, P2CON1)...........................................................................13-4

13.2.4 Port 2 Mode Register (P2MOD) ........................................................................................................13-5

13.3 Description of Operation.........................................................................................................................13-6

13.3.1 Output Port Function.......................................................................................................................... 13-6

13.3.2 Secondary Function............................................................................................................................ 13-6

Chapter 14

Contents

14. Port 3 ...........................................................................................................................................................14-1

14.1 Overview...............................................................................................................................................14-1

14.1.1 Features..............................................................................................................................................14-1

14.1.2 Configuration .....................................................................................................................................14-1

14.1.3 List of Pins .........................................................................................................................................14-1

14.2 Description of Registers..........................................................................................................................14-2

14.2.1 List of Registers .................................................................................................................................14-2

14.2.2 Port 3 Data Register (P3D) ................................................................................................................14-3

14.2.3 Port 3 Direction Register (P3DIR)..................................................................................................... 14-4

14.2.4 Port 3 Control Registers 0, 1 (P3CON0, P3CON1)...........................................................................14-5

14.2.5 Port 3 Mode Register 0 (P3MOD0) ...................................................................................................14-6

14.3 Description of Operation.........................................................................................................................14-7

14.3.1 Input/Output Port Functions............................................................................................................... 14-7

14.3.2 Secondary Function............................................................................................................................ 14-7

Chapter 15

15. Port 4 ...........................................................................................................................................................15-1

15.1 Overview...............................................................................................................................................15-1

15.1.1 Features..............................................................................................................................................15-1

15.1.2 Configuration .....................................................................................................................................15-1

15.1.3 List of Pins .........................................................................................................................................15-2

15.2 Description of Registers........................................................................................................................15-3

15.2.1 List of Registers .................................................................................................................................15-3

15.2.2 Port 4 Data Register (P4D) ................................................................................................................15-4

15.2.3 Port 4 Direction Register (P4DIR)..................................................................................................... 15-5

15.2.4 Port 4 Control Registers 0, 1 (P4CON0, P4CON1)...........................................................................15-6

15.2.5 Port 4 Mode Registers 0, 1 (P4MOD0, P4MOD1) ............................................................................15-8

15.3 Description of Operation.......................................................................................................................15-10

15.3.1 Input/Output Port Functions............................................................................................................. 15-10

Contents –4

ML610Q471/ML610Q472/ML610Q473 User’s Manual

Contents

15.3.2 Secondary and Tertiary Functions....................................................................................................15-10

Chapter 16

16. Port 6 ...........................................................................................................................................................16-1

16.1 General Description................................................................................................................................. 16-1

16.1.1 Features..............................................................................................................................................16-1

16.1.2 Configuration .....................................................................................................................................16-1

16.1.3 List of Pins .........................................................................................................................................16-1

16.2 Description of Registers..........................................................................................................................16-2

16.2.1 List of Registers .................................................................................................................................16-2

16.2.2 Port 6 Data Register (P6D) ................................................................................................................16-3

16.2.3 Port 6 Control Register 0 (P6CON0) .................................................................................................16-4

16.3 Description of Operation.......................................................................................................................16-5

16.3.1 Output Port Function.......................................................................................................................... 16-5

Chapter 17

17. RC Oscillation Type A/D Converter...........................................................................................................17-1

17.1 Overview...............................................................................................................................................17-1

17.1.1 Features..............................................................................................................................................17-1

17.1.2 Configuration .....................................................................................................................................17-1

17.1.3 List of Pins .........................................................................................................................................17-2

17.2 Description of Registers..........................................................................................................................17-3

17.2.1 List of Registers .................................................................................................................................17-3

17.2.2 RC-ADC Counter A Registers (RADCA0–1)....................................................................................17-4

17.2.3 RC-ADC Counter B Registers (RADCB0–1).................................................................................... 17-5

17.2.4 RC-ADC Mode Register (RADMOD).......................................................................................... ..... 17-6

17.2.5 RC-ADC Control Register (RADCON)............................................................................................. 17-7

17.3 Description of Operation.........................................................................................................................17-8

17.3.1 RC Oscillator Circuits........................................................................................................................17-8

17.3.2 Counter A/Counter B Reference Modes .......................................................................................... 17-10

17.3.3 Example of Use of RC Oscillation Type A/D Converter................................................................. 17-13

17.3.4 Monitoring RC Oscillation............................................................................................................... 17-17

17.4 Specifying Port Registers......................................................................................................................17-18

17.4.1 Functioning P47(RT1), P46(RS1), P45(CS1) and P44(IN1) as the RC-ADC(Ch1)........................ 17-18

Chapter 18

18. LCD Driver..................................................................................................................................................18-1

18.1 Overview...............................................................................................................................................18-1

18.1.1 Features ............................................................................................................................................18-2

18.1.2 Configuration of the LCD Drivers .....................................................................................................18-2

18.1.3 Configuration of the Bias Generation Circuit ....................................................................................18-3

18.1.4 List of Pins .........................................................................................................................................18-5

18.2 Description of Registers..........................................................................................................................18-6

18.2.1 List of Registers .................................................................................................................................18-6

18.2.2 Bias Circuit Control Register 0 (BIASCON)..................................................................................... 18-7

18.2.3 Display Mode Register 0 (DSPMOD0) ............................................................................................. 18-8

18.2.4 Display Control Register (DSPCON) ................................................................................................ 18-9

18.2.5 Display Registers (DSPR00 to DSPR15).........................................................................................18-10

18.3 Description of Operation.......................................................................................................................18-12

18.3.1 Operation of LCD Drivers and Bias Generation Circuit.................................................................. 18-12

18.3.2 Segment Mapping When the Programmable Display Allocation Function is Not Used ................. 18-13

18.3.3 Common Output Waveforms...........................................................................................................18-14

18.3.4 Segment Output Waveform..............................................................................................................18-16

Contents –5

ML610471/ML610472/ML610473 User’s Manual

Chapter 19

19. Power Supply Circuit.................................................................................................................................. 19-1

19.1 Overview.................................................................................................................................................19-1

19.1.1 Features..............................................................................................................................................19-1

19.1.2 Configuration .....................................................................................................................................19-1

19.1.3 List of Pins .........................................................................................................................................19-1

Chapter 20

20. uEASE Flash Writer System.........................................................................................................................20-1

20.1 Overview.................................................................................................................................................20-1

20.2 Method of Connecting to the uEASE...................................................................................................... 20-1

20.3 Method of writing to the Flash memory..................................................................................................20-2

20.4 Flash Memory Rewrite Function.............................................................................................................20-3

Chapter 21

21. Software Development ................................................................................................................................. 21-1

21.1 Overview.................................................................................................................................................21-1

21.2 Development Version Setting Sequence .................................................................................................21-1

21.3 Development Version Resetting Sequence..............................................................................................21-2

21.4 Notice for the Software Program Development ......................................................................................21-2

21.4.1 Notice for the Development Version Mode Setting Data .................................................................. 21-2

21.4.2 Notice for the Development Version Memory Size........................................................................... 21-4

21.5 The Detail Specification of Development Version..................................................................................21-5

Appendix

Contents

Appendix.A Registers......................................................................................................................................... A-1

Appendix.B Package Dimensions....................................................................................................................... B-1

Appendix.C Electrical Characteristics................................................................................................................ C-1

Appendix.D Application Circuit Example.......................................................................................................... D-1

Appendix.E Ckeck List........................................................................................................................................E-1

Contents –6

Chapter 1

Overview

ML610471/472/473/Q471/Q472/Q473 User's Manual

Chapter 1 Overview

1. Overview

1.1 Features

This LSI is a high performance CMOS 8-bit microcontroller equipped with an 8-bit CPU nX-U8/100 and integrated with

peripheral functions such as the UART, RC oscillation type A/D converter, and LCD driver.

The CPU nX-U8/100 is capable of efficient instruction execution in 1-intruction 1-clock mode by 3-stage pipe line

architecture parallel processing. Additionally, it adopts the low-/high-speed dual clock system, standby mode, and

process that prohibits leak current at high temperatures, and is most suitable for battery-driven applications.

MTP version (ML610Q471/ML610Q472/ML610Q473) can rewrite programs on-board, which can contribute to

reduction in product development TAT. The flash memory incorporated into this MTP version implements the mask

ROM-equivalent low-voltage operation (1.25V or higher) and low-power consumption (typically 5uA at low-speed

operation), enabling volume production by the MTP version.

For industrial use, ML610471P/ML610472P/ML610473P/ML610Q471P/ML610Q472P/ML610Q473P with the

extended operating ambient temperature ranging from -40°C to 85°C are available.

z CPU

- 8-bit RISC CPU (CPU name: nX-U8/100)

- Instruction system: 16-bit length instruction

- Instruction set: Transfer, arithmetic operations, comparison, logic operations, multiplication/division, bit

manipulations, bit logic operations, jump, conditional jump, call return stack manipulations, arithmetic shift,

and so on

- Flash Memory rewrite function (MTP version only)

- Minimum instruction execution time

30.5 μs (@ 32.768 kHz system clock)

2 μs (@ 500 kHz system clock)

z Internal memory

- ML610471/ML610472/ML610473

Internal 8KByte Mask ROM (4K x 16 bits) (including unusable 256Byte TEST area)

Internal 512Byte RAM (512 x 8 bits)

- ML610Q471/ML610Q472/ML610Q473

Internal 8KByte Flash ROM (4K x 16 bits) (including unusable 256Byte TEST area)

Internal 512Byte RAM (512 x 8 bits)

z Interrupt controller

- 1 non-maskable interrupt source:

Internal source: 1 (Watchdog Timer)

- 12 maskable interrupt sources:

Internal source: 8 (Timer 2, Timer 3, UART0, RC Oscillation type A/D converter, TBC128Hz, TBC32Hz,

TBC16Hz, TBC2Hz)

External source: 4 (P00, P01, P02, P03)

z Time base counter

- Low-speed time base counter x 1 channel

Frequency compensation (Compensation range: Approx. -488ppm to +488ppm. Compensation accuracy:

Approx. 0.48ppm)

- High-speed time base counter x 1 channel

z Watchdog timer

- Non-maskable interrupt and reset

- Free running

- Overflow period: 4 types selectable (125ms, 500ms, 2s, 8s)

1-1

ML610471/472/473/Q471/Q472/Q473 User's Manual

Chapter 1 Overview

z Timer

- 8 bits x 2 channels [also available is 16-bit configuration (using Timers 2 and 3) x 1 channels]

- Clock frequency measurement function mode (16-bit configuration using Timers 2 and 3 x 1 channel only)

z Capture

- Time base capture x 2 channels (4096 Hz to 32 Hz)

z UART

- TXD/RXD × 1 channel

- Bit length, parity/no parity, odd parity/even parity, 1 stop bit/2 stop bits

- Positive logic/negative logic selectable

- Built-in baud rate generator

z RC oscillation type A/D converter

- 16-bit counter

- Time division x 1 channels

z General-purpose port

- Input-only port: 4 channels (including secondary functions)

- Output-only port

ML610471/ML610Q471: 10 channels (including secondary functions)

ML610472/ML610Q472: 6 channels (including secondary functions)

ML610473/ML610Q473: 2 channels (including secondary functions)

- Input/output port: 7 channels (including secondary functions)

z LCD driver

- Number of segments

ML610471/ML610Q471:

Up to 55 dots (select among 11 segments x 5 commons, 12 segments x 4 commons, 13 segments x 3

commons, and 14 segments x 2 commons)

ML610472/ML610Q472:

Up to 75 dots (select among 15 segments x 5 commons, 16 segments x 4 commons, 17 segments x 3

commons, and 18 segments x 2 commons)

ML610473/ML610Q473:

Up to 95 dots (select among 19 segments x 5 commons, 20 segments x 4 commons, 21 segments x 3

commons, and 22 segments x 2 commons)

- 1/1 to 1/5 duty

- 1/2 or 1/3 bias (built-in bias generation circuit)

- Frame frequency selectable (approx. 64 Hz, 73 Hz, 85 Hz, and 102 Hz)

- Bias voltage multiplying clock selectable (8 types)

- LCD drive stop mode, LCD display mode, all LCDs on mode, and all LCDs off mode selectable

z Reset

- Reset through the RESET_N pin

- Power-on reset generation when powered on

- Reset by the watchdog timer (WDT) overflow

z Clock

- Low-speed clock (Operation of this LSI is not guaranteed under a condition with no supply of low-speed crystal

oscillation clock)

Crystal oscillation (32.768 kHz)

- High-speed clock

Built-in RC oscillation (500 kHz)

1-2

ML610471/472/473/Q471/Q472/Q473 User's Manual

Chapter 1 Overview

z Power management

- HALT mode: Suspends the instruction execution by CPU (peripheral circuits are in operating states)

- STOP mode: Stops the low-speed oscillation and high-speed oscillation (Operations of CPU and peripheral

circuits are stopped.)

- High-speed clock gear: The frequency of high-speed system clock can be changed by software (1/1, 1/2, 1/4, or

1/8 of the oscillation clock)

- Block control function: Completely stops the operation of any function block circuit that is not used (resets

registers and stops clock)

z Shipment

− Chip (Die)

ML610471-xxxWA / ML610Q471-xxxWA

ML610472-xxxWA / ML610Q472-xxxWA

ML610473-xxxWA / ML610Q473-xxxWA

ML610471P-xxxWA / ML610Q471P-xxxWA

ML610472P-xxxWA / ML610Q472P-xxxWA

ML610473P-xxxWA / ML610Q473P-xxxWA

− 48-pin plastic TQFP

ML610471-xxxTPZ03A / ML610Q471-xxxTPZ0AAL

ML610472-xxxTPZ03A / ML610Q472-xxxTPZ0AAL

ML610473-xxxTPZ03A / ML610Q473-xxxTPZ0AAL

ML610471P-xxxTPZ03A / ML610Q471P-xxxTPZ0AAL

ML610472P-xxxTPZ03A / ML610Q472P-xxxTPZ0AAL

ML610473P-xxxTPZ03A / ML610Q473P-xxxTPZ0AAL

− 64-pin plastic TQFP

ML610471-xxxTBZ03A / ML610Q471-xxxTBZ0ARL

ML610472-xxxTBZ03A / ML610Q472-xxxTBZ0ARL

ML610473-xxxTBZ03A / ML610Q473-xxxTBZ0ARL

ML610471P-xxxTBZ03A / ML610Q471P-xxxTBZ0ARL

ML610472P-xxxTBZ03A / ML610Q472P-xxxTBZ0ARL

ML610473P-xxxTBZ03A / ML610Q473P-xxxTBZ0ARL

xxx: ROM code number (xxx of the blank product is NNN, MTP version only)

Q: MTP version

P: Wide range temperature version (P version)

WA: Chip (Die)

TBZ0ARL: 64pin TQFP

TPZ0AAL: 48pin TQFP

z Guaranteed Operation Range

− Operating temperature: -20°C to +70°C (P version: -40°C to +85°C)

− Operating voltage: V

= 1.25V to 3.6V

DD

1-3

ML610471/472/473/Q471/Q472/Q473 User's Manual

)

(

)

Chapter 1 Overview

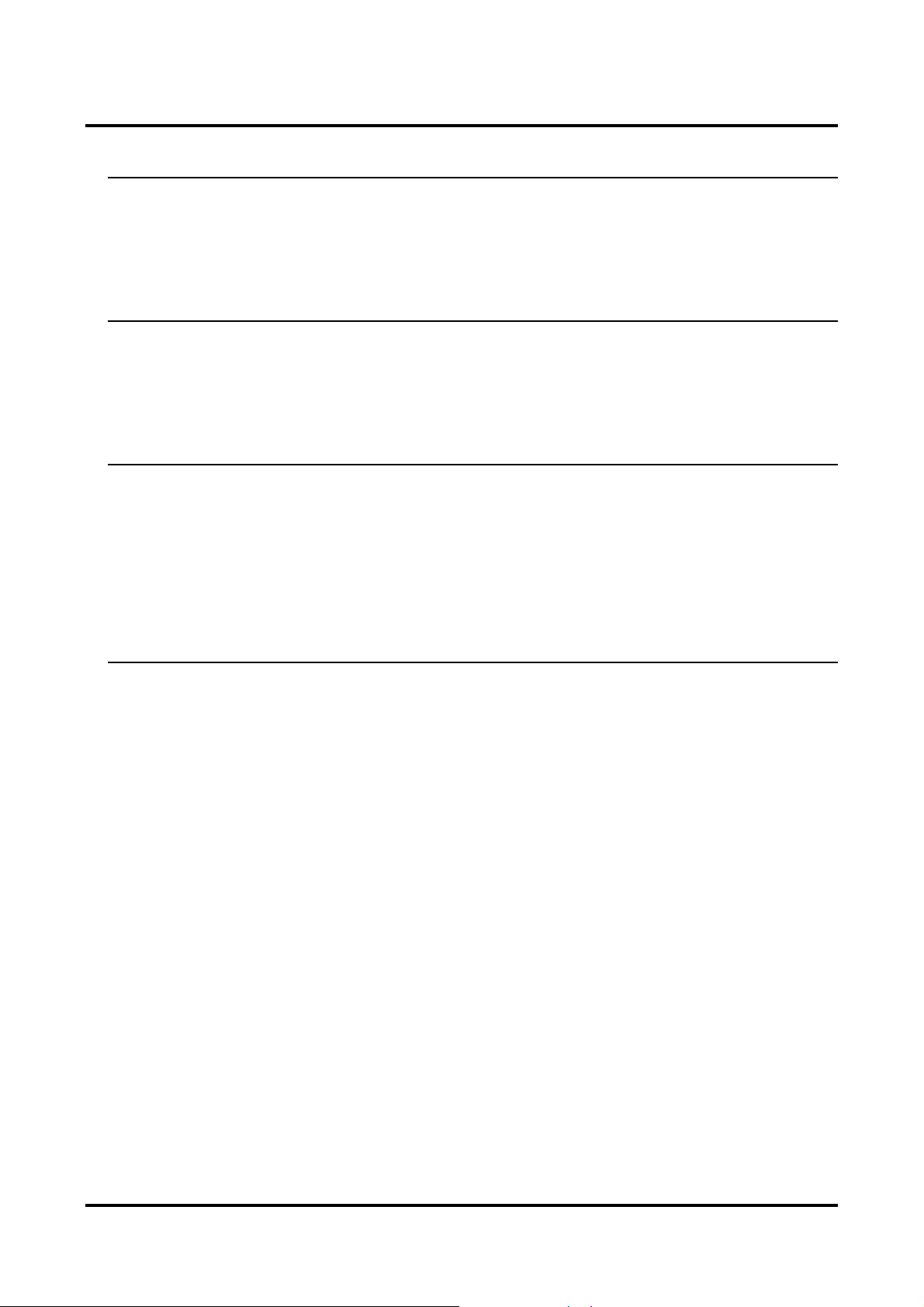

1.2 Configuration of Functional Blocks

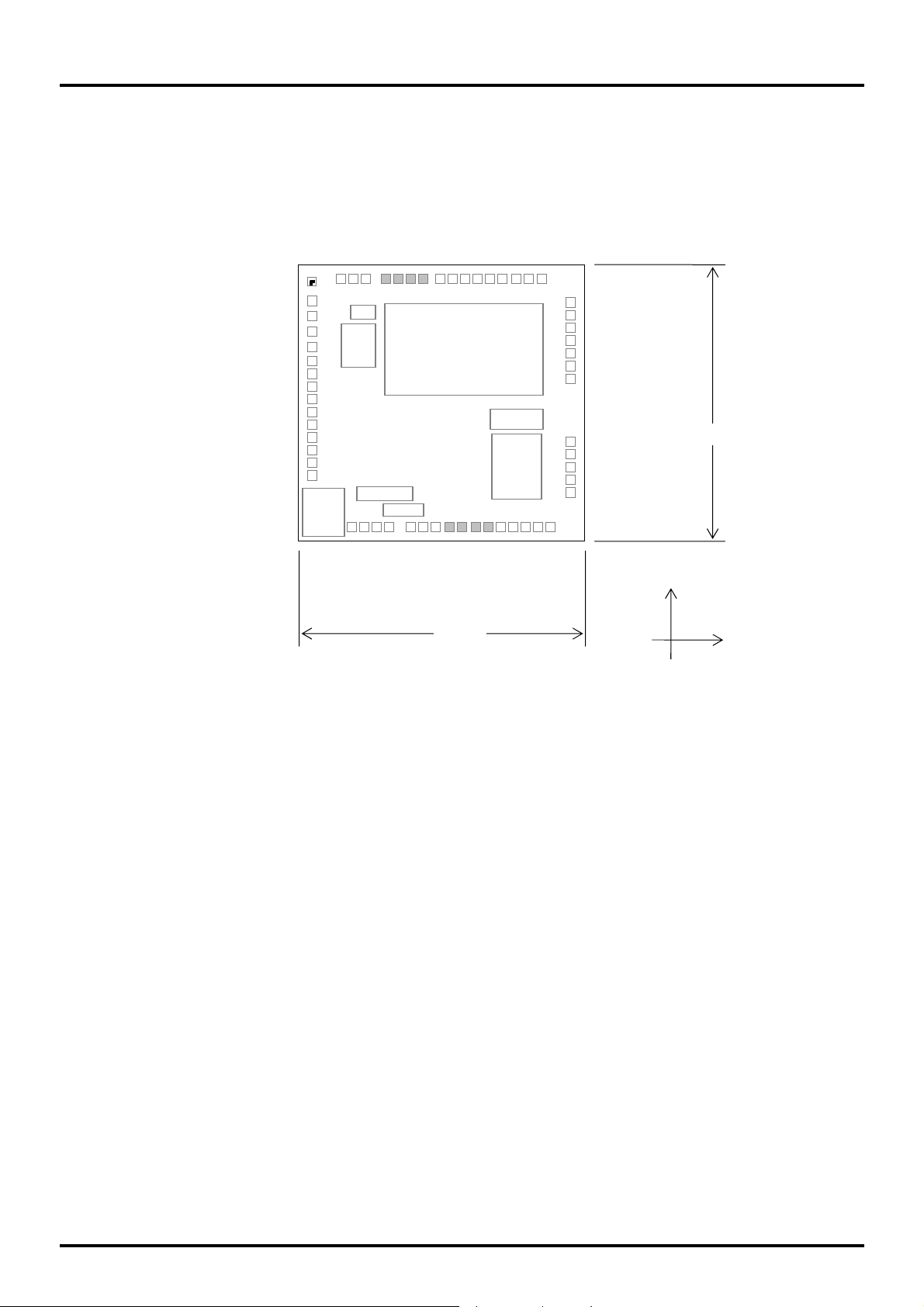

1.2.1 Block Diagram of ML610471/ML610472/ML610473

EPSW1−3

PSW

Timing

Controller

VDD

V

SS

Flash

Writer

RESET_N

TEST0

RESET &

TEST

XT0

XT1

LSCLK*

OSC

V

DDL

Power

RCM*

IN1*

CS1*

RS1*

RT1*

RC-ADC

×1

* Secondary function or Tertiary function

(*1) Select among 11 segments x 5 commons, 12 segments x 4 commons, 13 segments x 3 commons, and 14

segments x 2 commons with the register

(*2) Select among 15 segments x 5 commons, 16 segments x 4 commons, 17 segments x 3 commons, and 18

segments x 2 commons with the register

(*3) Select among 19 segments x 5 commons, 20 segments x 4 commons, 21 segments x 3 commons, and 22

segments x 2 commons with the register

Figure 1-1 Block Diagram of ML610471/ML610472/ML610473

CPU (nX-U8/100)

GREG

0−15

ALU

Instruction

Decoder

INT

1

INT

1

INT

4

INT

2

ELR1−3

LR

EA

SP

Instruction

Register

Data-bus

RAM

512 byte

Interrupt

Controller

WDT

TBC

Capture

×2

8bit Timer

×2

Display

register

110bit

ECSR1−3

DSR/CSR

PC

BUS

Controller

INT

INT

5

Program

Memory

(Mask)

8Kbyte

1

UART

GPIO

LCD

Driver

LCD

BIAS

RXD0*

TXD0*

P00 to P03

P20, P21

P35

P42 to P47

P60 to P67 (ML610471)

P60 to P63 (ML610472)

COM0 to COM4 (*1)(*2)(*3

SEG0 to SEG13 (ML610471) (*1)

SEG0 to SEG17 (ML610472) (*2)

SEG0 to SEG21

VL1, VL2, V

C1, C2

L3

ML610473) (*3

1-4

ML610471/472/473/Q471/Q472/Q473 User's Manual

)

(

)

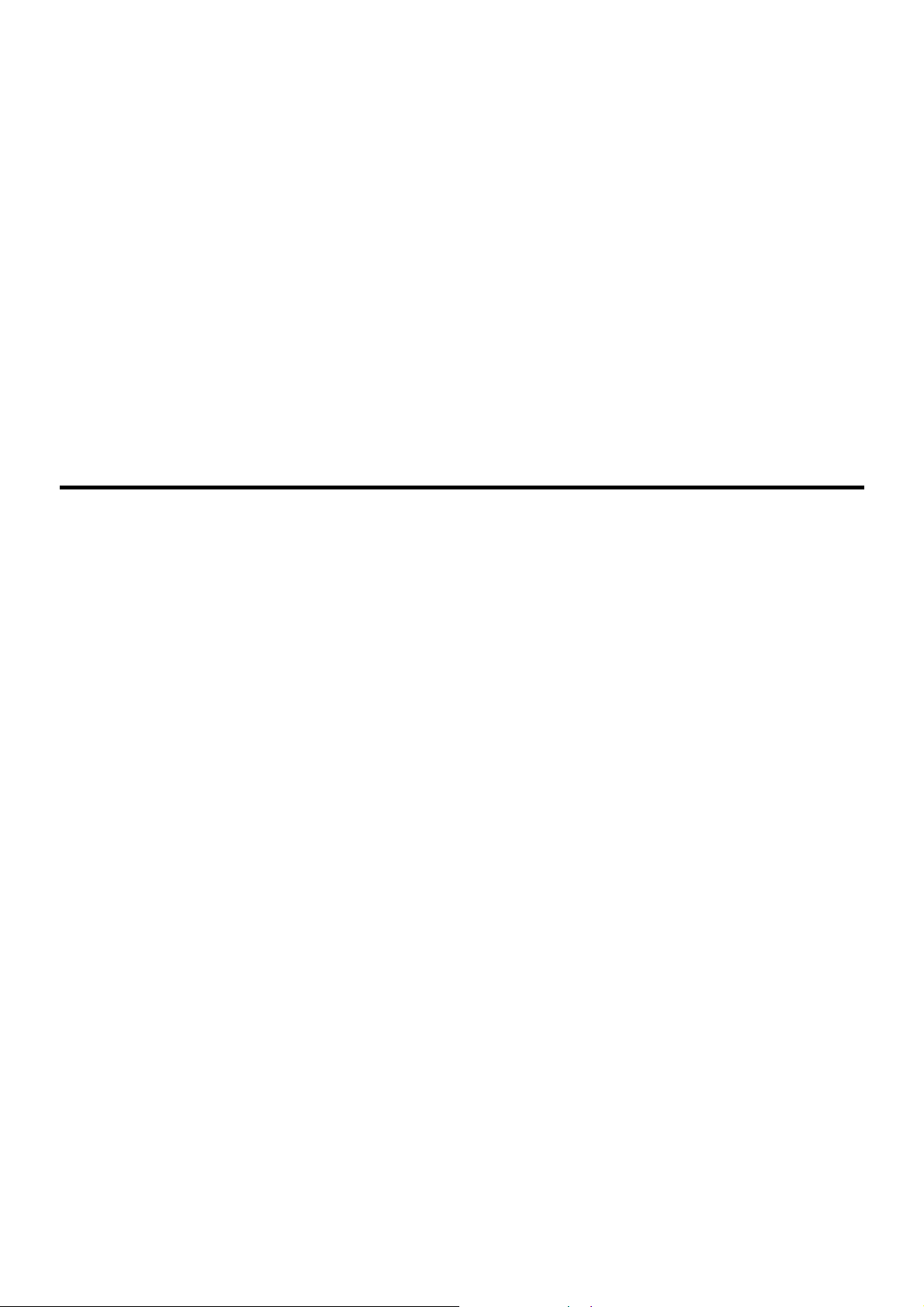

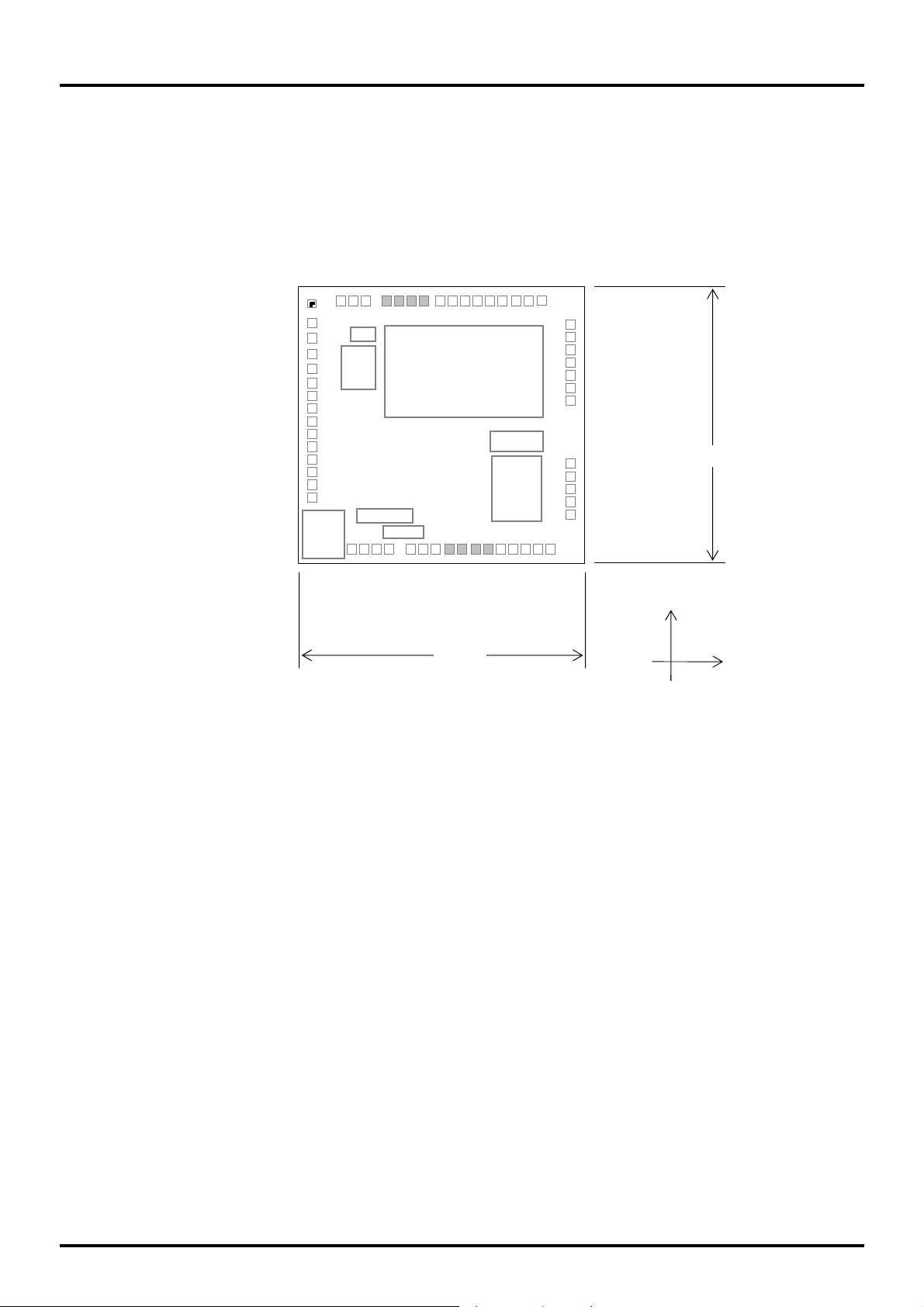

1.2.2 Block Diagram of ML610Q471/ML610Q472/ML610Q473

CPU (nX-U8/100)

EPSW1−3

PSW

Timing

Controller

Flash

Writer

GREG

0−15

ALU

Instruction

Decoder

ELR1−3

LR

EA

SP

Instruction

Register

ECSR1−3

DSR/CSR

PC

BUS

Controller

Program

Memory

(Flash)

8Kbyte

Chapter 1 Overview

VPP

VDD

V

SS

RESET_N

TEST0

XT0

XT1

LSCLK*

V

DDL

RCM*

IN1*

CS1*

RS1*

RT1*

RESET &

TEST

OSC

Power

RC-ADC

×1

Data-bus

RAM

512 byte

Interrupt

INT

1

INT

4

INT

2

Controller

WDT

TBC

Capture

×2

8bit Timer

×2

INT

1

INT

INT

5

1

UART

GPIO

RXD0*

TXD0*

P00 to P03

P20, P21

P35

P42 to P47

P60 to P67 (ML610Q471)

P60 to P63 (ML610Q472)

COM0 to COM4 (*1)(*2)(*3

SEG0 to SEG13 (ML610Q471) (*1)

SEG0 to SEG17 (ML610Q472) (*2)

SEG0 to SEG21

VL1, VL2, V

C1, C2

L3

ML610Q473) (*3

*

Secondary function or Tertiary function

Display

register

110bit

LCD

Driver

LCD

BIAS

(*1) Select among 11 segments x 5 commons, 12 segments x 4 commons, 13 segments x 3 commons, and 14

segments x 2 commons with the register

(*2) Select among 15 segments x 5 commons, 16 segments x 4 commons, 17 segments x 3 commons, and 18

segments x 2 commons with the register

(*3) Select among 19 segments x 5 commons, 20 segments x 4 commons, 21 segments x 3 commons, and 22

segments x 2 commons with the register

Figure 1-2 Block Diagram of ML610Q471/ML610Q472/ML610Q473

1-5

ML610471/472/473/Q471/Q472/Q473 User's Manual

Chapter 1 Overview

1.3 Pins

1.3.1 Pin Layout

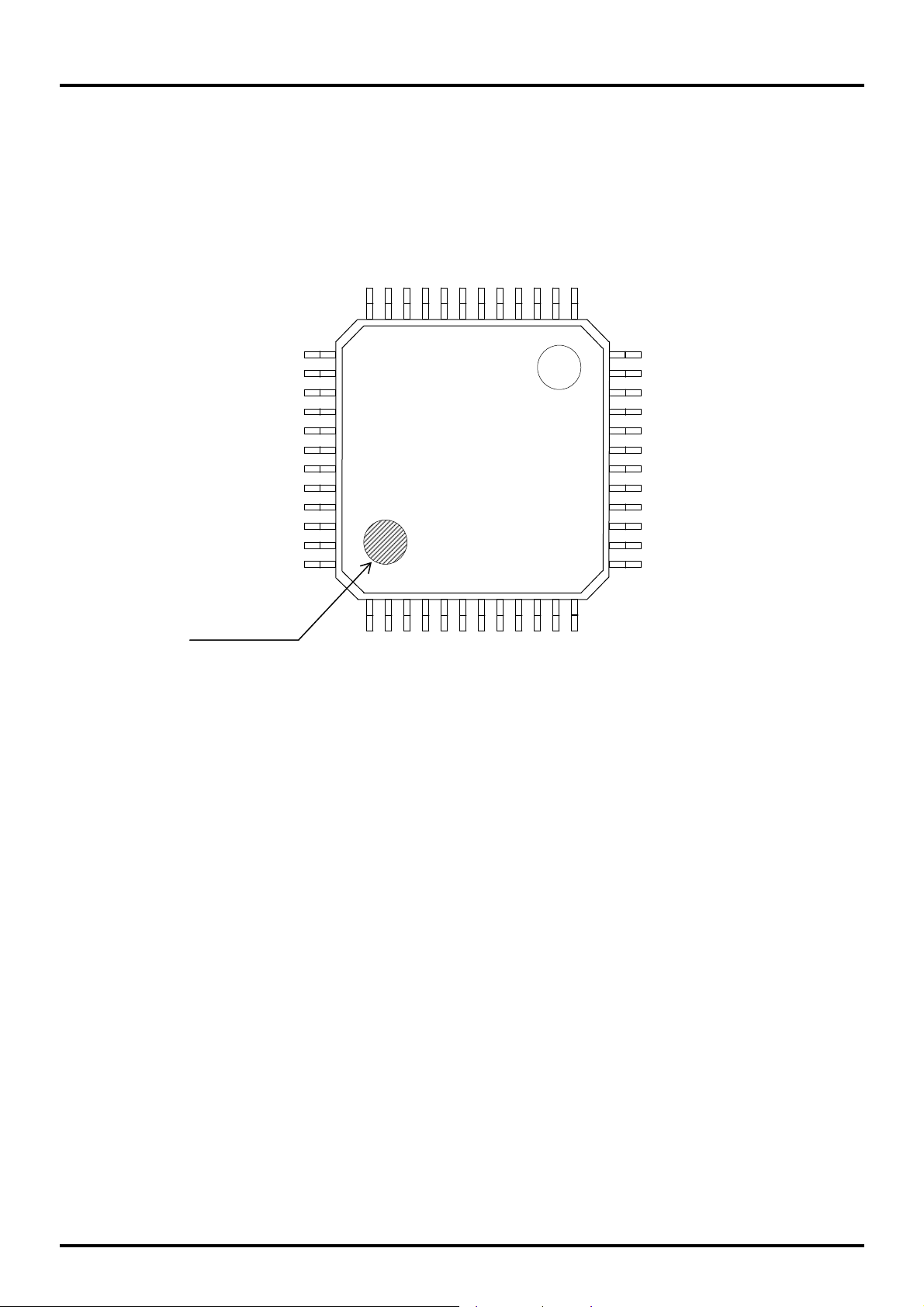

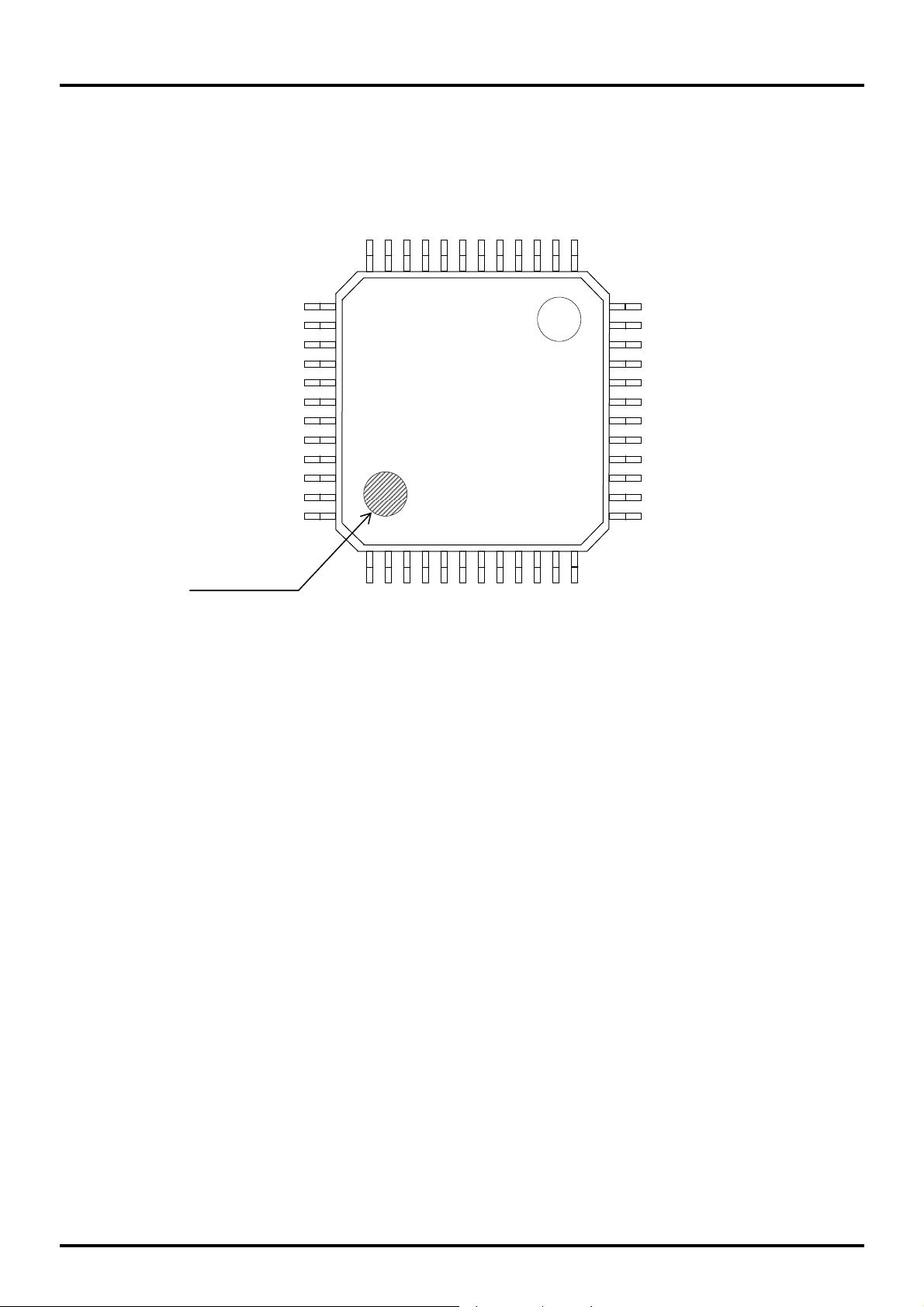

1.3.1.1 Pin Layout of ML610471/ML610Q471 48pin TQFP Package

P65

P66

P67

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

26

27

28

29

30

31

32

33

34

35

36

P64

P63

P62

P61

P60

P20

P43

P00

P01

P02

P03

NC(*1) / VPP(*2)

37

38

39

40

41

42

43

44

45

46

47

48

1 2 3 4 5 6 7 8 9

10

11

SEG5

25

24

23

22

21

20

19

18

17

16

15

14

13

12

SEG4

SEG3

COM4/SEG2

COM3/SEG1

COM2/SEG0

COM1

COM0

VL3

VL2

VL1

C2

C1

MIRROR FINISH

P44

P45

P46

P47

VSS

VDD

XT0

VDDL

XT1

TEST0

RESET_N

P35

(NC): No Connection

(*1) : ML610471

(*2) : ML610Q471

Figure 1-3 Pin Layout of ML610471/ML610Q471 48pin TQFP Package

1-6

ML610471/472/473/Q471/Q472/Q473 User's Manual

1.3.1.2 Pin Layout of ML610471/ML610Q471 64pin TQFP Package

NC

NC

P65

P66

P67

NC

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

NC

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

NC

P64

P63

P62

P61

P60

P20

P21

P42

P43

P00

P01

P02

P03

NC(*1) / VPP(*2)

NC

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

1 2 3 4 5 6 7 8 9

10

11

12

14

13

16

15

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

Chapter 1 Overview

NC

SEG4

SEG3

COM4/SEG2

COM3/SEG1

COM2/SEG0

COM1

COM0

VL3

VL2

VL1

C2

C1

NC

NC

NC

MIRROR FINISH

NC

NC

VSS

VDD

NC

XT0

VDDL

XT1

P44

P45

TEST0

RESET_N

NC

P46

P47

P35

(NC): No Connection

(*1) : ML610471

(*2) : ML610Q471

Figure 1-4 Pin Layout of ML610471/ML610Q471 64pin Package

1-7

ML610471/472/473/Q471/Q472/Q473 User's Manual

(*1)

Chapter 1 Overview

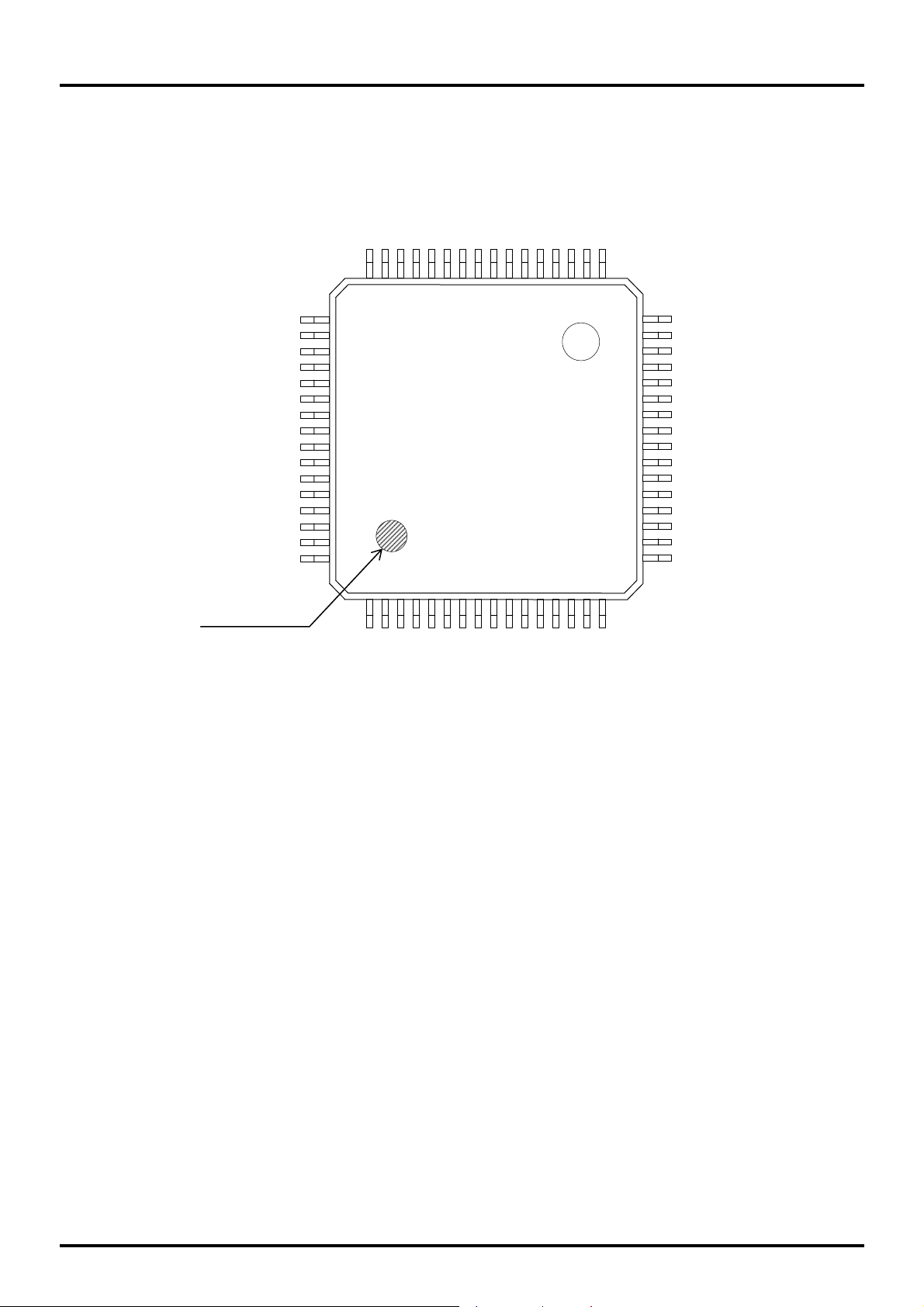

1.3.1.3 Pin Layout of ML610472/ML610Q472 48pin TQFP Package

SEG16

SEG15

SEG14

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

26

27

28

29

30

31

32

33

34

35

36

NC

SEG17

P63

P62

P61

P60

P20

P43

P00

P01

P02

P03

/ VPP(*2)

37

38

39

40

41

42

43

44

45

46

47

48

1 2 3 4 5 6 7 8 9

10

11

SEG5

25

24

23

22

21

20

19

18

17

16

15

14

13

12

SEG4

SEG3

COM4/SEG2

COM3/SEG1

COM2/SEG0

COM1

COM0

VL3

VL2

VL1

C2

C1

MIRROR FINISH

P44

P45

P46

P47

VSS

VDD

XT0

VDDL

XT1

TEST0

RESET_N

P35

(NC): No Connection

(*1) : ML610472

(*2) : ML610Q472

Figure 1-5 Pin Layout of ML610472/ML610Q472 48pin Package

1-8

ML610471/472/473/Q471/Q472/Q473 User's Manual

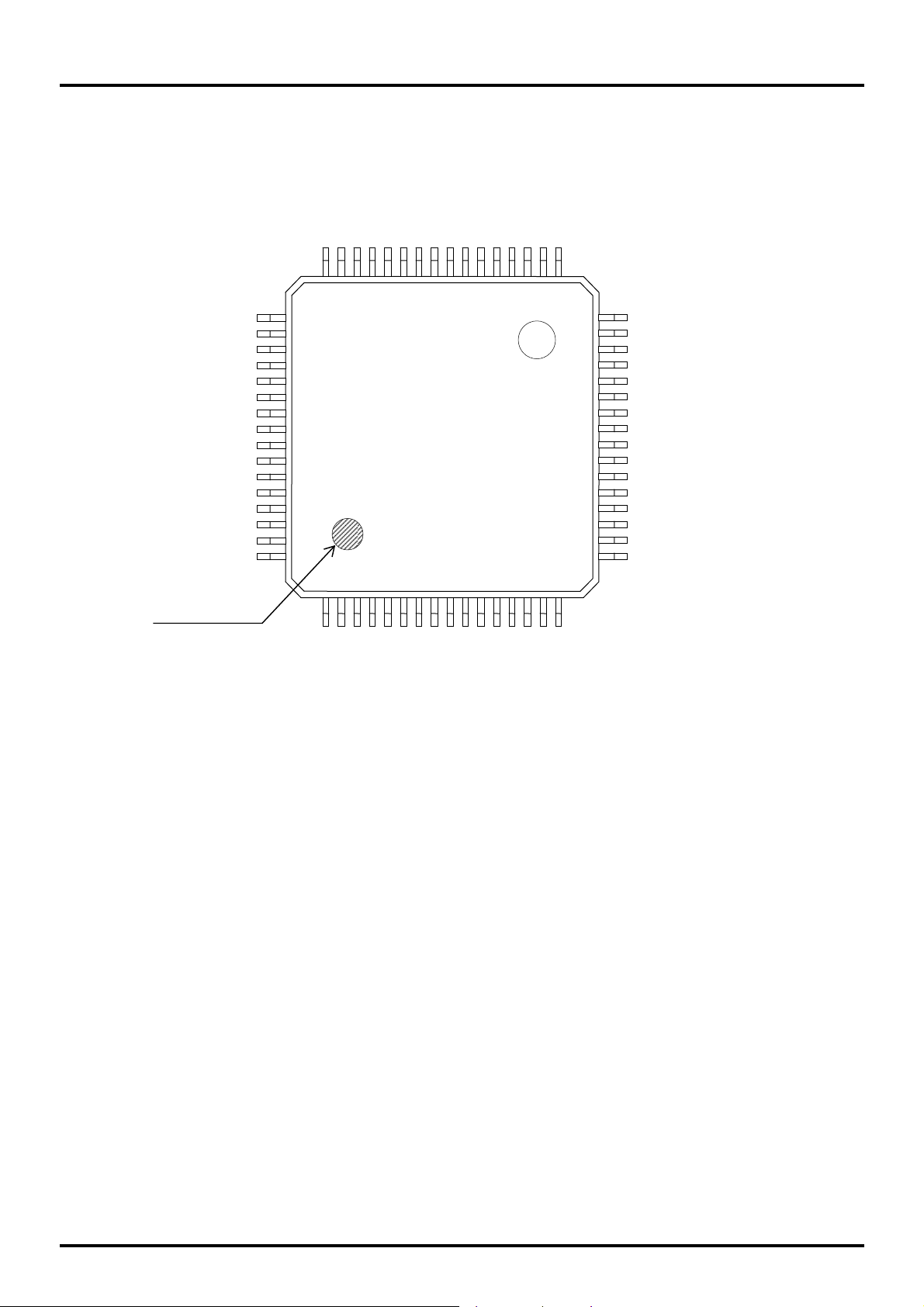

1.3.1.4 Pin Layout of ML610472/ML610Q472 64pin TQFP Package

NC

NC

SEG16

SEG15

SEG14

NC

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

36

37

38

39

40

41

42

43

44

45

46

47

48

NC

SEG17

P63

P62

P61

P60

P20

P21

P42

P43

P00

P01

P02

P03

NC(*1) / VPP(*2)

NC

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

1 2 3 4 5 6 7 8 9

10

11

12

13

SEG6

35

14

SEG5

34

15

NC

33

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

Chapter 1 Overview

NC

SEG4

SEG3

COM4/SEG2

COM3/SEG1

COM2/SEG0

COM1

COM0

VL3

VL2

VL1

C2

C1

NC

NC

NC

MIRROR FINISH

NC

NC

VSS

VDD

VDDL

NC

XT0

XT1

P44

P45

TEST0

RESET_N

NC

P46

P47

P35

(NC): No Connection

(*1) : ML610472

(*2) : ML610Q472

Figure 1-6 Pin Layout of ML610472/ML610Q472 64pin Package

1-9

ML610471/472/473/Q471/Q472/Q473 User's Manual

Chapter 1 Overview

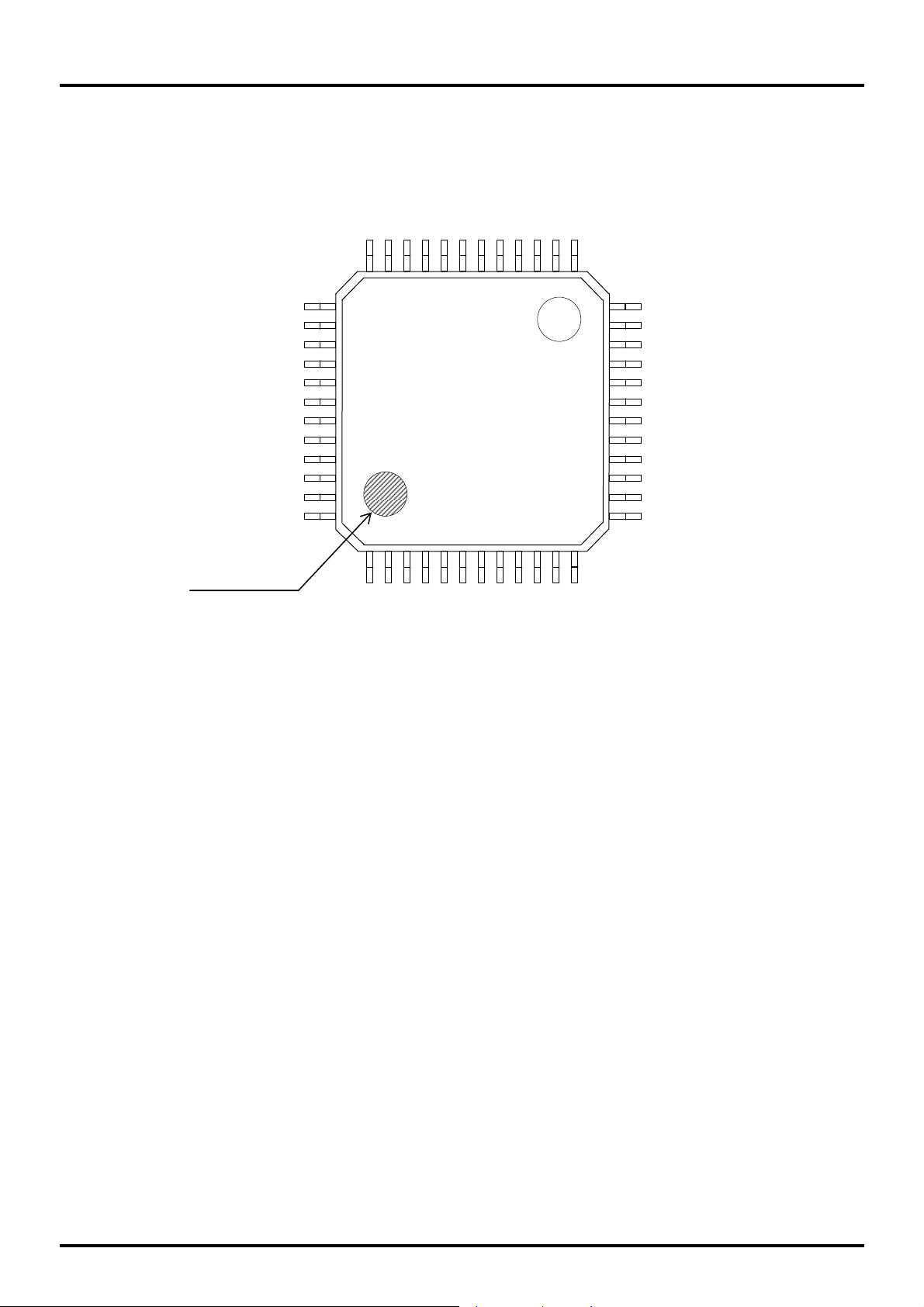

1.3.1.5 Pin Layout of ML610473/ML610Q473 48pin TQFP Package

SEG16

SEG15

SEG14

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

26

27

28

29

30

31

32

33

34

35

36

SEG17

SEG18

SEG19

SEG20

SEG21

P20

P43

P00

P01

P02

P03

NC(*1) / VPP(*2)

37

38

39

40

41

42

43

44

45

46

47

48

1 2 3 4 5 6 7 8 9

10

11

SEG5

25

24

23

22

21

20

19

18

17

16

15

14

13

12

SEG4

SEG3

COM4/SEG2

COM3/SEG1

COM2/SEG0

COM1

COM0

VL3

VL2

VL1

C2

C1

MIRROR FINISH

P44

P45

P46

P47

VSS

VDD

XT0

VDDL

XT1

TEST0

RESET_N

P35

(NC): No Connection

(*1) : ML610473

(*2) : ML610Q473

Figure 1-7 Pin Layout of ML610473/ML610Q473 48pin Package

1-10

ML610471/472/473/Q471/Q472/Q473 User's Manual

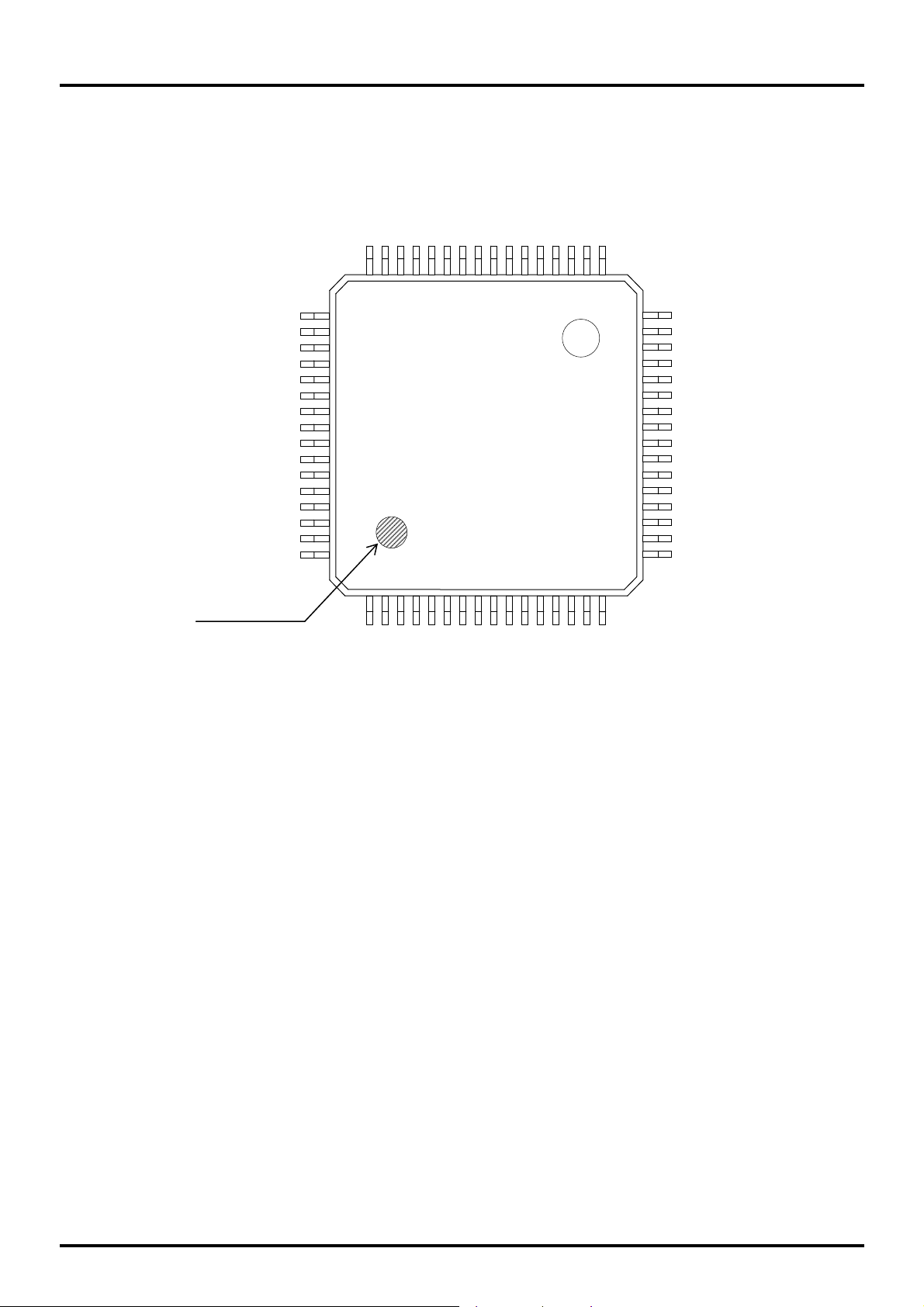

1.3.1.6 Pin Layout of ML610473/ML610Q473 64pin TQFP Package

NC

NC

SEG16

SEG15

SEG14

NC

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

36

37

38

39

40

41

42

43

44

45

46

47

48

NC

SEG17

SEG18

SEG19

SEG20

SEG21

P20

P21

P42

P43

P00

P01

P02

P03

NC(*1) / VPP(*2)

NC

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

1 2 3 4 5 6 7 8 9

10

11

12

13

SEG6

35

14

SEG5

34

15

NC

33

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

Chapter 1 Overview

NC

SEG4

SEG3

COM4/SEG2

COM3/SEG1

COM2/SEG0

COM1

COM0

VL3

VL2

VL1

C2

C1

NC

NC

NC

MIRROR FINISH

NC

NC

VSS

VDD

VDDL

NC

XT0

XT1

P44

P45

TEST0

RESET_N

NC

P46

P47

P35

(NC): No Connection

(*1) : ML610473

(*2) : ML610Q473

Figure 1-8 Pin Layout of ML610473/ML610Q473 64pin Package

1-11

ML610471/472/473/Q471/Q472/Q473 User's Manual

Chapter 1 Overview

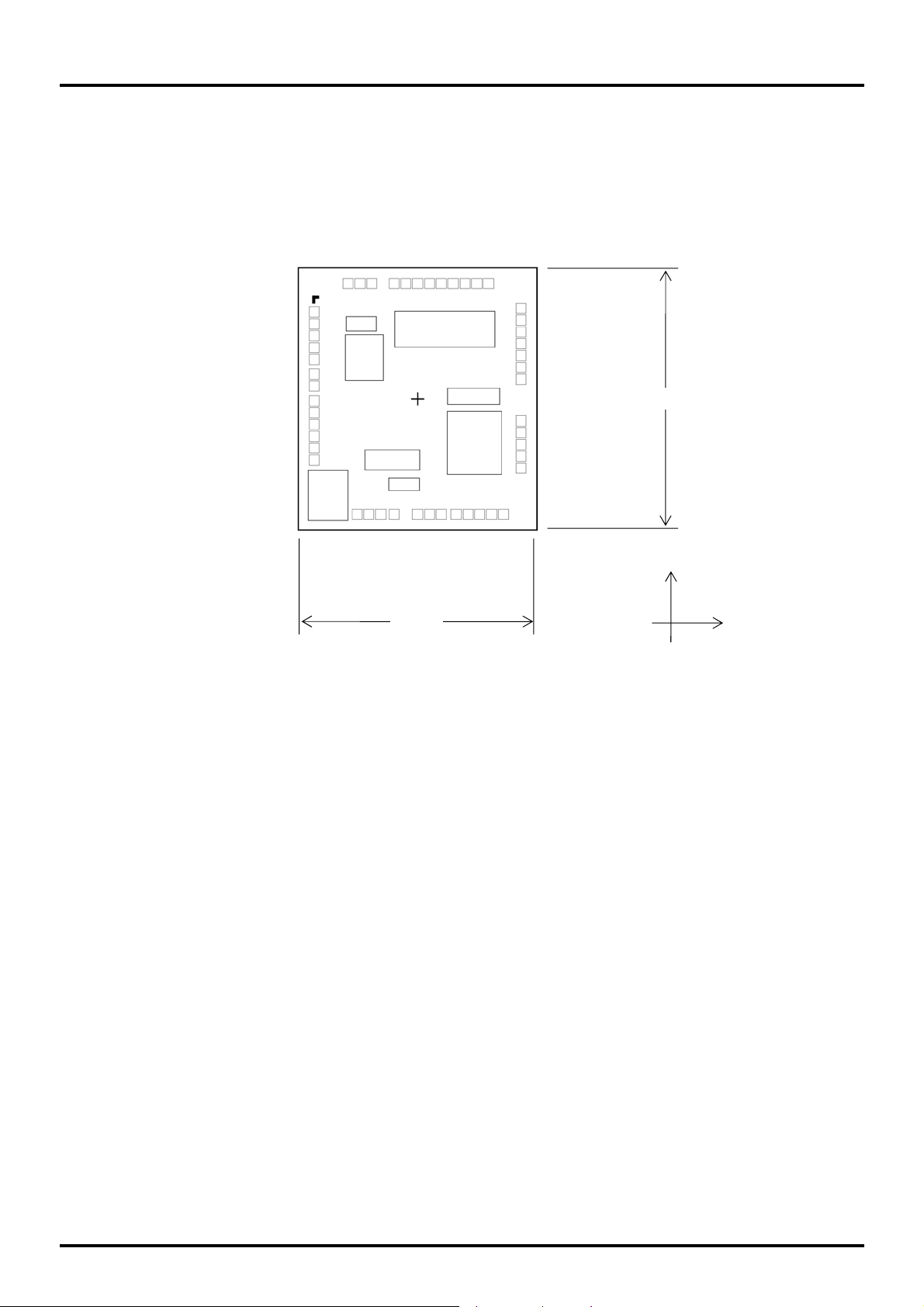

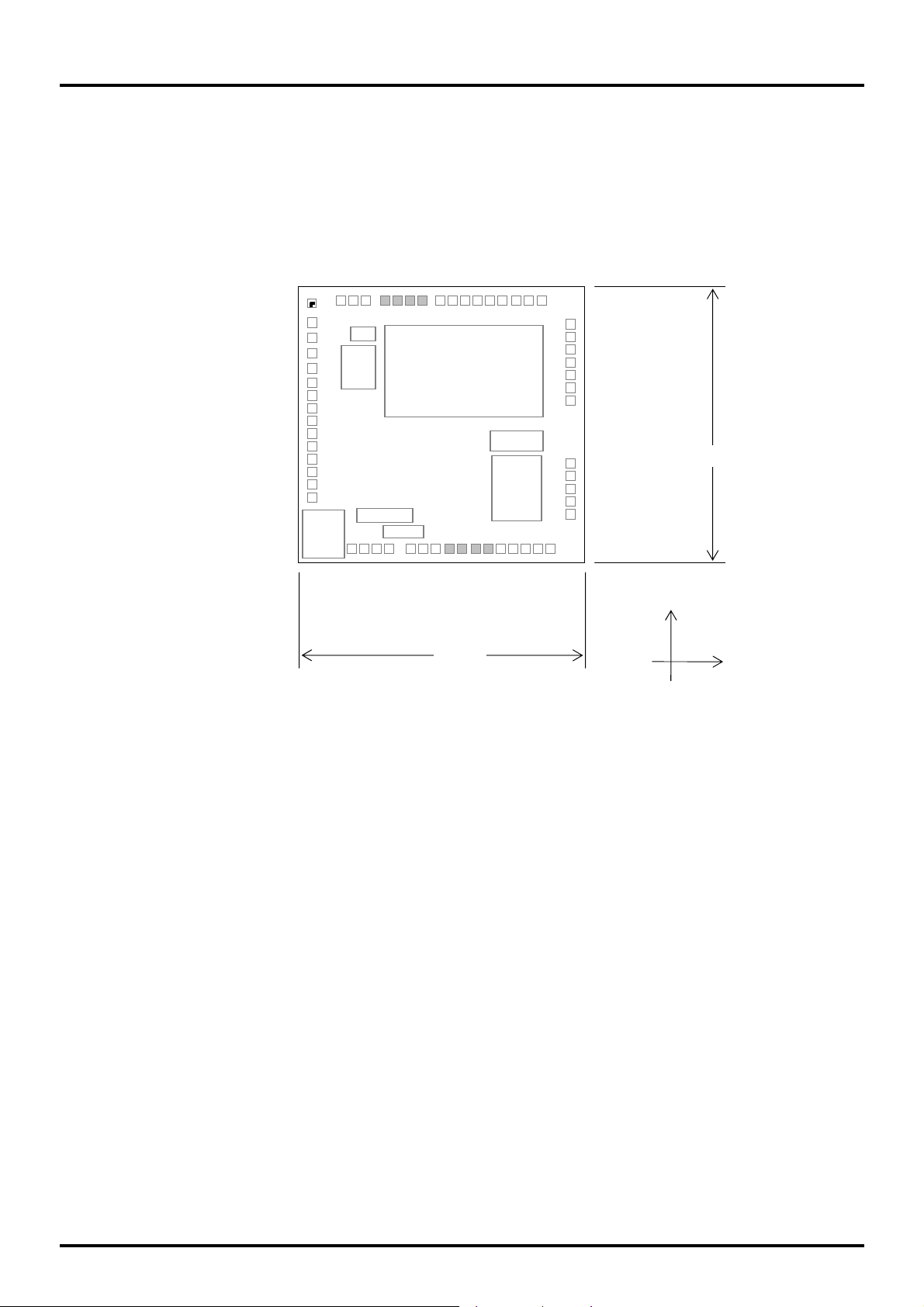

1.3.1.7 Pin Layout of ML610471 Chip

SEG13

SEG12

SEG11

31

32

33

34 P67

P64

P63

P62

P61

P60

P20

P21

P42

P43

P00

P01

P02

P03

37

38

39

40

41

42

43

44

45

46

47

48

49

P65

36

P66

35

SEG10

30

SEG9

29

SEG8

28

SEG7

27

SEG6

26

SEG5

25

SEG4

24

SEG3

23

COM4/SEG2

22

COM3/SEG1

21

COM2/SEG0

20

COM1

19

18

COM0

17

VL3

VL2

16

VL1

15

C2

14

C1

13

1.77mm

8

1 2 3 4 5 6 7

XT0

XT1

VSS

VDD

VDDL

1.61mm

9

11

12

10

P44

P45

P46

P47

P35

TEST0

RESET_N

Y

X

Chip size: 1.61 mm × 1.77 mm

PAD count: 49 pins

Minimum PAD pitch: 80μm

PAD aperture: 70μm×70μm

Chip thickness: 350μm

Voltage of the rear side of chip: V

level.

SS

Figure 1-9 Dimensions of ML610471 Chip

1-12

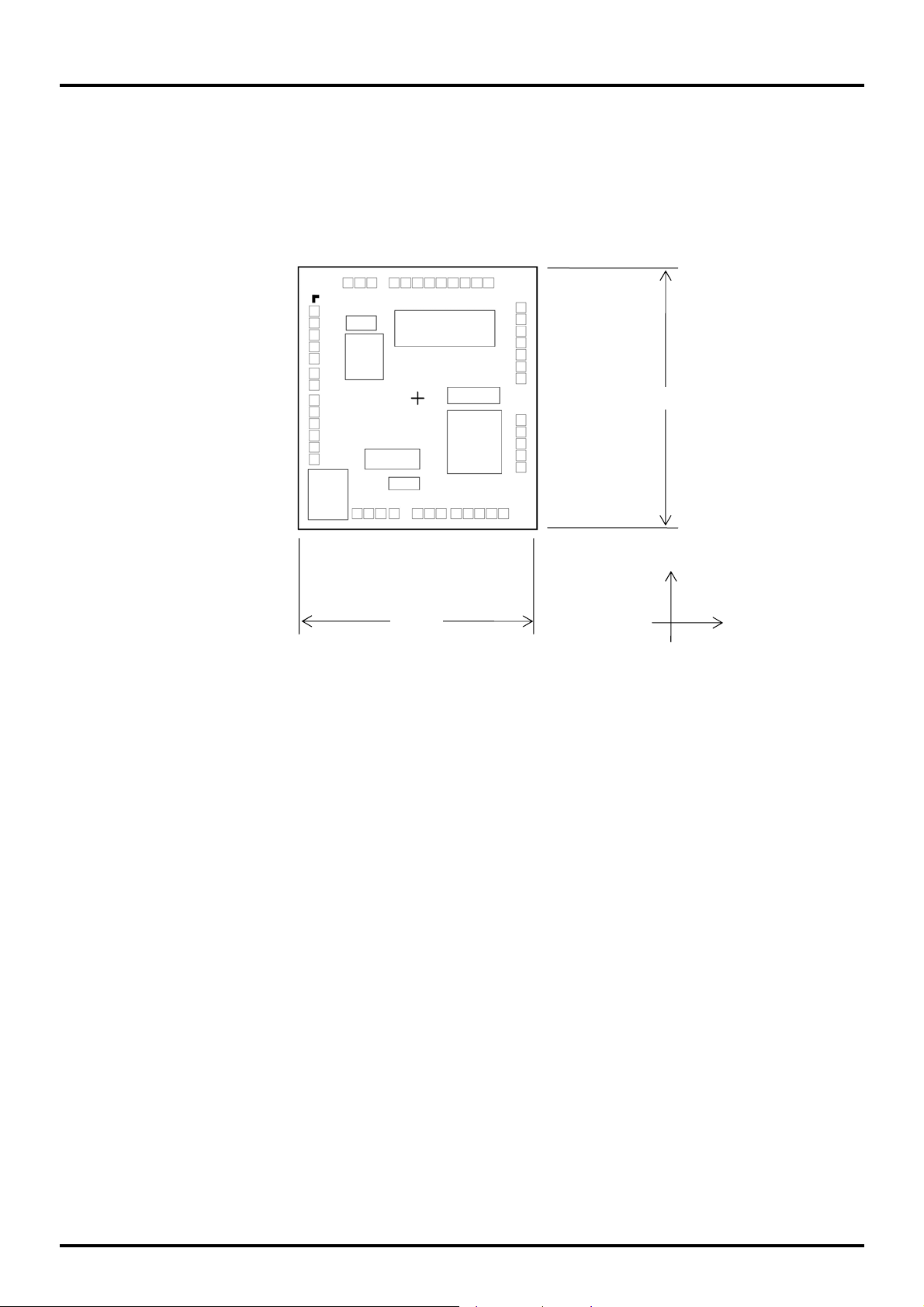

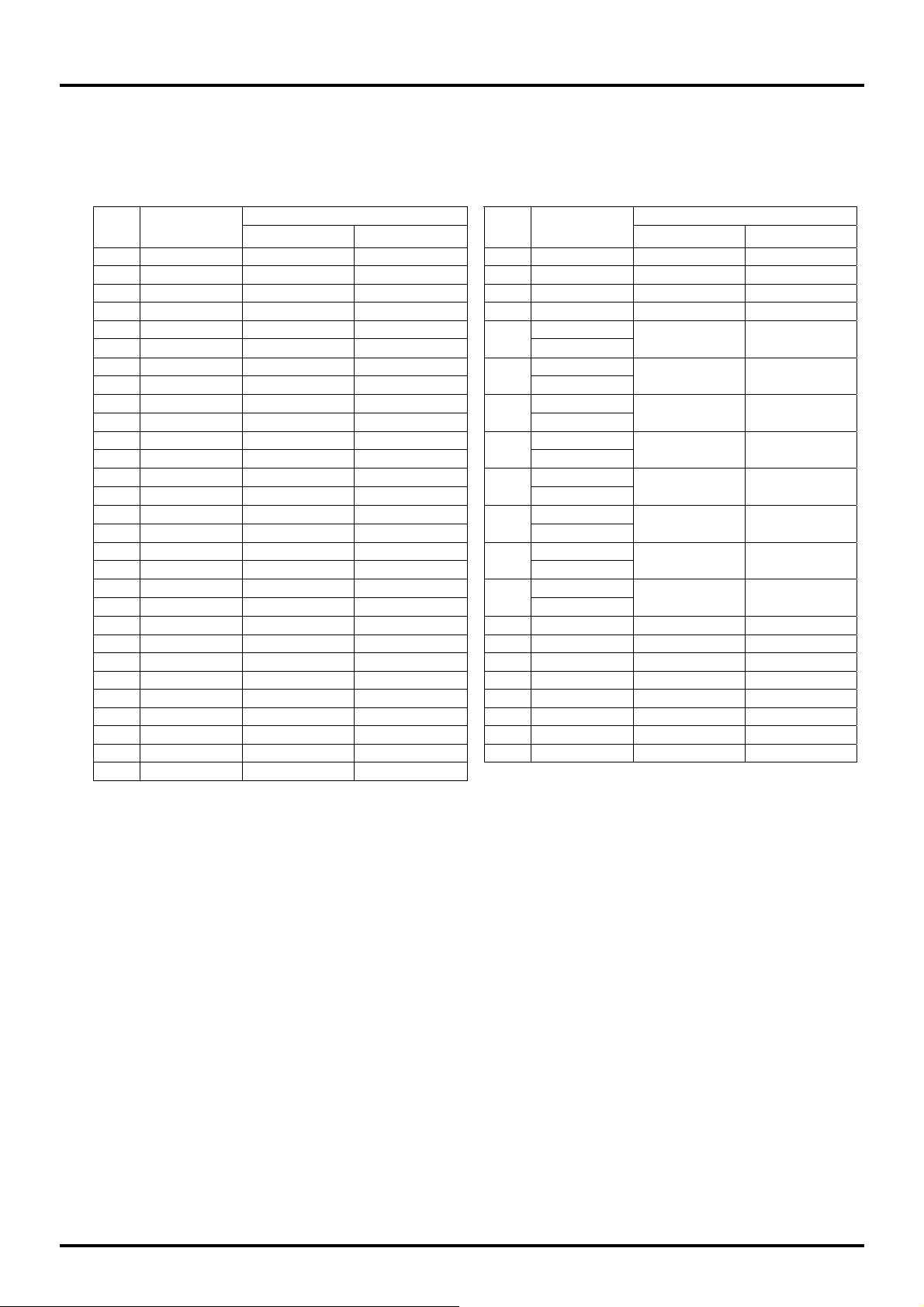

1.3.1.8 Pin Layout of ML610472 Chip

SEG17

P63

P62

P61

P60

P20

P21

P42

P43

P00

P01

P02

P03

37

38

39

40

41

42

43

44

45

46

47

48

49

SEG16

36

SEG15

35

ML610471/472/473/Q471/Q472/Q473 User's Manual

Chapter 1 Overview

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

31

32

33

34 SEG14

30

29

28

27

26

25

SEG4

24

SEG3

23

COM4/SEG2

22

COM3/SEG1

21

COM2/SEG0

20

COM1

19

18

COM0

17

VL3

VL2

16

VL1

15

C2

14

C1

13

1.77mm

8

1 2 3 4 5 6 7

XT0

XT1

VSS

VDD

VDDL

1.61mm

9

11

12

10

P44

P45

P46

P47

P35

TEST0

RESET_N

Y

X

Chip size: 1.61 mm × 1.77 mm

PAD count: 49 pins

Minimum PAD pitch: 80μm

PAD aperture: 70μm×70μm

Chip thickness: 350μm

Voltage of the rear side of chip: V

level.

SS

Figure 1-10 Dimensions of ML610472 Chip

1-13

ML610471/472/473/Q471/Q472/Q473 User's Manual

Chapter 1 Overview

1.3.1.9 Pin Layout of ML610473 Chip

SEG13

SEG12

SEG11

31

32

33

34 SEG14

SEG17

SEG18

SEG19

SEG20

SEG21

P20

P21

P42

P43

P00

P01

P02

P03

37

38

39

40

41

42

43

44

45

46

47

48

49

SEG16

36

SEG15

35

SEG10

30

SEG9

29

SEG8

28

SEG7

27

SEG6

26