Page 1

UE9 Product Page

Published on LabJack (http://labjack.com)

Home > UE9 User's Gui de

UE9 User's Guide

This is the complete user's guide for the UE9, including documentation for the LabJackUD driver.

Includes specifications in Appendix A.

To make a PDF of the whole manual, click "Export all" towards the upper-right of this page. Doing so

converts these pages to a PDF on-the-fly, using the latest content, and can take 20-30 seconds.

Make sure you have a current browser (we mostly test in Firefox and Chrome) and the current version

of Acrobat Reader. If it is not working for you, rather than a normal click of "Export all" do a right-click

and select "Save link as" or similar. Then wait 20-30 seconds and a dialog box will pop up asking

you where to save the PDF. Then you can open it in the real Acrobat Reader, not embedded in a

browser. If you still have problems, try the "Print all" option instead. In addition, an export is attached

below, but will not always be the latest version.

If you are looking at a PD F or hardcopy, realize that the original is an online document at http://labjack.com/support/ue9/usersguide.

Rather than using a PDF, though, we encourage you to use this web-based documentation. Some advantages:

We can quickly change or update content.

The site search includes the user's guide, forum, and all other resources at labjack.com. When you are looking for

something try using the site search.

For support, try going to the applicable user's guide page and post a comment. When appropriate we can then immediately

add/change content on that page to address the question.

One other trick worth mentioning, is to browse the table of contents to the left. Rather than clicking on all the links to browse, you

can click on the small black triangles to expand without reloading the whole page.

User's Guide

File attachment:

UE9_UG_Export_04282011.pdf

Preface

For the latest version of this and other documents, go to www.labjack.com.

Copyright 2012, LabJack Corporation

Package Contents:

The normal retail packaged UE9 or UE9-Pro consists of:

UE9 (-Pro) unit itself in red enclosure

USB cable (6 ft / 1.8 m)

Ethernet cable (6 ft / 1.8 m)

Power supply

Screwdriver

1

Page 2

Warranty:

The LabJack UE9 is covered by a 1 year limited warranty from LabJack Corporation, covering this product and parts against

defects in material or workmanship. The LabJack can be damaged by misconnection (such as connecting 120 VAC to any of the

screw terminals), and this warranty does not cover damage obviously caused by the customer. If you have a problem, contact

support@labjack.com for return authorization. In the case of warranty repairs, the customer is responsible for shipping to LabJack

Corporation, and LabJack Corporation will pay for the return shipping.

Limitation of Liability:

LabJack designs and manufactures measurement and automation peripherals that enable the connection of a PC to the realworld. Although LabJacks have various redundant protection mechanisms, it is possible, in the case of improper and/or

unreasonable use, to damage the LabJack and even the PC to which it is connected. LabJack Corporation will not be liable for

any such damage.

Except as specified herein, LabJack Corporation makes no warranties, express or implied, including but not limited to any implied

warranty or merchantability or fitness for a particular purpose. LabJack Corporation shall not be liable for any special, indirect,

incidental or consequential damages or losses, including loss of data, arising from any cause or theory.

LabJacks and associated products are not designed to be a critical component in life support or systems where malfunction can

reasonably be expected to result in personal injury. Customers using these products in such applications do so at their own risk

and agree to fully indemnify LabJack Corporation for any damages resulting from such applications.

LabJack assumes no liability for applications assistance or customer product design. Customers are responsible for their

applications using LabJack products. To minimize the risks associated with customer applications, customers should provide

adequate design and operating safeguards.

Reproduction of products or written or electronic information from LabJack Corporation is prohibited without permission.

Reproduction of any of these with alteration is an unfair and deceptive business practice.

Conformity Information (FCC, CE, RoHS):

See the Conformity Page and the text below:

FCC PART 15 STATEMENTS:

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC

Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in

a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used

in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment

in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his

own expense. The end user of this product should be aware that any changes or modifications made to this equipment without the

approval of the manufacturer could result in the product not meeting the Class B limits, in which case the FCC could void the user's

authority to operate the equipment.

Declaration of Conformity:

Manufacturers Name: LabJack Corporation

Manufacturers Address: 3232 S Vance St STE 100, Lakewood, CO 80227, USA

Declares that the product

Product Name: LabJack UE9 (-Pro)

Model Number: LJUE9 (-Pro)

conforms to the following Product Specifications:

EN 55011 Class B

EN 61326-1: 2002 General Requirements

and is marked with CE

RoHS:

The UE9 (-Pro) is RoHS compliant per the requirements of Directive 2002/95/EC.

1 - Installation on Windows

The LJUD driver requires a PC running Windows. For other operating systems, go to labjack.com for available support. Software

2

Page 3

will be installed to the LabJack directory which defaults to c:\Program Files\LabJack\.

Install the software first: Go to labjack.com/support/ue9.

Connect the USB cable: (See Section 2.2 for Ethernet installation tips) The USB cable provides data and power. After the UD

software installation is complete, connect the hardware and Windows should prompt with “Found New Hardware” and shortly after

the Found New Hardware Wizard will open. When the Wizard appears allow Windows to install automatically by accepting all

defaults.

Run LJControlPanel: From the Windows Start Menu, go to the LabJack group and run LJControlPanel. Click the “Find Devices”

button, and an entry should appear for the connected UE9 showing the serial number. Click on the “USB – 1” entry below the serial

number to bring up the UE9 configuration panel. Click on “Test” in the configuration panel to bring up the test panel where you can

view and control the various I/O on the UE9.

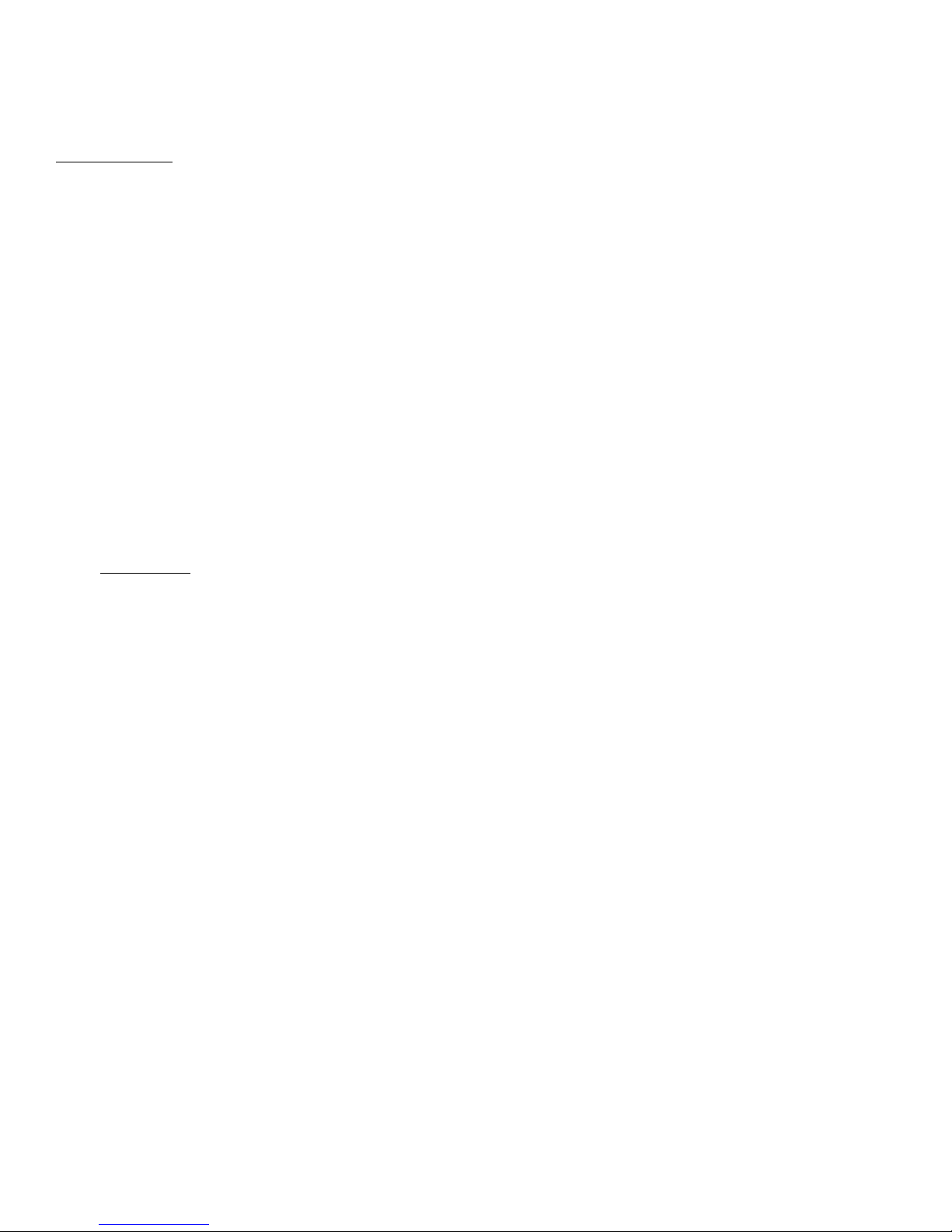

If LJControlPanel does not find the UE9, check Windows Device Manager to see if the UE9 installed correctly. One way to get to

the Device Manager is:

Start => Control Panel => System => Hardware => D evice Manager

The entry for the UE9 should appear as in the following figure. If it has a yellow caution symbol or exclamation point symbol, rightclick and select “Uninstall” or “Remove”. Then disconnect and reconnect the UE9 and repeat the Found New Hardware Wizard as

described above.

1.1 - Control Panel Application (LJControlPanel)

The LabJack Control Panel application (LJCP.exe) handles configuration and testing of the UE9. Click on the “Find LabJacks”

button to search for connected devices.

Figure 1-1. LJControlPanel Main Window

Figure 1-1 shows the results from a typical search. The application found one UE9 connected by USB and Ethernet. It also found a

second UE9 that is accessible only by Ethernet. The USB connection has been selected in Figure 1-1, bringing up the

configuration window on the right side.

Refresh: Reload the window using values read from the device.

Write to Device: Write the values from the window to the device. Depending on the values that have been changed, the

3

Page 4

application might prompt for a device reset.

Reset: Click to reset the selected device.

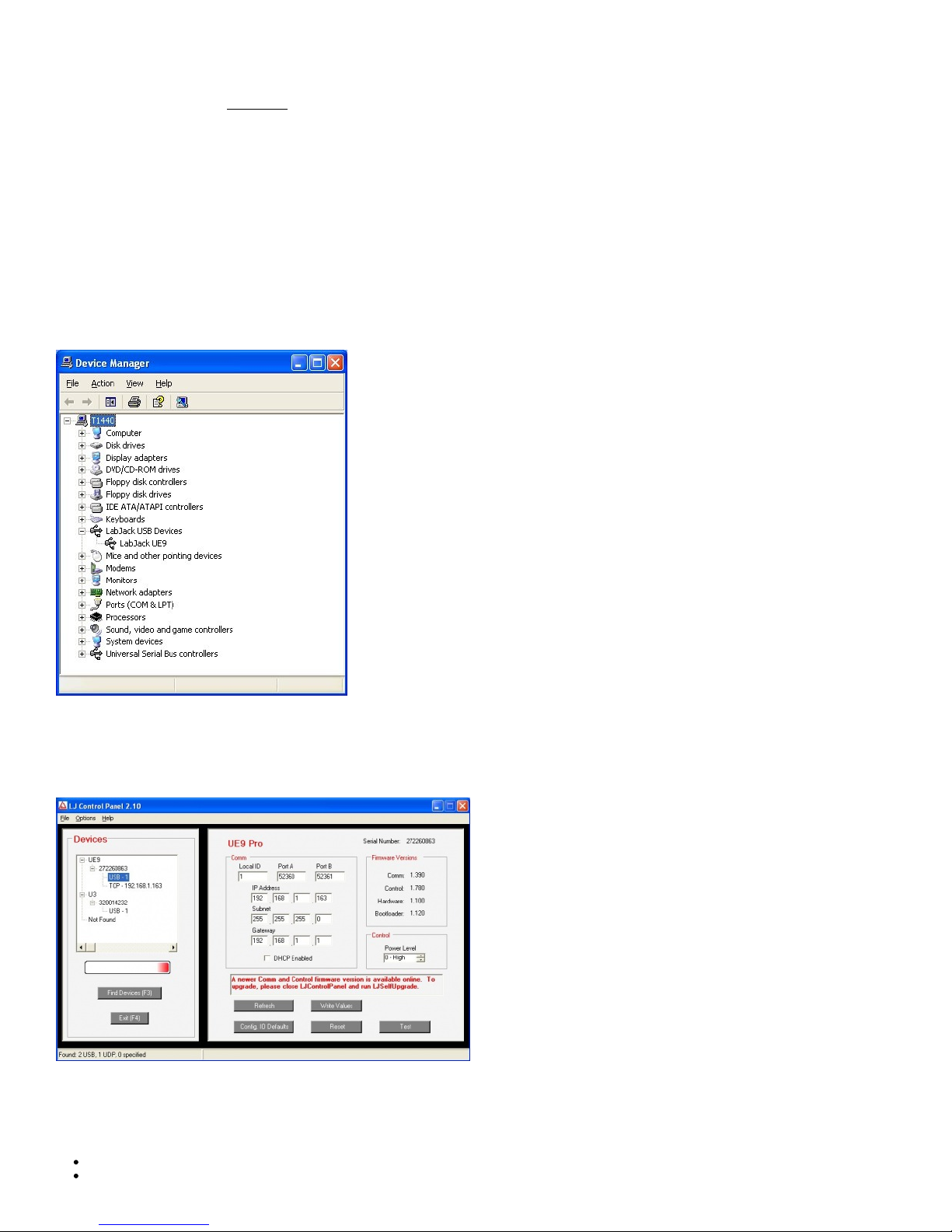

Test: Opens the window shown in Figure 1-2. This window continuously writes to and reads from the selected LabJack.

Figure 1-2. LJControlPanel Test Window

Selecting Options=>Settings from the main LJControlPanel menu brings up the window shown in Figure 1-3. This window allows

some features to of the LJControlPanel application to be customized.

Figure 1-3. LJControlPanel Settings Window

Search for USB devices: If selected, LJControlPanel will include USB when searching for devices.

Search for Ethernet devices using UDP broadcast packet: Normally, Ethernet connected devices are found using a

broadcast of the DiscoveryUDP command documented in Section 5.2.3. On some networks, however, it might not be

desirable to broadcast these UDP packets. There are also situations where a network might have proper TCP

communication between the PC and LabJack, but the broadcast UDP packet does not work.

Search for Ethernet devices using specified IP addresses. When this option is selected, LJControlPanel will specifically

search over TCP using each address in the list. On some networks this might be preferred over the UDP broadcast search.

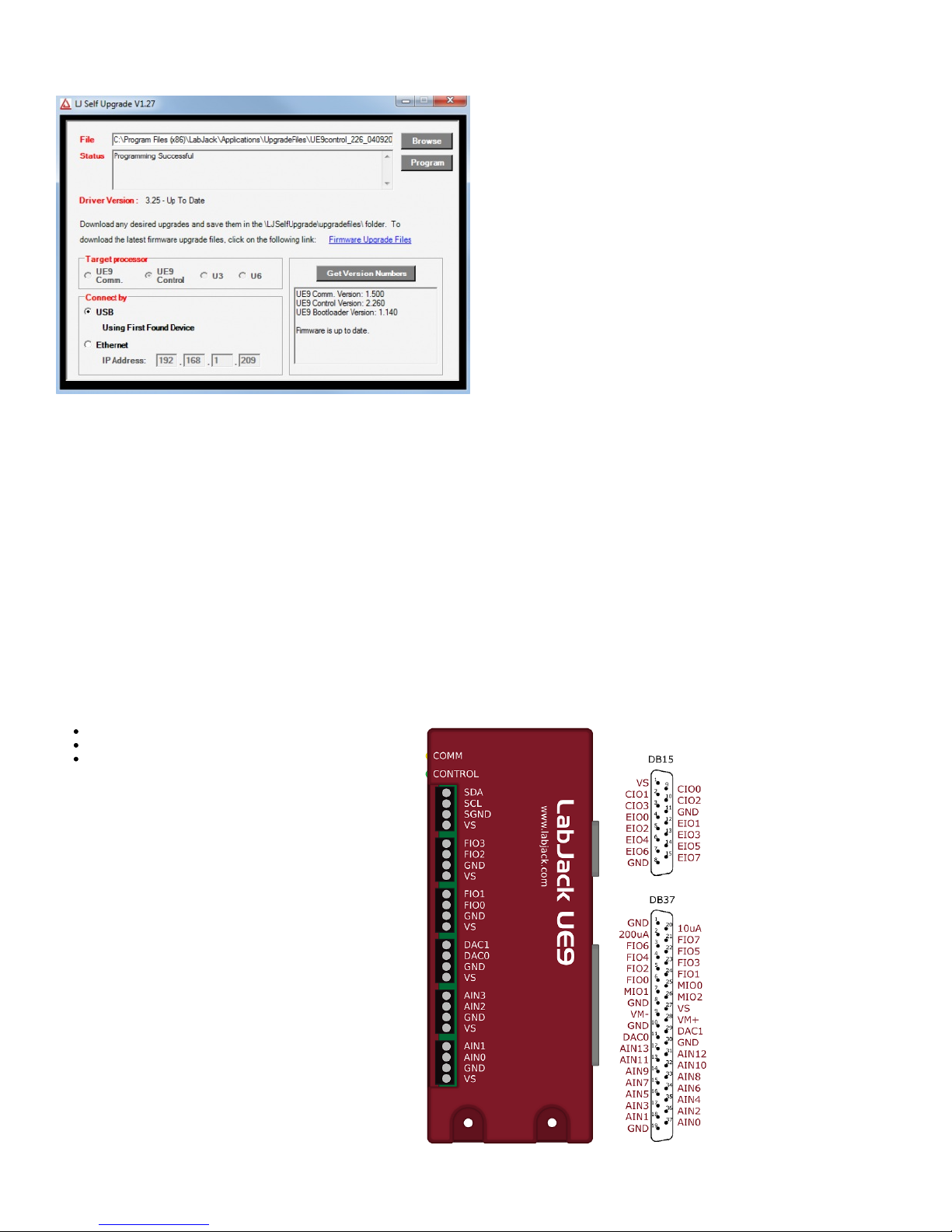

1.2 - Self-Upgrade Application (LJSelfUpgrade)

Both processors in the UE9 have field upgradeable flash memory. The self-upgrade application shown in Figure 1-4 programs the

latest firmware onto either processor.

First, put valid values in the “Connect by” box. If USB, select first found or specify a local ID. If Ethernet, specify the IP Address.

These values will be used for programming and everything else.

Click on “Get Version Numbers”, to find out the current firmware versions on the device. Then use the provided Internet link to go to

labjack.com and check for more recent firmware. Download firmware files to the …\LabJack\LJSelfUpgrade\upgradefiles\

directory.

Click the Browse button and select the upgrade file to program. Based on the file name, the application will determine whether the

4

Page 5

Comm or Control processor is to be programmed.

Click the Program button to begin the self-upgrade process.

Figure 1-4. Self-Upgrade Application

If problems are encountered during programming, try the following:

1. Unplug the UE9, wait 5 seconds then reconnect the UE9. Click OK then press program again.

2. If step 1 does not fix the problem unplug the UE9 and watch the C ontrol and Control LEDs while plugging the UE9 back in.

Follow the following steps based on the Comm and Control LEDs' activity.

1. If the Comm LED blinks several times and the Control LED is blinking rapidly (flash mode), connect a jumper

between FIO0 and SCL, then unplug the UE9, wait 5 seconds and plug the UE9 back in. Try programming again

(disconnect the jumper before programming).

2. If the Comm LED blinks several times and the Control LED has no activity, connect a jumper between FIO1 and

SCL, then unplug the UE9, wait 5 seconds and plug the UE9 back in. Try programming again (disconnect the jumper

before programming).

3. If the Comm LED has no activity, the UE9's Comm processor is not starting properly. Please restart your computer

and try programming again.

3. If there is no activity from the UE9's LEDs after following the above steps, please contact support.

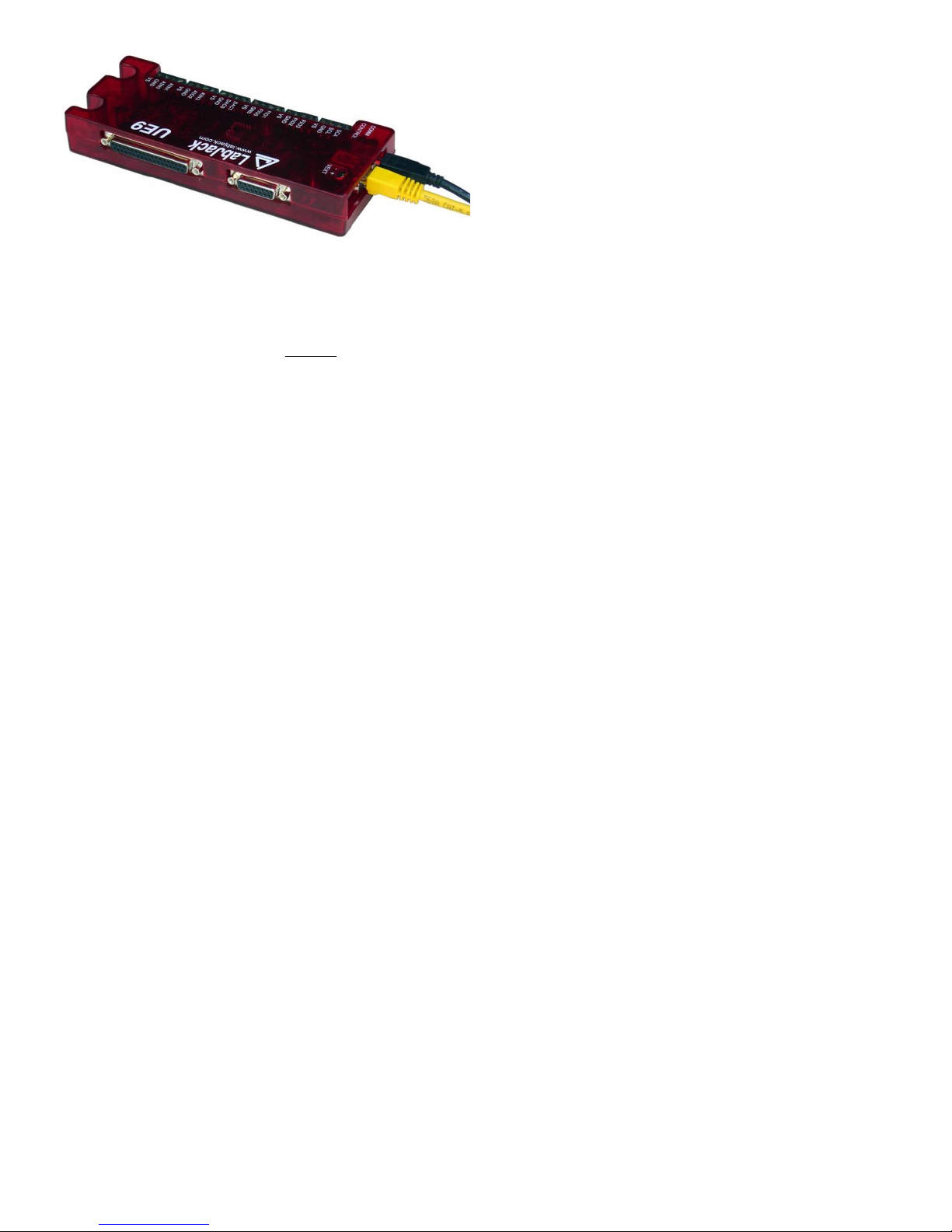

2 - Hardware Description

The UE9 has 3 different I/O areas:

Communication Edge,

Screw Terminal Edge,

DB Edge.

The communication edge has a USB type B connector (with

black cable connected in Figure 2-1), a 10Base-T Ethernet

connector (with yellow cable connected in Figure 2-1), and two

entry points for external power (screw-terminals or power jack).

The screw terminal edge has convenient connections for 4

analog inputs, both analog outputs, and 4 flexible digital I/O

(FIO). The screw terminals are arranged in blocks of 4, with each

block consisting of Vs, GND, and two I/O. Also on this edge are

two LEDs associated with the two processors in the UE9.

The DB Edge has 2 D-sub type connectors: a DB37 and DB15.

The DB37 has some digital I/O and all the analog I/O. The DB15

has 12 additional digital I/O.

5

Page 6

Figure 2-1. LabJack UE9

2.1 - USB

For information about USB installation, see Section 1.

The UE9 has a full-speed USB connection compatible with USB version 1.1 or 2.0. This connection can provide communication

and power (Vusb), but it is possible that some USB ports will not be able to provide enough power to run the UE9 at all speeds.

Certain low power USB ports can be limited to 100 milliamps, and some power modes of the UE9 use more than 100 milliamps.

A USB hub with a power supply (self-powered) will always provide 500 milliamps for each port.

USB ground is connected to the UE9 ground, and USB ground is generally the same as the ground of the PC chassis and AC

mains. In this case, the UE9 is not electrically isolated when the USB cable is connected.

The details of the UE9 USB interface are handled by the high level drivers (Windows LabJackUD DLL), so the following

information is really only needed when developing low-level drivers.

The LabJack vendor ID is 0×0CD5. The product ID for the U3 is 0×0009.

The USB interface consists of the normal bidirectional control endpoint 0 and two bidirectional bulk endpoints: Endpoint 1 and

Endpoint 2. Endpoint 1 consists of a 16 byte OUT endpoint (address = 0x01) and a 16 byte IN endpoint (address 0x81). Endpoint

2 consists of a 64 byte OUT endpoint (address = 0x02) and a 64 byte IN endpoint (address = 0x82).

Commands can be sent on either endpoint, and the response will be sent on the same endpoint, except that stream data is always

transferred on IN Endpoint 2, regardless of whether the stream start command was sent on OUT Endpoint 1 or 2.

Commands can be sent on both endpoints at the same time, but as with any connection on the UE9, do not send a second

command on an endpoint until after receiving the response to the first command.

Except for reading stream data, always write and read the actual number of bytes in the command and response. If the size is not

an even multiple of the endpoint size a short packet will be transferred. In general, small transfers will be faster on Endpoint 1 and

large transfers will be faster on Endpoint 2, but the time differences are small if any, and it is normal to do all communication

besides reading stream data on Endpoint 1. The main reason for the different endpoints is to simplify calling command/response

functions while a stream is in progress.

USB stream data is a special case where each 46-byte data packet is padded with 2 zeros on the end (not part of the protocol),

and then 4 of these 48-byte blocks are grouped together and sent in 3 transfers over the 64-byte endpoint. The host will generally

read stream data over USB in multiples of 192 bytes (64 samples). This means that at low scan rates there could be a long time

between reads and latency will be high, but this can be improved by oversampling.

The USB transceiver on the UE9 has a 128 byte hardware buffer on Endpoint 2. If the UE9 stream data buffer has one or more

StreamData packets available, they are moved to the USB buffer to await a read by the host. Once placed in this USB buffer, the

data cannot be removed (e.g. by a FlushBuffer command). To avoid confusion on future communication on Endpoint 2, this buffer

should always be emptied after streaming.

One way to empty this buffer is to continue reading data after StreamStop, until there is no more (the read times out). This should

not require a long timeout as the data is not being acquired, but simply waiting to be retrieved from the UE9 FIFO buffer.

Another option is to follow the StreamStop command with a FlushBuffer command. Then just try to read the last 128 bytes that

could still be in the USB buffer.

A third option is to do a StreamStop (and a FlushBuffer if desired), and then do not attempt to empty the USB buffer, but always

discard the first two StreamData packets after StreamStart.

2.2 - Ethernet

The UE9 has a 10Base-T Ethernet connection. This connection only provides communication, so power must be provided by an

external power supply or USB connection.

UE9 commands (Section 5) can all be sent using TCP, except for DiscoveryUDP. All commands, except stream related

commands, can also be sent using UDP.

The Ethernet connection on the UE9 has 1500 volts of galvanic isolation. As long as the USB cable is not connected, the overall

isolation level of the UE9 will be determined by the power supply. All power supplies shipped by LabJack Corporation with the

UE9 have at least 500 volts of isolation.

6

Page 7

See a note about power-over-Ethernet (POE) in Section 2.3.

The UE9 has a 10Base-T Ethernet connection. This connection only provides communication, so power must be provided by an

external power supply or USB connection. The UE9 ships with an Ethernet patch cable that would normally be used to connect to a

hub or switch. A direct connection from the UE9 to a computer might require a crossover cable (not included), but often the

network interface card (NIC) on modern computers is capable of automatically detecting the signal orientation and will work with

either cable type (patch or crossover).

The LEDs on a switch/hub/NIC can be used to determine if you have an electrically valid connection. An orange LED is often used

to indicate a good 10Base-T connection, but consult the manual for the switch/nub/NIC to be sure. In the case of a direct

connection between PC and UE9, if Windows says “A network cable is unplugged” or similar, it suggests that the UE9 is not

powered or the wrong type of cable is connected.

Complex networks might require the assistance of your network administrator to use the UE9, but the following information is often

sufficient for basic networks.

One basic requirement for TCP communication is that the UE9’s IP address must be part of the subnet and not already used.

Open a command prompt window and type “ipconfig” to see a listing of the IP address and subnet mask for a particular PC. If the

PC shows a subnet mask of 255.255.255.0, that means it can only talk to devices with the same first 3 bytes of the IP address.

The default IP address of the UE9 is 192.168.1.209, which will generally work on a network using the 192.168.1.* subnet (unless

another device is already using the .209 address). If the IP address of the UE9 needs to be changed, the easiest way is via USB

with the LJControlPanel application.

LJControlPanel and Ping (open a command prompt window and type “ping 192.168.1.209”) are useful utilities for testing basic

Ethernet communication. It is a good idea to attempt to Ping the desired IP address before connecting the UE9, to see if anything

is already using that address. A more extensive Ethernet troubleshooting utility called UE9ethertest is available. See the file

readme.txt in the UE9ethertest.zip archive for more information.

2.3 - Vext (Screw Terminals and Power Jack)

There are two connections for an external power supply (Vext): a two-pole screw terminal or a 2.1 mm center-positive power jack.

These connections are electrically the same, so generally only one is used at a time.

The nominal power supply voltage for the UE9 is 5 volts. Power can be provided from the USB connection (Vusb) or an external

power supply (Vext). The UE9 has an internal semiconductor switch that automatically selects between Vusb and Vext. Both power

sources can be connected at the same time, and either can be connected/disconnected at any time. As long as one supply

remains valid, the UE9 will operate normally. If both Vusb and Vext are connected and valid, the internal switch will select Vext.

The UE9 power supply requirement is nominally 5 volts at <200 mA (see Appendix A). This is generally provided by a wall-wart or

wall-transformer type of supply. A supply capable of 500 mA is recommended. The power jack connector is 2.1 × 5.5 mm, center

positive. A linear (regulated) or switching supply is acceptable. Switching supplies are generally noisier than linears, but the UE9

is not particularly sensitive to power supply noise, and most users will not notice any difference. One option is the CUI

EMSA050120K-P5P-SZ available from Digikey, for which you will also need a clip: EMS-AU (Australia), EMS-CC (China), EMSEU (Europe), EMS-UK (United Kingdom), or EMS-US (United States).

Another interesting option is a power-over-Ethernet (POE) adapter. The UE9 does not support POE itself, but there are POE

adapters that split out the data and power in such a manner that is acceptable for the UE9. These adapters consist of an injector

and splitter, and a single Ethernet cable carries data and power between the two. LabJack Corporation has done testing with the

WAPPOE unit from Linksys, which is an off-the-shelf POE adapter with the proper connections for a UE9.

2.4 - Comm and Control LEDs

There is a yellow LED associated with the Comm (communication) processor, and a green LED associated with the Control

processor.

The Comm LED flashes on reset and USB enumeration, and then only turns on when there is communication (USB/Ethernet)

traffic. This LED then turns off if there is no communication for about 200 ms.

The Control LED normally blinks continuously at about 2.5 Hz. In flash programming mode it blinks at about 8 Hz. If the LED is

blinking at about 0.5 Hz, that signifies the deprecated (no longer supported) low power mode. Those blink rates apply when the

UE9 is idle, as this LED also flashes on Control processor activity.

Normal Power-Up LED Behavior: When the USB cable is connected to the UE9 (no other connections at all and no software

running), both LEDs will start blinking. The Comm LED will blink a few times and then turn off. The Control LED will continue to

blink continuously.

2.5 - GND and SGND

The GND connections available at the screw-terminals and DB connectors provide a common ground for all LabJack functions. All

GND terminals are the same and connect to the same ground plane. This ground is the same as the ground line on the USB

connection, which is often the same as ground on the PC chassis and therefore AC mains ground. This ground is also the same

as the ground on either Vext connections (wall-wart power jack or minus screw terminals), but if an isolated supply is used, such as

the one included with the UE9, there is no common connection to AC mains ground.

SGND is located near the upper-left of the device. This terminal has a self-resetting thermal fuse in series with GND. This is often

a good terminal to use when connecting the ground from another separately powered system that could unknowingly already share

a common ground with the UE9.

The UE9 has separate ground planes on the PCB for analog and digital, but the planes are shorted together so the user only has

7

Page 8

to consider one common ground (GND).

See the AIN, DAC, and Digital I/O Sections for more information about grounding.

2.6 - Vs

The Vs terminals are designed as outputs for the internal supply voltage (nominally 5 volts). This will be the voltage provided from

the USB connection (Vusb) or an external power supply (Vext) as described in Section 2.3. The Vs connections are outputs, not

inputs. Do not connect a power source to Vs. All Vs terminals are the same.

2.7 - AIN

The LabJack UE9 has 14 user accessible analog inputs built-in. All the analog inputs are available on the DB37 connector, and

the first 4 are also available on the built-in screw terminals.

The analog inputs have variable resolution, where the time required per sample increases with increasing resolution. The value

passed for resolution is from 0-17, where 0-12 all correspond to 12-bit resolution, and 17 still results in 16-bit resolution but with

minimum noise. The UE9-Pro has an additional resolution setting of 18 that causes acquisitions to use the alternate highresolution converter (24-bit sigma-delta). Resolution is configured on a device basis, not for each channel.

The analog inputs are connected to a high impedance input buffer. The inputs are not pulled to 0.0 volts, as that would reduce the

input impedance, so readings obtained from floating channels will generally not be 0.0 volts. The readings from floating channels

depend on adjacent channels and sample rate. See Section 2.7.3.8.

When scanning multiple channels, the nominal channel-to-channel delay is specified in Appendix A, and includes enough settling

time to meet the specified performance. Some signal sources could benefit from increased settling, so a settling time parameter

is available that adds extra delay between configuring the multiplexers and acquiring a sample. The passed settling time value is

multiplied by 5 microseconds to get the approximate extra delay. This extra delay will impact the maximum possible data rates.

2.7.1 - Channel Numbers

The LabJack UE9 has 16 total built-in analog inputs. Two of these are connected internally (AIN14/AIN15), leaving 14 user

accessible analog inputs (AIN0-AIN13). The first 4 analog inputs, AIN0-AIN3, appear both on the screw terminals and on the DB37

connector. These connections are electrically the same, and the user must exercise caution only to use one connection or the

other, and not create a short circuit.

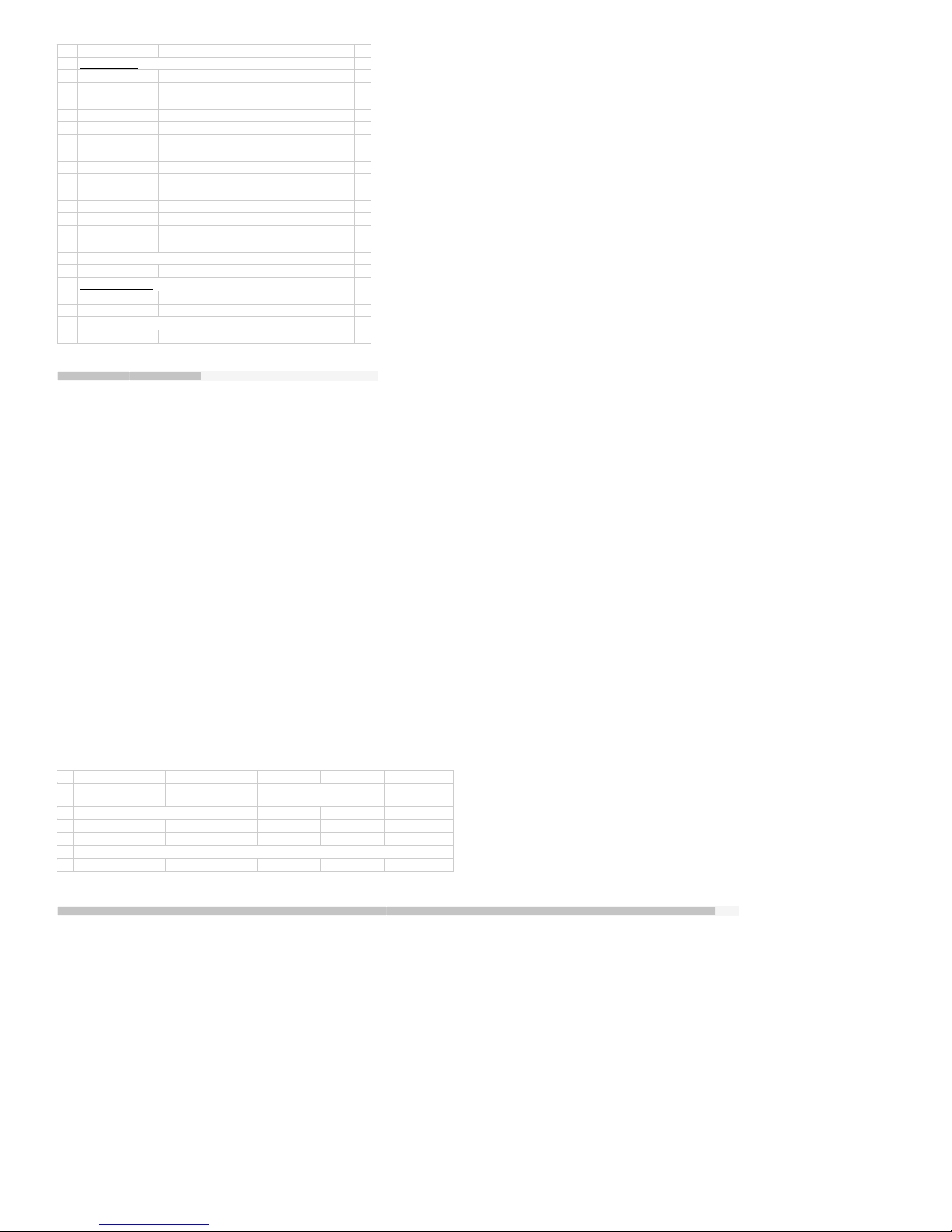

Following is a table showing the channel number to pass to acquire different readings from the internal channels (AIN14/15).

Channel#

14

Vref (~2.43 V)

128

Vref (~2.43 V)

132

Vsupply

133

Temp S ensor

15

GND

136

GND

140

Vsupply

141

Temp S ensor

Table 2.7.1-1. Inte rnal Channe ls

GND and Vref connect 0.0 volts and about 2.43 volts to the internal channels. These signals come through the same input path as

channels 0-13, and thus can be used to test various things.

Vsupply connects the 5 volt supply voltage (Vs) directly to the analog to digital converter through a voltage divider that attenuates it

by 40%. The attenuation of this voltage divider is not measured during the UE9 factory calibration, but the accuracy should typically

be within 0.2%. Note that a reading from this channel returns Vs during the execution of the command, and Vs might dip slightly

while increasing a command due to the increased current draw of the UE9, thus this reading might be slightly lower than a

comparative reading from an external DMM which averages over a longer time.

The channels with the same names are identical. For instance, channel 133 or 141 both read the same internal temperature

sensor. See Section 2.7.4 for information about the internal temperature sensor.

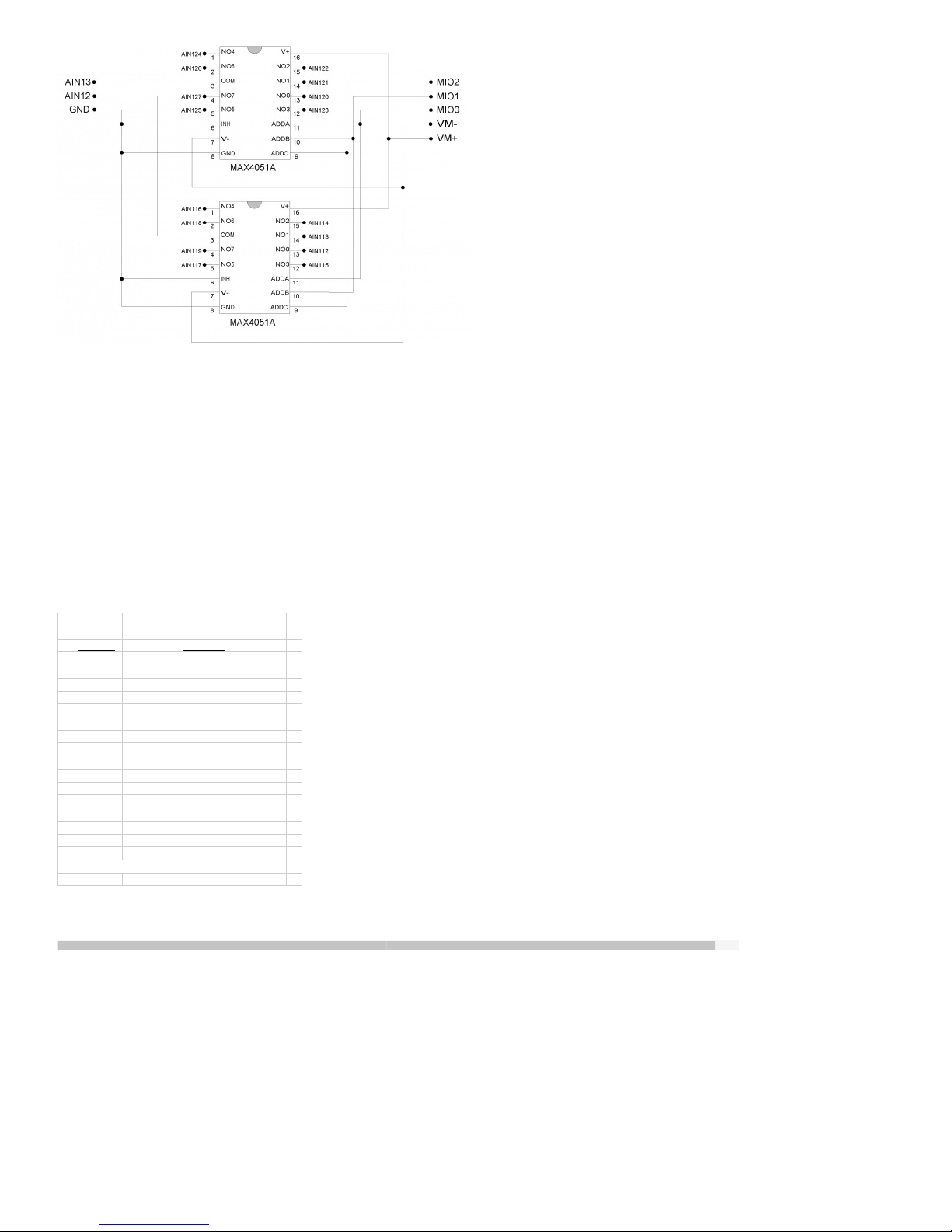

The Mux80 accessory uses multiplexer ICs to easily expand the total number of analog inputs available from 14 to 84, or you can

connect multiplexer chips yourself.

The DB37 connector has 3 MIO lines designed to address expansion multiplexer ICs (integrated circuits), allowing for up to 112

total external analog inputs. The MAX4051A (maxim-ic.com) is a recommended multiplexer, and a convenient ±5.8 volt power

supply is available so the multiplexers can pass bipolar signals (see Vm+/Vm- discussion in Section 2.12). Note that the EB37

experiment board accessory is a convenient way to connect up to 7 MAX4051A multiplexer chips, but the UE9s ±5.8 volt supply

should still be used to power the chips as the ±10 volt supply on the EB37 is beyond the rating of the MAX4051A. Figure 2-2

shows the typical connections for a pair of multiplexers.

8

Page 9

Figure 2-2. Typical External Multiplexer Connections

To make use of external multiplexers, the user must be comfortable reading a simple schematic (such as Figure 2-2) and making

basic connections on a solderless breadboard (such as the EB37 Experiment Board). Initially, it is recommended to test the basic

operation of the multiplexers without the MIO lines connected. Simply connect different voltages to NO0 and NO1, connect

ADDA/ADDB/ADDC to GND, and the NO0 voltage should appear on COM. Then connect ADDA to VS and the NO1 voltage

should appear on COM.

If any of the AIN channel numbers passed to a UE9 function are in the range 16-127 (extended channels), the MIO lines will

automatically be set to output and the correct state while sampling that channel. For instance, a channel number of 28 will cause

the MIO to be set to b100 and the ADC will sample AIN1. Channel number besides 16-127 will have no affect on the MIO. The

extended channel number mapping is shown in Table 2-2.

In command/response mode, after sampling an extended channel the MIO lines remain in that same condition until commanded

differently by another extended channel or another function. When streaming with any extended channels, the MIO lines are all set

to output-low for any non extended analog channels. For special channels (digital/timers/counters), the MIO are driven to

unspecified states. Note that the StopStream can occur during any sample within a scan, so the MIO lines will wind up configured

for any of the extended channels in the scan. If a stream does not have any extended channels, the MIO lines are not affected.

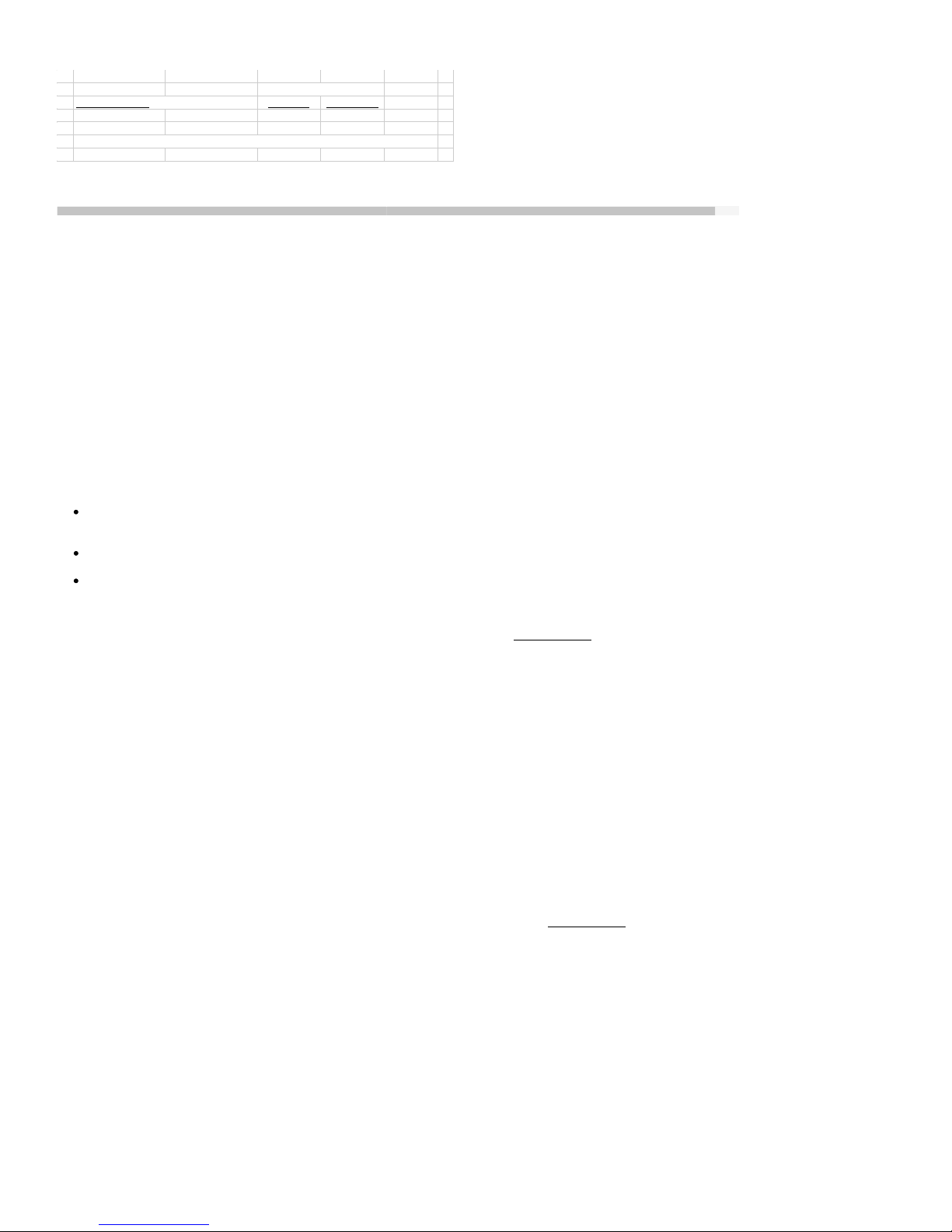

UE9

MIO Multiplexed

Channel

Channels

0

16-23124-31232-39340-47448-55556-63664-71772-79880-87988-951096-103

11

104-111

12

112-119

13

120-127

14

128-135

15

136-143

Table 2.7.2-1. Expa nded Channe l Ma pping

2.7.2 - Converting Binary Readings to Voltages

This information is only needed when using low-level functions and other ways of getting binary readings. Readings in volts already

have the calibration constants applied. The UD driver, for example, normally returns voltage readings unless binary readings are

specifically requested.

Following are the nominal input voltage ranges for the analog inputs.

9

Page 10

Gain

Max V

Min V

Unipolar15.07

-0.01

Unipolar22.53

-0.01

Unipolar41.26

-0.01

Unipolar80.62

-0.01

Bipolar15.07

-5.18

Table 2.7.2-1. Nominal Analog Input Voltage Ranges

The high-resolution converter on the UE9-Pro only supports the 0-5 and +/-5 volt ranges.

The readings returned by the analog inputs are raw binary values (low level functions). An approximate voltage conversion can be

performed as:

Volts(uncalibrated) = (Bits/65536)*Span

Where span is the maximum voltage minus the minimum voltage from the table above. For a proper voltage conversion, though,

use the calibration values (Slope and Offset) stored in the internal flash on the Control processor.

Volts = (Slope * Bits) + Offset

In both cases, “Bits” is always aligned to 16-bits, so if the raw binary value is 24-bit data it must be divided by 256 before

converting to voltage. Binary readings are always unsigned integers.

Since the UE9 uses multiplexers, all channels (except 129-135 and 137-143) have the same calibration for a given input range.

See Section 5.6 for details about the location of the UE9 calibration constants

2.7.3 - Typical Analog Input Connections

A common question is “can this sensor/signal be measured with the UE9”. Unless the signal has a voltage (referred to UE9

ground) beyond the limits in Appendix A, it can be connected without damaging the UE9, but more thought is required to

determine what is necessary to make useful measurements with the UE9 or any measurement device.

Voltage (versus ground): The analog inputs on the UE9 measure a voltage with respect to UE9 ground. When measuring

parameters other than voltage, or voltages too big or too small for the UE9, some sort of sensor or transducer is required to

produce the proper voltage signal. Examples are a temperature sensor, amplifier, resistive voltage divider, or perhaps a

combination of such things.

Impedance: When connecting the UE9, or any measuring device, to a signal source, it must be considered what impact the

measuring device will have on the signal. The main consideration is whether the currents going into or out of the UE9 analog input

will cause noticeable voltage errors due to the impedance of the source. See Appendix A for the recommended maximum source

impedance.

Resolution (and Accuracy): Based on the selected input range and resolution of the UE9, the resolution can be determined in

terms of voltage or engineering units. For example, assume some temperature sensor provides a 0-10 mV signal, corresponding

to 0-100 degrees C. Samples are then acquired with the UE9 using the 0-5 volt input range and 16-bit resolution, resulting in a

voltage resolution of about 5/65536 = 76 µV. That means there will be about 131 discrete steps across the 10 mV span of the

signal, and the overall resolution is 0.76 degrees C. If this experiment required a resolution of 0.1 degrees C, this configuration

would not be sufficient. Accuracy will also need to be considered. Appendix A places some boundaries on expected accuracy, but

an in-system calibration can generally be done to provide absolute accuracy down to the INL limits of the UE9.

Speed: How fast does the signal need to be sampled? For instance, if the signal is a waveform, what information is needed: peak,

average, RMS, shape, frequency, … ? Answers to these questions will help decide how many points are needed per waveform

cycle, and thus what sampling rate is required. In the case of multiple channels, the scan rate is also considered. See Sections 3.1

and 3.2.

2.7.3.1 - Signal from the LabJack

Each analog input on the UE9 measures the difference in voltage between that input and ground (GND). Since all I/O on the UE9

share a common ground, the voltage on a digital output or analog output can be measured by simply connecting a single wire from

that terminal to an AINx terminal.

2.7.3.2 - Unpowered Isolated Signal

An example of an unpowered isolated signal would be a thermocouple or photocell where the sensor leads are not shorted to any

external voltages. Such a sensor typically has two leads. The positive lead connects to an AINx terminal and the negative lead

connects to a GND terminal.

An exception might be a thermocouple housed in a metal probe where the negative lead of the thermocouple is shorted to the

metal probe housing. If this probe is put in contact with something (engine block, pipe, …) that is connected to ground or some

other external voltage, care needs to be taken to insure valid measurements and prevent damage.

2.7.3.3 - Signal Powered by the LabJack

A typical example of this type of signal is a 3-wire temperature sensor. The sensor has a power and ground wire that connect to Vs

and GND on the LabJack, and then has a signal wire that simply connects to an AINx terminal.

10

Page 11

Another variation is a 4-wire sensor where there are two signal wires (positive and negative) rather than one. If the negative signal

is the same as power ground, or can be shorted ground, then the positive signal can be connected to AINx and a measurement

can be made. A typical example where this does not work is a bridge type sensor, such as pressure sensor, providing the raw

bridge output (and no amplifier). In this case the signal voltage is the difference between the positive and negative signal, and the

negative signal cannot be shorted to ground. An instrumentation amplifier is required to convert the differential signal to signalended, and probably also to amplify the signal.

2.7.3.4 - Signal Powered Externally

An example is a box with a wire coming out that is defined as a 0-5 volt analog signal and a second wire labeled as ground. The

signal is known to have 0-5 volts compared to the ground wire, but the complication is what is the voltage of the box ground

compared to the LabJack ground.

If the box is known to be electrically isolated from the LabJack, the box ground can simply be connected to LabJack GND. An

example would be if the box was plastic, powered by an internal battery, and does not have any wires besides the signal and

ground which are connected to AINx and GND on the LabJack. Such a case is obviously isolated and easy to keep isolated. In

practical applications, though, signals thought to be isolated are often not at all, or perhaps are isolated at some time but the

isolation is easily lost at another time.

If the box ground is known to be the same as the LabJack GND, then perhaps only the one signal wire needs to be connected to

the LabJack, but it generally does not hurt to go ahead and connect the ground wire to LabJack GND with a 100 Ω resistor. You

definitely do not want to connect the grounds without a resistor.

If little is known about the box ground, a DMM can be used to measure the voltage of box ground compared to LabJack GND. As

long as an extreme voltage is not measured, it is generally OK to connect the box ground to LabJack GND, but it is a good idea to

put in a 100 Ω series resistor to prevent large currents from flowing on the ground. Use a small wattage resistor (typically 1/8 or 1/4

watt) so that it blows if too much current does flow. The only current that should flow on the ground is the return of the analog input

bias current, which is on the order of nanoamps for the UE9.

The SGND terminal can be used instead of GND for externally powered signals. A series resistor is not needed as SGND is fused

to prevent overcurrent, but a resistor will eliminate confusion that can be caused if the fuse is tripping and resetting.

In general, if there is uncertainty, a good approach is to use a DMM to measure the voltage on each signal/ground wire without any

connections to the UE9. If no large voltages are noted, connect the ground to UE9 SGND with a 100 Ω series resistor. Then again

use the DMM to measure the voltage of each signal wire before connecting to the UE9.

Another good general rule is to use the minimum number of ground connections. For instance, if connecting 8 sensors powered by

the same external supply, or otherwise referred to the same external ground, only a single ground connection is needed to the

UE9. Perhaps the ground leads from the 8 sensors would be twisted together, and then a single wire would be connected to a 100

Ω resistor which is connected to UE9 ground.

2.7.3.5 - Amplifying Small Signal Voltages

The best results are generally obtained when a signal voltage spans the full analog input range of the LabJack. If the signal is too

small it can be amplified before connecting to the LabJack. One good way to handle low-level signals such as thermocouples is

the LJTick-InAmp, which is a 2-channel instrumentation amplifier module that plugs into the UE9 screw-terminals.

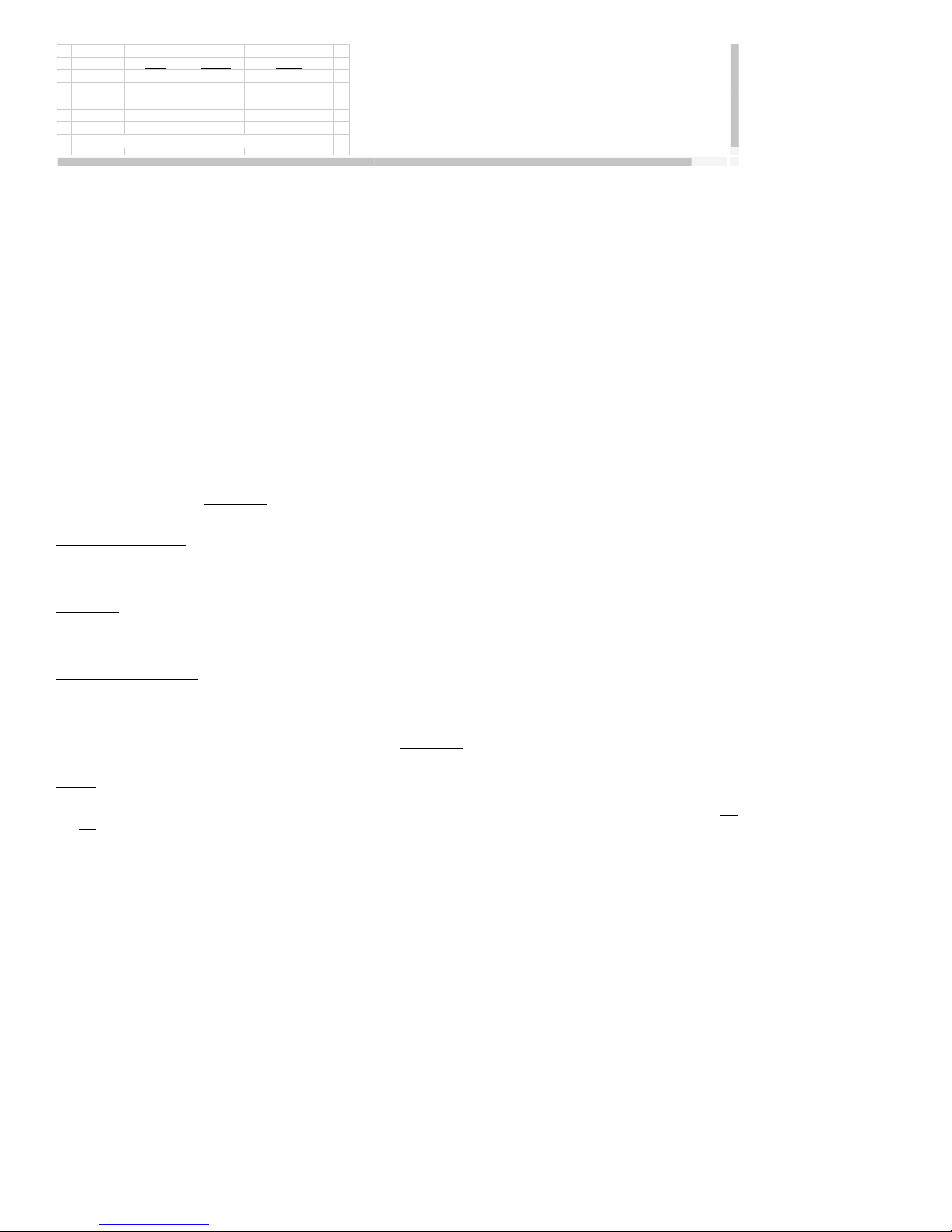

For a do-it-yourself solution, the following figure shows an operational amplifier (op-amp) configured as non-inverting:

Figure 2-3. Non-Inverting Op-Amp Configuration

The gain of this configuration is:

Vout = Vin * (1 + (R2/R1))

100 kΩ is a typical value for R2. Note that if R2=0 (short-circuit) and R1=inf (not installed), a simple buffer with a gain equal to 1 is

the result.

11

Page 12

There are numerous criteria used to choose an op-amp from the thousands that are available. One of the main criteria is that the

op-amp can handle the input and output signal range. Often, a single-supply rail-to-rail input and output (RIRO) is used as it can be

powered from Vs and GND and pass signals within the range 0-Vs. The OPA344 from Texas Instruments (ti.com) is good for many

5 volt applications. The max supply rating for the OPA344 is 5.5 volts, so for applications using Vm+/Vm- (~12 volts) or using the

±10 volt supply on the EB37, the LT1490A from Linear Technologies (linear.com) might be a good option.

The op-amp is used to amplify (and buffer) a signal that is referred to the same ground as the LabJack (single-ended). If instead

the signal is differential (i.e. there is a positive and negative signal both of which are different than ground), an instrumentation

amplifier (in-amp) should be used. An in-amp converts a differential signal to single-ended, and generally has a simple method to

set gain.

The EB37 experiment board is handy for building these circuits.

2.7.3.6 - Signal Voltages Beyond ±5 Volts (and Resistance

Measurement)

The nominal maximum analog input voltage range for the UE9 is ±5 volts. The easiest way to handle larger voltages is often by

using the LJTick-Divider, which is a two channel buffered divider module that plugs into the UE9 screw-terminals.

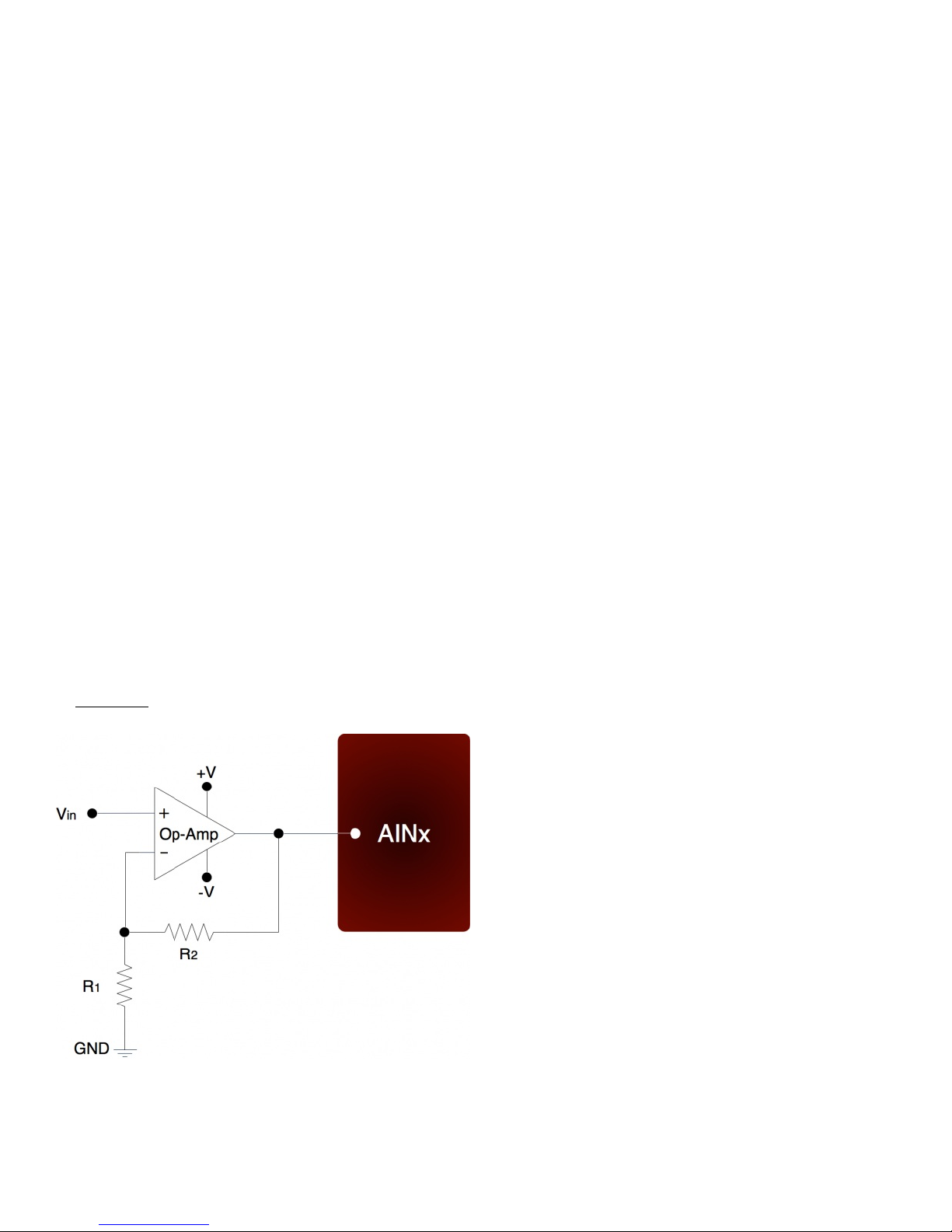

The basic way to handle higher voltages is with a resistive voltage divider. The following figure shows the resistive voltage divider

assuming that the source voltage (Vin) is referred to the same ground as the UE9 (GND).

Figure 2-4. Voltage Divider Circuit

The attenuation of this circuit is determined by the equation:

Vout = Vin * ( R2 / (R1+R2))

This divider is easily implemented by putting a resistor (R1) in series with the signal wire, and placing a second resistor (R2) from

the AIN terminal to a GND terminal. To maintain specified analog input performance, R1 should not exceed 10 kΩ, so R1 can

generally be fixed at 10 kΩ and R2 can be adjusted for the desired attenuation. For instance, R1 = R2 = 10 kΩ provides a divide

by 2, so a ±10 volt input will be scaled to ±5 volts and a 0-10 volt input will be scaled to 0-5 volts.

The divide by 2 configuration where R1 = R2 = 10 kΩ, presents a 20 kΩ load to the source, meaning that a ±10 volt signal will have

to be able to source/sink up to ±500 µA. Some signal sources might require a load with higher resistance, in which case a buffer

should be used. The following figure shows a resistive voltage divider followed by an op-amp configured as non-inverting unitygain (i.e. a buffer).

Figure 2-5. Buffered Voltage Divider Circuit

The op-amp is chosen to have low input bias currents so that large resistors can be used in the voltage divider. The LT1490A from

Linear Technologies (linear.com) is a good choice for dual-supply applications. The LT1490A only draws 40 µA of supply current,

thus many of these amps can be powered from the Vm+/Vm- supply on the UE9, and can pass signals in the ±5 volt range. Since

the input bias current is only -1 nA, large divider resistors such as R1 = R2 = 470 kΩ will only cause an offset of about -470 µV, and

yet present a load to the source of about 1 megaohm.

For 0-5 volt applications, where the amp will be powered from Vs and GND, the LT1490A is not the best choice. When the

amplifier input voltage is within 800 mV of the positive supply, the bias current jumps from -1 nA to +25 nA, which with R1 = 470 kΩ

will cause the offset to change from -470 µV to +12 mV. A better choice in this case would be the OPA344 from Texas Instruments

(ti.com). The OPA344 has a very small bias current that changes little across the entire voltage range. Note that when powering the

amp from Vs and GND, the input and output to the op-amp is limited to that range, so if Vs is 4.8 volts your signal range will be 0-

4.8 volts. If this is a concern, use the external wall-wart to supply power to the UE9 as it typically keeps Vs around 5.2 volts.

The EB37 experiment board is handy for building these circuits.

12

Page 13

The information above also applies to resistance measurement. A common way to measure resistance is to build a voltage

divider as shown in Figure 2-4, where one of the resistors is known and the other is the unknown. If Vin is known and Vout is

measured, the voltage divider equation can be rearranged to solve for the unknown resistance.

2.7.3.7 - Measuring Current (Including 4-20 mA) with a

Resistive Shunt

The best way to handle 4-20 mA signals is with the LJTick-CurrentShunt, which is a two channel active current to voltage converter

module that plugs into the UE9 screw-terminals.

The following figure shows a typical method to measure the current through a load, or to measure the 4-20 mA signal produced by

a 2-wire (loop-powered) current loop sensor. The current shunt shown in the figure is simply a resistor.

Figure 2-6. Current Measurement With Arbitrary Load or 2-Wire 4-20 mA Sensor

When measuring a 4-20 mA signal, a typical value for the shunt would be 240 Ω. This results in a 0.96 to 4.80 volt signal

corresponding to 4-20 mA. The external supply must provide enough voltage for the sensor and the shunt, so if the sensor requires

5 volts the supply must provide at least 9.8 volts.

For applications besides 4-20 mA, the shunt is chosen based on the maximum current and how much voltage drop can be

tolerated across the shunt. For instance, if the maximum current is 1.0 amp, and 2.5 volts of drop is the most that can be tolerated

without affecting the load, a 2.4 Ω resistor could be used. That equates to 2.4 watts, though, which would require a special high

wattage resistor. A better solution would be to use a 0.1 Ω shunt, and then use an amplifier to increase the small voltage produced

by that shunt. If the maximum current to measure is too high (e.g. 100 amps), it will be difficult to find a small enough resistor and a

hall-effect sensor should be considered instead of a shunt.

The following figure shows typical connections for a 3-wire 4-20 mA sensor. A typical value for the shunt would be 240 Ω which

results in 0.96 to 4.80 volts.

Figure 2-7. Current Measurement With 3-Wire 4-20 mA (Sourcing) Sensor

The sensor shown in Figure 2-7 is a sourcing type, where the signal sources the 4-20 mA current which is then sent through the

shunt resistor and sunk into ground. Another type of 3-wire sensor is the sinking type, where the 4-20 mA current is sourced from

the positive supply, sent through the shunt resistor, and then sunk into the signal wire. If sensor ground is connected to UE9 ground,

the sinking type of sensor presents a couple of problems, as the voltage across the shunt resistor is differential (neither side is at

ground) and at least one side of the resistor has a high common mode voltage (equal to the positive sensor supply). If the sensor

and/or UE9 are isolated, a possible solution is to connect the sensor signal or positive sensor supply to UE9 ground (instead of

sensor ground). This requires a good understanding of grounding and isolation in the system. The LJTick-CurrentShunt is often a

simple solution.

Both Figure 2-6 and 2-7 show a 0-100 Ω resistor in series with SGND, which is discussed in general in Section 2.7.3.4. In this

case, if SGND is used (rather than GND), a direct connection (0 Ω) should be good.

The best way to handle 4-20 mA signals is with the LJTick-CurrentShunt, which is a two channel active current to voltage converter

module that plugs into the UE9 screw-terminals.

2.7.3.8 - Floating/Unconnected Inputs

The reading from a floating (no external connection) analog input channel can be tough to predict and is likely to vary with sample

timing and adjacent sampled channels. Keep in mind that a floating channel is not at 0 volts, but rather is at an undefined voltage.

In order to see 0 volts, a 0 volt signal (such as GND) should be connected to the input.

Some data acquisition devices use a resistor, from the input to ground, to bias an unconnected input to read 0. This is often just

for “cosmetic” reasons so that the input reads close to 0 with floating inputs, and a reason not to do that is that this resistor can

degrade the input impedance of the analog input.

13

Page 14

In a situation where it is desired that a floating channel read a particular voltage, say to detect a broken wire, a resistor can be

placed from the AINx screw terminal to the desired voltage (GND, VS, DACx, …). A 10 kΩ resistor will pull the analog input

readings to within 1 binary count of any desired voltage, but obviously degrades the input impedance to 10 kΩ. For the specific

case of pulling a floating channel to 0 volts, a 100 kΩ resistor to GND can typically be used to provide analog input readings within

100 mV of ground.

2.7.4 - Internal Temperature Sensor

The UE9 has an internal temperature sensor. Although this sensor measures the temperature inside the UE9, it has been

calibrated to read ambient temperature. For accurate measurements the temperature of the entire UE9 must stabilize relative to

the ambient temperature, which can take on the order of 1 hour. Best results will be obtained in still air in an environment with

slowly changing ambient temperatures.

The internal temperature sensor is also affected by the operating speed of the UE9. With Control firmware V1.08 or higher, the

UE9 is in high power mode by default, which is assumed by the LabJack UD driver.

With the UD driver, the internal temperature sensor is read by acquiring analog input channel 133 or 141, and returns degrees K.

2.8 - DAC

There are two DACs (digital-to-analog converters or analog outputs) on the UE9. Each DAC can be set to a voltage between

about 0.02 and 4.86 volts with 12-bits of resolution.

Although the DAC values are based on an absolute reference voltage, and not the supply voltage, the DAC output buffers are

powered internally by Vs and thus the maximum output is limited to slightly less than Vs. Another implication of this is that high

frequency power supply noise might couple to the analog outputs.

The analog output commands are sent as raw binary values (low level functions). For a desired output voltage, the binary value can

be approximated as:

Bits(uncalibrated) = (Volts/4.86)*4096

For a proper calculation, though, use the calibration values (Slope and Offset) stored in the internal flash on the Control processor

(Table 2-4):

Bits = (Slope * Volts) + Offset

The DACs appear both on the screw terminals and on the DB37 connector. These connections are electrically the same, and the

user must exercise caution only to use one connection or the other, and not create a short circuit.

The DACS on the UE9 can be disabled. Prior to control firmware 1.98 when disabled they are placed in a high-impedance state,

firmware 1.98 and later always leaves the DACs enabled. Both DACs are enabled or disabled at the same time, so if a command

causes one DAC to be enabled the other is also enabled.

The power-up condition of the DACs can be configured by the user. From the factory, the DACS default to enabled at minimum

voltage (~0 volts). Note that even if the power-up default for a line is changed to a different voltage or disabled, there is a delay of

about 100 ms at power-up where the D ACs are in the factory default condition.

The analog outputs can withstand a continuous short-circuit to ground, even when set at maximum output.

Voltage should never be applied to the analog outputs, as they are voltage sources themselves. In the event that a voltage is

accidentally applied to either analog output, they do have protection against transient events such as ESD (electrostatic

discharge) and continuous overvoltage (or undervoltage) of a few volts.

There is an accessory available from LabJack called the LJTick-DAC that provides a pair of 14-bit analog outputs with a range of

±10 volts. The LJTick-DAC plugs into any digital I/O block, and thus up to 10 of these can be used per UE9 to add 20 analog

outputs.

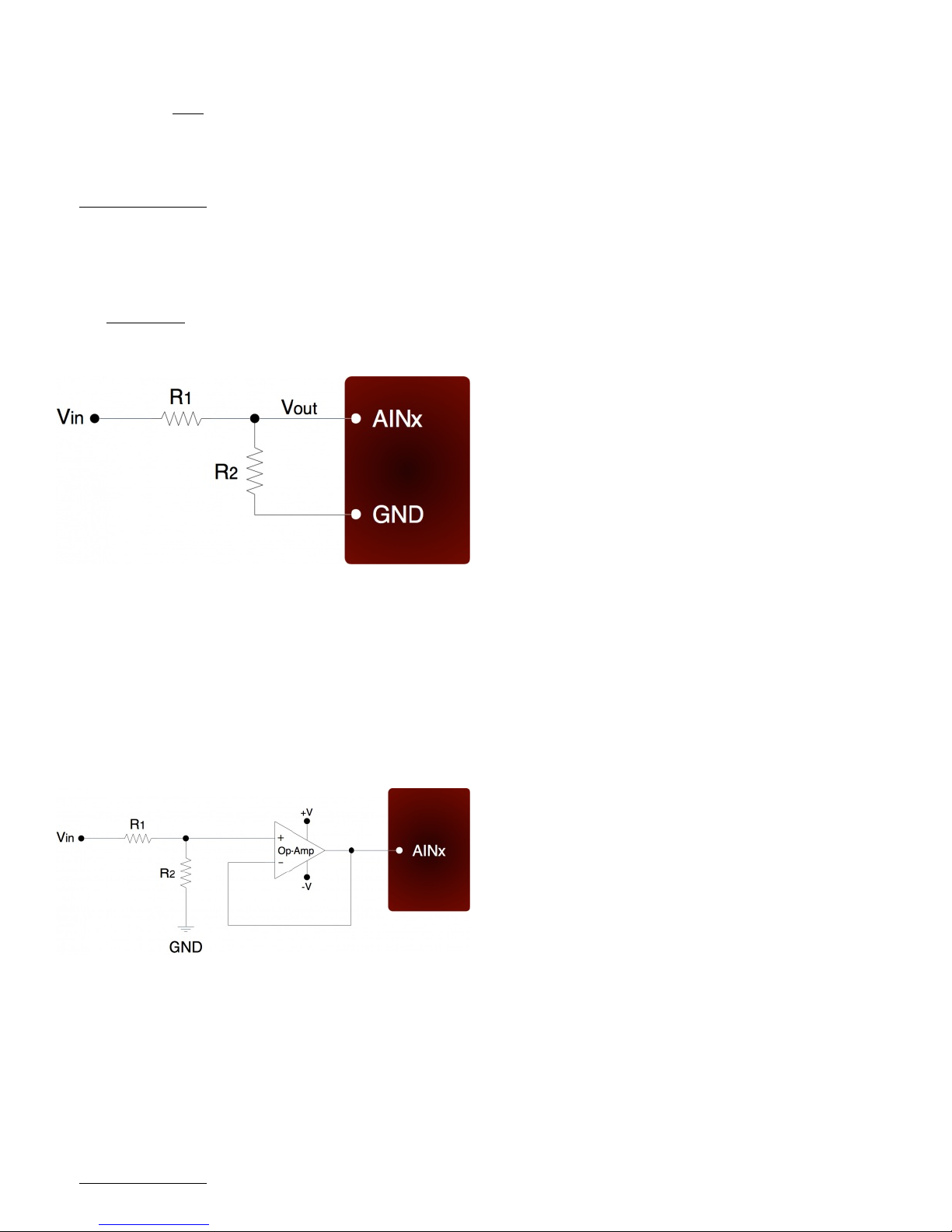

2.8.1 - Typical Analog Output Connections

2.8.1 - Typical Analog Output Connections

The DACs on the UE9 can output quite a bit of current, but have 50 Ω of source impedance that will cause voltage drop. To avoid

this voltage drop, an op-amp can be used to buffer the output, such as the non-inverting configuration shown in Figure 2-3. A

simple RC filter can be added between the DAC output and the amp input for further noise reduction. Note that the ability of the

amp to source/sink current near the power rails must still be considered. A possible op-amp choice would be the TLV246x family

(ti.com).

2.8.1.2 - Different Output Ranges

There is an accessory available from LabJack called the LJTick-DAC that provides a pair of 14-bit analog outputs with a range of

±10 volts. The LJTick-DAC plugs into any digital I/O block, and thus up to 10 of these can be used per UE9 to add 20 analog

outputs.

The typical output range of the DACs is about 0.02 to 4.86 volts. For other unipolar ranges, an op-amp in the non-inverting

configuration (Figure 2-3) can be used to provide the desired gain. For example, to increase the maximum output from 4.86 volts

to 10.0 volts, a gain of 2.06 is required. If R2 (in Figure 2-3) is chosen as 100 kΩ, then an R1 of 93.1 kΩ is the closest 1% resistor

14

Page 15

that provides a gain greater than 2.06. The +V supply for the op-amp would have to be greater than 10 volts.

For bipolar output ranges, such as ±10 volts, a similar op-amp circuit can be used to provide gain and offset, but of course the opamp must be powered with supplies greater than the desired output range (depending on the ability of the op-amp to drive it’s

outputs close to the power rails). For example, the EB37 experiment board provides power supplies that are typically ±9.5 volts. If

these supplies are used to power the LT1490A op-amp (linear.com), which has rail-to-rail capabilities, the outputs could be driven

very close to ±9.5 volts. If ±12 or ±15 volt supplies are available, then the op-amp might not need rail-to-rail capabilities to achieve

the desired output range.

A reference voltage is also required to provide the offset. In the following circuit, DAC1 is used to provide a reference voltage. The

actual value of DAC1 can be adjusted such that the circuit output is 0 volts at the DAC0 mid-scale voltage, and the value of R1 can

be adjusted to get the desired gain. A fixed reference (such as 2.5 volts) could also be used instead of DAC1.

Figure 2-8. ±10 Volt DAC Output Circuit

A two-point calibration should be done to determine the exact input/output relationship of this circuit. Refer to application note

SLOA097 from ti.com for further information about gain and offset design with op-amps.

2.9 - Digital I/O

The LabJack UE9 has 23 digital I/O. The LabJackUD driver uses the following bit numbers to specify all the digital lines:

0-7 FIO0-FIO7

8-15 EIO0-EIO7

16-19 CIO0-CIO3

20-22 MIO0-MIO2

The UE9 has 8 FIO (flexible digital I/O). The first 4 lines, FIO0-FIO3, appear both on the screw terminals and on the DB37

connector. These connections are electrically the same, and the user must exercise caution only to use one connection or the

other, and not create a short circuit. The upper 4 lines appear only on the DB37 connector. By default, the FIO lines are digital I/O,

but they can also be configured as up to 6 timers and 2 counters (see Timers/Counters Section of this User’s Guide).

The 8 EIO and 4 CIO lines appear only on the DB15 connector. See the DB15 Section of this User’s Guide for more information.

MIO are standard digital I/O that also have a special multiplexer control function described in Section 2.7 above (AIN). The MIO are

addressed as digital I/O bits 20-22 by the Windows driver. The MIO hardware (electrical specifications) is the same as the

EIO/CIO hardware.

All the digital I/O include an internal series resistor that provides overvoltage/short-circuit protection. These series resistors also

limit the ability of these lines to sink or source current. Refer to the specifications in Appendix A .

All digital I/O on the UE9 have 3 possible states: input, output-high, or output-low. Each bit of I/O can be configured individually.

When configured as an input, a bit has a ~100 kΩ pull-up resistor to 3.3 volts (all digital I/O are 5 volt tolerant). When configured as

output-high, a bit is connected to the internal 3.3 volt supply (through a series resistor). When configured as output-low, a bit is

connected to GND (through a series resistor).

The fact that the digital I/O are specified as 5-volt tolerant means that 5 volts can be connected to a digital input without problems

(see the actual limits in the specifications in Appendix A). If 5 volts is needed from a digital output, consider the following solutions:

In some cases, an open-collector style output can be used to get a 5V signal. To get a low set the line to output-low, and to

get a high set the line to input. When the line is set to input, the voltage on the line is determined by a pull-up resistor. The

UE9 has an internal ~100k resistor to 3.3V, but an external resistor can be added to a different voltage. Whether this will

work depends on how much current the load is going to draw and what the required logic thresholds are. Say for example a

10k resistor is added from EIO0 to VS. EIO0 has an internal 100k pull-up to 3.3 volts and a series output resistance of about

180 ohms. Assume the load draws just a few microamps or less and thus is negligible. When EIO0 is set to input, there will

be 100k to 3.3 volts in parallel with 10k to 5 volts, and thus the line will sit at about 4.85 volts. When the line is set to outputlow, there will be 180 ohms in series with the 10k, so the line will be pulled down to about 0.1 volts.

The surefire way to get 5 volts from a digital output is to add a simple logic buffer IC that is powered by 5 volts and

recognizes 3.3 volts as a high input. Consider the CD74ACT541E from TI (or the inverting CD74ACT540E). All that is

needed is a few wires to bring VS, GND, and the signal from the LabJack to the chip. This chip can level shift up to eight

0/3.3 volt signals to 0/5 volt signals and provides high output drive current (+/-24 mA).

Note that the 2 DAC channels on the U3 can be set to 5 volts, providing 2 output lines with such capability.

15

Page 16

The power-up condition of the digital I/O can be configured by the user. From the factory, all digital I/O are configured to power-up

as inputs. Note that even if the power-up default for a line is changed to output-high or output-low, there is a delay of about 100 ms

at power-up where all digital I/O are in the factory default condition.

The low-level Feedback function (Section 5.3.3) writes and reads all digital I/O. See Section 3.1 for timing information. For

information about using the digital I/O under the Windows LabJackUD driver, see Section 4.3.5.

Many function parameters contain specific bits within a single integer parameter to write/read specific information. In particular,

most digital I/O parameters contain the information for each bit of I/O in one integer, where each bit of I/O corresponds to the same

bit in the parameter (e.g. the direction of FIO0 is set in bit 0 of parameter FIODir). For instance, in the function ControlConfig, the

parameter FIODir is a single byte (8 bits) that writes/reads the power-up direction of each of the 8 FIO lines:

if FIODir is 0, all FIO lines are input,

if FIODir is 1 (20), FIO0 is output, FIO1-FIO7 are input,

if FIODir is 5 (20 + 22), FIO0 and FIO2 are output, all other FIO lines are input,

if FIODir is 255 (20 + … + 27), FIO0-FIO7 are output.

2.9.1 - Typical Digital I/O Connections

2.9.1.1 - Input: Driven Signals

The most basic connection to a UE9 digital input is a driven signal, often called push-pull. With a push-pull signal the source is

typically providing a high voltage for logic high and zero volts for logic low. This signal is generally connected directly to the UE9

digital input, considering the voltage specifications in Appendix A. If the signal is over 5 volts, it can still be connected with a series

resistor. The digital inputs have protective devices that clamp the voltage at GND and VS, so the series resistor is used to limit the

current through these protective devices. For instance, if a 24 volt signal is connected through a 22 kΩ series resistor, about 19

volts will be dropped across the resistor, resulting in a current of about 0.9 mA, which is no problem for the UE9. The series

resistor should be 22 kΩ or less, to make sure the voltage on the I/O line when low is pulled below 1.0 volts.

The other possible consideration with the basic push-pull signal is the ground connection. If the signal is known to already have a

common ground with the UE9, then no additional ground connection is used. If the signal is known to not have a common ground

with the UE9, then the signal ground can simply be connected to UE9 GND. If there is uncertainty about the relationship between

signal ground and UE9 ground (e.g. possible common ground through AC mains), then a ground connection with a 100 Ω series

resistor is generally recommended (see Section 2.7.3.4).

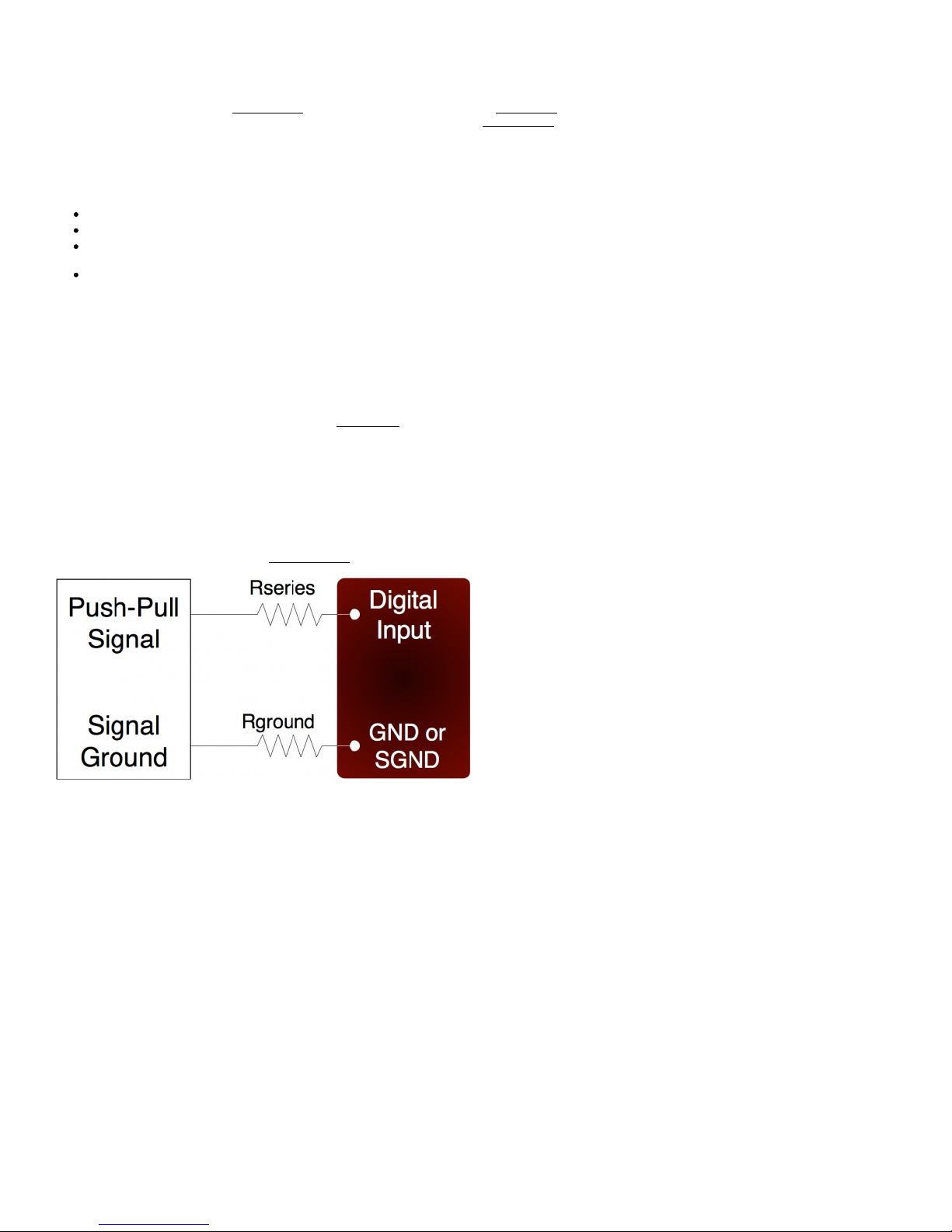

Figure 2-9. Driven Signal Connection To Digital Input

Figure 2-9 shows typical connections. Rground is typically 0-100 Ω. Rseries is typically 0 Ω (short-circuit) for 3.3/5 volt logic, or 22

kΩ (max) for high-voltage logic. Note that an individual ground connection is often not needed for every signal. Any signals

powered by the same external supply, or otherwise referred to the same external ground, should share a single ground connection

to the UE9 if possible.

When dealing with a new sensor, a push-pull signal is often incorrectly assumed when in fact the sensor provides an open-collector

signal as described next.

2.9.1.2 - Input: Open-Collector Signals

Open-collector (also called open-drain or NPN) is a very common type of digital signal. Rather than providing 5 volts and ground,

like the push-pull signal, an open-collector signal provides ground and high-impedance. This type of signal can be thought of as a

switch connected to ground. Since the UE9 digital inputs have a 100 kΩ internal pull-up resistor, an open-collector signal can

generally be connected directly to the input. When the signal is inactive, it is not driving any voltage and the pull-up resistor pulls the

digital input to logic high. When the signal is active, it drives 0 volts which overpowers the pull-up and pulls the digital input to logic

low. Sometimes, an external pull-up (e.g. 4.7 kΩ from Vs to digital input) will be installed to increase the strength and speed of the

logic high condition.

16

Page 17

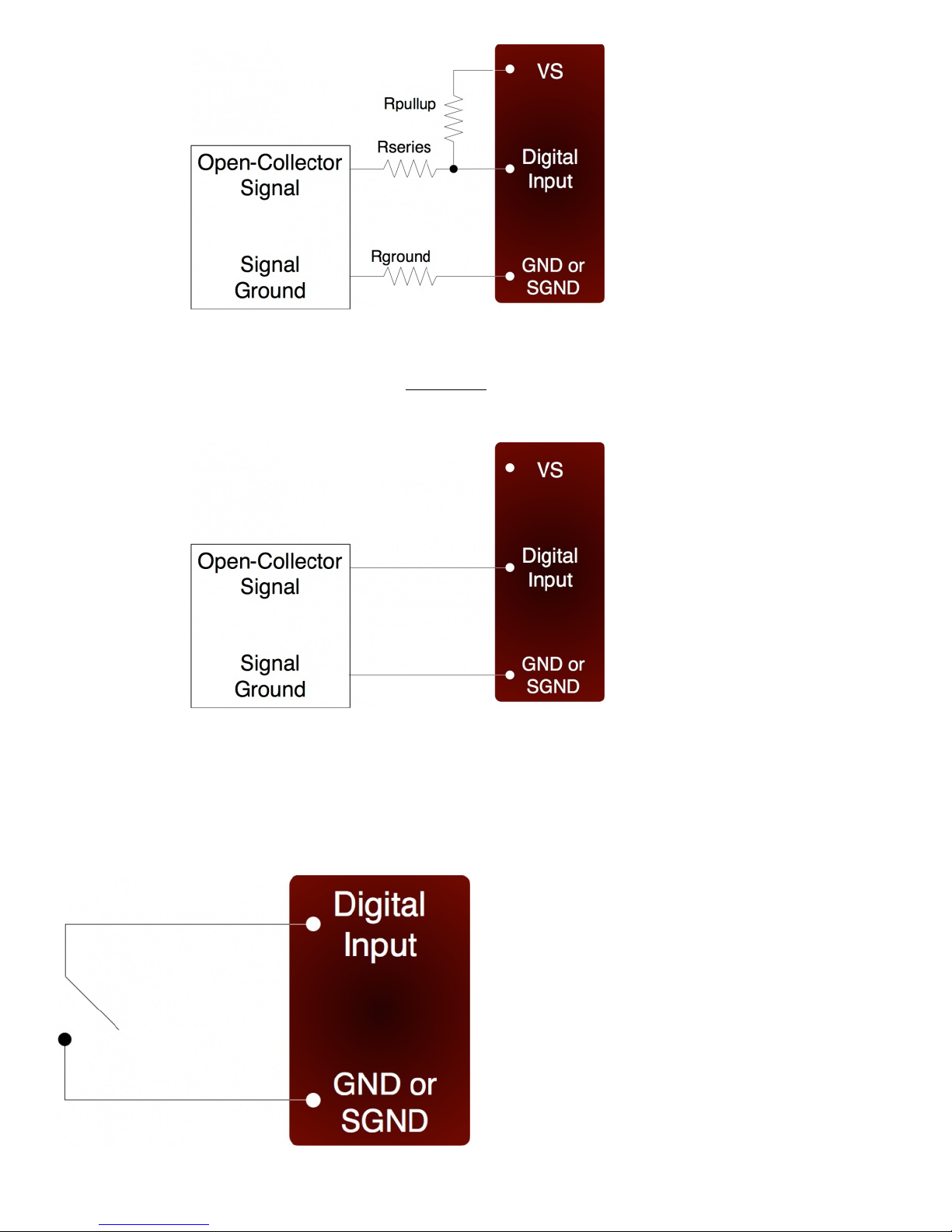

Figure 2-10. Open-Collector (NPN) Connection To Digital Input

Figure 2-10 shows typical connections. Rground is typically 0-100 Ω, Rseries is typically 0 Ω, and Rpullup, the external pull-up

resistor, is generally not required. If there is some uncertainty about whether the signal is really open-collector or could drive a

voltage beyond 5.8 volts, use an Rseries of 22 kΩ as discussed in Section 2.9.1.1, and the input should be compatible with an

open-collector signal or a driven signal up to at least 48 volts.

Without the optional resistors, the figure simplifies to:

Figure 2-10b. Simplified Open-Collector (NPN) Connection To Digital Input Without Optional Resistors

Note that an individual ground connection is often not needed for every signal. Any signals powered by the same external supply,

or otherwise referred to the same external ground, should share a single ground connection to the UE9 if possible.

2.9.1.3 - Input: Mechanical Switch Closure

To detect whether a mechanical switch (dry contact) is open or closed, connect one side of the switch to UE9 ground and the other

side to a digital input. The behavior is very similar to the open-collector described above.

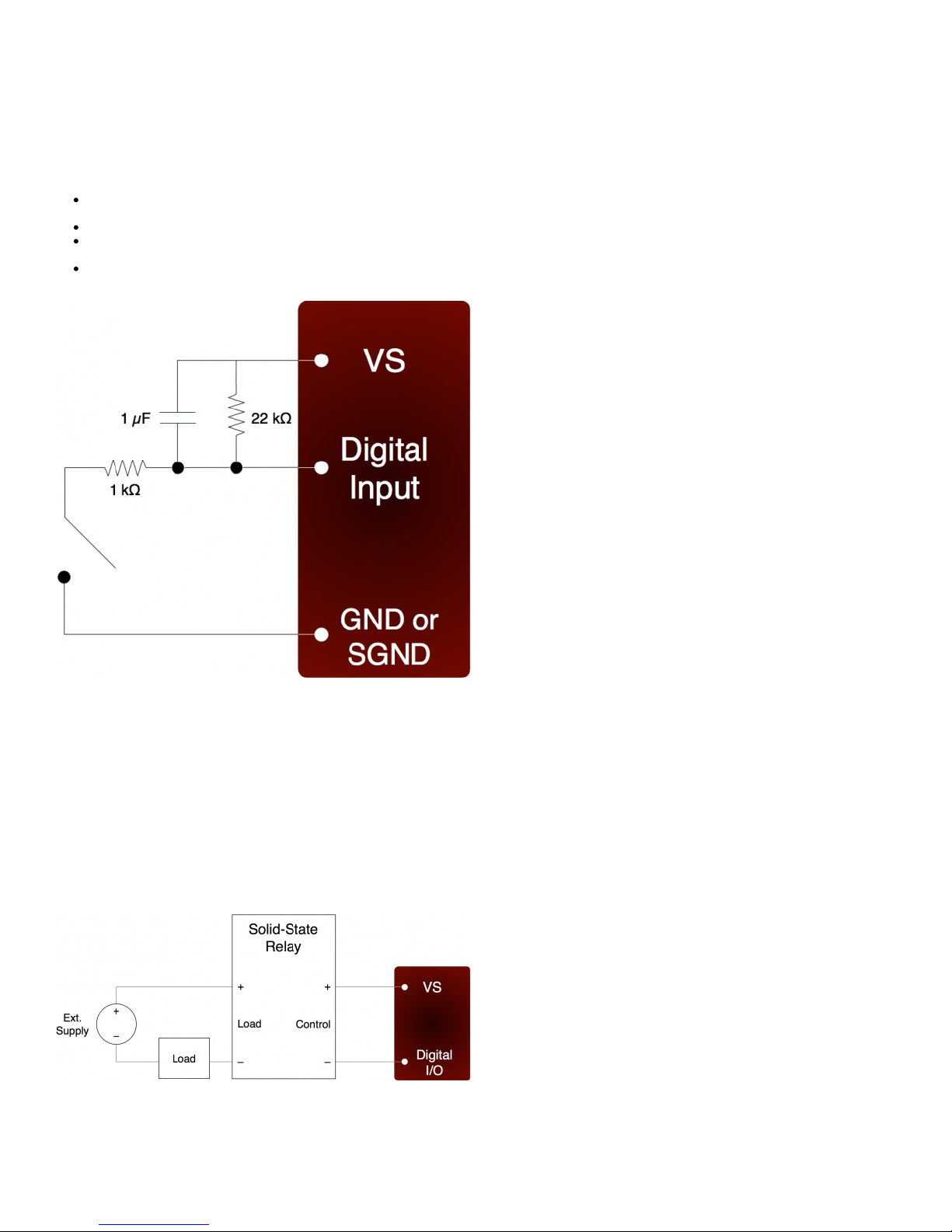

Figure 2-11. Basic Mechanical Switch Connection To Digital Input

17

Page 18

When the switch is open, the internal 100 kΩ pull-up resistor will pull the digital input to about 3.3 volts (logic high). When the switch

is closed, the ground connection will overpower the pull-up resistor and pull the digital input to 0 volts (logic low). Since the

mechanical switch does not have any electrical connections, besides to the LabJack, it can safely be connected directly to GND,

without using a series resistor or SGND.

When the mechanical switch is closed (and even perhaps when opened), it will bounce briefly and produce multiple electrical

edges rather than a single high/low transition. For many basic digital input applications, this is not a problem as the software can

simply poll the input a few times in succession to make sure the measured state is the steady state and not a bounce. For

applications using timers or counters, however, this usually is a problem. The hardware counters, for instance, are very fast and will

increment on all the bounces. Some solutions to this issue are:

Software Debounce: If it is known that a real closure cannot occur more than once per some interval, then software can be

used to limit the number of counts to that rate.

Firmware Debounce: See section 2.10.1 for information about timer mode 6.

Active Hardware Debounce: Integrated circuits are available to debounce switch signals. This is the most reliable hardware

solution. See the MAX6816 (maxim-ic.com) or EDE2008 (elabinc.com).

Passive Hardware Debounce: A combination of resistors and capacitors can be used to debounce a signal. This is not

foolproof, but works fine in most applications.

Figure 2-12. Passive Hardware Debounce

Figure 2-12 shows one possible configuration for passive hardware debounce. First, consider the case where the 1 kΩ resistor is

replaced by a short circuit. When the switch closes it immediately charges the capacitor and the digital input sees logic low, but

when the switch opens the capacitor slowly discharges through the 22 kΩ resistor with a time constant of 22 ms. By the time the

capacitor has discharged enough for the digital input to see logic high, the mechanical bouncing is done. The main purpose of the

1 kΩ resistor is to limit the current surge when the switch is close. 1 kΩ limits the maximum current to about 5 mA, but better results

might be obtained with smaller resistor values.

2.9.1.4 - Output: Controlling Relays

All the digital I/O lines have series resistance that restricts the amount of current they can sink or source, but solid-state relays

(SSRs) can usually be controlled directly by the digital I/O. The SSR is connected as shown in the following diagram, where VS (~5

volts) connects to the positive control input and the digital I/O line connects to the negative control input (sinking configuration).

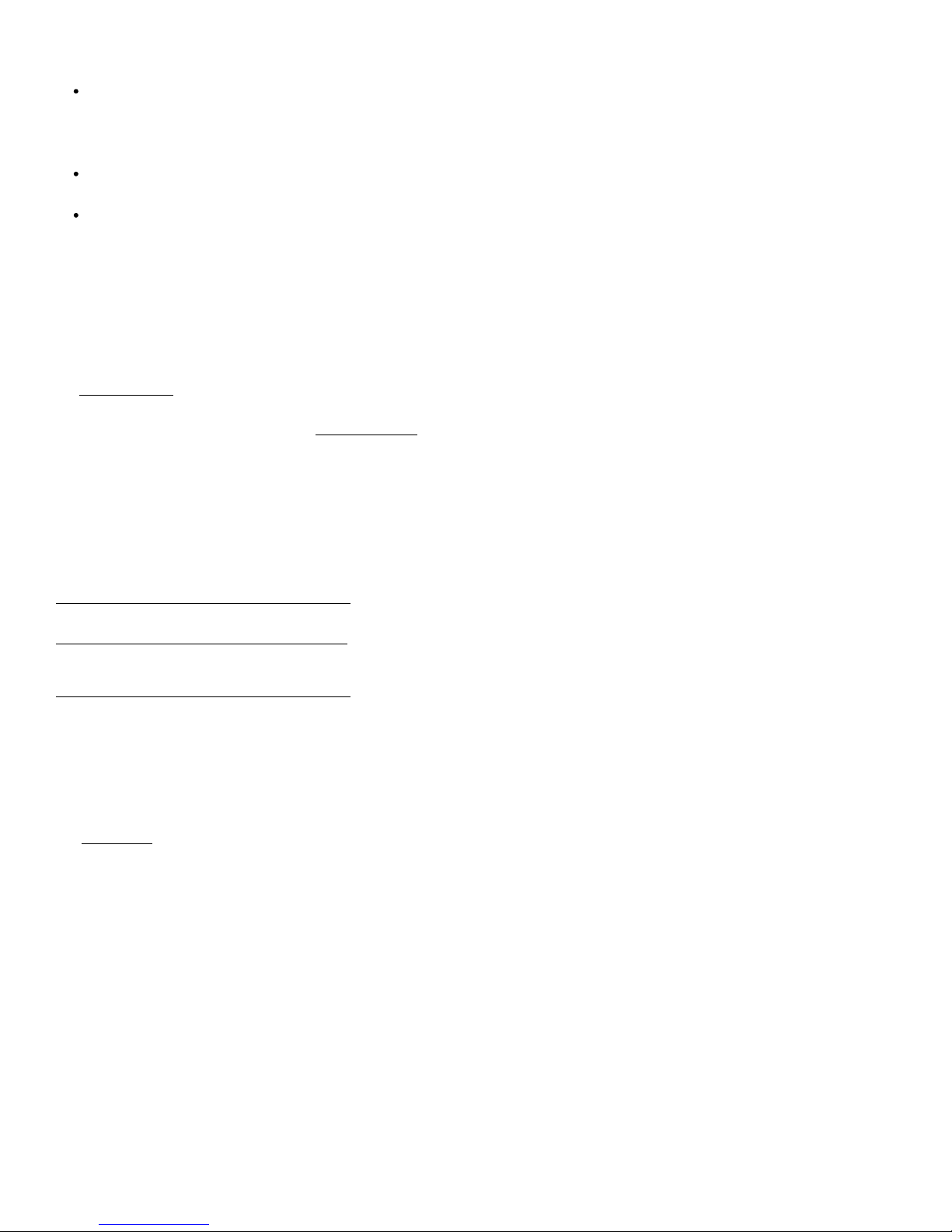

Figure 2-13. Relay Connections (Sinking Control, High-Side Load Switching)

When the digital line is set to output-low, control current flows and the relay turns on. When the digital line is set to input, control

current does not flow and the relay turns off. When the digital line is set to output-high, some current flows, but whether the relay is

on or off depends on the specifications of a particular relay. It is recommended to only use output-low and input.

18

Page 19

For example, the Series 1 (D12/D24) or Series T (TD12/TD24) relays from Crydom specify a max turn-on of 3.0 volts, a min turnoff of 1.0 volts, and a nominal input impedance of 1500 Ω.

When the digital line is set to output-low, it is the equivalent of a ground connection with 180 Ω (EIO/CIO/MIO) or 550 Ω (FIO)

in series. When using an EIO/CIO/MIO line, the resulting voltage across the control inputs of the relay will be about

5*1500/(1500+180) = 4.5 volts (the other 0.5 volts is dropped across the internal resistance of the EIO/CIO/MIO line). With

an FIO line the voltage across the inputs of the relay will be about 5*1500/(1500+550) = 3.7 volts (the other 1.3 volts are

dropped across the internal resistance of the FIO line). Both of these are well above the 3.0 volt threshold for the relay, so it

will turn on.

When the digital line is set to input, it is the equivalent of a 3.3 volt connection with 100 kΩ in series. The resulting voltage

across the control inputs of the relay will be close to zero, as virtually all of the 1.7 volt difference (between VS and 3.3) is

dropped across the internal 100 kΩ resistance. This is well below the 1.0 volt threshold for the relay, so it will turn off.

When the digital line is set to output-high, it is the equivalent of a 3.3 volt connection with 180 Ω (EIO/CIO/MIO) or 550 Ω

(FIO) in series. When using an EIO/CIO/MIO line, the resulting voltage across the control inputs of the relay will be about

1.7*1500/(1500+180) = 1.5 volts. With an FIO line the voltage across the inputs of the relay will be about

1.7*1500/(1500+550) = 1.2 volts. Both of these in the 1.0-3.0 volt region that is not defined for these example relays, so the

resulting state is unknown.

Mechanical relays require more control current than SSRs, and cannot be controlled directly by the digital I/O on the UE9. To

control higher currents with the digital I/O, some sort of buffer is used. Some options are a discrete transistor (e.g. 2N2222), a

specific chip (e.g. ULN2003), or an op-amp.

Note that the UE9 DACs can source enough current to control almost any SSR and even some mechanical relays, and thus can be

a convenient way to control 1 or 2 relays.

The RB12 relay board is a useful accessory available from LabJack. This board connects to the DB15 connector on the UE9 and

accepts up to 12 industry standard I/O modules (designed for Opto22 G4 modules and similar).

Another accessory available from LabJack is the LJTick-RelayDriver. This is a two channel module that plugs into the UE9 screwterminals, and allows two digital lines to each hold off up to 50 volts and sink up to 200 mA. This allows control of virtually any solidstate or mechanical relay.

2.10 - Timers/Counters

The UE9 has 6 timers (Timer0-Timer5) and 2 counters (Counter0-Counter1). When any of these timers or counters are enabled,

they take over an FIO line in sequence (Timer0, Timer1, …, Timer5, Counter0, Counter1). If any one of the 8 timers/counters is

enabled, it will take over FIO0. If any 2 are enabled, they will take over FIO0 and FIO1. If all 8 are enabled, they will take over all 8

FIO lines. Some examples:

1 Timer enabled, Counter0 disabled, Counter1 disabled

FIO0=Timer0

1 Timer enabled, Counter0 disabled, Counter1 enabled

FIO0=Timer0

FIO1=Counter1

6 Timers enabled, Counter0 enabled, Counter1 enabled

FIO0-FIO5=Timer0-Timer5

FIO6=Counter0

FIO7=Counter1

Timers and counters can appear on various pins, but other I/O lines never move. For example, Counter1 can appear anywhere

from FIO0 to FIO7, depending on how many timers are enabled and whether Counter0 is enabled.

Applicable digital I/O are automatically configured as input or output as needed when timers and counters are enabled, and stay

that way when the timers/counters are disabled.

See Section 2.9.1 for information about signal connections.

Each counter (Counter0 or Counter1) consists of a 32-bit register that accumulates the number of falling edges detected on the

external pin. If a counter is reset and read in the same function call, the read returns the value just before the reset.

Counter1 is used internally by stream mode, but in such a case only uses an FIO line if clock output or external triggering is used. If

any timers/counters are being used while starting/stopping a stream, the possible interaction between timer/counter configuration

and starting/stopping a stream needs to be considered.

The timers (Timer0-Timer5) have various modes available:

19

Page 20

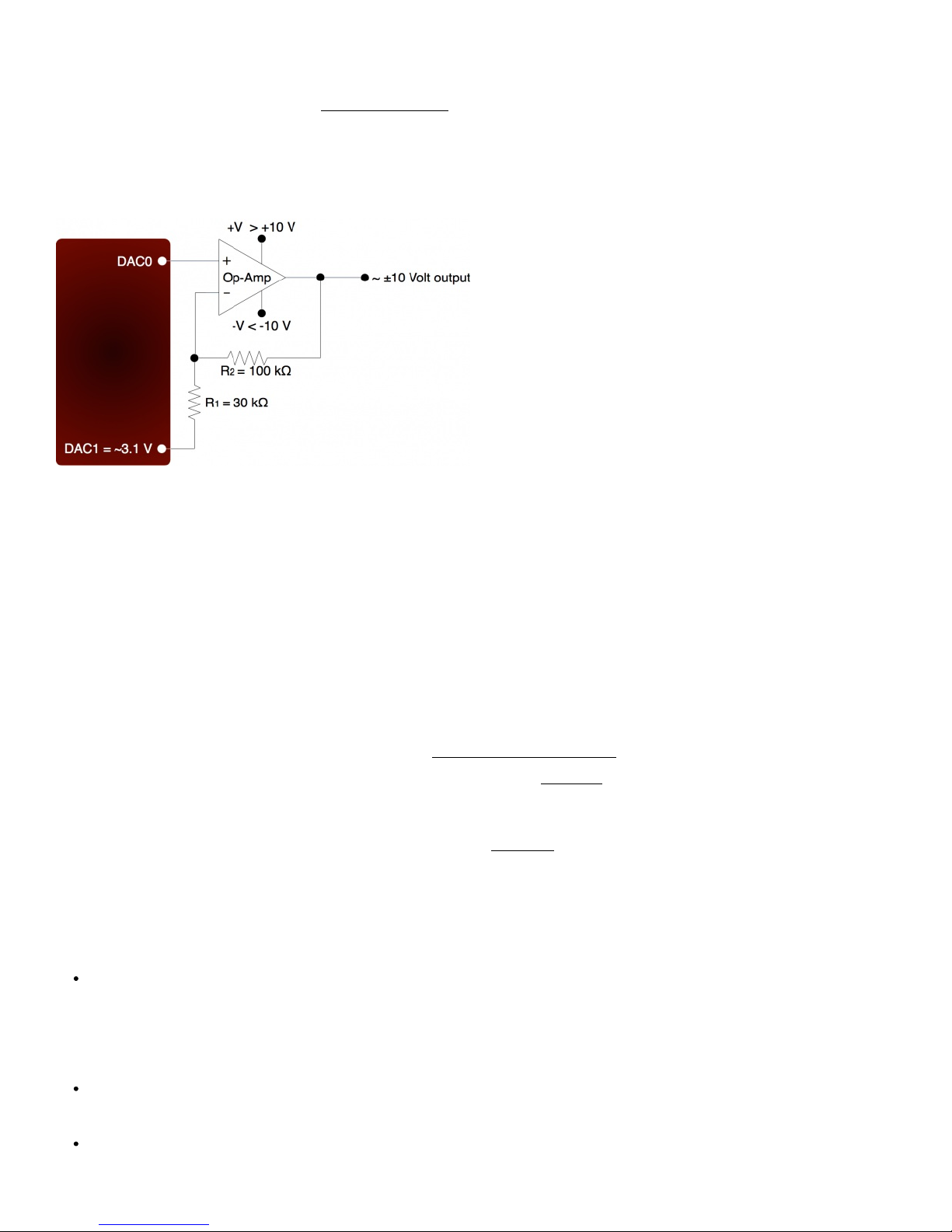

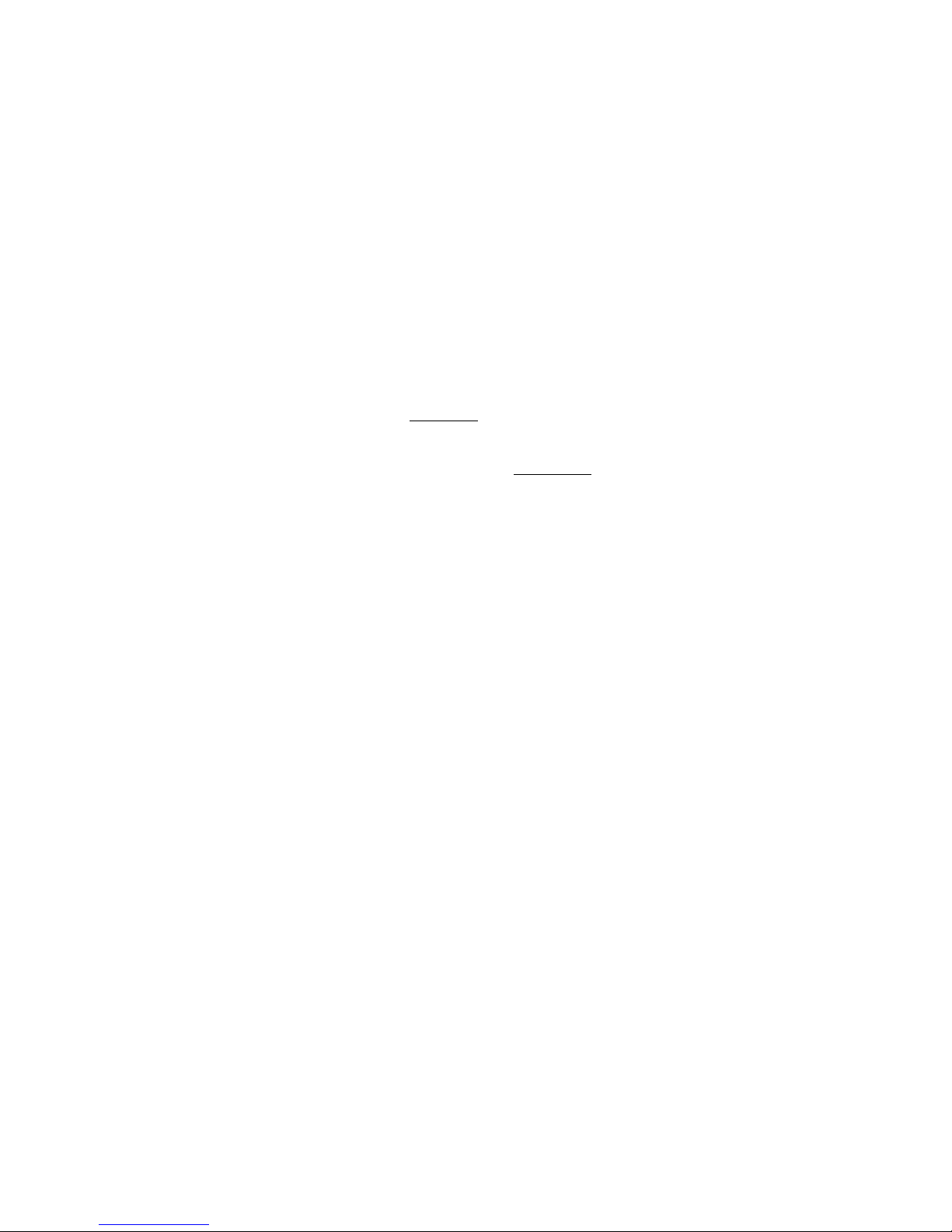

Timer Modes

0

16-bit PWM output

1

8-bit PW M output

2

Period input (32-bit, rising edges)

3

Period input (32-bit, falling edges)

4

Duty cycle input

5

Firmware counter input

6

Firmware counter input (with debounce)

7

Frequency output

8

Quadrature input

9

Timer stop input (odd timers only)

10

System timer low read

11

System timer hight read

12

Period input (16-bit, rising edges)

13

Period input (16-bit, falling edges)

Table 2.10-1. UE9 Timer Modes

TimerClockBase

0

750 kHz

1

48 MHz (Sy stem)

Table 2.10-2. UE9 Timer Clock Options

All timers use the same timer clock (which affects modes 0, 1, 2, 3, 4, 7, 12, and 13). The timer clock is determined by dividing the

base clock by the clock divisor. The divisor has a range of 0-255, where 0 corresponds to a division of 256. There are 2 choices

for the timer base clock.

The low level TimerCounter function has a bit called UpdateConfig that must be set to change the timer clock, timer modes, or

number of timers/counters enabled. When this bit is set, all timers and counters are re-initialized. The LabJackUD driver

automatically sets this bit if any write requests are executed related to mode, enabling/disabling, or clock configuration.

The low level TimerCounter function has UpdateReset bits for each timer that must be set to change the timer value. The

LabJackUD driver automatically sets the appropriate bit when a value write is executed.

The low level TimerCounter function has Reset bits for each counter that must be set to reset the counter to zero. The LabJackUD

automatically sets the appropriate bit when a reset request is executed.

2.10.1 - Timer Mode Descriptions

2.10.1.1 - PWM Output (16-Bit, Mode 0)

Outputs a pulse width modulated rectangular wave output. Value passed should be 0-65535, and determines what portion of the

total time is spent low (out of 65536 total increments). That means the duty cycle can be varied from 100% (0 out of 65536 are low)

to 0.0015% (65535 out of 65536 are low).

The overall frequency of the PWM output is the clock frequency specified by TimerClockBase/TimerClockDivisor divided by 216.

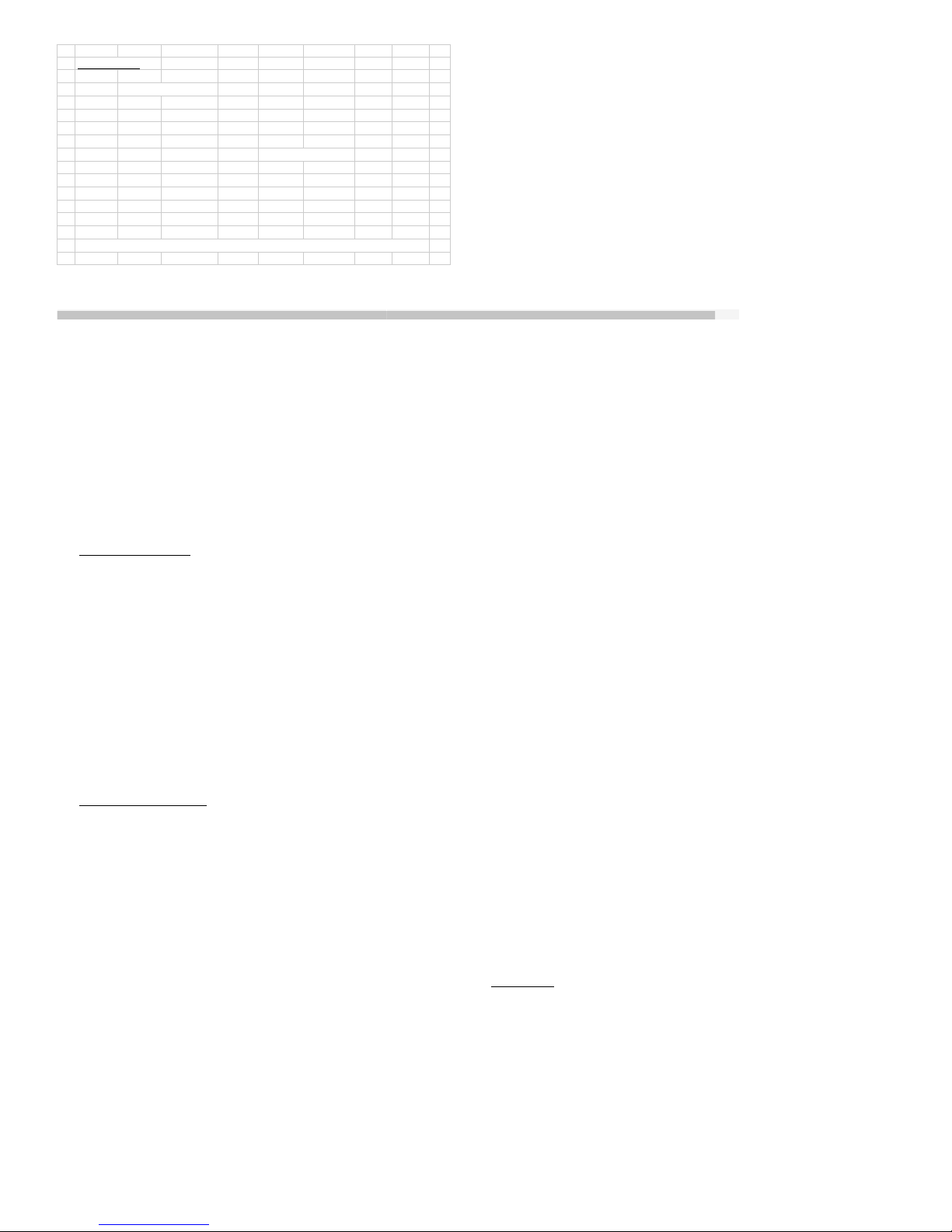

The following table shows the range of available PWM frequencies based on timer clock settings.

PWM16 Frequency

Ranges

TimerClockBase

Divisor=1

Divisor=256

0

750 kHz

11.44

0.04

750000

1

48 MHz (Sy stem)

732.42

2.86

48000000

Table 2.10.1.1-1. 16-bit PW M Fre quency Ranges

The same clock applies to all timers, so all 16-bit PWM channels will have the same frequency and will have their falling edges at

the same time.

PWM output starts by setting the digital line to output-low for the specified amount of time. The output does not necessarily start

instantly, but rather waits for the internal clock to roll. For example, if the PWM frequency is 100 Hz, that means the period is 10

milliseconds, and thus after the command is received by the device it could be anywhere from 0 to 10 milliseconds before the start

of the PWM output.

If a duty cycle of 0.0% (totally off) is required, consider using a simple inverter IC such as the CD74ACT540E from TI.

2.10.1.2 - PWM Output (8-Bit, Mode 1)

Outputs a pulse width modulated rectangular wave output. Value passed should be 0-65535, and determines what portion of the

total time is spent low (out of 65536 total increments). The lower byte is actually ignored since this is 8-bit PWM. That means the

duty cycle can be varied from 100% (0 out of 65536 are low) to 0.4% (65280 out of 65536 are low).

The overall frequency of the PWM output is the clock frequency specified by TimerClockBase/TimerClockDivisor divided by 28.

20

Page 21

The following table shows the range of available PWM frequencies based on timer clock settings.

PWM8 Frequency Ranges

TimerClockBase

Divisor=1

Divisor=256

0

750 kHz

2929.69

11.44

750000

1

48 MHz (Sy stem)

187500

732.42

48000000

Table 2.10.1.2-1. 8-bit PW M Fre quency Ranges