Page 1

LabJack U3 User’s Guide

Revision 1.02

2/6/2007

LabJack Corporation

www.labjack.com

support@labjack.com

Page 2

For the latest version of this and other documents, go to

LabJack designs and manufactures measurement and automation peripherals that enable the

connection of a PC to the real-world. Although LabJacks have various redundant protection

mechanisms, it is possible, in the case of improper and/or unreasonable use, to damage the

LabJack and even the PC to which it is connected. LabJack Corporation will not be liable for

any such damage.

Except as specified herein, LabJack Corporation makes no warranties, express or implied,

including but not limited to any implied warranty or merchantability or fitness for a particular

purpose. LabJack Corporation shall not be liable for any special, indirect, incidental or

consequential damages or losses, including loss of data, arising from any cause or theory.

LabJacks and associated products are not designed to be a critical component in life support or

systems where malfunction can reasonably be expected to result in personal injury. Customers

using these products in such applications do so at their own risk and agree to fully indemnify

LabJack Corporation for any damages resulting from such applications.

LabJack assumes no liability for applications assistance or customer product design.

Customers are responsible for their applications using LabJack products. To minimize the risks

associated with customer applications, customers should provide adequate design and

operating safeguards.

Reproduction of products or written or electronic information from LabJack Corporation is

prohibited without permission. Reproduction of any of these with alteration is an unfair and

deceptive business practice.

Copyright © 2007, LabJack Corporation

www.labjack.com.

2

Page 3

LabJack U3 User’s Guide Revision History

V1.00 released December 14

V1.01 released January 31

th

, 2006

st

, 2007

Section 2.13 – New section describing changes with hardware revision 1.21.

Section 4.2 – Various minor typo corrections.

Section 5.2.12 – Various changes to StreamData section.

Section 5.3 – Updated low-level errorcode list.

V1.02 released February 6

th

, 2007

Section 1.1 – Updated for current software.

Section 1.2 – Updated for current software.

Section 2.6.3.7 – Updated figures and various details in current measurement section.

3

Page 4

Table Of Contents

1. Installation on Windows ...........................................................................................................7

1.1 Control Panel Application (LJControlPanel) .......................................................................7

1.2 Self-Upgrade Application (LJSelfUpgrade).......................................................................10

2. Hardware Description.............................................................................................................12

2.1 USB ..................................................................................................................................12

2.2 Status LED .......................................................................................................................13

2.3 GND and SGND ...............................................................................................................13

2.4 Vs .....................................................................................................................................13

2.5 Flexible I/O (FIO/EIO).......................................................................................................13

2.6 AIN....................................................................................................................................14

2.6.1 Channel Numbers ......................................................................................................15

2.6.2 Converting Binary Readings to Voltages ...................................................................15

2.6.3 Typical Analog Input Connections .............................................................................17

2.6.4 Internal Temperature Sensor .....................................................................................23

2.7 DAC ..................................................................................................................................23

2.7.1 Typical Analog Output Connections............................................................................24

2.8 Digital I/O..........................................................................................................................25

2.8.1 Typical Digital I/O Connections...................................................................................26

2.9 Timers/Counters ...............................................................................................................30

2.9.1 Timer Mode Descriptions ............................................................................................32

2.9.2 Timer Operation/Performance Notes ..........................................................................36

2.10 SCL and SDA (or SCA) ..................................................................................................36

2.11 DB15...............................................................................................................................36

2.11.1 CB15 Terminal Board ...............................................................................................37

2.11.2 RB12 Relay Board ....................................................................................................37

2.12 U3-OEM..........................................................................................................................38

2.13 Hardware Revision Notes...............................................................................................39

3. Operation ...............................................................................................................................40

3.1 Command/Response........................................................................................................40

3.2 Stream Mode ....................................................................................................................42

3.2.1 Streaming Digital Inputs, Timers, and Counter0 .........................................................43

4. LabJackUD High-Level Driver................................................................................................44

4.1 Overview...........................................................................................................................44

4.1.1 Function Flexibility .....................................................................................................45

4.1.2 Multi-Threaded Operation ..........................................................................................46

4.2 Function Reference ..........................................................................................................48

4.2.1 ListAll().......................................................................................................................48

4.2.2 OpenLabJack() ..........................................................................................................49

4.2.3 eGet() and ePut() .......................................................................................................50

4.2.4 eAddGoGet()..............................................................................................................51

4.2.5 AddRequest().............................................................................................................51

4.2.6 Go()............................................................................................................................52

4.2.7 GoOne() .....................................................................................................................53

4.2.8 GetResult().................................................................................................................53

4.2.9 GetFirstResult() and GetNextResult()........................................................................54

4.2.10 DoubleToStringAddress() ........................................................................................55

4.2.11 StringToDoubleAddress() ........................................................................................55

4.2.12 StringToConstant()...................................................................................................56

4.2.13 ErrorToString() .........................................................................................................56

4.2.14 GetDriverVersion() ...................................................................................................57

4.2.15 TCVoltsToTemp() ....................................................................................................57

4.2.16 ResetLabJack()........................................................................................................57

iv

Page 5

4.2.17 eAIN().......................................................................................................................58

4.2.18 eDAC() .....................................................................................................................58

4.2.19 eDI().........................................................................................................................59

4.2.20 eDO() .......................................................................................................................59

4.2.21 eTCConfig() .............................................................................................................60

4.2.22 eTCValues().............................................................................................................61

4.3 Example Pseudocode.......................................................................................................62

4.3.1 Open ...........................................................................................................................62

4.3.2 Configuration...............................................................................................................62

4.3.3 Analog Inputs..............................................................................................................63

4.3.4 Analog Outputs ...........................................................................................................65

4.3.5 Digital I/O ....................................................................................................................65

4.3.6 Timers & Counters ......................................................................................................66

4.3.7 Stream Mode ..............................................................................................................68

4.3.8 Raw Output/Input........................................................................................................72

4.3.9 Easy Functions ...........................................................................................................72

4.3.10 Miscellaneous ...........................................................................................................73

4.4 Errorcodes........................................................................................................................75

5. Low-Level Function Reference ..............................................................................................78

5.1 General Protocol...............................................................................................................78

5.2 Low-Level Functions.........................................................................................................80

5.2.1 BadChecksum............................................................................................................80

5.2.2 ConfigU3 ....................................................................................................................81

5.2.3 ConfigIO.....................................................................................................................84

5.2.4 ConfigTimerClock ......................................................................................................86

5.2.5 Feedback ...................................................................................................................87

5.2.6 ReadMem (ReadCal) .................................................................................................95

5.2.7 WriteMem (WriteCal) .................................................................................................96

5.2.8 EraseMem (EraseCal) ...............................................................................................97

5.2.9 Reset..........................................................................................................................98

5.2.10 StreamConfig ...........................................................................................................99

5.2.11 StreamStart............................................................................................................101

5.2.12 StreamData............................................................................................................102

5.2.13 StreamStop ............................................................................................................103

5.3.14 Watchdog...............................................................................................................104

5.3.15 SPI .........................................................................................................................106

5.3.16 AsynchConfig.........................................................................................................108

5.3.17 AsynchTX...............................................................................................................109

5.3.18 AsynchRX ..............................................................................................................110

5.3.19 I2C .........................................................................................................................111

5.3.20 SHT1X ...................................................................................................................113

5.3 Errorcodes......................................................................................................................114

A. Specifications.......................................................................................................................116

B. Enclosure & PCB Drawings .................................................................................................119

v

Page 6

Table Of Figures

Figure 1-1. LJControlPanel Main Window....................................................................................7

Figure 1-2. LJControlPanel U3 Configure Defaults Window ........................................................8

Figure 1-3. LJControlPanel U3 Test Window...............................................................................9

Figure 1-4. LJControlPanel Settings Window ..............................................................................9

Figure 1-5. Self-Upgrade Application.........................................................................................10

Figure 2-1. LabJack U3..............................................................................................................12

Table 2-1. Analog Input Pin Locations .......................................................................................13

Table 2-2. ConfigIO Factory Default Values .............................................................................14

Table 2-3. ConfigTimerClock Factory Default Values ................................................................14

Table 2-4. Positive Channel Numbers .......................................................................................15

Table 2-5. Negative Channel Numbers......................................................................................15

Table 2-6. Nominal Analog Input Voltage Ranges (DAC1 Disabled) .........................................16

Table 2-7. Calibration Constant Memory Locations ...................................................................16

Table 2-8. Fixed Point Conversion Examples ............................................................................17

Table 2-9. Nominal Analog Input Voltage Ranges (DAC1 Enabled)..........................................17

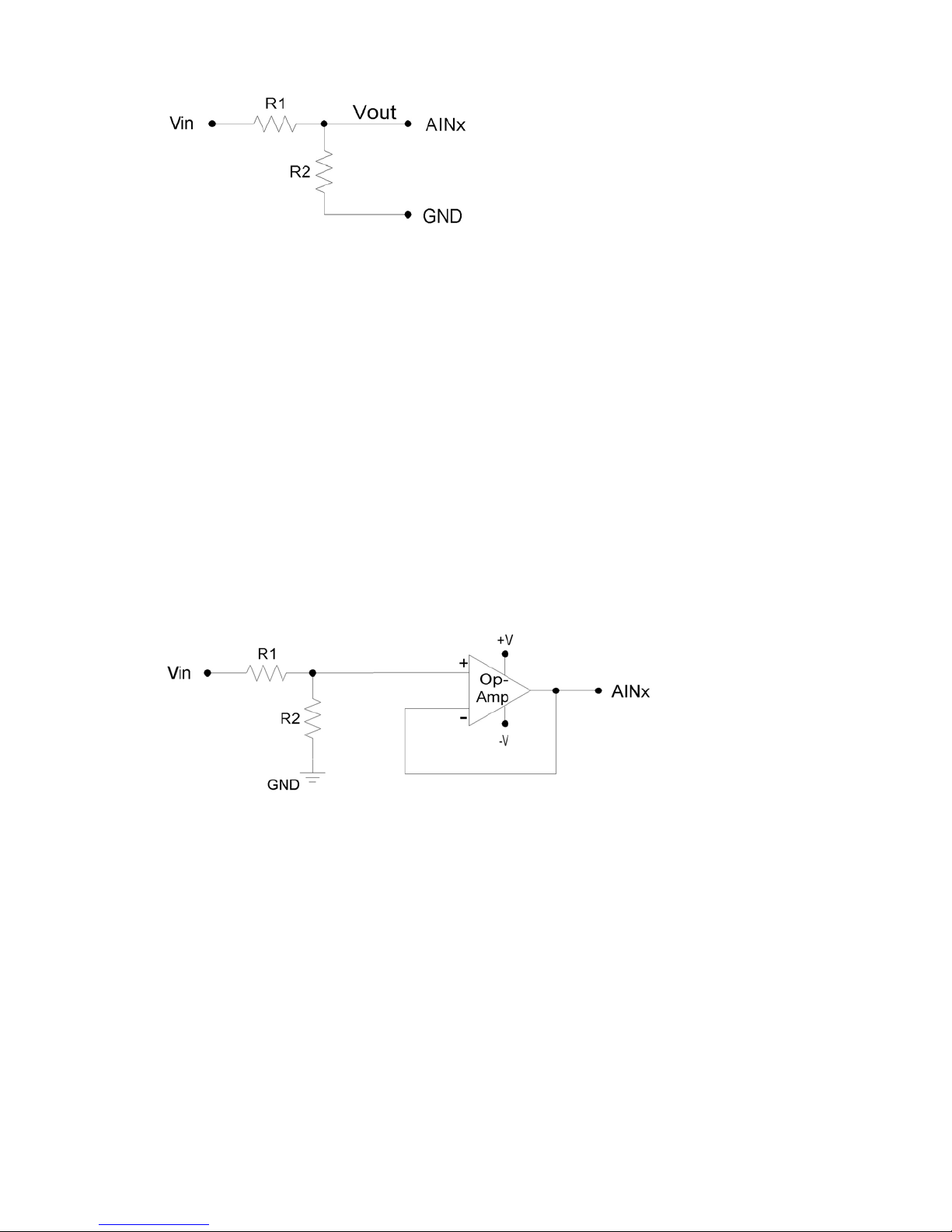

Figure 2-2. Non-Inverting Op-Amp Configuration ......................................................................20

Figure 2-3. Voltage Divider Circuit .............................................................................................21

Figure 2-4. Buffered Voltage Divider Circuit...............................................................................21

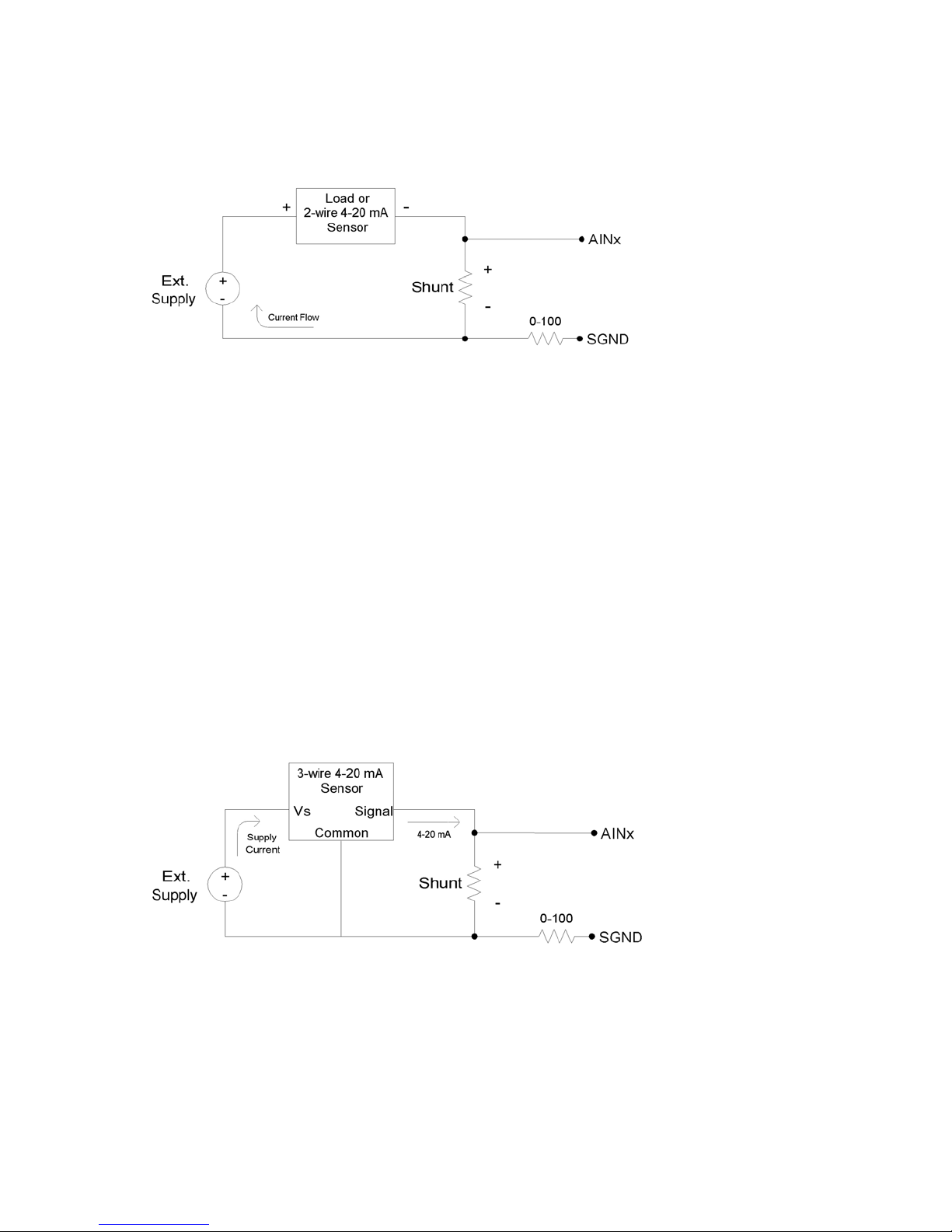

Figure 2-5. Current Measurement With Arbitrary Load or 2-Wire 4-20 mA Sensor ...................22

Figure 2-6. Current Measurement With 3-Wire 4-20 mA (Sourcing) Sensor .............................22

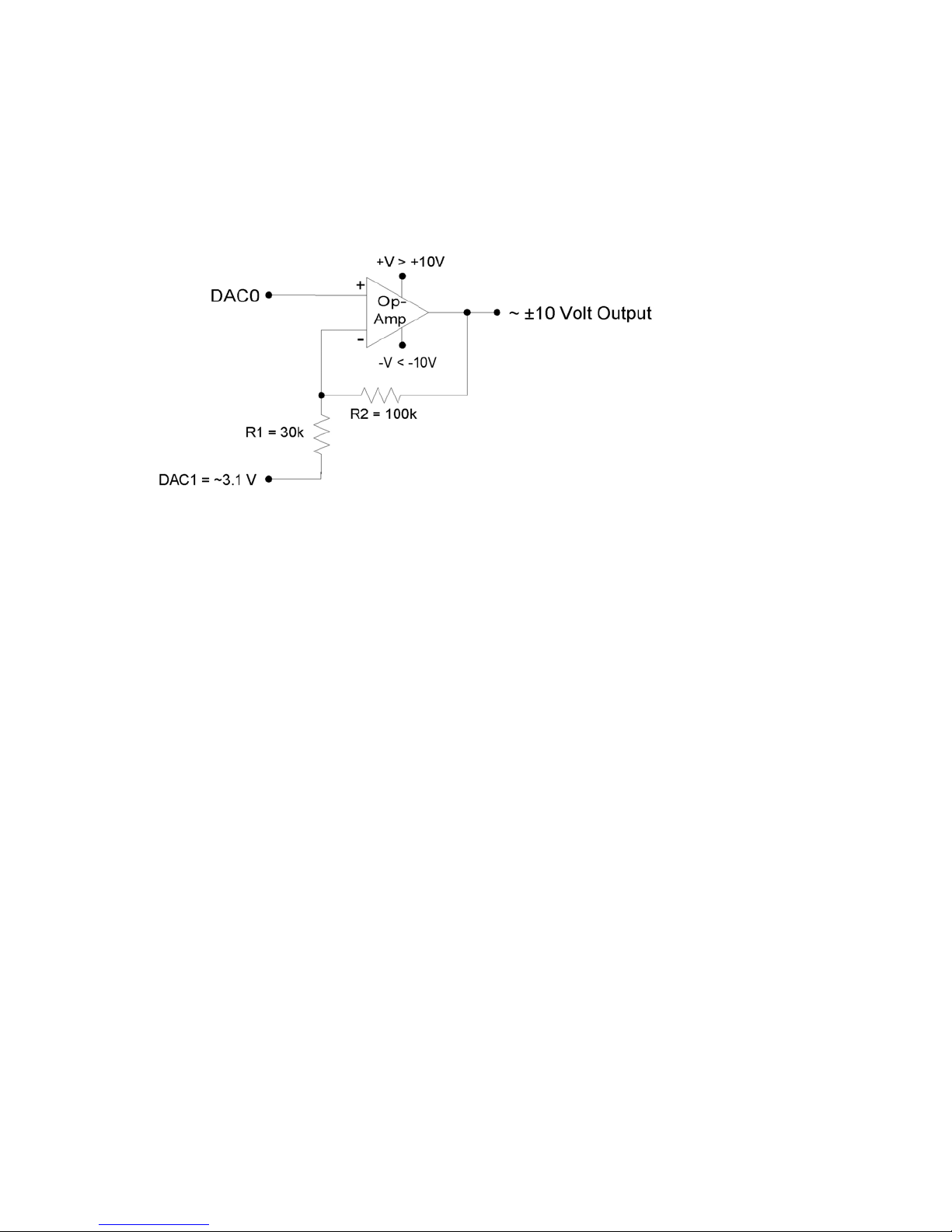

Figure 2-7. ±10 Volt DAC Output Circuit....................................................................................25

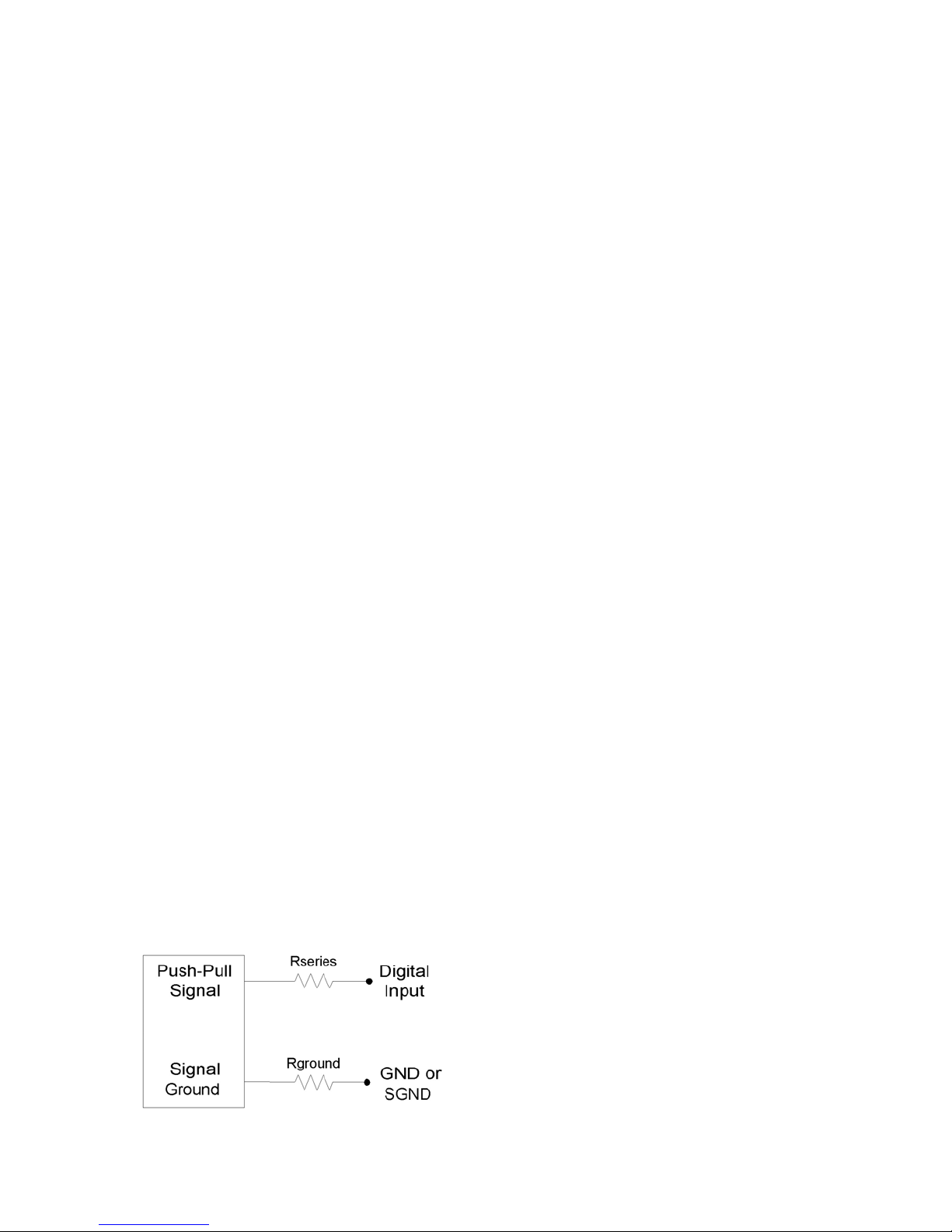

Figure 2-8. Driven Signal Connection To Digital Input ...............................................................26

Figure 2-9. Driven Signal Connection To Digital Input ...............................................................27

Figure 2-10. Basic Mechanical Switch Connection To Digital Input...........................................28

Figure 2-11. Passive Hardware Debounce ................................................................................28

Figure 2-12. Relay Connections (Sinking Control, High-Side Load Switching)..........................29

Table 3-1. Typical Feedback Function Execution Times (QuickSample=0, LongSettling=0) ....40

Table 3-2. Typical Feedback Function Execution Times (QuickSample=1, LongSettling=0) ....40

Table 3-3. Typical Feedback Function Execution Times (QuickSample=0, LongSettling=1) ....40

Table 3-4. Stream Performance.................................................................................................42

Table 3-5. Special Stream Channels .........................................................................................43

Table 4-1. Request Level Error Codes (Part 1)..........................................................................75

Table 4-2. Request Level Error Codes (Part 2)..........................................................................76

Table 4-3. Group Level Error Codes ..........................................................................................77

vi

Page 7

1. Installation on Windows

It is recommended to install the software before making a USB connection to the LabJack U3.

The LabJack UD driver requires a PC running Windows 98, ME, 2000, or XP. For other

operating systems, go to labjack.com for available support, if any. Software will be installed to

the LabJack directory which defaults to c:\Program Files\LabJack\.

Check labjack.com for the latest software & drivers, but in order to install DAQFactory Express

the CD must be used before installing updates.

When the USB cable is connected from the PC to the U3, on a USB port that has not

enumerated a U3 before, Windows will bring up the add new hardware wizard. If this is the first

time a U3 has been enumerated on any port on the PC, use the “specify location” option and

browse to the appropriate driver folder. There is a folder for Windows 98/ME and another folder

for Windows 2000/XP. These folders are installed in:

c:\Program Files\LabJack\drivers\install\U3\

If a U3 has been enumerated on the PC before, but just not on this particular port, the “install

automatically” option can be used in the Windows new hardware wizard.

After installation of the software, run LJControlPanel to configure and test the unit. Then run

LJSelfUpgrade to check for newer firmware.

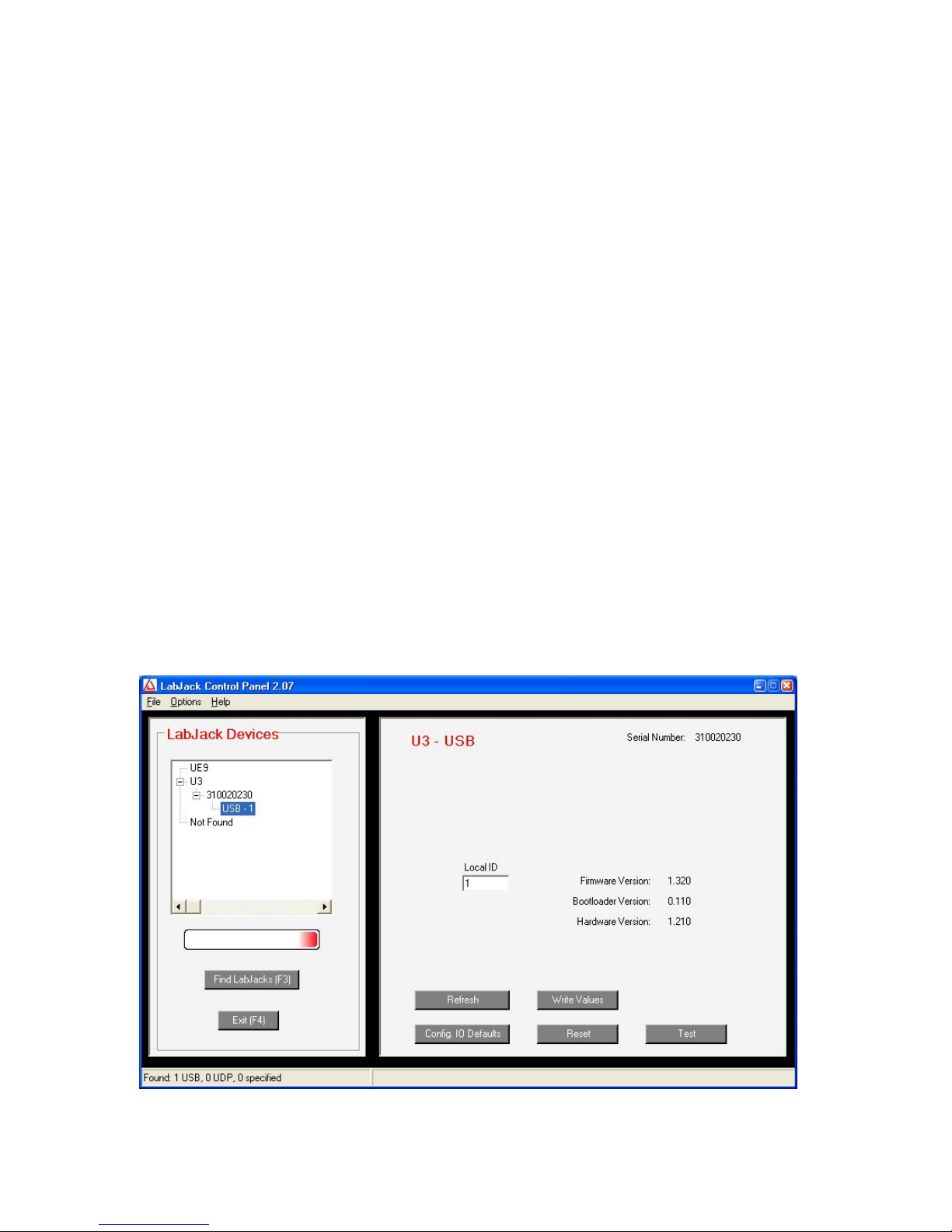

1.1 Control Panel Application (LJControlPanel)

The LabJack Control Panel application (LJCP.exe) handles configuration and testing of the U3.

Click on the “Find LabJacks” button to search for connected devices.

Figure 1-1. LJControlPanel Main Window

7

Page 8

Figure 1-1 shows the results from a typical search. The application found one U3 connected by

USB. The USB connection has been selected in Figure 1-1, bringing up the configuration

window on the right side.

• Refresh: Reload the window using values read from the device.

• Write Values: Write the Local ID from the window to the device.

• Config. IO Defaults: Opens the window shown in Figure 1-2.

• Reset: Click to reset the selected device.

• Test: Opens the window shown in Figure 1-3.

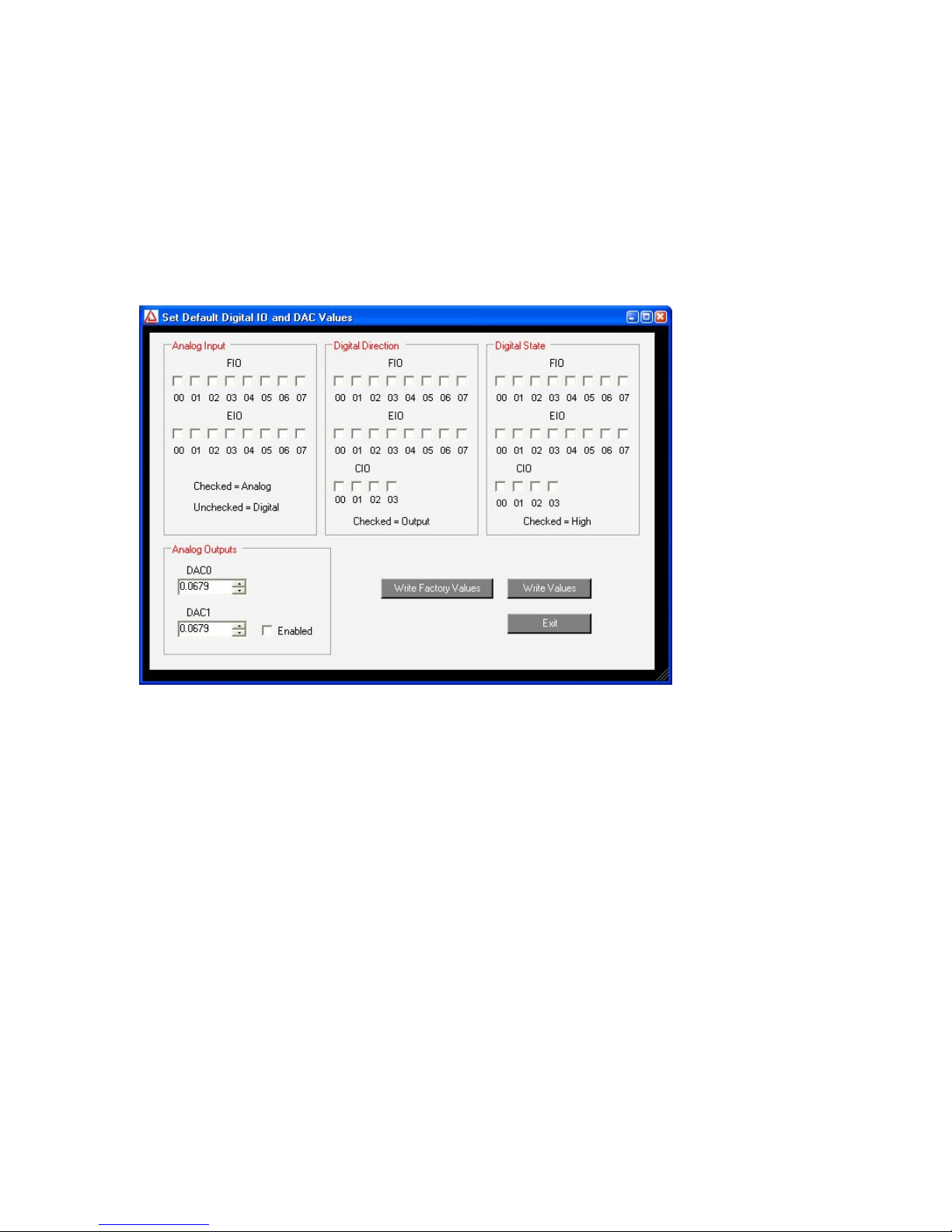

Figure 1-2. LJControlPanel U3 Configure Defaults Window

Figure 1-2 shows the configuration window for U3 defaults. These are the values that will be

loaded by the U3 at power-up or reset. The factory defaults, as shown above, are all lines

configured as digital input.

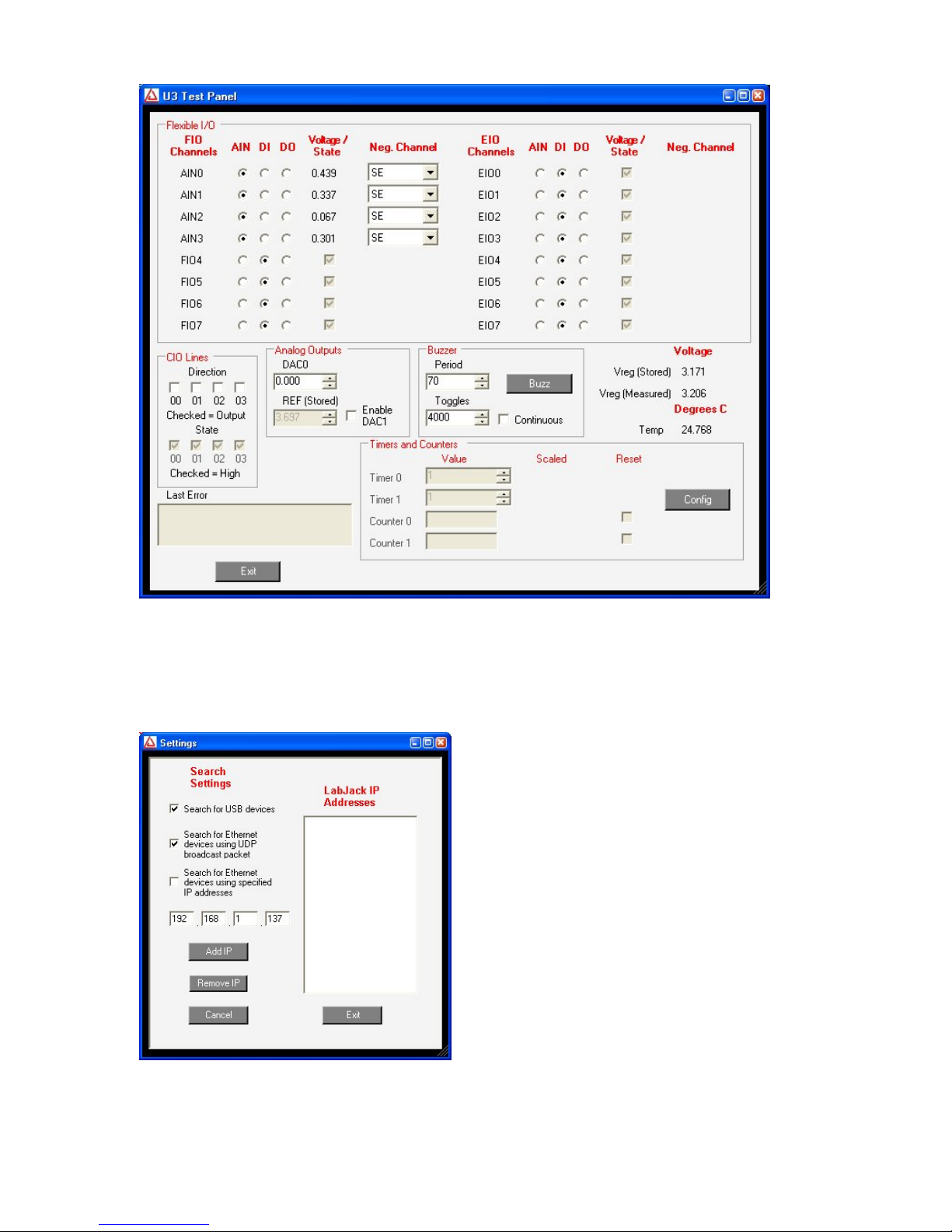

Figure 1-3 shows the U3 test window. This window continuously (once per second) writes to

and reads from the selected LabJack.

8

Page 9

Figure 1-3. LJControlPanel U3 Test Window

Selecting Options=>Settings from the main LJControlPanel menu brings up the window shown

in Figure 1-4. This window allows some features to of the LJControlPanel application to be

customized.

Figure 1-4. LJControlPanel Settings Window

9

Page 10

• Search for USB devices: If selected, LJControlPanel will include USB when searching

for devices.

• Search for Ethernet devices using UDP broadcast packet: Does not apply to the U3.

• Search for Ethernet devices using specified IP addresses: Does not apply to the U3.

1.2 Self-Upgrade Application (LJSelfUpgrade)

The processor in the U3 has field upgradeable flash memory. The self-upgrade application

shown in Figure 1-5 programs the latest firmware onto the processor.

USB is the only interface on the U3, and first found is the only option for self-upgrading the U3,

so no changes are needed in the “Connect by:” box. There must only be one U3 connected to

the PC when running LJSelfUpgrade.

Click on “Get Version Numbers”, to find out the current firmware versions on the device. Then

use the provided Internet link to go to labjack.com and check for more recent firmware.

Download firmware files to the …\LabJack\LJSelfUpgrade\upgradefiles\ directory.

Click the Browse button and select the upgrade file to program. Click the Program button to

begin the self-upgrade process.

Figure 1-5. Self-Upgrade Application

If problems are encountered during programming, try the following:

1. Unplug the U3, wait 5 seconds then reconnect the U3. Click OK then press

program again.

10

Page 11

2. If step 1 does not fix the problem unplug the U3 and watch the LED while

plugging the U3 back in. Follow the following steps based on the LED's activity.

a. If the LED is blinking continuously, connect a jumper between FIO0

and SCL then unplug the U3, wait 5 seconds and plug the U3 back in.

b. If the LED blinks several times and stays on, connect a jumper

between FIO1 and SCL then unplug the U3, wait 5 seconds and plug the

U3 back in.

c. If the LED blinks several times and stays off, the U3 is not

enumerating. Please restart your computer and try to program again.

d. If there is no LED activity, connect a jumper between FIO1 and SCL

then unplug the U3, wait 5 seconds and plug the U3 back in. If the LED is

blinking continuously click OK and program again. If the LED does not

blink connect a jumper between FIO0 and SCL then unplug the U3, wait 5

seconds and plug the U3 back in.

3. If there is no activity from the U3's LED after following the above steps, please

contact support.

11

Page 12

2. Hardware Description

The U3 has 3 different I/O areas:

• Communication Edge,

• Screw Terminal Edge,

• DB Edge.

The communication edge has a USB type B connector (with black cable connected in Figure 2-

1). All power and communication is handled by the USB interface.

The screw terminal edge has convenient connections for the analog outputs and 8 flexible I/O

(digital I/O, analog inputs, timers, or counters). The screw terminals are arranged in blocks of 4,

with each block consisting of Vs, GND, and two I/O. There is also a status LED located on the

left edge.

The DB Edge has a D-sub type connectors called DB15 which has the 8 EIO lines and 4 CIO

lines. The EIO lines are flexible like the FIO lines, while the CIO are dedicated digital I/O.

Figure 2-1. LabJack U3

2.1 USB

The U3 has a full-speed USB connection compatible with USB version 1.1 or 2.0. This

connection provides communication and power (Vusb). USB ground is connected to the U3

ground (GND), and USB ground is generally the same as the ground of the PC chassis and AC

mains.

The details of the U3 USB interface are handled by the high level drivers (Windows LabJackUD

DLL), so the following information is really only needed when developing low-level drivers.

12

Page 13

The USB interface consists of the normal bidirectional control endpoint 0 and two bidirectional

bulk endpoints: Endpoint 1 and Endpoint 2. Endpoint 1 consists of a 128 byte OUT endpoint

and a 128 byte IN endpoint. Endpoint 2 consists of a 0 byte OUT endpoint and a 256 byte IN

endpoint. Endpoint 2 OUT is not supported by the firmware, and should never be used.

All commands should always be sent on Endpoint 1, and the responses to commands will also

always be on Endpoint 1. Endpoint 2 is only used to send stream data from the U3 to the host.

2.2 Status LED

There is a green status LED on the LabJack U3. This LED blinks on reset, and then remains

steadily lit.

2.3 GND and SGND

The GND connections available at the screw-terminals and DB connectors provide a common

ground for all LabJack functions. This ground is the same as the ground line on the USB

connection, which is often the same as ground on the PC chassis and therefore AC mains

ground.

SGND is located on the screw terminal block with SDA and SCL. This terminal has a selfresetting thermal fuse in series with GND. This is often a good terminal to use when connecting

the ground from another separately powered system that could unknowingly already share a

common ground with the U3.

See the AIN, DAC, and Digital I/O Sections for more information about grounding.

2.4 Vs

The Vs terminals are designed as outputs for the internal supply voltage (nominally 5 volts).

This will be the voltage provided from the USB cable. The Vs connections are outputs, not

inputs. Do not connect a power source to Vs in normal situations. All Vs terminals are the

same.

2.5 Flexible I/O (FIO/EIO)

The first 16 I/O lines (FIO and EIO ports) on the LabJack U3 can be individually configured as

digital input, digital output, or analog input. In addition, up to 2 of these lines can be configured

as timers, and up to 2 of these lines can be configured as counters. If a line is configured as

analog, it is called AINx according to the following table:

AIN0 FIO0 AIN8 EIO0

AIN1 FIO1 AIN9 EIO1

AIN2 FIO2 AIN10 EIO2

AIN3 FIO3 AIN11 EIO3

AIN4 FIO4 AIN12 EIO4

AIN5 FIO5 AIN13 EIO5

AIN6 FIO6 AIN14 EIO6

AIN7 FIO7 AIN15 EIO7

Table 2-1. Analog Input Pin Locations

13

Page 14

Timers and counters can appear on various pins, but other I/O lines never move. For example,

Timer1 can appear anywhere from FIO0 to EIO1, depending on TimerCounterPinOffset and

whether Timer0 is enabled. On the other hand, FIO5 (for example), is always on the screw

terminal labeled FIO5, and AIN5 (if enabled) is always on that same screw terminal.

The first 8 flexible I/O lines (FIO0-FIO7) appear on built-in screw terminals. The other 8 flexible

I/O lines (EIO0-EIO7) are available on the DB15 connector.

Many software applications will need to initialize the flexible I/O to a known pin configuration.

That requires calls to the low-level functions ConfigIO and ConfigTimerClock. Following are the

values to set the pin configuration to the factory default state:

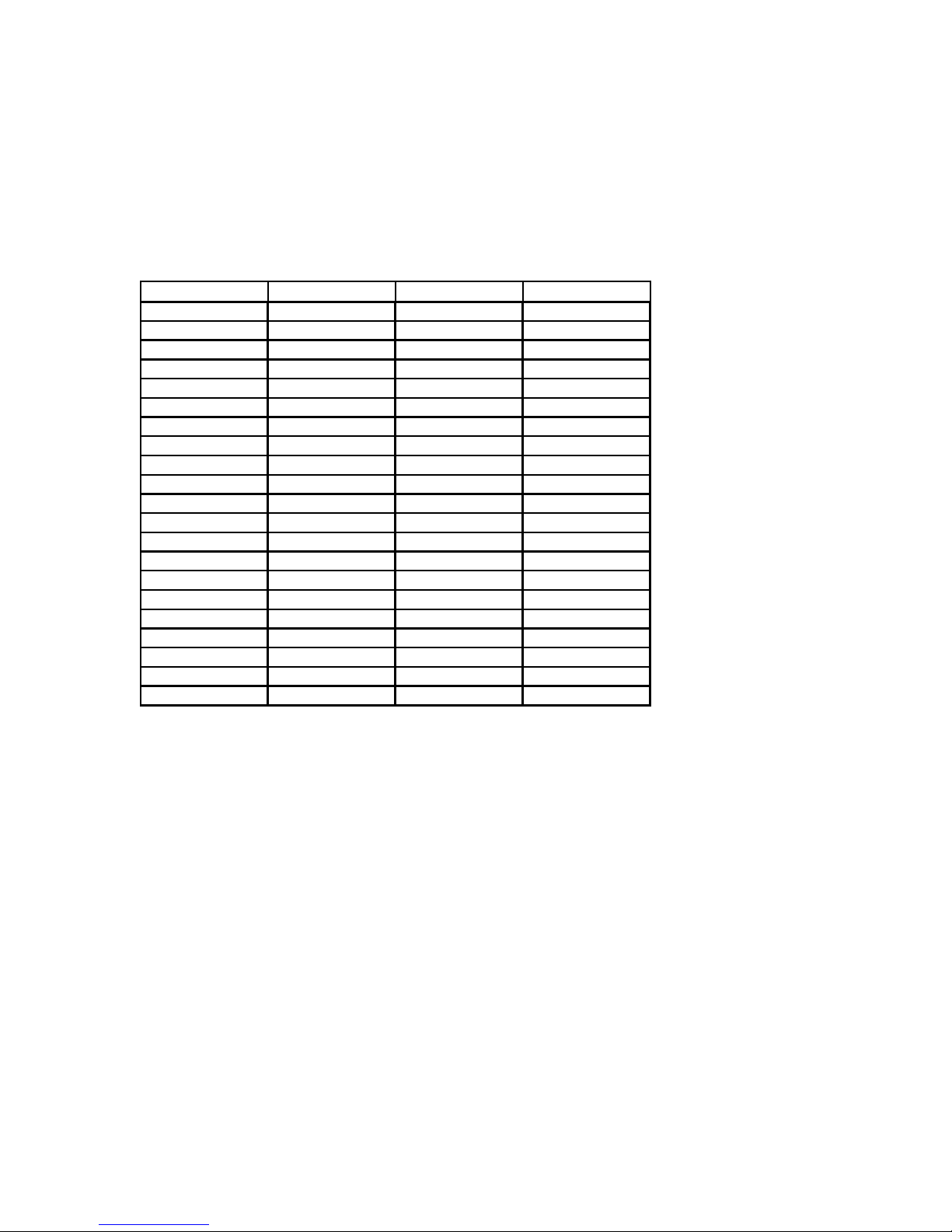

Byte #

6 WriteMask 15 Write all parameters.

8 TimerCounterConfig 0 No timers/counters. Offset=0.

9 DAC1Enable 0 DAC1 disabled.

10 FIOAnalog 0 FIO all digital.

11 EIOAnalog 0 EIO all digital.

able 2-2. ConfigIO Factory Default Values

T

Byte #

8 TimerClockConfig 130 Set clock to 48 MHz.

9 TimerClockDivisor 0 Divisor = 0.

T

able 2-3. ConfigTimerClock Factory Default Values

hen using the high-level LabJackUD driver, this could be done with requests to the following

W

IOTypes:

Put (lngHandle, LJ_ioPUT_CONFIG, LJ_chNUMBER_TIMERS_ENABLED, 0, 0);

e

ePut (lngHandle, LJ_ioPUT_CONFIG, LJ_chTIMER_COUNTER_PIN_OFFSET, 0, 0)

ePut (lngHandle, LJ_ioPUT_CONFIG, LJ_chTIMER_CLOCK_BASE, LJ_tc48MHZ, 0);

ePut (lngHandle, LJ_ioPUT_CONFIG, LJ_chTIMER_CLOCK_DIVISOR, 0, 0);

ePut (lngHandle, LJ_ioPUT_COUNTER_ENABLE, 0, 0, 0);

ePut (lngHandle, LJ_ioPUT_COUNTER_ENABLE, 1, 0, 0);

ePut (lngHandle, LJ_ioPUT_DAC_ENABLE, 1, 0, 0);

16);

ePut (lngHandle, LJ_ioPUT_ANALOG_ENABLE_PORT, 0,

0,

;

or with a single request to the following IOType created exactly for this purpose:

…

Put (lngHandle, LJ_ioPIN_CONFIGURATION_RESET, 0, 0, 0);

e

2.6 AIN

The LabJac

EIO0-EIO7). Single-ended measurements can be taken of any line compared to ground, or

differential measurements can be taken of any line to any other line.

A

nalog input resolution is 12-bits. The range of single-ended analog inputs is typically 0-2.44 or

0-3.6 volts, and the range of differential analog inputs is typically +/- 2.4 volts. The differential

input range is pseudobipolar, not true bipolar, as for valid measurements the voltage on every

analog input pin, with respect to ground, must be within -0.3 to +3.6 volts. See Appendix A for

voltage limits to avoid damage.

k U3 has up to 16 analog inputs available on the flexible I/O lines (FIO0-FIO7 and

14

Page 15

The analog inputs have a QuickS

e

xpense of increased noise. This is enabled by passing a nonzero value for put_config special

channel

LJ_chAIN_RESOLUTION. There is also a LongSettling option where additional settling

ample option where each conversion is done faster at the

time is added between the internal mulitplexer configuration and the analog to digital

conversion. This allows signals with more source impedance, and is enabled by passing a

nonzero value for put_config special channel

LJ_chAIN_SETTLING_TIME. Both of these

options

are disabled by default.

.6.1 Channel Numbers

2

The LabJack U3 has up to 16 ex

level functions specify a positive

ternal analog inputs, plus a few internal channels. The low-

and negative channel for each analog input conversion. With

the LabJackUD driver, the IOType LJ_ioGET_AIN is used for single-ended channels only, and

thus the negative channel is set to 31. There is an additional IOType called

LJ_ioGET_AIN_DIFF

that allows the user to specify the positive and negative channel.

Positive Channel #

0-7 AIN0-AIN7 (FIO0-FIO7)

8-15 AIN8-AIN15 (EIO0-EIO7)

30 Temp Sensor

31 Vreg

Table 2-4. Positive Channel Numbers

Channel 31 puts the internal Vreg (~3

2

.6.4 for information about the internal temperature sensor.

.3 volts) on the positive input of the ADC. See Section

Negative Channel #

0-7 AIN0-AIN7 (FIO0-FIO7)

8-15 AIN8-AIN15 (EIO0-EIO7)

30 Vref

31 Single-Ended

32 Special 0-3.6 (UD Only)

Table 2-5. Negative Channel Numbers

If the negative channel is set to anythin

re

turns a pseudobipolar value. If the negative channel is set to 31, the U3 does a single-ended

g besides 31, the U3 does a differential conversion and

conversion returns a unipolar value. Channel 30 puts the internal voltage reference Vref (~2.44

volts) on the negative input of the ADC.

Channel 32 is a special negative channe

d

river will actually pass 30 as the negative channel to the U3, and when the result is returned

the driver adds Vref to the value. This results is a full span on the positive channel of about 0

l supported by the LabJack driver. When used, the

to

4.88 volts (versus ground), but since the voltage on any analog input cannot exceed 3.6 volts,

only 75% of the converters range is used and the span is about 0 to 3.6 volts.

.6.2 Converting Binary Readings to Voltages

2

Following are the nominal input voltage ranges for the analog inputs, assuming that DAC1 is not

enabled.

15

Page 16

Max V Min V

Single-Ended 2.44 0.0

Differential 2.44 -2.44

Special 0-3.6 3.6 0.0

Table 2-6. Nominal Analog Input Voltage Ranges (DAC1 Disabled)

Note that the minimum

can be as

much as 2.44 volts less than the negative channel, not that a channel can measure

2.44 volts less than ground. The voltage of any analog input pin, c

in

the range -0.3 to +3.6 volts.

differential input voltage of -2.44 volts means that the positive channel

ompared to ground, must be

The “Special 0-3.6” range is obtained by doing a differential measurement where the negative

channel is set to the internal Vref (2.44 volts).

A

lthough the binary readings ha

ve 12-bit resolution, they are returned justified as 16-bit values,

so the approximate nominal conversion from binary to voltage is:

olts(uncalibrated) = (Bits/65536)*Span

V

(Single-Ended)

Volts(uncalibrated) = (Bits/65536)*Span – Span/2 (Differential)

Where span is the maximum voltage minus the minimum voltage fro

a

ctual nominal conversions are provided he s below, and sh

in t table ould be used if the actual

calibration constants are not read for some reason. Most applications wi

c

alibrations constants (Slope and Offset) stored in the internal flash.

m the table above. The

ll use the actual

Volts = (Slope * Bits) + Offset

Since the U3 uses multiplexed channels connected to a single analog-to-digital converter

ADC), all channels have the same calibration for a given configuratio

(

n.

T

able 2-4 shows where the var

when communication is initiated with the U3, three calls will be made to the ReadMem func

to retrieve the first 3 blocks of memory. This information can then be used to convert all a

put readings to voltages. The high level Windows DLL (LabJackUD) do

in

ious calibration values are stored in the Mem area. Generally

tion

nalog

es this automatically.

Starting

Block #

0 0 AIN SE Slope 3.7231E-05 volts/bit

0 8 AIN SE Offset 0.0000E+00 volts

0 16 AIN Diff Slope 7.4463E-05 volts/bit

0 24 AIN Diff Offset -2.4400E+00 volts

1 0 DAC0 Slope 5.1717E+01 bits/volt

1 8 DAC0 Offset 0.0000E+00 bits

1 16 DAC1 Slope 5.1717E+01 bits/volt

1 24 DAC1 Offset 0.0000E+00 bits

2 0 Temp Slope 1.3021E-02 degK/bit

2 8 Vref @Cal 2.4400E+00 volts

2 16 Vref*1.5 @Cal 3.6600E+00 volts

2 24 Vreg @Cal 3.3000E+00 volts

Byte Nominal Value

Table 2-7. Calibration Constant Memory Locations

16

Page 17

Each value in Table 2.4 is stored in 64-bit fixed point format (signed 32.32, little endian, 2’s

omplement). Following are some examples of fixed point byte arrays and the associated

c

floating point double values.

Fixed Point B

{0,0,0,0,0,0,0,0} 0.0000000000

{0,0,0,0,1,0,0,0} 1.0000000000

{0,0,0,0,255,255,255,255} -1.0000000000

{51,51,51,51,0,0,0,0} 0.2000000000

{205,204,204,204,255,255,255,255} -0.2000000000

{73,20,5,0,0,0,0,0} 0.0000775030

{225,122,20,110,2,0,0,0} 2.4300000000

{102,102,102,38,42,1,0,0} 298.1500000000

Table 2-8. Fixed Point Conversion Examples

yte Array

(LSB, …, MSB)

Floating Point Double

.6.2.1 Analog Inputs With DAC1 Enabled

2

he previous information assumed that DAC1 is disabled. If DAC1 is enabled, then the internal

T

reference (Vref = 2.44 volts) is not available for the

ADC, and instead the internal regulator

voltage (Vreg = 3.3 volts) is used as the reference for the ADC. Vreg is not as stable as Vref,

but more stable than Vs (5 volt power supply). Following are the nominal input voltage ranges

for the analog inputs, assuming that DAC1 is enabled.

Max V Min V

Sin

gle-Ended 3.3 0.0

ferential 3.3 -3.3

Dif

Special 0-3.6 3.6 0.0

Table 2-9. Nominal Analog Input

Voltage Ranges (DAC1 Enabled)

Note that the minimum differential input voltage of -3.3 volts mean

an be as much as 3.3 volts less than the negative channel, not that a channel can measure 3.3

c

volts less than ground. The voltage of any analog input pin, compared to ground, must be in t

s that the positive channel

he

range -0.3 to +3.6 volts, for specified performance. See Appendix A for voltage limits to avoid

damage.

The “Special 0-3.6” range is obtained by doing a differential measurement where the negative

c

hannel is

set to the ADC reference, which with DAC1 enabled is Vreg. This results is a full

span on the positive channel of about 0 to 6.6 volts (versus ground), but since the voltage on

any analog input cannot exceed 3.6 volts, only 55% of the converters range is used and the

span is about 0 to 3.6 volts.

When DAC1 is enabled, the slope/offset calibration constants are not used to convert raw

r

eadings to voltages. Rather

, the Vreg value is retrieved from the Mem area, and used with the

approximate single-ended or differential conversion equations above, where Span is Vreg

(single-ended) or 2Vreg (differential).

.6.3 Typical Analog Input Co2

nnections

A common question is “can this sensor/signal be measured with the U3”. Unless the signal has

a voltage (referred to U3 ground) beyond the limits in Appendix A, it can be connected without

17

Page 18

damaging the U3, but more thought is required to determine what is necessary to make useful

measurements with the U3 or any measurement device.

Voltage (versus ground): The single-ended analog inputs on the U3 measure a voltage with

respect to U3 ground. The differential inputs measure the voltage difference between two

hannels, but the voltage on each channel with respect to

c ground must still be within the

common mode limits specified in Appendix A. When measuring parameters other than voltag

or voltages too big or too small for the U3, some sort of sensor or transducer is required to

produce the proper voltage signal. Examples are a temperature sensor, amplifier, resistive

voltage divider, or perhaps a combination of such things.

Impedance: When connecting the U3, or any measuring device, to a signal source, it must b

considered what impact the measuring device will have on the signal. The main consideratio

whether the currents going into or out of the U3 analog in

is

errors due to the impedance of the source. To maintain consistent 12-bit results, it is

recommended to keep the source impedance less than 10 kΩ.

Resolution (and Accuracy): Based on the measurement type and resolution of the U3, the

resolution can be determined in terms of voltage or engineering units. For example, a

s

ome temperature sensor provides a 0-10 mV signal, correspon

Samples are then acquired with the U3 using the 0-2.44 volt single-ended input range, resu

in a voltage resolution of about 2.44/4096 = 596 μV. That means there will be about 17 discre

steps across the 10 mV span of the signal, and the temperature resolution is about 6 degrees

If this experiment required a resolution of 1 degrees C, this configuration would not be sufficient.

Accuracy will also need to be considered. Appendix A places some boundaries on expected

accuracy, but an in-system calibration can generally be done to provide absolute accuracy down

to the INL limits of the U3.

Speed: How fast does the signal need to be sampled? For instance, if the signal is a

waveform, what information is needed: peak, average, RMS, shape, frequency, … ? Answers

o these questions will help

t decide how many points are needed per waveform cycle, and thus

what sampling rate is required. In the case of multiple channels, the scan rate is also

considered. See Sections 3.1 and 3.2.

put will cause noticeable voltage

ssume

ding to 0-100 degrees C.

e,

e

n

lting

te

C.

2.6.3.1 Signal from the LabJack

ne example of measuring a signal from the U3 itself, is with O

3 share a common ground, so the voltage on an analog output (DAC) can be measured by

U

simply connecting a single wire from th

output must be set to a voltage within the range of the analog input.

at terminal to an AIN terminal (FIO/EIO). The analog

an analog output. All I/O on the

2.6.3.2 Unpowered isolated signal

n example of an unpowered isolated signal would be a photocell where A

ot shorted to any external voltages. Such a sensor typically has two leads, where the positive

n

lead connects to an AIN terminal and the

negative lead connects to a GND terminal.

the sensor leads are

2.6.3.3 Signal powered by the LabJack

typical example of this type of signal is a 3-wire temperature sensor. The sensor has a power A

nd ground wire that connect to Vs and GND on the LabJack, and then has a signal wire that

a

simply connects to an AI

N terminal.

18

Page 19

Another variation is a 4-wire sensor where there are two signal wires (positive and negative)

rather than one. If the negative signal is the same as power ground, or can be shorted ground,

then the positive signal can be connected to AIN and a single-ended measurement can be

made. A typical example where this

ensor, providing the raw bridge output (and no amplifier). In this case the signal voltage is the

s

difference between the positive and negative signal, and the negative signal cannot be shorte

does not work is a bridge type sensor, such as pressure

d

to ground. Such a signal could be measured using a differential input on the U3.

2.6.3.4 Signal powered externally

An example is a box with a wire coming out that is defined as a 0-5 volt analog signal and a

second wire labeled as ground. The signal is known to have 0-5 volts compared t

ire, but the complication is what is the voltage of the box ground compared to the LabJack

w

round.

g

o the ground

If the box is known to be electrically isolated from the LabJack, the box ground can simply be

connected to LabJack GND. An example would be if the box was plastic, powered by an

internal battery, and does not have any wires besides the signal and ground which are

connecte

d to AINx and GND on the LabJack.

If the box ground is known to be the same as the LabJack GND, then perhaps only the one

signal wire needs to be connected to the LabJack, but it generally does not hurt to go ahea

and connect the ground wire to LabJack GND with a 100 Ω resistor. You definitely do n

d

ot want

to connect the grounds without a resistor.

If little is known about the box ground, a DMM can be used to measure the voltage of box

ground compared to LabJack GND. As long as an extreme voltage is not measured, it is

generally OK to connect the box ground to LabJack GND, but it is a good idea to put in a 100 Ω

series resistor to prevent large currents fro

sistor (typically 1/8 or 1/4 watt) so that it blows if too much current does flow. The only

re

current that should flow on the ground is the return of the analog input bias current, which i

m flowing on the ground. Use a small wattage

s on

the order of … for the U3.

The SGND terminal (on the same terminal block as SDA/SCL) can be used instead of GND

for

externally powered signals. A series resistor is not needed as SGND is fused to prevent

overcurrent, but a resistor will eliminate confusion that can be caused if the fuse is tripping and

resetting.

In general, if there is uncertainty, a good approach is to use a DMM to measure the voltage on

each signal/ground wire without any connections to the U3. If no large voltages are noted

,

connect the ground to U3 SGND with a 100 Ω series resistor. Then again use the DMM to

measure th

e voltage of each signal wire before connecting to the U3.

Another good general rule is to use the minimum number of ground connections. For instance,

if connecting 8 sensors powered by the same external supply, or otherwise referred to the s

ame

external ground, only a single ground connection is needed to the U3. Perhaps the ground

leads from the 8 sensors would be twisted together, and then a single

a 100 Ω resistor which is connected to U3 ground.

to

wire would be connected

2.6.3.5 Amplifying small signal voltages

The best results are generally obtained when a signal voltage spans the full analog input range

of the LabJack. If the signal is too small it can be amp

lified before connecting to the LabJack.

19

Page 20

One good way to handle low-level signals such as thermocouples is the LJTick-InAmp, which is

2-channel instrumentation amplifier module that plugs into the U3 screw-terminals. Go to

a

labjack.com for more information.

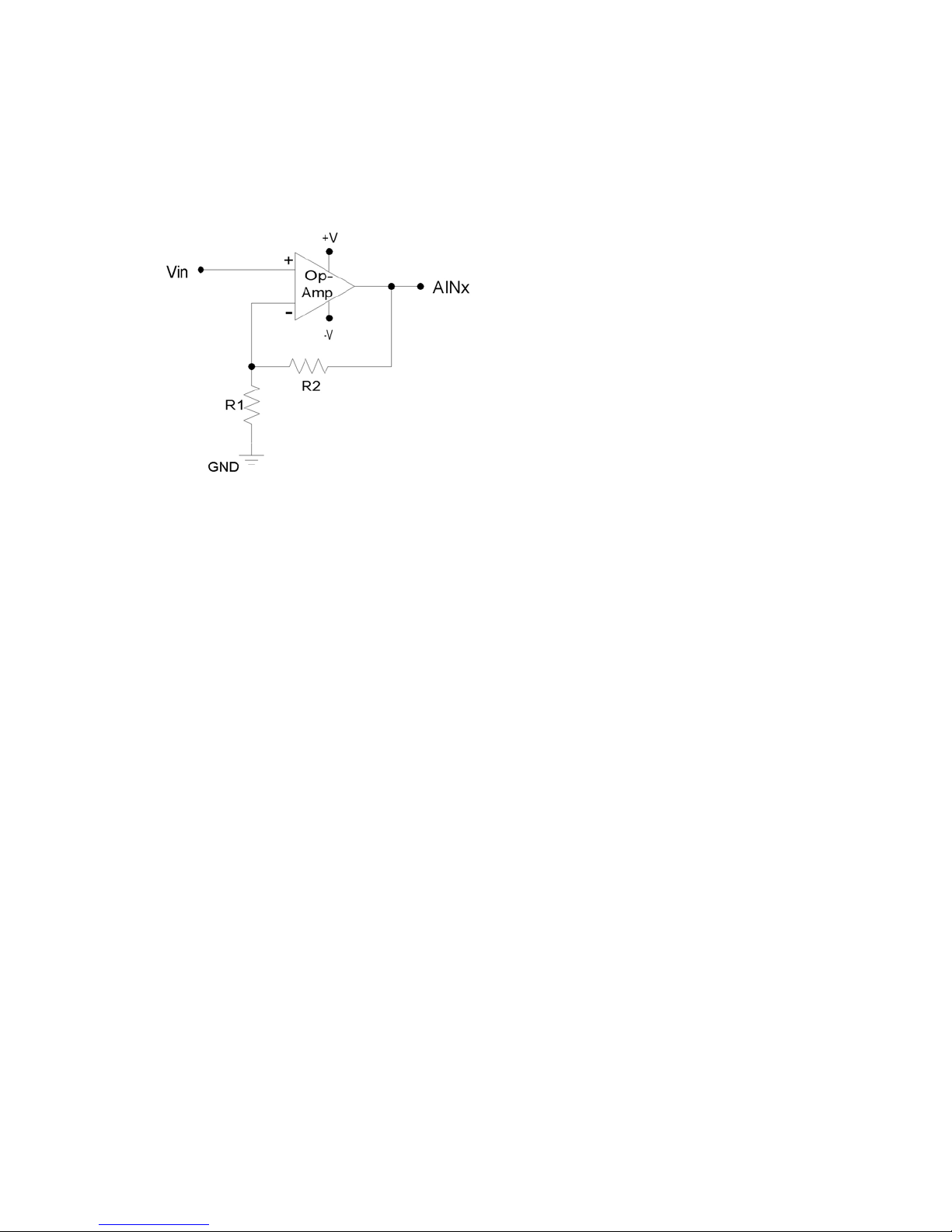

For a do-it-yourself solution, the following figure shows an operational amplifier (op-amp)

configured as non-inverting:

Figure 2-2. Non-Inverting Op-Amp Configuration

The gain of this configuration is:

Vout = Vin * (1 + (R2/R1))

00 kΩ is a typical value for R2. Note that if R2=0 (short-circuit) and R1=inf (not installed), a

1

simple buffer with a gain equal to

1 is the result.

There are numerous criteria

O

ne of the main criteria is that the op-amp can handle the input and output signal range. Often,

used to choose an op-amp from the thousands that are available.

a single-supply rail-to-rail input and output (RIRO) is used as it can be powered from Vs and

GND and pass signals within the range 0-Vs. Th

g

ood for many 5 volt applications.

e OPA344 from Texas Instruments (ti.com) is

The op-amp is used to amplify (and buffer) a signal that is referred to the same ground as the

LabJack (single-ended). If instead the signal is differential (i.e. there is a positive and negativ

e

signal both of which are different than ground), an instrumentation amplifier (in-amp) should be

used. An in-amp converts a differen

m

ethod to set gain.

tial signal to single-ended, and generally has a simple

2.6.3.6 Signal voltages beyond 0-2.44 volts (and resistance measurement)

The nominal maximum analog input voltage range for the U3 is 0-2.44 volts. The easiest w

handle larger voltage

d

ivider module that plugs into the U3 screw-terminals. More information is available at

la

bjack.com.

s is often by using the LJTick-Divider, which is a two channel buffered

The basic way to handle higher unipolar voltages is with a resistive voltage divider. The

following figure shows the resistive voltage divider assuming that the source voltage (Vin) is

referred to the same ground as the U3 (GND).

ay to

20

Page 21

Figure 2-3. Voltage Divider Circuit

The attenuation of this circuit is determined by the equation:

Vout = Vin * ( R2 / (R1+R2))

his divider is easily implemented by putting a resistor (R1) in series with the signal wire, and

T

placing a second resistor (R2) from the AIN terminal to a GND

nalog input performance, R1 should not exceed 10 kΩ, so R1 can generally be fixed at 10 kΩ

a

and R2 can be adjusted for th

ivide by 2.1, so a ~0-5 volt input will be scaled to the input range of the U3.

d

e desired attenuation. For instance, R2 = 9.1 kΩ provides a

terminal. To maintain specified

The divide by 2 configuration where R1 = R2 = 10 kΩ, presents a 20 kΩ load to the source,

meaning that a 5 volt signal will have to be able to source/sink up to

sources might require a load with higher resistance, in which case a buffer should be used.

following figure shows a resistive voltage divider followed by an op-amp confi

verting unity-gain (i.e. a buffer).

in

+250 µA. Some signal

The

gured as non-

Figure 2-4. Buffered Voltage Divider Circuit

The op-amp is chosen to have low input bias currents so that large resistors can be used in the

voltage divider. For 0-5 volt applications, where the amp will be powered from Vs and GND, a

good choice would be the OPA344 from Tex

small bias current that changes little across

th

e amp from Vs and GND, the input and output to the op-amp is limited to that range, so if Vs is

4.8 volts your signal range will be 0-4.8 volts.

The information above also applies to resistance measurement. A common way to measure

resistance is to build a voltage divider as shown in Figure 2-4, where one of the resistors is

known and the other is the unknown. If Vin is known and Vout is measured, the voltage divider

equation can be rearranged to solve for the unk

21

as Instruments (ti.com). The OPA344 has a very

the entire voltage range. Note that when powering

nown resistance.

Page 22

2.6.3.7 Measuring current (including 4-20 mA) with a resistive shunt

The following figure shows a typical method to measure the current through a load, or to

m

easure the 4-20 mA signal produced by a 2-wire (loop-powered) current loop sensor. The

urrent shunt shown in the figure is simply a resistor.

c

Figure 2-5. Current Measurement With Arbitrary Load or 2-Wire 4-20 mA Sensor

When measuring a 4-20 mA signal, a typical value for the shunt would be 120 Ω. This results in

a 0.48 to 2.40 volt signal corresponding to 4-20 mA. The external supply must p

voltage for the sensor and the shunt, so if the sensor requires 5 volts the supply

le

ast 7.4 volts.

For applications besides 4-20 mA, the shunt is chosen based on the maximum current and how

much voltage drop can be tolerated across the shunt. For instance, if the maximum current is

1.0 amp, and 1.

Ω

resistor could be used. That equates to 1.0 watts, though, which would require a special high

0 volts of drop is the most that can be tolerated without affecting the load, a 1.0

wattage resistor. A better solution would be to use a 0.1 Ω shunt, and then use an amplifier to

increase the small voltage produced by that shunt. If the maximum current to measure is too

high (e.g. 100 amps), it will be difficult to find a small enough resistor and a hall-effect sensor

should be considered instead of a shunt.

The following figure shows typical connections for a 3-wire 4-20 mA sensor. A typical value fo

the shunt would be 120 Ω which results in 0.48 to 2.40 volts.

rovide enough

must provide at

r

Figure 2-6. Current Measurement With 3-Wire 4-20 mA (Sourcing) Sensor

The sensor shown in Figure 2-6 is a sourcing type, where the signal sources the 4-20 mA

current which is then sent through the shunt resistor and sunk into ground. Another type of 3wire sensor is the sinking type, where the 4-20 mA current is sourced from

sent through the shunt resistor, and then sunk into the signal wire. If sen

connected to U3 ground, the sinking type of sensor presents a problem, as at least one sid

the resistor has a high common mode voltage (equal to the positive sensor supply). If the

sensor is isolated, a possible solution is to connect the sensor signal or positive sensor supply

22

the positive supply,

sor ground is

e of

Page 23

to U3 ground (instead of sensor ground). This requires a good understanding of ground

isolation in the system. The LJTick-CurrentShunt is often a simple solution.

Both Figure 2-5 and 2-6 show a 0-100 Ω resistor in series with SGND, which is discussed in

general in Section 2.6.3.4. In this case, if SGND is used (rather than GND), a direct connection

(0 Ω) should be good.

The best way to handle 4-20 mA signals is with the LJTick-CurrentShunt, which is a two chan

active current to voltage converter module that plugs into the U3 screw-terminals. More

information is available

at labjack.com.

ing and

nel

2.6.3.8 Floating/Unconnected Inputs

The reading from a floating (no external

p

redict and is likely to vary with sample timing and adjacent sampled channels. Keep in mind

th

at a floating channel is not at 0 volts, but rather is at an undefined voltage. In order to see 0

volts, a 0 volt signal (such as GND) should

Some data acquisition devices use a resistor, from the input to ground, to bias an unconnected

input to read 0. This is often just for "cosmetic" reasons so that the input reads close to 0 with

floating inputs, and a reason not to do that is that this resistor can degr

o

f the analog input.

In a situation where it is desired that a floating channel read a particular voltage, say to detect a

broken wire, a resistor can be placed from the AINx screw terminal to the desired voltage (GND,

VS, DACx, ...). A 10

d

esired voltage, but obviously degrades the input impedance to 100 kΩ. For the specific case

of pulling a floating channel to 0 volts, a 1 MΩ resistor to GND can typically be used to provide

analog input readings of less than 50 mV.

0 kΩ resistor should pull the analog input readings to within 50 mV of any

connection) analog input channel can be tough to

be connected to the input.

ade the input impedance

2.6.4 Internal Temperature Sensor

he U3 has an internal temperature sensorT

in

side the U3, which is warmer than ambient, it has been calibrated to read actual ambient

temperature. For accurate measurements th

relative to the ambient temperature, which ca

obtained in still air in an environment with slowly changing ambient temperatures.

With the UD driver, the internal temperature sensor is read by acquiring single-ended analo

input channel 30, and returns degrees K.

. Although this sensor measures the temperature

e temperature of the entire U3 must stabilize

n take on the order of 1 hour. Best results will be

g

2.7 DAC

he LabJack U3 has 1 or 2 analog outputsT

te

rminals. Each analog output can be set to a voltage between about 0.04 and 4.95 volts with

8-bits of reso

The second analog output is only available in certain configurations. In particular, if the analog

inputs are using the internal 2.4 volt reference (the most accurate option), then DAC1 outputs a

fixed voltage of 1.5*Vref. If DAC1 is enabled, the analog inputs use Vreg (3.3 volts) as the A

re

ference, which is not as stable as the internal 2.4 volt reference.

lution. The maximum output voltage is limited by the supply voltage to the U3.

(DAC0 and DAC1) that are available on the screw

DC

23

Page 24

The DAC outputs are derived as a percentage of Vreg, and then amplified by 1.5, so any

changes in Vreg will have a proportionate affect on the DAC outputs. Vreg is more stable than

Vs (5 volt supply voltage), as it is the output from a 3.3 volt regulator.

The DACs are derived from PWM signals that are affected by the timer clock frequency (Section

2.x). The default timer clock frequency of the U3 is set to 24 MHz, as this results in the

minimum DAC output noise. If the frequency is lowered, the DACs will have more noise, where

the frequency of the noise is the timer clock frequency divided by 2

8

.

The analog outputs have filters with a 3 dB cutoff around 16 Hz, limiting the frequency of output

waveforms to less than that.

The analog output commands are sent as raw binary values (low leve

o

utput voltage, the binary value can be approximated as:

l functions). For a desired

Bits(uncalibrated) = (Volts/4.9

5)*256

For a proper calculation, though, use the calibration values (Slope and Offset) stored in the

internal flash on the processor (Table 2-7):

Bits = (Slope * Volts) + Offset

The analog outputs can withstand a continuous short-circuit to ground, even when set at

maximum output.

Voltage should never be applie

In

the event that a voltage is accidentally applied to either analog output, they do have

d to the analog outputs, as they are voltage sources themselves.

protection against transient events such as ESD (electrostatic discharge) and continuous

overvoltage (or unde

rvoltage) of a few volts.

2.7.1 Typical Analog Output Connections

.7.1.1 High Current Output 2

T

he DACs on the U3 can output quite a bit of current, but have 50 Ω of source impedance that

will cause voltage drop. To avoid this voltage drop, an

such as the non-inverting configuration shown in Figu

b

etween the DAC output and the amp input for further noise reduction. Note that the ability of

the amp to source/sink current ne

ar the power rails must still be considered. A possible op-amp

choice would be the TLV246x family (ti.com).

2.7.1.2 Different Output Ranges

The typical output range of the DACs is about 0.04 to 4.95 volts. For other unipolar ranges, an

op-amp in the non-inverting configuration (Figure 2-3) can be used to provide the desired gain.

For example, to increase the maximum output

re

quired. If R2 (in Figure 2-3) is chosen as 100 kΩ, then an R1 of 97.6 kΩ is the closest 1%

resistor that provides a gain greater th

an 2.02. The +V supply for the op-amp would have to be

greater than 10 volts.

For bipolar output ranges, such as

±10 volts, a similar op-amp circuit can be used to provide

gain and offset, but of course the op-amp must be powered with supplies greater than the

desired output range (depending on the ability of the op-amp to drive it’s outputs close to the

from 4.95 volts to 10.0 volts, a gain of 2.02 is

op-amp can be used to buffer the output,

re 2-2. A simple RC filter can be added

24

Page 25

power rails). If

amp (linear.com), which can handle a supply span up to 44 volts.

A reference voltage is also required to provide the offset. In the following circuit, DAC1 is use

to provide a reference voltage. The actual value of DAC1 can be adjusted such that the circu

output is 0 volts at the DAC0 mid-scale voltage, and the value of R

d

esired gain. A fixed reference (such as 2.5 volts) could also be used instead of DAC1.

Figure 2-7. ±10 Volt DAC Output Circuit

±10, ±12, or ±15 volt supplies are available, consider using the LT1490A op-

1 can be adjusted to get the

d

it

A two-point calibration should be done to determine the exact input/output relationship of this

circuit. Ref to application note SLOA097 from ti.com for further information about gain and

offset design with op-amps.

er

2.8 Digital I/O

The LabJack U3 has up to 20 digital I/O channels. 16 are available from the flexible I/O lines,

and 4 dedicated digital I/O (C

can be individually config

logic and are 5 volt t

The LabJackUD driver uses the following bit numbers to specify all the digital lines:

0-7 FIO0-FIO7

8

-15 EIO0-EIO7

16-19 CIO0-CIO3

The 8 FIO lines app

only on the DB15 co

A

ll the digital I/O include an internal series resistor that provides overvoltage/short-circuit

protection. These series resistors also limit the ability of these lines to sink or source current.

Refer to the specifications in Appendix A.

All digital I/O on the U3 have 3 possible states: input, output-high, or output-low. Each bit

can be configured individually. When configured as an input, a bit has a ~100 kΩ pull-up

resistor to 3.3 volts (all digital I/O are 5 volt

c

onnected to the internal 3.3 volt supply (through a series resistor). When configured as output-

low, a bit is connected to GND (through a series resistor).

olerant.

ear on the built-in screw-terminals, while the 8 EIO and 4 CIO lines appear

nnector. See the DB15 Section of this User’s Guide for more information.

IO0-CIO3) are available on the DB15 connector. Each digital line

ured as input, output-high, or output-low. The digital I/O use 3.3 volt

of I/O

tolerant). When configured as output-high, a bit is

25

Page 26

The power-up condition of the digital I/O can be configured by the user. From the factory,

all

digital I/O are configured to power-up as inputs. Note that even if the power-up default for a lin

is changed to output-high or output-low, there is a delay of about xxx ms at power-up where all

digital I/O are in the factory default condition.

The low-level Feedback function (Section 5.2.5) writes and reads all digital I/O. For informatio

about using digital I/O under the Windows LabJackUD driver, see Section 4.3.5. See Section

3.1 for timing information.

M

any function parameters contain specific bits within a single integer parameter to write/read

specific information. In particular, most digital I/O parameters contain the information for each

bit of I/O in one integer, where each bit of I/O corresponds to the same bit in the parameter (e.g

the direction of FIO0 is set

C

onfigU3, the parameter FIODirection is a single byte (8 bits) that writes/reads the power-up

in bit 0 of parameter FIODir). For instance, in the low-level function

direction of each of the 8 FIO lines:

• if FIODirection is 0, all FIO lines are input,

0

• if FIODirection is 1 (2

• if FIODirection is 5 (2

• if FIODirection is 255 (2

), FIO0 is output, FIO1-FIO7 are input,

0

+ 22), FIO0 and FIO2 are output, all other FIO lines are input,

0

+ …

7

), FIO0-FIO7 are output.

+ 2

e

n

.

2.8

.1 Typical Digital I/O Connections

.8 1

2T.1. Input: Driven Signals

he most basic connection to a U3 digital input is a driven signal, often called push-pull. With a

push-pull signal the source is typically providing

logic low. This signal is generally connected dir

v

oltage specifications in Appendix A. If the signal is over 5 volts, it can still be connected with a

series resistor. The digital inputs h

ave protective devices that clamp the voltage at GND and

a high voltage for logic high and zero volts for

ectly to the U3 digital input, considering the

VS, so the series resistor is used to limit the current through these protective devices. For

instance, if a 24 volt signal is connected through a 10 kΩ series resistor, about 19 volts will be

dropped across the resistor, resulting in a current of 1.9 mA, which is no problem for the U3.

The other possible consideration with the basic push-pull signal is the ground connection. If th

signal is known to already have a common ground with the U3, then no additional ground

connection is used. If the signal is known to not have a common ground with the U3, then the

signal ground can simply be connected to U3 GND. If there is uncertainty about the relations

b

etween signal ground and U3 ground (e.g. possible common ground through AC mains), then

a ground connection with a ~10 Ω series resistor is generally recommended (see Section

2.7.3.4).

e

hip

Figure 2-8. Driven Signal Connection To Digital Input

26

Page 27

Figure 2-8 shows typical connections. Rground is typically 0-100 Ω. Rseries is typically 0 Ω

(short-circuit) for 3.3/5 volt logic, or 10 kΩ for high-voltage logic. Note that an individual ground

connection is often not needed for every signal. Any signals powered by the same external

supply, or otherwise referred to the same external ground, should share a single ground

connection to the U3 if possible.

When dealing with a new sensor, a push-pull signal is often incorrectly assumed when in fact

the sensor provides an open-collector signal as described ne

xt.

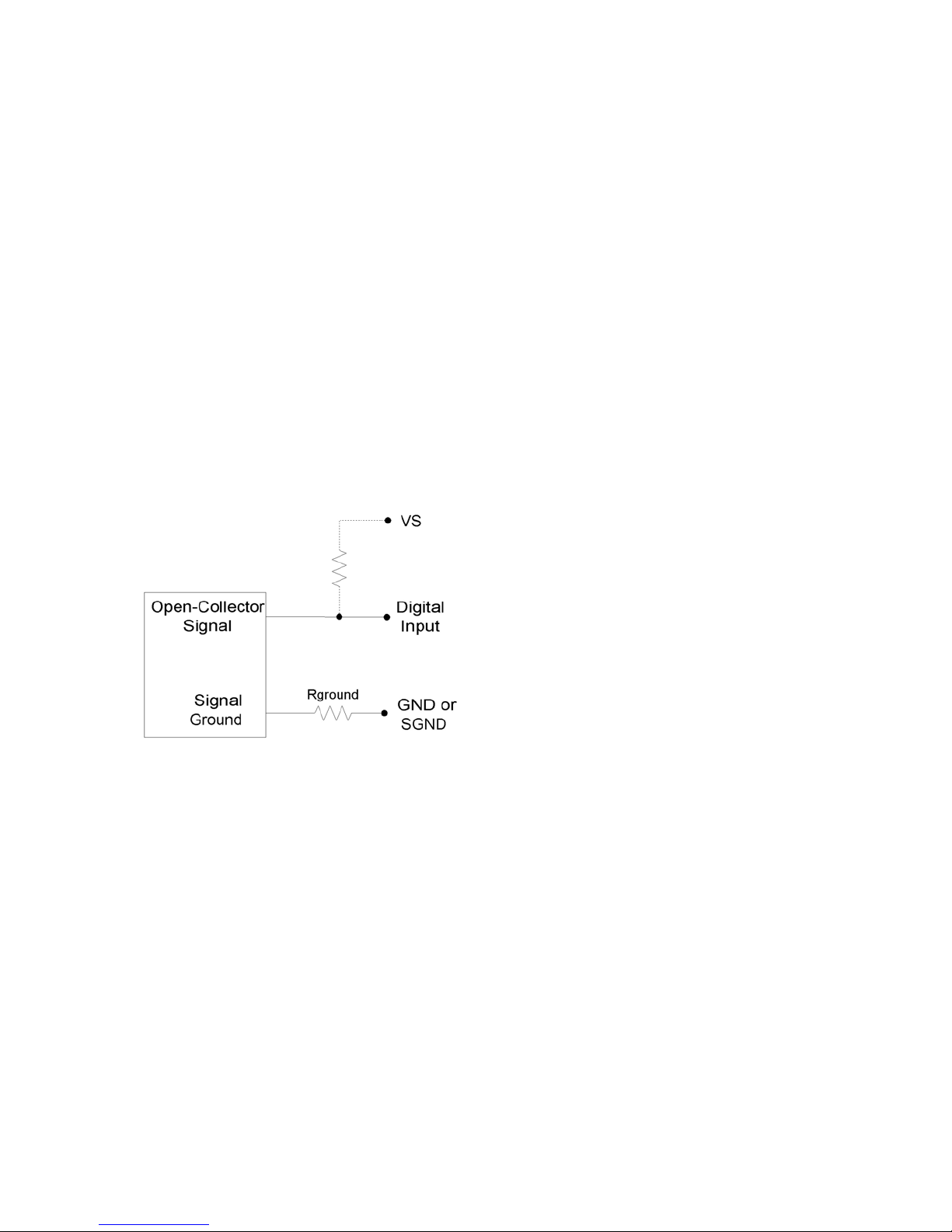

.8.1.2 Input: Open-Collector Signals

2

Open-collector (also called open-drain) is a very common type of digital signal. Rather than

providing 5 volts and ground, like the push-pull signal, an open-collector signal provides ground

and high-impedance. This type of signal can be thought of as a switch connected to ground.

Since the U3 digital inputs have a 100 kΩ internal pull-up resistor, an open-collector signa

generally be connected directly to

oltage and the pull-up resistor pulls the digital input to logic high. When the signal is active, it

v

the input. When the signal is inactive, it is not driving any

drives 0 volts which overpowers the pull-up and pulls the digital input to logic low. Sometimes,

an external pull-up (e.g. 4.7 kΩ from Vs to digital input) will be ins

nd speed of the logic high condition.

a

talled to increase the strength

l can

Figure 2-9. Driven Signal Connection To Digital Input

Figure 2-10 shows typical connections. Rground is typically 0-100 Ω, and the external pull-up

resistor is generally not required. Note that an individual ground connection is often not needed

for every signal. Any signals powered by the same external supply, or otherwise referred to the

same external ground, should share a single ground connection to the U3 if possible.

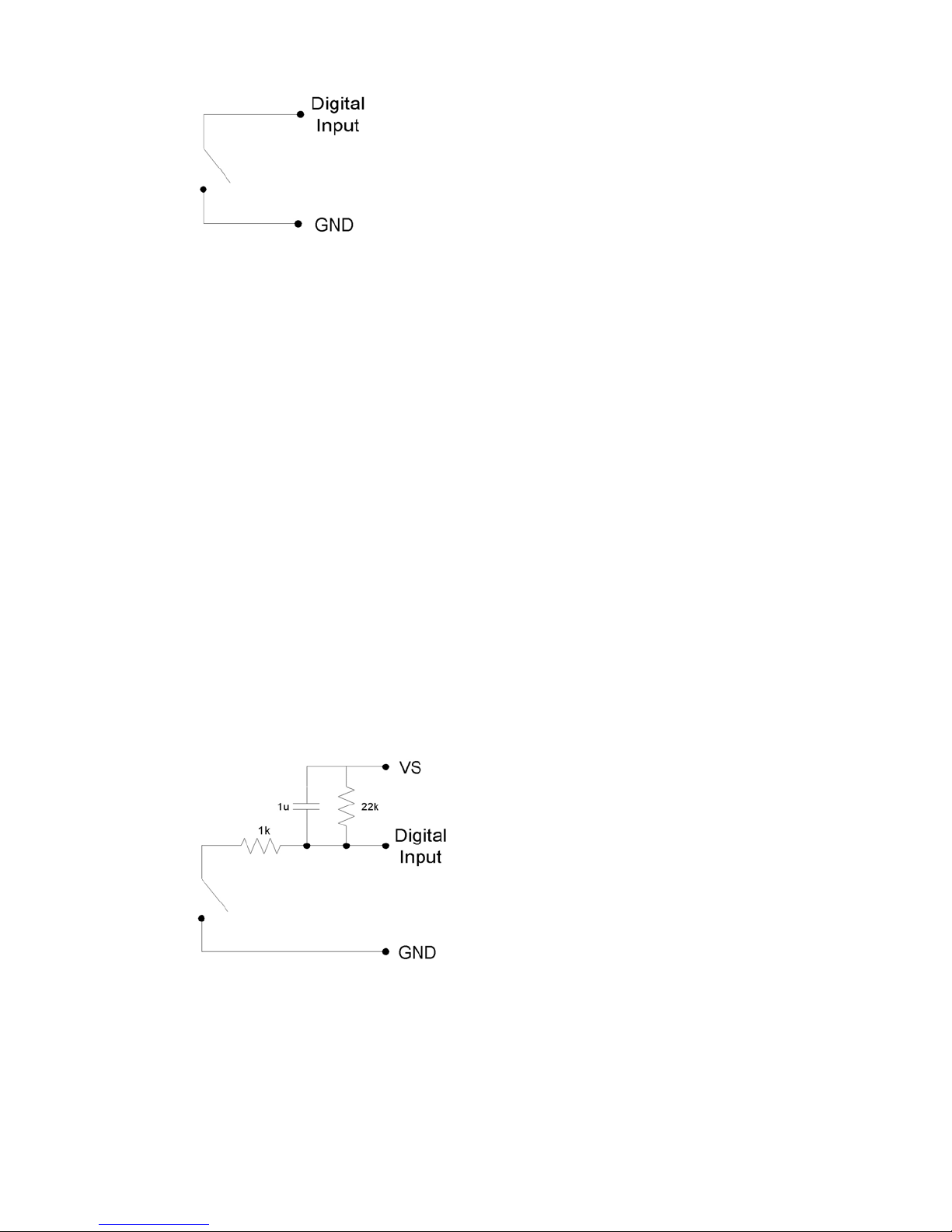

2.8.1.3 Input: Mechanical Switch Closure

To detect whether a mechanical switch is open or closed,

ground and the other side to a digital input. The beha

escribed above.

d

27

connect one side of the switch to U3

vior is very similar to the open-collector

Page 28

Figure 2-10. Basic Mechanical Switch Connection To Digital Input

When the switch is open, the internal 100 kΩ pull-up resistor will pull the digital input to about

3.3 volts (logic high). When the switch is closed, the ground connection will overpower the pullup resistor and pull the digital input to 0 volts (logic low). Since the mechanical switch does not

have any electrical connections, besides to the LabJack, it can safely be connected directly to

GND, without using a series resistor or SGND.

When the mechanical switch is closed (and even perhaps when opened), it will bounce briefly

and produce multiple electrical edges rather than a single high/low transition. For many basic

digital input applications, this is not a problem as the software can simply poll the input a few

times in succession to make sure the measured state is the steady state and not a bounce. Fo

applications using timers or counters, however,

c

ounters, for instance, are very fast and will increment on all the bounces. Some solutions to

this usually is a problem. The hardware

this issue are:

• Software Debounce: If it is known that a real closure cannot occur more than once pe

r

some interval, then software can be used to limit the number of counts to that rate.

• Firmware Debounce: See section 2.10.1 for information about timer mode 6.

• Active Hardware Debounce: Integrated circuits are available to debounce switch

signals.

This is the most reliable hardware solution. See the MAX6816 (maxim-ic.com)

or EDE2008 (elabinc.com).

• Passive Hardware Debounce: A combination of resistors and capacitors can be used to

debounce a signal. This is not foolproof, but works fine in most applications.

r

Figure 2-11. Passive Hardware Debounce

Figure 2-12 shows one possible configuration for passive hardware debounce. First, consider

the case where the 1 kΩ resistor is replaced by a short circuit. When the switch closes it

immediately charges the capacitor and the digital input sees logic low, but when the switch

opens the capacitor slowly discharges through the 22 kΩ resistor with a time constant of 22 ms.

By the time the capacitor has discharged e

mechanical bouncing is done. The main p

28

ough for the digital input to see logic high, the

n

urpose of the 1 kΩ resistor is to limit the current surge

Page 29

when the switch is closed. 1 kΩ limits the maximum current to about 5 mA, but better results

might be obtained with smaller resistor values.

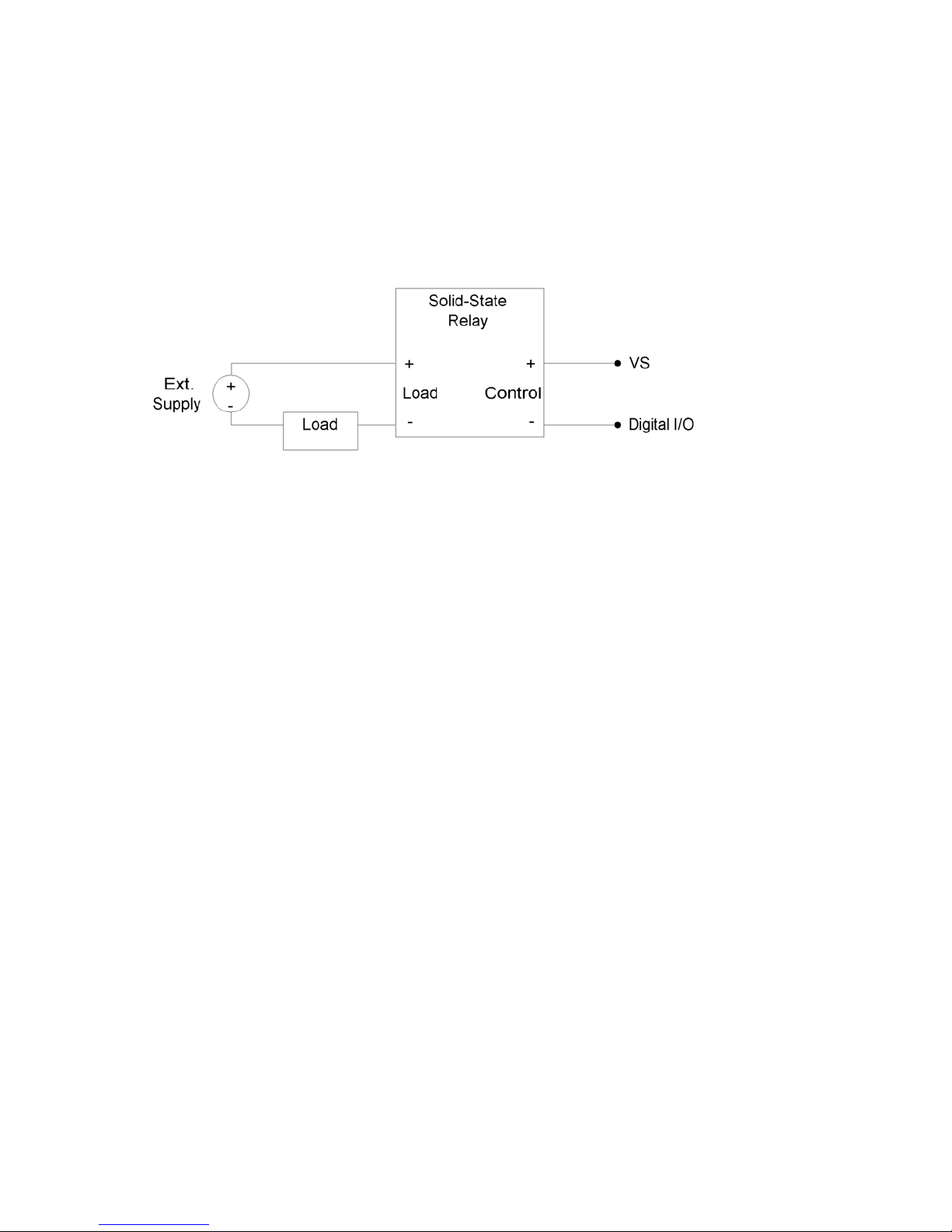

2.8.1.4 Output: Controlling Relays

All the digital I/O lines have series resistance that restricts the amount of current they can s

or source, but solid-state relays (SSRs) can usually be controlled directly by the digital I/O. The

SSR is connected as shown in the following diagram, where VS (~5 volts) connects to the

positive control input and the digital I/O line con

c

onfiguration).

nects to the negative control input (sinking

Figure 2-12. Relay Connections (Sinking Control, High-Side Load Switching)

When the digital line is set to output-low, control current flows and the relay turns on. When the

digital line is set to input, control current does not flow and the relay turns off. When the digital

line is set to output-high, some current flows, but whether the relay is on or off depends on the

specifications of a particular relay. It is recommended to only use output-low and input.

F

or example, the Series 1 (D12/D24) or Series T (TD12/TD24) relays from Crydom specify a

max turn-on of 3.0 volts, a min turn-off of 1.0 volts, and a nominal input impedance of 1500 Ω.

• When the digital line is set to output-low, it is the equivalent of a ground connection with

180 Ω (EIO/CIO) or 550 Ω (FIO) in series. When using an EIO/CIO/MIO line, the

resulting voltage across the control inputs of the relay will be about 5*1500/(1500+180) =

4.5 volts (the other 0.5 volts is dropped across the internal resistance of the EIO/CIO

line). With an FIO line the voltage across the inputs of the relay will be about

5*1500/(1500+550) = 3.7 volts (the other 1.3 volts are dropped across the internal

resistance of the FIO line). Both of these are well above the 3.0 volt threshold for the

relay, so it will turn on.

When the digital line is set to input, it is the equivalent of a 3.3 volt connection with 10

• 0

kΩ in series. The resulting voltage across the control inputs of the relay will be

zero, as virtually all of the 1.7 volt difference (between VS and 3.3) is dropped acro

internal 100 kΩ resistance. This is well below the 1.0 volt threshold for the relay, so it

will turn off.

• When the digital line is set to output-high, it is the equivalent of a 3.3 volt connection with

180 Ω (EIO/CIO) or 550 Ω (FIO) in series. When using an EIO/CIO line, the resulting

voltage across the control inputs of the relay will be about 1.7*1500/(1500+180) = 1.5

volts. With an FIO line the voltage across the inputs of the relay will be about

1.7*1500/(15

00+550) = 1.2 volts. Both of these in the 1.0-3.0 volt region that is not

defined for these example relays, so the resulting state is unknown.

ink

close to

ss the

29

Page 30

Mecha y

the dig uffer is

used. or

an op-a

N

mechanical relays, and thus can be a convenient way to control 1 or 2 relays.

The RB12 relay board is a useful accessory available from LabJack. This board connects to the

DB15 conne

O

Another accessory available from LabJack is the LJTick-RelayDriver. This is a

m

50 volts and sink up to 200 mA. This allows control of virtually any solid-state or mechanical

relay.

2

The U3 has 2 timers (Timer0-Timer1) and 2 counters (Counter0-Counter1). When any of these

timers or counters are enabled, they take over an FIO/EIO line in sequence (Timer0, Timer1,

Counter0, then Counter1), starting with FIO0+TimerCounterPinOffset. Some examples:

1 Timer enabled, Counter0 dis

FIO0=Timer0

1 Timer enabled, Counter0 disabled, Counter1 enabled, and TimerCounterPinOffset=2:

FIO2=Timer0

FIO3=Counter1

2 Timers enab

E

EIO1=Timer1

EIO2=Counter

EIO3=Counter1

Timers and counters can appear on various pins, but other I/O lines never move. For exa

Timer1 can ap

whether Timer

terminal labeled F

N

does not use an external FIO/EIO pin. Counter0 does not use an external An error will result if

an attempt is made to enable Counter0 when one of these frequencies are configured.

Similarly, an error will result if an attempt is made to configure one of these frequencies when

Counter0 is enabled.

Applicable digital I/O are automatically configured as input or output as needed when timers and

counters are enabled, and stay that way when the timers/counters are disabled.

See Section 2.8.1 for information about signal connections.

nical relays require more control current than SSRs, and cannot be controlled directly b

ital I/O on the U3. To control higher currents with the digital I/O, some sort of b

Some options are a discrete transistor (e.g. 2N2222), a specific chip (e.g. ULN2003),

mp.

ote that the U3 DACs can source enough current to control almost any SSR and even some

ctor on the U3 and accepts up to 12 industry standard I/O modules (designed for

pto22 G4 modules and similar).

two channel

odule that plugs into the U3 screw-terminals, and allows two digital lines to each hold off up to

.9 Timers/Counters

abled, Counter1 disabled, and TimerCounterPinOffset=0:

led, Counter0 enabled, Counter1 enabled, and TimerCounterPinOffset=8:

IO0=Timer0

0

mple,

pear anywhere from FIO0 to EIO1, depending on TimerCounterPinOffset and

0 is enabled. On the other hand, FIO5 (for example), is always on the screw

IO5, and AIN5 (if enabled) is always on that same screw terminal.

ote that Counter0 is not available with certain timer clock base frequencies. In such a case, it

30

Page 31

Each counter (Counter0 or Counter1) consists of a 32-bit register that accumulates the number

of falling edges detected on the external pin. If a counter is reset and read in the

c

all, the read returns the value just before the reset.

same function

T

he timers (Timer0-Timer1) have various modes available:

Timer Modes

0 16-bit PWM output

1 8-bit PWM output

2 Period input (32-bit, rising edges)

3 Period input (32-bit, falling edges)

4 Duty cycle input

5 Firmware counter input

6 Firmware counter input (with debounce)

7 Frequency output

8 Quadrature input

9 Timer stop input (odd timers only)

10

11 System timer high read

12 Period input (16-bit, rising edges)

13 Period input (16-bit, falling edges)

System timer low read

(default mode)

Both timers use the same timer clock. There are 7 choices

for the timer base clock:

TimerBaseClock

04 MHz

112 MHz

2 48 MHz (Default)

3 1 MHz /Divisor

4 4 MHz /Divisor