Page 1

U3 Product Page

Published on LabJack (http://labjack.com)

Home > Printer-frie ndly P DF > Printer-frie ndly P DF

U3 User's Guide

The complete user's guide for the U3, including documentation for the LabJackUD driver. Covers

hardware versions 1.20, 1.21, and 1.30 (LV/HV).

To make a PDF of the whole manual, click "Export all" towards the upper-right of this page. Doing so

converts these pages to a PDF on-the-fly, using the latest content, and can take 20-30 seconds.

Make sure you have a current browser (we mostly test in Firefox and Chrome) and the current version

of Acrobat Reader. If it is not working for you, rather than a normal click of "Export all" do a right-click

and select "Save link as" or similar. Then wait 20-30 seconds and a dialog box will pop up asking

you where to save the PDF. Then you can open it in the real Acrobat Reader, not embedded in a

browser. If you still have problems, try the "Print all" option instead. In addition, an export is attached

below, but will not always be the latest version.

If you are looking at a PDF or hardcopy, realize that the original is an online document at http://labjack.com/support/u3/users-guide.

Rather than using a PDF, though, we encourage you to use this web-based documentation. Some advantages:

We can quickly change or update content.

The site search includes the user's guide, forum, and all other resources at labjack.com. When you are looking for

something try using the site search.

For support, try going to the applicable user's guide page and post a comment. When appropriate we can then immediately

add/change content on that page to address the question.

One other trick worth mentioning, is to browse the table of contents to the left. Rather than clicking on all the links to browse, you

can click on the small black triangles to expand without reloading the whole page.

User's Guide

Preface

For the latest version of this and other documents, go to www.labjack.com.

Copyright 2012, LabJack Corporation

Package Co ntents:

The normal retail packaged U3 (-LV or -HV):

U3 unit itself in red enclosure

USB cable (6 ft / 1.8 m)

Screwdriver

Warranty:

The LabJack U3 is covered by a 1 year limited warranty from LabJack Corporation, covering this product and parts against

defects in material or workmanship. The LabJack can be damaged by misconnection (such as connecting 120 VAC to any of the

screw terminals), and this warranty does not cover damage obviously caused by the customer. If you have a problem, contact

support@labjack.com for return authorization. In the case of warranty repairs, the customer is responsible for shipping to LabJack

Corporation, and LabJack Corporation will pay for the return shipping.

Limitation of Liability:

LabJack designs and manufactures measurement and automation peripherals that enable the connection of a PC to the realworld. Although LabJacks have various redundant protection mechanisms, it is possible, in the case of improper and/or

unreasonable use, to damage the LabJack and even the PC to which it is connected. LabJack Corporation will not be liable for

any such damage.

Except as specified herein, LabJack Corporation makes no warranties, express or implied, including but not limited to any implied

warranty or merchantability or fitness for a particular purpose. LabJack Corporation shall not be liable for any special, indirect,

incidental or consequential damages or losses, including loss of data, arising from any cause or theory.

LabJacks and associated products are not designed to be a critical component in life support or systems where malfunction can

reasonably be expected to result in personal injury. Customers using these products in such applications do so at their own risk

and agree to fully indemnify LabJack Corporation for any damages resulting from such applications.

LabJack assumes no liability for applications assistance or customer product design. Customers are responsible for their

applications using LabJack products. To minimize the risks associ ated with customer applications, customers should provide

adequate design and operating safeguards.

Reproduction of products or written or electronic information from LabJack Corporation is prohibited without permission.

Reproduction of any of these with alteration is an unfair and deceptive busine ss practice.

Conformity Information (FCC, CE, RoHS):

See the Conformity Page and the text below:

FCC PART 15 STATEMENTS:

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FC C

Rules. These limits are designed to provide reasonable protection against harmful interference when the equi pment is operated in

a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, i f not i nstalled and used

in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment

in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his

own expense. The end user of this product should be aware that any changes or modifications made to this equipment without the

approval of the manufacturer could result in the product not meeting the Class A limi ts, in which case the FCC could void the user's

1

Page 2

authority to operate the equipment.

Declaration of Conformity:

Manufacturers Name: LabJack Corporation

Manufacturers Address: 3232 S Vance St STE 100, Lakewood, CO 80227, USA

Declares that the product

Product Name: LabJack U3 (-LV or -HV)

Model Number: LJU3 (-LV or -HV)

conforms to the following Product Specifications:

EN 55011 Class A

EN 61326-1: 2002 General Requirements

and is marked with CE

RoHS:

The U3 is RoHS compliant per the requirements of Directive 2002/95/EC.

1 - Installation

Windows

The LJUD driver requires a PC running Windows. For other operating systems, go to labjack.com for available support. Software

will be installed to the LabJack directory which defaults to c:\Program Files\LabJack\.

Install the software first by going to labjack.com/support/u3.

Connect the USB cable: The USB cable provides data and power. After the UD software installation is complete , connect the

hardware and Windows should prompt with “Found New Hardware” and shortly after the Found New Hardware Wizard will open.

When the Wizard appears allow Windows to install automatically by accepting all defaults.

Run LJC ontrolPane l: From the Windows Start Menu, go to the LabJack group and run LJControlPanel. Click the “Find Devices”

button, and an entry should appear for the connected U3 showing the serial number. Click on the “USB – 1” entry below the serial

number to bring up the U3 configuration panel. Click on “Test” in the confi guration panel to bring up the test panel where you can

view and control the various I/O on the U3.

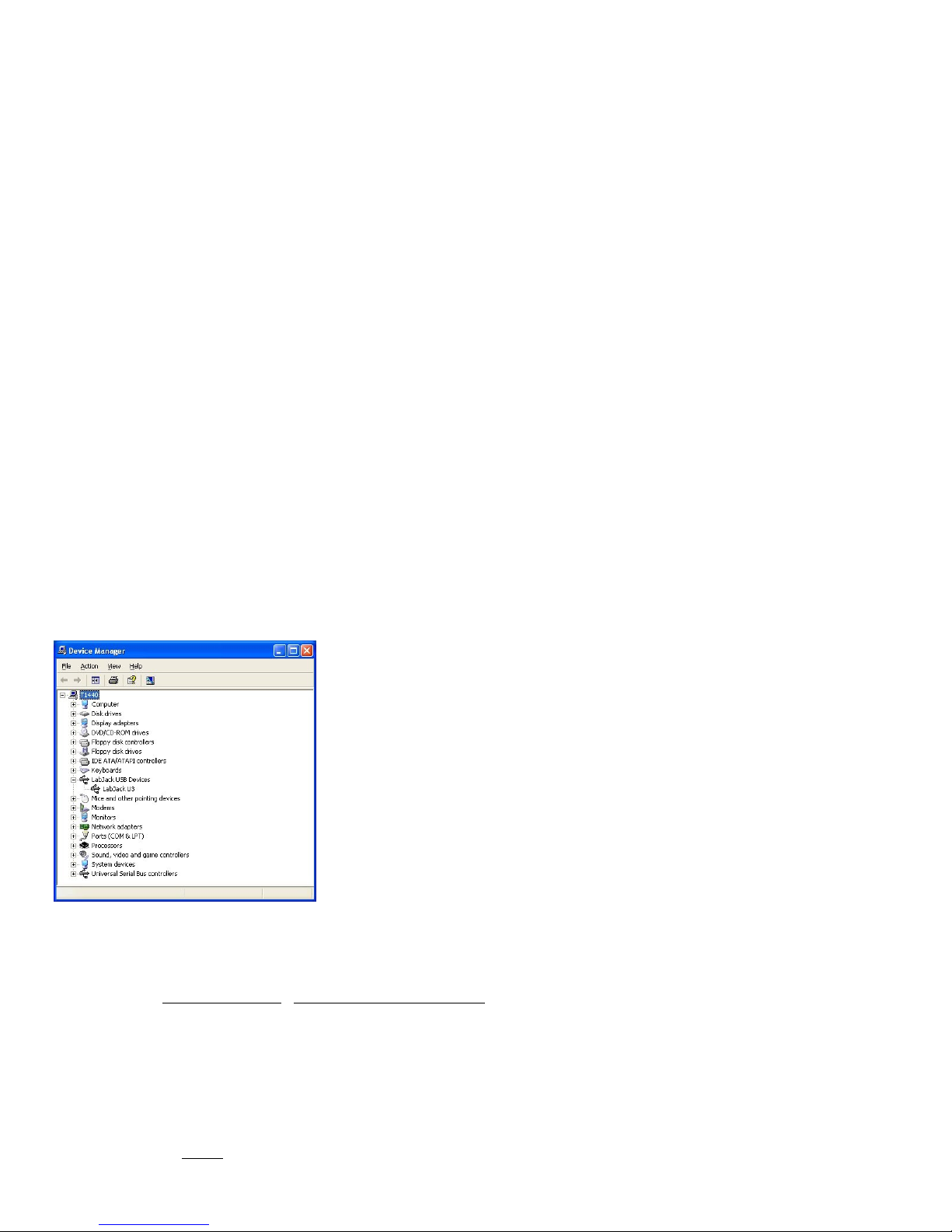

If LJControlPanel does not find the U3, check Windows Device Manager to see if the U3 installed correctly. One wa y to get to the

Device Manager is:

Start => Control Panel => System => Hardware => Device Manager

The entry for the U3 should appear as in the following figure. If it has a yellow caution symbol or exclamation point symbol, rightclick and select “Uninstall” or “Remove”. Then disconnect and reconnect the U3 and repeat the Found New Hardware Wizard as

described above.

Correctly Functioning U3 in Windows Device Manager

Linux and Mac OS X

The Exodriver is the native USB driver for Linux and Mac OS X. With it you can use low-level functions to interact with your U3 over

USB. The LJUD driver, LJControlPanel and LJSelfUpgrade applications are not available for Linux or Mac OS X.

Download the Exodriver at labjack.com/support/software or lab jack.com/support/linux-and-mac-os-x-drivers. For Mac OS X you

can use the Mac Installer for installation, otherwise use the source code and install script.

Mac OS X Installer

Unzi p the contents of Exodrive r_NativeUSB_Setup.zip and run E xodriver_NativeUSB_Setup.pkg. Then follow the installer’s

instructions to install the driver.

Source Code

Mac OS X Requirements

• OS X 10.5 or newer

• XCode developer tools

• libusb-1.0 library available at li busb.info

Linux Requirements

2

Page 3

• Linux kernel 2.6.28 or newer.

• GNU C Compiler

• libusb-1.0 library and development files (header files)

Installation

To install the driver from source code, first unzip the contents of the Exodriver source code. Then run the following commands in a

terminal (replace <Exodriver-Source-Directory> with the directory yo u unzipped the Exodriver source code to):

cd <Exodriver-Source-Directory>

sudo ./install.sh

Follow the install script’s instructions to install the driver.

For more Exodriver installa tion information go to the Exodriver page at labjack.com/sup port/linux-and-mac-os-x-drivers. The

source code download’s README, INSTALL.Li nux and INS TALL.MacOSX also provides more information. If you run into

problems, first take a look at the comments section of the Exodriver page as the issue may have been helped wi th previously.

After installation, to test your U3 connect it to your computer with a USB cable. The USB cable provides data and power. Build and

run one of the examples from the source code download. Alternatively, install LabJackPython (at

labjack.com/sup port/labjackpython) and run one of i ts examples.

1.1 - Control Panel Application (LJControlPanel)

The application LJControlPanel is included with the installation package below

LabJack Windows Driver and Software Installation Package

Name: LabJack-2014-10-14.exe

Size: 49.99 MB

Upload date: 2014-10-14 12:45

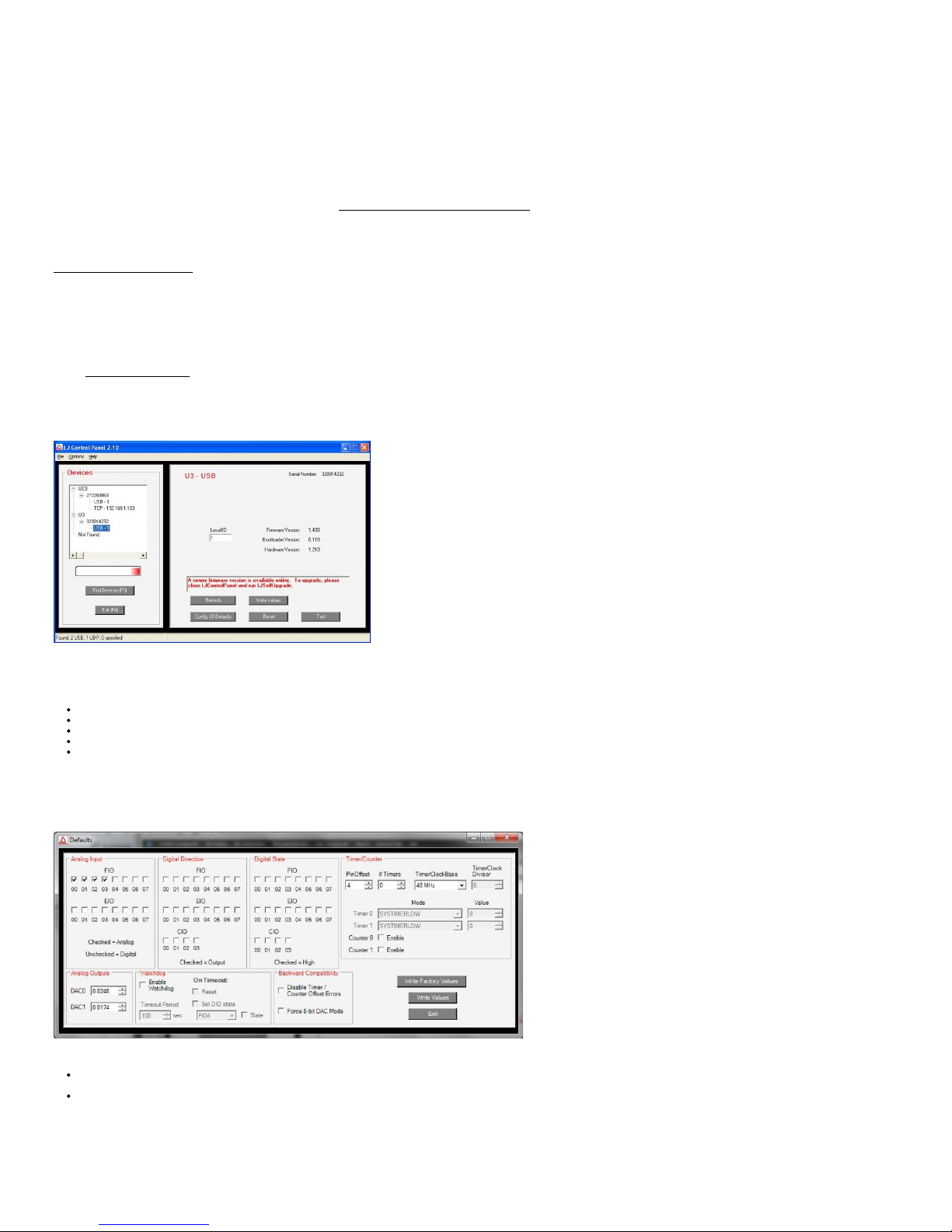

The LabJack Control Panel application (LJCP) handles configuration and testing of the UD series hardware. Click on the “Find

Devices” button to search for connected devices.

Figure 1-1. LJControlP anel Main Window

Figure 1-1 shows the results from a typical search. The application found two devices. The USB connection for a U3 has been

selected in Figure 1-1, bringing up the configuration window on the right side.

Refresh: Reload the window using values read from the device.

Write Values: Write the Local ID from the wi ndow to the device.

Config Defaults: Opens the window shown in F igure 1-2.

Reset: Click to re set the selected device.

Test: Opens the window shown in Figure 1-3.

Config Defaults:

This option provides control over the condition of the device at power-up or reset. Figure 1-2 shows a U3-HV with the fa ctory

default power-up configuration, whi ch means AIN0-AIN3 set to analog inp ut, F IO4 to CIO3 set to digital input, analog outputs set to

minimum voltage (near 0), a nd timers/counters/watchdog disabled.

Figure 1-2. LJControlP anel U3 Configure Defaults Window

Write Factory Values: Clicking this wi ll set everything back to the factory defaults and write those factory defaults to

nonvolatile memory.

Write Values: Change any desi red settings, a nd then click this to write the new settings to nonvolatile memory.

Test Panel:

Figure 1-3 shows the test window for a U3 device. This window co ntinuously (once per second) writes to and reads from the

selected LabJack.

3

Page 4

Figure 1-3. LJControlP anel U3 Test Window

Any configuration done on this screen is not written to no nvolatile memory. These settings just affect the current condition of the

device, not the reset/power-up condition.

When the test panel first loads it sets everything to factory default, so previous settings (or reset/power-up settings) will not be

shown.

LJCP Settings:

Selecting Options=>Settings from the main LJControlPanel menu brings up the window shown in Figure 1-4. Thi s window allows

some features to of the LJControlP anel application to be customized.

Figure 1-4. LJControlP anel Setting s Window

Search for US B devices: If selected, LJControlPanel will include USB when searching for devices.

Search for Ethernet devices using UDP broadcast packet: Only a pplies to UE9 device.

Search for Ethernet devices using specified IP addresses: Only applies to UE9 device.

LJControlPanel is normally installed by the main LabJack installer, which is the link at the top of the page.

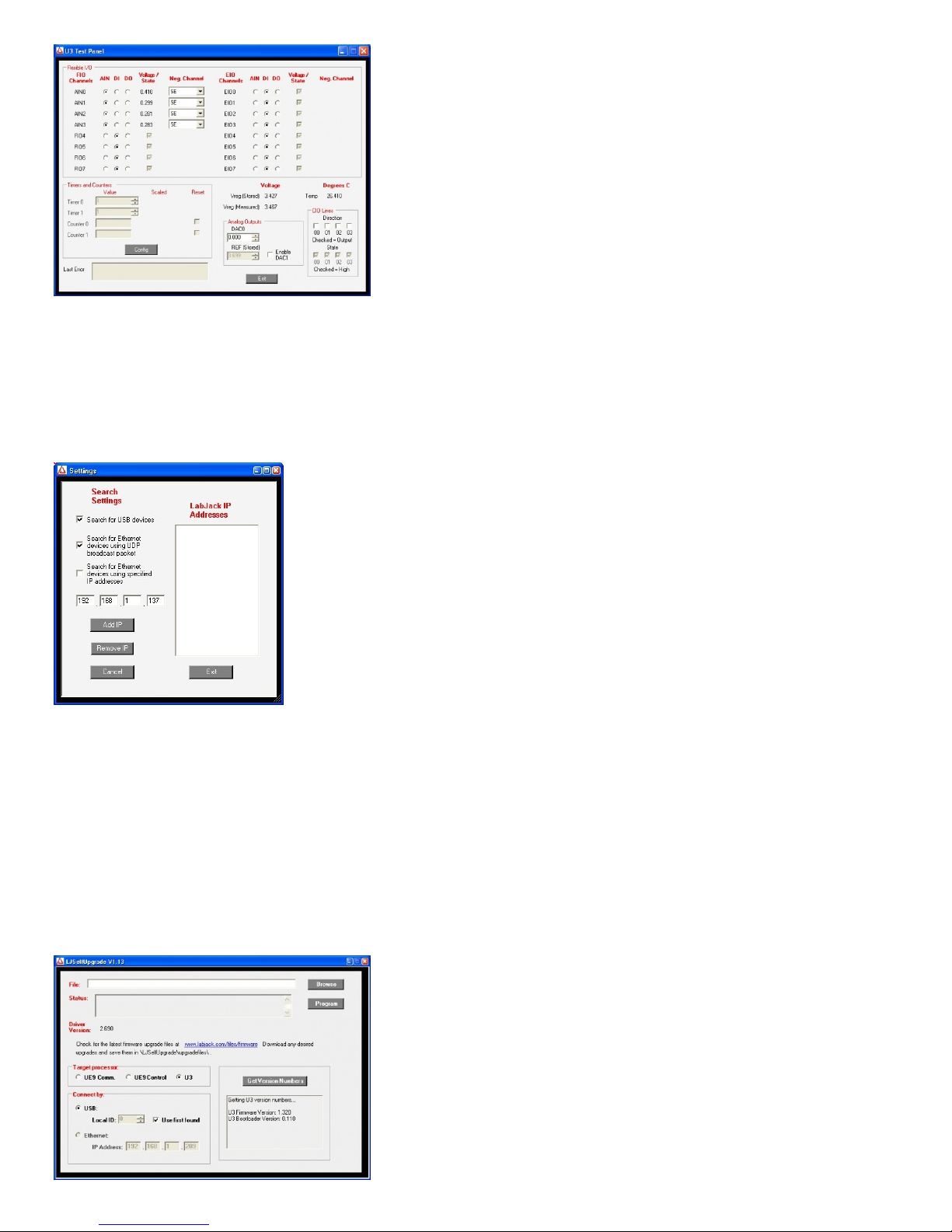

1.2 - Self-Upgrade Application (LJSelfUpgrade)

The processor in the U3 has field upgradeable flash memory. The self-upgrade application shown in Figure 1-5 programs the

latest firmware onto the processor.

USB is the only interface on the U3, and first fo und is the only option for self-upgrading the U3, so no chang es are needed in the

“Connect by:” box. There must only be one U3 connected to the PC when running LJSelfUpgrade.

Click on “Get Version Numbers”, to find out the current firmware versions on the device. Then use the provided Internet link to go to

labjack.com and check for more recent firmware. D ownload firmware files to the …\LabJack\LJSelfUpgrade\upgradefiles\

directory.

Click the Browse button and select the upgrade file to program. Click the Program button to begin the self-upgrade process.

4

Page 5

Figure 1-5. Self-Upgrade Application

If problems are encountered during programming, try the following:

1. Unplug the U3, wait 5 seconds then reconnect the U3. Click OK then press program again.

2. If step 1 does not fix the problem unplug the U3 and watch the LED while plugging the U3 back in. Follow the following steps

based on the LED's activity.

1. If the LED is blinking continuously (flash mode), connect a jumper between F IO4 and SPC (FIO0 to SCL on U3

1.20/1.21), then unplug the U3, wait 5 seconds and plug the U3 back in. Try programming again (disconnect the jumper

before programming).

2. If the LED blinks several times and stays on, connect a jumper between F IO5 and SPC (FIO1 to SCL on U3

1.20/1.21), then unplug the U3, wait 5 seconds and plug the U3 back in. Try programming again (disconnect the jumper

before programming).

3. If the LED blinks several times and stays off, the U3 is no t enumerating. Please restart your computer and try to

program again.

4. If there is no LED activity, connect a jumper between FIO5 and SPC (FIO1 to SCL on U3 1.20/1.21), then unplug the

U3, wait 5 seconds and plug the U3 back in. If the LED is blinking continuously click OK and program again (after

removing the jumper). If the LED does not blink connect a jumper between F IO4 and SPC (FIO0 to SCL on U3

1.20/1.21), then unplug the U3, wait 5 seconds and plug the U3 back in.

5. If the LED does a repeating pattern of 3 blinks then pause, the U3 has detected internal memory corruption and

you will have to contact LabJack Support.

3. If there is no activity fro m the U3's LED after following the above steps, please contact support.

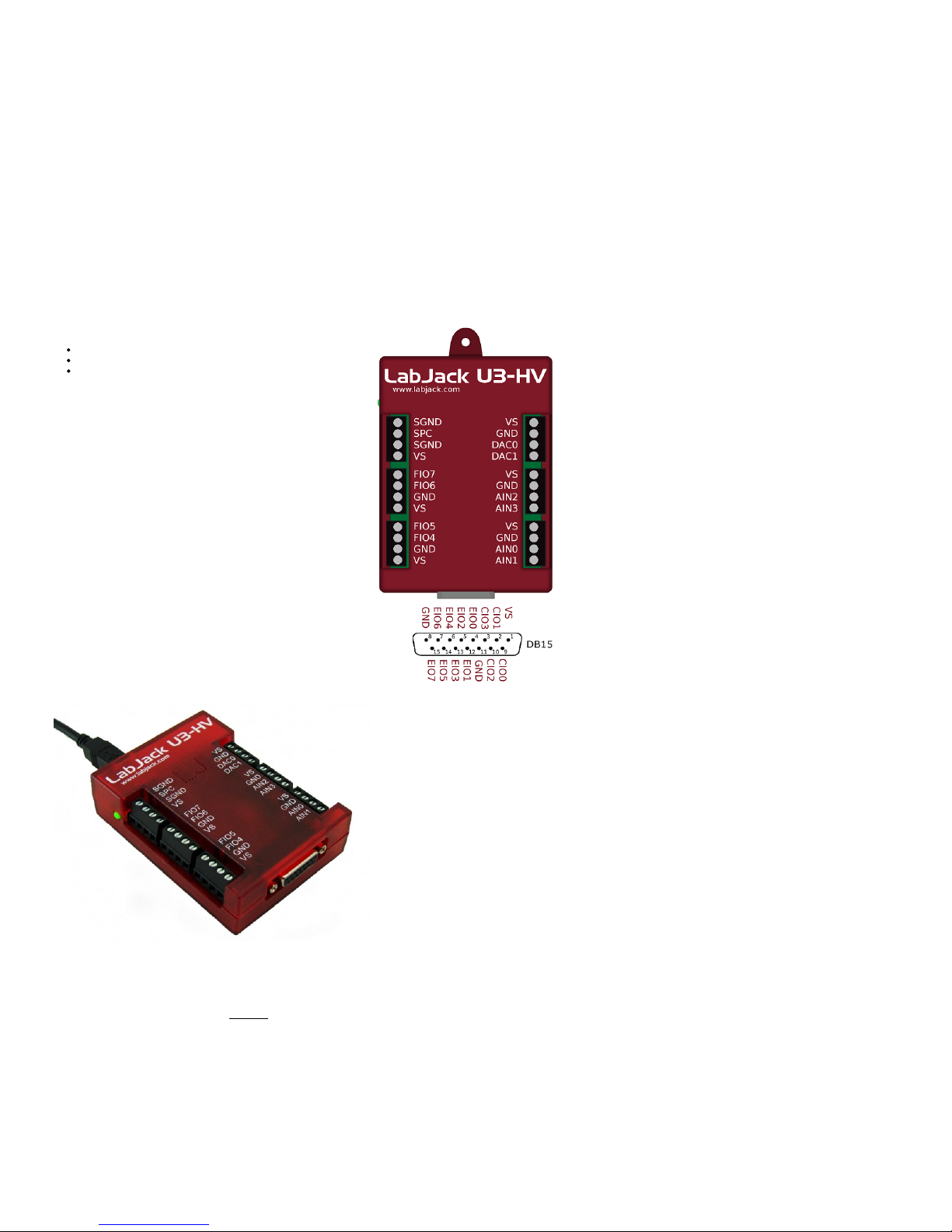

2 - Hardware Description

The U3 has 3 different I/O areas:

Communication Edge,

Screw Terminal Edge,

DB Edge.

The communication edge has a USB type B connector (with black cable

connected in Fi gure 2-1). All power a nd communication is handled by the

USB interface.

The screw terminal edge has convenient connections for the analog outputs

and 8 flexible I/O (digital I/O, analog inputs, timers, or counters). The screw

terminals are arranged in blocks of 4, with each block consisting of Vs, GND,

and two I/O. There is also a status L ED located on the left edge.

The DB Edge has a D-sub type conne ctors called DB15 which has the 8 EIO

lines and 4 CIO lines. The EIO lines are flexible like the FIO lines, while the

CIO are d edicated digital I/O.

Figure 2-1. LabJack U3

2.1 - USB

For information ab out US B installation, see Section 1.

The U3 has a full-speed USB connection compatible with USB version 1.1 or 2.0. Thi s connection provides communication and

power (Vusb). USB ground is connected to the U3 ground (GND), and USB ground is generally the same as the ground of the PC

chassis and A C mains.

The details of the U3 USB interface are handled by the high level d rivers (Windows LabJackUD DLL), so the following information

is really only needed when developing low-level drivers.

The LabJack vendor ID is 0x0CD5. The product ID for the U3 is 0x0003.

The USB interface consists of the normal bidirectional control endpoint (0 OUT & IN), 3 used bulk endpoints (1 OUT, 2 IN, 3 IN),

and 1 dummy endpoint (3 OUT). Endpoint 1 consists of a 64 byte OUT endpoint (address = 0x01). Endpoint 2 consists of a 64

byte IN endpoint (address = 0x82). Endpoint 3 consists of a dummy OUT endpoint (address = 0x03) and a 64 byte IN endpoint

(address = 0x83). Endpoint 3 OUT i s not supported by the firmware, and should never be used.

All commands should always be sent on Endpoint 1, and the responses to commands will always be on Endpoint 2. Endpoint 3 is

5

Page 6

only used to send stream data from the U3 to the host.

2.2 - Status LED

There is a green status LED on the LabJack U3. This LED blinks on reset, and then remains steadily li t. Other LED behavior is

generally related to flash upgrade modes ("Section 1.2":/support/u3/users-guide/1.2).

Normal Power-Up Status LED Behavior: When the USB cable is connected to the U3, the Status LED blinks 5-6 ti mes over 2

seconds and then remains solid on.

LED blinking continuously at about 4 Hz, even with no software running: This indicates that the U3 is in flash mode. See

Section 1.2 and reprogram the device.

2.3 - GND and SGND

The GND conne ctions available at the screw-terminals and DB connectors provide a common ground for all LabJack functio ns. All

GND terminals are the same and connect to the same ground plane. This ground is the same as the ground line on the USB

connection, whi ch is often the same as ground on the PC chassis and therefore AC mains ground.

SGND is located near the upper-left of the device. This terminal has a self-resetti ng thermal fuse in series with GND . Thi s is often

a good terminal to use when connecting the ground from another separately powered system that could unknowingly already share

a common ground with the U3.

See the AIN, DAC, and Digital I/O Sections for more information about grounding.

2.4 - VS

The Vs terminals are designed as outputs for the internal supply voltage (nominally 5 volts). This will be the volta ge provided from

the USB cable. The Vs connections are outputs, not inputs. Do not connect a power source to Vs in normal situations. All Vs

terminals are the same.

2.5 - Flexible I/O (FIO/EIO)

The FIO and EIO ports on the LabJack U3 can be individually configured as digital input, digital output, or analog input. Thi s is

FIO0-EIO7 on the U3-LV (16 lines), or FIO4-EIO7 on the U3-HV (12 lines). In addi tion, up to 2 of these li nes can be configured as

timers, and up to 2 of these lines can be configured as counters. If a line is configured as analog, it is called AINx according to the

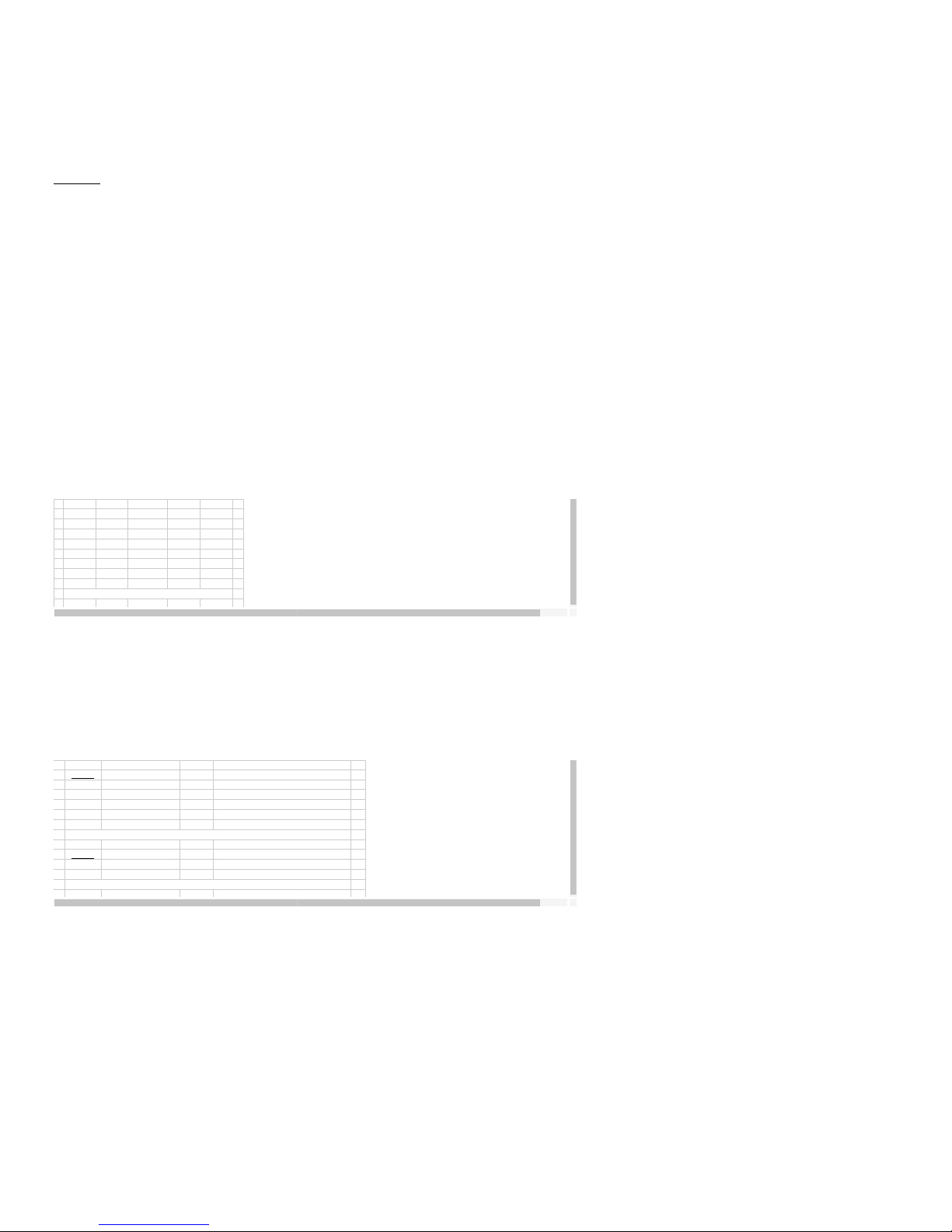

following table:

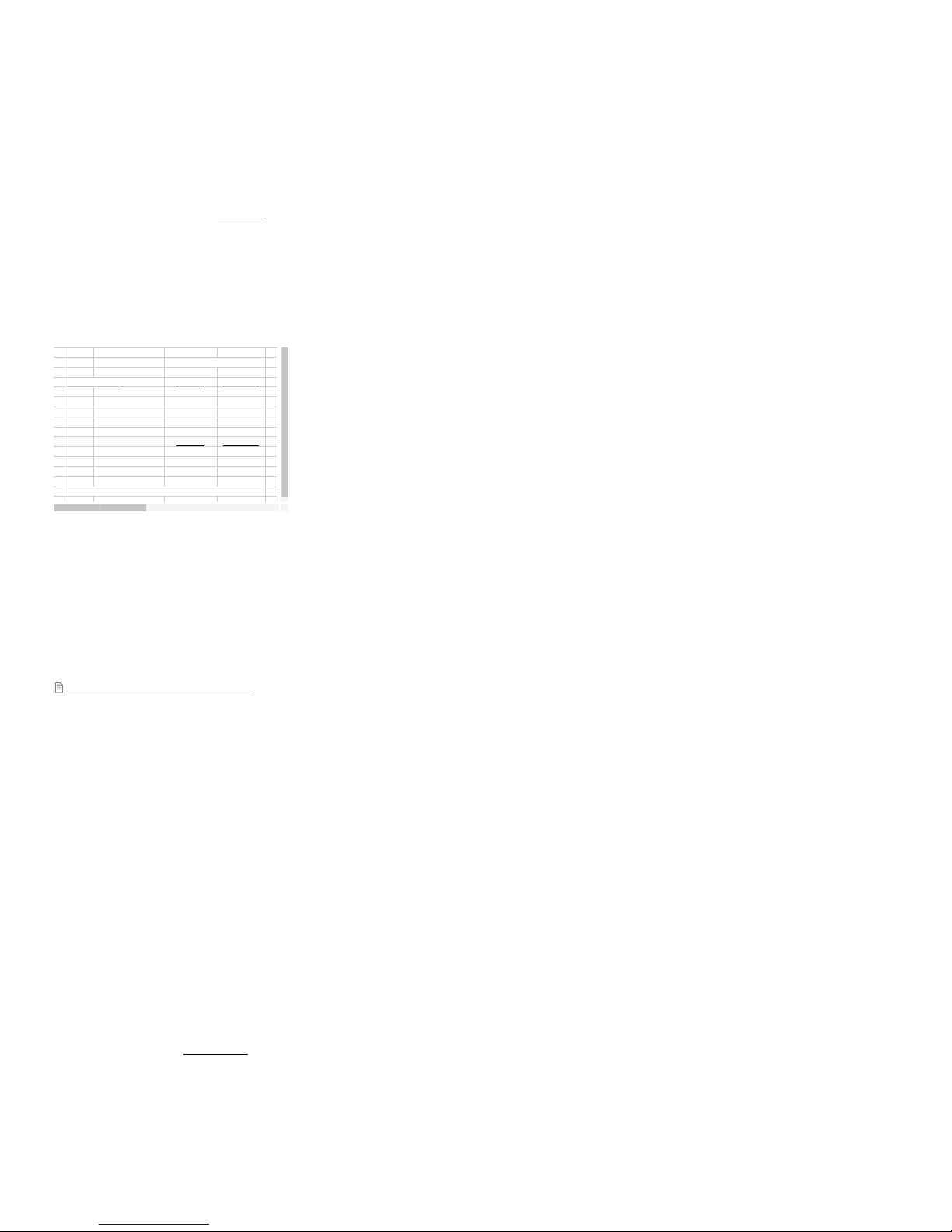

AIN0

FIO0

AIN8

EIO0

AIN1

FIO1

AIN9

EIO1

AIN2

FIO2

AIN10

EIO2

AIN3

FIO3

AIN11

EIO3

AIN4

FIO4

AIN12

EIO4

AIN5

FIO5

AIN13

EIO5

AIN6

FIO6

AIN14

EIO6

AIN7

FIO7

AIN15

EIO7

Table 2. 5-1. Analog Input Pin Locatio ns

On the U3-HV, compared to the -LV, the first four flexible I/O are fixed as analog inputs (AIN0-AIN3) with a nominal ±10 volt input

range. All di gital operations, including analog/digital confi guration, a re ignored on these 4 fixed analog inputs.

Timers and counters can appear on vario us pins, but other I/O lines never move. For example, Timer1 can appear anywhere from

FIO4 to EIO1 , depending on TimerCounterPinOffset and whether Timer0 is enabled. On the other hand, FIO5 (for example), i s

always on the screw terminal labeled FIO5, and AIN5 (if enabled) is always on that same screw termina l.

The first 8 flexible I/O lines (FIO0-FIO7) appear on built-in screw terminals. The other 8 flexible I/O lines (EIO0-EIO7) are available

on the DB 15 connector.

Many software applications will need to initialize the flexible I/O to a known pin configuration. That requires calls to the low-level

functions ConfigIO and ConfigTi merClock. Following are the values to set the pin configuration to the factory default state:

Byte #

6

WriteMask

15

Write all parameters

8

TimerCounterConfig

0

No Timers/Counters. Offset = 4

9

DAC1 Enable

0

DAC1 Disabled. (Ignored on HW 1.3)

10

FIOAnalog

0

FIO all digital.

11

EIOAnalog

0

EIO all digital.

Table 2. 5-2. ConfigIO Fa ctory Defaul t Value s

Byte #

8

TimerClockConfig

130

Set cloc k to 48MHz.

9

TimerClockDivisor

0

Divisor = 0.

Table 2. 5-3. ConfigTime rClock Factory Default Va lues

When using the high-level LabJackUD driver, thi s could be done with the following requests:

ePut (l ngHandle , LJ_io PUT_CONF IG, LJ_c hNUMBER _TIMERS_ ENABLED, 0, 0);

ePut (l ngHandle , LJ_io PUT_CONF IG, LJ_c hTIMER_ COUNTER_ PIN_OFFS ET, 4, 0);

ePut (l ngHandle , LJ_io PUT_CONF IG, LJ_c hTIMER_ CLOCK_BA SE, LJ_t c48MHZ, 0);

ePut (l ngHandle , LJ_io PUT_CONF IG, LJ_c hTIMER_ CLOCK_DI VISOR, 0 , 0);

ePut (l ngHandle , LJ_io PUT_COUN TER_ENAB LE, 0, 0, 0);

ePut (l ngHandle , LJ_io PUT_COUN TER_ENAB LE, 1, 0, 0);

ePut (l ngHandle , LJ_io PUT_DAC_ ENABLE, 1, 0, 0 ); //Ig nored on hardwa re rev 1 .30+.

ePut (l ngHandle , LJ_io PUT_ANAL OG_ENABL E_PORT, 0, 0, 1 6);

… or with a single request to the following IOType created exactly for this purpose:

ePut (l ngHandle , LJ_io PIN_CONF IGURATIO N_RESET , 0, 0, 0);

2.6 - AIN

The LabJack U3 has up to 16 analog inputs available on the flexi ble I/O lines (FIO0-FIO7 and EIO0-EIO7). Single-ended

measurements can be taken of any line compared to ground, or differential measurements can be taken of any line to any other

line.

Analog input resolutio n is 12-bits. The range of single-ended analo g inputs is normally about 0-2.44, and there is a “special” 0-3.6

volt range available. The range of differential analog inputs is typically ± 2.4 volts, but is pseudobipolar, not true bipolar. The

difference (positive channel minus negative channel) can be -2.4 volts, but neither input can have a voltage less than -0.3 volts to

6

Page 7

ground. For valid measurements, the voltage on every low-voltage analog input pin, with respect to ground, must be within -0.3 to

+3.6 volts. See Appendix A for voltage limits to avoid damage.

On the U3-HV, compared to the -LV, the first four flexible I/O are fixed as analog inputs (AIN0-AIN3), and have scaling such that the

input range is a true bipolar ±10 volts normally, and -10 to +20 volts when using the “special” range . The input impedance of these

four lines is roughly 1 MΩ, which is good, but less than the normal low voltage analog inputs. Analog/digital configuration and all

other digital operations on these pins are ignored. FIO4-EIO7 a re still available as flexible I/O, same as the U3-LV.

To get the special 0-3.6 volt or -10/+20 volt range, you do a differential reading with the negative channel set to 32, altho ugh the

reading is actually single-ended.

Because the scaling on the high-voltage inputs on the U3-HV (AIN0-AIN3) is inherently single-ended, a factory calibration is not

possible for differential readings. If a differential reading is requested where either channel is a high-voltage channel, the driver will

return the raw binary reading and the user must handle calibration/conversion.

The analog inputs have a Qui ckSample option where each conversion is done faster at the expense of increased noise. This is

enabled by passing a nonzero value for put_config special channel LJ_chAIN_RE SOLUTION. There is also a LongSettling option

where additional settling time is added between the internal multiplexer configuration and the analog to digital conversion. This

allows signals with more source impedance, and is enabled by passing a nonzero value for put_config special channel

LJ_chAIN_SE TTLING_TIME . Both o f these options are disabled by de fault. This applies to command/response mode only, and

the resulting typical data rates are discussed in Section 3.1. For stream mode, see Section 3.2.

Note that sinking excessive current i nto digital outputs can cause substanti al errors in analog input readings. S ee Section 2.8.1.4

for more info.

2.6.1 - Channel Numbers

The LabJack U3 has up to 16 external analog inputs, plus a few internal channels. The low-level functions specify a positive and

negative channel for each analog input conversion. With the LabJackUD driver, the IOType LJ_ioGET_AIN i s used for singleended channels only, and thus the negative channel is internally set to 31. There is an additional IOType called

LJ_ioGET_AIN_DIFF that allows the user to specify the positive and negative channel.

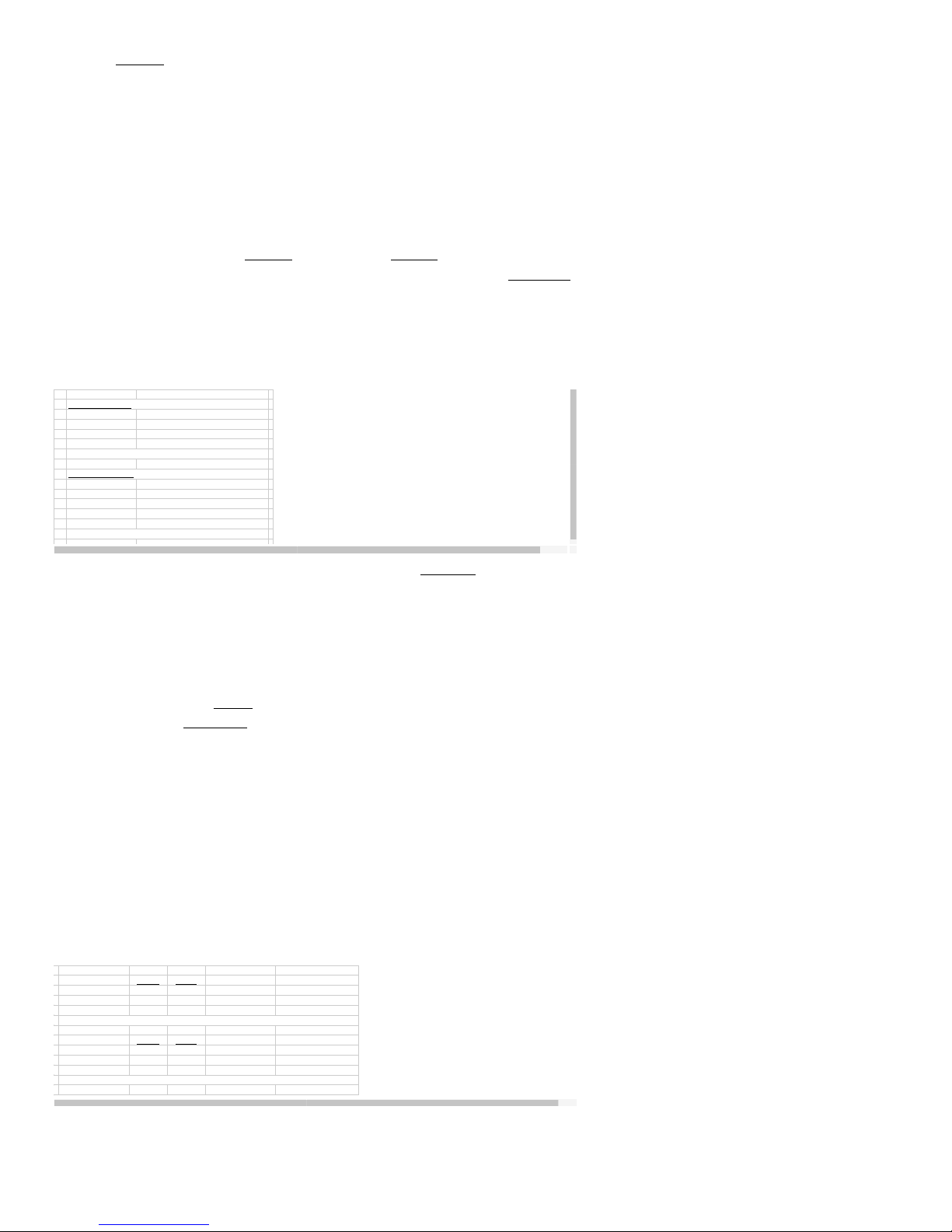

Positive Channel #

0-7

AIN0-AIN7 (FIO0-FIO7)

8-15

AIN8-AIN15 (EIO0-EIO7)

30

Temp Sensor

31

Vreg

Table 2. 6.1-1. Positive Cha nnel Numbe rs

Negative Channel #

0-7

AIN0-AIN7 (FIO0-FIO7)

8-15

AIN8-AIN15 (EIO0-EIO7)

30

Vref

31 or 199

Single-Ended

32

Special 0-3.6 or -10/+20 (UD Only)

Table 2. 6.1-2 Negati ve Channe l Numbers

Positive channel 31 puts the internal Vreg (~3.3 volts) on the posi tive input of the ADC . See Section 2.6.4 for information about the

internal temperature sensor.

If the negative channel is set to anything besides 31/199, the U3 does a differential conversion and returns a pseudobipolar value.

If the negative channel is set to 31/199, the U3 does a single-ended conversion and returns a unipolar value. Channel 30 puts the

internal voltage reference Vref (~2.44 volts) on the negative input of the ADC.

Channel 32 is a special negative channel supported by the LabJack UD driver. When used, the driver will actually pass 30 as the

negative channel to the U3, and when the result is returned the d river adds Vref to the value. For a low-voltage analog input this

results in a full span on the positive channel of about 0 to 4.88 volts (versus ground), but since the voltage on any analog input

cannot exceed 3.6 volts, only 75% of the converter’s range is used and the span is about 0 to 3.6 volts. For a high-voltage analog

input, channel 32 (special range) results in a span of about -10 to +20 volts.

In the U3 examples that accompany the Exodriver, u3.c also supports channel 32 in calls to eAIN().

Channel 32 is also supported in LabJackPython:

# On th e U3, wi re a ju mper fro m DAC0 t o FIO0, then ru n:

>>> imp ort u3

>>> d = u3.U3()

>>> d.c onfigIO( FIOAnal og = 1) # Set FI O0 to a nalog

>>> d.w riteRegi ster(50 00, 3) # Set DAC 0 to 3 V

>>> d.g etAIN(0, 32)

3.01411 40941996 127

For the four high-voltage channels on the U3-HV, the special channel negative channel also puts Vref on the negative. This results

in an overall range of about -10 to +20 volts on the positive input.

2.6.2 - Converting Binary Readings to Voltages

This information is only needed when using low-level functions and other ways of getting binary readings. Readings in volts already

have the calibration constants applied. The UD driver, for example, normally returns voltage readings unless binary readings are

specifically requested.

Following are the nomi nal input voltage ranges for the low-voltage analog inputs. This is all analog inp uts on the U3-LV, and AIN4AIN15 on the U3-HV.

Max V

Min V

Single-Ended

2.440Differential

2.44

-2.44

Special 0-3.6

3.60Table 2. 6.2-1. Nomina l Analog In put Voltage Range s for Low-Voltage Channe ls

Max V

Min V

Single-Ended

10.3

-10.3

Differential

N/A

N/A

Special -10/+20

20.1

-10.3

Table 2. 6.2-2. Nomina l Analog In put Voltage Range s for High-Voltage Chan nels

Note that the minimum differential input voltage of -2.44 volts means that the posi tive channel can be as much as 2.44 volts less

than the negative channel, not that a channel can measure 2.44 volts less than ground. The voltage of any lo w-voltage analog input

pin, compared to ground, must be in the range -0.3 to +3.6 volts.

The “special” range (0-3.6 on lo w-voltage channels and -10/+20 volts on high-voltage channels) is obtained by doing a differential

measurement where the negative channel is set to the internal Vref (2.44 volts). For low-voltage channels, simply do the low-

7

Page 8

voltage differential conversion as described below, then add the stored Vref value. For hi gh-voltage channels, d o the same thing,

then multip ly by the proper high-voltage slope, divide by the single-ended low-voltage slope, and add the proper high-voltage

offset. The UD driver handles these conversions auto matically.

Althoug h the binary readings have 12-bit resolution, they are returned justified as 16-bit value s, so the approximate nominal

conversion from binary to voltage is:

Volts(u ncalibra ted) = (Bits/65 536)*Spa n (Sing le-Ended )

Volts(u ncalibra ted) = (Bits/65 536)*Spa n – Spa n/2 (Dif ferentia l)

Binary readings are always unsigned integers.

Where span i s the maximum voltage minus the minimum vo ltage from the tables above. The actual nominal conversions are

provided in the tables below, and should be used if the actual calibration constants are not read for some reason. Most

applications will use the actual calibrations consta nts (S lope and Offset) stored in the internal flash.

Volts = (Slope * Bits) + Offse t

Since the U3 uses multiplexed channels connected to a single ana log-to-digital converter (ADC), all low-voltage channels have the

same calibration for a given configuration. High-voltage channels have individual sca ling circuitry out front, and thus the calibration

is unique for each channel.

See Section 5.4 for detail about the location of the U3 calibration constants.

2.6.2.1 - Analog Inputs With DAC1 Enabled (Hardware

Revisions 1.20 & 1.21 only)

This Section only applies to the older hardware revi sions 1.20 and 1.21. Starting wi th hardware revision 1.30, DAC1 is always

enabled and does not affe ct the analog inputs.

The previous information assumed that DAC1 is disabled. If DAC1 is enabled, then the internal reference (Vref = 2.44 volts) is not

available for the ADC, and instead the internal regulator voltage (Vre g = 3.3 volts) is used as the reference for the AD C. Vreg is

not as sta ble as Vref, but more stable than Vs (5 volt power supply). Following are the nominal input voltage ranges for the analog

inputs, assuming that DAC1 is enabled.

Max V

Min V

Single-Ended

3.30Differential

3.3

-3.3

Special -10/+20

N/A

N/A

Table 2. 6.2.1-1. Nomina l Analog I nput Voltage Ranges (DAC1 Enable d)

Note that the minimum differential input voltage of -3.3 volts means that the positive channel can be as much as 3.3 volts less than

the nega tive channel, not that a channel can measure 3.3 vo lts less than ground. The voltage of any analog input pi n, compared to

ground, must be in the range -0.3 to +3.6 volts, for specified performance. See Appendix A for voltage limits to avoid damage.

Negative channel numbers 30 and 32 are not valid with DA C1 enabled.

When DAC1 is enabled, the slope/offset calibration co nstants are not used to convert raw readings to voltages. Rather, the Vreg

value is retrieved from the Mem area, and used with the approximate single-ended or differential conversion equations above,

where Span i s Vreg (single-ended) or 2Vreg (differential).

2.6.3 - Typical Analog Input Connections

A common question is “can this sensor/signal be measured with the U3”. Unless the signal has a voltage (referred to U3 ground)

beyond the limits in Appendix A , it can be connected without damaging the U3, b ut more thought is required to determine what is

necessary to make useful measurements with the U3 or any measurement devi ce.

Voltage (versus ground): The single-ended analog inputs on the U3 measure a voltage with respect to U3 ground. The differential

inputs measure the voltage difference between two channels, but the voltage on each cha nnel with respect to ground must sti ll be

within the common mode limits specified in Appendix A. When measuring parameters other than voltage, or volta ges too big or

too small for the U3, some sort of sensor or transducer is required to produce the proper voltage signal. Examples are a

temperature sensor, amplifier, resistive voltage divider, or perhaps a combination of such things.

Impedance: When connecting the U3, or any measuring device, to a signal source, it must be considered what impact the

measuring devi ce will have on the signal. The main consideration is whether the currents going into or out of the U3 analog input

will cause noticeable voltage errors due to the impedance of the source. To maintain consistent 1 2-bit results, it is recommended

to keep the source impedance within the limits specified in App endix A.

Resolution (and Accuracy): Based on the measurement type and resolution of the U3, the resolution can be determined in terms of

voltage or engineering units. For example, assume some temperature sensor provi des a 0-10 mV signal, corresponding to 0-100

degrees C. Samples are then acquired with the U3 using the 0-2.44 volt single-ended input range, resulting in a voltage resolution

of about 2.44/4096 = 596 µV. That means there wi ll be about 17 discrete steps across the 10 mV span of the signal, and the

temperature resolution is about 6 degrees C. If this experiment re quired a resolution of 1 degrees C, this configuration would not

be sufficient. Accuracy will also need to be considered. Appendix A places some boundaries on expected accuracy, but an insystem calibration can generally be done to provide absolute accuracy down to the linearity (INL) li mits of the U3.

Speed: How fast does the signal need to be sampled? For instance, if the sig nal is a waveform, what information is needed: peak,

average, RMS, shape, frequency, … ? Answers to these questions will help decid e how many points are needed per waveform

cycle, a nd thus what sampling rate is required. In the case of multiple channels, the scan rate is also consi dered. See Sections 3.1

and 3.2.

2.6.3.1 - Signal from the LabJack

One example of measuring a signal from the U3 i tself, is wi th an analog output. All I/O on the U3 share a common ground, so the

voltage on an analog output (DAC) can be measured by simply connecting a single wire from that terminal to an AIN te rminal

(FIO/E IO). The analog output must be set to a voltage within the range of the analog input.

2.6.3.2 - Unpowered Isolated Signal

An example of an unpowered isolated signal would be a photocell where the sensor leads are not shorted to any external voltages.

Such a sensor typi cally has two leads, where the posi tive lead connects to an AIN terminal and the negative lead connects to a

GND terminal.

2.6.3.3 - Signal Powered By the LabJack

A typi cal example of thi s type of signal is a 3-wi re temperature sensor. The sensor has a power and ground wire that connect to Vs

and GND on the LabJack, and then has a signal wire tha t simply connects to an AIN terminal.

8

Page 9

Another variation is a 4-wire sensor where there are two signal wires (positive and nega tive) rather than one. If the negative signal

is the same as power ground, or can be shorte d ground, the n the positive signal can be connected to AIN a nd a single-ended

measurement can be made. A typical example where this does not work is a bridge type sensor, such as pressure sensor,

providing the raw bridge output (and no amplifier). In this case the signal voltage is the difference between the positive and

negative signal, and the negative signal ca nnot be shorted to ground. Such a signal could be measured using a differenti al input

on the U3.

2.6.3.4 - Signal Powered Externally

An example is a box wi th a wire coming out that is defined as a 0-2 volt analog signal and a second wire labeled as ground. The

signal is known to have 0-2 volts compared to the ground wire, but the complication is what is the voltage of the box ground

compared to the LabJack ground.

If the box is known to be electrically isolated from the LabJack, the box ground can simply be connected to LabJack GND . An

example would be if the box was plastic, powered by an internal battery, and does not have any wires besides the signal and

ground which a re connected to AINx and GND on the LabJack.

If the box ground is known to be the same as the LabJack GND, then perhaps only the one signal wire needs to be connected to

the LabJack, but it generally does not hurt to go ahead and connect the ground wire to LabJack GND with a 100 Ω resistor. You

definitely do not want to connect the grounds without a resistor.

If little is known about the box ground, a DMM can be used to measure the voltage of box ground compared to LabJack GND. As

long as an extreme voltage is not measured, it is generally OK to connect the box ground to LabJack GND, b ut it is a good idea to

put in a 100 Ω series resistor to prevent large currents from flowing on the ground. Use a small wattage resistor (typi cally 1/8 or 1/4

watt) so that i t blows if too much current does flow. The only current that should flow on the ground is the return of the analog inp ut

bias current, whi ch is only microamps.

The SGND terminals (on the same terminal block as SPC) can be used instead of GND fo r externally powered signals. A series

resistor is not needed as SGND is fused to prevent overcurrent, but a resistor will eliminate confusion that can be caused if the

fuse is tri pping and resetting .

In general, if there is uncertainty, a good approach is to use a DMM to measure the voltage on each sig nal/ground wi re without any

connections to the U3. If no large voltages are noted, connect the ground to U3 SGND with a 100 Ω series resistor. Then again use

the DMM to measure the voltage of each signal wi re before connecting to the U3 .

Another g ood general rule is to use the minimum number of ground connections. For instance, if connecting 8 sensors powered by

the same external supply, or otherwise referred to the same external ground, only a single ground connection is needed to the U3.

Perhaps the ground leads from the 8 sensors would be twisted together, and then a single wire would be connected to a 100 Ω

resistor which is conne cted to U3 ground.

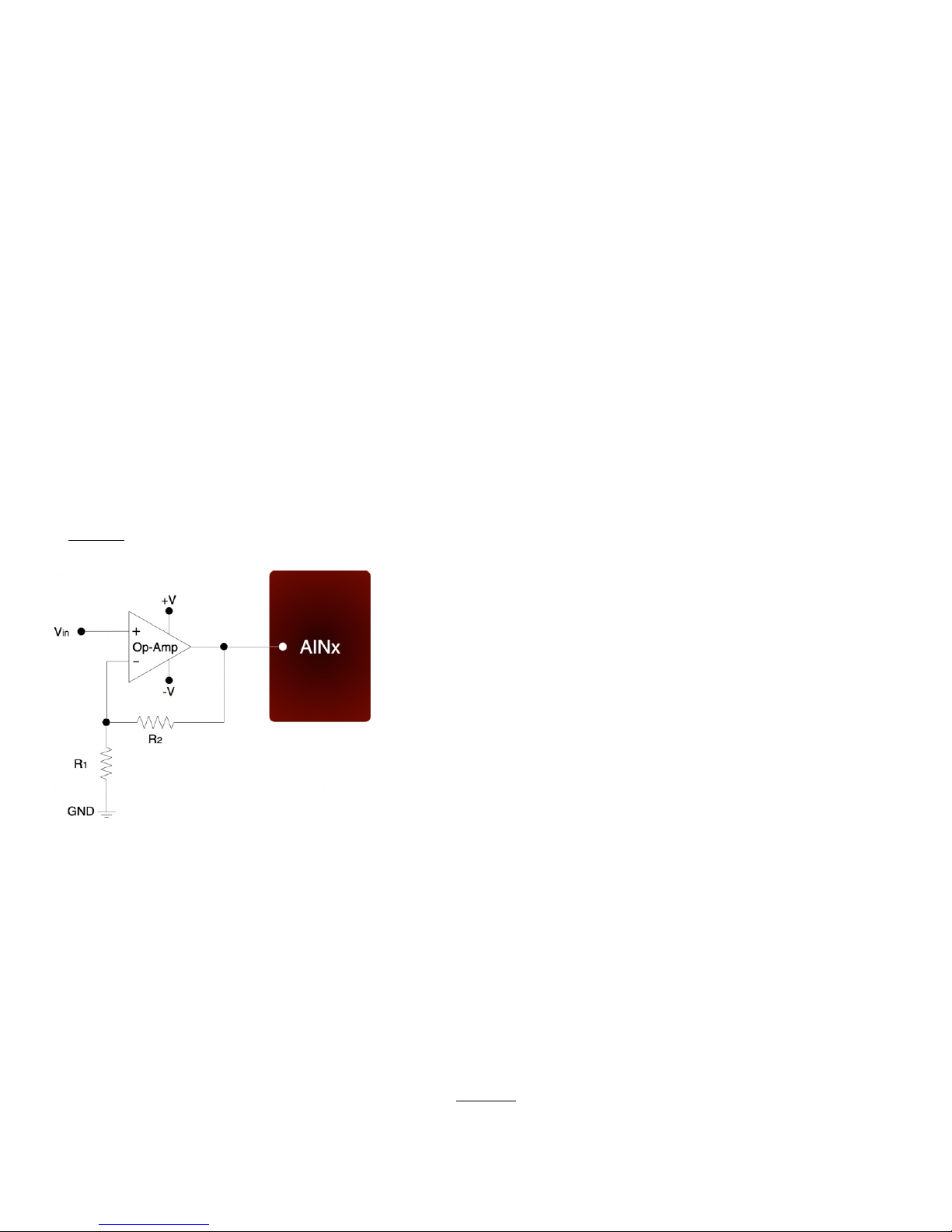

2.6.3.5 - Amplifying Small Signal Voltages

The best results are generally obtained when a signal voltage spans the full analog input range of the LabJack. If the signal is too

small it can be amplified before connecting to the LabJack. One good way to handle low-level signals such as thermocouples is

the LJTick-InA mp, whi ch is a 2-cha nnel instrumentation amplifier module that plugs into the U3 screw-terminals.

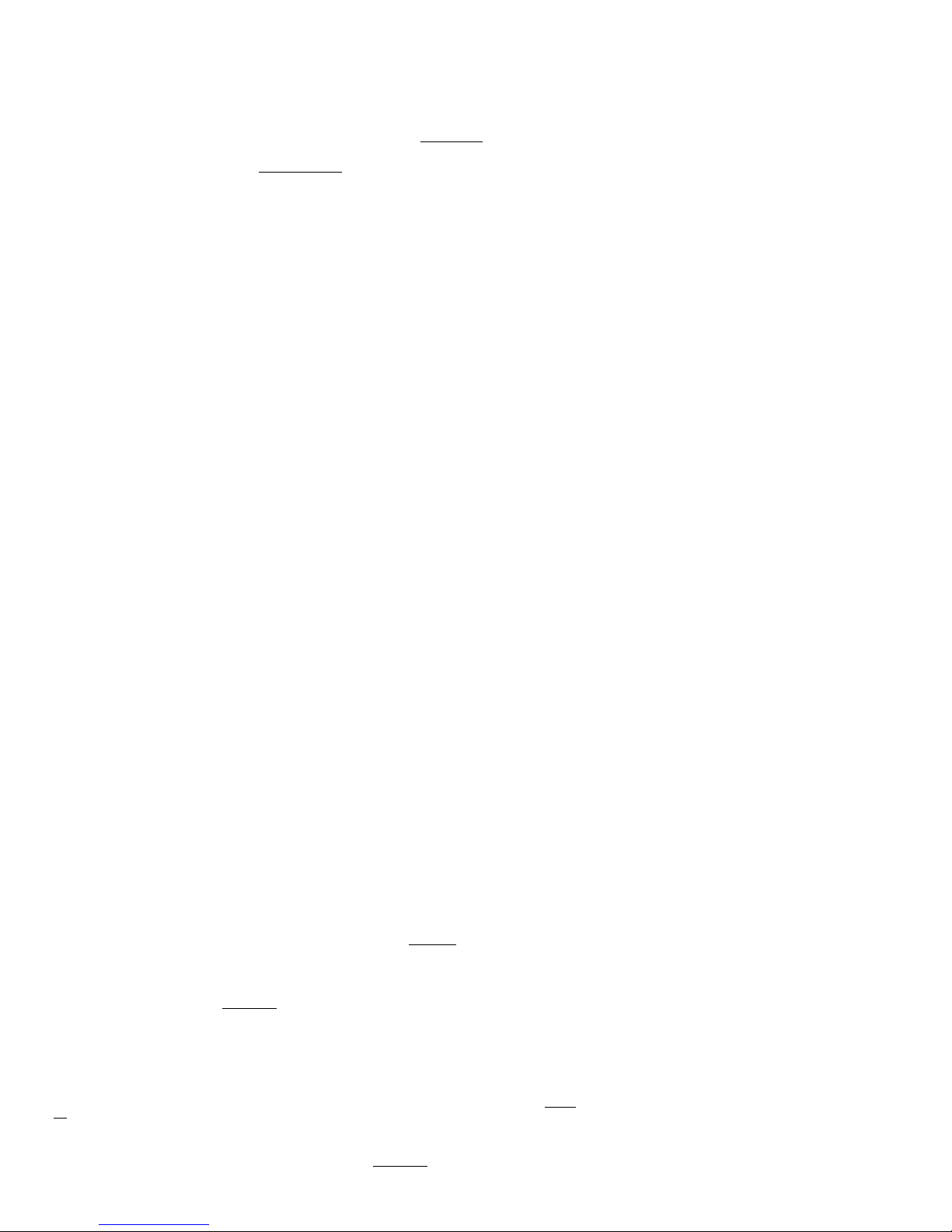

For a do-it-yourself solution, the following figure shows an operational amplifier (op-amp) configured as non-inve rting:

Figure 2.6-1. Non-Inverting Op-Amp Configuration

The gain of thi s configuration is:

Vout = Vin * (1 + (R2/ R1))

100 kΩ is a typical value for R2. Note that if R2=0 (short-circuit) and R1=inf (not installed), a simple buffer with a gain equal to 1 is

the result.

There are numerous criteria used to choose an op-amp fro m the thousands that are avai lable. One of the main criteria is that the

op-amp can handle the input and output signal range. Often, a single-supply rail-to-rail input and output (RIRO) is used as it can be

powered from Vs and GND and pass signals withi n the range 0-Vs. The OPA344 from Texas Instruments (ti.com) is good for many

5 volt applications.

The op-amp is used to amplify (and buffer) a signal that is referred to the same ground as the LabJack (single-ended). If instead

the signal is differential (i.e. there is a positive and negative signal both of which are different than ground), an i nstrumentation

amplifier (in-amp) should be used. An in-amp converts a differential signal to single-ended, and generally has a simple method to

set gain.

2.6.3.6 - Signal Voltages Beyond 0-2.44 Volts (and

Resistance Measurement)

The normal input range for a low voltage analog input channel (FIO/E IO) on the U3 is about 0-2.44 volts. There is also a Special 0-

3.6V range available on those inputs. The easiest way to handle la rger voltages is often by usi ng the LJTick-Di vider, which is a two

channel buffered divider module tha t plugs into the U3 screw-terminals.

The basic way to handle higher unipolar voltages is with a resistive voltage divider. The following figure shows the resistive voltage

divider assuming that the source voltage (Vin) is referred to the same ground as the U3 (GND).

9

Page 10

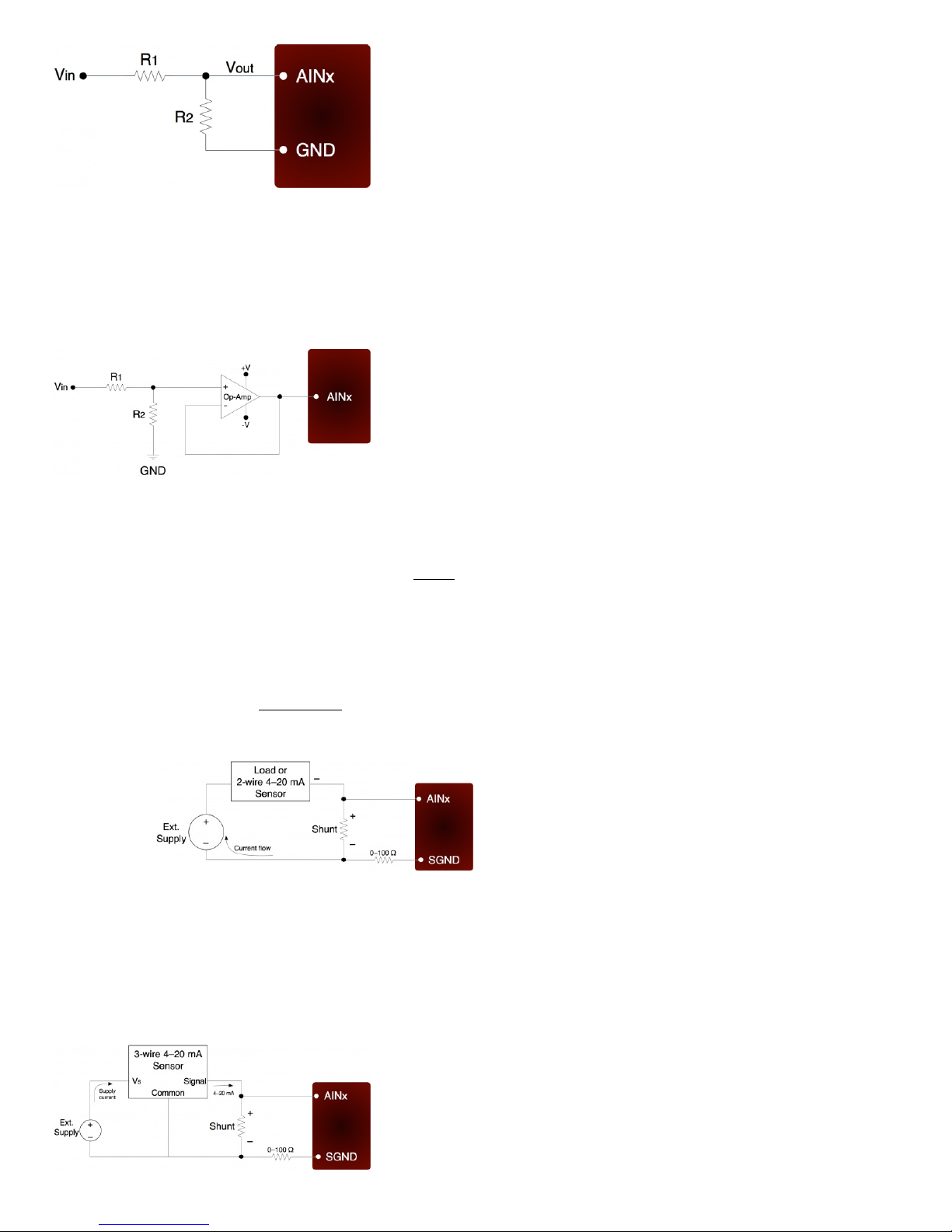

Figure 2.6-2. Vo ltage Divider Circuit

The attenuation of this circuit i s determined by the equation:

Vout = Vin * ( R2 / (R 1+R2))

This divider is easily implemented by putting a resistor (R1) in series with the signal wire, and placing a second resistor (R2) from

the AIN terminal to a GND terminal. To maintain specified analog input performance, R1 should not excee d the values specified in

Appendix A, so R1 can generally be fixed at the max recommended value and R2 can be adjusted for the desi red attenuation.

The divide by 2 configuration where R1 = R2 = 10 kΩ (max source impedance limit for lo w-voltage channels), presents a 20 kΩ

load to the source, meaning that a 5 volt signal will have to be able to source/sink up to +250 µA. Some signal sources might

require a load with hi gher resistance, in which case a buffer should be used. The following figure shows a resistive voltage divider

followed by an op-amp configured as non-inverti ng unity-gain (i.e. a buffer).

Figure 2.6-3. Buffered Voltage Divider Circuit

The op-amp is chosen to have low input bias currents so that large resistors can be used in the voltage divider. For 0-5 volt

applications, where the amp will be powered from Vs and GND, a good choice would be the OPA344 from Texas Instruments

(ti.com). The OPA344 has a very small bias current that changes li ttle across the entire voltage range. Note that when powering the

amp from Vs and GND, the input and output to the op-amp is limited to that range, so if Vs is 4.8 volts your signal range will be 0-

4.8 volts.

To handle bipolar voltages, you also need offset or level-shifting. Refer to application note SLOA097 from ti .com for more

information.

The information above also applies to resistance measurement. A common way to measure resistance is to build a voltage

divider as shown in Figure 2.6-2, where one of the resistors is known and the other is the unknown. If Vin is known and Vout is

measured, the vo ltage divider equation can be re arranged to solve for the unknown resistance.

2.6.3.7 - Measuring Current (Including 4-20 mA) with a

Resistive Shunt

The best way to handle 4-20 mA si gnals is with the LJTick-CurrentS hunt, which is a two cha nnel active current to voltage converter

module that plugs into the UE 9 screw-terminals.

The following figure shows a typical metho d to measure the current through a load, or to measure the 4-20 mA signal produced by

a 2-wire (loop-powered) current loop sensor. The current shunt shown in the figure is simply a resistor.

Figure 2.6-4. Current Measurement With Arbitrary Load or 2-Wire 4-20 mA Sensor

When measuring a 4-20 mA signal, a typi cal value for the shunt would be 120 Ω. This results in a 0.48 to 2.40 volt signal

corresponding to 4-20 mA. The external supply must provide enough voltage for the sensor and the shunt, so if the senso r requires

5 volts the supply must provide at least 7.4 volts.

For applications besides 4-20 mA, the shunt is chosen based on the maximum current and how much voltage drop can be

tolerated across the shunt. For instance, if the maximum current is 1.0 amp, and 1.0 volts of drop is the most that can be tolerated

without affecting the load, a 1.0 Ω resistor could be used. That equates to 1.0 watts, though, which would require a special high

wattage resistor. A better solution would be to use a 0.1 Ω shunt, and then use an amplifier to increase the small voltage produced

by that shunt. If the maxi mum current to measure is too high (e.g. 100 amps), it will be difficult to find a small enough resistor and a

hall-effect sensor should be considered instead of a shunt.

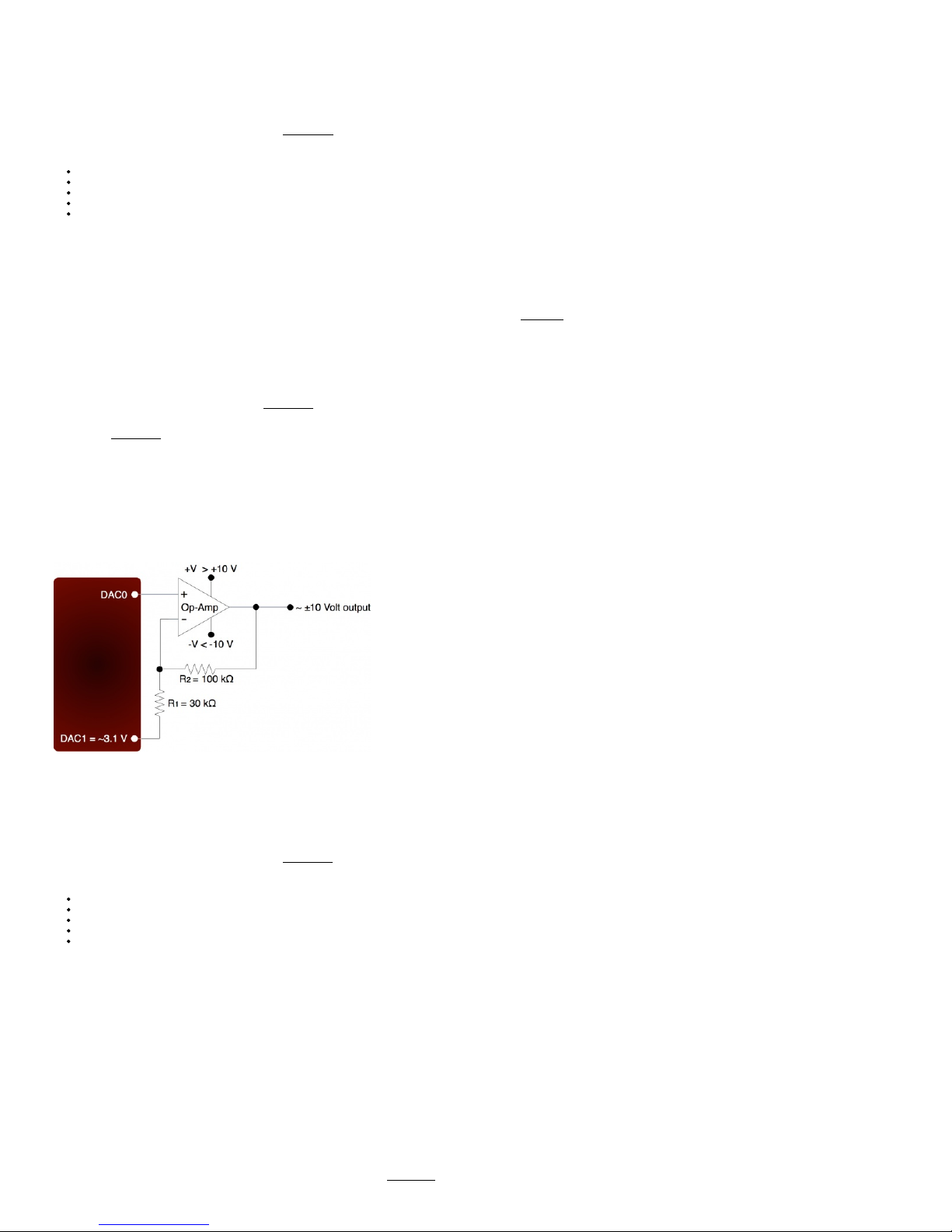

The following figure shows typical connections for a 3-wire 4-20 mA sensor. A typical value for the shunt would be 120 Ω which

results in 0.48 to 2.40 volts.

Figure 2.6-5. Current Measurement With 3-Wire 4-20 mA (Sourcing) Sensor

10

Page 11

The sensor shown in the above figure is a sourcing type, where the signal sources the 4-20 mA current which is then sent through

the shunt resistor and sunk into ground. A nother type of 3-wire sensor is the sinking type, where the 4-20 mA current is sourced

from the posi tive supply, sent through the shunt resistor, and then sunk into the signal wire. If sensor ground is connected to U3

ground, the sinking type of sensor presents a problem, as at least one side of the resistor has a high common mode voltage

(equal to the positive sensor supply). If the sensor is isolated, a possible solution is to connect the sensor signal or positive sensor

supply to U3 ground (instead of sensor ground). This requires a good understanding of grounding and isolation in the system. The

LJTick-CurrentS hunt is often a simple solution.

Both figures show a 0-100 Ω resistor in series with SGND, which i s discussed in general in Section 2.6.3.4. In this case, if S GND

is used (rather than GND), a direct connection (0 Ω) should be good.

The best way to handle 4-20 mA si gnals is with the LJTick-CurrentS hunt, which is a two cha nnel active current to voltage converter

module that plugs into the U3 screw-terminals.

2.6.3.8 - Floating/Unconnected Inputs

The reading from a floating (no external co nnection) analo g input channel can be tough to predict and is likely to vary wi th sample

timing and adjacent sampled channels. Keep in mi nd that a floating channel is not at 0 volts, but rather is at an undefined voltage.

In order to see 0 volts, a 0 volt signal (such as GND) should be connected to the input.

Some data acquisition devices use a resistor, from the input to ground, to bias an unconnected input to read 0. This is often just

for “cosmetic” reasons so tha t the input reads close to 0 with floating inputs, and a reason not to do that is that thi s resistor can

degrade the input impedance of the analog input.

In a situation whe re it is desired that a floating channel re ad a particular voltage, say to detect a broken wire, a resistor (pull-down

or pull-up) can be placed from the AINx screw terminal to the desi red volta ge (GND, VS, DACx, …). A 100 kΩ resistor should pull

the analog input readings to wi thin 50 mV of any desired voltage, but obviously degrades the input impedance to 100 kΩ. For the

specific case of pulling a floating channel to 0 volts, a 1 MΩ resistor to GND can typically be used to provide analog input readings

of less than 50 mV. This information is for a low-voltage analog input channel on a U3.

Note that the four high-voltage channels on the U3 -HV do sit at a predictable 1.4 volts. You can use a pull-down or pull-up resistor

with the high-voltage inputs, but because thei r input impedance is lower the resistor must be lower (~1k might be typical) and thus

the signal is going to have to drive substantial current.

2.6.3.9 - Signal Voltages Near Ground

The nominal input range of a low-voltage single-ended analog input is 0-2.44 volts. So the nominal minimum voltage is 0.0 volts,

but the variation in that minimum can be about +/-40 mV, and thus the actual minimum voltage could be 0.04 volts.

This is not an offset erro r, but just a minimum limit. Assume the minimum limit of your U3 happens to be 10 mV. If you apply a

voltage of 0.02 volts it will read 0.02 volts. If you apply a voltage of 0.01 volts it will read 0.01 volts. If you apply a voltage less than

0.01 volts, however, it will still read the minimum limi t of 0.01 volts in thi s case.

One impact of this, is that a short to GND is usually not a good test for noise and accuracy. We often use a 1.5 volt battery for

simple tests.

If performance all the way to 0.0 is needed, use a differential reading (which is pseudobipolar). Connect some other channel to

GND with a small jumper, and then take a differential re ading of your channel compared to that grounded channel.

The nominal input range of a high-voltage single-ended analog input is +/-10 volts, so readings around 0 .0 are right in the middle

of the range and not a n issue.

2.6.4 - Internal Temperature Sensor

The U3 has an internal temperature sensor. Although this sensor measures the temperature inside the U3, which is warmer than

ambient, it has been calibrated to read actual ambient te mperature, although should only be expected to be accurate to withi n a

few degrees C. For best results the temperature o f the entire U3 must stabilize relative to the ambient temperature, whi ch can take

on the order of 1 hour. Best results will be obtained in still air in an environment with slowly changing ambient temperatures.

With the UD driver, the internal temperature sensor is read by acquiring single-ended analo g input channel 30, and returns

degrees K. Use channel 30 anywhere you would use an analog input channel (e.g. wi th eAIN).

2.7 - DAC

The LabJack U3 has 2 analog outputs (DAC0 and DAC1) that are available on the screw terminals. E ach analog output can be

set to a voltage between about 0.04 and 4.95 volts with 10 bits of resolution (8 bits on older hardware revision 1.20/1.21). The

maximum output voltage is limited by the supply voltage to the U3.

Starting with hardware revision 1.30, DAC1 is always enabled and does not affect the analog inputs, but with older hardware the

second analog output is only available in certain co nfigurations. With hardware revisions <1.30, if the analog inp uts are using the

internal 2.4 volt reference (the most accurate option), then DAC1 outputs a fixed voltage of 1.5*Vref. Also with hardware revisions

<1.30, if DAC1 is enabled the analog inputs use Vreg (3.3 volts) as the AD C reference, which is not as sta ble as the internal 2.4

volt reference.

The DAC outputs are derived as a percentage of Vreg, and then amplified by 1.5, so any changes in Vreg will have a

proportionate affect on the DAC outputs. Vre g is more stable than Vs (5 volt supply voltage), as it is the output from a 3.3 volt

regulator.

The DACs are derived from PWM signals that are affected by the timer clock frequency (Section 2.9). The default timer clock

frequency of the U3 is set to 48 MHz, and this results in the minimum DAC output noise. If the frequency is lowered, the DACs will

have more noise, where the frequency of the noise is the timer clock frequency divided by 6 5536. This effect is more exaggerated

with the 10-bit DAC s on hardware revision 1.30+, compared to the 8-bit DACs on previous hardware revisions. The noise with a

timer clock of 48/12/4/1 MHz is roughly 5/20/100/600 mV. If lower noise performance is needed at lo wer timer clock frequencies,

use the power-up default setting in LJControlPanel to force the device to use 8-bit DAC mode (uses the low-level

CompatibilityOptions byte documented in Section 5.2.2). A large capacitor (at least 220 uF) from DAC n to GND can also be used

to reduce noi se.

The analog outputs have filters with a 3 dB cutoff around 16 Hz, limiting the frequency of output waveforms to less than that.

The analog output commands are sent as raw binary values (low level functions). For a desired output voltage, the binary value can

be approximated as:

Bits(un calibrat ed) = ( Volts/4. 95)*256

For a proper calculation, though, use the calibration values (Slope and Offset) stored in the internal flash on the processor (Section

5.4):

Bits = (Slope * Volts) + Offse t

The previous apply when usi ng the original 8-bit DAC commands suppo rted on all hardware versions. To take advantage of the

10-bit resolution on hardware revision 1.30, new commands have been added (Section 5.2.5) where the binary values are aligned

to 16-bits. The cal constants are still alig ned to 8-bits, however, so the slope and offset sho uld each be multiplied by 256 before

11

Page 12

using in the above formula.

The analog outputs can withstand a continuous short-circuit to ground, even when set at maximum output.

Voltage sho uld never be applied to the analog outputs, as they are voltage sources themselves. In the event that a voltage is

accidentally applied to either analog output, they do have protection against transi ent events such as ESD (electrostatic

discharge) and continuous overvoltage (or undervoltage) of a few volts.

There is an accessory available from LabJack called the LJTick-DAC that provid es a pair of 14-bit analog outputs with a rang e of

±10 volts. The LJTick-DAC plugs into any digital I/O block, and thus up to 10 of these can be used per U3 to add 20 ana log

outputs. The LJTick-DAC has various improvements compared to the built-in DACs on the U3:

Range of +10.0 to -10.0 volts.

Resolution of 14-bits.

Slew rate of 0.1 V/μs.

Based on a reference , rather than regulator, so more accurate and stable.

Does not affect analog inputs in any configura tion.

2.7.1 - Typical Analog Output Connections

2.7.1.1 - High Current Output

The DACs on the U3 can output quite a bit of current, but they have 50 Ω of source impedance that will cause voltage drop. To

avoid this voltage drop, an op-amp can be used to buffer the output, such as the non-inverting configuration shown in Figure 2-3. A

simple RC filter can be added between the DAC output and the amp input for further noise reduction. Note that the ability of the

amp to source/sink current near the power rails must still be considered. A possible op-amp choice would be the TLV246x family

(ti.com).

2.7.1.2 - Different Output Ranges

See the end of thi s section for information about the LJTick-D AC which has a +/-10V range.

The typical output range of the DACs is about 0.04 to 4.95 volts. For other unipolar ranges, an op-amp in the non-inverting

configuration (Figure 2.6-1) ca n be used to provi de the desired gain. For e xample, to increase the maximum output from 4.95 volts

to 10.0 volts, a gain of 2.02 is requi red. If R2 (in Figure 2-3) is chosen as 100 kΩ, then an R1 of 97.6 kΩ is the clo sest 1% resistor

that provides a gain greater than 2.02. The +V supply for the op-amp would have to be greater than 10 volts.

For bipolar output ranges, such as ±10 volts, a similar op-amp circuit can be used to provide gain and offset, but of course the opamp must be powered with supplies greater than the d esired output range (depending on the ability of the op-amp to drive it’s

outputs close to the power rai ls). If ±10, ±12, or ±15 volt supplies are available, consi der using the LT1490A op-amp (linear.com),

which can handle a supply span up to 44 volts.

A reference voltage is also required to provide the offset. In the following circuit, D AC1 is used to provide a reference voltage. The

actual value of DAC1 can be adjusted such that the circuit output is 0 volts at the DAC0 mid-scale voltage, and the value of R1 can

be adjusted to get the desired gain. A fixed reference (such as 2.5 volts) could also be used instead of DAC1.

Figure 2.7-1. ±10 Volt DAC Output Circuit

A two-point calibration should be done to determine the exact i nput/output relationship of this circuit. Refer to application note

SLOA097 from ti.com for further information about gain and offset design with op-amps.

LJTick-DAC:

There is an accessory available from LabJack called the LJTi ck-DAC that provides a pair of 14-bit analog outputs with a range of

±10 volts. The LJTick-DAC plugs into any digital I/O block, and thus up to 10 of these can be used per U3 to add 20 analog

outputs. The LJTick-DAC has various improvements compared to the built-in DACs on the U3:

Range of +10.0 to -10.0 volts.

Resolution of 14-bits.

Slew rate of 0.1 V/μs.

Based on a reference , rather than regulator, so more accurate and stable.

Does not affect analog inputs in any configura tion.

2.8 - Digital I/O

The LabJack U3 has up to 20 digital I/O channels. 16 are available from the flexible I/O lines, and 4 dedicated digital I/O (CIO0CIO3) are available on the DB15 connector. The first 4 lines, FIO0-FIO3, are unavailable on the U3-HV. Each digital line can be

individually configured as input, output-high, or output-low. The digital I/O use 3.3 volt logic and are 5 volt tolerant.

The LabJackUD driver uses the following bit numbers to specify all the di gital lines:

0-7 FIO0-FIO 7 (0-3 unavail able on U3-HV)

8-15 EIO0-EIO 7

16-19 CIO0-CIO 3

The 8 FIO lines appear on the built-in screw-terminals, while the 8 EIO and 4 CIO li nes appear only on the DB15 connector. See

the DB15 Section of this User’ s Guide for more information.

All the digital I/O include an internal series resistor that provi des overvoltage/short-circuit protection. These series resistors also

limit the ability of these lines to sink or source current. Refer to the speci fications in Appendix A .

12

Page 13

All digital I/O on the U3 have 3 possible states: input, output-hig h, or output-low. Each bit of I/O can be configured individually.

When configured as an input, a bit has a ~100 kΩ pull-up resistor to 3.3 volts (all digital I/O are 5 volt tolerant). When configured as

output-high, a bit is connected to the internal 3.3 volt supply (through a series resistor). When configured as output-low, a bit is

connected to GND (through a series resistor).

The fact that the digital I/O are specified as 5-volt tole rant means that 5 volts can be connected to a digital input without problems

(see the actual li mits in the speci fications in Appendix A). If 5 volts i s needed from a digital output, consider the following solutions:

In some cases, an open-collector style output can be used to get a 5V signal. To g et a low set the line to output-low, and to

get a high set the line to input. When the line is set to input, the voltage on the line is determined by a pull-up resistor. The

U3 has an internal ~100k resistor to 3.3V, but an external resistor can be added to a different voltage. Whether this will work

depends on how much current the load is going to draw and what the required logic thresholds are. Say for example a 10k

resistor is added from EIO0 to VS. EIO0 ha s an internal 100k pull-up to 3.3 volts and a series output resistance of about 180

ohms. Assume the load draws just a few microamps or less and thus is negligible. When EIO0 is set to input, there will be

100k to 3.3 volts in p arallel with 10k to 5 volts, and thus the line wi ll sit at about 4.85 volts. When the line is set to output-low,

there wi ll be 180 ohms in series with the 10k, so the line will be pulled down to about 0.1 volts.

The surefire way to get 5 volts from a digital output is to add a simple logic buffer IC that is powered by 5 volts and

recognizes 3.3 volts as a high input. Consider the CD74ACT541E from TI (or the inverti ng CD74ACT540E). All that is

needed is a few wi res to bring VS, GND, and the signal from the LabJack to the chip. This chip can level shi ft up to eight

0/3.3 volt signals to 0/5 vo lt signals and provi des high output drive current (+/-24 mA).

Note that the 2 DAC channe ls on the U3 can be set to 5 volts, providing 2 output lines with such capability.

The power-up condition of the digital I/O can be configured by the user with the "Config Defaults" option in LJControlP anel. F rom

the factory, all digital I/O are configured to power-up as inputs. Note that even if the power-up default for a line is changed to

output-high or output-low, there is a delay of a bout 5 ms at power-up where all digital I/O are in the factory default condition.

If you want a floating digital input to read low, an external pull-down resistor can be added to overpower the internal 100k pull-up.

4.7k to 22k would be a typical range for thi s pull-down, with 10k being a solid choice for most applications.

The low-level Feedback function (Section 5.2.5) writes and reads all digital I/O. For information about usi ng digital I/O under the

Windows LabJackUD driver, see Section 4.3.5. See Section 3.1 for timi ng information.

Many function parameters contain specific bits within a single integer parameter to write/read specific information. In particular,

most digital I/O parameters contain the information fo r each bit of I/O in one integer, where each bit of I/O corresponds to the same

bit in the parameter (e.g. the direction of FIO0 is set in bit 0 of parameter FIOD ir). For instance, in the low-level function ConfigU3,

the parameter FIODirection is a single byte (8 bits) that writes/reads the power-up direction of each of the 8 FIO lines:

if FIODirection is 0, all FIO lines are input,

if FIODirection is 1 (20), FIO0 is output, FIO1-FIO7 are input,

if FIODirection is 5 (20 + 22), FIO0 and FIO2 are output, all other FIO lines are input,

if FIODirection is 255 (20 + … + 27), FIO0-FIO7 are output.

2.8.1 - Typical Digital I/O Connections

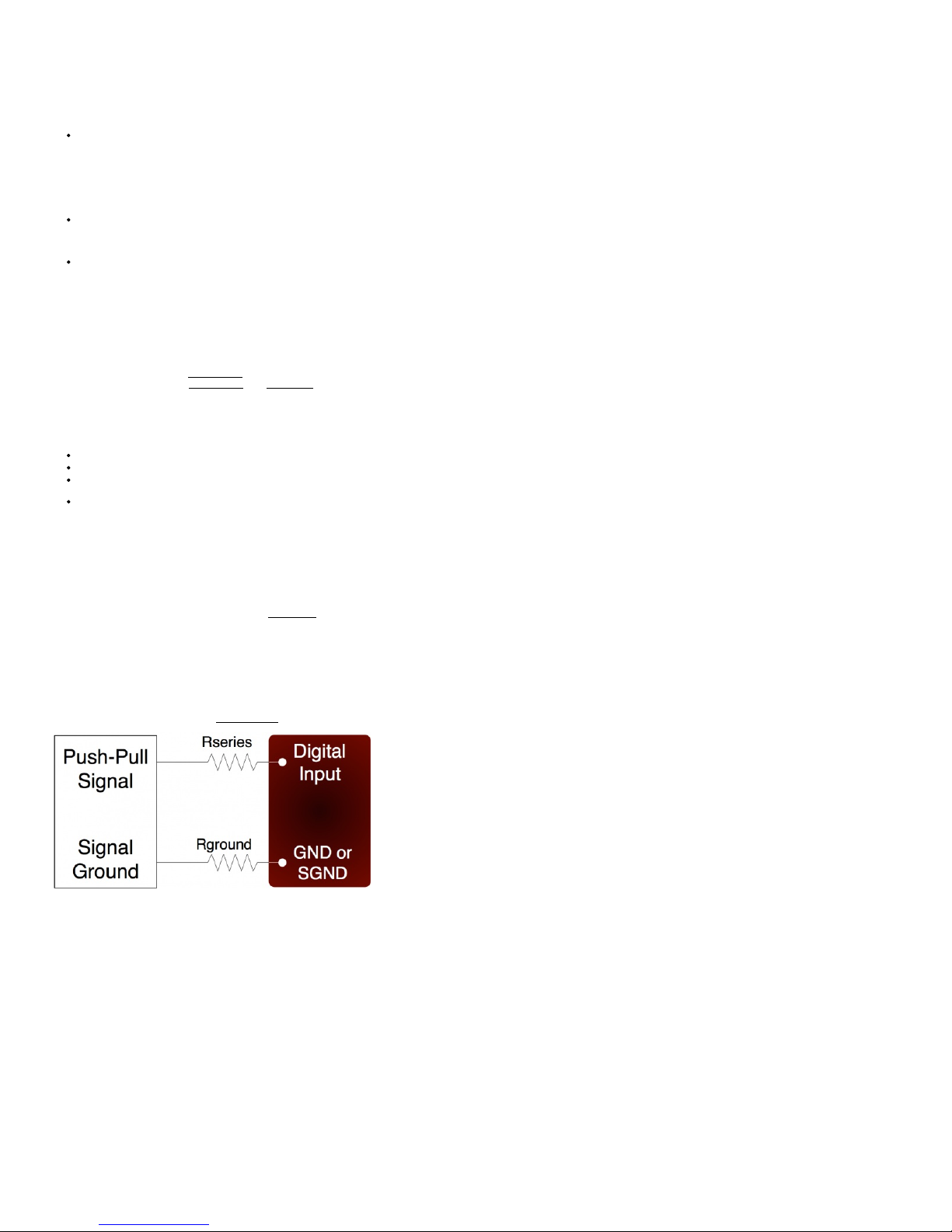

2.8.1.1 - Input: Driven Signals

The most basic connection to a U3 digital input i s a driven si gnal, often called push-pull. With a push-pull signal the source is

typically providing a high voltage for logic high and zero volts for logic low. Thi s signal is generally connected directly to the U3

digital input, considering the voltage specifications in Appendix A . If the sig nal is over 5 volts, it can still be connected with a series

resistor. The digital inputs have protective devices that clamp the voltage at GND and VS, so the series resistor is used to limit the

current through these protective devices. For instance, i f a 24 volt signal is connected through a 22 kΩ series resistor, a bout 19

volts will be dropped across the resistor, resulting in a current of 0.9 mA, which is no problem for the U3. The series resistor should

be 22 kΩ or less, to make sure the voltage on the I/O line when low is pulled below 0.8 volts.

The other possible consideration with the basic push-pull signal is the ground connection. If the signal is known to already have a

common ground with the U3, then no additional ground connection is used. If the signal is known to not have a common ground

with the U3, then the signal ground can simply be connected to U3 GND . If there is uncertainty about the relationship between

signal ground and U3 ground (e.g. possible common ground through AC mains), then a ground connection with a ~10 Ω series

resistor is generally recommended (see Section 2.6.3.4).

Figure 2.8-1. Driven Si gnal Connection To Digital Input

Figure 2.8-1 shows typical connections. Rground is typically 0-100 Ω. Rseries is typically 0 Ω (short-circuit) for 3.3/5 volt logic, or

22 kΩ (max) for hi gh-voltage logic. Note that an individual ground connection is often not needed for every signal. Any si gnals

powered by the same external supply, or otherwise referred to the same external ground, should share a sing le ground connection

to the U3 if possible.

When dealing with a new sensor, a push-pull signal is often incorrectly assumed when in fact the sensor provi des an open-collector

signal as described next.

2.8.1.2 - Input: Open-Collector Signals

Open-collector (also called open-drain o r NPN) is a very common type of digital signal. Rather than providing 5 volts and ground,

like the push-pull signal, an open-collector signal provides ground and hi gh-impedance. This type of signal can be thought of as a

switch connected to ground. Since the U3 digital inputs have a 100 kΩ internal pull-up resistor, an open-collector signal can

generally be connected directly to the input. When the signal is inactive, it is not drivi ng any voltage and the pull-up resistor pulls the

digital input to logic high. When the signal is active, it drives 0 volts which overpowers the pull-up and pulls the digital input to logic

low. Sometimes, an external pull-up (e.g. 4.7 kΩ from Vs to digital input) will be installed to increase the strength and speed of the

logic high condition.

13

Page 14

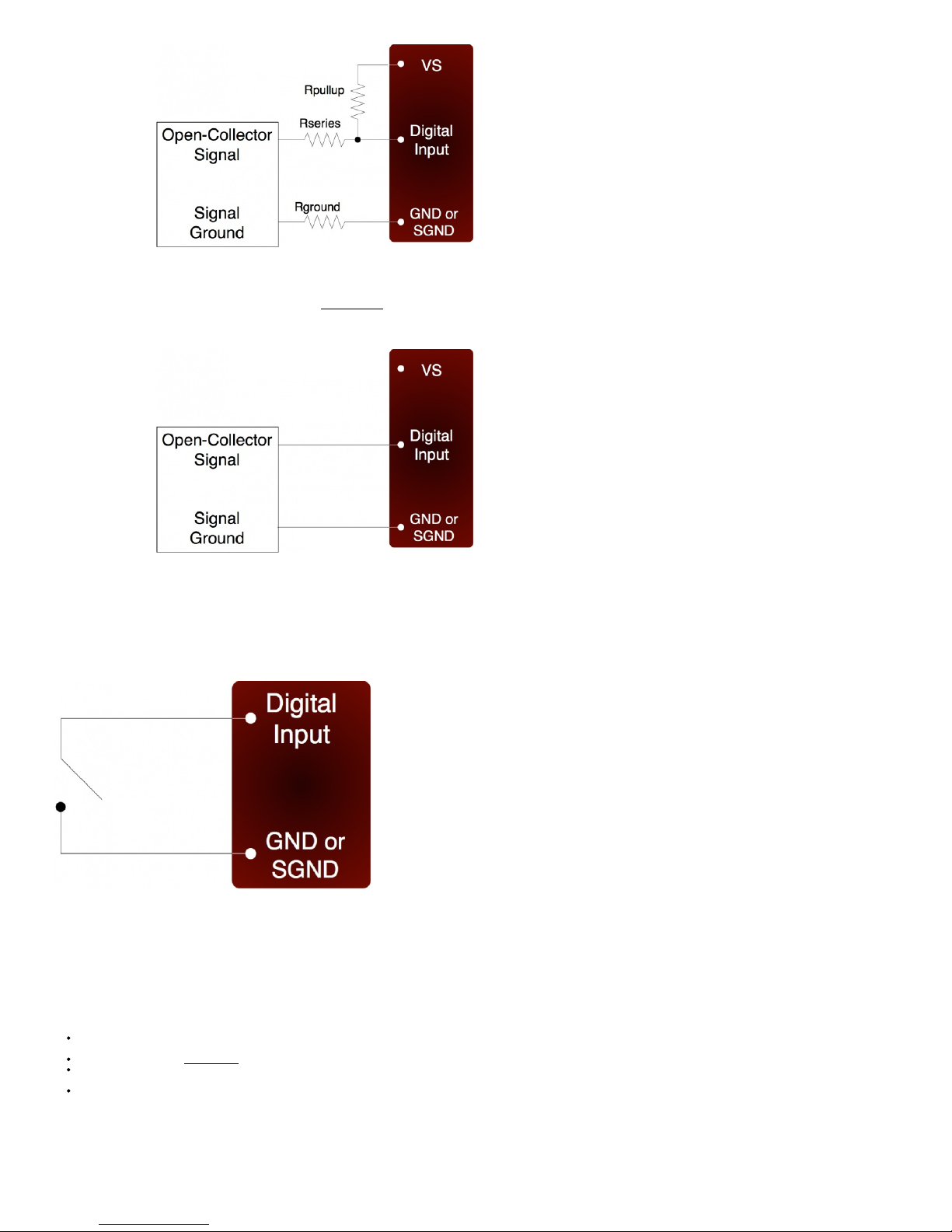

Figure 2.8-2. Open-Collector (NPN) Connection To Digital Input

Figure 2.8-2 shows typical connections. Rground is typically 0-100 Ω, Rseries is typically 0 Ω, and Rpullup, the external pull-up

resistor, is generally not required. If there is some uncertainty about whethe r the signal is really open-collector or could drive a

voltage beyond 5.8 volts, use an Rseries of 22 kΩ as discussed in Section 2.8.1.1, and the input should be compatible with an

open-collector si gnal or a driven signal up to at least 48 volts.

Without the optional resistors, the figure simplifies to:

Figure 2.8-3. Simplified Open-Collector (NPN) Connection To Digital Input Without Optional Re sistors

Note that an individual ground connection i s often not needed for every signal. Any signals powered by the same external supply,

or otherwi se referred to the same external ground, should share a single ground connection to the U3 if possible.

2.8.1.3 - Input: Mechanical Switch Closure

To detect whether a mechanical switch (dry contact) is open or closed, connect one side of the swi tch to U3 ground and the other

side to a digital input. The behavior is very similar to the open-collector described above.

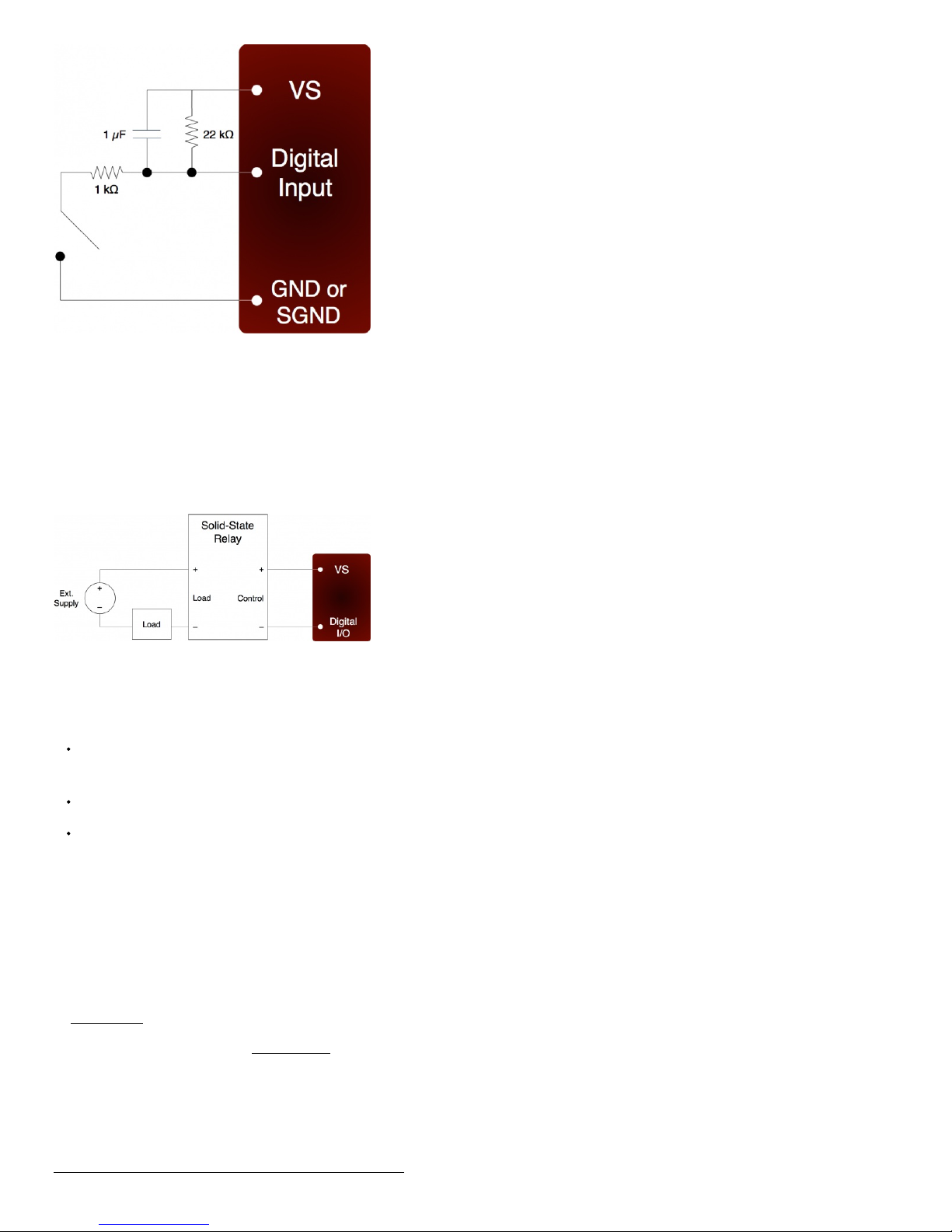

Figure 2.8-4. Basic Mechani cal Switch Connection To Digital Input

When the switch is open, the internal 100 kΩ pull-up resistor will p ull the digital input to about 3.3 volts (logic high). When the switch

is closed, the ground connection will overpower the pull-up resistor and pull the digital input to 0 volts (lo gic low). Since the

mechanical swi tch does not have any electrical connections, besides to the LabJack, it can safely be connected directly to GND,

without using a series resistor or SGND.

When the mechanical switch is closed (and even perhaps when opened), it will bounce briefly and produce multiple electrical

edges rather than a single hi gh/low transition. For many basic digi tal input applications, this is not a problem as the software can

simply poll the input a few ti mes in succession to make sure the measured state is the steady state and not a bounce . For

applications using ti mers or counters, however, this usually is a problem. The hardware counters, for instance, are very fast and will

increment on all the bounces. Some solutions to this issue are:

Software Debounce: If it is known that a real closure cannot occur more than once per some interval, then software can be

used to li mit the number of counts to that rate.

Firmware Debounce: See Section 2.9.1 for information about timer mode 6.

Active Hardware Debounce: Integrated circuits are avai lable to debounce switch signals. This is the most reliable hardware

solution. See the MAX6816 (maxim-ic.com) or EDE2008 (elabinc.com).

Passive Hardware Debounce: A combinati on of resistors and capacitors can be used to debounce a signal. Thi s is not

foolproof, but works fine in most applications.

14

Page 15

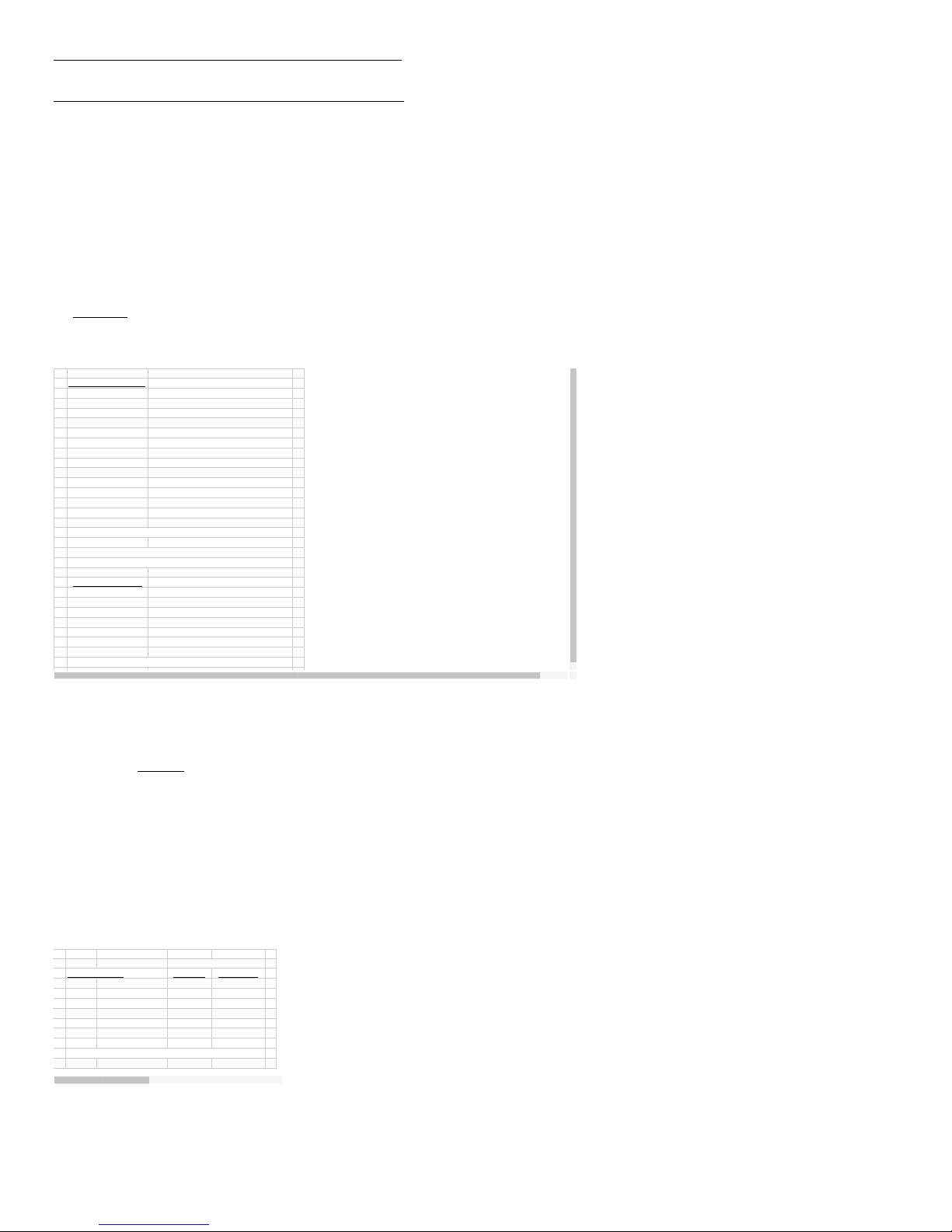

Figure 2.8-5. Passive Hardware Debounce

Figure 2.8-5 shows one possible confi guration for passi ve ha rdware debounce. First, consi der the case where the 1 kΩ resistor is

replaced by a short circuit. When the switch closes it immediately charges the capacitor and the digital input sees logic low, but

when the switch opens the capacitor slowly discharges through the 22 kΩ resistor with a time constant of 22 ms. B y the time the

capacitor has discharged enough for the d igital input to see logic high, the mechani cal bouncing is done. The main purpose of the

1 kΩ resistor is to limit the current surge when the switch is clo sed. 1 kΩ limits the maxi mum current to about 5 mA, but better

results might be obtained with smaller resistor values.

2.8.1.4 - Output: Controlling Relays

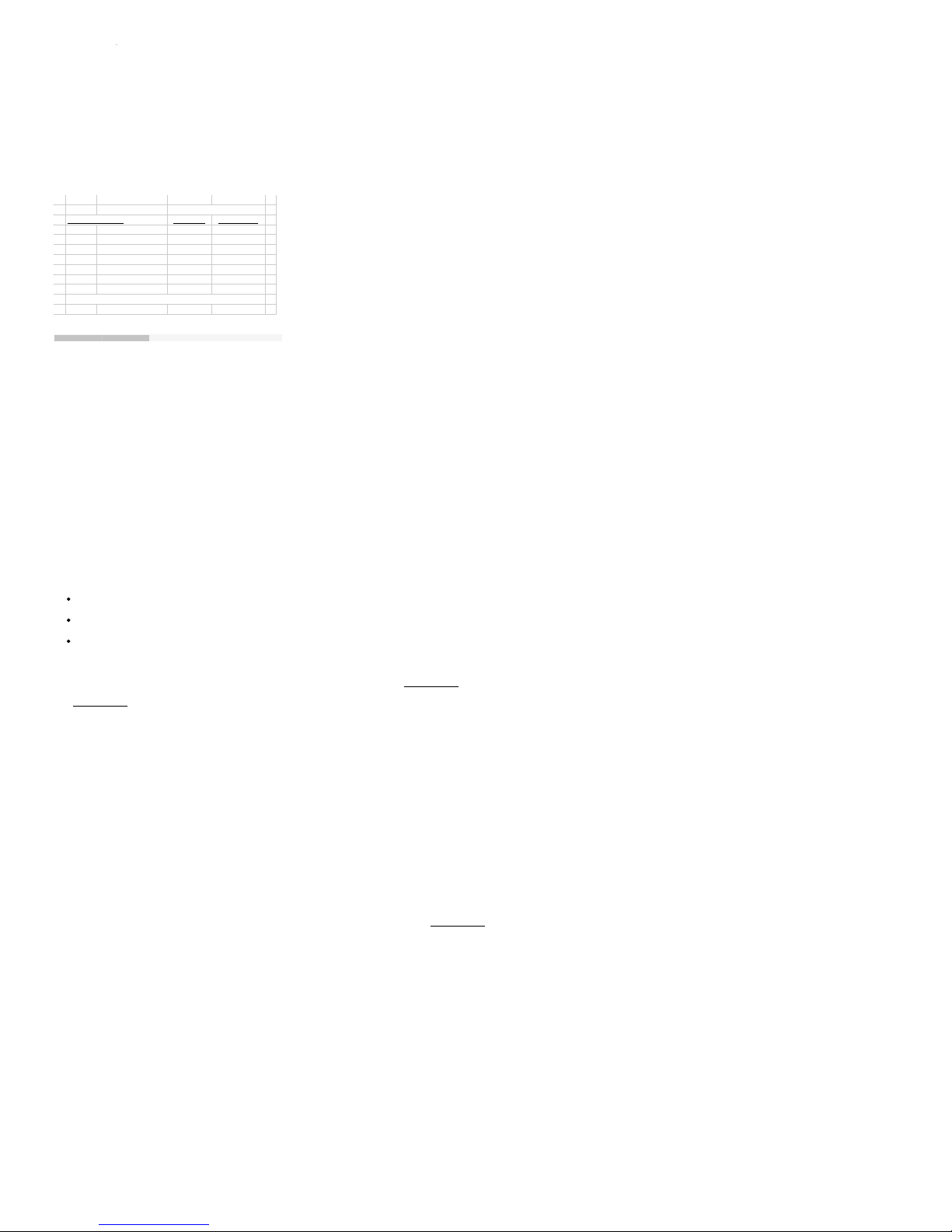

All the digital I/O lines have serie s resistance that restricts the amount of current they can sink or source, but solid-state relays

(SSRs) can usually be controlled directly by the digital I/O. The SSR is connected as shown in the following diagram, where VS (~5

volts) connects to the positive control input and the digital I/O line connects to the negative control i nput (sinking config uration).

Figure 2.8-6. Relay Connections (Sinking Control, High-Side Load Switching)

When the digital line is set to output-low, control current flows and the relay turns on. When the digital line is set to input, control

current does not flow a nd the relay turns off. Whe n the digital line is set to output-high, some current flows, but whether the relay is

on or off depends on the specifications of a particular relay. It is recommended to only use output-low and input.

For example, the Series 1 (D12/D24) or Series T (TD12/TD24) relays from Crydom specify a max turn-on of 3.0 volts, a min turnoff of 1.0 volts, and a nominal input impedance of 1500 Ω.

When the digital line is set to output-low, it is the equivalent of a ground connection wi th 180 Ω (EIO/CIO) or 550 Ω (FIO) in

series. When using an EIO/CIO line, the resulting voltage across the control inputs of the relay will be about

5*1500/(1500+180) = 4.5 volts (the other 0.5 volts is dropped across the internal resistance of the EIO/CIO line). With an FIO

line the voltage across the inputs of the relay will b e about 5*1500/(1500+550) = 3 .7 volts (the other 1.3 vo lts are dropped

across the internal resistance of the FIO line). Both of these are well above the 3.0 volt threshold for the relay, so it will turn on.

When the digital line is set to input, it is the equivalent of a 3.3 volt connection with 100 kΩ in series. The resulting vo ltage

across the control inputs of the relay will be close to zero, as vi rtually all of the 1.7 volt difference (between VS and 3.3) is

dropped across the internal 100 kΩ resistance. This is well below the 1.0 volt threshold for the relay, so it will turn off.

When the digital line is set to output-high, it is the equivalent of a 3.3 volt connection with 180 Ω (EIO/C IO) or 550 Ω (FIO) in

series. When using an EIO/CIO line, the resulting voltage across the control inputs of the relay will be about

1.7*1500/(1500+180) = 1.5 volts. With an FIO line the voltage across the inputs of the relay will be about

1.7*1500/(1500+550) = 1.2 volts. Both of these in the 1.0-3.0 volt region that is not defined for these example relays, so the

resulting state is unknown.

Note that sinking excessive current i nto digital outputs can cause noticeable shifts in analog input readings. For example, the FIO

sinking configuration above sinks about 2 .4 mA into the dig ital output to turn the SSR on, whi ch could cause a shift of roughly 1 mV

to analog input readings.

Mechanical relays require more control current than SSRs, and cannot be controlled directly by the digital I/O on the U3 . To control

higher currents with the digital I/O, some sort of buffer is used. S ome options are a discrete transistor (e.g. 2N2222), a specific

chip (e.g. ULN2003), or an op-amp.

Note that the U3 DACs can source enough current to contro l almost any SSR and even some mechanical relays, and thus can be

a convenient way to control 1 or 2 relays. With the DA Cs you would typically use a sourcing configuration (DAC/GND) rather than

sinking (VS/DAC).

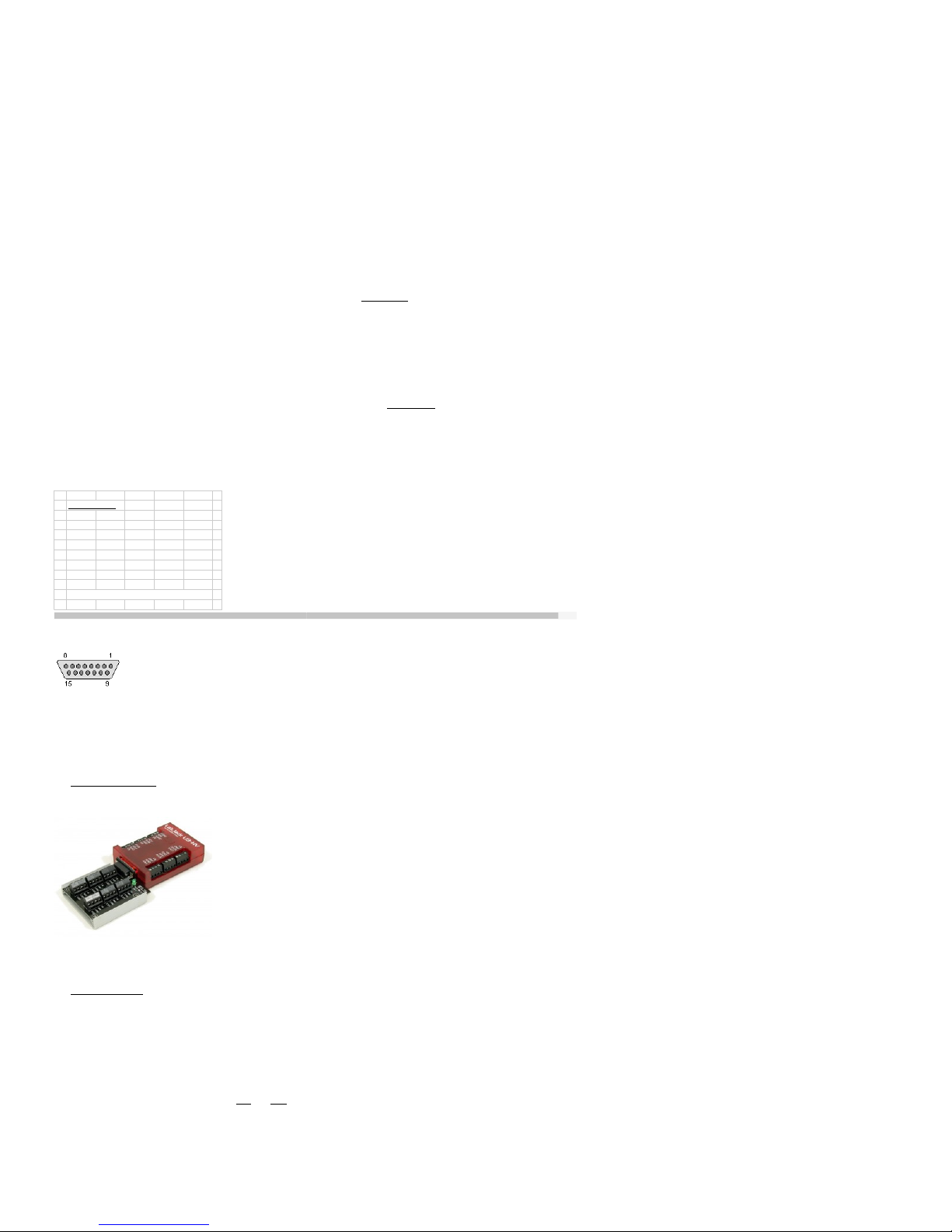

The RB12 relay board is a useful accessory available from LabJack. This board connects to the DB15 connector on the U3 and

accepts up to 12 industry standard I/O modules (designed for Opto22 G4 modules and similar).

Another a ccessory available from LabJack is the LJTick-RelayDriver. This is a two channel module that plugs into the U3 screwterminals, and allows two digital lines to each hold off up to 50 volts and sink up to 200 mA. This allows control of virtua lly any solidstate or mechanical relay.

2.9 - Timers/Counters

The U3 has 2 timers (Timer0-Timer1) and 2 counters (Counter0-Counter1). When any of these timers or counters are enabled, they

take over an FIO/EIO line in sequence (Timer0, Timer1, Counter0, then Counter1), starting with FIO0+TimerCounterPinOffset.

Some examples:

1 Timer enabled, Counter0 disabled, Counter1 disabled, and Ti merCounterPinOffset=4:

FIO4=Timer0

15

Page 16

1 Timer enabled, Counter0 disabled, Counter1 enabled, and TimerCounterPinOffset=6:

FIO6=Timer0

FIO7=Counter1

2 Timers enabled, Counter0 enabled, Counter1 enabled, and TimerCounterPinOffset=8:

EIO0=Timer0

EIO1=Timer1

EIO2=Counter0

EIO3=Counter1

Starting with hardware revision 1.30, timers/counters cannot appear on FIO0-3, and thus TimerCou nterPinOffset must be 4-8.

A value of 0-3 will result in an error. This error can be suppressed by a power-up default setting in LJControlPanel. If suppressed, a

0-3 will result i n an offset of 4.

Timers and counters can appear on vario us pins, but other I/O lines never move. For example, Timer1 can appear anywhere from

FIO4 to EIO1 , depending on TimerCounterPinOffset and whether Timer0 is enabled. On the other hand, FIO5 (for example), i s

always on the screw terminal labeled FIO5, and AIN5 (if enabled) is always on that same screw termina l.

Note that Counter0 is not available with certain timer clock base frequencies. In such a case, it does not use an external FIO/EIO

pin. An error will result if an attempt is made to enable Counter0 when one of these fre quencies is configured. Similarly, an error

will result if an atte mpt is made to configure one of these frequencies when Co unter0 is enabled.

Applicable digital I/O are automatically configured as input o r output as neede d when timers and counters are ena bled, and stay

that way when the timers/counters are disabled.

See Section 2.8.1 for information about signal connections.

Each counter (Counter0 or Counter1) consists of a 32-bit register that accumulates the number of falling edges detected on the

external pin. If a counter is reset and read in the same function call, the read returns the value just be fore the reset.

The timers (Timer0-Timer1) have various modes available:

Index (Low-level & UD)

0

16-bit PWM output

1

8-bit PWM output

2

Period input (32-bit, rising edges)

3

Period input (32-bit, falling edges)

4

Duty cy cle input

5

Firmware counter input

6

Firmware counter input (with debounce)

7

Frequency output

8

Quadrature input

9

Timer stop input (odd timers only)

10

System time r low rea d (default mo de)

11

Syst em timer hight read

12

Period input (16-bit, rising edges)

13

Period input (16-bit, falling edges)

Table 2. 9-1. U3 Time r Modes

Both timers use the same timer c lock.

There are 7 choices for the timer cl ock base:

Index (Low-level/UD)

0/20

4 MHz

1/21

12 MHz

2/22

48 MHz (default)

3/23

1 MHz /Divisor

4/24

4 MHz /Divisor

5/25

12 MHz /Divisor

6/26

48 MHz /Divisor

Table 2. 9-2. U3 Time r Clock Base Options

Note that these clocks apply to the U3 hardware revi sion 1.21+. With hardware revision 1.20 all clocks are half of the values

above.