Page 1

If it’s embedded, it’s Kontron

KTQ77/Flex Users Guide

KTD-N0848-C

Page 2

KTQ77/Flex Users Guide

KTD-N0848-C Page 2

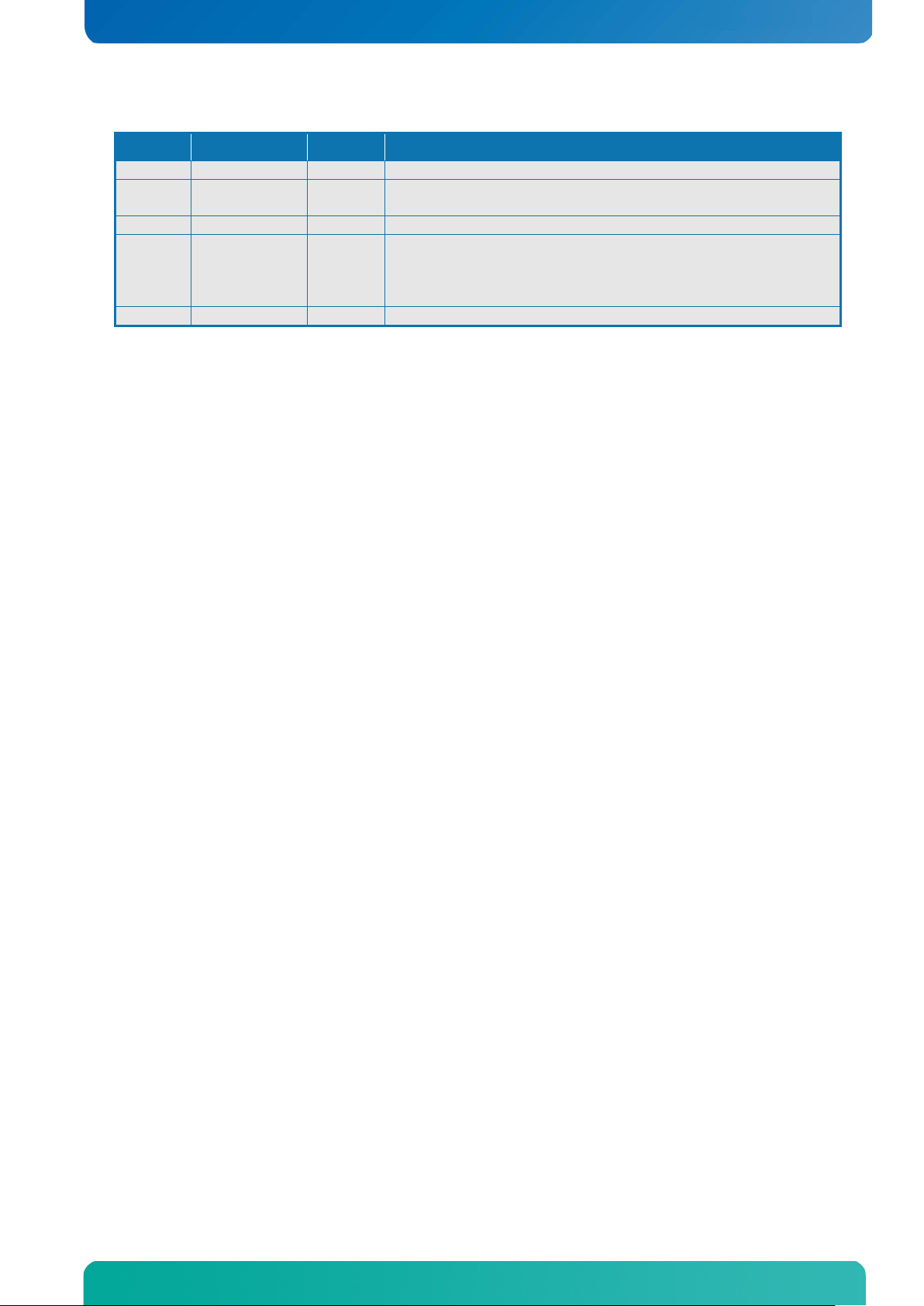

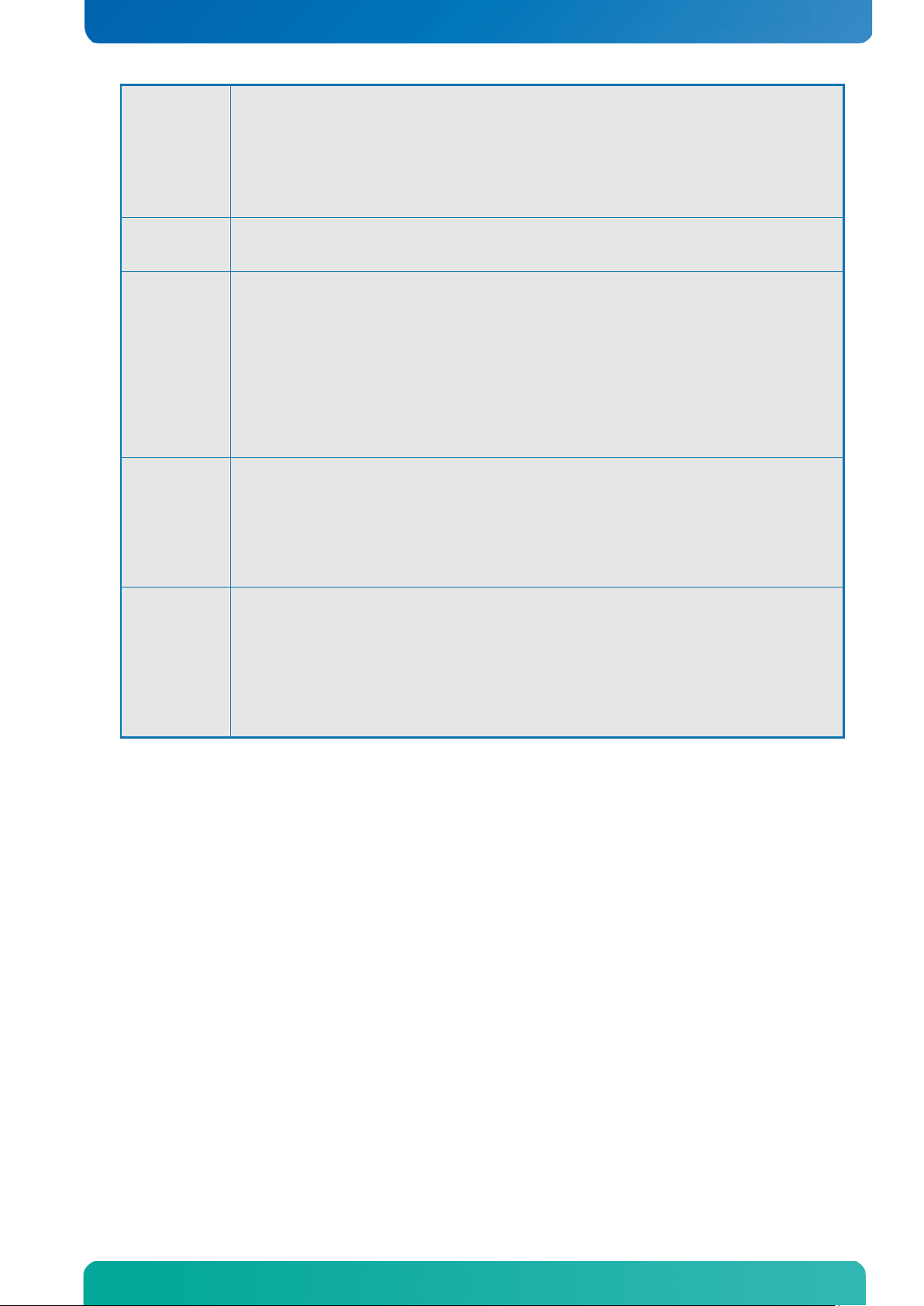

Revision

Date

By

Comment

Correction of Mic2 and Line2 location. Note on RAM speed.

EXT_BAT max. 3.47 V. Chapter 7.2.2 Riser Card note corrected.

B

Jan. 8th 2014

MLA

Added BIOS features: Force Boot Setup and PC Speaker /Beep.

Minor bugs. Removed 5V t olera nc e for some GPIO’s. J11 and

RAM list updated. Block diagram improved.

0

Jun. 29th 2012

MLA

Preliminary version

Document details

Document revis ion history.

C Jan. 19th 2015 MLA

A Aug. 22nd 2013 MLA

J30 descriptions corrected. 3.3V now 5% tolerance. CPU List

updated. BIOS part added. System Resources tables corrected.

Copyright Notice:

Copyright 2011, KONTRON Technology A/S, ALL RIGHTS RESERVED.

No part of this document may be reproduced or transmitted in any form or by any means, electronically

or mechanically, for any purpose, without the express written permission of KONTRON Technolo g y A/S.

Trademark Acknow ledgemen t:

Brand and product names are trademarks or registered trademarks of their respective owners.

Disclaimer:

KONTRON Technology A/S reserves the right to make changes, without notice, to any product,

including circuits and/or software described or contained in this manual in order to improve design

and/or performance.

Specifications listed in this manual are subject to change without notice. KONTRON Technology

assumes no responsibility or liability for the use of the described product(s), conveys no license or title

under any patent, copyright, or mask work rights to these products, and makes no representations or

warranties that these products are free from patent, copyright, or mask work right infringement, unless

otherwise specified. Applications that are described in this manual are for illustration purposes only.

KONTRON Technology A/S makes no representation or warranty that such application will be suitable

for the specified use without further testing or modification.

Life Support Polic y

KONTRON Technology’s PRODUCTS ARE NOT FOR USE AS CRITICAL COMPONENTS IN LIFE

SUPPORT DEVICES OR SYSTEMS WITHOUT EXPRESS WRITTEN APPROVAL OF THE GENERAL

MANAGER OF KONTRON Technology A/S.

As used herein:

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into

body, or (b) support or sustain life and whose failure to perform, when properly used in accordance with

instructions for use provided in the labelling, can be reasonably expected to result in significant injury to

the user.

A critical component is any component of a life support device or system whose failure to perform can

be reasonably expected to cause the failure of the life support device or system, or to affect its safety or

effectiveness.

Page 3

KTQ77/Flex Users Guide

KTD-N0848-C Page 3

Document details

KONTRON Technology Technical Support & Services

If you have questions about installing or using your KONTRON Technology Product, check this User’s

Manual first – you will find answers to most questions here. To obtain support, please contact your local

Distributor or Field Application Engineer (FAE).

Before Contacting Support: Please be prepared to provide as much information as possible:

• CPU Board

1. Type.

2. Part Number (find PN on label)

3. Serial Number if available (find SN on label)

• Configuration

1. CPU Type, Clock speed

2. DRAM Type and Size.

3. BIOS Revision (Find the Version Info in the BIOS Setup).

4. BIOS Settings different than Default Settings (Refer to the BIOS Setup Section).

• System

1. O/S Make and Version.

2. Driver Version numbers (Graphics, Network, and Audio).

3. Attached Hardware: Harddisks, CD-rom, LCD Panels etc.

Warranty

KONTRON Technology warrants its products to be free from defects in material and workmanship

during the warrant y period. If a pr oduct proves to be defective in material or workmanship during the

warranty period, KONTRON Technology will, at its sole option, repair or replace the product with a

similar product.

Replacement Product or parts may include remanufactured or refurbished parts or components.

The warranty does not cover:

1. Damage, deterioration or malfunction resulting from:

A. Accident, misuse, neg lect, fire, water, lightning, or oth er acts of nature, una uthorized produc t

modification, or failure to follow instructions supplied with the product.

B. Repair or attempted repair by anyone not authorized by KONTRON Technology.

C. Causes external to the product, such as electric power fluctuations or failure.

D. Normal wear and tear.

E. Any other causes which does not relate to a product defect.

2. Removal, installation, and set -up service charges.

Exclusion of damages:

KONTRON TECHNOLOGY LIABILIT Y IS LIMITED TO THE COST OF REPAIR OR REPLACEMENT

OF THE PRODUCT. KONTRON TECHNOLOGY SHALL NOT BE LIABLE FOR:

1. DAMAGE TO OTHER PROPERTY CAUSED BY ANY DEFECTS IN THE PRODUCT,

DAMAGES BASED UPON INCONVE NIENCE, LOS S OF USE OF TH E PRODUCT, LOSS OF

TIME, LOSS OF PROFITS, LOSS OF BUSINESS OPPORTUNITY, LOSS OF GOODWILL,

INTERFERENCE WITH BUSINESS RELATIONSHIPS, OR OTHER COMMERCIAL LOSS,

EVEN IF ADVISED OF THEIR POSSIBILITY OF SUCH DAMAGES.

2. ANY OTHER DAMAGES, WHETHER INCIDENTAL, CONSEQUENTIAL OR OTHERWISE.

3. ANY CLAIM AGAINST THE CUSTOMER BY ANY OTHER PARTY.

Page 4

KTQ77/Flex Users Guide

KTD-N0848-C Page 4

Contents

Introduction .............................................................................................. 8

1 Installation procedure ......................................................................... 9

1.1 Installing the board .......................................................................................................................... 9

1.2 Requirement according to IEC60950 ................................................................................................. 10

2 System Specification .......................................................................... 11

2.1 Component main data ..................................................................................................................... 11

2.2 System overview ............................................................................................................................. 15

2.3 Processor Support Table .................................................................................................................. 17

2.4 System Memory support ................................................................................................................... 20

2.5 KTQ77 Graphics Subsystem ............................................................................................................... 21

2.5.1 Intel® HD Graphics 4000/2500 ....................................................................................................... 21

2.6 Power Consumption ........................................................................................................................ 22

3 Connector Locations .......................................................................... 25

3.1 KTQ77/Flex – frontside .................................................................................................................... 25

3.2 KTQ77/Flex - backside ..................................................................................................................... 26

4 Connector Definitions ........................................................................ 27

5 IO-Area Connectors ............................................................................ 28

5.1 Display connectors (IO Area) ............................................................................................................ 28

5.1.1 Analogue VGA (VGA) ...................................................................................................................... 28

5.1.2 DP Connectors (DP0/DP1) ............................................................................................................... 29

5.2 Ethernet Connectors (IO Area).......................................................................................................... 30

5.3 USB Connectors (IO Area) ................................................................................................................ 31

5.3.1 USB Connector 0/1 (USB0/1) ......................................................................................................... 32

5.3.2 USB Connector 2/3 (USB2/3) ......................................................................................................... 33

5.3.3 USB Connector 4/5 (USB4/5) ......................................................................................................... 33

5.4 Audio Connector (IO Area) ............................................................................................................... 34

5.5 COM1 Connector (IO Area) ............................................................................................................... 35

6 Internal Connectors ........................................................................... 36

Page 5

KTQ77/Flex Users Guide

KTD-N0848-C Page 5

6.1

Power Connector (ATX/BTXPWR) ....................................................................................................... 36

6.2 Fan Connectors (FAN_CPU) (J28) and (FAN_SYS) (J29) ....................................................................... 37

6.3 PS/2 Keyboard and Mouse connector (KBDMSE) (J15)......................................................................... 38

6.4 Display connectors (Internal) ........................................................................................................... 39

6.4.1 LVDS Flat Panel Connector (LVDS) (J39) (optionally) ......................................................................... 39

6.5 SATA (Serial ATA) Disk interface (J22 – J27) ...................................................................................... 40

6.6 USB Connectors (USB) ..................................................................................................................... 41

6.6.1 USB Connector 6/7 ........................................................................................................................ 41

6.6.2 USB Connector 8/9 (USB8/9) (J18) ................................................................................................. 41

6.6.3 USB Connector 10/11 (USB10/11) (J17) .......................................................................................... 42

6.6.4 USB Connector 12/13 (USB12/13) (J16) .......................................................................................... 42

6.7 Serial COM2 – COM4 Ports (J19, J20, J21) .......................................................................................... 43

6.8 Audio Connectors............................................................................................................................ 44

6.8.1 CDROM Audio Input (CDROM) (J44) ................................................................................................. 44

6.8.2 Line2 and Mic2 .............................................................................................................................. 44

6.8.1 Audio Header Connector (AUDIO_HEAD) (J47) ................................................................................. 45

6.9 Front Panel Connector (FRONTPNL) (J36) .......................................................................................... 46

6.10 Feature Connector (FEATURE) (J30) .................................................................................................. 47

6.11 ”Load Default BIOS Settings” Jumper (J11) ....................................................................................... 49

6.12 ClrRTC (J12) ................................................................................................................................... 49

6.13 SPI Recover Jumper (J41) ................................................................................................................ 50

6.14 SPI Connector (SPI) (J40) ................................................................................................................ 51

6.15 XDP-CPU (Debug Port for CPU) (J14) ................................................................................................. 52

6.16 XDP-PCH (Debug Port for Chipset) (J13) ............................................................................................ 53

7 Slot Connectors (PCIe, mSATA, miniPCIe, PCI) ....................................... 54

7.1 PCIe Connectors.............................................................................................................................. 54

7.1.1 PCI-Express x16 Connector (PCIe x16).............................................................................................. 54

7.1.2 mSATA (J43) ................................................................................................................................. 56

7.1.3 miniPCI-Express mPCIe (J42) .......................................................................................................... 57

7.1.4 PCI-Express x4 Connector (PCIe x4) (J33) ........................................................................................ 58

7.2 PCI Slot Connectors ........................................................................................................................ 59

7.2.1 Signal Description – PCI Slot Connector ........................................................................................... 60

7.2.2 KTQ77 PCI IRQ & INT routing ........................................................................................................... 61

8 On-board - & mating connector types ................................................... 62

9 System Resources .............................................................................. 63

Page 6

KTQ77/Flex Users Guide

KTD-N0848-C Page 6

9.1

Memory Map ................................................................................................................................... 63

9.2 PCI Devices .................................................................................................................................... 64

9.3 Interrupt Usage .............................................................................................................................. 65

9.4 IO Map ........................................................................................................................................... 66

10 BIOS ................................................................................................ 67

10.1 Main .............................................................................................................................................. 67

10.2 Advanced ....................................................................................................................................... 68

10.2.1 Advanced - PCI Subsystem Settings ................................................................................................ 69

10.2.2 Advanced - APCI Settings ............................................................................................................. 74

10.2.3 Advanced - Trusted Computing ...................................................................................................... 75

10.2.4 Advanced - CPU Configuration ....................................................................................................... 76

10.2.5 Advanced - SATA Configuration ...................................................................................................... 78

10.2.6 Advanced - Intel ® Rapid Start Technology ..................................................................................... 82

10.2.7 Advanced - Intel TXT (LT) Configuration .......................................................................................... 83

10.2.8 Advanced - Intel ® Anti-Theft Technology Configuration .................................................................. 84

10.2.9 Advanced - AMT Configuration ....................................................................................................... 85

10.2.10 Advanced - Acoustic Management Configuration ............................................................................. 87

10.2.11 Advanced - USB Configuration ....................................................................................................... 88

10.2.12 Advanced - SMART Settings ........................................................................................................... 90

10.2.13 Advanced - Super IO Configuration................................................................................................. 91

10.2.14 Advanced - Voltage Monitor .......................................................................................................... 96

10.2.15 Advanced - Hardware Health Configuration ..................................................................................... 97

10.2.16 Advanced - LAN Configuration ....................................................................................................... 99

10.2.17 Advanced - Delay Startup ............................................................................................................ 101

10.2.18 Advanced - Serial Port Console Redirection ................................................................................... 102

10.2.19 Advanced - CPU PPM Configuration............................................................................................... 106

10.3 Chipset ........................................................................................................................................ 107

10.3.1 PCH-IO Configuration ................................................................................................................... 108

10.3.2 System Agent (SA) Configuration .................................................................................................. 114

10.4 Boot ............................................................................................................................................ 132

10.4.1 CSM16 parameters ....................................................................................................................... 134

10.4.2 Force Boot Setup ......................................................................................................................... 135

10.4.3 CSM parameters ........................................................................................................................... 136

10.5 Security ....................................................................................................................................... 137

10.5.1 HDD Security Configuration .......................................................................................................... 138

10.6 Save & Exit ................................................................................................................................... 139

11 AMI BIOS Beep Codes ....................................................................... 140

Page 7

KTQ77/Flex Users Guide

KTD-N0848-C Page 7

12 OS Setup ........................................................................................ 141

Page 8

KTQ77/Flex Users Guide

KTD-N0848-C Page 8

Introduction

Introduction

This manual describes the KTQ77/Flex boar d m ade by KONT RO N T echnolog y A/S. T he board will also

be denoted KTQ77 in this manual.

nd

The KTQ77 board is based on the Q7 7 chipset, support 2

and 4Core processors and also Pentium and Celeron processors. See “Processor Support Table for

more specific details.

Use of this Users Guide implies a basic knowledge of PC-AT hard- and software. This manual is

focused on describing the KTQ77 board’s speci al features and is not inte nded to be a standard PC -AT

textbook.

New users are recom mended to study the short inst allation procedure stated in the f ollowing chapter

before switching-on the power.

Note. LPT and LVDS are optionally for future variants.

All configuration and setup of the CPU board is either done automaticall y or manually by the user via

the BIOS setup menus. Only exception is the “Load Default BIOS Settings” Jumper.

and 3rd generation Intel® i7 -, i5 -, i3 2Core

Page 9

KTQ77/Flex Users Guide

KTD-N0848-C Page 9

Warning: Turn off PSU (Power Supply Unit) completely (no mains power connected to the

!

!

Warning: When mounting the board to chassis etc. please notice that the board contains

without reasonable care. A damaged component can result in malfunction or no function at all.

Installation procedure

Note: To clear all CMOS settings, including Password protection, move the Clear CMOS jumper in the

Secure CMOS is disabled.

1 Installation procedure

1.1 Installing the board

To get the board running, follow these steps. If the board shipped from KONTRON has already

components like DRAM, CPU and cooler mounted, then relevant steps below, can be skipped.

1. Turn off the PSU (Power Supply Unit)

2. Insert the DRAM(s) (UDIMM 240pin)

Be careful to push it in the slot(s) b efore locking th e tabs. For a list of approved DRAM contact your

Distributor or FAE. See also chapter “System Memory Support”.

3. Install the processor

The CPU is ke yed and will onl y mount in t he CPU sock et in one way. Use finger to open/ close t he

CPU socket. Refer to supported processor overview for details.

4. Cooler Installation

Use heat paste or adhesive pads between CPU and cooler and connect the Fan electrically to the

FAN_CPU connector.

5. Connecting Interfaces

Insert all external cables for hard disk , keyboard etc. A m onitor must be connected i n order to be

able change CMOS settings.

6. Connect and turn on PSU

Connect PSU to the board by the ATX/BTXPWR and the 4-pin ATX+12V connectors.

7. Power Button

The PWRBTN_IN must be toggled to start the Power supply; this is done by shorting pins 16

(PWRBTN_IN) and pin 18 (GND) on the FRONTPNL connector (see Connector description). A

“normally open” switch can be connected via the FRONTPNL connector.

8. BIOS Setup

Enter the BIOS setup by pressing the <Del> key during boot up.

Enter Exit Menu and Load Optimal Defaults.

Refer to the “BIOS Configuration / Setup“ section of this manual for details on BIOS setup .

Clear CMOS position (with or without power) for ~10 sec. This will Load Failsafe Defaults and make sure

9. Mounting the board to chassis

When fixing the Motherb oard on a chassis it is recomm ended using screws with integrated washer and

having diameter of ~7mm.

Note: Do not use washers with teeth, as they can damage the PCB and may cause short circuits.

PSU) or leave the Power Connectors unconnected while configuring the board. Otherwise

components (DRAM, LAN cards etc.) might get damaged. Make sure PSU has 3.3V monitoring

watchdog (standard ATX PSU feature), running the board without 3.3V will damage the board

within minutes.

components on both sides of the PCB which can easily be damaged if board is handled

Page 10

KTQ77/Flex Users Guide

KTD-N0848-C Page 10

ADVARSEL

When an interface/connector has a VCC (or other power) pin, which is directly connected to a power

Installation procedure

1.2 Requirement according to IEC60950

Users of KTQ77 family boards should take care when designing chassis interface connectors in order to

fulfil the IEC60950 standard:

plane like the VCC plane:

To protect the external power lines of the peripheral devices , the customer has to take care about:

• That the wires have suitable rating to withstand the maximum available power.

• That the enclosure of the peripheral device fulfils the fire protecting requirements of IEC60950.

Lithium Battery precautions:

CAUTION!

Danger of explosion if battery is incorrectly

replaced.

Replace only with same or equivalent type

recommended by manufacturer.

Dispose of used batteries according

to the manufacturer’s instructions.

ADVARSEL!

Lithiumbatteri – Eksplosionsfare ved fejlagtig

håndtering.

Udskiftning må kun ske med batteri

af samme fabrikat og type.

Levér det brugte batteri tilbage til leverandøren.

VARNING

Explosionsfara vid felaktigt batteribyte.

Använd samma batterityp eller en ekvivalent

typ som rekommenderas av apparattillverkaren.

Kassera använt batteri enligt fabrikantens

instruktion.

VORSICHT!

Explosionsgefahr bei unsachgemäßem

Austausch der Batterie.

Ersatz nur durch den selben oder einen vom

Hersteller empfohlenen gleichwertigen Typ.

Entsorgung gebrauchter Ba tterie n nach

Angaben des Herstellers.

Eksplosjonsfare ved feilaktig skifte av batteri.

Benytt samme batteritype eller en tilsvarende

type anbefalt av apparatfabrikanten.

Brukte batterier kasseres i henhold til

fabrikantens

instruksjoner.

VAROITUS

Paristo voi räjähtää, jos se on virheellisesti

asennettu.

Vaihda paristo ainoastaan laltevalmistajan

suosittelemaan

tyyppiin. Hävitä käytetty paristo valmistajan

ohjeiden

mukaisesti.

Page 11

KTQ77/Flex Users Guide

KTD-N0848-C Page 11

Form factor

KTQ77/Flex: Flex-ATX (190,5 mm by 228,6 mm)

Processor

Support the following Intel® Core™ processors via Socket H2 (LGA1155), ZIF Soc ket

Memory

• 4x DDR3 UDIMM 240pin socket

Chipset

Intel Q77 PCH (Platform Controller Hub)

Security

• Intel® Integrated TPM 1.2 support

Management

• Intel® AMT (Active Management Technology) 8.0

Audio

Audio, 7.1 Channel High Definition Audio Codec using the VIA 1708B codec

System Specification

2 System Specification

2.1 Component main da ta

The table below summarizes the features of the KTQ77/Flex embedded motherboard.

• Intel® Core™ i7, 2nd and 3rd Generation

• Intel® Core™ i5, 2nd and 3rd Generation

• Intel® Core™ i3, 2nd and 3rd Generation

• 1333/1600MHz system bus and 3/6/8MB internal cache.

• Up to 95W (Thermal Guideline)

• PCIe x16 (PEG) Gen3.0

• Support single and dual ranks DDR3 1066/1333/1600MT/s

(PC3-8500/PC3-10600/PC3-12800)

• Support system memory from 1GB and up to 4x 8GB

Note: Less than 4GB displayed in System Properties using 32bit OS

(Shared Video Memory/PCI resources is subtracted)

• ECC not supported

• Intel ® VT-d (Virtualisation Technology for Directed I/O)

• Intel ® TXT (Trusted Execution Technology)

• Intel ® vPRO

• Intel ® AMT (Active Management Technology) version 8.0

• Intel ® AT (Anti-Theft Technology)

• Intel ® HD Audio Technology

• Intel ® RST (Rapid Storage Technology)

• Intel ® RRT (Rapid Recover Technology)

• SATA (Serial ATA) 6Gb/s and 3Gb/s.

• USB 4x rev. 3.0/2.0 + 10x rev. 2.0

• PCIe x4 (in x16 slot) Gen2.0

• ACPI 3.0b compliant

• Triple Display support (Triple Graphic Pipes)

• Blue-ray HD video playbac k

• Line-out

• Line-in

• Surround output: SIDE, LFE, CEN, BACK and FRONT

• Microphone: MIC1 and MIC2

• CDROM in

• SPDIF (electrical Interface only)

• On-board speaker (Electromagnetic Sound Generator like Hycom HY-05LF)

Page 12

KTQ77/Flex Users Guide

KTD-N0848-C Page 12

Video

Intel ® HD Graphics 4000 or

I/O Control

Via ITE IT8516E Embedded Controller and Winbond W83627DHG I/O Controller

Peripheral

• 2x USB 2.0 ports on I/O area

LAN

• 1x 10/100/1000Mbits/s LAN (ETHER1) using Intel® Lewisville 82579LM Gigabit

Expansion

• 2x PCI slot(s) (PCI Local Bus Specification Revision 3.0, 33MHz)

System Specification

Intel ® HD Graphics 3000 or

Intel ® HD Graphics 2500 or

Intel ® HD Graphics 2000 or

Intel ® HD Graphics, depending on actual CPU.

Analogue VGA and digital display ports (2x DP) via the Mobile Intel ® Q77 Chipset.

• VGA (analogue panel)

• 2x DP (DisplayPort), comply with DisplayPort 1.2 specification.

• LVDS panel support (optional) up to 24 bit, 2 pixels/clock and 1920x1200.

• HDMI panel support via DP to HDMI Adapter Converter.

• Second VGA panel support via DP to VGA Adapter Converter

• Second DVI panel support via DP to DVI Adapter Converter

• Triple independent pipes for Mirror and/or independent display support

(both via LPC Bus interface)

interfaces

Support

Capabilities

• 4x USB 3.0 ports on I/O area

• 8x USB 2.0 ports on internal pinrows

• 4x Serial ports (RS232) on internal pinro ws

• 2x Serial ATA-600 IDE interfaces (blue)

• 4x Serial ATA-300 IDE interfaces (black)

• 1x Serial ATA-300 IDE interfaces (white), sh ared w ith mSATA

• RAID 0/1/5/10 support

• mSATA via mSATA connector, shared with SATA (white)

• PS/2 keyboard and mouse ports via pinrow

PHY connected to Q77 supporting AMT 8.0

• 2x 10/100/1000Mbits/s LAN (ETHER2/ETHER3)using Intel® Hartwell 82574L PCI

Express controllers

• PXE Netboot supported.

• Wake On LAN (WOL) supported

• PCI-Express slots:

o 1 slot PCIe x16 Gen3.0

o 1 slot PCIe x4 (in a x16 slot) Gen2 (EFT samples support only PCIe x1)

o 1 slot miniPCI-Express

• SMBus, compatib le with A CCE S BUS and I2C BU S, (via Feature connector)

• SPI bus routed to SPI connector

• DDC Bus routed to DP connector when DP Adapters are connected

• 5 x digital input, (via Feature connector)

• 13 x GPIOs (General Purpose I/Os), (via Feature connector)

• DAC, ADC, PWM and TIMER (Multiplexed), (via Feature connector)

• WAKE UP / Interrupt Inputs (Multiplexed), (via Feature connec tor )

• 3 Wire Bus for GPIO Expansion (up to 152 GPIOs), (via Feature connector)

• 8 bit Timer output, (via Feature connector)

Page 13

KTQ77/Flex Users Guide

KTD-N0848-C Page 13

Hardware

• Smart Fan control system, support Thermal® and Speed® cruise for FAN_CPU

Power

ATX/BTX (w. ATX+12V) PSU for full PCI/PCIe load.

Battery

BIOS

• Kontron Technology / AMI BIOS (EFI c ore ver sio n)

• RAID Support (RAID modes 0,1, 5 and 10)

Operating

• WinXP (32b *)

System Specification

Monitor

Subsystem

Supply Unit

• CPU die temperature input (Precision +/- 3ºC)

• Voltage monitoring

• Intrusion (Case Open) detect input, (via Feature connector)

• Sleep S4/S5# Indication, (via Feature connector)

• System Powergood Signal, (via Feature connector)

Exchangeable 3.0V Lithium battery for on-board Real Time Clock and CMOS RAM.

Manufacturer Panasonic / Part-number CR-2032L/BN, CR2032N/BN or CR-2032L/BE.

Approximate 5 years retention.

Current draw is 5,7µA when PSU is disconnected and 0 µA in S0 – S5.

CAUTION: Danger of explosion if the battery is incorrectly replaced. Replace

only with the same or equivalent type recommended by the manufacturer.

Dispose of used batteries according to th e manufacturer’s instructions.

• Support for ACPI 3.0 ( Advanced Configuration and Power Interface), Plug & Play

o Suspend (S1 mode)

o Suspend To Ram (S3 mode)

o Suspend To Disk (S4 mode)

• “Always On” BIOS power setting

Systems

Support

• Windows 7 (32b + 64b *)

• WES7 (32b * + 64b *)

• Linux Fedora *

• Linux Ubuntu * (RAID problem)

• VxWorks BSP, WES7 BSP, Kontron Linux BSP (not ready yet)

*= Out Of The Box installation test only

Page 14

KTQ77/Flex Users Guide

KTD-N0848-C Page 14

Environmental

Only Japanese brand Solid capacitors rated for 100 ºC used on board

System Specification

Conditions

Operating:

0°C – 60°C operating temperature (forced cooling). It is the customer’s

responsibility to provide sufficient airflow around each of the components to keep

them within allowed temperature range.

10% - 90% relative humidity (non-condensing)

Storage:

-20°C – 70°C; lower limit of storage temperature is defined by specification

restriction of on-board CR2032 battery. Board with battery has been verified for

storage temperature down to -40°C by Kontron.

5% - 95% relative humidit y (non-condensing)

Electro Static Discharge (ESD) / Radiated Emissions (EMI):

All Peripheral interfaces intended for connection to external equipment are ESD/

EMI protected.

EN 61000-4-2:2000 ESD Immunity

EN55022:1998 class B Generic Emission Standard.

Safety:

IEC 60950-1: 2005, 2nd Edition

UL 60950-1

CSA C22.2 No. 60950-1

Product Category: Information Technology Equipment Including Electrical

Business Equipment

Product Category CCN: NWGQ2, NWGQ8

File number: E194252

Theoretical MTBF:

216227 / 100903 hours @ 40ºC / 60ºC for the KTQ77/Flex

Restriction of Hazardous Substances (RoHS):

All boards in the KTQ77 family are RoHS compliant.

Capacitor utilization:

No Tantalum capacitors on board

Page 15

KTQ77/Flex Users Guide

KTD-N0848-C Page 15

System Specification

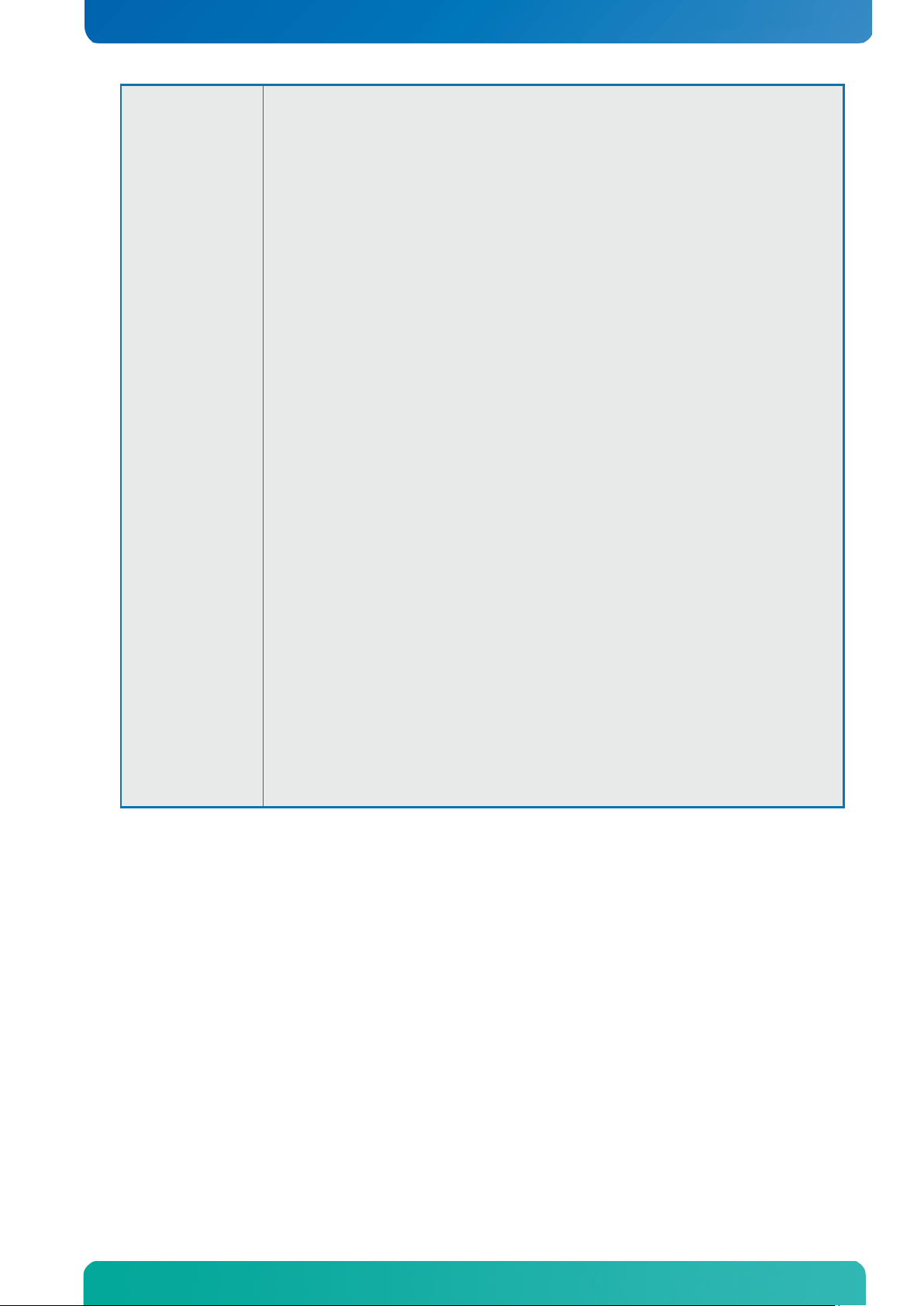

2.2 System overview

The block diagram below shows the architecture and main components of the KTQ77. The key

component on the board is the Intel

®

Q77 (Panther Point) Express Chipset.

More detailed block diagram on next page.

Page 16

KTQ77/Flex Users Guide

KTD-N0848-C Page 16

System Specification

Dual Channel DDR3

4 x DIMM

PCIe x16 Graphics

Ivy Bridge or

2x DisplayPort

VGA

PCIe x4 Slot

Intel 82574L 10/100/GBe

14x USB

6x SATA

SDVO to LVDS (option)

VIA Codec

SPI

SPI

TPM

Intel Lewisville PHY

Intel 82574L 10/100/GBe

mSATA

PCIe Mini Card

IO controller

IO controller

PCI slot

PCI slot

COM3/4

COM1/2

FAN CPU/SYS

FEATURE

1067/1333/1600

(4x Ge n 3.0 / 2.0)

ITE8516

Sandy Bridge

LGA1155

Q77 PCH

W83627DHG-P(T)

Page 17

KTQ77/Flex Users Guide

KTD-N0848-C Page 17

Processor

Brand

Clock

[GHz]

Turbo

[GHz]

Cores /

Threads

Bus

[MHz]

Cache

[MB]

CPU

Number

sSpec

no.

TG

[W/ºC]

Note

3.5

3.9

4 / 8

1333/1600

8

3770K

SR0PL

E1

77/67.4

HDG4000

I7 3rd Gen.

3.4

3.9

4 / 8

1333/1600

8

3770

SR0PK

E1

77/67.4

HDG4000

(Ivy Bridge)

3.1

3.9

4 / 8

1333/1600

8

3770S

SR0PN

E1

65/69.1

HDG4000

2.5

3.7

4 / 8

1333/1600

8

3770T

SR0PQ

E1

45/69.8

HDG4000

3.5

3.9

4 / 8

1066/1333

8

2700K

SR0DG

D2

95/72.6

HDG3000

I7 2nd Gen.

3.4

3.8

4 / 8

1066/1333

8

2600

SR00B

D2

95/72.6

HDG2000

(Sandy Bridge)

3.4

3.8

4 / 8

1066/1333

8

2600K

SR00C

D2

95/72.6

HDG3000

2.8

3.8

4 / 8

1066/1333

8

2600S

SR00E

D2

65/69.1

HDG2000

3.4

3.8

4 / 4

1333/1600

6

3570

SR0T7

N0

77/67.4

HDG2500

I5 3rd Gen.

3.4

3.8

4 / 4

1333/1600

6

3570K

SR0PM

E1

77/67.4

HDG4000

(Ivy Bridge)

3.3

3.7

4 / 4

1333/1600

6

3550

SR0P0

E1

77/67.4

HDG2500

3.2

3.6

4 / 4

1333/1600

6

3470

SR0T8

N0

77/67.4

HDG2500

3.1

3.8

4 / 4

1333/1600

6

3570S

SR0T9

N0

65/69.1

HDG2500

3.1

3.5

4 / 4

1333/1600

6

3450

SR0PF

E1

77/67.4

HDG2500

3.1

3.3

4 / 4

1333/1600

6

3350P

SR0WS

E1

69/67.4 -

3.0

3.7

4 / 4

1333/1600

6

3550S

SR0P3

E1

65/69.1

HDG2500

3.0

3.2

4 / 4

1333/1600

6

3330

SR0RQ

E1

77/67.4

HDG2500

2.9

3.6

4 / 4

1333/1600

6

3475S

SR0PP

E1

65/69.1

HDG4000

2.9

3.6

4 / 4

1333/1600

6

3470S

SR0TA

N0

65/69.1

HDG2500

2.9

3.6

2 / 4

1333/1600

3

3470T

SR0RJ

L1

35/65.0

HDG2500 *

2.8

3.5

4 / 4

1333/1600

6

3450S

SR0P2

E1

65/69.1

HDG2500

2.7

3.5

4 / 4

1333/1600

6

3330S

SR0RR

E1

65/

HDG2500

2.3

3.2

4 / 4

1333/1600

6

3570T

SR0P1

E1

45/69.8

HDG2500

3.3

3.7

4 / 4

1066/1333

6

2550K

SR0QH

D2

95/72.6

-

I5 2nd Gen.

3.3

3.7

4 / 4

1066/1333

6

2500K

SR008

D2

95/72.6

HDG3000

(Sandy Bridge)

3.3

3.7

4 / 4

1066/1333

6

2500

SR00T

D2

95/72.6

HDG2000

3.2

3.5

4 / 4

1066/1333

6

2450P

SR0G1

D2

95/72.6 -

3.1

3.4

4 / 4

1066/1333

6

2380P

SR0G2

D2

95/72.6

-

3.1

3.4

4 / 4

1066/1333

6

2400

SR00Q

D2

95/72.6

HDG2000

3.0

3.3

4 / 4

1066/1333

6

2320

SR02L

D2

95/72.6

HDG2000

2.9

3.2

4 / 4

1066/1333

6

2310

SR02K

D2

95/72.6

HDG2000

2.8

3.1

4 / 4

1066/1333

6

2300

SR00D

D2

95/72.6

HDG2000

2.7

3.7

4 / 4

1066/1333

6

2500S

SR009

D2

65/69.1

HDG2000

2.7

3.5

2 / 4

1066/1333

3

2390T

SR065

Q0

35/65.0

HDG2000

2.5

3.3

4 / 4

1066/1333

6

2405S

SR0BB

D2

65/69.1

HDG3000

2.5

3.3

4 / 4

1066/1333

6

2400S

SR00S

D2

65/69.1

HDG2000

2.3

3.3

4 / 4

1066/1333

6

2500T

SR00A

D2

45/69.8

HDG2000

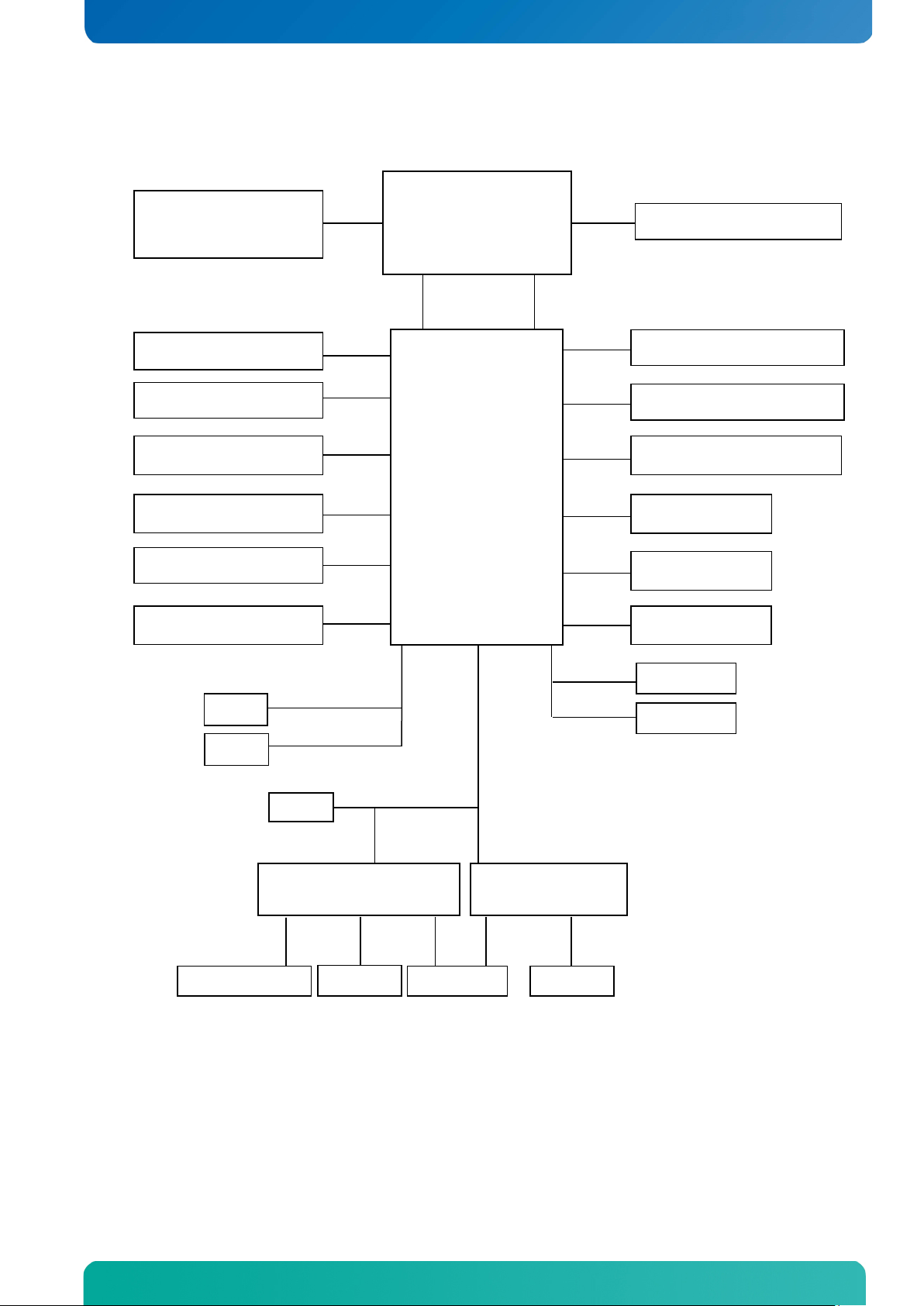

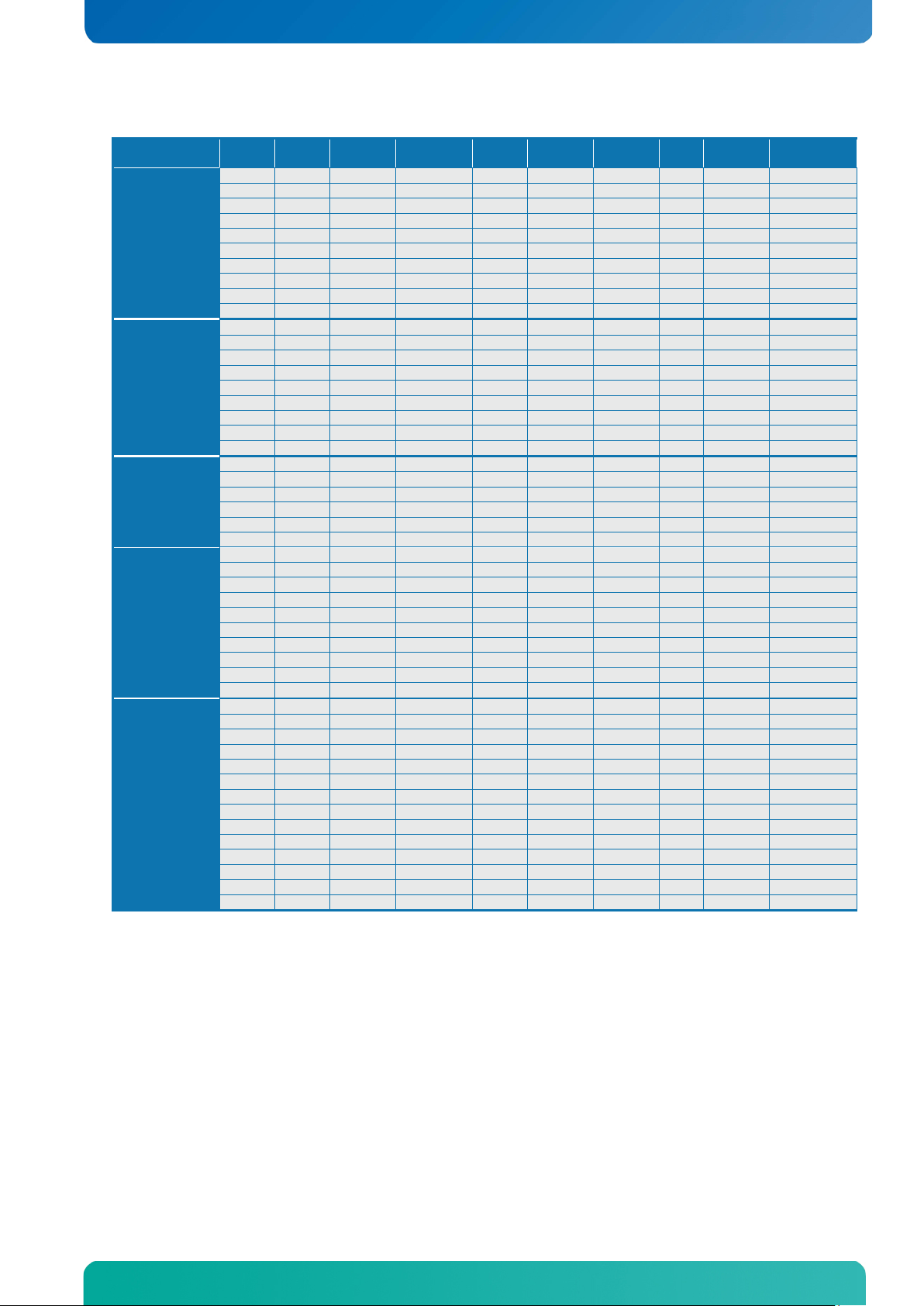

System Specification

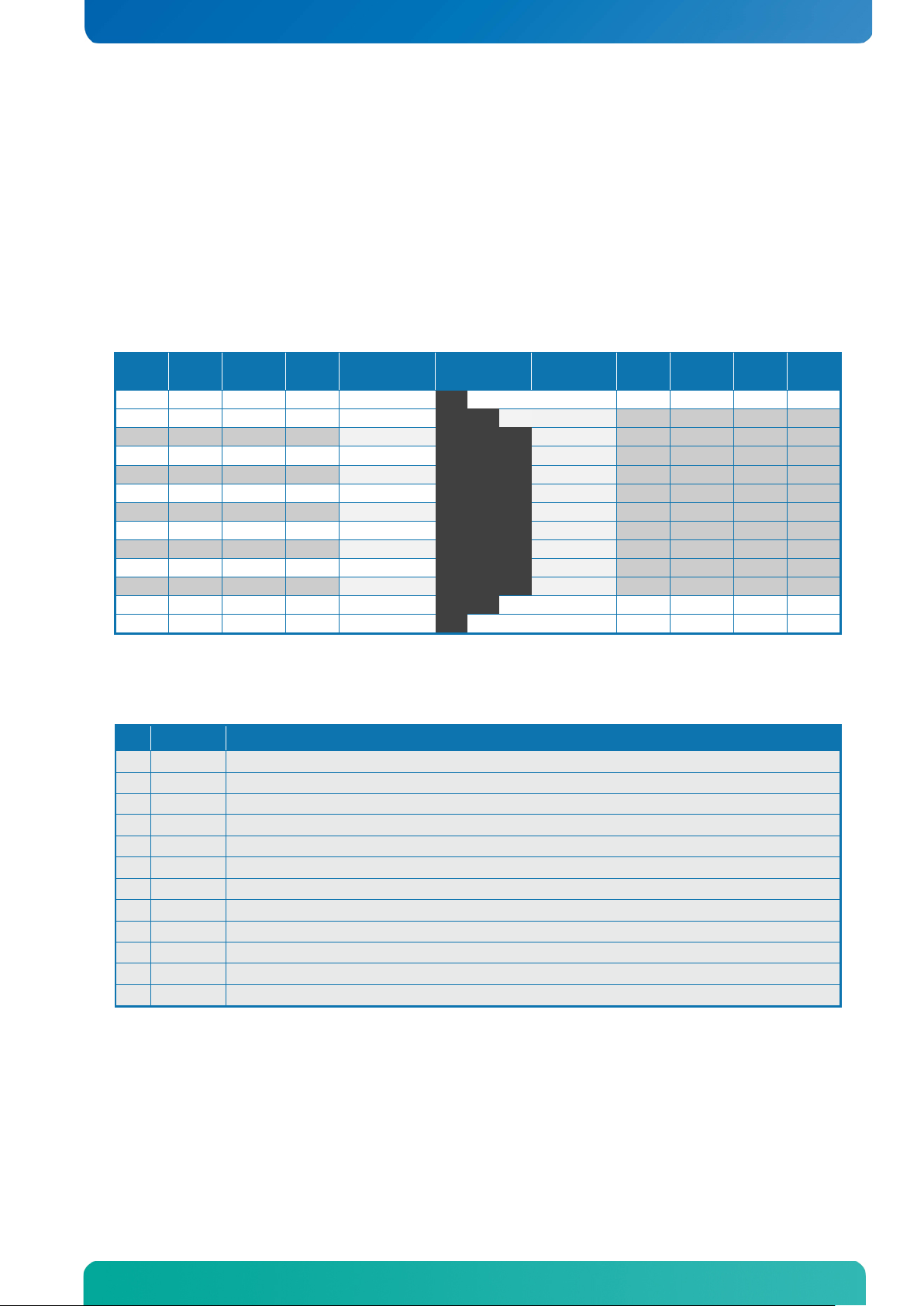

2.3 Processor Suppor t Table

The KTQ77 is designed to support the following LGA1155 processors (up to 95W power consumption):

nd

and 3rd generation Intel® Core™ i7 processor

2

nd

2

and 3rd generation Intel® Core™ i5 processor

nd

2

and 3rd generation Intel® Core™ i3 processor

Pentium and Celeron

In the following list you will find all CPU’s suppor t ed b y the chipset in ac cor din g to Inte l.

Embedded CPU’s are indic ated by green text, succ essfully tested CPU’s are indicated b y highlighted

text, successfully tested embedded CPU’s are indicated by green and highlighted text and failed

CPU’s are indicated by red text.

Some processors in the l ist are distributed from Kontron, thos e CPU’s are marked by an * (asterisk ).

However please notice that this marking is only guide line and maybe not fully updated.

Step

Page 18

KTQ77/Flex Users Guide

KTD-N0848-C Page 18

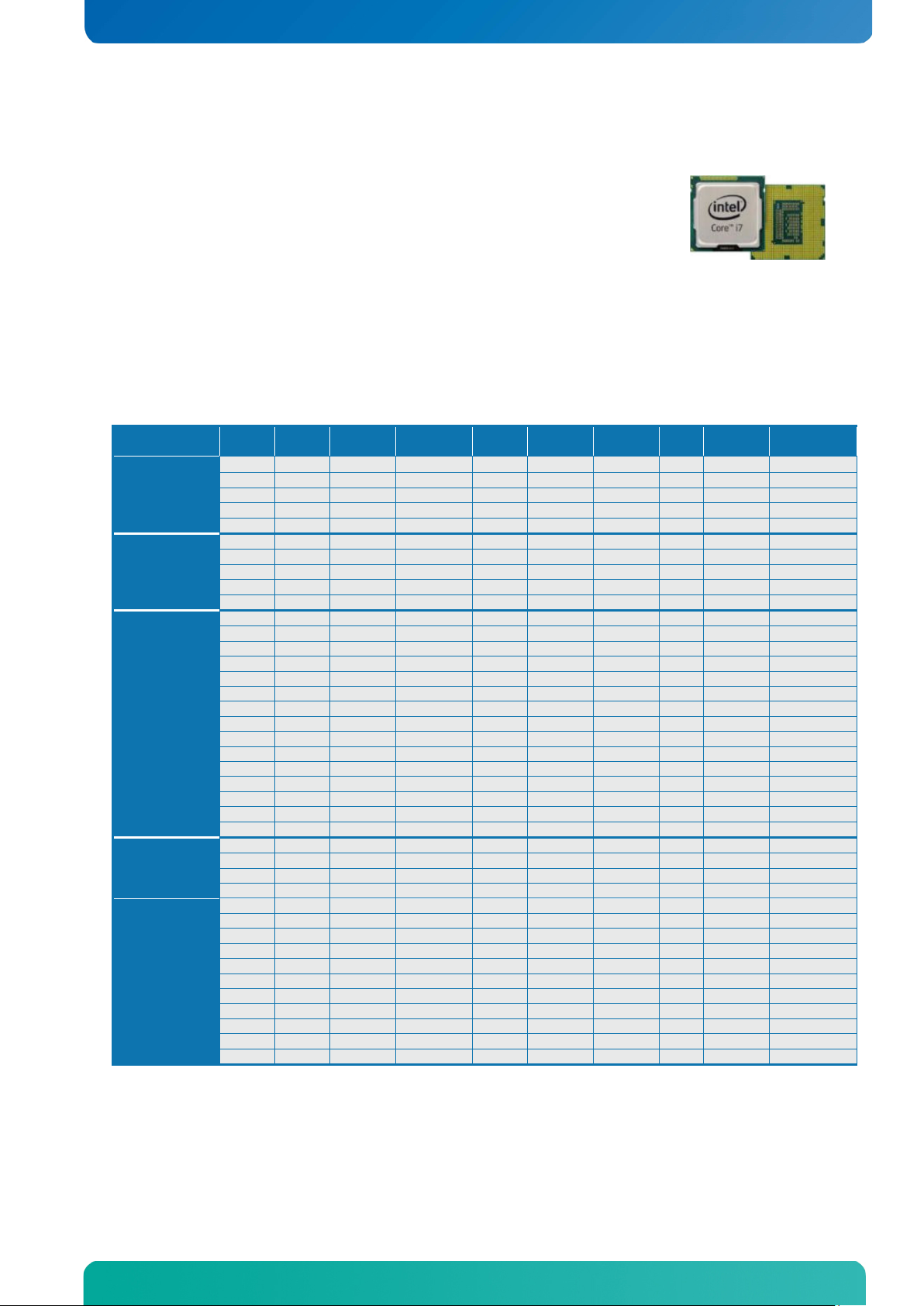

Processor

Brand

Clock

[GHz]

Turbo

[GHz]

Cores /

Threads

Bus

[MHz]

Cache

[MB]

CPU

Number

sSpec

no.

TG

[W/ºC]

Note

3.5 - 2 / 4

1333/1600

3

3250

SR0YX

P0

55/65.3

HDG2500

I3 3rd Gen.

3.4 - 2 / 4

1333/1600

3

3245

SR0YL

L1

55/65.3

HDG4000

(Ivy Bridge)

3.4 - 2 / 4

1333/1600

3

3240

SR0RH

L1

55/65.3

HDG2500

3.3 - 2 / 4

1333/1600

3

3225

SR0RF

L1

55/65.3

HDG4000

(No vPRO)

3.3 - 2 / 4

1333/1600

3

3220

SR0RG

L1

55/65.3

HDG2500

3.2 - 2 / 4

1333/1600

3

3210

SR0YY

P0

55/65.3

HDG2500

3.0 - 2 / 4

1333/1600

3

3250T

SR0YW

P0

35/65.0

HDG2500

2.9 - 2 / 4

1333/1600

3

3240T

SR0RK

L1

35/65.0

HDG2500

2.8 - 2 / 4

1333/1600

3

3220T

SR0RE

L1

35/65.3

HDG2500

3.4 - 2 / 4

1066/1333

3

2130

SR05W

Q0

65/69.1

HDG2000

I3 2nd Gen.

3.3 - 2 / 4

1066/1333

3

2125

SR0AY

J1

65/69.1

HDG3000

(Sandy Bridge)

3.3 - 2 / 4

1066/1333

3

2120

SR05Y

Q0

65/69.1

HDG2000

3.1 - 2 / 4

1066/1333

3

2105

SR0BA

J1

65/69.1

HDG3000

(No vPRO)

3.1 - 2 / 4

1066/1333

3

2100

SR05C

Q0

65/69.1

HDG2000

3.1 - 2 / 4

1066/1333

3

2102

SR05D

Q0

65/69.1

HDG2000

2.6 - 2 / 4

1066/1333

3

2120T

SR060

Q0

35/65.0

HDG2000

2.5 - 2 / 4

1066/1333

3

2100T

SR05Z

Q0

35/65.0

HDG2000

3.1 - 2 / 2

1066/1333

3

G870

SR057

Q0

65/69.1

HDG

3.0 - 2 / 2

1066/1333

3

G860

SR058

Q0

65/69.1

HDG

Pentium

2.9 - 2 / 2

1066/1333

3

G850

SR05Q

Q0

65/69.1

HDG

2.9 - 2 / 2

1066

3

G645

SR0RS

Q0

65/69.1

HDG

2.8 - 2 / 2

1066/1333

3

G840

SR05P

Q0

65/69.1

HDG

2.8 - 2 / 2

1066

3

G640

SR059

Q0

65/69.1

HDG

2.7 - 2 / 2

1066

3

G632

SR05N

Q0

65/69.1

HDG

2.7 - 2 / 2

1066

3

G630

SR05S

Q0

65/69.1

HDG

2.8 - 2 / 2

1066/1333

3

G860T

SR0MF

Q0

35/65.0

HDG

2.6 - 2 / 2

1066

3

G620

SR05R

Q0

65/69.1

HDG

2.6 - 2 / 2

1066

3

G622

- - 65/69.1

HDG

2.5 - 2 / 2

1066

3

G645T

SR0S0

Q0

35/65.0

HDG

2.4 - 2 / 2

1066

3

G640T

SR066

Q0

35/65.0

HDG

2.2 - 2 / 2

1066

3

G620T

SR05T

Q0

35/65.0

HDG

2.3 - 2 / 2

1066

3

G630T

SR05U

Q0

35/65.0

HDG

2.7 - 2 / 2

1333

2

G1620

SR10L

P0

55

HDG *

2.7 - 2 / 2

1066

2

G555

SR0RZ

Q0

65/69.1

HDG

2.6 - 2 / 2

1333

2

G1610

SR10K

P0

55

HDG *

2.6 - 2 / 2

1066

2

G550

SR061

Q0

65/69.1

HDG

2.5 - 2 / 2

1066

2

G540

SR05J

Q0

65/69.1

HDG

Celeron

2.4 - 2 / 2

1066

2

G530

SR05H

Q0

65/69.1

HDG

2.3 - 2 / 2

1333

2

G1610T

SR10M

P0

35/

HDG *

2.2 - 2 / 2

1066

2

G550T

SR05V

Q0

35/65.0

HDG

2.1 - 2 / 2

1066

2

G540T

SR05L

Q0

35/65.0

HDG

2.0 - 2 / 2

1066

2

G530T

SR05K

Q0

35/65.0

HDG

2.0 - 1 / 2

1066/1333

1.5

G470

SR0S7

Q0

35/65.5

HDG

1.8 - 1 / 2

1066

1.5

G460

SR0GR

Q0

35/65.5

HDG

1.6 - 1 / 1

1066

1

G440

SR0BY

Q0

35/65.5

HDG

System Specification

Step

(*) ECC not supported on KTQ77.

Not all CPUs, even of s ame type, support a ll functions ex . i7 3770K, i7 2600K, i5 3570K, 3450, 3450S,

3350P, 3330S, 3330 and i5 2500K, 2300, 2310, 232 0, 2380P, 2450P , 2550K doesn’t sup port vPro while

all other i7 and i5 does.

Intel® Turbo Boost T echnology 2.0 is sup ported by i5 and i7, as indicated in above list of processors,

and is enabling overclocking of all cores, when operated within the limits of thermal design power,

temperature and current.

Page 19

KTQ77/Flex Users Guide

KTD-N0848-C Page 19

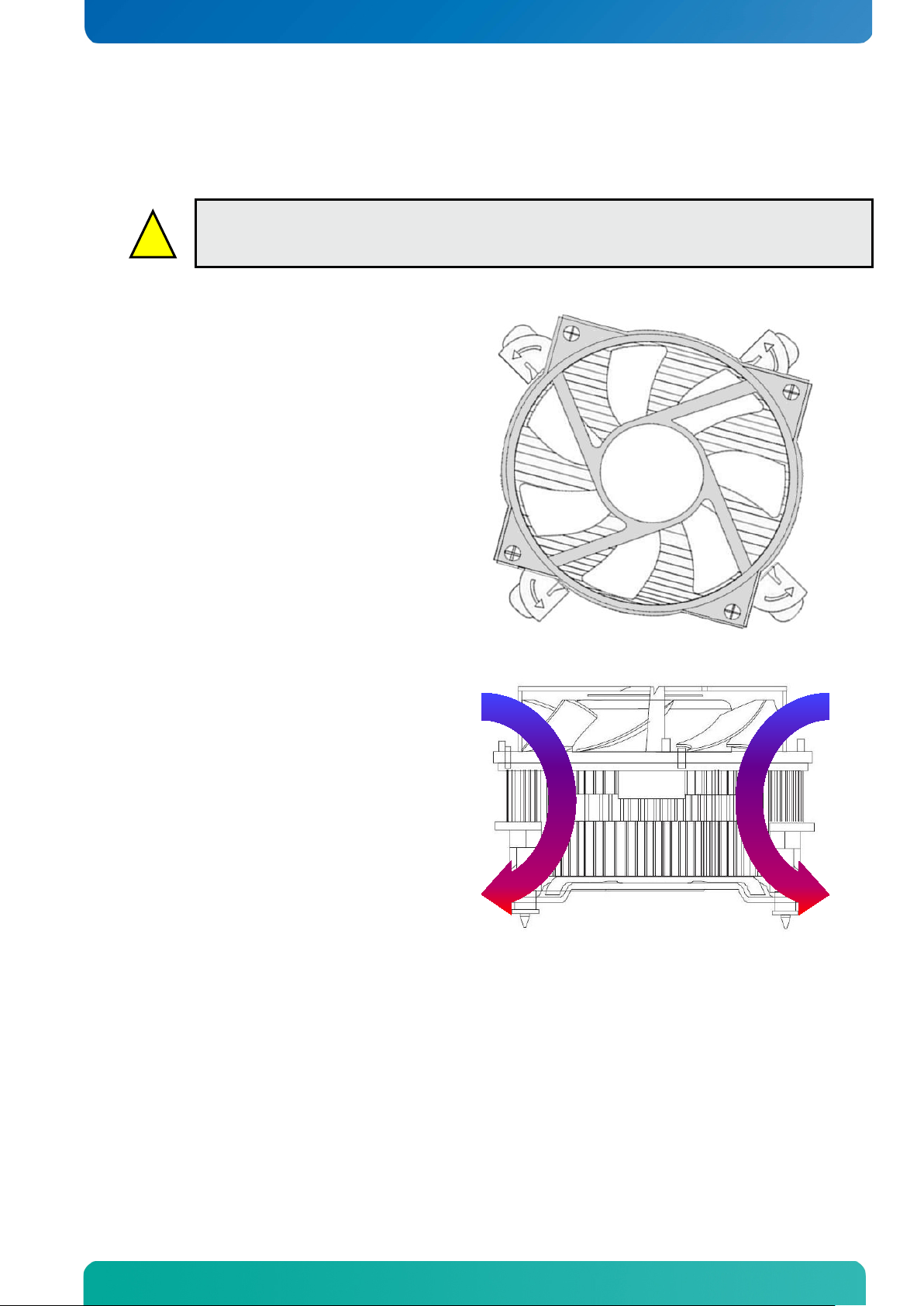

!

Warning: Make sure sufficient airflow is always present around the components located below

or is blocking the airflow around these components, causing reduced lifetime.

It is recommended to use a cooler like the Kontron

Components below the cooler

Note: The temperature of the air blo wn out of the cooler must be les s than 7 0ºC maximum in order not

System Specification

Sufficient cooling must be applied to the CPU in order to remove the effect as listed in above table

(Thermal Guideline). The sufficient cooling is also depending on the maximum (worst-case) ambient

operating temperature and the actual load of processor.

PN 1046-6305 “KTQ77 Cooler”.

The design of this cooler makes sure airflow is

always present around th e components below the

cooler. Even if F an is s et to be of f, it is s till runn ing

a minimum RPM (Rotation Per Minute).

the cooler. Different coolers are available on the market and some is not generating any airflow

Air sucked in to the cooler

Air blown out of the cooler

to overheat components near the C PU. Ho wever m ost CPU’s re quires m ax imum 67.4ºC , so in order n ot

to violate the CPU specification the temperature of the air should be maximum ~65ºC.

Page 20

KTQ77/Flex Users Guide

KTD-N0848-C Page 20

DIMM Type

Module

Memory

[Mill/s]

Processor

[MHz]

Resulting

[MHz]

Peak transfer

[MB/s]

DDR3 1066

PC3-8500

1066

1066 / 1333

533

8533

DDR3 1333

PC3-10600

1333

1333/1600

666

10666

DDR3 1600

PC3-12800

1600

1333

666

10666

DDR3 1600

PC3-12800

1600

1600

800

12800

DDR3 (SLOT B1)

System Specification

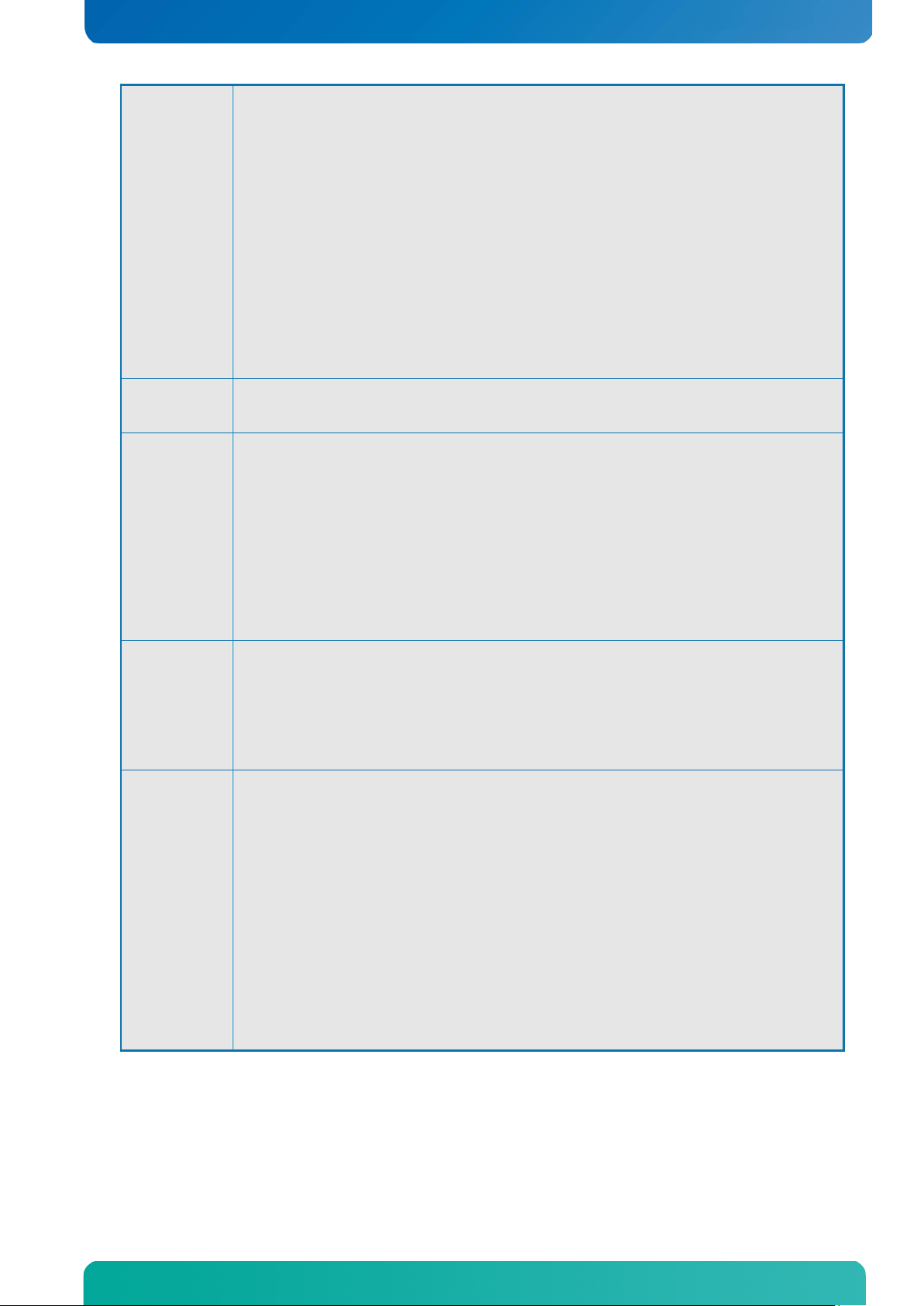

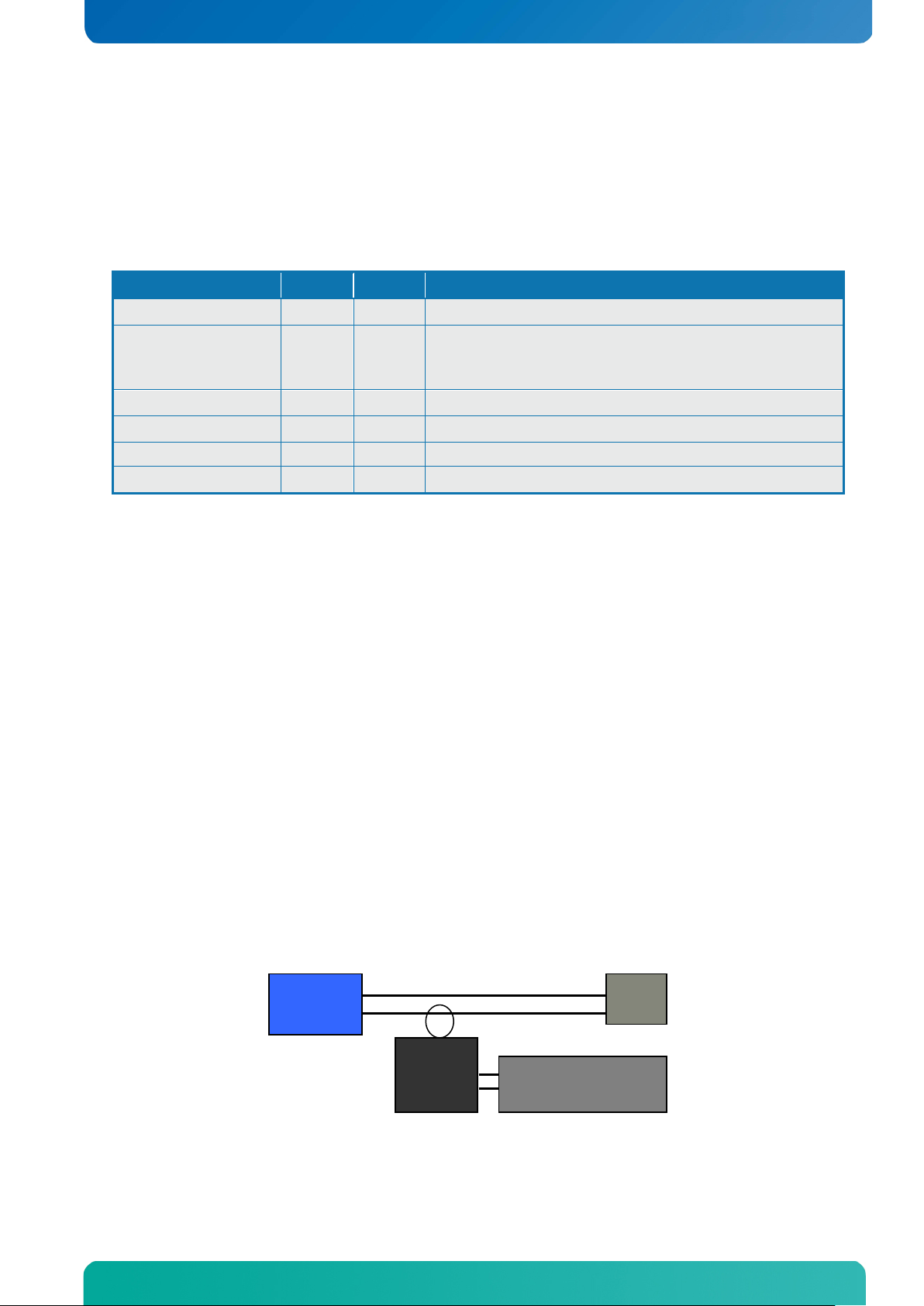

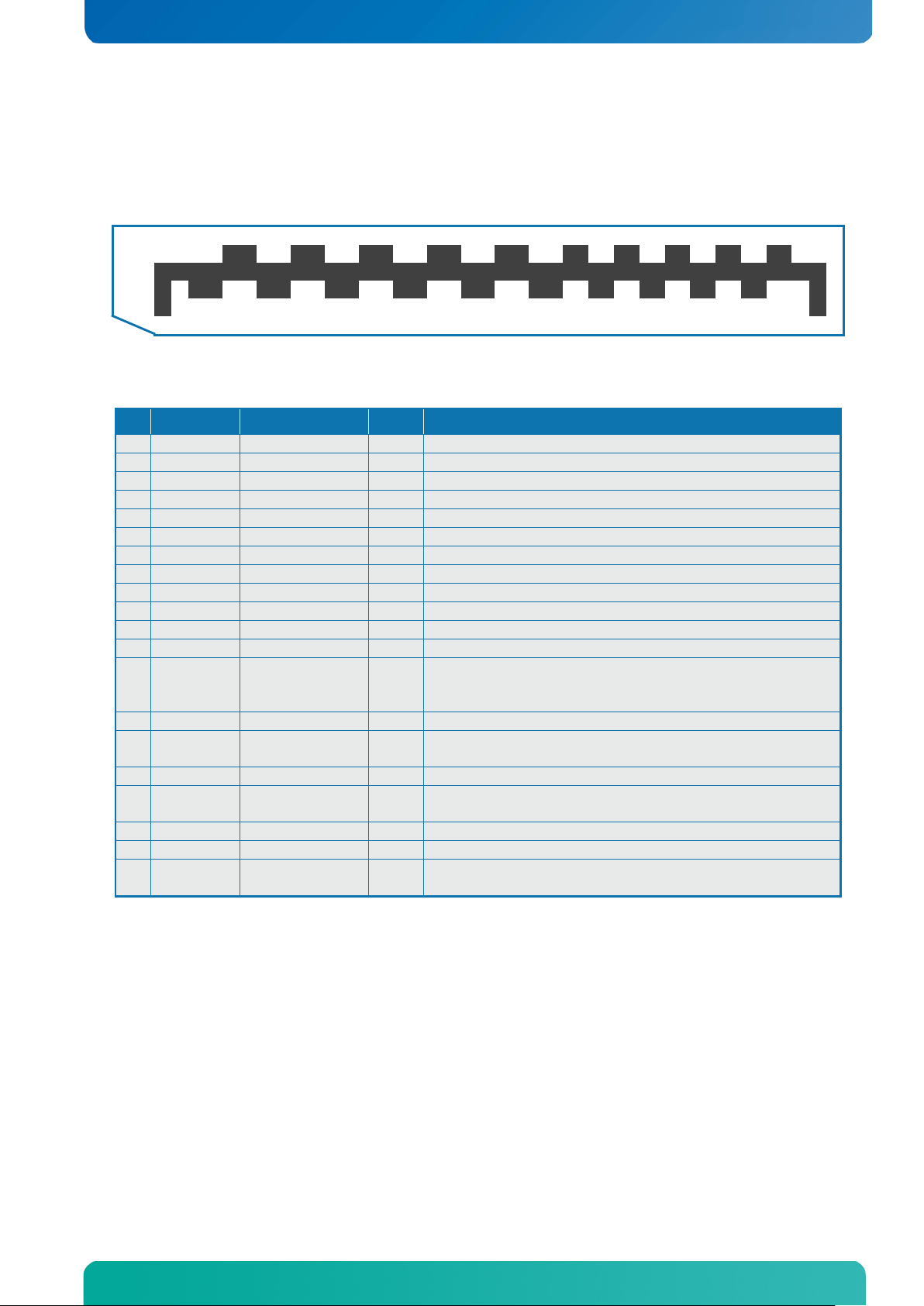

2.4 System Memor y support

The KTQ77/FLEX has four DDR3 UDIMM sockets. The sockets support the following memory features:

• 4x DDR3 1.5V UDIMM 240-pin

• Dual-channel with 2 UDIMM per channel

• Single/dual rank unbuffered 1333/1600MT/s (PC3-10600/PC3-12800)

The supported 2

From 1GB and up to 4x 8G B.

Note: Less than 4GB displayed in System Properties using 32bit OS

(Shared Video Memory/PCI resources is subtracted)

• SPD timings supported

• ECC not supported

The installed DDR3 DIMM should sup port Ser ial Presenc e Detect ( SPD) da ta str ucture. This allows t he

BIOS to configure the memory controller for optimal performance. If non-SPD memory is used, the

BIOS will attempt to configure the memory settings, but performance and reliability may be impacted.

Memory Operating Frequencies

Regardless of the DIMM type used, the memory frequency will either be equal to or less than the

processor system bus frequency. For example, if DDR3 1600 m emor y is used with a 1333 MHz s ys te m

bus frequency processor, the m emory clock will op erate at 666 MHz. The table below list s the resulting

operating memory frequencies based on the combination of DIMMs and processors.

nd

Generation Core i5 support 1066/1333 MT/s

Notes: Kontron offers the following memory modules:

Please notice that not all speeds are supported by all CPU’s.

1054-2766 1GB DDR3 1066

1031-9872 1GB DDR3 1333

1054-3706 1GB DDR3 1600

1054-2768 2GB DDR3 1066

1054-3702 2GB DDR3 1333

1054-3707 2GB DDR3 1600

1054-3700 4GB DDR3 1066

1054-3703 4GB DDR3 1333

1054-3708 4GB DDR3 1600

1054-3704 8GB DDR3 1333

1052-5601 8GB DDR3 1600

In order to support Intel ® AMT (Management Engine) SLOT A0 must always be populated. In case of

using more than a single DIMM it is recommended to populate A0 + B0 first.

name

Data

transfers

system bus

frequency

memory clock

frequency

DDR3 (SLOT B0)

DDR3 (SLOT A1)

DDR3 (SLOT A0)

rate

Page 21

KTQ77/Flex Users Guide

KTD-N0848-C Page 21

System Specification

2.5 KTQ77 Graphics Subsystem

The KTQ77 equipped wit h Intel 3rd generatio n Core i3, i5 or i7 processor, supports Intel ® HD Graphics

2500/4000 depending on specific processor and KTQ77 equipped with Intel 2

processor, s upports Intel ® HD Graphics 2000 (only i5-2400 supported). In the following o nly GFX for

rd

generation core processors are described.

3

All KTQ77 versions support analogue VG A and digital displ ay ports (2x DP) via the Intel ® Q77 Chipset.

Optionally LVDS support.

The DP interface supp orts the Displa yPort 1.2 specificatio n. The PCH supports High-bandwidth Digital

Content Protection for high definition content playback over di gital interfaces. T he PCH also integrates

audio codecs for audio support over DP interfaces.

Up to three displays (any three display outputs) can be activated at the same time and be used to

implement dual independent display support and/or mirror display support. PCIe and PCI graphics cards

can be used to replace on-board graphics or in combination with on-board graphi c s .

nd

generation Core i5

2.5.1 Intel® HD Graphics 4000/2500

Features of the Intel HD Graphics 4000/2500 build into the i3, i5 and i7 processors , includes:

• High quality graphics engine supporting

o DirectX11 and OpenGL 4.0 compliant

o Shader Model 5.0 support

o Intel ® Clear Video HD Technology

o Intel ® Quick Sync Video Technology

o Intel ® Flexible Display Interface (Intel ® FDI)

o Core frequency of 650 - 1150 (Turbo) MHz

o Memory Bandwidth up to 21.3 GB/s

o 6 3D Execution Units (HD Graphics 2500)

o 16 3D Execution Units(HD Graphics 4000)

o 1.62 GP/s and 2.7 GP/S pixel rate (DP outputs)

o Hardware Acceleration CVT HD and QSV

o Dynamic Video Memory Technology (DVMT) support up to 1720 MB

• LVDS panel Support (optional), 18/24 bit colours in up to WUXGA (1920x1200) @60 Hz and

SPWG (VESA) colour coding. OpenLDI (JEIDA) colour c oding is 18 bit with or without D it heri ng.

• DP0 and DP1

o 24/30 bit colours in WQXGA (2560x1600 pixels) and HDCP.

o DisplayPort standard 1.2

Use of DP Adapter Converters can implement HDMI

support or second VGA or DVI panel support.

The HDMI interface supports the HDMI 1.4a specification

and includes audio codecs. However lim itat i ons to the

resolution apply:

2048x1536 VGA

1920x1200 HDMI and DVI

DP to VGA DP to HDMI DP to DVI-D

PN 1045-5779 PN 1045-5781 PN 1045-5780

Page 22

KTQ77/Flex Users Guide

KTD-N0848-C Page 22

Supply

Min

Max

Note

ATX supplies

KTQ77

PSU

Gnd

Current

Tektronix DPO 2024

System Specification

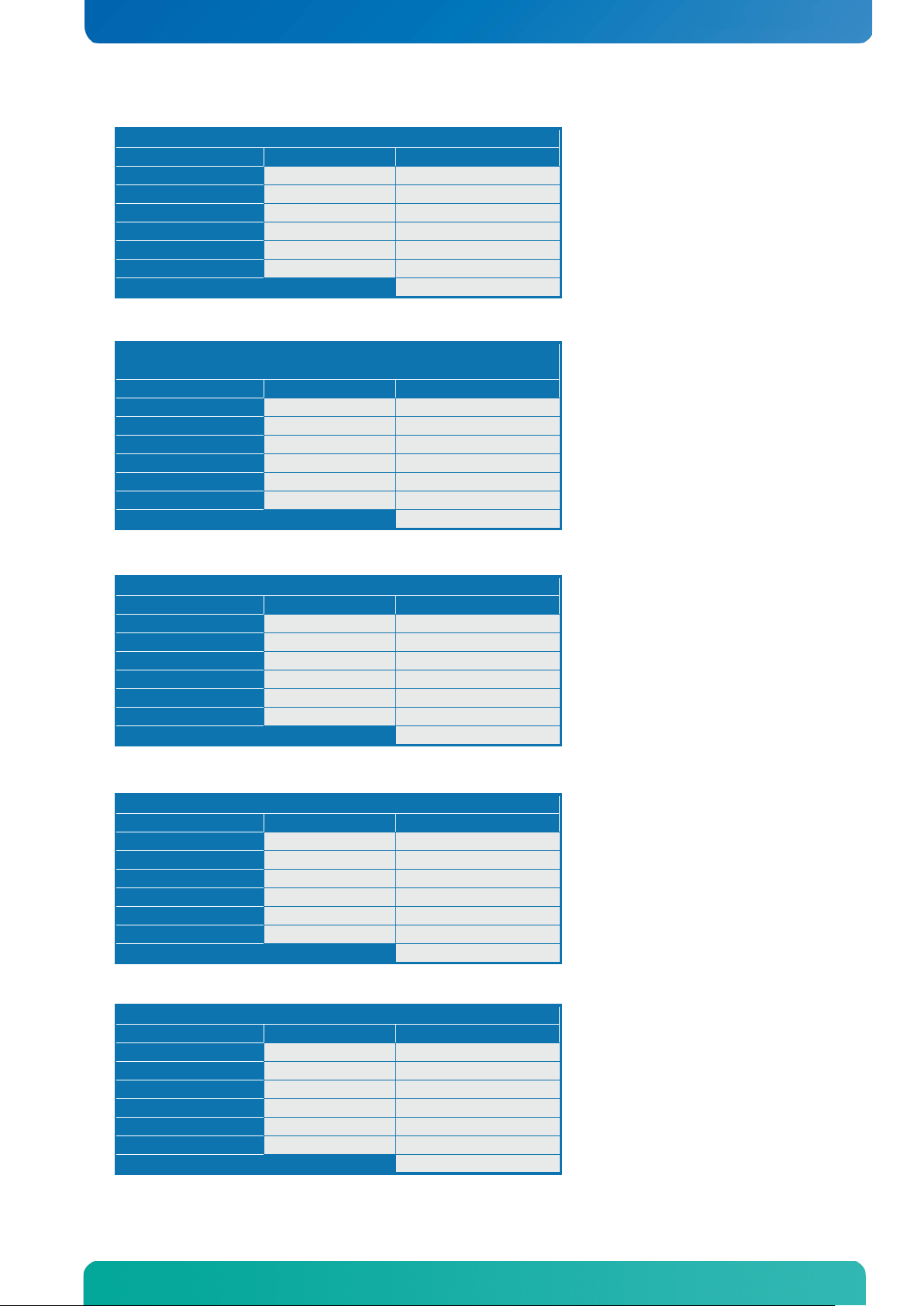

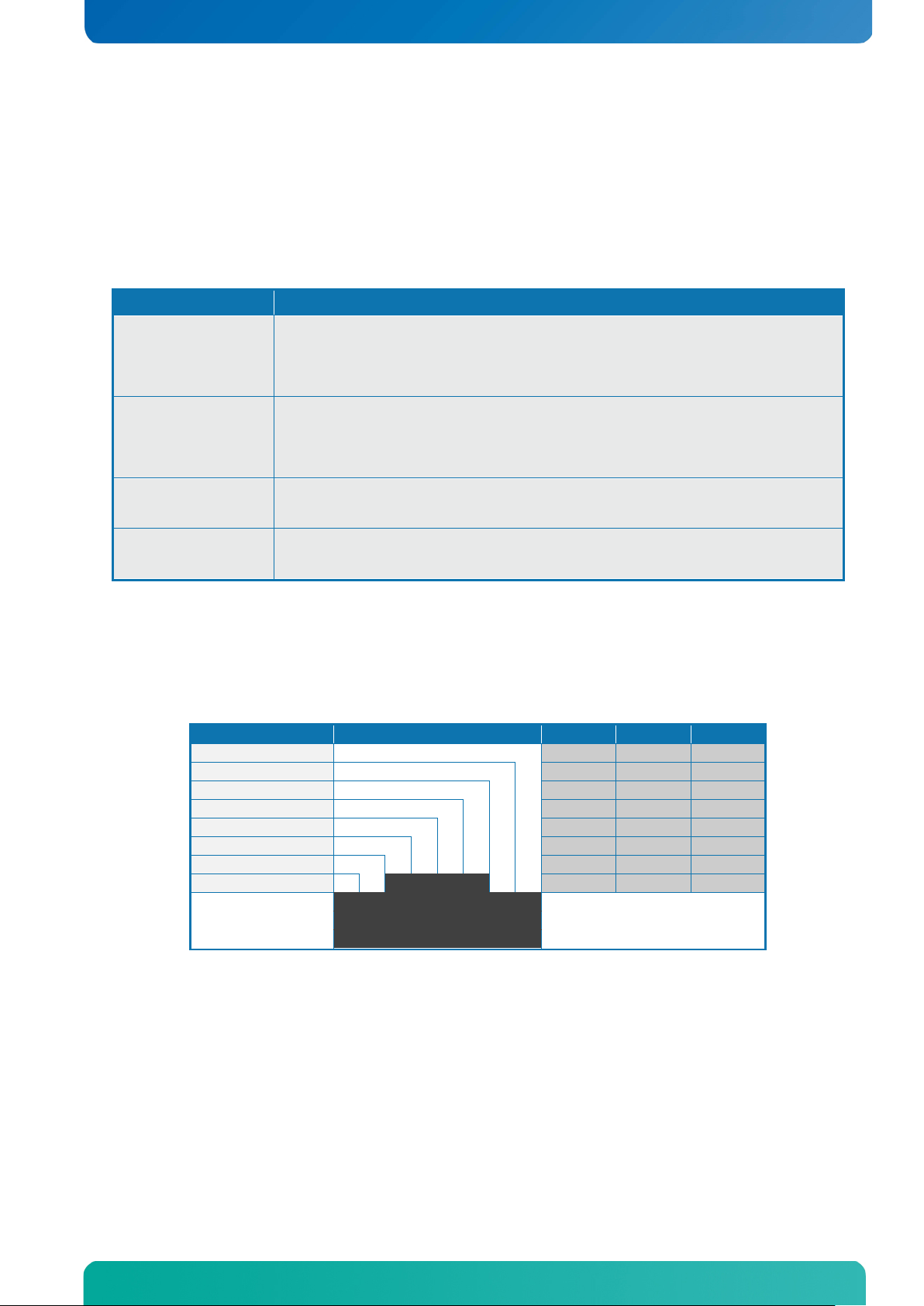

2.6 Power Consumption

In order to ensure safe operation of the board, the ATX12V power supply must monitor the supply

voltage and shut do wn if the supplies are out of ran ge – refer to the hardware manual for the actual

power supply specification. The KTQ77 board is powered through the ATX/BTX connector and

ATX+12V connector. Both connectors must be used in according to the ATX12V PSU standard.

The requirements to the supply voltages are as follows:

VCC3.3 3.135V 3.465V

Vcc 4.75V 5.25V

+12V 11.4V 12.6V

–12V –13.2V –10.8V

-5V -5,50V -4.5V Not required for the KTQ77 board

5VSB 4.75V 5.25V

More detailed Static Power Consumption

On the following pages the power consumption of the KTQ77 Board is measured under:

1- DOS, idle, mean

2- Windows7, Running 3DMARK 2005 & BiT 6, mean

3- S1, mean

4- S3, mean

5- S4, mean

The following items were used in the test setup:

Low Power Setup

Standard system conf iguration equipped with PCI card, Internal graphics , 2x SATA disks, Intel i3

CPU, 2x DIMM 2GB Modules, DP Monitor, Keyboard & Mous e. 1x 1-4G B USB Flash Stick , 1x 1GB

LAN

High Power Setup

Standard system configuration equipped with PCI card, PCIex4, PCIex16, miniPCIe WLAN, 4x

SATA disks, Intel i7 CPU, 4x DIMM 2GB Modules, DP M onitor, Keyboar d & Mouse, 3x 1-4GB US B

Flash Stick, 3x 1GB LAN.

Note: The Power consumption of Display and HD are not included.

Should be ±5% for compliance with the ATX specification

Should be ±5% for compliance with the ATX specification.

Should be minimum 5.00V measured at USB connectors

in order to meet the requirements of USB standard.

Should be ±5% for compliance with the ATX specification

Should be ±10% for compliance with the ATX specification

Should be ±5% for compliance with the ATX specification

Probe

Page 23

KTQ77/Flex Users Guide

KTD-N0848-C Page 23

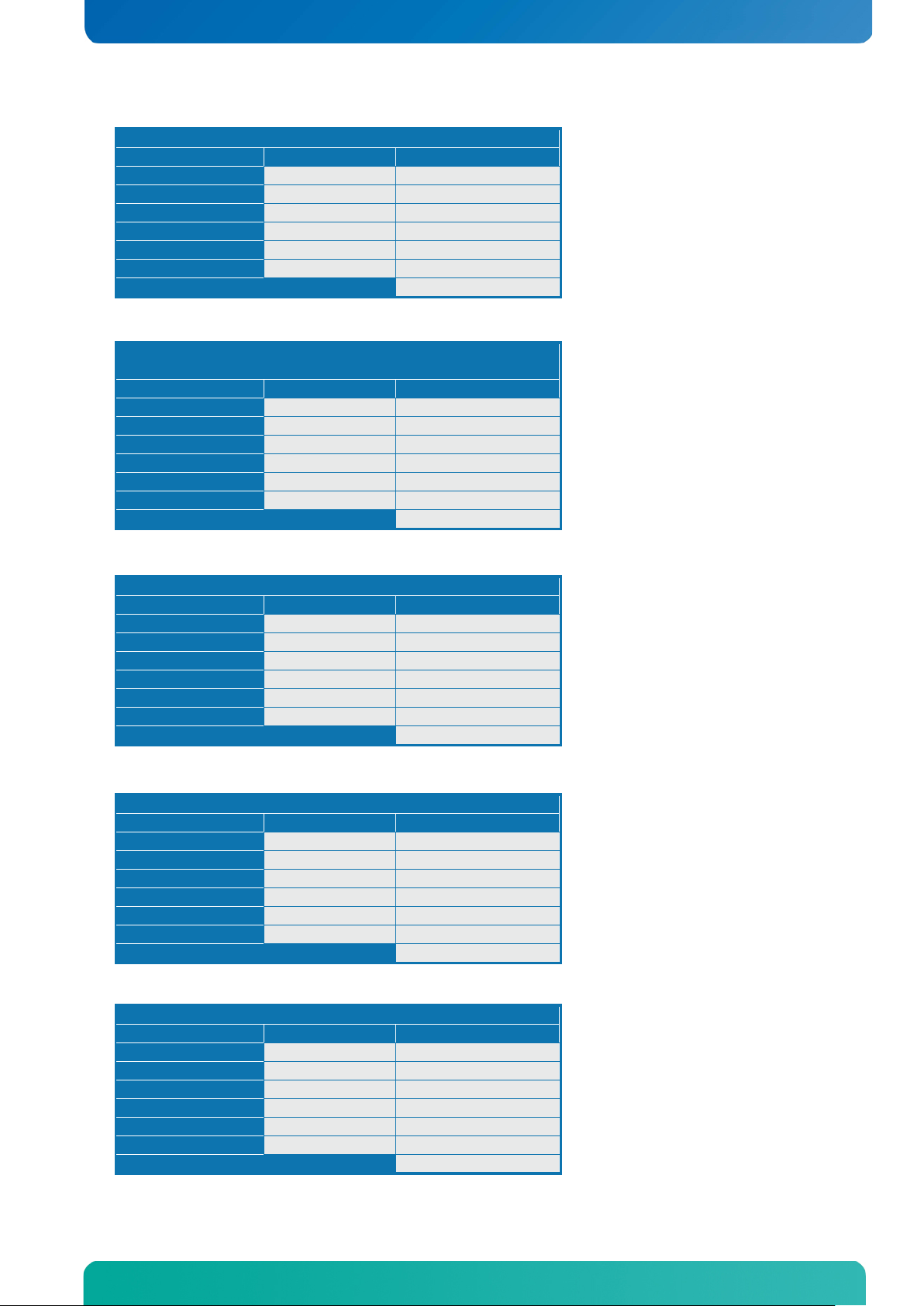

DOS Idle, Mean, No external load

Supply

Current draw

Power consumption

+12V

0,37A

3,96W

+12V P4

0,80A

9,60W

+5V

1,22A

6,10W

+3V3

0,25A

0,83W

-12V

< 100mA

5VSB

< 10 mA

Total

20,49W

Windows 7, mean

3DMARK2005 (first scene) & BiT 6

Supply

Current draw

Power consumption

+12V

0,37A

4,44W

+12V P4

1,62A

19,44W

+5V

2,15A

10,75W

+3V3

0,39A

1,29W

-12V

< 100mA

5VSB

< 10 mA

Total

35,92W

S1 Mode, Mean, No external load

Supply

Current draw

Power consumption

+12V

0,30A

3,60W

+12V P4

0,37A

4,44W

+5V

0,85A

4,25W

+3V3

0,28A

0,92W

-12V

< 100mA

5VSB

< 100mA

Total

13,21W

S3 Mode, Mean, No external load

Supply

Current draw

Power consumption

+12V

0

0W

+12V P4

0

0W

+5V

0

0W

+3V3

0

0W

-12V

0

0W

5VSB

< 100mA

<0.5W

Total

<0.5W

S4 Mode, Mean, No external load

Supply

Current draw

Power consumption

+12V

0

0W

+12V P4

0

0W

+5V

0

0W

+3V3

0

0W

-12V

0

0W

5VSB

< 100mA

<0.5W

Total

<0.5W

System Specification

Low Power Setup results:

Page 24

KTQ77/Flex Users Guide

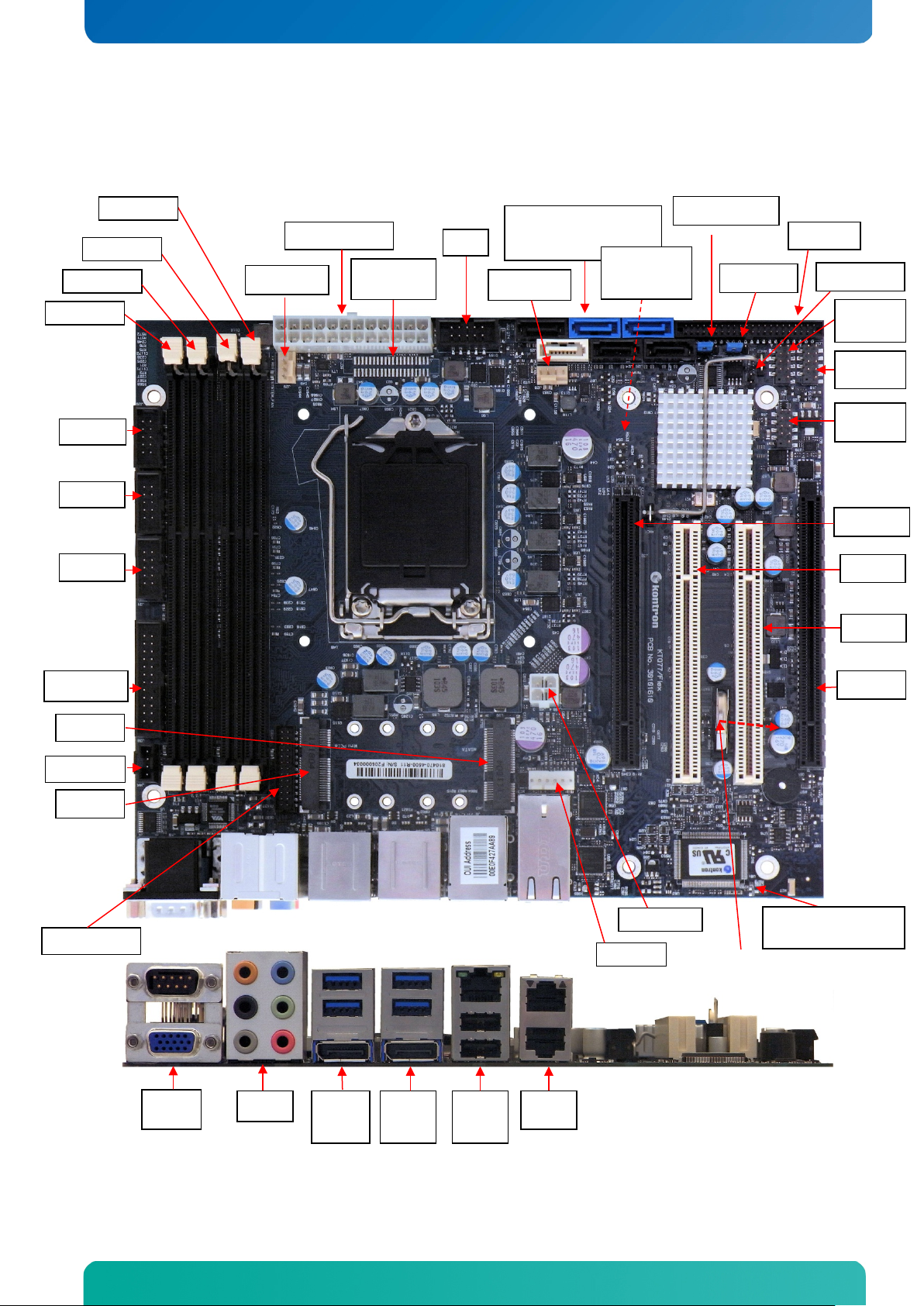

KTD-N0848-C Page 24

DOS Idle, Mean, No external load

Supply

Current draw

Power consumption

+12V

1,72A

20,64W

+12V P4

0,98A

11,76W

+5V

1,60A

8,00W

+3V3

1,38A

4,55W

-12V

< 500mA

5VSB

< 50 mA

Total

44,55W

Windows 7, mean

3DMARK2005 (first scene) & BiT 6

Supply

Current draw

Power consumption

+12V

1,70A

20,40W

+12V P4

3,60A

43,20W

+5V

2,60A

13,00W

+3V3

1,86A

6,138W

-12V

< 100mA

5VSB

< 10 mA

Total

82,74W

S1 Mode, Mean, No external load

Supply

Current draw

Power consumption

+12V

1,40A

16,80W

+12V P4

0,52A

6,24W

+5V

1,10A

5,50W

+3V3

1,26A

4,16W

-12V

< 100mA

5VSB

< 10 mA

Total

32,70W

S3 Mode, Mean, No external load

Supply

Current draw

Power consumption

+12V

0

0W

+12V P4

0

0W

+5V

0

0W

+3V3

0

0W

-12V

0

0W

5VSB

< 100mA

<0.5W

Total

<0.5W

S4 Mode, Mean, No external load

Supply

Current draw

Power consumption

+12V

0

0W

+12V P4

0

0W

+5V

0

0W

+3V3

0

0W

-12V

0

0W

5VSB

< 100mA

<0.5W

Total

<0.5W

System Specification

High Power Setup results:

Page 25

KTQ77/Flex Users Guide

KTD-N0848-C Page 25

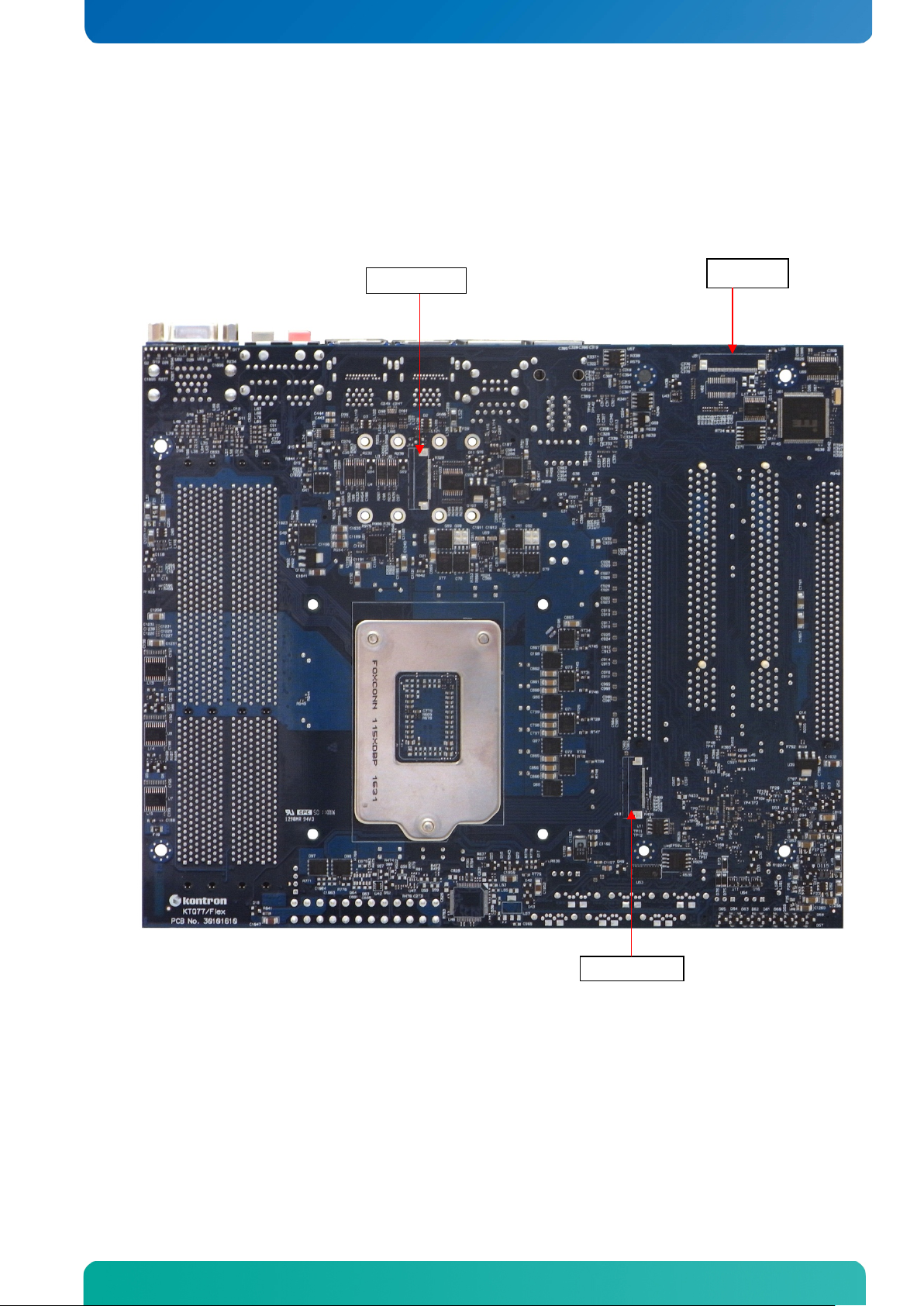

Connector Location

Feature

COM1

VGA

PCIex16

ATX/ BTXPWR

Audio

USB12

USB13

Frontpanel

CDROM

Audioheader

COM3

COM2

FAN_SYS

FAN_CPU

ETH1

USB4

COM4

PCI0

ETH2

ETH3

ClrCMOS

Sata5 - Sata0 - Sata1

(see note)

LVDS

(optionally)

PCIex4

SPI recover

SPI

USB1

DP0

USB3

DP1

Notes: Sata0/Sata1support up to 6GB/s and Sata2/Sata3/Sata4/Sata5 support up to 3GB/S.

XDP-PCH

(see note)

mSATA

mPCIe

PCI1

USB8

USB9

USB10

USB11

J12 (not used)

Battery is moved in final

board release

R978 System

Temperature Sensor

3 Connector Locations

3.1 KTQ77/Flex – frontside

Sata2 - Sata3 - Sata4

(backside)

USB2

USB0

USB5

USB0 – USB3 supports USB3.0/USB2.0, USB4 – USB13 supports USB2.0.

Page 26

KTQ77/Flex Users Guide

KTD-N0848-C Page 26

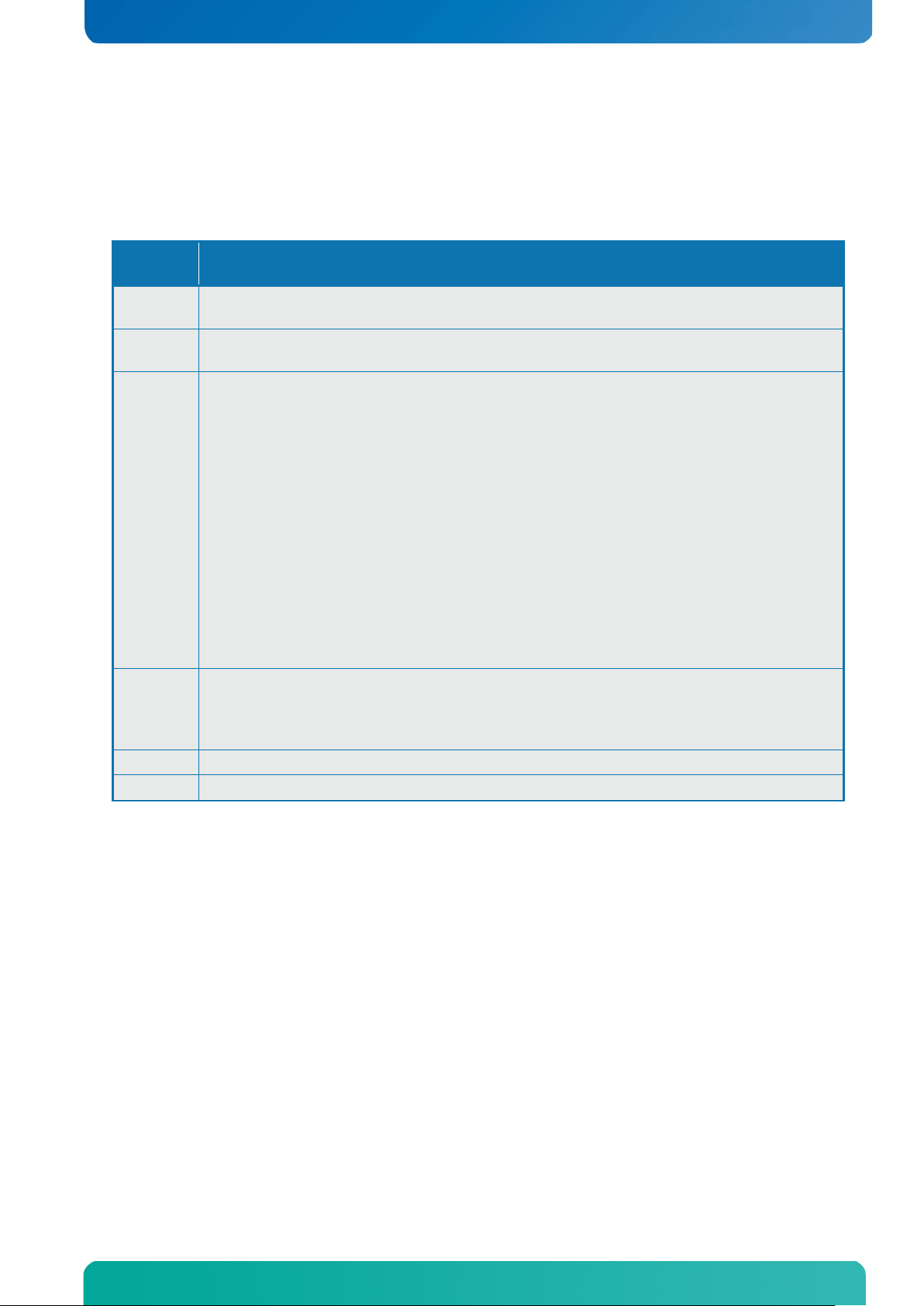

Connector Location

LPT (*)

XDP-CPU (*)

(*) The LPT connector and the XDP connectors are not mounted in volume production.

XDP-PCH (*)

3.2 KTQ77/Flex - backside

Page 27

KTQ77/Flex Users Guide

KTD-N0848-C Page 27

Connector Definitions

4 Connector Definitions

The following sections provide pin definitions and detailed description of all on-board connectors.

The connector definitions follow the following notation:

Column

name

Pin Shows the pin-numbers in the connector. The graphical layout of the connector definition

Signal The mnemonic name of the signal at the current pin. The notation “XX#” states that the

Type AI: Analogue Input.

Ioh: Typical current in mA flowing out of an output pin through a grounded load, while the

Pull U/D On-board pull-up or pull-down resistors on input pins or open-collector output pins.

Note Special remarks concerning the signal.

The abbreviation TBD is used for specifications which are not available yet or which are not sufficiently

specified by the component vendors.

Description

tables is made similar to the physical connectors.

signal “XX” is active low.

AO: Analogue Output.

I: Input, TTL compatible if nothing else stated.

IO: Input / Output. TTL compatible if nothing else stated.

IOT: Bi-directional tristate IO pin.

IS: Schmitt-trigger input, TTL compatible.

IOC: Input / open-collector Output, TTL compatible.

IOD: Input / Output, CMOS level Schmitt-triggered. (Open drain output)

NC: Pin not connected.

O: Output, TTL compatible.

OC: Output, open-collector or open-drain, TTL compatible.

OT: Output with tri-state capability, TTL compatible.

LVDS: Low Voltage Differential Signa l.

PWR: Power supply or ground reference pins.

output voltage is > 2.4 V DC (if nothing else stated).

Iol: Typical current in mA flowing into an output pin from a VCC connected load, while the

output voltage is < 0.4 V DC (if nothing else stated).

Page 28

KTQ77/Flex Users Guide

KTD-N0848-C Page 28

Pull

U/D

Pull

U/D

6

GND

PWR - -

/75R - A0

RED

1 11

NC - - -

7

GND

PWR - -

/75R - A0

GREEN

2 12

DDCDAT

IO

TBD

2K2

8

GND

PWR - -

/75R - A0

BLUE

3 13

HSYNC

O

TBD 9

5V

PWR - - 1 - - - NC

4 14

VSYNC

O

TBD

10 GND

PWR - - - -

PWR

GND

5 15

DDCCLK

IO

TBD

2K2

Pin

Signal

Description

1

RED

Analogue output carrying the red colour values. (75 Ohm cable impedance).

2

GREEN

Analogue output carrying the green colour values. (75 Ohm cable impedanc e).

3

BLUE

Analogue output carrying the blue colour values. (75 Ohm cable impedance).

4

NC

No Connection

5-8

GND

9 5V

This 5V supply is fused by a 1.1A resettable fuse.

10

GND

11

NC

No Connection

12

DDCDAT

Display Data Channel Data. Used as data signal to/from monitors with DDC interface.

13

HSYNC

CRT horizontal synchronization output.

14

VSYNC

CRT vertical synchronization output.

15

DDCCLK

Display Data Channel Clock. Used as clock signal to/from monitors with DDC interface.

IO-Area Connectors

5 IO-Area Connectors

5.1 Display connectors (IO Area)

The KTQ77 family provides one on-board Analogue VGA port, two on-board DP’s (DisplayPort) and

optionally one on-board LVDS panel interf ac e. Two graphic pipes are sup porte d; meaning that up to two

independent displays can be implemented using any two of the above mentioned graphic ports.

.

5.1.1 Analogue VGA (VGA)

Note

Note 1: The +5V supply is fused by a 1.1A resettable fuse

Signal Description - VGA Connector:

Ioh/Iol Type Signal PIN Signal Type Ioh/Iol

Note

Page 29

KTQ77/Flex Users Guide

KTD-N0848-C Page 29

19 17 15 13 11 9 7 5 3 1

20 18 16 14 12 10 8 6 4 2

Pin

Signal

Description

Type

Note

1

Lane 0 (p)

LVDS

2 GND

PWR

3 Lane 0 (n)

LVDS

4 Lane 1 (p)

LVDS

5 GND

PWR

6 Lane 1 (n)

LVDS

7 Lane 2 (p)

LVDS

8 GND

PWR

9 Lane 2 (n)

LVDS

10

Lane 3 (p)

LVDS

11

GND

PWR

12

Lane 3 (n)

LVDS

Internally pull down (1Mohm ) .

DDC channel on pin 15/17, If HDMI adapter used (3.3V)

14

Config2

(Not used)

O

Internally connected to GND

Aux Channel (+)

or DDC Clk

AUX (+) channel used by DP

DDC Clk used by HDMI

16

GND

PWR

Aux Channel (-)

or DDC Data

AUX (-) channel used by DP

DDC Data used by HDMI

18

Hot Plug

I Internally pull down (100Kohm).

19

Return

PWR

Same as GND

Fused by 1.5A resetable PTC fuse, common for DP0 and

DP1

IO-Area Connectors

5.1.2 DP Connectors (DP0/DP1)

The DP (DisplayPort) connectors are based on standard DP type Foxconn 3VD51203-H7JJ-7H or

similar.

13 Config1

15 Aux Ch (p)

17 Aux Ch (n)

20 3.3V PWR

Aux or DDC

selection

I

Aux channel on pin 15/17 selected as default (when NC)

Page 30

KTQ77/Flex Users Guide

KTD-N0848-C Page 30

Signal

PIN

Type

Ioh/Iol

Note

MDI0+

MDI0-

MDI1+

MDI2+

MDI2-

MDI1-

MDI3+

MDI3-

8 7 6 5 4 3 2 1

IO-Area Connectors

5.2 Ethernet Connect ors (IO Area)

The KTQ77 boards supports three channels of 1 0/10 0/ 1000 Mb Et her ne t , one (ETH1) is b as ed on Intel®

Lewisville 82579LM Gigabit PHY with AMT 8.0 support and the two other controllers (ETHER2 &

ETHER3) are based on Intel® Hartwell 82574L PCI Express controller.

In order to achieve the specified performance of the Ethernet port, minimum Category 5 twisted pair

cables must be used with 10/100MB and minimum Category 5E, 6 or 6E with 1Gb LAN networks.

The signals for the Ethernet ports are as follows:

Signal Description

MDI[0]+ / MDI[0]- In MDI mode, this is the first pair in 1000Base-T, i.e. the BI_DA+/- pair, and is

the transmit pair in 10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the BI_DB+/- pair, and is the receive

pair in 10Base-T and 100Base-TX.

MDI[1]+ / MDI[1]- In MDI mode, this is the second pair in 1000Base-T, i.e. the BI_DB+/- pair, and

is the receive pair in 10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the BI_DA+/- pair, and is the transmit

pair in 10Base-T and 100Base-TX.

MDI[2]+ / MDI[2]-

In MDI mode, this is the third pair in 1000Base-T, i.e. the BI_DC+/- pair.

In MDI crossover mode, this pair acts as the BI_DD+/- pair.

MDI[3]+ / MDI[3]-

Note: MDI = Media Dependent Interface.

Ethernet connector 1 (ETH1) is mounted together with USB Ports 4 and 5.

Ethernet connector 2 (ETH2) is mounted together with and above Ethernet connector 3 (ETH3).

The pinout of the RJ45 connectors is as follows:

In MDI mode, this is the fourth pair in 1000Base-T, i.e. the BI_DD+/- pair.

In MDI crossover mode, this pair acts as the BI_DC+/- pair.

Page 31

KTQ77/Flex Users Guide

KTD-N0848-C Page 31

IO-Area Connectors

5.3 USB Connectors (IO Area)

The KTQ77 board contain s two EHCI (Enhanced Host Control ler Interface) and one X HCI (Extensible

Host Controller Interface) . The two EHCI controllers, EHCI1 and EHCI2, supports up to fourteen USB

2.0 ports allowing data transfers up to 480Mb/s. The XHCI controller supports four USB 3.0 ports

allowing data trans fers up to 5Gb/s. The four USB 3.0 ports are shared with four of the US B 2.0 ports

(USB0 – USB3) from the EHCI1.

Legacy Keyboard/Mouse and wakeup from sleep states are supported. Over-current detection on al l

fourteen USB ports is supported. The following USB connectors are available in the IO Area.

USB Port 0 and 1 (via EHCI1/XHCI) are supplied on the combined USB0, USB1 and DP0 connector.

USB Port 2 and 3 (via EHCI1/XH CI) are supplied on the combined USB2, USB3 and DP1 connector.

USB Port 4 and 5 (via EHCI1) are supplied on the combined ETH1, USB4 and USB5 connector.

Note:

For USB2.0 cabling it is required to use only HiSpeed USB cable, specified in USB2.0 standard:

For USB3.0 cabling it is required to use only HiSpeed USB cable, specified in USB3.0 standard:

Page 32

KTQ77/Flex Users Guide

KTD-N0848-C Page 32

Note

Type

Signal

PIN

Signal

Type

Note

IO

USB1-

USB1+

IO 1

PWR

5V/SB5V

1 2 3 4 GND

PWR

IO

RX1-

5 6 7 8 9

TX1+

IO

IO

RX1+

TX1-

IO

PWR

GND IO

USB0-

USB0+

IO 1

PWR

5V/SB5V

1 2 3 4 GND

PWR

IO

RX0-

5 6 7 8 9

TX0+

IO

IO

RX0+

TX0-

IO

PWR

GND

IO-Area Connectors

5.3.1 USB Connector 0/1 (USB0/1)

USB Ports 0 and 1 are mounted together with DP0 port and supports USB3.0/USB2.0.

Note 1: In order to meet the requirements of USB standard, the 5V input supply must be at least 5.00V.

Signal Description

USB0+ USB0-

RX0+ RX0-

TX0+ TX0-

USB1+ USB1-

RX1+ RX1-

TX1+ TX1-

5V/SB5V

Differential pair works as Data/Address/Command Bus.

5V supply for external devices. SB5V is supplied during powerdown to allow

wakeup on USB device activity. Protected by resettable 1A fuse covering both USB

ports.

Page 33

KTQ77/Flex Users Guide

KTD-N0848-C Page 33

Note

Type

Signal

PIN

Signal

Type

Note

IO

USB3-

USB3+

IO 1

PWR

5V/SB5V

1 2 3 4 GND

PWR

IO

RX3-

5 6 7 8 9

TX3+

IO

IO

RX3+

TX3-

IO

PWR

GND IO

USB2-

USB2+

IO 1

PWR

5V/SB5V

1 2 3 4 GND

PWR

IO

RX2-

5 6 7 8 9

TX2+

IO

IO

RX2+

TX2-

IO

PWR

GND

Note

Type

Signal

PIN

Signal

Type

Note

1

PWR

5V/SB5V

1 2 3 4 GND

PWR

IO

USB5-

USB5+

IO 1

PWR

5V/SB5V

1 2 3 4 GND

PWR

IO

USB4-

USB4+

IO

IO-Area Connectors

5.3.2 USB Connector 2/3 (USB2/3)

USB Ports 2 and 3 are mounted together with DP1 port and supports USB3.0/USB2.0.

Note 1: In order to meet the requirements of USB standard, the 5V input supply must be at least 5.00V.

Signal Description

USB2+ USB2-

RX2+ RX2-

TX2+ TX2-

USB3+ USB3-

RX3+ RX3-

TX3+ TX3-

5V/SB5V

Differential pair works as Data/Address/Command Bus.

5V supply for external devices. SB5V is supplied during powerdown to allow

wakeup on USB device activity. Protected by resettable 1A fuse covering both USB

ports.

5.3.3 USB Connector 4/5 (USB4/5)

USB Ports 4 and 5 are mounted together with ETH1 port and supports USB2.0.

Note 1: In order to meet the requirements of USB standard, the 5V input supply must be at least 5.00V.

Signal Description

USB4+ USB4USB5+ USB5-

5V/SB5V

Differential pair works as Data/Address/Command Bus.

5V supply for external devices. SB5V is supplied during powerdown to allow wakeup

on USB device activity. Protected by resettable 1A fuse covering both USB ports.

Page 34

KTQ77/Flex Users Guide

KTD-N0848-C Page 34

Note

Type

Signal

Signal

Type

Note

OA

CEN-OUT

TIP TIP

LINE1-IN-L

IA

OA

LFE-OUT

RING

RING

LINE1-IN-R

IA

PWR

GND

SLEEVE

SLEEVE GND

PWR

OA

REAR-OUT-L

TIP TIP

FRONT-OUT-L

OA

OA

REAR-OUT-R

RING

RING

FRONT-OUT-R

OA

PWR

GND

SLEEVE

SLEEVE GND

PWR

OA

SIDE-OUT-L

TIP TIP MIC1-L

IA

OA

SIDE-OUT-R

RING

RING MIC1-R

IA

PWR

GND

SLEEVE

SLEEVE GND

PWR

Shared with Audio Header

Shared with Audio Header

Shared with Audio Header

Shared with Audio Header

Shared with Audio Header

Shared with Audio Header

Shared with Audio Header

Shared with Audio Header

Shared with Audio Header

Shared with Audio Header

Port

2-channel

4-channel

6-channel

8-channel

Light Blue

Line in

Line in

Line in

Line in

Lime

Line out

Front speaker out

Front speaker out

Front speaker out

Pink

Mic in

Mic in

Mic in

Mic in

Audio header

- - -

Side speaker out

Audio header

-

Rear speaker out

Rear speaker out

Rear speaker out

Audio header

-

-

Center/ Subwoofer

Center/ Subwoofer

IO-Area Connectors

5.4 Audio Connector (IO Area)

The on-board Aud io circuit im plements 7.1+2 Channel High Def inition Audio with UAA (Un iversal Audio

Architecture), featuring five 24-bit stereo DACs and three 20-bit stereo ADCs. The Following Audio

connector is available in IO Area.

Audio Speakers, Line-in and Microphone are available in the stacked audiojack connector

Signal Description Note

FRONT-OUT-L Front Speakers (Speaker Out Left).

FRONT-OUT-R Front Speakers (Speaker Out Right).

REAR-OUT-L

REAR-OUT-R

SIDE-OUT-L Side speakers (Surround Out Left)

SIDE-OUT-R Side speakers (Surround Out Right)

CEN-OUT Center Speaker (Center Out channel).

LFE-OUT Subwoofer Speaker (Low Freq. Effect Out).

MIC1 MIC Input 1

LINE1-IN Line in 1 signals

Rear Speakers (Surround Out Left).

Rear Speakers (Surround Out Right).

Page 35

KTQ77/Flex Users Guide

KTD-N0848-C Page 35

Signal

Description

Pull

U/D

Pull

U/D

- -

PWR

GND

5 9 RI I -

/5K - O DTR

4 8 CTS I -

/5K - O TxD

3 7 RTS O - /5K - I

RxD

2 6 DSR I -

/5K

/5K - I

DCD

1

IO-Area Connectors

5.5 COM1 Connector (IO Area)

Four RS232 serial ports are available on the KTQ77, COM1 is avai lab le in the IO Area while the oth er

COM ports are available on internal pin header connectors.

The typical definition of the signals in the COM ports is as follows:

TxD Transmitted Data, sends data to the communications link. The signal is set to the marking

state (-12V) on hardware reset when the transmitter is empty or when loop mode operation is

initiated.

RxD Received Data, receives data from the communications link.

DTR Data Terminal Ready, indicates to the modem etc. that the on-board UART is ready to

establish a communication link.

DSR Data Set Ready, indicates that the modem etc. is ready to establish a communications link.

RTS Request To Send, indicates to the modem etc. that the on-board UART is ready to exchange

data.

CTS Clear To Send, indicates that the modem or data set is ready to exchange data.

DCD Data Carrier Detect, indicates that the modem or data set has detected the data carrier.

RI Ring Indicator, indicates that the modem has received a ringing signal from the telephone line.

The pinout of Serial ports COM1 is as follows:

Note

Ioh/Iol Type Signal PIN Signal Type Ioh/Iol

Note

Page 36

KTQ77/Flex Users Guide

KTD-N0848-C Page 36

Note

Type

Signal

PIN

Signal

Type

Note

PWR

3V3

12

24 GND

PWR

PWR

+12V

11

23 5V

PWR

PWR

+12V

10

22 5V

PWR

PWR

SB5V

9

21 5V

PWR I P_OK

8

20 -5V

PWR 1

PWR

GND

7

19 GND

PWR

PWR

5V

6

18 GND

PWR

PWR

GND

5

17 GND

PWR

PWR

5V

4

16 PSON#

OC

PWR

GND

3

15 GND

PWR

PWR

3V3

2

14 -12V

PWR

PWR

3V3

1

13 3V3

PWR

Note

Type

Signal

PIN

Signal

Type

Note

PWR

GND

2 4

+12V

PWR 1

PWR

GND

1 3

+12V

PWR

1