Memory Module Specifi cations

KVR1333D3LS4R9S/4GI

4GB 1Rx4 512M x 72-Bit PC3-10600

CL9 Registered w/Parity 240-Pin DIMM

DESCRIPTION

This document describes ValueRAM's 512M x 72-bit (4GB)

DDR3L-1333 CL9 SDRAM (Synchronous DRAM), low voltage,

®

compatibility tested, registered w/parity, 1Rx4 ECC

Intel

memory module, based on eighteen 512M x 4-bit DDR3L-1333

FBGA components. The SPD is programmed to JEDEC standard latency DDR3-1333 timing of 9-9-9 at 1.5V. This 240-pin

DIMM uses gold contact fingers. The electrical and mechanical

specifications are as follows:

FEATURES

• JEDEC standard 1.35V (1.28V ~ 1.45V) and 1.5V (1.425V ~

1.575V) Power Supply

• VDDQ = 1.35V (1.28V ~ 1.45V) and 1.5V (1.425V ~ 1.575V)

• 667MHz fCK for 1333Mb/sec/pin

• 8 independent internal bank

• Programmable CAS Latency: 9, 8, 7, 6

• Programmable Additive Latency: 0, CL - 2, or CL - 1 clock

SPECIFICATIONS

CL(IDD) 9 cycles

Row Cycle Time (tRCmin) 49.5ns (min.)

Refresh to Active/Refresh 160ns (min.)

Command Time (tRFCmin)

Row Active Time (tRASmin) 36ns (min.)

Power (Operating) (1.35V) = TBD*

(1.50V) = TBD*

UL Rating 94 V - 0

Operating Temperature 0o C to 85o C

Storage Temperature -55o C to +100o C

*Power will vary depending on the SDRAM and

Register/PLL used.

• Programmable CAS Write Latency(CWL) = 7 (DDR3-1333)

• 8-bit pre-fetch

• Burst Length: 8 (Interleave without any limit, sequential with

starting address “000” only), 4 with tCCD = 4 which does not

allow seamless read or write [either on the fly using A12 or

MRS]

• Bi-directional Differential Data Strobe

• Internal(self) calibration : Internal self calibration through ZQ

pin (RZQ : 240 ohm ± 1%)

• On Die Termination using ODT pin

• On-DIMM thermal sensor (Grade B)

• Average Refresh Period 7.8us at lower than TCASE 85°C,

3.9us at 85°C < TCASE

< 95°C

• Asynchronous Reset

• PCB : Height 1.180” (30.00mm), double sided component

Continued >>

Document No. VALUERAM1027-001.A00 10/31/11 Page 1

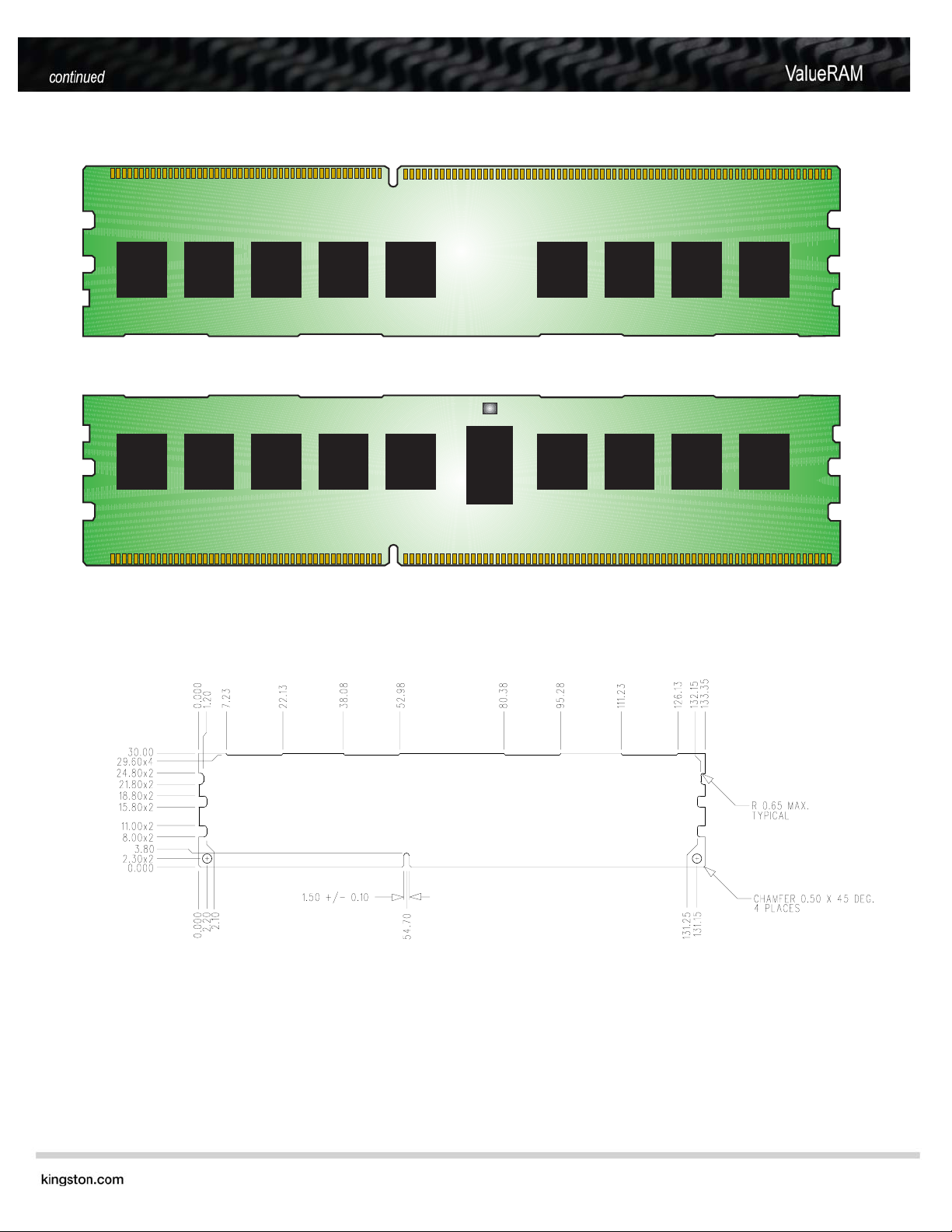

MODULE DIMENSIONS:

(units = millimeters)

Document No. VALUERAM1027-001.A00 Page 2

Loading...

Loading...