KGS HyperLynx User Manual

HyperLynx 入门指南

HK +852-26371886 SZ 755-88859921 www.kgs.com.hk SH 21-51087906 BJ 10-51665105

HyperLynx 入门指南

目录

使用叠层编辑器进行阻抗计算

使用 LineSim 进行布线前仿真

LineSim 串扰分析

BoardSim 的交互式仿真

BoardSim 端接向导

BoardSim 串扰分析

BoardSim 板级分析

BoardSim 差分和 GHz 仿真

直观的 IBIS 编辑器

建立一个 Databook 模型

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 2 页 共 71 页

HyperLynx 入门指南

使用叠层编辑器进行阻抗计算

在 BoardSim 和 LineSim 中均包括一个功能强大的叠层编辑器,使用它可以

很简单地对您的 PCB 进行叠层设计和修改,以及对每个信号层进行特性阻抗的

计算,以便您对信号反射和信号完整性的控制。

特性阻抗

传输线和负载阻抗的匹配,以及选择合适的端接器件的值对信号完整性是很

重要的。BoardSim 和 LineSim 的叠层编辑器正是对其控制的开始。

首先请记住特性阻抗 Z0 的计算等式:

Z0 = √(L/C)

增大电容可以通过一下方式:

加宽走线

减小信号层和参考层的距离

增加介电常数

这样就使等式的分母变大,也就降低的特性阻抗 Z0。当然,减小电容就使

Z0 增大。

而反射系数的计算等式如下:

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 3 页 共 71 页

HyperLynx 入门指南

Refl. % = (ZL - Z0) / (ZL + Z0)

当我们进行 PCB 设计时,对那些驱动端上升或下降时间小于等于 5ns 的单

端信号线必须进行端接。这个功能能够帮助我们选择合适的端接值,以便我们知

道这个端接值 ZL(例如:终端端接),以便我们可以控制信号反射和信号完整性,

或者为了达到理想的目标特性阻抗值,调整优化我们的叠层结构。

建立一个新的 LineSim 原理图

点击工具条上的图标“New LineSim Schematic” ,便可以建立一个

新的 LineSim 原理图,或者通过菜单选择 File -> New LineSim File…。

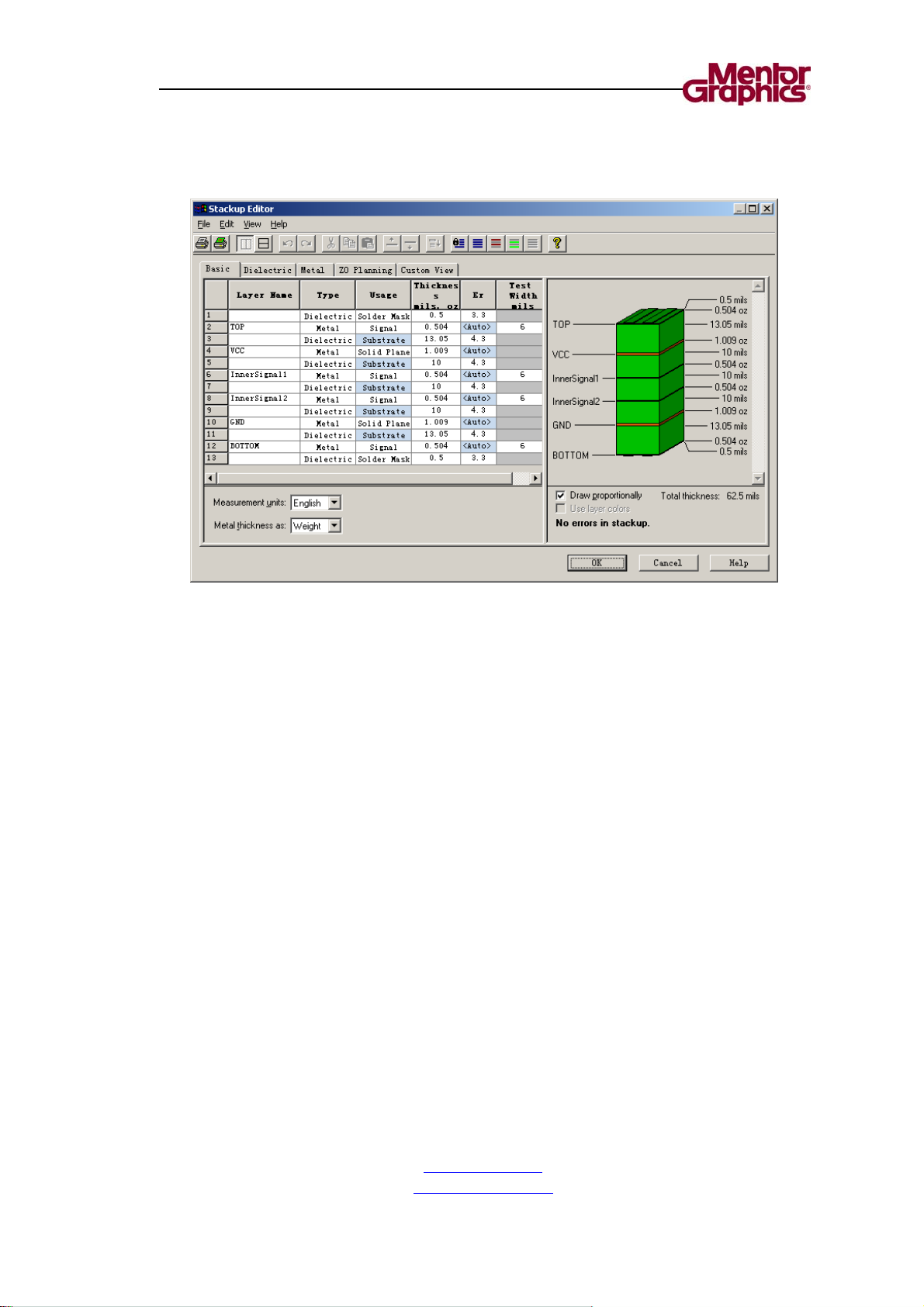

选择工具条上绿色的叠层图标“Edit PCB Stackup”

,或者通过菜单

的 Edit -> Stackup…选项,您将看到一个 6 层板的叠层结构图以及各层和

介质层的参数。

双击您需要编辑的项目表格,例如介质层厚度、线宽等等,根据需要编

辑顶层、底层和各个走线层、参考层以及介质层的参数,您可以分别选

择 Basic、Dielectric、Metal、Z0 Planning、Custom V iew 进行各个项目的

编辑。

另外,您可以在左边的叠层参数窗口中通过鼠标拖动的方式对叠层的结

构进行调整,也可以在右边的叠层示意图中进行鼠标拖动的操作。编辑

各项参数,直到得到您需要的特性阻抗值。

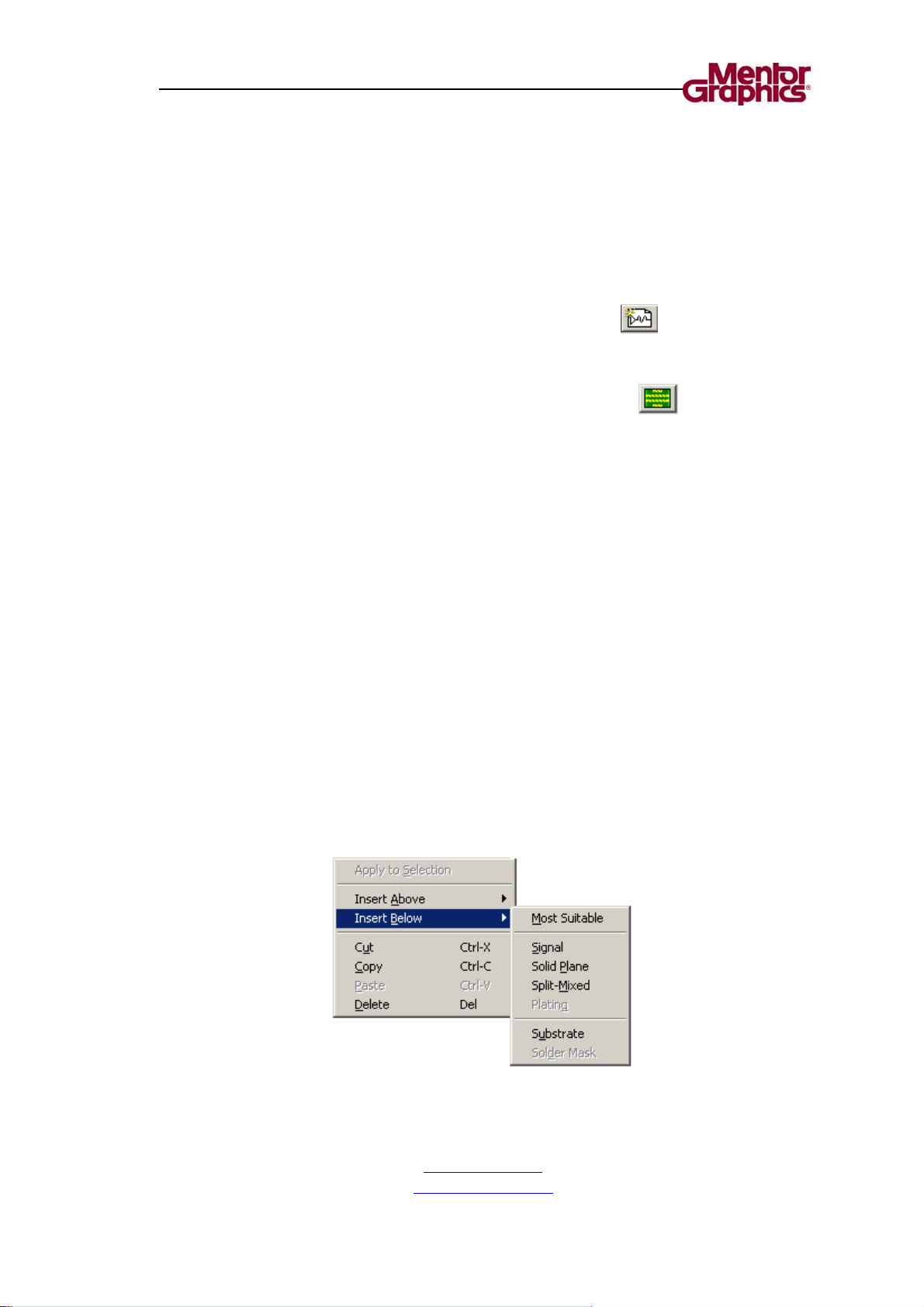

增加新的层

在叠层编辑器“Stackup Editor”的左边叠层参数编辑窗口中单击您需要

增加层的位置,单击右键弹出菜单,选择在当前位置的上面或者下面增

加层,如下图所示:

例如,现在要将目前的 6 层板改为 8 层板,这样我们可以在第三层位置

单击,然后点击鼠标右键选择 Insert Below 选项中的 Solid Plane 选项,

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 4 页 共 71 页

HyperLynx 入门指南

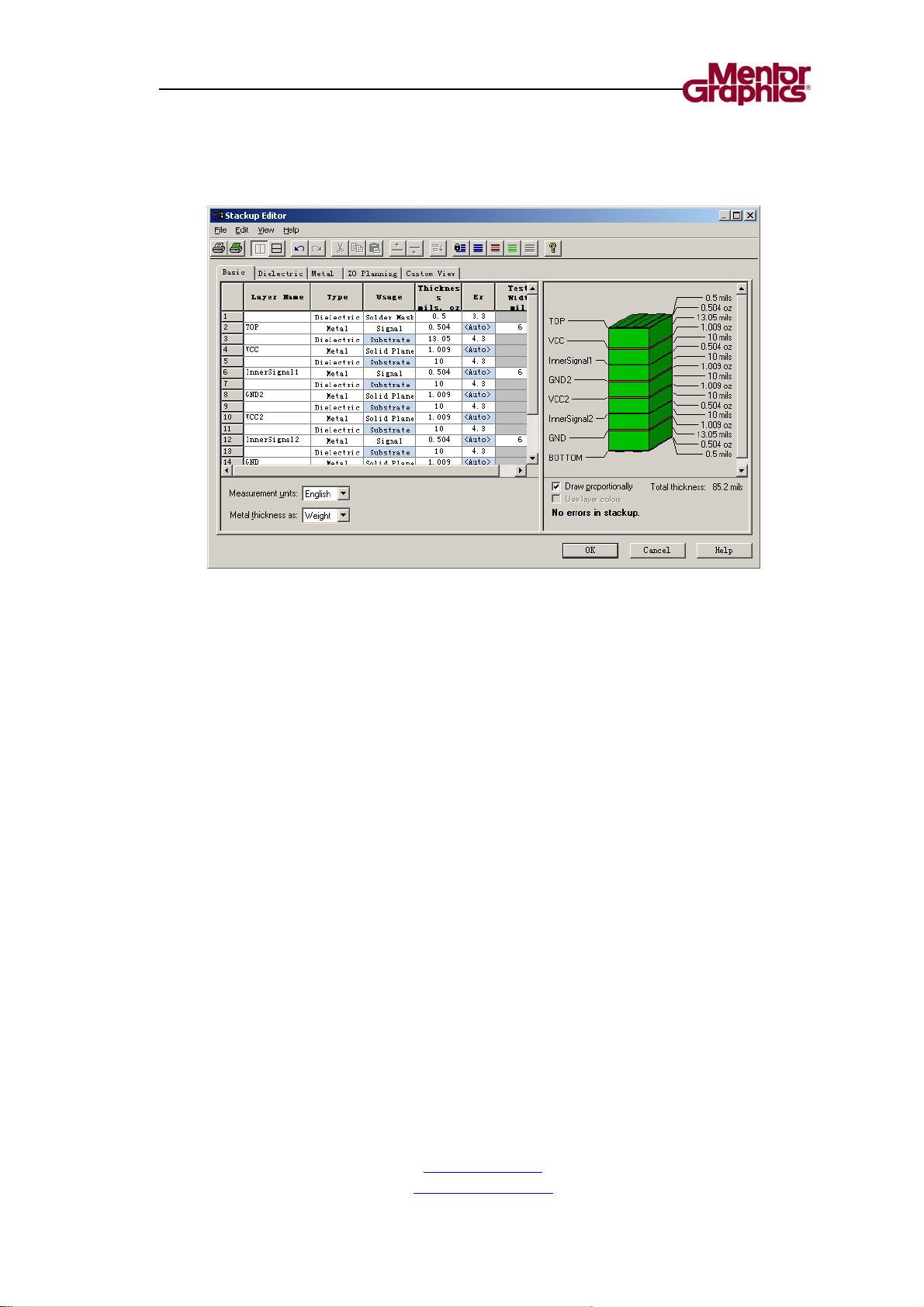

增加一个 GND2 的参考层(层的名称可以增加层后,在 Layer Name 的

栏目位置进行修改),用同样的方法,增加一个 VCC2 的参考层。增加层

后如下图:

增加层后再根据您的需要对各层的参数进行设定,以满足您的特性阻抗

需要。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 5 页 共 71 页

HyperLynx 入门指南

使用 LineSim 进行布线前仿真

在 PCB板上的所有信号中,时钟网络不管对信号完整性还是 EMC辐射问题,

始终都是最应该被关注的。让我们来看看 LineSim 是如何帮助您对时钟网络进行

仿真的,以及在您设计原理图时和设计 PCB 之前制定物理上的布线约束条件。

LineSim 可以帮助您在设计的任何阶段快速地进入和解决“what-if”的信号

完整性和 EMC 问题。它的分析是基于 LineSim 的独特方便的点击式的传输线建

立方式。以下介绍均已 HyperL ynx V7.0 为例。

LineSim 的特点:

•

在 PCB 设计之前制定高速网络的布线约束规则。

• 这种方式是查找和解决设计过程中可能出现的问题最为省钱的方式。

建立原理图之前

点击工具条上的图标按钮 ,编辑 PCB 叠层的图标,检查一下叠层结

构是否是您目前设计所要的(默认是 6 层板)。您可以根据您的需要增加、

删除或者编辑各层。

点击 OK 按钮。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 6 页 共 71 页

HyperLynx 入门指南

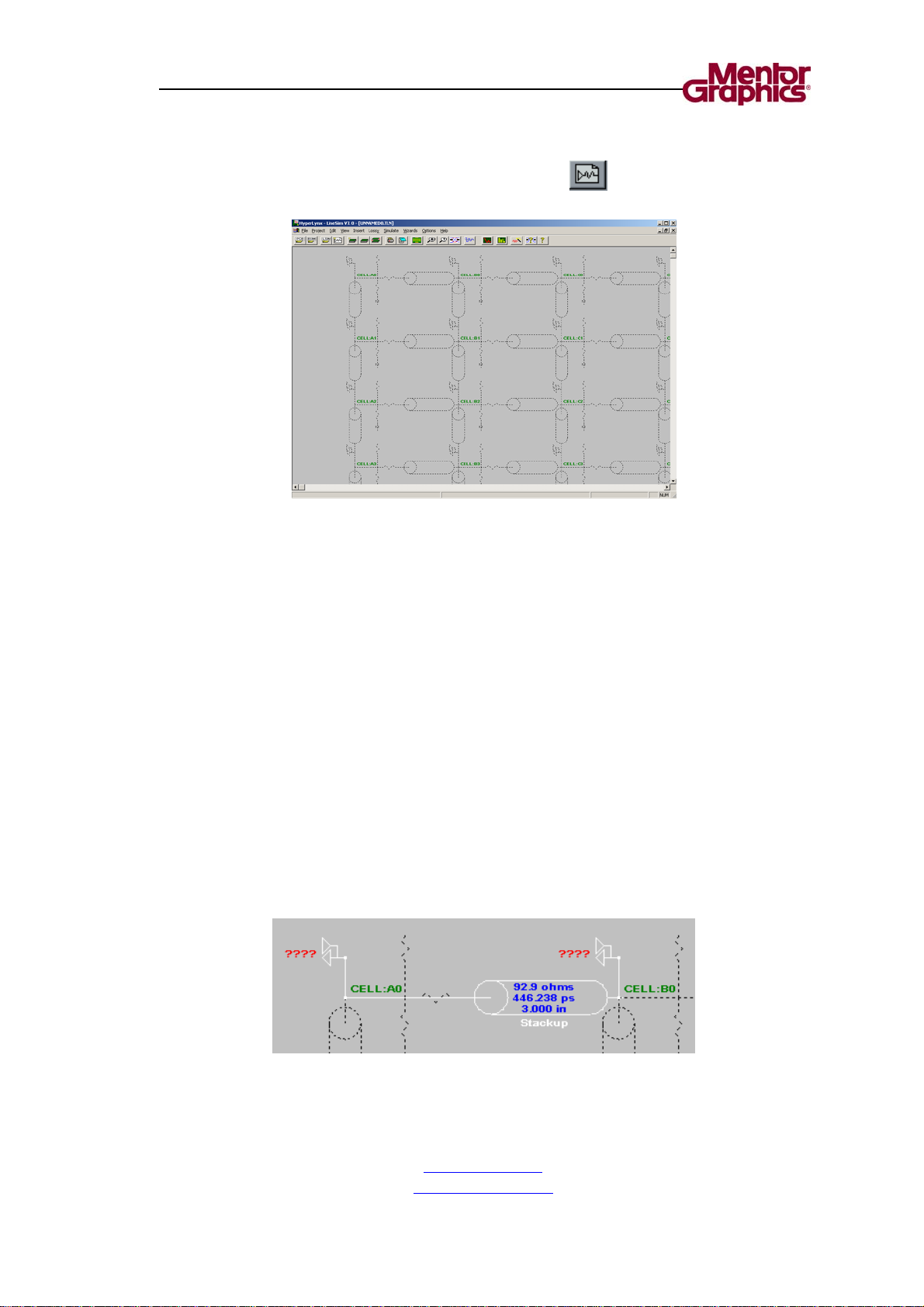

建立一个原理图

单击工具条上的新建 LineSim 原理图图标按钮 ,建立新的 LineSim 原理

图。如下图。

一根传输线包括传输线(互连)、IC 和无源器件。

• 在 LineSim 中,您可以左键点击灰色的各元素(传输线、IC 或者无源器

件)便可以激活它们,这样就可以把它们加入到原理图中。

• 点击各个元素就可以进入它们的物理特性模型(选择一个 IC 模型、指定

特性阻抗、改变元件值等等)

您可以感觉到这种方式比设计传统的原理图更快更简单,它不需要选择器件

符号和连线等操作过程。

激活单元

点击第一排的两个IC符号以便激活 LineSim原理图中的驱动器和接收器

IC(CELL A0 和 B0)

点击连接两个 IC 之间的标准的传输线符号,就可以激活此传输线。如下

图。

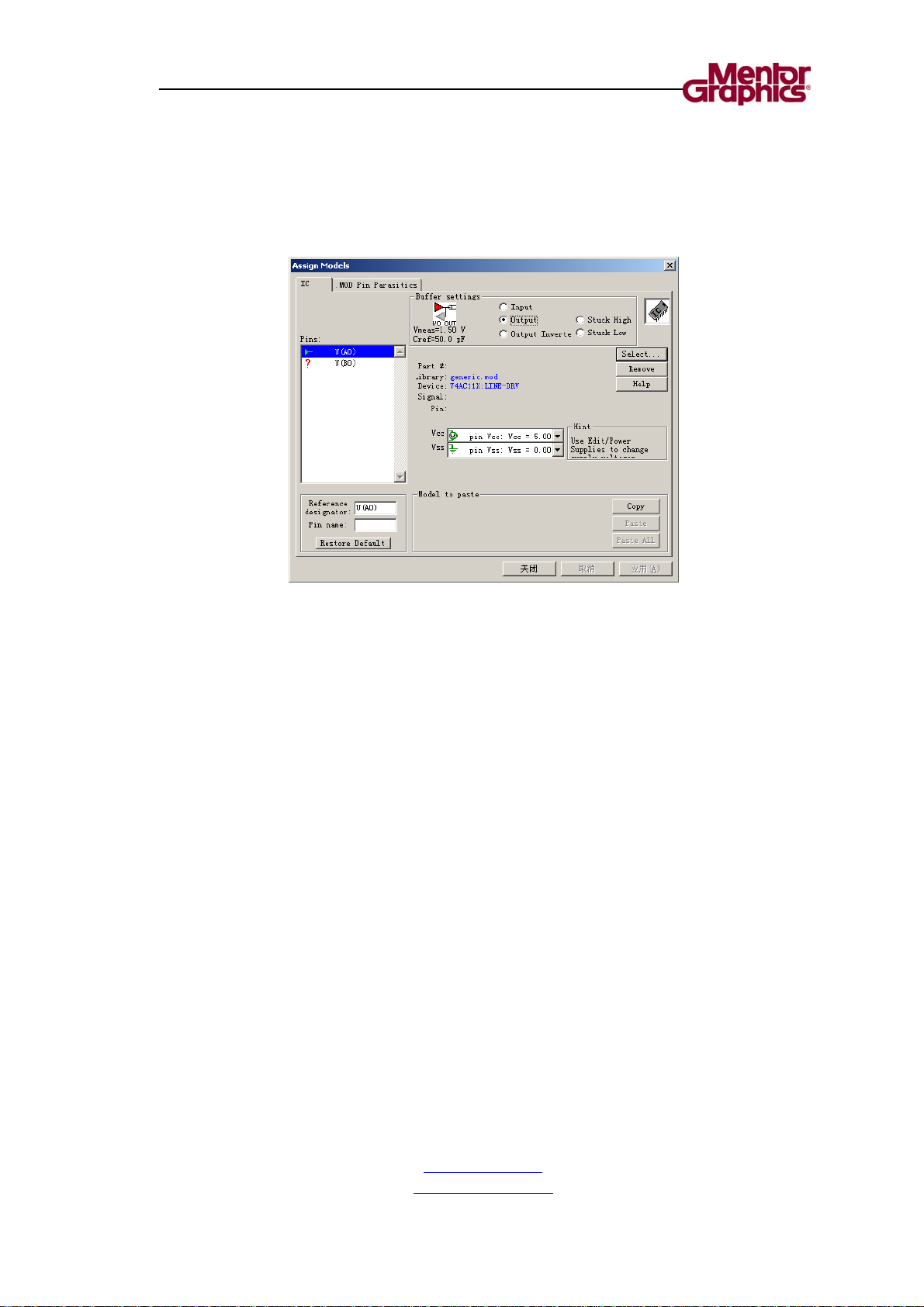

指派一个驱动器

右键点击单元 CELL A0 的 IC 图标(我们将设定它为驱动端)。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 7 页 共 71 页

HyperLynx 入门指南

点击指派模型(Assign Models)窗口右边的“Select…”按钮。

选择 Generic.mod 库按钮。

在 Devices 列表中,选择 74AC11X:LINE-DRV (清单列表中第一个 74AC

系列器件),再点击 OK 按钮。

在 Buffer Setting 对话框中点击单选按钮“Output”,使其设置为驱动端。

如下图。

指派一个接收器

在窗口左边的 Pins 列表中选择 U(B0);点击右边的“Select…”按钮。

选择 Generic.mod 库按钮。

选择 74HCXX:GATE-2,点击 OK 按钮。

确认单选按钮“Input”被选中,将其设置为接收端。

点击“关闭”按钮。

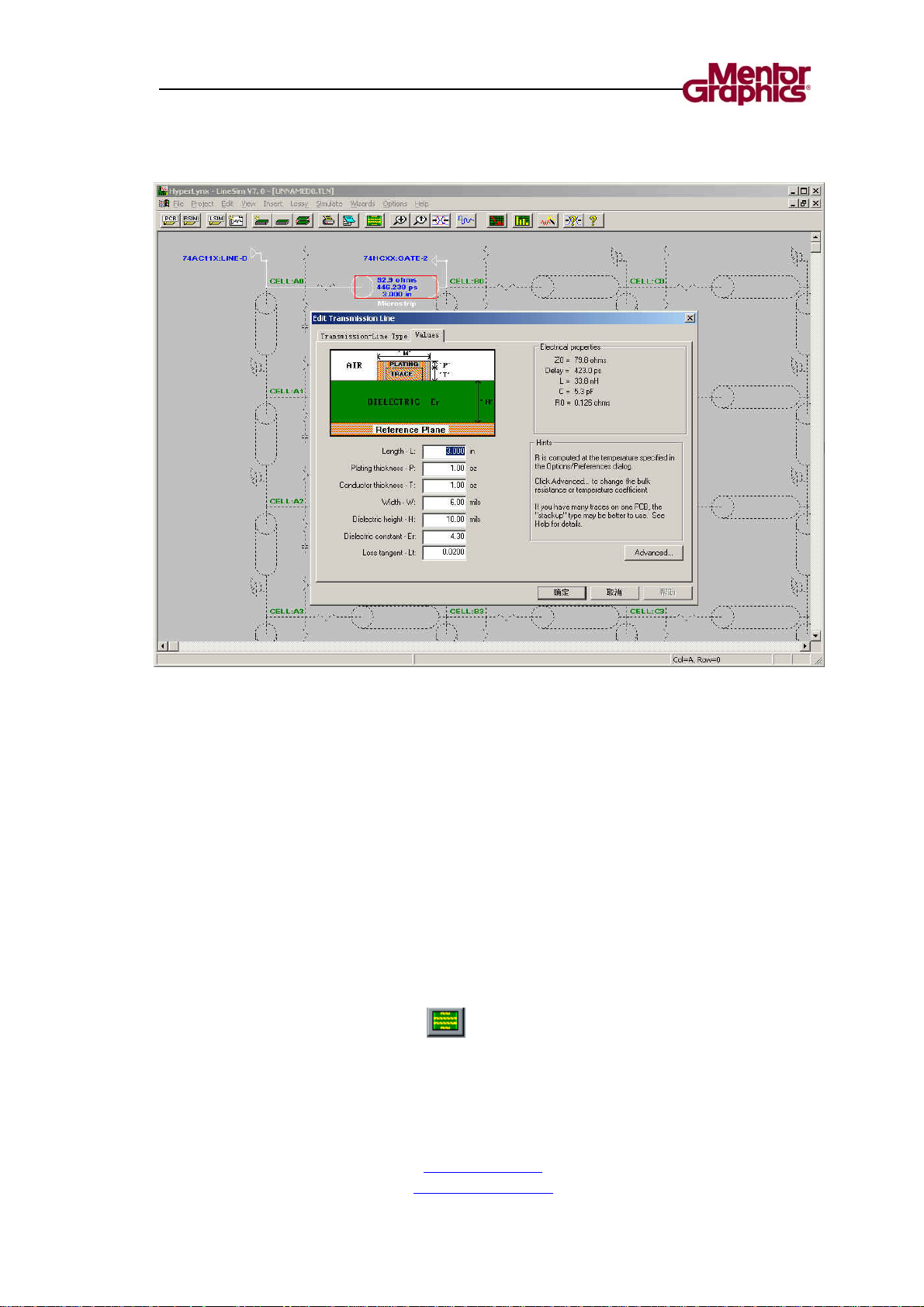

选择一个传输线模型

右键点击传输线符号,发一些时间分别点击传输线类型页中的各种传输

线类型单选按钮,可以通过 Values 页面对各种传输线模型进行参数和模

型的了解。

提示:可以通过点击编辑传输线对话框中上部的传输线类型

(Transmission-Line Type)页和值(Values)页对所选的传输线参数进行设置,

如下图。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 8 页 共 71 页

HyperLynx 入门指南

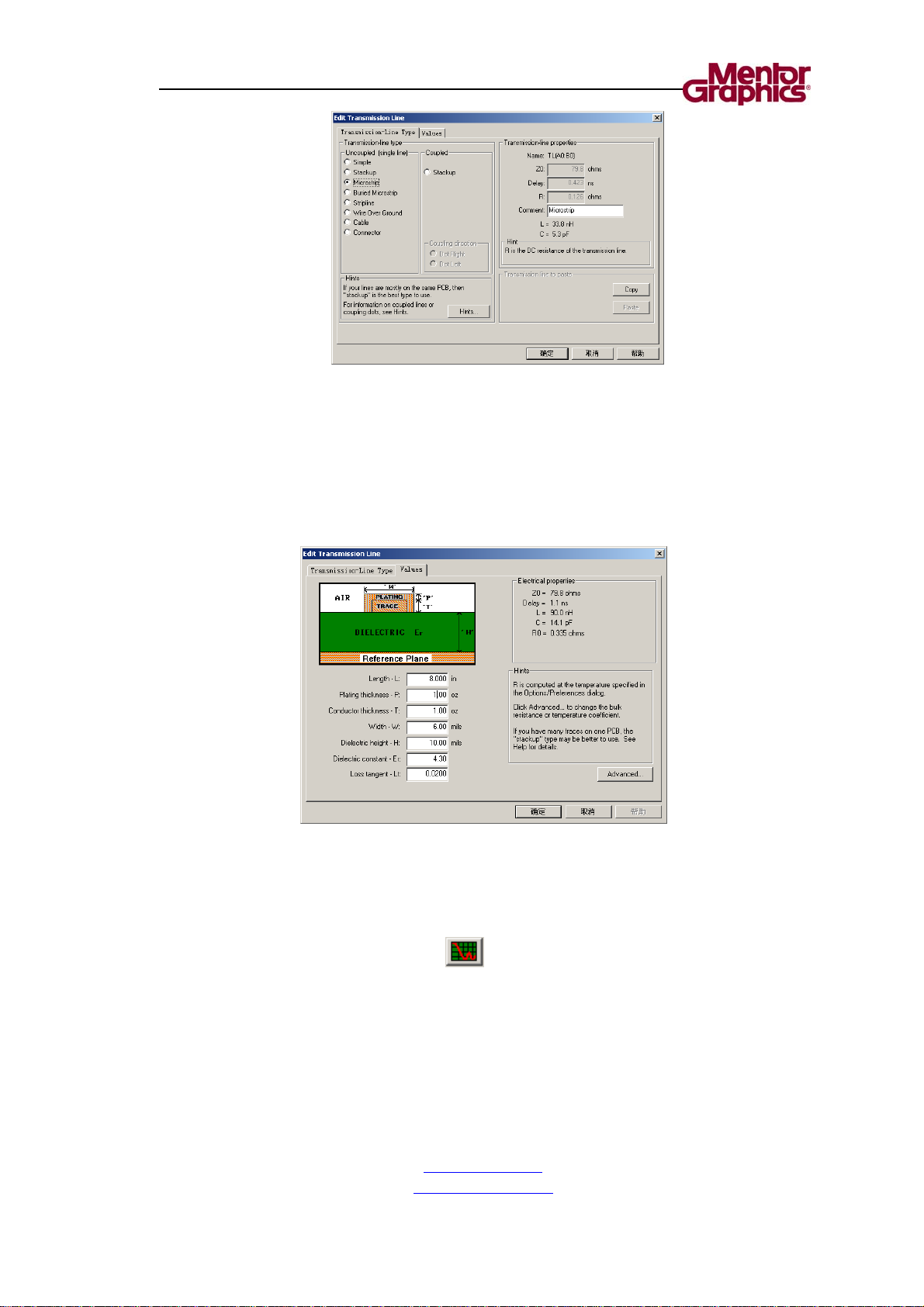

“What-if”分析

选择微带线 Microstrip 单选按钮。

设置线长为 8 Inches(当然,您可以根据您的需要进行长度设置,我们这

里只是为了进行“what-if”分析。如下图。

选择确定,关闭对话框。

对时钟线进行仿真

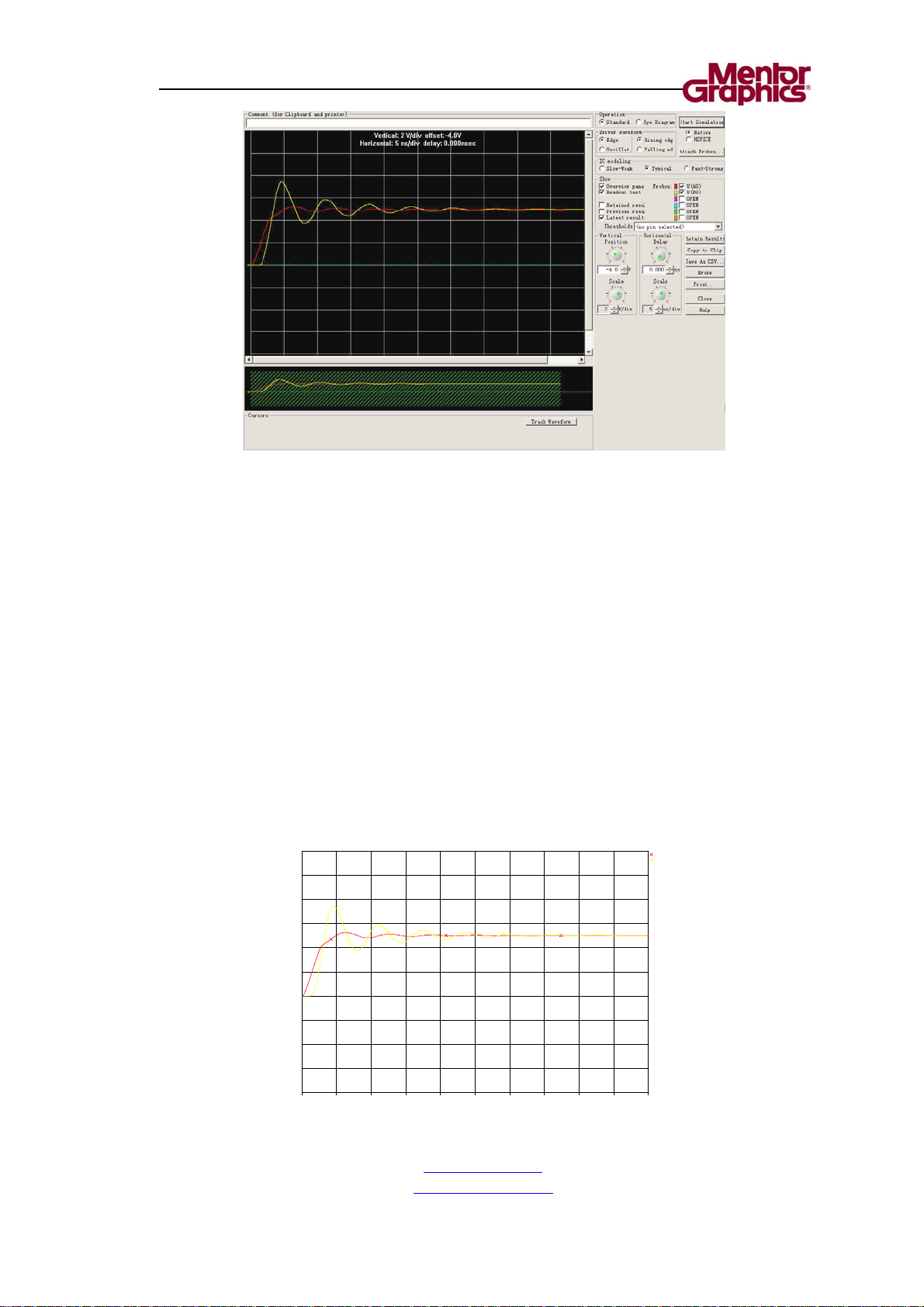

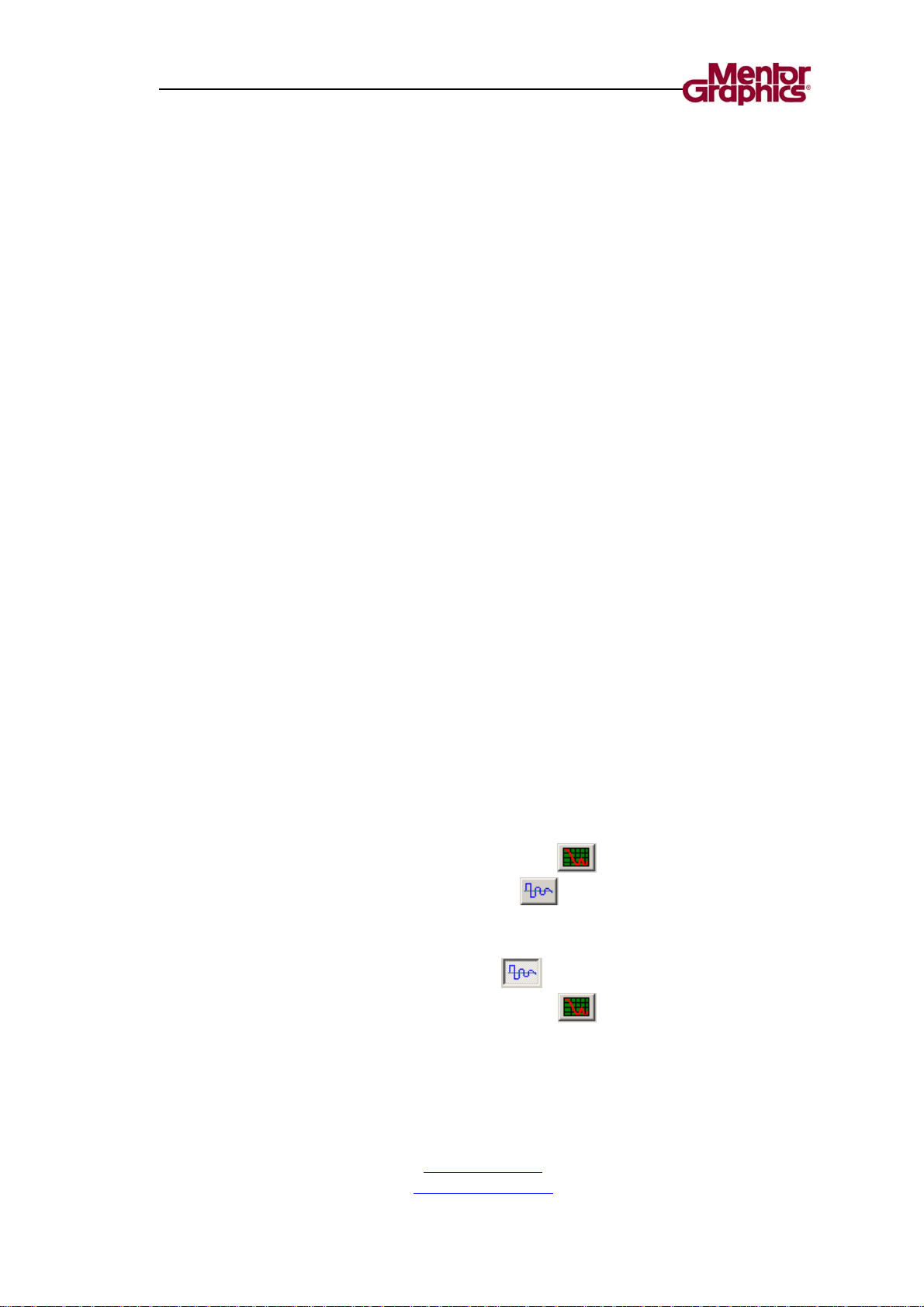

点击工具条上的示波器图标 (Open oscilloscope/Simulator )。

点击右上的“Start Simulation”按钮开始仿真(探头将被自动指派)。

仿真状态对话框被打开并开始仿真。 如下图所示。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 9 页 共 71 页

HyperLynx 入门指南

(示波器探头的通道颜色也同样地被显示于原理图中,每一个被测点各有一

种探头一样颜色的箭头。您可以拖拉示波器的窗口以便查看原理图中各探头的测

试位置和颜色。)

注意观察示波器中接收端的电压波形(黄色的示波器探头)有很大的过冲和

下冲-这样,在接收端 IC 每个周期将会收到一个非常陡的沿的时钟信号(如果

您设计中有这样的时钟网络,您的设计将会失败),这也是在高频设计中考虑得

比较多的因素;而且这样的波形将会引起很强的电磁辐射。

选择示波器窗口中的“Copy to Clip”按钮,将波形拷贝到剪贴板中。

选择开始菜单中“开始” -> “程序” -> “附件” -> “写字板” (或

者使用 Microsoft Office Word 等编辑工具)

使用快捷键 Ctrl-v 将波形粘贴到写字板中。 如下图。

12.000

10.000

8.000

6.000

4.000

Vo l t age -V-

2.000

0.000

-2.000

-4.000

-6.000

-8.000

0.000 5.000 10.000 15.000 20.000 25.000 30.000 35.000 40.000 45.000 50.000

Show Latest W aveform = YES, S how P revious Waveform = YES

OSCILLOSCOPE

Design file: UNNAM E D0. TLN Designer: XCM

BoardSim/Li neS im, HyperLy nx

Time (ns)

Date: Wednes day Mar. 24, 2004 Time: 17:04: 30

Probe 1:U(A0)

Probe 2:U(B0)

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 10 页 共 71 页

HyperLynx 入门指南

这是一个很方便的文档-不管对您的设计组还是管理者-您所做的文档可

能会起到指导设计进程时间表的作用。

显然,我们不能设计这样拓扑的一根走线(例如 8 Inches)。但是为什么会

出现这样的信号问题呢?

答案是驱动端的“沿速率”或者开关速度与走线长度的比。

基本上有三种办法可以解决这个问题,请参考以下的“3T”。

1. Technology

(工艺)

-减慢驱动 IC 的开关速度(很困难,这将影响您的

时序)。

2. Topology

3. Termination

(拓扑)

(端接)

-减小布线的长度到临界范围内或更短。

-使用无源器件匹配走线末端的特性阻抗到 Z0。

Technology

(工业)

-让我们假设我们的时序裕量要求与 CMOS 驱动端的一

致(下降沿 1.9ns)。

Topology

(拓扑)

-需要遵循的一个规则是走线长度延迟不超过驱动端开关

速率的 1/6,让我们看看这个网络上的工作情况。使用 FR-4 板材,信号延迟是

5.8 in/ns(大约 6 in/ns)。

让我们看看我们的驱动沿速率以便决定走线的线长。

关闭示波器窗口。

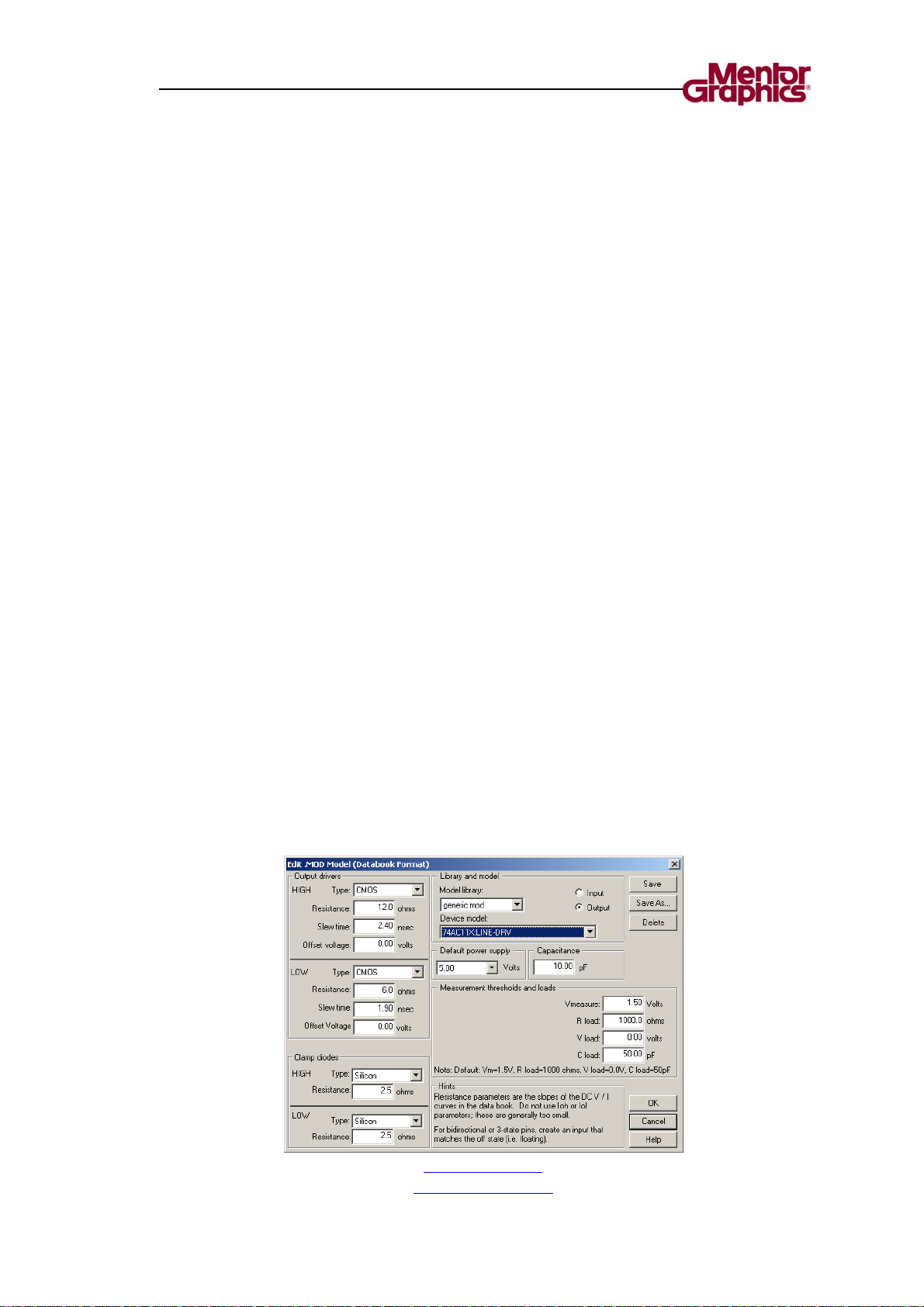

选择菜单 Edit -> Databook IC Models(.MOD)。

在 Library and Model 下的 Model Library 下拉框中选择 generic.mod,

以及在 Device Model 下拉框中选择 74AC11X:Line-Drv ,请注意对话框

左边 Output Drivers 中 Slew Time 的高/低电平值。如下图:

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 11 页 共 71 页

HyperLynx 入门指南

选择最坏的情况的 Slew Time(这个例子中的低电平情况),然后乘以 6

Inches(信号传输速率)。

第一个进入的波形信号传输延迟:

转换为电气长度

= Slew Rate (ns)×6 (in/ns)

= 1.9 (ns) ×6 (in/ns) = 11.4 in

再将此值乘以 1/6(布线规则),得到使用这个驱动器最大(建议)的布线长

度。

最大的布线长度:1.9 in(未端接的条件下)

注意:如果您使用 FR-4 板材, 就不要通过以上的一堆乘法计算了,您可以

直接利于 Slew Time 的 ns 时间作为最大的走线长度,由于 6 x 1/6 = 1。

现在返回到原理图,右键点传输线符号,点击 Values 的表页,在走线长

度(Length)栏输入 1.9 Inches。

点击确定,使用示波器功能重新仿真一次波形。

您应该能看到一些难看的振铃信号,每一种规则都是您设计的指导。这就是

为什么要先做仿真,而不是盲目地进行设计,它们在某些特定情况下可能正常工

作,也可能不能正常工作。

再继续减小布线的长度,直到振铃停止,您就可以建立一个布线约束了

-这就是这个网络最大的布线长度值(除非被正确端接)。

重要提示:

通过不断的试验,您应该可以得到振铃较小时最大的未端接布线长度为大约

0.5 inches。很明显,这种类型的约束如果太经常使用,对于 PCB 设计工程师或

者布线器,会是一件很可怕的事。现在,让我们来看看解决同一问题的另一种方

法-端接(第三个 T)。

时钟线上的串连端接

让我们再来回顾一下这根 8-inch 走线的情况(这里要强调的是增加一个好的

串行端接的效果)。

右键点击传输线符号。

点击 Values 的表页,在走线长度(Length)栏改回 8 Inches。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 12 页 共 71 页

HyperLynx 入门指南

点击工具条上的示波器图标 。

点击右上的“Start Simulation”按钮开始仿真。

您将看到有大量过冲和振铃的一个信号波形。

现在我们再对这根传输线进行分析,这次我们使用一个串行端接。

对于串连端接,串行电阻的最优值计算公式如下:

Rt = Z0 - Zd

公式中:

Rt = 串行端接电阻阻值(欧姆)

Z0 = 传输线的特性阻抗值

Zd = 驱动端的输出阻抗

对于这根时钟线的 Z0 在 LineSim 的传输线符号中显示。

增加一个串连端接

左键点击位于驱动 IC 和传输线符号之间的电阻符号,选择插入电阻

(Resistor )。

右键点击电阻符号,输入其阻值 63 欧。如下图。

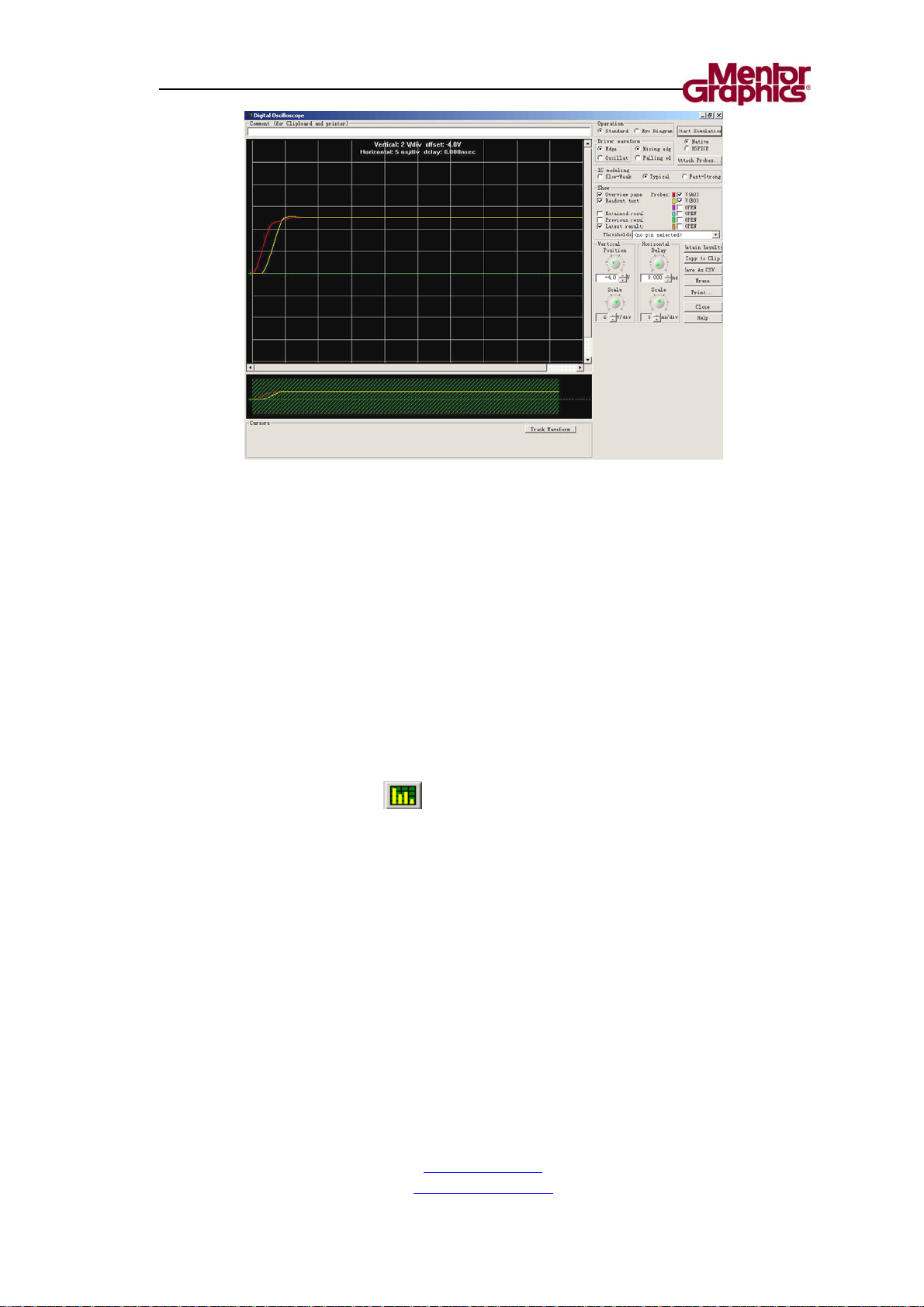

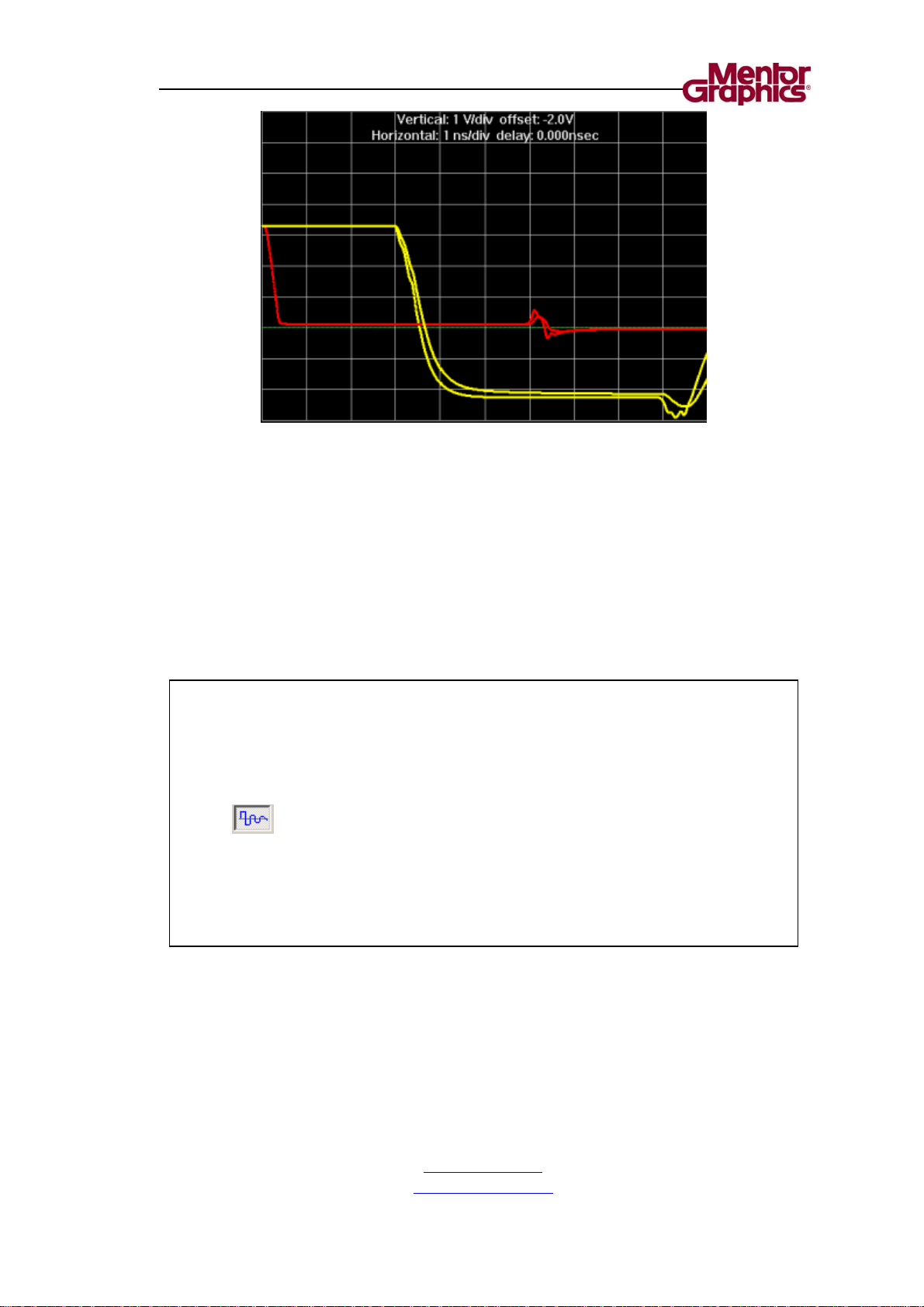

重新仿真

点击工具条上的示波器图标 。

点击 Start Simulation 按钮开始仿真。

请注意这次干净的波形,如下图。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 13 页 共 71 页

HyperLynx 入门指南

通过选择示波器窗口右边“Show”选项下的“Previous result”复选框,

打开刚才前面的波形,对比两次仿真的结果。

看看这是多么的简单!您可以在这里做任何的象这样假设的传输线,串行、

并行、多板等等仿真。

只需花一会儿的时间,让端接、仿真过程完成的如此漂亮!

对于在改善了信号完整性之前的信号 EMI 问题,真的没有必要去测试,如

果您有兴趣,可以做一个对比。现在,信号完整性问题解决了,让我们来看看

EMI 的测试效果。

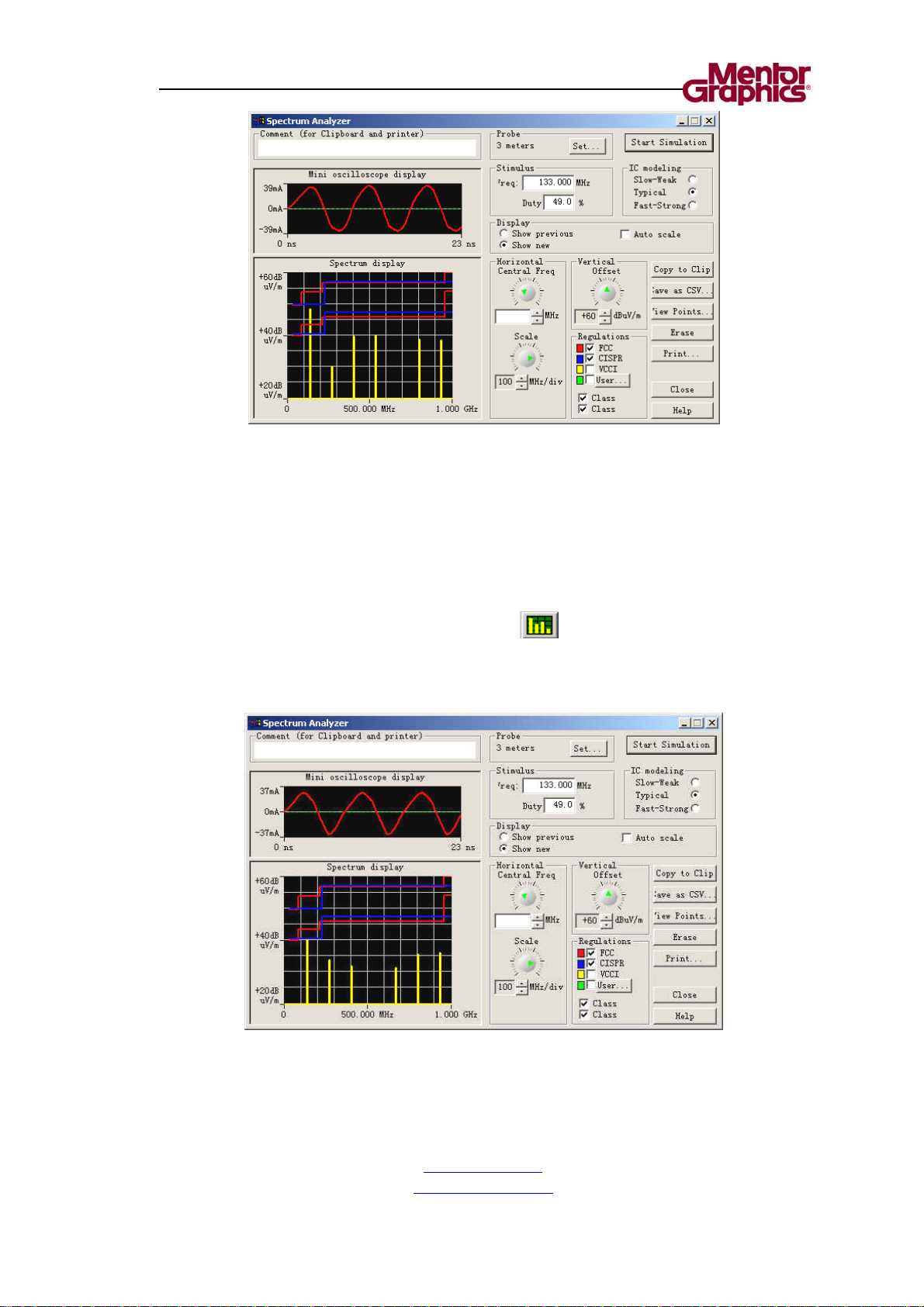

关闭示波器窗口,点击 LineSim 工具条上的频谱分析仪(spectrum

analyzer)图标按钮 。将打开频谱分析窗口。

向上点击垂直偏移(Vertical Offset)设置按钮,将 Class A 和 Class B 的

标准线位于分析窗口中。

点击右上的开始仿真“Start Simulation” 按钮,开始仿真,并得出结果,

如下图。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 14 页 共 71 页

HyperLynx 入门指南

时钟基频的辐射值超过了 FCC 和 CISPR 的 Class B 的标准限制,因此,为

了达到目标,我们可以尝试将线长缩短一些。

点击 Close 按钮,退出频谱分析窗口。

右键点击传输线符号,编辑传输线窗口将跳出。

选择 Values 页表改变传输线的长度为 4 Inches。

关闭编辑传输线对话框。

再次点击频谱分析仪工具条图标按钮 。

点击开始仿真“Start Simulation”按 钮 ,观 察 133MHz 频率处的辐射值,

可以发现现在可以通过 FCC 和 CISPR 的 Class B 标准。如下图。

花了不到 10 分钟的时间就解决了在实验室可能要花大量的时间去重复实验

验证的 EMI 问题。

如果您继续使用这个网络做 What-if 分析,您将发现 4 Inches 的长度是这个

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 15 页 共 71 页

HyperLynx 入门指南

串行端接时钟网络的限制(假定您需要考虑 CISPR EMC 限制);如果您想提供

一些 133MHz 的裕量也许需要更短一些。这样,您就可以得到这些的一些设计的

物理约束参数。

有损传输线模型

由于设计的产品的速度越来越快,以及 IC 产生的时钟沿的速率也越来越快,

分析 PCB 走线和介质材料的损耗变得越来越重要。幸运的是,在 LineSim 和

BoardSim 中的有损模型也是简单到只要点击一个按钮就可以了。马上,我们就

将看到。

注意:损耗通过衰减电压幅值和软化信号边沿引起信号的失真。最终结果经

常是增加了信号延迟。从物理上来说,损耗是由于 PCB 走线和周围的介质材料

的发热而引起的。在高频情况下,损耗将更加严重,所以对于边沿较陡的器件损

耗将更严重。

更改原理图

如果频谱分析仪窗口还开着,请关闭它。

更改驱动端模型为一个开关边沿速率更快的模型:在驱动 IC 符号上点击

右键,点击 Select 按钮,选择 EASY.MOD 库,再选择

“CMOS,3.3V,Ultra-Fast,”,然后点击 OK 按钮,关闭窗口。

移除串行电阻:左键点击串行电阻符号处,选择 None。

延迟传输线:在原理图上右键点击传输线,选择 Values 页表,改变线长

为 20 Inches。

我们改变了这些参数,是因为更快的驱动沿和更长的走线将会引起更多的损

耗。

对有损和无损的仿真对比

点击工具条上的红绿色的示波器图标按钮 。

确认工具条上蓝灰色的有损仿真图标 处于未点击状态。

点击开始仿真“Start Simulation”按钮。

确认示波器窗口中 Show 下的复选框“Previous Results”是被选中的。

现在点击工具条上的有损仿真图标

处于有损仿真状态。

点击红绿色的工具条示波器图标按钮 ,点击开始仿真“Start

Simulation”按钮,重新仿真。

注意观察对有损仿真波形的不同点:例如,黄色的接收端波形增加了额

外的延迟。如下图:

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 16 页 共 71 页

HyperLynx 入门指南

使用更快的驱动端 IC,例如使用 Multi-Gigabit,超高频串行总线(例如 PCI

Express、HyperTransport 等等)。损耗的仿真效果将更加明显。

用 XTK 和其他可信赖的信号完整性工具使用的同样的“W 元素”算法,

LineSim 和 BoardSim 都可以进行损耗仿真。这个算法可以自动地计算象趋肤效

应等一些复杂的问题。

现在您可以看到在 HyperLynx 中进行有损效应的仿真是多么的容易了――

只需要一个按钮就可以完成后续的一系列仿真。

选项:

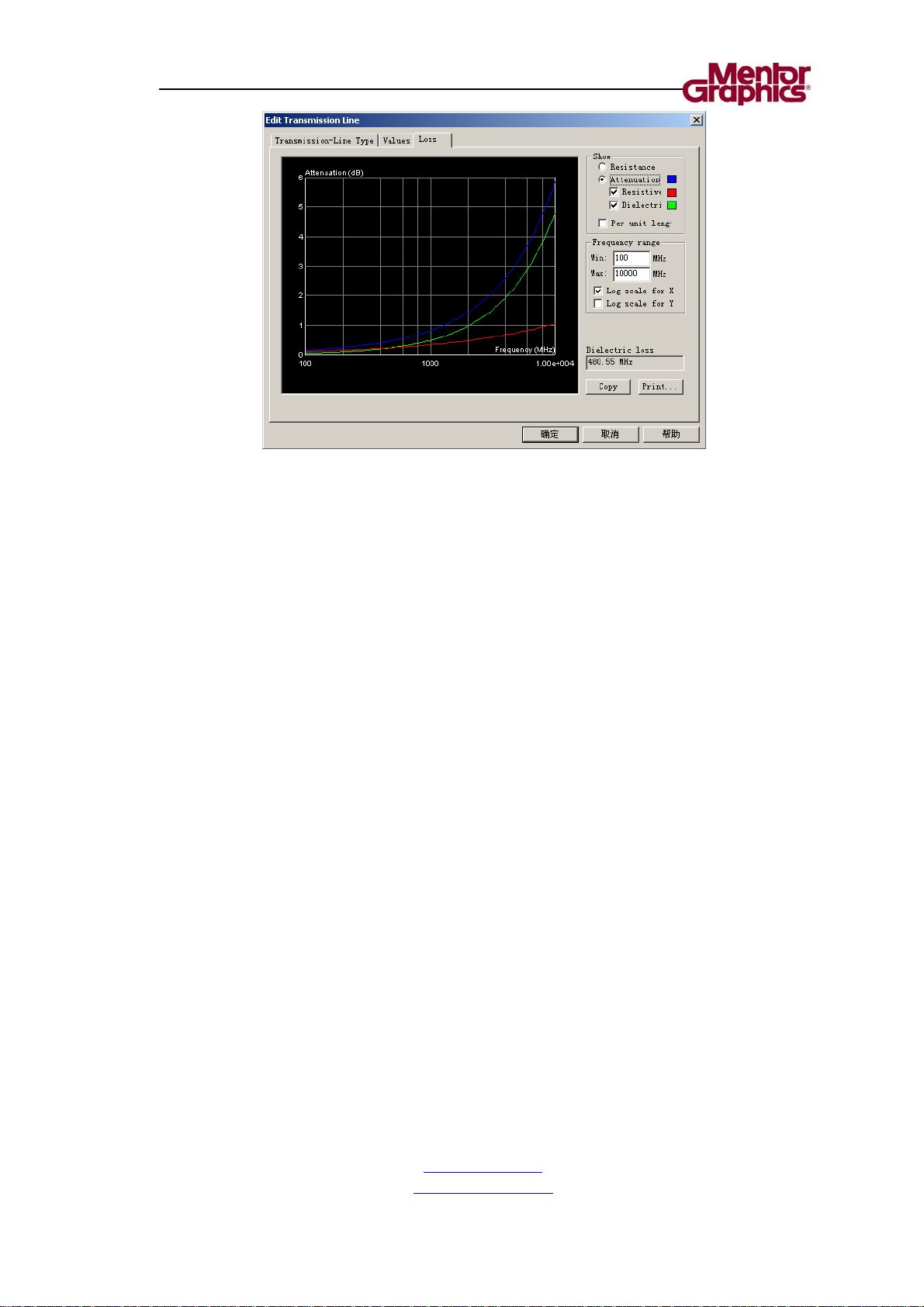

高级的用户可能想测试在频域上的损耗:

在原理图的传输线符号上点击鼠标右键。

点击频域(Frequency Domain)查看表“Loss”,请注意只有在有损仿

真

被使能时才出现此图表。

点击衰减率按钮,确认 Resistive 和 Dielectric 复选框已经被选中。

请注意曲线显示在高频时信号的衰减是如何增加的,对于这根传输线在

480MHz 以后,介质损耗(绿色)占了主导作用,而阻抗的损耗(红色)

作用越来越小。如下图。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 17 页 共 71 页

HyperLynx 入门指南

支持 HSPICE 仿真

IBIS 模型广泛地应用于信号完整性仿真,但是对于超高频的 IC 并不都可用。

例如在 multi-gigabit(或者“3GIO”)串行总线的收发器中。通常,这些 IC 的厂

商都只提供加密的 HSPICE 格式模型。

幸运的是,使用一种叫“SPICELynx”的功能,LineSim 和 BoardSim 都能

够运行 HSPICE 作为一种可选仿真。 这可以让用户使用 HSPICE 模型交互式地

仿真一些网络,提供了同样的友好的工作环境。

注意:在 HyperLynx 中运行 HSPICE 要求用户有 HSPICE 的授权,大部分

的 3GIO 技术均有此授权。

设置 HSPICE 仿真

在 HyperLynx中设置 HSPICE 仿真就像设置一个平常的 IBIS 仿真一样方便。

看一个例子,首先确认一些 HSPICE 模型的可用性。

关闭打开的任何窗口。

选择菜单的 Options / Directories

如果需要,使用编辑按钮增加以下的 IC 模型路径: “<HyperLynx 路径

\Libs\Spice”

注意:如果您还没有 SPICE 例子模型,你必须阅读一些相关的知识。

现在,在原理图中左键点击接收端 IC 符号,移除它。

右键点击驱动端 IC,点击 Select 按钮。

点击 SPICE 单选按钮,只显示 SPICE 文件;如果您的路径设置正确并

有部分模型,您将看到少量的“.inc”文件。如下图:

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 18 页 共 71 页

HyperLynx 入门指南

选择列表中第一个 SPICE 模型并点击 OK 按钮。

注意一个 spreadsheet 电子表格显示 SPICE 模型的“ports”。仿真之前,

每一个 Ports 必须被连接,注意电源 Ports(“VCC”和“ XGND”)可 以

被 LineSim 自动地连接。

连接 SPICE 模型的输入 port 到 LineSim 的数字仿真中:点击 Vin 的电

路连接单元,选择 Stimulus。

连接 SPICE 模型的输出 port 到原理图的 A0 单元:点击 Vout 电路连接

单元,选择 U(A0)。

注意选择这个 HSPICE模型就像选择 IBIS模型,除了它们有一些额外的 Ports

需要被接通。

运行 HSPICE 仿真

现在我们准备运行 HSPICE 仿真,虽然你实际上并不能产生波形和浏览它,

除非您的 PC 上有 HSPICE 的授权。

点击红绿色的工具条示波器图标按钮 。

点击右上角的开始仿真“Start Simulation”按钮开始仿真。

LineSim 将给出一个信息说:发现了一个 HSPICE 模型,因此要从

HyperLynx 的内置仿真器切换到 HSPICE 仿真。

点击 OK;出现一个对话框给出一些 HSPICE 文件的控制和输出显示。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 19 页 共 71 页

HyperLynx 入门指南

点击 OK。如果您有 SPICE,一个窗口打开,显示出 HSPICE 信息和运

行信息;当仿真完成,HSPICE 波形显示在 LineSim 的示波器窗口中。

如果您没有 HSPICE,将出现一个窗口告诉您找不到 HSPICE。

LineSim 已经被设计成仿真 HSPICE 就像感觉在运行 LineSim 仿真。这样可

以帮助用户单独运行 HSPICE 的操作不习惯:通过手工建立网络列表、手工运行

场分析、产生触发文本、打开一个单独的工具去浏览波形等等。

HyperLynx“包含”的 HSPICE 对于布线后的分析特别有用(网络列表几乎

不需要手工建立);进行眼图分析,而在 HSPICE 中进行长的数字触发显得相当

不方便。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 20 页 共 71 页

HyperLynx 入门指南

LineSim 串扰分析

LineSim 的串扰选项帮助您制定布线前的布线约束。

在这个例子中我们将研究不同的方法来控制一般总线上的串扰。

总线设计的间距

假设您正在设计一个总线,想保证在每一根总线上的互相串扰不超过

200mV,让我们来看看 LineSim 的串扰仿真功能如何帮助您达到您的目标,建立

合适的布线约束条件规则。

总线上的串扰仿真

在现在的数字系统的典型总线一般包括许多物理上的并行走线-16、32、64

位,甚至更多的信号线。可是,当您对这样的一组总线进行仿真时,很明显您不

会对所有的信号同时进行仿真(如果包括所有的信号进行仿真将浪费大量的时

间)。相反,您应该利用串扰的特点,对造成串扰的受害网络影响最显著的两个

网络进行仿真分析:受害网络两边距离最近的两个网络。所以,一般来说,您应

该集中尽力来分析仿真这三根网络组。

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 21 页 共 71 页

HyperLynx 入门指南

建立基本的传输线

选项:为了在 Demo 中节省时间,您可以跳过前面的这些步骤,而直接在

您的 HYPFILES 目录中打开“XT Trace Separation.TLN”。

让我们开始通过在原理图中建立一组三个相邻的走线。

点击工具条上的新建 LineSim 原理图图标 ,建立一个新的 LineSim

原理图。

左键点击 CELL:A0 和 B0。

左键点击这两个 IC 符号之间的一段传输线。

在传输线符号上点击右键,打开传输线编辑对话框。

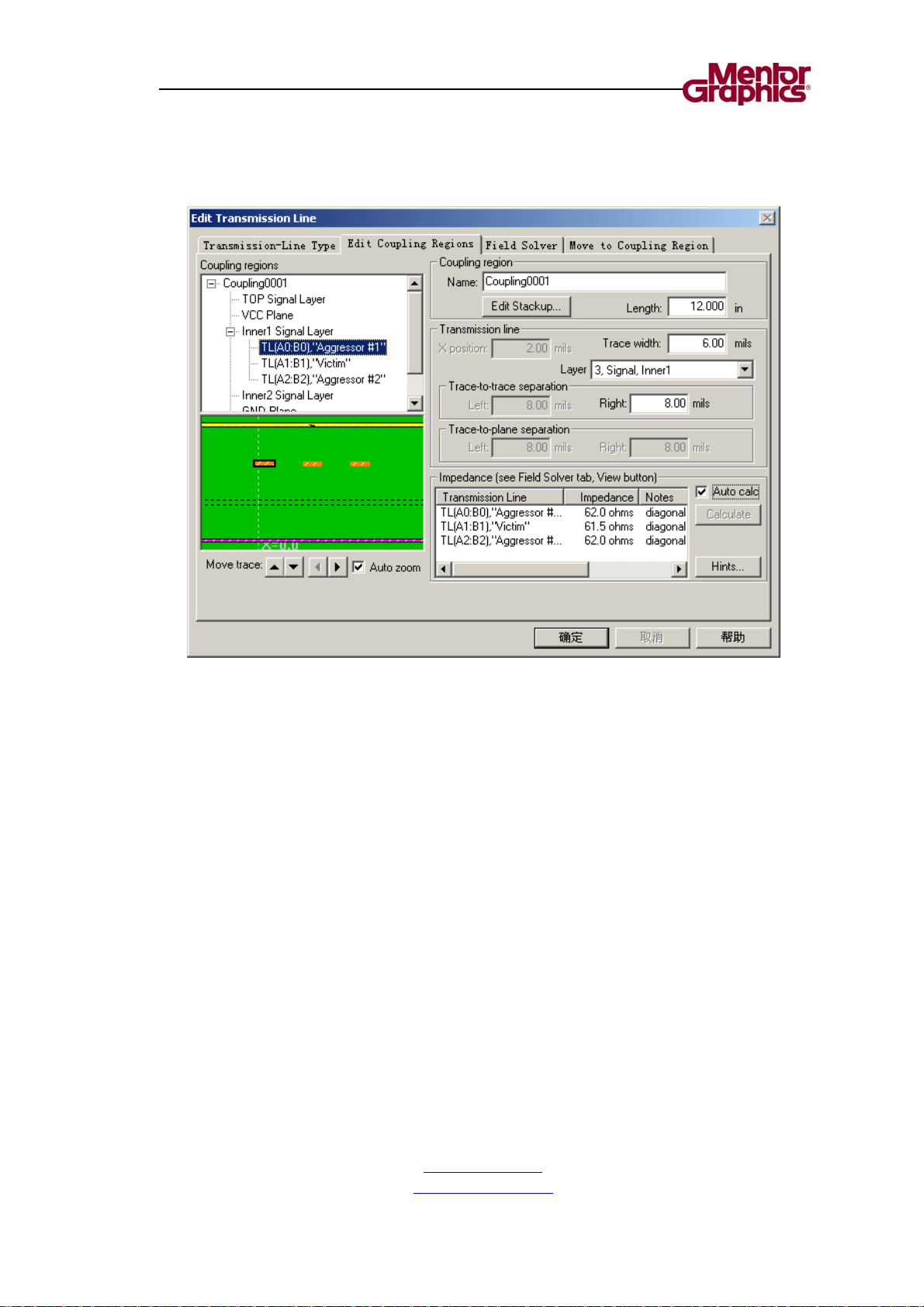

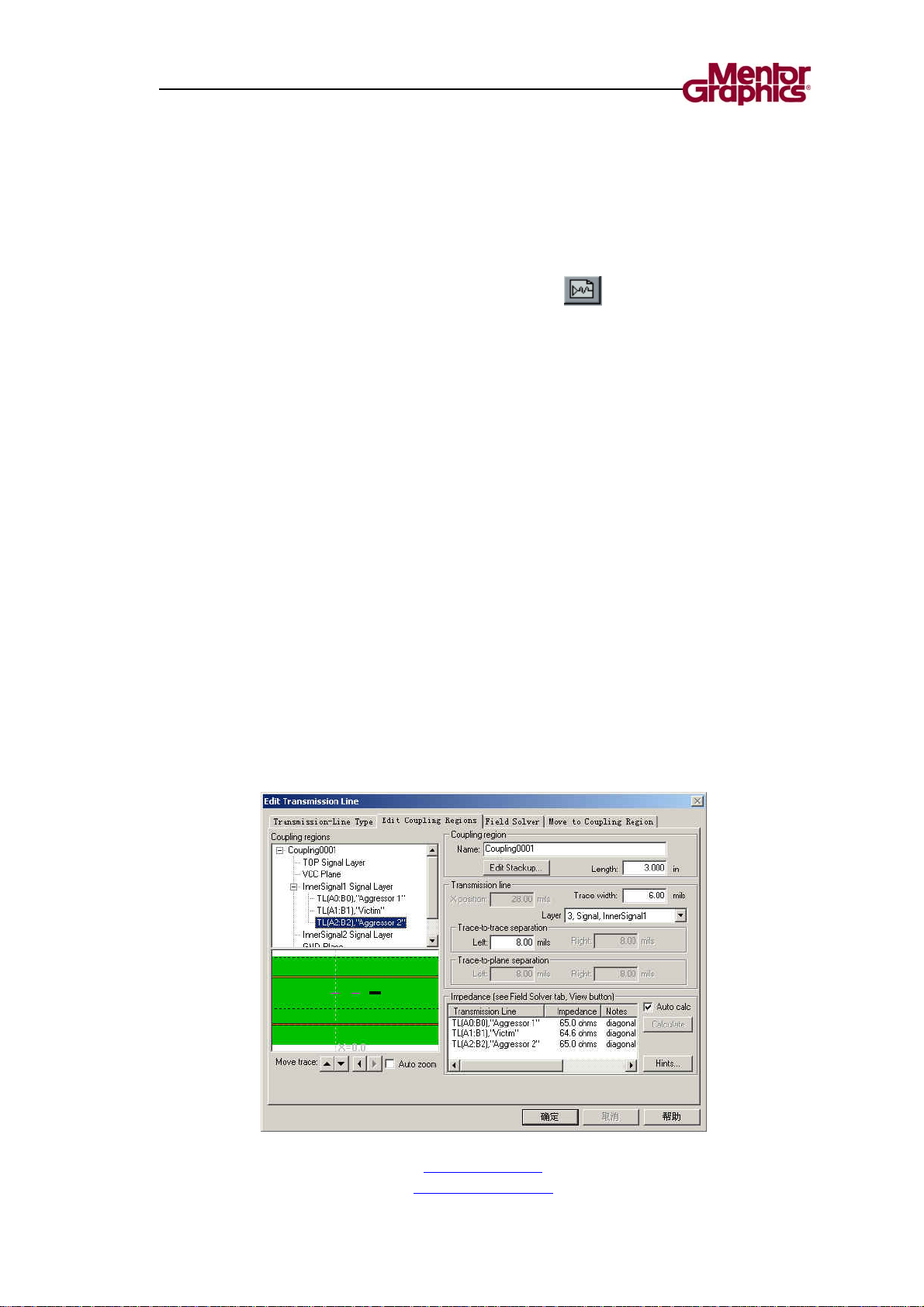

在“Coupled”中选择单选按钮“Stackup”。将进入“Add to Coupling

Regions”对话框页,(New Coupling)将出现在左边的窗口中。

现在点击“Edit coupling Region”表页,这里可以浏览我们建立的耦合

区域的截面图。从这里,点击 Layer 对话框中的下拉菜单,从中选择“3,

Signal, InnerSignal1”,以及不选择“Auto Zoom”复选框以便可以浏览

整个叠层结构。

点击传输线类型“Transmission-Line Type”页表,在 Comment 域中填

上“Aggressor 1”。

点击“确定”按钮退出。

重复以上的几个步骤,用同样的方法建立第二和第三根网络,必须注意

保证三根传输线处于同一个耦合区域“Coupling0001”中,命名第二根

位于中间的传输线为“Victim” [TL(A1,B1)],而第三根位于右边的

传输线命名为“Aggressor 2”[TL(A2,B2)]。它们之间的左右位置可以

通过窗口底部的左右方向的箭头移动,按照需要调整三根传输线的位置,

如下图:

HK +852-26371886 SZ 755-8885 9921 www.kgs.com.hk SH 21-5108 7906 BJ 10-5166 5105

support@kgs.com.hk

第 22 页 共 71 页

Loading...

Loading...