Kenwood Z-919 Service manual

CD/MD-CH DSP CONTROL CD RECEIVER

Z919

SERVICE MANUAL

C

2000-5 PRINTED IN JAPAN

B51-7635-00 ( N ) 1694

Panel assy

(A64-2119-02) : K type

(A64-2120-02) : M type

Panel escutcheon

: K type only

(B01-0887-05)

DC cord

(E30-4737-15)

Front glass

(B10-3229-02)

Knob (FM,AM,FWD,REV)

(K25-1114-03)

Sub panel assy

(A22-2803-13) : K type

(A22-2857-03) : M type

Remote controller assy

(RC-601)

(A70-2006-05)

Size AAA battary

(Not supplied)

Mounting hardware assy

(J21-7596 -02)

Mounting hardware

(J21-7673 -05)

Screw set

(N99-1559-05)

Screw set

: K type only

(N99-1694-05)

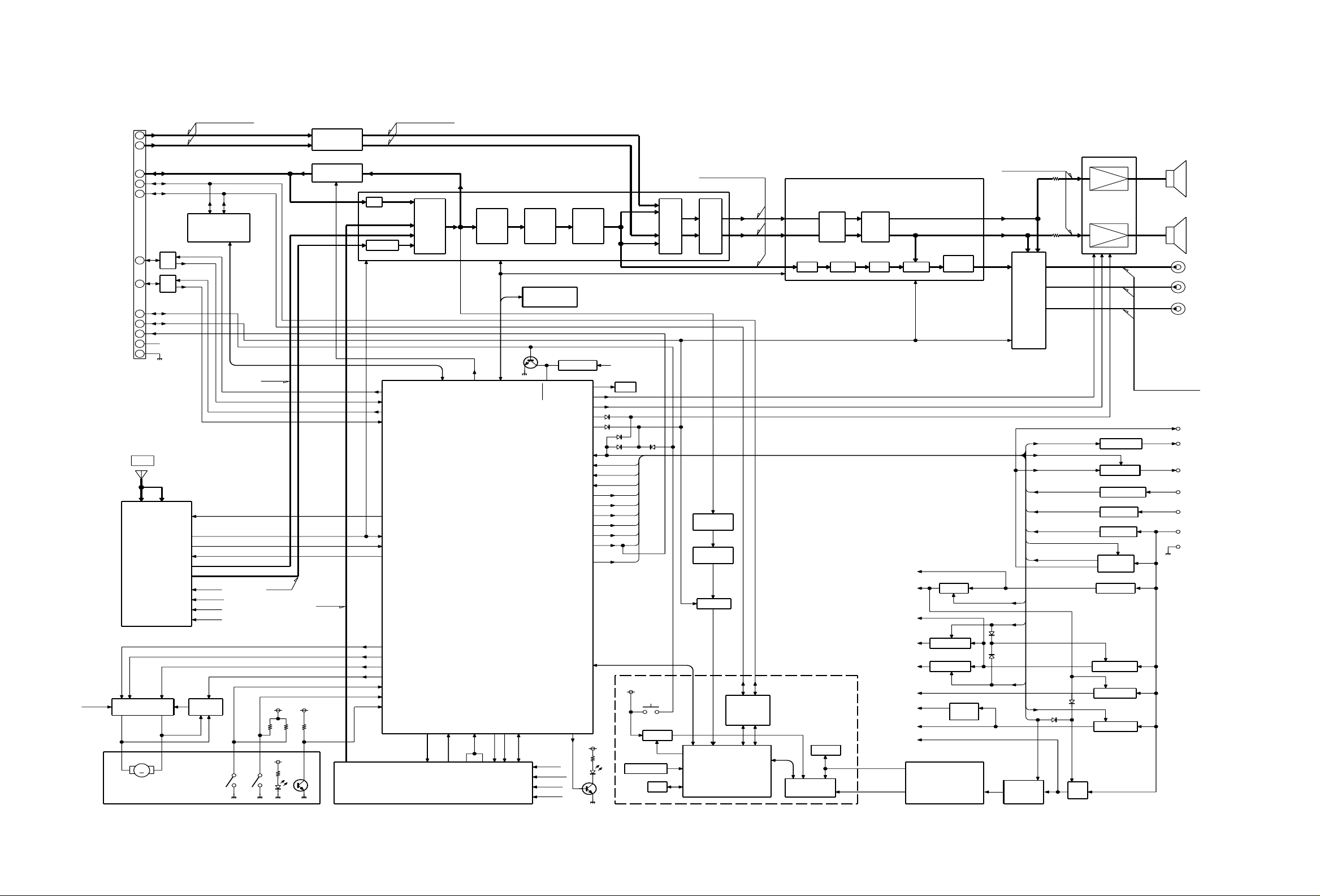

Z919

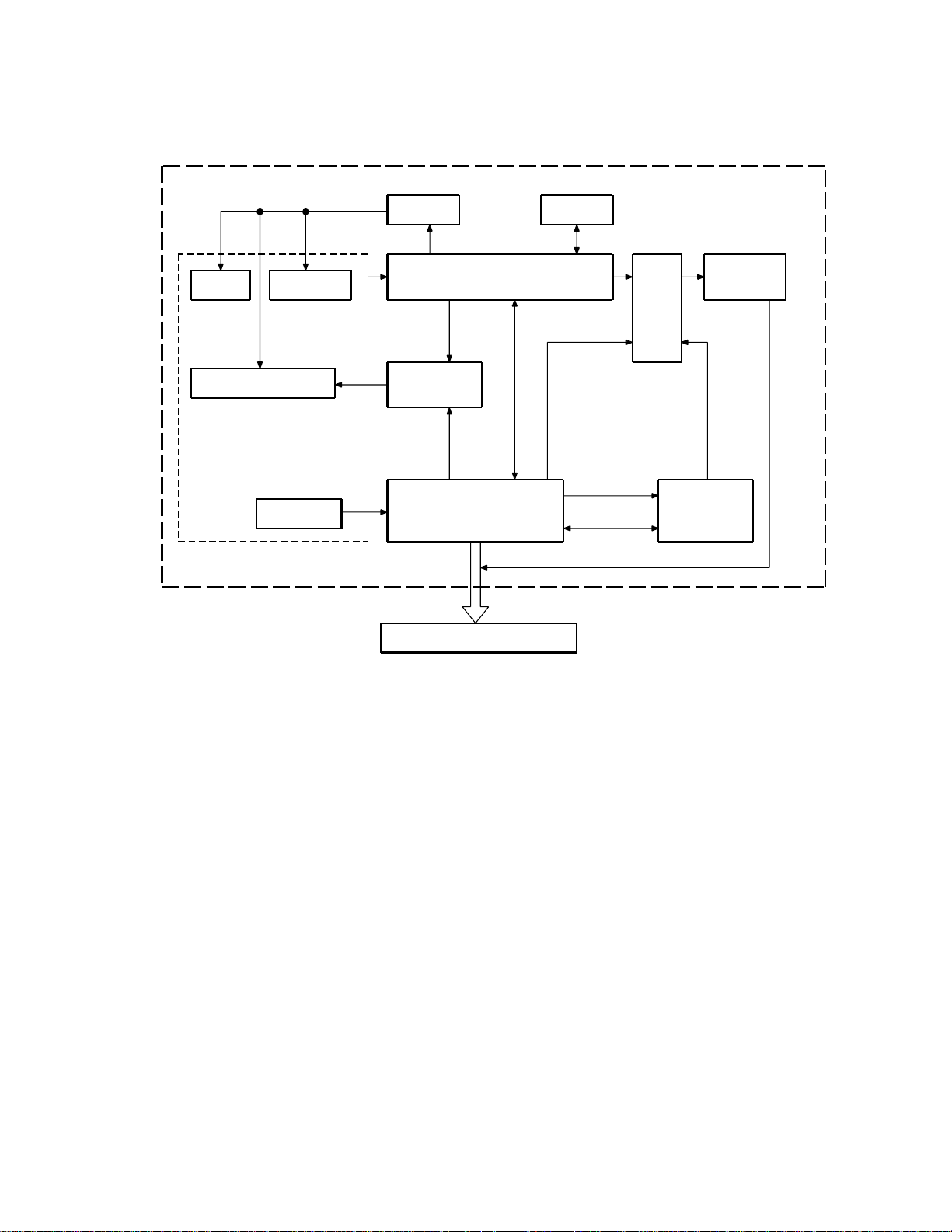

BLOCK DIAGRAM

PROCESSOR UNIT (X32-4800-00)

SPINDLESLED

OPTICAL PICKUP

SLED SW

IC11

DRIVER

IC2

uPD67324B

SERVO DPS&ROM DECODER

IC10

RF MATRIX

AMPLIFIER

IC1

M30620MC-XXXGP

ROM : 128K

RAM : 10K

IC6

DRAM

(DMA)

MULTIPLEX BUS

SIO (DMA)

IICBUS

IICBUS

IC3

SW

IC5

IC9

PCM1716

DAC

STA013

MP3

DECODER

SYSTEM COMPUTER

2

SW 14V

MZ-BUS

FRONT IN

REAR IN

AUDIO I/O

BUS +

BUS ON

BUS OFF

RESET

MUTE

ILLUMI

IC21

CN

BUS -

B.U

GND

MAIN

A1

W02-3119-15

MOTOR

DRIVER

PANEL MECHA

D40-1112-35

AM ANT

FM DET OUT

AM DET OUT

F/E

M

MD,CD:

MD,CD-CH:

Q14,15

17,18

I/F

I/F

B.U

FM ANT

FM SD

REQUEST

TAPE:

CLK

DATA

FSD

CE

IC2

IC23,

Q34

MD,CD:

MD,CD-CH:

TAPE,TV: 566mV

FM:

AM:

379mV

364mV

FM:

340mV

AM:

MZ-BUS

I/F

UPD74042BGT

PON 5V

COM +B

FM +B

AM +B

SPEED

CONT

OPEN SW

TV:

358mV

343mV

572mV

189mV

600mV

763mV

200mV

CLOSE SW

AM:

160mV

FM:

400mV

B.U 5V

PON 5V

PON 5V

IC10,11,14,15

ISO

NJM4565M

IC13

ANA SW

TC4W66F

CD:

379mV

IC6

ISO

NC,MPX

CD MECHA

DXM-1701

AUDIO OUT

MD,CD-CH:

IC3

SYS ON

ON REQ

SYS OFF

OFF REQ

PLL CLK

PLL DATA

PLL CE

FSD

FM SD

REQUEST

MOTOR +

MOTORT CTRL

SPEED

OPEN DET

CLOSE DET

CD DET

MD,CD:

TAPE,TV:

FM:

INPUT

SEL

427mV

409mV

674mV

682mV

225mVAM:

B DIC

B IRQ

B DCOM

CD LO/EJ

CD MOTOR

CD SW1

SW 1

LO/EJ

MOTOR

B C/D

B CLK

B RST

784215YGC-038

CD SW2

CD SW3

SW 2

SW 3

SYSTEM u-COM

A MUTE R

Z919Z919

BLOCK DIAGRAM

E VOL, TONE, NC, MPX

VOL MUTE TONE SEL

IC5

2

E P ROM

S-24C01BFJA

Q13

E CLK

RELAY

CD MUTE

A MUTE L

CD STOP

M STOP

E DATA

CD RST

M RST

CD CLK

CD DATA

M CLK

M DATA

RESET

B.U 5V

M SW 5V

AUD +B

SRV +B

IC9

VDD DET

BEEP

P STBY

P MUTE

MUTE

BU DET

ACC DET

SMALL

ANT CON

P CON

ILLUMI

AMP CON

SC CON

MC CLK

SC DATA

SC REQ

P RST

Q11

SVR

DIAG

P ON

FM

AM

G ILL

TDA7400

B.U 5V

BZ1

BUZ

B.U 5V

RST SW

S6

Q11

B.U 5V

5V SW

IC4

REMOCON

KEY

SWITCH UNIT (X25-8530-11)

IC3

MD,CD:

MD,CD-CH:

TAPE,TV:

FM:

AM:

VOL

BAL

FAD

IC16

L-R MIX

AMP

LEVEL

DET

Q22

MUTE

LEVEL

IC1

MZ-BUS

DRIVER

HA12187

PANEL u-COM

MB90583BPFV110

953mV

913mV

1507mV

1522mV

505mV

IC17

HPF,LPF,VOL

TDA7401

HPF MUTE

VOL MUTE LPF MUX /INV

B.U 5V

PON 5V

COM +B

FM +B

AM +B

AUDIO +B

M SW 5V

SRV +B

SW 14V

ILLUMI

ED1

VFD

CN1930M

A2

+B

FAC

N-INV

Q32

5V SW

Q9

FM8V SW

Q8

AM8V SW

IC25

M 5V

DC/DC

W02-3221-05

AVR

Q42-47

P ON

MD,CD:

MD,CD-CH:

TAPE,TV:

FM

AM

Q24,63

ILLUMI

14V SW

FM:

AM:

MUTE

939mV

900mV

1486mV

1500mV

498mV

SRV ON

ILLUMI

AMP CON

ANT CON

SMALL

ACC DET

B.U DET

P CON

DIAG

14V

SW

IC20

Q57,59

PWR AMP

TDA7386

Q21

AMP CON

Q19

ANT CON

Q25

SMALL DET

Q26

ACC DET

Q27

B.U DET

IC12

P CON

IC26

D5V AVR

T8V AVR

A8V AVR

SRV AVR

IC4,Q35

IC19,Q39

IC24

MD,CD:

MD,CD-CH:

TAPE,TV:

FM:

AM:

888mV

850mV

1404mV

1417mV

470mV

P CON

AMP CON

ANT CON

SMALL

ACC

B.U

GND

FRONT

SP OUT

REAR

SP OUT

FRONT

PRE OUT

REAR

PRE OUT

NON-FAD

PRE OUT

3

4

Z919

COMPONENTS DESCRIPTION

Synthesizer Unit (X14-6260-xx)

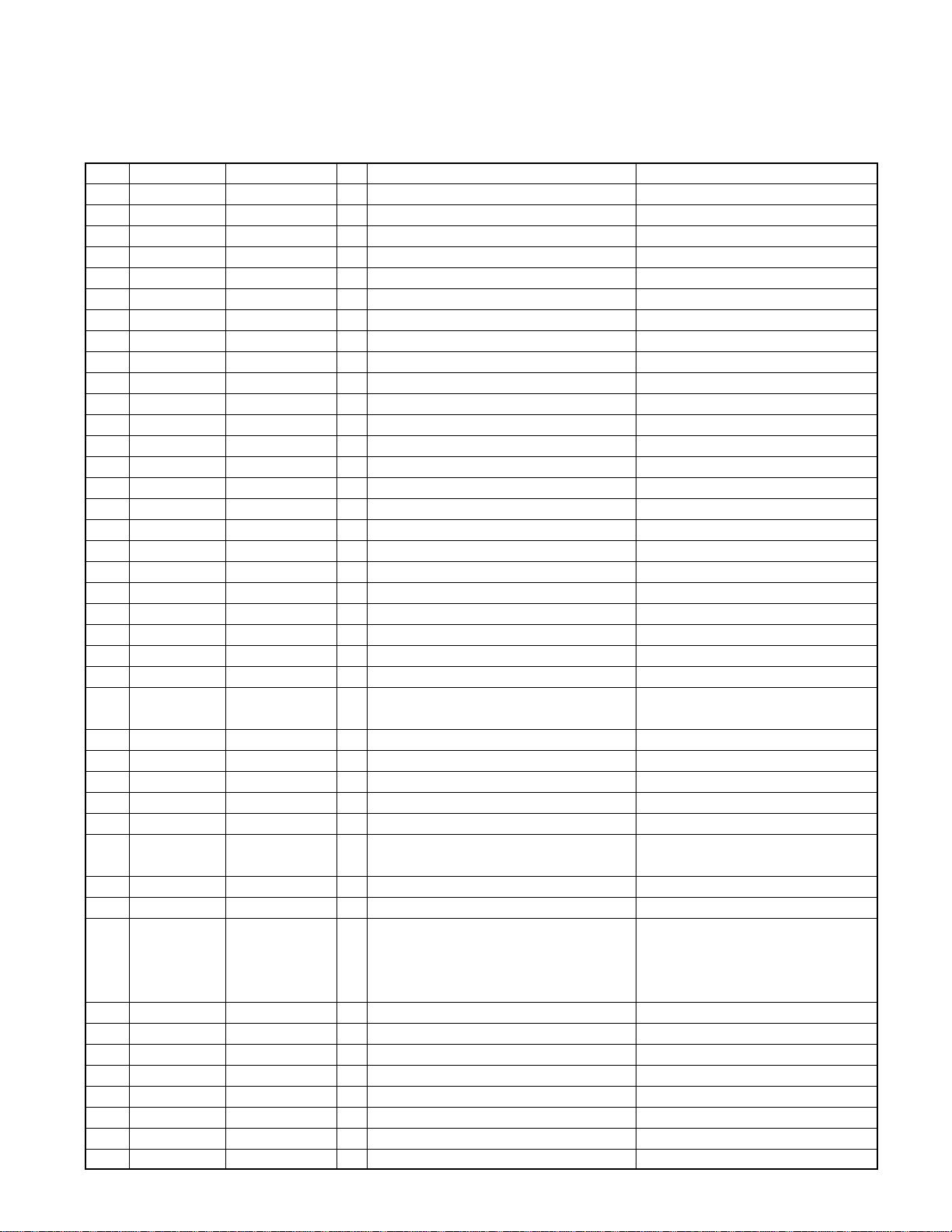

Ref. No. Components Name Application / Functions Operation / Condition / Compatibility

IC2 UPD72042BGT MZ-BUS Interface IC MZ-BUS Communication Interface

IC3 784215YGC-038 Microcomputer System Microcomputer

IC4 M5237ML Regulator IC Tuner+B

IC5 S-24C01B E2PROM Tuner Adjustment Data Memory

IC6 TDA7400 Electronic Volume EVOL, LOUD, TONE, BAL, FAD, FMNC, MPX

IC7 TC7W02F Logic IC (NOR) Logic circuit for muting

IC9 S-80830ANNP Power source detection System Microcomputer Reset

IC10 NJM4565M-TE2 Ope Amp (2 enclosed) Isolation Circuit (DSP Input Lch)

IC11 NJM4565M-TE2 Ope Amp (2 enclosed) Isolation Circuit (DSP Input Rch)

IC12 L9820D013TR P-CON P-CON, ANT-CON output control

IC13 TC4W66F Analog Switch Switch for head and slave unit switching

IC14 NJM4565M-TE2 Ope Amp (2 enclosed) Isolation Circuit (DSP Input Lch)

IC15 NJM4565M-TE2 Ope Amp (2 enclosed) Isolation Circuit (DSP Input Rch)

IC16 NJM4565M-TE2 Ope Amp (2 enclosed) Reference voltage output, level meter circuit

Ic17 TDA7401 Electronic Volume HPF, LPF, VOL, MUTE

IC19 M5237ML Regulator IC Audio+B

IC20 TDA7386 Power IC Power amp for speaker output

IC21 BA6219BFP-Y Motor Driver Panel mechanism motor control

IC23 NJM2130F Ope Amp (1 enclosed) Panel mechanism motor control

IC24 LM2675M-ADJ Switching Regulator Servo+B

IC25 BA05T Regulator IC 5V switch for CD mechanism

IC26 M5278D05 Regulator IC Backup 5V

Q1 DTC144EUA Illumination switch ON when Micon 56 pin is “H”

Q2 DTA144EUA for BUS communication (BUS communication illumination output)

Q3 DTA144EK Switch for head ON when Micon 84 pin is “H” (When outputting own source)

and slave unit switching OFF when Micon 84 pin is “L” (When inputting other source)

Q5 UMC2N DC/DC+B switch ON when Micon 56 pin is “H” (DC/DC+B output)

Q6 DTC124EK AM+B switch ON when Micon 7 pin is “H” (AM+B output)

Q7 DTC124Ek FM+B switch ON when Micon 8 pin is “H” (FM+B output)

Q8 CPH3105 AM+B switch ON when Micon 7 pin is “H” (AM+B output)

Q9 CPH3105 FM+B switch ON when Micon 8 pin is “H” (FM+B output)

Q10 DTC124EK Buzzer switch ON when Micon 87 pin is “H”

Q11 DTC114YK Switch for guide illumination ON when Micon 49 pin is “H” (Guide illumination lights up)

Q12 DTC114EK Switch for head ON when Micon 84 pin is “H” (When outputting own source)

and slave unit switching OFF when Micon 49 pin is “L” (When inputting other source)

Q13 DTC144EK Reset Switch ON when panel reset request is “H” (Resetting action)

Q14 UMG2N System ON/OFF Request Switch ON when Micon 95, 96 pin is “L” or slaves BUS

ON/OFF request (each requelsing system ON/OFF)

Q16 DTA124EK Mute Switch ON when Micon 74,75 pin is “H”, backup detection,

and reset request from panel (Mute ON)

Q17 UMA2N System ON/OFF Switch ON when Micon 95, 96 pin is “L”

(Each requesting system ON/OFF)

Q19 2SB1277(Q,R) Antenna Control ON when Micon 3 pin is “H” (Antenna control output)

Q20 2SV2412K

Q21 DTA123JK External Amplifier Control ON when Micon 83,75 pin is “H”

5

Z919

COMPONENTS DESCRIPTION

Ref. No. Components Name Application / Functions Operation / Condition / Compatibility

Q22 DTC124EK Level Meter Mute Swtich ON when “H” at Q16 ON (level meter mute processing)

Q23 DTC144Ek Navu Mute Switch ON when nave mute is “H” (mute processing)

Q24 2SC4081 DC/DC+B Switch ON when micon 56 pin is “H” (DC/DC+B output)

Q25 DTC144EK Samll Detection ON when small signal is “H” (Dimmer processing)

Q26 2SC2412K ACC Detection ON when detecting ACC, OFF when non-detecting ACC.

Q27 2SC2412K B,U Detecton

Q28 DTC144EK IC17 (Electronic Vol.) Mute Switch ON when “H” at Q16 ON (IC17 mute processing)

Q29 DTC144EK

Q30 2SD2114K Switch for Head and ON when micon 84 pin is “H” (When outputting own source)

Q31 DTC144EUA Pre-out mute switch ON when Q31 is ON and and “L” (pre-out mute actoin)

Q32 DTB123YK P_ON 5V switch ON at time of micon 100 pin “L” (P_ON 5V output)

Q33 DTA124EUA Pre-out mute switch ON when Q16 is ON and and “H” (pre-out mute actoin)

Q34 DTC114YK

Q35 2SB1184 Tuner+B switch On when micon 7 or 8 pin is “H” (Tuner +B output)

Q39 2SB1184 Audio +B switch ON when P_ON 5V is ON (Audio +B output)

Q40 DTA124EK Tuner+B switch On when micon 7 or 8 pin is “H” (Tuner +B output)

Q41 DTA124EK Audio +B switch ON when P_ON 5V is ON (Audio +B output)

Q42 DTC343TK Audio mute front Lch ON when Q33 ON and “H” (Mute processing)

Q43 DTC343TK Audio mute front Rch ON when Q33 ON and “H” (Mute processing)

Q44 DTC343TK Audio mute in rear Lch ON when Q33 ON and “H” (Mute processing)

Q45 DTC343TK Audio mute in rear Rch ON when Q33 ON and “H” (Mute processing)

Q46 DTC343TK Audio mute nonfender Lch ON when Q33 ON and “H” (Mute processing)

Q47 DTC343TK Audio mute nonfender Rch ON when Q33 ON and “H” (Mute processing)

Q49 DTC144EK Tuner+B switch On when micon 7 or 8 pin is “H” (Tuner +B output)

Q50 2SC2412K Illumination switch ON when micon 56 pin is “H” (Panel illumination is ON.)

Q53 DTC114YUA Power IC SVR control switch ON when micon 91 pin is “H” (SVR discharge)

Q54 DTC144EK Audio+B switch ON when P_ON 5V is ON (Audio +B output)

Q56 UMC2N Switch 14V ON when micon 56 pin is “H” or P_ON 5V is ON (SW 14V output)

Q57 2SC4081 Switch 14V ON when micon 56 pin is “H” or P_ON 5V is ON (SW 14V output)

Q59 CPH3105 Switch 14V ON when micon 56 pin is “H” or P_ON 5V is ON (SW 14V output)

Q63 CPH3105 DC/DC+B Switch ON when micon 56 pin is “H” (DC/DC+B output)

Panel Mechanism torque control switch

Slave unit switching OFF when micon 84 pin is “L” (When inputting other source)

Panel Mechanism speed control switch

ON when detecting B and U, OFF when detecting instant diminishing

ON when micon 51 pin is “H” (Weak panel mechanism torque)

ON when micon 57 pin is “H” (Panel mechanism actoin, low speed)

Switch Unit (X25-8530-11)

Ref. No. Components Name Application / Functions Operation / Condition / Compatibility

IC1 HA12187FP BUS-IC IC for BUS communication

IC3 MB90583BPFV110 Panel micon IC for panel control

IC4 RS-171 Remote control light receiving IC Output 2 pin pulse when receiving remate control

Q5 DTA144EUA Swotch for PANEL 5V ON when base is “L”

Q10 DTC114EUA VFD 5V control ON when base is “H”

Q11 DTA144YK VFD 5V SW ON when base is “L”

Q12 DTC114EUA FL+B detection SW ON when base is “H”

Q13 DTC114EUA VFD blanking control ON when base is “H”

6

MICROCOMPUTER’S TERMINAL DESCRIPTION

System Microcomputer 784215YGC (X14-6260-xx : IC3)

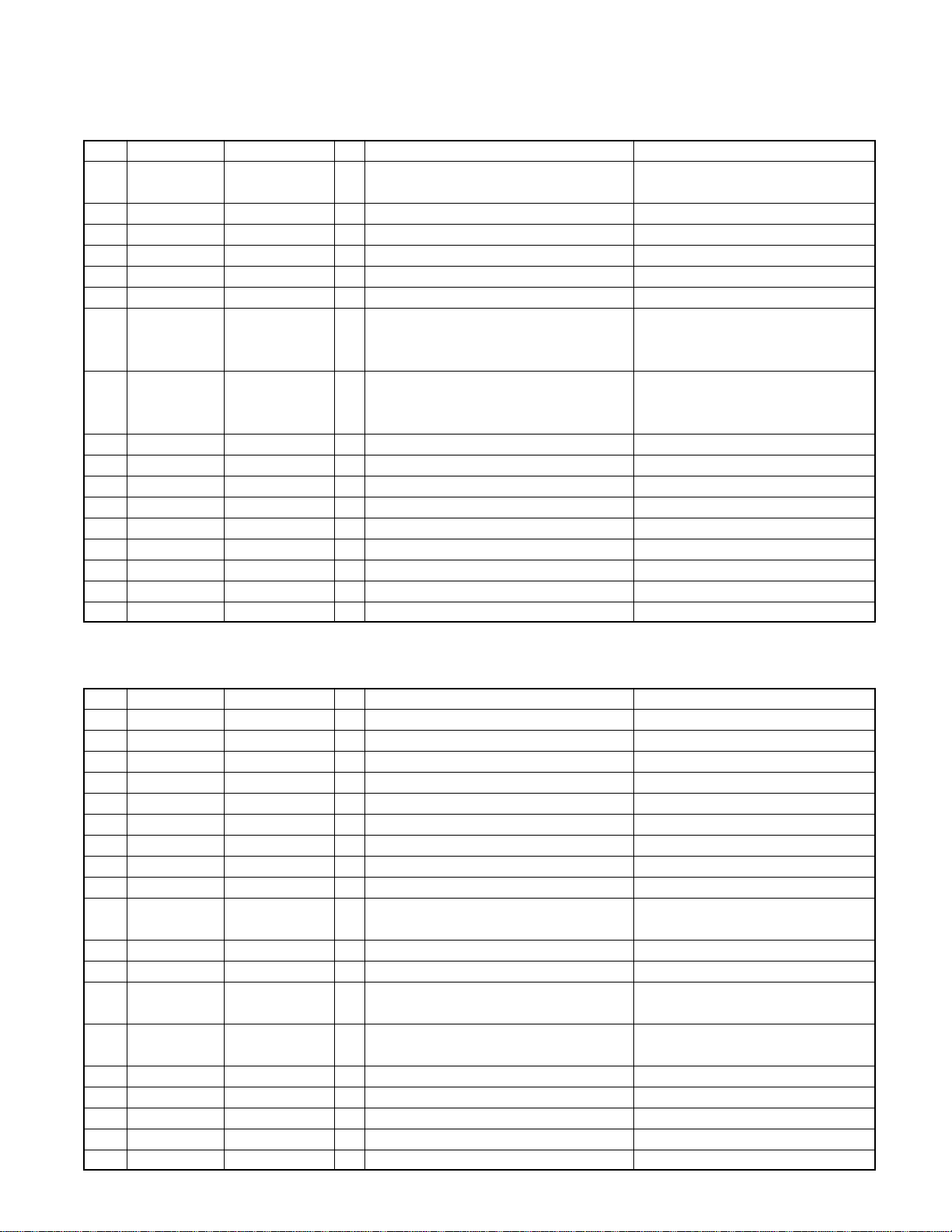

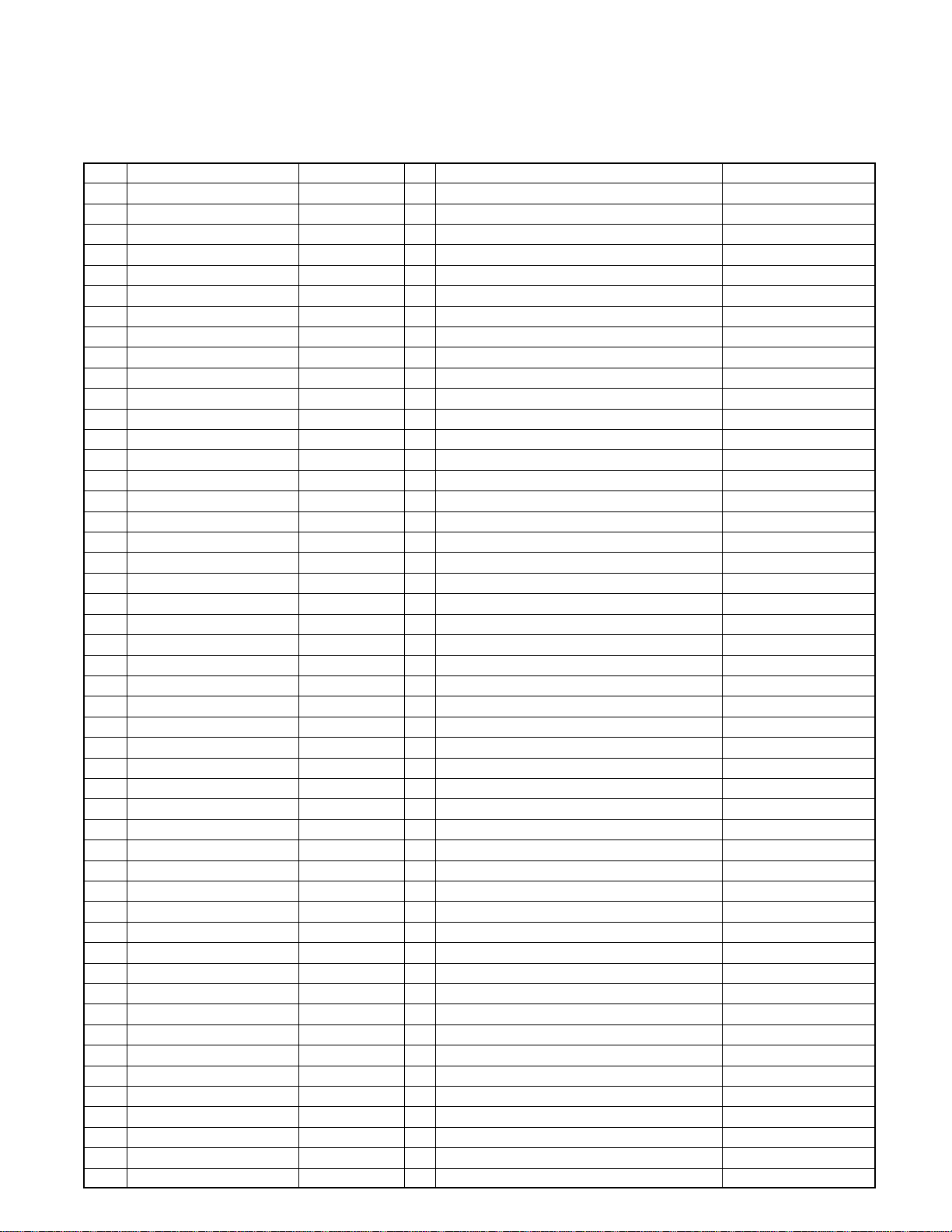

Pin Pin Name Function I/O Description Processing Operation

1 P120/RTP0 DIAG I

2 P121/RTP1 P_CON O P-CON control output terminal L: Off / H: On

3 P122/RTP2 P_ANT O Power antenna control output terminal L: Off / H: On

4 P123/RTP3 BU_DET I Back up detection terminal L: Back up on detection

5 P124/RTP4 ACC_DET I ACC detection terminal L: Acc On detection

6 P125/RTP5 O Not used

7 P126/RTP6 AM+B O Tuner AM power control terminal

8 P127/RTP7 FM+B O Tuner FM power control terminal

9 Vdd Vdd – 5V potential

10 X2 X2 –

11 X1 X1 I

12 Vss Vss – GND potential

13 XT2 XT2 –

14 XT1 XT1 I

15 RESET RESET I System reset input L: Reset / LÆH: Processing begins

16 P00/INTP0 BIRQ I Communication request from K-Bus Request at rising edge

17 P01/INTP1 O Not used OPEN (L-fixed)

18 P02/INTP2 O Not used OPEN (L-fixed)

19 P03/INTP3 PN_SC_REQ I Communication request from panel micon Request at rising edge

20 P04/INTP4 O Not used OPEN (L-fixed)

21 P05/INTP5 O Not used OPEN (L-fixed)

22 P06/INTP6 REF_CON O A/D port reference voltage control terminal

23 AVdd AVdd – Connected to Vdd

24 AVref0 AVref0 – A/D port reference voltage terminal

25 P10/ANI0 FSD I S-meter detection terminal (Adjust to) FM: 2.85V at ANT 35dBµ

26 P11/ANI1 OPEN I Panel mechanism open switch L: Panel full-open

27 P12/ANI2 CLOSE I Panel mechanism close switch L: Panel full-close

28 P13/ANI3 CD_DET I CD in place/not in place detection terminal L: Disk in place / H: Disk not in place

29 P14/ANI4 I Not used Connected to GND

30 P15/ANI5 I Not used Connected to GND

31 P16/ANI6 SEL1 I Changed according to destination SEL1, SEL2 / H, L M-type

32 P17/ANI7 SEL2 I Changed according to destination Refer to 31 pin

33 AVss AVss – Connected to Vss

34 P130/ANO0 ST_SEL0 I

35 P131/ANO1 ST_SEL1 I

36 AVref1 AVref1 – Not used Connected to VDD

37 P70/RxD2/SI2 I Not used Connected to GND

38 P71/TxD2/SO2 PLL_DATA O PLL-IC data output terminal

39

P72/ASCK2/SCK2

40 P20/RxD1/SI1 BDIC I K-Bus data input terminal

41 P21/TxD1/SO1 BDCOM O K-Bus data output terminal

42

P22/ASCK1/SCK1

PLL_CLK O PLL-IC clock output terminal

BCLK O K-Bus clock output terminal

PCON-IC excess voltage & current detection terminal

Main system clock oscillation terminal (12.58MHz)

Main system clock oscillation terminal (12.58MHz)

Sub-system clock oscillation terminal (32.768KHz)

Sub-system clock oscillation terminal (32.768KHz)

IC2 III (TDA7400) Roll Off Comp setting terminal

IC2 III (TDA7400) Roll Off Comp setting terminal

L: Abnormal / H: Normal

Voltage at AM: ANT 35dBµ

SEL1, SEL2 / H, H K-type

SEL0, SEL1 / L, H Change1

SEL0, SE11 / H, L Change2

SEL0, SEL1 / H, H Change3

SEL0, SEL1 / L, L Initial setting

Refer to 31 pin

Z919

7

Z919

Pin Pin Name Function I/O Description Processing Operation

43 P23/PCL O Not used Open (L-fixed)

44 P24/BUZ O Not used Open (L-fixed)

45 P25/SI0/SDA0 CD_DATA I/O CD mecha control data I/O terminal

46 P26/SO0 O Not used Open (L-fixed)

47

P27/SCK0/SCL0

48 P80/A0 O Not used Open (L-fixed)

49 P81/A1 G_ILLUM O Guide illumination power control terminal L: Off / H: On

50 P82/A2 O Not used Open (L-fixed)

51 P83/A3 T_CTRL O Panel mech torque control terminal L: Strong / H: Weak

52 P84/A4 PN_SC_CON O Panel micon wakeup control terminal L: Off / H: Wakeup

53 P85/A5 PN_SC_DATA I Panel micon data input terminal

54 P86/A6 PN_MC_CLK O Panel micon clock output terminal

55 P87/A7 PN_RST O Panel micon reset outputterminal L: Panel micon reset

56 P40/AD0 ILLUM O Key illumination power control terminal L: Off / H: On

57 P41/AD1 MOTOR_SPD O

58 P42/AD2 O Not used Open (L-fixed)

59 P43/AD3 CD_MUTE I CD mechanism mute detection terminal L: Mute requested.

60 P44/AD4 CD_RST O CD mechanism reset contorl terminal L: CD mechanism micon recet

61 P45/AD5 O Not used Open (L-fixed)

62 P46/AD6 CD_STOP O

63 P47/AD7 CD_SW2 I CD mechanism switch2 (8cm/12cm) L: 12cm disk

64 P50/A8 CD_SW1 I CD mechanism switch1 (Loading start) L: Disk in place

65 P51/A9 CD_SW3 I CD mechanism switch3 (Down & limit) L: Loading complete

66 P52/A10 O Not used Open (L-fixed)

67 P53/A11 O Not used Open (L-fixed)

68 P54/A12 O Not used Open (L-fixed)

69 P55/A13 O Not used Open (L-fixed)

70 P56/A14 CD_MOTOR O CD mechanism motor control terminal MOTOR, LOEJ / L, Hi-Z stop

71 P57/A15 CD_LOEJ I/O CD mechanism loading/eject control terminal Refer to 70 pin

72 Vss Vss – GND potential

73 P60/A16 O Not used Open (L-fixed)

74 P61/A17 P_MUTE O PWR-IC mute control terminal L: Off / H: On

75 P62/A18 MUTE O Mute control output terminal L: Off / H: On

76 P63/A19 BC/D O K-Bus comand / Data control terminal L: data / H: Command

77 P64/RD BCS O K-Bus CS control terminal

78 P65/WR BRST O K-Bus reset control terminal L: BUS-IC reset

79 P66/WAIT MOTOR+ O Panel mechanism motor control (+direction) M+, M– / L, L stop

80 P67/ASTB MOTOR– O Panel mechanism motor control (–direction) Refer to 79 pin.

81 Vdd Vdd – 5V potential

82 P100/TI5/TO5 SRV_PN O Servo power control output terminal H: Servo +B On

83 P101/TI6/TO6 AMP_CON O

8

MICROCOMPUTER’S TERMINAL DESCRIPTION

CD_CLK O CD mecha control clock I/O terminal

Actiononly when reset releasing

Panel mechanism processing speed control terminal

CD mechanism control wakeup contorl output terminal

External amp basss boost level control terminal

Highspeed: L / Lowspeed: H (Angle adjustment: Lowspeed)

L→H: Action start

L: Off / H: Wakeup

MOTOR, LOEJ / H, L loading

MOTOR, LOEJ / H, H eject

MOTOR, LOEJ / H, Hi-Z brake

M+, M– / L ,H reverse

M+, M– /H, L forward

M+, M– /H, H brake

Z919

MICROCOMPUTER’S TERMINAL DESCRIPTION

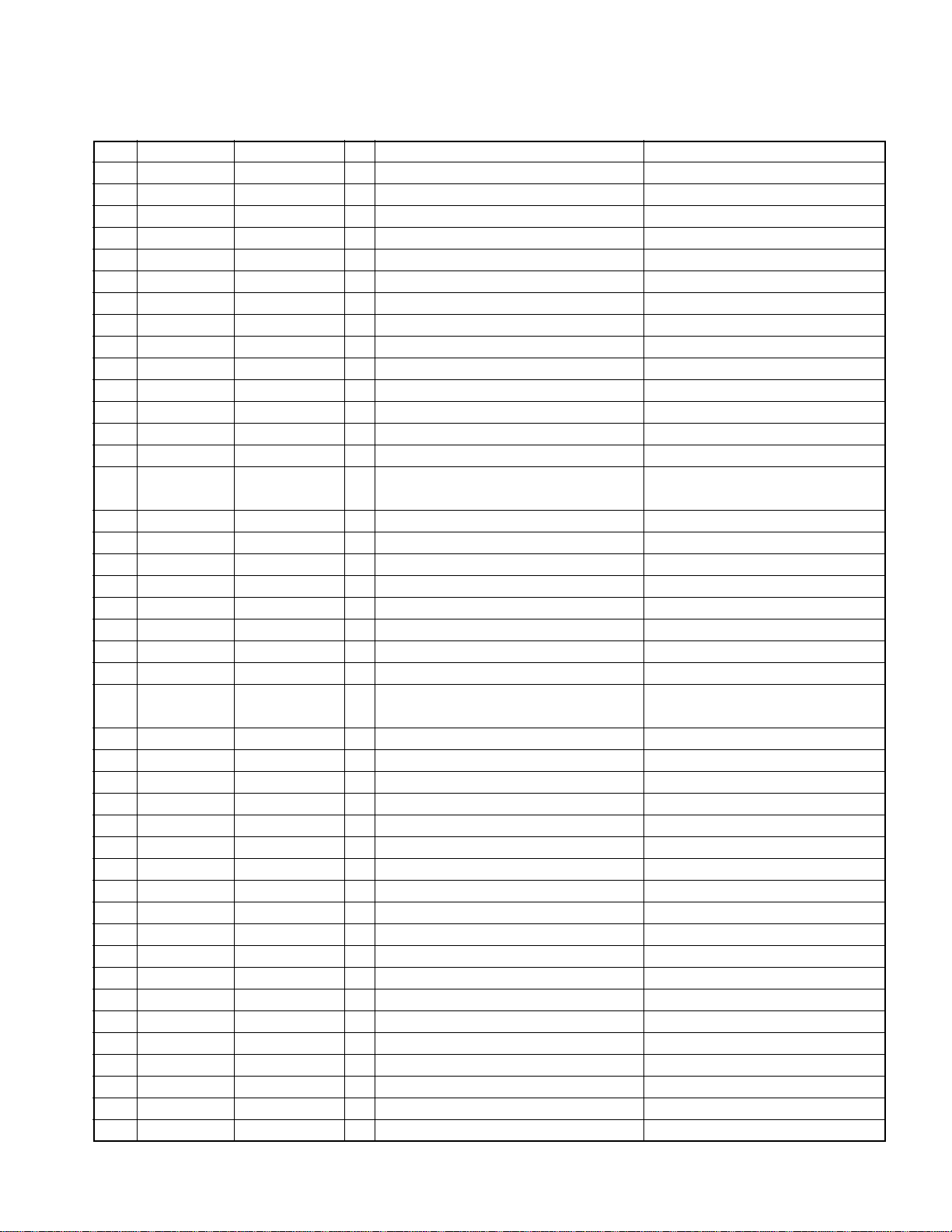

Pin Pin Name Function I/O Description Processing Operation

84 P102/TI7/TO7 RELAY O BUS-AUDIO switching control terminal L: Other source inpout

H: Own source outpout

85 P103/I8/TO8 PLL_CE O PLL-IC CE output terminal

86 P30/TO0 FM_SD I FM SD detection terminal L: No station / H: Station in place

87 P31/TO1 BEEP O Beep output terminal L: Off / H: On

88 P32/TO2 REQUEST O Seek control terminal When seek: L / When receiving: H

89 P33/TI1 TEST (Not used) O

90 P34/TI2 STBY O PWR-IC pwer cotnrol termianl L: Off / H: On

91 P35/TI00 SVR_ON O SVR control terminal L: Normal

92 P36/TI01 OFF_REQ I K-Bus Off request detection terminal L: System Off request detection

93 P37 ON_REQ I K-Bus On request detection terminal L: System On request detection

94 TEST/Vpp TEST – Direct connection with Vss

95 P90 SYS_OFF O K-Bus Off request output terminal L: System Off request detection

96 P91 SYS_ON O K-Bus On request output terminal L: System On request detection

97 P92 EVOL_DATA I/O Electronic voluem data I/O terminal

98 P93 EVOL_CLK O Electronic voluem clock output terminal

99 P94 SMALL I SMALL detection terminal L: On / H: Off

100 P95 P_PN O P-ON control output terminal L: On / H: Off

Temperature protecton control terminal (not used)

When in test mode: L / Other: H

Rising: 400ms after PON

Falling: Same as PCON

H: When discharging After STBY falling

H within 5 seconds

Panel Microcomputer MB90583BPFV110 (X25-8530-11 : IC3)

Pin Pin Name Function I/O Description Processing Operation

1 P22/A18 KR3 I Take in key, Key Return3

2 P23/A19 KR3 I Take in key, Key Return4

3~8 NC O Not used

9 Vss – GND

10~15 NC O Not used

16~18 – O GND

19 P43/SIN1 P_ON O Power control on ambient IC’s L: On / H: Off

20 P44/SOT1 VFD_DATA O

21 Vcc – 5V

22 P45/SCK1 VFD_CLK O VFD (Illumination tube) serial clock output

23,24 NC O Not used

25 C C 0.1µF condensor connection pin

26 P71 SC_DATA O When EFECT/SOURCE key is pressed when

27 P72 SC_REQ O By active change (“Lo→Hi”), send

28 DVRH – 5V

29 DVSS – GND

30 P73/DAO0 NC O Not used. Open

31 P74/DAO1 REF_CON O AVD port refeence voltage control terminal

32 AVCC – 5V potential

VFD (Illumination tube) serial data output terminal

terminal(Z)(M)(D) 2.10MHz, (J)(MZ) 1.57MHz

ACC/POWER Off, send key code to system micon

transmission request for key code to system micon

9

Z919

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin Pin Name Function I/O Description Processing Operation

33 AVRH – AD port reference voltage input terminal

34,35 AVRL – GND

36 P50/AN0/SIN3 LEVEL_M I HEAD spec analyzer signal input terminal

37~39 NC O Not used

40 Vss Vss GND

41~44 NC O Not used

45 P80/IRQ0 SC_CON I

46 P81/IRQ1 NC O Not used Open

47 MD0 Vcc I Chip mode selection terminal (Hi) Pull up (5V)

48 MD1 Vcc I Chip mode selection terminal Pull up (5V)

49 MD2 Vss I Chip mode selection terminal Pull down (GND)

50 HSTX HSTX I Hardware reset terminal H: Reset

51 P82/IRQ2 KR0 I keyreturn 0 (Effective key during STBY)

52 P83/IRQ3 NC O Not used Open

53 P84/IRQ4 MC_CLK I Due to active change (clock),

54 P85/IRQ5 NC O Not used Open

55 P86/IRQ6 SYS_ON O HA12187FP STBY terminal L: STBY

56 P87/IRQ7 VFD_ON O VFD 5V control terminal "H": on "L": off

57~61 NC O Not used

62 P65/CKOT VFD_LAT O VFD latch control terminal L→H for latching

63 TX TX O IE Bus output

64 RX RX I IE Bus input

65~68 NC O Not used

69

P94/TOT1/OUT0

70

P95/TOT2/OUT1

71 P96/PWC REMOCON I Remote control signal input terminal

72~77 NC O Not used

78 X0A X0A Connected to GND

79 Vss Vss GND

80 X0 X0 Main clock input terminal

81 X1 X1 Main clock input terminal

82 Vcc Vcc 5V

83 P00/AD00 NC O Not used Open

84 P01/AD01 Pull up 5V I For flushing 5V

85~90 NC O Not used

91 P10/AD08 KS0 O Keyscan 0 for outputting keyscan signal

92 P11/AD09 KS1 O Keyscan 1 for outputting keyscan signal

93 P12/AD10 KS2 O Keyscan 2 for outputting keyscan signal

94 P13/AD11 KS3 O Keyscan 3 for outputting keyscan signal

95 P14/AD12 KS4 O Keyscan 4 for outputting keyscan signal

96~98 NC O Not used

99 P20/A16 KR1 I Keyreturn 1 for taking in key

100 P21/A17 KR2 Keyreturn 2 for taking in key

VFD_BLK O Duty is switched by blank output control

NC O Not used Open

System performance condition detection terminal

key data is sent to the system micon

(Lo: Blank ON / H: Blank OFF)

10

Z919

MICROCOMPUTER’S TERMINAL DESCRIPTION

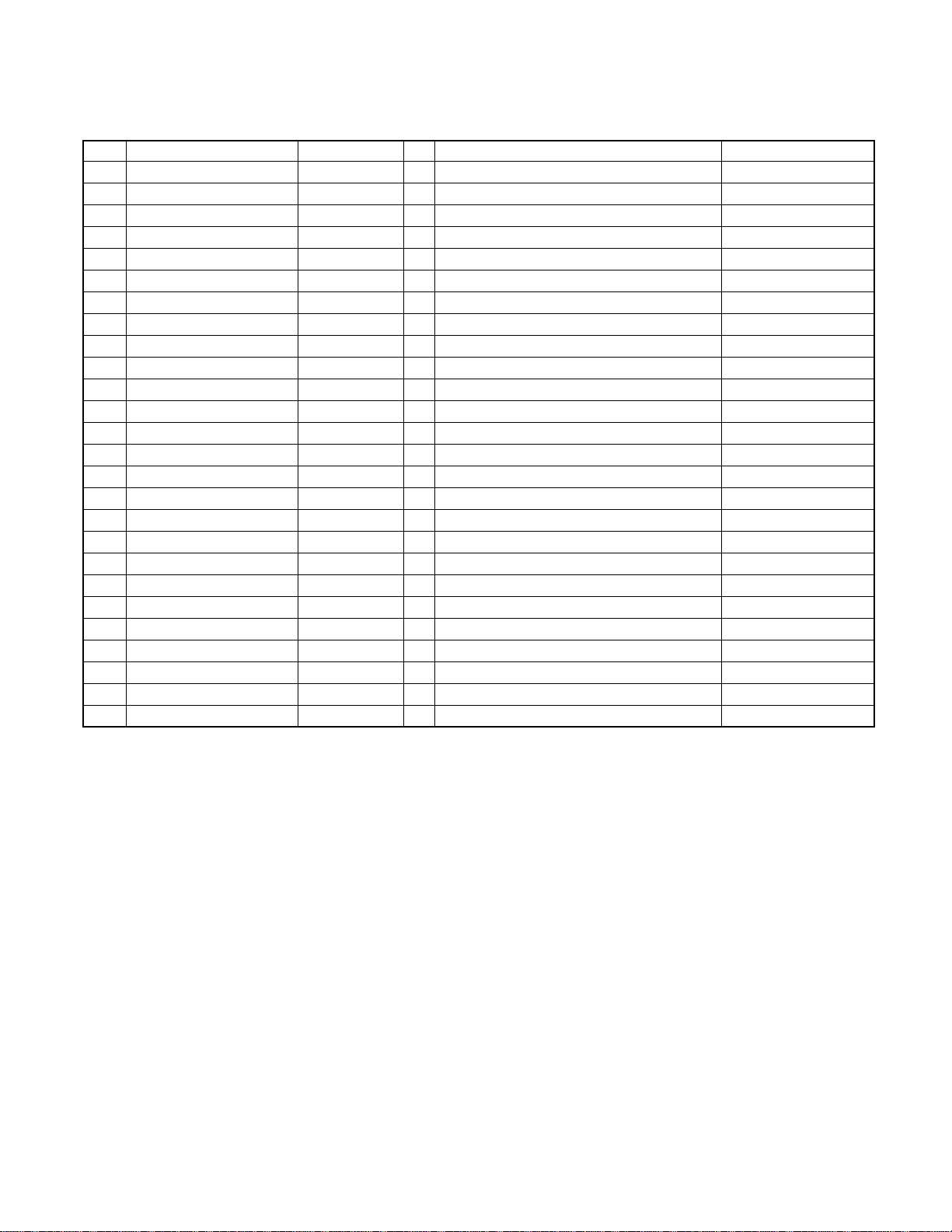

Mechanism Microcomputer M30620MCAA56GP (X32-4800-00 : IC1)

Pin Pin Name Function I/O Description Processing Operation

1~5 NC O –

6 BYTE BYTE I Switching Bus width 8Bit/16Bit H

7 CNVss CNVss I – L

8,9 NC O –

10 RESET RESET I Reset terminal L: Reset, H: Normal

11 Xout Xout O Clock output –

12 Vss Vss – – –

13 Xin Xin I Clock input –

14 Vcc Vcc – – –

15 P85/NMI NMI I L: Interrupt, H: Normal

16 P84/INT2 INT3 I Servo DSP (Processor section) interrupt terminal L: Interrupt, H: Normal

17 P83/INT1 INT2 I Servo DSP (Decoder section) interrupt terminal L: Interrupt, H: Normal

18 P82/INT0 INT1 I Servo DSP (ATAP section) interrupt terminal L: Interrupt, H: Normal

19,20 NC O –

21 P77/TA3IN DCS O DAC chip selection L: Select

22 P76/TA3OUT PD O Ambient IC resetting L: Rest, H: Normal

23 P75/TA2IN/W ML O DAC micon communication data latch line H: Latch

24 P74/TA2OUT/W MC O DAC micon communication clock line –

25 P73/CTS2/TA1IN/V MD O DAC micon communication data line –

26 P72/CLK2/TA1OUT/V NC O – L

27

P71/RxD2/SCL/TA0IN/TB5IN

28 P70/TxD2/SDAT/TA0OUT I2C_DATA I/O For mechanical control communication (data) –

29 P67/TxD1 MP3_I2C_DATA I/O For STA013 control communication (data) –

30 P66/RxD1 R O For flush writing L

31 P65/CLK1 MP3_I2C_CLK I/O F or STA013 control communication (clock) –

32 P64/CTS1/RS1/CLKS1 W O For flush writing L

33 P63TxD0 MP3_DATA O For MP3 data transmission (data) –

34 P62/RxD0 NC O – L

35 P61/CLK0 MP3_CLK O For MP3 data transmission (clock) –

36 P60/CTS0/RTS0 MP3_REQ I MP3 data request –

37 P57/RDY/CLKOUT WAIT I Multiplex path wait terminal L: Busy, H: Ready

38 P56/ALE ALE O For muliplex bus –

39 P55/HOLD HOLD I For flush writing L

40 P54/HLDA HLDA O – L

41 P53/BCLK NC O – L

42 P52/RD RDM O For multiplex bus –

43 P51/WRH/BHE NC O L

44 P50/WRL/WR WRM O For multiplex bus –

45 P47/CS3 CS3 O M24B chip selection L: Select

46~53 NC O –

54 P36/A14 MUTE-R O Mute (right) terminal L: Mute

55 P35/A13 MUTE-L O Mute (left) terminal L: Mute

56 P34/A12 LDON O Laser On/Off terminal L: Off, H: On

57 P33/A11 MP3/CD O CD-DA/MP3 switching terminal L: CD-DA, H: MP3

58 P32/A10 PON O Ambient IC power control terminal L: Off, H: On

59 P31/A9 CDRW O RW switching terminal H: RW, L: Other

60 Vcc Vcc – – –

61 P30/A8 (/–/D7) NC O – L

62 Vss Vss – – –

I2C_CLK I/O For mechanical control communication (Clock) –

11

Z919

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin Pin Name Function I/O Description Processing Operation

63 P27/A7 (/D7/D6) AD7 I/O Address/Data (7 Bit) Line –

64 P26/A6 (/D6/D5) AD6 I/O Address/Data (6 Bit) Line

65 P25/A5 (/D5/D4) AD5 I/O Address/Data (5 Bit) Line

66 P24/A4 (/D4/D3) AD4 I/O Address/Data (4 Bit) Line

67 P23/A3 (/D3/D2) AD3 I/O Address/Data (3 Bit) Line

68 P22/A2 (/D2/D1) AD2 I/O Address/Data (2 Bit) Line

69 P21/A1 (/D1/D0) AD1 I/O Address/Data (1 Bit) Line

70 P20/A0 (/D0/–) AD0 i/O Address/Data (0 Bit) Line

71 P17/D15/INT5 RFOK I RFOK interrupt terminal (Not Used) L: Interrupt, H: Normal

72 P16/D14/INT4 MSTOP I MSTOP etection terminal L: Interrupt, H: Normal

73 P15/D13/INT3 INT4 I L: Interrupt, H: Normal

74~78 NC O –

79 P07/D7 T3 I

80 P06/D6 T2 I

81 P05/D5 T1 I

82 P04/D4 EMPH I Emphasis On/Off L: Off, H: On

83 P03/D3 RFOK I RFOK terminal L: NG, H: OK

84 P02/D2 NC O – L

85 P01/D1 SW3 I Internal track detection switch L: On, H: Off

86 P00/D0 DETECT I Detrack amount L: DETECT

87~93 NC O –

94 P100/AN0 AGND – – –

95 Vss NC O – L

96 VREF NC – – L

97 AVcc AVcc – – –

98~100

NC O –

Test port for testing by those in charge of electricity

Test port for testing by those in charge of electricity

Test port for testing by those in charge of electricity

L

L

L

12

CIRCUIT DESCRIPTION (MP3)

Z919

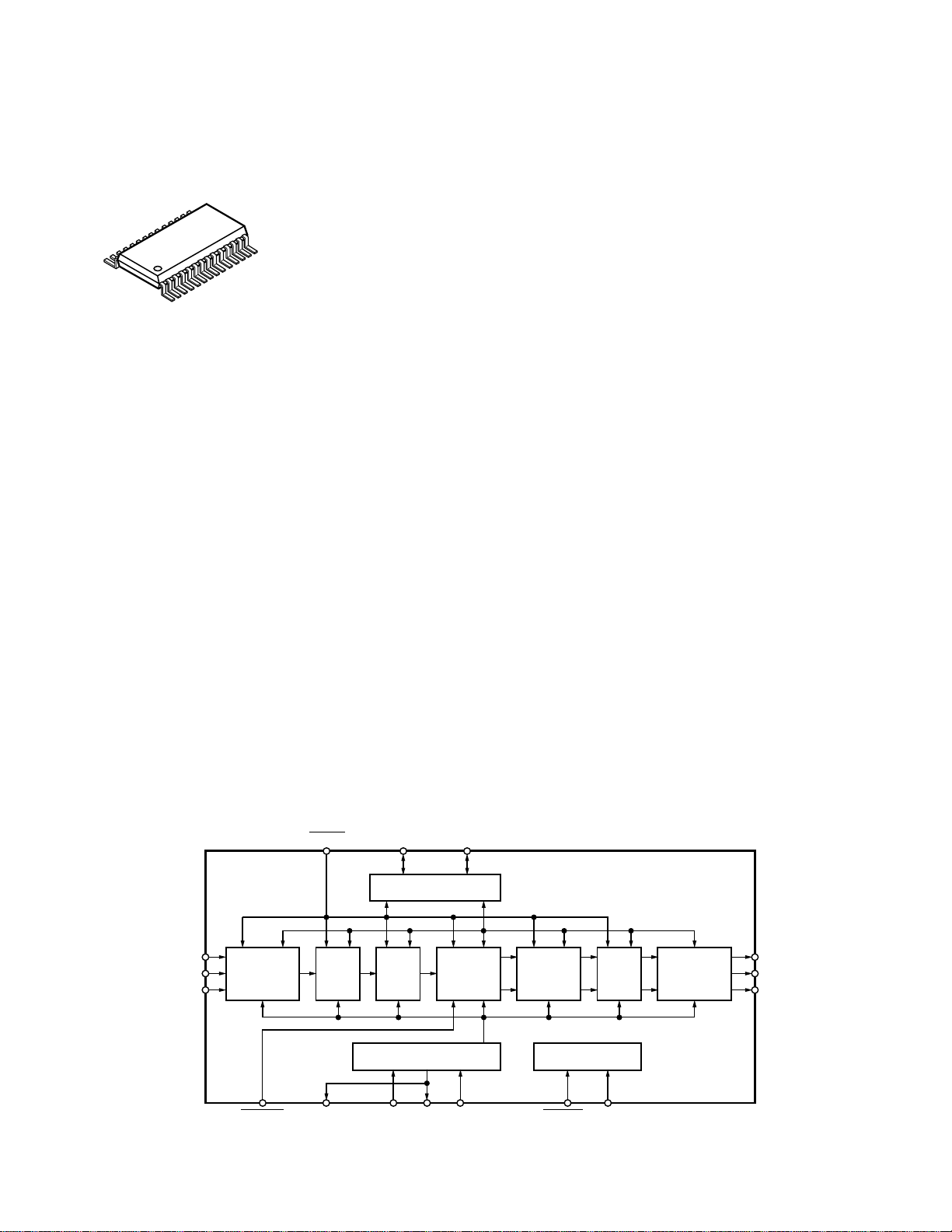

MP3 DSP IC : STA013 (X32-4800 : IC5)

OUT SIDE VIEW

SINGLE CHIP MPEG2 LAYER 3 DECODER SUPPORT-

ING.

Note (Z919 is guaranteed to the MPEG 1.0 Layer III.)

• All features specified for Layer III in ISO/IEC11172-3

(MPEG 1 Audio)

• All features specified for Layer III in ISO/IEC13818-3.2

(MPEG 2 Audio)

• Lower sampling frequencies syntax extension, (not specified by ISO) called MPEG2.5

DECODES LAYER III STEREO CHANNELS , DU AL CHAN-

NEL, SINGLE CHANNEL (MONO)

SUPPORTING ALL THE MPEG 1 & 2 SAMPLING FRE-

QUENCIES AND THE EXTENSION TO MPEG 2.5: 48,

44.1, 32, 24, 22.05, 16, 12, 11.025, 8kHz

ACCEPTS MPEG 2.5 LAYER III ELEMENTARY COM-

PRESSED BIT STREAM WITH DATA RATE FROM 8 Kbit/

s UP TO 320 Kbit/s

DIGIT AL VOLUME CONTROL

DIGITAL BASS & TREBLE CONTROL

SERIAL BITSTREAM INPUT INTERFACE

ANCILLARY DATA EXTRACTION VIA I2C INTERFACE

SERIAL PCM OUTPUT INTERFACE (I2C AND OTHER

FORMATS)

PLL FOR INTERNAL CLOCK AND FOR OUTPUT PCM

CLOCK GENERATION

LOW POWER CONSUMPTION: 85mW AT 2.4V

CRC CHECK AND SYNCHRONISATION ERROR DE-

TECTION WITH SOFTWARE INDICATORS

I2C CONTROL BUS

LOW POWER 3.3V CMOS TECHNOLOGY

10MHz,14.31818 MHz, OR 14.7456MHz EXTERNAL IN-

PUT CLOCK OR BUILT-IN INDUSTRY STANDARD XTAL

OSCILLATOR DIFFERENT FREQUENCIES MAY BE

SUPPORTED UPON REQUEST TO STM

Note Z919 : 10MHz

APPLICATIONS

PC SOUND CARDS

MULTIMEDIA PLAYERS

DESCRIPTION

The STA013 is a fully integrated high flexibility MPEG Layer

III Audio Decoder, capable of decoding Layer III compressed

elementary streams, as specified in MPEG 1 and MPEG 2

ISO standards.The device decoders also elementary streams

compressed by using low sampling rates, as specified by

MPEG 2.5.

STA013 receives the input data through a Serial Input

Interface.The decoded signal is a stereo,mono, or dual channel digital output that can be sent directly to a D/A converter,

by the PCM Output Interface.This interface is software programmable to adapt the STA013 digital output to the most

common DACs architectures used on the market.

The functional STA013 chip partitioning is described in Fig. 1.

SDI

SCKR

BIT_EN

RESET SDA SCL

SERIAL

6

INPUT

7

INTERFACE

828212012 2425

SRC INT OUT_CLK/

26

BUFFER

SYSTEM & AUDIO CLOCKS

DATA_REQ

34

I2C CONTROL

MPEG 2.5

PARSER

XTI XTO OCLK TESTEN

LAYER III

DECODER

CORE

CHANNEL

CONFIG.&

VOLUME

CONTROL

TEST INTERFACE

OUTPUT

BUFFER

SCANEN

Fig. 1 Block diagram: MPEG 2.5 Layer III Decoder hardware Partitioning

PCM

OUTPUT

INTERFACE

10

11

95

SDO

SCKT

LRCKT

13

Loading...

Loading...